不揮発性半導体記憶装置

【課題】非選択メモリセルに流れる逆方向電流を低減させた不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、複数のメモリセルを有するメモリセルアレイと、選択第1配線に選択第1配線電圧を供給し、非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、アクセス対象となるメモリセルに接続された第2配線である選択第2配線に選択第2配線電圧を供給し、その他の第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路とを備え、メモリセルは、第1ダイオードのアノード側に第2配線が接続され、第1ダイオードのカソード側に第1配線が接続され、メモリセルアレイは、第2配線制御回路及びメモリセル間の第2配線に挿入され、第2配線制御回路側をアノード、メモリセル側をカソードとする第2ダイオードを有することを特徴とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、複数のメモリセルを有するメモリセルアレイと、選択第1配線に選択第1配線電圧を供給し、非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、アクセス対象となるメモリセルに接続された第2配線である選択第2配線に選択第2配線電圧を供給し、その他の第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路とを備え、メモリセルは、第1ダイオードのアノード側に第2配線が接続され、第1ダイオードのカソード側に第1配線が接続され、メモリセルアレイは、第2配線制御回路及びメモリセル間の第2配線に挿入され、第2配線制御回路側をアノード、メモリセル側をカソードとする第2ダイオードを有することを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

実施形態は、不揮発性半導体記憶装置に関する。

【背景技術】

【0002】

近年、クロスポイント型のメモリセルに、酸化膜の上下を電極で挟んだ構造を持つReRAM(Resistive RAM)を用いた不揮発性半導体記憶装置が注目されている。このメモリセルは、ReRAMとダイオード等の整流素子とを組み合わせたものがある。

【0003】

このメモリセルの動作としては、酸化膜の上下電極に所定のセット電圧が印加されることで酸化膜の抵抗値が低くなるセット動作と、所定のリセット電圧が印加されることで酸化膜の抵抗値が高くなるリセット動作がある。また、初期工程においては、これらセット動作及びリセット動作を可能するために酸化膜に電流パスを形成するフォーミングを実行する必要もある。

【0004】

所定の選択メモリセルにこれら動作或いはフォーミングを実行する場合、他の非選択メモリセルがこれら動作或いはフォーミングが起こらないように、メモリセルアレイには、非選択メモリセルに対してダイオードの逆方向のバイアスが印加されるようなバイアス状態を作り出す。しかし、この場合、非選択メモリセルでは逆方向電流が発生してしまい、その大きさは、回路規模が大きくなると無視できないものとなる。特に、フォーミングではセット動作、リセット動作よりも大きな逆方向バイアスが印加されるため大きな問題となる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−177387号

【発明の概要】

【発明が解決しようとする課題】

【0006】

非選択メモリセルに流れる逆方向電流を低減させた不揮発性半導体記憶装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

実施形態に係る不揮発性半導体記憶装置は、互いに交差する複数の第1配線及び第2配線、並びに、前記複数の第1配線及び第2配線の各交差部に設けられ、可変抵抗素子及び第1ダイオードを直列接続してなる複数のメモリセルを有するメモリセルアレイと、アクセス対象となる前記メモリセルに接続された前記第1配線である選択第1配線に選択第1配線電圧を供給し、その他の前記第1配線である非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、前記アクセス対象となるメモリセルに接続された前記第2配線である選択第2配線に選択第2配線電圧を供給し、その他の前記第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路とを備え、前記メモリセルは、前記第1ダイオードのアノード側に前記第2配線が接続され、前記第1ダイオードのカソード側に前記第1配線が接続され、前記メモリセルアレイは、前記第2配線制御回路及び前記メモリセル間の前記第2配線に挿入され、前記第2配線制御回路側をアノード、前記メモリセル側をカソードとする第2ダイオードを有することを特徴とする。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態に係る不揮発性半導体記憶装置のブロック図である。

【図2】本実施形態に係る不揮発性半導体記憶装置のメモリセルアレイの一部の斜視図である。

【図3】図2におけるI−I´線で切断して矢印方向に見たメモリセル1個分の断面図である。

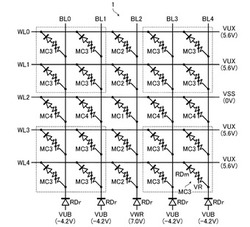

【図4】本実施形態に係る不揮発性半導体記憶装置のメモリセルアレイの回路図及びフォーミング時のメモリセルアレイのバイアス状態を示す図である。

【図5】図4に示すメモリセルのバイアス状態を見易くした等価回路図である。

【図6】本実施形態に係る不揮発性半導体記憶装置におけるフォーミング時の非選択メモリセルに流れる逆方向電流の低減効果を説明する図である。

【図7】本実施形態に係る不揮発性半導体記憶装置の断面図の一例である。

【図8】本実施形態に係る不揮発性半導体記憶装置の断面図の他の例である。

【図9】本実施形態に係る不揮発性半導体記憶装置の断面図の他の例である。

【図10】第2の実施形態に係る不揮発性半導体記憶装置の断面図の一例である。

【図11】本実施形態に係る不揮発性半導体記憶装置の断面図の他の例である。

【図12】第3の実施形態に係る不揮発性半導体記憶装置の断面図の一例である。

【図13】比較例に係る不揮発性半導体記憶装置のメモリセルアレイの回路図及びフォーミング時のメモリセルアレイのバイアス状態を示す図である。

【図14】図13に示すメモリセルのバイアス状態を見易くした等価回路図である。

【発明を実施するための形態】

【0009】

以下、図面を参照しながら実施形態に係る不揮発性半導体記憶装置について説明する。

【0010】

[第1の実施形態]

<全体構成>

図1は、第1の実施形態に係る不揮発性半導体記憶装置のブロック図である。

この不揮発性半導体記憶装置は、後述するReRAM(可変抵抗素子)を使用したメモリセルをマトリクス状に配置したメモリセルアレイ1を備える。メモリセルアレイ1のビット線BL方向に隣接する位置には、メモリセルアレイ1のビット線BLを制御し、メモリセルへのデータ書き込み及びメモリセルからのデータ読み出しを行うカラム制御回路2(第2配線制御回路)が設けられている。また、メモリセルアレイ1のワード線WL方向に隣接する位置には、メモリセルアレイ1のワード線WLを選択し、メモリセルへのデータ書き込み及びメモリセルからのデータ読み出しに必要な電圧を供給するロウ制御回路3(第1配線制御回路)が設けられている。なお、カラム制御回路2及びロウ制御回路3はデータ書込み部に含まれる。

【0011】

データ入出力バッファ4は、図示しない外部のホストにI/O線を介して接続され、書き込みデータの受け取り、読み出しデータの出力、アドレスデータやコマンドデータの受け取りを行う。データ入出力バッファ4は、受け取った書き込みデータをカラム制御回路2に送り、カラム制御回路2から読み出したデータを受け取って外部に出力する。外部からデータ入出力バッファ4に供給されたアドレスは、アドレスレジスタ5を介してカラム制御回路2及びロウ制御回路3に送られる。また、ホストからデータ入出力バッファ4に供給されたコマンドは、コマンド・インタフェース6に送られる。コマンド・インタフェース6は、ホストからの外部制御信号を受け、データ入出力バッファ4に入力されたデータが書き込みデータかコマンドかアドレスかを判断し、コマンドであれば受け取りコマンド信号としてステートマシン7に転送する。ステートマシン7は、この不揮発性半導体記憶装置全体の管理を行うもので、ホストからのコマンドを受け付け、読み出し、書き込み、データの入出力管理等を行う。また、外部のホストは、ステートマシン7が管理するステータス情報を受け取り、動作結果を判断することも可能である。このステータス情報は書き込みの制御にも利用される。

【0012】

また、ステートマシン7によってパルスジェネレータ9が制御される。この制御により、パルスジェネレータ9は任意の電圧、任意のタイミングのパルスを出力することが可能となる。具体的には、ステートマシン7が、外部から与えられたアドレスをアドレスレジスタ5を介して入力し、どのメモリセルへのアクセスかを判定し、そのメモリセルに対応するパラメータを用いて、パルスジェネレータ9からのパルスの高さ・幅を制御する。ここで、形成されたパルスはカラム制御回路2及びロウ制御回路3で選択された任意の配線へ転送することが可能である。

【0013】

なお、メモリセルアレイ1以外の周辺回路はメモリセルアレイ1の直下のシリコン基板に形成可能であり、これにより、この半導体記憶装置のチップ面積はほぼ、メモリセルアレイ1の面積に等しくすることも可能である。

【0014】

<メモリセル及びメモリセルアレイ>

図2は、メモリセルアレイ1の一部の斜視図であり、図3は、図2におけるI−I´線で切断して矢印方向に見たメモリセル1つ分の断面図である。

【0015】

複数本のワード線WL0〜WL2(第1配線)が平行に配設され、これと交差して複数本のビット線BL0〜BL2(第2配線)が平行に配設され、これらの各交差部に両配線に挟まれるようにメモリセルMCが配置される。ワード線WL及びビット線BLは、熱に強く、且つ抵抗値の低い材料が望ましく、例えばW、WSi、NiSi、CoSi等を用いることができる。

【0016】

メモリセルMCは、図3に示すように、可変抵抗素子VRと非オーミック素子NOの直列接続回路からなる。

【0017】

可変抵抗素子VRとしては、電圧印加によって、電流、熱、化学エネルギ等を介して抵抗値を変化させることができるもので、上下にバリアメタル及び接着層として機能する電極EL1、EL2が配置される。電極材としては、Pt、Au、Ag、TiAlN、SrRuO、Ru、RuN、Ir、Co、Ti、TiN、TaN、LaNiO、Al、PtIrOx、PtRhOx、Rh/TaAlN等が用いられる。また、配向性を一様にするようなメタル膜の挿入も可能である。さらに、別途バッファ層、バリアメタル層、接着層等を挿入することも可能である。

【0018】

可変抵抗素子VRは、遷移元素となる陽イオンを含む複合化合物であって陽イオンの移動により抵抗値が変化するもの(ReRAM)を用いることができる。

【0019】

<セット動作、リセット動作、フォーミング>

次に、メモリセルMCの動作について簡単に説明しておく。ここでは、非オーミック素子NOとしてダイオードを用いたユニポーラ動作をするメモリセルMCについて説明する。なお、ここで説明する動作は、一例であって、物質によって様々な動作が考えられることに留意されたい。

【0020】

このユニポーラ動作をするメモリセルMCの場合、メモリセルMCに印加する電圧の極性を切り替えることなく、電圧値と電圧印加時間を制御することによって、可変抵抗素子VRの抵抗状態を切り替えることができる。以下、高抵抗状態の可変抵抗素子VRを低抵抗状態にする動作を「セット動作」、低抵抗状態の可変抵抗素子VRを高抵抗状態にする動作を「リセット動作」と呼ぶ。

【0021】

セット動作では、可変抵抗素子VRに対して、例えば1.5Vの程度の電圧(以下、「セット電圧」と呼ぶ)、10nA程度の電流を10〜100ns程度の時間印加する。このように、可変抵抗素子VRに高電圧を印加することで可変抵抗素子VR内部のカチオン(正電荷イオン)の移動が起こり、絶縁状態の物質が電気化学ポテンシャル的に(準)安定な導電体物質の直列結合の状態に相変化する。その結果、可変抵抗素子VRの抵抗状態が、高抵抗状態から低抵抗状態へと遷移する。

【0022】

一方、リセット動作では、可変抵抗素子VRに対して、例えば0.6Vの電圧(以下、「リセット電圧」と呼ぶ)、1〜10μA程度の電流を500n〜2μs程度の時間印加する。このように、可変抵抗素子VRに長時間、低電圧を印加すると可変抵抗素子VR内部でジュール熱が発生し、これによって、原子が熱拡散して熱平衡状態に変化する。その結果、可変抵抗素子VRの抵抗状態が、低抵抗状態から高抵抗状態へと遷移する。

【0023】

ところで、製造直後の可変抵抗素子VRは、抵抗値が変化しない定常的な高抵抗状態となっている。そのため、可変抵抗素子VRに上記セット動作或いはリセット動作をさせるために、可変抵抗素子VRに対してフォーミングと呼ばれる処理を施す必要がある。このフォーミングは、可変抵抗素子VRの上下の電極EL1、EL2間に所定の電圧(以下、「フォーミング電圧」と呼ぶ)を印加し、可変抵抗素子VRにフィラメントパスと呼ばれる低抵抗領域を形成することをいう。そして、この際用いられるフォーミング電圧は、セット電圧やリセット電圧よりも遙かに高く、例えば5〜10Vの大きさとなる。

【0024】

次に、本実施形態の理解を容易にするために、比較例に係る不揮発性半導体記憶装置におけるフォーミングについて説明しておく。

【0025】

図13は、比較例に係る不揮発性半導体記憶装置におけるフォーミング時のメモリセルアレイのバイアス状態を示す図であり、図14は、図13中に示すメモリセルMC1〜MC4のバイアス状態を見易くした等価回路図である。

【0026】

図13には、ワード線WL0〜WL4(第1配線)、ビット線BL0〜BL4(第2配線)、並びに、これらワード線WL及びビット線BLの各交差部に設けられたメモリセルMCが示されている。また、メモリセルMCは、直列接続された可変抵抗素子VRとダイオードRDmからなる。ダイオードRDmのカソード及びアノードは、それぞれビット線BL及びワード線WLに接続されている。したがって、ワード線WLの電圧よりもビット線BLの電圧が高い場合、メモリセルMCには順方向バイアスが掛かり、順方向電流が流れる。逆に、ビット線BLの電圧よりもワード線WLの電圧が高い場合、メモリセルMCには逆方向バイアスが掛かり、逆方向電流が流れる。

【0027】

以上示した構成のメモリセルアレイについて、以下では、ワード線WL2及びビット線BL2に接続されたメモリセルMCをフォーミングする場合を例に説明する。以下において、フォーミング対象(アクセス対象)となるメモリセルMCを「選択メモリセル」、その他のメモリセルMCを「非選択メモリセル」、選択メモリセルに接続されたワード線WLを「選択ワード線」(選択第1配線)、その他のワード線WLを「非選択ワード線」(非選択第1配線)、選択メモリセルに接続されたビット線BLを「選択ビット線」(選択第2配線)、その他のビット線BLを「非選択ビット線」(非選択第2配線)と呼ぶ。したがって、本例では、選択ワード線がワード線WL2、選択ビット線がビット線BL2となる。

【0028】

選択ワード線WL2及び選択ビット線BL2間に接続された選択メモリセルMC2をフォーミングする場合、選択ビット線BLに6.2Vのフォーミング電圧VWR、選択ワード線WLに接地電圧VSS(0V)を印加すると共に、非選択ビット線BLに0.5Vの非選択ビット線電圧VUB、非選択ワード線WLに5.7Vの非選択ワード線電圧VUXを印加する。

【0029】

ここで、ダイオードRDmを一般的な電圧−電流特性を持つ素子であると仮定し、メモリセルMC1、MC2、MC3及びMC4のダイオードRDmにおける電圧降下を、それぞれ、0.9V、0.5V、5.2V及び0.5Vとすると、選択ワード線WL2及び選択ビット線BL2に接続された選択メモリセルMC1には、フォーミングに必要な6.2Vの順方向バイアスが掛かる。

【0030】

一方、非選択ワード線WL0、WL1、WL3及びWL4並びに選択ビット線BL2に接続された非選択メモリセルMC2には、0.5Vの順方向バイアス、非選択ワード線WL0、WL1、WL3及びWL4並びに非選択ビット線BL0、BL1、BL3及びBL4に接続された非選択メモリセルMC3には、5.2Vの逆方向バイアス、選択ワード線WL2並びに非選択ビット線BL0、BL1、BL3及びBL4に接続された非選択メモリセルMC4には、0.5Vの順方向バイアスがそれぞれ掛かる。但し、これらメモリセルMC2〜MC4に掛かるバイアスは、フォーミングできない程度の大きさである。

【0031】

つまり、メモリセルアレイを図13に示すようなバイアス状態にすることで、選択メモリセルMC1のみをフォーミングすることができる。

【0032】

しかし、図13に示す場合、図中点線で囲まれた非選択メモリセルMC3については、5.7Vもの逆方向バイアスが掛かり、大きな逆方向電流が流れてしまう。しかも、メモリセルアレイを構成するメモリセルMCの大半が非選択メモリセルMC3になることを考えるとその影響は大きく、特に大規模なメモリセルアレイの場合、消費電力として無視できない大きさになる。このこと程度の違いはあるにせよセット動作時或いはリセット動作時においても同様のことが言える。

【0033】

そこで、本実施形態では、メモリセルMC3に掛かる逆方向バイアスを抑制するようにビット線BLに対してダイオードを挿入させる。なお、このダイオードとメモリセルMCのダイオードRDmを区別するため、メモリセルMCのダイオードRDmを「メモリセル内ダイオード」(第1ダイオード)、ビット線BLに挿入させるダイオードを「逆方向電流低減用ダイオード」(第2ダイオード)と呼ぶことにする。

【0034】

図4は、本実施形態に係る不揮発性半導体記憶装置のメモリセルアレイ1の等価回路図であり、フォーミング時のバイアス状態も併せて示している。また、図5は、図4中に示すメモリセルMC1〜MC4のバイアス状態を見易くした等価回路図である。

【0035】

本実施形態に係る不揮発性半導体記憶装置のメモリセルアレイ1は、図13に示すメモリセルアレイの複数のビット線BLに対して、それぞれ電圧供給元であるカラム制御回路2側をアノード、メモリセルMC側をカソードとする逆方向電流低減用ダイオードRDrが挿入されている。

【0036】

本実施形態のフォーミングの場合、選択ビット線BLに例えば7.0Vのフォーミング電圧VWR(選択第2配線電圧)、選択ワード線WLに例えば接地電圧VSS(0V)(選択第1配線電圧)を印加すると共に、非選択ビット線BLに例えば−4.2Vの非選択ビット線電圧VUB(非選択第2配線電圧)、非選択ワード線WLに例えば5.6Vの非選択ワード線電圧VUX(非選択第1配線電圧)を印加する。

【0037】

この場合、逆方向電流低減用ダイオードRDrの電圧−電流特性をメモリセル内ダイオードRDmの電圧−電流特性と同程度であると仮定すると、メモリセルMC1、MC2、MC3及びMC4のメモリセル内ダイオードRDmにおける電圧降下は、それぞれ、例えば0.9V、0.5V、4.95V及び0.65Vとなる。また、選択ビット線BL及び非選択ビット線BLに挿入された逆方向電流低減用ダイオードRDrは、それぞれ、例えば0.9V及び4.85Vとなる。

【0038】

これによって、選択メモリセルMC1には、フォーミングに必要な6.1Vの順方向バイアスが掛かる。

【0039】

一方、非選択メモリセルMC2には、0.5Vの順方向バイアス、非選択メモリセルMC3には、4.95Vの逆方向バイアス、非選択メモリセルMC4には、0.65Vの順方向バイアスがそれぞれ掛かる。

【0040】

つまり、メモリセルアレイ1を図4に示すようなバイアス状態にすることで、比較例と同様に選択メモリセルMC1のみをフォーミングすることができる一方、比較例と比べて非選択メモリセルMC3に掛かる逆方向バイアスと、非選択メモリセルMC3に流れる逆方向電流を低減させることができる。つまり、非選択メモリセルMC3における消費電力を低減させることができる。

【0041】

図6は、本実施形態と比較例におけるメモリセルMC3に流れる逆方向電流を対比させたグラフである。図中左のグラフが比較例におけるメモリセル内ダイオードRDmの電圧−電流特性、図中右のグラフが本実施形態におけるメモリセル内ダイオードRDmの電圧−電流特性を示している。

【0042】

比較例の場合、非選択メモリセルMC3のメモリセル内ダイオードRDmには5.2Vの逆方向バイアスが掛かるため、非選択メモリセルMC3に流れる逆方向電流I1´は、およそ9.64×10−8Aになる。この場合、2K×8Kのメモリセルアレイであれば、非選択メモリセルMC3に流れる総逆方向電流は、9.64×10−8A×(2K×8K−2K−8K+1)=1.62Aとなり、これは回路を破壊してしまうほどの大きさとなる。また、非選択メモリセルMC3における総消費電力は、5.2V×1.62A=8.41Wにもなる。

【0043】

これに対し、本実施形態の場合、非選択メモリセルMC3のメモリセル内ダイオードRDmには、4.95Vの逆方向バイアスしか掛からない。そのため、非選択メモリセルMC3に流れる逆方向電流I1は、およそ5.78×10−8Aになる。この場合、2K×8Kのメモリセルアレイ1であれば、非選択メモリセルMC3に流れる総逆方向電流は、5.78×10−8A×(2K×8K−2K−8K+1)=0.97Aまで抑制される。なお、この逆方向電流I1は、メモリセルMC4に流れる順方向電流I2と、非選択ビット線BLに挿入された逆方向電流低減用ダイオードRDrに流れる逆方向電流I3の和になる。また、非選択メモリセルMC3における総消費電力も、4.95V×0.97A=4.80Wまで抑制される。

【0044】

つまり、本実施形態によれば、非選択メモリセルMC3に流れる逆方向電流を比較例と比べて40%程度削減することができ(図6中白抜き矢印a1)、非選択メモリセルMC3における総消費電力も比較例と比べて43%程度削減することができる。

【0045】

<逆方向電流低減用ダイオードの構造及び形成方法>

次に、逆方向電流低減用ダイオードRDrの構造及び形成方法の例を図7〜図9に示す不揮発性半導体記憶装置の断面図を用いて説明する。

【0046】

図7に示す場合、不揮発性半導体記憶装置は、図示しないP型シリコン基板上に積層されたディープN型ウエル107、このディープN型ウエル107上に設けられたロウ方向に延びる複数の素子分離溝113を備える。また、ディープN型ウエル107上の2つの素子分離溝113間に形成されたP型ウエル103を備える。

【0047】

このP型ウエル103上部には、ドナー(第1導電型不純物)が高濃度にドープされたN型高濃度領域101(第1導電型不純物領域)と、アクセプタ(第2導電型不純物領域)が高濃度にドープされたP型高濃度領域102(第2導電型不純物領域)が形成されている。このうちN型高濃度領域101は、P型ウエル103との関係で逆方向電流低減用ダイオードRDrを構成するP+/Nの片側階段接合を形成する。

【0048】

また、P型ウエル103上には、カラム制御回路2からメモリセルMCへ延びるビット線BLとなる金属配線が形成されている。この金属配線は、N型高濃度領域101及びP型高濃度領域102間の位置において、カラム制御回路2側に延びる部分金属配線104aと、メモリセルMC側に延びる部分金属配線104bとに分断されている。そして、部分金属配線104a及び104bは、積層方向に延びるビア105を介してP型高濃度領域102及びN型高濃度領域101にそれぞれ接続されている。

【0049】

次に、図7に示す構造の製造方法について説明する。

始めに、図示しないP型シリコン基板上にディープN型ウエル107を形成した後、ロウ方向に延びる複数の素子分離溝113を形成する。

【0050】

続けて、素子分離溝113間のディープN型ウエル107中にアクセプタをドープしてP型ウエル103を形成する。

【0051】

続けて、P型ウエル103中にドナーを高濃度にドープしてN型高濃度領域101を形成する。これによって、N型高濃度領域101及びP型ウエル103からN+/Pの片側段階接合が形成される。なお、この工程は、カラム制御回路2等のMOSFETのソース・ドレイン形成時に同時に行うこともできる。

【0052】

続けて、比較的高い逆耐圧の逆方向電流低減用ダイオードRDrを実現するため、N型高濃度領域101から十分離れた領域にドナーを高濃度でドープしてP型高濃度領域102を形成する。

【0053】

最後に、N型高濃度領域101、P型高濃度領域102、P型ウエル103及び素子分離溝113上に図示しない層間絶縁膜を形成する。その後、この層間絶縁膜を貫通するように、N型高濃度領域101及びP型高濃度領域102に接続する複数のビア105を形成し、これらビア105に接続する部分金属配線104b及び104aを形成すれば、図7に示す構造を作ることができる。

【0054】

図8は、N型ウエル106中にP+/Nの片側階段接合が形成された例である。つまり、図8に示す不揮発性半導体記憶装置の場合、図示しないP型シリコン基板上の2つの素子分離溝113間にN型ウエル106が形成されており、このN型ウエル106上部にN型高濃度領域101(第1導電型不純物領域)とP型高濃度領域102(第2導電型不純物領域)が形成されている。そして、P型高濃度領域102とN型ウエル106との接合によって、逆方向電流低減用ダイオードRDrを構成するP+/Nの片側階段接合が形成されている。

【0055】

図9は、ウエル同士が接合されてPN接合が形成された例である。つまり、図9に示す不揮発性半導体記憶装置の場合、2つの素子分離溝113間のディープN型ウエル107上にロウ方向にストライプ状に延びるP型ウエル103及びN型ウエル106が形成されている。また、これらP型ウエル103上部及びN型ウエル106上部には、それぞれP型高濃度領域102(第2導電型領域)及びN型高濃度領域101(第1導電型領域)が形成されている。そして、P型ウエル103とN型ウエル106との接合によって、逆方向電流低減用ダイオードRDrを構成するPN接合が形成されている。

【0056】

<まとめ>

以上、本実施形態によれば、カラム制御回路及びメモリセル間に逆方向電流低減用ダイオードを挿入させることで、比較例と比べて、非選択ワード線及び非選択ビット線に接続された非選択メモリセルに流れる逆方向電流と、この非選択メモリセルにおける消費電力を大幅に低減させることができる。

【0057】

[第2の実施形態]

第1の実施形態で説明した逆方向電流低減用ダイオードの構造及び形成方法は、いずれも逆方向電流低減用ダイオードを他の素子と別個独立に設けるというものであった。これに対し、第2の実施形態では、カラム制御回路等の周辺回路を構成するMOSFETのソース又はドレインとなる不純物高濃度領域と逆方向電流低減用ダイオードのアノード又はカソードとなる不純物高濃度領域とを共通に形成させた構造及び形成方法の例について、図10及び図11に示す不揮発性半導体記憶装置の断面図を用いて説明する。

【0058】

図10に示す場合、不揮発性半導体記憶装置は、P型シリコン基板208、このP型シリコン基板208上の一部に形成されたディープN型ウエル207、このディープN型ウエル207上に形成されたP型ウエル203、並びに、このP型ウエル203の両側に接合して形成されたN型ウエル206を備える。

【0059】

これらのうちP型ウエル203上部には、ドナー(第1導電型不純物)が高濃度にドープされた2つのN型高濃度領域201(第1導電型不純物領域)が形成されている。これら2つのN型高濃度領域201は、N型MOSFETのソースおよびドレインを構成するものであり、これら2つのN型高濃度領域201の間のP型ウエル203上には、ゲート酸化膜211を介してスペーサ210に挟まれたN型MOSFETのゲートとなるポリシリコン209が形成されている。また、N型ウエル206上部には、アクセプタ(第2導電型不純物)が高濃度にドープされたP型高濃度領域202(第2導電型不純物領域)が形成されている。そして、このP型高濃度領域202は、N型ウエル202との関係で逆方向電流低減用ダイオードRDrを構成するP+/Nの片側階段接合を形成する。なお、N型高濃度領域201とP型高濃度領域202を十分に離して配置すれば、逆方向電流低減用ダイオードRDrの逆耐圧を高くすることができる。

次に、図10に示す構造の製造方法について説明する。

【0060】

始めに、ディープN型ウエル107形成後のP型シリコン基板208中にアクセプタをドープしてP型ウエル203を形成する共に、このP型ウエル203に接する領域にドナーをドープしてN型ウエル206を形成する。

【0061】

続いて、P型ウエル203上にゲート酸化膜211と、ポリシリコン209を形成した後、N型MOSFETのゲートを加工する。

【0062】

続いて、P型ウエル203中のゲートの両側の領域にドナーを高濃度にドープし、2つのN型高濃度領域201を形成する。

【0063】

続いて、P型ウエル203に隣接するN型ウエル202中にP型イオンを注入しP型高濃度領域202を形成する。これによって、P型高濃度領域202及びN型ウエル206からP+/Nの片側階段接合が形成される。

【0064】

最後に、N型高濃度領域201、P型高濃度領域202等に接続されるビア205と、このビア205に接続される必要な金属配線を形成すれば図10に示す構造を作ることができる。

【0065】

図11は、P型MOSFETのソース及びドレインとなるP型高濃度領域と逆方向電流低減用ダイオードのアノードとなるP型高濃度領域とを共通に形成させた例である。つまり、図11に示す不揮発性半導体装置の場合、N型ウエル208上部にアクセプタ(第1導電型不純物)を高濃度にドープさせた2つのP型高濃度領域202(第1導電型不純物領域)が形成されている。これら2つのP型不純物領域202は、それぞれP型MOSFETのソース及びドレインとなる。また、P型ウエル203上部には、ドナー(第2導電型不純物)を高濃度にドープさせたN型高濃度領域201(第2導電型不純物領域)が形成されている。このN型高濃度領域201は、逆方向電流低減用ダイオードRDrのカソードとなる。そして、N型高濃度領域201及びP型ウエル203との接合によって、逆方向電流低減用ダイオードRDrを構成するN+/Pの片側階段接合が形成される。

【0066】

なお、図11に示す不揮発性半導体記憶装置の場合、P型MOSFETのドレイン側のP型ウエル203は、P型MOSFETがオフ状態の時、接地電圧VSSに駆動させる必要がある。したがって、この不揮発性半導体記憶装置には、P型ウエル203と接地電圧VSSとを接続するためのトランジスタ214が設けられている。そして、このトランジスタ214は、P型MOSFETがオン状態の時にオフ状態、P型MOSFETがオフ状態の時にオン状態となるように制御信号CNTで制御される。

【0067】

本実施形態によれば、第1の実施形態と同様の効果を奏するばかりでなく、周辺回路のMOSFETのソース又はドレインとなる不純物高濃度領域とダイオードのアノード又はカソードとなる不純物高濃度領域とが共通になっているため、第1の実施形態と比べて、チップ面積の小さい不揮発性半導体記憶装置を提供することができる。

【0068】

[第3の実施形態]

第3の実施形態では、逆方向電流低減用ダイオードを横置き型のポリシリコンダイオードとした場合の構造及び形成方法の例について、図12に示す不揮発性半導体記憶装置の断面図を用いて説明する。

【0069】

図12に示す場合、不揮発性半導体記憶装置は、図示しないP型シリコン基板上に形成されたポリシリコン薄膜を備える。このポリシリコン薄膜は、ポリシリコンに対してドナー(第1導電型不純物)を高濃度にドープさせたN型ポリシリコン薄膜311(第1導電型不純物領域)と、ポリシリコンに対してアクセプタ(第2導電型不純物)を高濃度にドープさせたP型ポリシリコン薄膜312(第2導電型不純物領域)からなる。これらN型ポリシリコン薄膜311とP型ポリシリコン薄膜312とは接合しており、これによって逆方向電流低減用ダイオードとなるPN接合が構成されている。また、N型ポリシリコン薄膜311及びP型ポリシリコン薄膜312上には、ビット線BL等の必要な金属配線304がビア305を介して接続されている。

【0070】

次に、図12に示す構造の製造方法について説明する。

始めに、図示しないP型シリコン基板上にポリシリコン薄膜を形成する。この際、ポリシリコン薄膜は、均一の不純物濃度を保てる厚さで成膜することが望まし。但し、順方向電流に関してメモリセル内ダイオードRDmと同等の性能を得るには、後に形成される逆方向電流低減用ダイオードRDrとメモリセル内ダイオードRDmの断面積が同程度になるように、ポリシリコン薄膜の厚さを設定しておく必要がある。同様に、逆方向電流低減用ダイオードRDrの長さは、十分な逆耐圧を確保するのに必要な分(例えば、80nm以上)だけとって形成しておく。

【0071】

続いて、ポリシリコン薄膜の一部に対して、ドナーを高濃度にドープしてN型ポリシリコン薄膜311を形成すると共に、このN型ポリシリコン薄膜311に隣接する領域に対してアクセプタを高濃度にドープしてP型ポリシリコン薄膜312を形成する。なお、N型ポリシリコン薄膜311を形成する際には、リソグラフィでP型ポリシリコン薄膜312となる領域をカバーした上で、ドナーをドープさせる。同様に、P型ポリシリコン薄膜312を形成する際には、リソグラフィでN型ポリシリコン薄膜311となる領域をカバーした上で、アクセプタをドープさせる。また、N型ポリシリコン薄膜311及びP型ポリシリコン薄膜312によって構成されるPN接合は、P型ポリシリコン薄膜312からN型ポリシリコン薄膜311へ向かう方向を非選択メモリセルMC3に掛かる逆方向バイアスが緩和される方向となるように形成する。以上によって逆方向電流低減用ダイオードRDrとなるポリシリコンダイオードが形成される。

【0072】

最後に、ポリシリコン薄膜上に図示しない層間絶縁膜を形成する。その後、この層間絶縁膜を貫通するように、N型ポリシリコン薄膜311及びP型ポリシリコン薄膜312に接続される複数のビア305を形成し、これらビア315に接続される金属配線304を形成すれば、図12に示す構造を作ることができる。

【0073】

本実施形態によれば、逆方向電流低減用ダイオードとしてポリシリコンダイオードを用いた場合であっても、第1及び第2の実施形態と同様の効果を得ることができる。

【0074】

[その他]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【0075】

例えば、上記実施形態では、いずれの場合も、ワード線を第1配線、ビット線を第2配線として説明したが、ビット線を第1配線、ワード線を第2配線とすることもできる。また、第1導電型不純物と第2導電型不純物は互いに入れ替わっても良い。

【0076】

更に、上記実施形態は、主にフォーミングについて説明したが、セット動作時、或いはリセット動作時に非選択メモリセルに逆方向電流が流れる不揮発性半導体記憶装置であれば、上記実施形態をいずれも適用することができる。

【符号の説明】

【0077】

1・・・メモリセルアレイ、2・・・カラム制御回路、3・・・ロウ制御回路、4・・・データ入出力バッファ、5・・・アドレスレジスタ、6・・・コマンド・インタフェース、7・・・ステートマシン、9・・・パルスジェネレータ、101、201・・・N型高濃度領域、102、202・・・P型高濃度領域、103、203・・・P型ウエル、104、304・・・金属配線、105、205、305・・・ビア、106、206・・・N型ウエル、107、207・・・ディープN型ウエル、208・・・P型シリコン基板、209・・・ポリシリコン、210・・・カバー、113・・・素子分離溝、214・・・トランジスタ、311・・・N型ポリシリコン薄膜、312・・・P型ポリシリコン薄膜。

【技術分野】

【0001】

実施形態は、不揮発性半導体記憶装置に関する。

【背景技術】

【0002】

近年、クロスポイント型のメモリセルに、酸化膜の上下を電極で挟んだ構造を持つReRAM(Resistive RAM)を用いた不揮発性半導体記憶装置が注目されている。このメモリセルは、ReRAMとダイオード等の整流素子とを組み合わせたものがある。

【0003】

このメモリセルの動作としては、酸化膜の上下電極に所定のセット電圧が印加されることで酸化膜の抵抗値が低くなるセット動作と、所定のリセット電圧が印加されることで酸化膜の抵抗値が高くなるリセット動作がある。また、初期工程においては、これらセット動作及びリセット動作を可能するために酸化膜に電流パスを形成するフォーミングを実行する必要もある。

【0004】

所定の選択メモリセルにこれら動作或いはフォーミングを実行する場合、他の非選択メモリセルがこれら動作或いはフォーミングが起こらないように、メモリセルアレイには、非選択メモリセルに対してダイオードの逆方向のバイアスが印加されるようなバイアス状態を作り出す。しかし、この場合、非選択メモリセルでは逆方向電流が発生してしまい、その大きさは、回路規模が大きくなると無視できないものとなる。特に、フォーミングではセット動作、リセット動作よりも大きな逆方向バイアスが印加されるため大きな問題となる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−177387号

【発明の概要】

【発明が解決しようとする課題】

【0006】

非選択メモリセルに流れる逆方向電流を低減させた不揮発性半導体記憶装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

実施形態に係る不揮発性半導体記憶装置は、互いに交差する複数の第1配線及び第2配線、並びに、前記複数の第1配線及び第2配線の各交差部に設けられ、可変抵抗素子及び第1ダイオードを直列接続してなる複数のメモリセルを有するメモリセルアレイと、アクセス対象となる前記メモリセルに接続された前記第1配線である選択第1配線に選択第1配線電圧を供給し、その他の前記第1配線である非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、前記アクセス対象となるメモリセルに接続された前記第2配線である選択第2配線に選択第2配線電圧を供給し、その他の前記第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路とを備え、前記メモリセルは、前記第1ダイオードのアノード側に前記第2配線が接続され、前記第1ダイオードのカソード側に前記第1配線が接続され、前記メモリセルアレイは、前記第2配線制御回路及び前記メモリセル間の前記第2配線に挿入され、前記第2配線制御回路側をアノード、前記メモリセル側をカソードとする第2ダイオードを有することを特徴とする。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態に係る不揮発性半導体記憶装置のブロック図である。

【図2】本実施形態に係る不揮発性半導体記憶装置のメモリセルアレイの一部の斜視図である。

【図3】図2におけるI−I´線で切断して矢印方向に見たメモリセル1個分の断面図である。

【図4】本実施形態に係る不揮発性半導体記憶装置のメモリセルアレイの回路図及びフォーミング時のメモリセルアレイのバイアス状態を示す図である。

【図5】図4に示すメモリセルのバイアス状態を見易くした等価回路図である。

【図6】本実施形態に係る不揮発性半導体記憶装置におけるフォーミング時の非選択メモリセルに流れる逆方向電流の低減効果を説明する図である。

【図7】本実施形態に係る不揮発性半導体記憶装置の断面図の一例である。

【図8】本実施形態に係る不揮発性半導体記憶装置の断面図の他の例である。

【図9】本実施形態に係る不揮発性半導体記憶装置の断面図の他の例である。

【図10】第2の実施形態に係る不揮発性半導体記憶装置の断面図の一例である。

【図11】本実施形態に係る不揮発性半導体記憶装置の断面図の他の例である。

【図12】第3の実施形態に係る不揮発性半導体記憶装置の断面図の一例である。

【図13】比較例に係る不揮発性半導体記憶装置のメモリセルアレイの回路図及びフォーミング時のメモリセルアレイのバイアス状態を示す図である。

【図14】図13に示すメモリセルのバイアス状態を見易くした等価回路図である。

【発明を実施するための形態】

【0009】

以下、図面を参照しながら実施形態に係る不揮発性半導体記憶装置について説明する。

【0010】

[第1の実施形態]

<全体構成>

図1は、第1の実施形態に係る不揮発性半導体記憶装置のブロック図である。

この不揮発性半導体記憶装置は、後述するReRAM(可変抵抗素子)を使用したメモリセルをマトリクス状に配置したメモリセルアレイ1を備える。メモリセルアレイ1のビット線BL方向に隣接する位置には、メモリセルアレイ1のビット線BLを制御し、メモリセルへのデータ書き込み及びメモリセルからのデータ読み出しを行うカラム制御回路2(第2配線制御回路)が設けられている。また、メモリセルアレイ1のワード線WL方向に隣接する位置には、メモリセルアレイ1のワード線WLを選択し、メモリセルへのデータ書き込み及びメモリセルからのデータ読み出しに必要な電圧を供給するロウ制御回路3(第1配線制御回路)が設けられている。なお、カラム制御回路2及びロウ制御回路3はデータ書込み部に含まれる。

【0011】

データ入出力バッファ4は、図示しない外部のホストにI/O線を介して接続され、書き込みデータの受け取り、読み出しデータの出力、アドレスデータやコマンドデータの受け取りを行う。データ入出力バッファ4は、受け取った書き込みデータをカラム制御回路2に送り、カラム制御回路2から読み出したデータを受け取って外部に出力する。外部からデータ入出力バッファ4に供給されたアドレスは、アドレスレジスタ5を介してカラム制御回路2及びロウ制御回路3に送られる。また、ホストからデータ入出力バッファ4に供給されたコマンドは、コマンド・インタフェース6に送られる。コマンド・インタフェース6は、ホストからの外部制御信号を受け、データ入出力バッファ4に入力されたデータが書き込みデータかコマンドかアドレスかを判断し、コマンドであれば受け取りコマンド信号としてステートマシン7に転送する。ステートマシン7は、この不揮発性半導体記憶装置全体の管理を行うもので、ホストからのコマンドを受け付け、読み出し、書き込み、データの入出力管理等を行う。また、外部のホストは、ステートマシン7が管理するステータス情報を受け取り、動作結果を判断することも可能である。このステータス情報は書き込みの制御にも利用される。

【0012】

また、ステートマシン7によってパルスジェネレータ9が制御される。この制御により、パルスジェネレータ9は任意の電圧、任意のタイミングのパルスを出力することが可能となる。具体的には、ステートマシン7が、外部から与えられたアドレスをアドレスレジスタ5を介して入力し、どのメモリセルへのアクセスかを判定し、そのメモリセルに対応するパラメータを用いて、パルスジェネレータ9からのパルスの高さ・幅を制御する。ここで、形成されたパルスはカラム制御回路2及びロウ制御回路3で選択された任意の配線へ転送することが可能である。

【0013】

なお、メモリセルアレイ1以外の周辺回路はメモリセルアレイ1の直下のシリコン基板に形成可能であり、これにより、この半導体記憶装置のチップ面積はほぼ、メモリセルアレイ1の面積に等しくすることも可能である。

【0014】

<メモリセル及びメモリセルアレイ>

図2は、メモリセルアレイ1の一部の斜視図であり、図3は、図2におけるI−I´線で切断して矢印方向に見たメモリセル1つ分の断面図である。

【0015】

複数本のワード線WL0〜WL2(第1配線)が平行に配設され、これと交差して複数本のビット線BL0〜BL2(第2配線)が平行に配設され、これらの各交差部に両配線に挟まれるようにメモリセルMCが配置される。ワード線WL及びビット線BLは、熱に強く、且つ抵抗値の低い材料が望ましく、例えばW、WSi、NiSi、CoSi等を用いることができる。

【0016】

メモリセルMCは、図3に示すように、可変抵抗素子VRと非オーミック素子NOの直列接続回路からなる。

【0017】

可変抵抗素子VRとしては、電圧印加によって、電流、熱、化学エネルギ等を介して抵抗値を変化させることができるもので、上下にバリアメタル及び接着層として機能する電極EL1、EL2が配置される。電極材としては、Pt、Au、Ag、TiAlN、SrRuO、Ru、RuN、Ir、Co、Ti、TiN、TaN、LaNiO、Al、PtIrOx、PtRhOx、Rh/TaAlN等が用いられる。また、配向性を一様にするようなメタル膜の挿入も可能である。さらに、別途バッファ層、バリアメタル層、接着層等を挿入することも可能である。

【0018】

可変抵抗素子VRは、遷移元素となる陽イオンを含む複合化合物であって陽イオンの移動により抵抗値が変化するもの(ReRAM)を用いることができる。

【0019】

<セット動作、リセット動作、フォーミング>

次に、メモリセルMCの動作について簡単に説明しておく。ここでは、非オーミック素子NOとしてダイオードを用いたユニポーラ動作をするメモリセルMCについて説明する。なお、ここで説明する動作は、一例であって、物質によって様々な動作が考えられることに留意されたい。

【0020】

このユニポーラ動作をするメモリセルMCの場合、メモリセルMCに印加する電圧の極性を切り替えることなく、電圧値と電圧印加時間を制御することによって、可変抵抗素子VRの抵抗状態を切り替えることができる。以下、高抵抗状態の可変抵抗素子VRを低抵抗状態にする動作を「セット動作」、低抵抗状態の可変抵抗素子VRを高抵抗状態にする動作を「リセット動作」と呼ぶ。

【0021】

セット動作では、可変抵抗素子VRに対して、例えば1.5Vの程度の電圧(以下、「セット電圧」と呼ぶ)、10nA程度の電流を10〜100ns程度の時間印加する。このように、可変抵抗素子VRに高電圧を印加することで可変抵抗素子VR内部のカチオン(正電荷イオン)の移動が起こり、絶縁状態の物質が電気化学ポテンシャル的に(準)安定な導電体物質の直列結合の状態に相変化する。その結果、可変抵抗素子VRの抵抗状態が、高抵抗状態から低抵抗状態へと遷移する。

【0022】

一方、リセット動作では、可変抵抗素子VRに対して、例えば0.6Vの電圧(以下、「リセット電圧」と呼ぶ)、1〜10μA程度の電流を500n〜2μs程度の時間印加する。このように、可変抵抗素子VRに長時間、低電圧を印加すると可変抵抗素子VR内部でジュール熱が発生し、これによって、原子が熱拡散して熱平衡状態に変化する。その結果、可変抵抗素子VRの抵抗状態が、低抵抗状態から高抵抗状態へと遷移する。

【0023】

ところで、製造直後の可変抵抗素子VRは、抵抗値が変化しない定常的な高抵抗状態となっている。そのため、可変抵抗素子VRに上記セット動作或いはリセット動作をさせるために、可変抵抗素子VRに対してフォーミングと呼ばれる処理を施す必要がある。このフォーミングは、可変抵抗素子VRの上下の電極EL1、EL2間に所定の電圧(以下、「フォーミング電圧」と呼ぶ)を印加し、可変抵抗素子VRにフィラメントパスと呼ばれる低抵抗領域を形成することをいう。そして、この際用いられるフォーミング電圧は、セット電圧やリセット電圧よりも遙かに高く、例えば5〜10Vの大きさとなる。

【0024】

次に、本実施形態の理解を容易にするために、比較例に係る不揮発性半導体記憶装置におけるフォーミングについて説明しておく。

【0025】

図13は、比較例に係る不揮発性半導体記憶装置におけるフォーミング時のメモリセルアレイのバイアス状態を示す図であり、図14は、図13中に示すメモリセルMC1〜MC4のバイアス状態を見易くした等価回路図である。

【0026】

図13には、ワード線WL0〜WL4(第1配線)、ビット線BL0〜BL4(第2配線)、並びに、これらワード線WL及びビット線BLの各交差部に設けられたメモリセルMCが示されている。また、メモリセルMCは、直列接続された可変抵抗素子VRとダイオードRDmからなる。ダイオードRDmのカソード及びアノードは、それぞれビット線BL及びワード線WLに接続されている。したがって、ワード線WLの電圧よりもビット線BLの電圧が高い場合、メモリセルMCには順方向バイアスが掛かり、順方向電流が流れる。逆に、ビット線BLの電圧よりもワード線WLの電圧が高い場合、メモリセルMCには逆方向バイアスが掛かり、逆方向電流が流れる。

【0027】

以上示した構成のメモリセルアレイについて、以下では、ワード線WL2及びビット線BL2に接続されたメモリセルMCをフォーミングする場合を例に説明する。以下において、フォーミング対象(アクセス対象)となるメモリセルMCを「選択メモリセル」、その他のメモリセルMCを「非選択メモリセル」、選択メモリセルに接続されたワード線WLを「選択ワード線」(選択第1配線)、その他のワード線WLを「非選択ワード線」(非選択第1配線)、選択メモリセルに接続されたビット線BLを「選択ビット線」(選択第2配線)、その他のビット線BLを「非選択ビット線」(非選択第2配線)と呼ぶ。したがって、本例では、選択ワード線がワード線WL2、選択ビット線がビット線BL2となる。

【0028】

選択ワード線WL2及び選択ビット線BL2間に接続された選択メモリセルMC2をフォーミングする場合、選択ビット線BLに6.2Vのフォーミング電圧VWR、選択ワード線WLに接地電圧VSS(0V)を印加すると共に、非選択ビット線BLに0.5Vの非選択ビット線電圧VUB、非選択ワード線WLに5.7Vの非選択ワード線電圧VUXを印加する。

【0029】

ここで、ダイオードRDmを一般的な電圧−電流特性を持つ素子であると仮定し、メモリセルMC1、MC2、MC3及びMC4のダイオードRDmにおける電圧降下を、それぞれ、0.9V、0.5V、5.2V及び0.5Vとすると、選択ワード線WL2及び選択ビット線BL2に接続された選択メモリセルMC1には、フォーミングに必要な6.2Vの順方向バイアスが掛かる。

【0030】

一方、非選択ワード線WL0、WL1、WL3及びWL4並びに選択ビット線BL2に接続された非選択メモリセルMC2には、0.5Vの順方向バイアス、非選択ワード線WL0、WL1、WL3及びWL4並びに非選択ビット線BL0、BL1、BL3及びBL4に接続された非選択メモリセルMC3には、5.2Vの逆方向バイアス、選択ワード線WL2並びに非選択ビット線BL0、BL1、BL3及びBL4に接続された非選択メモリセルMC4には、0.5Vの順方向バイアスがそれぞれ掛かる。但し、これらメモリセルMC2〜MC4に掛かるバイアスは、フォーミングできない程度の大きさである。

【0031】

つまり、メモリセルアレイを図13に示すようなバイアス状態にすることで、選択メモリセルMC1のみをフォーミングすることができる。

【0032】

しかし、図13に示す場合、図中点線で囲まれた非選択メモリセルMC3については、5.7Vもの逆方向バイアスが掛かり、大きな逆方向電流が流れてしまう。しかも、メモリセルアレイを構成するメモリセルMCの大半が非選択メモリセルMC3になることを考えるとその影響は大きく、特に大規模なメモリセルアレイの場合、消費電力として無視できない大きさになる。このこと程度の違いはあるにせよセット動作時或いはリセット動作時においても同様のことが言える。

【0033】

そこで、本実施形態では、メモリセルMC3に掛かる逆方向バイアスを抑制するようにビット線BLに対してダイオードを挿入させる。なお、このダイオードとメモリセルMCのダイオードRDmを区別するため、メモリセルMCのダイオードRDmを「メモリセル内ダイオード」(第1ダイオード)、ビット線BLに挿入させるダイオードを「逆方向電流低減用ダイオード」(第2ダイオード)と呼ぶことにする。

【0034】

図4は、本実施形態に係る不揮発性半導体記憶装置のメモリセルアレイ1の等価回路図であり、フォーミング時のバイアス状態も併せて示している。また、図5は、図4中に示すメモリセルMC1〜MC4のバイアス状態を見易くした等価回路図である。

【0035】

本実施形態に係る不揮発性半導体記憶装置のメモリセルアレイ1は、図13に示すメモリセルアレイの複数のビット線BLに対して、それぞれ電圧供給元であるカラム制御回路2側をアノード、メモリセルMC側をカソードとする逆方向電流低減用ダイオードRDrが挿入されている。

【0036】

本実施形態のフォーミングの場合、選択ビット線BLに例えば7.0Vのフォーミング電圧VWR(選択第2配線電圧)、選択ワード線WLに例えば接地電圧VSS(0V)(選択第1配線電圧)を印加すると共に、非選択ビット線BLに例えば−4.2Vの非選択ビット線電圧VUB(非選択第2配線電圧)、非選択ワード線WLに例えば5.6Vの非選択ワード線電圧VUX(非選択第1配線電圧)を印加する。

【0037】

この場合、逆方向電流低減用ダイオードRDrの電圧−電流特性をメモリセル内ダイオードRDmの電圧−電流特性と同程度であると仮定すると、メモリセルMC1、MC2、MC3及びMC4のメモリセル内ダイオードRDmにおける電圧降下は、それぞれ、例えば0.9V、0.5V、4.95V及び0.65Vとなる。また、選択ビット線BL及び非選択ビット線BLに挿入された逆方向電流低減用ダイオードRDrは、それぞれ、例えば0.9V及び4.85Vとなる。

【0038】

これによって、選択メモリセルMC1には、フォーミングに必要な6.1Vの順方向バイアスが掛かる。

【0039】

一方、非選択メモリセルMC2には、0.5Vの順方向バイアス、非選択メモリセルMC3には、4.95Vの逆方向バイアス、非選択メモリセルMC4には、0.65Vの順方向バイアスがそれぞれ掛かる。

【0040】

つまり、メモリセルアレイ1を図4に示すようなバイアス状態にすることで、比較例と同様に選択メモリセルMC1のみをフォーミングすることができる一方、比較例と比べて非選択メモリセルMC3に掛かる逆方向バイアスと、非選択メモリセルMC3に流れる逆方向電流を低減させることができる。つまり、非選択メモリセルMC3における消費電力を低減させることができる。

【0041】

図6は、本実施形態と比較例におけるメモリセルMC3に流れる逆方向電流を対比させたグラフである。図中左のグラフが比較例におけるメモリセル内ダイオードRDmの電圧−電流特性、図中右のグラフが本実施形態におけるメモリセル内ダイオードRDmの電圧−電流特性を示している。

【0042】

比較例の場合、非選択メモリセルMC3のメモリセル内ダイオードRDmには5.2Vの逆方向バイアスが掛かるため、非選択メモリセルMC3に流れる逆方向電流I1´は、およそ9.64×10−8Aになる。この場合、2K×8Kのメモリセルアレイであれば、非選択メモリセルMC3に流れる総逆方向電流は、9.64×10−8A×(2K×8K−2K−8K+1)=1.62Aとなり、これは回路を破壊してしまうほどの大きさとなる。また、非選択メモリセルMC3における総消費電力は、5.2V×1.62A=8.41Wにもなる。

【0043】

これに対し、本実施形態の場合、非選択メモリセルMC3のメモリセル内ダイオードRDmには、4.95Vの逆方向バイアスしか掛からない。そのため、非選択メモリセルMC3に流れる逆方向電流I1は、およそ5.78×10−8Aになる。この場合、2K×8Kのメモリセルアレイ1であれば、非選択メモリセルMC3に流れる総逆方向電流は、5.78×10−8A×(2K×8K−2K−8K+1)=0.97Aまで抑制される。なお、この逆方向電流I1は、メモリセルMC4に流れる順方向電流I2と、非選択ビット線BLに挿入された逆方向電流低減用ダイオードRDrに流れる逆方向電流I3の和になる。また、非選択メモリセルMC3における総消費電力も、4.95V×0.97A=4.80Wまで抑制される。

【0044】

つまり、本実施形態によれば、非選択メモリセルMC3に流れる逆方向電流を比較例と比べて40%程度削減することができ(図6中白抜き矢印a1)、非選択メモリセルMC3における総消費電力も比較例と比べて43%程度削減することができる。

【0045】

<逆方向電流低減用ダイオードの構造及び形成方法>

次に、逆方向電流低減用ダイオードRDrの構造及び形成方法の例を図7〜図9に示す不揮発性半導体記憶装置の断面図を用いて説明する。

【0046】

図7に示す場合、不揮発性半導体記憶装置は、図示しないP型シリコン基板上に積層されたディープN型ウエル107、このディープN型ウエル107上に設けられたロウ方向に延びる複数の素子分離溝113を備える。また、ディープN型ウエル107上の2つの素子分離溝113間に形成されたP型ウエル103を備える。

【0047】

このP型ウエル103上部には、ドナー(第1導電型不純物)が高濃度にドープされたN型高濃度領域101(第1導電型不純物領域)と、アクセプタ(第2導電型不純物領域)が高濃度にドープされたP型高濃度領域102(第2導電型不純物領域)が形成されている。このうちN型高濃度領域101は、P型ウエル103との関係で逆方向電流低減用ダイオードRDrを構成するP+/Nの片側階段接合を形成する。

【0048】

また、P型ウエル103上には、カラム制御回路2からメモリセルMCへ延びるビット線BLとなる金属配線が形成されている。この金属配線は、N型高濃度領域101及びP型高濃度領域102間の位置において、カラム制御回路2側に延びる部分金属配線104aと、メモリセルMC側に延びる部分金属配線104bとに分断されている。そして、部分金属配線104a及び104bは、積層方向に延びるビア105を介してP型高濃度領域102及びN型高濃度領域101にそれぞれ接続されている。

【0049】

次に、図7に示す構造の製造方法について説明する。

始めに、図示しないP型シリコン基板上にディープN型ウエル107を形成した後、ロウ方向に延びる複数の素子分離溝113を形成する。

【0050】

続けて、素子分離溝113間のディープN型ウエル107中にアクセプタをドープしてP型ウエル103を形成する。

【0051】

続けて、P型ウエル103中にドナーを高濃度にドープしてN型高濃度領域101を形成する。これによって、N型高濃度領域101及びP型ウエル103からN+/Pの片側段階接合が形成される。なお、この工程は、カラム制御回路2等のMOSFETのソース・ドレイン形成時に同時に行うこともできる。

【0052】

続けて、比較的高い逆耐圧の逆方向電流低減用ダイオードRDrを実現するため、N型高濃度領域101から十分離れた領域にドナーを高濃度でドープしてP型高濃度領域102を形成する。

【0053】

最後に、N型高濃度領域101、P型高濃度領域102、P型ウエル103及び素子分離溝113上に図示しない層間絶縁膜を形成する。その後、この層間絶縁膜を貫通するように、N型高濃度領域101及びP型高濃度領域102に接続する複数のビア105を形成し、これらビア105に接続する部分金属配線104b及び104aを形成すれば、図7に示す構造を作ることができる。

【0054】

図8は、N型ウエル106中にP+/Nの片側階段接合が形成された例である。つまり、図8に示す不揮発性半導体記憶装置の場合、図示しないP型シリコン基板上の2つの素子分離溝113間にN型ウエル106が形成されており、このN型ウエル106上部にN型高濃度領域101(第1導電型不純物領域)とP型高濃度領域102(第2導電型不純物領域)が形成されている。そして、P型高濃度領域102とN型ウエル106との接合によって、逆方向電流低減用ダイオードRDrを構成するP+/Nの片側階段接合が形成されている。

【0055】

図9は、ウエル同士が接合されてPN接合が形成された例である。つまり、図9に示す不揮発性半導体記憶装置の場合、2つの素子分離溝113間のディープN型ウエル107上にロウ方向にストライプ状に延びるP型ウエル103及びN型ウエル106が形成されている。また、これらP型ウエル103上部及びN型ウエル106上部には、それぞれP型高濃度領域102(第2導電型領域)及びN型高濃度領域101(第1導電型領域)が形成されている。そして、P型ウエル103とN型ウエル106との接合によって、逆方向電流低減用ダイオードRDrを構成するPN接合が形成されている。

【0056】

<まとめ>

以上、本実施形態によれば、カラム制御回路及びメモリセル間に逆方向電流低減用ダイオードを挿入させることで、比較例と比べて、非選択ワード線及び非選択ビット線に接続された非選択メモリセルに流れる逆方向電流と、この非選択メモリセルにおける消費電力を大幅に低減させることができる。

【0057】

[第2の実施形態]

第1の実施形態で説明した逆方向電流低減用ダイオードの構造及び形成方法は、いずれも逆方向電流低減用ダイオードを他の素子と別個独立に設けるというものであった。これに対し、第2の実施形態では、カラム制御回路等の周辺回路を構成するMOSFETのソース又はドレインとなる不純物高濃度領域と逆方向電流低減用ダイオードのアノード又はカソードとなる不純物高濃度領域とを共通に形成させた構造及び形成方法の例について、図10及び図11に示す不揮発性半導体記憶装置の断面図を用いて説明する。

【0058】

図10に示す場合、不揮発性半導体記憶装置は、P型シリコン基板208、このP型シリコン基板208上の一部に形成されたディープN型ウエル207、このディープN型ウエル207上に形成されたP型ウエル203、並びに、このP型ウエル203の両側に接合して形成されたN型ウエル206を備える。

【0059】

これらのうちP型ウエル203上部には、ドナー(第1導電型不純物)が高濃度にドープされた2つのN型高濃度領域201(第1導電型不純物領域)が形成されている。これら2つのN型高濃度領域201は、N型MOSFETのソースおよびドレインを構成するものであり、これら2つのN型高濃度領域201の間のP型ウエル203上には、ゲート酸化膜211を介してスペーサ210に挟まれたN型MOSFETのゲートとなるポリシリコン209が形成されている。また、N型ウエル206上部には、アクセプタ(第2導電型不純物)が高濃度にドープされたP型高濃度領域202(第2導電型不純物領域)が形成されている。そして、このP型高濃度領域202は、N型ウエル202との関係で逆方向電流低減用ダイオードRDrを構成するP+/Nの片側階段接合を形成する。なお、N型高濃度領域201とP型高濃度領域202を十分に離して配置すれば、逆方向電流低減用ダイオードRDrの逆耐圧を高くすることができる。

次に、図10に示す構造の製造方法について説明する。

【0060】

始めに、ディープN型ウエル107形成後のP型シリコン基板208中にアクセプタをドープしてP型ウエル203を形成する共に、このP型ウエル203に接する領域にドナーをドープしてN型ウエル206を形成する。

【0061】

続いて、P型ウエル203上にゲート酸化膜211と、ポリシリコン209を形成した後、N型MOSFETのゲートを加工する。

【0062】

続いて、P型ウエル203中のゲートの両側の領域にドナーを高濃度にドープし、2つのN型高濃度領域201を形成する。

【0063】

続いて、P型ウエル203に隣接するN型ウエル202中にP型イオンを注入しP型高濃度領域202を形成する。これによって、P型高濃度領域202及びN型ウエル206からP+/Nの片側階段接合が形成される。

【0064】

最後に、N型高濃度領域201、P型高濃度領域202等に接続されるビア205と、このビア205に接続される必要な金属配線を形成すれば図10に示す構造を作ることができる。

【0065】

図11は、P型MOSFETのソース及びドレインとなるP型高濃度領域と逆方向電流低減用ダイオードのアノードとなるP型高濃度領域とを共通に形成させた例である。つまり、図11に示す不揮発性半導体装置の場合、N型ウエル208上部にアクセプタ(第1導電型不純物)を高濃度にドープさせた2つのP型高濃度領域202(第1導電型不純物領域)が形成されている。これら2つのP型不純物領域202は、それぞれP型MOSFETのソース及びドレインとなる。また、P型ウエル203上部には、ドナー(第2導電型不純物)を高濃度にドープさせたN型高濃度領域201(第2導電型不純物領域)が形成されている。このN型高濃度領域201は、逆方向電流低減用ダイオードRDrのカソードとなる。そして、N型高濃度領域201及びP型ウエル203との接合によって、逆方向電流低減用ダイオードRDrを構成するN+/Pの片側階段接合が形成される。

【0066】

なお、図11に示す不揮発性半導体記憶装置の場合、P型MOSFETのドレイン側のP型ウエル203は、P型MOSFETがオフ状態の時、接地電圧VSSに駆動させる必要がある。したがって、この不揮発性半導体記憶装置には、P型ウエル203と接地電圧VSSとを接続するためのトランジスタ214が設けられている。そして、このトランジスタ214は、P型MOSFETがオン状態の時にオフ状態、P型MOSFETがオフ状態の時にオン状態となるように制御信号CNTで制御される。

【0067】

本実施形態によれば、第1の実施形態と同様の効果を奏するばかりでなく、周辺回路のMOSFETのソース又はドレインとなる不純物高濃度領域とダイオードのアノード又はカソードとなる不純物高濃度領域とが共通になっているため、第1の実施形態と比べて、チップ面積の小さい不揮発性半導体記憶装置を提供することができる。

【0068】

[第3の実施形態]

第3の実施形態では、逆方向電流低減用ダイオードを横置き型のポリシリコンダイオードとした場合の構造及び形成方法の例について、図12に示す不揮発性半導体記憶装置の断面図を用いて説明する。

【0069】

図12に示す場合、不揮発性半導体記憶装置は、図示しないP型シリコン基板上に形成されたポリシリコン薄膜を備える。このポリシリコン薄膜は、ポリシリコンに対してドナー(第1導電型不純物)を高濃度にドープさせたN型ポリシリコン薄膜311(第1導電型不純物領域)と、ポリシリコンに対してアクセプタ(第2導電型不純物)を高濃度にドープさせたP型ポリシリコン薄膜312(第2導電型不純物領域)からなる。これらN型ポリシリコン薄膜311とP型ポリシリコン薄膜312とは接合しており、これによって逆方向電流低減用ダイオードとなるPN接合が構成されている。また、N型ポリシリコン薄膜311及びP型ポリシリコン薄膜312上には、ビット線BL等の必要な金属配線304がビア305を介して接続されている。

【0070】

次に、図12に示す構造の製造方法について説明する。

始めに、図示しないP型シリコン基板上にポリシリコン薄膜を形成する。この際、ポリシリコン薄膜は、均一の不純物濃度を保てる厚さで成膜することが望まし。但し、順方向電流に関してメモリセル内ダイオードRDmと同等の性能を得るには、後に形成される逆方向電流低減用ダイオードRDrとメモリセル内ダイオードRDmの断面積が同程度になるように、ポリシリコン薄膜の厚さを設定しておく必要がある。同様に、逆方向電流低減用ダイオードRDrの長さは、十分な逆耐圧を確保するのに必要な分(例えば、80nm以上)だけとって形成しておく。

【0071】

続いて、ポリシリコン薄膜の一部に対して、ドナーを高濃度にドープしてN型ポリシリコン薄膜311を形成すると共に、このN型ポリシリコン薄膜311に隣接する領域に対してアクセプタを高濃度にドープしてP型ポリシリコン薄膜312を形成する。なお、N型ポリシリコン薄膜311を形成する際には、リソグラフィでP型ポリシリコン薄膜312となる領域をカバーした上で、ドナーをドープさせる。同様に、P型ポリシリコン薄膜312を形成する際には、リソグラフィでN型ポリシリコン薄膜311となる領域をカバーした上で、アクセプタをドープさせる。また、N型ポリシリコン薄膜311及びP型ポリシリコン薄膜312によって構成されるPN接合は、P型ポリシリコン薄膜312からN型ポリシリコン薄膜311へ向かう方向を非選択メモリセルMC3に掛かる逆方向バイアスが緩和される方向となるように形成する。以上によって逆方向電流低減用ダイオードRDrとなるポリシリコンダイオードが形成される。

【0072】

最後に、ポリシリコン薄膜上に図示しない層間絶縁膜を形成する。その後、この層間絶縁膜を貫通するように、N型ポリシリコン薄膜311及びP型ポリシリコン薄膜312に接続される複数のビア305を形成し、これらビア315に接続される金属配線304を形成すれば、図12に示す構造を作ることができる。

【0073】

本実施形態によれば、逆方向電流低減用ダイオードとしてポリシリコンダイオードを用いた場合であっても、第1及び第2の実施形態と同様の効果を得ることができる。

【0074】

[その他]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【0075】

例えば、上記実施形態では、いずれの場合も、ワード線を第1配線、ビット線を第2配線として説明したが、ビット線を第1配線、ワード線を第2配線とすることもできる。また、第1導電型不純物と第2導電型不純物は互いに入れ替わっても良い。

【0076】

更に、上記実施形態は、主にフォーミングについて説明したが、セット動作時、或いはリセット動作時に非選択メモリセルに逆方向電流が流れる不揮発性半導体記憶装置であれば、上記実施形態をいずれも適用することができる。

【符号の説明】

【0077】

1・・・メモリセルアレイ、2・・・カラム制御回路、3・・・ロウ制御回路、4・・・データ入出力バッファ、5・・・アドレスレジスタ、6・・・コマンド・インタフェース、7・・・ステートマシン、9・・・パルスジェネレータ、101、201・・・N型高濃度領域、102、202・・・P型高濃度領域、103、203・・・P型ウエル、104、304・・・金属配線、105、205、305・・・ビア、106、206・・・N型ウエル、107、207・・・ディープN型ウエル、208・・・P型シリコン基板、209・・・ポリシリコン、210・・・カバー、113・・・素子分離溝、214・・・トランジスタ、311・・・N型ポリシリコン薄膜、312・・・P型ポリシリコン薄膜。

【特許請求の範囲】

【請求項1】

互いに交差する複数の第1配線及び第2配線、並びに、前記複数の第1配線及び第2配線の各交差部に設けられ、可変抵抗素子及び第1ダイオードを直列接続してなる複数のメモリセルを有するメモリセルアレイと、

アクセス対象となる前記メモリセルに接続された前記第1配線である選択第1配線に選択第1配線電圧を供給し、その他の前記第1配線である非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、

前記アクセス対象となるメモリセルに接続された前記第2配線である選択第2配線に選択第2配線電圧を供給し、その他の前記第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路と

を備え、

前記メモリセルは、前記第1ダイオードのアノード側に前記第2配線が接続され、前記第1ダイオードのカソード側に前記第1配線が接続され、

前記メモリセルアレイは、前記第2配線制御回路及び前記メモリセル間の前記第2配線に挿入された前記第2配線制御回路側をアノード、前記メモリセル側をカソードとする第2ダイオードを有し、

前記非選択第2配線電圧は、前記非選択第1配線電圧よりも低く、

前記非選択第1配線電圧は、前記選択第1配線電圧よりも高く且つ前記選択第2配線よりも低く、

前記非選択第2配線電圧は、前記選択第1配線電圧よりも低く、

前記メモリセルアレイは、ウエル上に形成されており、

前記第2ダイオードは、前記ウエル中に形成された第1導電型不純物がドープされた第1導電型不純物領域、並びに、前記ウエル中に形成された前記第1導電型不純物とは異なる第2導電型不純物がドープされた第2導電型不純物領域からなり、

前記第2配線制御回路は、ソース及びドレインのいずれか一方を前記第2ダイオードの第1導電型不純物領域と共通に形成させた電界効果トランジスタを有する

ことを特徴とする不揮発性半導体記憶装置。

【請求項2】

互いに交差する複数の第1配線及び第2配線、並びに、前記複数の第1配線及び第2配線の各交差部に設けられ、可変抵抗素子及び第1ダイオードを直列接続してなる複数のメモリセルを有するメモリセルアレイと、

アクセス対象となる前記メモリセルに接続された前記第1配線である選択第1配線に選択第1配線電圧を供給し、その他の前記第1配線である非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、

前記アクセス対象となるメモリセルに接続された前記第2配線である選択第2配線に選択第2配線電圧を供給し、その他の前記第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路と

を備え、

前記メモリセルは、前記第1ダイオードのアノード側に前記第2配線が接続され、前記第1ダイオードのカソード側に前記第1配線が接続され、

前記メモリセルアレイは、前記第2配線制御回路及び前記メモリセル間の前記第2配線に挿入され、前記第2配線制御回路側をアノード、前記メモリセル側をカソードとする第2ダイオードを有する

ことを特徴とする不揮発性半導体記憶装置。

【請求項3】

前記非選択第2配線電圧は、前記非選択第1配線電圧よりも低い

ことを特徴とする請求項2記載の不揮発性半導体記憶装置。

【請求項4】

前記非選択第1配線電圧は、前記選択第1配線電圧よりも高く且つ前記選択第2配線よりも低く、

前記非選択第2配線電圧は、前記選択第1配線電圧よりも低い

ことを特徴とする請求項2又は3記載の不揮発性半導体記憶装置。

【請求項5】

前記メモリセルアレイは、ウエル上に形成されており、

前記第2ダイオードは、前記ウエル中に形成された第1導電型不純物がドープされた第1導電型不純物領域、並びに、前記ウエル中に形成された前記第1導電型不純物とは異なる第2導電型不純物がドープされた第2導電型不純物領域からなる

ことを特徴とする請求項2〜4のいずれか1項記載の不揮発性半導体記憶装置。

【請求項6】

前記第2配線制御回路は、ソース及びドレインのいずれか一方を前記第2ダイオードの第1導電型不純物領域と共通となるように形成させた電界効果トランジスタを有する

ことを特徴とする請求項5記載の不揮発性半導体記憶装置。

【請求項7】

前記第2ダイオードは、ポリシリコンダイオードである

ことを特徴とする請求項2〜4のいずれか1項記載の不揮発性半導体記憶装置。

【請求項1】

互いに交差する複数の第1配線及び第2配線、並びに、前記複数の第1配線及び第2配線の各交差部に設けられ、可変抵抗素子及び第1ダイオードを直列接続してなる複数のメモリセルを有するメモリセルアレイと、

アクセス対象となる前記メモリセルに接続された前記第1配線である選択第1配線に選択第1配線電圧を供給し、その他の前記第1配線である非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、

前記アクセス対象となるメモリセルに接続された前記第2配線である選択第2配線に選択第2配線電圧を供給し、その他の前記第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路と

を備え、

前記メモリセルは、前記第1ダイオードのアノード側に前記第2配線が接続され、前記第1ダイオードのカソード側に前記第1配線が接続され、

前記メモリセルアレイは、前記第2配線制御回路及び前記メモリセル間の前記第2配線に挿入された前記第2配線制御回路側をアノード、前記メモリセル側をカソードとする第2ダイオードを有し、

前記非選択第2配線電圧は、前記非選択第1配線電圧よりも低く、

前記非選択第1配線電圧は、前記選択第1配線電圧よりも高く且つ前記選択第2配線よりも低く、

前記非選択第2配線電圧は、前記選択第1配線電圧よりも低く、

前記メモリセルアレイは、ウエル上に形成されており、

前記第2ダイオードは、前記ウエル中に形成された第1導電型不純物がドープされた第1導電型不純物領域、並びに、前記ウエル中に形成された前記第1導電型不純物とは異なる第2導電型不純物がドープされた第2導電型不純物領域からなり、

前記第2配線制御回路は、ソース及びドレインのいずれか一方を前記第2ダイオードの第1導電型不純物領域と共通に形成させた電界効果トランジスタを有する

ことを特徴とする不揮発性半導体記憶装置。

【請求項2】

互いに交差する複数の第1配線及び第2配線、並びに、前記複数の第1配線及び第2配線の各交差部に設けられ、可変抵抗素子及び第1ダイオードを直列接続してなる複数のメモリセルを有するメモリセルアレイと、

アクセス対象となる前記メモリセルに接続された前記第1配線である選択第1配線に選択第1配線電圧を供給し、その他の前記第1配線である非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、

前記アクセス対象となるメモリセルに接続された前記第2配線である選択第2配線に選択第2配線電圧を供給し、その他の前記第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路と

を備え、

前記メモリセルは、前記第1ダイオードのアノード側に前記第2配線が接続され、前記第1ダイオードのカソード側に前記第1配線が接続され、

前記メモリセルアレイは、前記第2配線制御回路及び前記メモリセル間の前記第2配線に挿入され、前記第2配線制御回路側をアノード、前記メモリセル側をカソードとする第2ダイオードを有する

ことを特徴とする不揮発性半導体記憶装置。

【請求項3】

前記非選択第2配線電圧は、前記非選択第1配線電圧よりも低い

ことを特徴とする請求項2記載の不揮発性半導体記憶装置。

【請求項4】

前記非選択第1配線電圧は、前記選択第1配線電圧よりも高く且つ前記選択第2配線よりも低く、

前記非選択第2配線電圧は、前記選択第1配線電圧よりも低い

ことを特徴とする請求項2又は3記載の不揮発性半導体記憶装置。

【請求項5】

前記メモリセルアレイは、ウエル上に形成されており、

前記第2ダイオードは、前記ウエル中に形成された第1導電型不純物がドープされた第1導電型不純物領域、並びに、前記ウエル中に形成された前記第1導電型不純物とは異なる第2導電型不純物がドープされた第2導電型不純物領域からなる

ことを特徴とする請求項2〜4のいずれか1項記載の不揮発性半導体記憶装置。

【請求項6】

前記第2配線制御回路は、ソース及びドレインのいずれか一方を前記第2ダイオードの第1導電型不純物領域と共通となるように形成させた電界効果トランジスタを有する

ことを特徴とする請求項5記載の不揮発性半導体記憶装置。

【請求項7】

前記第2ダイオードは、ポリシリコンダイオードである

ことを特徴とする請求項2〜4のいずれか1項記載の不揮発性半導体記憶装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−69928(P2013−69928A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−208194(P2011−208194)

【出願日】平成23年9月22日(2011.9.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月22日(2011.9.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]