不揮発性記憶装置

【課題】プロセス耐性が高く、高い性能を維持する不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、第1導電部と、第2導電部と、記憶層と、を含む不揮発性記憶装置が提供される。前記記憶層は、前記第1導電部と前記第2導電部との間に設けられる。前記記憶層は、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能である。前記記憶層は、カルコパイライト構造を有する。

【解決手段】実施形態によれば、第1導電部と、第2導電部と、記憶層と、を含む不揮発性記憶装置が提供される。前記記憶層は、前記第1導電部と前記第2導電部との間に設けられる。前記記憶層は、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能である。前記記憶層は、カルコパイライト構造を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、不揮発性記憶装置に関する。

【背景技術】

【0002】

近年、小型携帯機器が世界的に普及し、同時に、高速情報伝送網の大幅な進展に伴い、小型で大容量の不揮発性記憶装置の需要が急速に拡大してきている。記憶密度の限界を大幅に超えることを目指した新規メモリがいくつか提案されている。例えば、低抵抗状態と高抵抗状態とを有する抵抗変化材料を用いたメモリが提案されている。抵抗変化型の不揮発性装置において、安定して高い性能を発揮することが望まれる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−84512号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置を提供する。

【課題を解決するための手段】

【0005】

本発明の実施形態によれば、第1導電部と、第2導電部と、記憶層と、を含む不揮発性記憶装置が提供される。前記記憶層は、前記第1導電部と前記第2導電部との間に設けられる。前記記憶層は、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能である。前記記憶層は、カルコパイライト構造を有する。

【図面の簡単な説明】

【0006】

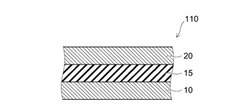

【図1】第1の実施形態に係る不揮発性記憶装置の構成を例示する模式的断面図である。

【図2】第1の実施形態に係る不揮発性記憶装置の構成を例示する模式図である。

【図3】第1の実施形態に係る不揮発性記憶装置の動作を例示する模式図である。

【図4】不揮発性記憶装置の特性を例示する表である。

【図5】不揮発性記憶装置の特性を例示するグラフ図である。

【図6】第2の実施形態に係る不揮発性記憶装置の構成を例示する模式的斜視図である。

【図7】第2の実施形態に係る不揮発性記憶装置の構成を例示する模式図である。

【図8】第2の実施形態に係る不揮発性記憶装置の一部の構成を例示する模式的断面図である。

【図9】第2の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的斜視図である。

【図10】第2の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的斜視図である。

【図11】第3の実施形態に係る不揮発性記憶装置の構成を例示する模式的斜視図である。

【図12】第3の実施形態に係る不揮発性記憶装置の構成を例示する模式的平面図である。

【図13】第4の実施形態に係る不揮発性記憶装置の構成を例示する模式的断面図である。

【図14】第4の実施形態に係る不揮発性記憶装置の動作を例示する模式的断面図である。

【図15】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

【図16】図16(a)〜図16(c)は、第4の実施形態に係る別の不揮発性記憶装置を例示する模式的断面図である。

【図17】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

【図18】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

【図19】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

【図20】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

【図21】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

【発明を実施するための形態】

【0007】

以下に、本発明の各実施の形態について図面を参照しつつ説明する。

なお、図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

なお、本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

【0008】

(第1の実施形態)

図1は、第1の実施形態に係る不揮発性記憶装置の構成を例示する模式的断面図である。

図1に表したように、本実施形態に係る不揮発性記憶装置110は、第1導電部10と、第2導電部20と、記憶層15と、を含む。記憶層15は、第1導電部10と第2導電部20との間に設けられる。

【0009】

記憶層15には、第1導電部10と第2導電部20とを介して電流が供給される。記憶層15は、その電流により、抵抗が低い第1状態(低抵抗状態)と、第1状態よりも抵抗が高い第2状態(高抵抗状態)との間を可逆的に遷移可能である。記憶層15は、カルコパイライト構造を有する。

【0010】

記憶層15は、例えば、AxMyXzで表される材料を含む。ここで、「A」は、例えば、Mn、Fe、Co、Ni、Cu、Zn、Mg、Al及びGaよりなる群から選択された少なくともいずれかである。「M」は、例えば、Si、Ge、Al及びGaよりなる群から選択された少なくともいずれかである。「X」は、例えば、N、P及びAsよりなる群から選択された少なくともいずれかを含む。

【0011】

上記の「M」は、「A」とは異なる元素を含む。これにより、AxMyXzで表される化合物は、カルトパイライト構造となる。

【0012】

また、実施形態において、「A」は、遷移元素を含むことができる。例えば、Aとして遷移元素が用いられる。また、Aとして、複数の種類の元素(例えば元素αと元素β)が用いられる場合において、複数の元素の少なくともいずれかが遷移元素とすることができる。例えば、記憶層15として(αx1β1−x1)xMyXzで表される材料を用いることができ、元素α及び元素βの少なくともいずれかは、遷移元素である。

【0013】

図2は、第1の実施形態に係る不揮発性記憶装置の構成を例示する模式図である。

図2は、記憶層15の結晶構造を例示している。なお、この例では、「A」はCoであり、「M」はSiであり、「X」はNである。図2に表したように、記憶層15は、カルコパイライト構造を有する。

【0014】

例えば、酸化物を用いた抵抗変化素子を半導体プロセスにさらすと、抵抗変化素子の特性が大きく変化する場合があることが分かった。例えば、抵抗変化素子に用いられる酸化物が過酷な半導体プロセスにより変質し、実際のデバイスを形成したときに所望の特性が得難いことが分かった。特に、半導体プロセスで用いられるウエットプロセスを酸化物の抵抗変化部に適用すると、所望の特性を維持することが困難である。例えば、抵抗変化素子が半導体プロセスを経るとダメージを受け、抵抗変化素子におけるスイッチング回数が減る。このことは、本願発明者が実験により見出した課題であり、実施形態は、この新に見出された課題を解決する。

【0015】

本実施形態に係る不揮発性記憶装置110においては、記憶層15として、カルコパイライト構造を有する化合物を用いる。カルコパイライト構造を有する化合物においては、元素どうしが強固に結合しているため、プロセス耐性が高い。そして、実施形態においては、記憶層15として、酸化物などのような比較的不安定な材料を用いた場合に比べて、種々のプロセスを経た後でも、良好で安定した特性を維持できる。

【0016】

以下、本実施形態に係る不揮発性記憶装置110における動作の例をモデル的に説明する。

図3は、第1の実施形態に係る不揮発性記憶装置の動作を例示する模式図である。

図3に表したように、記憶層15は、抵抗(抵抗率)が低い低抵抗状態(低抵抗状態LR)と、低抵抗状態よりも抵抗(抵抗率)が相対的に高い高抵抗状態(高抵抗状態HR)とを有する。記憶層15において、低抵抗状態LRと、高抵抗状態HRと、の間を可逆的に遷移可能である。

【0017】

以下では、記憶層15の初期状態が高抵抗状態HRである場合として説明する。

記憶層15に設けられた電位勾配により、記憶層15を変化させ、記憶層15を低抵抗状態LRにすることにより情報の書き込みを行う。

【0018】

記憶層15は、位置が固定された陽イオン(第1陽イオン51)と、移動可能な陽イオン(第2陽イオン52)と、陰イオン53と、を含む。例えば、第1陽イオン51として上記の「M」の元素が用いられ、第2陽イオン52として上記の「A」の元素が用いられ、陰イオン53として上記の「X」の元素が用いられる。例えば、第2陽イオン52の少なくとも一部は、遷移元素である。すなわち、第2陽イオン52の価数は変化可能である。

【0019】

まず、例えば、第2導電部20の電位が、第1導電部10の電位よりも相対的に低い状態を作る。例えば、第1導電部10を固定電位(例えば、接地電位)とし、第2導電部20に負の電位を与える。これにより、第2陽イオン52の一部が結晶中(記憶層15の中)を第2導電部20(陰極)に向けて移動する。結晶である記憶層15の内部において、第2陽イオン52の数が、陰イオン53に対して相対的に減少する。

【0020】

第2導電部20の側に移動した第2陽イオン52は、第2導電部20から電子を受取り、例えば、金属原子52mとして析出して金属層17が形成される。すなわち、記憶層15のうちで第2導電部20に近い領域では、第2陽イオン52が還元されて金属的に振る舞う。これにより、電気抵抗が減少する。

【0021】

一方、記憶層15の内部では、陰イオン53が過剰となるため、記憶層15の内部に残された第2陽イオン52の価数が上昇する。これにより、記憶層15において、電子伝導性が発現する。その結果、記憶層15全体として、低抵抗状態LRへと変化する。この動作を、セット動作SOという。セット動作SOは、例えば書き込み動作である。

【0022】

書き込んだ情報の読み出しは、例えば電圧パルスを記憶層15に印加し、記憶層15の抵抗値を検出することにより行う。この時、電圧パルスの大きさは、記憶層15の抵抗が変化しない程度の微小な値とされる。

【0023】

なお、以上説明した過程は、一種の電気分解である。例えば、第1導電部10(陽極)の側では電気化学的酸化により酸化剤が生じ、第2導電部20(陰極)の側では電気化学的還元により還元剤が生じる。

【0024】

一方、低抵抗状態LRを高抵抗状態HRに戻す動作(リセット動作RO)の際には、例えば、記憶層15に大電流パルスを印加し、それによるジュール熱によって記憶層15を加熱して、記憶層15の酸化還元反応を促進させる。ジュール熱により、第2陽イオン52は、熱的により安定な結晶構造内(記憶層15の内部)へと戻り、初期の高抵抗状態HRが現れる。リセット動作ROは、例えば消去動作である。

【0025】

また、セット動作SOとは逆極性の電圧パルスを印加してもリセット動作ROを行うことができる。例えば、第1導電部10を固定電位とし、第2導電部20に正の電位を与えることにより、第2導電部20の近傍の金属原子52mは第2導電部20に電子を与え、第2陽イオン52となる。第2陽イオン52は、記憶層15内の電位勾配により記憶層15の内部に戻る。これにより、初期の高抵抗状態HRへと変化する。

このようにして、本実施形態に係る不揮発性記憶装置110の書き込み動作及び消去動作、すなわち、セット動作SO及びリセット動作ROが行われる。

【0026】

実施形態おいては、例えば、カルコパイライト構造を有する化合物(結晶)における、陽イオンの移動に基づく電流が利用される。この陽イオンの移動を容易にするために、イオン半径が大きい陰イオンを用いる。例えば、「X」として、N、P及びAsよりなる群から選択された少なくともいずれかを用いることにより、陰イオンのイオン半径を大きくすることができ、陽イオンが容易に移動できるようになる。

【0027】

なお、記憶層15として酸化物を用いた場合においては、酸素イオンが陰イオンとなる。酸素イオン(陰イオン)のイオン半径は小さく、陽イオンが移動し難い。このため、この構成においては、良好なスイッチングが得にくいと考えられる。

【0028】

実施形態に係る不揮発性記憶装置110においては、陽イオンの移動を容易にする構成を用いることで、良好で安定した電気的特性を得ることができる。

【0029】

また、記憶層15として、窒化物の材料を用いることで、プロセス耐性を向上し易くなる。このように、「X」として、N、P及びAsのように3価の元素(陰イオン53となる元素)を用いることで、プロセス耐性が向上し易くなる。

【0030】

実施形態においては、記憶層15として、非酸化物を用いる。そして、陰イオンの価数をあげることで耐性が向上する。例えば、珪素と酸素とを含む骨格よりも珪素と窒素とを含む骨格の方が強い。さらに、酸素よりも窒素の方が、イオン半径が大きい。窒素を用いることで、陽イオン(例えばCoイオン)が結晶構造中を通る経路が大きくなり、陽イオンが動き易くできる。これにより、スイッチング確率が高くなる。そして、耐久性(endurance)が向上する。

【0031】

なお、カルコパイライト構造を有する化合物としてCuInSe2などがある。この化合物の太陽電池などへ応用が検討されている。この場合には、電子が励起され、励起された電子が移動する機構が利用される。すなわち、太陽電池においては、イオンが移動する機構ではなく、電子の移動に基づく電流が利用される。これに対して、実施形態に係る不揮発性記憶装置110においては、カルコパイライト構造を有する化合物におけるイオン(例えば陽イオン)の移動が利用される。

【0032】

例えば、スピネル構造を有する材料は、電池の材料として用いることができ、この構造においてイオンが移動する機構は知られている。しかしながら、カルコパイライト構造を有する化合物におけるイオンの移動を利用したデバイスについては従来知られていない。本実施形態においては、カルコパイライト構造におけるイオンの移動に基づく抵抗の変化が利用される。

【0033】

実施形態において、記憶層15が上記のAxMyXzで表される材料を含む場合において、「A」が遷移元素を含むことで、例えば、記憶動作におけるリテンション時間を長くすることができる。

【0034】

以下、記憶層15に関する材料の特性の例について説明する。以下では、種々の組成の材料に関して、プロセス耐性としてDHF(100倍に希釈した希釈フッ酸)処理後のスイッチング確率について説明する。

【0035】

試料においては、直径が約60mmで、厚さ約1mmのガラス基板からなるディスクが用いられる。このディスクの上に、下部電極層が設けられ、下部電極層の上に記憶層15となる試料層が設けられ、その上に上部電極層(保護層)が設けられる。下部電極層及び上部電極層(保護層)には、厚さが500nmのPt膜が用いられる。

【0036】

記憶層15となる原料を含む所定のターゲットを用い、所定の雰囲気でのRFマグネトロンスパッタにより、記憶層15が形成できる。記憶層15の形成の際のディスクの温度は300℃〜600℃の範囲内の値に維持される。記憶層15の厚さは、約10nmである。記憶層15は、形成された後に、上記のDHFに1分間接触させられる。

【0037】

上部電極層に、タングステン(W)のプローブを接触させ、記憶層15に電流を通電する。プローブの先端の径は、約10nmである。書き込み動作においては、下部電極層とプローブとの間に10ナノ秒(ns)で1ボルト(V)の電圧パルスを印加する。消去動作においては、下部電極層とプローブとの間に、100nsで0.1Vの電圧パルスを印加する。この書き込み動作と消去動作とを繰り返して実施したときに、記憶層15における高抵抗状態HRの抵抗値の、低抵抗状態LRの抵抗値に対する比(オンオフ比)が1,000以上であるときのスイッチング回数SWN(サイクル)が評価値として用いられる。

【0038】

第1試料においては、記憶層15としてCoSiN2が用いられる。第1試料における記憶層15は、Co:Si=1:1の合金ターゲットを用い、50%のArと、50%のN2と、を含む雰囲気中でのRFマグネトロンスパッタにより形成される。第1試料においては、10箇所の通電点において、スイッチング回数SWNは10,000サイクル以上である。

【0039】

以下の各試料において、説明しない部分は、上記の第1試料と同様である。

第2試料においては、記憶層15としてMnSiN2が用いられる。

第3試料においては、記憶層15としてFeSiN2が用いられる。

第4試料においては、記憶層15としてFe0.7SiN2が用いられる。

第5試料においては、記憶層15としてMnGeN2が用いられる。

第6試料においては、記憶層15としてFeGeN2が用いられる。

第7試料においては、記憶層15としてCoGeN2が用いられる。

第8試料においては、記憶層15としてFe0.7GeN2が用いられる。

第9試料においては、記憶層15としてCoSiP2が用いられる。

第10試料においては、記憶層15としてMnSiP2が用いられる。

第11試料においては、記憶層15としてFeSiP2が用いられる。

第12試料においては、記憶層15としてFe0.7SiP2が用いられる。

第13試料においては、記憶層15としてMnGeP2が用いられる。

第14試料においては、記憶層15としてFeGeP2が用いられる。

第15試料においては、記憶層15としてCoGeP2が用いられる。

第16試料においては、記憶層15としてFe0.7GeP2が用いられる。

第17試料においては、記憶層15としてCo0.5Zn0.5SiN2が用いられる。

第18試料においては、記憶層15としてMn0.5Zn0.5SiN2が用いられる。

第19試料においては、記憶層15としてFe0.5Zn0.5SiN2が用いられる。

第20試料においては、記憶層15としてFe0.5Zn0.25SiN2が用いられる。

【0040】

以上の第2〜第20試料においては、10箇所の通電点において、スイッチング回数SWNは10,000サイクル以上である。

【0041】

第21試料においては、記憶層15としてZnV2O4が用いられる。

第22試料においては、記憶層15としてZnCr2O4が用いられる。

第23試料においては、記憶層15としてZnMn2O4が用いられる。

第24試料においては、記憶層15としてZnCo2O4が用いられる。

第25試料においては、記憶層15としてMgCr2O4が用いられる。

第26試料においては、記憶層15としてMgMn2O4が用いられる。

【0042】

第21〜第26試料のそれぞれにおいて、試料の1,000箇所にプローブを接触させたときに、1,000以上のオンオフ比が得られるのは、それぞれ、2箇所、1箇所、2箇所、4箇所、6箇所、7箇所である。第21〜第26試料においては、1サイクルのスイッチング確率は、70%未満である。

【0043】

第1〜第20試料においては、記憶層15はカルコパイライト構造を有する。第21〜第26試料においては、記憶層15はカルコパイライト構造を有していない。このように、記憶層15がカルコパイライト構造を有することで、DHF処理のようなプロセスを経た後においても、良好な電気的特性が得られる。

【0044】

このように、記憶層15は、例えば、窒化コバルト、珪窒化マンガン、珪窒化鉄、窒化ゲルマニウムマンガン、窒化ゲルマニウム鉄、窒化ゲルマニウムコバルト、珪リン化コバルト、珪リン化マンガン、珪リン化鉄、リン化ゲルマニウムマンガン、リン化ゲルマニウム鉄、リン化ゲルマニウムコバルト、珪窒化コバルト亜鉛、珪窒化マンガン亜鉛、及び、珪窒化鉄亜鉛よりなる群から選択された少なくともいずれかを含む。

【0045】

本実施形態において、記憶層15に含まれるAxMyXzの組成比xは、例えば、0.3≦x≦1を満たす。上記の組成比yは、0.9≦y≦1.1を満たす。さらに、1.9≦(z/y)≦2.1を満たす。

これにより、プロセス耐性が高い記憶層15を得易くなる。これにより、高い性能を維持する不揮発性記憶装置が提供できる。

【0046】

以下、組成比x、組成比y及び組成比zを変えたときの記憶層15の特性の例について説明する。

図4は、不揮発性記憶装置の特性を例示する表である。

図4には、カルコパイライト構造を有する化合物AxMyXzにおいて、組成比x、組成比y及び組成比zを変えたときの、スイッチング回数(寿命)の判定Evを示している。ここで、記憶層15において、低抵抗状態と高抵抗状態との相互の遷移(スイッチング)を繰り返したときに、オンオフ比が1,000以上を維持できるスイッチング回数SWNが10,000サイクル以上の場合が、良好な特性が得られている状態である。スイッチング回数SWNが10,000サイクル未満の場合は、特性が良くない状態である。

図4においては、良好な特性が得られている状態は、「判定Ev」に関して「X」と表示されている。特性が良くない状態は、「判定Ev」に関して「O」と表示されている。 図4においては、「A」としてCoを用い、「M」としてSiを用い、「X」としてNを用いた時の例が示されている。

【0047】

図4から分かるように、組成比xが0.29以下または1.01以上のときは、良好な特性が得られない(判定Evは「X」)。組成比xが0.31以上0.99以下であっても、組成比yが、0.89以下、または、1.11以上のときは、良好な特性が得られない(判定Evは「X」)。

【0048】

これに対し、組成比xが0.31以上0.99以下であり、かつ、組成比yが、0.91以上1.09以下のときに、組成比zの値によって、良好な特性が得られる条件が存在する(判定Evは「O」)。

【0049】

図5は、不揮発性記憶装置の特性を例示するグラフ図である。

図5は、図4に例示した、組成比xが0.31以上で0.99以下の試料に関し、組成比y及び組成比zと、判定Evと、の関係を示している。図5の横軸は組成比yであり、図5の縦軸は組成比zである。図5中の「O」の表示は、良好な特性が得られること(スイッチング回数SWNが10,000サイクル以上)を示し、図5中の「X」の表示は、特性が良くないこと(スイッチング回数SWNが10,000サイクル未満)を示す。

【0050】

図5から分かるように、組成比yが、0.89以下、または、1.11以上のときは、良好な特性が得られないのに対して組成比yが、0.91以上1.09以下のときに、良好な特性が得られる。このことから、0.9≦y≦1.1のときに良好な特性が得られると考えられる。

【0051】

そして、良好な特性が得られる組成比zの条件は、組成比yによって変化する。すなわち、この例では、1.9y≦z≦2.1yのときに良好な特性が得られる。すなわち、1.9≦(z/y)≦2.1のときに良好な特性が得られる。

【0052】

また、図4では、「A」がCoで、「M」がSiで、「X」がNの時の例が示されているが、Aが、Mn、Fe、Ni、Cu、Zn、Mg、AlまたはGaのときも同様の傾向となる。また、Mが、Ge、AlまたはGaのときも同様の傾向となる。また、Xが、PまたはAsのときも同様の傾向となる。

【0053】

以上から、実施形態においては、上記のAxMyXzで表された材料を記憶層15に用いる場合、0.3≦x≦1、0.9≦y≦1.1、及び、1.9≦(z/y)≦2.1を満たす条件に設定することが好ましい。これにより、良好なスイッチング特性がより得易くなる。

【0054】

なお、「X」は、1%以下のハロゲン元素を含むことができる。「X」が、ハロゲン元素を含むことにより、例えば結晶化温度が低くなる。また、「X」が、ハロゲン元素を含むことにより、スイッチング特性のばらつきを小さくすることができる。

【0055】

本実施形態において、第1導電部10及び第2導電部20の少なくともいずれかは、不純物がドープされた、Si、及び、III-V族化合物半導体の少なくともいずれかを含むことが望ましい。

【0056】

Siは、ダイヤモンド構造を有する。ダイヤモンド構造は、カルコパイライト構造に類似する。III-V族化合物半導体は、ウルファイト構造または閃亜鉛構造を有する。これらの結晶構造も、カルコパイライト構造と類似する。Si、及び、III-V族化合物半導体における元素の結びつきの状態は、記憶層15における元素の結びつきの状態と、同様になる。

【0057】

記憶層15における結晶構造と類似の結晶構造を有する材料を、第1導電部10及び第2導電部20の少なくともいずれかに用いることで、例えば、他の材料を用いた場合に比べて、記憶層15における結晶欠陥が低減できる。また、第1導電部10と記憶層15との間の界面、及び、第2導電部20と記憶層15との間の界面における結晶の劣化が抑制できる。これにより、良好な電気的特性が得易くなる。

【0058】

(第2の実施形態)

本実施形態に係る不揮発性記憶装置は、クロスポイント型の構成を有する。

図6は、第2の実施形態に係る不揮発性記憶装置の構成を例示する模式的斜視図である。

図7は、第2の実施形態に係る不揮発性記憶装置の構成を例示する模式図である。

図6及び図7に表したように、本実施形態に係る不揮発性記憶装置210においては、基板30が設けられる。基板30の主面に対して並行な平面をX−Y平面とする。X−Y平面内の1つの方向をX軸方向とする。X−Y平面内においてX軸方向に対して垂直な方向をY軸方向とする。X軸方向とY軸方向とに対して垂直な方向をZ軸方向とする。

【0059】

不揮発性記憶装置210において、基板30の主面の上に、X軸方向に延在する帯状の第1の配線(ワード線WLi−1、WLi、WLi+1)が設けられる。さらに、Y軸方向に延在する帯状の第2の配線(ビット線BLj−1、BLj、BLj+1)が、設けられる。第2の配線(ビット線BLj−1、BLj、BLj+1)は、第1の配線(ワード線WLi−1、WLi、WLi+1)に対向する。

【0060】

なお、上記では、第1の配線の延在方向が第2の配線の延在方向に対して直交するが、第1の配線の延在方向が第2の配線の延在方向と交差(非平行)すれば良い。

【0061】

なお、上記において添え字i及び添え字jは任意である。すなわち、第1の配線の数及び第2の配線の数は、任意である。

本具体例では、第1の配線がワード線となり、第2の配線がビット線となる。ただし、第1の配線がビット線で、第2の配線がワード線でも良い。以下では、第1の配線がワード線であり、第2の配線がビット線であるとして説明する。

【0062】

図6及び図7に表したように、第1の配線と第2の配線との間にメモリセル33が設けられる。

【0063】

図7に表したように、例えば、ワード線WLi−1、WLi、WLi+1の一端は、選択スイッチであるMOSトランジスタRSWを介して、デコーダ機能を有するワード線ドライバ31に接続される。ビット線BLj−1、BLj、BLj+1の一端は、選択スイッチであるMOSトランジスタCSWを介して、デコーダ及び読み出し機能を有するビット線ドライバ32に接続される。

【0064】

MOSトランジスタRSWのゲートには、ワード線(ロウ)を選択するための選択信号Ri−1、Ri、Ri+1が入力され、MOSトランジスタCSWのゲートには、ビット線(カラム)を選択するための選択信号Ci−1、Ci、Ci+1が入力される。

【0065】

メモリセル33は、ワード線WLi−1、WLi、WLi+1と、ビット線BLj−1、BLj、BLj+1と、が互いに対向する交差部に配置される。メモリセル33には、書き込み/読み出し時における回り込み電流(sneak current)を防止するための整流素子34を付加することができる。

【0066】

図8は、第2の実施形態に係る不揮発性記憶装置の一部の構成を例示する模式的断面図である。

図8に表したように、ワード線WLiとビット線BLjとの間には、メモリセル33及び整流素子34が設けられる。なお、ワード線WLiとビット線BLjとの上下の配置の関係は任意である。ワード線WLiとビット線BLjとの間における、メモリセル33と整流素子34との配置の順番は、任意である。

【0067】

図8に表したように、メモリセル33は、記憶部22を含む。記憶部22は、第1導電部10と、第2導電部20と、第1導電部10と第2導電部20との間に設けられた記憶層15と、を含む。記憶層15には、第1の実施形態に関して説明した構成が適用できる。

【0068】

メモリセル33は、保護層33Bをさらに含むことができる。本具体例では、保護層33Bは、記憶部22のビット線BLjの側に設けられているが、保護層33Bは、記憶部22のワード線WLiの側に設けても良く、整流素子34とワード線WLiとの間に設けても良い。メモリセル33は、記憶部22と保護層33Bとの間に設けられたヒータ層35をさらに含むことができる。ヒータ層35及び保護層33Bは、必要に応じて設けられ、省略可能である。

【0069】

なお、第1導電部10及び第2導電部20の少なくともいずれかとして、記憶部22に隣接する、例えば、ワード線WLi、整流素子34、ヒータ層35、保護層33B、ビット線BLjの少なくともいずれかを用いても良い。

【0070】

図9及び図10は、第2の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的斜視図である。

図9及び図10に表したように、本実施形態に係る不揮発性記憶装置211及び212においては、ワード線、ビット線、及び、それらの間に設けられたメモリセル33を含む積層構造体が、複数積み重ねられる。これにより、3次元構造の不揮発性記憶装置が形成される。

【0071】

本実施形態に係る不揮発性記憶装置210、211、212においては、駆動部となるワード線ドライバ31及びビット線ドライバ32は、ワード線WLi及びビット線BLjを介して、記憶層15への電圧の印加、及び、記憶層15への電流の通電、の少なくともいずれかを行う。これにより、記憶層15に変化を発生させて情報を書き込む。例えば、駆動部は、記憶層15に電圧を印加して記憶層15に変化を発生させて情報を書き込む。また、書き込んだ情報を読み出すことができる。また、消去を行うことができる。

【0072】

本実施形態に係る不揮発性記憶装置210、211、212においても、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置が提供できる。

【0073】

(第3の実施の形態)

本実施形態に係る不揮発性記憶装置は、プローブメモリ型の構成を有する。

図11は、第3の実施形態に係る不揮発性記憶装置の構成を例示する模式的斜視図である。

図12は、第3の実施形態に係る不揮発性記憶装置の構成を例示する模式的平面図である。

図11及び図12に表したように、本実施形態に係る不揮発性記憶装置250では、XYスキャナ516の上に、電極521の上に設けられた記憶層15が配置されている。記憶層15に対向するように、プローブアレイが配置される。電極521は、例えば、基板520上に設けられる。

【0074】

プローブアレイは、例えば、基板523と、基板523の一面側にアレイ状に配置される複数のプローブ(ヘッド)524と、を有する。プローブ524として、例えば、カンチレバーが用いられる。複数のプローブ524は、マルチプレクスドライバ525、526により駆動される。

複数のプローブ524は、それぞれ、基板523内のマイクロアクチュエータを用いて個別に動作可能である。また、全てをまとめて同じ動作をさせて記憶媒体(記憶層15)のデータエリア531に対してアクセスを行うこともできる。

【0075】

例えば、電極521が第1導電部10として用いられ、プローブ524が第2導電部20として用いられる。また、記憶層15の上に導電性の保護層が設けられる場合は、その保護層が、第2導電部20となる。

【0076】

例えば、マルチプレクスドライバ525、526を用いて、全てのプローブ524をX方向に一定周期で往復動作させ、記憶媒体(記憶層15)のサーボエリア532からY方向の位置情報を読み出す。Y方向の位置情報は、ドライバ515に転送される。

ドライバ515は、この位置情報に基づいてXYスキャナ516を駆動し、記憶媒体(記憶層15)をY方向に移動させ、記憶媒体(記憶層15)とプローブとの位置決めを行う。

両者の位置決めが完了したら、データエリア531上のプローブ524を用いてデータの書き込み、読み出しまたは消去を行う。

【0077】

例えば、1つのデータエリア531に対応して1つのプローブ(ヘッド)が設けられ、1つのサーボエリア532に対して1つのプローブが設けられる。各プローブ524は、例えばマルチプレクスドライバ525、526を介して、駆動部600に接続される。駆動部600は、それぞれのプローブ524に、情報記憶のための、電圧及び電流の少なくともいずれかを供給する。記憶層15は、プローブ524を介して与えられた電圧及び電流によって、高抵抗状態と低抵抗状態との間を遷移する。また、駆動部600は、記憶層15に記憶された高抵抗状態と低抵抗状態とを検出し、記憶された情報を読み出す。

【0078】

このような構成の不揮発性記憶装置250は、記憶層15と、記憶層15への電圧の印加、及び、記憶層15への電流の通電、の少なくともいずれかによって、記憶層15に変化を発生させて情報を記憶する駆動部600と、を備える。不揮発性記憶装置250は、記憶層15に併設されたプローブ524をさらに備え、駆動部600は、プローブ524を介して、記憶層15の記憶単位に対して電圧の印加及び電流の通電の少なくともいずれかを行う。これにより、記憶層15に変化を発生させて情報を記憶する。

【0079】

なお、駆動部600は、上記のドライバ515及びXYスキャナ516を含むこともでき、逆に、駆動部は、上記のドライバ515及びXYスキャナ516に含まれても良い。

【0080】

本実施形態に係るプローブメモリ型の不揮発性記憶装置250においても、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置が提供できる。

【0081】

(第4の実施の形態)

本実施形態に係る不揮発性記憶装置は、フラッシュメモリ型の構成を有する。

図13は、第4の実施形態に係る不揮発性記憶装置の構成を例示する模式的断面図である。

図14は、第4の実施形態に係る不揮発性記憶装置の動作を例示する模式的断面図である。

図13に表したように、本実施形態に係る不揮発性記憶装置260においては、フラッシュメモリ型のメモリセルを有する。このメモリセルは、MIS(metal-insulator-semiconductor)トランジスタの構成を有する。

【0082】

半導体基板41の表面領域には、複数の拡散層42が形成される。複数の拡散層42の間にチャネル領域42cが設けられる。チャネル領域42c上には、ゲート絶縁層43が形成される。ゲート絶縁層43上には、実施形態に係る記憶層15が形成される。記憶層15の上には、コントロールゲート電極45が形成される。

【0083】

記憶層15は、第1の実施形態で説明した構成を有する。例えば、チャネル領域42cが第1導電部10であり、コントロールゲート電極45が第2導電部20であると見なすことができる。また、ゲート絶縁層43と、コントロールゲート電極45との間に、第1導電部10、第2導電部20及び記憶層15を含む記憶部22が設けられても良い。以下の図においては、記憶部22を、適宜、記憶層15として省略して表示する。

【0084】

半導体基板41は、ウェル領域でも良い。半導体基板41は、拡散層42の導電形に対して逆の導電形を有する。コントロールゲート電極45は、ワード線となる。コントロールゲート電極45には、例えば、導電性ポリシリコンが用いられる。

【0085】

本実施形態においては、図示しない駆動部が、コントロールゲート電極45に接続されて設けられる。駆動部は、コントロールゲート電極45を介して、記憶層15への電圧の印加、及び、記憶層15への電流の通電、の少なくともいずれかを行う。

【0086】

図14に表したように、セット(書き込み)動作SOでは、コントロールゲート電極45に電位V1を与え、半導体基板41に電位V2を与える。

電位V1及び電位V2の差は、記憶層15が変化、すなわち、抵抗が変化するのに十分な大きさである。ただし、電位の差の極性は、特に、限定されない。すなわち、V1>V2、及び、V1<V2のいずれでも良い。

【0087】

例えば、初期状態(リセット状態)において、記憶層15が高抵抗状態HRであると仮定すると、ゲート絶縁層43が厚くなったことになるため、メモリセル(MISトランジスタ)の閾値は、高くなる。

【0088】

この状態から電位V1、V2を与えて記憶層15を低抵抗状態LRに変化させると、ゲート絶縁層43が薄くなったことになるため、メモリセル(MISトランジスタ)の閾値は、低くなる。

【0089】

なお、電位V2は、半導体基板41に与えたが、これに代えて、メモリセルのチャネル領域42cに拡散層42から電位V2を転送するようにしても良い。なお、同図において、矢印Aeは電子の移動を表し、矢印Aiはイオンの移動を表している。

【0090】

一方、リセット(消去)動作ROでは、コントロールゲート電極45に電位V1’を与え、拡散層42の一方に電位V3を与え、拡散層42の他方に電位V4(<V3)を与える。電位V1’は、セット状態のメモリセルの閾値を越える値にする。

【0091】

この時、メモリセルはオンになり、電子が拡散層42の他方から一方に向かって流れると共に、ホットエレクトロンが発生する。このホットエレクトロンは、ゲート絶縁層43を介して記憶層15に注入されるため、記憶層15の温度が上昇する。

【0092】

これにより、記憶層15は、低抵抗状態LRから高抵抗状態HRに変化するため、ゲート絶縁層43が厚くなったことになり、メモリセル(MISトランジスタ)の閾値は、高くなる。

【0093】

このように、フラッシュメモリと類似した原理により、メモリセルの閾値を変えることができ、不揮発性記憶装置として利用できる。

本実施形態に係る不揮発性記憶装置260においては、記憶層15として第1の実施形態に関して説明した記憶層15を用いているので、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置が提供できる。

【0094】

図15は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

図16(a)〜図16(c)は、第4の実施形態に係る別の不揮発性記憶装置を例示する模式的断面図である。

本実施形態に係る別の不揮発性記憶装置261は、NAND型フラッシュメモリである。図15は、NANDセルユニット261cの回路図を示している。図26(a)は、NANDセルユニット261cの構造を例示している。

【0095】

図15に表したように、NANDセルユニット261cは、直列接続される複数のメモリセルMCからなるNANDストリングと、その両端に1つずつ接続される合計2つのセレクトゲートトランジスタSTと、を含む。

【0096】

図16(a)に表したように、p形半導体基板41a内には、n形ウェル領域41b及びp形ウェル領域41cが設けられる。p形ウェル領域41c内に、NANDセルユニット261cが形成される。

【0097】

この例では、メモリセルMCは、セレクトゲートトランジスタSTと同じ構造を有する。具体的には、これらは、n形拡散層42と、n形拡散層42の間のチャネル領域42c上のゲート絶縁層43と、ゲート絶縁層43上の記憶層15と、記憶層15上のコントロールゲート電極45と、を含む。

【0098】

図15に表したように、各コントロールゲート電極45(CG)は、駆動部600に電気的に接続される。なお、駆動部600は、NANDセルユニット261cが設けられる基板に設けられても良く、それとは別の基板に設けられても良い。

【0099】

メモリセルMCの記憶層15の状態(高抵抗状態HR及び低抵抗状態LR)は、図14に関して説明した動作により変化させることが可能である。これに対し、セレクトゲートトランジスタSTの記憶層15は、セット状態、すなわち、低抵抗状態LRに固定される。

【0100】

セレクトゲートトランジスタSTの1つは、ソース線SLに接続され、他の1つは、ビット線BLに接続される。

【0101】

セット(書き込み)動作SOの前には、NANDセルユニット261c内の全てのメモリセルは、リセット状態(抵抗大)になっているものとする。セット(書き込み)動作SOにおいては、ソース線SL側のメモリセルMCからビット線BL側のメモリセルに向かって1つずつ順番に行われる。選択されたワード線(コントロールゲート電極)WLに書き込み電位としてV1(正電位)を与え、非選択のワード線WLに転送電位(メモリセルMCがオンになる電位)としてVpassを与える。ソース線SL側のセレクトゲートトランジスタSTをオフ、ビット線BL側のセレクトゲートトランジスタSTをオンにし、ビット線BLから選択されたメモリセルMCのチャネル領域42cにプログラムデータを転送する。

【0102】

例えば、プログラムデータが“1”の時は、選択されたメモリセルMCのチャネル領域42cに書き込み禁止電位(例えば、V1と同じ程度の電位)を転送し、選択されたメモリセルMCの記憶層15の抵抗値が高い状態から低い状態に変化しないようにする。

【0103】

また、プログラムデータが“0”の時は、選択されたメモリセルMCのチャネル領域42cにV2(<V1)を転送し、選択されたメモリセルMCの記憶層15の抵抗値を高い状態から低い状態に変化させる。

【0104】

一方、リセット(消去)動作ROでは、例えば、全てのワード線(コントロールゲート電極)WLにV1’を与え、NANDセルユニット261c内の全てのメモリセルMCをオンにする。また、2つのセレクトゲートトランジスタSTをオンにし、ビット線BLにV3を与え、ソース線SLにV4(<V3)を与える。

【0105】

この時、ホットエレクトロンがNANDセルユニット261c内の全てのメモリセルMCの記憶層15に注入されるため、NANDセルユニット261c内の全てのメモリセルMCに対して一括してリセット動作が実行される。

【0106】

読み出し動作は、選択されたワード線(コントロールゲート電極)WLに読み出し電位(正電位)を与え、非選択のワード線(コントロールゲート電極)WLには、メモリセルMCがデータ“0”、“1”によらず必ずオンになる電位を与える。

また、2つのセレクトゲートトランジスタSTをオンにし、NANDストリングに読み出し電流を供給する。

選択されたメモリセルMCは、読み出し電位が印加されると、それに記憶されたデータの値に応じてオンまたはオフになるため、例えば、読み出し電流の変化を検出することにより、データを読み出すことができる。

【0107】

図16(b)に表したように、本実施形態に係る別の不揮発性記憶装置262では、セレクトゲートトランジスタSTについては、記憶層15を設けずに、通常のMISトランジスタが用いられている。このように、セレクトゲートトランジスタSTの構造は任意である。

【0108】

図16(c)に表したように、本実施形態に係る別の不揮発性記憶装置263では、NANDストリングを構成する複数のメモリセルMCのゲート絶縁層がp形半導体層47に置き換えられている。

【0109】

図17は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

図18は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

本実施形態に係る別の不揮発性記憶装置264は、NOR型フラッシュメモリである。図17は、NORセルユニット264cの回路図を示している。図18は、NORセルユニット264cの構造を例示している。

【0110】

図18に表したように、p形半導体基板41a内には、n形ウェル領域41b及びp形ウェル領域41cが形成される。p形ウェル領域41c内に、NORセルが形成される。NORセルは、ビット線BLとソース線SLとの間に接続される1つのメモリセル(MISトランジスタ)MCを含む。メモリセルMCは、n形拡散層42と、n形拡散層42の間のチャネル領域42c上のゲート絶縁層43と、ゲート絶縁層43上の記憶層15と、記憶層15上のコントロールゲート電極45と、を含む。

【0111】

図17に表したように、各コントロールゲート電極45(CG)は、駆動部600に電気的に接続される。なお、駆動部600は、NORセルユニット264cが設けられる基板に設けられても良く、それとは別の基板に設けられても良い。不揮発性記憶装置264においても、図14に関して説明した動作が実施される。

【0112】

図19は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

図20は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

本実施形態に係る別の不揮発性記憶装置265は、2トラ型フラッシュメモリである。図19は、2トラセルユニット265cの回路図を示している。図20は、2トラセルユニット265cの構造を例示している。

【0113】

図19及び図20に表したように、2トラセルユニット265cは、NANDセルユニットの特徴とNORセルの特徴とを併せ持ったセル構造を有する。

【0114】

p形半導体基板41a内には、n形ウェル領域41b及びp形ウェル領域41cが形成される。p形ウェル領域41c内に、2トラセルユニット265cが形成される。

【0115】

2トラセルユニット265cは、直列接続される1つのメモリセルMCと、1つのセレクトゲートトランジスタSTと、を含む。メモリセルMCは、セレクトゲートトランジスタSTと同じ構造を有する。具体的には、これらは、n形拡散層42と、n形拡散層42の間のチャネル領域42c上のゲート絶縁層43と、ゲート絶縁層43上の記憶層15と、記憶層15上のコントロールゲート電極45と、を含む。セレクトゲートトランジスタSTは、ソース線SLに接続され、メモリセルMCは、ビット線BLに接続される。各コントロールゲート電極45(CG)は、駆動部600に電気的に接続される。なお、駆動部600は、2トラセルユニット265cが設けられる基板に設けられても良く、それとは別の基板に設けられても良い。不揮発性記憶装置265においても、図14に関して説明した動作が実施される。

【0116】

図21は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

図21に表したように、本実施形態に係る別の不揮発性記憶装置266では、セレクトゲートトランジスタSTについては、記憶層15を設けずに、通常のMISトランジスタが用いられている。このように、セレクトゲートトランジスタSTの構造は、任意である。

【0117】

また、実施形態に係る不揮発性記憶装置を記憶媒体に応用しても良い。

【0118】

本実施形態によれば、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置が提供される。

【0119】

以上、具体例を参照しつつ、本発明の実施の形態について説明した。しかし、本発明の実施形態は、これらの具体例に限定されるものではない。例えば、不揮発性記憶装置に含まれる第1導電部、第2導電部、記憶層、整流素子、基板、配線及び駆動部などの各要素の具体的な構成に関しては、当業者が公知の範囲から適宜選択することにより本発明を同様に実施し、同様の効果を得ることができる限り、本発明の範囲に包含される。

また、各具体例のいずれか2つ以上の要素を技術的に可能な範囲で組み合わせたものも、本発明の要旨を包含する限り本発明の範囲に含まれる。

【0120】

その他、本発明の実施の形態として上述した不揮発性記憶装置を基にして、当業者が適宜設計変更して実施し得る全ての不揮発性記憶装置も、本発明の要旨を包含する限り、本発明の範囲に属する。

【0121】

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

【0122】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0123】

10…第1導電部、 15…記憶層、 17…金属層、 20…第2導電部、 22…記憶部、 30…基板、 31…ワード線ドライバ、 32…ビット線ドライバ、 33…メモリセル、 33B…保護層、 34…整流素子、 35…ヒータ層、 41…半導体基板、 41a…p形半導体基板、 41b…n形ウェル領域、 41c…p形ウェル領域、 42…拡散層(n形核酸層)、 42c…チャネル領域、 43…ゲート絶縁層、 45…コントロールゲート電極、 47…p形半導体層、 51…第1陽イオン、 52…第2陽イオン、 52m…金属原子、 53…陰イオン、 110、210、211、212、220、250、260、261〜266…不揮発性記憶装置、 261c…NANDセルユニット、 264c…NORセルユニット、 265c…2トラセルユニット、 515…ドライバ、 516…XYスキャナ、 520…基板、 521…電極、 523…基板、 524…プローブ、 525、526…マルチプレクスドライバ、 531…データエリア、 532…サーボエリア、 600…駆動部、 Ae、Ai…矢印、 BL…ビット線、 CWS…トランジスタ、 HR…高抵抗状態、 LR…低抵抗状態、 MC…メモリセル、 RSW…トランジスタ、 SL…ソース線、 ST…セレクトゲートトランジスタ、 WL…ワード線

【技術分野】

【0001】

本発明の実施形態は、不揮発性記憶装置に関する。

【背景技術】

【0002】

近年、小型携帯機器が世界的に普及し、同時に、高速情報伝送網の大幅な進展に伴い、小型で大容量の不揮発性記憶装置の需要が急速に拡大してきている。記憶密度の限界を大幅に超えることを目指した新規メモリがいくつか提案されている。例えば、低抵抗状態と高抵抗状態とを有する抵抗変化材料を用いたメモリが提案されている。抵抗変化型の不揮発性装置において、安定して高い性能を発揮することが望まれる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−84512号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置を提供する。

【課題を解決するための手段】

【0005】

本発明の実施形態によれば、第1導電部と、第2導電部と、記憶層と、を含む不揮発性記憶装置が提供される。前記記憶層は、前記第1導電部と前記第2導電部との間に設けられる。前記記憶層は、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能である。前記記憶層は、カルコパイライト構造を有する。

【図面の簡単な説明】

【0006】

【図1】第1の実施形態に係る不揮発性記憶装置の構成を例示する模式的断面図である。

【図2】第1の実施形態に係る不揮発性記憶装置の構成を例示する模式図である。

【図3】第1の実施形態に係る不揮発性記憶装置の動作を例示する模式図である。

【図4】不揮発性記憶装置の特性を例示する表である。

【図5】不揮発性記憶装置の特性を例示するグラフ図である。

【図6】第2の実施形態に係る不揮発性記憶装置の構成を例示する模式的斜視図である。

【図7】第2の実施形態に係る不揮発性記憶装置の構成を例示する模式図である。

【図8】第2の実施形態に係る不揮発性記憶装置の一部の構成を例示する模式的断面図である。

【図9】第2の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的斜視図である。

【図10】第2の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的斜視図である。

【図11】第3の実施形態に係る不揮発性記憶装置の構成を例示する模式的斜視図である。

【図12】第3の実施形態に係る不揮発性記憶装置の構成を例示する模式的平面図である。

【図13】第4の実施形態に係る不揮発性記憶装置の構成を例示する模式的断面図である。

【図14】第4の実施形態に係る不揮発性記憶装置の動作を例示する模式的断面図である。

【図15】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

【図16】図16(a)〜図16(c)は、第4の実施形態に係る別の不揮発性記憶装置を例示する模式的断面図である。

【図17】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

【図18】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

【図19】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

【図20】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

【図21】第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

【発明を実施するための形態】

【0007】

以下に、本発明の各実施の形態について図面を参照しつつ説明する。

なお、図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

なお、本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

【0008】

(第1の実施形態)

図1は、第1の実施形態に係る不揮発性記憶装置の構成を例示する模式的断面図である。

図1に表したように、本実施形態に係る不揮発性記憶装置110は、第1導電部10と、第2導電部20と、記憶層15と、を含む。記憶層15は、第1導電部10と第2導電部20との間に設けられる。

【0009】

記憶層15には、第1導電部10と第2導電部20とを介して電流が供給される。記憶層15は、その電流により、抵抗が低い第1状態(低抵抗状態)と、第1状態よりも抵抗が高い第2状態(高抵抗状態)との間を可逆的に遷移可能である。記憶層15は、カルコパイライト構造を有する。

【0010】

記憶層15は、例えば、AxMyXzで表される材料を含む。ここで、「A」は、例えば、Mn、Fe、Co、Ni、Cu、Zn、Mg、Al及びGaよりなる群から選択された少なくともいずれかである。「M」は、例えば、Si、Ge、Al及びGaよりなる群から選択された少なくともいずれかである。「X」は、例えば、N、P及びAsよりなる群から選択された少なくともいずれかを含む。

【0011】

上記の「M」は、「A」とは異なる元素を含む。これにより、AxMyXzで表される化合物は、カルトパイライト構造となる。

【0012】

また、実施形態において、「A」は、遷移元素を含むことができる。例えば、Aとして遷移元素が用いられる。また、Aとして、複数の種類の元素(例えば元素αと元素β)が用いられる場合において、複数の元素の少なくともいずれかが遷移元素とすることができる。例えば、記憶層15として(αx1β1−x1)xMyXzで表される材料を用いることができ、元素α及び元素βの少なくともいずれかは、遷移元素である。

【0013】

図2は、第1の実施形態に係る不揮発性記憶装置の構成を例示する模式図である。

図2は、記憶層15の結晶構造を例示している。なお、この例では、「A」はCoであり、「M」はSiであり、「X」はNである。図2に表したように、記憶層15は、カルコパイライト構造を有する。

【0014】

例えば、酸化物を用いた抵抗変化素子を半導体プロセスにさらすと、抵抗変化素子の特性が大きく変化する場合があることが分かった。例えば、抵抗変化素子に用いられる酸化物が過酷な半導体プロセスにより変質し、実際のデバイスを形成したときに所望の特性が得難いことが分かった。特に、半導体プロセスで用いられるウエットプロセスを酸化物の抵抗変化部に適用すると、所望の特性を維持することが困難である。例えば、抵抗変化素子が半導体プロセスを経るとダメージを受け、抵抗変化素子におけるスイッチング回数が減る。このことは、本願発明者が実験により見出した課題であり、実施形態は、この新に見出された課題を解決する。

【0015】

本実施形態に係る不揮発性記憶装置110においては、記憶層15として、カルコパイライト構造を有する化合物を用いる。カルコパイライト構造を有する化合物においては、元素どうしが強固に結合しているため、プロセス耐性が高い。そして、実施形態においては、記憶層15として、酸化物などのような比較的不安定な材料を用いた場合に比べて、種々のプロセスを経た後でも、良好で安定した特性を維持できる。

【0016】

以下、本実施形態に係る不揮発性記憶装置110における動作の例をモデル的に説明する。

図3は、第1の実施形態に係る不揮発性記憶装置の動作を例示する模式図である。

図3に表したように、記憶層15は、抵抗(抵抗率)が低い低抵抗状態(低抵抗状態LR)と、低抵抗状態よりも抵抗(抵抗率)が相対的に高い高抵抗状態(高抵抗状態HR)とを有する。記憶層15において、低抵抗状態LRと、高抵抗状態HRと、の間を可逆的に遷移可能である。

【0017】

以下では、記憶層15の初期状態が高抵抗状態HRである場合として説明する。

記憶層15に設けられた電位勾配により、記憶層15を変化させ、記憶層15を低抵抗状態LRにすることにより情報の書き込みを行う。

【0018】

記憶層15は、位置が固定された陽イオン(第1陽イオン51)と、移動可能な陽イオン(第2陽イオン52)と、陰イオン53と、を含む。例えば、第1陽イオン51として上記の「M」の元素が用いられ、第2陽イオン52として上記の「A」の元素が用いられ、陰イオン53として上記の「X」の元素が用いられる。例えば、第2陽イオン52の少なくとも一部は、遷移元素である。すなわち、第2陽イオン52の価数は変化可能である。

【0019】

まず、例えば、第2導電部20の電位が、第1導電部10の電位よりも相対的に低い状態を作る。例えば、第1導電部10を固定電位(例えば、接地電位)とし、第2導電部20に負の電位を与える。これにより、第2陽イオン52の一部が結晶中(記憶層15の中)を第2導電部20(陰極)に向けて移動する。結晶である記憶層15の内部において、第2陽イオン52の数が、陰イオン53に対して相対的に減少する。

【0020】

第2導電部20の側に移動した第2陽イオン52は、第2導電部20から電子を受取り、例えば、金属原子52mとして析出して金属層17が形成される。すなわち、記憶層15のうちで第2導電部20に近い領域では、第2陽イオン52が還元されて金属的に振る舞う。これにより、電気抵抗が減少する。

【0021】

一方、記憶層15の内部では、陰イオン53が過剰となるため、記憶層15の内部に残された第2陽イオン52の価数が上昇する。これにより、記憶層15において、電子伝導性が発現する。その結果、記憶層15全体として、低抵抗状態LRへと変化する。この動作を、セット動作SOという。セット動作SOは、例えば書き込み動作である。

【0022】

書き込んだ情報の読み出しは、例えば電圧パルスを記憶層15に印加し、記憶層15の抵抗値を検出することにより行う。この時、電圧パルスの大きさは、記憶層15の抵抗が変化しない程度の微小な値とされる。

【0023】

なお、以上説明した過程は、一種の電気分解である。例えば、第1導電部10(陽極)の側では電気化学的酸化により酸化剤が生じ、第2導電部20(陰極)の側では電気化学的還元により還元剤が生じる。

【0024】

一方、低抵抗状態LRを高抵抗状態HRに戻す動作(リセット動作RO)の際には、例えば、記憶層15に大電流パルスを印加し、それによるジュール熱によって記憶層15を加熱して、記憶層15の酸化還元反応を促進させる。ジュール熱により、第2陽イオン52は、熱的により安定な結晶構造内(記憶層15の内部)へと戻り、初期の高抵抗状態HRが現れる。リセット動作ROは、例えば消去動作である。

【0025】

また、セット動作SOとは逆極性の電圧パルスを印加してもリセット動作ROを行うことができる。例えば、第1導電部10を固定電位とし、第2導電部20に正の電位を与えることにより、第2導電部20の近傍の金属原子52mは第2導電部20に電子を与え、第2陽イオン52となる。第2陽イオン52は、記憶層15内の電位勾配により記憶層15の内部に戻る。これにより、初期の高抵抗状態HRへと変化する。

このようにして、本実施形態に係る不揮発性記憶装置110の書き込み動作及び消去動作、すなわち、セット動作SO及びリセット動作ROが行われる。

【0026】

実施形態おいては、例えば、カルコパイライト構造を有する化合物(結晶)における、陽イオンの移動に基づく電流が利用される。この陽イオンの移動を容易にするために、イオン半径が大きい陰イオンを用いる。例えば、「X」として、N、P及びAsよりなる群から選択された少なくともいずれかを用いることにより、陰イオンのイオン半径を大きくすることができ、陽イオンが容易に移動できるようになる。

【0027】

なお、記憶層15として酸化物を用いた場合においては、酸素イオンが陰イオンとなる。酸素イオン(陰イオン)のイオン半径は小さく、陽イオンが移動し難い。このため、この構成においては、良好なスイッチングが得にくいと考えられる。

【0028】

実施形態に係る不揮発性記憶装置110においては、陽イオンの移動を容易にする構成を用いることで、良好で安定した電気的特性を得ることができる。

【0029】

また、記憶層15として、窒化物の材料を用いることで、プロセス耐性を向上し易くなる。このように、「X」として、N、P及びAsのように3価の元素(陰イオン53となる元素)を用いることで、プロセス耐性が向上し易くなる。

【0030】

実施形態においては、記憶層15として、非酸化物を用いる。そして、陰イオンの価数をあげることで耐性が向上する。例えば、珪素と酸素とを含む骨格よりも珪素と窒素とを含む骨格の方が強い。さらに、酸素よりも窒素の方が、イオン半径が大きい。窒素を用いることで、陽イオン(例えばCoイオン)が結晶構造中を通る経路が大きくなり、陽イオンが動き易くできる。これにより、スイッチング確率が高くなる。そして、耐久性(endurance)が向上する。

【0031】

なお、カルコパイライト構造を有する化合物としてCuInSe2などがある。この化合物の太陽電池などへ応用が検討されている。この場合には、電子が励起され、励起された電子が移動する機構が利用される。すなわち、太陽電池においては、イオンが移動する機構ではなく、電子の移動に基づく電流が利用される。これに対して、実施形態に係る不揮発性記憶装置110においては、カルコパイライト構造を有する化合物におけるイオン(例えば陽イオン)の移動が利用される。

【0032】

例えば、スピネル構造を有する材料は、電池の材料として用いることができ、この構造においてイオンが移動する機構は知られている。しかしながら、カルコパイライト構造を有する化合物におけるイオンの移動を利用したデバイスについては従来知られていない。本実施形態においては、カルコパイライト構造におけるイオンの移動に基づく抵抗の変化が利用される。

【0033】

実施形態において、記憶層15が上記のAxMyXzで表される材料を含む場合において、「A」が遷移元素を含むことで、例えば、記憶動作におけるリテンション時間を長くすることができる。

【0034】

以下、記憶層15に関する材料の特性の例について説明する。以下では、種々の組成の材料に関して、プロセス耐性としてDHF(100倍に希釈した希釈フッ酸)処理後のスイッチング確率について説明する。

【0035】

試料においては、直径が約60mmで、厚さ約1mmのガラス基板からなるディスクが用いられる。このディスクの上に、下部電極層が設けられ、下部電極層の上に記憶層15となる試料層が設けられ、その上に上部電極層(保護層)が設けられる。下部電極層及び上部電極層(保護層)には、厚さが500nmのPt膜が用いられる。

【0036】

記憶層15となる原料を含む所定のターゲットを用い、所定の雰囲気でのRFマグネトロンスパッタにより、記憶層15が形成できる。記憶層15の形成の際のディスクの温度は300℃〜600℃の範囲内の値に維持される。記憶層15の厚さは、約10nmである。記憶層15は、形成された後に、上記のDHFに1分間接触させられる。

【0037】

上部電極層に、タングステン(W)のプローブを接触させ、記憶層15に電流を通電する。プローブの先端の径は、約10nmである。書き込み動作においては、下部電極層とプローブとの間に10ナノ秒(ns)で1ボルト(V)の電圧パルスを印加する。消去動作においては、下部電極層とプローブとの間に、100nsで0.1Vの電圧パルスを印加する。この書き込み動作と消去動作とを繰り返して実施したときに、記憶層15における高抵抗状態HRの抵抗値の、低抵抗状態LRの抵抗値に対する比(オンオフ比)が1,000以上であるときのスイッチング回数SWN(サイクル)が評価値として用いられる。

【0038】

第1試料においては、記憶層15としてCoSiN2が用いられる。第1試料における記憶層15は、Co:Si=1:1の合金ターゲットを用い、50%のArと、50%のN2と、を含む雰囲気中でのRFマグネトロンスパッタにより形成される。第1試料においては、10箇所の通電点において、スイッチング回数SWNは10,000サイクル以上である。

【0039】

以下の各試料において、説明しない部分は、上記の第1試料と同様である。

第2試料においては、記憶層15としてMnSiN2が用いられる。

第3試料においては、記憶層15としてFeSiN2が用いられる。

第4試料においては、記憶層15としてFe0.7SiN2が用いられる。

第5試料においては、記憶層15としてMnGeN2が用いられる。

第6試料においては、記憶層15としてFeGeN2が用いられる。

第7試料においては、記憶層15としてCoGeN2が用いられる。

第8試料においては、記憶層15としてFe0.7GeN2が用いられる。

第9試料においては、記憶層15としてCoSiP2が用いられる。

第10試料においては、記憶層15としてMnSiP2が用いられる。

第11試料においては、記憶層15としてFeSiP2が用いられる。

第12試料においては、記憶層15としてFe0.7SiP2が用いられる。

第13試料においては、記憶層15としてMnGeP2が用いられる。

第14試料においては、記憶層15としてFeGeP2が用いられる。

第15試料においては、記憶層15としてCoGeP2が用いられる。

第16試料においては、記憶層15としてFe0.7GeP2が用いられる。

第17試料においては、記憶層15としてCo0.5Zn0.5SiN2が用いられる。

第18試料においては、記憶層15としてMn0.5Zn0.5SiN2が用いられる。

第19試料においては、記憶層15としてFe0.5Zn0.5SiN2が用いられる。

第20試料においては、記憶層15としてFe0.5Zn0.25SiN2が用いられる。

【0040】

以上の第2〜第20試料においては、10箇所の通電点において、スイッチング回数SWNは10,000サイクル以上である。

【0041】

第21試料においては、記憶層15としてZnV2O4が用いられる。

第22試料においては、記憶層15としてZnCr2O4が用いられる。

第23試料においては、記憶層15としてZnMn2O4が用いられる。

第24試料においては、記憶層15としてZnCo2O4が用いられる。

第25試料においては、記憶層15としてMgCr2O4が用いられる。

第26試料においては、記憶層15としてMgMn2O4が用いられる。

【0042】

第21〜第26試料のそれぞれにおいて、試料の1,000箇所にプローブを接触させたときに、1,000以上のオンオフ比が得られるのは、それぞれ、2箇所、1箇所、2箇所、4箇所、6箇所、7箇所である。第21〜第26試料においては、1サイクルのスイッチング確率は、70%未満である。

【0043】

第1〜第20試料においては、記憶層15はカルコパイライト構造を有する。第21〜第26試料においては、記憶層15はカルコパイライト構造を有していない。このように、記憶層15がカルコパイライト構造を有することで、DHF処理のようなプロセスを経た後においても、良好な電気的特性が得られる。

【0044】

このように、記憶層15は、例えば、窒化コバルト、珪窒化マンガン、珪窒化鉄、窒化ゲルマニウムマンガン、窒化ゲルマニウム鉄、窒化ゲルマニウムコバルト、珪リン化コバルト、珪リン化マンガン、珪リン化鉄、リン化ゲルマニウムマンガン、リン化ゲルマニウム鉄、リン化ゲルマニウムコバルト、珪窒化コバルト亜鉛、珪窒化マンガン亜鉛、及び、珪窒化鉄亜鉛よりなる群から選択された少なくともいずれかを含む。

【0045】

本実施形態において、記憶層15に含まれるAxMyXzの組成比xは、例えば、0.3≦x≦1を満たす。上記の組成比yは、0.9≦y≦1.1を満たす。さらに、1.9≦(z/y)≦2.1を満たす。

これにより、プロセス耐性が高い記憶層15を得易くなる。これにより、高い性能を維持する不揮発性記憶装置が提供できる。

【0046】

以下、組成比x、組成比y及び組成比zを変えたときの記憶層15の特性の例について説明する。

図4は、不揮発性記憶装置の特性を例示する表である。

図4には、カルコパイライト構造を有する化合物AxMyXzにおいて、組成比x、組成比y及び組成比zを変えたときの、スイッチング回数(寿命)の判定Evを示している。ここで、記憶層15において、低抵抗状態と高抵抗状態との相互の遷移(スイッチング)を繰り返したときに、オンオフ比が1,000以上を維持できるスイッチング回数SWNが10,000サイクル以上の場合が、良好な特性が得られている状態である。スイッチング回数SWNが10,000サイクル未満の場合は、特性が良くない状態である。

図4においては、良好な特性が得られている状態は、「判定Ev」に関して「X」と表示されている。特性が良くない状態は、「判定Ev」に関して「O」と表示されている。 図4においては、「A」としてCoを用い、「M」としてSiを用い、「X」としてNを用いた時の例が示されている。

【0047】

図4から分かるように、組成比xが0.29以下または1.01以上のときは、良好な特性が得られない(判定Evは「X」)。組成比xが0.31以上0.99以下であっても、組成比yが、0.89以下、または、1.11以上のときは、良好な特性が得られない(判定Evは「X」)。

【0048】

これに対し、組成比xが0.31以上0.99以下であり、かつ、組成比yが、0.91以上1.09以下のときに、組成比zの値によって、良好な特性が得られる条件が存在する(判定Evは「O」)。

【0049】

図5は、不揮発性記憶装置の特性を例示するグラフ図である。

図5は、図4に例示した、組成比xが0.31以上で0.99以下の試料に関し、組成比y及び組成比zと、判定Evと、の関係を示している。図5の横軸は組成比yであり、図5の縦軸は組成比zである。図5中の「O」の表示は、良好な特性が得られること(スイッチング回数SWNが10,000サイクル以上)を示し、図5中の「X」の表示は、特性が良くないこと(スイッチング回数SWNが10,000サイクル未満)を示す。

【0050】

図5から分かるように、組成比yが、0.89以下、または、1.11以上のときは、良好な特性が得られないのに対して組成比yが、0.91以上1.09以下のときに、良好な特性が得られる。このことから、0.9≦y≦1.1のときに良好な特性が得られると考えられる。

【0051】

そして、良好な特性が得られる組成比zの条件は、組成比yによって変化する。すなわち、この例では、1.9y≦z≦2.1yのときに良好な特性が得られる。すなわち、1.9≦(z/y)≦2.1のときに良好な特性が得られる。

【0052】

また、図4では、「A」がCoで、「M」がSiで、「X」がNの時の例が示されているが、Aが、Mn、Fe、Ni、Cu、Zn、Mg、AlまたはGaのときも同様の傾向となる。また、Mが、Ge、AlまたはGaのときも同様の傾向となる。また、Xが、PまたはAsのときも同様の傾向となる。

【0053】

以上から、実施形態においては、上記のAxMyXzで表された材料を記憶層15に用いる場合、0.3≦x≦1、0.9≦y≦1.1、及び、1.9≦(z/y)≦2.1を満たす条件に設定することが好ましい。これにより、良好なスイッチング特性がより得易くなる。

【0054】

なお、「X」は、1%以下のハロゲン元素を含むことができる。「X」が、ハロゲン元素を含むことにより、例えば結晶化温度が低くなる。また、「X」が、ハロゲン元素を含むことにより、スイッチング特性のばらつきを小さくすることができる。

【0055】

本実施形態において、第1導電部10及び第2導電部20の少なくともいずれかは、不純物がドープされた、Si、及び、III-V族化合物半導体の少なくともいずれかを含むことが望ましい。

【0056】

Siは、ダイヤモンド構造を有する。ダイヤモンド構造は、カルコパイライト構造に類似する。III-V族化合物半導体は、ウルファイト構造または閃亜鉛構造を有する。これらの結晶構造も、カルコパイライト構造と類似する。Si、及び、III-V族化合物半導体における元素の結びつきの状態は、記憶層15における元素の結びつきの状態と、同様になる。

【0057】

記憶層15における結晶構造と類似の結晶構造を有する材料を、第1導電部10及び第2導電部20の少なくともいずれかに用いることで、例えば、他の材料を用いた場合に比べて、記憶層15における結晶欠陥が低減できる。また、第1導電部10と記憶層15との間の界面、及び、第2導電部20と記憶層15との間の界面における結晶の劣化が抑制できる。これにより、良好な電気的特性が得易くなる。

【0058】

(第2の実施形態)

本実施形態に係る不揮発性記憶装置は、クロスポイント型の構成を有する。

図6は、第2の実施形態に係る不揮発性記憶装置の構成を例示する模式的斜視図である。

図7は、第2の実施形態に係る不揮発性記憶装置の構成を例示する模式図である。

図6及び図7に表したように、本実施形態に係る不揮発性記憶装置210においては、基板30が設けられる。基板30の主面に対して並行な平面をX−Y平面とする。X−Y平面内の1つの方向をX軸方向とする。X−Y平面内においてX軸方向に対して垂直な方向をY軸方向とする。X軸方向とY軸方向とに対して垂直な方向をZ軸方向とする。

【0059】

不揮発性記憶装置210において、基板30の主面の上に、X軸方向に延在する帯状の第1の配線(ワード線WLi−1、WLi、WLi+1)が設けられる。さらに、Y軸方向に延在する帯状の第2の配線(ビット線BLj−1、BLj、BLj+1)が、設けられる。第2の配線(ビット線BLj−1、BLj、BLj+1)は、第1の配線(ワード線WLi−1、WLi、WLi+1)に対向する。

【0060】

なお、上記では、第1の配線の延在方向が第2の配線の延在方向に対して直交するが、第1の配線の延在方向が第2の配線の延在方向と交差(非平行)すれば良い。

【0061】

なお、上記において添え字i及び添え字jは任意である。すなわち、第1の配線の数及び第2の配線の数は、任意である。

本具体例では、第1の配線がワード線となり、第2の配線がビット線となる。ただし、第1の配線がビット線で、第2の配線がワード線でも良い。以下では、第1の配線がワード線であり、第2の配線がビット線であるとして説明する。

【0062】

図6及び図7に表したように、第1の配線と第2の配線との間にメモリセル33が設けられる。

【0063】

図7に表したように、例えば、ワード線WLi−1、WLi、WLi+1の一端は、選択スイッチであるMOSトランジスタRSWを介して、デコーダ機能を有するワード線ドライバ31に接続される。ビット線BLj−1、BLj、BLj+1の一端は、選択スイッチであるMOSトランジスタCSWを介して、デコーダ及び読み出し機能を有するビット線ドライバ32に接続される。

【0064】

MOSトランジスタRSWのゲートには、ワード線(ロウ)を選択するための選択信号Ri−1、Ri、Ri+1が入力され、MOSトランジスタCSWのゲートには、ビット線(カラム)を選択するための選択信号Ci−1、Ci、Ci+1が入力される。

【0065】

メモリセル33は、ワード線WLi−1、WLi、WLi+1と、ビット線BLj−1、BLj、BLj+1と、が互いに対向する交差部に配置される。メモリセル33には、書き込み/読み出し時における回り込み電流(sneak current)を防止するための整流素子34を付加することができる。

【0066】

図8は、第2の実施形態に係る不揮発性記憶装置の一部の構成を例示する模式的断面図である。

図8に表したように、ワード線WLiとビット線BLjとの間には、メモリセル33及び整流素子34が設けられる。なお、ワード線WLiとビット線BLjとの上下の配置の関係は任意である。ワード線WLiとビット線BLjとの間における、メモリセル33と整流素子34との配置の順番は、任意である。

【0067】

図8に表したように、メモリセル33は、記憶部22を含む。記憶部22は、第1導電部10と、第2導電部20と、第1導電部10と第2導電部20との間に設けられた記憶層15と、を含む。記憶層15には、第1の実施形態に関して説明した構成が適用できる。

【0068】

メモリセル33は、保護層33Bをさらに含むことができる。本具体例では、保護層33Bは、記憶部22のビット線BLjの側に設けられているが、保護層33Bは、記憶部22のワード線WLiの側に設けても良く、整流素子34とワード線WLiとの間に設けても良い。メモリセル33は、記憶部22と保護層33Bとの間に設けられたヒータ層35をさらに含むことができる。ヒータ層35及び保護層33Bは、必要に応じて設けられ、省略可能である。

【0069】

なお、第1導電部10及び第2導電部20の少なくともいずれかとして、記憶部22に隣接する、例えば、ワード線WLi、整流素子34、ヒータ層35、保護層33B、ビット線BLjの少なくともいずれかを用いても良い。

【0070】

図9及び図10は、第2の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的斜視図である。

図9及び図10に表したように、本実施形態に係る不揮発性記憶装置211及び212においては、ワード線、ビット線、及び、それらの間に設けられたメモリセル33を含む積層構造体が、複数積み重ねられる。これにより、3次元構造の不揮発性記憶装置が形成される。

【0071】

本実施形態に係る不揮発性記憶装置210、211、212においては、駆動部となるワード線ドライバ31及びビット線ドライバ32は、ワード線WLi及びビット線BLjを介して、記憶層15への電圧の印加、及び、記憶層15への電流の通電、の少なくともいずれかを行う。これにより、記憶層15に変化を発生させて情報を書き込む。例えば、駆動部は、記憶層15に電圧を印加して記憶層15に変化を発生させて情報を書き込む。また、書き込んだ情報を読み出すことができる。また、消去を行うことができる。

【0072】

本実施形態に係る不揮発性記憶装置210、211、212においても、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置が提供できる。

【0073】

(第3の実施の形態)

本実施形態に係る不揮発性記憶装置は、プローブメモリ型の構成を有する。

図11は、第3の実施形態に係る不揮発性記憶装置の構成を例示する模式的斜視図である。

図12は、第3の実施形態に係る不揮発性記憶装置の構成を例示する模式的平面図である。

図11及び図12に表したように、本実施形態に係る不揮発性記憶装置250では、XYスキャナ516の上に、電極521の上に設けられた記憶層15が配置されている。記憶層15に対向するように、プローブアレイが配置される。電極521は、例えば、基板520上に設けられる。

【0074】

プローブアレイは、例えば、基板523と、基板523の一面側にアレイ状に配置される複数のプローブ(ヘッド)524と、を有する。プローブ524として、例えば、カンチレバーが用いられる。複数のプローブ524は、マルチプレクスドライバ525、526により駆動される。

複数のプローブ524は、それぞれ、基板523内のマイクロアクチュエータを用いて個別に動作可能である。また、全てをまとめて同じ動作をさせて記憶媒体(記憶層15)のデータエリア531に対してアクセスを行うこともできる。

【0075】

例えば、電極521が第1導電部10として用いられ、プローブ524が第2導電部20として用いられる。また、記憶層15の上に導電性の保護層が設けられる場合は、その保護層が、第2導電部20となる。

【0076】

例えば、マルチプレクスドライバ525、526を用いて、全てのプローブ524をX方向に一定周期で往復動作させ、記憶媒体(記憶層15)のサーボエリア532からY方向の位置情報を読み出す。Y方向の位置情報は、ドライバ515に転送される。

ドライバ515は、この位置情報に基づいてXYスキャナ516を駆動し、記憶媒体(記憶層15)をY方向に移動させ、記憶媒体(記憶層15)とプローブとの位置決めを行う。

両者の位置決めが完了したら、データエリア531上のプローブ524を用いてデータの書き込み、読み出しまたは消去を行う。

【0077】

例えば、1つのデータエリア531に対応して1つのプローブ(ヘッド)が設けられ、1つのサーボエリア532に対して1つのプローブが設けられる。各プローブ524は、例えばマルチプレクスドライバ525、526を介して、駆動部600に接続される。駆動部600は、それぞれのプローブ524に、情報記憶のための、電圧及び電流の少なくともいずれかを供給する。記憶層15は、プローブ524を介して与えられた電圧及び電流によって、高抵抗状態と低抵抗状態との間を遷移する。また、駆動部600は、記憶層15に記憶された高抵抗状態と低抵抗状態とを検出し、記憶された情報を読み出す。

【0078】

このような構成の不揮発性記憶装置250は、記憶層15と、記憶層15への電圧の印加、及び、記憶層15への電流の通電、の少なくともいずれかによって、記憶層15に変化を発生させて情報を記憶する駆動部600と、を備える。不揮発性記憶装置250は、記憶層15に併設されたプローブ524をさらに備え、駆動部600は、プローブ524を介して、記憶層15の記憶単位に対して電圧の印加及び電流の通電の少なくともいずれかを行う。これにより、記憶層15に変化を発生させて情報を記憶する。

【0079】

なお、駆動部600は、上記のドライバ515及びXYスキャナ516を含むこともでき、逆に、駆動部は、上記のドライバ515及びXYスキャナ516に含まれても良い。

【0080】

本実施形態に係るプローブメモリ型の不揮発性記憶装置250においても、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置が提供できる。

【0081】

(第4の実施の形態)

本実施形態に係る不揮発性記憶装置は、フラッシュメモリ型の構成を有する。

図13は、第4の実施形態に係る不揮発性記憶装置の構成を例示する模式的断面図である。

図14は、第4の実施形態に係る不揮発性記憶装置の動作を例示する模式的断面図である。

図13に表したように、本実施形態に係る不揮発性記憶装置260においては、フラッシュメモリ型のメモリセルを有する。このメモリセルは、MIS(metal-insulator-semiconductor)トランジスタの構成を有する。

【0082】

半導体基板41の表面領域には、複数の拡散層42が形成される。複数の拡散層42の間にチャネル領域42cが設けられる。チャネル領域42c上には、ゲート絶縁層43が形成される。ゲート絶縁層43上には、実施形態に係る記憶層15が形成される。記憶層15の上には、コントロールゲート電極45が形成される。

【0083】

記憶層15は、第1の実施形態で説明した構成を有する。例えば、チャネル領域42cが第1導電部10であり、コントロールゲート電極45が第2導電部20であると見なすことができる。また、ゲート絶縁層43と、コントロールゲート電極45との間に、第1導電部10、第2導電部20及び記憶層15を含む記憶部22が設けられても良い。以下の図においては、記憶部22を、適宜、記憶層15として省略して表示する。

【0084】

半導体基板41は、ウェル領域でも良い。半導体基板41は、拡散層42の導電形に対して逆の導電形を有する。コントロールゲート電極45は、ワード線となる。コントロールゲート電極45には、例えば、導電性ポリシリコンが用いられる。

【0085】

本実施形態においては、図示しない駆動部が、コントロールゲート電極45に接続されて設けられる。駆動部は、コントロールゲート電極45を介して、記憶層15への電圧の印加、及び、記憶層15への電流の通電、の少なくともいずれかを行う。

【0086】

図14に表したように、セット(書き込み)動作SOでは、コントロールゲート電極45に電位V1を与え、半導体基板41に電位V2を与える。

電位V1及び電位V2の差は、記憶層15が変化、すなわち、抵抗が変化するのに十分な大きさである。ただし、電位の差の極性は、特に、限定されない。すなわち、V1>V2、及び、V1<V2のいずれでも良い。

【0087】

例えば、初期状態(リセット状態)において、記憶層15が高抵抗状態HRであると仮定すると、ゲート絶縁層43が厚くなったことになるため、メモリセル(MISトランジスタ)の閾値は、高くなる。

【0088】

この状態から電位V1、V2を与えて記憶層15を低抵抗状態LRに変化させると、ゲート絶縁層43が薄くなったことになるため、メモリセル(MISトランジスタ)の閾値は、低くなる。

【0089】

なお、電位V2は、半導体基板41に与えたが、これに代えて、メモリセルのチャネル領域42cに拡散層42から電位V2を転送するようにしても良い。なお、同図において、矢印Aeは電子の移動を表し、矢印Aiはイオンの移動を表している。

【0090】

一方、リセット(消去)動作ROでは、コントロールゲート電極45に電位V1’を与え、拡散層42の一方に電位V3を与え、拡散層42の他方に電位V4(<V3)を与える。電位V1’は、セット状態のメモリセルの閾値を越える値にする。

【0091】

この時、メモリセルはオンになり、電子が拡散層42の他方から一方に向かって流れると共に、ホットエレクトロンが発生する。このホットエレクトロンは、ゲート絶縁層43を介して記憶層15に注入されるため、記憶層15の温度が上昇する。

【0092】

これにより、記憶層15は、低抵抗状態LRから高抵抗状態HRに変化するため、ゲート絶縁層43が厚くなったことになり、メモリセル(MISトランジスタ)の閾値は、高くなる。

【0093】

このように、フラッシュメモリと類似した原理により、メモリセルの閾値を変えることができ、不揮発性記憶装置として利用できる。

本実施形態に係る不揮発性記憶装置260においては、記憶層15として第1の実施形態に関して説明した記憶層15を用いているので、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置が提供できる。

【0094】

図15は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

図16(a)〜図16(c)は、第4の実施形態に係る別の不揮発性記憶装置を例示する模式的断面図である。

本実施形態に係る別の不揮発性記憶装置261は、NAND型フラッシュメモリである。図15は、NANDセルユニット261cの回路図を示している。図26(a)は、NANDセルユニット261cの構造を例示している。

【0095】

図15に表したように、NANDセルユニット261cは、直列接続される複数のメモリセルMCからなるNANDストリングと、その両端に1つずつ接続される合計2つのセレクトゲートトランジスタSTと、を含む。

【0096】

図16(a)に表したように、p形半導体基板41a内には、n形ウェル領域41b及びp形ウェル領域41cが設けられる。p形ウェル領域41c内に、NANDセルユニット261cが形成される。

【0097】

この例では、メモリセルMCは、セレクトゲートトランジスタSTと同じ構造を有する。具体的には、これらは、n形拡散層42と、n形拡散層42の間のチャネル領域42c上のゲート絶縁層43と、ゲート絶縁層43上の記憶層15と、記憶層15上のコントロールゲート電極45と、を含む。

【0098】

図15に表したように、各コントロールゲート電極45(CG)は、駆動部600に電気的に接続される。なお、駆動部600は、NANDセルユニット261cが設けられる基板に設けられても良く、それとは別の基板に設けられても良い。

【0099】

メモリセルMCの記憶層15の状態(高抵抗状態HR及び低抵抗状態LR)は、図14に関して説明した動作により変化させることが可能である。これに対し、セレクトゲートトランジスタSTの記憶層15は、セット状態、すなわち、低抵抗状態LRに固定される。

【0100】

セレクトゲートトランジスタSTの1つは、ソース線SLに接続され、他の1つは、ビット線BLに接続される。

【0101】

セット(書き込み)動作SOの前には、NANDセルユニット261c内の全てのメモリセルは、リセット状態(抵抗大)になっているものとする。セット(書き込み)動作SOにおいては、ソース線SL側のメモリセルMCからビット線BL側のメモリセルに向かって1つずつ順番に行われる。選択されたワード線(コントロールゲート電極)WLに書き込み電位としてV1(正電位)を与え、非選択のワード線WLに転送電位(メモリセルMCがオンになる電位)としてVpassを与える。ソース線SL側のセレクトゲートトランジスタSTをオフ、ビット線BL側のセレクトゲートトランジスタSTをオンにし、ビット線BLから選択されたメモリセルMCのチャネル領域42cにプログラムデータを転送する。

【0102】

例えば、プログラムデータが“1”の時は、選択されたメモリセルMCのチャネル領域42cに書き込み禁止電位(例えば、V1と同じ程度の電位)を転送し、選択されたメモリセルMCの記憶層15の抵抗値が高い状態から低い状態に変化しないようにする。

【0103】

また、プログラムデータが“0”の時は、選択されたメモリセルMCのチャネル領域42cにV2(<V1)を転送し、選択されたメモリセルMCの記憶層15の抵抗値を高い状態から低い状態に変化させる。

【0104】

一方、リセット(消去)動作ROでは、例えば、全てのワード線(コントロールゲート電極)WLにV1’を与え、NANDセルユニット261c内の全てのメモリセルMCをオンにする。また、2つのセレクトゲートトランジスタSTをオンにし、ビット線BLにV3を与え、ソース線SLにV4(<V3)を与える。

【0105】

この時、ホットエレクトロンがNANDセルユニット261c内の全てのメモリセルMCの記憶層15に注入されるため、NANDセルユニット261c内の全てのメモリセルMCに対して一括してリセット動作が実行される。

【0106】

読み出し動作は、選択されたワード線(コントロールゲート電極)WLに読み出し電位(正電位)を与え、非選択のワード線(コントロールゲート電極)WLには、メモリセルMCがデータ“0”、“1”によらず必ずオンになる電位を与える。

また、2つのセレクトゲートトランジスタSTをオンにし、NANDストリングに読み出し電流を供給する。

選択されたメモリセルMCは、読み出し電位が印加されると、それに記憶されたデータの値に応じてオンまたはオフになるため、例えば、読み出し電流の変化を検出することにより、データを読み出すことができる。

【0107】

図16(b)に表したように、本実施形態に係る別の不揮発性記憶装置262では、セレクトゲートトランジスタSTについては、記憶層15を設けずに、通常のMISトランジスタが用いられている。このように、セレクトゲートトランジスタSTの構造は任意である。

【0108】

図16(c)に表したように、本実施形態に係る別の不揮発性記憶装置263では、NANDストリングを構成する複数のメモリセルMCのゲート絶縁層がp形半導体層47に置き換えられている。

【0109】

図17は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

図18は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

本実施形態に係る別の不揮発性記憶装置264は、NOR型フラッシュメモリである。図17は、NORセルユニット264cの回路図を示している。図18は、NORセルユニット264cの構造を例示している。

【0110】

図18に表したように、p形半導体基板41a内には、n形ウェル領域41b及びp形ウェル領域41cが形成される。p形ウェル領域41c内に、NORセルが形成される。NORセルは、ビット線BLとソース線SLとの間に接続される1つのメモリセル(MISトランジスタ)MCを含む。メモリセルMCは、n形拡散層42と、n形拡散層42の間のチャネル領域42c上のゲート絶縁層43と、ゲート絶縁層43上の記憶層15と、記憶層15上のコントロールゲート電極45と、を含む。

【0111】

図17に表したように、各コントロールゲート電極45(CG)は、駆動部600に電気的に接続される。なお、駆動部600は、NORセルユニット264cが設けられる基板に設けられても良く、それとは別の基板に設けられても良い。不揮発性記憶装置264においても、図14に関して説明した動作が実施される。

【0112】

図19は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式図である。

図20は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

本実施形態に係る別の不揮発性記憶装置265は、2トラ型フラッシュメモリである。図19は、2トラセルユニット265cの回路図を示している。図20は、2トラセルユニット265cの構造を例示している。

【0113】

図19及び図20に表したように、2トラセルユニット265cは、NANDセルユニットの特徴とNORセルの特徴とを併せ持ったセル構造を有する。

【0114】

p形半導体基板41a内には、n形ウェル領域41b及びp形ウェル領域41cが形成される。p形ウェル領域41c内に、2トラセルユニット265cが形成される。

【0115】

2トラセルユニット265cは、直列接続される1つのメモリセルMCと、1つのセレクトゲートトランジスタSTと、を含む。メモリセルMCは、セレクトゲートトランジスタSTと同じ構造を有する。具体的には、これらは、n形拡散層42と、n形拡散層42の間のチャネル領域42c上のゲート絶縁層43と、ゲート絶縁層43上の記憶層15と、記憶層15上のコントロールゲート電極45と、を含む。セレクトゲートトランジスタSTは、ソース線SLに接続され、メモリセルMCは、ビット線BLに接続される。各コントロールゲート電極45(CG)は、駆動部600に電気的に接続される。なお、駆動部600は、2トラセルユニット265cが設けられる基板に設けられても良く、それとは別の基板に設けられても良い。不揮発性記憶装置265においても、図14に関して説明した動作が実施される。

【0116】

図21は、第4の実施形態に係る別の不揮発性記憶装置の構成を例示する模式的断面図である。

図21に表したように、本実施形態に係る別の不揮発性記憶装置266では、セレクトゲートトランジスタSTについては、記憶層15を設けずに、通常のMISトランジスタが用いられている。このように、セレクトゲートトランジスタSTの構造は、任意である。

【0117】

また、実施形態に係る不揮発性記憶装置を記憶媒体に応用しても良い。

【0118】

本実施形態によれば、プロセス耐性が高く、高い性能を維持する不揮発性記憶装置が提供される。

【0119】

以上、具体例を参照しつつ、本発明の実施の形態について説明した。しかし、本発明の実施形態は、これらの具体例に限定されるものではない。例えば、不揮発性記憶装置に含まれる第1導電部、第2導電部、記憶層、整流素子、基板、配線及び駆動部などの各要素の具体的な構成に関しては、当業者が公知の範囲から適宜選択することにより本発明を同様に実施し、同様の効果を得ることができる限り、本発明の範囲に包含される。

また、各具体例のいずれか2つ以上の要素を技術的に可能な範囲で組み合わせたものも、本発明の要旨を包含する限り本発明の範囲に含まれる。

【0120】

その他、本発明の実施の形態として上述した不揮発性記憶装置を基にして、当業者が適宜設計変更して実施し得る全ての不揮発性記憶装置も、本発明の要旨を包含する限り、本発明の範囲に属する。

【0121】

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

【0122】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0123】

10…第1導電部、 15…記憶層、 17…金属層、 20…第2導電部、 22…記憶部、 30…基板、 31…ワード線ドライバ、 32…ビット線ドライバ、 33…メモリセル、 33B…保護層、 34…整流素子、 35…ヒータ層、 41…半導体基板、 41a…p形半導体基板、 41b…n形ウェル領域、 41c…p形ウェル領域、 42…拡散層(n形核酸層)、 42c…チャネル領域、 43…ゲート絶縁層、 45…コントロールゲート電極、 47…p形半導体層、 51…第1陽イオン、 52…第2陽イオン、 52m…金属原子、 53…陰イオン、 110、210、211、212、220、250、260、261〜266…不揮発性記憶装置、 261c…NANDセルユニット、 264c…NORセルユニット、 265c…2トラセルユニット、 515…ドライバ、 516…XYスキャナ、 520…基板、 521…電極、 523…基板、 524…プローブ、 525、526…マルチプレクスドライバ、 531…データエリア、 532…サーボエリア、 600…駆動部、 Ae、Ai…矢印、 BL…ビット線、 CWS…トランジスタ、 HR…高抵抗状態、 LR…低抵抗状態、 MC…メモリセル、 RSW…トランジスタ、 SL…ソース線、 ST…セレクトゲートトランジスタ、 WL…ワード線

【特許請求の範囲】

【請求項1】

第1導電部と、

第2導電部と、

前記第1導電部と前記第2導電部との間に設けられ、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能で、カルコパイライト構造を有する記憶層と、

を備え、

前記記憶層は、AxMyXz(Aは、Mn、Fe、Co、Ni、Cu、Zn、Mg、Al及びGaよりなる群から選択された少なくともいずれかであり遷移元素を含み、は、Si、Ge、Al及びGaよりなる群から選択された少なくともいずれかであり、Xは、N、P及びAsよりなる群から選択された少なくともいずれかを含み、0.3≦x≦1、0.9≦y≦1.1、1.9≦(z/y)≦2.1である)で表される材料を含み、

前記第1導電部及び前記第2導電部の少なくともいずれかは、不純物がドープされた、Si、及び、III-V族化合物半導体の少なくともいずれかを含む不揮発性記憶装置。

【請求項2】

第1導電部と、

第2導電部と、

前記第1導電部と前記第2導電部との間に設けられ、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能で、カルコパイライト構造を有する記憶層と、

を備えた不揮発性記憶装置。

【請求項3】

前記記憶層は、AxMyXz(Aは、Mn、Fe、Co、Ni、Cu、Zn、Mg、Al及びGaよりなる群から選択された少なくともいずれかであり、Mは、Si、Ge、Al及びGaよりなる群から選択された少なくともいずれかであり、Xは、N、P及びAsよりなる群から選択された少なくともいずれかを含み、0.3≦x≦1、0.9≦y≦1.1、1.9≦(z/y)≦2.1である)で表される材料を含む請求項2記載の不揮発性記憶装置。

【請求項4】

前記Aは、遷移元素を含む請求項3記載の不揮発性記憶装置。

【請求項5】

前記記憶層は、珪窒化コバルト、珪窒化マンガン、珪窒化鉄、窒化ゲルマニウムマンガン、窒化ゲルマニウム鉄、窒化ゲルマニウムコバルト、珪リン化コバルト、珪リン化マンガン、珪リン化鉄、リン化ゲルマニウムマンガン、リン化ゲルマニウム鉄、リン化ゲルマニウムコバルト、珪窒化コバルト亜鉛、珪窒化マンガン亜鉛、及び、珪窒化鉄亜鉛よりなる群から選択された少なくともいずれかを含む請求項2記載の不揮発性記憶装置。

【請求項6】

前記第1導電部及び前記第2導電部の少なくともいずれかは、不純物がドープされた、Si、及び、III-V族化合物半導体の少なくともいずれかを含む請求項2〜5のいずれか1つに記載の不揮発性記憶装置。

【請求項1】

第1導電部と、

第2導電部と、

前記第1導電部と前記第2導電部との間に設けられ、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能で、カルコパイライト構造を有する記憶層と、

を備え、

前記記憶層は、AxMyXz(Aは、Mn、Fe、Co、Ni、Cu、Zn、Mg、Al及びGaよりなる群から選択された少なくともいずれかであり遷移元素を含み、は、Si、Ge、Al及びGaよりなる群から選択された少なくともいずれかであり、Xは、N、P及びAsよりなる群から選択された少なくともいずれかを含み、0.3≦x≦1、0.9≦y≦1.1、1.9≦(z/y)≦2.1である)で表される材料を含み、

前記第1導電部及び前記第2導電部の少なくともいずれかは、不純物がドープされた、Si、及び、III-V族化合物半導体の少なくともいずれかを含む不揮発性記憶装置。

【請求項2】

第1導電部と、

第2導電部と、

前記第1導電部と前記第2導電部との間に設けられ、前記第1導電部と前記第2導電部とを介して供給される電流により、抵抗が低い第1状態と前記第1状態よりも抵抗が高い第2状態との間を可逆的に遷移可能で、カルコパイライト構造を有する記憶層と、

を備えた不揮発性記憶装置。

【請求項3】

前記記憶層は、AxMyXz(Aは、Mn、Fe、Co、Ni、Cu、Zn、Mg、Al及びGaよりなる群から選択された少なくともいずれかであり、Mは、Si、Ge、Al及びGaよりなる群から選択された少なくともいずれかであり、Xは、N、P及びAsよりなる群から選択された少なくともいずれかを含み、0.3≦x≦1、0.9≦y≦1.1、1.9≦(z/y)≦2.1である)で表される材料を含む請求項2記載の不揮発性記憶装置。

【請求項4】

前記Aは、遷移元素を含む請求項3記載の不揮発性記憶装置。

【請求項5】

前記記憶層は、珪窒化コバルト、珪窒化マンガン、珪窒化鉄、窒化ゲルマニウムマンガン、窒化ゲルマニウム鉄、窒化ゲルマニウムコバルト、珪リン化コバルト、珪リン化マンガン、珪リン化鉄、リン化ゲルマニウムマンガン、リン化ゲルマニウム鉄、リン化ゲルマニウムコバルト、珪窒化コバルト亜鉛、珪窒化マンガン亜鉛、及び、珪窒化鉄亜鉛よりなる群から選択された少なくともいずれかを含む請求項2記載の不揮発性記憶装置。

【請求項6】

前記第1導電部及び前記第2導電部の少なくともいずれかは、不純物がドープされた、Si、及び、III-V族化合物半導体の少なくともいずれかを含む請求項2〜5のいずれか1つに記載の不揮発性記憶装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2013−110279(P2013−110279A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−254283(P2011−254283)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]