二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般には、半導体デバイスの製造方法に関し、特に、金属ゲート電極を備えたゲートスタックを有するCMOSデバイスの製造方法および、これで製作されるCMOSデバイスに関する。

【背景技術】

【0002】

今日まで、半導体産業は、金属−酸化物−半導体電界効果トランジスタ(MOSFET)の幾何寸法のスケーリングによって活発な状態である。二酸化シリコン(SiO2)をゲート誘電体として、多結晶シリコン(poly-Si)をゲート材料として用いる従来のMOSFET技術では、100nmまたはそれ以下にスケールダウンした場合、多くの問題が発生する。

【0003】

ゲート誘電体の厚さが減少すると、ゲート直接トンネル電流の指数関数的な増加が生ずる。45nmテクノロジーノード超についてこの問題を解決する1つの手法は、ゲート誘電体として、いわゆる高誘電率(high-k)誘電体の導入である。高誘電率(high-k)誘電体は、SiO2の誘電定数より大きい誘電定数(k)、即ち、k>3.9を示す誘電体である。高誘電率(high-k)誘電体は、より大きな物理厚さ(SiO2と比べて)を可能にし、より薄いSiO2層で得られるものと同じ実効静電容量が得られる。より大きな物理厚さの高誘電率(high-k)材料は、ゲート漏れ電流を減少させる。

【0004】

2nm未満のSiO2酸化物厚さでは、ポリシリコン(poly-Si)空乏効果は、ポリSiゲートで支配的であることからスタートする。この問題の解決法は、ゲート材料として、金属の導入である。金属ゲートの利点は、ポリシリコン空乏効果の排除、極めて低い抵抗、可能性あるドーパント侵入がないこと、高誘電率(high-k)誘電体とのより良好な適合性である。

【0005】

金属ゲートを導入することによって、MOSFETの閾値電圧は、金属の仕事関数によって制御されるようになる。金属ゲート電極に関して、NMOSとPMOSとで異なる仕事関数が必要になるため、仕事関数の調整は単純明快なものではない。このことは、n−MOSFETについて機能する(n型)金属(ポリSiと置換)(即ち、好ましくは、約3.9eV〜約4.2eVの仕事関数)および、p−MOSFETについて機能する(p型)金属(即ち、好ましくは、約4.9eV〜約5.2eVの仕事関数)を必要とする。ポリシリコンゲート電極の仕事関数は、イオン注入(implantation)によって調整可能であるが、金属ゲート電極の仕事関数は、容易に変化しない材料の性質である。

【発明の概要】

【発明が解決しようとする課題】

【0006】

新たなゲート材料、例えば、金属ゲート電極と組み合わせた高誘電率(high-k)誘電体などの導入は、簡単ではない。エッチングや剥ぎ取り(strip)など、従来のゲート第1製造処理ステップにおいて問題が生ずることがあるためである。従って、相補型金属−酸化物−半導体デバイス(CMOS)における高誘電率(high-k)ゲート誘電体と金属ゲート誘電体との集積化では、新たな代替物を処理フローに導入する必要がある。CMOSデバイスにおける金属ゲートと高誘電率(high-k)誘電体との集積化のための最新の先行技術において利用できる可能性があるが、高誘電率(high-k)/金属半導体デバイスのために簡単化した集積機構、より具体的には、簡単化した二重金属二重誘電体(DMDD)集積機構のニーズが存在する。

【課題を解決するための手段】

【0007】

1つの発明態様は、二重仕事関数半導体デバイスに関するものであり、該デバイスは、半導体基板と、半導体基板の第1領域にあって、第1ゲートスタックを含む第1トランジスタと、半導体基板の第2領域にあって、第2ゲートスタックを含む第2トランジスタとを備え、

第1ゲートスタックは、第1実効仕事関数を有し、第2ゲートスタックは、第1実効仕事関数とは異なる第2実効仕事関数を有し、

第1ゲートスタックは、第2ゲート誘電体キャップ層の上にある第2金属ゲート電極を備え、第2ゲート誘電体キャップ層はバリア金属ゲート電極の上にあり、バリア金属ゲート電極は第1金属ゲート電極層の上にあり、第1金属ゲート電極層はゲート誘電体ホスト層の上にあり、ゲート誘電体ホスト層は第1ゲート誘電体キャップ層の上にあり、第1ゲート誘電体キャップ層は第1領域において半導体基板の上にあり、

第2ゲートスタックは、第2ゲート誘電体キャップ層の上にある第2金属ゲート電極を備え、第2ゲート誘電体キャップ層は第1金属ゲート電極の上にあり、第1金属ゲート電極はゲート誘電体ホスト層の上にあり、ゲート誘電体ホスト層は第2領域において半導体基板の上にあり、

第1および第2ゲートスタックの第2金属ゲート電極層は、第1および第2ゲートスタックの第1金属ゲート電極層と同じ金属組成からなる。

【0008】

本発明の第1態様の実施形態によれば、第1ゲートスタックの第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数を調整するように選択される。

【0009】

本発明の第1態様の他の実施形態によれば、第2ゲートスタックの第1金属ゲート電極層、第2ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数を調整するように選択される。

【0010】

本発明の第1態様の他の実施形態によれば、第1実効仕事関数は、第2実効仕事関数より大きい。好ましくは、第1ゲートスタックの第1実効仕事関数は、4.9eV〜5.5eVの範囲である。第2実効仕事関数は、好ましくは、3.9eV〜4.5eVの範囲である。第1トランジスタは、好ましくは、PMOSトランジスタである。第2トランジスタは、好ましくは、NMOSトランジスタである。

【0011】

本発明の第1態様の他の実施形態によれば、第1ゲート誘電体キャップ層は、Alベースの誘電体である。より具体的には、第1ゲート誘電体キャップ層は、AlO,AlN,AlONおよびこれらの混合物からなるグループから選択される。

【0012】

本発明の第1態様の他の実施形態によれば、第2ゲート誘電体キャップ層は、ランタン系列ベースの誘電体である。より具体的には、第2ゲート誘電体キャップ層は、DyO,LaO,GdO,ErOおよびこれらの混合物からなるグループから選択される。

【0013】

本発明の第1態様の他の実施形態によれば、バリア金属ゲート電極層は、TiNを含む。代替として、バリア金属ゲート電極層は、TaNを含んでもよい。

【0014】

本発明の第1態様の他の実施形態によれば、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される材料を含む。

【0015】

本発明の第1態様の他の実施形態によれば、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCyNzOw(x,y,z,wの実数値は0<x,y,z,w<1)を含む。

【0016】

本発明の第1態様の他の実施形態によれば、ゲート誘電体ホスト層は、SiO2,SiON,HfO2,ZrO2およびこれらの混合物からなるグループから選択される。

【0017】

第1態様の好ましい実施形態によれば、第1ゲート誘電体キャップ層は、AlO,AlN,AlONおよびこれらの混合物からなるグループから選択され、第2ゲート誘電体キャップ層は、DyO,LaO,GdO,ErOおよびこれらの混合物からなるグループから選択され、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される材料を含み、バリア金属ゲート電極層は、TiNを含む。

【0018】

本発明の第2の発明態様は、二重仕事関数半導体デバイスを形成する方法に関するものであり、該方法は、半導体基板に第1領域および第2領域を設けることと、

【0019】

第1実効仕事関数を有する第1ゲートスタックを第1領域に形成し、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタックを第2領域に形成することとを含み、

第1ゲート誘電体キャップ層を第1領域に形成するステップ、

ゲート誘電体層を第1領域および第2領域に形成して、第1領域においてゲート誘電体層を第1ゲート誘電体キャップ層の上に載せるステップ、

第1金属ゲート電極材料を第1領域および第2領域に形成して、第1金属ゲート電極材料をゲート誘電体層の上に載せるステップ、

バリア金属ゲート電極層を第1領域に形成して、バリア金属ゲート電極層を第1金属ゲート電極層の上に載せるステップ、

第2ゲート誘電体キャップ層を第2領域に形成して、第2ゲート誘電体キャップ層を第1金属ゲート電極層の上に載せるステップ、

第2金属ゲート電極層を第1領域および第2領域に形成して、第2金属ゲート電極層を第2ゲート誘電体キャップ層の上に載せるステップを含み、

第1ゲートスタックおよび第2ゲートスタックの第2金属ゲート電極層は、第1ゲートスタックおよび第2ゲートスタックの第1金属ゲート電極層と同じ金属組成からなる。

【0020】

本発明の第2態様の実施形態によれば、該方法は、第2金属ゲート電極層、第2ゲート誘電体キャップ層、バリア金属ゲート電極層、ゲート誘電体ホスト層および第1ゲート誘電体キャップ層をパターン化して、第1ゲートスタックを形成すること、および、

【0021】

第2金属ゲート電極層、第2ゲート誘電体キャップ層、第1金属ゲート電極層およびゲート誘電体ホスト層をパターン化して、第2ゲートスタックを形成することをさらに含む。

【0022】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数を調整するように選択される。

【0023】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層、第2ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数を調整するように選択される。

【0024】

本発明の第2態様の他の実施形態によれば、第1実効仕事関数は、第2実効仕事関数より大きい。

【0025】

本発明の第2態様の他の実施形態によれば、第1実効仕事関数は、4.9eV〜5.5eVの範囲である。

【0026】

本発明の第2態様の他の実施形態によれば、第2実効仕事関数は、3.9eV〜4.5eVの範囲である。

【0027】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数をPMOS実効仕事関数に向けて調整するように選択される。

【0028】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数をNMOS実効仕事関数に向けて調整するように選択される。

【0029】

本発明の第2態様の他の実施形態によれば、第1ゲート誘電体キャップ層は、Alベースの誘電体である。より具体的には、第1ゲート誘電体キャップ層は、AlO,AlN,AlONおよびこれらの混合物からなるグループから選択される。

【0030】

本発明の第2態様の他の実施形態によれば、第2ゲート誘電体キャップ層は、ランタン系列ベースの誘電体である。より具体的には、第2ゲート誘電体キャップ層は、DyO,LaO,GdO,ErOおよびこれらの混合物からなるグループから選択される。

【0031】

本発明の第2態様の他の実施形態によれば、バリア金属ゲート電極層は、TiNまたはTaNを含む。

【0032】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される材料を含む。

【0033】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCyNzOw(x,y,z,wの実数値は0<x,y,z,w<1)を含む。

【0034】

本発明の第2態様の他の実施形態によれば、ゲート誘電体ホスト層は、SiO2,SiON,HfO2,ZrO2およびこれらの混合物からなるグループから選択される。

【図面の簡単な説明】

【0035】

全ての図面は、本発明の幾つかの態様および実施形態を図示することを意図している。記載した図面は、概略的で非限定的に過ぎない。図面において、幾つかの要素のサイズは、説明目的のために、誇張したり、スケールどおりに描いていないこともある。例示の実施形態は、図面の参照した図に示している。ここで開示した実施形態および図面は、限定的なものではなく、例示的なものと考えることを意図している。異なる図面では、同じ参照符号は、同じまたは類似の要素を参照している。

【0036】

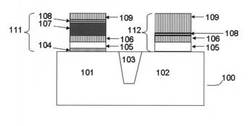

【図1】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図2】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図3】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図4】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図5】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図6】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図7】本発明の態様に係る二重仕事関数半導体デバイスの概略断面図を示す。

【発明を実施するための形態】

【0037】

本発明の1つ又はそれ以上の実施形態について、添付した図面を参照して詳細に説明する。本発明はこれに限定されない。記載した図面は、概略的かつ非限定的なものである。図面において、幾つかの要素のサイズは、説明目的のために誇張したり、縮尺どおり描写していないことがある。寸法および相対寸法は、本発明の実際の具体化に必ずしも対応していない。当業者は、その範囲で包囲される本発明の多数の変化および変更を認識できる。従って、好ましい実施形態の説明は、本発明の範囲を限定するものとみなすべきでない。

【0038】

さらに、説明での用語、「第1」、「第2」などは、類似の要素を区別するための使用しており、必ずしも連続した順または時間順を記述するためではない。こうして用いた用語は、適切な状況下で交換可能であり、本発明の実施形態は、ここで説明したり図示したものとは別の順番で動作可能である。

【0039】

さらに、説明および請求項の中の用語「上(top)」、「下(bottom)」、「の上に(over)」、「の下に(under)」等は、説明目的で使用しており、必ずしも相対的な位置を記述するためのものでない。こうして用いた用語は、適切な状況下で交換可能であって、ここで説明した本発明の実施形態がここで説明または図示した以外の他の向きで動作可能であると理解すべきである。例えば。ある要素の「下方(underneath)」および「上方(above)」は、この要素の対向側に配置されることを示す。

【0040】

ここで提供した説明において、多数の特定の詳細を記述している。しかしながら、本発明の実施形態は、これらの特定の詳細なしでも実用化できると理解される。例えば、周知の方法、構造およびテクニックは、本説明の理解を曖昧にしないために詳細には示していない。

【0041】

ここでは、特定の化学名または化学式が与えられた場合、その材料は、化学名で識別される化学量論的に正確な式の非化学量論的な変形を含んでもよい。式中の元素の下付き数値が無いのは、数字の「1」を意味する。本発明の目的では、正確な化学量論的数字の±20%の範囲内の変動は、その化学名または化学式に含まれる。代数的な下付き文字が与えられた場合、各下付き数値に対して約±20%の範囲内の変動は含まれる。こうして変動する値は、合計しても必ずしも整数にならず、この逸脱は予測される。こうした変動は、処理条件の意図した選択および制御、あるいは意図した処理変動に起因して、生ずることがある。

【0042】

用語「備える、含む(comprising)」は、それ以降に列挙された手段に限定されるものと解釈すべきでなく、他の要素またはステップを除外していないことに留意する。そして「手段A,Bを備えるデバイス」という表現の範囲は、構成要素A,Bだけからなる素子に限定すべきでない。本発明に関して、デバイスの関連した構成要素だけがA,Bであることを意味する。

【0043】

本発明の種々の実施形態は、半導体デバイスのパラメータ、例えば、閾値電圧(Vt)、実効仕事関数(WFeff)、使用する材料の物理的特性、例えば、仕事関数(WF)、フェルミ準位などを参照している。本書で用いている定義は、下記のように整理できる。

【0044】

MOSFETデバイスにおいて、ゲートは、チャネルを導通させるための閾値電圧(Vt)を要する。相補型MOS(CMOS)処理は、n−チャネルおよびp−チャネル(それぞれNMOS、PMOS)トランジスタの両方を製造する。閾値電圧Vtの差、即ち、NMOS、PMOSトランジスタ間の閾値電圧の差は、実効仕事関数の差(ΔWFeff)と呼ばれるものによって影響を受ける。実効仕事関数の差は、NMOSトランジスタの実効仕事関数とPMOSトランジスタの実効仕事関数との差である。

【0045】

PMOSトランジスタおよびNMOSトランジスタについてそれぞれ閾値電圧(Vt)を設定するには、個々のPMOSおよびNMOSのゲート材料(ゲートスタック)の実効仕事関数の差およびこれらの対応するチャネル領域が、チャネル処理およびゲート処理を通じて独立に設定される。換言すると、ゲート誘電体(即ち、ホスト誘電体および任意の異なるキャップ層を含む)およびゲート電極(少なくとも1つの金属層を含む)は、ゲートスタック(デバイス)の実効仕事関数(WFeff)を決定する。さらに、ゲート処理自体(即ち、異なるステップ及び/又は印加される熱処理の順序)は、ゲートスタック(デバイス)の実効仕事関数(WFeff)に影響を及ぼす。

【0046】

ゲートスタック(デバイス)の実効仕事関数(WFeff)は、ゲート誘電体材料、ゲート電極材料の選択および実施するゲート処理によって調整可能なパラメータである。これに対して、ゲート電極(しばしば金属ゲート電極または金属層電極または金属制御電極と称される)の仕事関数(WF)は、材料固有の性質である。一般に、ある材料の仕事関数は、電子が初期にフェルミ準位にある場合、材料中の電子を材料原子の外部へ真空に脱出させるのに要するエネルギーの単位、電子ボルト(eV)である。ゲート電極の仕事関数は、堆積状態(as-deposited)の仕事関数または材料固有の仕事関数とも称される。

【0047】

シリコン基板では、負チャネルMOSFET(またはNMOS)デバイスのゲート電極は、約4.1eV(±0.3eV)のn型仕事関数を有し、正チャネルMOSFET(またはPMOS)デバイスのゲート電極は、約5.2eV(±0.3eV)のp型仕事関数を有するであろう。

【0048】

高誘電率(high-k)誘電体は、SiO2の誘電定数より大きい誘電定数(k)、即ち、k>3.9を示す誘電体である。高誘電率(high-k)誘電体は、より大きな物理厚さ(SiO2と比べて)を可能にし、より薄いSiO2層で得られるものと同じ実効静電容量が得られる。

【0049】

下記において、本発明は、シリコン(Si)基板を参照して説明するが、本発明は他の半導体基板にも同じように適用されると理解すべきである。実施形態において、「基板」は、半導体基板、例えば、シリコン、ガリウムヒ素(GaAs)、ガリウムヒ素リン(GaAsP)、インジウムリン(InP)、ゲルマニウム(Ge)またはシリコンゲルマニウム(SiGe)の基板などを含む。「基板」は、半導体基板部分へ追加された、例えば、SiO2層またはSi3N4層などの絶縁層を含んでもよい。そして、用語「基板」は、シリコン・オン・ガラス基板、シリコン・オン・サファイア基板を含んでもよい。用語「基板」は、対象となる層または部分の下地となる層のための要素を一般に規定するために用いられる。「基板」は、ある層、例えば、ガラスや金属層が上に形成される他の何れかのベースであってもよい。従って、基板は、ウエハ、例えば、ブランケットウエハなどでもよく、あるいは、他のベース材料に付着した層、例えば、下側層の上に成長したエピタキシャル層でもよい。

【0050】

本発明の第1態様は、二重仕事関数半導体デバイスに関するものであり、該二重仕事関数半導体デバイスは、

半導体基板と、

半導体基板の第1領域に、第1ゲートスタックを含む第1トランジスタと、半導体基板の第2領域に、第2ゲートスタックを含む第2トランジスタとを備え、

第1ゲートスタックは、第1実効仕事関数を有し、第2ゲートスタックは、第1実効仕事関数とは異なる第2実効仕事関数を有し、

第1ゲートスタックは、第2ゲート誘電体キャップ層の上にあって、これと接触する第2金属ゲート電極と、バリア金属ゲート電極の上にあって、これと接触する第2ゲート誘電体キャップ層と、第1金属ゲート電極層の上にあって、これと接触するバリア金属ゲート電極と、ゲート誘電体ホスト層の上にあって、これと接触する第1金属ゲート電極層と、第1ゲート誘電体キャップ層の上にあって、これと接触するゲート誘電体ホスト層と、第1領域において半導体基板の上にあって、これと接触する第1ゲート誘電体キャップ層とを備え、

第2ゲートスタックは、第2ゲート誘電体キャップ層の上にあって、これと接触する第2金属ゲート電極と、第1金属ゲート電極の上にあって、これと接触する第2ゲート誘電体キャップ層と、ゲート誘電体ホスト層の上にあって、これと接触する第1金属ゲート電極と、第2領域において半導体基板の上にあって、これと接触するゲート誘電体ホスト層とを備え、

第1および第2ゲートスタックの第2金属ゲート電極層は、第1および第2ゲートスタックの第1金属ゲート電極層と同じ金属組成からなる。

【0051】

図7は、本発明の第1態様に係る二重仕事関数半導体デバイスの断面図を示す。

【0052】

第1金属ゲート電極、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、この層スタックが第1ゲートスタック111の第1実効仕事関数WF1effを調整できるように選択される。必要に応じて、ゲート誘電体ホスト層も、第1ゲートスタック111の第1実効仕事関数WF1effをさらに調整するように選択してもよい。好ましくは、第1ゲートスタック111の第1実効仕事関数WF1effは、約5.2eV(±0.3eV)の値に向けて適合される。第1ゲートスタックは、好ましくは、正チャネルMOSFET(またはPMOS)デバイス用に形成される。そして、第1トランジスタは、好ましくは、PMOSトランジスタを備える。

【0053】

第1金属ゲート電極、第2金属ゲート電極および第2ゲート誘電体キャップ層は、この層スタックが第2ゲートスタック112の第2実効仕事関数WF2effを調整できるように選択される。必要に応じて、この層スタックは、第2実効仕事関数WF2effをさらに調整するように、ゲート誘電体ホスト層を含んでもよい。好ましくは、第2ゲートスタック112の第2実効仕事関数WF2effは、約4.2eV(±0.3eV)の値に向けて適合される。第2ゲートスタックは、好ましくは、負チャネルMOSFET(またはNMOS)デバイス用に形成される。そして、第2トランジスタは、好ましくは、NMOSトランジスタを備える。

【0054】

一実施形態において、第1トランジスタはPMOSトランジスタを備え、第2トランジスタはNMOSトランジスタを備え、第1ゲート誘電体キャップ層は、好ましくは、第2ゲート誘電体キャップ層からの他の誘電体元素と比較して、より高い電気陰性度を持つ誘電体元素を含む。

【0055】

第1ゲート誘電体キャップ層は、好ましくは、より負に帯電した原子を持つ誘電体元素を含み、一方、第2ゲート誘電体キャップ層は、好ましくは、より正に帯電した原子を持つ他の誘電体元素を含む。第1ゲート誘電体キャップ層は、好ましくは、Alベースの誘電体、例えば、AlO,AlN,AlONおよびこれらの混合物を含む。一方、第2ゲート誘電体キャップ層は、好ましくは、ランタン系列ベースの誘電体、例えば、DyO(N),LaO(N),ScO(N),GdO(N),TbO(N),YbO(N),ErO(N)およびこれらの混合物の何れかを含む。

【0056】

一実施形態において、第1および第2金属ゲート電極は、p型仕事関数を有する金属層を含んでもよい。好都合には、第1および第2金属ゲート電極は、p型仕事関数を有する金属層からなる。第1および第2金属層は、Taベース、Wベース、Moベースの材料を含んでもよい。より好都合には、金属ゲート電極は、TaxCyNzOw(x,y,z,wの実数値は0<x,y,z,w<1)からなる。

【0057】

他の実施形態において、第1および第2金属ゲート電極は、n型仕事関数を有する金属層を含んでもよい。好都合には、第1および第2金属ゲート電極は、n型仕事関数を有する金属層からなる。第1および第2金属層は、Taベース、Tiベースの材料を含んでもよい。より好都合には、第1および第2金属層材料は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される。

【0058】

一実施形態において、ゲート誘電体ホスト層は、SiO2,SiON,HfO2,ZrO2およびこれらの混合物からなるグループから選択される。これらの材料は、シリコン基板との安定した界面という利点を示す。

【0059】

バリア金属ゲート電極は、好ましくは、第1実効仕事関数に対する、第1トランジスタでの第2ゲート誘電体キャップ層および第2金属ゲート電極の影響を阻止する金属含有材料を含む。バリア金属ゲート電極の金属含有材料は、第1実効仕事関数を調整するように選択してもよい(第1ゲート誘電体キャップ層と共に)。好都合には、バリア金属ゲート電極は、TiNを含んでもよい。バリア金属ゲート電極は、TaNを含んでもよい。

【0060】

本発明の第2態様は、二重仕事関数半導体デバイスを製造する方法に関するものであり、該方法は、下記ステップを含む。

【0061】

・半導体基板に第1領域および第2領域を設けること、

・第1実効仕事関数を有する第1ゲートスタックを第1領域に備える第1トランジスタを形成し、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタックを第2領域に有する第2トランジスタを形成すること、

・第1ゲート誘電体キャップ層を第1領域だけに形成すること、

・ゲート誘電体ホスト層を第1領域および第2領域に形成して、ゲート誘電体ホスト層を第1領域において第1ゲート誘電体キャップ層の上に載せること、

・第1金属ゲート電極材料を第1領域および第2領域に形成して、第1金属ゲート電極材料をゲート誘電体ホスト層の上に載せること、

・バリア金属ゲート電極層を第1領域だけに形成して、バリア金属ゲート電極層を第1金属ゲート電極層の上に載せること、

・第2ゲート誘電体キャップ層を第1領域および第2領域に形成して、第1領域において第2ゲート誘電体キャップ層をバリア金属ゲート電極層の上に載せ、第2領域において第2ゲート誘電体キャップ層を第1金属ゲート電極層の上に載せること、

・第2金属ゲート電極層を第1領域および第2領域に形成して、第2金属ゲート電極層を第2ゲート誘電体キャップ層の上に載せることを含み、

・第2金属ゲート電極層は、第1金属ゲート電極層と同じ金属を含む。

【0062】

図1〜図7を参照して、本発明の第2態様に係る二重仕事関数半導体デバイスの製造方法のための異なる処理ステップをより詳細に説明する。

【0063】

図1は、半導体基板100、例えば、シリコン基板を示す。基板100は、複数の別個の領域を含んでもよい。最も好ましくは、2つの別個の領域が基板100において規定することができ、即ち、図1に示すように、第1領域101と第2領域102である。第1領域101は、デバイスの第1活性領域とも称され、第1トランジスタが形成される部分であり、第2領域102は、デバイスの第2活性領域とも称され、第2トランジスタが形成される部分である。

【0064】

第1領域101および第2領域102は、絶縁領域103によって互いに電気絶縁してもよい。第1領域101および第2領域102を相互に分離する可能な方法は、両者の間にSTI(shallow trench isolation)を使用することである。STIは、深く狭い溝であり、集積回路内で隣接するデバイス間で半導体基板にエッチングされ、酸化物で充填されて、両者の電気的分離を提供する。代替として、LOCOS(local oxidation of silicon:シリコン局所酸化)を用いてもよい。第1領域101は、例えば、PMOS領域であり、第2領域102例えば、NMOS領域であり、その逆でもよい。

【0065】

基板に第1および第2領域を設けた後、第1ゲートスタックおよび第2ゲートスタックが第1および第2活性領域にそれぞれ形成される。その後、第1領域101だけに存在する第1ゲート誘電体キャップ層104が設けられる(図2)。第1ゲート誘電体キャップ層104の設置は、当業者に周知であるような従来の処理ステップおよび設備を用いてもよく、例えば、最初にゲート誘電体キャップ層を基板上の第1および第2領域の両方に堆積し、続いて、従来のリソグラフステップを用いてゲート誘電体キャップ層をパターン化して、第2領域102にあるゲート誘電体キャップ層の一部を除去する。

【0066】

第1ゲート誘電体キャップ層104の材料は、第1ゲートスタックの第1実効仕事関数を調整するように選択される。さらに後でも、集積構造において、第1/第2金属ゲート電極層の材料は、第1ゲートスタックの第1実効仕事関数をさらに調整するように選択される。

【0067】

一実施形態において、第1ゲート誘電体キャップ層104は、Alベースの誘電体、またはランタン系列ベースの誘電体でもよい。第1ゲート誘電体キャップ層104は、LaO(N),AlO(N),AlN,DyO(N),ScO(N),GdO(N),CeO(N),TbO(N),ErO(N),YbO(N)またはこれらの組合せを含んでもよい。

【0068】

第1ゲート誘電体キャップ層104の材料に応じて、この層は、第1実効仕事関数をNMOSデバイスまたはPMOSデバイスに向けて調整するのに適したものでもよい。例えば、DyOは、より正に帯電した原子を持つ誘電体として知られており、誘電体(例えば、HfSiON−DyOスタック)の内蔵(built-in)ダイポール電界は、金属ゲート(例えば、TiN)の仕事関数とは独立して、NMOSデバイスの閾値電圧に適合できる。こうしてDyO層は、NMOSトランジスタに適した実効仕事関数を決定することになる。

【0069】

例えば、AlOは、より負に帯電した原子を持つ誘電体として知られており、誘電体(例えば、HfSiON−AlOスタック)の内蔵(built-in)ダイポール電界は、金属ゲート(例えば、TiN)の仕事関数とは独立して、PMOSデバイスの閾値電圧に適合できる。こうしてAlO層は、PMOSトランジスタに適した実効仕事関数を決定することになる。

【0070】

第1ゲート誘電体キャップ層104は、好ましくは、0.2nm〜2nmの範囲、より好ましくは0.2nm〜1nmの範囲、さらにより好ましくは0.2nm〜0.5nmの範囲の等価酸化膜厚(EOT: Equivalent Oxide Thickness)を有してもよい。これは、0.5〜2nmの範囲の誘電体キャップ層114の物理厚さに対応する。

【0071】

第1ゲート誘電体キャップ層104は、ALD,PVDまたはCVDなど任意の堆積技術を用いて形成される。

【0072】

(第1)ゲート誘電体キャップ層104を第1領域101に設けた後、ゲート誘電体ホスト層105を第1領域101および第2領域102に設ける。ゲート誘電体ホスト層105は、第1領域101では(第1)ゲート誘電体キャップ層104の上にあって、これと接触しており、第2領域102では基板100の上にあって、これと接触している(図2)。

【0073】

ゲート誘電体ホスト層105は、絶縁材料、例えば、二酸化シリコン(SiO2),窒化シリコン(SiN)または酸窒化シリコン(SixOyN1−x−y)、あるいは高誘電率(high-k)誘電体(即ち、k>3.9)、例えば、HfO2,TaOx,Al2O3,ZrO2またはこれらの組合せ等、からなる層でもよい。これらの材料は、シリコン基板100との安定した界面という利点を提供する。

【0074】

ゲート誘電体ホスト層は、熱酸化、化学気相成長(CVD)または、当業者に知られている何れかの他の適切な方法によって形成してもよい。ゲート誘電体ホスト層105は、誘電体材料のスタックを含んでもよく、例えば、高誘電率(high-k)材料が、基板100と高誘電率(high-k)材料の間にある(任意の)界面誘電体層(不図示)の上に形成される。

【0075】

ゲート誘電体ホスト層105は、好ましくは、0.5nm〜4nmの範囲の厚さを有する。第2領域でのゲート誘電体ホスト層の厚さは、第1領域でのゲート誘電体ホスト層の厚さより大きくてもよい。

【0076】

ゲート誘電体ホスト層105を設けた後、第1金属ゲート電極層106をゲート誘電体ホスト層105の上に横たわる(その上に接触する)ように設ける。その後、バリア金属ゲート電極層107を、第1金属ゲート電極層106の上に、これと接触するように設ける(図3)。

【0077】

第1金属ゲート電極層106は、第1(堆積状態:as-deposited)の仕事関数を有するように形成される。第1金属ゲート電極層106は、金属ゲートを形成する金属含有材料を含む。金属含有材料とは、金属、金属合金、金属シリサイド、導電性金属窒化物、導電性金属酸化物などである。該金属に応じて、第1金属ゲート電極層106の仕事関数は、従来のp型ドープ半導体の仕事関数または従来のn型ドープ半導体の仕事関数と同程度にできる。例えば、ニッケル(Ni),酸化ルテニウム(RuO),窒化モリブデン(MoN)は、p型ドープ半導体材料の仕事関数と同程度の仕事関数を有する。例えば、ルテニウム(Ru),ジルコニウム(Zr),ニオブ(Nb),タンタル(Ta),チタンシリサイド(TiSi2)は、n型ドープ半導体材料の仕事関数と同程度の仕事関数を有する。例えば、TiNは、中間ギャップの仕事関数を有し、即ち、p型ドープ半導体材料とn型ドープ半導体材料の仕事関数の間になる(SiO2上のTiNでは、約4.65eV〜4.8eV)。

【0078】

例えば、金属ゲート電極層106は、第1領域101においてNMOSゲート電極(即ち、NMOSトランジスタ)を形成するのに適した第1(堆積状態:as-deposited)の仕事関数を有するように形成できる。しかし、これは、第2領域102においてPMOSゲート電極(即ち、PMOSトランジスタ)を形成するのに適していない。逆も同様に、金属ゲート電極層115は、第1領域101においてPMOSゲート電極を形成するのに適した第1(堆積状態:as-deposited)の仕事関数を有するように形成できる。しかし、これは、第2領域102においてNMOSゲート電極を形成するのに適していない。

【0079】

両方の領域(NMOSおよびPMOS)について1つの金属ゲート電極材料を用いた二重仕事関数半導体デバイスの形成では、金属ゲート電極層106の仕事関数は、選択的に調整する必要がある。即ち、金属ゲート電極材料106の仕事関数は、第1(堆積状態:as-deposited)の仕事関数が適していない領域において調整する必要がある。堆積状態(as-deposited)の仕事関数とは、材料固有の仕事関数を意味する。

【0080】

第1領域101において第1金属ゲート電極層106の下に配置された第1ゲート誘電体キャップ層104は、第1金属ゲート電極層106の堆積状態の仕事関数WFの第1仕事関数シフトを誘起するようになる。

【0081】

第1金属ゲート電極層106は、0.5nm〜10nmの範囲、より好ましくは5nm〜10nmの範囲の厚さを有し、ALD、CVDまたはPVDなどの堆積技術を用いて堆積される。

【0082】

第1金属ゲート電極層106の形成後、バリア金属電極層107が第1金属ゲート電極層106の上に、これと接触するように形成される(図3)。バリア金属ゲート電極材料107は、0.5nm〜10nmの範囲、より好ましくは5nm〜10nmの範囲の厚さを有し、ALD、CVDまたはPVDなどの堆積技術を用いて堆積される。

【0083】

さらに、バリア金属電極層107の一部、即ち、第2領域にある部分は、当業者に知られた従来のエッチング技術を用いて除去される(図4)。第1金属ゲート電極層106は、エッチング停止層として使用してもよい。こうしてバリア金属ゲート電極層107は、第1金属ゲート電極層106に向けて選択的にエッチングされる。好ましくは、ウェットエッチングが使用できる。例えば、第1金属ゲート電極層がTa2Cを含み、バリア金属層107がTiNを含む場合、第2領域にあるTiNの一部が、高い選択性を持つウェットエッチングを用いてTa2Cに向けて選択的に除去される。

【0084】

バリア金属ゲート電極層107は、好ましくは、下地である第1金属ゲート電極層106に向けて選択的にエッチングできる材料を含む。バリア金属ゲート電極層107は、金属含有材料をさらに含む。第1領域において、最終的な第1ゲートスタックの実効仕事関数は、第1金属ゲート電極層106の仕事関数によって決定され、バリア金属電極層107の仕事関数によって決定され、そして、第1ゲート誘電体キャップ層104によってさらに調整される。

【0085】

バリア金属ゲート電極層107は、下記の処理ステップにおいてこのバリア金属電極層107の上部に形成される追加の層によって誘起され得る実効仕事関数への影響を阻止するのに充分な厚さを有する。バリア金属ゲート電極層107の厚さは、2nm〜5nmの範囲である。

【0086】

処理フローでのこの時点で、第1ゲートスタックは、第1誘電体キャップ層104の上に、これと接触するゲート誘電体ホスト層105の上に、これと接触する第1金属ゲート電極層106の上に、これと接触するバリア金属ゲート電極層107を含む。第2ゲートスタックは、第1誘電体キャップ層104の上に、これと接触するゲート誘電体ホスト層105の上に、これと接触する第1金属ゲート電極層106を含む。

【0087】

次の処理ステップ(図5)において、第2ゲート誘電体キャップ層108が第1領域101および第2領域102に形成される。より詳細には、第2ゲート誘電体キャップ層108は、第1領域101では第1金属ゲート電極層106の上にこれと接触するように、第2領域102ではバリア金属ゲート電極層107の上にこれと接触するように形成される。好ましくは、等角(conformal)の第2ゲート誘電体キャップ層108が、ALD、CVDまたはPVDを用いて形成される。

【0088】

第2ゲート誘電体キャップ層108は、LaO(N),AlO(N),AlN,DyO(N),ScO(N),GdO(N),CeO(N),TbO(N),ErO(N)またはこれらの組合せを含んでもよい。第2ゲート誘電体キャップ層108の材料に応じて、この層は、NMOSデバイスまたはPMOSデバイスに向けて第1実効仕事関数を調整するのに適したものでもよい。例えば、DyOは、より正に帯電した原子を持つ誘電体として知られており、誘電体(例えば、HfSiON−DyOスタック)の内蔵(built-in)ダイポール電界は、金属ゲート(TiN)の仕事関数とは独立して、NMOSデバイスの閾値電圧に適合できる。こうしてDyO層は、NMOSトランジスタに適した実効仕事関数を決定することになる。

【0089】

例えば、AlOは、より負に帯電した原子を持つ誘電体として知られており、誘電体(例えば、HfSiON−AlOスタック)の内蔵(built-in)ダイポール電界は、金属ゲート(TiN)の仕事関数とは独立して、PMOSデバイスの閾値電圧に適合できる。こうしてAlO層は、PMOSトランジスタに適した実効仕事関数を決定することになる。

【0090】

第2ゲート誘電体キャップ層108は、好ましくは、0.2nm〜2nmの範囲、より好ましくは0.2nm〜1nmの範囲、さらにより好ましくは0.2nm〜0.5nmの範囲の等価酸化膜厚(EOT: Equivalent Oxide Thickness)を有してもよい。これは、0.5〜2nmの範囲の誘電体キャップ層114の物理厚さに対応する。

【0091】

例えば、第1領域(第1ゲートスタック)は、AlOを含む第1ゲート誘電体キャップ層104を含んでもよい。この誘電体は、(第1)ゲートスタックの実効仕事関数をP型に向けて調整するのに適したものとして知られている。第2領域(第2ゲートスタック)における第2ゲート誘電体層108は、LaOを含んでもよい。この誘電体は、(第2)ゲートスタックの実効仕事関数をN型に向けて調整するのに適したものとして知られている。第1ゲート誘電体キャップ層104および第2ゲート誘電体キャップ層108としてAlOおよびLaOをそれぞれ用いることによって、第1および第2ゲートスタックの実効仕事関数は、例えば、Ta2Cを含む同じ第1金属ゲート電極層106を用いて、PMOSおよびNMOSに向けてそれぞれ調整することができる。

【0092】

本発明の幾つかの実施形態の利点は、第2ゲート誘電体キャップ層108は、第2領域102において第2ゲートスタック(第2トランジスタ)の実効仕事関数を調整するためだけのものであり、第1領域101において第1ゲートスタックに存在したままであることである。バリア金属層107の存在により、第2ゲート誘電体キャップ層108は、第1ゲートスタックの実効仕事関数に影響を及ぼさない。

【0093】

本発明の幾つかの実施形態の利点は、第2ゲート誘電体キャップ層108は、選択的にエッチングする必要がない。本発明の幾つかの実施形態の利点は、二重仕事関数半導体デバイスを製造するための処理ステップ数が著しく減少することである。第2ゲート誘電体キャップ層はエッチングする必要がないため、レジスト塗布、レジストのリソグラフ露光、レジストの現像およびエッチングというステップを含む追加のパターン形成ステップなしで、第2ゲート誘電体キャップ層をデバイス全体に渡って堆積させることができる。

【0094】

第2領域102において第2ゲートスタックの実効仕事関数を調整するのに適した第2ゲート誘電体キャップ層108を有するために、次の処理ステップでは、第2金属ゲート電極層109が第1領域101および第2領域102に形成される。その結果、第2金属ゲート電極層109は、第2ゲート誘電体キャップ層108に(この上に接触して)横たわる(図6)。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属を含み、より好ましくは、第1金属ゲート電極層106と同じ金属組成からなる。

【0095】

本発明の幾つかの実施形態の利点は、同一の金属ゲート電極材料が、第1ゲートスタック(第1トランジスタ)および第2ゲートスタック(第2トランジスタ)の両方で用いられることである。

【0096】

続く処理ステップでは、従来の技術(リソグラフ、エッチング)を用いて層スタックがパターン化されて、第1ゲートスタック111を第1領域101に、第2ゲートスタック112を第2領域102に形成する(図7)。第1ゲートスタック111は、第1ゲート誘電体キャップ層104の上に、これと接触するゲート誘電体ホスト層105の上に、これと接触する第1金属ゲート電極層106の上に、これと接触するバリア金属電極層107の上に、これと接触する第2ゲート誘電体キャップ層108の上に、これと接触する第2金属ゲート電極層109を含む。

【0097】

第2ゲートスタック112は、第1ゲート誘電体キャップ層104の上に、これと接触するゲート誘電体ホスト層105の上に、これと接触する第1金属ゲート電極層106の上に、これと接触するバリア金属電極層107の上に、これと接触する第2ゲート誘電体キャップ層108を含む。

【0098】

第1ゲートスタック111での第1実効仕事関数は、バリア金属電極層107、第1金属ゲート電極層106および第1ゲート誘電体キャップ層104の組合せによって決定される。第2ゲートスタック112での第2実効仕事関数は、第1金属ゲート電極層106、第2金属ゲート電極層109および、第1金属ゲート電極層106と第2金属ゲート電極層109の間に挟まれた第2ゲート誘電体キャップ層108の組合せによって決定される。第1実効仕事関数および第2実効仕事関数は相違する。第1ゲートスタックの第1実効仕事関数は、好ましくは、第2ゲートスタックの第2実効仕事関数より大きい。第1実効仕事関数は、好ましくは、PMOSデバイスに適しており、第2実効仕事関数は、好ましくは、NMOSデバイスに適しており、逆も同様である。

【0099】

バリア金属ゲート電極層107は、第1ゲートスタック111の第1実効仕事関数に対する第2金属ゲート電極層109および第2ゲート誘電体キャップ層108の影響を防止する。

【0100】

本発明の幾つかの実施形態の利点は、第2ゲート誘電体キャップ層108が選択的除去ステップを経験する必要がないことである。フォトレジストの剥離、ゲートエッジでのホスト誘電体のアンダーカット、表面化学攻撃の問題に関する心配がない。

【0101】

本発明の幾つかの実施形態の更なる利点は、ゲート誘電体ホスト層に向かう選択的エッチングを必要しないため、処理ステップが簡単かつ費用効果的に維持できることである。

【0102】

本発明の幾つかの実施形態の他の利点は、第1ゲートスタック111の第1実効仕事関数が、第1ゲート誘電体キャップ層だけでなく、バリア金属ゲート電極層107として適切な材料を選ぶことによるバリア金属ゲート電極層107の仕事関数調整機能も用いることによって、ある理想的な値に向けて影響を与えられることである。

【0103】

上述の説明は、本発明の幾つかの実施形態を詳しく述べている。しかしながら、上述が文章中にどのように詳説されているかに関わらず、本発明は多くの方法で実用化できることは理解されよう。本発明の幾つかの特徴または態様を説明する場合、特定の用語の使用が、該用語がここで再定義されて、その用語が関連した本発明の特徴または態様の何れか特定の特性を含むように限定されることを意味することとすべきでないことに留意すべきである。

【0104】

上記詳細な説明は、種々の実施形態に適用されるような本発明の新規な特徴を示し、説明し、指摘するとともに、本発明の精神から逸脱することなく、説明したデバイスまたはプロセスの形態および詳細における種々の省略、置換、変化が当業者によって可能であることと理解されよう。

【技術分野】

【0001】

本発明は、一般には、半導体デバイスの製造方法に関し、特に、金属ゲート電極を備えたゲートスタックを有するCMOSデバイスの製造方法および、これで製作されるCMOSデバイスに関する。

【背景技術】

【0002】

今日まで、半導体産業は、金属−酸化物−半導体電界効果トランジスタ(MOSFET)の幾何寸法のスケーリングによって活発な状態である。二酸化シリコン(SiO2)をゲート誘電体として、多結晶シリコン(poly-Si)をゲート材料として用いる従来のMOSFET技術では、100nmまたはそれ以下にスケールダウンした場合、多くの問題が発生する。

【0003】

ゲート誘電体の厚さが減少すると、ゲート直接トンネル電流の指数関数的な増加が生ずる。45nmテクノロジーノード超についてこの問題を解決する1つの手法は、ゲート誘電体として、いわゆる高誘電率(high-k)誘電体の導入である。高誘電率(high-k)誘電体は、SiO2の誘電定数より大きい誘電定数(k)、即ち、k>3.9を示す誘電体である。高誘電率(high-k)誘電体は、より大きな物理厚さ(SiO2と比べて)を可能にし、より薄いSiO2層で得られるものと同じ実効静電容量が得られる。より大きな物理厚さの高誘電率(high-k)材料は、ゲート漏れ電流を減少させる。

【0004】

2nm未満のSiO2酸化物厚さでは、ポリシリコン(poly-Si)空乏効果は、ポリSiゲートで支配的であることからスタートする。この問題の解決法は、ゲート材料として、金属の導入である。金属ゲートの利点は、ポリシリコン空乏効果の排除、極めて低い抵抗、可能性あるドーパント侵入がないこと、高誘電率(high-k)誘電体とのより良好な適合性である。

【0005】

金属ゲートを導入することによって、MOSFETの閾値電圧は、金属の仕事関数によって制御されるようになる。金属ゲート電極に関して、NMOSとPMOSとで異なる仕事関数が必要になるため、仕事関数の調整は単純明快なものではない。このことは、n−MOSFETについて機能する(n型)金属(ポリSiと置換)(即ち、好ましくは、約3.9eV〜約4.2eVの仕事関数)および、p−MOSFETについて機能する(p型)金属(即ち、好ましくは、約4.9eV〜約5.2eVの仕事関数)を必要とする。ポリシリコンゲート電極の仕事関数は、イオン注入(implantation)によって調整可能であるが、金属ゲート電極の仕事関数は、容易に変化しない材料の性質である。

【発明の概要】

【発明が解決しようとする課題】

【0006】

新たなゲート材料、例えば、金属ゲート電極と組み合わせた高誘電率(high-k)誘電体などの導入は、簡単ではない。エッチングや剥ぎ取り(strip)など、従来のゲート第1製造処理ステップにおいて問題が生ずることがあるためである。従って、相補型金属−酸化物−半導体デバイス(CMOS)における高誘電率(high-k)ゲート誘電体と金属ゲート誘電体との集積化では、新たな代替物を処理フローに導入する必要がある。CMOSデバイスにおける金属ゲートと高誘電率(high-k)誘電体との集積化のための最新の先行技術において利用できる可能性があるが、高誘電率(high-k)/金属半導体デバイスのために簡単化した集積機構、より具体的には、簡単化した二重金属二重誘電体(DMDD)集積機構のニーズが存在する。

【課題を解決するための手段】

【0007】

1つの発明態様は、二重仕事関数半導体デバイスに関するものであり、該デバイスは、半導体基板と、半導体基板の第1領域にあって、第1ゲートスタックを含む第1トランジスタと、半導体基板の第2領域にあって、第2ゲートスタックを含む第2トランジスタとを備え、

第1ゲートスタックは、第1実効仕事関数を有し、第2ゲートスタックは、第1実効仕事関数とは異なる第2実効仕事関数を有し、

第1ゲートスタックは、第2ゲート誘電体キャップ層の上にある第2金属ゲート電極を備え、第2ゲート誘電体キャップ層はバリア金属ゲート電極の上にあり、バリア金属ゲート電極は第1金属ゲート電極層の上にあり、第1金属ゲート電極層はゲート誘電体ホスト層の上にあり、ゲート誘電体ホスト層は第1ゲート誘電体キャップ層の上にあり、第1ゲート誘電体キャップ層は第1領域において半導体基板の上にあり、

第2ゲートスタックは、第2ゲート誘電体キャップ層の上にある第2金属ゲート電極を備え、第2ゲート誘電体キャップ層は第1金属ゲート電極の上にあり、第1金属ゲート電極はゲート誘電体ホスト層の上にあり、ゲート誘電体ホスト層は第2領域において半導体基板の上にあり、

第1および第2ゲートスタックの第2金属ゲート電極層は、第1および第2ゲートスタックの第1金属ゲート電極層と同じ金属組成からなる。

【0008】

本発明の第1態様の実施形態によれば、第1ゲートスタックの第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数を調整するように選択される。

【0009】

本発明の第1態様の他の実施形態によれば、第2ゲートスタックの第1金属ゲート電極層、第2ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数を調整するように選択される。

【0010】

本発明の第1態様の他の実施形態によれば、第1実効仕事関数は、第2実効仕事関数より大きい。好ましくは、第1ゲートスタックの第1実効仕事関数は、4.9eV〜5.5eVの範囲である。第2実効仕事関数は、好ましくは、3.9eV〜4.5eVの範囲である。第1トランジスタは、好ましくは、PMOSトランジスタである。第2トランジスタは、好ましくは、NMOSトランジスタである。

【0011】

本発明の第1態様の他の実施形態によれば、第1ゲート誘電体キャップ層は、Alベースの誘電体である。より具体的には、第1ゲート誘電体キャップ層は、AlO,AlN,AlONおよびこれらの混合物からなるグループから選択される。

【0012】

本発明の第1態様の他の実施形態によれば、第2ゲート誘電体キャップ層は、ランタン系列ベースの誘電体である。より具体的には、第2ゲート誘電体キャップ層は、DyO,LaO,GdO,ErOおよびこれらの混合物からなるグループから選択される。

【0013】

本発明の第1態様の他の実施形態によれば、バリア金属ゲート電極層は、TiNを含む。代替として、バリア金属ゲート電極層は、TaNを含んでもよい。

【0014】

本発明の第1態様の他の実施形態によれば、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される材料を含む。

【0015】

本発明の第1態様の他の実施形態によれば、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCyNzOw(x,y,z,wの実数値は0<x,y,z,w<1)を含む。

【0016】

本発明の第1態様の他の実施形態によれば、ゲート誘電体ホスト層は、SiO2,SiON,HfO2,ZrO2およびこれらの混合物からなるグループから選択される。

【0017】

第1態様の好ましい実施形態によれば、第1ゲート誘電体キャップ層は、AlO,AlN,AlONおよびこれらの混合物からなるグループから選択され、第2ゲート誘電体キャップ層は、DyO,LaO,GdO,ErOおよびこれらの混合物からなるグループから選択され、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される材料を含み、バリア金属ゲート電極層は、TiNを含む。

【0018】

本発明の第2の発明態様は、二重仕事関数半導体デバイスを形成する方法に関するものであり、該方法は、半導体基板に第1領域および第2領域を設けることと、

【0019】

第1実効仕事関数を有する第1ゲートスタックを第1領域に形成し、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタックを第2領域に形成することとを含み、

第1ゲート誘電体キャップ層を第1領域に形成するステップ、

ゲート誘電体層を第1領域および第2領域に形成して、第1領域においてゲート誘電体層を第1ゲート誘電体キャップ層の上に載せるステップ、

第1金属ゲート電極材料を第1領域および第2領域に形成して、第1金属ゲート電極材料をゲート誘電体層の上に載せるステップ、

バリア金属ゲート電極層を第1領域に形成して、バリア金属ゲート電極層を第1金属ゲート電極層の上に載せるステップ、

第2ゲート誘電体キャップ層を第2領域に形成して、第2ゲート誘電体キャップ層を第1金属ゲート電極層の上に載せるステップ、

第2金属ゲート電極層を第1領域および第2領域に形成して、第2金属ゲート電極層を第2ゲート誘電体キャップ層の上に載せるステップを含み、

第1ゲートスタックおよび第2ゲートスタックの第2金属ゲート電極層は、第1ゲートスタックおよび第2ゲートスタックの第1金属ゲート電極層と同じ金属組成からなる。

【0020】

本発明の第2態様の実施形態によれば、該方法は、第2金属ゲート電極層、第2ゲート誘電体キャップ層、バリア金属ゲート電極層、ゲート誘電体ホスト層および第1ゲート誘電体キャップ層をパターン化して、第1ゲートスタックを形成すること、および、

【0021】

第2金属ゲート電極層、第2ゲート誘電体キャップ層、第1金属ゲート電極層およびゲート誘電体ホスト層をパターン化して、第2ゲートスタックを形成することをさらに含む。

【0022】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数を調整するように選択される。

【0023】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層、第2ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数を調整するように選択される。

【0024】

本発明の第2態様の他の実施形態によれば、第1実効仕事関数は、第2実効仕事関数より大きい。

【0025】

本発明の第2態様の他の実施形態によれば、第1実効仕事関数は、4.9eV〜5.5eVの範囲である。

【0026】

本発明の第2態様の他の実施形態によれば、第2実効仕事関数は、3.9eV〜4.5eVの範囲である。

【0027】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数をPMOS実効仕事関数に向けて調整するように選択される。

【0028】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数をNMOS実効仕事関数に向けて調整するように選択される。

【0029】

本発明の第2態様の他の実施形態によれば、第1ゲート誘電体キャップ層は、Alベースの誘電体である。より具体的には、第1ゲート誘電体キャップ層は、AlO,AlN,AlONおよびこれらの混合物からなるグループから選択される。

【0030】

本発明の第2態様の他の実施形態によれば、第2ゲート誘電体キャップ層は、ランタン系列ベースの誘電体である。より具体的には、第2ゲート誘電体キャップ層は、DyO,LaO,GdO,ErOおよびこれらの混合物からなるグループから選択される。

【0031】

本発明の第2態様の他の実施形態によれば、バリア金属ゲート電極層は、TiNまたはTaNを含む。

【0032】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される材料を含む。

【0033】

本発明の第2態様の他の実施形態によれば、第1金属ゲート電極層および第2金属ゲート電極層は、TaxCyNzOw(x,y,z,wの実数値は0<x,y,z,w<1)を含む。

【0034】

本発明の第2態様の他の実施形態によれば、ゲート誘電体ホスト層は、SiO2,SiON,HfO2,ZrO2およびこれらの混合物からなるグループから選択される。

【図面の簡単な説明】

【0035】

全ての図面は、本発明の幾つかの態様および実施形態を図示することを意図している。記載した図面は、概略的で非限定的に過ぎない。図面において、幾つかの要素のサイズは、説明目的のために、誇張したり、スケールどおりに描いていないこともある。例示の実施形態は、図面の参照した図に示している。ここで開示した実施形態および図面は、限定的なものではなく、例示的なものと考えることを意図している。異なる図面では、同じ参照符号は、同じまたは類似の要素を参照している。

【0036】

【図1】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図2】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図3】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図4】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図5】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図6】二重仕事関数半導体デバイスの製造方法についての本発明の実施形態に係る幾つかの処理ステップに対応したデバイスの概略断面図を示す。

【図7】本発明の態様に係る二重仕事関数半導体デバイスの概略断面図を示す。

【発明を実施するための形態】

【0037】

本発明の1つ又はそれ以上の実施形態について、添付した図面を参照して詳細に説明する。本発明はこれに限定されない。記載した図面は、概略的かつ非限定的なものである。図面において、幾つかの要素のサイズは、説明目的のために誇張したり、縮尺どおり描写していないことがある。寸法および相対寸法は、本発明の実際の具体化に必ずしも対応していない。当業者は、その範囲で包囲される本発明の多数の変化および変更を認識できる。従って、好ましい実施形態の説明は、本発明の範囲を限定するものとみなすべきでない。

【0038】

さらに、説明での用語、「第1」、「第2」などは、類似の要素を区別するための使用しており、必ずしも連続した順または時間順を記述するためではない。こうして用いた用語は、適切な状況下で交換可能であり、本発明の実施形態は、ここで説明したり図示したものとは別の順番で動作可能である。

【0039】

さらに、説明および請求項の中の用語「上(top)」、「下(bottom)」、「の上に(over)」、「の下に(under)」等は、説明目的で使用しており、必ずしも相対的な位置を記述するためのものでない。こうして用いた用語は、適切な状況下で交換可能であって、ここで説明した本発明の実施形態がここで説明または図示した以外の他の向きで動作可能であると理解すべきである。例えば。ある要素の「下方(underneath)」および「上方(above)」は、この要素の対向側に配置されることを示す。

【0040】

ここで提供した説明において、多数の特定の詳細を記述している。しかしながら、本発明の実施形態は、これらの特定の詳細なしでも実用化できると理解される。例えば、周知の方法、構造およびテクニックは、本説明の理解を曖昧にしないために詳細には示していない。

【0041】

ここでは、特定の化学名または化学式が与えられた場合、その材料は、化学名で識別される化学量論的に正確な式の非化学量論的な変形を含んでもよい。式中の元素の下付き数値が無いのは、数字の「1」を意味する。本発明の目的では、正確な化学量論的数字の±20%の範囲内の変動は、その化学名または化学式に含まれる。代数的な下付き文字が与えられた場合、各下付き数値に対して約±20%の範囲内の変動は含まれる。こうして変動する値は、合計しても必ずしも整数にならず、この逸脱は予測される。こうした変動は、処理条件の意図した選択および制御、あるいは意図した処理変動に起因して、生ずることがある。

【0042】

用語「備える、含む(comprising)」は、それ以降に列挙された手段に限定されるものと解釈すべきでなく、他の要素またはステップを除外していないことに留意する。そして「手段A,Bを備えるデバイス」という表現の範囲は、構成要素A,Bだけからなる素子に限定すべきでない。本発明に関して、デバイスの関連した構成要素だけがA,Bであることを意味する。

【0043】

本発明の種々の実施形態は、半導体デバイスのパラメータ、例えば、閾値電圧(Vt)、実効仕事関数(WFeff)、使用する材料の物理的特性、例えば、仕事関数(WF)、フェルミ準位などを参照している。本書で用いている定義は、下記のように整理できる。

【0044】

MOSFETデバイスにおいて、ゲートは、チャネルを導通させるための閾値電圧(Vt)を要する。相補型MOS(CMOS)処理は、n−チャネルおよびp−チャネル(それぞれNMOS、PMOS)トランジスタの両方を製造する。閾値電圧Vtの差、即ち、NMOS、PMOSトランジスタ間の閾値電圧の差は、実効仕事関数の差(ΔWFeff)と呼ばれるものによって影響を受ける。実効仕事関数の差は、NMOSトランジスタの実効仕事関数とPMOSトランジスタの実効仕事関数との差である。

【0045】

PMOSトランジスタおよびNMOSトランジスタについてそれぞれ閾値電圧(Vt)を設定するには、個々のPMOSおよびNMOSのゲート材料(ゲートスタック)の実効仕事関数の差およびこれらの対応するチャネル領域が、チャネル処理およびゲート処理を通じて独立に設定される。換言すると、ゲート誘電体(即ち、ホスト誘電体および任意の異なるキャップ層を含む)およびゲート電極(少なくとも1つの金属層を含む)は、ゲートスタック(デバイス)の実効仕事関数(WFeff)を決定する。さらに、ゲート処理自体(即ち、異なるステップ及び/又は印加される熱処理の順序)は、ゲートスタック(デバイス)の実効仕事関数(WFeff)に影響を及ぼす。

【0046】

ゲートスタック(デバイス)の実効仕事関数(WFeff)は、ゲート誘電体材料、ゲート電極材料の選択および実施するゲート処理によって調整可能なパラメータである。これに対して、ゲート電極(しばしば金属ゲート電極または金属層電極または金属制御電極と称される)の仕事関数(WF)は、材料固有の性質である。一般に、ある材料の仕事関数は、電子が初期にフェルミ準位にある場合、材料中の電子を材料原子の外部へ真空に脱出させるのに要するエネルギーの単位、電子ボルト(eV)である。ゲート電極の仕事関数は、堆積状態(as-deposited)の仕事関数または材料固有の仕事関数とも称される。

【0047】

シリコン基板では、負チャネルMOSFET(またはNMOS)デバイスのゲート電極は、約4.1eV(±0.3eV)のn型仕事関数を有し、正チャネルMOSFET(またはPMOS)デバイスのゲート電極は、約5.2eV(±0.3eV)のp型仕事関数を有するであろう。

【0048】

高誘電率(high-k)誘電体は、SiO2の誘電定数より大きい誘電定数(k)、即ち、k>3.9を示す誘電体である。高誘電率(high-k)誘電体は、より大きな物理厚さ(SiO2と比べて)を可能にし、より薄いSiO2層で得られるものと同じ実効静電容量が得られる。

【0049】

下記において、本発明は、シリコン(Si)基板を参照して説明するが、本発明は他の半導体基板にも同じように適用されると理解すべきである。実施形態において、「基板」は、半導体基板、例えば、シリコン、ガリウムヒ素(GaAs)、ガリウムヒ素リン(GaAsP)、インジウムリン(InP)、ゲルマニウム(Ge)またはシリコンゲルマニウム(SiGe)の基板などを含む。「基板」は、半導体基板部分へ追加された、例えば、SiO2層またはSi3N4層などの絶縁層を含んでもよい。そして、用語「基板」は、シリコン・オン・ガラス基板、シリコン・オン・サファイア基板を含んでもよい。用語「基板」は、対象となる層または部分の下地となる層のための要素を一般に規定するために用いられる。「基板」は、ある層、例えば、ガラスや金属層が上に形成される他の何れかのベースであってもよい。従って、基板は、ウエハ、例えば、ブランケットウエハなどでもよく、あるいは、他のベース材料に付着した層、例えば、下側層の上に成長したエピタキシャル層でもよい。

【0050】

本発明の第1態様は、二重仕事関数半導体デバイスに関するものであり、該二重仕事関数半導体デバイスは、

半導体基板と、

半導体基板の第1領域に、第1ゲートスタックを含む第1トランジスタと、半導体基板の第2領域に、第2ゲートスタックを含む第2トランジスタとを備え、

第1ゲートスタックは、第1実効仕事関数を有し、第2ゲートスタックは、第1実効仕事関数とは異なる第2実効仕事関数を有し、

第1ゲートスタックは、第2ゲート誘電体キャップ層の上にあって、これと接触する第2金属ゲート電極と、バリア金属ゲート電極の上にあって、これと接触する第2ゲート誘電体キャップ層と、第1金属ゲート電極層の上にあって、これと接触するバリア金属ゲート電極と、ゲート誘電体ホスト層の上にあって、これと接触する第1金属ゲート電極層と、第1ゲート誘電体キャップ層の上にあって、これと接触するゲート誘電体ホスト層と、第1領域において半導体基板の上にあって、これと接触する第1ゲート誘電体キャップ層とを備え、

第2ゲートスタックは、第2ゲート誘電体キャップ層の上にあって、これと接触する第2金属ゲート電極と、第1金属ゲート電極の上にあって、これと接触する第2ゲート誘電体キャップ層と、ゲート誘電体ホスト層の上にあって、これと接触する第1金属ゲート電極と、第2領域において半導体基板の上にあって、これと接触するゲート誘電体ホスト層とを備え、

第1および第2ゲートスタックの第2金属ゲート電極層は、第1および第2ゲートスタックの第1金属ゲート電極層と同じ金属組成からなる。

【0051】

図7は、本発明の第1態様に係る二重仕事関数半導体デバイスの断面図を示す。

【0052】

第1金属ゲート電極、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、この層スタックが第1ゲートスタック111の第1実効仕事関数WF1effを調整できるように選択される。必要に応じて、ゲート誘電体ホスト層も、第1ゲートスタック111の第1実効仕事関数WF1effをさらに調整するように選択してもよい。好ましくは、第1ゲートスタック111の第1実効仕事関数WF1effは、約5.2eV(±0.3eV)の値に向けて適合される。第1ゲートスタックは、好ましくは、正チャネルMOSFET(またはPMOS)デバイス用に形成される。そして、第1トランジスタは、好ましくは、PMOSトランジスタを備える。

【0053】

第1金属ゲート電極、第2金属ゲート電極および第2ゲート誘電体キャップ層は、この層スタックが第2ゲートスタック112の第2実効仕事関数WF2effを調整できるように選択される。必要に応じて、この層スタックは、第2実効仕事関数WF2effをさらに調整するように、ゲート誘電体ホスト層を含んでもよい。好ましくは、第2ゲートスタック112の第2実効仕事関数WF2effは、約4.2eV(±0.3eV)の値に向けて適合される。第2ゲートスタックは、好ましくは、負チャネルMOSFET(またはNMOS)デバイス用に形成される。そして、第2トランジスタは、好ましくは、NMOSトランジスタを備える。

【0054】

一実施形態において、第1トランジスタはPMOSトランジスタを備え、第2トランジスタはNMOSトランジスタを備え、第1ゲート誘電体キャップ層は、好ましくは、第2ゲート誘電体キャップ層からの他の誘電体元素と比較して、より高い電気陰性度を持つ誘電体元素を含む。

【0055】

第1ゲート誘電体キャップ層は、好ましくは、より負に帯電した原子を持つ誘電体元素を含み、一方、第2ゲート誘電体キャップ層は、好ましくは、より正に帯電した原子を持つ他の誘電体元素を含む。第1ゲート誘電体キャップ層は、好ましくは、Alベースの誘電体、例えば、AlO,AlN,AlONおよびこれらの混合物を含む。一方、第2ゲート誘電体キャップ層は、好ましくは、ランタン系列ベースの誘電体、例えば、DyO(N),LaO(N),ScO(N),GdO(N),TbO(N),YbO(N),ErO(N)およびこれらの混合物の何れかを含む。

【0056】

一実施形態において、第1および第2金属ゲート電極は、p型仕事関数を有する金属層を含んでもよい。好都合には、第1および第2金属ゲート電極は、p型仕事関数を有する金属層からなる。第1および第2金属層は、Taベース、Wベース、Moベースの材料を含んでもよい。より好都合には、金属ゲート電極は、TaxCyNzOw(x,y,z,wの実数値は0<x,y,z,w<1)からなる。

【0057】

他の実施形態において、第1および第2金属ゲート電極は、n型仕事関数を有する金属層を含んでもよい。好都合には、第1および第2金属ゲート電極は、n型仕事関数を有する金属層からなる。第1および第2金属層は、Taベース、Tiベースの材料を含んでもよい。より好都合には、第1および第2金属層材料は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される。

【0058】

一実施形態において、ゲート誘電体ホスト層は、SiO2,SiON,HfO2,ZrO2およびこれらの混合物からなるグループから選択される。これらの材料は、シリコン基板との安定した界面という利点を示す。

【0059】

バリア金属ゲート電極は、好ましくは、第1実効仕事関数に対する、第1トランジスタでの第2ゲート誘電体キャップ層および第2金属ゲート電極の影響を阻止する金属含有材料を含む。バリア金属ゲート電極の金属含有材料は、第1実効仕事関数を調整するように選択してもよい(第1ゲート誘電体キャップ層と共に)。好都合には、バリア金属ゲート電極は、TiNを含んでもよい。バリア金属ゲート電極は、TaNを含んでもよい。

【0060】

本発明の第2態様は、二重仕事関数半導体デバイスを製造する方法に関するものであり、該方法は、下記ステップを含む。

【0061】

・半導体基板に第1領域および第2領域を設けること、

・第1実効仕事関数を有する第1ゲートスタックを第1領域に備える第1トランジスタを形成し、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタックを第2領域に有する第2トランジスタを形成すること、

・第1ゲート誘電体キャップ層を第1領域だけに形成すること、

・ゲート誘電体ホスト層を第1領域および第2領域に形成して、ゲート誘電体ホスト層を第1領域において第1ゲート誘電体キャップ層の上に載せること、

・第1金属ゲート電極材料を第1領域および第2領域に形成して、第1金属ゲート電極材料をゲート誘電体ホスト層の上に載せること、

・バリア金属ゲート電極層を第1領域だけに形成して、バリア金属ゲート電極層を第1金属ゲート電極層の上に載せること、

・第2ゲート誘電体キャップ層を第1領域および第2領域に形成して、第1領域において第2ゲート誘電体キャップ層をバリア金属ゲート電極層の上に載せ、第2領域において第2ゲート誘電体キャップ層を第1金属ゲート電極層の上に載せること、

・第2金属ゲート電極層を第1領域および第2領域に形成して、第2金属ゲート電極層を第2ゲート誘電体キャップ層の上に載せることを含み、

・第2金属ゲート電極層は、第1金属ゲート電極層と同じ金属を含む。

【0062】

図1〜図7を参照して、本発明の第2態様に係る二重仕事関数半導体デバイスの製造方法のための異なる処理ステップをより詳細に説明する。

【0063】

図1は、半導体基板100、例えば、シリコン基板を示す。基板100は、複数の別個の領域を含んでもよい。最も好ましくは、2つの別個の領域が基板100において規定することができ、即ち、図1に示すように、第1領域101と第2領域102である。第1領域101は、デバイスの第1活性領域とも称され、第1トランジスタが形成される部分であり、第2領域102は、デバイスの第2活性領域とも称され、第2トランジスタが形成される部分である。

【0064】

第1領域101および第2領域102は、絶縁領域103によって互いに電気絶縁してもよい。第1領域101および第2領域102を相互に分離する可能な方法は、両者の間にSTI(shallow trench isolation)を使用することである。STIは、深く狭い溝であり、集積回路内で隣接するデバイス間で半導体基板にエッチングされ、酸化物で充填されて、両者の電気的分離を提供する。代替として、LOCOS(local oxidation of silicon:シリコン局所酸化)を用いてもよい。第1領域101は、例えば、PMOS領域であり、第2領域102例えば、NMOS領域であり、その逆でもよい。

【0065】

基板に第1および第2領域を設けた後、第1ゲートスタックおよび第2ゲートスタックが第1および第2活性領域にそれぞれ形成される。その後、第1領域101だけに存在する第1ゲート誘電体キャップ層104が設けられる(図2)。第1ゲート誘電体キャップ層104の設置は、当業者に周知であるような従来の処理ステップおよび設備を用いてもよく、例えば、最初にゲート誘電体キャップ層を基板上の第1および第2領域の両方に堆積し、続いて、従来のリソグラフステップを用いてゲート誘電体キャップ層をパターン化して、第2領域102にあるゲート誘電体キャップ層の一部を除去する。

【0066】

第1ゲート誘電体キャップ層104の材料は、第1ゲートスタックの第1実効仕事関数を調整するように選択される。さらに後でも、集積構造において、第1/第2金属ゲート電極層の材料は、第1ゲートスタックの第1実効仕事関数をさらに調整するように選択される。

【0067】

一実施形態において、第1ゲート誘電体キャップ層104は、Alベースの誘電体、またはランタン系列ベースの誘電体でもよい。第1ゲート誘電体キャップ層104は、LaO(N),AlO(N),AlN,DyO(N),ScO(N),GdO(N),CeO(N),TbO(N),ErO(N),YbO(N)またはこれらの組合せを含んでもよい。

【0068】

第1ゲート誘電体キャップ層104の材料に応じて、この層は、第1実効仕事関数をNMOSデバイスまたはPMOSデバイスに向けて調整するのに適したものでもよい。例えば、DyOは、より正に帯電した原子を持つ誘電体として知られており、誘電体(例えば、HfSiON−DyOスタック)の内蔵(built-in)ダイポール電界は、金属ゲート(例えば、TiN)の仕事関数とは独立して、NMOSデバイスの閾値電圧に適合できる。こうしてDyO層は、NMOSトランジスタに適した実効仕事関数を決定することになる。

【0069】

例えば、AlOは、より負に帯電した原子を持つ誘電体として知られており、誘電体(例えば、HfSiON−AlOスタック)の内蔵(built-in)ダイポール電界は、金属ゲート(例えば、TiN)の仕事関数とは独立して、PMOSデバイスの閾値電圧に適合できる。こうしてAlO層は、PMOSトランジスタに適した実効仕事関数を決定することになる。

【0070】

第1ゲート誘電体キャップ層104は、好ましくは、0.2nm〜2nmの範囲、より好ましくは0.2nm〜1nmの範囲、さらにより好ましくは0.2nm〜0.5nmの範囲の等価酸化膜厚(EOT: Equivalent Oxide Thickness)を有してもよい。これは、0.5〜2nmの範囲の誘電体キャップ層114の物理厚さに対応する。

【0071】

第1ゲート誘電体キャップ層104は、ALD,PVDまたはCVDなど任意の堆積技術を用いて形成される。

【0072】

(第1)ゲート誘電体キャップ層104を第1領域101に設けた後、ゲート誘電体ホスト層105を第1領域101および第2領域102に設ける。ゲート誘電体ホスト層105は、第1領域101では(第1)ゲート誘電体キャップ層104の上にあって、これと接触しており、第2領域102では基板100の上にあって、これと接触している(図2)。

【0073】

ゲート誘電体ホスト層105は、絶縁材料、例えば、二酸化シリコン(SiO2),窒化シリコン(SiN)または酸窒化シリコン(SixOyN1−x−y)、あるいは高誘電率(high-k)誘電体(即ち、k>3.9)、例えば、HfO2,TaOx,Al2O3,ZrO2またはこれらの組合せ等、からなる層でもよい。これらの材料は、シリコン基板100との安定した界面という利点を提供する。

【0074】

ゲート誘電体ホスト層は、熱酸化、化学気相成長(CVD)または、当業者に知られている何れかの他の適切な方法によって形成してもよい。ゲート誘電体ホスト層105は、誘電体材料のスタックを含んでもよく、例えば、高誘電率(high-k)材料が、基板100と高誘電率(high-k)材料の間にある(任意の)界面誘電体層(不図示)の上に形成される。

【0075】

ゲート誘電体ホスト層105は、好ましくは、0.5nm〜4nmの範囲の厚さを有する。第2領域でのゲート誘電体ホスト層の厚さは、第1領域でのゲート誘電体ホスト層の厚さより大きくてもよい。

【0076】

ゲート誘電体ホスト層105を設けた後、第1金属ゲート電極層106をゲート誘電体ホスト層105の上に横たわる(その上に接触する)ように設ける。その後、バリア金属ゲート電極層107を、第1金属ゲート電極層106の上に、これと接触するように設ける(図3)。

【0077】

第1金属ゲート電極層106は、第1(堆積状態:as-deposited)の仕事関数を有するように形成される。第1金属ゲート電極層106は、金属ゲートを形成する金属含有材料を含む。金属含有材料とは、金属、金属合金、金属シリサイド、導電性金属窒化物、導電性金属酸化物などである。該金属に応じて、第1金属ゲート電極層106の仕事関数は、従来のp型ドープ半導体の仕事関数または従来のn型ドープ半導体の仕事関数と同程度にできる。例えば、ニッケル(Ni),酸化ルテニウム(RuO),窒化モリブデン(MoN)は、p型ドープ半導体材料の仕事関数と同程度の仕事関数を有する。例えば、ルテニウム(Ru),ジルコニウム(Zr),ニオブ(Nb),タンタル(Ta),チタンシリサイド(TiSi2)は、n型ドープ半導体材料の仕事関数と同程度の仕事関数を有する。例えば、TiNは、中間ギャップの仕事関数を有し、即ち、p型ドープ半導体材料とn型ドープ半導体材料の仕事関数の間になる(SiO2上のTiNでは、約4.65eV〜4.8eV)。

【0078】

例えば、金属ゲート電極層106は、第1領域101においてNMOSゲート電極(即ち、NMOSトランジスタ)を形成するのに適した第1(堆積状態:as-deposited)の仕事関数を有するように形成できる。しかし、これは、第2領域102においてPMOSゲート電極(即ち、PMOSトランジスタ)を形成するのに適していない。逆も同様に、金属ゲート電極層115は、第1領域101においてPMOSゲート電極を形成するのに適した第1(堆積状態:as-deposited)の仕事関数を有するように形成できる。しかし、これは、第2領域102においてNMOSゲート電極を形成するのに適していない。

【0079】

両方の領域(NMOSおよびPMOS)について1つの金属ゲート電極材料を用いた二重仕事関数半導体デバイスの形成では、金属ゲート電極層106の仕事関数は、選択的に調整する必要がある。即ち、金属ゲート電極材料106の仕事関数は、第1(堆積状態:as-deposited)の仕事関数が適していない領域において調整する必要がある。堆積状態(as-deposited)の仕事関数とは、材料固有の仕事関数を意味する。

【0080】

第1領域101において第1金属ゲート電極層106の下に配置された第1ゲート誘電体キャップ層104は、第1金属ゲート電極層106の堆積状態の仕事関数WFの第1仕事関数シフトを誘起するようになる。

【0081】

第1金属ゲート電極層106は、0.5nm〜10nmの範囲、より好ましくは5nm〜10nmの範囲の厚さを有し、ALD、CVDまたはPVDなどの堆積技術を用いて堆積される。

【0082】

第1金属ゲート電極層106の形成後、バリア金属電極層107が第1金属ゲート電極層106の上に、これと接触するように形成される(図3)。バリア金属ゲート電極材料107は、0.5nm〜10nmの範囲、より好ましくは5nm〜10nmの範囲の厚さを有し、ALD、CVDまたはPVDなどの堆積技術を用いて堆積される。

【0083】

さらに、バリア金属電極層107の一部、即ち、第2領域にある部分は、当業者に知られた従来のエッチング技術を用いて除去される(図4)。第1金属ゲート電極層106は、エッチング停止層として使用してもよい。こうしてバリア金属ゲート電極層107は、第1金属ゲート電極層106に向けて選択的にエッチングされる。好ましくは、ウェットエッチングが使用できる。例えば、第1金属ゲート電極層がTa2Cを含み、バリア金属層107がTiNを含む場合、第2領域にあるTiNの一部が、高い選択性を持つウェットエッチングを用いてTa2Cに向けて選択的に除去される。

【0084】

バリア金属ゲート電極層107は、好ましくは、下地である第1金属ゲート電極層106に向けて選択的にエッチングできる材料を含む。バリア金属ゲート電極層107は、金属含有材料をさらに含む。第1領域において、最終的な第1ゲートスタックの実効仕事関数は、第1金属ゲート電極層106の仕事関数によって決定され、バリア金属電極層107の仕事関数によって決定され、そして、第1ゲート誘電体キャップ層104によってさらに調整される。

【0085】

バリア金属ゲート電極層107は、下記の処理ステップにおいてこのバリア金属電極層107の上部に形成される追加の層によって誘起され得る実効仕事関数への影響を阻止するのに充分な厚さを有する。バリア金属ゲート電極層107の厚さは、2nm〜5nmの範囲である。

【0086】

処理フローでのこの時点で、第1ゲートスタックは、第1誘電体キャップ層104の上に、これと接触するゲート誘電体ホスト層105の上に、これと接触する第1金属ゲート電極層106の上に、これと接触するバリア金属ゲート電極層107を含む。第2ゲートスタックは、第1誘電体キャップ層104の上に、これと接触するゲート誘電体ホスト層105の上に、これと接触する第1金属ゲート電極層106を含む。

【0087】

次の処理ステップ(図5)において、第2ゲート誘電体キャップ層108が第1領域101および第2領域102に形成される。より詳細には、第2ゲート誘電体キャップ層108は、第1領域101では第1金属ゲート電極層106の上にこれと接触するように、第2領域102ではバリア金属ゲート電極層107の上にこれと接触するように形成される。好ましくは、等角(conformal)の第2ゲート誘電体キャップ層108が、ALD、CVDまたはPVDを用いて形成される。

【0088】

第2ゲート誘電体キャップ層108は、LaO(N),AlO(N),AlN,DyO(N),ScO(N),GdO(N),CeO(N),TbO(N),ErO(N)またはこれらの組合せを含んでもよい。第2ゲート誘電体キャップ層108の材料に応じて、この層は、NMOSデバイスまたはPMOSデバイスに向けて第1実効仕事関数を調整するのに適したものでもよい。例えば、DyOは、より正に帯電した原子を持つ誘電体として知られており、誘電体(例えば、HfSiON−DyOスタック)の内蔵(built-in)ダイポール電界は、金属ゲート(TiN)の仕事関数とは独立して、NMOSデバイスの閾値電圧に適合できる。こうしてDyO層は、NMOSトランジスタに適した実効仕事関数を決定することになる。

【0089】

例えば、AlOは、より負に帯電した原子を持つ誘電体として知られており、誘電体(例えば、HfSiON−AlOスタック)の内蔵(built-in)ダイポール電界は、金属ゲート(TiN)の仕事関数とは独立して、PMOSデバイスの閾値電圧に適合できる。こうしてAlO層は、PMOSトランジスタに適した実効仕事関数を決定することになる。

【0090】

第2ゲート誘電体キャップ層108は、好ましくは、0.2nm〜2nmの範囲、より好ましくは0.2nm〜1nmの範囲、さらにより好ましくは0.2nm〜0.5nmの範囲の等価酸化膜厚(EOT: Equivalent Oxide Thickness)を有してもよい。これは、0.5〜2nmの範囲の誘電体キャップ層114の物理厚さに対応する。

【0091】

例えば、第1領域(第1ゲートスタック)は、AlOを含む第1ゲート誘電体キャップ層104を含んでもよい。この誘電体は、(第1)ゲートスタックの実効仕事関数をP型に向けて調整するのに適したものとして知られている。第2領域(第2ゲートスタック)における第2ゲート誘電体層108は、LaOを含んでもよい。この誘電体は、(第2)ゲートスタックの実効仕事関数をN型に向けて調整するのに適したものとして知られている。第1ゲート誘電体キャップ層104および第2ゲート誘電体キャップ層108としてAlOおよびLaOをそれぞれ用いることによって、第1および第2ゲートスタックの実効仕事関数は、例えば、Ta2Cを含む同じ第1金属ゲート電極層106を用いて、PMOSおよびNMOSに向けてそれぞれ調整することができる。

【0092】

本発明の幾つかの実施形態の利点は、第2ゲート誘電体キャップ層108は、第2領域102において第2ゲートスタック(第2トランジスタ)の実効仕事関数を調整するためだけのものであり、第1領域101において第1ゲートスタックに存在したままであることである。バリア金属層107の存在により、第2ゲート誘電体キャップ層108は、第1ゲートスタックの実効仕事関数に影響を及ぼさない。

【0093】

本発明の幾つかの実施形態の利点は、第2ゲート誘電体キャップ層108は、選択的にエッチングする必要がない。本発明の幾つかの実施形態の利点は、二重仕事関数半導体デバイスを製造するための処理ステップ数が著しく減少することである。第2ゲート誘電体キャップ層はエッチングする必要がないため、レジスト塗布、レジストのリソグラフ露光、レジストの現像およびエッチングというステップを含む追加のパターン形成ステップなしで、第2ゲート誘電体キャップ層をデバイス全体に渡って堆積させることができる。

【0094】

第2領域102において第2ゲートスタックの実効仕事関数を調整するのに適した第2ゲート誘電体キャップ層108を有するために、次の処理ステップでは、第2金属ゲート電極層109が第1領域101および第2領域102に形成される。その結果、第2金属ゲート電極層109は、第2ゲート誘電体キャップ層108に(この上に接触して)横たわる(図6)。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属を含み、より好ましくは、第1金属ゲート電極層106と同じ金属組成からなる。

【0095】

本発明の幾つかの実施形態の利点は、同一の金属ゲート電極材料が、第1ゲートスタック(第1トランジスタ)および第2ゲートスタック(第2トランジスタ)の両方で用いられることである。

【0096】

続く処理ステップでは、従来の技術(リソグラフ、エッチング)を用いて層スタックがパターン化されて、第1ゲートスタック111を第1領域101に、第2ゲートスタック112を第2領域102に形成する(図7)。第1ゲートスタック111は、第1ゲート誘電体キャップ層104の上に、これと接触するゲート誘電体ホスト層105の上に、これと接触する第1金属ゲート電極層106の上に、これと接触するバリア金属電極層107の上に、これと接触する第2ゲート誘電体キャップ層108の上に、これと接触する第2金属ゲート電極層109を含む。

【0097】

第2ゲートスタック112は、第1ゲート誘電体キャップ層104の上に、これと接触するゲート誘電体ホスト層105の上に、これと接触する第1金属ゲート電極層106の上に、これと接触するバリア金属電極層107の上に、これと接触する第2ゲート誘電体キャップ層108を含む。

【0098】

第1ゲートスタック111での第1実効仕事関数は、バリア金属電極層107、第1金属ゲート電極層106および第1ゲート誘電体キャップ層104の組合せによって決定される。第2ゲートスタック112での第2実効仕事関数は、第1金属ゲート電極層106、第2金属ゲート電極層109および、第1金属ゲート電極層106と第2金属ゲート電極層109の間に挟まれた第2ゲート誘電体キャップ層108の組合せによって決定される。第1実効仕事関数および第2実効仕事関数は相違する。第1ゲートスタックの第1実効仕事関数は、好ましくは、第2ゲートスタックの第2実効仕事関数より大きい。第1実効仕事関数は、好ましくは、PMOSデバイスに適しており、第2実効仕事関数は、好ましくは、NMOSデバイスに適しており、逆も同様である。

【0099】

バリア金属ゲート電極層107は、第1ゲートスタック111の第1実効仕事関数に対する第2金属ゲート電極層109および第2ゲート誘電体キャップ層108の影響を防止する。

【0100】

本発明の幾つかの実施形態の利点は、第2ゲート誘電体キャップ層108が選択的除去ステップを経験する必要がないことである。フォトレジストの剥離、ゲートエッジでのホスト誘電体のアンダーカット、表面化学攻撃の問題に関する心配がない。

【0101】

本発明の幾つかの実施形態の更なる利点は、ゲート誘電体ホスト層に向かう選択的エッチングを必要しないため、処理ステップが簡単かつ費用効果的に維持できることである。

【0102】

本発明の幾つかの実施形態の他の利点は、第1ゲートスタック111の第1実効仕事関数が、第1ゲート誘電体キャップ層だけでなく、バリア金属ゲート電極層107として適切な材料を選ぶことによるバリア金属ゲート電極層107の仕事関数調整機能も用いることによって、ある理想的な値に向けて影響を与えられることである。

【0103】

上述の説明は、本発明の幾つかの実施形態を詳しく述べている。しかしながら、上述が文章中にどのように詳説されているかに関わらず、本発明は多くの方法で実用化できることは理解されよう。本発明の幾つかの特徴または態様を説明する場合、特定の用語の使用が、該用語がここで再定義されて、その用語が関連した本発明の特徴または態様の何れか特定の特性を含むように限定されることを意味することとすべきでないことに留意すべきである。

【0104】

上記詳細な説明は、種々の実施形態に適用されるような本発明の新規な特徴を示し、説明し、指摘するとともに、本発明の精神から逸脱することなく、説明したデバイスまたはプロセスの形態および詳細における種々の省略、置換、変化が当業者によって可能であることと理解されよう。

【特許請求の範囲】

【請求項1】

半導体基板と、

半導体基板の第1領域にあって、第1実効仕事関数を有する第1ゲートスタックを含む第1トランジスタと、

半導体基板の第2領域にあって、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタックを含む第2トランジスタとを備え、

第1ゲートスタックは、第2ゲート誘電体キャップ層の上にある第2金属ゲート電極と、

バリア金属ゲート電極の上にある第2ゲート誘電体キャップ層と、

第1金属ゲート電極層の上にあるバリア金属ゲート電極と、

ゲート誘電体ホスト層の上にある第1金属ゲート電極層と、

第1ゲート誘電体キャップ層の上にあるゲート誘電体ホスト層と、

第1領域において半導体基板の上にある第1ゲート誘電体キャップ層とを含み、

第2ゲートスタックは、第2ゲート誘電体キャップ層の上にある第2金属ゲート電極と、

第1金属ゲート電極の上にある第2ゲート誘電体キャップ層と、

ゲート誘電体ホスト層の上にある第1金属ゲート電極と、

第2領域において半導体基板の上にあるゲート誘電体ホスト層とを含み、

第1ゲートスタックおよび第2ゲートスタックの第2金属ゲート電極層は、第1ゲートスタックおよび第2ゲートスタックの第1金属ゲート電極層と同じ金属組成からなる二重仕事関数半導体デバイス。

【請求項2】

第1ゲートスタックの第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数を調整するように選択される請求項1記載の二重仕事関数半導体デバイス。

【請求項3】

第2ゲートスタックの第1金属ゲート電極層、第2ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数を調整するように選択される請求項1または2記載の二重仕事関数半導体デバイス。

【請求項4】

バリア金属電極層は、TiNまたはTaNを含む請求項1〜3のいずれかに記載の二重仕事関数半導体デバイス。

【請求項5】

第1実効仕事関数は、第2実効仕事関数より大きい請求項1〜4のいずれかに記載の二重仕事関数半導体デバイス。

【請求項6】

第1ゲート誘電体キャップ層は、AlO,AlN,AlONおよびこれらの混合物からなるグループから選択され、

第2ゲート誘電体キャップ層は、DyO,LaO,GdO,ErOおよびこれらの混合物からなるグループから選択され、

第1金属ゲート電極層および第2金属ゲート電極層は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される材料を含み、

バリア金属電極層は、TiNを含む請求項5記載の二重仕事関数半導体デバイス。

【請求項7】

半導体基板に第1領域および第2領域を設けることと、

第1実効仕事関数を有する第1ゲートスタックを第1領域に形成し、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタックを第2領域に形成することとを含む二重仕事関数半導体デバイスの製造方法であって、

第1ゲート誘電体キャップ層を第1領域に形成するステップと、

ゲート誘電体ホスト層を第1領域および第2領域に形成して、第1領域においてゲート誘電体ホスト層を第1ゲート誘電体キャップ層の上に載せるステップと、

第1金属ゲート電極材料を第1領域および第2領域に形成して、第1金属ゲート電極材料をゲート誘電体ホスト層の上に載せるステップと、

バリア金属ゲート電極層を第1領域に形成して、バリア金属ゲート電極層を第1金属ゲート電極層の上に載せるステップと、

第2ゲート誘電体キャップ層を第2領域に形成して、第2ゲート誘電体キャップ層を第1金属ゲート電極層の上に載せるステップと、

第2金属ゲート電極層を第1領域および第2領域に形成して、第2金属ゲート電極層を第2ゲート誘電体キャップ層の上に載せるステップとを含み、

第2金属ゲート電極層は、第1金属ゲート電極層と同じ金属組成からなるようにした二重仕事関数半導体デバイスの製造方法。

【請求項8】

第2金属ゲート電極層、第2ゲート誘電体キャップ層、バリア金属ゲート電極層、ゲート誘電体ホスト層および第1ゲート誘電体キャップ層をパターン化して、第1ゲートスタックを形成するステップと、

第2金属ゲート電極層、第2ゲート誘電体キャップ層、第1金属ゲート電極層およびゲート誘電体ホスト層をパターン化して、第2ゲートスタックを形成するステップとをさらに含む請求項7記載の二重仕事関数半導体デバイスの製造方法。

【請求項9】

第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数を調整するように選択される請求項7または8記載の二重仕事関数半導体デバイスの製造方法。

【請求項10】

第1金属ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数を調整するように選択される請求項7〜9のいずれかに記載の二重仕事関数半導体デバイスの製造方法。

【請求項11】

第1実効仕事関数は、第2実効仕事関数より大きい請求項7〜10のいずれかに記載の二重仕事関数半導体デバイスの製造方法。

【請求項12】

バリア金属ゲート電極層は、TiNまたはTaNを含む請求項7〜11のいずれかに記載の二重仕事関数半導体デバイスの製造方法。

【請求項1】

半導体基板と、

半導体基板の第1領域にあって、第1実効仕事関数を有する第1ゲートスタックを含む第1トランジスタと、

半導体基板の第2領域にあって、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタックを含む第2トランジスタとを備え、

第1ゲートスタックは、第2ゲート誘電体キャップ層の上にある第2金属ゲート電極と、

バリア金属ゲート電極の上にある第2ゲート誘電体キャップ層と、

第1金属ゲート電極層の上にあるバリア金属ゲート電極と、

ゲート誘電体ホスト層の上にある第1金属ゲート電極層と、

第1ゲート誘電体キャップ層の上にあるゲート誘電体ホスト層と、

第1領域において半導体基板の上にある第1ゲート誘電体キャップ層とを含み、

第2ゲートスタックは、第2ゲート誘電体キャップ層の上にある第2金属ゲート電極と、

第1金属ゲート電極の上にある第2ゲート誘電体キャップ層と、

ゲート誘電体ホスト層の上にある第1金属ゲート電極と、

第2領域において半導体基板の上にあるゲート誘電体ホスト層とを含み、

第1ゲートスタックおよび第2ゲートスタックの第2金属ゲート電極層は、第1ゲートスタックおよび第2ゲートスタックの第1金属ゲート電極層と同じ金属組成からなる二重仕事関数半導体デバイス。

【請求項2】

第1ゲートスタックの第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数を調整するように選択される請求項1記載の二重仕事関数半導体デバイス。

【請求項3】

第2ゲートスタックの第1金属ゲート電極層、第2ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数を調整するように選択される請求項1または2記載の二重仕事関数半導体デバイス。

【請求項4】

バリア金属電極層は、TiNまたはTaNを含む請求項1〜3のいずれかに記載の二重仕事関数半導体デバイス。

【請求項5】

第1実効仕事関数は、第2実効仕事関数より大きい請求項1〜4のいずれかに記載の二重仕事関数半導体デバイス。

【請求項6】

第1ゲート誘電体キャップ層は、AlO,AlN,AlONおよびこれらの混合物からなるグループから選択され、

第2ゲート誘電体キャップ層は、DyO,LaO,GdO,ErOおよびこれらの混合物からなるグループから選択され、

第1金属ゲート電極層および第2金属ゲート電極層は、TaxCy(x,yの実数値は0<x,y<1)からなるグループから選択される材料を含み、

バリア金属電極層は、TiNを含む請求項5記載の二重仕事関数半導体デバイス。

【請求項7】

半導体基板に第1領域および第2領域を設けることと、

第1実効仕事関数を有する第1ゲートスタックを第1領域に形成し、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタックを第2領域に形成することとを含む二重仕事関数半導体デバイスの製造方法であって、

第1ゲート誘電体キャップ層を第1領域に形成するステップと、

ゲート誘電体ホスト層を第1領域および第2領域に形成して、第1領域においてゲート誘電体ホスト層を第1ゲート誘電体キャップ層の上に載せるステップと、

第1金属ゲート電極材料を第1領域および第2領域に形成して、第1金属ゲート電極材料をゲート誘電体ホスト層の上に載せるステップと、

バリア金属ゲート電極層を第1領域に形成して、バリア金属ゲート電極層を第1金属ゲート電極層の上に載せるステップと、

第2ゲート誘電体キャップ層を第2領域に形成して、第2ゲート誘電体キャップ層を第1金属ゲート電極層の上に載せるステップと、

第2金属ゲート電極層を第1領域および第2領域に形成して、第2金属ゲート電極層を第2ゲート誘電体キャップ層の上に載せるステップとを含み、

第2金属ゲート電極層は、第1金属ゲート電極層と同じ金属組成からなるようにした二重仕事関数半導体デバイスの製造方法。

【請求項8】

第2金属ゲート電極層、第2ゲート誘電体キャップ層、バリア金属ゲート電極層、ゲート誘電体ホスト層および第1ゲート誘電体キャップ層をパターン化して、第1ゲートスタックを形成するステップと、

第2金属ゲート電極層、第2ゲート誘電体キャップ層、第1金属ゲート電極層およびゲート誘電体ホスト層をパターン化して、第2ゲートスタックを形成するステップとをさらに含む請求項7記載の二重仕事関数半導体デバイスの製造方法。

【請求項9】

第1金属ゲート電極層、バリア金属ゲート電極層および第1ゲート誘電体キャップ層は、第1ゲートスタックの第1実効仕事関数を調整するように選択される請求項7または8記載の二重仕事関数半導体デバイスの製造方法。

【請求項10】

第1金属ゲート電極層および第2ゲート誘電体キャップ層は、第2ゲートスタックの第2実効仕事関数を調整するように選択される請求項7〜9のいずれかに記載の二重仕事関数半導体デバイスの製造方法。

【請求項11】

第1実効仕事関数は、第2実効仕事関数より大きい請求項7〜10のいずれかに記載の二重仕事関数半導体デバイスの製造方法。

【請求項12】

バリア金属ゲート電極層は、TiNまたはTaNを含む請求項7〜11のいずれかに記載の二重仕事関数半導体デバイスの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2009−290200(P2009−290200A)

【公開日】平成21年12月10日(2009.12.10)

【国際特許分類】

【外国語出願】

【出願番号】特願2009−104311(P2009−104311)

【出願日】平成21年4月22日(2009.4.22)

【出願人】(591060898)アイメック (302)

【氏名又は名称原語表記】IMEC

【出願人】(507350912)タイワン・セミコンダクター・マニュファクチャリング・カンパニー・リミテッド (15)

【氏名又は名称原語表記】Taiwan Semiconductor Manufacturing Company Ltd.

【Fターム(参考)】

【公開日】平成21年12月10日(2009.12.10)

【国際特許分類】

【出願番号】特願2009−104311(P2009−104311)

【出願日】平成21年4月22日(2009.4.22)

【出願人】(591060898)アイメック (302)

【氏名又は名称原語表記】IMEC

【出願人】(507350912)タイワン・セミコンダクター・マニュファクチャリング・カンパニー・リミテッド (15)

【氏名又は名称原語表記】Taiwan Semiconductor Manufacturing Company Ltd.

【Fターム(参考)】

[ Back to top ]