代用ソース/ドレインフィンFET加工

【課題】finFETにおける高集積化可能な、高濃度ソースドレインの形成方法の提供。

【解決手段】ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを形成する。チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有するゲートスタックを形成する。チャネル領域を残したまま、ソース領域およびドレイン領域をエッチング除去する。ソース領域およびドレイン領域に隣接したチャネル領域の両側にソースエピタキシー領域およびドレインエピタキシー領域を形成する。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を成長させながら、その場ドープされる。

【解決手段】ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを形成する。チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有するゲートスタックを形成する。チャネル領域を残したまま、ソース領域およびドレイン領域をエッチング除去する。ソース領域およびドレイン領域に隣接したチャネル領域の両側にソースエピタキシー領域およびドレインエピタキシー領域を形成する。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を成長させながら、その場ドープされる。

【発明の詳細な説明】

【発明の詳細な説明】

【0001】

〔背景〕

1:技術分野

本発明は、一般的にフィン電界効果トランジスタ(finFET)および、より具体的には代用ソースおよび代用ドレインを有するfinFETに関する。

【0002】

2:関連技術の説明

finFETは、従来の金属酸化膜半導体電界効果トランジスタ(MOSFET)と同じ原理で動作する、非平面の多重ゲートトランジスタである。シリコンのアイランドまたはフィンは、最初にウエハ上にパターン化される。フィンの形成後、パターン化されたゲート物質がフィンに対して垂直になるよう、ゲートスタックは配置され、パターン化される。パターン化されたゲート物質がフィンをオーバーラップする場合、finFETのためのゲートが形成される。finFETは、フィンにおける両方の垂直な側壁に1つのゲートを有する。フィンの上部の表面の大きさによって、finFETはフィンの上部においてゲートを有していてもよい。

【0003】

例えば、図1は、シリコンオンインシュレーター(SOI)ウエハに形成されたfinFET100を示す。フィン構造102は、酸化物層108から出て、浅溝分離(STI)106より高くなっている。ゲートスタック104は、多重ゲートを形成する3つの側にフィン構造102を積み重ねる。チャネル領域は、フィン構造102上において、ゲートスタック104の下の領域によって規定される。ソース領域およびドレイン領域は、フィン構造102の反対の端部におけるチャネル領域に隣接している。

【0004】

図2は、SOIウエハの酸化物層208において形成される従来のMOSFET200を示す。finFET100(図1)に対して、シリコン領域202は、STI206を有する平面であり、この平面によってゲートスタック204をシリコン領域202の片面のみに積み重ね、単一のゲートのみを形成させる。

【0005】

finFETの多重ゲートは、従来のMOSFET以上に多くの改良点がある。例えば、finFETは、短チャネル効果に対して頑丈であるし、閾値下の振れを改良しながらも高い電流駆動を提供する。

【0006】

しかしながら、finFETの非平面の性質は、加工中にいくつかの問題がある。例えば、従来の注入機は、表面にイオンを注入するための照準線を必要とする。finFETのソースまたはドレインの垂直な側壁にドープするために、ウエハはチルト角度で注入されなければならない。近くのfinFETからの遮蔽効果を克服するために、注入物は、多数の角度または方向で行なわれる必要があり、注入機のツールの複雑さ、注入コストおよび処理時間を増加させる。遮蔽効果を最小限にするために十分離れた非平面の構造を十分遠くに置く設計基準が採用されてもよい。しかしながら、構造空間を増加させるための設計基準を使用することは、密度の低い回路となる。チルト角度の注入物に代わる1つのものとしては、プラズマドーピングがある。しかしながら、プラズマドーピングは、ドーピング制御のような不利な点を内包しており、ドーピング濃度を制限する。

【0007】

〔要約〕

具体的な実施形態において、finFETは、ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを備えるように形成される。フィンは、半導体ウエハにエッチングされる。ゲートスタックは、チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有する。ソース領域およびドレイン領域は、フィンにおけるチャネル領域を残した状態でエッチングされる。エピタキシャル半導体は、ソース領域およびドレイン領域に隣接したチャネル領域の両側において成長される。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を形成しながら、その場ドープされる(doped in-situ)。ソースエピタキシー領域およびドレインエピタキシー領域は、チャネル領域における電子またはホールの移動性を良くするために、チャネル領域に歪を持たせている。

【0008】

〔図の説明〕

図1は、finFETを示す図である。

【0009】

図2は、SOI MOSFETを示す図である。

【0010】

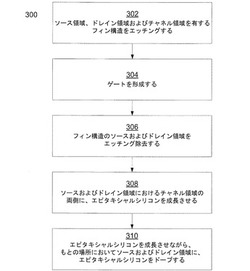

図3は、finFETを形成するための典型的な処理を示すフローチャートである。

【0011】

図4(A)は、図3に示される典型的な処理において、加工の初期段階のfinFETの典型的な実施形態を示す斜視図である。

【0012】

図4(B)は、図4(A)における点線に沿って切られた平面402を示す典型的な実施形態の断面図である。

【0013】

図4(C)は、図4(A)における点線に沿って切られた平面404を示す典型的な実施形態の他の断面図である。

【0014】

図5(A)〜5(C),6(A)〜6(C),7(A)〜7(C),8(A)〜8(C),9(A)〜9(C)および10(A)〜10(C)は、図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【0015】

図11(A)〜11(C)は、SOIウエハにおけるfinFETの典型的な実施形態を示す図である。

【0016】

図12(A)〜12(C)は、非対称のソース領域およびドレイン領域を有するfinFETの典型的な実施形態を示す図である。

【0017】

図13(A)〜13(C)は、finFETを加工するための他の典型的な処理の段階を示す図である。

【0018】

図14(A)〜14(C)は、finFETを加工するための他の典型的な処理の段階を示す図である。

【0019】

図15(A)〜15(C)は、finFETを加工するための他の典型的な処理の段階を示す図である。

【0020】

図は、例示を目的として、本発明の様々な実施形態を示している。当業者は、ここに例示された構造および方法に代わるものが本発明の原理から離れることなく適応されることは、以下の記載から認識するだろう。

【0021】

〔詳細な説明〕

次の記載は、当業者が様々な実施形態を行い、使用することを可能にするために提示されている。具体的な装置、技術およびアプリケーションの記述は、単に例として示されている。ここに記載された例についての様々な修正は、当業者にとって明白であり、ここに定義された原理は、様々な実施形態の精神および範囲から離れることなく他の例またはアプリケーションに適応されてもよい。したがって、様々な実施形態は、ここに記載された例に限定されるものではなく、クレームに等しい範囲に一致している。

【0022】

図3は、finFETを組み立てるための典型的な処理300を示す図である。対応する図4(A)〜4(C),5(A)〜5(C),6(A)〜6(C),7(A)〜7(C),8(A)〜8(C)および10(A)〜10(C)は、典型的な処理300(図3)における加工の様々な段階におけるfinFETを示す図である。

【0023】

具体的に、図4(A)〜4(C)は、半導体ウエハの一部である基板400を示す図である。典型的な本実施形態において、基板400は、バルクシリコンウエハの一部である。しかしながら、SOIウエハのような他のタイプのウエハまたは基板が使用されてもよい。また、シリコン以外の半導体物質としてGe,SiGe,SiC,GeP,GeN,InGaAs,InSb,InAs,GaSbおよびInPを含むものが使用されてもよいが、これらに限定されるものではない。

【0024】

図3に関して、オペレーション302において、フィン構造は、基板上にエッチングされる。図5(A)〜5(C)は、ウエハのシリコンに直接接続されるフィン構造500の形成後における基板400を示す図である。このオペレーションは、フィン構造500を形成するための標準的な半導体のマスキング技術およびエッチング技術を使用してもよい。

【0025】

要求されるものではないが、STI領域は、フィン構造500の形成後に、形成されてもよい。図5(A)〜5(C)は、STI502の形成後における基板400を示す図である。フィン構造の形成後、STI絶縁物質は、基板上に配置されてもよい。STI502の上部504がフィン構造500の上部506と略平坦となるまで、化学的機械的研磨(CMP)またはエッチバックのような平坦化技術がSTI絶縁物質を除去するために使用されてもよい。図5(A)〜5(C)は、STI502がフィン構造500と完全に平坦であることを示すが、実際にはこれらの領域には小さい段差が存在する。小さい段差が存在しているので、それら領域は、略平坦であると考えられる。他の典型的な処理において、STIの形成は、その処理の後に行われても良い。例えば、STIの形成は、図14(A)〜14(C)および15(A)〜15(C)に関して以下に記述されるように、ソース/ドレイン領域がエッチングされ、満たされた後に、行なわれても良い。

【0026】

STI領域が形成されている場合、フィン構造の一部を露出するようにエッチバックが使用されてもよい。図6(A)〜6(C)は、フィン構造500の上部600を露出するためのSTI502のエッチバック後における基板400を示す図である。フィン構造500の底部602は、STI502によって覆われる。ある例において、STI絶縁物質は、二酸化ケイ素で構成される。この例において、ウエハのシリコン上における酸化物について選択的なエッチングが、フィン構造500の著しい量をエッチングすることなく、STI502をエッチングするために使用されてもよい。また、フォトレジストマスクまたはフォトレジストハードマスクは、エッチバックの間、フィン構造500を保護するために使用されてもよい。STI領域を形成する他の典型的な処理において、例えば図12(A)〜12(C)に関して以下に述べられるように、エッチバックは、ソース/ドレイン領域がエッチングされ、満たされた後の処理後に行われてもよい。

【0027】

図3に関して、オペレーション304において、finFETのゲートは、ゲートスタックが配置され、パターン化されることによって形成される。図7(A)〜7(C)は、ゲートを形成するために、ゲートスタックが配置され、パターン化された後における基板400を示す図である。ゲートスタックの配置は、基板400上のゲート誘電体700を成長させるか、配置させることで始まる。図7(A)〜7(C)は、フィン構造500およびSTI502上に存在するゲート誘電体700を示す。したがって、図7(A)〜7(C)の場合において、ゲート誘電体700は、付着物質、または、STI502の絶縁物質と同様のシリコンで形成された物質である。ゲート誘電体700は、熱酸化物であるならば、STI502上におけるゲート誘電体700の一部は、存在しない。

【0028】

次に、伝導性のゲート物質702が配置される。ある例において、伝導性のゲート物質702は、ポリシリコンまたはアモルファスシリコンであり、抵抗を小さくするために注入されてもよく、ゲート仕事関数を定めるために注入されてもよい。金属のような他の伝導性のゲート物質が使用されてもよい。

【0029】

他の典型的な実施形態において、ゲートスタックは、高誘電率(High−k)金属ゲート(HKMG)スタックであってもよい。例えば、チタン窒化物のような金属ゲート、高誘電率のゲート誘電体を有する金属ゲート、ハフニウム酸化物(HfO2)、ジルコニウム酸化物(ZrO2)または二酸化チタン(TiO2)のような金属ゲートが使用されてもよい。HKMGスタックは、dielectric(誘電体)−firstの処理、gate−firstの処理、dielectric−lastの処理、gate−lastの処理で形成されてもよい。

【0030】

例えば、dielectric−lastのHKMG処理において、ゲートスタックは、最初に従来の二酸化ケイ素、ライン処理のフロントエンドの間に犠牲スタックとして使用されるポリシリコンスタックとして形成されてもよい。そして、ライン処理のバックエンドに移る前に、この犠牲スタックは、除去され、高誘電率の誘電体および金属ゲートを含むゲートスタックと取替えられてもよい。これは、gate−lastのHKMG処理の例である。

【0031】

gate−lastのHKMG処理の他の例において、ゲート誘電体は、高誘電率物質(従来の誘電体を備える、または、備えない)で形成されてもよく、ゲート物質用のポリシリコンで形成されてもよい。そして、ライン処理のバックエンドに移る前に、ポリシリコンゲートは、除去され、金属ゲートに取り替えられる。ライン処理のフロントエンドにおいて初期に配置されたゲート誘電体が残る。これは、dielectric−firstのHKMG処理の間に形成される。

【0032】

gate−firstの処理、dielectric−firstのHKMG処理、高誘電率と金属ゲートの両方は、ライン処理のフロントエンドの間に形成される。

【0033】

ゲートスタックが配置された後、ハードマスク層704は、配置され、パターン化される。パターン化されたハードマスクは、伝導性のゲート物質702をエッチングするために使用され、選択的にゲート誘電体700をエッチングするために使用される。残存しているゲートスタック物質は、ゲート706を形成する。チャネル708は、略ゲート706によって覆われているフィン構造500における領域である。ソースおよびドレイン710は、チャネル708に隣接するフィン構造500の一方の端に存在する。記載されている個々の装置において、ソースおよびドレインは、それらが交換可能なように、一緒に記載されている。

【0034】

他の処理において、ハードマスクは、フォトレジストマスクがゲート706をパターン化するために使用される場合、省略されてもよい。ゲート誘電体は、ウエハ全体の上でエッチングされることなく残っていてもよい。例えば、図8(A)〜8(C)に関して記載されるようなスペーサーエッチングステップにおいて除去されてもよい。

【0035】

図3に関して、オペレーション306において、ソース/ドレイン領域のいくつか、または、全てがフィン構造のゲートが残っている状態において、チャネル領域を残したままエッチングされてもよい。このオペレーションのある例において、スペーサーに加えて、このゲートのハードマスクは、ソース/ドレインのエッチングのためのマスクとして使用されてもよい。図8(A)〜8(C)は、スペーサー800の形成およびフィン構造500を除去するためのソースおよびドレイン710(図7(A))のエッチングの後における基板400を示す図である。スペーサー800の形成は、基板400上の絶縁スペーサー物質の配置で始まる。包括的なスペーサーエッチングが、行なわれても良い。ゲート706の側壁において物質を絶縁するスペーサーがエッチングから保護される。例えば、エッチングが設定時間またはエンドポイントにおいて完成した後、スペーサー800は残される。さらに、ハードマスク層704およびスペーサー800は、ソースおよびドレイン710(図7(A))をエッチングするためのマスクとして使用されてもよい。ソースおよびドレインのエッチング後に、フィン構造500のチャネル708を残したまま、ソースおよびドレイン710からシリコンの殆どまたは全てが除去される。

【0036】

オペレーション306は、スペーサーに関するオペレーションを省略してもよい。オペレーション306のこの形態は、ソースおよびドレイン領域をエッチングするために、ハードマスクのみを使用するようにしてもよい。オペレーション306の他の例において、フォトレジストマスクがハードマスクの代わりに使用されてもよい。

【0037】

図3に関して、オペレーション308において、オペレーション306においてエッチングされたソースおよびドレインの一部は、シリコンで満たされる。図10(A)〜10(C)は、エッチングされたソースおよびドレイン710(図7(A))が、シリコン1000で満たされた後における基板400を示す図である。これは、例えば、シリコンを配置させるか、エピタキシャルシリコンを成長させることによって行なわれる。チャネル708の側壁がソースおよびドレインのエッチングの間に損傷した場合、その側壁は、例えば損傷した側壁を消耗させために側壁を熱で酸化させることによって、選択的に、新たなシリコンを受けるよう備えていてもよい。ソースおよびドレイン710(図7)がシリコンであったとしても、他の半導体は、それら領域を満たすように使用される。この場合、チャネル領域およびソース/ドレイン領域は、異なる物質で構成されていてもよい。

【0038】

図3に関して、オペレーション308と同時に行なうオペレーション310において、ソースおよびドレインは、シリコンで満たされた状態で、その場ドープされる(doped in-situ)。図10(A)〜10(C)に関して、シリコン1000を配置するか、成長させながらドープすることによって、チルト角度およびプラズマ注入は、回避されてもよい。さらに、その場ドーピング(in-situ doping)によって、シリコン1000において一定の高濃度ドーピングを許容するので、ソースおよびドレインの抵抗は、単独での注入に比べて小さくてもよい。ソースおよびドレインの注入物を活性化に関連した熱ステップは、回避されてもよい。

【0039】

包括的なシリコンの配置または成長が使用される場合、付加的なエッチングステップが非ソースおよび非ドレイン領域からシリコンを除去するために必要である。CMPまたはエッチバック(マスキングステップを有する、または、有しない)が、非伝導である領域からシリコンを除去する(例えば、ソースおよびドレインを短くするシリコンを除去する)ために使用されてもよい。例えば、図10(A)〜10(C)に示されるように、エッチングされたソースおよびドレイン710(図7(A))を満たすために配置されたシリコン1000は、ゲート706の上部が露出され、ソースおよびドレインがともに短くならないように、エッチングバックされる。

【0040】

図10(A)〜10(C)のシリコン1000が特別な影で示されているが、シリコン1000の結晶構造は、装置によって変えても良い。例えば、シリコン1000がエピタキシャル処理で生成される場合、ソースおよびドレイン領域におけるシリコン1000の一部は、STI上のシリコン1000の一部が多結晶である一方、結晶であってもよい。シリコン1000について、1つの影の使用は、シリコン1000が一定の結晶構造を有している、または、他の一定の特性を有していることを示すことを意図していない。

【0041】

また、選択的なエピタキシャル成長は、露出しているシリコンにおいてのみシリコンを成長させるために使用されてもよく(例えば、オペレーション306におけるソースおよびドレインの除去後に露出されるウエハおよびフィンのシリコン部分)、他の物質について使用されなくてもよい(例えば、STI絶縁体)。図9(A)〜9(C)は、エッチングされたソースおよびドレイン710(図7(A))を満たすための選択的なシリコン900の成長後における基板400を示す。選択的なエピタキシーについて、エッチバックステップは、必要でなくても良い。図9(A)〜9(C)は、図10(A)〜10(C)と対照的であり、非選択的な成長およびエッチバックステップ後の基板400を示す。図9(A)〜9(C)において、ソースおよびドレイン900の形状は、ソースおよびドレイン領域を再成長させるために選択的にエピタキシーを使用することによって生成される典型的な形状であることを意図しているだけである。ソースおよびドレイン領域の他の形状が、この発明の典型的な実施形態から逸脱することなく生成されてもよい。

【0042】

熱収支を制御するために、最初に、高温度エピタキシー処理が、高品質シリコンの初期の厚みを成長させるために使用されてもよい。ポリシリコンは、ソースおよびドレインを満たすために低温度で配置されてもよい。CMP、エッチバックまたは両方がウエハを平坦化するために使用されてもよい。さらに、エッチバックは、上述したように、非ソースおよび非ドレイン領域からシリコンを除去するために必要とされる。

【0043】

図9(A)〜9(C)および図10(A)〜10(C)がエッチングされたソースおよびドレインがシリコンで完全に満たされるが、他の場合において、ソースおよびドレイン領域の一部のみがシリコンで満たされる必要がある。

【0044】

低抵抗ソースおよびドレインを生成することに加えて、ソースおよびドレイン710(図7(A))の置換は、チャネル708(図10(A))に歪を加えてもよい。例えば、SiGeまたはSiC(シリコン基板を使用する場合)が、ソースおよびドレイン領域がエッチング除去されるチャネル708(図10(A))の側面において選択的なエピタキシーで成長されてもよい。Si(チャネルを形成する他の半導体物質)と比較してSiGeまたはSiCの異なる格子定数は、チャネル708において半導体を歪め、チャネル708における電子またはホールの移動性を増加させる。

【0045】

第1の典型的なプロセスがいくつかの処理ステップに関して記載されているが、当業者であれば、他の既知の処理ステップが機能的finFETを製造するために必要とされてもよいと認識する。例えば、閾値調整注入物は、n型またはp型のfinFETのための閾値電圧を適切に設定するために必要とされる。他の例として、シリコンの配置またはエピタキシャル成長によるソースおよびドレインの再補充は、2度行なわれても良い。p型finFETはp型ソースおよびドレインを必要とし、n型finFETはn型ソースおよびドレインを必要とする。

【0046】

図11(A)〜11(C)は、基板1100におけるfinFETの他の典型的な実施形態を示す図である。この典型的な実施形態は、SOIウエハが上述のバルクウエハに代えて基板1100のために使用されることを除いて、図10(A)〜10(C)において記載されている典型的な実施形態に類似している。また、この典型的な実施形態に使用される処理は、STI領域の形成を含まない。図11(A)〜11(C)におけるソースおよびドレイン1102の形状は、ソースおよびドレイン領域を再成長させるために選択的にエピタキシーを使用することによって、生成される典型的な形状であることを意図しているのみである。ソースおよびドレイン領域の他の形状が発明の実施形態から逸脱することなく生成されてもよい。

【0047】

図12(A)〜12(C)は、異なる物質の特性を有する非対称のソース1200およびドレイン1202を有するfinFETの他の典型的な実施形態を示す図である。例えば、ソース1200およびドレイン1202は、異なる物質で構成されてもよい。他の例として、2つの領域についてのドーピングは、異なっていてもよい。また、他の例において、2つの領域の歪みは、異なっていてもよい。この典型的な実施形態は、ソース1200とドレイン1202が別々に成長される必要がある。図12(A)〜12(C)におけるソース1200およびドレイン1202の形状は、ソースおよびドレイン領域を再成長させるために選択的にエピタキシーを使用することによって生成される典型的な形状であることを意図しているだけである。ソースおよびドレイン領域の他の形状は、発明の実施形態から逸脱することなく、生成されてもよい。

【0048】

図13(A)〜13(C)は、他の典型的な処理の段階を示す図である。この典型的な処理は、図5(A)〜5(C)に関して上述したSTIエッチバックステップが処理において後に行なわれることを除いて、典型的な処理300(図3)に類似している。図13(A)〜13(C)は、フィン構造1306の形成、STI1304(図5(A)〜5(C)に関して記載される)の配置、ソースドレイン1302(オペレーション306,308,310に記載される)のエッチングおよび補充の後における基板1300を示す。しかしながら、STI1304のエッチバックに記載されている)は、まだ生じていない。STIエッチバックステップ(図5(A)〜5(C))は、ゲート形成(オペレーション304)に優先して、いくつかのポイントで生じる。基板1300は、SOIウエハとして示される。しかしながら、この処理は、バルクウエハ上で同様に使用され得る。

【0049】

図14(A)〜14(C)は、finFETの加工のための他の典型的な処理の段階を示す図である。この典型的な処理は、ソースおよびドレインのエッチングおよび補充がフィン構造の形成に優先して行なわれることを除いて、典型的な処理300(図3)に類似する。この処理において、標準的なフォトレジストマスクが、補充に優先してソースおよびドレイン1402をエッチング除去するために使用されてもよい。さらに、ソースおよびドレイン1402を形成するシリコンのみがエッチングされ、補充されてもよい。領域1404は、エッチングされないままであり、基板1400の原型の上部表面である。この典型的な処理における後の段階によって、オペレーション302に関して、上述のフィン構造を形成する。基板1400は、SOIウエハとして示される。しかしながら、この処理は、バルクウエハと共に使用される。

【0050】

図15(A)〜15(C)は、finFETの加工のための他の典型的な処理の段階を示す図である。この典型的な処理は、ソースおよびドレイン1502がエッチングされ、補充されることに加え、ソースおよびドレイン1502の周囲の領域1504がエッチングされ、補充されることを除いて、図14(A)〜14(C)に関して上述のような典型的な処理に類似している。領域1506は、基板1500の原型の上部表面に残る。この典型的な処理における後の段階は、オペレーション302に関して上述のようにフィン構造を形成する。基板1500は、SOIウエハとして示される。しかしながら、この処理は、バルクウエハと共に使用されてもよい。

【0051】

図15(A)〜15(C)のソースおよびドレイン1052周囲におけるソースおよびドレイン1502および領域1504は、ある特別な影で示されているが、これら領域の結晶構造は、装置によって変えてもよい。本発明の特別な実施形態の先の記述は、例示および図の目的で提示されている。それらは、本発明を、開示の具体的な形状に徹底的に、または、限定的にするものではなく、多くの修正および変更が上述の教示を参照すれば可能であることが理解されるべきである。例えば、エピタキシーがこれらの領域においてシリコンを再補充するために使用される場合、領域1506に隣接するシリコンは、領域1506から離れているシリコンが多結晶である一方、結晶であってもよい。1つの陰の使用は、これら領域が一定の結晶構造を有するか、他の一定の特性を有していることを意味することを意図していない。

【0052】

本発明の特別な実施形態における先の記述は、例示および図の目的で提示されている。それらは、本発明を、開示の具体的な形状に徹底的に、または、限定的にするものではなく、多くの修正および変更が上述の教示を参照すれば可能であることが理解されるべきである。

【図面の簡単な説明】

【0053】

【図1】finFETを示す図である。

【図2】SOI MOSFETを示す図である。

【図3】finFETを形成するための典型的な処理を示すフローチャートである。

【図4】図3に示される典型的な処理において、加工の初期段階のfinFETの典型的な実施形態を示す斜視図である。

【図5】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図6】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図7】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図8】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図9】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図10】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図11】SOIウエハにおけるfinFETの典型的な実施形態を示す図である。

【図12】非対称のソース領域およびドレイン領域を有するfinFETの典型的な実施形態を示す図である。

【図13】finFETを加工するための他の典型的な処理の段階を示す図である。

【図14】finFETを加工するための他の典型的な処理の段階を示す図である。

【図15】finFETを加工するための他の典型的な処理の段階を示す図である。

【発明の詳細な説明】

【0001】

〔背景〕

1:技術分野

本発明は、一般的にフィン電界効果トランジスタ(finFET)および、より具体的には代用ソースおよび代用ドレインを有するfinFETに関する。

【0002】

2:関連技術の説明

finFETは、従来の金属酸化膜半導体電界効果トランジスタ(MOSFET)と同じ原理で動作する、非平面の多重ゲートトランジスタである。シリコンのアイランドまたはフィンは、最初にウエハ上にパターン化される。フィンの形成後、パターン化されたゲート物質がフィンに対して垂直になるよう、ゲートスタックは配置され、パターン化される。パターン化されたゲート物質がフィンをオーバーラップする場合、finFETのためのゲートが形成される。finFETは、フィンにおける両方の垂直な側壁に1つのゲートを有する。フィンの上部の表面の大きさによって、finFETはフィンの上部においてゲートを有していてもよい。

【0003】

例えば、図1は、シリコンオンインシュレーター(SOI)ウエハに形成されたfinFET100を示す。フィン構造102は、酸化物層108から出て、浅溝分離(STI)106より高くなっている。ゲートスタック104は、多重ゲートを形成する3つの側にフィン構造102を積み重ねる。チャネル領域は、フィン構造102上において、ゲートスタック104の下の領域によって規定される。ソース領域およびドレイン領域は、フィン構造102の反対の端部におけるチャネル領域に隣接している。

【0004】

図2は、SOIウエハの酸化物層208において形成される従来のMOSFET200を示す。finFET100(図1)に対して、シリコン領域202は、STI206を有する平面であり、この平面によってゲートスタック204をシリコン領域202の片面のみに積み重ね、単一のゲートのみを形成させる。

【0005】

finFETの多重ゲートは、従来のMOSFET以上に多くの改良点がある。例えば、finFETは、短チャネル効果に対して頑丈であるし、閾値下の振れを改良しながらも高い電流駆動を提供する。

【0006】

しかしながら、finFETの非平面の性質は、加工中にいくつかの問題がある。例えば、従来の注入機は、表面にイオンを注入するための照準線を必要とする。finFETのソースまたはドレインの垂直な側壁にドープするために、ウエハはチルト角度で注入されなければならない。近くのfinFETからの遮蔽効果を克服するために、注入物は、多数の角度または方向で行なわれる必要があり、注入機のツールの複雑さ、注入コストおよび処理時間を増加させる。遮蔽効果を最小限にするために十分離れた非平面の構造を十分遠くに置く設計基準が採用されてもよい。しかしながら、構造空間を増加させるための設計基準を使用することは、密度の低い回路となる。チルト角度の注入物に代わる1つのものとしては、プラズマドーピングがある。しかしながら、プラズマドーピングは、ドーピング制御のような不利な点を内包しており、ドーピング濃度を制限する。

【0007】

〔要約〕

具体的な実施形態において、finFETは、ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを備えるように形成される。フィンは、半導体ウエハにエッチングされる。ゲートスタックは、チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有する。ソース領域およびドレイン領域は、フィンにおけるチャネル領域を残した状態でエッチングされる。エピタキシャル半導体は、ソース領域およびドレイン領域に隣接したチャネル領域の両側において成長される。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を形成しながら、その場ドープされる(doped in-situ)。ソースエピタキシー領域およびドレインエピタキシー領域は、チャネル領域における電子またはホールの移動性を良くするために、チャネル領域に歪を持たせている。

【0008】

〔図の説明〕

図1は、finFETを示す図である。

【0009】

図2は、SOI MOSFETを示す図である。

【0010】

図3は、finFETを形成するための典型的な処理を示すフローチャートである。

【0011】

図4(A)は、図3に示される典型的な処理において、加工の初期段階のfinFETの典型的な実施形態を示す斜視図である。

【0012】

図4(B)は、図4(A)における点線に沿って切られた平面402を示す典型的な実施形態の断面図である。

【0013】

図4(C)は、図4(A)における点線に沿って切られた平面404を示す典型的な実施形態の他の断面図である。

【0014】

図5(A)〜5(C),6(A)〜6(C),7(A)〜7(C),8(A)〜8(C),9(A)〜9(C)および10(A)〜10(C)は、図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【0015】

図11(A)〜11(C)は、SOIウエハにおけるfinFETの典型的な実施形態を示す図である。

【0016】

図12(A)〜12(C)は、非対称のソース領域およびドレイン領域を有するfinFETの典型的な実施形態を示す図である。

【0017】

図13(A)〜13(C)は、finFETを加工するための他の典型的な処理の段階を示す図である。

【0018】

図14(A)〜14(C)は、finFETを加工するための他の典型的な処理の段階を示す図である。

【0019】

図15(A)〜15(C)は、finFETを加工するための他の典型的な処理の段階を示す図である。

【0020】

図は、例示を目的として、本発明の様々な実施形態を示している。当業者は、ここに例示された構造および方法に代わるものが本発明の原理から離れることなく適応されることは、以下の記載から認識するだろう。

【0021】

〔詳細な説明〕

次の記載は、当業者が様々な実施形態を行い、使用することを可能にするために提示されている。具体的な装置、技術およびアプリケーションの記述は、単に例として示されている。ここに記載された例についての様々な修正は、当業者にとって明白であり、ここに定義された原理は、様々な実施形態の精神および範囲から離れることなく他の例またはアプリケーションに適応されてもよい。したがって、様々な実施形態は、ここに記載された例に限定されるものではなく、クレームに等しい範囲に一致している。

【0022】

図3は、finFETを組み立てるための典型的な処理300を示す図である。対応する図4(A)〜4(C),5(A)〜5(C),6(A)〜6(C),7(A)〜7(C),8(A)〜8(C)および10(A)〜10(C)は、典型的な処理300(図3)における加工の様々な段階におけるfinFETを示す図である。

【0023】

具体的に、図4(A)〜4(C)は、半導体ウエハの一部である基板400を示す図である。典型的な本実施形態において、基板400は、バルクシリコンウエハの一部である。しかしながら、SOIウエハのような他のタイプのウエハまたは基板が使用されてもよい。また、シリコン以外の半導体物質としてGe,SiGe,SiC,GeP,GeN,InGaAs,InSb,InAs,GaSbおよびInPを含むものが使用されてもよいが、これらに限定されるものではない。

【0024】

図3に関して、オペレーション302において、フィン構造は、基板上にエッチングされる。図5(A)〜5(C)は、ウエハのシリコンに直接接続されるフィン構造500の形成後における基板400を示す図である。このオペレーションは、フィン構造500を形成するための標準的な半導体のマスキング技術およびエッチング技術を使用してもよい。

【0025】

要求されるものではないが、STI領域は、フィン構造500の形成後に、形成されてもよい。図5(A)〜5(C)は、STI502の形成後における基板400を示す図である。フィン構造の形成後、STI絶縁物質は、基板上に配置されてもよい。STI502の上部504がフィン構造500の上部506と略平坦となるまで、化学的機械的研磨(CMP)またはエッチバックのような平坦化技術がSTI絶縁物質を除去するために使用されてもよい。図5(A)〜5(C)は、STI502がフィン構造500と完全に平坦であることを示すが、実際にはこれらの領域には小さい段差が存在する。小さい段差が存在しているので、それら領域は、略平坦であると考えられる。他の典型的な処理において、STIの形成は、その処理の後に行われても良い。例えば、STIの形成は、図14(A)〜14(C)および15(A)〜15(C)に関して以下に記述されるように、ソース/ドレイン領域がエッチングされ、満たされた後に、行なわれても良い。

【0026】

STI領域が形成されている場合、フィン構造の一部を露出するようにエッチバックが使用されてもよい。図6(A)〜6(C)は、フィン構造500の上部600を露出するためのSTI502のエッチバック後における基板400を示す図である。フィン構造500の底部602は、STI502によって覆われる。ある例において、STI絶縁物質は、二酸化ケイ素で構成される。この例において、ウエハのシリコン上における酸化物について選択的なエッチングが、フィン構造500の著しい量をエッチングすることなく、STI502をエッチングするために使用されてもよい。また、フォトレジストマスクまたはフォトレジストハードマスクは、エッチバックの間、フィン構造500を保護するために使用されてもよい。STI領域を形成する他の典型的な処理において、例えば図12(A)〜12(C)に関して以下に述べられるように、エッチバックは、ソース/ドレイン領域がエッチングされ、満たされた後の処理後に行われてもよい。

【0027】

図3に関して、オペレーション304において、finFETのゲートは、ゲートスタックが配置され、パターン化されることによって形成される。図7(A)〜7(C)は、ゲートを形成するために、ゲートスタックが配置され、パターン化された後における基板400を示す図である。ゲートスタックの配置は、基板400上のゲート誘電体700を成長させるか、配置させることで始まる。図7(A)〜7(C)は、フィン構造500およびSTI502上に存在するゲート誘電体700を示す。したがって、図7(A)〜7(C)の場合において、ゲート誘電体700は、付着物質、または、STI502の絶縁物質と同様のシリコンで形成された物質である。ゲート誘電体700は、熱酸化物であるならば、STI502上におけるゲート誘電体700の一部は、存在しない。

【0028】

次に、伝導性のゲート物質702が配置される。ある例において、伝導性のゲート物質702は、ポリシリコンまたはアモルファスシリコンであり、抵抗を小さくするために注入されてもよく、ゲート仕事関数を定めるために注入されてもよい。金属のような他の伝導性のゲート物質が使用されてもよい。

【0029】

他の典型的な実施形態において、ゲートスタックは、高誘電率(High−k)金属ゲート(HKMG)スタックであってもよい。例えば、チタン窒化物のような金属ゲート、高誘電率のゲート誘電体を有する金属ゲート、ハフニウム酸化物(HfO2)、ジルコニウム酸化物(ZrO2)または二酸化チタン(TiO2)のような金属ゲートが使用されてもよい。HKMGスタックは、dielectric(誘電体)−firstの処理、gate−firstの処理、dielectric−lastの処理、gate−lastの処理で形成されてもよい。

【0030】

例えば、dielectric−lastのHKMG処理において、ゲートスタックは、最初に従来の二酸化ケイ素、ライン処理のフロントエンドの間に犠牲スタックとして使用されるポリシリコンスタックとして形成されてもよい。そして、ライン処理のバックエンドに移る前に、この犠牲スタックは、除去され、高誘電率の誘電体および金属ゲートを含むゲートスタックと取替えられてもよい。これは、gate−lastのHKMG処理の例である。

【0031】

gate−lastのHKMG処理の他の例において、ゲート誘電体は、高誘電率物質(従来の誘電体を備える、または、備えない)で形成されてもよく、ゲート物質用のポリシリコンで形成されてもよい。そして、ライン処理のバックエンドに移る前に、ポリシリコンゲートは、除去され、金属ゲートに取り替えられる。ライン処理のフロントエンドにおいて初期に配置されたゲート誘電体が残る。これは、dielectric−firstのHKMG処理の間に形成される。

【0032】

gate−firstの処理、dielectric−firstのHKMG処理、高誘電率と金属ゲートの両方は、ライン処理のフロントエンドの間に形成される。

【0033】

ゲートスタックが配置された後、ハードマスク層704は、配置され、パターン化される。パターン化されたハードマスクは、伝導性のゲート物質702をエッチングするために使用され、選択的にゲート誘電体700をエッチングするために使用される。残存しているゲートスタック物質は、ゲート706を形成する。チャネル708は、略ゲート706によって覆われているフィン構造500における領域である。ソースおよびドレイン710は、チャネル708に隣接するフィン構造500の一方の端に存在する。記載されている個々の装置において、ソースおよびドレインは、それらが交換可能なように、一緒に記載されている。

【0034】

他の処理において、ハードマスクは、フォトレジストマスクがゲート706をパターン化するために使用される場合、省略されてもよい。ゲート誘電体は、ウエハ全体の上でエッチングされることなく残っていてもよい。例えば、図8(A)〜8(C)に関して記載されるようなスペーサーエッチングステップにおいて除去されてもよい。

【0035】

図3に関して、オペレーション306において、ソース/ドレイン領域のいくつか、または、全てがフィン構造のゲートが残っている状態において、チャネル領域を残したままエッチングされてもよい。このオペレーションのある例において、スペーサーに加えて、このゲートのハードマスクは、ソース/ドレインのエッチングのためのマスクとして使用されてもよい。図8(A)〜8(C)は、スペーサー800の形成およびフィン構造500を除去するためのソースおよびドレイン710(図7(A))のエッチングの後における基板400を示す図である。スペーサー800の形成は、基板400上の絶縁スペーサー物質の配置で始まる。包括的なスペーサーエッチングが、行なわれても良い。ゲート706の側壁において物質を絶縁するスペーサーがエッチングから保護される。例えば、エッチングが設定時間またはエンドポイントにおいて完成した後、スペーサー800は残される。さらに、ハードマスク層704およびスペーサー800は、ソースおよびドレイン710(図7(A))をエッチングするためのマスクとして使用されてもよい。ソースおよびドレインのエッチング後に、フィン構造500のチャネル708を残したまま、ソースおよびドレイン710からシリコンの殆どまたは全てが除去される。

【0036】

オペレーション306は、スペーサーに関するオペレーションを省略してもよい。オペレーション306のこの形態は、ソースおよびドレイン領域をエッチングするために、ハードマスクのみを使用するようにしてもよい。オペレーション306の他の例において、フォトレジストマスクがハードマスクの代わりに使用されてもよい。

【0037】

図3に関して、オペレーション308において、オペレーション306においてエッチングされたソースおよびドレインの一部は、シリコンで満たされる。図10(A)〜10(C)は、エッチングされたソースおよびドレイン710(図7(A))が、シリコン1000で満たされた後における基板400を示す図である。これは、例えば、シリコンを配置させるか、エピタキシャルシリコンを成長させることによって行なわれる。チャネル708の側壁がソースおよびドレインのエッチングの間に損傷した場合、その側壁は、例えば損傷した側壁を消耗させために側壁を熱で酸化させることによって、選択的に、新たなシリコンを受けるよう備えていてもよい。ソースおよびドレイン710(図7)がシリコンであったとしても、他の半導体は、それら領域を満たすように使用される。この場合、チャネル領域およびソース/ドレイン領域は、異なる物質で構成されていてもよい。

【0038】

図3に関して、オペレーション308と同時に行なうオペレーション310において、ソースおよびドレインは、シリコンで満たされた状態で、その場ドープされる(doped in-situ)。図10(A)〜10(C)に関して、シリコン1000を配置するか、成長させながらドープすることによって、チルト角度およびプラズマ注入は、回避されてもよい。さらに、その場ドーピング(in-situ doping)によって、シリコン1000において一定の高濃度ドーピングを許容するので、ソースおよびドレインの抵抗は、単独での注入に比べて小さくてもよい。ソースおよびドレインの注入物を活性化に関連した熱ステップは、回避されてもよい。

【0039】

包括的なシリコンの配置または成長が使用される場合、付加的なエッチングステップが非ソースおよび非ドレイン領域からシリコンを除去するために必要である。CMPまたはエッチバック(マスキングステップを有する、または、有しない)が、非伝導である領域からシリコンを除去する(例えば、ソースおよびドレインを短くするシリコンを除去する)ために使用されてもよい。例えば、図10(A)〜10(C)に示されるように、エッチングされたソースおよびドレイン710(図7(A))を満たすために配置されたシリコン1000は、ゲート706の上部が露出され、ソースおよびドレインがともに短くならないように、エッチングバックされる。

【0040】

図10(A)〜10(C)のシリコン1000が特別な影で示されているが、シリコン1000の結晶構造は、装置によって変えても良い。例えば、シリコン1000がエピタキシャル処理で生成される場合、ソースおよびドレイン領域におけるシリコン1000の一部は、STI上のシリコン1000の一部が多結晶である一方、結晶であってもよい。シリコン1000について、1つの影の使用は、シリコン1000が一定の結晶構造を有している、または、他の一定の特性を有していることを示すことを意図していない。

【0041】

また、選択的なエピタキシャル成長は、露出しているシリコンにおいてのみシリコンを成長させるために使用されてもよく(例えば、オペレーション306におけるソースおよびドレインの除去後に露出されるウエハおよびフィンのシリコン部分)、他の物質について使用されなくてもよい(例えば、STI絶縁体)。図9(A)〜9(C)は、エッチングされたソースおよびドレイン710(図7(A))を満たすための選択的なシリコン900の成長後における基板400を示す。選択的なエピタキシーについて、エッチバックステップは、必要でなくても良い。図9(A)〜9(C)は、図10(A)〜10(C)と対照的であり、非選択的な成長およびエッチバックステップ後の基板400を示す。図9(A)〜9(C)において、ソースおよびドレイン900の形状は、ソースおよびドレイン領域を再成長させるために選択的にエピタキシーを使用することによって生成される典型的な形状であることを意図しているだけである。ソースおよびドレイン領域の他の形状が、この発明の典型的な実施形態から逸脱することなく生成されてもよい。

【0042】

熱収支を制御するために、最初に、高温度エピタキシー処理が、高品質シリコンの初期の厚みを成長させるために使用されてもよい。ポリシリコンは、ソースおよびドレインを満たすために低温度で配置されてもよい。CMP、エッチバックまたは両方がウエハを平坦化するために使用されてもよい。さらに、エッチバックは、上述したように、非ソースおよび非ドレイン領域からシリコンを除去するために必要とされる。

【0043】

図9(A)〜9(C)および図10(A)〜10(C)がエッチングされたソースおよびドレインがシリコンで完全に満たされるが、他の場合において、ソースおよびドレイン領域の一部のみがシリコンで満たされる必要がある。

【0044】

低抵抗ソースおよびドレインを生成することに加えて、ソースおよびドレイン710(図7(A))の置換は、チャネル708(図10(A))に歪を加えてもよい。例えば、SiGeまたはSiC(シリコン基板を使用する場合)が、ソースおよびドレイン領域がエッチング除去されるチャネル708(図10(A))の側面において選択的なエピタキシーで成長されてもよい。Si(チャネルを形成する他の半導体物質)と比較してSiGeまたはSiCの異なる格子定数は、チャネル708において半導体を歪め、チャネル708における電子またはホールの移動性を増加させる。

【0045】

第1の典型的なプロセスがいくつかの処理ステップに関して記載されているが、当業者であれば、他の既知の処理ステップが機能的finFETを製造するために必要とされてもよいと認識する。例えば、閾値調整注入物は、n型またはp型のfinFETのための閾値電圧を適切に設定するために必要とされる。他の例として、シリコンの配置またはエピタキシャル成長によるソースおよびドレインの再補充は、2度行なわれても良い。p型finFETはp型ソースおよびドレインを必要とし、n型finFETはn型ソースおよびドレインを必要とする。

【0046】

図11(A)〜11(C)は、基板1100におけるfinFETの他の典型的な実施形態を示す図である。この典型的な実施形態は、SOIウエハが上述のバルクウエハに代えて基板1100のために使用されることを除いて、図10(A)〜10(C)において記載されている典型的な実施形態に類似している。また、この典型的な実施形態に使用される処理は、STI領域の形成を含まない。図11(A)〜11(C)におけるソースおよびドレイン1102の形状は、ソースおよびドレイン領域を再成長させるために選択的にエピタキシーを使用することによって、生成される典型的な形状であることを意図しているのみである。ソースおよびドレイン領域の他の形状が発明の実施形態から逸脱することなく生成されてもよい。

【0047】

図12(A)〜12(C)は、異なる物質の特性を有する非対称のソース1200およびドレイン1202を有するfinFETの他の典型的な実施形態を示す図である。例えば、ソース1200およびドレイン1202は、異なる物質で構成されてもよい。他の例として、2つの領域についてのドーピングは、異なっていてもよい。また、他の例において、2つの領域の歪みは、異なっていてもよい。この典型的な実施形態は、ソース1200とドレイン1202が別々に成長される必要がある。図12(A)〜12(C)におけるソース1200およびドレイン1202の形状は、ソースおよびドレイン領域を再成長させるために選択的にエピタキシーを使用することによって生成される典型的な形状であることを意図しているだけである。ソースおよびドレイン領域の他の形状は、発明の実施形態から逸脱することなく、生成されてもよい。

【0048】

図13(A)〜13(C)は、他の典型的な処理の段階を示す図である。この典型的な処理は、図5(A)〜5(C)に関して上述したSTIエッチバックステップが処理において後に行なわれることを除いて、典型的な処理300(図3)に類似している。図13(A)〜13(C)は、フィン構造1306の形成、STI1304(図5(A)〜5(C)に関して記載される)の配置、ソースドレイン1302(オペレーション306,308,310に記載される)のエッチングおよび補充の後における基板1300を示す。しかしながら、STI1304のエッチバックに記載されている)は、まだ生じていない。STIエッチバックステップ(図5(A)〜5(C))は、ゲート形成(オペレーション304)に優先して、いくつかのポイントで生じる。基板1300は、SOIウエハとして示される。しかしながら、この処理は、バルクウエハ上で同様に使用され得る。

【0049】

図14(A)〜14(C)は、finFETの加工のための他の典型的な処理の段階を示す図である。この典型的な処理は、ソースおよびドレインのエッチングおよび補充がフィン構造の形成に優先して行なわれることを除いて、典型的な処理300(図3)に類似する。この処理において、標準的なフォトレジストマスクが、補充に優先してソースおよびドレイン1402をエッチング除去するために使用されてもよい。さらに、ソースおよびドレイン1402を形成するシリコンのみがエッチングされ、補充されてもよい。領域1404は、エッチングされないままであり、基板1400の原型の上部表面である。この典型的な処理における後の段階によって、オペレーション302に関して、上述のフィン構造を形成する。基板1400は、SOIウエハとして示される。しかしながら、この処理は、バルクウエハと共に使用される。

【0050】

図15(A)〜15(C)は、finFETの加工のための他の典型的な処理の段階を示す図である。この典型的な処理は、ソースおよびドレイン1502がエッチングされ、補充されることに加え、ソースおよびドレイン1502の周囲の領域1504がエッチングされ、補充されることを除いて、図14(A)〜14(C)に関して上述のような典型的な処理に類似している。領域1506は、基板1500の原型の上部表面に残る。この典型的な処理における後の段階は、オペレーション302に関して上述のようにフィン構造を形成する。基板1500は、SOIウエハとして示される。しかしながら、この処理は、バルクウエハと共に使用されてもよい。

【0051】

図15(A)〜15(C)のソースおよびドレイン1052周囲におけるソースおよびドレイン1502および領域1504は、ある特別な影で示されているが、これら領域の結晶構造は、装置によって変えてもよい。本発明の特別な実施形態の先の記述は、例示および図の目的で提示されている。それらは、本発明を、開示の具体的な形状に徹底的に、または、限定的にするものではなく、多くの修正および変更が上述の教示を参照すれば可能であることが理解されるべきである。例えば、エピタキシーがこれらの領域においてシリコンを再補充するために使用される場合、領域1506に隣接するシリコンは、領域1506から離れているシリコンが多結晶である一方、結晶であってもよい。1つの陰の使用は、これら領域が一定の結晶構造を有するか、他の一定の特性を有していることを意味することを意図していない。

【0052】

本発明の特別な実施形態における先の記述は、例示および図の目的で提示されている。それらは、本発明を、開示の具体的な形状に徹底的に、または、限定的にするものではなく、多くの修正および変更が上述の教示を参照すれば可能であることが理解されるべきである。

【図面の簡単な説明】

【0053】

【図1】finFETを示す図である。

【図2】SOI MOSFETを示す図である。

【図3】finFETを形成するための典型的な処理を示すフローチャートである。

【図4】図3に示される典型的な処理において、加工の初期段階のfinFETの典型的な実施形態を示す斜視図である。

【図5】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図6】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図7】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図8】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図9】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図10】図3において示された典型的な処理において、加工の様々な段階の典型的な実施形態を示す図である。

【図11】SOIウエハにおけるfinFETの典型的な実施形態を示す図である。

【図12】非対称のソース領域およびドレイン領域を有するfinFETの典型的な実施形態を示す図である。

【図13】finFETを加工するための他の典型的な処理の段階を示す図である。

【図14】finFETを加工するための他の典型的な処理の段階を示す図である。

【図15】finFETを加工するための他の典型的な処理の段階を示す図である。

【特許請求の範囲】

【請求項1】

ソース領域、ドレイン領域および前記ソース領域と前記ドレイン領域との間のチャネル領域を有するフィンを備えたフィン電解効果トランジスタ(finFET)を加工するための方法であって、

半導体基板において前記フィンをエッチングするステップと、

前記チャネル領域においてゲートスタックを形成するステップと、を含み、

前記ゲートスタックは、前記チャネル領域にダイレクトコンタクトした絶縁層と、前記絶縁層にダイレクトコンタクトしたゲート物質とを有し、

前記チャネル領域を残すように、前記ソース領域および前記ドレイン領域をエッチングするステップと、

前記ソース領域および前記ドレイン領域に隣接する前記チャネル領域の両側において、ソースエピタキシー領域およびドレインエピタキシー領域それぞれを形成するために、エピタキシャル半導体を成長させるステップと、

前記エピタキシャル半導体を成長させながら、前記エピタキシャル半導体をその場ドーピングするステップと、を含む方法。

【請求項2】

前記フィンの周り、および、前記フィン上に、絶縁層を配置するステップと、

前記フィンの表面に略同一平面の上部表面を有するように、前記絶縁層を研磨するステップと、を含む、請求項1に記載の方法。

【請求項3】

前記ゲートスタックを形成するステップに優先して、絶縁層を配置するステップおよび前記絶縁層を研磨するステップが行なわれる、請求項2に記載の方法。

【請求項4】

前記フィンの底部分を覆う一方で、前記フィンの上部分が露出するように、前記絶縁層をエッチバックするステップを含む、請求項3に記載の方法。

【請求項5】

前記フィンをエッチングするステップに優先して、前記ソースおよび前記ドレインをエッチングするステップおよび前記エピタキシャル半導体を成長させるステップが行なわれる、請求項1に記載の方法。

【請求項6】

前記チャネル領域は、固有の歪みを有し、前記ソースエピタキシー領域は第1歪みを有し、前記ソースエピタキシー領域の前記第1歪みは、前記チャネル領域における電子またはホールの移動性を良くするために、前記チャネル領域の少なくとも一部における前記固有の歪みを修正する、請求項1に記載の方法。

【請求項7】

前記半導体基板は、バルクシリコンウエハである、請求項1に記載の方法。

【請求項8】

前記ドレインエピタキシー領域は、前記半導体ウエハと異なる物質である、請求項1に記載の方法。

【請求項9】

前記エピタキシャル半導体は、前記半導体基板の物質に選択的に成長される、請求項1に記載の方法。

【請求項10】

前記ゲートスタックの一部を除去するステップと、

前記チャネル領域上に金属ゲートを形成するステップと、を含む、請求項1に記載の方法。

【請求項11】

前記チャネル領域上に前記金属ゲートを形成する前に、前記チャネル領域に誘電層を配置するステップを含む、請求項10に記載の方法。

【請求項12】

半導体基板におけるfinFETであって、

前記半導体基板から突き出る第1側面と、前記第1側面と反対側であって、前記半導体基板から突き出る第2側面とを有するチャネル領域と、

前記チャネル領域を覆うゲートスタックとを備え、

前記ゲートスタックは、前記チャネル領域の前記第1側面および前記第2側面とダイレクトコンタクトした絶縁層と、前記絶縁層にダイレクトコンタクトする伝導性のゲート物質とを含み、

前記チャネル領域においてエピタキシャリーに成長される半導体のソースエピタキシー領域を備え、前記ソースエピタキシー領域は、ドープされ、

前記ソースエピタキシー領域から離れた前記チャネル領域においてエピタキシャルに成長される半導体のドレインエピタキシー領域を備え、前記ドレインエピタキシー領域は、ドープされる、finFET。

【請求項13】

前記チャネル領域は、固有の歪みを有し、前記ソースエピタキシー領域および前記ドレインエピタキシー領域は、第1歪みを有し、前記ソースエピタキシー領域および前記ドレインエピタキシー領域の第1歪みは、前記チャネル領域における電子とホールの移動性を良くするために、前記チャネル領域の少なくと一部の前記固有の歪みを修正する、請求項12に記載のfinFET。

【請求項14】

前記半導体基板は、バルクシリコンウエハである、請求項12に記載のfinFET。

【請求項15】

前記ドレインエピタキシー領域は、前記半導体ウエハと異なる物質である、請求項12に記載のfinFET。

【請求項16】

前記ソースエピタキシー領域および前記ドレインエピタキシー領域は、異なる材料特性を有している、請求項12に記載のfinFET。

【請求項17】

前記ゲート物質は、金属である、請求項12に記載のfinFET。

【請求項18】

前記絶縁物質は、ハフニウムを含む、請求項12に記載のfinFET。

【請求項1】

ソース領域、ドレイン領域および前記ソース領域と前記ドレイン領域との間のチャネル領域を有するフィンを備えたフィン電解効果トランジスタ(finFET)を加工するための方法であって、

半導体基板において前記フィンをエッチングするステップと、

前記チャネル領域においてゲートスタックを形成するステップと、を含み、

前記ゲートスタックは、前記チャネル領域にダイレクトコンタクトした絶縁層と、前記絶縁層にダイレクトコンタクトしたゲート物質とを有し、

前記チャネル領域を残すように、前記ソース領域および前記ドレイン領域をエッチングするステップと、

前記ソース領域および前記ドレイン領域に隣接する前記チャネル領域の両側において、ソースエピタキシー領域およびドレインエピタキシー領域それぞれを形成するために、エピタキシャル半導体を成長させるステップと、

前記エピタキシャル半導体を成長させながら、前記エピタキシャル半導体をその場ドーピングするステップと、を含む方法。

【請求項2】

前記フィンの周り、および、前記フィン上に、絶縁層を配置するステップと、

前記フィンの表面に略同一平面の上部表面を有するように、前記絶縁層を研磨するステップと、を含む、請求項1に記載の方法。

【請求項3】

前記ゲートスタックを形成するステップに優先して、絶縁層を配置するステップおよび前記絶縁層を研磨するステップが行なわれる、請求項2に記載の方法。

【請求項4】

前記フィンの底部分を覆う一方で、前記フィンの上部分が露出するように、前記絶縁層をエッチバックするステップを含む、請求項3に記載の方法。

【請求項5】

前記フィンをエッチングするステップに優先して、前記ソースおよび前記ドレインをエッチングするステップおよび前記エピタキシャル半導体を成長させるステップが行なわれる、請求項1に記載の方法。

【請求項6】

前記チャネル領域は、固有の歪みを有し、前記ソースエピタキシー領域は第1歪みを有し、前記ソースエピタキシー領域の前記第1歪みは、前記チャネル領域における電子またはホールの移動性を良くするために、前記チャネル領域の少なくとも一部における前記固有の歪みを修正する、請求項1に記載の方法。

【請求項7】

前記半導体基板は、バルクシリコンウエハである、請求項1に記載の方法。

【請求項8】

前記ドレインエピタキシー領域は、前記半導体ウエハと異なる物質である、請求項1に記載の方法。

【請求項9】

前記エピタキシャル半導体は、前記半導体基板の物質に選択的に成長される、請求項1に記載の方法。

【請求項10】

前記ゲートスタックの一部を除去するステップと、

前記チャネル領域上に金属ゲートを形成するステップと、を含む、請求項1に記載の方法。

【請求項11】

前記チャネル領域上に前記金属ゲートを形成する前に、前記チャネル領域に誘電層を配置するステップを含む、請求項10に記載の方法。

【請求項12】

半導体基板におけるfinFETであって、

前記半導体基板から突き出る第1側面と、前記第1側面と反対側であって、前記半導体基板から突き出る第2側面とを有するチャネル領域と、

前記チャネル領域を覆うゲートスタックとを備え、

前記ゲートスタックは、前記チャネル領域の前記第1側面および前記第2側面とダイレクトコンタクトした絶縁層と、前記絶縁層にダイレクトコンタクトする伝導性のゲート物質とを含み、

前記チャネル領域においてエピタキシャリーに成長される半導体のソースエピタキシー領域を備え、前記ソースエピタキシー領域は、ドープされ、

前記ソースエピタキシー領域から離れた前記チャネル領域においてエピタキシャルに成長される半導体のドレインエピタキシー領域を備え、前記ドレインエピタキシー領域は、ドープされる、finFET。

【請求項13】

前記チャネル領域は、固有の歪みを有し、前記ソースエピタキシー領域および前記ドレインエピタキシー領域は、第1歪みを有し、前記ソースエピタキシー領域および前記ドレインエピタキシー領域の第1歪みは、前記チャネル領域における電子とホールの移動性を良くするために、前記チャネル領域の少なくと一部の前記固有の歪みを修正する、請求項12に記載のfinFET。

【請求項14】

前記半導体基板は、バルクシリコンウエハである、請求項12に記載のfinFET。

【請求項15】

前記ドレインエピタキシー領域は、前記半導体ウエハと異なる物質である、請求項12に記載のfinFET。

【請求項16】

前記ソースエピタキシー領域および前記ドレインエピタキシー領域は、異なる材料特性を有している、請求項12に記載のfinFET。

【請求項17】

前記ゲート物質は、金属である、請求項12に記載のfinFET。

【請求項18】

前記絶縁物質は、ハフニウムを含む、請求項12に記載のfinFET。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−30776(P2013−30776A)

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願番号】特願2012−167379(P2012−167379)

【出願日】平成24年7月27日(2012.7.27)

【出願人】(512197766)アドバンスド イオン ビーム テクノロジー,インコーポレイテッド (2)

【氏名又は名称原語表記】ADVANCED ION BEAM TECHNOLOGY,INC.

【住所又は居所原語表記】5F,No.18,Creation Road 1,Science Park,Hsin−Chu 300,TAIWAN(R.O.C.)

【Fターム(参考)】

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願日】平成24年7月27日(2012.7.27)

【出願人】(512197766)アドバンスド イオン ビーム テクノロジー,インコーポレイテッド (2)

【氏名又は名称原語表記】ADVANCED ION BEAM TECHNOLOGY,INC.

【住所又は居所原語表記】5F,No.18,Creation Road 1,Science Park,Hsin−Chu 300,TAIWAN(R.O.C.)

【Fターム(参考)】

[ Back to top ]