仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、一般に、半導体デバイスに関し、特に、電界効果トランジスタ(FET)デバイスに関する。

【背景技術】

【0002】

ハイブリッド配向技術(Hybrid orientation technology、HOT)は、PFET反転層のための表面と、NFET反転層のための表面とを提供する。HOT技術を達成する低コストの手段により、FETの1つのタイプのデバイス・ボディが酸化物(シリコン・オン・インシュレータ(SOI))によって分離され、他のものは、バルク・ウェハに物理的に結合される。HOTにおいては、トライゲート(trigate)・デバイスが示されたが、一般に、電気的閾値電圧(Vt)調整手段を欠いたものであった。設計には、完全な空乏効果及び制御された短チャネル効果を保証するために、幅及び高さの制御が必要とされるので、通常、バルク・シリコン上でトライゲート・デバイスにおけるフィンの高さを設定することが重要である。

【0003】

トライゲート技術は、65nmノードを超える、相補型金属酸化膜半導体(CMOS)技術のスケーリングを拡張するために提案された。さらに、接合分離型FinFET又は酸化物分離型FinFETのいずれかを提供するバルクFinFET統合スキームが導入された。さらに、個々のデバイスにおけるドーパントの変動のために、デバイスのサイズが物理的に減少するにつれて、一般に、ドーピングによる閾値電圧の制御は、ますます効果がなくなっている。さらに、Vtの制御は、CMOSデバイスの更なるスケーリングに対する主要な障壁にもなっている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

従って、FETデバイスにおける閾値電圧をより良く制御できるデバイスに対する必要性が残っている。

【課題を解決するための手段】

【0005】

上記に鑑みて、本発明の1つの実施形態は、基板と、基板の上のシリコン・ゲルマニウム(SiGe)層と、SiGe層の上の、SiGe層に隣接した半導体層と、基板、SiGe層及び半導体層に隣接した絶縁層と、絶縁層に隣接した一対の第1のゲート構造体と、絶縁層の上の第2のゲート構造体とを含む電界効果トランジスタ(FET)を提供する。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び半導体の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体は、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

【0006】

本発明の別の実施形態は、基板と、基板に隣接したシリコン・ゲルマニウム(SiGe)層と、基板に隣接した第1の電界効果トランジスタ(FET)と、SiGe層に隣接した第2のFETとを含む集積回路を提供し、第1のFETは、FinFET及びトライゲート構造体のいずれかを含むことができ、第2のFETは、FinFET及びトライゲート構造体のいずれかを含むことができ、第1のFETは基板の上の半導体層と、半導体層の上の絶縁層と、半導体層の上の誘電体層と、誘電体層及び絶縁層の上のポリシリコン層とを含むことができる。さらに、第2のFETは、SiGe層の上の半導体層と、半導体層の上の、SiGe層に隣接した誘電体と、誘電体層の上の、SiGe層に隣接したポリシリコン層とを含むことができる。さらに、SiGe層は、炭素を含むことができる。集積回路は、基板内に複数の注入ウェル領域をさらに含むことができ、注入ウェル領域の少なくとも1つはSiGe層に接触する。さらに、集積回路は、基板内に複数の注入ウェル領域をさらに含むことができ、注入ウェル領域の少なくとも1つは半導体層に接触する。

【0007】

本発明の別の態様は、シリコン基板と、シリコン基板の上のシリコン・ゲルマニウム(SiGe)層と、シリコン基板の上の第1の電界効果トランジスタ(FET)と、SiGe層に接触する第2のFETとを含むトランジスタを提供し、第2のFETは、部分空乏型FET構造体を含むことが好ましい。第1のFETは、シリコン基板の上の半導体層と、半導体層の上の絶縁層と、半導体層の上の誘電体層と、誘電体層及び絶縁層の上のポリシリコン層とを含むことが好ましい。さらに、第2のFETは、SiGe層の上の半導体層と、半導体層の上の、SiGe層に隣接した誘電体層と、誘電体層の上の、SiGe層に隣接したポリシリコン層とを含むことが好ましい。また、SiGe層は炭素を含むことが好ましい。好ましくは、トランジスタは、基板内に複数の注入ウェル領域をさらに含み、注入ウェル領域の少なくとも1つはSiGe層に接触する。また、トランジスタは、基板内に複数の注入ウェル領域をさらに含むことができ、注入ウェル領域の少なくとも1つは半導体層に接触する。トランジスタは、第1のFETとシリコン基板との間に絶縁層をさらに含むことが好ましい。さらに、トランジスタは、絶縁層内に空間電荷領域を含むことができる。さらに、トランジスタは、第2のFETと基板との間に、SiGe層に対して実質的に平坦なボディ領域をさらに含むことが好ましい。トランジスタは、ボディ領域内の中立領域をさらに含むことが好ましい。さらに、第1のFETは第1の幅を含み、第2のFETは第2の幅を含み、第2の幅は第1の幅より広い。

【0008】

本発明の別の実施形態は、電界効果トランジスタ(FET)を製造する方法を提供し、この方法は、基板の上にシリコン・ゲルマニウム(SiGe)層を形成するステップと、SiGe層の上に、SiGe層に隣接して半導体層を堆積させるステップと、基板、SiGe層及び半導体層に隣接して絶縁層を構成するステップと、絶縁層に隣接して一対の第1のゲート構造体を配置するステップと、絶縁層の上に第2のゲート構造体を形成するステップとを含み、構成するステップは、SiGe層の側面、並びに前記半導体層の上面、半導体層の下面及び半導体層の側面に隣接して絶縁層を形成するステップを含むことができる。構成するステップは、絶縁層により第1のゲート構造体の対をカプセル封入するステップを含むことが好ましい。

【0009】

本発明の別の態様は、トランジスタを製造する方法を提供し、この方法は、シリコン基板の上にシリコン・ゲルマニウム(SiGe)層を形成するステップと、シリコン基板の上に第1の電界効果トランジスタ(FET)を構成するステップと、第2のFETを前記SiGe層に接触させるステップとを含み、構成するステップは、第1のFETをシリコン基板に接触させるステップを含むことが好ましく、構成するステップは、シリコン基板の上に半導体層を形成するステップと、半導体層の上に絶縁層を形成するステップと、半導体層の上に誘電体層を形成するステップと、誘電体層及び絶縁層の上にポリシリコン層を形成するステップとを含むことが好ましい。第2のFETは、SiGe層の上に半導体層を配置するステップと、半導体層の上に、前記SiGe層に隣接して誘電体層を配置するステップと、誘電体層の上に、SiGe層に隣接してポリシリコン層を配置するステップとを含むことが好ましい。この方法は、第1のFETと基板の間、及び、第2のFETと基板の間に絶縁層を形成するステップをさらに含むことができる。さらに、この方法は、第1の幅を有する第1のFETを構成するステップと、第2の幅を有する第2のFETを構成するステップとをさらに含むことができ、第2の幅は第1の幅より広い。

【0010】

本発明の実施形態のこれらの態様及び他の態様は、以下の説明及び添付図面と併せて考察すると、より良く認識され、理解される。しかしながら、以下の説明は、本発明の好ましい実施形態及び本発明の多くの具体的な詳細を示すが、例示の目的で与えられるものであり、限定を目的とするものではないことを理解すべきである。本発明の精神から逸脱することなく本発明の実施形態の範囲内で多くの変更及び修正を行うことができ、本発明の実施形態はこのような修正の全てを含むものである。

【図面の簡単な説明】

【0011】

【図1】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図2】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図3】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図4】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図5】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図6】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図7】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図8】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図9】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図10】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図11】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図12】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図13】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図14】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図15】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図16】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図17】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図18】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図19】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図20】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図21】本発明の第3の実施形態による集積回路構造体の連続的な製造の概略図である。

【図22】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図23】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図24】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図25】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図26】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図27】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図28】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図29】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図30】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図31】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図32】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図33】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図34】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図35】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図36】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図37】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図38】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【発明を実施するための形態】

【0012】

本発明の実施形態は、図面に関する以下の詳細な説明からより良く理解されるであろう。

【0013】

本発明の実施形態、並びに本発明の様々な特徴及び利点の詳細は、添付図面において示され、以下の説明において詳述される限定的ではない実施形態を参照して、より完全に説明される。図面に示される特徴は、必ずしも一定の縮尺で描かれていないことに留意すべきである。周知の要素及び処理技術の説明は、本発明の実施形態を必要以上に分かりにくくしないように省略される。本明細書で用いられる例は、単に、本発明の実施形態を実施する方法の理解を容易にすること、及び、さらに当業者が本発明の実施形態を実施できるようにすることを意図するものである。従って、これらの例は、本発明の実施形態の範囲を限定するものとして解釈されるべきではない。

【0014】

述べられたように、FETデバイスにおける閾値電圧をより良く制御することができるデバイスに対する必要性が残っている。本発明の実施形態は、トライゲート構成の自己整合されたボディ・コンタクト型SiGeベース・デバイスを有する構造体を提供することによって、これを達成するものである。ここで図を参照すると、より特定的には、図全体にわたって一貫して同様の参照符号が対応する特徴的形態を示す図1乃至図38を参照すると、本発明の好ましい実施形態が示される。

【0015】

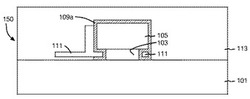

図1乃至図10は、本発明の第1の実施形態を示す。まず、図1に示されるように、本発明の第1の実施形態の構造体が、最初に、約200μmから500μmまでの好ましい厚さを有する半導体(例えば、シリコン)ウェハ101で始めることによって形成される。ウェハ101は、{100}結晶配向を有するバルク・シリコンを含むことが好ましい。その後、約550℃の好ましい成長温度で、分子ビーム・エピタキシ(MBE)、原子層堆積(ALD)、又は化学気相堆積(CVD)技術を用いて、シリコン・ウェハ101上に、随意的に炭素を有するシリコン・ゲルマニウム(SiGe)層(例えば、p−型SiGe層)の層103がエピタキシャル成長される。例えば、1重量%までの炭素をSiGe層103に添加し、SiGe層103内の歪みを軽減させることができる。SiGe層は、15nmから50nmまでの間の近似的な厚さを有することが好ましい。

【0016】

次に、周知のMBE又はCVD技術を用いて、SiGe層103の上に、別のシリコン層105がエピタキシャル成長される。シリコン層105は、{100}結晶配向と、おおよそ7nmから50nmまでの範囲の好ましい厚さとを有するシリコンを含むことが好ましい。{100}シリコンを用いることにより、後に形成されるチャネルのために高移動度の面を用いることが可能になる。次に、図2に示されるように、トライゲート・ボディは、上部シリコン層105をエッチングし、次にシリコンに対して露出されたSiGe層103を選択的にエッチングするエッチングを使用し、下部シリコン・ウェハ101上で停止することによって定められる。プラズマ・エッチング、反応性イオン・エッチング(RIE)、湿式エッチング、又は金属酸化物半導体(MOS)デバイスに適した他の任意の周知のエッチング・プロセスを用いて、エッチング・プロセスを達成することもできる。その後、選択的エッチングなどの等方性エッチング技術を用いて、又はSiよりずっと速い速度でSiGeを酸化させる約600℃での熱酸化を行い、引き続き等方性SiO2エッチングを行うことによって、SiGe層103の端部分を選択的に除去し、残りの上部シリコン領域105をアンダーカットする。

【0017】

図3に示されるように、好ましくは約900度での高温酸化を用いて、デバイスの上に犠牲酸化物107が熱成長される。次に、図4及び図5に示されるように、酸化物層107が、湿式エッチング、好ましくは緩衝フッ化水素(HF)溶液を用いて除去され、ゲート品質の誘電体109aが成長又は堆積される。この誘電体109aは、二酸化シリコン、又は窒素化された二酸化シリコン、或いはハフニウム・シリケート、二酸化ハフニウム等のような高k誘電体のいずれかを含むことができる。図6及び図7に示されるように、ポリシリコン層111が、CVDのような共形(conformal)堆積プロセスを用いて堆積

され、このことにより、最終的なトライゲート・デバイスのボディ・ゲートが形成される。ポリシリコン層111は、好ましくは上部シリコン領域105をアンダーカットする領域を完全に充填するのに十分な厚さからなり、かつ、好ましくは6nmから200nmまでの間の近似的な厚さを有する。

【0018】

次に、レジスト120が、ポリシリコン層111上に堆積され、シリコン・ボディ領域105の上のポリシリコン層111の部分の上部が露出されるまで、例えば、スピンオン及びエッチバック・プロセスによって平坦化される。次に、通常のフォトリソグラフィ・プロセスによって、レジスト120がパターン形成される。

【0019】

その後、異方性RIEプロセスを行って、ポリシリコン層111及び酸化物層109aの部分をエッチングし、下部シリコン層101及び上部シリコン層105を露出させる。SiGe層103の側部を固定するポリシリコン111の残りの部分は、デバイスのボディ・ゲートとして働き、レジスト120によって保護されるポリシリコン111の残りの部分は、デバイスのコンタクト領域として働く。続いて、図8に示されるように、デバイスの露出された部分の上に、露出されたシリコン面又は堆積された高k誘電体の熱酸化及び/又は窒化を通して、CVD技術或いはALD技術により、第3の誘電体層109bが成長される。誘電体層109aは、1nmから50nmまでの近似的な厚さを有することが好ましく、ポリシリコン・ボディゲート領域111を囲む領域において誘電体層109aと共形に配合される。さらに、酸化物層109bは、デバイスの最終的な電界効果トランジスタ(FET)部分のためのゲート酸化物として働く。次に、図9及び図10に示されるように、FETゲートが、酸化物層109bの上にポリシリコン層113を(例えば、CVDを用いて)堆積させることによって構成され、トライゲート構造体(2つのボディ・ゲート111及び1つのFETゲート113)が形成される。ポリシリコン層113は、フィン(シリコン領域105)の少なくとも2倍の高さを有することが好ましい。さらに、周知のプロセスを用いて、デバイス150上に、ソース/ドレイン・コンタクト112、主ゲート・コンタクト116及びボディゲート・コンタクト114が形成される。

【0020】

本発明の第1の実施形態は、効果的で安価なトライゲート半導体構造体150と、バルク・シリコン・ウェハ101上への製造方法とを提供する。本発明の第1の実施形態は、フィン105の高さが、正確なシリコン・エッチング時間にほとんど左右されないことを可能にするエッチング停止材料を提供することにより、バルク・シリコン101上のトライゲート・フィン高を良好に制御するゲート型ボディ・コンタクト114を提供するものである。さらに、ゲート型ボディ・コンタクト114により、トライゲート・フィン105が、ボディ内に注入される電荷を有することが可能になり、これによりVtが変化することが可能になり、必要に応じてボディ電位が動的に変化又は「フローティング」させることがさらに可能になる。このように、閾値電圧より正の(more positive)電圧(n型

FETの場合の、又はp型FETの場合は反対)を用いてボディ・コンタクト144を「オフ」にゲーティングすることによって、Vtの基板バイアスへの依存及びチャネル・ドライブの損失といった有害なボディ効果を防ぐことができる。

【0021】

具体的には、基板101からトライゲートFETボディ111までのボディ・コンタクト114は、ボディ・コンタクト・ゲート114が閾値電圧より低いときにのみ電気的に連続しており、その時点で、ボディ・コンタクト・ゲート111により囲まれているボディ・コンタクト114が堆積され、導電性になる(p型トライゲートFETの場合は、逆も真である)。このように、1つの構造体において、最適な動作のための柔軟性が達成される。従って、デバイス150は、半導体材料に適用された電場の影響によって少なくとも部分的に分離される。

【0022】

従って、本発明の第1の実施形態は、(1)トライゲートにおけるVt制御へのキーであるよく制御されたフィン高、(2)バルク寄生チャネル(図示せず)のよく制御された分離、及び(3)分離用ゲート113へのカットオフ電圧の印加による、トライゲート・デバイスのボディ・コンタクトを選択的に「フローティングさせる」機会を用いて、基板101からバルク・トライゲート・フィン105を分離させる。

【0023】

図11乃至図16に示される本発明の第2の実施形態においては、ウェハ101、SiGe層103及びシリコン層105を含む、第1の実施形態において提供されたものと同じベース基板が形成される。その後、図11に示されるように、シリコン層105の上で、第1のマスク106aがパターン形成され、下にあるシリコン層105の一部分を露出させる。周知のイオン注入技術を用いて、深い注入ウェル領域108が形成される。例えば、ウェル領域108は、デバイスの最終的なp−ウェル領域として働くことができる。イオン注入パラメータによって、ウェル領域108は、代替的に、デバイスの最終的なn−ウェル領域として働くこともできる。次に、図12に示されるように、ハードマスク110が、シリコン105の上に堆積され、5nmから50nmまでの間の近似的な厚さを有することができる。ハードマスク110は、二酸化シリコン及び/又は窒化シリコンを含むことが好ましく、酸化/窒化又はCVD技術を用いて形成されることが好ましい。

【0024】

その後、ハードマスク層110の上に第2のマスク106bが形成され、図12に示されるように、マスク106b及び下にあるハードマスク層110の部分が、下にあるシリコン層105の層に至るまで選択的にエッチングされる。次に、図13に示されるように第2のマスク106bを剥離した後、別のエッチング・プロセスを行って、シリコン層105の露出された領域を除去し、SiGe層103の部分を露出させる。図13の左手のフィン105は、通常、デバイスのNFET部分になり、図13の右手のフィン205は、通常、デバイスのPFET部分になる。勿論、当業者であれば、最初の注入ウェル領域108が予め形成されたときの最初のイオン注入パラメータによって、NFET部分及びPFET部分を反転させ得る(すなわち、右手のフィン205がNFETになり、左手のフィン105がPFETになる)ことを理解するであろう。随意的な酸素イオン注入プロセス(図13に下向き矢印で全体的に示されるような)を行うこともできる。

【0025】

次に、図14に示されるように、緩衝HF又はRIEを用いて、ハードマスク層110の残りの領域がエッチングされ、デバイスの露出された部分の上に酸化物層112が形成される。Siのものに比べてずっと速い速度でSiGeを酸化させる約600℃の酸化雰囲気において、酸化物層112が形成される。図15に示されるように、ポリシリコン層114は、CVD技術を用いてデバイスの上に堆積され、12nmから150nmまでの間の近似的な厚さ又はトライゲート・フィン105、205の高さの約2倍を有することが好ましく、ポリシリコン層114は平坦化される。その後、図16に示されるように、ポリシリコン層114が選択的にパターン形成され、周知の技術を用いてエッチングされ、トライゲート構造体160を形成する。トライゲート構造体160は、半導体フィン105、205と、フィン105、205の上部並びに右側及び左側にあるチャネル面(図示せず)と、チャネル面上のゲート誘電体112と、ゲート誘電体領域112に連続しているゲート電極114とを含む。

【0026】

本発明の第2の実施形態は、フィン高を精密に制御する方法で、トライゲートCMOSデバイス160におけるVtの電気的設定をもたらすことができる構造体及び方法を提供する。フィン105、205の高さは、シリコン領域105の厚さによって与えられ、SiGe層103の選択的エッチング/酸化の特性によって可能になる。さらに、トライゲート構造体の場合、フィン105、205の幅とフィン105、205の高さの比は、2:1から1:2までの間の比であることが好ましい。さらに、電圧を漸減的不純物濃度(retrograde)ウェル108に印加し、Vtを変える又は制御することもできる。

【0027】

図17乃至図25に、本発明の第3の実施形態が示される。第1の表面配向を有するシリコン基板101と、埋込み酸化物領域103と、第2の表面配向を有するシリコン領域105とを含むハイブリッドSOIベース基板が準備される。基板101は{100}の表面配向を有し、第2のシリコン領域は{110}の表面配向を有するが、その反対及び他の組み合わせも可能である。その後、図17に示されるように、シリコン層105の上に、二酸化シリコン(SiO2)層100及び窒化シリコン(Si3N4)層106が連続的に堆積される。SiO2層100は、5nmから50nmまでの間の近似的な厚さを有することが好ましく、Si3N4層106は、5nmから50nmまでの間の近似的な厚さを有することが好ましい。次に、図18に示されるように、選択的エッチング・プロセスを行って、埋込み酸化物層103、シリコン層105、SiO2層100及びSi3N4層106の一部分を除去し、これにより下にある基板層101の一部分を露出させる。

【0028】

図19に示されるように、SiGe層103、シリコン層105、SiO2層100及びSi3N4層106の残りの層で構成されるスタックの両側に、犠牲側壁スペーサ102が形成される。これらのスペーサは、CVDによる酸化シリコン又は窒化シリコンを含むことができ、約4nmから60nmまでの間の幅であることが好ましい。側壁スペーサ102は、Si3N4層106の上部高さをほんの少し下回る高さに形成することができる。次に、約5nmから50nmまでの間の好ましい厚さを有する薄いSiGe層107が、露出された基板101の上にエピタキシャル成長され、続いて、概ね図20に示されるようなシリコン層105の高さまで、シリコン層104がエピタキシャル成長される。シリコン層104は、約3nmから50nmまでの間の厚さであることが好ましく、基板101と同じ結晶配向を有する。その後、図21に示されるように、化学機械研磨及び/又はRIEエッチバックを用いて、SiO2層100、Si3N4層106及び側壁スペーサ102の上部をエッチングすることによって、構造体を平坦化する。

【0029】

次に、図22に示されるように、n−ウェル注入領域112が、シリコン層104内に形成され、基板層101内、側壁スペーサ102の周り及びSiGe層103の下方に延びる。次に、図23に示されるように、トライゲート・フィン領域104、105が、フォトレジストを用いてパターン形成され、選択的エッチング・プロセスが行われ、シリコン層104及びシリコン層105からフィンを形成する。その深さが下部SiGe層103まで延び、よってSiGe領域107もフィン104内に達すると、フィン・エッチングを停止することができる。約600℃の適切な温度でO2を用いる露出されたSiGeの選択的酸化が続いて行われる。緩衝HFエッチングを用いて、この酸化プロセス中に露出されたフィン側壁及びその上部に成長される少量の二酸化シリコンを除去し、酸化されたSiGe領域の大部分を完全な状態のまま残す。

【0030】

図24に示されるように、酸窒化シリコンを形成するための熱酸化/窒化、及び/又は、シリコン層104、105の各々の周りに高k材料を形成するためのALD又はCVD技術によって、ゲート誘電体材料116が堆積される。材料116の厚さは、約1nmから50nmまでの間であることが好ましい。このプロセスに続いて、ポリシリコン層118が、デバイスの上に堆積され、選択的にパターン形成され、エッチングされてゲート電極を形成する。図25に示されるわずかに異なる実施形態においては、p−ウェル注入領域119が、n−ウェル注入領域120に沿って形成される。一般に、本発明の第3の実施形態によると、バルクp−型シリコン層101内に、n−ウェル領域112(図24)を形成することができる。代替的に、バルクp−型シリコン層101内に、バルクn−バンド分離型p−ウェル注入領域119を形成することもできる。更なる代案として、バルクn−型シリコン層101内に、p−ウェル注入領域(図示せず)を形成することができる。当業者であれば、n−ウェル領域112、120及びp−ウェル領域119を交換できることを容易に理解するであろう。更に別の代替的な実施形態においては、SOI層101は、{110}結晶配向を有するシリコンを含むことができ、デバイス170のPFET部分は該デバイス170のバルク部分内にあり、デバイス170のNFET部分はSOI層101内にある。図17乃至図25によると、デバイス170のバルク部分は、一般に、デバイスの左手部分により定められる。これらの実施形態の全てにおいて、説明されたウェルは、通常のフォトリソグラフィを使用してレジストをパターン形成し、ウェルが所望される場所に開口部を形成すること及びp−型種又はn−型種のイオン注入によって形成することができる。n−バンドの場合、p−ウェル(p−型)種(典型的には、ホウ素)に比べると、高いエネルギー、よってより深いn−バンド(n−型)種(典型的には、ヒ素)の注入を用いることによって、p−ウェルを注入するのに用いられるものと同じマスクを用いてn−バンドを注入することができる。

【0031】

一般に、本発明の第3の実施形態は、1つのデバイスがSOI層101内にあり、他方がバルク領域内もある、閾値電圧を電気的に制御することができるHOTトライゲート・デバイス170を提供する。このHOTトライゲート・デバイス170は、低コストのハイブリッド・ウェル解決法及びバックゲート解決法を提供し、それぞれウェル・バイアス及びバックゲート・バイアスを通してVtを電気的に変える。埋込み酸化物103の下方のウェル領域112、119は、トライゲート・ボディ105のための効果的なバックゲートである。ドーピングがより少ないとき、ドーピングの変動がVtのばらつきにあまり影響を与えず、かつ、適切なウェル・バイアス及びバックゲート・バイアスによりプロセスが引き起こしたVtのばらつきを電気的に修正できるので、電気制御によりVtを設定することにより、ドーピングにあまり依存しないこと、よってよく制御されたデバイスVtが可能になる。

【0032】

図26乃至図38に、本発明の第4の実施形態が示される。バルク・ウェハ101、SiGe層103及びシリコン層105を含む、第1及び第2の実施形態において提供されたものと同じベース基板が形成される。第3の実施形態と同様に、図26に示されるように、シリコン層105の上に、SiO2層100及びSi3N4層106が連続的に堆積される。SiO2層100の近似的な厚さは5nmから50nmまでであることが好ましく、Si3N4層106の近似的な厚さは5nmから50nmまでであることが好ましい。次に、Si3N4層106の上に、フォトレジスト・マスク122が堆積され、選択的に形成される。次に、随意的に、図27に示されるように、選択的エッチング・プロセスを行って、SiO2層100及びSi3N4層106の一部分を除去し、これにより下にあるシリコン層105の一部分を露出させる。

【0033】

その後、図28に示されるように、フォトレジスト・マスクを剥離し、SiO2層100をエッチバックし、SiO2層100の端部を除去する。次に、図29に示されるように、周知のエッチング・プロセスを用いて、Si3N4層106を除去する。図30に示されるように、SiO2層100により保護されていない領域において構造体をエッチングし、下にあるシリコン基板層101の上面に至るまで、露出された領域において上部シリコン層105及び下にあるSiGe層103を除去し、これにより1つのフィン構造体128及び1つのメサ構造体129が形成される。図31は、SiGe層103の選択的エッチバックが行われた後の構造体を示す。このエッチングは、フィン128を完全にアンダーカットするのに十分な期間のものであるが、メサ129をアンダーカットするのに十分なものではない。図31に示されるデバイスの左手側のフィン構造体128は、図31及び図32に示される図の面外にあるために、非ハッシュ・ラインで示されるソース/ドレイン領域144によって支持される。

【0034】

次に、SiO2層100の選択的剥離除去が行われ、これにより図31の左手のフィン構造体128の上で、随意的なマスク(図示せず)がパターン形成され、より幅広のフィン構造体129(図31の右手のフィン構造体129)の上のSiO2層100が除去される。SiO2層の剥離中にフィン128がマスクされた場合、フィン128は、構造体128の両側においてのみゲーティングされる。フィン128がマスクされない場合には、上面もゲーティングされ、フィンは、トライゲート・トランジスタを形成することができる。結果として得られるデバイスが、図32に示される。次に、図33に示されるように、構造体全体の上に、好ましくは窒化シリコン又は酸化シリコンを含む共形のスペーサ125が堆積される。このスペーサは、フィン129の幅の約2.5倍から3.5倍までであることが好ましい。その後、図34に示されるように、指向性エッチング・プロセスを行い、これにより左手のフィン構造体128及び右手のフィン構造体129の両方の領域においてシリコン層105の下方にある領域を除いて、スペーサ125が除去される。

【0035】

次に、図35に示されるように、フィン構造体128、129の上に、ゲート誘電体層130が堆積される。シリコン酸窒化物を形成するための酸化及び/又は窒化、及び/又は、高k誘電体を形成するためのCVD/ALDを用いて、ゲート誘電体層130を形成することができる。ゲート誘電体層130は、約1nmから5nmまでの間の厚さであることが好ましい。次に、図36に示されるように、ポリシリコン層132が、デバイスの上に堆積され、対応するフィン構造体128及びメサ構造体129の上で選択的にエッチングされ、ゲート電極を形成する。ポリシリコン層132は、フィン128、129の高さの2倍より高いことが好ましい。

【0036】

空間電荷領域134が、図37に示されるデバイス180のフィン構造体128及びメサ構造体129の各々の中に形成される。トランジスタ・ボディ内の電子キャリアの大部分に反発するゲート電極132の電気的影響のために、空間電荷領域134は「空間電荷」状態になる。一般に、フィン構造体128は、完全空乏型FinFET又はトライゲート・デバイスであり、メサ構造体129は、部分空乏型のバルク・コンタクト式ボディFETデバイスである。構造体128は、十分に小さい容量で作製され、ゲート電極が大部分のキャリアのフィン(又はボディ)全体を空乏化し、該構造体128をいわゆる「完全空乏型デバイス」にし、対照的に、メサ構造体129は、SiGe層103/Si層101はシリコン層105と連続的であることにより、大きい容積を有し、ゲート電極132により大部分のキャリアがデバイスのボディの一部分だけを有効に空乏化することができ、よって「部分空乏型」と呼ばれる。さらに、周知の手順に従って、デバイス180内にウェル領域(図示せず)を注入し、PFET及びNFETを形成することができる。図38は、図37のデバイス180の平面図であり、各フィン128、129のそれぞれのポリシリコン・ゲート領域132と共に、フィン構造体128のソース/ドレイン領域146a及びフィン構造体129のソース/ドレイン領域146bをさらに示す。

【0037】

本発明の第4の実施形態は、絶縁体分離型FinFET又はトライゲート・デバイス128、及び、ボディ・コンタクトを有するバルク部分空乏型FET129の両方を、低コスト、低容量プロセスで提供する。従って、本発明の第4の実施形態は、トライゲート構造体におけるVt制御へのキーであるよく制御されたフィン高と、バルク寄生チャネルのよく制御された分離を用いて、基板101からのバルク・トライゲート・フィン105の分離を提供する。フィン高は、SiGe層103によって正確に制御され、このことにより、SiGe層103の上方にシリコン層105の厚さに等しいフィン高を構築することが可能になる。さらに、部分空乏型FET129は、その基板101に電気的バイアスをかけることによって更に調整されるVtを有することができる。本発明の第4の実施形態は、SiGeベースのバルク統合を用いて、バルク基板101上にFinFET及び/又はトライゲートを生成する。SiGe層103の制限された選択的エッチバックを付加し、その後薄い酸化物充填プロセスを行うことによって、本発明の第4の実施形態は、酸化物分離型フィン及びバルク結合型FETの両方を達成する。

【0038】

本発明の幾つかの実施形態は、集積回路チップに形成することができる。結果として得られる集積回路チップは、生ウェハの形態で(即ち、多数のパッケージされていないチップを有する単一のウェハとして)、ベア・ダイとして、又はパッケージされた形態で、製造業者により流通させることができる。後者の場合、チップは、単一のチップ・パッケージ(マザーボード又は他のより高いレベルのキャリアに取り付けられたリード線を有するプラスチック製キャリアのような)、又は、マルチチップ・パッケージ(片面又は両面の相互接続部、或いは埋め込まれた相互接続部を有するセラミック製キャリアのような)の中にマウントされる。いずれにせよ、その後、チップは、他のチップ、別個の回路素子、及び/又は、(a)マザーボードなどの中間製品又は(b)最終製品のいずれかの部品のような他の信号処理デバイスと共に統合される。最終製品は、玩具及び他のローエンド用途から、ディスプレイ、キーボード又は他の入力デバイス、及び中央処理装置を有する高性能コンピュータ製品に及ぶ、集積回路チップを含む何らかの製品とすることができる。

【0039】

上記の特定の実施形態の説明は、本発明の一般的な性質を十分に明らかにするものであるため、他者は、現在の知識を適用して、包括的な概念から逸脱することなく種々の用途のためにこの特定の実施形態を容易に改変し及び/又は適合させることができ、従って、このような適合及び改変は、開示された実施形態の均等物の意味及び範囲内にあるものと理解されるべきであり、かつ、そのように意図されている。本明細書において用いられている用語又は術語は、説明を目的とするものであり、限定を目的とするものではないことを理解すべきである。従って、好ましい実施形態に関して本発明の実施形態を説明してきたが、当業者であれば、本発明の実施形態は添付の特許請求の範囲の趣旨及び範囲内で改変して実施できることが分かるであろう。

【技術分野】

【0001】

本発明の実施形態は、一般に、半導体デバイスに関し、特に、電界効果トランジスタ(FET)デバイスに関する。

【背景技術】

【0002】

ハイブリッド配向技術(Hybrid orientation technology、HOT)は、PFET反転層のための表面と、NFET反転層のための表面とを提供する。HOT技術を達成する低コストの手段により、FETの1つのタイプのデバイス・ボディが酸化物(シリコン・オン・インシュレータ(SOI))によって分離され、他のものは、バルク・ウェハに物理的に結合される。HOTにおいては、トライゲート(trigate)・デバイスが示されたが、一般に、電気的閾値電圧(Vt)調整手段を欠いたものであった。設計には、完全な空乏効果及び制御された短チャネル効果を保証するために、幅及び高さの制御が必要とされるので、通常、バルク・シリコン上でトライゲート・デバイスにおけるフィンの高さを設定することが重要である。

【0003】

トライゲート技術は、65nmノードを超える、相補型金属酸化膜半導体(CMOS)技術のスケーリングを拡張するために提案された。さらに、接合分離型FinFET又は酸化物分離型FinFETのいずれかを提供するバルクFinFET統合スキームが導入された。さらに、個々のデバイスにおけるドーパントの変動のために、デバイスのサイズが物理的に減少するにつれて、一般に、ドーピングによる閾値電圧の制御は、ますます効果がなくなっている。さらに、Vtの制御は、CMOSデバイスの更なるスケーリングに対する主要な障壁にもなっている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

従って、FETデバイスにおける閾値電圧をより良く制御できるデバイスに対する必要性が残っている。

【課題を解決するための手段】

【0005】

上記に鑑みて、本発明の1つの実施形態は、基板と、基板の上のシリコン・ゲルマニウム(SiGe)層と、SiGe層の上の、SiGe層に隣接した半導体層と、基板、SiGe層及び半導体層に隣接した絶縁層と、絶縁層に隣接した一対の第1のゲート構造体と、絶縁層の上の第2のゲート構造体とを含む電界効果トランジスタ(FET)を提供する。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び半導体の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体は、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

【0006】

本発明の別の実施形態は、基板と、基板に隣接したシリコン・ゲルマニウム(SiGe)層と、基板に隣接した第1の電界効果トランジスタ(FET)と、SiGe層に隣接した第2のFETとを含む集積回路を提供し、第1のFETは、FinFET及びトライゲート構造体のいずれかを含むことができ、第2のFETは、FinFET及びトライゲート構造体のいずれかを含むことができ、第1のFETは基板の上の半導体層と、半導体層の上の絶縁層と、半導体層の上の誘電体層と、誘電体層及び絶縁層の上のポリシリコン層とを含むことができる。さらに、第2のFETは、SiGe層の上の半導体層と、半導体層の上の、SiGe層に隣接した誘電体と、誘電体層の上の、SiGe層に隣接したポリシリコン層とを含むことができる。さらに、SiGe層は、炭素を含むことができる。集積回路は、基板内に複数の注入ウェル領域をさらに含むことができ、注入ウェル領域の少なくとも1つはSiGe層に接触する。さらに、集積回路は、基板内に複数の注入ウェル領域をさらに含むことができ、注入ウェル領域の少なくとも1つは半導体層に接触する。

【0007】

本発明の別の態様は、シリコン基板と、シリコン基板の上のシリコン・ゲルマニウム(SiGe)層と、シリコン基板の上の第1の電界効果トランジスタ(FET)と、SiGe層に接触する第2のFETとを含むトランジスタを提供し、第2のFETは、部分空乏型FET構造体を含むことが好ましい。第1のFETは、シリコン基板の上の半導体層と、半導体層の上の絶縁層と、半導体層の上の誘電体層と、誘電体層及び絶縁層の上のポリシリコン層とを含むことが好ましい。さらに、第2のFETは、SiGe層の上の半導体層と、半導体層の上の、SiGe層に隣接した誘電体層と、誘電体層の上の、SiGe層に隣接したポリシリコン層とを含むことが好ましい。また、SiGe層は炭素を含むことが好ましい。好ましくは、トランジスタは、基板内に複数の注入ウェル領域をさらに含み、注入ウェル領域の少なくとも1つはSiGe層に接触する。また、トランジスタは、基板内に複数の注入ウェル領域をさらに含むことができ、注入ウェル領域の少なくとも1つは半導体層に接触する。トランジスタは、第1のFETとシリコン基板との間に絶縁層をさらに含むことが好ましい。さらに、トランジスタは、絶縁層内に空間電荷領域を含むことができる。さらに、トランジスタは、第2のFETと基板との間に、SiGe層に対して実質的に平坦なボディ領域をさらに含むことが好ましい。トランジスタは、ボディ領域内の中立領域をさらに含むことが好ましい。さらに、第1のFETは第1の幅を含み、第2のFETは第2の幅を含み、第2の幅は第1の幅より広い。

【0008】

本発明の別の実施形態は、電界効果トランジスタ(FET)を製造する方法を提供し、この方法は、基板の上にシリコン・ゲルマニウム(SiGe)層を形成するステップと、SiGe層の上に、SiGe層に隣接して半導体層を堆積させるステップと、基板、SiGe層及び半導体層に隣接して絶縁層を構成するステップと、絶縁層に隣接して一対の第1のゲート構造体を配置するステップと、絶縁層の上に第2のゲート構造体を形成するステップとを含み、構成するステップは、SiGe層の側面、並びに前記半導体層の上面、半導体層の下面及び半導体層の側面に隣接して絶縁層を形成するステップを含むことができる。構成するステップは、絶縁層により第1のゲート構造体の対をカプセル封入するステップを含むことが好ましい。

【0009】

本発明の別の態様は、トランジスタを製造する方法を提供し、この方法は、シリコン基板の上にシリコン・ゲルマニウム(SiGe)層を形成するステップと、シリコン基板の上に第1の電界効果トランジスタ(FET)を構成するステップと、第2のFETを前記SiGe層に接触させるステップとを含み、構成するステップは、第1のFETをシリコン基板に接触させるステップを含むことが好ましく、構成するステップは、シリコン基板の上に半導体層を形成するステップと、半導体層の上に絶縁層を形成するステップと、半導体層の上に誘電体層を形成するステップと、誘電体層及び絶縁層の上にポリシリコン層を形成するステップとを含むことが好ましい。第2のFETは、SiGe層の上に半導体層を配置するステップと、半導体層の上に、前記SiGe層に隣接して誘電体層を配置するステップと、誘電体層の上に、SiGe層に隣接してポリシリコン層を配置するステップとを含むことが好ましい。この方法は、第1のFETと基板の間、及び、第2のFETと基板の間に絶縁層を形成するステップをさらに含むことができる。さらに、この方法は、第1の幅を有する第1のFETを構成するステップと、第2の幅を有する第2のFETを構成するステップとをさらに含むことができ、第2の幅は第1の幅より広い。

【0010】

本発明の実施形態のこれらの態様及び他の態様は、以下の説明及び添付図面と併せて考察すると、より良く認識され、理解される。しかしながら、以下の説明は、本発明の好ましい実施形態及び本発明の多くの具体的な詳細を示すが、例示の目的で与えられるものであり、限定を目的とするものではないことを理解すべきである。本発明の精神から逸脱することなく本発明の実施形態の範囲内で多くの変更及び修正を行うことができ、本発明の実施形態はこのような修正の全てを含むものである。

【図面の簡単な説明】

【0011】

【図1】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図2】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図3】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図4】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図5】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図6】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図7】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図8】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図9】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図である。

【図10】本発明の第1の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図11】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図12】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図13】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図14】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図15】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図16】本発明の第2の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図17】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図18】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図19】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図20】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図21】本発明の第3の実施形態による集積回路構造体の連続的な製造の概略図である。

【図22】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図23】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図24】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図25】本発明の第3の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図26】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図27】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図28】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図29】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図30】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図31】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図32】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図33】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図34】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図35】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図36】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図37】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【図38】本発明の第4の実施形態による、集積回路構造体の連続的な製造の概略図ある。

【発明を実施するための形態】

【0012】

本発明の実施形態は、図面に関する以下の詳細な説明からより良く理解されるであろう。

【0013】

本発明の実施形態、並びに本発明の様々な特徴及び利点の詳細は、添付図面において示され、以下の説明において詳述される限定的ではない実施形態を参照して、より完全に説明される。図面に示される特徴は、必ずしも一定の縮尺で描かれていないことに留意すべきである。周知の要素及び処理技術の説明は、本発明の実施形態を必要以上に分かりにくくしないように省略される。本明細書で用いられる例は、単に、本発明の実施形態を実施する方法の理解を容易にすること、及び、さらに当業者が本発明の実施形態を実施できるようにすることを意図するものである。従って、これらの例は、本発明の実施形態の範囲を限定するものとして解釈されるべきではない。

【0014】

述べられたように、FETデバイスにおける閾値電圧をより良く制御することができるデバイスに対する必要性が残っている。本発明の実施形態は、トライゲート構成の自己整合されたボディ・コンタクト型SiGeベース・デバイスを有する構造体を提供することによって、これを達成するものである。ここで図を参照すると、より特定的には、図全体にわたって一貫して同様の参照符号が対応する特徴的形態を示す図1乃至図38を参照すると、本発明の好ましい実施形態が示される。

【0015】

図1乃至図10は、本発明の第1の実施形態を示す。まず、図1に示されるように、本発明の第1の実施形態の構造体が、最初に、約200μmから500μmまでの好ましい厚さを有する半導体(例えば、シリコン)ウェハ101で始めることによって形成される。ウェハ101は、{100}結晶配向を有するバルク・シリコンを含むことが好ましい。その後、約550℃の好ましい成長温度で、分子ビーム・エピタキシ(MBE)、原子層堆積(ALD)、又は化学気相堆積(CVD)技術を用いて、シリコン・ウェハ101上に、随意的に炭素を有するシリコン・ゲルマニウム(SiGe)層(例えば、p−型SiGe層)の層103がエピタキシャル成長される。例えば、1重量%までの炭素をSiGe層103に添加し、SiGe層103内の歪みを軽減させることができる。SiGe層は、15nmから50nmまでの間の近似的な厚さを有することが好ましい。

【0016】

次に、周知のMBE又はCVD技術を用いて、SiGe層103の上に、別のシリコン層105がエピタキシャル成長される。シリコン層105は、{100}結晶配向と、おおよそ7nmから50nmまでの範囲の好ましい厚さとを有するシリコンを含むことが好ましい。{100}シリコンを用いることにより、後に形成されるチャネルのために高移動度の面を用いることが可能になる。次に、図2に示されるように、トライゲート・ボディは、上部シリコン層105をエッチングし、次にシリコンに対して露出されたSiGe層103を選択的にエッチングするエッチングを使用し、下部シリコン・ウェハ101上で停止することによって定められる。プラズマ・エッチング、反応性イオン・エッチング(RIE)、湿式エッチング、又は金属酸化物半導体(MOS)デバイスに適した他の任意の周知のエッチング・プロセスを用いて、エッチング・プロセスを達成することもできる。その後、選択的エッチングなどの等方性エッチング技術を用いて、又はSiよりずっと速い速度でSiGeを酸化させる約600℃での熱酸化を行い、引き続き等方性SiO2エッチングを行うことによって、SiGe層103の端部分を選択的に除去し、残りの上部シリコン領域105をアンダーカットする。

【0017】

図3に示されるように、好ましくは約900度での高温酸化を用いて、デバイスの上に犠牲酸化物107が熱成長される。次に、図4及び図5に示されるように、酸化物層107が、湿式エッチング、好ましくは緩衝フッ化水素(HF)溶液を用いて除去され、ゲート品質の誘電体109aが成長又は堆積される。この誘電体109aは、二酸化シリコン、又は窒素化された二酸化シリコン、或いはハフニウム・シリケート、二酸化ハフニウム等のような高k誘電体のいずれかを含むことができる。図6及び図7に示されるように、ポリシリコン層111が、CVDのような共形(conformal)堆積プロセスを用いて堆積

され、このことにより、最終的なトライゲート・デバイスのボディ・ゲートが形成される。ポリシリコン層111は、好ましくは上部シリコン領域105をアンダーカットする領域を完全に充填するのに十分な厚さからなり、かつ、好ましくは6nmから200nmまでの間の近似的な厚さを有する。

【0018】

次に、レジスト120が、ポリシリコン層111上に堆積され、シリコン・ボディ領域105の上のポリシリコン層111の部分の上部が露出されるまで、例えば、スピンオン及びエッチバック・プロセスによって平坦化される。次に、通常のフォトリソグラフィ・プロセスによって、レジスト120がパターン形成される。

【0019】

その後、異方性RIEプロセスを行って、ポリシリコン層111及び酸化物層109aの部分をエッチングし、下部シリコン層101及び上部シリコン層105を露出させる。SiGe層103の側部を固定するポリシリコン111の残りの部分は、デバイスのボディ・ゲートとして働き、レジスト120によって保護されるポリシリコン111の残りの部分は、デバイスのコンタクト領域として働く。続いて、図8に示されるように、デバイスの露出された部分の上に、露出されたシリコン面又は堆積された高k誘電体の熱酸化及び/又は窒化を通して、CVD技術或いはALD技術により、第3の誘電体層109bが成長される。誘電体層109aは、1nmから50nmまでの近似的な厚さを有することが好ましく、ポリシリコン・ボディゲート領域111を囲む領域において誘電体層109aと共形に配合される。さらに、酸化物層109bは、デバイスの最終的な電界効果トランジスタ(FET)部分のためのゲート酸化物として働く。次に、図9及び図10に示されるように、FETゲートが、酸化物層109bの上にポリシリコン層113を(例えば、CVDを用いて)堆積させることによって構成され、トライゲート構造体(2つのボディ・ゲート111及び1つのFETゲート113)が形成される。ポリシリコン層113は、フィン(シリコン領域105)の少なくとも2倍の高さを有することが好ましい。さらに、周知のプロセスを用いて、デバイス150上に、ソース/ドレイン・コンタクト112、主ゲート・コンタクト116及びボディゲート・コンタクト114が形成される。

【0020】

本発明の第1の実施形態は、効果的で安価なトライゲート半導体構造体150と、バルク・シリコン・ウェハ101上への製造方法とを提供する。本発明の第1の実施形態は、フィン105の高さが、正確なシリコン・エッチング時間にほとんど左右されないことを可能にするエッチング停止材料を提供することにより、バルク・シリコン101上のトライゲート・フィン高を良好に制御するゲート型ボディ・コンタクト114を提供するものである。さらに、ゲート型ボディ・コンタクト114により、トライゲート・フィン105が、ボディ内に注入される電荷を有することが可能になり、これによりVtが変化することが可能になり、必要に応じてボディ電位が動的に変化又は「フローティング」させることがさらに可能になる。このように、閾値電圧より正の(more positive)電圧(n型

FETの場合の、又はp型FETの場合は反対)を用いてボディ・コンタクト144を「オフ」にゲーティングすることによって、Vtの基板バイアスへの依存及びチャネル・ドライブの損失といった有害なボディ効果を防ぐことができる。

【0021】

具体的には、基板101からトライゲートFETボディ111までのボディ・コンタクト114は、ボディ・コンタクト・ゲート114が閾値電圧より低いときにのみ電気的に連続しており、その時点で、ボディ・コンタクト・ゲート111により囲まれているボディ・コンタクト114が堆積され、導電性になる(p型トライゲートFETの場合は、逆も真である)。このように、1つの構造体において、最適な動作のための柔軟性が達成される。従って、デバイス150は、半導体材料に適用された電場の影響によって少なくとも部分的に分離される。

【0022】

従って、本発明の第1の実施形態は、(1)トライゲートにおけるVt制御へのキーであるよく制御されたフィン高、(2)バルク寄生チャネル(図示せず)のよく制御された分離、及び(3)分離用ゲート113へのカットオフ電圧の印加による、トライゲート・デバイスのボディ・コンタクトを選択的に「フローティングさせる」機会を用いて、基板101からバルク・トライゲート・フィン105を分離させる。

【0023】

図11乃至図16に示される本発明の第2の実施形態においては、ウェハ101、SiGe層103及びシリコン層105を含む、第1の実施形態において提供されたものと同じベース基板が形成される。その後、図11に示されるように、シリコン層105の上で、第1のマスク106aがパターン形成され、下にあるシリコン層105の一部分を露出させる。周知のイオン注入技術を用いて、深い注入ウェル領域108が形成される。例えば、ウェル領域108は、デバイスの最終的なp−ウェル領域として働くことができる。イオン注入パラメータによって、ウェル領域108は、代替的に、デバイスの最終的なn−ウェル領域として働くこともできる。次に、図12に示されるように、ハードマスク110が、シリコン105の上に堆積され、5nmから50nmまでの間の近似的な厚さを有することができる。ハードマスク110は、二酸化シリコン及び/又は窒化シリコンを含むことが好ましく、酸化/窒化又はCVD技術を用いて形成されることが好ましい。

【0024】

その後、ハードマスク層110の上に第2のマスク106bが形成され、図12に示されるように、マスク106b及び下にあるハードマスク層110の部分が、下にあるシリコン層105の層に至るまで選択的にエッチングされる。次に、図13に示されるように第2のマスク106bを剥離した後、別のエッチング・プロセスを行って、シリコン層105の露出された領域を除去し、SiGe層103の部分を露出させる。図13の左手のフィン105は、通常、デバイスのNFET部分になり、図13の右手のフィン205は、通常、デバイスのPFET部分になる。勿論、当業者であれば、最初の注入ウェル領域108が予め形成されたときの最初のイオン注入パラメータによって、NFET部分及びPFET部分を反転させ得る(すなわち、右手のフィン205がNFETになり、左手のフィン105がPFETになる)ことを理解するであろう。随意的な酸素イオン注入プロセス(図13に下向き矢印で全体的に示されるような)を行うこともできる。

【0025】

次に、図14に示されるように、緩衝HF又はRIEを用いて、ハードマスク層110の残りの領域がエッチングされ、デバイスの露出された部分の上に酸化物層112が形成される。Siのものに比べてずっと速い速度でSiGeを酸化させる約600℃の酸化雰囲気において、酸化物層112が形成される。図15に示されるように、ポリシリコン層114は、CVD技術を用いてデバイスの上に堆積され、12nmから150nmまでの間の近似的な厚さ又はトライゲート・フィン105、205の高さの約2倍を有することが好ましく、ポリシリコン層114は平坦化される。その後、図16に示されるように、ポリシリコン層114が選択的にパターン形成され、周知の技術を用いてエッチングされ、トライゲート構造体160を形成する。トライゲート構造体160は、半導体フィン105、205と、フィン105、205の上部並びに右側及び左側にあるチャネル面(図示せず)と、チャネル面上のゲート誘電体112と、ゲート誘電体領域112に連続しているゲート電極114とを含む。

【0026】

本発明の第2の実施形態は、フィン高を精密に制御する方法で、トライゲートCMOSデバイス160におけるVtの電気的設定をもたらすことができる構造体及び方法を提供する。フィン105、205の高さは、シリコン領域105の厚さによって与えられ、SiGe層103の選択的エッチング/酸化の特性によって可能になる。さらに、トライゲート構造体の場合、フィン105、205の幅とフィン105、205の高さの比は、2:1から1:2までの間の比であることが好ましい。さらに、電圧を漸減的不純物濃度(retrograde)ウェル108に印加し、Vtを変える又は制御することもできる。

【0027】

図17乃至図25に、本発明の第3の実施形態が示される。第1の表面配向を有するシリコン基板101と、埋込み酸化物領域103と、第2の表面配向を有するシリコン領域105とを含むハイブリッドSOIベース基板が準備される。基板101は{100}の表面配向を有し、第2のシリコン領域は{110}の表面配向を有するが、その反対及び他の組み合わせも可能である。その後、図17に示されるように、シリコン層105の上に、二酸化シリコン(SiO2)層100及び窒化シリコン(Si3N4)層106が連続的に堆積される。SiO2層100は、5nmから50nmまでの間の近似的な厚さを有することが好ましく、Si3N4層106は、5nmから50nmまでの間の近似的な厚さを有することが好ましい。次に、図18に示されるように、選択的エッチング・プロセスを行って、埋込み酸化物層103、シリコン層105、SiO2層100及びSi3N4層106の一部分を除去し、これにより下にある基板層101の一部分を露出させる。

【0028】

図19に示されるように、SiGe層103、シリコン層105、SiO2層100及びSi3N4層106の残りの層で構成されるスタックの両側に、犠牲側壁スペーサ102が形成される。これらのスペーサは、CVDによる酸化シリコン又は窒化シリコンを含むことができ、約4nmから60nmまでの間の幅であることが好ましい。側壁スペーサ102は、Si3N4層106の上部高さをほんの少し下回る高さに形成することができる。次に、約5nmから50nmまでの間の好ましい厚さを有する薄いSiGe層107が、露出された基板101の上にエピタキシャル成長され、続いて、概ね図20に示されるようなシリコン層105の高さまで、シリコン層104がエピタキシャル成長される。シリコン層104は、約3nmから50nmまでの間の厚さであることが好ましく、基板101と同じ結晶配向を有する。その後、図21に示されるように、化学機械研磨及び/又はRIEエッチバックを用いて、SiO2層100、Si3N4層106及び側壁スペーサ102の上部をエッチングすることによって、構造体を平坦化する。

【0029】

次に、図22に示されるように、n−ウェル注入領域112が、シリコン層104内に形成され、基板層101内、側壁スペーサ102の周り及びSiGe層103の下方に延びる。次に、図23に示されるように、トライゲート・フィン領域104、105が、フォトレジストを用いてパターン形成され、選択的エッチング・プロセスが行われ、シリコン層104及びシリコン層105からフィンを形成する。その深さが下部SiGe層103まで延び、よってSiGe領域107もフィン104内に達すると、フィン・エッチングを停止することができる。約600℃の適切な温度でO2を用いる露出されたSiGeの選択的酸化が続いて行われる。緩衝HFエッチングを用いて、この酸化プロセス中に露出されたフィン側壁及びその上部に成長される少量の二酸化シリコンを除去し、酸化されたSiGe領域の大部分を完全な状態のまま残す。

【0030】

図24に示されるように、酸窒化シリコンを形成するための熱酸化/窒化、及び/又は、シリコン層104、105の各々の周りに高k材料を形成するためのALD又はCVD技術によって、ゲート誘電体材料116が堆積される。材料116の厚さは、約1nmから50nmまでの間であることが好ましい。このプロセスに続いて、ポリシリコン層118が、デバイスの上に堆積され、選択的にパターン形成され、エッチングされてゲート電極を形成する。図25に示されるわずかに異なる実施形態においては、p−ウェル注入領域119が、n−ウェル注入領域120に沿って形成される。一般に、本発明の第3の実施形態によると、バルクp−型シリコン層101内に、n−ウェル領域112(図24)を形成することができる。代替的に、バルクp−型シリコン層101内に、バルクn−バンド分離型p−ウェル注入領域119を形成することもできる。更なる代案として、バルクn−型シリコン層101内に、p−ウェル注入領域(図示せず)を形成することができる。当業者であれば、n−ウェル領域112、120及びp−ウェル領域119を交換できることを容易に理解するであろう。更に別の代替的な実施形態においては、SOI層101は、{110}結晶配向を有するシリコンを含むことができ、デバイス170のPFET部分は該デバイス170のバルク部分内にあり、デバイス170のNFET部分はSOI層101内にある。図17乃至図25によると、デバイス170のバルク部分は、一般に、デバイスの左手部分により定められる。これらの実施形態の全てにおいて、説明されたウェルは、通常のフォトリソグラフィを使用してレジストをパターン形成し、ウェルが所望される場所に開口部を形成すること及びp−型種又はn−型種のイオン注入によって形成することができる。n−バンドの場合、p−ウェル(p−型)種(典型的には、ホウ素)に比べると、高いエネルギー、よってより深いn−バンド(n−型)種(典型的には、ヒ素)の注入を用いることによって、p−ウェルを注入するのに用いられるものと同じマスクを用いてn−バンドを注入することができる。

【0031】

一般に、本発明の第3の実施形態は、1つのデバイスがSOI層101内にあり、他方がバルク領域内もある、閾値電圧を電気的に制御することができるHOTトライゲート・デバイス170を提供する。このHOTトライゲート・デバイス170は、低コストのハイブリッド・ウェル解決法及びバックゲート解決法を提供し、それぞれウェル・バイアス及びバックゲート・バイアスを通してVtを電気的に変える。埋込み酸化物103の下方のウェル領域112、119は、トライゲート・ボディ105のための効果的なバックゲートである。ドーピングがより少ないとき、ドーピングの変動がVtのばらつきにあまり影響を与えず、かつ、適切なウェル・バイアス及びバックゲート・バイアスによりプロセスが引き起こしたVtのばらつきを電気的に修正できるので、電気制御によりVtを設定することにより、ドーピングにあまり依存しないこと、よってよく制御されたデバイスVtが可能になる。

【0032】

図26乃至図38に、本発明の第4の実施形態が示される。バルク・ウェハ101、SiGe層103及びシリコン層105を含む、第1及び第2の実施形態において提供されたものと同じベース基板が形成される。第3の実施形態と同様に、図26に示されるように、シリコン層105の上に、SiO2層100及びSi3N4層106が連続的に堆積される。SiO2層100の近似的な厚さは5nmから50nmまでであることが好ましく、Si3N4層106の近似的な厚さは5nmから50nmまでであることが好ましい。次に、Si3N4層106の上に、フォトレジスト・マスク122が堆積され、選択的に形成される。次に、随意的に、図27に示されるように、選択的エッチング・プロセスを行って、SiO2層100及びSi3N4層106の一部分を除去し、これにより下にあるシリコン層105の一部分を露出させる。

【0033】

その後、図28に示されるように、フォトレジスト・マスクを剥離し、SiO2層100をエッチバックし、SiO2層100の端部を除去する。次に、図29に示されるように、周知のエッチング・プロセスを用いて、Si3N4層106を除去する。図30に示されるように、SiO2層100により保護されていない領域において構造体をエッチングし、下にあるシリコン基板層101の上面に至るまで、露出された領域において上部シリコン層105及び下にあるSiGe層103を除去し、これにより1つのフィン構造体128及び1つのメサ構造体129が形成される。図31は、SiGe層103の選択的エッチバックが行われた後の構造体を示す。このエッチングは、フィン128を完全にアンダーカットするのに十分な期間のものであるが、メサ129をアンダーカットするのに十分なものではない。図31に示されるデバイスの左手側のフィン構造体128は、図31及び図32に示される図の面外にあるために、非ハッシュ・ラインで示されるソース/ドレイン領域144によって支持される。

【0034】

次に、SiO2層100の選択的剥離除去が行われ、これにより図31の左手のフィン構造体128の上で、随意的なマスク(図示せず)がパターン形成され、より幅広のフィン構造体129(図31の右手のフィン構造体129)の上のSiO2層100が除去される。SiO2層の剥離中にフィン128がマスクされた場合、フィン128は、構造体128の両側においてのみゲーティングされる。フィン128がマスクされない場合には、上面もゲーティングされ、フィンは、トライゲート・トランジスタを形成することができる。結果として得られるデバイスが、図32に示される。次に、図33に示されるように、構造体全体の上に、好ましくは窒化シリコン又は酸化シリコンを含む共形のスペーサ125が堆積される。このスペーサは、フィン129の幅の約2.5倍から3.5倍までであることが好ましい。その後、図34に示されるように、指向性エッチング・プロセスを行い、これにより左手のフィン構造体128及び右手のフィン構造体129の両方の領域においてシリコン層105の下方にある領域を除いて、スペーサ125が除去される。

【0035】

次に、図35に示されるように、フィン構造体128、129の上に、ゲート誘電体層130が堆積される。シリコン酸窒化物を形成するための酸化及び/又は窒化、及び/又は、高k誘電体を形成するためのCVD/ALDを用いて、ゲート誘電体層130を形成することができる。ゲート誘電体層130は、約1nmから5nmまでの間の厚さであることが好ましい。次に、図36に示されるように、ポリシリコン層132が、デバイスの上に堆積され、対応するフィン構造体128及びメサ構造体129の上で選択的にエッチングされ、ゲート電極を形成する。ポリシリコン層132は、フィン128、129の高さの2倍より高いことが好ましい。

【0036】

空間電荷領域134が、図37に示されるデバイス180のフィン構造体128及びメサ構造体129の各々の中に形成される。トランジスタ・ボディ内の電子キャリアの大部分に反発するゲート電極132の電気的影響のために、空間電荷領域134は「空間電荷」状態になる。一般に、フィン構造体128は、完全空乏型FinFET又はトライゲート・デバイスであり、メサ構造体129は、部分空乏型のバルク・コンタクト式ボディFETデバイスである。構造体128は、十分に小さい容量で作製され、ゲート電極が大部分のキャリアのフィン(又はボディ)全体を空乏化し、該構造体128をいわゆる「完全空乏型デバイス」にし、対照的に、メサ構造体129は、SiGe層103/Si層101はシリコン層105と連続的であることにより、大きい容積を有し、ゲート電極132により大部分のキャリアがデバイスのボディの一部分だけを有効に空乏化することができ、よって「部分空乏型」と呼ばれる。さらに、周知の手順に従って、デバイス180内にウェル領域(図示せず)を注入し、PFET及びNFETを形成することができる。図38は、図37のデバイス180の平面図であり、各フィン128、129のそれぞれのポリシリコン・ゲート領域132と共に、フィン構造体128のソース/ドレイン領域146a及びフィン構造体129のソース/ドレイン領域146bをさらに示す。

【0037】

本発明の第4の実施形態は、絶縁体分離型FinFET又はトライゲート・デバイス128、及び、ボディ・コンタクトを有するバルク部分空乏型FET129の両方を、低コスト、低容量プロセスで提供する。従って、本発明の第4の実施形態は、トライゲート構造体におけるVt制御へのキーであるよく制御されたフィン高と、バルク寄生チャネルのよく制御された分離を用いて、基板101からのバルク・トライゲート・フィン105の分離を提供する。フィン高は、SiGe層103によって正確に制御され、このことにより、SiGe層103の上方にシリコン層105の厚さに等しいフィン高を構築することが可能になる。さらに、部分空乏型FET129は、その基板101に電気的バイアスをかけることによって更に調整されるVtを有することができる。本発明の第4の実施形態は、SiGeベースのバルク統合を用いて、バルク基板101上にFinFET及び/又はトライゲートを生成する。SiGe層103の制限された選択的エッチバックを付加し、その後薄い酸化物充填プロセスを行うことによって、本発明の第4の実施形態は、酸化物分離型フィン及びバルク結合型FETの両方を達成する。

【0038】

本発明の幾つかの実施形態は、集積回路チップに形成することができる。結果として得られる集積回路チップは、生ウェハの形態で(即ち、多数のパッケージされていないチップを有する単一のウェハとして)、ベア・ダイとして、又はパッケージされた形態で、製造業者により流通させることができる。後者の場合、チップは、単一のチップ・パッケージ(マザーボード又は他のより高いレベルのキャリアに取り付けられたリード線を有するプラスチック製キャリアのような)、又は、マルチチップ・パッケージ(片面又は両面の相互接続部、或いは埋め込まれた相互接続部を有するセラミック製キャリアのような)の中にマウントされる。いずれにせよ、その後、チップは、他のチップ、別個の回路素子、及び/又は、(a)マザーボードなどの中間製品又は(b)最終製品のいずれかの部品のような他の信号処理デバイスと共に統合される。最終製品は、玩具及び他のローエンド用途から、ディスプレイ、キーボード又は他の入力デバイス、及び中央処理装置を有する高性能コンピュータ製品に及ぶ、集積回路チップを含む何らかの製品とすることができる。

【0039】

上記の特定の実施形態の説明は、本発明の一般的な性質を十分に明らかにするものであるため、他者は、現在の知識を適用して、包括的な概念から逸脱することなく種々の用途のためにこの特定の実施形態を容易に改変し及び/又は適合させることができ、従って、このような適合及び改変は、開示された実施形態の均等物の意味及び範囲内にあるものと理解されるべきであり、かつ、そのように意図されている。本明細書において用いられている用語又は術語は、説明を目的とするものであり、限定を目的とするものではないことを理解すべきである。従って、好ましい実施形態に関して本発明の実施形態を説明してきたが、当業者であれば、本発明の実施形態は添付の特許請求の範囲の趣旨及び範囲内で改変して実施できることが分かるであろう。

【特許請求の範囲】

【請求項1】

電界効果トランジスタ(FET)であって、

基板と、

前記基板の上のシリコン・ゲルマニウム(SiGe)層と、

前記SiGe層の上の、前記SiGe層に隣接した半導体層と、

前記基板、前記SiGe層及び前記半導体層に隣接した絶縁層と、

前記絶縁層に隣接した一対の第1のゲート構造体と、

前記絶縁層の上の第2のゲート構造体と

を備えるFET。

【請求項2】

前記絶縁層は、前記SiGe層の側面、並びに前記半導体層の上面、前記半導体層の下面及び前記半導体層の側面に隣接している、請求項1に記載のFET。

【請求項3】

前記SiGe層は炭素を含む、請求項1に記載のFET。

【請求項4】

前記第1のゲート構造体の対は、前記第2のゲート構造体に対して実質的に横断方向である、請求項1に記載のFET。

【請求項5】

前記第1のゲート構造体の対は、前記絶縁層によりカプセル封入される、請求項1に記載のFET。

【請求項6】

基板と、

前記基板に隣接したシリコン・ゲルマニウム(SiGe)層と、

前記基板に隣接した第1の電界効果トランジスタ(FET)と、

前記SiGe層に隣接した第2のFETと

を備える集積回路。

【請求項7】

前記第1のFETは、FinFET及びトライゲート構造体のいずれかを含む、請求項6に記載の集積回路。

【請求項8】

前記第2のFETは、FinFET及びトライゲート構造体のいずれかを含む、請求項6に記載の集積回路。

【請求項9】

前記第1のFETは、

前記基板の上の半導体層と、

前記半導体層の上の絶縁層と、

前記半導体層の上の誘電体層と、

前記誘電体層及び前記絶縁層の上のポリシリコン層と

を含む、請求項6に記載の集積回路。

【請求項10】

前記第2のFETは、

前記SiGe層の上の半導体層と、

前記半導体層の上の、前記SiGe層に隣接した誘電体層と、

前記誘電体層の上の、前記SiGe層に隣接したポリシリコン層と

を含む、請求項6に記載の集積回路。

【請求項11】

前記SiGe層は炭素を含む、請求項6に記載の集積回路。

【請求項12】

前記基板内の複数の注入ウェル領域をさらに備え、前記注入ウェル領域の少なくとも1つは前記SiGe層に接触する、請求項6に記載の集積回路。

【請求項13】

前記基板内の複数の注入ウェル領域をさらに備え、前記注入ウェル領域の少なくとも1つは前記半導体層に接触する、請求項9に記載の集積回路。

【請求項14】

シリコン基板と、

前記シリコン基板の上のシリコン・ゲルマニウム(SiGe)層と、

前記シリコン基板の上の第1の電界効果トランジスタ(FET)と、

前記SiGe層に接触する第2のFETと

を備えるトランジスタ。

【請求項15】

前記第1のFETは、FinFET及びトライゲート構造体のいずれかを含む、請求項14に記載のトランジスタ。

【請求項16】

前記第2のFETは、部分空乏型FET構造体を含む、請求項14に記載のトランジスタ。

【請求項17】

前記第1のFETは、

前記シリコン基板の上の半導体層と、

前記半導体層の上の絶縁層と、

前記半導体層の上の誘電体層と、

前記誘電体層及び前記絶縁層の上のポリシリコン層と

を含む、請求項14に記載のトランジスタ。

【請求項18】

前記第2のFETは、

前記SiGe層の上の半導体層と、

前記半導体層の上の、前記SiGe層に隣接した誘電体層と、

前記誘電体層の上の、前記SiGe層に隣接したポリシリコン層と

を含む、請求項14に記載のトランジスタ。

【請求項19】

前記SiGe層は炭素を含む、請求項14に記載のトランジスタ。

【請求項20】

前記基板内の複数の注入ウェル領域をさらに備え、前記注入ウェル領域の少なくとも1つは前記SiGe層に接触する、請求項14に記載のトランジスタ。

【請求項21】

前記基板内の複数の注入ウェル領域をさらに備え、前記注入ウェル領域の少なくとも1つは前記半導体層に接触する、請求項17に記載のトランジスタ。

【請求項22】

前記第1のFETと前記シリコン基板の間の絶縁層をさらに備える、請求項14に記載のトランジスタ。

【請求項23】

前記絶縁層内の空間電荷領域をさらに備える、請求項22に記載のトランジスタ。

【請求項24】

前記第2のFETと前記基板の間のボディ領域をさらに備え、前記ボディ領域は、前記SiGe層に対して実質的に平坦である、請求項14に記載のトランジスタ。

【請求項25】

前記ボディ領域内の中立領域をさらに備える、請求項24に記載のトランジスタ。

【請求項26】

前記第1のFETは第1の幅を含み、前記第2のFETは第2の幅を含み、前記第2の幅は前記第1の幅より広い、請求項14に記載のトランジスタ。

【請求項27】

電界効果トランジスタ(FET)を製造する方法であって、

基板の上にシリコン・ゲルマニウム(SiGe)層を形成するステップと、

前記SiGe層の上に、前記SiGe層に隣接して半導体層を堆積させるステップと、

前記基板、前記SiGe層及び前記半導体層に隣接して絶縁層を構成するステップと、

前記絶縁層に隣接して一対の第1のゲート構造体を配置するステップと、

前記絶縁層の上に第2のゲート構造体を形成するステップと

を含む方法。

【請求項28】

前記構成するステップは、前記SiGe層の側面、並びに前記半導体層の上面、前記半導体層の下面及び前記半導体層の側面に隣接して前記絶縁層を形成するステップを含む、請求項27に記載の方法。

【請求項29】

前記構成するステップは、前記絶縁層により前記第1のゲート構造体の対をカプセル封入するステップを含む、請求項27に記載の方法。

【請求項30】

トランジスタを製造する方法であって、

シリコン基板の上にシリコン・ゲルマニウム(SiGe)層を形成するステップと、

前記シリコン基板の上に第1の電界効果トランジスタ(FET)を構成するステップと、

第2のFETを前記SiGe層に接触させるステップと

を含む方法。

【請求項31】

前記構成するステップは、前記第1のFETを前記シリコン基板に接触させるステップを含む、請求項30に記載の方法。

【請求項32】

前記構成するステップは、

前記シリコン基板の上に半導体層を形成するステップと、

前記半導体層の上に絶縁層を形成するステップと、

前記半導体層の上に誘電体層を形成するステップと、

前記誘電体層及び前記絶縁層の上にポリシリコン層を形成するステップと

を含む、請求項30に記載の方法。

【請求項33】

前記第2のFETは、

前記SiGe層の上に半導体層を配置するステップと、

前記半導体層の上に、前記SiGe層に隣接して誘電体層を配置するステップと、

前記誘電体層の上に、前記SiGe層に隣接してポリシリコン層を配置するステップとにより形成される、請求項30に記載の方法。

【請求項34】

前記第1のFETと前記基板の間、及び、前記第2のFETと前記基板の間に絶縁層を形成するステップをさらに含む、請求項30に記載の方法。

【請求項35】

第1の幅を有する前記第1のFETを構成するステップと、第2の幅を有する前記第2のFETを構成するステップとをさらに含み、前記第2の幅は前記第1の幅より広い、請求項30に記載の方法。

【請求項1】

電界効果トランジスタ(FET)であって、

基板と、

前記基板の上のシリコン・ゲルマニウム(SiGe)層と、

前記SiGe層の上の、前記SiGe層に隣接した半導体層と、

前記基板、前記SiGe層及び前記半導体層に隣接した絶縁層と、

前記絶縁層に隣接した一対の第1のゲート構造体と、

前記絶縁層の上の第2のゲート構造体と

を備えるFET。

【請求項2】

前記絶縁層は、前記SiGe層の側面、並びに前記半導体層の上面、前記半導体層の下面及び前記半導体層の側面に隣接している、請求項1に記載のFET。

【請求項3】

前記SiGe層は炭素を含む、請求項1に記載のFET。

【請求項4】

前記第1のゲート構造体の対は、前記第2のゲート構造体に対して実質的に横断方向である、請求項1に記載のFET。

【請求項5】

前記第1のゲート構造体の対は、前記絶縁層によりカプセル封入される、請求項1に記載のFET。

【請求項6】

基板と、

前記基板に隣接したシリコン・ゲルマニウム(SiGe)層と、

前記基板に隣接した第1の電界効果トランジスタ(FET)と、

前記SiGe層に隣接した第2のFETと

を備える集積回路。

【請求項7】

前記第1のFETは、FinFET及びトライゲート構造体のいずれかを含む、請求項6に記載の集積回路。

【請求項8】

前記第2のFETは、FinFET及びトライゲート構造体のいずれかを含む、請求項6に記載の集積回路。

【請求項9】

前記第1のFETは、

前記基板の上の半導体層と、

前記半導体層の上の絶縁層と、

前記半導体層の上の誘電体層と、

前記誘電体層及び前記絶縁層の上のポリシリコン層と

を含む、請求項6に記載の集積回路。

【請求項10】

前記第2のFETは、

前記SiGe層の上の半導体層と、

前記半導体層の上の、前記SiGe層に隣接した誘電体層と、

前記誘電体層の上の、前記SiGe層に隣接したポリシリコン層と

を含む、請求項6に記載の集積回路。

【請求項11】

前記SiGe層は炭素を含む、請求項6に記載の集積回路。

【請求項12】

前記基板内の複数の注入ウェル領域をさらに備え、前記注入ウェル領域の少なくとも1つは前記SiGe層に接触する、請求項6に記載の集積回路。

【請求項13】

前記基板内の複数の注入ウェル領域をさらに備え、前記注入ウェル領域の少なくとも1つは前記半導体層に接触する、請求項9に記載の集積回路。

【請求項14】

シリコン基板と、

前記シリコン基板の上のシリコン・ゲルマニウム(SiGe)層と、

前記シリコン基板の上の第1の電界効果トランジスタ(FET)と、

前記SiGe層に接触する第2のFETと

を備えるトランジスタ。

【請求項15】

前記第1のFETは、FinFET及びトライゲート構造体のいずれかを含む、請求項14に記載のトランジスタ。

【請求項16】

前記第2のFETは、部分空乏型FET構造体を含む、請求項14に記載のトランジスタ。

【請求項17】

前記第1のFETは、

前記シリコン基板の上の半導体層と、

前記半導体層の上の絶縁層と、

前記半導体層の上の誘電体層と、

前記誘電体層及び前記絶縁層の上のポリシリコン層と

を含む、請求項14に記載のトランジスタ。

【請求項18】

前記第2のFETは、

前記SiGe層の上の半導体層と、

前記半導体層の上の、前記SiGe層に隣接した誘電体層と、

前記誘電体層の上の、前記SiGe層に隣接したポリシリコン層と

を含む、請求項14に記載のトランジスタ。

【請求項19】

前記SiGe層は炭素を含む、請求項14に記載のトランジスタ。

【請求項20】

前記基板内の複数の注入ウェル領域をさらに備え、前記注入ウェル領域の少なくとも1つは前記SiGe層に接触する、請求項14に記載のトランジスタ。

【請求項21】

前記基板内の複数の注入ウェル領域をさらに備え、前記注入ウェル領域の少なくとも1つは前記半導体層に接触する、請求項17に記載のトランジスタ。

【請求項22】

前記第1のFETと前記シリコン基板の間の絶縁層をさらに備える、請求項14に記載のトランジスタ。

【請求項23】

前記絶縁層内の空間電荷領域をさらに備える、請求項22に記載のトランジスタ。

【請求項24】

前記第2のFETと前記基板の間のボディ領域をさらに備え、前記ボディ領域は、前記SiGe層に対して実質的に平坦である、請求項14に記載のトランジスタ。

【請求項25】

前記ボディ領域内の中立領域をさらに備える、請求項24に記載のトランジスタ。

【請求項26】

前記第1のFETは第1の幅を含み、前記第2のFETは第2の幅を含み、前記第2の幅は前記第1の幅より広い、請求項14に記載のトランジスタ。

【請求項27】

電界効果トランジスタ(FET)を製造する方法であって、

基板の上にシリコン・ゲルマニウム(SiGe)層を形成するステップと、

前記SiGe層の上に、前記SiGe層に隣接して半導体層を堆積させるステップと、

前記基板、前記SiGe層及び前記半導体層に隣接して絶縁層を構成するステップと、

前記絶縁層に隣接して一対の第1のゲート構造体を配置するステップと、

前記絶縁層の上に第2のゲート構造体を形成するステップと

を含む方法。

【請求項28】

前記構成するステップは、前記SiGe層の側面、並びに前記半導体層の上面、前記半導体層の下面及び前記半導体層の側面に隣接して前記絶縁層を形成するステップを含む、請求項27に記載の方法。

【請求項29】

前記構成するステップは、前記絶縁層により前記第1のゲート構造体の対をカプセル封入するステップを含む、請求項27に記載の方法。

【請求項30】

トランジスタを製造する方法であって、

シリコン基板の上にシリコン・ゲルマニウム(SiGe)層を形成するステップと、

前記シリコン基板の上に第1の電界効果トランジスタ(FET)を構成するステップと、

第2のFETを前記SiGe層に接触させるステップと

を含む方法。

【請求項31】

前記構成するステップは、前記第1のFETを前記シリコン基板に接触させるステップを含む、請求項30に記載の方法。

【請求項32】

前記構成するステップは、

前記シリコン基板の上に半導体層を形成するステップと、

前記半導体層の上に絶縁層を形成するステップと、

前記半導体層の上に誘電体層を形成するステップと、

前記誘電体層及び前記絶縁層の上にポリシリコン層を形成するステップと

を含む、請求項30に記載の方法。

【請求項33】

前記第2のFETは、

前記SiGe層の上に半導体層を配置するステップと、

前記半導体層の上に、前記SiGe層に隣接して誘電体層を配置するステップと、

前記誘電体層の上に、前記SiGe層に隣接してポリシリコン層を配置するステップとにより形成される、請求項30に記載の方法。

【請求項34】

前記第1のFETと前記基板の間、及び、前記第2のFETと前記基板の間に絶縁層を形成するステップをさらに含む、請求項30に記載の方法。

【請求項35】

第1の幅を有する前記第1のFETを構成するステップと、第2の幅を有する前記第2のFETを構成するステップとをさらに含み、前記第2の幅は前記第1の幅より広い、請求項30に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【公開番号】特開2012−256903(P2012−256903A)

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願番号】特願2012−163637(P2012−163637)

【出願日】平成24年7月24日(2012.7.24)

【分割の表示】特願2008−523986(P2008−523986)の分割

【原出願日】平成18年7月21日(2006.7.21)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【復代理人】

【識別番号】100085545

【弁理士】

【氏名又は名称】松井 光夫

【復代理人】

【識別番号】100118599

【弁理士】

【氏名又は名称】村上 博司

【Fターム(参考)】

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願日】平成24年7月24日(2012.7.24)

【分割の表示】特願2008−523986(P2008−523986)の分割

【原出願日】平成18年7月21日(2006.7.21)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【復代理人】

【識別番号】100085545

【弁理士】

【氏名又は名称】松井 光夫

【復代理人】

【識別番号】100118599

【弁理士】

【氏名又は名称】村上 博司

【Fターム(参考)】

[ Back to top ]