仮想計算機システム

【課題】

PCI-Expressバスに代表される汎用のIOバスを有するサーバにおいて、32bitアドレッシングモードのI/Oアクセスを可能とするLPAR環境を提供する。

【解決手段】

(1) LPAR上のOSで発行されたIOトランザクションが32bitフォーマットであった場合で、かつ変換後の絶対アドレスが32bit空間を超えている場合に、IOトランザクションのパケットフォーマットを変換する。

(2) LPAR上のOSで発行されたIOトランザクションにECRCが付与されていた場合に、ECRCを再計算して最終受領先で正常に受信できるようにする。

(3) ECRCが既にエラーになっていた場合には、同じエラーを再現するようなECRCパターンを生成してパケットに付与する。

(4) 前記のECRC生成について、32bitと64bitのCRC演算器を搭載して同時に計算し、パケット生成時にバス上のデータ長を元に正しいCRC演算結果を選択する。

PCI-Expressバスに代表される汎用のIOバスを有するサーバにおいて、32bitアドレッシングモードのI/Oアクセスを可能とするLPAR環境を提供する。

【解決手段】

(1) LPAR上のOSで発行されたIOトランザクションが32bitフォーマットであった場合で、かつ変換後の絶対アドレスが32bit空間を超えている場合に、IOトランザクションのパケットフォーマットを変換する。

(2) LPAR上のOSで発行されたIOトランザクションにECRCが付与されていた場合に、ECRCを再計算して最終受領先で正常に受信できるようにする。

(3) ECRCが既にエラーになっていた場合には、同じエラーを再現するようなECRCパターンを生成してパケットに付与する。

(4) 前記のECRC生成について、32bitと64bitのCRC演算器を搭載して同時に計算し、パケット生成時にバス上のデータ長を元に正しいCRC演算結果を選択する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、単一の計算機で複数のOSを稼動させることが可能で、かつOS間での不正アクセスによる誤動作の防止・エラー発生時の処理機能を持つ仮想計算機システムに関し、特にCPUとIOデバイスの間のIOバス上で、メモリアドレスのフォーマット変換方法と、エラーのチェック方法並びに、それらを用いた仮想計算機システムに関する。

【背景技術】

【0002】

論理分割 (Logical Partition) は、単一のサーバ上で複数のオペレーティングシステム (Operating System、以下OS) を同時に動作させる技術である。 論理分割では、ハイパバイザと呼ばれる管理プログラムがサーバ管理者からの指示に従って、サーバの計算機資源 (メモリ領域、及びIOデバイスなどを含む) を複数の論理区画 (LPAR) に分割して、各LPAR上で1つずつのOSを動作させる。

【0003】

論理分割では、LPAR上のOSや、LPAR上のOSに割り付けられたIOデバイスのメモリアクセスをアドレス変換し、該LPARに割り付けられたメモリ領域内のアドレス (絶対アドレス) にアクセスさせる必要がある。このアドレスは、LPAR上のOSがアドレス変換して得た物理アドレス (以下、実アドレス) とは一般に異なる。

【0004】

また、あるOSの動作によって他のLPAR上のOSが停止、もしくは誤動作してはならない。そのためには、あるOSの動作によって他のLPAR上のOSが停止、もしくは誤動作してはならない。そのためには、あるOSが他のLPARの資源へアクセスできないこと (以下、アイソレーション) を保証する必要がある。

【0005】

ところで、Intel社のIA-32アーキテクチャに代表されるPCサーバでは近年、IOバスとしてPCI-Expressバスが広く用いられるようになってきている。PCI-Expressは、PCIバスと同様、論理分割を意識した設計を為されていないため、IOデバイス発のアクセスによってアイソレーションが保たれない (以下、アイソレーション障害) 恐れがある。具体的にはOSやIOドライバに不良がある場合や、IOカードの故障時でハードウェアによってエラーを検出できなかった場合に、アイソレーションが保証できない。そのため、PCサーバで論理分割を実現するには、IOデバイス発のアクセスに対してアイソレーションを保証することが従来から課題となっていた。

【0006】

上記の課題に対し、従来では特にPCIバスを念頭に置いて、特開2004-220218 (特許文献1) が提案されている。特許文献1では、チップセット内のI/O Ctrl Unit内にアドレス修飾機能を埋め込んだ例と、IOバス上にアクセス監視カードを装備し、その中でアドレス修飾機能を埋め込んだ例によって、実現するとしている。

【0007】

【特許文献1】特開2004-220218

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、特許文献1では、特にアクセス監視カードの方式をPCI-Expressバス上で採用した場合に、以下に示すような課題が解決されない。

【0009】

第1の課題は、LPAR上のOSが小さいアドレスフォーマット (32bitアドレスフォーマット) で動作している場合、32bit未満の実アドレスに対応する絶対アドレスが32bitを超え、大きいアドレスフォーマット (64bitアドレスフォーマット) とする必要がある。PCI-Expressのパケットでは、32bitと64bitのアドレスフォーマットが許されるが、32bitアドレスは3ダブルワード長のパケットであり、64bitアドレスは4ダブルワード長のパケットとなっており、単純に絶対アドレスで置き換えることが出来ない。

【0010】

第2の課題は、PCI-Expressのパケット内には、パケットを最初に生成した生成元と、最後に受領した最終受領先で、パケット内のデータにエラーが無いかを保証するためのECRC (End-to-End CRC) を埋め込むことが出来る。 このECRCは、アドレス変換やアドレスフォーマット変換を実施すると、そのままではエラーとなってしまう。

【0011】

第3の課題は、何らかの方式により第2の課題を解決してパケットの最終受領先でECRCを一致させた場合に、もしアドレス変換やアドレスフォーマット変換時に既にECRCがエラーであった場合に、本来検知する必要があるエラーが検知不能となってしまう。

【0012】

第4に、データバス上に流れるパケットのCRCを計算する場合に、上記のフォーマット変換によるパケットサイズの変更や、転送時のデータのバイト長によって、64bitブロックがまとめて来る場合と、32bitブロックしかバス上に無い場合がある。どちらの場合もスループットを最大化するために1サイクルで処理する必要があるが、データブロックのサイズを判定してからCRC演算するのでは処理が間に合わず、2サイクル処理となってしまう。

【0013】

本発明は、上記の課題を解決することを目的とする。

【課題を解決するための手段】

【0014】

本発明は、LPAR上で発行されたIOトランザクションが32bitフォーマットであった場合で、かつ変換後の絶対アドレスが32bit空間を超えている場合に、IOトランザクションのパケットフォーマットを変換する。

【0015】

次に、LPAR上で発行されたIOトランザクションにECRCが付与されていた場合に、ECRCを再計算して最終受領先で正常に受信できるようにする。

【0016】

この時、ECRCが既にエラーになっていた場合には、同じエラーを再現するようなECRCパターンを生成してパケットに付与する。

【0017】

前記のECRCについて、32bitと64bitのCRC演算器を搭載して同時に計算し、パケット生成時にバス上のデータ長を元に正しいCRC演算結果を選択することで、CRCの毎サイクル生成を可能とし、スループットを最大化する。

【発明の効果】

【0018】

PCI-Expressを採用するサーバにおいて、IOバス上に本発明を適用したアクセス監視カードを実装することにより、下記の利点が得られる。

【0019】

LPAR上で、32bitアドレッシングモードで動作するOSの動作を可能にする。

【0020】

ECRCを付与して信頼性を高めたIOトランザクションを、LPAR上のOSで、スループットを最大に保ったまま使用する手段を提供する。

【発明を実施するための最良の形態】

【0021】

以下に図面を用いて、本発明の実施の形態例を示す。

【実施例1】

【0022】

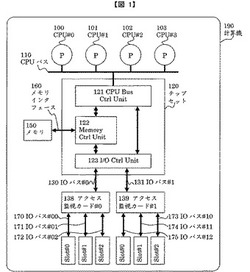

図1に本発明が想定するサーバの概略を示す。本実施例では、複数のCPUを接続可能な110 CPUバスに、4つのCPU (100〜103) が接続されている例を示す。本実施例では、CPU数を4としているが、4以外でも構わない。

【0023】

このCPUバスを制御する120 チップセットがあり、チップセットはCPUバスのほかに、130 IOバス#0及び131 IOバス#1、160 メモリインタフェースの制御を行っている。このIOバスは、現在一般に使われているPCI-Expressバスなどを想定している。

【0024】

なお本実施例ではIOバスを130及び131のように2バス接続する構成例を示しているが、2本以外の構成でも構わない。

【0025】

120 チップセットは、CPUバスを制御する121 CPU Bus Ctrl Unitと、メモリインタフェースを制御する122 Memory Ctrl Unit、IOバスを制御する123 IO Ctrl Unitから成る。

【0026】

130 IOバス#0と170〜172 IOバス#00〜02の間には138 アクセス監視カード#0が組み込まれ、131 IOバス#1と173〜175 IOバス#10〜12の間には139 アクセス監視カードが組み込まれる。

【0027】

本発明では、このCPUとチップセット、150 メモリと、IOバス間のアクセス監視カード、IOバスに接続されるIOデバイス (図面では示していない) をまとめて計算機と想定している。

【0028】

このサーバで提供される仮想計算機システムは、ハイパバイザと呼ばれるソフトウェアによって実現される。

【0029】

図2に仮想計算機システムで使用されるアドレスマップの相関図を示す。

【0030】

図1のサーバにより提供されるアドレスマップを絶対アドレス空間と呼ぶ。図2の実アドレス空間はOSが使用するアドレスを示し、図2の仮想アドレス空間とはアプリケーションプログラムが使用するアドレスを示している。

【0031】

図2は2つのOSが各LPAR上で動作している例を示しており、それぞれOS A、及びOS Bであるものとしている。OS A及びOS Bの上で動作する、異なるアプリケーションプログラムが使用する仮想アドレスVAとVBが、それぞれ非論理分割時にはRAとRBで示されるアドレスに変換されるものとする。論理分割運用時でハイパバイザによるアドレス変換が無い場合、RAとRBが同じ値であると、同じ絶対アドレスをOS AとOS Bがそれぞれアクセスするため、正常に動作できない。ハイパバイザはこれを防ぐために、RA及びRBに対応する、PA及びPB (≠PA) に対するアクセスを行わせている。

【0032】

仮想計算機における、CPU及びIOデバイスからのアクセスを以下に説明する。

【0033】

CPUからのアクセスの場合、OS AがVAをRAに変換するTLBエントリをCPUに登録しようとするのをハイパバイザが検知し、ハイパバイザがOSに代わってVAをPAに変換するTLBエントリの登録を行う。ハイパバイザは、各LPARへのメモリの割り付け状況とRAから、PAを算出可能である。実際にアプリケーションプログラムがVAにアクセスする際には、VAをPAに変換するTLBエントリがハイパバイザによって登録されているため、該アクセスはRAではなくPAをアクセスすることになり、図2で示すLPARごとのアドレス変換が実現されている。

【0034】

一方、IOデバイスからのアクセスの場合、CPUからのアクセスと異なりTLBに相当するアドレス変換機能が無いため、ハイパバイザによるアドレス変換は出来ない。そこで本発明では、図1における138 アクセス監視カード#0を図3のように構成することによって、IOからのトランザクションパケットに応じて該パケットを発生させたLPARを識別して、LPAR毎に異なるアドレスにアクセスするようにアドレス変換を行う。以下このアドレス変換の仕組みを、図を用いて説明する。なお、139 アクセス監視カード#1についても全く同じ回路を使用するため、本実施例では138のみの説明を行う。

【0035】

図3は138 アクセス監視カードの構成例を示す。138 アクセス監視カードは、130 IOバス#0に接続されており、200 I/O Bus Ctrl UnitによりIOバスの制御を行っている。本実施例のI/Oデバイス側では、Slot#0からSlot#2がある構成を示している。I/Oバスへのアクセス要求は、204 Bus Arb (バス調停回路) によって調停され、制御される。

【0036】

170〜172 IOバスのいずれかのスロットから、他のIOバスまたはCPU、メモリに対するトランザクションパケットが発行された場合、IOバスを介して該パケットが138 アクセス監視カード#0に伝達される。アクセス監視カードでは、204 Bus Arbが、IOバス170〜172に同時にトランザクションパケットの処理要求が来た時、どのバスの情報を受け付けるかを判定すると同時に、一連のパケット変換の間、選択したパケットが発行されたスロット番号を記憶して、どのパケットをどのLPARと対応付けするかを判断する指標を、210 発行元Slot番号として出力する。

【0037】

処理選択したパケットがECRCを持つ場合、206 ECRCチェックによってECRCをチェックする。チェック完了時に、エラーの有無と、エラーだった場合にはそのCRCパターンが209 ECRCチェック結果として205 プロトコル変換部に出力される。

【0038】

それと同時に、IOバスから入力されたパケット内のアドレスフィールドを切り出し、207 アドレスに宛先アドレスとして載せる。 同じく、パケットのデータフィールドを切り出し、208 データに載せる。

【0039】

この宛先アドレスを203のAdr修飾部で、そのアドレスの値と、210 発行元Slot番号に基づいて、201 Adr変換情報に記憶されているLPAR情報に基づいて修飾する。

【0040】

この修飾の内容は、前述のLPARごとに異なるアドレスにアクセスするよう、アドレス変換することを指している。続いて202 Adr Decでアクセス先とアクセス可否の判定を行う。最後に、205 プロトコル変換部で送出パケットのフォーマットを整える。 この時、もし209 ECRCチェック結果がエラーであった場合は、同時に送られているエラーのCRCデータとなるよう、プロトコル変換する。 この結果を、220 パケットバスを経由して200 I/O Bus Ctrl Unitに送り、そこから130 I/Oバス#0にパケットを送出する。

【0041】

図4にこのアドレス修飾部203の構成例を示す。図4に示す回路例では、201 Adr変換情報に格納されたアドレス変換に関する情報を使用する。この情報には次のものが含まれる。(1) インタリーブ及びアドレス領域情報、(2) スロット単位での所属LPAR情報、(3) 実アドレス範囲に応じたLPARごとのアドレス加算値。図6にこれらの情報を格納するレジスタのフォーマットを示す。

【0042】

(1) インターリーブおよびアドレス領域情報については、図2で説明したアドレスマップのうちの絶対アドレスで指定された範囲に対して、アドレス種別、インターリーブ有無・範囲指定、宛先バス・スロット番号の各情報が含まれる。アドレス種別は該アドレス範囲がメモリデバイス、もしくはMemory Mapped IO (以下MMIO) によってIOデバイスに割り付けられているかの区別が格納される。 該アドレス範囲がメモリデバイスに割り当てられている場合、特定のノードのメモリデバイスに割り付けられているか、もしくは複数のノードのメモリデバイス間でインターリーブされているかの情報が、インターリーブ有無・範囲指定のフィールドに格納される。 該アドレス範囲がIOデバイスに割り付けられている (以下、MMIO) 場合、アクセス対照となるIOデバイスのバス番号、およびスロット番号が、宛先バス・スロット番号のフィールドに格納される。

インターリーブ及びアドレス領域情報はサーバの初期化シーケンス中にBIOS (Basic IO System)、もしくはファームウェアによって設定され、特に論理分割をサポートしないサーバにおいても、これに類する情報を所持している。

【0043】

(2) スロット単位での所属LPAR情報は、発行元PCI−Expressスロットごとにアクセス可能な (=同一のLPARに属している) スロットを識別するための情報である。 本情報中の許可ビットが1にセットされているスロットに対してのみアクセスが許可される。 本情報は各LPARの生成時にハイパバイザによって設定される。 また本レジスタフォーマットのバリエーションとして、許可ビットが0になっているスロットに対してのみアクセスを許可する、としても構わない。

本情報は、発行元IOスロットと発行先IOスロットの組み合わせ1つに対して1ビットの容量で済むため、少ない記憶容量で制御を実装できる。

【0044】

(3) 実アドレス範囲に応じたLPARごとの加算値は、LPARごとに固有の、実アドレスから絶対アドレスへのアドレス変換を行うための情報である。 本情報は各LPARの生成時にハイパバイザによって設定される。

【0045】

なお、図6で示した制御情報フォーマットでは、個々の IOバス#00〜02が、それぞれ最大2スロットまで制御できるが、制御情報を増やすことで、より多くのスロットを制御することも可能である。

【0046】

図4に示す203 Adr修飾部は、304a、304bアドレス加算値と、アドレス領域情報、204 Bus Arbから入力される210 発行元スロット番号、及びIOバストランザクション(207アドレス)を入力として受信する。本実施例では、アドレス加算値が210 発行元スロット番号ごとに2つある例を示しているが、2つ以外でも構わない。

【0047】

IOバストランザクションは、301 Tx復号回路により、リード・ライトなどのトランザクションの種別と、トランザクションが32bitアドレスだったか、64bitアドレスだったかを記録するTx情報、及びアクセス先を示す307 実アドレスに分離される。Tx情報については、Adr修飾部では何も操作せずに、そのまま出力される。

【0048】

304a,304b アドレス加算値は、210 発行元スロット番号によって選択された後、305a Base及びSize部と、306a、306b Offset部に分離される。

【0049】

307 実アドレスは、303a、303b 加算器に入力され、306a、306b Offsetと加算される。

【0050】

310 64bit変換では、307 実アドレスが32bitフォーマットである場合に、Offset加算時に64bitとなる場合に備え、あらかじめ64bit形式に拡張する。

【0051】

302 Adr変換判定回路は、309a、309bの加算結果と、307実アドレスの内の1つを選択し、312 絶対アドレスとして出力する。

【0052】

図5は、202 Adr Decの構成例を示す。202 Adr Decは、図4の203 Adr修飾部から出力される308 Tx情報、及び312 絶対アドレス、311 アドレス変換有無を受信し、さらに201 Adr変換情報からインタリーブ及びアドレス領域情報、Slot単位での所属LPAR情報と、204 Bus Arbからは210 発行元Slot番号を受信して、図3の200 I/O Bus Ctrl Unitに対し、トランザクション (以下 Inbound Tx) を発行する。

【0053】

図7に205 プロトコル変換部の構成例を示す。308 Tx情報により、I/Oデバイスが発行したトランザクションパケットが32bitアドレスモードであったことが通知されると、64bitアドレス形式である211 絶対アドレスの値が、32bit未満の領域であった場合に限り、アドレス形式を32bit形式のTLPパケットに再変換して、220 パケットバス上に送出する。

【0054】

また、前記32bit/64bit判定後、確定したトランザクションパケットについて、32bit CRCと64bit CRCを同時に演算する。これは、データ長によっては64bitバス上に32bitしかデータが載っていない場合があるため、64bit幅のデータでも32bit幅のデータでもスループットを最大化するためには2種類のCRC演算器を準備し、常にCRC演算を行った上で、正しいデータ幅の計算結果を採用するという実装方式が必要な為である。

【0055】

209 ECRCチェック結果からECRCエラーが報告されていた場合、計算したCRCの値510 ECRCパターンと、チェック結果のCRCエラーパターンを使用し、アドレス変換後のデータでも同じエラーパターンが発生するECRCを作成して、トランザクションパケットに付与する。

【実施例2】

【0056】

実施例2は実施例1におけるスロットが、138 アクセス監視カード#0の下に必ず1つしか無いことが保証される場合の例である。

【0057】

この時、Bus Arbは必要なくなり、Slot番号に関わる制御も不要となるため、図8に示すとおり、制御が大幅に簡素になる。

【0058】

この方式は、例えばI/Oカードに、少ないゲート数で188 アクセス監視カード#0相当の機能を有する付加論理を実装することが出来るため、LPAR上のOSからの制御を前提としないPCI-Expressカードの部品をそのまま使って、LPAR環境で利用可能なI/Oカードを製造することが可能である。

【0059】

以上の様に本発明は、仮想計算機システムにおいて、PCI-Expressにより接続されたI/Oデバイスについて、トランザクションパケットのアイソレーション障害を防止しながらアドレス変換とアドレスフォーマット変換を行い、論理分割機能を実現する。また、既存のPCI-Express I/Oカードの部品を使用して論理分割に対応したI/Oカードを製造する手段を提供する。

【図面の簡単な説明】

【0060】

【図1】本発明が想定するサーバの構成例のブロック図。

【図2】本発明が想定するアドレスマップ図。

【図3】本発明におけるアクセス監視カードの構成例1のブロック図。

【図4】本発明におけるAdr修飾部の構成ブロック図。

【図5】本発明におけるAdr Decの構成ブロック図。

【図6】本発明におけるAdr変換情報のフォーマット図。

【図7】本発明におけるプロトコル変換部のブロック図。

【図8】本発明におけるアクセス監視カードの構成例2のブロック図

【符号の説明】

【0061】

100〜103 CPU#0〜CPU#3

110 CPUバス

120 チップセット

121 CPU Bus Ctrl Unit

122 Memory Ctrl Unit

123 I/O Ctrl Unit

130、131 IOバス#0、IOバス#1

138、139 アクセス監視カード#0、アクセス監視カード#1

150 メモリ

160 メモリインタフェース

170〜175 IOバス#00〜IOバス#12

188 アクセス監視カード#0

190 計算機

200 I/O Bus Ctrl Unit

201 Adr変換情報

202 Adr Dec

203 Adr 修飾部

204 Bus Arb

205 プロトコル変換部

206 ECRCチェック

207 アドレス

208 データ

209 ECRCチェック結果

210 発行元Slot番号

211 絶対アドレス

220 パケットバス

250 I/O Bus Ctrl Unit

251 Adr変換情報

252 Adr Dec

253 Adr 修飾部

255 プロトコル変換部

256 ECRCチェック

257 アドレス

258 データ

259 ECRCチェック結果

270 パケットバス

301 Tx復号回路

302 Adr変換判定回路

303a、303b 加算器

304a、304b アドレス加算値

305a、305b Base,Size

306a、306b Offset

307 実アドレス

308 Tx情報

309a、309b 加算結果

310 64bit変換

311 アドレス変換有無

312 絶対アドレス

401 アクセス先判定回路

402 アクセス可否判定

403 宛先Reg

404 INT生成

405 アイソレーション障害レジスタ

411 アドレス種別

412 宛先スロット番号

413 Inbound Tx

500 32bit整形

501 32bit CRC生成

502 64bit CRC生成

503 CRCレジスタ

510 ECRCパターン

511 アドレス・データ

【技術分野】

【0001】

本発明は、単一の計算機で複数のOSを稼動させることが可能で、かつOS間での不正アクセスによる誤動作の防止・エラー発生時の処理機能を持つ仮想計算機システムに関し、特にCPUとIOデバイスの間のIOバス上で、メモリアドレスのフォーマット変換方法と、エラーのチェック方法並びに、それらを用いた仮想計算機システムに関する。

【背景技術】

【0002】

論理分割 (Logical Partition) は、単一のサーバ上で複数のオペレーティングシステム (Operating System、以下OS) を同時に動作させる技術である。 論理分割では、ハイパバイザと呼ばれる管理プログラムがサーバ管理者からの指示に従って、サーバの計算機資源 (メモリ領域、及びIOデバイスなどを含む) を複数の論理区画 (LPAR) に分割して、各LPAR上で1つずつのOSを動作させる。

【0003】

論理分割では、LPAR上のOSや、LPAR上のOSに割り付けられたIOデバイスのメモリアクセスをアドレス変換し、該LPARに割り付けられたメモリ領域内のアドレス (絶対アドレス) にアクセスさせる必要がある。このアドレスは、LPAR上のOSがアドレス変換して得た物理アドレス (以下、実アドレス) とは一般に異なる。

【0004】

また、あるOSの動作によって他のLPAR上のOSが停止、もしくは誤動作してはならない。そのためには、あるOSの動作によって他のLPAR上のOSが停止、もしくは誤動作してはならない。そのためには、あるOSが他のLPARの資源へアクセスできないこと (以下、アイソレーション) を保証する必要がある。

【0005】

ところで、Intel社のIA-32アーキテクチャに代表されるPCサーバでは近年、IOバスとしてPCI-Expressバスが広く用いられるようになってきている。PCI-Expressは、PCIバスと同様、論理分割を意識した設計を為されていないため、IOデバイス発のアクセスによってアイソレーションが保たれない (以下、アイソレーション障害) 恐れがある。具体的にはOSやIOドライバに不良がある場合や、IOカードの故障時でハードウェアによってエラーを検出できなかった場合に、アイソレーションが保証できない。そのため、PCサーバで論理分割を実現するには、IOデバイス発のアクセスに対してアイソレーションを保証することが従来から課題となっていた。

【0006】

上記の課題に対し、従来では特にPCIバスを念頭に置いて、特開2004-220218 (特許文献1) が提案されている。特許文献1では、チップセット内のI/O Ctrl Unit内にアドレス修飾機能を埋め込んだ例と、IOバス上にアクセス監視カードを装備し、その中でアドレス修飾機能を埋め込んだ例によって、実現するとしている。

【0007】

【特許文献1】特開2004-220218

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、特許文献1では、特にアクセス監視カードの方式をPCI-Expressバス上で採用した場合に、以下に示すような課題が解決されない。

【0009】

第1の課題は、LPAR上のOSが小さいアドレスフォーマット (32bitアドレスフォーマット) で動作している場合、32bit未満の実アドレスに対応する絶対アドレスが32bitを超え、大きいアドレスフォーマット (64bitアドレスフォーマット) とする必要がある。PCI-Expressのパケットでは、32bitと64bitのアドレスフォーマットが許されるが、32bitアドレスは3ダブルワード長のパケットであり、64bitアドレスは4ダブルワード長のパケットとなっており、単純に絶対アドレスで置き換えることが出来ない。

【0010】

第2の課題は、PCI-Expressのパケット内には、パケットを最初に生成した生成元と、最後に受領した最終受領先で、パケット内のデータにエラーが無いかを保証するためのECRC (End-to-End CRC) を埋め込むことが出来る。 このECRCは、アドレス変換やアドレスフォーマット変換を実施すると、そのままではエラーとなってしまう。

【0011】

第3の課題は、何らかの方式により第2の課題を解決してパケットの最終受領先でECRCを一致させた場合に、もしアドレス変換やアドレスフォーマット変換時に既にECRCがエラーであった場合に、本来検知する必要があるエラーが検知不能となってしまう。

【0012】

第4に、データバス上に流れるパケットのCRCを計算する場合に、上記のフォーマット変換によるパケットサイズの変更や、転送時のデータのバイト長によって、64bitブロックがまとめて来る場合と、32bitブロックしかバス上に無い場合がある。どちらの場合もスループットを最大化するために1サイクルで処理する必要があるが、データブロックのサイズを判定してからCRC演算するのでは処理が間に合わず、2サイクル処理となってしまう。

【0013】

本発明は、上記の課題を解決することを目的とする。

【課題を解決するための手段】

【0014】

本発明は、LPAR上で発行されたIOトランザクションが32bitフォーマットであった場合で、かつ変換後の絶対アドレスが32bit空間を超えている場合に、IOトランザクションのパケットフォーマットを変換する。

【0015】

次に、LPAR上で発行されたIOトランザクションにECRCが付与されていた場合に、ECRCを再計算して最終受領先で正常に受信できるようにする。

【0016】

この時、ECRCが既にエラーになっていた場合には、同じエラーを再現するようなECRCパターンを生成してパケットに付与する。

【0017】

前記のECRCについて、32bitと64bitのCRC演算器を搭載して同時に計算し、パケット生成時にバス上のデータ長を元に正しいCRC演算結果を選択することで、CRCの毎サイクル生成を可能とし、スループットを最大化する。

【発明の効果】

【0018】

PCI-Expressを採用するサーバにおいて、IOバス上に本発明を適用したアクセス監視カードを実装することにより、下記の利点が得られる。

【0019】

LPAR上で、32bitアドレッシングモードで動作するOSの動作を可能にする。

【0020】

ECRCを付与して信頼性を高めたIOトランザクションを、LPAR上のOSで、スループットを最大に保ったまま使用する手段を提供する。

【発明を実施するための最良の形態】

【0021】

以下に図面を用いて、本発明の実施の形態例を示す。

【実施例1】

【0022】

図1に本発明が想定するサーバの概略を示す。本実施例では、複数のCPUを接続可能な110 CPUバスに、4つのCPU (100〜103) が接続されている例を示す。本実施例では、CPU数を4としているが、4以外でも構わない。

【0023】

このCPUバスを制御する120 チップセットがあり、チップセットはCPUバスのほかに、130 IOバス#0及び131 IOバス#1、160 メモリインタフェースの制御を行っている。このIOバスは、現在一般に使われているPCI-Expressバスなどを想定している。

【0024】

なお本実施例ではIOバスを130及び131のように2バス接続する構成例を示しているが、2本以外の構成でも構わない。

【0025】

120 チップセットは、CPUバスを制御する121 CPU Bus Ctrl Unitと、メモリインタフェースを制御する122 Memory Ctrl Unit、IOバスを制御する123 IO Ctrl Unitから成る。

【0026】

130 IOバス#0と170〜172 IOバス#00〜02の間には138 アクセス監視カード#0が組み込まれ、131 IOバス#1と173〜175 IOバス#10〜12の間には139 アクセス監視カードが組み込まれる。

【0027】

本発明では、このCPUとチップセット、150 メモリと、IOバス間のアクセス監視カード、IOバスに接続されるIOデバイス (図面では示していない) をまとめて計算機と想定している。

【0028】

このサーバで提供される仮想計算機システムは、ハイパバイザと呼ばれるソフトウェアによって実現される。

【0029】

図2に仮想計算機システムで使用されるアドレスマップの相関図を示す。

【0030】

図1のサーバにより提供されるアドレスマップを絶対アドレス空間と呼ぶ。図2の実アドレス空間はOSが使用するアドレスを示し、図2の仮想アドレス空間とはアプリケーションプログラムが使用するアドレスを示している。

【0031】

図2は2つのOSが各LPAR上で動作している例を示しており、それぞれOS A、及びOS Bであるものとしている。OS A及びOS Bの上で動作する、異なるアプリケーションプログラムが使用する仮想アドレスVAとVBが、それぞれ非論理分割時にはRAとRBで示されるアドレスに変換されるものとする。論理分割運用時でハイパバイザによるアドレス変換が無い場合、RAとRBが同じ値であると、同じ絶対アドレスをOS AとOS Bがそれぞれアクセスするため、正常に動作できない。ハイパバイザはこれを防ぐために、RA及びRBに対応する、PA及びPB (≠PA) に対するアクセスを行わせている。

【0032】

仮想計算機における、CPU及びIOデバイスからのアクセスを以下に説明する。

【0033】

CPUからのアクセスの場合、OS AがVAをRAに変換するTLBエントリをCPUに登録しようとするのをハイパバイザが検知し、ハイパバイザがOSに代わってVAをPAに変換するTLBエントリの登録を行う。ハイパバイザは、各LPARへのメモリの割り付け状況とRAから、PAを算出可能である。実際にアプリケーションプログラムがVAにアクセスする際には、VAをPAに変換するTLBエントリがハイパバイザによって登録されているため、該アクセスはRAではなくPAをアクセスすることになり、図2で示すLPARごとのアドレス変換が実現されている。

【0034】

一方、IOデバイスからのアクセスの場合、CPUからのアクセスと異なりTLBに相当するアドレス変換機能が無いため、ハイパバイザによるアドレス変換は出来ない。そこで本発明では、図1における138 アクセス監視カード#0を図3のように構成することによって、IOからのトランザクションパケットに応じて該パケットを発生させたLPARを識別して、LPAR毎に異なるアドレスにアクセスするようにアドレス変換を行う。以下このアドレス変換の仕組みを、図を用いて説明する。なお、139 アクセス監視カード#1についても全く同じ回路を使用するため、本実施例では138のみの説明を行う。

【0035】

図3は138 アクセス監視カードの構成例を示す。138 アクセス監視カードは、130 IOバス#0に接続されており、200 I/O Bus Ctrl UnitによりIOバスの制御を行っている。本実施例のI/Oデバイス側では、Slot#0からSlot#2がある構成を示している。I/Oバスへのアクセス要求は、204 Bus Arb (バス調停回路) によって調停され、制御される。

【0036】

170〜172 IOバスのいずれかのスロットから、他のIOバスまたはCPU、メモリに対するトランザクションパケットが発行された場合、IOバスを介して該パケットが138 アクセス監視カード#0に伝達される。アクセス監視カードでは、204 Bus Arbが、IOバス170〜172に同時にトランザクションパケットの処理要求が来た時、どのバスの情報を受け付けるかを判定すると同時に、一連のパケット変換の間、選択したパケットが発行されたスロット番号を記憶して、どのパケットをどのLPARと対応付けするかを判断する指標を、210 発行元Slot番号として出力する。

【0037】

処理選択したパケットがECRCを持つ場合、206 ECRCチェックによってECRCをチェックする。チェック完了時に、エラーの有無と、エラーだった場合にはそのCRCパターンが209 ECRCチェック結果として205 プロトコル変換部に出力される。

【0038】

それと同時に、IOバスから入力されたパケット内のアドレスフィールドを切り出し、207 アドレスに宛先アドレスとして載せる。 同じく、パケットのデータフィールドを切り出し、208 データに載せる。

【0039】

この宛先アドレスを203のAdr修飾部で、そのアドレスの値と、210 発行元Slot番号に基づいて、201 Adr変換情報に記憶されているLPAR情報に基づいて修飾する。

【0040】

この修飾の内容は、前述のLPARごとに異なるアドレスにアクセスするよう、アドレス変換することを指している。続いて202 Adr Decでアクセス先とアクセス可否の判定を行う。最後に、205 プロトコル変換部で送出パケットのフォーマットを整える。 この時、もし209 ECRCチェック結果がエラーであった場合は、同時に送られているエラーのCRCデータとなるよう、プロトコル変換する。 この結果を、220 パケットバスを経由して200 I/O Bus Ctrl Unitに送り、そこから130 I/Oバス#0にパケットを送出する。

【0041】

図4にこのアドレス修飾部203の構成例を示す。図4に示す回路例では、201 Adr変換情報に格納されたアドレス変換に関する情報を使用する。この情報には次のものが含まれる。(1) インタリーブ及びアドレス領域情報、(2) スロット単位での所属LPAR情報、(3) 実アドレス範囲に応じたLPARごとのアドレス加算値。図6にこれらの情報を格納するレジスタのフォーマットを示す。

【0042】

(1) インターリーブおよびアドレス領域情報については、図2で説明したアドレスマップのうちの絶対アドレスで指定された範囲に対して、アドレス種別、インターリーブ有無・範囲指定、宛先バス・スロット番号の各情報が含まれる。アドレス種別は該アドレス範囲がメモリデバイス、もしくはMemory Mapped IO (以下MMIO) によってIOデバイスに割り付けられているかの区別が格納される。 該アドレス範囲がメモリデバイスに割り当てられている場合、特定のノードのメモリデバイスに割り付けられているか、もしくは複数のノードのメモリデバイス間でインターリーブされているかの情報が、インターリーブ有無・範囲指定のフィールドに格納される。 該アドレス範囲がIOデバイスに割り付けられている (以下、MMIO) 場合、アクセス対照となるIOデバイスのバス番号、およびスロット番号が、宛先バス・スロット番号のフィールドに格納される。

インターリーブ及びアドレス領域情報はサーバの初期化シーケンス中にBIOS (Basic IO System)、もしくはファームウェアによって設定され、特に論理分割をサポートしないサーバにおいても、これに類する情報を所持している。

【0043】

(2) スロット単位での所属LPAR情報は、発行元PCI−Expressスロットごとにアクセス可能な (=同一のLPARに属している) スロットを識別するための情報である。 本情報中の許可ビットが1にセットされているスロットに対してのみアクセスが許可される。 本情報は各LPARの生成時にハイパバイザによって設定される。 また本レジスタフォーマットのバリエーションとして、許可ビットが0になっているスロットに対してのみアクセスを許可する、としても構わない。

本情報は、発行元IOスロットと発行先IOスロットの組み合わせ1つに対して1ビットの容量で済むため、少ない記憶容量で制御を実装できる。

【0044】

(3) 実アドレス範囲に応じたLPARごとの加算値は、LPARごとに固有の、実アドレスから絶対アドレスへのアドレス変換を行うための情報である。 本情報は各LPARの生成時にハイパバイザによって設定される。

【0045】

なお、図6で示した制御情報フォーマットでは、個々の IOバス#00〜02が、それぞれ最大2スロットまで制御できるが、制御情報を増やすことで、より多くのスロットを制御することも可能である。

【0046】

図4に示す203 Adr修飾部は、304a、304bアドレス加算値と、アドレス領域情報、204 Bus Arbから入力される210 発行元スロット番号、及びIOバストランザクション(207アドレス)を入力として受信する。本実施例では、アドレス加算値が210 発行元スロット番号ごとに2つある例を示しているが、2つ以外でも構わない。

【0047】

IOバストランザクションは、301 Tx復号回路により、リード・ライトなどのトランザクションの種別と、トランザクションが32bitアドレスだったか、64bitアドレスだったかを記録するTx情報、及びアクセス先を示す307 実アドレスに分離される。Tx情報については、Adr修飾部では何も操作せずに、そのまま出力される。

【0048】

304a,304b アドレス加算値は、210 発行元スロット番号によって選択された後、305a Base及びSize部と、306a、306b Offset部に分離される。

【0049】

307 実アドレスは、303a、303b 加算器に入力され、306a、306b Offsetと加算される。

【0050】

310 64bit変換では、307 実アドレスが32bitフォーマットである場合に、Offset加算時に64bitとなる場合に備え、あらかじめ64bit形式に拡張する。

【0051】

302 Adr変換判定回路は、309a、309bの加算結果と、307実アドレスの内の1つを選択し、312 絶対アドレスとして出力する。

【0052】

図5は、202 Adr Decの構成例を示す。202 Adr Decは、図4の203 Adr修飾部から出力される308 Tx情報、及び312 絶対アドレス、311 アドレス変換有無を受信し、さらに201 Adr変換情報からインタリーブ及びアドレス領域情報、Slot単位での所属LPAR情報と、204 Bus Arbからは210 発行元Slot番号を受信して、図3の200 I/O Bus Ctrl Unitに対し、トランザクション (以下 Inbound Tx) を発行する。

【0053】

図7に205 プロトコル変換部の構成例を示す。308 Tx情報により、I/Oデバイスが発行したトランザクションパケットが32bitアドレスモードであったことが通知されると、64bitアドレス形式である211 絶対アドレスの値が、32bit未満の領域であった場合に限り、アドレス形式を32bit形式のTLPパケットに再変換して、220 パケットバス上に送出する。

【0054】

また、前記32bit/64bit判定後、確定したトランザクションパケットについて、32bit CRCと64bit CRCを同時に演算する。これは、データ長によっては64bitバス上に32bitしかデータが載っていない場合があるため、64bit幅のデータでも32bit幅のデータでもスループットを最大化するためには2種類のCRC演算器を準備し、常にCRC演算を行った上で、正しいデータ幅の計算結果を採用するという実装方式が必要な為である。

【0055】

209 ECRCチェック結果からECRCエラーが報告されていた場合、計算したCRCの値510 ECRCパターンと、チェック結果のCRCエラーパターンを使用し、アドレス変換後のデータでも同じエラーパターンが発生するECRCを作成して、トランザクションパケットに付与する。

【実施例2】

【0056】

実施例2は実施例1におけるスロットが、138 アクセス監視カード#0の下に必ず1つしか無いことが保証される場合の例である。

【0057】

この時、Bus Arbは必要なくなり、Slot番号に関わる制御も不要となるため、図8に示すとおり、制御が大幅に簡素になる。

【0058】

この方式は、例えばI/Oカードに、少ないゲート数で188 アクセス監視カード#0相当の機能を有する付加論理を実装することが出来るため、LPAR上のOSからの制御を前提としないPCI-Expressカードの部品をそのまま使って、LPAR環境で利用可能なI/Oカードを製造することが可能である。

【0059】

以上の様に本発明は、仮想計算機システムにおいて、PCI-Expressにより接続されたI/Oデバイスについて、トランザクションパケットのアイソレーション障害を防止しながらアドレス変換とアドレスフォーマット変換を行い、論理分割機能を実現する。また、既存のPCI-Express I/Oカードの部品を使用して論理分割に対応したI/Oカードを製造する手段を提供する。

【図面の簡単な説明】

【0060】

【図1】本発明が想定するサーバの構成例のブロック図。

【図2】本発明が想定するアドレスマップ図。

【図3】本発明におけるアクセス監視カードの構成例1のブロック図。

【図4】本発明におけるAdr修飾部の構成ブロック図。

【図5】本発明におけるAdr Decの構成ブロック図。

【図6】本発明におけるAdr変換情報のフォーマット図。

【図7】本発明におけるプロトコル変換部のブロック図。

【図8】本発明におけるアクセス監視カードの構成例2のブロック図

【符号の説明】

【0061】

100〜103 CPU#0〜CPU#3

110 CPUバス

120 チップセット

121 CPU Bus Ctrl Unit

122 Memory Ctrl Unit

123 I/O Ctrl Unit

130、131 IOバス#0、IOバス#1

138、139 アクセス監視カード#0、アクセス監視カード#1

150 メモリ

160 メモリインタフェース

170〜175 IOバス#00〜IOバス#12

188 アクセス監視カード#0

190 計算機

200 I/O Bus Ctrl Unit

201 Adr変換情報

202 Adr Dec

203 Adr 修飾部

204 Bus Arb

205 プロトコル変換部

206 ECRCチェック

207 アドレス

208 データ

209 ECRCチェック結果

210 発行元Slot番号

211 絶対アドレス

220 パケットバス

250 I/O Bus Ctrl Unit

251 Adr変換情報

252 Adr Dec

253 Adr 修飾部

255 プロトコル変換部

256 ECRCチェック

257 アドレス

258 データ

259 ECRCチェック結果

270 パケットバス

301 Tx復号回路

302 Adr変換判定回路

303a、303b 加算器

304a、304b アドレス加算値

305a、305b Base,Size

306a、306b Offset

307 実アドレス

308 Tx情報

309a、309b 加算結果

310 64bit変換

311 アドレス変換有無

312 絶対アドレス

401 アクセス先判定回路

402 アクセス可否判定

403 宛先Reg

404 INT生成

405 アイソレーション障害レジスタ

411 アドレス種別

412 宛先スロット番号

413 Inbound Tx

500 32bit整形

501 32bit CRC生成

502 64bit CRC生成

503 CRCレジスタ

510 ECRCパターン

511 アドレス・データ

【特許請求の範囲】

【請求項1】

複数のCPUとメモリと複数のIOデバイスを、それぞれ制御部とCPUバス、メモリインタフェース、IOバスにより接続し、前記IOバス上のメモリとIOデバイスの間のアクセスを監視するアクセス監視装置を備えた物理計算機上にハイパバイザの制御下で複数のLPARを生成する仮想計算機システムにおいて、

前記IOデバイスからメモリへのアクセス時に、該アクセスを発生させたデバイスが属するLPARで確保しているアドレス空間にアドレス変換する手段と、前記アドレス変換の結果、変換前のアドレスフォーマットではビット数が足りず、指定出来ない場合に、アドレス領域を拡張したフォーマットに変換する手段を有することを特徴とする仮想計算機システム。

【請求項2】

前記アドレス変換時や、アドレスフォーマット変換時に、トランザクションパケットに埋め込まれたECRCを再計算し、トランザクションパケット内のECRCを置き換える手段を有することを特徴とする請求項1記載の仮想計算機システム。

【請求項3】

前記ECRC再計算時に、変換前のトランザクションパケットに埋め込まれていたECRCをチェックし、エラーがあった場合には同じエラーパターンを再計算したECRCに埋め込む手段を有することを特徴とする請求項2記載の仮想計算機システム。

【請求項4】

前記ECRC再計算時に、IOバスに流れるビットパターンを32bit CRC演算器と64bit CRC演算器で同時に演算し、IOバス上に実際に存在していたデータやアドレスが、32bit幅であったか、64bit幅であったかを前記演算後に判定してCRC演算データを収めるレジスタにセットすることを特徴とする請求項2の仮想計算機システム。

【請求項1】

複数のCPUとメモリと複数のIOデバイスを、それぞれ制御部とCPUバス、メモリインタフェース、IOバスにより接続し、前記IOバス上のメモリとIOデバイスの間のアクセスを監視するアクセス監視装置を備えた物理計算機上にハイパバイザの制御下で複数のLPARを生成する仮想計算機システムにおいて、

前記IOデバイスからメモリへのアクセス時に、該アクセスを発生させたデバイスが属するLPARで確保しているアドレス空間にアドレス変換する手段と、前記アドレス変換の結果、変換前のアドレスフォーマットではビット数が足りず、指定出来ない場合に、アドレス領域を拡張したフォーマットに変換する手段を有することを特徴とする仮想計算機システム。

【請求項2】

前記アドレス変換時や、アドレスフォーマット変換時に、トランザクションパケットに埋め込まれたECRCを再計算し、トランザクションパケット内のECRCを置き換える手段を有することを特徴とする請求項1記載の仮想計算機システム。

【請求項3】

前記ECRC再計算時に、変換前のトランザクションパケットに埋め込まれていたECRCをチェックし、エラーがあった場合には同じエラーパターンを再計算したECRCに埋め込む手段を有することを特徴とする請求項2記載の仮想計算機システム。

【請求項4】

前記ECRC再計算時に、IOバスに流れるビットパターンを32bit CRC演算器と64bit CRC演算器で同時に演算し、IOバス上に実際に存在していたデータやアドレスが、32bit幅であったか、64bit幅であったかを前記演算後に判定してCRC演算データを収めるレジスタにセットすることを特徴とする請求項2の仮想計算機システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2009−282651(P2009−282651A)

【公開日】平成21年12月3日(2009.12.3)

【国際特許分類】

【出願番号】特願2008−132627(P2008−132627)

【出願日】平成20年5月21日(2008.5.21)

【出願人】(000005108)株式会社日立製作所 (27,607)

【出願人】(000233295)日立情報通信エンジニアリング株式会社 (195)

【Fターム(参考)】

【公開日】平成21年12月3日(2009.12.3)

【国際特許分類】

【出願日】平成20年5月21日(2008.5.21)

【出願人】(000005108)株式会社日立製作所 (27,607)

【出願人】(000233295)日立情報通信エンジニアリング株式会社 (195)

【Fターム(参考)】

[ Back to top ]