任意信号発生装置

【課題】比較的低い周波数のサンプリング周波数を用いつつ、生成する信号の周波数帯域を拡張することができ、より高周波域までの任意波形の信号を生成可能にする。

【解決手段】 広帯域の任意波形の目的信号を生成する任意信号発生装置であって、前記目的信号の所定の周波数領域毎の複素周波数信号がそれぞれ入力されて複素時間信号をそれぞれ生成する複数の信号生成部と、前記複数の信号生成部の出力をそれぞれアナログ信号に変換する複数のD/A変換器と、前記複数のD/A変換器の出力のうち各信号生成部に割り当てられた周波数領域に対応したイメージ信号をそれぞれ選択的に出力する複数のフィルタと、前記複数のフィルタからの各複素時間信号を夫々合成する複数の位相合成部と、前記複数の位相合成部の出力を合成して前記目的信号を出力する信号合成部とを備えることを特徴とする。

【解決手段】 広帯域の任意波形の目的信号を生成する任意信号発生装置であって、前記目的信号の所定の周波数領域毎の複素周波数信号がそれぞれ入力されて複素時間信号をそれぞれ生成する複数の信号生成部と、前記複数の信号生成部の出力をそれぞれアナログ信号に変換する複数のD/A変換器と、前記複数のD/A変換器の出力のうち各信号生成部に割り当てられた周波数領域に対応したイメージ信号をそれぞれ選択的に出力する複数のフィルタと、前記複数のフィルタからの各複素時間信号を夫々合成する複数の位相合成部と、前記複数の位相合成部の出力を合成して前記目的信号を出力する信号合成部とを備えることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、広帯域の任意波形の目的信号を生成する任意信号発生装置に関する。

【背景技術】

【0002】

従来、パルスレーダ等に用いられるパルス幅の小さい信号を生成する技術として、ステップリカバリダイオード、アバランシェダイオード、高速論理ゲート等を用いて目的信号を生成する技術が知られている。これらの技術は、アナログ信号処理によりパルス幅の小さい信号を生成する技術であり、温度や湿度等の環境変化による回路特性の変化、素子や材料の特性の経年変化等により、性能が変化する虞がある。

【0003】

また、アナログ信号処理用の回路は、一度作成されると、その後の変更が困難であり、仕様や目的の変更に対して必ずしも自由度が高いとは言えない。例えば、レーダ用の信号発生装置としての用途の場合、レーダの割り当て周波数が変更されても、アナログ回路では対応困難である。さらに、送信波のスペクトルを変更する場合、外付けのフィルタを変更する等の対策が必要であるが、アナログ回路では、送信スペクトルの形状やレベルを適応的に変更することは困難である。

【0004】

このため、近年では、デジタル信号処理によって目的信号を生成する技術が採用されることが多い。このデジタル信号処理による信号発生装置としては、例えば特許文献1に開示されているようなダイレクトデジタルシンセサイザ(Direct Digital Synthesizer;DDS)が知られている。DDSは、波形データの入ったメモリの指定アドレスを更新して行き、その指定アドレスのデータをD/A変換によりアナログ波形に変換することで、任意の波形を発生させる技術である。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−225022号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に開示されているようなDDSによる信号発生装置は、基準クロック周波数に同期してその基準クロックの有理数倍の周期を有する信号波形をデジタル的に合成した後、D/A変換を行っている。よって、サンプリング定理により、目的信号に含まれる最高周波数の2倍以上のサンプリング周波数でD/A変換器を動作させなければならない。このため、目的信号のパルス幅を小さくすると、必要とされるサンプリング周波数がパルス幅に反比例して高くなる。よって、生成可能な信号の周波数には限界がある。

【0007】

本発明は上記事情に鑑みてなされたもので、比較的低い周波数のサンプリング周波数を用いつつ、生成する信号の周波数帯域を拡張することができ、より高周波域までの任意波形の信号を生成可能な任意信号発生装置を提供することを目的としている。

【課題を解決するための手段】

【0008】

本発明の一態様の任意信号発生装置は、広帯域の任意波形の目的信号を生成する任意信号発生装置であって、前記目的信号の所定の周波数領域毎の複素周波数信号がそれぞれ入力されて複素時間信号をそれぞれ生成する複数の信号生成部と、前記複数の信号生成部の出力をそれぞれアナログ信号に変換する複数のD/A変換器と、前記複数のD/A変換器の出力のうち各信号生成部に割り当てられた周波数領域に対応したイメージ信号をそれぞれ選択的に出力する複数のフィルタと、前記複数のフィルタからの各複素時間信号を夫々合成する複数の位相合成部と、前記複数の位相合成部の出力を合成して前記目的信号を出力する信号合成部とを備えることを特徴とする。

【発明の効果】

【0009】

本発明によれば、比較的低い周波数のサンプリング周波数を用いつつ、生成する信号の周波数帯域を拡張することができ、より高周波域までの任意波形の信号を生成することが可能となる。

【図面の簡単な説明】

【0010】

【図1】本発明の第1の実施の形態に係る任意信号発生装置を示すブロック図。

【図2】先願文献1,2における任意信号発生の基本アルゴリズムを示す説明図。

【図3】目的信号のスペクトルの一例を示す説明図。

【図4】デジタル信号生成モジュールSG1の出力に対応するスペクトルを示す説明図。

【図5】信号処理モジュールM1内のD/A変換器5a,5bの出力を示す説明図。

【図6】信号処理モジュールM1内のフィルタ6a,6bの出力を示す説明図。

【図7】デジタル信号生成モジュールSG2の出力に対応するスペクトルを示す説明図。

【図8】信号処理モジュールM2内のD/A変換器5a,5bの出力を示す説明図。

【図9】信号処理モジュールM2内のフィルタ6a,6bの出力を示す説明図。

【図10】デジタル信号生成モジュールSG3の出力に対応するスペクトルを示す説明図。

【図11】信号処理モジュールM3内のD/A変換器5a,5bの出力を示す説明図。

【図12】信号処理モジュールM3内のフィルタ6a,6bの出力を示す説明図。

【図13】デジタル信号生成モジュールSG4の出力に対応するスペクトルを示す説明図。

【図14】信号処理モジュールM4内のD/A変換器5a,5bの出力を示す説明図。

【図15】信号処理モジュールM4内のフィルタ6a’,6b’の出力を示す説明図。

【図16】混合器3の出力を示す説明図。

【図17】本発明の第2の実施の形態に係る任意信号発生装置を示すブロック図。

【図18】D/A変換器5a,5bの出力を示す説明図。

【図19】0次ホールド特性を示す説明図。

【図20】0次ホールド特性におけるD/A変換器15a,15bの出力を示す説明図。

【図21】0次ホールド特性におけるD/A変換器15a,15bの振幅特性を示す説明図。

【図22】RZ特性を示す説明図。

【図23】RZ特性におけるD/A変換器15a,15bの出力を示す説明図。

【図24】RZ特性におけるD/A変換器15a,15bの振幅特性を示す説明図。

【図25】信号処理モジュールM1内のフィルタ6a,6bの出力を示す説明図。

【図26】信号処理モジュールM2内のフィルタ6a,6bの出力を示す説明図。

【図27】信号処理モジュールM3内のフィルタ6a,6bの出力を示す説明図。

【図28】信号処理モジュールM4内のフィルタ6a’,6b’の出力を示す説明図。

【図29】混合器3の出力を示す説明図。

【図30】本発明の第3の実施の形態に係る任意信号発生装置を示すブロック図。

【図31】MIX特性を示す説明図。

【図32】MIX特性におけるD/A変換器25a,25bの出力を示す説明図。

【図33】MIX特性におけるD/A変換器25a,25bの振幅特性を示す説明図。

【図34】信号処理モジュールM1内のフィルタ6a,6bの出力を示す説明図。

【図35】信号処理モジュールM2内のフィルタ6a,6bの出力を示す説明図。

【図36】信号処理モジュールM3内のフィルタ6a,6bの出力を示す説明図。

【図37】MIX特性における信号処理モジュールM4内のフィルタ6a’,6b’の出力を示す説明図。

【図38】混合器3の出力を示す説明図。

【発明を実施するための形態】

【0011】

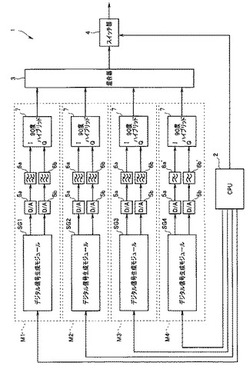

以下、図面を参照して本発明の実施の形態について詳細に説明する。図1は本発明の第1の実施の形態に係る任意信号発生装置を示すブロック図である。

【0012】

図1に示す任意信号発生装置1は、生成したい任意の周波数帯域の目的信号を時間領域で離散化した信号を用い、この信号をデジタル信号処理して実際の目的信号を生成する。従来のデジタル信号処理では、精度は高いが扱える周波数は比較的低いため、任意の広帯域の信号を処理することは難しい。本実施の形態においては、総ポイント数がNの任意の目的信号をデジタル信号処理が可能なP組の信号に分割して並列処理を行う。信号処理の都合上、P組に分割後の各組のポイント数は2のべき乗が好ましい。すなわちN/P=2a(aは任意の自然数)が好ましい。ただし、ゼロパディングによりポイント数を変更することは容易であることから、2のべき乗に限ることなく、任意の数で分割して処理することが可能である。

【0013】

ところで、本件出願人は、先に出願した特願2008−299937号明細書(以下、先願文献1という)及び特願2009−217484号明細書(以下、先願文献2という)において、このような並列処理を行う任意信号発生装置を既に提案している。先ず、図2を参照して先願文献1,2における任意信号発生の基本アルゴリズムについて説明する。

【0014】

図2に模式的に示すように、目的信号として時間的に連続したアナログ信号を想定し、このアナログ信号を離散化および離散フーリエ変換により周波数領域のスペクトルに変換し、その出力スペクトルを複数の成分に分割する。図2においては、A,B,C,Dの4つの成分に分割した例を示している。この4つの成分のうち、最も周波数の低いAの成分が直接的にデジタル信号処理の可能な周波数帯域である。

【0015】

成分Aの信号は、逆離散フーリエ変換し、D/A変換する。成分Bの信号は、成分Aの周波数帯域にシフトさせ、逆離散フーリエ変換し、D/A変換によりアナログ信号に変換し、更に、直交変調して周波数帯域を成分Aに隣接する高周波側にシフトする。同様に、成分Cの信号も、成分Aの周波数帯域にシフトさせ、逆離散フーリエ変換し、D/A変換によりアナログ信号に変換し、直交変調により周波数帯域を成分Bに隣接する高周波側にシフトする。同様に、成分Dの信号も、成分Aの周波数帯域にシフトさせ、逆離散フーリエ変換し、D/A変換によりアナログ信号に変換し、直交変調により周波数帯域を成分Cに続く高周波側にシフトする。最後に、アナログ信号に変換した成分Aの信号と、アナログ信号に変換して高周波側にシフトした成分B,C,Dの信号を合成することにより、目的信号と同様の信号を得ることができる。

【0016】

このことは、各成分毎に並列処理する複数の信号モジュールを用意し、各信号モジュールに目的信号の周波数領域の複素スペクトルを分割して与え、各信号モジュールでデジタル信号処理可能な成分を処理すると共に、デジタル信号処理の困難な高周波成分をアナログ信号処理で直交変調することにより、並列数Pに比例した広帯域の任意信号を生成(合成)できることを意味する。1つのモジュールで処理し得る周波数帯域幅をBwとするとき、生成可能な信号の周波数帯域は、Bw・Pとなる。つまり、処理し得る周波数帯域がBwである信号モジュールさえあれば、これを複数用意することで周波数帯域Bw・Pの目的信号を得ることができる。これにより、先願文献1,2における任意信号発生装置では、各モジュールのサンプリング周波数を比較的低い周波数に抑えつつ高い周波数の任意信号を生成することができる。

【0017】

ところが、先願文献1,2に開示した装置では、高い周波数の信号を扱う直交変調器及び局部発振器が必要であり消費電力が大きいという欠点がある。また、直交変調器及び局部発振器は比較的高価でしかもサイズが大きいので、コスト増及び大型化も招来してしまうという欠点もある。

【0018】

そこで、本実施の形態においては、D/A変換器のイメージ信号を利用することで、直交変調器及び局部発振器に代えて受動回路で構成される位相合成部としての90度ハイブリッドを採用することを可能にして、低消費電力、小型サイズ、低コストの任意信号発生器を実現する。

【0019】

本実施の形態においては、実時間の目的信号を離散化および離散フーリエ変換した結果得られるスペクトルのうち独立な周波数成分をP分割し、各周波数領域で信号処理を行うP個の信号処理モジュールを採用する。図1では、P=4の例を示している。即ち、信号処理モジュールM1,M2,M3,M4は、マイクロコンピュータ(CPU)を中心として構成されるコントローラ2から入力されるスペクトル情報(振幅、位相)に基づいて、それぞれ、周波数領域D,C,B,Aの信号を分割生成する。

【0020】

即ち、コントローラ2は、目的信号を離散フーリエ変換してD,C,B,Aの4つの周波数領域の信号成分に分割し、それぞれのスペクトル情報を、信号処理モジュールM1,M2,M3,M4に入力複素周波数信号として与える。各信号処理モジュールM1,M2,M3,M4は、フィルタ部を除いて同様の構成であり、それぞれ、コントローラ2からの離散データをデジタル信号処理するデジタル信号生成モジュールSG1,SG2,SG3,SG4を備えている。

【0021】

なおここでは処理の都合上、目的信号のスペクトルを低域から順にA,B,C,Dに分割し、それぞれ信号生成モジュールM4,M3,M2,M1で生成する例を示すが、分割信号と信号生成モジュールの対応はこれに限らない。

【0022】

各デジタル信号生成モジュールSG1,SG2,SG3,SG4は、ハードウェア実装、ソフトウェア実装、或いはハードウェア処理とソフトウェア処理の混在実装によって構成することができる。例えば、各デジタル信号生成モジュールSG1,SG2,SG3,SG4をハードウェアで構成する場合には、離散フーリエ変換された複素周波数信号を逆離散フーリエ変換する逆離散フーリエ変換器、逆離散フーリエ変換された並列データを直列データ(シリアルデータ)に変換する並直列変換器、並直列変換器の出力データを逓倍するインターポレータ、逓倍された信号から所望の周波数帯域のスペクトルを取り出す複素バンドパスフィルタ(複素BPF)、複素BPFからの出力を、I(In-Phase;同相成分)信号とQ(Quadrature;直交成分)信号とに分離するIQ分離器等によって構成することができる。

【0023】

各デジタル信号生成モジュールSG1〜SG4は、A〜Dの各領域の信号を低域に周波数シフトした複素時間信号を生成する。例えば、目的信号を図2のA〜Dの領域の信号に分割して処理するものとすると、デジタル信号生成モジュールSG1は、D領域のスペクトルを低域周波数にシフトしたときに得られる複素時間信号を生成する。また、デジタル信号生成モジュールSG2は、C領域のスペクトルを低域周波数にシフトしたときに得られる複素時間信号を生成する。また、デジタル信号生成モジュールSG3は、B領域のスペクトルを低域周波数にシフトしたときに得られる複素時間信号を生成し、デジタル信号生成モジュールSG4は、A領域のスペクトルを低域周波数にシフトしたときに得られる複素時間信号を生成する。

【0024】

各デジタル信号生成モジュールSG1〜SG4の出力は複素時間信号であり、その実数部と虚数部の信号をそれぞれD/A変換器5a,5bに与える。D/A変換器5a,5bは、デジタル信号生成モジュールSG1〜SG4の出力をアナログ信号に変換する。

【0025】

この場合において、D/A変換器5a,5bにおいて最低限必要とされるサンプリング周波数は、分割後の帯域幅と等しくなり、サンプリング周波数を分割数Pに反比例した値に低減することができる。D/A変換器5a,5bの出力はフィルタ6a,6b又は6a',6b'に与えられる。フィルタ6a,6bはバンドパスフィルタであり、フィルタ6a',6b'はローパスフィルタである。フィルタ6a,6b,6a',6b'は、入力されたアナログ信号を帯域制限する。

【0026】

本実施の形態においては、フィルタ6a,6b,6a’,6bは、D/A変換器5a,5bのD/A変換の際に生じるイメージ信号を取り出すようになっている。即ち、フィルタ6a,6b,6a’,6bは、D/A変換器5a,5bの出力からデジタル信号生成モジュールSG1〜SG4による周波数シフト前の帯域成分を取り出す。

【0027】

フィルタ6a,6b,6a’,6bの出力は、90度ハイブリッド7に供給される。90度ハイブリッド7は、受動素子で構成されており、位相が90度異なる2つの入力信号を合成して出力する。混合器3は、各信号処理モジュールM1,M2,M3,M4で生成された信号を合成してスイッチ部4に出力する。スイッチ部4は、例えば、FETやPINダイオード等の半導体デバイスを用いて構成され、コントローラ2により信号の通過と遮断が制御される。スイッチ部4は、合成信号の通過と遮断により、各モジュール間の信号生成処理時間の差や信号伝達時間の差による合成信号の歪みを除去した信号を得るようになっている。

【0028】

ただし、M4,M3,M2,M1の違いは、フィルタ部(6a,6b,6a',6b')の特性だけであるから、適切な通過帯域を持つフィルタを使用すれば、分割後の帯域と信号生成モジュールの対応関係は一意的ではない。

【0029】

次に、このように構成された実施の形態の動作について図3乃至図16を参照して説明する。ただし図中の*は共役複素数を表している。

【0030】

コントローラ2が設定する目的信号をx(n)とする。コントローラ2はこの目的信号x(n)を離散フーリエ変換して信号処理モジュールM1〜M4に与える。コントローラ2が目的信号x(n)を総ポイント数Nで離散フーリエ変換処理するものとし、この変換処理の結果スペクトルX(m)が得られるものとする。デジタル信号生成モジュールSG1〜SG4は、スペクトルX(m)を逆離散フーリエ変換してD/A変換器5a,5bに出力する。

【0031】

この処理を更に詳しく説明する。

x(n)とX(m)との関係は離散フーリエ変換対となり(1)式で表わすことができる。ただしnは離散時間インデックスを,mは離散周波数インデックスを表している。

【0032】

X(m)を(2)式のように振幅と位相に分解すれば、(1)式は(3)式のように表記できる。

【0033】

なお、x(n)とX(m)は周期Nの周期関数であるから以下の関係がある。

【0034】

x(n)=x(n±N)=x(n±2N)=x(n±3N)・・・

X(m)=X(m±N)=X(m±2N)=X(m±3N)・・・

さらにej(2π/N)mnはmとnに関して周期Nの周期関数である。

【0035】

まず、(3)式を直接IQ分離する場合を考える。

【0036】

IQ分離後の実数部出力xr(n)は次式で表わせる。

【0037】

xr(n)の離散フーリエ変換後のスペクトルをXr(m)とすれば、 Xr(m)=Xr1(m)+Xr2(m)となる。ただし

一方、(3)式にIQ分離を施した後の虚数部出力xi(n)は次式で表わせる。

【0038】

xi(n)の離散フーリエ変換後のスペクトルをXi(m)とすれば、 Xi(m)=Xi1(m)+Xi2(m)となる。ただし

Xr(m),Xi(m)をホールド特性がデルタ関数で表わされるD/A変換器5a,5bに入力した場合に得られるD/A変換器5a,5bの出力スペクトルはXr(m),Xi(m)のmを−∞〜+∞まで拡張したものとなる。

【0039】

次に、目的信号を周波数領域で4分割して、信号処理モジュールM1〜M4において処理する場合について説明する。いま、実数信号である目的信号x(n)を総ポイント数Nで複素離散フーリエ変換して得たスペクトルX(m)が図3で表わされる場合を考える。図3のA〜Dは、目的信号を周波数領域で4分割したことを示している。ただし簡略化のためにX(m)の振幅成分のみ図示してある。

【0040】

下記(10)式のN個の要素のうち前半のN/2個を除去したものを新たにX'(m)とおけば、X'(m)は下記(11)式で与えられる。

【0041】

X(m)={X(0),X(1),X(2),・・・,X(N-1)}…(10)

X'(m)={X(N/2),X(N/2+1),X(N/2+2),…,X(N-1)}…(11)

ここで、X'(m)の要素を4つに均等分割したものを頭から順にX1(m),X2(m),X3(m),X4(m)とおけば、X1(m),X2(m),X3(m),X4(m)はそれぞれ下記(12)式〜(15)式で与えられる。

【0042】

X1(m)={X(N/2),X(N/2+1),X(N/2+2),…X(N/2+N/8-1)}…(12)

X2(m)={X(N/2+N/8),X(N/2+N/8+1),X(N/2+N/8+2),…X(N/2+N/4-1)}…(13)

X3(m)={X(N/2+N/4),X(N/2+N/4+1),X(N/2+N/4+2),…X(N/2+3N/8-1)}…(14)

X4(m)={X(N/2+3N/8),X(N/2+3N/8+1),X(N/2+3N/8+2),…X(N-1)}…(15)

計算上の都合から、X1(m)のデータ列の後ろにゼロをN/8個だけ付加した配列をX12(m)とし,X2(m)のデータ列の前にゼロをN/8個だけ付加した配列を新たにX22(m)とし,X3(m)のデータ列の後ろにゼロをN/8個だけ付加した配列をX32(m)とし,X4(m)のデータ列の前にゼロをN/8個だけ付加した配列をX42(m)とおく。すると、下記(16-1)〜(16-4)式が得られる。

【0043】

X12(m)={X(N/2),X(N/2+1),X(N/2+2),…X(N/2+N/8-1),0,0,…,0}…(16-1)

X22(m)={0,0,…,0,X(N/2+N/8),X(N/2+N/8+1),X(N/2+N/8+2),…X(N/2+N/4-1)}…(16-2)

X32(m)={X(N/2+N/4),X(N/2+N/4+1),X(N/2+N/4+2),…X(N/2+3N/8-1),0,0,…,0}…(16-3)

X42(m)={0,0,…,0,X(N/2+N/4),X(N/2+N/4+1),X(N/2+N/4+2),…X(N/2+3N/8-1)}…(16-4)

これらのスペクトルX12(m),X22(m),X32(m),X42(m)がそれぞれデジタル信号生成モジュールSG1〜SG4に分配される。各デジタル信号生成モジュールSG1〜SG1は、それぞれ入力されたスペクトルを総ポイント数N/4で逆離散フーリエ変換する。

【0044】

X12(m)を総ポイント数N/4で逆離散フーリエ変換した結果をx12(n)とおけばx12(n)は下記(17)式で表わされる。

【0045】

この(17)式は、デジタル信号生成モジュールSG1の出力を表す。図4は(17)式で表される信号のスペクトルを表している。デジタル信号生成モジュールSG1の出力はD/A変換器5a,5bに与えられる。

【0046】

いま、(1)式の目的信号を得るために必要なD/A変換器5a,5bのサンプリング周波数がfsであるものとする。この場合には、(17)式の信号x12(n)をアナログ信号に変換するためのサンプリング周波数はfs/4でよい。

【0047】

ここで、D/A変換器5a,5bのホールド特性がデルタ関数で与えられるものとする。そうすると、D/A変換器5a,5bの出力は図5に示すものとなる。このD/A変換器5a,5bの出力はそれぞれバンドバスフィルタ6a,6bに与えられる。フィルタ6a,6bはそれぞれD/A変換器5a,5bの出力を帯域制限して90度ハイブリッド7に出力する。

【0048】

信号処理モジュールM1のフィルタ6a,6bの通過帯域を(3/8)fs〜fs/2に設定することにより、図6に示す出力が得られる。90度ハイブリッド7は、受動素子で構成されており、位相が90度異なる2つの入力信号を合成して出力する。

【0049】

他の信号処理モジュールM2〜M4についても同様である。即ち、図7に示すスペクトルX22(m)を総ポイント数N/4で逆離散フーリエ変換した結果をx22(n)とおけばx22(n)は式(18)で表わされる。

【0050】

この(18)式は、デジタル信号生成モジュールSG2の出力を表す。デジタル信号生成モジュールSG2の出力はD/A変換器5a,5bに与えられる。(18)式の信号x22(n)をアナログ信号に変換するためのサンプリング周波数をfs/4とし,DA変換器のホールド特性をデルタ関数とすれば、D/A変換器5a,5bの出力スペクトルは図8に示すものとなる。

【0051】

このD/A変換器5a,5bの出力はそれぞれバンドバスフィルタ6a,6bに与えられる。フィルタ6a,6bはそれぞれD/A変換器5a,5bの出力を帯域制限して90度ハイブリッド7に出力する。信号処理モジュールM2のフィルタ6a,6bの通過帯域を(1/4)fs〜(3/8)fsに設定することにより、図9に示す出力が得られる。

【0052】

同様に、図10に示すスペクトルX32(m)を総ポイント数N/4で逆離散フーリエ変換した結果をx32(n)とおけばx32(n)は式(19)で表わされる。

【0053】

この(19)式は、デジタル信号生成モジュールSG3の出力を表す。デジタル信号生成モジュールSG3の出力はD/A変換器5a,5bに与えられる。(19)式の信号x32(n)をアナログ信号に変換するためのサンプリング周波数をfs/4とし,DA変換器のホールド特性をデルタ関数とすれば、D/A変換器5a,5bの出力スペクトルは図11に示すものとなる。

【0054】

このD/A変換器5a,5bの出力はそれぞれバンドバスフィルタ6a,6bに与えられる。フィルタ6a,6bはそれぞれD/A変換器5a,5bの出力を帯域制限して90度ハイブリッド7に出力する。信号処理モジュールM3のフィルタ6a,6bの通過帯域を(1/8)fs〜(1/4)fsに設定することにより、図12に示す出力が得られる。

【0055】

同様に、図13に示すスペクトルX42(m)を総ポイント数N/4で逆離散フーリエ変換した結果をx42(n)とおけばx42(n)は式(20)で表わされる。

【0056】

この(20)式は、デジタル信号生成モジュールSG4の出力を表す。デジタル信号生成モジュールSG4の出力はD/A変換器5a,5bに与えられる。(20)式の信号x42(n)をアナログ信号に変換するためのサンプリング周波数をfs/4とし,DA変換器のホールド特性をデルタ関数とすれば、D/A変換器5a,5bの出力スペクトルは図14に示すものとなる。

【0057】

このD/A変換器5a,5bの出力はそれぞれフィルタ6a’,6b’に与えられる。フィルタ6a’,6b’はそれぞれD/A変換器5a,5bの出力を帯域制限して90度ハイブリッド7に出力する。信号処理モジュールM4のフィルタ6a’,6b’の通過帯域をDC〜(1/8)fsに設定することにより、図15に示す出力が得られる。

【0058】

最後に、混合器3において、図6、図9、図12及び図15にそれぞれ示す信号処理モジュールM1〜M4の出力を加算することで、図16に示す目的信号を定数倍した信号が得られる。

【0059】

このように本実施の形態においては、広帯域の目的信号を生成する場合に、目的信号を複数の周波数領域に分割し、分割した周波数成分を低域にシフトして処理することで、低いサンプリング周波数での処理を可能にする。そして、フィルタがアナログ信号への変換時に発生するイメージ信号を選択することで元の周波数帯域の信号に戻し、混合器がフィルタ出力を合成することにより目的信号を得る。元の周波数帯域の信号に戻すための直交変調器及び局部発振器は不要であり、これらの回路に代えてIQ軸の信号を合成する90度ハイブリッドを用いればよく、消費電力を低減させると共に、コスト増及び大型化を抑制することができる。

【0060】

図17は本発明の第2の実施の形態に係る任意信号発生装置を示すブロック図である。図17において図1と同一の構成要素には同一符号を付して説明を省略する。

【0061】

本実施の形態はD/A変換器5a,5bに代えてD/A変換器15a,15bを採用した点が第1の実施の形態と異なるのみである。

【0062】

本実施の形態においても上記図16に示すスペクトルを有する最高周波数がfs/2の実数の目的信号を生成するものとして説明する。

【0063】

コントローラ2は、総ポイント数Nの複素離散フーリエ変換処理によって得た目的信号の複素スペクトルのうち独立な半分のスペクトルをX1(m),X2(m),X3(m),X4(m)((12)〜(15)式)に均等分割する。これらのスペクトル又は(16-1)〜(16-4)式に示すX12(m),X22(m),X32(m),X42(m)をそれぞれ各信号処理モジュールM1〜M4に与える。各信号処理モジュールM1〜M4のデジタル信号生成モジュールSG1〜SG4は、それぞれスペクトルX12(m),X22(m),X32(m),X42(m)に対し総ポイント数がN/4の逆離散フーリエ変換を行う。

【0064】

これらのデジタル信号生成モジュールSG1〜SG4の出力はD/A変換器15a,15bに与えられる。デジタル信号生成モジュールSG1の出力信号は、上述したように、式(17)で表わされる。デジタル信号生成モジュールSG1は、式(17)で表わされる信号を、離散時間ステップTs'毎に出力する(ただしTs'=4・Ts ,Ts=1/fs)。図1のD/A変換器5a,5bのホールド特性がデルタ関数で表される場合には、D/A変換器5a,5bの出力信号x12(t)は、下記式(21)で表すことができる。また、この(21)式の波形は図18によって示すことができる。

【0065】

x12(t)のフーリエ変換値X12(f)は下記式(22)で示される。

【0066】

第1の実施の形態におけるD/A変換器5a,5bとしては、ホールド特性がデルタ関数となる理想的なD/A変換器を想定した。しかし、ホールド特性がデルタ関数のD/A変換器を構成することは実際には不可能である。そこで、本実施の形態は、D/A変換器15a,15bとして、出力が有限のホールド特性を有するD/A変換器を用いた例を説明する。

【0067】

例えば、D/A変換器15a,15bのホールド特性をg(t)とし,g(t)のフーリエ変換がG(f)で表わせるものとして検討を行う。このときD/A変換器15a,15bの出力信号をx13(t)とおけば、x13(t)は下記式(23)で表わされる。

【0068】

式(23)のフーリエ変換をX13(f)とおけば、X13(f)は式(24),(25)で表わされる。

【0069】

ここで、D/A変換器15a,15bのホールド特性を0次ホールド特性g1(t)で表わせば、g1(t)の波形は図19に示すものとなる。この場合には、D/A変換器15a,15bの出力信号x13(t)は図20に示すものとなる。

【0070】

この0次ホールド特性g1(t)のフーリエ変換G1(f)は、下記式(26)で表わされる。

式(26)の振幅成分|G1(f)|は下記式(27)で示される。この振幅成分|G1(f)|の波形を図21に示す。

【0071】

図21に示すように、振幅成分|G1(f)|は、周波数1/Ts'でヌルを有する。その結果、周波数1/Ts'近傍では避けられない大きな歪みが生じてしまう。よって1/Ts'近傍の信号は、任意信号発生器のスペクトル成分として有効に活用することができない。

【0072】

そこで、本実施の形態においてはD/A変換器15a,15bのホールド特性としてホールド特性g2(t)(以下、RZ特性ということもある)を採用する。図22はこのRZ特性を示している。

【0073】

RZ特性のD/A変換器15a,15bの出力信号は、図23に示すものとなる。そして、RZ特性g2(t)のフーリエ変換値G2(f)は下記式(28)で表わされる。

【0074】

またスペルトルの振幅|G2(f)|は下記式(29)で表わされる。図24は振幅|G2(f)|の波形を示す。

【0075】

信号処理モジュールM1のD/A変換器15a,15bの出力に対し、フィルタ6a,6bによって周波数3(fs/8)〜fs/2の成分を抽出すれば、フィルタ6a,6bの出力スペクトルは図25に示すものとなる。

【0076】

同様に、デジタル信号生成モジュールSG2の出力信号は、上記式(18)で表わされる。デジタル信号生成モジュールSG2は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM2内のD/A変換器15a,15bのホールド特性も図22に示すg2(t)とし、D/A変換器15a,15bの出力からフィルタ6a,6bで周波数fs/4〜3(fs/8)の成分を抽出すると、フィルタ出力は図26に示すスペクトルとなる。

【0077】

また、デジタル信号生成モジュールSG3の出力信号は、上記式(19)で表わされる。デジタル信号生成モジュールSG3は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM3内のD/A変換器15a,15bのホールド特性も図22に示すg2(t)とし、D/A変換器15a,15bの出力からフィルタ6a,6bで周波数fs/8〜fs/4の成分を抽出すると、フィルタ出力は図27に示すスペクトルとなる。

【0078】

また、デジタル信号生成モジュールSG4の出力信号は、上記式(20)で表わされる。デジタル信号生成モジュールSG4は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM4内のD/A変換器15a,15bのホールド特性も図22に示すg2(t)とし、D/A変換器15a,15bの出力からフィルタ6a’,6b’で周波数DC〜fs/8の成分を抽出すると、フィルタ出力は図28に示すスペクトルとなる。

【0079】

各信号処理モジュールM1〜M4の出力信号を混合器3により加算することにより、図29に示すスペクトルが得られる。

【0080】

このように本実施の形態においても、低いサンプリング周波数で広帯域の目的信号を生成する場合において、直交変調器及び局部発振器に代えて90度ハイブリッドを採用することができ、消費電力を低減させると共に、コスト増及び大型化を抑制することができる。また、本実施の形態においては、D/A変換器として実際に用いられるD/A変換器を採用した場合でも、確実に目的信号を生成することができる。

【0081】

なお、D/A変換器15a,15bにより、上記式(28)のsinc関数のスペクトルが上記式(17),(18),(19),(20)のスペクトルに乗算されており、各フィルタ6a,6b,6a’,6b’の出力スペクトルには歪みが生じている。

【0082】

このように、各信号処理モジュールM1〜M4が、平坦な通過特性を有していない場合には、各信号処理モジュールM1〜M4に与えるスペクトル情報の振幅を、コントローラ2によって補正したい量だけ加減することにより、各信号処理モジュールM1〜M4の通過特性を平坦にすることができる。

【0083】

更に、任意信号発生装置の外部に存在する伝送路の周波数特性が平坦でない場合には、各信号処理モジュールに設定するスペクトル情報にプリディストーション処理を施すことにより、伝送路の周波数特性を補正することも可能である。なお、プリディストーション処理は、予め逆特性の非線形歪を加えておくことで歪補償を行う非線形信号処理である。

【0084】

図30は本発明の第3の実施の形態に係る任意信号発生装置を示すブロック図である。図30において図17と同一の構成要素には同一符号を付して説明を省略する。

【0085】

本実施の形態はD/A変換器15a,15bに代えてD/A変換器25a,25bを採用すると共に、コントローラ2によってこれらのD/A変換器25a,25bを制御可能に構成した点が第2の実施の形態と異なる。

【0086】

本実施の形態においても上記図16に示すスペクトルを有する最高周波数がfs/2の実数の目的信号を生成するものとして説明する。

【0087】

本実施の形態におけるD/A変換器25a,25bは、図31に示すホールド特性g3(t)で動作することができる。なお、このホールド特性を以後MIX特性ともいう。このようなホールド特性を有するD/A変換器25a,25bの出力信号は図32に示すものとなる。ホールド特性g3(t)のフーリエ変換G3(f)は、下記式(30)で表わされる。

【0088】

また、フーリエ変換G3(f)の振幅|G3(f)|は下記式(31)によって示すことができる。図33はその波形を示している。

【0089】

本実施の形態においては、D/A変換器25a,25bは、MIX特性モードだけでなく、0ホールド特性モード、RZ特性モードを選択することができるようになっている。D/A変換器25a,25bは、コントローラ2によって制御されて、これらの特性のうちの1つを選択してD/A変換を行うようになっている。

【0090】

本実施の形態においても、コントローラ2は、総ポイント数Nの複素離散フーリエ変換処理によって得た目的信号のスペクトルのうち半分のスペクトルをX1(m),X2(m),X3(m),X4(m)((12)〜(15)式)に均等分割する。これらのスペクトル又は(16-1)〜(16-4)式に示すX12(m),X22(m),X32(m),X42(m)をそれぞれ各信号処理モジュールM1〜M4に与える。各信号処理モジュールM1〜M4のデジタル信号生成モジュールSG1〜SG4は、それぞれスペクトルX12(m),X22(m),X32(m),X42(m)に対し総ポイント数がN/4の逆離散フーリエ変換を行う。

【0091】

これらのデジタル信号生成モジュールSG1〜SG4の出力はD/A変換器25a,25bに与えられる。デジタル信号生成モジュールSG1の出力信号は、上述したように、式(17)で表わされる。デジタル信号生成モジュールSG1は、式(17)で表わされる信号を、離散時間ステップTs'毎に出力する(ただしTs'=4・Ts )。

【0092】

信号処理モジュールM1のD/A変換器25a,25bのホールド特性は、図31に示したホールド特性g3(t)であるものとする。この場合には、D/A変換器25a,25bの出力に対し、フィルタ6a,6bによって周波数3(fs/8)〜fs/2の成分を抽出すると、フィルタ6a,6bの出力スペクトルは図34に示すものとなる。

【0093】

同様に、デジタル信号生成モジュールSG2の出力信号は、上記式(18)で表わされる。デジタル信号生成モジュールSG2は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM2内のD/A変換器25a,25bのホールド特性も図31に示すg3(t)であるものとする。この場合には、D/A変換器25a,25bの出力からフィルタ6a,6bで周波数fs/4〜3(fs/8)の成分を抽出すると、フィルタ出力は図35に示すスペクトルとなる。

【0094】

また、デジタル信号生成モジュールSG3の出力信号は、上記式(19)で表わされる。デジタル信号生成モジュールSG3は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM3内のD/A変換器25a,25bのホールド特性も図31に示すg3(t)であるものとする。この場合には、D/A変換器25a,25bの出力からフィルタ6a,6bで周波数fs/8〜fs/4の成分を抽出すると、フィルタ出力は図36に示すスペクトルとなる。

【0095】

また、デジタル信号生成モジュールSG4の出力信号は、上記式(20)で表わされる。デジタル信号生成モジュールSG4は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。ここで、信号処理モジュールM4内のD/A変換器25a,25bのホールド特性が図31に示すg3(t)であるものとする。この場合においてD/A変換器25a,25bの出力からフィルタ6a’,6b’で周波数DC〜fs/8の成分を抽出すると、フィルタ出力は図37に示すスペクトルとなる。即ち、この場合には、DC近傍においてヌルが発生し、DC近傍では信号の欠落が生じてしまう。

【0096】

そこで、本実施の形態においては、コントローラ2は、信号処理モジュールM4内のD/A変換器25a,25bについては、例えばRZモードで動作させる。この場合には、D/A変換器25a,25bの出力からフィルタ6a’,6b’で周波数DC〜fs/8の成分を抽出すると、フィルタ出力は図28に示すスペクトルとなる。

【0097】

各信号処理モジュールM1〜M4の出力信号を混合器3により加算することにより、図38に示すスペクトルが得られる。

【0098】

このように本実施の形態においては、上記各実施の形態と同様の効果が得られると共に、各信号処理モジュールにおいて処理する帯域において、D/A変換器の出力が効率よく得られるモードを設定するようになっている。これにより、全ての帯域において目的信号に近似した波形を得ることができる。なお、本実施の形態においても、各帯域には若干の歪みが生じるが、例えば、コントローラ2の出力を各帯域の波形特性に応じて増減させることにより、等価的に通過特性を平坦にすることができる。

【0099】

なお、上記各実施の形態においては、目的信号の占有周波数帯域幅(DC〜fs/2)を均等に4分割して、サンプリング周波数がfs/4の4個のデジタル信号生成モジュールで分散処理する手法を説明したが、分割数は任意の自然数として構わない。また周波数帯域を不均等に分割しても構わない。サンプリング周波数もエイリアシングが生じない範囲で自由に決定して構わない。

【0100】

また、DA変換器のホールド特性は、0次ホールド特性,RZ特性,MIX特性に限らず、DA変換器から出力されるイメージ信号が効率的に得られるような任意の特性として構わない。

【0101】

なお、上記各実施の形態では各信号処理モジュールはそれぞれ互いに異なる周波数の信号を発生する、換言すればそれぞれ重なる周波数領域の信号を扱わないこととしているが、これに限られない。複数の信号処理モジュールで重複して扱う周波数領域が存在していても、それを考慮して目的信号を設定すればよい。

【0102】

また、目的信号の周波数帯域内に、出力を希望しない特定の周波数領域が存在している場合には、その特定の周波数領域をいずれの信号モジュールでも扱わないことで、特定の周波数領域の信号を含まない目的信号を得ることができる。例えば法規制等により出力を制限されている周波数領域が存在している場合に、その周波数領域を扱わないことで、法規制に対応した目的信号を得ることができる。

【0103】

また、上記各実施の形態の装置をレーダ送信信号の発生器として用いることにより、低いサンプリング周波数で動作する信号生成モジュールを効果的に並列動作させながら、ターゲットの特性、ターゲットの距離、測定分解能に応じて最適なレーダ送信信号を効果的に生成することができる。しかも、目的信号をデジタル信号処理を基本として生成するため、動作環境変化や経年変化による特性変化が小さく、送信波のスペクトルの形状やレベルを適応的に変更することのできるレーダ信号発生器等の任意信号発生装置を実現することができる。

【0104】

また、逆離散フーリエ変換にて信号生成を行うことは、直交周波数多重分割(Orthogonal Frequency Division Multiplexing)方式による変調と等価であるため、サブキャリアの一部若しくは全てを使ってデータ通信用の送信波を生成することができる。すなわち、上記各実施の形態の任意信号発生装置は、1つの信号発生装置でレーダ等の送信波とデータ通信のOFDM被変調波とを時分割方式で生成することができる。

【符号の説明】

【0105】

1 任意信号発生装置

2 コントローラ

3 混合器

4 スイッチ部

M1〜M4 信号処理モジュール

SG1〜SG4 デジタル信号生成モジュール

【技術分野】

【0001】

本発明は、広帯域の任意波形の目的信号を生成する任意信号発生装置に関する。

【背景技術】

【0002】

従来、パルスレーダ等に用いられるパルス幅の小さい信号を生成する技術として、ステップリカバリダイオード、アバランシェダイオード、高速論理ゲート等を用いて目的信号を生成する技術が知られている。これらの技術は、アナログ信号処理によりパルス幅の小さい信号を生成する技術であり、温度や湿度等の環境変化による回路特性の変化、素子や材料の特性の経年変化等により、性能が変化する虞がある。

【0003】

また、アナログ信号処理用の回路は、一度作成されると、その後の変更が困難であり、仕様や目的の変更に対して必ずしも自由度が高いとは言えない。例えば、レーダ用の信号発生装置としての用途の場合、レーダの割り当て周波数が変更されても、アナログ回路では対応困難である。さらに、送信波のスペクトルを変更する場合、外付けのフィルタを変更する等の対策が必要であるが、アナログ回路では、送信スペクトルの形状やレベルを適応的に変更することは困難である。

【0004】

このため、近年では、デジタル信号処理によって目的信号を生成する技術が採用されることが多い。このデジタル信号処理による信号発生装置としては、例えば特許文献1に開示されているようなダイレクトデジタルシンセサイザ(Direct Digital Synthesizer;DDS)が知られている。DDSは、波形データの入ったメモリの指定アドレスを更新して行き、その指定アドレスのデータをD/A変換によりアナログ波形に変換することで、任意の波形を発生させる技術である。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−225022号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に開示されているようなDDSによる信号発生装置は、基準クロック周波数に同期してその基準クロックの有理数倍の周期を有する信号波形をデジタル的に合成した後、D/A変換を行っている。よって、サンプリング定理により、目的信号に含まれる最高周波数の2倍以上のサンプリング周波数でD/A変換器を動作させなければならない。このため、目的信号のパルス幅を小さくすると、必要とされるサンプリング周波数がパルス幅に反比例して高くなる。よって、生成可能な信号の周波数には限界がある。

【0007】

本発明は上記事情に鑑みてなされたもので、比較的低い周波数のサンプリング周波数を用いつつ、生成する信号の周波数帯域を拡張することができ、より高周波域までの任意波形の信号を生成可能な任意信号発生装置を提供することを目的としている。

【課題を解決するための手段】

【0008】

本発明の一態様の任意信号発生装置は、広帯域の任意波形の目的信号を生成する任意信号発生装置であって、前記目的信号の所定の周波数領域毎の複素周波数信号がそれぞれ入力されて複素時間信号をそれぞれ生成する複数の信号生成部と、前記複数の信号生成部の出力をそれぞれアナログ信号に変換する複数のD/A変換器と、前記複数のD/A変換器の出力のうち各信号生成部に割り当てられた周波数領域に対応したイメージ信号をそれぞれ選択的に出力する複数のフィルタと、前記複数のフィルタからの各複素時間信号を夫々合成する複数の位相合成部と、前記複数の位相合成部の出力を合成して前記目的信号を出力する信号合成部とを備えることを特徴とする。

【発明の効果】

【0009】

本発明によれば、比較的低い周波数のサンプリング周波数を用いつつ、生成する信号の周波数帯域を拡張することができ、より高周波域までの任意波形の信号を生成することが可能となる。

【図面の簡単な説明】

【0010】

【図1】本発明の第1の実施の形態に係る任意信号発生装置を示すブロック図。

【図2】先願文献1,2における任意信号発生の基本アルゴリズムを示す説明図。

【図3】目的信号のスペクトルの一例を示す説明図。

【図4】デジタル信号生成モジュールSG1の出力に対応するスペクトルを示す説明図。

【図5】信号処理モジュールM1内のD/A変換器5a,5bの出力を示す説明図。

【図6】信号処理モジュールM1内のフィルタ6a,6bの出力を示す説明図。

【図7】デジタル信号生成モジュールSG2の出力に対応するスペクトルを示す説明図。

【図8】信号処理モジュールM2内のD/A変換器5a,5bの出力を示す説明図。

【図9】信号処理モジュールM2内のフィルタ6a,6bの出力を示す説明図。

【図10】デジタル信号生成モジュールSG3の出力に対応するスペクトルを示す説明図。

【図11】信号処理モジュールM3内のD/A変換器5a,5bの出力を示す説明図。

【図12】信号処理モジュールM3内のフィルタ6a,6bの出力を示す説明図。

【図13】デジタル信号生成モジュールSG4の出力に対応するスペクトルを示す説明図。

【図14】信号処理モジュールM4内のD/A変換器5a,5bの出力を示す説明図。

【図15】信号処理モジュールM4内のフィルタ6a’,6b’の出力を示す説明図。

【図16】混合器3の出力を示す説明図。

【図17】本発明の第2の実施の形態に係る任意信号発生装置を示すブロック図。

【図18】D/A変換器5a,5bの出力を示す説明図。

【図19】0次ホールド特性を示す説明図。

【図20】0次ホールド特性におけるD/A変換器15a,15bの出力を示す説明図。

【図21】0次ホールド特性におけるD/A変換器15a,15bの振幅特性を示す説明図。

【図22】RZ特性を示す説明図。

【図23】RZ特性におけるD/A変換器15a,15bの出力を示す説明図。

【図24】RZ特性におけるD/A変換器15a,15bの振幅特性を示す説明図。

【図25】信号処理モジュールM1内のフィルタ6a,6bの出力を示す説明図。

【図26】信号処理モジュールM2内のフィルタ6a,6bの出力を示す説明図。

【図27】信号処理モジュールM3内のフィルタ6a,6bの出力を示す説明図。

【図28】信号処理モジュールM4内のフィルタ6a’,6b’の出力を示す説明図。

【図29】混合器3の出力を示す説明図。

【図30】本発明の第3の実施の形態に係る任意信号発生装置を示すブロック図。

【図31】MIX特性を示す説明図。

【図32】MIX特性におけるD/A変換器25a,25bの出力を示す説明図。

【図33】MIX特性におけるD/A変換器25a,25bの振幅特性を示す説明図。

【図34】信号処理モジュールM1内のフィルタ6a,6bの出力を示す説明図。

【図35】信号処理モジュールM2内のフィルタ6a,6bの出力を示す説明図。

【図36】信号処理モジュールM3内のフィルタ6a,6bの出力を示す説明図。

【図37】MIX特性における信号処理モジュールM4内のフィルタ6a’,6b’の出力を示す説明図。

【図38】混合器3の出力を示す説明図。

【発明を実施するための形態】

【0011】

以下、図面を参照して本発明の実施の形態について詳細に説明する。図1は本発明の第1の実施の形態に係る任意信号発生装置を示すブロック図である。

【0012】

図1に示す任意信号発生装置1は、生成したい任意の周波数帯域の目的信号を時間領域で離散化した信号を用い、この信号をデジタル信号処理して実際の目的信号を生成する。従来のデジタル信号処理では、精度は高いが扱える周波数は比較的低いため、任意の広帯域の信号を処理することは難しい。本実施の形態においては、総ポイント数がNの任意の目的信号をデジタル信号処理が可能なP組の信号に分割して並列処理を行う。信号処理の都合上、P組に分割後の各組のポイント数は2のべき乗が好ましい。すなわちN/P=2a(aは任意の自然数)が好ましい。ただし、ゼロパディングによりポイント数を変更することは容易であることから、2のべき乗に限ることなく、任意の数で分割して処理することが可能である。

【0013】

ところで、本件出願人は、先に出願した特願2008−299937号明細書(以下、先願文献1という)及び特願2009−217484号明細書(以下、先願文献2という)において、このような並列処理を行う任意信号発生装置を既に提案している。先ず、図2を参照して先願文献1,2における任意信号発生の基本アルゴリズムについて説明する。

【0014】

図2に模式的に示すように、目的信号として時間的に連続したアナログ信号を想定し、このアナログ信号を離散化および離散フーリエ変換により周波数領域のスペクトルに変換し、その出力スペクトルを複数の成分に分割する。図2においては、A,B,C,Dの4つの成分に分割した例を示している。この4つの成分のうち、最も周波数の低いAの成分が直接的にデジタル信号処理の可能な周波数帯域である。

【0015】

成分Aの信号は、逆離散フーリエ変換し、D/A変換する。成分Bの信号は、成分Aの周波数帯域にシフトさせ、逆離散フーリエ変換し、D/A変換によりアナログ信号に変換し、更に、直交変調して周波数帯域を成分Aに隣接する高周波側にシフトする。同様に、成分Cの信号も、成分Aの周波数帯域にシフトさせ、逆離散フーリエ変換し、D/A変換によりアナログ信号に変換し、直交変調により周波数帯域を成分Bに隣接する高周波側にシフトする。同様に、成分Dの信号も、成分Aの周波数帯域にシフトさせ、逆離散フーリエ変換し、D/A変換によりアナログ信号に変換し、直交変調により周波数帯域を成分Cに続く高周波側にシフトする。最後に、アナログ信号に変換した成分Aの信号と、アナログ信号に変換して高周波側にシフトした成分B,C,Dの信号を合成することにより、目的信号と同様の信号を得ることができる。

【0016】

このことは、各成分毎に並列処理する複数の信号モジュールを用意し、各信号モジュールに目的信号の周波数領域の複素スペクトルを分割して与え、各信号モジュールでデジタル信号処理可能な成分を処理すると共に、デジタル信号処理の困難な高周波成分をアナログ信号処理で直交変調することにより、並列数Pに比例した広帯域の任意信号を生成(合成)できることを意味する。1つのモジュールで処理し得る周波数帯域幅をBwとするとき、生成可能な信号の周波数帯域は、Bw・Pとなる。つまり、処理し得る周波数帯域がBwである信号モジュールさえあれば、これを複数用意することで周波数帯域Bw・Pの目的信号を得ることができる。これにより、先願文献1,2における任意信号発生装置では、各モジュールのサンプリング周波数を比較的低い周波数に抑えつつ高い周波数の任意信号を生成することができる。

【0017】

ところが、先願文献1,2に開示した装置では、高い周波数の信号を扱う直交変調器及び局部発振器が必要であり消費電力が大きいという欠点がある。また、直交変調器及び局部発振器は比較的高価でしかもサイズが大きいので、コスト増及び大型化も招来してしまうという欠点もある。

【0018】

そこで、本実施の形態においては、D/A変換器のイメージ信号を利用することで、直交変調器及び局部発振器に代えて受動回路で構成される位相合成部としての90度ハイブリッドを採用することを可能にして、低消費電力、小型サイズ、低コストの任意信号発生器を実現する。

【0019】

本実施の形態においては、実時間の目的信号を離散化および離散フーリエ変換した結果得られるスペクトルのうち独立な周波数成分をP分割し、各周波数領域で信号処理を行うP個の信号処理モジュールを採用する。図1では、P=4の例を示している。即ち、信号処理モジュールM1,M2,M3,M4は、マイクロコンピュータ(CPU)を中心として構成されるコントローラ2から入力されるスペクトル情報(振幅、位相)に基づいて、それぞれ、周波数領域D,C,B,Aの信号を分割生成する。

【0020】

即ち、コントローラ2は、目的信号を離散フーリエ変換してD,C,B,Aの4つの周波数領域の信号成分に分割し、それぞれのスペクトル情報を、信号処理モジュールM1,M2,M3,M4に入力複素周波数信号として与える。各信号処理モジュールM1,M2,M3,M4は、フィルタ部を除いて同様の構成であり、それぞれ、コントローラ2からの離散データをデジタル信号処理するデジタル信号生成モジュールSG1,SG2,SG3,SG4を備えている。

【0021】

なおここでは処理の都合上、目的信号のスペクトルを低域から順にA,B,C,Dに分割し、それぞれ信号生成モジュールM4,M3,M2,M1で生成する例を示すが、分割信号と信号生成モジュールの対応はこれに限らない。

【0022】

各デジタル信号生成モジュールSG1,SG2,SG3,SG4は、ハードウェア実装、ソフトウェア実装、或いはハードウェア処理とソフトウェア処理の混在実装によって構成することができる。例えば、各デジタル信号生成モジュールSG1,SG2,SG3,SG4をハードウェアで構成する場合には、離散フーリエ変換された複素周波数信号を逆離散フーリエ変換する逆離散フーリエ変換器、逆離散フーリエ変換された並列データを直列データ(シリアルデータ)に変換する並直列変換器、並直列変換器の出力データを逓倍するインターポレータ、逓倍された信号から所望の周波数帯域のスペクトルを取り出す複素バンドパスフィルタ(複素BPF)、複素BPFからの出力を、I(In-Phase;同相成分)信号とQ(Quadrature;直交成分)信号とに分離するIQ分離器等によって構成することができる。

【0023】

各デジタル信号生成モジュールSG1〜SG4は、A〜Dの各領域の信号を低域に周波数シフトした複素時間信号を生成する。例えば、目的信号を図2のA〜Dの領域の信号に分割して処理するものとすると、デジタル信号生成モジュールSG1は、D領域のスペクトルを低域周波数にシフトしたときに得られる複素時間信号を生成する。また、デジタル信号生成モジュールSG2は、C領域のスペクトルを低域周波数にシフトしたときに得られる複素時間信号を生成する。また、デジタル信号生成モジュールSG3は、B領域のスペクトルを低域周波数にシフトしたときに得られる複素時間信号を生成し、デジタル信号生成モジュールSG4は、A領域のスペクトルを低域周波数にシフトしたときに得られる複素時間信号を生成する。

【0024】

各デジタル信号生成モジュールSG1〜SG4の出力は複素時間信号であり、その実数部と虚数部の信号をそれぞれD/A変換器5a,5bに与える。D/A変換器5a,5bは、デジタル信号生成モジュールSG1〜SG4の出力をアナログ信号に変換する。

【0025】

この場合において、D/A変換器5a,5bにおいて最低限必要とされるサンプリング周波数は、分割後の帯域幅と等しくなり、サンプリング周波数を分割数Pに反比例した値に低減することができる。D/A変換器5a,5bの出力はフィルタ6a,6b又は6a',6b'に与えられる。フィルタ6a,6bはバンドパスフィルタであり、フィルタ6a',6b'はローパスフィルタである。フィルタ6a,6b,6a',6b'は、入力されたアナログ信号を帯域制限する。

【0026】

本実施の形態においては、フィルタ6a,6b,6a’,6bは、D/A変換器5a,5bのD/A変換の際に生じるイメージ信号を取り出すようになっている。即ち、フィルタ6a,6b,6a’,6bは、D/A変換器5a,5bの出力からデジタル信号生成モジュールSG1〜SG4による周波数シフト前の帯域成分を取り出す。

【0027】

フィルタ6a,6b,6a’,6bの出力は、90度ハイブリッド7に供給される。90度ハイブリッド7は、受動素子で構成されており、位相が90度異なる2つの入力信号を合成して出力する。混合器3は、各信号処理モジュールM1,M2,M3,M4で生成された信号を合成してスイッチ部4に出力する。スイッチ部4は、例えば、FETやPINダイオード等の半導体デバイスを用いて構成され、コントローラ2により信号の通過と遮断が制御される。スイッチ部4は、合成信号の通過と遮断により、各モジュール間の信号生成処理時間の差や信号伝達時間の差による合成信号の歪みを除去した信号を得るようになっている。

【0028】

ただし、M4,M3,M2,M1の違いは、フィルタ部(6a,6b,6a',6b')の特性だけであるから、適切な通過帯域を持つフィルタを使用すれば、分割後の帯域と信号生成モジュールの対応関係は一意的ではない。

【0029】

次に、このように構成された実施の形態の動作について図3乃至図16を参照して説明する。ただし図中の*は共役複素数を表している。

【0030】

コントローラ2が設定する目的信号をx(n)とする。コントローラ2はこの目的信号x(n)を離散フーリエ変換して信号処理モジュールM1〜M4に与える。コントローラ2が目的信号x(n)を総ポイント数Nで離散フーリエ変換処理するものとし、この変換処理の結果スペクトルX(m)が得られるものとする。デジタル信号生成モジュールSG1〜SG4は、スペクトルX(m)を逆離散フーリエ変換してD/A変換器5a,5bに出力する。

【0031】

この処理を更に詳しく説明する。

x(n)とX(m)との関係は離散フーリエ変換対となり(1)式で表わすことができる。ただしnは離散時間インデックスを,mは離散周波数インデックスを表している。

【0032】

X(m)を(2)式のように振幅と位相に分解すれば、(1)式は(3)式のように表記できる。

【0033】

なお、x(n)とX(m)は周期Nの周期関数であるから以下の関係がある。

【0034】

x(n)=x(n±N)=x(n±2N)=x(n±3N)・・・

X(m)=X(m±N)=X(m±2N)=X(m±3N)・・・

さらにej(2π/N)mnはmとnに関して周期Nの周期関数である。

【0035】

まず、(3)式を直接IQ分離する場合を考える。

【0036】

IQ分離後の実数部出力xr(n)は次式で表わせる。

【0037】

xr(n)の離散フーリエ変換後のスペクトルをXr(m)とすれば、 Xr(m)=Xr1(m)+Xr2(m)となる。ただし

一方、(3)式にIQ分離を施した後の虚数部出力xi(n)は次式で表わせる。

【0038】

xi(n)の離散フーリエ変換後のスペクトルをXi(m)とすれば、 Xi(m)=Xi1(m)+Xi2(m)となる。ただし

Xr(m),Xi(m)をホールド特性がデルタ関数で表わされるD/A変換器5a,5bに入力した場合に得られるD/A変換器5a,5bの出力スペクトルはXr(m),Xi(m)のmを−∞〜+∞まで拡張したものとなる。

【0039】

次に、目的信号を周波数領域で4分割して、信号処理モジュールM1〜M4において処理する場合について説明する。いま、実数信号である目的信号x(n)を総ポイント数Nで複素離散フーリエ変換して得たスペクトルX(m)が図3で表わされる場合を考える。図3のA〜Dは、目的信号を周波数領域で4分割したことを示している。ただし簡略化のためにX(m)の振幅成分のみ図示してある。

【0040】

下記(10)式のN個の要素のうち前半のN/2個を除去したものを新たにX'(m)とおけば、X'(m)は下記(11)式で与えられる。

【0041】

X(m)={X(0),X(1),X(2),・・・,X(N-1)}…(10)

X'(m)={X(N/2),X(N/2+1),X(N/2+2),…,X(N-1)}…(11)

ここで、X'(m)の要素を4つに均等分割したものを頭から順にX1(m),X2(m),X3(m),X4(m)とおけば、X1(m),X2(m),X3(m),X4(m)はそれぞれ下記(12)式〜(15)式で与えられる。

【0042】

X1(m)={X(N/2),X(N/2+1),X(N/2+2),…X(N/2+N/8-1)}…(12)

X2(m)={X(N/2+N/8),X(N/2+N/8+1),X(N/2+N/8+2),…X(N/2+N/4-1)}…(13)

X3(m)={X(N/2+N/4),X(N/2+N/4+1),X(N/2+N/4+2),…X(N/2+3N/8-1)}…(14)

X4(m)={X(N/2+3N/8),X(N/2+3N/8+1),X(N/2+3N/8+2),…X(N-1)}…(15)

計算上の都合から、X1(m)のデータ列の後ろにゼロをN/8個だけ付加した配列をX12(m)とし,X2(m)のデータ列の前にゼロをN/8個だけ付加した配列を新たにX22(m)とし,X3(m)のデータ列の後ろにゼロをN/8個だけ付加した配列をX32(m)とし,X4(m)のデータ列の前にゼロをN/8個だけ付加した配列をX42(m)とおく。すると、下記(16-1)〜(16-4)式が得られる。

【0043】

X12(m)={X(N/2),X(N/2+1),X(N/2+2),…X(N/2+N/8-1),0,0,…,0}…(16-1)

X22(m)={0,0,…,0,X(N/2+N/8),X(N/2+N/8+1),X(N/2+N/8+2),…X(N/2+N/4-1)}…(16-2)

X32(m)={X(N/2+N/4),X(N/2+N/4+1),X(N/2+N/4+2),…X(N/2+3N/8-1),0,0,…,0}…(16-3)

X42(m)={0,0,…,0,X(N/2+N/4),X(N/2+N/4+1),X(N/2+N/4+2),…X(N/2+3N/8-1)}…(16-4)

これらのスペクトルX12(m),X22(m),X32(m),X42(m)がそれぞれデジタル信号生成モジュールSG1〜SG4に分配される。各デジタル信号生成モジュールSG1〜SG1は、それぞれ入力されたスペクトルを総ポイント数N/4で逆離散フーリエ変換する。

【0044】

X12(m)を総ポイント数N/4で逆離散フーリエ変換した結果をx12(n)とおけばx12(n)は下記(17)式で表わされる。

【0045】

この(17)式は、デジタル信号生成モジュールSG1の出力を表す。図4は(17)式で表される信号のスペクトルを表している。デジタル信号生成モジュールSG1の出力はD/A変換器5a,5bに与えられる。

【0046】

いま、(1)式の目的信号を得るために必要なD/A変換器5a,5bのサンプリング周波数がfsであるものとする。この場合には、(17)式の信号x12(n)をアナログ信号に変換するためのサンプリング周波数はfs/4でよい。

【0047】

ここで、D/A変換器5a,5bのホールド特性がデルタ関数で与えられるものとする。そうすると、D/A変換器5a,5bの出力は図5に示すものとなる。このD/A変換器5a,5bの出力はそれぞれバンドバスフィルタ6a,6bに与えられる。フィルタ6a,6bはそれぞれD/A変換器5a,5bの出力を帯域制限して90度ハイブリッド7に出力する。

【0048】

信号処理モジュールM1のフィルタ6a,6bの通過帯域を(3/8)fs〜fs/2に設定することにより、図6に示す出力が得られる。90度ハイブリッド7は、受動素子で構成されており、位相が90度異なる2つの入力信号を合成して出力する。

【0049】

他の信号処理モジュールM2〜M4についても同様である。即ち、図7に示すスペクトルX22(m)を総ポイント数N/4で逆離散フーリエ変換した結果をx22(n)とおけばx22(n)は式(18)で表わされる。

【0050】

この(18)式は、デジタル信号生成モジュールSG2の出力を表す。デジタル信号生成モジュールSG2の出力はD/A変換器5a,5bに与えられる。(18)式の信号x22(n)をアナログ信号に変換するためのサンプリング周波数をfs/4とし,DA変換器のホールド特性をデルタ関数とすれば、D/A変換器5a,5bの出力スペクトルは図8に示すものとなる。

【0051】

このD/A変換器5a,5bの出力はそれぞれバンドバスフィルタ6a,6bに与えられる。フィルタ6a,6bはそれぞれD/A変換器5a,5bの出力を帯域制限して90度ハイブリッド7に出力する。信号処理モジュールM2のフィルタ6a,6bの通過帯域を(1/4)fs〜(3/8)fsに設定することにより、図9に示す出力が得られる。

【0052】

同様に、図10に示すスペクトルX32(m)を総ポイント数N/4で逆離散フーリエ変換した結果をx32(n)とおけばx32(n)は式(19)で表わされる。

【0053】

この(19)式は、デジタル信号生成モジュールSG3の出力を表す。デジタル信号生成モジュールSG3の出力はD/A変換器5a,5bに与えられる。(19)式の信号x32(n)をアナログ信号に変換するためのサンプリング周波数をfs/4とし,DA変換器のホールド特性をデルタ関数とすれば、D/A変換器5a,5bの出力スペクトルは図11に示すものとなる。

【0054】

このD/A変換器5a,5bの出力はそれぞれバンドバスフィルタ6a,6bに与えられる。フィルタ6a,6bはそれぞれD/A変換器5a,5bの出力を帯域制限して90度ハイブリッド7に出力する。信号処理モジュールM3のフィルタ6a,6bの通過帯域を(1/8)fs〜(1/4)fsに設定することにより、図12に示す出力が得られる。

【0055】

同様に、図13に示すスペクトルX42(m)を総ポイント数N/4で逆離散フーリエ変換した結果をx42(n)とおけばx42(n)は式(20)で表わされる。

【0056】

この(20)式は、デジタル信号生成モジュールSG4の出力を表す。デジタル信号生成モジュールSG4の出力はD/A変換器5a,5bに与えられる。(20)式の信号x42(n)をアナログ信号に変換するためのサンプリング周波数をfs/4とし,DA変換器のホールド特性をデルタ関数とすれば、D/A変換器5a,5bの出力スペクトルは図14に示すものとなる。

【0057】

このD/A変換器5a,5bの出力はそれぞれフィルタ6a’,6b’に与えられる。フィルタ6a’,6b’はそれぞれD/A変換器5a,5bの出力を帯域制限して90度ハイブリッド7に出力する。信号処理モジュールM4のフィルタ6a’,6b’の通過帯域をDC〜(1/8)fsに設定することにより、図15に示す出力が得られる。

【0058】

最後に、混合器3において、図6、図9、図12及び図15にそれぞれ示す信号処理モジュールM1〜M4の出力を加算することで、図16に示す目的信号を定数倍した信号が得られる。

【0059】

このように本実施の形態においては、広帯域の目的信号を生成する場合に、目的信号を複数の周波数領域に分割し、分割した周波数成分を低域にシフトして処理することで、低いサンプリング周波数での処理を可能にする。そして、フィルタがアナログ信号への変換時に発生するイメージ信号を選択することで元の周波数帯域の信号に戻し、混合器がフィルタ出力を合成することにより目的信号を得る。元の周波数帯域の信号に戻すための直交変調器及び局部発振器は不要であり、これらの回路に代えてIQ軸の信号を合成する90度ハイブリッドを用いればよく、消費電力を低減させると共に、コスト増及び大型化を抑制することができる。

【0060】

図17は本発明の第2の実施の形態に係る任意信号発生装置を示すブロック図である。図17において図1と同一の構成要素には同一符号を付して説明を省略する。

【0061】

本実施の形態はD/A変換器5a,5bに代えてD/A変換器15a,15bを採用した点が第1の実施の形態と異なるのみである。

【0062】

本実施の形態においても上記図16に示すスペクトルを有する最高周波数がfs/2の実数の目的信号を生成するものとして説明する。

【0063】

コントローラ2は、総ポイント数Nの複素離散フーリエ変換処理によって得た目的信号の複素スペクトルのうち独立な半分のスペクトルをX1(m),X2(m),X3(m),X4(m)((12)〜(15)式)に均等分割する。これらのスペクトル又は(16-1)〜(16-4)式に示すX12(m),X22(m),X32(m),X42(m)をそれぞれ各信号処理モジュールM1〜M4に与える。各信号処理モジュールM1〜M4のデジタル信号生成モジュールSG1〜SG4は、それぞれスペクトルX12(m),X22(m),X32(m),X42(m)に対し総ポイント数がN/4の逆離散フーリエ変換を行う。

【0064】

これらのデジタル信号生成モジュールSG1〜SG4の出力はD/A変換器15a,15bに与えられる。デジタル信号生成モジュールSG1の出力信号は、上述したように、式(17)で表わされる。デジタル信号生成モジュールSG1は、式(17)で表わされる信号を、離散時間ステップTs'毎に出力する(ただしTs'=4・Ts ,Ts=1/fs)。図1のD/A変換器5a,5bのホールド特性がデルタ関数で表される場合には、D/A変換器5a,5bの出力信号x12(t)は、下記式(21)で表すことができる。また、この(21)式の波形は図18によって示すことができる。

【0065】

x12(t)のフーリエ変換値X12(f)は下記式(22)で示される。

【0066】

第1の実施の形態におけるD/A変換器5a,5bとしては、ホールド特性がデルタ関数となる理想的なD/A変換器を想定した。しかし、ホールド特性がデルタ関数のD/A変換器を構成することは実際には不可能である。そこで、本実施の形態は、D/A変換器15a,15bとして、出力が有限のホールド特性を有するD/A変換器を用いた例を説明する。

【0067】

例えば、D/A変換器15a,15bのホールド特性をg(t)とし,g(t)のフーリエ変換がG(f)で表わせるものとして検討を行う。このときD/A変換器15a,15bの出力信号をx13(t)とおけば、x13(t)は下記式(23)で表わされる。

【0068】

式(23)のフーリエ変換をX13(f)とおけば、X13(f)は式(24),(25)で表わされる。

【0069】

ここで、D/A変換器15a,15bのホールド特性を0次ホールド特性g1(t)で表わせば、g1(t)の波形は図19に示すものとなる。この場合には、D/A変換器15a,15bの出力信号x13(t)は図20に示すものとなる。

【0070】

この0次ホールド特性g1(t)のフーリエ変換G1(f)は、下記式(26)で表わされる。

式(26)の振幅成分|G1(f)|は下記式(27)で示される。この振幅成分|G1(f)|の波形を図21に示す。

【0071】

図21に示すように、振幅成分|G1(f)|は、周波数1/Ts'でヌルを有する。その結果、周波数1/Ts'近傍では避けられない大きな歪みが生じてしまう。よって1/Ts'近傍の信号は、任意信号発生器のスペクトル成分として有効に活用することができない。

【0072】

そこで、本実施の形態においてはD/A変換器15a,15bのホールド特性としてホールド特性g2(t)(以下、RZ特性ということもある)を採用する。図22はこのRZ特性を示している。

【0073】

RZ特性のD/A変換器15a,15bの出力信号は、図23に示すものとなる。そして、RZ特性g2(t)のフーリエ変換値G2(f)は下記式(28)で表わされる。

【0074】

またスペルトルの振幅|G2(f)|は下記式(29)で表わされる。図24は振幅|G2(f)|の波形を示す。

【0075】

信号処理モジュールM1のD/A変換器15a,15bの出力に対し、フィルタ6a,6bによって周波数3(fs/8)〜fs/2の成分を抽出すれば、フィルタ6a,6bの出力スペクトルは図25に示すものとなる。

【0076】

同様に、デジタル信号生成モジュールSG2の出力信号は、上記式(18)で表わされる。デジタル信号生成モジュールSG2は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM2内のD/A変換器15a,15bのホールド特性も図22に示すg2(t)とし、D/A変換器15a,15bの出力からフィルタ6a,6bで周波数fs/4〜3(fs/8)の成分を抽出すると、フィルタ出力は図26に示すスペクトルとなる。

【0077】

また、デジタル信号生成モジュールSG3の出力信号は、上記式(19)で表わされる。デジタル信号生成モジュールSG3は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM3内のD/A変換器15a,15bのホールド特性も図22に示すg2(t)とし、D/A変換器15a,15bの出力からフィルタ6a,6bで周波数fs/8〜fs/4の成分を抽出すると、フィルタ出力は図27に示すスペクトルとなる。

【0078】

また、デジタル信号生成モジュールSG4の出力信号は、上記式(20)で表わされる。デジタル信号生成モジュールSG4は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM4内のD/A変換器15a,15bのホールド特性も図22に示すg2(t)とし、D/A変換器15a,15bの出力からフィルタ6a’,6b’で周波数DC〜fs/8の成分を抽出すると、フィルタ出力は図28に示すスペクトルとなる。

【0079】

各信号処理モジュールM1〜M4の出力信号を混合器3により加算することにより、図29に示すスペクトルが得られる。

【0080】

このように本実施の形態においても、低いサンプリング周波数で広帯域の目的信号を生成する場合において、直交変調器及び局部発振器に代えて90度ハイブリッドを採用することができ、消費電力を低減させると共に、コスト増及び大型化を抑制することができる。また、本実施の形態においては、D/A変換器として実際に用いられるD/A変換器を採用した場合でも、確実に目的信号を生成することができる。

【0081】

なお、D/A変換器15a,15bにより、上記式(28)のsinc関数のスペクトルが上記式(17),(18),(19),(20)のスペクトルに乗算されており、各フィルタ6a,6b,6a’,6b’の出力スペクトルには歪みが生じている。

【0082】

このように、各信号処理モジュールM1〜M4が、平坦な通過特性を有していない場合には、各信号処理モジュールM1〜M4に与えるスペクトル情報の振幅を、コントローラ2によって補正したい量だけ加減することにより、各信号処理モジュールM1〜M4の通過特性を平坦にすることができる。

【0083】

更に、任意信号発生装置の外部に存在する伝送路の周波数特性が平坦でない場合には、各信号処理モジュールに設定するスペクトル情報にプリディストーション処理を施すことにより、伝送路の周波数特性を補正することも可能である。なお、プリディストーション処理は、予め逆特性の非線形歪を加えておくことで歪補償を行う非線形信号処理である。

【0084】

図30は本発明の第3の実施の形態に係る任意信号発生装置を示すブロック図である。図30において図17と同一の構成要素には同一符号を付して説明を省略する。

【0085】

本実施の形態はD/A変換器15a,15bに代えてD/A変換器25a,25bを採用すると共に、コントローラ2によってこれらのD/A変換器25a,25bを制御可能に構成した点が第2の実施の形態と異なる。

【0086】

本実施の形態においても上記図16に示すスペクトルを有する最高周波数がfs/2の実数の目的信号を生成するものとして説明する。

【0087】

本実施の形態におけるD/A変換器25a,25bは、図31に示すホールド特性g3(t)で動作することができる。なお、このホールド特性を以後MIX特性ともいう。このようなホールド特性を有するD/A変換器25a,25bの出力信号は図32に示すものとなる。ホールド特性g3(t)のフーリエ変換G3(f)は、下記式(30)で表わされる。

【0088】

また、フーリエ変換G3(f)の振幅|G3(f)|は下記式(31)によって示すことができる。図33はその波形を示している。

【0089】

本実施の形態においては、D/A変換器25a,25bは、MIX特性モードだけでなく、0ホールド特性モード、RZ特性モードを選択することができるようになっている。D/A変換器25a,25bは、コントローラ2によって制御されて、これらの特性のうちの1つを選択してD/A変換を行うようになっている。

【0090】

本実施の形態においても、コントローラ2は、総ポイント数Nの複素離散フーリエ変換処理によって得た目的信号のスペクトルのうち半分のスペクトルをX1(m),X2(m),X3(m),X4(m)((12)〜(15)式)に均等分割する。これらのスペクトル又は(16-1)〜(16-4)式に示すX12(m),X22(m),X32(m),X42(m)をそれぞれ各信号処理モジュールM1〜M4に与える。各信号処理モジュールM1〜M4のデジタル信号生成モジュールSG1〜SG4は、それぞれスペクトルX12(m),X22(m),X32(m),X42(m)に対し総ポイント数がN/4の逆離散フーリエ変換を行う。

【0091】

これらのデジタル信号生成モジュールSG1〜SG4の出力はD/A変換器25a,25bに与えられる。デジタル信号生成モジュールSG1の出力信号は、上述したように、式(17)で表わされる。デジタル信号生成モジュールSG1は、式(17)で表わされる信号を、離散時間ステップTs'毎に出力する(ただしTs'=4・Ts )。

【0092】

信号処理モジュールM1のD/A変換器25a,25bのホールド特性は、図31に示したホールド特性g3(t)であるものとする。この場合には、D/A変換器25a,25bの出力に対し、フィルタ6a,6bによって周波数3(fs/8)〜fs/2の成分を抽出すると、フィルタ6a,6bの出力スペクトルは図34に示すものとなる。

【0093】

同様に、デジタル信号生成モジュールSG2の出力信号は、上記式(18)で表わされる。デジタル信号生成モジュールSG2は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM2内のD/A変換器25a,25bのホールド特性も図31に示すg3(t)であるものとする。この場合には、D/A変換器25a,25bの出力からフィルタ6a,6bで周波数fs/4〜3(fs/8)の成分を抽出すると、フィルタ出力は図35に示すスペクトルとなる。

【0094】

また、デジタル信号生成モジュールSG3の出力信号は、上記式(19)で表わされる。デジタル信号生成モジュールSG3は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。信号処理モジュールM3内のD/A変換器25a,25bのホールド特性も図31に示すg3(t)であるものとする。この場合には、D/A変換器25a,25bの出力からフィルタ6a,6bで周波数fs/8〜fs/4の成分を抽出すると、フィルタ出力は図36に示すスペクトルとなる。

【0095】

また、デジタル信号生成モジュールSG4の出力信号は、上記式(20)で表わされる。デジタル信号生成モジュールSG4は離散時間ステップTs'毎に出力信号を出力する。ただしTs'=4・Tsである。ここで、信号処理モジュールM4内のD/A変換器25a,25bのホールド特性が図31に示すg3(t)であるものとする。この場合においてD/A変換器25a,25bの出力からフィルタ6a’,6b’で周波数DC〜fs/8の成分を抽出すると、フィルタ出力は図37に示すスペクトルとなる。即ち、この場合には、DC近傍においてヌルが発生し、DC近傍では信号の欠落が生じてしまう。

【0096】

そこで、本実施の形態においては、コントローラ2は、信号処理モジュールM4内のD/A変換器25a,25bについては、例えばRZモードで動作させる。この場合には、D/A変換器25a,25bの出力からフィルタ6a’,6b’で周波数DC〜fs/8の成分を抽出すると、フィルタ出力は図28に示すスペクトルとなる。

【0097】

各信号処理モジュールM1〜M4の出力信号を混合器3により加算することにより、図38に示すスペクトルが得られる。

【0098】

このように本実施の形態においては、上記各実施の形態と同様の効果が得られると共に、各信号処理モジュールにおいて処理する帯域において、D/A変換器の出力が効率よく得られるモードを設定するようになっている。これにより、全ての帯域において目的信号に近似した波形を得ることができる。なお、本実施の形態においても、各帯域には若干の歪みが生じるが、例えば、コントローラ2の出力を各帯域の波形特性に応じて増減させることにより、等価的に通過特性を平坦にすることができる。

【0099】

なお、上記各実施の形態においては、目的信号の占有周波数帯域幅(DC〜fs/2)を均等に4分割して、サンプリング周波数がfs/4の4個のデジタル信号生成モジュールで分散処理する手法を説明したが、分割数は任意の自然数として構わない。また周波数帯域を不均等に分割しても構わない。サンプリング周波数もエイリアシングが生じない範囲で自由に決定して構わない。

【0100】

また、DA変換器のホールド特性は、0次ホールド特性,RZ特性,MIX特性に限らず、DA変換器から出力されるイメージ信号が効率的に得られるような任意の特性として構わない。

【0101】

なお、上記各実施の形態では各信号処理モジュールはそれぞれ互いに異なる周波数の信号を発生する、換言すればそれぞれ重なる周波数領域の信号を扱わないこととしているが、これに限られない。複数の信号処理モジュールで重複して扱う周波数領域が存在していても、それを考慮して目的信号を設定すればよい。

【0102】

また、目的信号の周波数帯域内に、出力を希望しない特定の周波数領域が存在している場合には、その特定の周波数領域をいずれの信号モジュールでも扱わないことで、特定の周波数領域の信号を含まない目的信号を得ることができる。例えば法規制等により出力を制限されている周波数領域が存在している場合に、その周波数領域を扱わないことで、法規制に対応した目的信号を得ることができる。

【0103】

また、上記各実施の形態の装置をレーダ送信信号の発生器として用いることにより、低いサンプリング周波数で動作する信号生成モジュールを効果的に並列動作させながら、ターゲットの特性、ターゲットの距離、測定分解能に応じて最適なレーダ送信信号を効果的に生成することができる。しかも、目的信号をデジタル信号処理を基本として生成するため、動作環境変化や経年変化による特性変化が小さく、送信波のスペクトルの形状やレベルを適応的に変更することのできるレーダ信号発生器等の任意信号発生装置を実現することができる。

【0104】

また、逆離散フーリエ変換にて信号生成を行うことは、直交周波数多重分割(Orthogonal Frequency Division Multiplexing)方式による変調と等価であるため、サブキャリアの一部若しくは全てを使ってデータ通信用の送信波を生成することができる。すなわち、上記各実施の形態の任意信号発生装置は、1つの信号発生装置でレーダ等の送信波とデータ通信のOFDM被変調波とを時分割方式で生成することができる。

【符号の説明】

【0105】

1 任意信号発生装置

2 コントローラ

3 混合器

4 スイッチ部

M1〜M4 信号処理モジュール

SG1〜SG4 デジタル信号生成モジュール

【特許請求の範囲】

【請求項1】

広帯域の任意波形の目的信号を生成する任意信号発生装置であって、

前記目的信号の所定の周波数領域毎の複素周波数信号がそれぞれ入力されて複素時間信号をそれぞれ生成する複数の信号生成部と、

前記複数の信号生成部の出力をそれぞれアナログ信号に変換する複数のD/A変換器と、

前記複数のD/A変換器の出力のうち各信号生成部に割り当てられた周波数領域に対応したイメージ信号をそれぞれ選択的に出力する複数のフィルタと、

前記複数のフィルタからの各複素時間信号を夫々合成する複数の位相合成部と、

前記複数の位相合成部の出力を合成して前記目的信号を出力する信号合成部と

を備えることを特徴とする任意信号発生装置。

【請求項2】

前記複素周波数信号は、時間領域の信号を離散フーリエ変換して複数の周波数領域に分割した信号であることを特徴とする請求項1に記載の任意信号発生装置。

【請求項3】

前記複数のD/A変換器は、周波数領域毎に異なるホールド特性で動作する

ことを特徴とする請求項1又は2に記載の任意信号発生装置。

【請求項1】

広帯域の任意波形の目的信号を生成する任意信号発生装置であって、

前記目的信号の所定の周波数領域毎の複素周波数信号がそれぞれ入力されて複素時間信号をそれぞれ生成する複数の信号生成部と、

前記複数の信号生成部の出力をそれぞれアナログ信号に変換する複数のD/A変換器と、

前記複数のD/A変換器の出力のうち各信号生成部に割り当てられた周波数領域に対応したイメージ信号をそれぞれ選択的に出力する複数のフィルタと、

前記複数のフィルタからの各複素時間信号を夫々合成する複数の位相合成部と、

前記複数の位相合成部の出力を合成して前記目的信号を出力する信号合成部と

を備えることを特徴とする任意信号発生装置。

【請求項2】

前記複素周波数信号は、時間領域の信号を離散フーリエ変換して複数の周波数領域に分割した信号であることを特徴とする請求項1に記載の任意信号発生装置。

【請求項3】

前記複数のD/A変換器は、周波数領域毎に異なるホールド特性で動作する

ことを特徴とする請求項1又は2に記載の任意信号発生装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【公開番号】特開2012−13455(P2012−13455A)

【公開日】平成24年1月19日(2012.1.19)

【国際特許分類】

【出願番号】特願2010−148118(P2010−148118)

【出願日】平成22年6月29日(2010.6.29)

【出願人】(000005348)富士重工業株式会社 (3,010)

【Fターム(参考)】

【公開日】平成24年1月19日(2012.1.19)

【国際特許分類】

【出願日】平成22年6月29日(2010.6.29)

【出願人】(000005348)富士重工業株式会社 (3,010)

【Fターム(参考)】

[ Back to top ]