伝送線路及びこれを有する配線基板並びに半導体装置

【課題】 多ピン高速LSIと接続する配線基板において、伝送線路の断面構造を適切に制御することによって伝送損失を調整することができるようにする。

【解決手段】 異なる二つの配線層に一本ずつ信号配線を配置し上下に重ならないよう水平方向に一定距離ずらしてなる一対の差動ペアが多数形成された多層配線基板において、二本の信号配線の水平方向のずらし量をd、二本の信号配線を隔てる絶縁層の厚みをt、隣接する信号配線との配線周期、すなわち隣接差動配線との間隔と信号配線幅の和をpとした時、D=d(t/p3)1/2で表される値Dが0.2<D<1.2の範囲内に収まっている部分があることを特徴とする。

【解決手段】 異なる二つの配線層に一本ずつ信号配線を配置し上下に重ならないよう水平方向に一定距離ずらしてなる一対の差動ペアが多数形成された多層配線基板において、二本の信号配線の水平方向のずらし量をd、二本の信号配線を隔てる絶縁層の厚みをt、隣接する信号配線との配線周期、すなわち隣接差動配線との間隔と信号配線幅の和をpとした時、D=d(t/p3)1/2で表される値Dが0.2<D<1.2の範囲内に収まっている部分があることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、多数の高速信号を入出力する半導体素子を実装するための配線基板に関するものである。

【背景技術】

【0002】

近年のLSI(Large Scale Integrated circuit)の高速化に伴い、LSIを実装する配線基板での伝送線路における信号の減衰が問題になってきている。GHz級の速度の信号においては、表皮効果による信号減衰が増大し伝送波形の劣化が顕著になる。従って、低損失で良好な信号波形を保ちつつ高速信号を伝送できる伝送線路の実現が要求されている。

【0003】

また、LSIの高速化と同時にLSIの信号数の増大・基板接続パッドの微細化も進んでいる。すなわち、LSIの高機能化のためにLSIから入出力される信号が増加しているが、LSIの高機能化・低コスト化のためには外形サイズを小さくする必要があるため、基板接続パッド径とパッド間隔の微細化が進行している。その結果、LSIと接続する配線基板において、高密度で多信号を引き回せる伝送線路の実現が求められている。

【0004】

このように、LSIの高速化と多ピン化、微細化に対応するため、高速信号を低損失で伝送し、高密度で配線できる信号配線が要求されている。

【0005】

この要求に応えるため、二本の信号配線で一つの信号を伝送する差動伝送線路が提案されている。差動伝送線路は二本の信号配線を伝播してきた信号の差を一つの信号とするため、コモンモードノイズがキャンセル可能であり、振幅を二倍にできる利点を持つ。

【0006】

代表的な差動伝送線路構造としては、図25(a)に示すようなコプレーナ構造、図25(b)に示すようなマイクロストリップ構造、図25(c)に示すようなストリップ構造、図25(d)に示すようなタンデム構造、図25(e)に示すようなダイアゴナル構造、等がある。

【0007】

ダイアゴナル構造の差動伝送線路については、特許文献1においてLSI内の伝送線路に適用した例が示され、非特許文献1には配線基板に適用した例が示されている。ダイアゴナル構造は異なる配線層に信号配線を配置し、水平方向に一定距離ずらす、という構造をとる。この構造をとることにより、特に隣接配線とのクロストークを削減する効果が示されている。

【0008】

一方、高速信号を低損失で伝送するために、伝送線路だけでなく、それら伝送線路と接続するLSIを制御することも行われている。例えば、配線基板の信号線路で生じる伝送損失を補正するため、LSIの送信回路にプリエンファシスと呼ばれる波形補正回路を組み込むことが行われている。これは、一般のデジタル波形は矩形波をしており低周波から高周波までの広い周波数成分を含むが、伝送線路における損失量は高周波成分の方が大きいため、波形の立ち上がりが鈍くなって波形劣化が生じてしまう。この対策として、送信信号の高周波成分だけを増幅しておくことによって高周波成分の減衰量を予備補償しておき、伝送線路を伝播した後の信号の周波数スペクトルを理想的な分布に近づけて波形の立ち上がりを鋭くする手法がプリエンファシスである。一例として特許文献2には伝送線路の損失を実験やシミュレーションによって評価する手法が開示されており、送信信号にプリエンファシスを施した際の伝送波形を算出する例が示されている。また、その伝送線路における高周波成分の損失を予備補償する手法として、特許文献3には伝送損失に応答して送信側のドライバを適応的に制御する手法が開示されている。このように、伝送線路の伝播特性をあらかじめ評価した上でプリエンファシスの設定を決定することにより、最適な伝送波形を得ることができる。

【0009】

【特許文献1】特開2005−101587号公報

【特許文献2】特開2006−090788号公報

【特許文献3】特表2002−525977号公報

【非特許文献1】2006年電子情報通信学会総合大会論文集 p316「シフテッド・ペアライン信号線におけるクロストーク測定」

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかし、特許文献1と非特許文献1においては、ダイアゴナル構造の差動伝送線路の損失を小さく抑えるための明確な設計指針がなかった。

【0011】

一般に、伝送線路の伝播損失αは、単位長あたりの抵抗R、コンダクタンスG、特性インピーダンスZ0を用いて、以下の数式(1)によって表される。

【0012】

α=(1/2)(R/Z0)+(1/2)GZ0 (1)

数式(1)において、第一項が導体損失、第二項が誘電損失を表す。導体損失は伝送線路の導体の抵抗に起因する。特に高周波においては、電流は表皮効果によって導体の表面のみを流れるため電流の流れる断面積が小さくなり、導体損失が増加する。第二項の誘電損失は線路を構成する誘電体によるもので、誘電体の誘電正接tanδと周波数fに比例する。第二項のGは線路のキャパシタンスC、周波数f、絶縁体の誘電正接tanδを用いて以下の数式(2)によって表せる。

【0013】

G=2πfCtanδ (2)

一般に、信号線路の幅が広くなると、電流の通る断面積が広くなるため抵抗Rが減少して導体損失が減少するが、その一方でキャパシタンスCが増加するためコンダクタンスGが増加し、誘電損失が増加する。従って、信号線路の幅や間隔などの寸法と伝送損失との関係が明確ではなく、伝送損失を小さくするために一般的に当てはまる設計指針というものが存在しなかった。そして、実際の伝送線路の設計においては、伝送線路の終端抵抗と特性インピーダンスとが等しくなるように線路幅が決定され、伝送損失を小さくするために線路幅や線路間隔を変更する、ということは行われていなかった。

【0014】

また、特許文献2、3に開示されたような伝送線路の伝播特性をあらかじめ評価した上でプリエンファシスの設定を決定する方法については以下のような課題がある。LSIに設定されるプリエンファシスは配線の損失に応じて調整されるが、LSIに接続される多数の配線の長さは一定ではないため、配線によって損失の大きさにばらつきがある。従って、全ての配線に対する波形補正を同じ設定にすると、全ての信号に対して最適な補正を行うことができない。しかし、信号配線ごとに波形補正を調整することは、多信号を有するLSIにおいては多大のコストや工数を要してしまう。

【0015】

上記の問題に鑑み、本発明の目的は、多ピン高速LSIと接続する配線基板において、伝送線路の断面構造を適切に設計することによって伝送損失を調整することのできる差動伝送線路を実現することである。

【0016】

本発明はまた、上記の差動伝送線路を用いて、多信号を有するLSIと接続する際には全ての信号に対して等しい設定の波形補正を実施し、最適な補正を得ることのできる伝送線路を有する配線基板を提供しようとするものである。

【課題を解決するための手段】

【0017】

本発明によれば、異なる二つの配線層に一本ずつ信号配線を配置しこれら二本の信号配線を上下に重ならないよう水平方向に一定距離ずらしてなる一対の差動ペアが複数形成された多層配線基板において、前記二本の信号配線の水平方向のずらし量をd、前記二本の信号配線を隔てる絶縁層の厚みをt、隣接する信号配線との配線周期、すなわち隣接差動配線との間隔と信号配線幅の和をpとした時、D=d(t/p3)1/2で表される値Dが0.2<D<1.2の範囲内に収まっている部分があることを特徴とする伝送線路が提供される。

【0018】

上記の伝送線路においては、前記二つの配線層のさらに上または下あるいは上下両方の配線層にグラウンドプレーンまたは電源プレーンが形成されていても良い。

【0019】

上記の伝送線路においてはまた、前記隣接する信号配線との配線周期が位置によって異なっていることが望ましく、あるいはまた前記信号配線幅が位置によって異なっていても良い。

【0020】

本発明による配線基板は、異なる二つの配線層に一本ずつ信号配線を配置しこれら二本の信号配線を上下に重ならないよう水平方向に一定距離ずらしてなる一対の差動ペアが複数形成された多層配線基板において、前記二本の信号配線の水平方向のずらし量をd、前記二本の信号配線を隔てる絶縁層の厚みをt、隣接する信号配線との配線周期、すなわち隣接差動配線との間隔と信号配線幅の和をpとした時、D=d(t/p3)1/2で表される値Dが0.2<D<1.2の範囲内に収まっていることを特徴とする。以降、このDを規格化ずらし量と呼ぶ。

【0021】

また、前記差動ペアは前記配線基板上部に実装された半導体素子から離れるに従って隣接する差動ペアとの間隔を広げていることを特徴とする。この際、同時にずらし量を調整して特性インピーダンスを一定に保ちつつ、規格化ずらし量Dを0.2<D<1.2の範囲に保っていることを特徴とする。

【0022】

さらに、前記差動ペアは半導体素子から離れるに従って配線幅が太くなっていることを特徴とする。

【0023】

また、前記差動ペアを有する配線基板は、配線長の長い差動ペアと配線長の短い差動ペアとを有し、それらの差動ペアは配線基板上部に実装された半導体素子と接続されており、前記配線長の長い差動ペアのある地点における配線周期は、前記半導体素子から等しい距離における前記配線長の短い差動ペアの配線周期よりも広い部分があることを特徴とする。

【0024】

本発明によればまた、上記の配線基板に半導体素子または半導体パッケージを搭載してなる半導体装置が提供される。

【0025】

[発明の作用]

前記差動ペアは異なる二つの配線層に一本ずつ信号配線を配置し水平方向に一定距離ずらす構造をとる。この差動ペアの差動特性インピーダンスは、信号配線幅w、絶縁層厚みt、ずらし量d、配線周期p、絶縁層の誘電率εrによって一意に決まる。通常、絶縁層の誘電率と絶縁層厚みは基板の材質・種類によって決まり、配線周期は信号配線が接続される半導体素子のパッドピッチや基板のビアピッチ、基板の面積などの制約を受けてある程度決定される。残る二つの要素は信号配線幅wとずらし量dであるが、これら二つの要素にはある程度の自由度があり、この二つを変化させることによって差動特性インピーダンスを調整することができる。そして、ある値の差動特性インピーダンスは複数通りの信号配線幅・ずらし量の組み合わせによって実現することができる。すなわち、信号配線幅が広い場合にはずらし量も大きくし、信号配線幅が細い場合にはずらし量も小さくすることによって等しい差動特性インピーダンスを実現することができる。

【0026】

差動特性インピーダンスを一定に保ちつつ信号配線幅とずらし量を変化させる場合、ずらし量を小さくして信号配線幅を細くすると信号配線の断面積が小さくなってしまうため導体損失が大きくなってしまう。逆に、信号配線幅を太くしてずらし量を配線周期・絶縁層厚みに対して大きくすると、差動ペアを構成する信号配線同士の電界結合よりも隣接する信号配線との結合が強くなる。その結果、電流が信号配線の端部に集中して電流が通る断面積が小さくなってしまい、導体損失が大きくなる。従って、信号配線幅とずらし量は小さくしすぎても大きくしすぎても導体損失が大きくなってしまう。そこで、前述した規格化ずらし量Dを0.2<D<1.2の範囲内に収めることによって電流の通る断面積を広くすることができ、導体損失の小さい差動伝送線路を実現することができる。

【0027】

また、差動特性インピーダンスを一定に保ちつつ配線周期を広げると、ずらし量を小さくするか信号配線幅を広くするため、隣接配線との電磁界結合が小さくなって信号配線の側面よりも上下の面に電流が流れるようになり、導体損失を小さくすることができる。このように、配線周期を広げることによって伝送損失を小さくすることができる。

【発明の効果】

【0028】

本発明による伝送線路は伝送損失を小さくできるという効果を有し、この伝送線路を有する配線基板は、多数の信号配線(信号パッド)が高密度に形成された半導体素子から配線を引き出す場合にも、差動特性インピーダンスを一定に保ちつつ伝送損失を小さく抑えることができる。

【0029】

また、配線長の長い信号配線の単位長さ辺りの伝送損失を配線長の短い信号配線のそれよりも小さくすることにより、配線全体での伝送損失を同程度に揃えることができる。これにより、半導体素子に搭載された波形補正回路が同一の設定であったとしても、配線長が異なる複数の信号配線に対して最適な波形補正を行うことができ、回路規模の増大を抑制して低コストで半導体装置を提供することができる。

【発明を実施するための最良の形態】

【0030】

[第1の実施形態]

次に、本発明の第一の実施形態について図面を参照して説明する。

【0031】

[構造]

まず、構造について説明する。

【0032】

図1は本発明の第一の実施形態による半導体装置の斜視図であり、図2はその半導体装置の断面図である。この半導体装置においては、多層の配線基板1の上面に半導体集積回路素子2が搭載され、接続用導体3を介して他の回路と接続されている。

【0033】

この配線基板1は、第一の絶縁層1a、第二の絶縁層1b、第三の絶縁層1c、第四の絶縁層1dを積層して構成される。第一の絶縁層1aの上面には第一配線層5aが、第二の絶縁層1bの上面には第二配線層5bが、第三の絶縁層1cの上面には第三配線層5cが、第四の絶縁層1dの上面に第四配線層5d、下面に第五配線層5eがそれぞれ形成されている。第二配線層5bには信号配線4aが、第三配線層5cには信号配線5bがそれぞれ形成されており、それぞれの信号配線は層間接続用ビアを介して第五配線層5eに設けられたBGA(Ball Grid Array)ランド6と接続されるほか、配線基板上部の半導体素子2と接続されている。また、第一配線層5aにはグラウンド電極7が、第四配線層5dにはグラウンド電極8がそれぞれ設けられており、両者のグラウンド電極はいずれかの配線層において接続することで同電位としている。このグラウンド電極も信号配線と同様、層間接続ビアや接続用導体3を介して半導体素子2やBGAランド6に接続されている。

【0034】

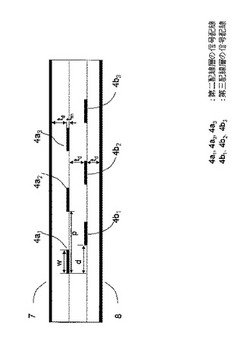

図3は図2のA−A’における配線基板1の断面図である。信号配線4a1と4b1、信号配線4a2と4b2、信号配線4a3と4b3がそれぞれ一対の差動ペアを構成している。この差動線路は、二つの信号配線が上下に隣接する配線層に配置されており、かつ水平方向に距離dずらして配置している。すなわち、信号配線4a1と4b1、信号配線4a2と4b2、信号配線4a3と4b3をそれぞれ距離dだけ水平方向にずらしている。そしてこれらの差動ペアを配線周期pの間隔で配置している。配線周期pというのは、同じ層における隣接差動配線との間隔であり、言い換えれば隣接差動配線との間隔と信号配線幅との和である。各配線の導体厚みはtm、絶縁層の厚みはtd、各信号配線4の幅はwである。

【0035】

ここで、配線周期p、ずらし量d、配線幅(線路幅)w、絶縁層厚みtdは、以下の数式(4)を満たす。

【0036】

D=d(td/p3)1/2=0.5 (4)

規格化ずらし量Dを0.2<D<1.2の範囲内に収めることによって、伝送損失の小さい伝送線路を提供することができる。この電気特性上の作用については、実施例を用いて後述する。

【0037】

次に、このパッケージ用基板の製造方法について述べる。図1の基板1は一般的に用いられている回路基板を使用する。例えば、有機材料(エポキシ、ポリイミド、フッ素樹脂、PPE樹脂、フェノール樹脂等)を使用した基板や、セラミック、ガラス、シリコン、コンポジット材などの絶縁材料を用いた基板を用いることができる。各層のパターニングの形成はエッチングや印刷等の技術を用いる。また層間接続ビアは、絶縁材料にレーザー照射やドリル加工によって穴を形成し、金属ペースト充填やめっき等によって導通させることによって形成する。

【0038】

[実施例1]

第一の実施形態に示した配線基板1を、比誘電率εr=3.1、誘電正接tanδ=0.023で実現した。この数値は、プリント基板の材料として広く用いられているエポキシ系樹脂の物性値である。絶縁層厚みtd=100μm、配線周期p=100μmの時に、配線幅wとずらし量dを変化させた時の差動特性インピーダンスZdiffを電磁界シミュレータで計算した。この結果を図4に示す。

【0039】

図4の計算結果から分かるように、配線幅wを固定してずらし量dを増加させると差動特性インピーダンスは上昇し、ずらし量dを固定して配線幅wを増加させると差動特性インピーダンスZdiffは減少する。差動ペアの差動特性インピーダンスZdiffの目標値を100Ωとする場合、配線幅wとずらし量dの組み合わせは表1に示すように複数の組み合わせで実現できる。

【0040】

【表1】

【0041】

同様にして配線周期pが75μm、150μmの場合についても、差動特性インピーダンスZdiffが100Ωになる配線幅wとずらし量dの組み合わせを電磁界シミュレーションによって求めた。そして、それらZdiff=100Ωになる場合の周波数10GHzにおける伝送損失αをシミュレーションによって求めた。このずらし量dと単位長さ辺りの伝送損失αとの関係を図5に示す。

【0042】

図5より、ずらし量dの変化に対して伝送損失αが極小点を持ち、それよりもずらし量が小さい場合でも大きい場合でも伝送損失が大きくなることが分かる。この理由に関する考察を以下に示す。

【0043】

図6はp=100μm、w=33μm、d=0μmの時の磁界分布、図7はp=100μm、w=46μm、d=82μmの時の磁界分布、図8はp=100μm、w=55μm、d=160μmの時の磁界分布である。シミュレーション結果によると、図7の構造の時が最も伝送損失が小さい。

【0044】

図6の構造の伝送線路はずらし量d=0μmで、磁界が差動ペアを構成する2本の信号配線の間に集中しており、電流は信号配線が向かい合う辺に分布している。それに対し、図7の伝送線路は信号配線の側面にも電流が分布しており、かつ図6の伝送路よりも配線幅wが広いため、電流の通る断面積が大きくなっている。

【0045】

図8の構造の伝送線路はさらに配線幅wとずらし量dを大きくしている。磁界は電流が通る信号配線と隣接する信号配線との間に集中しており、差動ペアの間には磁界結合がなく、またグラウンド電極との間の電磁界結合も弱い。このことは、電流が信号配線の横の辺に集中していることを示している。この結果、電流が通る経路の断面積が小さくなり、伝送損失が大きくなっている。

【0046】

このように、配線幅とずらし量が小さい場合には、電流が差動ペアの向かい合う辺だけに集中し、かつ配線幅が小さいため、電流の通る断面積が小さくなってしまう。逆にずらし量が配線周期や絶縁層厚みに対して大きい場合には、磁界の結合は隣接信号配線との間に集中し、電流は横の辺だけに分布してしまい、やはり電流の通る断面積が小さくなってしまう。このことは、電流経路の断面積は、信号配線が隣接する信号配線と結合しない範囲内でずらし量dと配線幅wを広げる時に最大になることを示している。すなわち、配線幅wとずらし量dを適切な値に設定することにより、電流が信号配線の差動ペアの向かい合う辺と横の辺両方に分布し、かつ配線幅wをある程度大きくすることができるため、電流の通る断面積を大きくすることができる。電流経路の断面積が大きければ抵抗が小さくなり、伝送損失を小さくすることができる。

【0047】

このずらし量dの適切な値は、図5から分かるように配線周期pによって変化する。これは、ずらし量dが一定でも配線周期pが大きければ隣接信号配線との結合量が小さくなり、差動ペアの信号線路同士の結合が大きくなって電流経路の断面積が大きくなるからである。また、適切なずらし量dは、絶縁層厚みtdと配線周期pの比p/tdによっても変化する。これは、配線周期pに対して絶縁層厚みtdが大きければ相対的な配線周期が小さくなり、相対的なずらし量が大きくなるからである。従って、最適なずらし量dは、配線周期pと、絶縁層厚みtdと配線周期pの比p/tdとに依存する。そこで、ずらし量dを配線周期pと(p/t)1/2で規格化した規格化ずらし量Dを、D=d(t/p3)1/2のように定義する。

【0048】

図9は、図5に示した伝送損失を規格化ずらし量Dに対してプロットしたグラフである。0.2<D<1.2の時に伝送損失が小さくなることから、規格化ずらし量Dがこの範囲内に収まるように配線周期p、絶縁層厚みtd、ずらし量dを選択することにより、電流経路の断面積が大きく抵抗の小さい、伝送損失の小さい伝送線路を提供することができる。

【0049】

配線周期p、絶縁層厚みtd、ずらし量d、配線幅wの値の例としては、p=100μm、td=100μm、d=82μm、w=46μmとすることによってD=0.82となり、0.2<D<1.2の範囲に収めることができる。また、絶縁層厚みが異なる場合の例としては、p=75μm、td=30μm、d=50μm、w=20μmとすることによってD=0.42となり、上記の範囲に収めることができる。これらの値の時に、伝送損失が極小となっている。

【0050】

[実施例2]

第一の実施形態に示した配線基板1を別の絶縁樹脂で実現した例として、比誘電率εr=4.0、誘電正接tanδ=0.006で実現した。この数値は、プリント基板の低損失材料として広く用いられているポリフェニレンエーテル(PPE)の物性値である。

【0051】

絶縁層厚みtd=100μmとし、配線周期p=75μm、100μm、150μm、200μmそれぞれの場合の差動特性インピーダンスZdiff=100Ωとなる配線幅wとずらし量dの組み合わせを電磁界シミュレーションによって求め、その際の伝送損失を計算した。

【0052】

規格化ずらし量Dに対する単位長さ辺りの伝送損失αを図10に示す。この結果から、規格化ずらし量Dが0.2<D<1.2の範囲内にある時に伝送損失が小さくなっていることが分かる。このことは、絶縁材料の比誘電率が変わっても最適な規格化ずらし量は変わらない、ということを示している。配線周期p、絶縁層厚みtd、ずらし量d、配線幅wの値の例としては、p=150μm、td=100μm、d=152μm、W=65μmとすることによってD=0.83となり、0.2<D<1.2の範囲に収めることができる。この時に、伝送損失の小さい伝送線路を実現することができる。

【0053】

[実施例3]

第一の実施形態に示した配線基板1を別の絶縁樹脂で実現した例として、比誘電率εr=2.0、誘電正接tanδ=0.0005で実現した。この数値は、フッ素樹脂材料として知られるテトラフルオロエチレン・ヘキサフルオロプロピレン共重合体(FEP)の物性値である。

【0054】

絶縁層厚みを実施例1、実施例2とは異なるtd=30μmとし、配線周期p=50μm、75μm、100μmの時に、差動特性インピーダンスZdiff=100Ωとなる配線幅wとずらし量dの組み合わせを電磁界シミュレーションによって求め、その際の伝送損失を計算した。

【0055】

規格化ずらし量Dに対する単位長さ辺りの伝送損失αを図11に示す。この結果から、規格化ずらし量が0.2<D<1.2の範囲内にある時に伝送損失αが小さくなっていることが分かる。配線周期p、絶縁層厚みtd、ずらし量d、配線幅wの値の例としては、p=100μm、td=30μm、d=90μm、w=40μmとすることによってD=0.83となり、0.2<D<1.2の範囲に収めることができる。この時、伝送損失の小さい伝送線路を実現することができる。

【0056】

[第二の実施形態]

次に、本発明の第二の実施形態について図面を参照して説明する。

【0057】

図12は図1に示す半導体装置の上面図であり、図2に示した各配線層の導体のうち信号配線4だけを示している。半導体素子2と接続された信号配線群4は半導体素子2を中心に放射状に広がっており、半導体素子2に近い領域では配線が密に配置されているが、半導体素子2から離れるに従って信号線路間の間隔が広がっていることが本実施形態の特徴である。

【0058】

図13(a)、図13(b)は、それぞれ図12におけるB−B’、C−C’での配線基板1の断面図である。信号配線4a1と4b1、信号配線4a2と4b2、信号配線4a3と4b3がそれぞれ一対の差動線路を構成している。この差動線路は、二つの信号配線が上下に隣接する配線層に配置されており、かつ水平方向にずらして配置している。各配線の導体厚みはtm、絶縁層の厚みはtd、信号配線4の幅はwで一定である。

【0059】

断面B−B’においては、差動線路間をpaの周期で配置し、差動線路を構成する二つの信号配線は水平方向にdaの距離ずらして配置している。すなわち、信号配線4a1と4b1、信号配線4a2と4b2、信号配線4a3と4b3をそれぞれ距離daだけ水平方向にずらしている。これに対し断面C−C’においては、差動線路間をpbの周期で配置し、差動線路を構成する二つの信号配線を水平方向に距離dbだけずらしている。ここで、da>db、pa<pbである。

【0060】

一般に線路の特性インピーダンスZは、信号線路のインダクタンスLと線路が周囲の導体との間に有するキャパシタンスをCとすると、以下の数式(5)によって表現される。

【0061】

Z=(L/C)1/2 (5)

ここで、インダクタンスLとキャパシタンスCは、配線幅w、差動内線路間隔d、絶縁層厚みtd、導体厚みtm、絶縁層の誘電率、周辺の導体との距離によって変化する。この実施形態は半導体素子2から離れるに従って差動線路の周期pが大きくなることが特徴であるが、周期pが増加するに従って線路のずらし量dを減少させることにより差動特性インピーダンスを一定に保っている。

【0062】

このように、差動特性インピーダンスを一定に保ちつつ配線周期を変化させることによって、半導体素子に近い領域では高密度に配線を行い、半導体素子から遠い領域では伝送損失の小さい差動伝送線路を提供することができる。そして、差動特性インピーダンスを一定に保っているので、不要な反射のない伝送線路を提供できる。配線周期が大きいと伝送損失が小さくなる理由については、実施例4で説明する。

【0063】

[実施例4]

第二の実施形態に示した配線基板1を比誘電率εr=3.1、誘電正接tanδ=0.023の樹脂基板で実現した。これは実施例1の基板と同一の物性値である。絶縁層厚みtdを100μmとし、配線周期pを75μm、100μm、150μmとして、差動特性インピーダンスが100Ωとなる配線幅wとずらし量dを電磁界シミュレーションによって求めた。それらの場合の伝送損失αを配線幅wに対してプロットした結果を図14に示す。配線幅wが一定でも配線周期pを大きくすることにより伝送損失αが減少することが分かる。

【0064】

今、配線幅wを35μmで一定とし、図13(a)の半導体素子に近い領域の配線周期paを75μm、ずらし量daを37μmとし、図13(b)の半導体素子から遠い領域の配線周期pbを25μm、ずらし量dbを25μmとする伝送路を構成した。電磁界シミュレーションによって求めた(p,d)=(75μm,37μm)の時の伝送損失αは0.741dB、(p,d)=(150μm,25μm)の時の伝送損失αは0.707dBであり、配線周期の大きい(p,d)=(150μm,25μm)の時の方が伝送損失は小さかった。

【0065】

それぞれの断面における磁界分布と伝送損失を電磁界シミュレーションによって求めた。図15はpa=75μmの断面の磁界分布、図16はpa=150μmの断面の磁界分布である。配線周期pが大きい場合(図16)には磁界が差動ペアの間に集中して分布し、隣接配線との間には磁界結合が見られない。一方、配線周期pが小さい場合(図15)には隣接配線との間にも磁界結合がみられる。このように、配線周期pを大きくすることによって、隣接配線との間の磁界結合を弱くすることができ、それによって伝送損失の小さい差動伝送線路を提供することができる。

【0066】

[第三の実施形態]

次に、第三の実施形態について図面を参照して説明する。

【0067】

図17(a)、図17(b)は、それぞれ図12におけるB−B’、C−C’での配線基板1の断面図である。第二の実施形態と同様、信号配線9a1と9b1、信号配線9a2と9b2、信号配線9a3と9b3がそれぞれ一対の差動線路を構成している。断面B−B’における差動線路のずらし量をda2、配線幅をwa2、差動線路間周期をpa2とし、断面C−C’における差動線路のずらし量をdb2、配線幅をwb2、差動線路間周期をpb2とする。ここで、da2>db2、pa2<pb2、wa2<wb2である。第二の実施形態と異なる点は、半導体素子2から離れるに従って配線幅が広くなっている点である。尚、ここではda2>db2としているが、da2とdb2の関係は配線周期p、配線幅wによって変化するので、da2<db2となる場合もある。

【0068】

図14から分かるように、配線周期pと配線幅wを適切に広げれば伝送損失αを小さくすることができる。伝送損失αは配線幅wの変化に対して極小点を持つので、規格化ずらし量Dが0.2<D<1.2になる範囲で配線幅wを広げることが望ましい。

【0069】

図18は信号配線9a1、9a2、9a3を上から見た図であり、半導体素子2から離れるに従って連続的に配線幅を広げている。また図19に示すように、各信号配線の配線幅を段階的に広げてもよい。

【0070】

このように、半導体素子から離れるに従って複数の信号配線の配線周期と配線幅を広げることによって、半導体素子に近い領域では高密度に配線を行い、半導体素子から遠い領域では伝送損失の小さい差動伝送線路を提供することができる。そして、差動特性インピーダンスを一定に保っているので、不要な反射のない伝送線路を提供できる。

【0071】

[実施例5]

第三の実施形態に示した配線基板1を比誘電率εr=3.1、誘電正接tanδ=0.023の樹脂基板で実現した。これは実施例1の基板と同一の物性値である。絶縁層厚みtd=30μmとし、図17(a)の半導体素子に近い領域では(p,w,d)=(50,20,60)、図17(b)の半導体素子から遠い領域では(p,w,d)=(75,25,80)とした。電磁界シミュレーションによって求めた(p,w,d)=(50,20,60)の時の伝送損失αは0.94dB、(p,w,d)=(75,25,80)の時の伝送損失αは0.87dBであり、配線幅と配線周期の広い場合の方が伝送損失は小さくなった。

【0072】

[第四の実施形態]

次に、本発明の第四の実施形態について説明する。図20は本実施形態の半導体装置の上面図である。多層の配線基板11の上部中央に半導体素子10が実装されており、配線基板11に設けられた信号配線が半導体素子10から放射状に広がっている。配線基板11は正方形であり、一部の信号配線12はその正方形の各辺の中央部に向かって引き回され、別の信号配線13は正方形の角に向かって引き回されている。従って、信号配線13の方が信号配線12よりも配線長が長い。伝送線路の構造が同一の場合、信号配線の配線長が長くなると伝送損失が大きくなるが、本実施形態の配線基板は下記の構造をとることによって信号配線12と信号配線13の伝送損失をほぼ等しい値にしている。

【0073】

図21は図20の曲線D−D’における断面図である。図21(a)は信号配線12付近の断面図であり、図21(b)は信号配線13付近の断面図である。なお、曲線D−D’上の各点は半導体素子10からの配線長が等しい。図21において、信号配線12の配線幅、差動配線間周期、ずらし量をそれぞれwD1、pD1、dD1とし、また信号配線13の配線幅、差動配線間周期、ずらし量をそれぞれwD2、pD2、dD2とする。

【0074】

曲線D−D’上の点は半導体素子10からの配線長が等しいが、ここでは信号配線12と13の配線幅、差動配線間周期を同一とはせず、pD1<pD2、wD1<wD2とし、差動特性インピーダンスを100Ωにするためにずらし量を調整し、dD1<dD2としている。

【0075】

このように、基板内に配線長の長い信号配線と短い信号配線が存在する場合、配線長の長い信号配線の差動配線間周期と配線幅を広くすることにより、配線長の長い信号配線の単位長さ辺りの伝送損失を小さくすることができる。従って、長い信号配線の配線全体の伝送損失を、配線長の短い信号配線の全体の伝送損失とほぼ等しくすることができる。

【0076】

[第五の実施形態]

次に、本発明の第五の実施形態について説明する。図22は本実施形態の半導体装置の断面図である。多層の配線基板14の上面中央に半導体素子10が、上面端部には半導体モジュール17がそれぞれ実装されている。配線基板14は上から順に第一〜第五の配線層14a、14b、14c、14d、14eからなり、第二配線層14bに信号配線15が、第三配線層14cに信号配線16がそれぞれ形成され、半導体素子10と半導体モジュール17とを接続している。信号配線15と16が一組でダイアゴナル配線を形成している。

【0077】

図23は本実施形態の半導体装置の上面図である。配線基板14の上面中央に半導体素子10が実装され、その周囲に複数の半導体モジュール17(例えば17a、17b)が配置されている。半導体素子10から信号配線が放射状に広がっており、半導体モジュール17との間で高速信号を伝送している。配線基板14は正方形に近い形状をしており、正方形の角に近い位置に実装された半導体モジュール17bと半導体素子10との距離は比較的長く、正方形の各辺の中央に近い位置に実装された半導体モジュール17aと半導体素子10との距離は比較的短い。そして、半導体モジュール17aと接続される信号配線の配線周期は、半導体モジュール17bと接続される信号配線の配線周期よりも狭くなっている。

【0078】

図24は図23の曲線E−E’における配線基板の断面図である。曲線E−E’上の各点は、半導体素子10からの配線長が等しい。図24(a)は半導体モジュール17aと接続される信号配線15a、16aの断面図であり、図25(b)は半導体モジュール17bと接続される信号配線15b、16bの断面図である。信号配線15a、16aの配線幅、ずらし量、配線周期をそれぞれwEa、dEa、pEaとし、信号配線15b、16bの配線幅、ずらし量、配線周期をそれぞれwEb、dEb、pEbとする。ここで、差動ペア(a15a、16a)と(a15b、16b)の配線幅、差動配線周期を同一とはせず、pEa<pEb、wEa<wEbとし、差動特性インピーダンスを100Ωにするためにずらし量を調整し、dEa<dEbとしている。この結果、差動ペア(a15a、16a)は差動ペア(a15b、16b)と比較して、配線長が短く、単位長さ辺りの伝送損失が大きい。

【0079】

このように、配線基板14上に半導体素子10と複数の半導体モジュール17を実装し、それぞれの半導体モジュールから半導体素子10までの距離が異なる場合、半導体素子10から遠い半導体モジュールと接続する信号配線の差動配線間周期と配線幅を広くして単位長さ辺りの伝送損失を小さくすることにより、配線長が長いことによる伝送損失の増大を相殺することができ、信号配線全体の伝送損失を等しくすることができる。その結果、信号配線の伝送損失を予備補償するプリエンファシスのような波形補正機能が半導体素子10に搭載されている場合、全ての信号配線に対するプリエンファシスの設定を単一にしても、全ての信号配線に対して最適な波形補正を施すことができる。

【0080】

半導体モジュール17の例としては、LSIなどの半導体素子、半導体素子を基板に実装した半導体パッケージ、光電気変換素子を基板上に実装した光モジュールなどが挙げられる。

【図面の簡単な説明】

【0081】

【図1】図1は、本発明の第一の実施形態による半導体装置の斜視図である。

【図2】図2は、図1の半導体装置の断面図である。

【図3】図3は、図2の配線基板のA−A’による断面図である。

【図4】図4は、第一の実施形態において実施例1の配線基板の材料を用いたダイアゴナル線路のずらし量と差動特性インピーダンスの関係を示すグラフ図である。

【図5】図5は、実施例1の配線基板の材料を用いたダイアゴナル線路の差動特性インピーダンス100Ωにおけるずらし量と伝送損失との関係を示すグラフ図である。

【図6】図6は、実施例1の配線基板の材料を用いたダイアゴナル線路のp=100μm、w=33μm、d=0μmの時の磁界分布を示した図である。

【図7】図7は、実施例1の配線基板の材料を用いたダイアゴナル線路のp=100μm、w=46μm、d=82μmの時の磁界分布を示した図である。

【図8】図8は、実施例1の配線基板の材料を用いたダイアゴナル線路のp=100μm、w=55μm、d=160μmの時の磁界分布を示した図である。

【図9】図9は、実施例1の配線基板の材料を用いたダイアゴナル線路の差動特性インピーダンス100Ωにおける規格化ずらし量と伝送損失との関係を示すグラフ図である。

【図10】図10は、実施例2の配線基板の材料を用いたダイアゴナル線路の差動特性インピーダンス100Ωにおける規格化ずらし量と伝送損失との関係を示すグラフ図である。

【図11】図11は、実施例3の配線基板の材料を用いたダイアゴナル線路の差動特性インピーダンス100Ωにおける規格化ずらし量と伝送損失との関係を示すグラフ図である。

【図12】図12は、第二の実施形態による半導体装置の上面図である。

【図13】図13(a)、(b)は、第二の実施形態における図12の配線基板のB−B’、C−C’における断面図である。

【図14】図14は、実施例4の配線基板を用いたダイアゴナル線路の配線幅と伝送損失との関係を示すグラフ図である。

【図15】図15は、図13(a)の断面における磁界分布を示した図である。

【図16】図16は、図13(b)の断面における磁界分布を示した図である。

【図17】図17(a)、(b)は、第三の実施形態の図12におけるB−B’、C−C’での配線基板の断面図である。

【図18】図18は、第三の実施形態による配線基板の伝送線路の一例を部分的に示す上面図である。

【図19】図19は、第三の実施形態による配線基板の伝送線路の別の例を部分的に示す上面図である。

【図20】図20は、第四の実施形態による半導体装置の上面図である。

【図21】図21(a)、(b)は、図20の配線基板のD−D’における断面図である。

【図22】図22は、第五の実施形態による半導体装置の断面図である。

【図23】図23は、第五の実施形態による半導体装置の上面図である。

【図24】図24(a)、(b)は、図23の配線基板のE−E’における断面図である。

【図25】従来の代表的な差動伝送線路構造の断面図である。

【符号の説明】

【0082】

1、11、14:配線基板

1a:第一の絶縁層

1b:第二の絶縁層

1c:第三の絶縁層

1d:第四の絶縁層

2、10:半導体素子

3:接続用導体

4a1、4a2、4a3、9a1、9a2、9a3:第二配線層の信号配線

4b1、4b2、4b3、9b1、9b2、9b3:第三配線層の信号配線

5a、14a:第一配線層

5b、14b:第二配線層

5c、14c:第三配線層

5d、14d:第四配線層

5e、14e:第五配線層

6:BGAランド

7、8:グラウンド電極

12:配線長の短い信号配線

13:配線長の長い信号配線

15:第二配線層の信号配線

16:第三配線層の信号配線

17:半導体モジュール

【技術分野】

【0001】

本発明は、多数の高速信号を入出力する半導体素子を実装するための配線基板に関するものである。

【背景技術】

【0002】

近年のLSI(Large Scale Integrated circuit)の高速化に伴い、LSIを実装する配線基板での伝送線路における信号の減衰が問題になってきている。GHz級の速度の信号においては、表皮効果による信号減衰が増大し伝送波形の劣化が顕著になる。従って、低損失で良好な信号波形を保ちつつ高速信号を伝送できる伝送線路の実現が要求されている。

【0003】

また、LSIの高速化と同時にLSIの信号数の増大・基板接続パッドの微細化も進んでいる。すなわち、LSIの高機能化のためにLSIから入出力される信号が増加しているが、LSIの高機能化・低コスト化のためには外形サイズを小さくする必要があるため、基板接続パッド径とパッド間隔の微細化が進行している。その結果、LSIと接続する配線基板において、高密度で多信号を引き回せる伝送線路の実現が求められている。

【0004】

このように、LSIの高速化と多ピン化、微細化に対応するため、高速信号を低損失で伝送し、高密度で配線できる信号配線が要求されている。

【0005】

この要求に応えるため、二本の信号配線で一つの信号を伝送する差動伝送線路が提案されている。差動伝送線路は二本の信号配線を伝播してきた信号の差を一つの信号とするため、コモンモードノイズがキャンセル可能であり、振幅を二倍にできる利点を持つ。

【0006】

代表的な差動伝送線路構造としては、図25(a)に示すようなコプレーナ構造、図25(b)に示すようなマイクロストリップ構造、図25(c)に示すようなストリップ構造、図25(d)に示すようなタンデム構造、図25(e)に示すようなダイアゴナル構造、等がある。

【0007】

ダイアゴナル構造の差動伝送線路については、特許文献1においてLSI内の伝送線路に適用した例が示され、非特許文献1には配線基板に適用した例が示されている。ダイアゴナル構造は異なる配線層に信号配線を配置し、水平方向に一定距離ずらす、という構造をとる。この構造をとることにより、特に隣接配線とのクロストークを削減する効果が示されている。

【0008】

一方、高速信号を低損失で伝送するために、伝送線路だけでなく、それら伝送線路と接続するLSIを制御することも行われている。例えば、配線基板の信号線路で生じる伝送損失を補正するため、LSIの送信回路にプリエンファシスと呼ばれる波形補正回路を組み込むことが行われている。これは、一般のデジタル波形は矩形波をしており低周波から高周波までの広い周波数成分を含むが、伝送線路における損失量は高周波成分の方が大きいため、波形の立ち上がりが鈍くなって波形劣化が生じてしまう。この対策として、送信信号の高周波成分だけを増幅しておくことによって高周波成分の減衰量を予備補償しておき、伝送線路を伝播した後の信号の周波数スペクトルを理想的な分布に近づけて波形の立ち上がりを鋭くする手法がプリエンファシスである。一例として特許文献2には伝送線路の損失を実験やシミュレーションによって評価する手法が開示されており、送信信号にプリエンファシスを施した際の伝送波形を算出する例が示されている。また、その伝送線路における高周波成分の損失を予備補償する手法として、特許文献3には伝送損失に応答して送信側のドライバを適応的に制御する手法が開示されている。このように、伝送線路の伝播特性をあらかじめ評価した上でプリエンファシスの設定を決定することにより、最適な伝送波形を得ることができる。

【0009】

【特許文献1】特開2005−101587号公報

【特許文献2】特開2006−090788号公報

【特許文献3】特表2002−525977号公報

【非特許文献1】2006年電子情報通信学会総合大会論文集 p316「シフテッド・ペアライン信号線におけるクロストーク測定」

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかし、特許文献1と非特許文献1においては、ダイアゴナル構造の差動伝送線路の損失を小さく抑えるための明確な設計指針がなかった。

【0011】

一般に、伝送線路の伝播損失αは、単位長あたりの抵抗R、コンダクタンスG、特性インピーダンスZ0を用いて、以下の数式(1)によって表される。

【0012】

α=(1/2)(R/Z0)+(1/2)GZ0 (1)

数式(1)において、第一項が導体損失、第二項が誘電損失を表す。導体損失は伝送線路の導体の抵抗に起因する。特に高周波においては、電流は表皮効果によって導体の表面のみを流れるため電流の流れる断面積が小さくなり、導体損失が増加する。第二項の誘電損失は線路を構成する誘電体によるもので、誘電体の誘電正接tanδと周波数fに比例する。第二項のGは線路のキャパシタンスC、周波数f、絶縁体の誘電正接tanδを用いて以下の数式(2)によって表せる。

【0013】

G=2πfCtanδ (2)

一般に、信号線路の幅が広くなると、電流の通る断面積が広くなるため抵抗Rが減少して導体損失が減少するが、その一方でキャパシタンスCが増加するためコンダクタンスGが増加し、誘電損失が増加する。従って、信号線路の幅や間隔などの寸法と伝送損失との関係が明確ではなく、伝送損失を小さくするために一般的に当てはまる設計指針というものが存在しなかった。そして、実際の伝送線路の設計においては、伝送線路の終端抵抗と特性インピーダンスとが等しくなるように線路幅が決定され、伝送損失を小さくするために線路幅や線路間隔を変更する、ということは行われていなかった。

【0014】

また、特許文献2、3に開示されたような伝送線路の伝播特性をあらかじめ評価した上でプリエンファシスの設定を決定する方法については以下のような課題がある。LSIに設定されるプリエンファシスは配線の損失に応じて調整されるが、LSIに接続される多数の配線の長さは一定ではないため、配線によって損失の大きさにばらつきがある。従って、全ての配線に対する波形補正を同じ設定にすると、全ての信号に対して最適な補正を行うことができない。しかし、信号配線ごとに波形補正を調整することは、多信号を有するLSIにおいては多大のコストや工数を要してしまう。

【0015】

上記の問題に鑑み、本発明の目的は、多ピン高速LSIと接続する配線基板において、伝送線路の断面構造を適切に設計することによって伝送損失を調整することのできる差動伝送線路を実現することである。

【0016】

本発明はまた、上記の差動伝送線路を用いて、多信号を有するLSIと接続する際には全ての信号に対して等しい設定の波形補正を実施し、最適な補正を得ることのできる伝送線路を有する配線基板を提供しようとするものである。

【課題を解決するための手段】

【0017】

本発明によれば、異なる二つの配線層に一本ずつ信号配線を配置しこれら二本の信号配線を上下に重ならないよう水平方向に一定距離ずらしてなる一対の差動ペアが複数形成された多層配線基板において、前記二本の信号配線の水平方向のずらし量をd、前記二本の信号配線を隔てる絶縁層の厚みをt、隣接する信号配線との配線周期、すなわち隣接差動配線との間隔と信号配線幅の和をpとした時、D=d(t/p3)1/2で表される値Dが0.2<D<1.2の範囲内に収まっている部分があることを特徴とする伝送線路が提供される。

【0018】

上記の伝送線路においては、前記二つの配線層のさらに上または下あるいは上下両方の配線層にグラウンドプレーンまたは電源プレーンが形成されていても良い。

【0019】

上記の伝送線路においてはまた、前記隣接する信号配線との配線周期が位置によって異なっていることが望ましく、あるいはまた前記信号配線幅が位置によって異なっていても良い。

【0020】

本発明による配線基板は、異なる二つの配線層に一本ずつ信号配線を配置しこれら二本の信号配線を上下に重ならないよう水平方向に一定距離ずらしてなる一対の差動ペアが複数形成された多層配線基板において、前記二本の信号配線の水平方向のずらし量をd、前記二本の信号配線を隔てる絶縁層の厚みをt、隣接する信号配線との配線周期、すなわち隣接差動配線との間隔と信号配線幅の和をpとした時、D=d(t/p3)1/2で表される値Dが0.2<D<1.2の範囲内に収まっていることを特徴とする。以降、このDを規格化ずらし量と呼ぶ。

【0021】

また、前記差動ペアは前記配線基板上部に実装された半導体素子から離れるに従って隣接する差動ペアとの間隔を広げていることを特徴とする。この際、同時にずらし量を調整して特性インピーダンスを一定に保ちつつ、規格化ずらし量Dを0.2<D<1.2の範囲に保っていることを特徴とする。

【0022】

さらに、前記差動ペアは半導体素子から離れるに従って配線幅が太くなっていることを特徴とする。

【0023】

また、前記差動ペアを有する配線基板は、配線長の長い差動ペアと配線長の短い差動ペアとを有し、それらの差動ペアは配線基板上部に実装された半導体素子と接続されており、前記配線長の長い差動ペアのある地点における配線周期は、前記半導体素子から等しい距離における前記配線長の短い差動ペアの配線周期よりも広い部分があることを特徴とする。

【0024】

本発明によればまた、上記の配線基板に半導体素子または半導体パッケージを搭載してなる半導体装置が提供される。

【0025】

[発明の作用]

前記差動ペアは異なる二つの配線層に一本ずつ信号配線を配置し水平方向に一定距離ずらす構造をとる。この差動ペアの差動特性インピーダンスは、信号配線幅w、絶縁層厚みt、ずらし量d、配線周期p、絶縁層の誘電率εrによって一意に決まる。通常、絶縁層の誘電率と絶縁層厚みは基板の材質・種類によって決まり、配線周期は信号配線が接続される半導体素子のパッドピッチや基板のビアピッチ、基板の面積などの制約を受けてある程度決定される。残る二つの要素は信号配線幅wとずらし量dであるが、これら二つの要素にはある程度の自由度があり、この二つを変化させることによって差動特性インピーダンスを調整することができる。そして、ある値の差動特性インピーダンスは複数通りの信号配線幅・ずらし量の組み合わせによって実現することができる。すなわち、信号配線幅が広い場合にはずらし量も大きくし、信号配線幅が細い場合にはずらし量も小さくすることによって等しい差動特性インピーダンスを実現することができる。

【0026】

差動特性インピーダンスを一定に保ちつつ信号配線幅とずらし量を変化させる場合、ずらし量を小さくして信号配線幅を細くすると信号配線の断面積が小さくなってしまうため導体損失が大きくなってしまう。逆に、信号配線幅を太くしてずらし量を配線周期・絶縁層厚みに対して大きくすると、差動ペアを構成する信号配線同士の電界結合よりも隣接する信号配線との結合が強くなる。その結果、電流が信号配線の端部に集中して電流が通る断面積が小さくなってしまい、導体損失が大きくなる。従って、信号配線幅とずらし量は小さくしすぎても大きくしすぎても導体損失が大きくなってしまう。そこで、前述した規格化ずらし量Dを0.2<D<1.2の範囲内に収めることによって電流の通る断面積を広くすることができ、導体損失の小さい差動伝送線路を実現することができる。

【0027】

また、差動特性インピーダンスを一定に保ちつつ配線周期を広げると、ずらし量を小さくするか信号配線幅を広くするため、隣接配線との電磁界結合が小さくなって信号配線の側面よりも上下の面に電流が流れるようになり、導体損失を小さくすることができる。このように、配線周期を広げることによって伝送損失を小さくすることができる。

【発明の効果】

【0028】

本発明による伝送線路は伝送損失を小さくできるという効果を有し、この伝送線路を有する配線基板は、多数の信号配線(信号パッド)が高密度に形成された半導体素子から配線を引き出す場合にも、差動特性インピーダンスを一定に保ちつつ伝送損失を小さく抑えることができる。

【0029】

また、配線長の長い信号配線の単位長さ辺りの伝送損失を配線長の短い信号配線のそれよりも小さくすることにより、配線全体での伝送損失を同程度に揃えることができる。これにより、半導体素子に搭載された波形補正回路が同一の設定であったとしても、配線長が異なる複数の信号配線に対して最適な波形補正を行うことができ、回路規模の増大を抑制して低コストで半導体装置を提供することができる。

【発明を実施するための最良の形態】

【0030】

[第1の実施形態]

次に、本発明の第一の実施形態について図面を参照して説明する。

【0031】

[構造]

まず、構造について説明する。

【0032】

図1は本発明の第一の実施形態による半導体装置の斜視図であり、図2はその半導体装置の断面図である。この半導体装置においては、多層の配線基板1の上面に半導体集積回路素子2が搭載され、接続用導体3を介して他の回路と接続されている。

【0033】

この配線基板1は、第一の絶縁層1a、第二の絶縁層1b、第三の絶縁層1c、第四の絶縁層1dを積層して構成される。第一の絶縁層1aの上面には第一配線層5aが、第二の絶縁層1bの上面には第二配線層5bが、第三の絶縁層1cの上面には第三配線層5cが、第四の絶縁層1dの上面に第四配線層5d、下面に第五配線層5eがそれぞれ形成されている。第二配線層5bには信号配線4aが、第三配線層5cには信号配線5bがそれぞれ形成されており、それぞれの信号配線は層間接続用ビアを介して第五配線層5eに設けられたBGA(Ball Grid Array)ランド6と接続されるほか、配線基板上部の半導体素子2と接続されている。また、第一配線層5aにはグラウンド電極7が、第四配線層5dにはグラウンド電極8がそれぞれ設けられており、両者のグラウンド電極はいずれかの配線層において接続することで同電位としている。このグラウンド電極も信号配線と同様、層間接続ビアや接続用導体3を介して半導体素子2やBGAランド6に接続されている。

【0034】

図3は図2のA−A’における配線基板1の断面図である。信号配線4a1と4b1、信号配線4a2と4b2、信号配線4a3と4b3がそれぞれ一対の差動ペアを構成している。この差動線路は、二つの信号配線が上下に隣接する配線層に配置されており、かつ水平方向に距離dずらして配置している。すなわち、信号配線4a1と4b1、信号配線4a2と4b2、信号配線4a3と4b3をそれぞれ距離dだけ水平方向にずらしている。そしてこれらの差動ペアを配線周期pの間隔で配置している。配線周期pというのは、同じ層における隣接差動配線との間隔であり、言い換えれば隣接差動配線との間隔と信号配線幅との和である。各配線の導体厚みはtm、絶縁層の厚みはtd、各信号配線4の幅はwである。

【0035】

ここで、配線周期p、ずらし量d、配線幅(線路幅)w、絶縁層厚みtdは、以下の数式(4)を満たす。

【0036】

D=d(td/p3)1/2=0.5 (4)

規格化ずらし量Dを0.2<D<1.2の範囲内に収めることによって、伝送損失の小さい伝送線路を提供することができる。この電気特性上の作用については、実施例を用いて後述する。

【0037】

次に、このパッケージ用基板の製造方法について述べる。図1の基板1は一般的に用いられている回路基板を使用する。例えば、有機材料(エポキシ、ポリイミド、フッ素樹脂、PPE樹脂、フェノール樹脂等)を使用した基板や、セラミック、ガラス、シリコン、コンポジット材などの絶縁材料を用いた基板を用いることができる。各層のパターニングの形成はエッチングや印刷等の技術を用いる。また層間接続ビアは、絶縁材料にレーザー照射やドリル加工によって穴を形成し、金属ペースト充填やめっき等によって導通させることによって形成する。

【0038】

[実施例1]

第一の実施形態に示した配線基板1を、比誘電率εr=3.1、誘電正接tanδ=0.023で実現した。この数値は、プリント基板の材料として広く用いられているエポキシ系樹脂の物性値である。絶縁層厚みtd=100μm、配線周期p=100μmの時に、配線幅wとずらし量dを変化させた時の差動特性インピーダンスZdiffを電磁界シミュレータで計算した。この結果を図4に示す。

【0039】

図4の計算結果から分かるように、配線幅wを固定してずらし量dを増加させると差動特性インピーダンスは上昇し、ずらし量dを固定して配線幅wを増加させると差動特性インピーダンスZdiffは減少する。差動ペアの差動特性インピーダンスZdiffの目標値を100Ωとする場合、配線幅wとずらし量dの組み合わせは表1に示すように複数の組み合わせで実現できる。

【0040】

【表1】

【0041】

同様にして配線周期pが75μm、150μmの場合についても、差動特性インピーダンスZdiffが100Ωになる配線幅wとずらし量dの組み合わせを電磁界シミュレーションによって求めた。そして、それらZdiff=100Ωになる場合の周波数10GHzにおける伝送損失αをシミュレーションによって求めた。このずらし量dと単位長さ辺りの伝送損失αとの関係を図5に示す。

【0042】

図5より、ずらし量dの変化に対して伝送損失αが極小点を持ち、それよりもずらし量が小さい場合でも大きい場合でも伝送損失が大きくなることが分かる。この理由に関する考察を以下に示す。

【0043】

図6はp=100μm、w=33μm、d=0μmの時の磁界分布、図7はp=100μm、w=46μm、d=82μmの時の磁界分布、図8はp=100μm、w=55μm、d=160μmの時の磁界分布である。シミュレーション結果によると、図7の構造の時が最も伝送損失が小さい。

【0044】

図6の構造の伝送線路はずらし量d=0μmで、磁界が差動ペアを構成する2本の信号配線の間に集中しており、電流は信号配線が向かい合う辺に分布している。それに対し、図7の伝送線路は信号配線の側面にも電流が分布しており、かつ図6の伝送路よりも配線幅wが広いため、電流の通る断面積が大きくなっている。

【0045】

図8の構造の伝送線路はさらに配線幅wとずらし量dを大きくしている。磁界は電流が通る信号配線と隣接する信号配線との間に集中しており、差動ペアの間には磁界結合がなく、またグラウンド電極との間の電磁界結合も弱い。このことは、電流が信号配線の横の辺に集中していることを示している。この結果、電流が通る経路の断面積が小さくなり、伝送損失が大きくなっている。

【0046】

このように、配線幅とずらし量が小さい場合には、電流が差動ペアの向かい合う辺だけに集中し、かつ配線幅が小さいため、電流の通る断面積が小さくなってしまう。逆にずらし量が配線周期や絶縁層厚みに対して大きい場合には、磁界の結合は隣接信号配線との間に集中し、電流は横の辺だけに分布してしまい、やはり電流の通る断面積が小さくなってしまう。このことは、電流経路の断面積は、信号配線が隣接する信号配線と結合しない範囲内でずらし量dと配線幅wを広げる時に最大になることを示している。すなわち、配線幅wとずらし量dを適切な値に設定することにより、電流が信号配線の差動ペアの向かい合う辺と横の辺両方に分布し、かつ配線幅wをある程度大きくすることができるため、電流の通る断面積を大きくすることができる。電流経路の断面積が大きければ抵抗が小さくなり、伝送損失を小さくすることができる。

【0047】

このずらし量dの適切な値は、図5から分かるように配線周期pによって変化する。これは、ずらし量dが一定でも配線周期pが大きければ隣接信号配線との結合量が小さくなり、差動ペアの信号線路同士の結合が大きくなって電流経路の断面積が大きくなるからである。また、適切なずらし量dは、絶縁層厚みtdと配線周期pの比p/tdによっても変化する。これは、配線周期pに対して絶縁層厚みtdが大きければ相対的な配線周期が小さくなり、相対的なずらし量が大きくなるからである。従って、最適なずらし量dは、配線周期pと、絶縁層厚みtdと配線周期pの比p/tdとに依存する。そこで、ずらし量dを配線周期pと(p/t)1/2で規格化した規格化ずらし量Dを、D=d(t/p3)1/2のように定義する。

【0048】

図9は、図5に示した伝送損失を規格化ずらし量Dに対してプロットしたグラフである。0.2<D<1.2の時に伝送損失が小さくなることから、規格化ずらし量Dがこの範囲内に収まるように配線周期p、絶縁層厚みtd、ずらし量dを選択することにより、電流経路の断面積が大きく抵抗の小さい、伝送損失の小さい伝送線路を提供することができる。

【0049】

配線周期p、絶縁層厚みtd、ずらし量d、配線幅wの値の例としては、p=100μm、td=100μm、d=82μm、w=46μmとすることによってD=0.82となり、0.2<D<1.2の範囲に収めることができる。また、絶縁層厚みが異なる場合の例としては、p=75μm、td=30μm、d=50μm、w=20μmとすることによってD=0.42となり、上記の範囲に収めることができる。これらの値の時に、伝送損失が極小となっている。

【0050】

[実施例2]

第一の実施形態に示した配線基板1を別の絶縁樹脂で実現した例として、比誘電率εr=4.0、誘電正接tanδ=0.006で実現した。この数値は、プリント基板の低損失材料として広く用いられているポリフェニレンエーテル(PPE)の物性値である。

【0051】

絶縁層厚みtd=100μmとし、配線周期p=75μm、100μm、150μm、200μmそれぞれの場合の差動特性インピーダンスZdiff=100Ωとなる配線幅wとずらし量dの組み合わせを電磁界シミュレーションによって求め、その際の伝送損失を計算した。

【0052】

規格化ずらし量Dに対する単位長さ辺りの伝送損失αを図10に示す。この結果から、規格化ずらし量Dが0.2<D<1.2の範囲内にある時に伝送損失が小さくなっていることが分かる。このことは、絶縁材料の比誘電率が変わっても最適な規格化ずらし量は変わらない、ということを示している。配線周期p、絶縁層厚みtd、ずらし量d、配線幅wの値の例としては、p=150μm、td=100μm、d=152μm、W=65μmとすることによってD=0.83となり、0.2<D<1.2の範囲に収めることができる。この時に、伝送損失の小さい伝送線路を実現することができる。

【0053】

[実施例3]

第一の実施形態に示した配線基板1を別の絶縁樹脂で実現した例として、比誘電率εr=2.0、誘電正接tanδ=0.0005で実現した。この数値は、フッ素樹脂材料として知られるテトラフルオロエチレン・ヘキサフルオロプロピレン共重合体(FEP)の物性値である。

【0054】

絶縁層厚みを実施例1、実施例2とは異なるtd=30μmとし、配線周期p=50μm、75μm、100μmの時に、差動特性インピーダンスZdiff=100Ωとなる配線幅wとずらし量dの組み合わせを電磁界シミュレーションによって求め、その際の伝送損失を計算した。

【0055】

規格化ずらし量Dに対する単位長さ辺りの伝送損失αを図11に示す。この結果から、規格化ずらし量が0.2<D<1.2の範囲内にある時に伝送損失αが小さくなっていることが分かる。配線周期p、絶縁層厚みtd、ずらし量d、配線幅wの値の例としては、p=100μm、td=30μm、d=90μm、w=40μmとすることによってD=0.83となり、0.2<D<1.2の範囲に収めることができる。この時、伝送損失の小さい伝送線路を実現することができる。

【0056】

[第二の実施形態]

次に、本発明の第二の実施形態について図面を参照して説明する。

【0057】

図12は図1に示す半導体装置の上面図であり、図2に示した各配線層の導体のうち信号配線4だけを示している。半導体素子2と接続された信号配線群4は半導体素子2を中心に放射状に広がっており、半導体素子2に近い領域では配線が密に配置されているが、半導体素子2から離れるに従って信号線路間の間隔が広がっていることが本実施形態の特徴である。

【0058】

図13(a)、図13(b)は、それぞれ図12におけるB−B’、C−C’での配線基板1の断面図である。信号配線4a1と4b1、信号配線4a2と4b2、信号配線4a3と4b3がそれぞれ一対の差動線路を構成している。この差動線路は、二つの信号配線が上下に隣接する配線層に配置されており、かつ水平方向にずらして配置している。各配線の導体厚みはtm、絶縁層の厚みはtd、信号配線4の幅はwで一定である。

【0059】

断面B−B’においては、差動線路間をpaの周期で配置し、差動線路を構成する二つの信号配線は水平方向にdaの距離ずらして配置している。すなわち、信号配線4a1と4b1、信号配線4a2と4b2、信号配線4a3と4b3をそれぞれ距離daだけ水平方向にずらしている。これに対し断面C−C’においては、差動線路間をpbの周期で配置し、差動線路を構成する二つの信号配線を水平方向に距離dbだけずらしている。ここで、da>db、pa<pbである。

【0060】

一般に線路の特性インピーダンスZは、信号線路のインダクタンスLと線路が周囲の導体との間に有するキャパシタンスをCとすると、以下の数式(5)によって表現される。

【0061】

Z=(L/C)1/2 (5)

ここで、インダクタンスLとキャパシタンスCは、配線幅w、差動内線路間隔d、絶縁層厚みtd、導体厚みtm、絶縁層の誘電率、周辺の導体との距離によって変化する。この実施形態は半導体素子2から離れるに従って差動線路の周期pが大きくなることが特徴であるが、周期pが増加するに従って線路のずらし量dを減少させることにより差動特性インピーダンスを一定に保っている。

【0062】

このように、差動特性インピーダンスを一定に保ちつつ配線周期を変化させることによって、半導体素子に近い領域では高密度に配線を行い、半導体素子から遠い領域では伝送損失の小さい差動伝送線路を提供することができる。そして、差動特性インピーダンスを一定に保っているので、不要な反射のない伝送線路を提供できる。配線周期が大きいと伝送損失が小さくなる理由については、実施例4で説明する。

【0063】

[実施例4]

第二の実施形態に示した配線基板1を比誘電率εr=3.1、誘電正接tanδ=0.023の樹脂基板で実現した。これは実施例1の基板と同一の物性値である。絶縁層厚みtdを100μmとし、配線周期pを75μm、100μm、150μmとして、差動特性インピーダンスが100Ωとなる配線幅wとずらし量dを電磁界シミュレーションによって求めた。それらの場合の伝送損失αを配線幅wに対してプロットした結果を図14に示す。配線幅wが一定でも配線周期pを大きくすることにより伝送損失αが減少することが分かる。

【0064】

今、配線幅wを35μmで一定とし、図13(a)の半導体素子に近い領域の配線周期paを75μm、ずらし量daを37μmとし、図13(b)の半導体素子から遠い領域の配線周期pbを25μm、ずらし量dbを25μmとする伝送路を構成した。電磁界シミュレーションによって求めた(p,d)=(75μm,37μm)の時の伝送損失αは0.741dB、(p,d)=(150μm,25μm)の時の伝送損失αは0.707dBであり、配線周期の大きい(p,d)=(150μm,25μm)の時の方が伝送損失は小さかった。

【0065】

それぞれの断面における磁界分布と伝送損失を電磁界シミュレーションによって求めた。図15はpa=75μmの断面の磁界分布、図16はpa=150μmの断面の磁界分布である。配線周期pが大きい場合(図16)には磁界が差動ペアの間に集中して分布し、隣接配線との間には磁界結合が見られない。一方、配線周期pが小さい場合(図15)には隣接配線との間にも磁界結合がみられる。このように、配線周期pを大きくすることによって、隣接配線との間の磁界結合を弱くすることができ、それによって伝送損失の小さい差動伝送線路を提供することができる。

【0066】

[第三の実施形態]

次に、第三の実施形態について図面を参照して説明する。

【0067】

図17(a)、図17(b)は、それぞれ図12におけるB−B’、C−C’での配線基板1の断面図である。第二の実施形態と同様、信号配線9a1と9b1、信号配線9a2と9b2、信号配線9a3と9b3がそれぞれ一対の差動線路を構成している。断面B−B’における差動線路のずらし量をda2、配線幅をwa2、差動線路間周期をpa2とし、断面C−C’における差動線路のずらし量をdb2、配線幅をwb2、差動線路間周期をpb2とする。ここで、da2>db2、pa2<pb2、wa2<wb2である。第二の実施形態と異なる点は、半導体素子2から離れるに従って配線幅が広くなっている点である。尚、ここではda2>db2としているが、da2とdb2の関係は配線周期p、配線幅wによって変化するので、da2<db2となる場合もある。

【0068】

図14から分かるように、配線周期pと配線幅wを適切に広げれば伝送損失αを小さくすることができる。伝送損失αは配線幅wの変化に対して極小点を持つので、規格化ずらし量Dが0.2<D<1.2になる範囲で配線幅wを広げることが望ましい。

【0069】

図18は信号配線9a1、9a2、9a3を上から見た図であり、半導体素子2から離れるに従って連続的に配線幅を広げている。また図19に示すように、各信号配線の配線幅を段階的に広げてもよい。

【0070】

このように、半導体素子から離れるに従って複数の信号配線の配線周期と配線幅を広げることによって、半導体素子に近い領域では高密度に配線を行い、半導体素子から遠い領域では伝送損失の小さい差動伝送線路を提供することができる。そして、差動特性インピーダンスを一定に保っているので、不要な反射のない伝送線路を提供できる。

【0071】

[実施例5]

第三の実施形態に示した配線基板1を比誘電率εr=3.1、誘電正接tanδ=0.023の樹脂基板で実現した。これは実施例1の基板と同一の物性値である。絶縁層厚みtd=30μmとし、図17(a)の半導体素子に近い領域では(p,w,d)=(50,20,60)、図17(b)の半導体素子から遠い領域では(p,w,d)=(75,25,80)とした。電磁界シミュレーションによって求めた(p,w,d)=(50,20,60)の時の伝送損失αは0.94dB、(p,w,d)=(75,25,80)の時の伝送損失αは0.87dBであり、配線幅と配線周期の広い場合の方が伝送損失は小さくなった。

【0072】

[第四の実施形態]

次に、本発明の第四の実施形態について説明する。図20は本実施形態の半導体装置の上面図である。多層の配線基板11の上部中央に半導体素子10が実装されており、配線基板11に設けられた信号配線が半導体素子10から放射状に広がっている。配線基板11は正方形であり、一部の信号配線12はその正方形の各辺の中央部に向かって引き回され、別の信号配線13は正方形の角に向かって引き回されている。従って、信号配線13の方が信号配線12よりも配線長が長い。伝送線路の構造が同一の場合、信号配線の配線長が長くなると伝送損失が大きくなるが、本実施形態の配線基板は下記の構造をとることによって信号配線12と信号配線13の伝送損失をほぼ等しい値にしている。

【0073】

図21は図20の曲線D−D’における断面図である。図21(a)は信号配線12付近の断面図であり、図21(b)は信号配線13付近の断面図である。なお、曲線D−D’上の各点は半導体素子10からの配線長が等しい。図21において、信号配線12の配線幅、差動配線間周期、ずらし量をそれぞれwD1、pD1、dD1とし、また信号配線13の配線幅、差動配線間周期、ずらし量をそれぞれwD2、pD2、dD2とする。

【0074】

曲線D−D’上の点は半導体素子10からの配線長が等しいが、ここでは信号配線12と13の配線幅、差動配線間周期を同一とはせず、pD1<pD2、wD1<wD2とし、差動特性インピーダンスを100Ωにするためにずらし量を調整し、dD1<dD2としている。

【0075】

このように、基板内に配線長の長い信号配線と短い信号配線が存在する場合、配線長の長い信号配線の差動配線間周期と配線幅を広くすることにより、配線長の長い信号配線の単位長さ辺りの伝送損失を小さくすることができる。従って、長い信号配線の配線全体の伝送損失を、配線長の短い信号配線の全体の伝送損失とほぼ等しくすることができる。

【0076】

[第五の実施形態]

次に、本発明の第五の実施形態について説明する。図22は本実施形態の半導体装置の断面図である。多層の配線基板14の上面中央に半導体素子10が、上面端部には半導体モジュール17がそれぞれ実装されている。配線基板14は上から順に第一〜第五の配線層14a、14b、14c、14d、14eからなり、第二配線層14bに信号配線15が、第三配線層14cに信号配線16がそれぞれ形成され、半導体素子10と半導体モジュール17とを接続している。信号配線15と16が一組でダイアゴナル配線を形成している。

【0077】

図23は本実施形態の半導体装置の上面図である。配線基板14の上面中央に半導体素子10が実装され、その周囲に複数の半導体モジュール17(例えば17a、17b)が配置されている。半導体素子10から信号配線が放射状に広がっており、半導体モジュール17との間で高速信号を伝送している。配線基板14は正方形に近い形状をしており、正方形の角に近い位置に実装された半導体モジュール17bと半導体素子10との距離は比較的長く、正方形の各辺の中央に近い位置に実装された半導体モジュール17aと半導体素子10との距離は比較的短い。そして、半導体モジュール17aと接続される信号配線の配線周期は、半導体モジュール17bと接続される信号配線の配線周期よりも狭くなっている。

【0078】

図24は図23の曲線E−E’における配線基板の断面図である。曲線E−E’上の各点は、半導体素子10からの配線長が等しい。図24(a)は半導体モジュール17aと接続される信号配線15a、16aの断面図であり、図25(b)は半導体モジュール17bと接続される信号配線15b、16bの断面図である。信号配線15a、16aの配線幅、ずらし量、配線周期をそれぞれwEa、dEa、pEaとし、信号配線15b、16bの配線幅、ずらし量、配線周期をそれぞれwEb、dEb、pEbとする。ここで、差動ペア(a15a、16a)と(a15b、16b)の配線幅、差動配線周期を同一とはせず、pEa<pEb、wEa<wEbとし、差動特性インピーダンスを100Ωにするためにずらし量を調整し、dEa<dEbとしている。この結果、差動ペア(a15a、16a)は差動ペア(a15b、16b)と比較して、配線長が短く、単位長さ辺りの伝送損失が大きい。

【0079】

このように、配線基板14上に半導体素子10と複数の半導体モジュール17を実装し、それぞれの半導体モジュールから半導体素子10までの距離が異なる場合、半導体素子10から遠い半導体モジュールと接続する信号配線の差動配線間周期と配線幅を広くして単位長さ辺りの伝送損失を小さくすることにより、配線長が長いことによる伝送損失の増大を相殺することができ、信号配線全体の伝送損失を等しくすることができる。その結果、信号配線の伝送損失を予備補償するプリエンファシスのような波形補正機能が半導体素子10に搭載されている場合、全ての信号配線に対するプリエンファシスの設定を単一にしても、全ての信号配線に対して最適な波形補正を施すことができる。

【0080】

半導体モジュール17の例としては、LSIなどの半導体素子、半導体素子を基板に実装した半導体パッケージ、光電気変換素子を基板上に実装した光モジュールなどが挙げられる。

【図面の簡単な説明】

【0081】

【図1】図1は、本発明の第一の実施形態による半導体装置の斜視図である。

【図2】図2は、図1の半導体装置の断面図である。

【図3】図3は、図2の配線基板のA−A’による断面図である。

【図4】図4は、第一の実施形態において実施例1の配線基板の材料を用いたダイアゴナル線路のずらし量と差動特性インピーダンスの関係を示すグラフ図である。

【図5】図5は、実施例1の配線基板の材料を用いたダイアゴナル線路の差動特性インピーダンス100Ωにおけるずらし量と伝送損失との関係を示すグラフ図である。

【図6】図6は、実施例1の配線基板の材料を用いたダイアゴナル線路のp=100μm、w=33μm、d=0μmの時の磁界分布を示した図である。

【図7】図7は、実施例1の配線基板の材料を用いたダイアゴナル線路のp=100μm、w=46μm、d=82μmの時の磁界分布を示した図である。

【図8】図8は、実施例1の配線基板の材料を用いたダイアゴナル線路のp=100μm、w=55μm、d=160μmの時の磁界分布を示した図である。

【図9】図9は、実施例1の配線基板の材料を用いたダイアゴナル線路の差動特性インピーダンス100Ωにおける規格化ずらし量と伝送損失との関係を示すグラフ図である。

【図10】図10は、実施例2の配線基板の材料を用いたダイアゴナル線路の差動特性インピーダンス100Ωにおける規格化ずらし量と伝送損失との関係を示すグラフ図である。

【図11】図11は、実施例3の配線基板の材料を用いたダイアゴナル線路の差動特性インピーダンス100Ωにおける規格化ずらし量と伝送損失との関係を示すグラフ図である。

【図12】図12は、第二の実施形態による半導体装置の上面図である。

【図13】図13(a)、(b)は、第二の実施形態における図12の配線基板のB−B’、C−C’における断面図である。

【図14】図14は、実施例4の配線基板を用いたダイアゴナル線路の配線幅と伝送損失との関係を示すグラフ図である。

【図15】図15は、図13(a)の断面における磁界分布を示した図である。

【図16】図16は、図13(b)の断面における磁界分布を示した図である。

【図17】図17(a)、(b)は、第三の実施形態の図12におけるB−B’、C−C’での配線基板の断面図である。

【図18】図18は、第三の実施形態による配線基板の伝送線路の一例を部分的に示す上面図である。

【図19】図19は、第三の実施形態による配線基板の伝送線路の別の例を部分的に示す上面図である。

【図20】図20は、第四の実施形態による半導体装置の上面図である。

【図21】図21(a)、(b)は、図20の配線基板のD−D’における断面図である。

【図22】図22は、第五の実施形態による半導体装置の断面図である。

【図23】図23は、第五の実施形態による半導体装置の上面図である。

【図24】図24(a)、(b)は、図23の配線基板のE−E’における断面図である。

【図25】従来の代表的な差動伝送線路構造の断面図である。

【符号の説明】

【0082】

1、11、14:配線基板

1a:第一の絶縁層

1b:第二の絶縁層

1c:第三の絶縁層

1d:第四の絶縁層

2、10:半導体素子

3:接続用導体

4a1、4a2、4a3、9a1、9a2、9a3:第二配線層の信号配線

4b1、4b2、4b3、9b1、9b2、9b3:第三配線層の信号配線

5a、14a:第一配線層

5b、14b:第二配線層

5c、14c:第三配線層

5d、14d:第四配線層

5e、14e:第五配線層

6:BGAランド

7、8:グラウンド電極

12:配線長の短い信号配線

13:配線長の長い信号配線

15:第二配線層の信号配線

16:第三配線層の信号配線

17:半導体モジュール

【特許請求の範囲】

【請求項1】

異なる二つの配線層に一本ずつ信号配線を配置しこれら二本の信号配線を上下に重ならないよう水平方向に一定距離ずらしてなる一対の差動ペアが複数形成された多層配線基板において、

前記二本の信号配線の水平方向のずらし量をd、前記二本の信号配線を隔てる絶縁層の厚みをt、隣接する信号配線との配線周期、すなわち隣接差動配線との間隔と信号配線幅の和をpとした時、D=d(t/p3)1/2で表される値Dが0.2<D<1.2の範囲内に収まっている部分があることを特徴とする伝送線路。

【請求項2】

前記二つの配線層のさらに上または下あるいは上下両方の配線層にグラウンドプレーンまたは電源プレーンが形成されていることを特徴とする請求項1に記載の伝送線路。

【請求項3】

前記隣接する信号配線との配線周期が位置によって異なっていることを特徴とする請求項1または2に記載の伝送線路。

【請求項4】

前記信号配線幅が位置によって異なっていることを特徴とする請求項1〜3のいずれかに記載の伝送線路。

【請求項5】

請求項1〜4のいずれかに記載の伝送線路を有する配線基板。

【請求項6】

請求項1〜4のいずれかに記載の伝送線路を有する配線基板に半導体素子または半導体パッケージを搭載し、前記伝送線路と前記半導体素子または半導体パッケージとを接続してなる半導体装置。

【請求項7】

請求項6に記載の半導体装置であって、前記配線基板は配線長の長い差動ペアと配線長の短い差動ペアとを有し、それらの差動ペアは当該配線基板に搭載された前記半導体素子と接続されており、前記配線長の長い差動ペアのある地点における配線周期は、前記半導体素子から等しい距離における前記配線長の短い差動ペアの配線周期よりも広いことを特徴とする半導体装置。

【請求項8】

請求項6に記載の半導体装置であって、前記配線基板の中央に前記半導体素子が搭載され、前記差動ペアは前記半導体素子から離れるに従って隣接する差動ペアとの間隔が広がっていることを特徴とする半導体装置。

【請求項9】

請求項6に記載の半導体装置であって、前記配線基板の中央に前記半導体素子が搭載され、前記差動ペアは前記半導体素子から離れるに従って前記信号配線幅が太くなっていることを特徴とする半導体装置。

【請求項1】

異なる二つの配線層に一本ずつ信号配線を配置しこれら二本の信号配線を上下に重ならないよう水平方向に一定距離ずらしてなる一対の差動ペアが複数形成された多層配線基板において、

前記二本の信号配線の水平方向のずらし量をd、前記二本の信号配線を隔てる絶縁層の厚みをt、隣接する信号配線との配線周期、すなわち隣接差動配線との間隔と信号配線幅の和をpとした時、D=d(t/p3)1/2で表される値Dが0.2<D<1.2の範囲内に収まっている部分があることを特徴とする伝送線路。

【請求項2】

前記二つの配線層のさらに上または下あるいは上下両方の配線層にグラウンドプレーンまたは電源プレーンが形成されていることを特徴とする請求項1に記載の伝送線路。

【請求項3】

前記隣接する信号配線との配線周期が位置によって異なっていることを特徴とする請求項1または2に記載の伝送線路。

【請求項4】

前記信号配線幅が位置によって異なっていることを特徴とする請求項1〜3のいずれかに記載の伝送線路。

【請求項5】

請求項1〜4のいずれかに記載の伝送線路を有する配線基板。

【請求項6】

請求項1〜4のいずれかに記載の伝送線路を有する配線基板に半導体素子または半導体パッケージを搭載し、前記伝送線路と前記半導体素子または半導体パッケージとを接続してなる半導体装置。

【請求項7】

請求項6に記載の半導体装置であって、前記配線基板は配線長の長い差動ペアと配線長の短い差動ペアとを有し、それらの差動ペアは当該配線基板に搭載された前記半導体素子と接続されており、前記配線長の長い差動ペアのある地点における配線周期は、前記半導体素子から等しい距離における前記配線長の短い差動ペアの配線周期よりも広いことを特徴とする半導体装置。

【請求項8】

請求項6に記載の半導体装置であって、前記配線基板の中央に前記半導体素子が搭載され、前記差動ペアは前記半導体素子から離れるに従って隣接する差動ペアとの間隔が広がっていることを特徴とする半導体装置。

【請求項9】

請求項6に記載の半導体装置であって、前記配線基板の中央に前記半導体素子が搭載され、前記差動ペアは前記半導体素子から離れるに従って前記信号配線幅が太くなっていることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図6】

【図7】

【図8】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図6】

【図7】

【図8】

【図15】

【図16】

【公開番号】特開2008−109331(P2008−109331A)

【公開日】平成20年5月8日(2008.5.8)

【国際特許分類】

【出願番号】特願2006−289462(P2006−289462)

【出願日】平成18年10月25日(2006.10.25)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成18年度 文部科学省「超高速コンピュータ用光インターコネクションの研究開発」委託研究、産業活力再生特別措置法第30条の適用を受ける特許出願

【出願人】(000004237)日本電気株式会社 (19,353)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

【公開日】平成20年5月8日(2008.5.8)

【国際特許分類】

【出願日】平成18年10月25日(2006.10.25)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成18年度 文部科学省「超高速コンピュータ用光インターコネクションの研究開発」委託研究、産業活力再生特別措置法第30条の適用を受ける特許出願

【出願人】(000004237)日本電気株式会社 (19,353)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

[ Back to top ]