伝送装置、伝送方法、画像形成装置、送信装置及び受信装置

【課題】併走クロックを使用する信号伝送において、併走クロックの周波数を落とすことなく、信号の長距離伝送を行うことを可能とする。

【解決手段】送信側の通信装置1と受信側の通信装置4との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置である。送信側の通信装置1は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置4送信する。受信側の通信装置は、受信したデータの少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信する。

【解決手段】送信側の通信装置1と受信側の通信装置4との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置である。送信側の通信装置1は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置4送信する。受信側の通信装置は、受信したデータの少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、伝送装置、伝送方法、画像形成装置、送信装置及び受信装置に係り、特に、併走クロックを用いて長距離の信号伝送を行う伝送装置、伝送方法、前記伝送装置を使用した画像形成装置、前記伝送装置を構成する送信装置及び受信装置に関する。

【背景技術】

【0002】

一般に、プリンタ、複写機等、あるいは、それらの両機能等を備えた複合機において、幅方向が広い用紙に印刷を行う幅広機と呼ばれる装置は、本体と本体に載せた可動部(ヘッド中継上の基板)との間の距離が長くなるために、その間での信号の伝送には長距離伝送を行う必要がある。信号の長距離伝送には、EMIの影響と信号品質の劣化とを避けるため、差動伝送方法が用いられることが多い。また、伝送用のケーブルとしてFFC(Flat Flexible Cable)を用い、差動伝送方法によりデータ伝送を行おうとす場合、FFCが長いと、高周波成分が損失して信号を劣化させるため、これを回避するために転送レートを落として確実に信号の伝送を行う方法に関する従来技術が、例えば、特許文献1等に記載されて知られている。

【0003】

この従来技術は、信号を確実に伝送する目的のために、低コストのLVDS(Low Voltage Differential Signal)ドライバ、LVDSレシーバを使用し、かつ、分周回路と逓倍回路とを使用することにより高周波を低周波に変換し、長距離伝送する信号の転送レートを落として伝送を行う方法に関するものである。すなわち、この従来技術は、長距離伝送したい高周波の信号を送信側の分周回路により一旦汎用のドライバICやレシーバICで処理可能な周波数(低周波)の信号に分周し、低い周波数レートに変換された信号をドライバICから伝送路に送出し、伝送路を介した長距離伝送を行い、この低い周波数レートに変換された信号を受信した受信側のレシーバICが、逓倍回路により受信した低い周波数レートの信号を元の高周波の信号に復元するというものである。

【0004】

また、EMIの影響とそれによる信号品質の劣化とを避けるために、SSCG(Spread Spectrum Clock Generator)を使用する場合があるが、この場合には、クロック変調の影響によりジッタ成分が発生してしまうために信号の伝送が困難となってしまう。そこで、信号の転送レートを落として確実に信号の伝送を行う方法に関する他の従来技術が、例えば、特許文献2等に記載されて知られている。

【0005】

この他の従来技術は、SSCGによる画像への悪影響を低減する目的のために、CCDが原稿を読み取ることにより得られたアナログ電気信号を増幅し、デジタル信号に変換するAFEと、SSCGを利用して所定周波数のクロック信号を周波数変調し、得られた内部基準クロック信号に基づいて、CCD及びAFEを制御する信号であって、周波数変動を有する制御信号を生成するタイミングジェネレータと、デジタル信号に所定の画像処理を実行して得られる画像にSSCGの影響がスジとして現れるかどうかを判定する画像データ判定部とを備え、画像データ判定部が「SSCGの影響がスジとして現れる」と判定した場合に、タイミングジェネレータが生成する制御信号の周波数を変更するというものである。

【発明の概要】

【発明が解決しようとする課題】

【0006】

信号の伝送方法には、クロック埋め込みタイプとクロック併走タイプとがあり、クロック埋め込みタイプは、コストが高いために、一般にはクロック併走タイプが良く用いられている。前述した従来技術は、クロック併走タイプの信号伝送方法を適用して信号の転送レートを落として信号の伝送を行う場合、併走クロックの周波数を落とさなければならず、これに伴って送信側及び受信側の通信装置を構成するFPGA(Field Programmable Gate Array)あるいはASIC(Application Specific Integrated Circuit)のシステムクロックの周波数を落とさなければならず、装置全体の処理速度を低下させてしまうという問題点を生じさせてしまう。

【0007】

本発明の目的は、前述した従来技術の問題点を解決し、併走クロックを使用する信号伝送において、併走クロックの周波数を落とすことなく、信号の長距離伝送を行うことを可能とした伝送装置、伝送方法、前記伝送装置を使用した画像形成装置、前記伝送装置を構成する送信装置及び受信装置を提供することにある。

【課題を解決するための手段】

【0008】

前記目的を達成するため、本発明は、送信側の通信装置と受信側の通信装置との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置において、前記送信側の通信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記受信側の通信装置は、受信したデータの前記少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする。

【発明の効果】

【0009】

本発明によれば、併走クロックの転送レートを落とすことなく、信号の長距離伝送を行うことができ、これにより、本発明による信号の伝送装置を採用するシステムでの処理速度を低下させるようなことを防止することができる。

【図面の簡単な説明】

【0010】

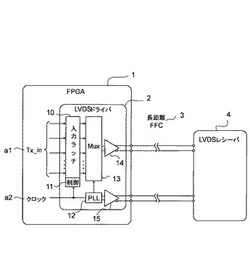

【図1】本発明の実施形態による伝送装置を含む伝送システム全体の概略構成を示すブロック図である。

【図2】図1において、SSCG回路2aの使用状況による伝送波形、すなわち、レシーバ側の入力端で観測したアイパターンの波形を説明する図である。

【図3】受信側の通信装置におけるレシーバスキューマージンについて説明する図である。

【図4】図3で説明したレシーバスキューマージンの規定を満たさない例について説明する図である。

【図5】本発明の一実施形態による伝送装置の構成例を示すブロック図である。

【図6】従来技術による信号の伝送方法の具体例を説明する図である。

【図7】本発明の実施形態による信号の伝送方法の具体例を説明する図である。

【図8】データの伝送方法を切り替えて信号データの送信を行うようにした送信側の通信装置の構成を示すブロック図である。

【図9】本発明の実施形態における送信データ構成の具体例について説明する図である。

【図10】送信側の通信装置の回路構成を示すブロック図である。

【図11】受信側の通信装置であるLVDSレシーバの回路構成を示すブロック図である。

【図12】従来技術による伝送方法の場合に受信側に送信されるシリアルデータのデータ列を示す図である。

【図13】図12に示すシリアルデータをパラレル変換したデータ列を示す図である。

【図14】本発明の実施形態による伝送方法の場合に受信側に送信されるシリアルデータのデータ列を示す図である。

【図15】図14に示すシリアルデータをパラレル変換したデータ列を示す図である。

【図16】Mode切り替え信号の送信データへの埋め込み方法を説明する図である。

【図17】図1に示して説明した伝送システムにより伝送された伝送データが正常に伝送されていることを検証する構成について説明する図である。

【図18】図1に示して説明した伝送システムの送信側のトランスミッタ部を構成するASICまたはFPGA3aに入力されるクロックを切り替える構成について説明する図である。

【図19】SSCG回路のモードを切り替える構成について説明する図である。

【図20】本発明の実施形態による伝送装置を備える画像形成装置の外観を示す斜視図である。

【図21】図20に示す画像形成装置の構成を説明する縦断面図である。

【発明を実施するための形態】

【0011】

以下、本発明による伝送装置、伝送方法、画像形成装置、送信装置及び受信装置の実施形態を図面により詳細に説明する。以下に説明する本発明の実施形態での信号伝送の基本的な考え方は、送信側の通信装置が同一のデータを連続した複数ビットとした複数のデータ群として送信し、受信側の通信装置が送られてきた連続した複数の同一データを含むデータ群の2ビット目以降を有効なデータとするものである。

【0012】

図1は本発明の実施形態による伝送装置を含む伝送システム全体の概略構成を示すブロック図である。

【0013】

図1に示す伝送システムは、送信側の装置である送信装置を、クロック発振器OSC1aと、SSCG回路2aと、トランスミッタ部を構成するASICまたはFPGA3aとにより構成し、また、受信側装置である受信装置を、レシーバ部を構成するASICまたはFPGA4aにより構成し、送信装置を構成するASICまたはFPGA3aと受信装置を構成するASICまたはFPGA4aとを伝送路により接続して構成されている。

【0014】

そして、クロック発振器OSC1aからのクロック信号が、SSCG回路2aを介してシステムクロックとしてトランスミッタ部を構成するASICまたはFPGA3aに入力され、ASICまたはFPGA3aは、入力されたシステムクロックを使用して、送信データをレシーバ部を構成するASICまたはFPGA4aに送信している。

【0015】

前述のような構成を有する伝送システムは、EMIの影響とそれによる信号品質の劣化とを避けることができるものであるが、SSCGによるクロック変調の影響によりジッタ成分が発生してしまうために信号の伝送が困難となってしまうことがある。そこで、信号の転送レートを落として確実に信号の伝送を行う必要が生じる。

【0016】

また、図1に示す伝送システムに用いられているASIC、FPGA等のデバイスによってはSSCGに対応していない場合がある。例えば、入力についてはSSCGに対応したスキューマージンが規定されているが、出力に関しては規定されていないといった場合がある。この場合、SSCG非対応のデバイスから出力される信号を評価する必要がでてくる。この信号の評価は、本来、レシーバ側の入力端でのスキューマージンであるRSKM(Receiver Skew Margine)を評価すれば十分であったのが、SSCGを使用している場合、正常に出力がなされる保証はない。さらに、トランスミッタ部の出力に関しても評価しなければならない場合があり、工数が膨大になってしまう。

【0017】

後述する本発明においては、正常に伝送がなされていることを確認してから伝送を開始するため、データの取りこぼしを防ぐことが可能となり、また、波形の評価処理についても削減することが可能となる。

【0018】

図2は図1において、SSCG回路2aの使用状況による伝送波形、すなわち、レシーバ側の入力端で観測したアイパターンの波形を説明する図であり、図2(a)はSSCG回路OFFのアイパターンの波形、図2(b)はSSCG回路を−1%(ダウンスプレッド)としたときのアイパターンの波形、図2(c)はSSCG回路を−3%(ダウンスプレッド)としたときのアイパターンの波形を示している。アイパターンは、信号を繰り返し伝送して重ね合わせることによって得ることが可能であり、このアイパターンにより伝送信号を正しく評価することが可能なアイパターンの時間幅を決定することができ、それにより、信号を正しく評価することができる。

【0019】

図2に示す3つのアイパターンの波形から、SSCG回路の変調レートを上げるにつれてジッタ成分が増加していることが判る。また、SSCG回路を使用した場合、ドライバ側からの反射による影響も顕著となる。

【0020】

図3は受信側の通信装置におけるレシーバスキューマージンについて説明する図であり、図1の説明におけるレシーバの規定値であるスキューマージンを説明するものである。図3には、クロック併走型レシーバにおいて、ある転送レートのデータを受信する場合のレシーバの規定値(RSKM:レシーバスキューマージン)について示している。

【0021】

レシーバの規定値は、転送されるデータの1ビットの時間幅を1UIとしたときに、データを正しく受信するために許されるレシーバスキューマージンの値であり、図3に示す例では、規定値を評価するための基準としてのレシーバスキューマージンの値が0.25UI以下であることである。そして、このレシーバスキューマージンの値は、クロックエッジのなまりによるトリガポイントのズレと、伝送路のスキュー+送信側のドライバ出力端でのスキューと、ジッタ量との和として算出することができる。

【0022】

もし、レシーバスキューマージンを満たすことができなかった場合、UIの値を大きくするために、転送クロックのレートを落とす(受信側でのシリアル/パラレル変換比率は固定)、または、シリアル/パラレル変換比率を下げる(転送クロックは固定)といった方法を採用することが考えられる。但し、レシーバ側のシリアル/パラレル変換比率が固定であるといった制限がある場合、必然的に前者の方法を採用することになる。

【0023】

また、受信側のレシーバの種類によっては、レシーバスキューマージンの値が転送クロックのレートに依存しないものもあり、この場合、長距離伝送時の信号の減衰特性によって、クロックがより鈍るために信号(データ)を正常に伝送することが不可能となる。さらに、EMI対策として、SSCG回路を用いた場合ジッタ成分が増大し、この結果、クロック及びデータのマージンが削られてしまい、信号を正常に伝送することが不可能となる。

【0024】

本発明の実施形態による伝送装置は、ジッタ量についてデータの立ち上がりに関して緩和することができるので、レシーバスキューマージンを満たすことが従来技術による伝送装置と比較して容易であるという優位性を有している。これにより、本発明の実施形態によれば、より安価なFFC、LVDSレシーバの組み合わせにより長距離伝送を実現することが可能となる。また、前述までの説明において、SSCG回路2aを用いた伝送システムとその課題とついて説明したが、本発明の実施形態による伝送装置を含む伝送システムは、図1に示すシステムにおけるSSCG回路2aを用いない伝送システムであっても、レシーバスキューマージンを満たすことが容易になる。

【0025】

図4は図3で説明したレシーバスキューマージンの規定を満たさない例について説明する図である。

【0026】

一般に、信号を長距離伝送すると信号の減衰が発生し、信号の立ち上がりがなまってしまい、レシーバスキューマージンの値が図3により説明した規定値より大きくなって、規定を満たさなくなってしまう。この結果、信号を繰り返し伝送し重ね合わせて、信号を正しく受信することができる時間幅を決定し、信号の評価を行うアイパターンは、図4にデータDATAとして示す図4の長四角で示すように狭くなってしまうことになり、レシーバのスキューマージンの規定値を満たすことができなくなってしまう。

【0027】

以下に説明する本発明の実施形態は、送信側の通信装置が同一の1ビットのデータを連続した複数ビットとして送信し、受信側の通信装置が送られてきた連続した複数の同一データの2ビット目以降の1ビットを有効なデータとするものである。

【0028】

図5は本発明の一実施形態による伝送装置の構成例を示すブロック図である。ここで説明する本発明の実施形態による伝送装置は、前提条件として、信号の伝送方法にクロック併走タイプの信号伝送方法を使用するものとする。

【0029】

図5に示す本発明の実施形態は、図1における送信装置のトランスミッタ部を構成するFPGA3aと受信装置のレシーバ部を構成するFPGA4aとに対応するものであり、送信側の通信装置を構成しているFPGA1と受信側の通信装置としてのLVDSレシーバ4とが信号用及びクロック用のFFC3により接続されて構成されている。そして、FPGA1内には、LVDSドライバ2が構成されており、LVDSドライバ2は、入力される送信データ信号である Tx_in a1をラッチする入力ラッチ10と、入力されるFPGA1のシステムクロックであるクロック信号a2を受け、入力ラッチ10への書き込み、読み出しを制御する制御部11と、入力されるクロック信号a2から信号伝送用のクロック信号を生成するPLL(Phase Locked Loop)回路12と、入力ラッチ10からの送信データをパラレル/シリアル変換するMux回路13と、Mux回路13及びPLL回路12のそれぞれからの送信データ及びクロック信号をLVDSに変換する差動ドライバ回路14、15とにより構成されている。なお、本発明の実施形態による伝送装置を利用する広幅機におけるはFFCの長さは、一般に、1m〜3mであることが多い。

【0030】

次に、前述したように構成される本発明の実施形態の伝送装置における信号の流れについて説明する。

【0031】

LVDSドライバ2へは、FPGA1の内部からパラレルのデータ信号である Tx_in a1とクロック信号a2が入力される。但し、このクロック信号はFPGA1のシステムクロックである。なお、図示しないが、FPGA1の内部には、他の処理回路等が含まれ、データ信号である Tx_in a1とクロック信号a2は、FPGA1の外部から与えられるものである。

【0032】

データ信号である Tx_in a1は、LVDSドライバ2内の入力ラッチ回路10に入力され、制御部11によりラッチするタイミングがコントロールされて入力ラッチ回路10にラッチされる。入力ラッチ回路10にラッチされたデータ信号 Tx_in は、制御部11にコントロールされて読み出されてMux回路13に渡される。そして、Mux回路13を介してパラレル/シリアル変換されたデータ信号は、その信号レベルが差動ドライバ回路14においてLVDSに変換され、FFC3を経てLVDSレシーバ4へ送信される。

【0033】

また、クロック信号a2は、制御部11に供給されると共に、PLL回路12を介してMux回路13にも供給され、そのレベルが差動ドライバ回路15においてLVDSに変換され、FFC3を経てLVDSレシーバ4へ送信される。

【0034】

なお、本発明の実施形態では、同一の1ビットのデータを連続した複数ビットのデータ列とするデータ変換を行っているが、このための処理は、FPGA1内のLVDSドライバ2の前段に設けられる図示しない論理回路により行われる。これについては、図10を参照して後述する。

【0035】

図6は従来技術による信号の伝送方法の具体例を説明する図、図7は本発明の実施形態による信号の伝送方法の具体例を説明する図であり、次に、図6、図7を参照して、従来技術と本発明の実施形態とによる信号伝送方法の相違について説明する。なお、ここで説明する例は、シリアル/パラレルの比率が1:7の場合、すなわち、1クロックサイクル内に7ビットのデータを入れ込んで伝送することができる場合の例であり、また、併走クロックである転送クロックとして、1クロックのレベルHighとLow とが3:4の非対象クロック信号を使用した例である。なお、1クロックサイクル内に何ビットのデータを入れ込むかは、任意に設定することができる。

【0036】

図6に示す従来技術による伝送方法の場合、送信側の通信装置は、転送データとして、7ビットのパラレルの転送データa〜gをシリアル変換して、aからgの順で1クロックサイクル内に転送する。受信側の通信装置は、転送されてきたデータの各ビットが有効なものとして受信する。このとき、正常にデータが伝送されるためには、各データのそれぞれのアイパターンが、図3、図4を参照して説明したように受信側の通信装置であるレシーバの規定値を確保できていることが必要となる。

【0037】

前述したような従来技術でのデータの伝送に対して、図7に示す本発明の実施形態による伝送方法の場合、送信側の通信装置であるFPGA1内のLVDSドライバ2は、転送データとして、先に説明したように併走クロックの1サイクル内に伝送することができる7ビット分のデータの内2ビットまたは3ビットのデータを、それぞれ同一の連続する複数ビットのシリアルデータとして併走クロックの1サイクル内で送信している。図示している例の場合、転送データは、a、a、a、b、b、b、bの順で、各群が同一データを持つ2群のデータとして送信されるとして示しているが、この順は、a、a、a、b、b、c、cの順で、各群が同一データを持つ3群のデータとすることもできる。受信側の通信装置は、転送されてきた連続する複数の同一のデータを持つデータ群の2ビット目のデータ、あるいは、2ビット目以降の何れか1ビットのデータを有効なものとして受信する。図示例では、2ビット目のデータaと2ビット目のデータbとを有効なものとして受信することとしているが、データbについては、3ビット目あるいは4ビット目のデータを有効なものとして受信してもよい。また、転送データとして、a、a、a、b、b、c、cの順でデータが送信されてきた場合、それぞれ、2ビット目のデータa、b、cが有効なデータとして受信される。

【0038】

本発明の実施形態は、前述したように同一のデータを複数ビットに渡って送信することによって、受信側のレシーバでデータを受信するために規定されるアイパターンを広げることができるので、伝送するための条件が悪くなった(図7に示して説明した例では、1クロックサイクル内で2ビットまたは3ビットのデータしか転送できない)としても、受信側の通信装置としてのレシーバの規定値を確保することができ、確実にデータの転送を行うことが可能となる。

【0039】

図8はデータの伝送方法を切り替えて信号データの送信を行うようにした送信側の通信装置の構成を示すブロック図である。

【0040】

図8に示す送信側の通信装置は、図5により説明した送信側の通信装置の場合と同様に、送信側の通信装置を構成するFPGA1内に、LVDSドライバ2が構成されており、LVDSドライバ2は、入力される送信データ信号である Tx_in a1及びMode切り替え信号a3をラッチする入力ラッチ10と、入力されるFPGA1のシステムクロックであるクロック信号a2を受け、入力ラッチ10への書き込み、読み出しを制御する制御部11と、入力されるクロック信号a2から信号伝送用のクロック信号を生成するPLL(Phase Locked Loop)回路12と、入力ラッチ10からの送信データ及びMode切り替え信号をパラレル/シリアル変換するMux回路13と、Mux回路13及びPLL回路12のそれぞれからの送信データ、Mode信号及びクロック信号をLVDSに変換する差動ドライバ回路14、15、16とにより構成されている。

【0041】

図8に示す送信側の通信装置は、図5に示して説明した送信側の通信装置が、データ信号として Tx_in a1のみを伝送するのに対して、Mode切り替え信号a3を追加して他のデータ信号と共に伝送を行うようにしたものである。

【0042】

図8に示して説明したように構成される送信側の通信装置を使用する伝送装置は、Mode切替信号を用いることによって、受信側の通信装置のレシーバに、信号の伝送方法が、前述したような本発明の実施形態による伝送方法であるか、従来技術として説明したような送信側の通信装置が転送データとして送信した1クロックサイクル内の全データを、受信側の通信装置が有効なものとして受信する伝送方法であるかを判断させて、その伝送方法に従った処理を実行させることができる。

【0043】

図9は本発明の実施形態における送信データ構成の具体例について説明する図である。図9に示す例においても、図6、図7とは図の表記が左右逆となっているが、図6、図7により説明した場合と同様に転送データの変換前のデータd1を、1クロックサイクル内でデータaからデータgの7ビットがデータaから順に送信されるものであるとし、これらのデータa〜gを1つのクロックサイクルの中で、2ビットのデータd2、2ビットのデータd3、3ビットのデータd4の3回に分け、3クロックサイクルで送信するものとしている。

【0044】

そして、1回目の送信時には変換前の2ビットのデータa、bが取り出され、それらのデータが1クロックサイクル内で送信されるように変換される。この場合、変換後のデータ列は、3ビットのa、a、aのデータ列と、4ビットのb、b、b、bのデータ列との2つのデータ列とされ、このデータ列d2がLVDSドライバに送られ、受信側に送信されることになる。

【0045】

また、2回目の送信時には変換前の2ビットのデータc、dが取り出され、それらのデータが次の1クロックサイクル内で送信されるように変換される。この場合、変換後のデータ列は、3ビットのc、c、cのデータ列と、4ビットのd、d、d、dのデータ列との2つのデータ列とされ、このデータ列d3がLVDSドライバに送られ、受信側に送信されることになる。

【0046】

また、3回目の送信時には変換前の3ビットのデータe、f、gが取り出され、それらのデータが次の1クロックサイクル内で送信されるように変換される。この場合、変換後のデータ列は、2ビットのe、eのデータ列と、2ビットのf、fのデータ列と、3ビットのg、g、gのデータ列との3つのデータ列とされ、このデータ列d4がLVDSドライバに送られ、受信側に送信されることになる。

【0047】

なお、図9には、併走クロックの波形を示していないが、前述したようなデータの変換を行うと、3回目の送信のように、併走クロックの1サイクル内における波形の立ち下がり部分を挟んで同一のデータが並べられるようになる場合が生じるが、併走クロックの1サイクル内における波形の立ち下がり部分のエッジのなまりは、図7、図3により説明したレシーバの規定値に影響を及ぼすことはなく、本発明を実施する上で何ら問題となることはない。

【0048】

前述したようなデータの変換は、変換後のデータが2ビット以上同一のデータとしたデータ列とされていればよく、前述の例にとらわれることはない。また、伝送環境が悪いときには、必要に応じて変換後のデータ列の構成を変更して対応することができる。

【0049】

図10は送信側の通信装置の回路構成を示すブロック図である。図10に示す送信側の通信装置の回路構成は、図8により説明した送信側の通信装置であるFPGA1の内部回路構成を示すものである。

【0050】

図10に示すように、送信側の通信装置であるFPGA1は、その内部に、図8に示して説明したものと同一のLVDSドライバ22と、外部から入力される送信データ信号である Tx_in a1及びMode切り替え信号a3を一時的に保持する FIFO MEMORY20と、FIFO MEMORY20 から出力されるデータ列、外部から入力される送信データ信号である Tx_in a1及びMode切り替え信号a3の一方を選択してLVDSドライバ22渡すセレクタ21とを有して構成されている。

【0051】

前述したように構成される送信側の通信装置は、パラレルデータ信号として入力される送信データ信号 Tx_in a1を、Modeセレクト信号a3によって、従来技術の場合と同様な方法による伝送方法で送信するか、本発明の実施形態による伝送方法で送信するかを選択することが可能である。そして、本発明の実施形態による伝送方法を使用し、複数ビットのデータ連続して送信する場合、入力されるデータ信号 Tx_in a1は、FIFO MEMORY20 に一旦保持された後に、セレクタ21により選択されてLVDSドライバ22へ入力されることになる。すなわち、前述した送信側の通信装置において、入力されたデータ信号 Tx_in a1の変換前のデータは、一旦、FIFO MEMORY20 に格納され、送信されるデータが、順次セレクタ24に送られことになる。本発明の実施形態により伝送方法の場合、図9により説明したように、変換前の7ビットのデータ列が3回に分けて送信されるので、FIFO MEMORY20 から出力されるデータをセレクタに書き込む際には、3回に分けて書き込まれる。セレクタに書き込まれたデータは、順次LVDSドライバ22へ転送される。

【0052】

前述から判るように、本発明の実施形態による伝送方法を使用した場合、外部からのデータ信号 Tx_in a1がFIFO MEMORY20 に入力される速度に対して、FIFO MEMORY20 からセレクタに出力される速度が1/3になるので、前述のFIFO MEMORY20 は、その入出力の速度差を吸収する機能を果たしている。

【0053】

また、従来技術の場合と同様な方法による伝送方法を採用する場合、入力される送信データ信号である Tx_in a1及びMode切り替え信号a3は、FIFO MEMORY 20を介することなく、セレクタ21に入力され、そのままセレクタ21を通ってLVDSドライバ22へ送信される。

【0054】

前述で説明した送信側の通信装置におけるFIFO MEMORY 20及びセレクタ21が、入力される送信データ信号を、同一のデータが連続した複数ビットのデータ列なるようにデータ変換を行う論理回路を構成ている。

【0055】

図11は受信側の通信装置であるLVDSレシーバの回路構成を示すブロック図である。

【0056】

図11に示す受信側の通信装置であるLVDSレシーバ4は、送信側のLVDSドライバ2から送信されてきたデータ信号、併走クロック信号を受け取る差動レシーバ41、42と、データ信号をシリアル/パラレル変換するMux回路43と、クロック信号を受け取るPLL回路44と、Mux回路43からのデータ信号を一時的に保持する入力ラッチ回路45と、入力ラッチ回路45の書き込み、読み出しを制御する制御回路46とにより構成される。

【0057】

前述したように構成される受信側の通信装置において、LVDSレシーバ4には、FFCを介してシリアルデータと併走クロックとが入力される。それらのデータは、差動レシーバ41、42においてそれらのレベルが論理レベルに変換されると共に、差動信号がシングルエンドの信号に変換される。そして、データは、Mux回路43に入力され、Mux回路43でシリアル/パラレル変換される。入力されたクロック信号は、PLL回路44を経てMux回路43、制御回路46に供給されると共に、外部のシステムクロックとして出力される。Mux回路43から出力されたパラレルのデータ信号はラッチ回路45を経て外部へ出力される。制御回路46は、Mux回路43から出力されたパラレルのデータ信号をラッチ回路45に書き込む制御を行う。

【0058】

前述において、LVDSレシーバ4の外部へ出力されたデータは、データの伝送が本発明による伝送方法を示すModeで行われていた場合、後述するような複数の同一ビットのデータ列の先頭ビットを捨てる処理が行われ、データの伝送が従来技術による伝送方法を示すModeで行われていた場合、データを捨てることなく、1つのクロックサイクル内に含まれる全ビットのデータが有効なデータであるものとして扱うように処理が行われる。

【0059】

次に、本発明の実施形態における受信側の通信装置のLVDSレシーバ4の出力側に接続された論理回路で、受信した複数の同一ビットのデータ列の先頭ビットを捨てる処理について説明するが、まず、従来技術による伝送方法の場合について説明する。

【0060】

図12は従来技術による伝送方法の場合に受信側に送信されるシリアルデータのデータ列を示す図、図13は図12に示すシリアルデータをパラレル変換したデータ列を示す図である。

【0061】

従来技術による伝送方法の場合、全てのビットx1〜x7が有効なビットであり、図12に示すように、x1からx7の順にシリアルデータ列として受信側の通信送信に送信される。このシリアルデータ列は、受信側の通信装置のレシーバ回路によりシリアル/パラレル変換されて、図13に示すようなビットx1〜x7のパラレルデータとされる。このビットx1〜x7のパラレルデータの各ビットは、全て有効なデータとして扱われてレシーバ回路から出力される。

【0062】

図14は本発明の実施形態による伝送方法の場合に受信側に送信されるシリアルデータのデータ列を示す図、図15は図14に示すシリアルデータをパラレル変換したデータ列を示す図である。

【0063】

本発明の実施形態による伝送方法の場合も、図14に示すように、従来技術の場合と同様に、1クロックサイクル内にビットx1からx7の順に送信データがシリアルデータ列として受信側の通信送信に送信される。このシリアルデータ列は、受信側の通信装置のレシーバ回路によりシリアル/パラレル変換されて、図15に示すようなビットx1〜x7のパラレルデータとされる。

【0064】

本発明の実施形態による伝送方法の場合、送信する7ビットのデータのビットx1〜x7の内、x2、x5との2ビットのみが有効データである。このデータ列を受信側の通信装置におけるレシーバ回路でシリアル/パラレル変換すると図15に示すようになる。この場合、x2とx5との2ビットのみが有効データであるため、このデータのみをレシーバから出力させる。

【0065】

前述において、受信側の通信装置としてのレシーバ回路がFPGAに内蔵されて構成去れている場合、有効なx2とx5との2ビットのデータのみを外部に出力させ、また、レシーバが汎用ICである場合、該当の出力ピンのみを外部と接続することにより、先頭ビットを捨てるようにすればよい。

【0066】

図16はMode切り替え信号の送信データへの埋め込み方法を説明する図である。

【0067】

Mode切り替え信号を受信側の通信装置へ送信する方法としては、2つの方法がある。その1つは、Mode切り替え信号を送信データ内に埋め込んで、常時送信する方法、または、必要なときに何時でも送信することができるようにした方法であり、もう1つは、送信すべき一連のデータを送信する前にMode切り替え信号を送信する方法である。図16に示す例は、Mode切り替え信号を送信データ内に埋め込んだ場合の例である。

【0068】

Mode切り替え信号を送信データ内に埋め込んで常時送信する場合、図16に示すように、受信側の通信装置であるレシーバ回路が有効とするデータの中に埋め込むことによって実現することが可能である。もちろん、Mode切り替え信号のデータについても、2ビット以上のデータのかたまりとして送信する必要がある。このようなMode切り替え信号の送信方法は、Mode切り替え信号用に、送信すべき一連のデータの中に2ビット以上を常に確保しなければならないため、送信データの転送レートそのものは落ちてしまうが、データの送信中であってもModeを切り替えることができるというメリットを得ることができる。

【0069】

一方、送信すべき一連のデータを送る前にMode切り替え信号を送る場合、送信データの転送レートを落とすことがなく、Mode切り替え信号を常時送る方法よりも送信データの転送レートが早いが、送信データの送信途中でModeを切り替えることができないというデメリットが生じることになる。

【0070】

図17は図1に示して説明した伝送システムにより伝送された伝送データが正常に伝送されていることを検証する構成について説明する図である。

【0071】

伝送データが正常に伝送されているか否かで特に問題となるのは受信装置のレシーバ部を構成するFPGA4a内のLVDSレシーバがSSCGに対応していない場合である。SSCGをかけた信号が正常に出力されない場合、図1に示した伝送システムを使用した画像形成装置では、出力されたデータによる画像に、画像チリや縦筋が生じる等の影響を与えることがある。このため、間違ったデータが後段に出力されることを防止する必要がある。このため、伝送波形が正常に伝送されていることを確認する必要がある。本発明の実施形態では、そのための手段として、比較回路をLVDSレシーバの直後に配置することとしている。なお、このような検証は、送信側の通信装置が、SSCG回路を使用していない場合にも行われてよい。

【0072】

図17に示した伝送データが正常に伝送されていることを検証するための構成は、図1に示して説明したシステムのレシーバ部であるFPGA4aの後段に比較回路5aを接続したものである。そして、図17には示していない送信側のトランスミッタ部を構成するASICまたはFPGA3aから画像データを送信する直前に予め定めたパターンを有するテストパターンを複数回送信させる。レシーバ側の比較回路5aは、送信されてきたテストパターンを、予め決められているパターンと比較し、合致しているときにイネーブル信号をLVDSレシーバ(FPGA)4aに入力し、比較の結果が複数回(テストパターンの送信回数より少なくてもよい)に渡って合致しなかったときにディスイネーブル信号をLVDSレシーバ(FPGA)4aに入力する。なお、前述のテストパターンは、複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群により構成されたものとする。

【0073】

また、前述のイネーブル信号、あるいは、ディスイネーブル信号は、送信側のトランスミッタ部を構成するASICまたはFPGA3aへ送信することができ、これにより、送信側において、受信したイネーブル信号、あるいは、ディスイネーブル信号をモード切り替え信号として用い、SSCG回路の使用の可否を選択するようにすることができる。また、送信側でSSCG回路を使用しておらず、かつ、ディスイネーブル信号を受信した場合、連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上としたテストパターンで検証を行うこと等も可能である。そして、送信側の通信装置は、テストパターンを、複数ビットの内の3ビット以上を連続する同一データとし、これによる検証の結果が正常であり、受信側からイネーブル信号を受けた場合、その後のデータの送信を連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信する。送信側の通信装置は、テストパターンの同一データのビット数を順次増加させていき、受信側の通信送信からデータを正常に受信することができなかった旨の報告を受ける毎に、順次前記連続する同一データのビット数の最少数を増加させて送信するようにする。さらに、ビット幅を最大に広げても(SSCG回路を使用しない場合にも)正常に信号を送信することができなかった場合、SC(Serviceman Call)という形でエラーを発することもできる。

【0074】

前述では、伝送データが正常に伝送されていることの検証を、送信側の通信装置からテストパターンを送信することにより行うとして説明したが、この検証は、実際のデータ送信時に行うようにすることもできる。その場合、送信する画像データを誤り検出可能なデータとし、受信側において、受信した画像データに対する誤り検出を行うようにすればよい。

【0075】

図18は図1に示して説明した伝送システムの送信側のトランスミッタ部を構成するASICまたはFPGA3aに入力されるクロックを切り替える構成について説明する図である。

【0076】

図1に示して説明した伝送システムの例では、クロック発振器OSC1aからのクロック信号をSSCG回路2aを介してシステムクロックとしてトランスミッタ部を構成するASICまたはFPGA3aに入力していたが、図18に示す例では、送信側のトランスミッタ部を構成するASICまたはFPGA3a内にクロック分岐回路6aを設け、OSC回路1aからASICまたはFPGA3aに入力するクロック信号を、OSC回路1aから直接入力されるものと、SSCG回路2aを介して入力されるものとの2種類としている。

【0077】

これらの2種類のクロック信号は、ASICまたはFPGA3a内のクロック分岐回路6aに入力されて、クロック分岐回路6aおいて分岐され、片方のみがシステムクロックとして用いられる。このクロック分岐回路6aには、レシーバ側からクロック切り替え信号が入力されており、この切り替え信号によってどちらのクロックを選択するのかが決定される。この切り替え信号としては、図17により説明したイネーブル信号、あるいは、ディスイネーブル信号によるモード切り替え信号を使用することができる。

【0078】

図19はSSCG回路のモードを切り替える構成について説明する図である。

【0079】

図18により説明した例は、トランスミッタ部を構成するASICまたはFPGA3aが、クロック分岐回路6aを有して、SSCG回路2aを介したクロックを使用するか否かを選択するものであったが、図19に示す例は、SSCG回路2a自身が持つモード選択機能を用いて、トランスミッタ部を構成するASICまたはFPGA3aが、SSCG回路2aの機能を有効としたクロックを使用するか否かを選択するものである。

【0080】

SSCG回路2aは、デバイスにもよるが、その機能をオン、オフするモードを選択することが可能に構成されている場合があり、その場合、SSCG2a回路には、モードを設定するための入力ピンが備えられている。図19に示す例では、トランスミッタ部を構成するASICまたはFPGA3aが、該当するピンへの入力(モード切り替え信号)を切り替えることによってモードを変更し、SSCG回路2aの機能(クロック信号を周波数変調する機能)をオンまたはオフにすることが可能である。これにより、トランスミッタ部を構成するASICまたはFPGA3aは、SSCG回路2aの機能を有効としたクロックを使用するか否かを選択するすることが可能となる。このモード切り替え信号は、ASICまたはFPGA3a内で生成される。また、ASICまたはFPGA3aは、前述のモード切り替え信号を、図17により説明したイネーブル信号、あるいは、ディスイネーブル信号によるモード切り替え信号をレシーバ側から受信して生成してもよいし、前述の図17により説明したイネーブル信号、あるいは、ディスイネーブル信号によるモード切り替え信号をそのまま使用してもよい。

【0081】

前述した本発明の実施形態は、送信側の通信装置が、複数ビットに渡って連続した同一のデータを送信し、受信側の通信送信が、受信した複数ビットの同一データの2ビット目を有効なものとするとして説明したが、本発明は、受信側の通信送信が、受信した複数ビットの同一データの2ビット目以降の任意のビットを有効なものとするようにすることもできる。

【0082】

また、本発明は、送信側の通信装置が、SSCG回路を用いない場合、前記第1のモードにより、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記SSCG回路を用いた場合、前記第2のモードにより、前記連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信するようにしてもよい。

【0083】

また、本発明は、送信側の通信装置が、データ送信の開始時に、1クロック周期の中に複数の異なるビットのデータを入れ込んだデータと同一のデータを予め定めた複数回前記受信側の通信装置に送信し、受信側の通信送信から全てのデータを正常に受信することができた旨の報告を受けた場合、前記そのままデータの送信を続行し、受信側の通信装置から全データの内の1回でも正常に受信することができなかった旨の報告を受けた場合、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内の2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信するようにすることができる。

【0084】

また、本発明は、送信側の通信装置が、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内の2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受けた場合、前記連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受ける毎に、順次前記連続する同一データのビット数の最少数を増加させて送信し、受信側の通信装置が、連続する3ビット以上の同一データを持つデータ群の内、3ビット目以降の何れか1ビットのデータを有効なデータとして受信するようにすることができる。

【0085】

前述した本発明の実施形態によれば、コストの安いクロック併走タイプの LVDS ICを使用し、併走クロックの転送レートを落とすことなく、信号の長距離伝送を行うことができ、これにより、本発明による信号の伝送装置を採用するシステムでの処理速度を低下させるようなことを防止することができ、また、システムの変更を少なくすることができるので、システムのコストを抑制することができる。

【0086】

また、前述した本発明の実施形態によれば、受信側において、先頭ビットのアイパターンが十分に開いていない場合、クロックスキューがある場合にも、信号を正しく伝送することができる。さらに、前述した本発明の実施形態によれば、SSCG回路を使用した場合であっても長距離伝送を実現することができ、しかも、SSCG回路を使用した場合、EMIによる信号の伝送への影響を軽減することができる。

【0087】

図20は本発明の実施形態による伝送装置を備える画像形成装置の外観を示す斜視図、図21は図20に示す画像形成装置の構成を説明する縦断面図であり、次に、図20、図21を参照して、本発明の実施形態による伝送装置を備える画像形成装置について説明する。図20、図21に示す画像形成装置は、インクジェット記録装置の例である。

【0088】

図20に示すインクジェット記録装置は、シリアル型インクジェット記録装置であり、図20に示すように記録装置100と、それを支持する本体フレーム170とを備えて構成されている。記録装置100の内部には、ガイドロッド110及び幅ガイド120が掛け渡され、これらのガイドロッド110及び副ガイド120に、キャリッジ151が矢印A方向(主走査方向)に動作可能なように保持されている。キャリッジ151は、タイミングベルト111と接続されており、主走査モータ190と駆動プーリ280とによってタイミングベルト111を駆動することにより主走査方向Aを往復移動する。タイミングベルト111には加圧コロ120によって張力が掛けられており、たるむことなくキャリッジ150を駆動することができる。

【0089】

印字媒体150は、キャリッジ151が往復移動する下部を矢印B方向(副走査方向)に間欠的に搬送され、印字媒体150には、キャリッジ151に搭載された記録ヘッドから吐出されるインクにより所定の画像が形成される。

【0090】

また、記録装置100には、インクを供給するカートリッジ160と記録ヘッドをクリーニングする維持機構126が備えられている。

【0091】

また、キャリッジ151内には、エンコーダセンサが配置されており、キャリッジ151は、主走査方向に掛け渡されたエンコーダシートを連続的に読み取ることにより、主走査方向位置を検知しながら駆動される。

【0092】

図21を参照すると、図21に示す画像形成装置には、ガイドロッド110及び副ガイド120が左右側板203、204間に掛け渡され、これらのガイドロッド110及び副ガイド120にキャリッジ151が軸受け、副ガイド受け部212により保持され、図20に示す矢印Aの主走査方向に摺動可能とされている。

【0093】

キャリッジ515には、黒(K)のインク滴を吐出する記録ヘッド221、222、イエロー(Y)、マゼンタ(M)、シアン(C)の各色のインク滴を吐出する記録ヘッド223、224、225が搭載されている。

【0094】

そして、キャリッジ151を移動走査する主走査機構は、主走査方向の一方側に配置される主走査モータ190と、主走査モータ190によって回転駆動される駆動プーリ207と、主走査方向の他方側に配置された従動プーリ214と、駆動プーリ207と従動プーリ214との間に掛け回されたタイミングベルト209とを備えて構成されている。なお、従動プーリ214は、図示しないテンションスプリングによって外方(駆動プーリ20に対して離れる方向)にテンションが掛けられている。また、タイミングベルト209は、キャリッジ151の背面側に設けたベルト保持部211に一部が固定保持されており、これにより、主走査方向にキャリッジ151を牽引する。キャリッジ151と装置本体との間はキャリッジ側基板206と制御回路等が載置された本体側基板210とを結ぶフレキシブルフラットケーブル(FFC)215により電気的に接続され、FFC215は、主走査の摺動に耐えうるようにされている。

【0095】

また、キャリッジ151の主走査方向に沿うようにエンコーダシート200が配置されており、キャリッジ151に設けたエンコーダセンサ213によりエンコーダシート200を読取る。これにより、キャリッジ151の主走査方向の位置を検知することができる。このキャリッジ151の主走査領域の内、記録領域には、印字媒体150としての用紙が図示しない紙送り機構によってキャリッジ151の主走査方向と直交する図20に矢示Bとして示した方向(副走査方向)に間欠的に搬送される。

【0096】

前述したように構成される画像形成装置は、キャリッジ151を主走査方向に移動させ、図示しない印字媒体としての用紙を間欠的に送りながら、記録ヘッド221〜225を画像情報に応じて駆動して液滴を吐出させることによって印字媒体上に所要の画像を形成することができる。

【0097】

そして、前述した画像形成装置におけるキャリッジ側基板206と本体側基板210とを結ぶFFC215を介して、本体側基板210上の制御回路からキャリッジ151上の記録ヘッド221〜225に送信する記録ヘッド駆動用のデータの伝送のために、図5〜図16までに説明した伝送方法、伝送装置が使用される。なお、図5〜図16までに説明した本発明の実施形態は、FFC3のデータを伝送するラインを1組だけ示して説明したが、前述したような画像形成装置に使用する場合、FFC3のデータを伝送するラインを、複数の記録ヘッド対応に設け、各ラインをLVDSドライバ及びLVDSレシーバのMuxの相互に接続する構成とされる。

【符号の説明】

【0098】

1 FPGA(Field Programmable Gate Array)

2 LVDS(Low Voltage Differential Signal)ドライバ

2a SSCG(Spread Spectrum Clock Generator)回路

3 FFC(Flat Flexible Cable)

4 LVDSレシーバ

10、45 入力ラッチ

11、46 制御部

12、44 PLL(Phase Locked Loop)回路

13、43 Mux回路

14、15、16 差動ドライバ回路

20 FIFO MEMORY

21 セレクタ

22 LVDSドライバ

41、42 差動レシーバ回路

【先行技術文献】

【特許文献】

【0099】

【特許文献1】特開平7−87138号公報

【特許文献2】特開2010−68131号公報

【技術分野】

【0001】

本発明は、伝送装置、伝送方法、画像形成装置、送信装置及び受信装置に係り、特に、併走クロックを用いて長距離の信号伝送を行う伝送装置、伝送方法、前記伝送装置を使用した画像形成装置、前記伝送装置を構成する送信装置及び受信装置に関する。

【背景技術】

【0002】

一般に、プリンタ、複写機等、あるいは、それらの両機能等を備えた複合機において、幅方向が広い用紙に印刷を行う幅広機と呼ばれる装置は、本体と本体に載せた可動部(ヘッド中継上の基板)との間の距離が長くなるために、その間での信号の伝送には長距離伝送を行う必要がある。信号の長距離伝送には、EMIの影響と信号品質の劣化とを避けるため、差動伝送方法が用いられることが多い。また、伝送用のケーブルとしてFFC(Flat Flexible Cable)を用い、差動伝送方法によりデータ伝送を行おうとす場合、FFCが長いと、高周波成分が損失して信号を劣化させるため、これを回避するために転送レートを落として確実に信号の伝送を行う方法に関する従来技術が、例えば、特許文献1等に記載されて知られている。

【0003】

この従来技術は、信号を確実に伝送する目的のために、低コストのLVDS(Low Voltage Differential Signal)ドライバ、LVDSレシーバを使用し、かつ、分周回路と逓倍回路とを使用することにより高周波を低周波に変換し、長距離伝送する信号の転送レートを落として伝送を行う方法に関するものである。すなわち、この従来技術は、長距離伝送したい高周波の信号を送信側の分周回路により一旦汎用のドライバICやレシーバICで処理可能な周波数(低周波)の信号に分周し、低い周波数レートに変換された信号をドライバICから伝送路に送出し、伝送路を介した長距離伝送を行い、この低い周波数レートに変換された信号を受信した受信側のレシーバICが、逓倍回路により受信した低い周波数レートの信号を元の高周波の信号に復元するというものである。

【0004】

また、EMIの影響とそれによる信号品質の劣化とを避けるために、SSCG(Spread Spectrum Clock Generator)を使用する場合があるが、この場合には、クロック変調の影響によりジッタ成分が発生してしまうために信号の伝送が困難となってしまう。そこで、信号の転送レートを落として確実に信号の伝送を行う方法に関する他の従来技術が、例えば、特許文献2等に記載されて知られている。

【0005】

この他の従来技術は、SSCGによる画像への悪影響を低減する目的のために、CCDが原稿を読み取ることにより得られたアナログ電気信号を増幅し、デジタル信号に変換するAFEと、SSCGを利用して所定周波数のクロック信号を周波数変調し、得られた内部基準クロック信号に基づいて、CCD及びAFEを制御する信号であって、周波数変動を有する制御信号を生成するタイミングジェネレータと、デジタル信号に所定の画像処理を実行して得られる画像にSSCGの影響がスジとして現れるかどうかを判定する画像データ判定部とを備え、画像データ判定部が「SSCGの影響がスジとして現れる」と判定した場合に、タイミングジェネレータが生成する制御信号の周波数を変更するというものである。

【発明の概要】

【発明が解決しようとする課題】

【0006】

信号の伝送方法には、クロック埋め込みタイプとクロック併走タイプとがあり、クロック埋め込みタイプは、コストが高いために、一般にはクロック併走タイプが良く用いられている。前述した従来技術は、クロック併走タイプの信号伝送方法を適用して信号の転送レートを落として信号の伝送を行う場合、併走クロックの周波数を落とさなければならず、これに伴って送信側及び受信側の通信装置を構成するFPGA(Field Programmable Gate Array)あるいはASIC(Application Specific Integrated Circuit)のシステムクロックの周波数を落とさなければならず、装置全体の処理速度を低下させてしまうという問題点を生じさせてしまう。

【0007】

本発明の目的は、前述した従来技術の問題点を解決し、併走クロックを使用する信号伝送において、併走クロックの周波数を落とすことなく、信号の長距離伝送を行うことを可能とした伝送装置、伝送方法、前記伝送装置を使用した画像形成装置、前記伝送装置を構成する送信装置及び受信装置を提供することにある。

【課題を解決するための手段】

【0008】

前記目的を達成するため、本発明は、送信側の通信装置と受信側の通信装置との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置において、前記送信側の通信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記受信側の通信装置は、受信したデータの前記少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする。

【発明の効果】

【0009】

本発明によれば、併走クロックの転送レートを落とすことなく、信号の長距離伝送を行うことができ、これにより、本発明による信号の伝送装置を採用するシステムでの処理速度を低下させるようなことを防止することができる。

【図面の簡単な説明】

【0010】

【図1】本発明の実施形態による伝送装置を含む伝送システム全体の概略構成を示すブロック図である。

【図2】図1において、SSCG回路2aの使用状況による伝送波形、すなわち、レシーバ側の入力端で観測したアイパターンの波形を説明する図である。

【図3】受信側の通信装置におけるレシーバスキューマージンについて説明する図である。

【図4】図3で説明したレシーバスキューマージンの規定を満たさない例について説明する図である。

【図5】本発明の一実施形態による伝送装置の構成例を示すブロック図である。

【図6】従来技術による信号の伝送方法の具体例を説明する図である。

【図7】本発明の実施形態による信号の伝送方法の具体例を説明する図である。

【図8】データの伝送方法を切り替えて信号データの送信を行うようにした送信側の通信装置の構成を示すブロック図である。

【図9】本発明の実施形態における送信データ構成の具体例について説明する図である。

【図10】送信側の通信装置の回路構成を示すブロック図である。

【図11】受信側の通信装置であるLVDSレシーバの回路構成を示すブロック図である。

【図12】従来技術による伝送方法の場合に受信側に送信されるシリアルデータのデータ列を示す図である。

【図13】図12に示すシリアルデータをパラレル変換したデータ列を示す図である。

【図14】本発明の実施形態による伝送方法の場合に受信側に送信されるシリアルデータのデータ列を示す図である。

【図15】図14に示すシリアルデータをパラレル変換したデータ列を示す図である。

【図16】Mode切り替え信号の送信データへの埋め込み方法を説明する図である。

【図17】図1に示して説明した伝送システムにより伝送された伝送データが正常に伝送されていることを検証する構成について説明する図である。

【図18】図1に示して説明した伝送システムの送信側のトランスミッタ部を構成するASICまたはFPGA3aに入力されるクロックを切り替える構成について説明する図である。

【図19】SSCG回路のモードを切り替える構成について説明する図である。

【図20】本発明の実施形態による伝送装置を備える画像形成装置の外観を示す斜視図である。

【図21】図20に示す画像形成装置の構成を説明する縦断面図である。

【発明を実施するための形態】

【0011】

以下、本発明による伝送装置、伝送方法、画像形成装置、送信装置及び受信装置の実施形態を図面により詳細に説明する。以下に説明する本発明の実施形態での信号伝送の基本的な考え方は、送信側の通信装置が同一のデータを連続した複数ビットとした複数のデータ群として送信し、受信側の通信装置が送られてきた連続した複数の同一データを含むデータ群の2ビット目以降を有効なデータとするものである。

【0012】

図1は本発明の実施形態による伝送装置を含む伝送システム全体の概略構成を示すブロック図である。

【0013】

図1に示す伝送システムは、送信側の装置である送信装置を、クロック発振器OSC1aと、SSCG回路2aと、トランスミッタ部を構成するASICまたはFPGA3aとにより構成し、また、受信側装置である受信装置を、レシーバ部を構成するASICまたはFPGA4aにより構成し、送信装置を構成するASICまたはFPGA3aと受信装置を構成するASICまたはFPGA4aとを伝送路により接続して構成されている。

【0014】

そして、クロック発振器OSC1aからのクロック信号が、SSCG回路2aを介してシステムクロックとしてトランスミッタ部を構成するASICまたはFPGA3aに入力され、ASICまたはFPGA3aは、入力されたシステムクロックを使用して、送信データをレシーバ部を構成するASICまたはFPGA4aに送信している。

【0015】

前述のような構成を有する伝送システムは、EMIの影響とそれによる信号品質の劣化とを避けることができるものであるが、SSCGによるクロック変調の影響によりジッタ成分が発生してしまうために信号の伝送が困難となってしまうことがある。そこで、信号の転送レートを落として確実に信号の伝送を行う必要が生じる。

【0016】

また、図1に示す伝送システムに用いられているASIC、FPGA等のデバイスによってはSSCGに対応していない場合がある。例えば、入力についてはSSCGに対応したスキューマージンが規定されているが、出力に関しては規定されていないといった場合がある。この場合、SSCG非対応のデバイスから出力される信号を評価する必要がでてくる。この信号の評価は、本来、レシーバ側の入力端でのスキューマージンであるRSKM(Receiver Skew Margine)を評価すれば十分であったのが、SSCGを使用している場合、正常に出力がなされる保証はない。さらに、トランスミッタ部の出力に関しても評価しなければならない場合があり、工数が膨大になってしまう。

【0017】

後述する本発明においては、正常に伝送がなされていることを確認してから伝送を開始するため、データの取りこぼしを防ぐことが可能となり、また、波形の評価処理についても削減することが可能となる。

【0018】

図2は図1において、SSCG回路2aの使用状況による伝送波形、すなわち、レシーバ側の入力端で観測したアイパターンの波形を説明する図であり、図2(a)はSSCG回路OFFのアイパターンの波形、図2(b)はSSCG回路を−1%(ダウンスプレッド)としたときのアイパターンの波形、図2(c)はSSCG回路を−3%(ダウンスプレッド)としたときのアイパターンの波形を示している。アイパターンは、信号を繰り返し伝送して重ね合わせることによって得ることが可能であり、このアイパターンにより伝送信号を正しく評価することが可能なアイパターンの時間幅を決定することができ、それにより、信号を正しく評価することができる。

【0019】

図2に示す3つのアイパターンの波形から、SSCG回路の変調レートを上げるにつれてジッタ成分が増加していることが判る。また、SSCG回路を使用した場合、ドライバ側からの反射による影響も顕著となる。

【0020】

図3は受信側の通信装置におけるレシーバスキューマージンについて説明する図であり、図1の説明におけるレシーバの規定値であるスキューマージンを説明するものである。図3には、クロック併走型レシーバにおいて、ある転送レートのデータを受信する場合のレシーバの規定値(RSKM:レシーバスキューマージン)について示している。

【0021】

レシーバの規定値は、転送されるデータの1ビットの時間幅を1UIとしたときに、データを正しく受信するために許されるレシーバスキューマージンの値であり、図3に示す例では、規定値を評価するための基準としてのレシーバスキューマージンの値が0.25UI以下であることである。そして、このレシーバスキューマージンの値は、クロックエッジのなまりによるトリガポイントのズレと、伝送路のスキュー+送信側のドライバ出力端でのスキューと、ジッタ量との和として算出することができる。

【0022】

もし、レシーバスキューマージンを満たすことができなかった場合、UIの値を大きくするために、転送クロックのレートを落とす(受信側でのシリアル/パラレル変換比率は固定)、または、シリアル/パラレル変換比率を下げる(転送クロックは固定)といった方法を採用することが考えられる。但し、レシーバ側のシリアル/パラレル変換比率が固定であるといった制限がある場合、必然的に前者の方法を採用することになる。

【0023】

また、受信側のレシーバの種類によっては、レシーバスキューマージンの値が転送クロックのレートに依存しないものもあり、この場合、長距離伝送時の信号の減衰特性によって、クロックがより鈍るために信号(データ)を正常に伝送することが不可能となる。さらに、EMI対策として、SSCG回路を用いた場合ジッタ成分が増大し、この結果、クロック及びデータのマージンが削られてしまい、信号を正常に伝送することが不可能となる。

【0024】

本発明の実施形態による伝送装置は、ジッタ量についてデータの立ち上がりに関して緩和することができるので、レシーバスキューマージンを満たすことが従来技術による伝送装置と比較して容易であるという優位性を有している。これにより、本発明の実施形態によれば、より安価なFFC、LVDSレシーバの組み合わせにより長距離伝送を実現することが可能となる。また、前述までの説明において、SSCG回路2aを用いた伝送システムとその課題とついて説明したが、本発明の実施形態による伝送装置を含む伝送システムは、図1に示すシステムにおけるSSCG回路2aを用いない伝送システムであっても、レシーバスキューマージンを満たすことが容易になる。

【0025】

図4は図3で説明したレシーバスキューマージンの規定を満たさない例について説明する図である。

【0026】

一般に、信号を長距離伝送すると信号の減衰が発生し、信号の立ち上がりがなまってしまい、レシーバスキューマージンの値が図3により説明した規定値より大きくなって、規定を満たさなくなってしまう。この結果、信号を繰り返し伝送し重ね合わせて、信号を正しく受信することができる時間幅を決定し、信号の評価を行うアイパターンは、図4にデータDATAとして示す図4の長四角で示すように狭くなってしまうことになり、レシーバのスキューマージンの規定値を満たすことができなくなってしまう。

【0027】

以下に説明する本発明の実施形態は、送信側の通信装置が同一の1ビットのデータを連続した複数ビットとして送信し、受信側の通信装置が送られてきた連続した複数の同一データの2ビット目以降の1ビットを有効なデータとするものである。

【0028】

図5は本発明の一実施形態による伝送装置の構成例を示すブロック図である。ここで説明する本発明の実施形態による伝送装置は、前提条件として、信号の伝送方法にクロック併走タイプの信号伝送方法を使用するものとする。

【0029】

図5に示す本発明の実施形態は、図1における送信装置のトランスミッタ部を構成するFPGA3aと受信装置のレシーバ部を構成するFPGA4aとに対応するものであり、送信側の通信装置を構成しているFPGA1と受信側の通信装置としてのLVDSレシーバ4とが信号用及びクロック用のFFC3により接続されて構成されている。そして、FPGA1内には、LVDSドライバ2が構成されており、LVDSドライバ2は、入力される送信データ信号である Tx_in a1をラッチする入力ラッチ10と、入力されるFPGA1のシステムクロックであるクロック信号a2を受け、入力ラッチ10への書き込み、読み出しを制御する制御部11と、入力されるクロック信号a2から信号伝送用のクロック信号を生成するPLL(Phase Locked Loop)回路12と、入力ラッチ10からの送信データをパラレル/シリアル変換するMux回路13と、Mux回路13及びPLL回路12のそれぞれからの送信データ及びクロック信号をLVDSに変換する差動ドライバ回路14、15とにより構成されている。なお、本発明の実施形態による伝送装置を利用する広幅機におけるはFFCの長さは、一般に、1m〜3mであることが多い。

【0030】

次に、前述したように構成される本発明の実施形態の伝送装置における信号の流れについて説明する。

【0031】

LVDSドライバ2へは、FPGA1の内部からパラレルのデータ信号である Tx_in a1とクロック信号a2が入力される。但し、このクロック信号はFPGA1のシステムクロックである。なお、図示しないが、FPGA1の内部には、他の処理回路等が含まれ、データ信号である Tx_in a1とクロック信号a2は、FPGA1の外部から与えられるものである。

【0032】

データ信号である Tx_in a1は、LVDSドライバ2内の入力ラッチ回路10に入力され、制御部11によりラッチするタイミングがコントロールされて入力ラッチ回路10にラッチされる。入力ラッチ回路10にラッチされたデータ信号 Tx_in は、制御部11にコントロールされて読み出されてMux回路13に渡される。そして、Mux回路13を介してパラレル/シリアル変換されたデータ信号は、その信号レベルが差動ドライバ回路14においてLVDSに変換され、FFC3を経てLVDSレシーバ4へ送信される。

【0033】

また、クロック信号a2は、制御部11に供給されると共に、PLL回路12を介してMux回路13にも供給され、そのレベルが差動ドライバ回路15においてLVDSに変換され、FFC3を経てLVDSレシーバ4へ送信される。

【0034】

なお、本発明の実施形態では、同一の1ビットのデータを連続した複数ビットのデータ列とするデータ変換を行っているが、このための処理は、FPGA1内のLVDSドライバ2の前段に設けられる図示しない論理回路により行われる。これについては、図10を参照して後述する。

【0035】

図6は従来技術による信号の伝送方法の具体例を説明する図、図7は本発明の実施形態による信号の伝送方法の具体例を説明する図であり、次に、図6、図7を参照して、従来技術と本発明の実施形態とによる信号伝送方法の相違について説明する。なお、ここで説明する例は、シリアル/パラレルの比率が1:7の場合、すなわち、1クロックサイクル内に7ビットのデータを入れ込んで伝送することができる場合の例であり、また、併走クロックである転送クロックとして、1クロックのレベルHighとLow とが3:4の非対象クロック信号を使用した例である。なお、1クロックサイクル内に何ビットのデータを入れ込むかは、任意に設定することができる。

【0036】

図6に示す従来技術による伝送方法の場合、送信側の通信装置は、転送データとして、7ビットのパラレルの転送データa〜gをシリアル変換して、aからgの順で1クロックサイクル内に転送する。受信側の通信装置は、転送されてきたデータの各ビットが有効なものとして受信する。このとき、正常にデータが伝送されるためには、各データのそれぞれのアイパターンが、図3、図4を参照して説明したように受信側の通信装置であるレシーバの規定値を確保できていることが必要となる。

【0037】

前述したような従来技術でのデータの伝送に対して、図7に示す本発明の実施形態による伝送方法の場合、送信側の通信装置であるFPGA1内のLVDSドライバ2は、転送データとして、先に説明したように併走クロックの1サイクル内に伝送することができる7ビット分のデータの内2ビットまたは3ビットのデータを、それぞれ同一の連続する複数ビットのシリアルデータとして併走クロックの1サイクル内で送信している。図示している例の場合、転送データは、a、a、a、b、b、b、bの順で、各群が同一データを持つ2群のデータとして送信されるとして示しているが、この順は、a、a、a、b、b、c、cの順で、各群が同一データを持つ3群のデータとすることもできる。受信側の通信装置は、転送されてきた連続する複数の同一のデータを持つデータ群の2ビット目のデータ、あるいは、2ビット目以降の何れか1ビットのデータを有効なものとして受信する。図示例では、2ビット目のデータaと2ビット目のデータbとを有効なものとして受信することとしているが、データbについては、3ビット目あるいは4ビット目のデータを有効なものとして受信してもよい。また、転送データとして、a、a、a、b、b、c、cの順でデータが送信されてきた場合、それぞれ、2ビット目のデータa、b、cが有効なデータとして受信される。

【0038】

本発明の実施形態は、前述したように同一のデータを複数ビットに渡って送信することによって、受信側のレシーバでデータを受信するために規定されるアイパターンを広げることができるので、伝送するための条件が悪くなった(図7に示して説明した例では、1クロックサイクル内で2ビットまたは3ビットのデータしか転送できない)としても、受信側の通信装置としてのレシーバの規定値を確保することができ、確実にデータの転送を行うことが可能となる。

【0039】

図8はデータの伝送方法を切り替えて信号データの送信を行うようにした送信側の通信装置の構成を示すブロック図である。

【0040】

図8に示す送信側の通信装置は、図5により説明した送信側の通信装置の場合と同様に、送信側の通信装置を構成するFPGA1内に、LVDSドライバ2が構成されており、LVDSドライバ2は、入力される送信データ信号である Tx_in a1及びMode切り替え信号a3をラッチする入力ラッチ10と、入力されるFPGA1のシステムクロックであるクロック信号a2を受け、入力ラッチ10への書き込み、読み出しを制御する制御部11と、入力されるクロック信号a2から信号伝送用のクロック信号を生成するPLL(Phase Locked Loop)回路12と、入力ラッチ10からの送信データ及びMode切り替え信号をパラレル/シリアル変換するMux回路13と、Mux回路13及びPLL回路12のそれぞれからの送信データ、Mode信号及びクロック信号をLVDSに変換する差動ドライバ回路14、15、16とにより構成されている。

【0041】

図8に示す送信側の通信装置は、図5に示して説明した送信側の通信装置が、データ信号として Tx_in a1のみを伝送するのに対して、Mode切り替え信号a3を追加して他のデータ信号と共に伝送を行うようにしたものである。

【0042】

図8に示して説明したように構成される送信側の通信装置を使用する伝送装置は、Mode切替信号を用いることによって、受信側の通信装置のレシーバに、信号の伝送方法が、前述したような本発明の実施形態による伝送方法であるか、従来技術として説明したような送信側の通信装置が転送データとして送信した1クロックサイクル内の全データを、受信側の通信装置が有効なものとして受信する伝送方法であるかを判断させて、その伝送方法に従った処理を実行させることができる。

【0043】

図9は本発明の実施形態における送信データ構成の具体例について説明する図である。図9に示す例においても、図6、図7とは図の表記が左右逆となっているが、図6、図7により説明した場合と同様に転送データの変換前のデータd1を、1クロックサイクル内でデータaからデータgの7ビットがデータaから順に送信されるものであるとし、これらのデータa〜gを1つのクロックサイクルの中で、2ビットのデータd2、2ビットのデータd3、3ビットのデータd4の3回に分け、3クロックサイクルで送信するものとしている。

【0044】

そして、1回目の送信時には変換前の2ビットのデータa、bが取り出され、それらのデータが1クロックサイクル内で送信されるように変換される。この場合、変換後のデータ列は、3ビットのa、a、aのデータ列と、4ビットのb、b、b、bのデータ列との2つのデータ列とされ、このデータ列d2がLVDSドライバに送られ、受信側に送信されることになる。

【0045】

また、2回目の送信時には変換前の2ビットのデータc、dが取り出され、それらのデータが次の1クロックサイクル内で送信されるように変換される。この場合、変換後のデータ列は、3ビットのc、c、cのデータ列と、4ビットのd、d、d、dのデータ列との2つのデータ列とされ、このデータ列d3がLVDSドライバに送られ、受信側に送信されることになる。

【0046】

また、3回目の送信時には変換前の3ビットのデータe、f、gが取り出され、それらのデータが次の1クロックサイクル内で送信されるように変換される。この場合、変換後のデータ列は、2ビットのe、eのデータ列と、2ビットのf、fのデータ列と、3ビットのg、g、gのデータ列との3つのデータ列とされ、このデータ列d4がLVDSドライバに送られ、受信側に送信されることになる。

【0047】

なお、図9には、併走クロックの波形を示していないが、前述したようなデータの変換を行うと、3回目の送信のように、併走クロックの1サイクル内における波形の立ち下がり部分を挟んで同一のデータが並べられるようになる場合が生じるが、併走クロックの1サイクル内における波形の立ち下がり部分のエッジのなまりは、図7、図3により説明したレシーバの規定値に影響を及ぼすことはなく、本発明を実施する上で何ら問題となることはない。

【0048】

前述したようなデータの変換は、変換後のデータが2ビット以上同一のデータとしたデータ列とされていればよく、前述の例にとらわれることはない。また、伝送環境が悪いときには、必要に応じて変換後のデータ列の構成を変更して対応することができる。

【0049】

図10は送信側の通信装置の回路構成を示すブロック図である。図10に示す送信側の通信装置の回路構成は、図8により説明した送信側の通信装置であるFPGA1の内部回路構成を示すものである。

【0050】

図10に示すように、送信側の通信装置であるFPGA1は、その内部に、図8に示して説明したものと同一のLVDSドライバ22と、外部から入力される送信データ信号である Tx_in a1及びMode切り替え信号a3を一時的に保持する FIFO MEMORY20と、FIFO MEMORY20 から出力されるデータ列、外部から入力される送信データ信号である Tx_in a1及びMode切り替え信号a3の一方を選択してLVDSドライバ22渡すセレクタ21とを有して構成されている。

【0051】

前述したように構成される送信側の通信装置は、パラレルデータ信号として入力される送信データ信号 Tx_in a1を、Modeセレクト信号a3によって、従来技術の場合と同様な方法による伝送方法で送信するか、本発明の実施形態による伝送方法で送信するかを選択することが可能である。そして、本発明の実施形態による伝送方法を使用し、複数ビットのデータ連続して送信する場合、入力されるデータ信号 Tx_in a1は、FIFO MEMORY20 に一旦保持された後に、セレクタ21により選択されてLVDSドライバ22へ入力されることになる。すなわち、前述した送信側の通信装置において、入力されたデータ信号 Tx_in a1の変換前のデータは、一旦、FIFO MEMORY20 に格納され、送信されるデータが、順次セレクタ24に送られことになる。本発明の実施形態により伝送方法の場合、図9により説明したように、変換前の7ビットのデータ列が3回に分けて送信されるので、FIFO MEMORY20 から出力されるデータをセレクタに書き込む際には、3回に分けて書き込まれる。セレクタに書き込まれたデータは、順次LVDSドライバ22へ転送される。

【0052】

前述から判るように、本発明の実施形態による伝送方法を使用した場合、外部からのデータ信号 Tx_in a1がFIFO MEMORY20 に入力される速度に対して、FIFO MEMORY20 からセレクタに出力される速度が1/3になるので、前述のFIFO MEMORY20 は、その入出力の速度差を吸収する機能を果たしている。

【0053】

また、従来技術の場合と同様な方法による伝送方法を採用する場合、入力される送信データ信号である Tx_in a1及びMode切り替え信号a3は、FIFO MEMORY 20を介することなく、セレクタ21に入力され、そのままセレクタ21を通ってLVDSドライバ22へ送信される。

【0054】

前述で説明した送信側の通信装置におけるFIFO MEMORY 20及びセレクタ21が、入力される送信データ信号を、同一のデータが連続した複数ビットのデータ列なるようにデータ変換を行う論理回路を構成ている。

【0055】

図11は受信側の通信装置であるLVDSレシーバの回路構成を示すブロック図である。

【0056】

図11に示す受信側の通信装置であるLVDSレシーバ4は、送信側のLVDSドライバ2から送信されてきたデータ信号、併走クロック信号を受け取る差動レシーバ41、42と、データ信号をシリアル/パラレル変換するMux回路43と、クロック信号を受け取るPLL回路44と、Mux回路43からのデータ信号を一時的に保持する入力ラッチ回路45と、入力ラッチ回路45の書き込み、読み出しを制御する制御回路46とにより構成される。

【0057】

前述したように構成される受信側の通信装置において、LVDSレシーバ4には、FFCを介してシリアルデータと併走クロックとが入力される。それらのデータは、差動レシーバ41、42においてそれらのレベルが論理レベルに変換されると共に、差動信号がシングルエンドの信号に変換される。そして、データは、Mux回路43に入力され、Mux回路43でシリアル/パラレル変換される。入力されたクロック信号は、PLL回路44を経てMux回路43、制御回路46に供給されると共に、外部のシステムクロックとして出力される。Mux回路43から出力されたパラレルのデータ信号はラッチ回路45を経て外部へ出力される。制御回路46は、Mux回路43から出力されたパラレルのデータ信号をラッチ回路45に書き込む制御を行う。

【0058】

前述において、LVDSレシーバ4の外部へ出力されたデータは、データの伝送が本発明による伝送方法を示すModeで行われていた場合、後述するような複数の同一ビットのデータ列の先頭ビットを捨てる処理が行われ、データの伝送が従来技術による伝送方法を示すModeで行われていた場合、データを捨てることなく、1つのクロックサイクル内に含まれる全ビットのデータが有効なデータであるものとして扱うように処理が行われる。

【0059】

次に、本発明の実施形態における受信側の通信装置のLVDSレシーバ4の出力側に接続された論理回路で、受信した複数の同一ビットのデータ列の先頭ビットを捨てる処理について説明するが、まず、従来技術による伝送方法の場合について説明する。

【0060】

図12は従来技術による伝送方法の場合に受信側に送信されるシリアルデータのデータ列を示す図、図13は図12に示すシリアルデータをパラレル変換したデータ列を示す図である。

【0061】

従来技術による伝送方法の場合、全てのビットx1〜x7が有効なビットであり、図12に示すように、x1からx7の順にシリアルデータ列として受信側の通信送信に送信される。このシリアルデータ列は、受信側の通信装置のレシーバ回路によりシリアル/パラレル変換されて、図13に示すようなビットx1〜x7のパラレルデータとされる。このビットx1〜x7のパラレルデータの各ビットは、全て有効なデータとして扱われてレシーバ回路から出力される。

【0062】

図14は本発明の実施形態による伝送方法の場合に受信側に送信されるシリアルデータのデータ列を示す図、図15は図14に示すシリアルデータをパラレル変換したデータ列を示す図である。

【0063】

本発明の実施形態による伝送方法の場合も、図14に示すように、従来技術の場合と同様に、1クロックサイクル内にビットx1からx7の順に送信データがシリアルデータ列として受信側の通信送信に送信される。このシリアルデータ列は、受信側の通信装置のレシーバ回路によりシリアル/パラレル変換されて、図15に示すようなビットx1〜x7のパラレルデータとされる。

【0064】

本発明の実施形態による伝送方法の場合、送信する7ビットのデータのビットx1〜x7の内、x2、x5との2ビットのみが有効データである。このデータ列を受信側の通信装置におけるレシーバ回路でシリアル/パラレル変換すると図15に示すようになる。この場合、x2とx5との2ビットのみが有効データであるため、このデータのみをレシーバから出力させる。

【0065】

前述において、受信側の通信装置としてのレシーバ回路がFPGAに内蔵されて構成去れている場合、有効なx2とx5との2ビットのデータのみを外部に出力させ、また、レシーバが汎用ICである場合、該当の出力ピンのみを外部と接続することにより、先頭ビットを捨てるようにすればよい。

【0066】

図16はMode切り替え信号の送信データへの埋め込み方法を説明する図である。

【0067】

Mode切り替え信号を受信側の通信装置へ送信する方法としては、2つの方法がある。その1つは、Mode切り替え信号を送信データ内に埋め込んで、常時送信する方法、または、必要なときに何時でも送信することができるようにした方法であり、もう1つは、送信すべき一連のデータを送信する前にMode切り替え信号を送信する方法である。図16に示す例は、Mode切り替え信号を送信データ内に埋め込んだ場合の例である。

【0068】

Mode切り替え信号を送信データ内に埋め込んで常時送信する場合、図16に示すように、受信側の通信装置であるレシーバ回路が有効とするデータの中に埋め込むことによって実現することが可能である。もちろん、Mode切り替え信号のデータについても、2ビット以上のデータのかたまりとして送信する必要がある。このようなMode切り替え信号の送信方法は、Mode切り替え信号用に、送信すべき一連のデータの中に2ビット以上を常に確保しなければならないため、送信データの転送レートそのものは落ちてしまうが、データの送信中であってもModeを切り替えることができるというメリットを得ることができる。

【0069】

一方、送信すべき一連のデータを送る前にMode切り替え信号を送る場合、送信データの転送レートを落とすことがなく、Mode切り替え信号を常時送る方法よりも送信データの転送レートが早いが、送信データの送信途中でModeを切り替えることができないというデメリットが生じることになる。

【0070】

図17は図1に示して説明した伝送システムにより伝送された伝送データが正常に伝送されていることを検証する構成について説明する図である。

【0071】

伝送データが正常に伝送されているか否かで特に問題となるのは受信装置のレシーバ部を構成するFPGA4a内のLVDSレシーバがSSCGに対応していない場合である。SSCGをかけた信号が正常に出力されない場合、図1に示した伝送システムを使用した画像形成装置では、出力されたデータによる画像に、画像チリや縦筋が生じる等の影響を与えることがある。このため、間違ったデータが後段に出力されることを防止する必要がある。このため、伝送波形が正常に伝送されていることを確認する必要がある。本発明の実施形態では、そのための手段として、比較回路をLVDSレシーバの直後に配置することとしている。なお、このような検証は、送信側の通信装置が、SSCG回路を使用していない場合にも行われてよい。

【0072】

図17に示した伝送データが正常に伝送されていることを検証するための構成は、図1に示して説明したシステムのレシーバ部であるFPGA4aの後段に比較回路5aを接続したものである。そして、図17には示していない送信側のトランスミッタ部を構成するASICまたはFPGA3aから画像データを送信する直前に予め定めたパターンを有するテストパターンを複数回送信させる。レシーバ側の比較回路5aは、送信されてきたテストパターンを、予め決められているパターンと比較し、合致しているときにイネーブル信号をLVDSレシーバ(FPGA)4aに入力し、比較の結果が複数回(テストパターンの送信回数より少なくてもよい)に渡って合致しなかったときにディスイネーブル信号をLVDSレシーバ(FPGA)4aに入力する。なお、前述のテストパターンは、複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群により構成されたものとする。

【0073】

また、前述のイネーブル信号、あるいは、ディスイネーブル信号は、送信側のトランスミッタ部を構成するASICまたはFPGA3aへ送信することができ、これにより、送信側において、受信したイネーブル信号、あるいは、ディスイネーブル信号をモード切り替え信号として用い、SSCG回路の使用の可否を選択するようにすることができる。また、送信側でSSCG回路を使用しておらず、かつ、ディスイネーブル信号を受信した場合、連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上としたテストパターンで検証を行うこと等も可能である。そして、送信側の通信装置は、テストパターンを、複数ビットの内の3ビット以上を連続する同一データとし、これによる検証の結果が正常であり、受信側からイネーブル信号を受けた場合、その後のデータの送信を連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信する。送信側の通信装置は、テストパターンの同一データのビット数を順次増加させていき、受信側の通信送信からデータを正常に受信することができなかった旨の報告を受ける毎に、順次前記連続する同一データのビット数の最少数を増加させて送信するようにする。さらに、ビット幅を最大に広げても(SSCG回路を使用しない場合にも)正常に信号を送信することができなかった場合、SC(Serviceman Call)という形でエラーを発することもできる。

【0074】

前述では、伝送データが正常に伝送されていることの検証を、送信側の通信装置からテストパターンを送信することにより行うとして説明したが、この検証は、実際のデータ送信時に行うようにすることもできる。その場合、送信する画像データを誤り検出可能なデータとし、受信側において、受信した画像データに対する誤り検出を行うようにすればよい。

【0075】

図18は図1に示して説明した伝送システムの送信側のトランスミッタ部を構成するASICまたはFPGA3aに入力されるクロックを切り替える構成について説明する図である。

【0076】

図1に示して説明した伝送システムの例では、クロック発振器OSC1aからのクロック信号をSSCG回路2aを介してシステムクロックとしてトランスミッタ部を構成するASICまたはFPGA3aに入力していたが、図18に示す例では、送信側のトランスミッタ部を構成するASICまたはFPGA3a内にクロック分岐回路6aを設け、OSC回路1aからASICまたはFPGA3aに入力するクロック信号を、OSC回路1aから直接入力されるものと、SSCG回路2aを介して入力されるものとの2種類としている。

【0077】

これらの2種類のクロック信号は、ASICまたはFPGA3a内のクロック分岐回路6aに入力されて、クロック分岐回路6aおいて分岐され、片方のみがシステムクロックとして用いられる。このクロック分岐回路6aには、レシーバ側からクロック切り替え信号が入力されており、この切り替え信号によってどちらのクロックを選択するのかが決定される。この切り替え信号としては、図17により説明したイネーブル信号、あるいは、ディスイネーブル信号によるモード切り替え信号を使用することができる。

【0078】

図19はSSCG回路のモードを切り替える構成について説明する図である。

【0079】

図18により説明した例は、トランスミッタ部を構成するASICまたはFPGA3aが、クロック分岐回路6aを有して、SSCG回路2aを介したクロックを使用するか否かを選択するものであったが、図19に示す例は、SSCG回路2a自身が持つモード選択機能を用いて、トランスミッタ部を構成するASICまたはFPGA3aが、SSCG回路2aの機能を有効としたクロックを使用するか否かを選択するものである。

【0080】

SSCG回路2aは、デバイスにもよるが、その機能をオン、オフするモードを選択することが可能に構成されている場合があり、その場合、SSCG2a回路には、モードを設定するための入力ピンが備えられている。図19に示す例では、トランスミッタ部を構成するASICまたはFPGA3aが、該当するピンへの入力(モード切り替え信号)を切り替えることによってモードを変更し、SSCG回路2aの機能(クロック信号を周波数変調する機能)をオンまたはオフにすることが可能である。これにより、トランスミッタ部を構成するASICまたはFPGA3aは、SSCG回路2aの機能を有効としたクロックを使用するか否かを選択するすることが可能となる。このモード切り替え信号は、ASICまたはFPGA3a内で生成される。また、ASICまたはFPGA3aは、前述のモード切り替え信号を、図17により説明したイネーブル信号、あるいは、ディスイネーブル信号によるモード切り替え信号をレシーバ側から受信して生成してもよいし、前述の図17により説明したイネーブル信号、あるいは、ディスイネーブル信号によるモード切り替え信号をそのまま使用してもよい。

【0081】

前述した本発明の実施形態は、送信側の通信装置が、複数ビットに渡って連続した同一のデータを送信し、受信側の通信送信が、受信した複数ビットの同一データの2ビット目を有効なものとするとして説明したが、本発明は、受信側の通信送信が、受信した複数ビットの同一データの2ビット目以降の任意のビットを有効なものとするようにすることもできる。

【0082】

また、本発明は、送信側の通信装置が、SSCG回路を用いない場合、前記第1のモードにより、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記SSCG回路を用いた場合、前記第2のモードにより、前記連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信するようにしてもよい。

【0083】

また、本発明は、送信側の通信装置が、データ送信の開始時に、1クロック周期の中に複数の異なるビットのデータを入れ込んだデータと同一のデータを予め定めた複数回前記受信側の通信装置に送信し、受信側の通信送信から全てのデータを正常に受信することができた旨の報告を受けた場合、前記そのままデータの送信を続行し、受信側の通信装置から全データの内の1回でも正常に受信することができなかった旨の報告を受けた場合、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内の2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信するようにすることができる。

【0084】

また、本発明は、送信側の通信装置が、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内の2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受けた場合、前記連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受ける毎に、順次前記連続する同一データのビット数の最少数を増加させて送信し、受信側の通信装置が、連続する3ビット以上の同一データを持つデータ群の内、3ビット目以降の何れか1ビットのデータを有効なデータとして受信するようにすることができる。

【0085】

前述した本発明の実施形態によれば、コストの安いクロック併走タイプの LVDS ICを使用し、併走クロックの転送レートを落とすことなく、信号の長距離伝送を行うことができ、これにより、本発明による信号の伝送装置を採用するシステムでの処理速度を低下させるようなことを防止することができ、また、システムの変更を少なくすることができるので、システムのコストを抑制することができる。

【0086】

また、前述した本発明の実施形態によれば、受信側において、先頭ビットのアイパターンが十分に開いていない場合、クロックスキューがある場合にも、信号を正しく伝送することができる。さらに、前述した本発明の実施形態によれば、SSCG回路を使用した場合であっても長距離伝送を実現することができ、しかも、SSCG回路を使用した場合、EMIによる信号の伝送への影響を軽減することができる。

【0087】

図20は本発明の実施形態による伝送装置を備える画像形成装置の外観を示す斜視図、図21は図20に示す画像形成装置の構成を説明する縦断面図であり、次に、図20、図21を参照して、本発明の実施形態による伝送装置を備える画像形成装置について説明する。図20、図21に示す画像形成装置は、インクジェット記録装置の例である。

【0088】

図20に示すインクジェット記録装置は、シリアル型インクジェット記録装置であり、図20に示すように記録装置100と、それを支持する本体フレーム170とを備えて構成されている。記録装置100の内部には、ガイドロッド110及び幅ガイド120が掛け渡され、これらのガイドロッド110及び副ガイド120に、キャリッジ151が矢印A方向(主走査方向)に動作可能なように保持されている。キャリッジ151は、タイミングベルト111と接続されており、主走査モータ190と駆動プーリ280とによってタイミングベルト111を駆動することにより主走査方向Aを往復移動する。タイミングベルト111には加圧コロ120によって張力が掛けられており、たるむことなくキャリッジ150を駆動することができる。

【0089】

印字媒体150は、キャリッジ151が往復移動する下部を矢印B方向(副走査方向)に間欠的に搬送され、印字媒体150には、キャリッジ151に搭載された記録ヘッドから吐出されるインクにより所定の画像が形成される。

【0090】

また、記録装置100には、インクを供給するカートリッジ160と記録ヘッドをクリーニングする維持機構126が備えられている。

【0091】

また、キャリッジ151内には、エンコーダセンサが配置されており、キャリッジ151は、主走査方向に掛け渡されたエンコーダシートを連続的に読み取ることにより、主走査方向位置を検知しながら駆動される。

【0092】

図21を参照すると、図21に示す画像形成装置には、ガイドロッド110及び副ガイド120が左右側板203、204間に掛け渡され、これらのガイドロッド110及び副ガイド120にキャリッジ151が軸受け、副ガイド受け部212により保持され、図20に示す矢印Aの主走査方向に摺動可能とされている。

【0093】

キャリッジ515には、黒(K)のインク滴を吐出する記録ヘッド221、222、イエロー(Y)、マゼンタ(M)、シアン(C)の各色のインク滴を吐出する記録ヘッド223、224、225が搭載されている。

【0094】

そして、キャリッジ151を移動走査する主走査機構は、主走査方向の一方側に配置される主走査モータ190と、主走査モータ190によって回転駆動される駆動プーリ207と、主走査方向の他方側に配置された従動プーリ214と、駆動プーリ207と従動プーリ214との間に掛け回されたタイミングベルト209とを備えて構成されている。なお、従動プーリ214は、図示しないテンションスプリングによって外方(駆動プーリ20に対して離れる方向)にテンションが掛けられている。また、タイミングベルト209は、キャリッジ151の背面側に設けたベルト保持部211に一部が固定保持されており、これにより、主走査方向にキャリッジ151を牽引する。キャリッジ151と装置本体との間はキャリッジ側基板206と制御回路等が載置された本体側基板210とを結ぶフレキシブルフラットケーブル(FFC)215により電気的に接続され、FFC215は、主走査の摺動に耐えうるようにされている。

【0095】

また、キャリッジ151の主走査方向に沿うようにエンコーダシート200が配置されており、キャリッジ151に設けたエンコーダセンサ213によりエンコーダシート200を読取る。これにより、キャリッジ151の主走査方向の位置を検知することができる。このキャリッジ151の主走査領域の内、記録領域には、印字媒体150としての用紙が図示しない紙送り機構によってキャリッジ151の主走査方向と直交する図20に矢示Bとして示した方向(副走査方向)に間欠的に搬送される。

【0096】

前述したように構成される画像形成装置は、キャリッジ151を主走査方向に移動させ、図示しない印字媒体としての用紙を間欠的に送りながら、記録ヘッド221〜225を画像情報に応じて駆動して液滴を吐出させることによって印字媒体上に所要の画像を形成することができる。

【0097】

そして、前述した画像形成装置におけるキャリッジ側基板206と本体側基板210とを結ぶFFC215を介して、本体側基板210上の制御回路からキャリッジ151上の記録ヘッド221〜225に送信する記録ヘッド駆動用のデータの伝送のために、図5〜図16までに説明した伝送方法、伝送装置が使用される。なお、図5〜図16までに説明した本発明の実施形態は、FFC3のデータを伝送するラインを1組だけ示して説明したが、前述したような画像形成装置に使用する場合、FFC3のデータを伝送するラインを、複数の記録ヘッド対応に設け、各ラインをLVDSドライバ及びLVDSレシーバのMuxの相互に接続する構成とされる。

【符号の説明】

【0098】

1 FPGA(Field Programmable Gate Array)

2 LVDS(Low Voltage Differential Signal)ドライバ

2a SSCG(Spread Spectrum Clock Generator)回路

3 FFC(Flat Flexible Cable)

4 LVDSレシーバ

10、45 入力ラッチ

11、46 制御部

12、44 PLL(Phase Locked Loop)回路

13、43 Mux回路

14、15、16 差動ドライバ回路

20 FIFO MEMORY

21 セレクタ

22 LVDSドライバ

41、42 差動レシーバ回路

【先行技術文献】

【特許文献】

【0099】

【特許文献1】特開平7−87138号公報

【特許文献2】特開2010−68131号公報

【特許請求の範囲】

【請求項1】

送信側の通信装置と受信側の通信装置との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置において、

前記送信側の通信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、

前記受信側の通信装置は、受信したデータの前記少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする伝送装置。

【請求項2】

請求項1に記載の伝送装置において、

前記送信側の通信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置に送信する第1のモードと、1クロック周期の中に複数の異なるビットのデータを入れ込んだデータを前記受信側の通信装置に送信する第2のモードとを切り替え可能に備えることを特徴とする伝送装置。

【請求項3】

請求項2に記載の伝送装置において

前記受信側の通信装置は、第1のモードにより送信されたデータを受信した際、受信したデータの前記少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信し、第2のモードにより送信されたデータを受信した際、受信した1クロック周期の中の複数の異なるビットのデータの全てを有効なデータとして受信することを特徴とする伝送装置。

【請求項4】

請求項2または3記載の伝送装置において、

前記送信側の通信装置は、前記第1のモードと第2のモードとを切り替えるモード切り替え信号を、前記受信側の通信装置に送信するデータの中に埋め込んで送信することにより、前記受信側の通信装置にモードの切り替えを指示することを特徴とする伝送装置。

【請求項5】

請求項2または3記載の伝送装置において、

前記送信側の通信装置は、データ送信の開始時に、前記第2のモードにより、1クロック周期の中に複数の異なるビットのデータを入れ込んだデータと同一のデータを予め定めた複数回前記受信側の通信装置に送信し、前記受信側の通信送信から全てのデータを正常に受信することができた旨の報告を受けた場合、前記第2のモードでのデータの送信を続行し、前記受信側の通信装置から全データの内の1回でも正常に受信することができなかった旨の報告を受けた場合、前記第1のモードに切り替えてデータの送信を行うことを特徴とする伝送装置。

【請求項6】

請求項3記載の伝送装置において、

前記送信側の通信装置は、前記第1のモードにより、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受けた場合、前記連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受ける毎に、順次前記連続する同一データのビット数の最少数を増加させて送信し、

前記受信側の通信装置は、連続する3ビット以上の同一データを持つデータ群の内、3ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする伝送装置。

【請求項7】

請求項3記載の伝送装置において、

前記送信側の通信装置は、クロック信号を周波数変調するSSCG回路を有し、該SSCG回路を用いない場合、前記第1のモードにより、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記SSCG回路を用いた場合、前記第2のモードにより、前記連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信することを特徴とする伝送装置。

【請求項8】

請求項3記載の伝送装置において、

前記送信側の通信装置は、クロック信号を周波数変調するSSCG回路を有し、該SSCG回路を用い、前記第1のモードにより、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受けた場合、前記SSCG回路を不使用とすることを特徴とする伝送装置。

【請求項9】

請求項8記載の伝送装置において、

前記送信側の通信装置は、クロック分岐回路を有し、該クロック分岐回路は、前記受信側の通信送信からデータを正常に受信することができなかった旨の報告を受けた場合、OSC回路から入力されたクロック信号と、前記SSCG回路を介したクロック信号とのうち、OSCから入力されたクロック信号を有効とすることを特徴とする伝送装置。

【請求項10】

請求項8記載の伝送装置において、

前記送信側の通信装置は、前記受信側の通信送信からデータを正常に受信することができなかった旨の報告を受けた場合、前記SSCG回路が前記報告を受け、自回路のクロック信号を周波数変調する機能を停止することを特徴とする伝送装置。

【請求項11】

請求項1ないし10のうちいずれか1記載の伝送装置において、

前記送信側の通信装置と受信側の通信装置との間でデータ信号の伝送が、差動伝送方式を使用して行われることを特徴とする伝送装置。

【請求項12】

送信側の通信装置と受信側の通信装置との間で、クロック信号と併走してデータ信号の伝送を行う伝送方法において、

前記送信側の通信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、

前記受信側の通信装置は、受信したデータの前記少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする伝送方法。

【請求項13】

複数の記録ヘッドを備えて構成される画像形成装置において、

前記複数の記録ヘッドを駆動する制御回路と前記複数の記録ヘッドと間での駆動信号の伝送のために、請求項1ないし11のうちいずれか1記載の伝送装置を備えたことを特徴とする画像形成装置。

【請求項14】

受信装置に対して、クロック信号と併走してデータ信号の送信を行う送信装置において、

前記送信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として送信することを特徴とする送信装置。

【請求項15】

送信装置から、クロック信号と併走してデータ信号の受信を行う受信装置において、

前記受信装置は、受信したデータの少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする受信装置。

【請求項1】

送信側の通信装置と受信側の通信装置との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置において、

前記送信側の通信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、

前記受信側の通信装置は、受信したデータの前記少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする伝送装置。

【請求項2】

請求項1に記載の伝送装置において、

前記送信側の通信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置に送信する第1のモードと、1クロック周期の中に複数の異なるビットのデータを入れ込んだデータを前記受信側の通信装置に送信する第2のモードとを切り替え可能に備えることを特徴とする伝送装置。

【請求項3】

請求項2に記載の伝送装置において

前記受信側の通信装置は、第1のモードにより送信されたデータを受信した際、受信したデータの前記少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信し、第2のモードにより送信されたデータを受信した際、受信した1クロック周期の中の複数の異なるビットのデータの全てを有効なデータとして受信することを特徴とする伝送装置。

【請求項4】

請求項2または3記載の伝送装置において、

前記送信側の通信装置は、前記第1のモードと第2のモードとを切り替えるモード切り替え信号を、前記受信側の通信装置に送信するデータの中に埋め込んで送信することにより、前記受信側の通信装置にモードの切り替えを指示することを特徴とする伝送装置。

【請求項5】

請求項2または3記載の伝送装置において、

前記送信側の通信装置は、データ送信の開始時に、前記第2のモードにより、1クロック周期の中に複数の異なるビットのデータを入れ込んだデータと同一のデータを予め定めた複数回前記受信側の通信装置に送信し、前記受信側の通信送信から全てのデータを正常に受信することができた旨の報告を受けた場合、前記第2のモードでのデータの送信を続行し、前記受信側の通信装置から全データの内の1回でも正常に受信することができなかった旨の報告を受けた場合、前記第1のモードに切り替えてデータの送信を行うことを特徴とする伝送装置。

【請求項6】

請求項3記載の伝送装置において、

前記送信側の通信装置は、前記第1のモードにより、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受けた場合、前記連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受ける毎に、順次前記連続する同一データのビット数の最少数を増加させて送信し、

前記受信側の通信装置は、連続する3ビット以上の同一データを持つデータ群の内、3ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする伝送装置。

【請求項7】

請求項3記載の伝送装置において、

前記送信側の通信装置は、クロック信号を周波数変調するSSCG回路を有し、該SSCG回路を用いない場合、前記第1のモードにより、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記SSCG回路を用いた場合、前記第2のモードにより、前記連続する同一データとして持つ複数のデータ群の連続する同一データのビット数を3ビット以上として送信することを特徴とする伝送装置。

【請求項8】

請求項3記載の伝送装置において、

前記送信側の通信装置は、クロック信号を周波数変調するSSCG回路を有し、該SSCG回路を用い、前記第1のモードにより、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内2ビットを連続する同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、前記受信側の通信送信から複数回に渡ってデータを正常に受信することができなかった旨の報告を受けた場合、前記SSCG回路を不使用とすることを特徴とする伝送装置。

【請求項9】

請求項8記載の伝送装置において、

前記送信側の通信装置は、クロック分岐回路を有し、該クロック分岐回路は、前記受信側の通信送信からデータを正常に受信することができなかった旨の報告を受けた場合、OSC回路から入力されたクロック信号と、前記SSCG回路を介したクロック信号とのうち、OSCから入力されたクロック信号を有効とすることを特徴とする伝送装置。

【請求項10】

請求項8記載の伝送装置において、

前記送信側の通信装置は、前記受信側の通信送信からデータを正常に受信することができなかった旨の報告を受けた場合、前記SSCG回路が前記報告を受け、自回路のクロック信号を周波数変調する機能を停止することを特徴とする伝送装置。

【請求項11】

請求項1ないし10のうちいずれか1記載の伝送装置において、

前記送信側の通信装置と受信側の通信装置との間でデータ信号の伝送が、差動伝送方式を使用して行われることを特徴とする伝送装置。

【請求項12】

送信側の通信装置と受信側の通信装置との間で、クロック信号と併走してデータ信号の伝送を行う伝送方法において、

前記送信側の通信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置に送信し、

前記受信側の通信装置は、受信したデータの前記少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする伝送方法。

【請求項13】

複数の記録ヘッドを備えて構成される画像形成装置において、

前記複数の記録ヘッドを駆動する制御回路と前記複数の記録ヘッドと間での駆動信号の伝送のために、請求項1ないし11のうちいずれか1記載の伝送装置を備えたことを特徴とする画像形成装置。

【請求項14】

受信装置に対して、クロック信号と併走してデータ信号の送信を行う送信装置において、

前記送信装置は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として送信することを特徴とする送信装置。

【請求項15】

送信装置から、クロック信号と併走してデータ信号の受信を行う受信装置において、

前記受信装置は、受信したデータの少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信することを特徴とする受信装置。

【図1】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図4】

【図21】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図4】

【図21】

【公開番号】特開2012−213145(P2012−213145A)

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願番号】特願2012−43526(P2012−43526)

【出願日】平成24年2月29日(2012.2.29)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願日】平成24年2月29日(2012.2.29)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]