位相同期回路及び無線機

【課題】位相同期回路のセトリング時間を短縮する。

【解決手段】位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備える。

【解決手段】位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、位相同期回路及び無線機に関する。

【背景技術】

【0002】

無線機に用いる局部発振器(LO:Local Oscillator) には、電圧制御発振器(VCO) の周波数を制御する位相同期回路(Phase-Locked Loop:PLL) が用いられる。PLL の構成として、位相周波数比較器(Phase Frequency Detector : PFD) およびチャージポンプ(Charge Pump :CP) を用いた回路が広く用いられている。通常のPLL では、LO の周波数切り替え時に所望の周波数に安定するまでの時間(セトリング時間) が長いという課題がある。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】C.-Y. Yang and S.-I. Liu, “Fast-switching frequency synthesizer with a discriminator-aided phase detector,” IEEE Journal of Solid-State Circuits, vol. 35, no. 10, pp. 1445-1452, Oct. 2000

【発明の概要】

【発明が解決しようとする課題】

【0004】

セトリング時間を短縮する手法の1 つとして、非特許文献1記載の技術がある。

【0005】

非特許文献1記載の技術は、過渡応答中のループ帯域を広げ、所望の周波数となった際にループ帯域を狭める手法である。

【0006】

上述した非特許文献1に開示されるPLL では、過渡応答中に周波数の大きなオーバーシュートが発生するため、セトリング時間が十分短縮できない。

【0007】

本発明は、上述した課題を解決するためになされたものであって、位相同期回路のセトリング時間を短縮することを目的とする。

【課題を解決するための手段】

【0008】

実施形態の位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備えることを特徴とする。

【図面の簡単な説明】

【0009】

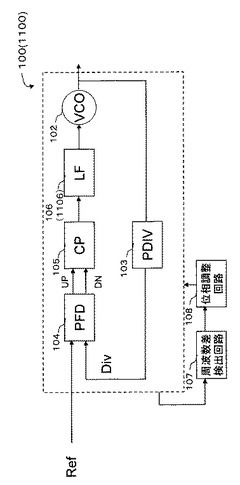

【図1】第1の実施形態に係る位相同期回路を示すブロック図。

【図2】第1の実施形態に係る周波数差検出回路の詳細な構成を示すブロック図。

【図3】比較信号の1例を示す図。

【図4】第1の実施形態に係る位相同期回路の周波数応答を示す図。

【図5】第2の実施形態に係る位相同期回路を示すブロック図。

【図6】第2の実施形態に係る周波数検出器の動作を説明する図。

【図7】第3の実施形態に係る位相同期回路を示すブロック図。

【図8】第3の実施形態に係る位相同期回路の動作を説明する図。

【図9】第4の実施形態に係る位相同期回路を示すブロック図。

【図10】第4の実施形態に係る位相同期回路の動作を説明する図。

【図11】第4の実施形態に係る位相同期回路の変形例を示す図。

【図12】第5 の実施形態に係る位相同期回路を示すブロック図。

【図13】第5 の実施形態に係る位相同期回路の動作を説明する図。

【図14】第1パルス幅検出回路及び第2パルス幅検出回路の具体的構成を示す図。

【図15】第6 の実施形態に係る位相同期回路を示すブロック図。

【図16】パルス幅検出回路602の具体的構成を示す図。

【図17】第7の実施形態に係る位相同期回路の動作を説明する図。

【図18】第8の実施形態に係る位相同期回路を示すブロック図。

【図19】第8の実施形態に係る位相同期回路の動作を説明する図。

【図20】第9の実施形態に係る位相同期回路を示すブロック図。

【図21】第10の実施形態に係る位相同期回路を示すブロック図。

【図22】第11の実施形態に係るループフィルタを示すブロック図。

【図23】一般的なループフィルタの動作を説明する図。

【図24】第12の実施形態に係る位相同期回路の動作を説明する図。

【図25】第14の実施形態に係る位相同期回路を示すブロック図。

【図26】第14の実施形態に係る位相同期回路の動作を説明する図。

【図27】第15の実施形態にかかる無線機を示すブロック図。

【発明を実施するための形態】

【0010】

以下、本発明の一実施形態について、図面を参照して説明する。尚、各図において同一箇所については同一の符号を付し、重複した説明は省略する。

【0011】

<第1の実施形態>

図1は、第1の実施形態に係る位相同期回路(PLL)100を示すブロック図である。

【0012】

位相同期回路100は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器(Voltage Controlled Oscillator : VCO)102 と、発振信号を分周して分周信号を生成する分周器(Divider : DIV)103 と、分周信号と基準信号との位相を比較して、比較信号(パルス信号)を生成する位相比較器(PFD )104と、比較信号に応じた電流を出力するチャージポンプ(CP)105 と、電流をフィルタリングし、制御信号を生成するループフィルタ(Loop Filter : LF)106 と、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路107 と、検出信号が生成されると、分周信号と基準信号との位相を同期させる位相調整回路108とを有している。

【0013】

以下では、位相同期回路100の各構成について、より詳細に説明する。

【0014】

位相比較器104 は、基準信号REF と分周信号Div とを比較し、比較結果に基づいて後段のチャージポンプ105 を制御する比較信号(パルス信号)を生成する。

【0015】

チャージポンプ105 は、比較信号に基づいてループフィルタ106 に電流を出力する。具体的には、電流をループフィルタ106に供給するか、または、ループフィルタ106から電流を引き出す。チャージポンプ105 は、図示しない複数の電流源と複数のスイッチを有する。

【0016】

ループフィルタ106 は、チャージポンプ105 から供給、または引き出された電流を制御信号(制御電圧)に変換する。

【0017】

電圧制御発振器102 は、制御信号に基づいて変化する発振周波数の発振信号を生成する。電圧制御発振器102 は、制御信号に対して正負どちらの周波数利得を持ってもよいが、ここでは正の周波数利得を持つものとして説明する。

【0018】

分周器103 は、電圧制御発振器102 の発振信号を分周して、分周信号を出力する。

【0019】

周波数差検出回路107 は、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が極小となった場合に、検出信号を出力する。ここで、定数倍の値は1以上の値であればよく、定数倍の値が1である場合、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分とは、分周信号の周波数と基準信号の周波数との差分である。

【0020】

図2は、周波数差検出回路107の詳細な構成を示すブロック図である。周波数差検出回路107は、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する算出部109と、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を保持する保持部110を備える。保持部110は、例えば、以前、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を保持する。算出部109が、基準信号の1周期ごとに分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する場合、保持部110は、基準信号の1周期前に算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を保持する。また、算出部109が、分周信号の1周期ごとに分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する場合、保持部110は、分周信号の1周期前に算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を保持する。

【0021】

周波数差検出回路107は、例えば、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分と、保持部110が保持する分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分との正負が反転した場合に極小と判定する。すなわち、周波数差検出回路107は、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が負であり、保持部110が保持する分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が正である場合に極小であると判定し、検出信号を出力する。または、周波数差検出回路107は、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が正であり、保持部110が保持する分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が負である場合に極小であると判定し、検出信号を出力する。また、周波数差検出回路107は、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分がゼロとなった場合にも極小と判定する。

【0022】

検出信号が入力されると、位相調整回路108は、基準信号Ref と分周信号Div の位相を同期させることで、基準信号Refの位相と分周信号Divの位相との差分を小さくする。具体的には、位相調整回路108は、分周器103を制御することにより、分周信号の位相を基準信号の位相に合わせる。あるいは位相調整回路108が、基準信号の位相を制御することで、基準信号の位相を分周信号の位相に合わせるようにしてもよい。位相調整回路108の具体的構成及び動作は後述する。

【0023】

次に、本実施形態にかかる位相同期回路 100の信号の流れを説明する。

【0024】

電圧制御発振器102 が生成する発振信号は、分周器103 により分周され、分周信号に変換される。分周信号は、位相比較器104 に入力される。

【0025】

位相比較器104 は、基準信号Ref と分周信号Div とを比較し、基準信号Ref と分周信号Divとの位相差分に応じた比較信号(第1比較信号又は第2比較信号)を生成する。以下では、第1比較信号のことをUP信号と称し、第2比較信号のことをDN信号と称する。

【0026】

図3に、一般的な比較信号の例を示す。位相比較器104は、基準信号Ref の位相が、分周信号Divの位相より早い場合、基準信号Ref の立ち上がりエッジから分周信号の立ち上がりエッジまでの幅である第1パルス幅を有するUP 信号 を生成する。一方、位相比較器104は、分周信号Div の位相が、基準信号Refの位相より早い場合、分周信号Div の立ち上がりエッジから基準信号の立ち上がりエッジまでの幅である第2パルス幅を有するDN信号を生成する。図3において、UP信号、DN信号ともに、パルスの凸の部分は、信号がHIであり、パルスの凹の部分は、信号がLOWであることを示す。

なお、以上の説明では、UP信号、DN信号共に、基準信号と分周信号の立ち上がりエッジ間のパルス幅の信号であると説明したが、基準信号の立下りエッジと分周信号の立ち下がりエッジ間のパルス幅の信号であっても良い。

【0027】

チャージポンプ105 は、UP信号がHI のときにループフィルタ106 に電流を供給し、DN信号がHI のときにループフィルタ106 から電流を引き出す。ここで、図3のように、信号の開始時は、基準信号Ref が分周信号Div より周波数が高く、かつ基準信号Refの位相が分周信号Divの位相より進んでいる場合を考える。基準信号Ref の方が分周信号Div より位相が進んでいる場合、位相比較器104 はUP 信号を生成する。前述したように、UP 信号がHI のとき、チャージポンプ105 は、ループフィルタ106 に電流を供給する。したがって、ループフィルタの制御信号(制御電圧)は高くなる。電圧制御発振器102 は正の周波数利得を持つので、制御電圧が高くなると発振周波数は高くなる。その結果、分周器103 の出力である分周信号Div も周波数が高くなる。以上のようなフィードバックにより、分周信号Div の周波数が基準信号Ref の周波数に近づき、最終的に同期する。

【0028】

図3の例では、分周信号の周波数が基準信号の周波数と一致した時点において、基準信号と分周信号の位相がずれている。その分だけ位相比較器104は、UP信号を出力することとなる。その結果、分周信号の周波数は基準信号の周波数より高くなる。周波数差検出回路107 および位相調整回路108 を有しない位相同期回路では、分周信号と基準信号の周波数が一致した場合であっても、位相がずれているため、分周信号と基準信号の周波数がすぐには一致せず、一致するまでの時間(セトリング時間)が長くなってしまう。

【0029】

一方、本実施形態の位相同期回路101は、周波数差検出回路107 および位相調整回路108 を有し、周波数差検出回路107 により基準信号Refの周波数の定数倍の値と分周信号Div の周波数の定数倍の値との差分が極小となる時点を検出し、位相調整回路108により基準信号Ref と分周信号Div の位相を同期させる。その結果、基準信号の位相と分周信号の位相との差を小さくすることができ、周波数のオーバーシュートを減らしセトリング時間を短縮することができる。

【0030】

図4は、第1の実施形態に係る位相同期回路100の周波数応答を示す図である。図4の実線は、周波数差検出回路107 および位相調整回路108 を有しない位相同期回路(以下、第2位相同期回路と称する)の周波数応答を示し、点線は、周波数差検出回路107 および位相調整回路108 を有する位相同期回路100の周波数応答を示すである。

【0031】

図4より、本実施例の位相同期回路100の周波数応答は第2位相同期回路に比べ、発振信号の周波数のオーバーシュートが減り、発振信号の周波数が所望周波数に収束するまでの時間(セトリング時間) が短縮されていることがわかる。

【0032】

以上、本実施形態にかかる位相同期回路100によれば、周波数差検出回路107及び位相調整回路108を設けることで、セトリング時間を短縮することができる。

【0033】

なお、本実施形態に係る位相同期回路101の保持部110は、基準信号の周波数の定数倍の値と分周信号の周波数の定数倍の値との差分として、1周期前の差分を保持するとして説明したが、2周期以上前の差分を保持するようにしても良い。

【0034】

<第2の実施形態>

図5は、第2の実施形態に係る位相同期回路200を示すブロック図である。

【0035】

第2 の実施形態に係る位相同期回路200は、周波数差検出回路207の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107の構成と異なる。それ以外の構成は同様の構成である。

【0036】

周波数差検出回路207は、カウンタ201と差分検出回路202とからなる算出部209と、保持部110とを備える。算出部209は、基準信号の1周期中に含まれる発振信号のサイクル数と、分周器103の分周数との差から分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する。

【0037】

カウンタ201には、発振信号と基準信号Ref が入力される。カウンタ201は、基準信号Refの1周期中に含まれる発振信号のサイクル数をカウントして、サイクル数を出力する。

【0038】

差分検出回路202は、カウンタ201がカウントしたサイクル数と分周器103の分周数との差分を算出する。この差分は、第1の実施形態で周波数差検出回路107が算出すると説明した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分に対応する。差分検出回路202が算出した差分は、保持部110に記憶される。差分検出回路202は、算出した差分と、保持部110に記憶された、基準信号の1周期前に算出された差分を比較する。差分検出回路202は、比較した差分の符号が変化した場合に、検出信号を出力する。

【0039】

図6は、第2の実施形態にかかる周波数差検出器207の動作を説明する図である。以下では、分周器103 で設定される分周数が「1024」 である場合を考える。

【0040】

カウンタ201 は、基準信号Refの立ち上がり又は立ち下がりを基準とし、その次(1周期後)の立ち上がり又は立ち下がりまでの発振信号のサイクル数をカウントする。図6の例では、カウンタ201は、立ち上がりAと立ち上がりBの間に含まれる発振信号のサイクル数として「1018」をカウントする。カウンタ201は、立ち上がりB時点 「1018」 を出力する。

【0041】

差分検出回路202は、カウンタ201の出力「1018」と分周器103の分周数「1024」との差分である「-6」を算出する。算出した差分「-6」と基準信号の1周期前に算出した差分である「-14」と比較すると、差分の符号は変化していない。従って、差分検出回路202は、検出信号を出力せず、算出した差分「-6」を保持部110に記憶する。

次に、カウンタ201は、基準信号Refの立ち上がりBと立ち上がりCの間に含まれる発振信号のサイクル数として「1026」をカウントする。カウンタ201は、立ち上がりC時点で「1026」を出力する。差分検出回路202は、カウンタの出力「1026」と分周器103の分周数「1024」との差分である「2」を算出する。差分検出回路202は、算出した差分「2」と保持部110に保持された基準信号の1周期前の差分である「-6」と比較する。この場合、差分の符合が反転しているため、差分検出回路202は、検出信号を出力する。以上より、差分検出回路202が、差分の符号を検出することにより、分周信号の周波数が、基準信号の周波数に近くなるタイミングを検出することができる。

【0042】

差分検出回路202が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0043】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0044】

<第3の実施形態>

図7は、第3の実施形態に係る位相同期回路300を示すブロック図である。第3の実施形態に係る位相同期回路300は、周波数差検出回路307の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107の構成と異なる。

【0045】

周波数差検出回路307は、モニタ301と差分検出回路302とを備える算出部309と、保持部110とを備える構成である。また、分周器103は、発振信号のサイクル数をカウントし、発振信号のサイクル数が分周器103の分周数になった場合に、サイクル数を0にリセットするカウンタ103Aを備える。

【0046】

算出部309は、カウンタ103Aの値と基準信号の1周期前のカウンタ103Aの値との差分から分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分の値を算出する。

【0047】

モニタ301 は、基準信号Ref1周期ごとに、分周器103のカウンタ103Aの値をモニタして、カウンタ103Aの値を出力する。

【0048】

差分検出回路302は、カウンタ103Aの値と基準信号1周期前に算出されたカウンタ103Aの値との差分を算出する。この差分は、第1の実施形態で周波数差検出回路107が算出すると説明した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分に対応する。差分検出回路302が算出した差分は、保持部110に記憶される。差分検出回路302は、算出した差分と、保持部110に記憶された、基準信号の1周期前に算出された差分を比較し、差分の符号が変化した場合に、検出信号を出力する。この差分を比較することにより、分周信号の周波数が基準信号の周波数に対して高いか低いかを検出することが可能となる。

【0049】

図8は、第3 の実施形態に係る位相同期回路300の動作を説明する図である。

【0050】

モニタ301 は、基準信号Refの立ち上がり又は立下りを基準とし、その時点での分周器103 のカウンタ103Aの値をモニタする。図8 の立ち上がりA 時点において、カウンタ103Aの値は「554」である。モニタ103Aは、立ち上がりA時点のカウンタ103Aの値として「554」を出力する。また、モニタ103Aは、基準信号Refの1周期後の立ち上がりB時点において、カウンタ103Aの値として「548」をモニタして、出力する。 差分検出回路302は、立ち上がりB時点と基準信号1周期前の立ち上がりA時点とのカウンタ103Aの値「554」の差分「-6」を算出する。差分検出回路302は、算出した差分「-6」と1周期前に算出した差分「-14」とを比較する。この場合、差分の符号は変化していないので、差分検出回路302は、検出信号を出力せず、検出した差分「-6」を保持部110に保持させる。

【0051】

次に、モニタ103Aは、立ち上がり時点Bから基準信号Refの1周期後の立ち上がり時点Cにおけるカウンタ103Aの値として「550」をモニタし出力する。差分検出回路302は、立ち上がり時点Cにおけるカウンタ103Aの値と基準信号1周期前の立ち上がり時点Bにおけるカウンタ103Aの値の差分「2」を算出する。差分検出回路302は、保持部110に保持された基準信号1周期前の差分「-6」と比較する。この場合、差分の符号が反転しているため、差分検出回路302は、検出信号を出力する。以上より、差分検出回路302は、差分の符号反転を検出することができ、分周信号の周波数が基準信号の周波数に近くなるタイミングを検出することができる。

【0052】

差分検出回路302が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号と基準信号の位相との差分を小さくする。

【0053】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0054】

<第4の実施形態>

図9は、第4の実施形態に係る位相同期回路400を示すブロック図である。第4の実施形態に係る位相同期回路400は、周波数差検出回路407の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107の構成と異なる。

【0055】

周波数差検出回路407は,ディジタル位相検出器401(TDC:Time to digital converter)と差分検出回路402とを備える算出部409と、保持部110とを備える構成である。算出部409は、基準信号の位相と分周信号の位相との位相差を検出し、検出した位相差と、基準信号又は分周信号の1周期前に検出した位相差との差分から分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する。

【0056】

ディジタル位相検出器401は、遅延回路401Cの入力端子401Aとフリップフロップ(図示せず。)のクロック入力端子401Bと遅延回路401Cを備える。遅延回路401の入力端子401Aには、分周信号あるいは分周器103中の信号が入力される。フリップフロップ(図示せず。)のクロック入力端子401Bには、基準信号Refが入力される。

【0057】

ディジタル位相検出器401は、基準信号の位相と分周信号の位相との位相差を検出する。具体的には、ディジタル位相検出器401は、分周信号が遅延回路401Cの入力端子401Aに入力されてから基準信号がフリップフロップ(図示せず。)のクロック入力端子401Bに入力されるまでの遅れが、遅延回路の遅延段の何段分に相当するかを検出する。ディジタル位相検出器401は、この遅延段の段数から基準信号の位相と分周信号の位相差を検出する。

【0058】

差分検出回路402は、ディジタル位相検出器401が検出した遅延段数と、分周信号の1周期前に算出された遅延段数との差分を算出する。ここで、この差分が、第1の実施形態で周波数差検出回路107が算出すると説明した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分に対応する。そして、差分検出回路402が算出した差分は、保持部110に記憶される。差分検出回路402は、算出した差分と保持部110に記憶された、分周信号の1周期前に算出した差分とを比較し、差分の符号が変化した場合に、検出信号を出力する。

【0059】

図10は、第4 の実施形態に係る位相同期回路400の動作を説明する図である。

【0060】

ディジタル位相検出器401には、分周信号Div が遅延回路401Cの入力端子401Aに、基準信号Ref がフリップフロップ(図示せず。)のクロック入力端子401Bにそれぞれ入力される。ディジタル位相検出器401は、分周信号からの基準信号の遅れが、遅延回路の遅延段の何段分に相当するかを検出する。

【0061】

図10において、分周信号Divの立ち上がりAと基準信号Refの立ち上がりBとの間の時間差がディジタル位相検出器401の遅延段の「554」 段として検出されたとする。また、分周信号Divの1周期後の立ち上がりCと基準信号Refの立ち上がりDとの間の時間差がディジタル位相検出器401の遅延段の「548」 段と検出されたとする。差分検出回路402は、立ち上がりC−D間の遅延段と立ち上がりA−B間の遅延段との差分「-6」 を算出する。差分検出回路402は、1周期前に算出した差分「-14」と比較し、符号が変化していないことを検出する。その結果、検出信号は出力しない。差分検出回路402は、算出した差分「-6」を保持部110に保持させる。次に、ディジタル位相検出器401は、分周信号の立ち上がりCから1周期後の立ち上がりEと基準信号Refの立ち上がりFとの間の時間差がディジタル位相検出器401 の遅延段の「550」 段と検出されたとする。差分検出回路402は、立ち上がりE-F間の遅延段と1周期前の立ち上がりC−D間の遅延段との間の差分「2」 を検出する。差分検出回路402は、保持部110に保持された1周期前に算出した差分「-6」と比較する。その結果、前のサイクルと符号が反転していることを検出する。その結果、差分検出回路402は、検出信号を出力する。

【0062】

差分検出回路402が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0063】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0064】

尚、本実施形態では、ディジタル位相検出器701 には、分周信号Div が遅延回路401Cの入力端子401Aに、基準信号Ref がフリップフロップ(図示せず。)のクロック入力端子401Bに入力される構成としたが、例えば基準信号Ref が遅延回路401Cの入力端子401Aに、分周信号Div がフリップフロップ(図示せず。)のクロック入力端子401Bに入力される構成としてもよい。

【0065】

(変形例)

図11に、本実施形態の位相同期回路の変形例を示す。本実施形態では、差分検出回路402が、差分を検出するとともに、検出した差分と1周期前の差分との符号反転を検出するいずれの機能も備えていた。しかしながら、図11の変形例に示すように、差分出力回路402Aが、差分を検出し、符号反転検出回路402Bが、符号反転を検出し、検出した際には検出信号を出力するものとしてよい。

【0066】

<第5の実施形態>

図12は、第5 の実施形態に係る位相同期回路500を示すブロック図である。第5の実施形態に係る位相同期回路500は、周波数差検出回路507の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107の構成と異なる。

【0067】

周波数差検出回路507は、算出部509と保持部110とを備える。算出部509は、第1パルス幅検出回路501と第1の差分検出回路502と、第2パルス幅検出回路503と第2の差分検出回路504と、符号反転検出回路505とを備える。

算出部509は、位相比較器104が出力するUP信号のパルス幅である第1パルス幅又はDN信号のパルス幅である第2パルス幅と、1つ前の比較信号(UP信号またはDN信号)の第1又は第2パルス幅との差分から分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分の値を検出する。

【0068】

第1パルス幅検出回路501は、位相比較器104の出力のうちUP 信号の第1パルス幅を検出する。図14に、第1パルス幅検出回路501及び第2パルス幅検出回路503の具体例を示す。

【0069】

第1パルス幅検出回路501は、第1インバータ501Aと第1ディジタル位相検出器(第1TDC)501Bとを備える。位相比較器104の出力のうちUP信号は、第1ディジタル位相検出器501Bの遅延回路501B3の入力端子501B1に入力される。また、UP信号は、第1インバータ501Aによって符号が反転され、第1ディジタル位相検出器501Bのフリップフロップ(図示せず。)のクロック入力端子501B2に入力される。第1ディジタル位相検出器501Bは、UP信号の立ち上がりが遅延回路501B3の入力端子501B1に入力されてから、UP信号の立下りの反転信号がフリップフロップ(図示せず。)のクロック入力端子501B2に入力されるまでの遅れが、第1ディジタル位相検出器501Bの遅延回路501B3の遅延段の段数として検出できる。この遅延段の段数をUP信号の第1パルス幅として検出する。

【0070】

第1差分出力回路502は、第1パルス幅検出回路501が検出したUP信号の第1パルス幅と1つ前に検出したUP信号の第1パルス幅との差分を検出する。保持部110は、算出した差分を保持する。

【0071】

第2パルス幅検出回路503は、位相比較器104の出力のうちDN信号の第2パルス幅を検出する。

【0072】

第2パルス幅検出回路503は、第2インバータ503Aと第2ディジタル位相検出器(第2TDC)503Bとを備える。位相比較器104の出力のうちDN信号は、第2ディジタル位相検出器503Bの遅延回路503B3の入力端子503B1に入力される。また、DN信号は、第2インバータ503Aによって符号が反転され、第2ディジタル位相検出器503Bのフリップフロップ(図示せず。)のクロック入力端子503B2に入力される。第2ディジタル位相検出器503Bは、DN信号の立ち上がりが遅延回路503B3の入力端子503B1に入力されてから、DN信号の立下りの反転信号がフリップフロップ(図示せず。)のクロック入力端子503B2に入力されるまでの遅れが、第2ディジタル位相検出器503Bの遅延回路503B3の遅延段の段数として検出できる。この遅延段の段数をDN信号の第2パルス幅として検出する。

【0073】

第2差分検出回路504は、第2パルス幅検出回路503が検出したDN信号の第2パルス幅と1つ前に検出したDN信号の第2パルス幅との差分を検出する。保持部110は算出した差分を保持する。

【0074】

符号反転検出回路505は、第1パルス幅又は第2パルス幅いずれかの差分の符号が反転する際に検出信号を出力する。ここで、第1パルス幅の差分、又は第2パルス幅の差分いずれか一方が、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分と対応する。

【0075】

図13は、第5 の実施形態に係る位相同期回路500の動作を説明する図である。

【0076】

第1パルス幅検出回路501は、 UP 信号の第1パルス幅を、第2パルス幅検出回路503は、DN 信号の第2パルス幅を、それぞれ検出する。第1の差分検出回路502、第2の差分検出回路504は、それぞれのパルス幅について、1つ前のデータとの差分を検出する。

【0077】

符号反転検出回路505は、第1の差分検出回路502、第2の差分検出回路504、それぞれが検出した第1パルス幅の差分、若しくは第2パルス幅の差分の符号が反転しているか否かを検出する。符号反転検出回路505は、符号の反転を検出した際、検出信号を出力する。

【0078】

ここで、符号反転検出回路505は、実際の動作では、第1差分出力回路502 が出力した差分および第2差分出力回路504 が出力した差分が入力されると、第1パルス幅と第2パルス幅のうちパルス幅が長い方の、パルス幅の差分の符号の反転を検出し、検出信号を出力する。

【0079】

図13を見るとわかるように、パルス幅が短い方のパルス幅の差分は、パルス幅が一定で(図13では、第2パルス幅が「10」で一定。)、パルス幅の差分は0だからである。すなわち、通常、符号の反転は検出されない。尚、第1パルス幅と第2パルス幅の長さが逆転するタイミング(図13では、第1パルス幅が「20」→「10」となり、第2パルス幅が、「10」→「18」となったタイミング)では、パルス幅が短い方(第1パルス幅)のパルス幅の差分は、「0」ではない。したがって、符号反転検出回路505は、パルス幅が短い方(第1パルス幅)の、パルス幅の差分の符号も検出し、差分の符号が反転した場合には、検出信号を出力する。

【0080】

図13の例においては、パルス幅は、UP信号のパルス幅(第1パルス幅)の方がDN信号のパルス幅(第2パルス幅)と比べて長く、符号反転検出回路505は、第1パルス幅に対応する差分の符号が反転する際に検出信号を出力する。

【0081】

ここで、パルス幅が短い方のパルス幅の差分が「0」の状態が継続する理由を以下で説明する。図13の例では、基準信号の位相が分周信号の位相より早い場合、位相比較器104は、基準信号の位相と分周信号の位相差に応じた大きさの第1パルス幅(「10」より大きな値)のUP信号を出力するとともに、基準信号の位相と分周信号の位相差によらず、第2パルス幅が「10」で一定なDN信号を出力する。一方、分周信号の位相が基準信号の位相より早い場合、位相比較器104は、分周信号の位相が基準信号の位相差に応じた大きさの第2パルス幅(「10」より大きな値)のDN信号を出力するとともに、基準信号の位相と分周信号の位相差によらず、第1パルス幅が「10」で一定なUP信号を出力する。

【0082】

すなわち、基準信号の位相が分周信号の位相より早い状態が継続した場合、位相比較器104は、第2パルス幅が「10」のDN信号を継続して出力し、分周信号の位相が基準信号の位相より早い状態が継続した場合、第1パルス幅が「10」のUP信号を継続して出力することとなる。したがって、基準信号の位相が分周信号の位相いずれかが早い状態が継続した場合、パルス幅が短い方のパルス幅の差分が、「0」となる状態が継続することとなる。

【0083】

したがって、通常、符号反転検出回路505は、UP信号とDN信号のうちパルス幅が長い信号に対応する差分の符号が反転する際に検出信号を出力する。

【0084】

尚、図13の例では、位相比較器104は、何も検知しない場合にパルス幅「10」の信号を出力するとしたが、何も検知しない場合に信号を出力しないようにしても良い。

【0085】

図13の例では、UP信号がDN信号よりパルス幅が長い場合であって、UP 信号のパルス幅が前のパルス幅と等しい場合、基準信号に対する分周信号の遅延に変化がなく、基準信号と分周信号の周波数が等しいこととなる。したがって、UP信号のパルス幅の変化が極小となるタイミング、即ち符号が反転するタイミングを検出することで分周信号と基準信号の周波数がほぼ等しくなるタイミングを検出することが可能となる。

【0086】

図13において、第1パルス幅検出回路501は、UP信号の立ち上がりAと立ち下がりB 間のパルス幅は「32」であり、立ち上がりCと立ち下がりD 間のパルス幅は「34」であり、立ち上がりEと立ち下がりFとの間のパルス幅は「31」 と検出する。第1の差分検出回路502は、立下りDのタイミングで差分「2」を算出し、立下りFのタイミングで「-3」を算出する。したがって、立下りF のタイミングで、符号反転検出回路505は、差分の符号が反転したことを検出し、検出信号を出力する。

【0087】

符号反転検出回路505が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号と基準信号の位相との差分を小さくする。

【0088】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0089】

<第6の実施形態>

図15は、6の実施形態に係る位相同期回路600を示すブロック図である。第6の実施形態に係る位相同期回路600は、周波数差検出回路607の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107と異なる。

【0090】

周波数差検出回路607 は、算出部609と保持部110とを備える。算出部609は、論理回路601と、パルス幅検出回路602と、差分出力回路603と、符号反転検出回路604とを備える。

【0091】

論理回路601は、位相比較器104の出力のUP 信号とDN 信号の排他的論理和である第3の比較信号を出力する。

【0092】

パルス幅検出回路602は、第3比較信号のパルス幅を検出する。

【0093】

図16に、パルス幅検出回路602の具体的構成を示す。

【0094】

パルス幅検出回路602は、インバータ602Aとディジタル位相検出器(TDC)602Bとを備える。第3比較信号は、ディジタル位相検出器602Bの遅延回路602B3の入力端子602B1に入力される。また、第3比較信号は、インバータ602Aによって符号が反転され、ディジタル位相検出器602Bのフリップフロップ(図示せず。)のクロック入力端子602B2に入力される。ディジタル位相検出器602Bは、第3比較信号の立ち上がりが遅延回路602B3の入力端子602B1に入力されてから、第3比較信号の立下りの反転信号がフリップフロップ(図示せず。)のクロック入力端子602B2に入力されるまでの遅れが、第1ディジタル位相検出器501Bの遅延回路602B3の遅延段の段数として検出できる。この遅延段の段数を第3比較信号の第1パルス幅として検出する。

【0095】

差分出力回路603は、パルス幅検出回路602が検出した第3の比較信号のパルス幅と、1つ前にパルス幅検出回路602が検出した第3の比較信号のパルス幅との差分を検出する。ここで、図13でも示したように、第3の比較信号のうち、UP信号又はDN信号のいずれか一方は、一定となり、いずれか一方のみ変化する。例えば、分周信号の位相が基準信号の位相よりも遅れている場合、UP 信号のパルス幅だけが変化し、DN信号のパルス幅は一定となる。この場合、差分出力回路603は、UP信号のパルス幅の差分を検出する。一方、基準信号の位相が分周信号の位相よりも遅れている場合、差分出力回路603は、DN信号のパルス幅の差分を検出する。

【0096】

保持部110は、算出した差分を保持する。

【0097】

符号反転検出回路604は、差分出力回路603から入力された差分の符号が反転した場合に検出信号を出力する。符号反転検出回路604には、UP信号のパルス幅の差分、又はDN信号のパルス幅の差分が入力される。符号反転検出回路604は、差分の符号が反転するタイミングを検出することで分周信号と基準信号の周波数差が極小となるタイミングを検出する。

【0098】

符号反転検出回路505が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで、分周信号と基準信号の位相との差分を小さくする。

【0099】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0100】

<第7の実施形態>

次に、第7 の実施形態に係る位相同期回路700を説明する。第7の実施形態に係る位相同期回路700は、図5に示す第2の実施形態にかかる位相同期回路200と同様の構成を備える。図17は、第7の実施形態に係る位相同期回路700の動作を説明する図である。第7の実施形態に係る位相同期回路700を図5、図17を用いて説明する。本実施形態にかかる位相同期回路700は、差分検出回路702の機能が、第2の実施形態にかかる位相同期回路200の差分検出回路702の機能と異なる。

【0101】

第2の実施形態に係る位相同期回路200では、差分検出回路702は、差分の符号が反転したことを検出していた。

【0102】

本実施形態にかかる位相同期回路700では、差分検出回路702は、新たに算出した差分と、1周期前の差分との差を求める。差分検出回路702は、その差と差分検出回路702が新たに算出した差分との和を求めることにより、次に差分検出回路702が算出する差分の予測を行う。差分検出回路702は、次に差分検出回路702が算出する差分の予測を行うことで、差分の符号が反転する前に検出信号を出力する。

【0103】

例えば、図17において、差分検出回路702は、算出した差分「-21」と、1周期前に算出した差分「-28」との差「7」を算出する。差分検出回路702は、算出した差分「-21」と差「7」との和である「-14」を算出する。この「-14」が、次に差分検出回路702が算出する差分の予測値となる。このようにして、差分検出回路702は、1周期ごとに差分の予測値を算出する。図17の例では、予測値「-14」を算出した後、「-7」、「2」を算出する。予測値が「-7」から「2」となると、差分の予測値の符号が反転しているため、差分検出回路702は、検出信号を出力する。

【0104】

本実施形態の位相同期回路700によれば、差分検出回路702は、実際に差分の符号が反転する前に検出信号を出力することができる。

【0105】

差分検出回路702が検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0106】

以上、本実施形態にかかる位相同期回路700によれば、より早いタイミングで、分周信号の位相と基準信号の位相を同期させることができるため、セトリング時間をより短縮することができる。

【0107】

<第8の実施形態>

図18は、第8の実施形態に係る位相同期回路800を示すブロック図である。

【0108】

第8の実施形態にかかる位相同期回路800は、位相調整回路808の構成が、第1 の実施形態で示した位相同期回路100の位相調整回路108の構成と異なる。

【0109】

位相調整回路808は、タイミング調整回路801と位相設定回路802とを備える。

【0110】

本実施形態の位相調整回路808は、検出信号が入力されると分周器103を制御し、分周信号の位相を基準信号の位相に合わせることで、分周信号と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0111】

タイミング調整回路801は、周波数差検出回路107 の検出信号と基準信号Refとを入力とし、検出信号が入力された次の基準信号Refの立ち上がりエッジあるいは立ち下がりエッジでタイミング信号を出力する。

【0112】

位相設定回路802は、タイミング信号が入力されると分周器103のカウンタ103Aの値を所定の値に設定する。

【0113】

図19は、位相同期回路800の動作を説明する図である。

【0114】

図19のDiv counter は分周器103のカウンタ103Aの値を示す。周波数差検出回路107から検出信号が入力されると、タイミング調整回路801は、基準信号Ref の立ち上がりでタイミング信号を出力する。位相設定回路802は、タイミング調整回路801からタイミング信号が入力されると、分周器103のカウンタ103Aの値を「0」にリセットする。

【0115】

図19の点線は、カウンタ103Aの値をリセットしない場合のカウンタ103Aの値の一例を示す。カウンタ103Aの値をリセットすると、カウンタ103Aの値は、図19の点線から実線のように変化する。位相設定回路802は、基準信号Ref の立ち上がりのタイミングに合わせてカウンタ103Aの値を「0」にリセットすることで、分周信号及び基準信号の周波数、位相が同期する。

【0116】

差分検出回路202が検出信号を出力すると、位相調整回路808は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0117】

本実施形態にかかる位相同期回路800によれば、周波数が一致したタイミングで位相を同期させるため、図19に示すように、オーバーシュートを減少し、セトリング時間を短縮することができる。

【0118】

<第9の実施形態>

図20は、第9 の実施形態に係る位相同期回路900を示すブロック図である。第9の実施形態にかかる位相同期回路900は、位相調整回路908の構成が、第1の実施形態で示した位相同期回路100の位相調整回路108の構成と異なる。

【0119】

位相調整回路908は、遅延回路901を備える。

【0120】

本実施形態の位相調整回路908は、検出信号が入力されると基準信号の位相を分周信号の位相と合わせることで、分周信号及び基準信号の周波数、位相を同期させる。

【0121】

具体的には、遅延回路901が、分周信号の位相と基準信号Refの位相を等しくするように基準信号Ref2の位相を遅延量だけ遅延させる。遅延回路901は、基準信号Ref2 の位相を遅延させる複数の遅延段902と、遅延段902 の複数の出力から信号を選択する選択回路903 を備える。ここで、選択回路903が出力した信号が基準信号Refとなる。遅延回路901は、選択回路903がどの遅延段902の出力を選択するか制御することで、分周信号Divの位相と基準信号Refの位相との差分が小さく(ゼロも含む。)なるように遅延量を調整する。

【0122】

選択回路903には、周波数差検出回路107から検出信号が入力され、分周器103から分周信号が入力される。選択回路902は、検出信号が入力された後、分周信号Div の出力がHI になったタイミングで、遅延段902の出力のうち分周信号Div に最も位相の近い出力を選択し、基準信号Ref として出力する。これにより分周信号は基準信号に対して周波数、位相とも同期する。

【0123】

本実施形態にかかる位相同期回路900によれば、周波数が一致したタイミングで位相を同期させるため、オーバーシュートを減少し、セトリング時間を短縮することができる。

【0124】

<第10の実施形態>

図21は、第10の実施形態に係る位相同期回路1000を示すブロック図である。第10の実施形態にかかる位相同期回路1000は、位相調整回路1008の構成が、第1 の実施形態で示した位相同期回路100の位相調整回路108の構成と異なる。

【0125】

位相調整回路1008は、分周器(MUX)1001を備える構成である。

【0126】

本実施形態の位相調整回路1008は、検出信号が入力されると基準信号の位相を分周信号の位相と合わせることにより、基準信号の位相と分周信号の位相を同期させる。位相調整回路1008は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0127】

分周器1001は、基準信号Ref より周波数の高い基準信号Ref2 を入力とし,基準信号Ref2 を分周し、基準信号Refを出力する。

【0128】

周波数差検出回路107から検出信号が入力されると、分周信号Div の出力がHI になったタイミングで、分周器1001 のカウンタ(図示せず)をリセットする。これにより分周信号は基準信号に対して周波数、位相とも同期する。

【0129】

これにより分周信号は基準信号に対して周波数、位相とも同期する.

本実施形態にかかる位相同期回路によれば、周波数が一致したタイミングで位相を同期させるため、オーバーシュートを減少し、セトリング時間を短縮することができる。

【0130】

<第11の実施形態>

図22は、第11の実施形態に係る位相同期回路1100について説明する。位相同期回路1100は、第1の実施形態に係る位相同期回路100と同様の構成である。位相同期回路1100は、ループフィルタ1106の構成、機能が位相同期回路100のループフィルタ106と異なる。

【0131】

図22に、第11の実施形態に係る位相同期回路1100のループフィルタ1106を示す。

【0132】

図22に示すように、ループフィルタ1106は、一端がチャージポンプ105に接続され、他端が電圧制御発振器102に接続された接続部1805と、一端が接続部1805に接続され、他端が第1電源電位(本実施形態では、グランド)に接続された第1コンデンサ1803と、第1コンデンサ1803と並列に配置され、一端が接続部1805に接続された抵抗1801と、一端が抵抗1801と直列に接続され、他端が第1電源電位に接続された第2コンデンサ1802と、抵抗1801に並列に配置され、一端が第2コンデンサ1802の一端と接続され、ONのときは他端が接続部1805に接続され、OFFのときは、他端が接続部1805に接続されないスイッチ1804とを備え、周波数差検出回路107が検出信号を生成前は、スイッチ1804がONとなり、周波数差検出回路107が検出信号を生成すると、スイッチ1804がOFFとなる。

【0133】

図22のループフィルタ1106において、抵抗1801 と第2コンデンサ1802 の間の端子Vb は、制御電圧端子Va に比べて応答が遅い。図23に一般的なPLLにおけるループフィルタの動作を説明する。図23(a)に示すように、位相比較器104がUP 信号を出力している間、ループフィルタ106に電流が供給される。このとき、Vb はVa より応答が遅く、VbとVaの間で電圧差が生じる。周波数差検出回路107が検出信号を出力し、分周信号と基準信号の周波数、位相ともに同期した場合において、ループフィルタのVa とVb に電圧差が生じている場合、図23(b)に示すように、第1コンデンサ1801から第2コンデンサ1803へと電流が流れ、Va はVb に近付いていく。その結果、電圧制御発振器102の周波数が下がってしまう。これによって、図23(c)に示すように、分周信号を基準信号の周波数と位相に合わせるために、UP信号が再び流れる。このように、VbはVaより応答が遅いため、Vaの電圧が安定しない。その結果、セトリング時間が増加してしまう。

【0134】

本実施形態のループフィルタ1106では、これを防ぐために、周波数差検出回路107が検出信号を出力されるまで、スイッチ1804 をONとし、検出信号が出力されたらスイッチ1804をOFFとする。スイッチ1804をONとしている間、第2コンデンサ1802の一端はスイッチ1804を介して接続部1805に接続される。したがって、VaとVbに電圧差が生じないため、VaとVbとが変化することがなくなる。その結果、分周信号を基準信号の周波数と位相に合わせるためのセトリング時間を減少させることが出来る。

【0135】

<第12の実施形態>

次に、第12の実施形態にかかる位相同期回路1200を説明する。位相同期回路1200は、図18に示す第8の実施形態に係る位相同期回路800と同様の構成である。位相同期回路1200は、位相比較器1204の機能が、位相同期回路800の位相比較器104の機能と異なる。

【0136】

本実施形態に係る位相比較器1204は、周波数差検出回路107 により検出信号が出力されると、一定時間の間、位相比較器1204 の動作を停止させる。

【0137】

図24は、本実施形態の位相同期回路1200の動作を説明する図である。図24に示すように、位相同期回路1200は、分周器103のカウンタをリセットすることにより分周信号の位相を基準信号の位相に合わせる。このとき、基準信号Ref の信号はHI になっているため、位相比較器を停止させる機能を有さない場合、位相比較器はUP 信号を出力してしまう。これを防ぐため、周波数差検出回路108 が検出信号を出力してから一定時間の間位相比較器1204の動作を停止させる。位相比較器1204は、少なくとも周波数差検出回路107が検出信号を生成してから、位相調整回路808が前記分周信号と前記基準信号との位相を同期させるまでの間、比較信号を生成しないことが好ましい。そのため、周波数差検出回路107が検出信号を生成してから、次に基準信号が立ち上がるタイミングまでを含む一定時間の間、位相比較器1204の動作を停止させる。

【0138】

<第13の実施形態>

次に、第13の実施形態にかかる位相同期回路1300を説明する。位相同期回路1300は、図18に示す第8の実施形態に係る位相同期回路800と同様の構成である。位相同期回路1300は、チャージポンプ1305の機能が、位相同期回路800のチャージポンプ105の機能と異なる。

【0139】

第13の実施形態にかかるチャージポンプ1305 は、周波数差検出回路107 により検出信号が出力されると、一定時間の間、チャージポンプ1305の動作を停止させる。

【0140】

位相同期回路1300の動作において、分周器103のカウンタをリセットすることにより分周信号の位相を基準信号の位相に合わせる。このとき、基準信号Ref の信号はHI になっているため、位相比較器104はUP 信号を出力してしまう。このとき、位相比較器104がUP 信号を出力してもチャージポンプ1305 が動作しないよう動作を停止させる。チャージポンプ1305は、少なくとも周波数差検出回路107が検出信号を生成してから、位相調整回路108が前記分周信号と前記基準信号との位相を同期させるまでの間、電流を供給しないことが好ましい。そのため、周波数差検出回路107が検出信号を生成してから、次に基準信号が立ち上がるタイミングまでを含む一定時間の間、チャージポンプ1305の動作を停止させる。

【0141】

<第14の実施形態>

図25は、第14の実施形態に係る位相同期回路1400を示すブロック図である。図26は、位相同期回路1400の動作を説明する図である。

【0142】

図25に示すように、位相同期回路1400は、実施形態1の位相同期回路と比べて、ミスエッジカウンタ1401を更に備える構成である。

【0143】

図26に示すように、ミスエッジカウンタ1401は、基準信号と分周信号の位相差が2πを越えた回数をカウントする。チャージポンプ105 は、ミスエッジカウンタ1401の値に応じてチャージポンプの電流を調整する。

【0144】

周波数差検出回路108により検出信号が出力されたときにミスエッジカウンタ1401のカウンタを0にリセットする。これにより、チャージポンプの電流は通常の値となる。

【0145】

<第15の実施形態>

図27は、第15の実施形態にかかる無線機2000である。

【0146】

無線機2000は、無線信号を送信および受信するアンテナ2001 と,アンテナ2001により受信した無線信号を増幅し,増幅信号を生成する第1増幅器2002 と、発振信号を生成する位相同期回路100と、増幅信号と発振信号とを乗算し、受信ベースバンド信号を生成する第1ミキサ回路2004 と、送信ベースバンド信号と発振信号とを乗算し、送信信号を生成する第2ミキサ回路2005 と、送信信号を増幅し無線信号を出力する第2増幅器2006 とを有する。

【0147】

本実施形態にかかる無線機2000では、位相同期回路100が、発振信号の周波数の切り替え時に、セトリング時間を短縮することができる。

【0148】

なお、本発明は上記の実施形態のそのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記の実施形態に開示されている複数の構成要素の適宜な組み合わせにより、種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施形態にわたる構成要素を適宜組み合わせてもよい。

【符号の説明】

【0149】

100、200、300、400、500、600、700、800、900、1000、1100、1200、1300、1400・・・位相同期回路、102・・・電圧制御発振器、103、1001・・・分周器、103A・・・カウンタ、104、1204・・・位相比較器、105、1305・・・チャージポンプ、106、1106・・・ループフィルタ、107、207、307、407、507、607・・・周波数差検出回路、108、808、908、1008・・・位相調整回路、109、209、309、409、509、609・・・算出部、110・・・保持部、201・・・カウンタ、202、302、402、702・・・差分検出回路、301・・・モニタ、401・・・TDC、401A、501B1、503B1、602B1・・・入力端子、401B、501B2、503B2、602B2・・・クロック入力端子、401C、501B3、503B3、602B3、901・・・遅延回路、402A・・・差分出力回路、402B、505・・・符号反転検出回路、501・・・第1パルス幅検出回路、502・・・第1差分出力回路、503・・・第2パルス幅検出回路、504・・・第2差分出力回路、501A・・・第1インバータ、501B・・・第1TDC、503A・・・第2インバータ、503B・・・第2TDC、601・・・論理回路、602・・・パルス幅検出回路、603・・・差分出力回路、604・・・符号反転検出回路、602A・・・インバータ、602B・・・TDC、801・・・タイミング調整回路、802・・・位相設定回路、902・・・遅延段、903・・・選択回路、1801・・・抵抗、1802・・・第2コンデンサ、1803・・・第1コンデンサ、1804・・・スイッチ、1805・・・接続部、1401・・・ミスエッジカウンタ、2000・・・無線機、2001・・・アンテナ、2002・・・第1増幅器、2004・・・第1ミキサ回路、2005・・・第2ミキサ回路、2006・・・第2増幅器。

【技術分野】

【0001】

本発明の実施形態は、位相同期回路及び無線機に関する。

【背景技術】

【0002】

無線機に用いる局部発振器(LO:Local Oscillator) には、電圧制御発振器(VCO) の周波数を制御する位相同期回路(Phase-Locked Loop:PLL) が用いられる。PLL の構成として、位相周波数比較器(Phase Frequency Detector : PFD) およびチャージポンプ(Charge Pump :CP) を用いた回路が広く用いられている。通常のPLL では、LO の周波数切り替え時に所望の周波数に安定するまでの時間(セトリング時間) が長いという課題がある。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】C.-Y. Yang and S.-I. Liu, “Fast-switching frequency synthesizer with a discriminator-aided phase detector,” IEEE Journal of Solid-State Circuits, vol. 35, no. 10, pp. 1445-1452, Oct. 2000

【発明の概要】

【発明が解決しようとする課題】

【0004】

セトリング時間を短縮する手法の1 つとして、非特許文献1記載の技術がある。

【0005】

非特許文献1記載の技術は、過渡応答中のループ帯域を広げ、所望の周波数となった際にループ帯域を狭める手法である。

【0006】

上述した非特許文献1に開示されるPLL では、過渡応答中に周波数の大きなオーバーシュートが発生するため、セトリング時間が十分短縮できない。

【0007】

本発明は、上述した課題を解決するためになされたものであって、位相同期回路のセトリング時間を短縮することを目的とする。

【課題を解決するための手段】

【0008】

実施形態の位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備えることを特徴とする。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に係る位相同期回路を示すブロック図。

【図2】第1の実施形態に係る周波数差検出回路の詳細な構成を示すブロック図。

【図3】比較信号の1例を示す図。

【図4】第1の実施形態に係る位相同期回路の周波数応答を示す図。

【図5】第2の実施形態に係る位相同期回路を示すブロック図。

【図6】第2の実施形態に係る周波数検出器の動作を説明する図。

【図7】第3の実施形態に係る位相同期回路を示すブロック図。

【図8】第3の実施形態に係る位相同期回路の動作を説明する図。

【図9】第4の実施形態に係る位相同期回路を示すブロック図。

【図10】第4の実施形態に係る位相同期回路の動作を説明する図。

【図11】第4の実施形態に係る位相同期回路の変形例を示す図。

【図12】第5 の実施形態に係る位相同期回路を示すブロック図。

【図13】第5 の実施形態に係る位相同期回路の動作を説明する図。

【図14】第1パルス幅検出回路及び第2パルス幅検出回路の具体的構成を示す図。

【図15】第6 の実施形態に係る位相同期回路を示すブロック図。

【図16】パルス幅検出回路602の具体的構成を示す図。

【図17】第7の実施形態に係る位相同期回路の動作を説明する図。

【図18】第8の実施形態に係る位相同期回路を示すブロック図。

【図19】第8の実施形態に係る位相同期回路の動作を説明する図。

【図20】第9の実施形態に係る位相同期回路を示すブロック図。

【図21】第10の実施形態に係る位相同期回路を示すブロック図。

【図22】第11の実施形態に係るループフィルタを示すブロック図。

【図23】一般的なループフィルタの動作を説明する図。

【図24】第12の実施形態に係る位相同期回路の動作を説明する図。

【図25】第14の実施形態に係る位相同期回路を示すブロック図。

【図26】第14の実施形態に係る位相同期回路の動作を説明する図。

【図27】第15の実施形態にかかる無線機を示すブロック図。

【発明を実施するための形態】

【0010】

以下、本発明の一実施形態について、図面を参照して説明する。尚、各図において同一箇所については同一の符号を付し、重複した説明は省略する。

【0011】

<第1の実施形態>

図1は、第1の実施形態に係る位相同期回路(PLL)100を示すブロック図である。

【0012】

位相同期回路100は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器(Voltage Controlled Oscillator : VCO)102 と、発振信号を分周して分周信号を生成する分周器(Divider : DIV)103 と、分周信号と基準信号との位相を比較して、比較信号(パルス信号)を生成する位相比較器(PFD )104と、比較信号に応じた電流を出力するチャージポンプ(CP)105 と、電流をフィルタリングし、制御信号を生成するループフィルタ(Loop Filter : LF)106 と、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路107 と、検出信号が生成されると、分周信号と基準信号との位相を同期させる位相調整回路108とを有している。

【0013】

以下では、位相同期回路100の各構成について、より詳細に説明する。

【0014】

位相比較器104 は、基準信号REF と分周信号Div とを比較し、比較結果に基づいて後段のチャージポンプ105 を制御する比較信号(パルス信号)を生成する。

【0015】

チャージポンプ105 は、比較信号に基づいてループフィルタ106 に電流を出力する。具体的には、電流をループフィルタ106に供給するか、または、ループフィルタ106から電流を引き出す。チャージポンプ105 は、図示しない複数の電流源と複数のスイッチを有する。

【0016】

ループフィルタ106 は、チャージポンプ105 から供給、または引き出された電流を制御信号(制御電圧)に変換する。

【0017】

電圧制御発振器102 は、制御信号に基づいて変化する発振周波数の発振信号を生成する。電圧制御発振器102 は、制御信号に対して正負どちらの周波数利得を持ってもよいが、ここでは正の周波数利得を持つものとして説明する。

【0018】

分周器103 は、電圧制御発振器102 の発振信号を分周して、分周信号を出力する。

【0019】

周波数差検出回路107 は、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が極小となった場合に、検出信号を出力する。ここで、定数倍の値は1以上の値であればよく、定数倍の値が1である場合、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分とは、分周信号の周波数と基準信号の周波数との差分である。

【0020】

図2は、周波数差検出回路107の詳細な構成を示すブロック図である。周波数差検出回路107は、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する算出部109と、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を保持する保持部110を備える。保持部110は、例えば、以前、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を保持する。算出部109が、基準信号の1周期ごとに分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する場合、保持部110は、基準信号の1周期前に算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を保持する。また、算出部109が、分周信号の1周期ごとに分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する場合、保持部110は、分周信号の1周期前に算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を保持する。

【0021】

周波数差検出回路107は、例えば、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分と、保持部110が保持する分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分との正負が反転した場合に極小と判定する。すなわち、周波数差検出回路107は、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が負であり、保持部110が保持する分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が正である場合に極小であると判定し、検出信号を出力する。または、周波数差検出回路107は、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が正であり、保持部110が保持する分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が負である場合に極小であると判定し、検出信号を出力する。また、周波数差検出回路107は、算出部109が算出した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分がゼロとなった場合にも極小と判定する。

【0022】

検出信号が入力されると、位相調整回路108は、基準信号Ref と分周信号Div の位相を同期させることで、基準信号Refの位相と分周信号Divの位相との差分を小さくする。具体的には、位相調整回路108は、分周器103を制御することにより、分周信号の位相を基準信号の位相に合わせる。あるいは位相調整回路108が、基準信号の位相を制御することで、基準信号の位相を分周信号の位相に合わせるようにしてもよい。位相調整回路108の具体的構成及び動作は後述する。

【0023】

次に、本実施形態にかかる位相同期回路 100の信号の流れを説明する。

【0024】

電圧制御発振器102 が生成する発振信号は、分周器103 により分周され、分周信号に変換される。分周信号は、位相比較器104 に入力される。

【0025】

位相比較器104 は、基準信号Ref と分周信号Div とを比較し、基準信号Ref と分周信号Divとの位相差分に応じた比較信号(第1比較信号又は第2比較信号)を生成する。以下では、第1比較信号のことをUP信号と称し、第2比較信号のことをDN信号と称する。

【0026】

図3に、一般的な比較信号の例を示す。位相比較器104は、基準信号Ref の位相が、分周信号Divの位相より早い場合、基準信号Ref の立ち上がりエッジから分周信号の立ち上がりエッジまでの幅である第1パルス幅を有するUP 信号 を生成する。一方、位相比較器104は、分周信号Div の位相が、基準信号Refの位相より早い場合、分周信号Div の立ち上がりエッジから基準信号の立ち上がりエッジまでの幅である第2パルス幅を有するDN信号を生成する。図3において、UP信号、DN信号ともに、パルスの凸の部分は、信号がHIであり、パルスの凹の部分は、信号がLOWであることを示す。

なお、以上の説明では、UP信号、DN信号共に、基準信号と分周信号の立ち上がりエッジ間のパルス幅の信号であると説明したが、基準信号の立下りエッジと分周信号の立ち下がりエッジ間のパルス幅の信号であっても良い。

【0027】

チャージポンプ105 は、UP信号がHI のときにループフィルタ106 に電流を供給し、DN信号がHI のときにループフィルタ106 から電流を引き出す。ここで、図3のように、信号の開始時は、基準信号Ref が分周信号Div より周波数が高く、かつ基準信号Refの位相が分周信号Divの位相より進んでいる場合を考える。基準信号Ref の方が分周信号Div より位相が進んでいる場合、位相比較器104 はUP 信号を生成する。前述したように、UP 信号がHI のとき、チャージポンプ105 は、ループフィルタ106 に電流を供給する。したがって、ループフィルタの制御信号(制御電圧)は高くなる。電圧制御発振器102 は正の周波数利得を持つので、制御電圧が高くなると発振周波数は高くなる。その結果、分周器103 の出力である分周信号Div も周波数が高くなる。以上のようなフィードバックにより、分周信号Div の周波数が基準信号Ref の周波数に近づき、最終的に同期する。

【0028】

図3の例では、分周信号の周波数が基準信号の周波数と一致した時点において、基準信号と分周信号の位相がずれている。その分だけ位相比較器104は、UP信号を出力することとなる。その結果、分周信号の周波数は基準信号の周波数より高くなる。周波数差検出回路107 および位相調整回路108 を有しない位相同期回路では、分周信号と基準信号の周波数が一致した場合であっても、位相がずれているため、分周信号と基準信号の周波数がすぐには一致せず、一致するまでの時間(セトリング時間)が長くなってしまう。

【0029】

一方、本実施形態の位相同期回路101は、周波数差検出回路107 および位相調整回路108 を有し、周波数差検出回路107 により基準信号Refの周波数の定数倍の値と分周信号Div の周波数の定数倍の値との差分が極小となる時点を検出し、位相調整回路108により基準信号Ref と分周信号Div の位相を同期させる。その結果、基準信号の位相と分周信号の位相との差を小さくすることができ、周波数のオーバーシュートを減らしセトリング時間を短縮することができる。

【0030】

図4は、第1の実施形態に係る位相同期回路100の周波数応答を示す図である。図4の実線は、周波数差検出回路107 および位相調整回路108 を有しない位相同期回路(以下、第2位相同期回路と称する)の周波数応答を示し、点線は、周波数差検出回路107 および位相調整回路108 を有する位相同期回路100の周波数応答を示すである。

【0031】

図4より、本実施例の位相同期回路100の周波数応答は第2位相同期回路に比べ、発振信号の周波数のオーバーシュートが減り、発振信号の周波数が所望周波数に収束するまでの時間(セトリング時間) が短縮されていることがわかる。

【0032】

以上、本実施形態にかかる位相同期回路100によれば、周波数差検出回路107及び位相調整回路108を設けることで、セトリング時間を短縮することができる。

【0033】

なお、本実施形態に係る位相同期回路101の保持部110は、基準信号の周波数の定数倍の値と分周信号の周波数の定数倍の値との差分として、1周期前の差分を保持するとして説明したが、2周期以上前の差分を保持するようにしても良い。

【0034】

<第2の実施形態>

図5は、第2の実施形態に係る位相同期回路200を示すブロック図である。

【0035】

第2 の実施形態に係る位相同期回路200は、周波数差検出回路207の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107の構成と異なる。それ以外の構成は同様の構成である。

【0036】

周波数差検出回路207は、カウンタ201と差分検出回路202とからなる算出部209と、保持部110とを備える。算出部209は、基準信号の1周期中に含まれる発振信号のサイクル数と、分周器103の分周数との差から分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する。

【0037】

カウンタ201には、発振信号と基準信号Ref が入力される。カウンタ201は、基準信号Refの1周期中に含まれる発振信号のサイクル数をカウントして、サイクル数を出力する。

【0038】

差分検出回路202は、カウンタ201がカウントしたサイクル数と分周器103の分周数との差分を算出する。この差分は、第1の実施形態で周波数差検出回路107が算出すると説明した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分に対応する。差分検出回路202が算出した差分は、保持部110に記憶される。差分検出回路202は、算出した差分と、保持部110に記憶された、基準信号の1周期前に算出された差分を比較する。差分検出回路202は、比較した差分の符号が変化した場合に、検出信号を出力する。

【0039】

図6は、第2の実施形態にかかる周波数差検出器207の動作を説明する図である。以下では、分周器103 で設定される分周数が「1024」 である場合を考える。

【0040】

カウンタ201 は、基準信号Refの立ち上がり又は立ち下がりを基準とし、その次(1周期後)の立ち上がり又は立ち下がりまでの発振信号のサイクル数をカウントする。図6の例では、カウンタ201は、立ち上がりAと立ち上がりBの間に含まれる発振信号のサイクル数として「1018」をカウントする。カウンタ201は、立ち上がりB時点 「1018」 を出力する。

【0041】

差分検出回路202は、カウンタ201の出力「1018」と分周器103の分周数「1024」との差分である「-6」を算出する。算出した差分「-6」と基準信号の1周期前に算出した差分である「-14」と比較すると、差分の符号は変化していない。従って、差分検出回路202は、検出信号を出力せず、算出した差分「-6」を保持部110に記憶する。

次に、カウンタ201は、基準信号Refの立ち上がりBと立ち上がりCの間に含まれる発振信号のサイクル数として「1026」をカウントする。カウンタ201は、立ち上がりC時点で「1026」を出力する。差分検出回路202は、カウンタの出力「1026」と分周器103の分周数「1024」との差分である「2」を算出する。差分検出回路202は、算出した差分「2」と保持部110に保持された基準信号の1周期前の差分である「-6」と比較する。この場合、差分の符合が反転しているため、差分検出回路202は、検出信号を出力する。以上より、差分検出回路202が、差分の符号を検出することにより、分周信号の周波数が、基準信号の周波数に近くなるタイミングを検出することができる。

【0042】

差分検出回路202が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0043】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0044】

<第3の実施形態>

図7は、第3の実施形態に係る位相同期回路300を示すブロック図である。第3の実施形態に係る位相同期回路300は、周波数差検出回路307の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107の構成と異なる。

【0045】

周波数差検出回路307は、モニタ301と差分検出回路302とを備える算出部309と、保持部110とを備える構成である。また、分周器103は、発振信号のサイクル数をカウントし、発振信号のサイクル数が分周器103の分周数になった場合に、サイクル数を0にリセットするカウンタ103Aを備える。

【0046】

算出部309は、カウンタ103Aの値と基準信号の1周期前のカウンタ103Aの値との差分から分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分の値を算出する。

【0047】

モニタ301 は、基準信号Ref1周期ごとに、分周器103のカウンタ103Aの値をモニタして、カウンタ103Aの値を出力する。

【0048】

差分検出回路302は、カウンタ103Aの値と基準信号1周期前に算出されたカウンタ103Aの値との差分を算出する。この差分は、第1の実施形態で周波数差検出回路107が算出すると説明した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分に対応する。差分検出回路302が算出した差分は、保持部110に記憶される。差分検出回路302は、算出した差分と、保持部110に記憶された、基準信号の1周期前に算出された差分を比較し、差分の符号が変化した場合に、検出信号を出力する。この差分を比較することにより、分周信号の周波数が基準信号の周波数に対して高いか低いかを検出することが可能となる。

【0049】

図8は、第3 の実施形態に係る位相同期回路300の動作を説明する図である。

【0050】

モニタ301 は、基準信号Refの立ち上がり又は立下りを基準とし、その時点での分周器103 のカウンタ103Aの値をモニタする。図8 の立ち上がりA 時点において、カウンタ103Aの値は「554」である。モニタ103Aは、立ち上がりA時点のカウンタ103Aの値として「554」を出力する。また、モニタ103Aは、基準信号Refの1周期後の立ち上がりB時点において、カウンタ103Aの値として「548」をモニタして、出力する。 差分検出回路302は、立ち上がりB時点と基準信号1周期前の立ち上がりA時点とのカウンタ103Aの値「554」の差分「-6」を算出する。差分検出回路302は、算出した差分「-6」と1周期前に算出した差分「-14」とを比較する。この場合、差分の符号は変化していないので、差分検出回路302は、検出信号を出力せず、検出した差分「-6」を保持部110に保持させる。

【0051】

次に、モニタ103Aは、立ち上がり時点Bから基準信号Refの1周期後の立ち上がり時点Cにおけるカウンタ103Aの値として「550」をモニタし出力する。差分検出回路302は、立ち上がり時点Cにおけるカウンタ103Aの値と基準信号1周期前の立ち上がり時点Bにおけるカウンタ103Aの値の差分「2」を算出する。差分検出回路302は、保持部110に保持された基準信号1周期前の差分「-6」と比較する。この場合、差分の符号が反転しているため、差分検出回路302は、検出信号を出力する。以上より、差分検出回路302は、差分の符号反転を検出することができ、分周信号の周波数が基準信号の周波数に近くなるタイミングを検出することができる。

【0052】

差分検出回路302が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号と基準信号の位相との差分を小さくする。

【0053】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0054】

<第4の実施形態>

図9は、第4の実施形態に係る位相同期回路400を示すブロック図である。第4の実施形態に係る位相同期回路400は、周波数差検出回路407の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107の構成と異なる。

【0055】

周波数差検出回路407は,ディジタル位相検出器401(TDC:Time to digital converter)と差分検出回路402とを備える算出部409と、保持部110とを備える構成である。算出部409は、基準信号の位相と分周信号の位相との位相差を検出し、検出した位相差と、基準信号又は分周信号の1周期前に検出した位相差との差分から分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を算出する。

【0056】

ディジタル位相検出器401は、遅延回路401Cの入力端子401Aとフリップフロップ(図示せず。)のクロック入力端子401Bと遅延回路401Cを備える。遅延回路401の入力端子401Aには、分周信号あるいは分周器103中の信号が入力される。フリップフロップ(図示せず。)のクロック入力端子401Bには、基準信号Refが入力される。

【0057】

ディジタル位相検出器401は、基準信号の位相と分周信号の位相との位相差を検出する。具体的には、ディジタル位相検出器401は、分周信号が遅延回路401Cの入力端子401Aに入力されてから基準信号がフリップフロップ(図示せず。)のクロック入力端子401Bに入力されるまでの遅れが、遅延回路の遅延段の何段分に相当するかを検出する。ディジタル位相検出器401は、この遅延段の段数から基準信号の位相と分周信号の位相差を検出する。

【0058】

差分検出回路402は、ディジタル位相検出器401が検出した遅延段数と、分周信号の1周期前に算出された遅延段数との差分を算出する。ここで、この差分が、第1の実施形態で周波数差検出回路107が算出すると説明した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分に対応する。そして、差分検出回路402が算出した差分は、保持部110に記憶される。差分検出回路402は、算出した差分と保持部110に記憶された、分周信号の1周期前に算出した差分とを比較し、差分の符号が変化した場合に、検出信号を出力する。

【0059】

図10は、第4 の実施形態に係る位相同期回路400の動作を説明する図である。

【0060】

ディジタル位相検出器401には、分周信号Div が遅延回路401Cの入力端子401Aに、基準信号Ref がフリップフロップ(図示せず。)のクロック入力端子401Bにそれぞれ入力される。ディジタル位相検出器401は、分周信号からの基準信号の遅れが、遅延回路の遅延段の何段分に相当するかを検出する。

【0061】

図10において、分周信号Divの立ち上がりAと基準信号Refの立ち上がりBとの間の時間差がディジタル位相検出器401の遅延段の「554」 段として検出されたとする。また、分周信号Divの1周期後の立ち上がりCと基準信号Refの立ち上がりDとの間の時間差がディジタル位相検出器401の遅延段の「548」 段と検出されたとする。差分検出回路402は、立ち上がりC−D間の遅延段と立ち上がりA−B間の遅延段との差分「-6」 を算出する。差分検出回路402は、1周期前に算出した差分「-14」と比較し、符号が変化していないことを検出する。その結果、検出信号は出力しない。差分検出回路402は、算出した差分「-6」を保持部110に保持させる。次に、ディジタル位相検出器401は、分周信号の立ち上がりCから1周期後の立ち上がりEと基準信号Refの立ち上がりFとの間の時間差がディジタル位相検出器401 の遅延段の「550」 段と検出されたとする。差分検出回路402は、立ち上がりE-F間の遅延段と1周期前の立ち上がりC−D間の遅延段との間の差分「2」 を検出する。差分検出回路402は、保持部110に保持された1周期前に算出した差分「-6」と比較する。その結果、前のサイクルと符号が反転していることを検出する。その結果、差分検出回路402は、検出信号を出力する。

【0062】

差分検出回路402が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0063】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0064】

尚、本実施形態では、ディジタル位相検出器701 には、分周信号Div が遅延回路401Cの入力端子401Aに、基準信号Ref がフリップフロップ(図示せず。)のクロック入力端子401Bに入力される構成としたが、例えば基準信号Ref が遅延回路401Cの入力端子401Aに、分周信号Div がフリップフロップ(図示せず。)のクロック入力端子401Bに入力される構成としてもよい。

【0065】

(変形例)

図11に、本実施形態の位相同期回路の変形例を示す。本実施形態では、差分検出回路402が、差分を検出するとともに、検出した差分と1周期前の差分との符号反転を検出するいずれの機能も備えていた。しかしながら、図11の変形例に示すように、差分出力回路402Aが、差分を検出し、符号反転検出回路402Bが、符号反転を検出し、検出した際には検出信号を出力するものとしてよい。

【0066】

<第5の実施形態>

図12は、第5 の実施形態に係る位相同期回路500を示すブロック図である。第5の実施形態に係る位相同期回路500は、周波数差検出回路507の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107の構成と異なる。

【0067】

周波数差検出回路507は、算出部509と保持部110とを備える。算出部509は、第1パルス幅検出回路501と第1の差分検出回路502と、第2パルス幅検出回路503と第2の差分検出回路504と、符号反転検出回路505とを備える。

算出部509は、位相比較器104が出力するUP信号のパルス幅である第1パルス幅又はDN信号のパルス幅である第2パルス幅と、1つ前の比較信号(UP信号またはDN信号)の第1又は第2パルス幅との差分から分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分の値を検出する。

【0068】

第1パルス幅検出回路501は、位相比較器104の出力のうちUP 信号の第1パルス幅を検出する。図14に、第1パルス幅検出回路501及び第2パルス幅検出回路503の具体例を示す。

【0069】

第1パルス幅検出回路501は、第1インバータ501Aと第1ディジタル位相検出器(第1TDC)501Bとを備える。位相比較器104の出力のうちUP信号は、第1ディジタル位相検出器501Bの遅延回路501B3の入力端子501B1に入力される。また、UP信号は、第1インバータ501Aによって符号が反転され、第1ディジタル位相検出器501Bのフリップフロップ(図示せず。)のクロック入力端子501B2に入力される。第1ディジタル位相検出器501Bは、UP信号の立ち上がりが遅延回路501B3の入力端子501B1に入力されてから、UP信号の立下りの反転信号がフリップフロップ(図示せず。)のクロック入力端子501B2に入力されるまでの遅れが、第1ディジタル位相検出器501Bの遅延回路501B3の遅延段の段数として検出できる。この遅延段の段数をUP信号の第1パルス幅として検出する。

【0070】

第1差分出力回路502は、第1パルス幅検出回路501が検出したUP信号の第1パルス幅と1つ前に検出したUP信号の第1パルス幅との差分を検出する。保持部110は、算出した差分を保持する。

【0071】

第2パルス幅検出回路503は、位相比較器104の出力のうちDN信号の第2パルス幅を検出する。

【0072】

第2パルス幅検出回路503は、第2インバータ503Aと第2ディジタル位相検出器(第2TDC)503Bとを備える。位相比較器104の出力のうちDN信号は、第2ディジタル位相検出器503Bの遅延回路503B3の入力端子503B1に入力される。また、DN信号は、第2インバータ503Aによって符号が反転され、第2ディジタル位相検出器503Bのフリップフロップ(図示せず。)のクロック入力端子503B2に入力される。第2ディジタル位相検出器503Bは、DN信号の立ち上がりが遅延回路503B3の入力端子503B1に入力されてから、DN信号の立下りの反転信号がフリップフロップ(図示せず。)のクロック入力端子503B2に入力されるまでの遅れが、第2ディジタル位相検出器503Bの遅延回路503B3の遅延段の段数として検出できる。この遅延段の段数をDN信号の第2パルス幅として検出する。

【0073】

第2差分検出回路504は、第2パルス幅検出回路503が検出したDN信号の第2パルス幅と1つ前に検出したDN信号の第2パルス幅との差分を検出する。保持部110は算出した差分を保持する。

【0074】

符号反転検出回路505は、第1パルス幅又は第2パルス幅いずれかの差分の符号が反転する際に検出信号を出力する。ここで、第1パルス幅の差分、又は第2パルス幅の差分いずれか一方が、分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分と対応する。

【0075】

図13は、第5 の実施形態に係る位相同期回路500の動作を説明する図である。

【0076】

第1パルス幅検出回路501は、 UP 信号の第1パルス幅を、第2パルス幅検出回路503は、DN 信号の第2パルス幅を、それぞれ検出する。第1の差分検出回路502、第2の差分検出回路504は、それぞれのパルス幅について、1つ前のデータとの差分を検出する。

【0077】

符号反転検出回路505は、第1の差分検出回路502、第2の差分検出回路504、それぞれが検出した第1パルス幅の差分、若しくは第2パルス幅の差分の符号が反転しているか否かを検出する。符号反転検出回路505は、符号の反転を検出した際、検出信号を出力する。

【0078】

ここで、符号反転検出回路505は、実際の動作では、第1差分出力回路502 が出力した差分および第2差分出力回路504 が出力した差分が入力されると、第1パルス幅と第2パルス幅のうちパルス幅が長い方の、パルス幅の差分の符号の反転を検出し、検出信号を出力する。

【0079】

図13を見るとわかるように、パルス幅が短い方のパルス幅の差分は、パルス幅が一定で(図13では、第2パルス幅が「10」で一定。)、パルス幅の差分は0だからである。すなわち、通常、符号の反転は検出されない。尚、第1パルス幅と第2パルス幅の長さが逆転するタイミング(図13では、第1パルス幅が「20」→「10」となり、第2パルス幅が、「10」→「18」となったタイミング)では、パルス幅が短い方(第1パルス幅)のパルス幅の差分は、「0」ではない。したがって、符号反転検出回路505は、パルス幅が短い方(第1パルス幅)の、パルス幅の差分の符号も検出し、差分の符号が反転した場合には、検出信号を出力する。

【0080】

図13の例においては、パルス幅は、UP信号のパルス幅(第1パルス幅)の方がDN信号のパルス幅(第2パルス幅)と比べて長く、符号反転検出回路505は、第1パルス幅に対応する差分の符号が反転する際に検出信号を出力する。

【0081】

ここで、パルス幅が短い方のパルス幅の差分が「0」の状態が継続する理由を以下で説明する。図13の例では、基準信号の位相が分周信号の位相より早い場合、位相比較器104は、基準信号の位相と分周信号の位相差に応じた大きさの第1パルス幅(「10」より大きな値)のUP信号を出力するとともに、基準信号の位相と分周信号の位相差によらず、第2パルス幅が「10」で一定なDN信号を出力する。一方、分周信号の位相が基準信号の位相より早い場合、位相比較器104は、分周信号の位相が基準信号の位相差に応じた大きさの第2パルス幅(「10」より大きな値)のDN信号を出力するとともに、基準信号の位相と分周信号の位相差によらず、第1パルス幅が「10」で一定なUP信号を出力する。

【0082】

すなわち、基準信号の位相が分周信号の位相より早い状態が継続した場合、位相比較器104は、第2パルス幅が「10」のDN信号を継続して出力し、分周信号の位相が基準信号の位相より早い状態が継続した場合、第1パルス幅が「10」のUP信号を継続して出力することとなる。したがって、基準信号の位相が分周信号の位相いずれかが早い状態が継続した場合、パルス幅が短い方のパルス幅の差分が、「0」となる状態が継続することとなる。

【0083】

したがって、通常、符号反転検出回路505は、UP信号とDN信号のうちパルス幅が長い信号に対応する差分の符号が反転する際に検出信号を出力する。

【0084】

尚、図13の例では、位相比較器104は、何も検知しない場合にパルス幅「10」の信号を出力するとしたが、何も検知しない場合に信号を出力しないようにしても良い。

【0085】

図13の例では、UP信号がDN信号よりパルス幅が長い場合であって、UP 信号のパルス幅が前のパルス幅と等しい場合、基準信号に対する分周信号の遅延に変化がなく、基準信号と分周信号の周波数が等しいこととなる。したがって、UP信号のパルス幅の変化が極小となるタイミング、即ち符号が反転するタイミングを検出することで分周信号と基準信号の周波数がほぼ等しくなるタイミングを検出することが可能となる。

【0086】

図13において、第1パルス幅検出回路501は、UP信号の立ち上がりAと立ち下がりB 間のパルス幅は「32」であり、立ち上がりCと立ち下がりD 間のパルス幅は「34」であり、立ち上がりEと立ち下がりFとの間のパルス幅は「31」 と検出する。第1の差分検出回路502は、立下りDのタイミングで差分「2」を算出し、立下りFのタイミングで「-3」を算出する。したがって、立下りF のタイミングで、符号反転検出回路505は、差分の符号が反転したことを検出し、検出信号を出力する。

【0087】

符号反転検出回路505が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号と基準信号の位相との差分を小さくする。

【0088】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0089】

<第6の実施形態>

図15は、6の実施形態に係る位相同期回路600を示すブロック図である。第6の実施形態に係る位相同期回路600は、周波数差検出回路607の構成が、第1の実施形態で示した位相同期回路100の周波数差検出回路107と異なる。

【0090】

周波数差検出回路607 は、算出部609と保持部110とを備える。算出部609は、論理回路601と、パルス幅検出回路602と、差分出力回路603と、符号反転検出回路604とを備える。

【0091】

論理回路601は、位相比較器104の出力のUP 信号とDN 信号の排他的論理和である第3の比較信号を出力する。

【0092】

パルス幅検出回路602は、第3比較信号のパルス幅を検出する。

【0093】

図16に、パルス幅検出回路602の具体的構成を示す。

【0094】

パルス幅検出回路602は、インバータ602Aとディジタル位相検出器(TDC)602Bとを備える。第3比較信号は、ディジタル位相検出器602Bの遅延回路602B3の入力端子602B1に入力される。また、第3比較信号は、インバータ602Aによって符号が反転され、ディジタル位相検出器602Bのフリップフロップ(図示せず。)のクロック入力端子602B2に入力される。ディジタル位相検出器602Bは、第3比較信号の立ち上がりが遅延回路602B3の入力端子602B1に入力されてから、第3比較信号の立下りの反転信号がフリップフロップ(図示せず。)のクロック入力端子602B2に入力されるまでの遅れが、第1ディジタル位相検出器501Bの遅延回路602B3の遅延段の段数として検出できる。この遅延段の段数を第3比較信号の第1パルス幅として検出する。

【0095】

差分出力回路603は、パルス幅検出回路602が検出した第3の比較信号のパルス幅と、1つ前にパルス幅検出回路602が検出した第3の比較信号のパルス幅との差分を検出する。ここで、図13でも示したように、第3の比較信号のうち、UP信号又はDN信号のいずれか一方は、一定となり、いずれか一方のみ変化する。例えば、分周信号の位相が基準信号の位相よりも遅れている場合、UP 信号のパルス幅だけが変化し、DN信号のパルス幅は一定となる。この場合、差分出力回路603は、UP信号のパルス幅の差分を検出する。一方、基準信号の位相が分周信号の位相よりも遅れている場合、差分出力回路603は、DN信号のパルス幅の差分を検出する。

【0096】

保持部110は、算出した差分を保持する。

【0097】

符号反転検出回路604は、差分出力回路603から入力された差分の符号が反転した場合に検出信号を出力する。符号反転検出回路604には、UP信号のパルス幅の差分、又はDN信号のパルス幅の差分が入力される。符号反転検出回路604は、差分の符号が反転するタイミングを検出することで分周信号と基準信号の周波数差が極小となるタイミングを検出する。

【0098】

符号反転検出回路505が、検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで、分周信号と基準信号の位相との差分を小さくする。

【0099】

以上、本実施形態にかかる位相同期回路によれば、セトリング時間を短縮することができる。

【0100】

<第7の実施形態>

次に、第7 の実施形態に係る位相同期回路700を説明する。第7の実施形態に係る位相同期回路700は、図5に示す第2の実施形態にかかる位相同期回路200と同様の構成を備える。図17は、第7の実施形態に係る位相同期回路700の動作を説明する図である。第7の実施形態に係る位相同期回路700を図5、図17を用いて説明する。本実施形態にかかる位相同期回路700は、差分検出回路702の機能が、第2の実施形態にかかる位相同期回路200の差分検出回路702の機能と異なる。

【0101】

第2の実施形態に係る位相同期回路200では、差分検出回路702は、差分の符号が反転したことを検出していた。

【0102】

本実施形態にかかる位相同期回路700では、差分検出回路702は、新たに算出した差分と、1周期前の差分との差を求める。差分検出回路702は、その差と差分検出回路702が新たに算出した差分との和を求めることにより、次に差分検出回路702が算出する差分の予測を行う。差分検出回路702は、次に差分検出回路702が算出する差分の予測を行うことで、差分の符号が反転する前に検出信号を出力する。

【0103】

例えば、図17において、差分検出回路702は、算出した差分「-21」と、1周期前に算出した差分「-28」との差「7」を算出する。差分検出回路702は、算出した差分「-21」と差「7」との和である「-14」を算出する。この「-14」が、次に差分検出回路702が算出する差分の予測値となる。このようにして、差分検出回路702は、1周期ごとに差分の予測値を算出する。図17の例では、予測値「-14」を算出した後、「-7」、「2」を算出する。予測値が「-7」から「2」となると、差分の予測値の符号が反転しているため、差分検出回路702は、検出信号を出力する。

【0104】

本実施形態の位相同期回路700によれば、差分検出回路702は、実際に差分の符号が反転する前に検出信号を出力することができる。

【0105】

差分検出回路702が検出信号を出力すると、位相調整回路108は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0106】

以上、本実施形態にかかる位相同期回路700によれば、より早いタイミングで、分周信号の位相と基準信号の位相を同期させることができるため、セトリング時間をより短縮することができる。

【0107】

<第8の実施形態>

図18は、第8の実施形態に係る位相同期回路800を示すブロック図である。

【0108】

第8の実施形態にかかる位相同期回路800は、位相調整回路808の構成が、第1 の実施形態で示した位相同期回路100の位相調整回路108の構成と異なる。

【0109】

位相調整回路808は、タイミング調整回路801と位相設定回路802とを備える。

【0110】

本実施形態の位相調整回路808は、検出信号が入力されると分周器103を制御し、分周信号の位相を基準信号の位相に合わせることで、分周信号と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0111】

タイミング調整回路801は、周波数差検出回路107 の検出信号と基準信号Refとを入力とし、検出信号が入力された次の基準信号Refの立ち上がりエッジあるいは立ち下がりエッジでタイミング信号を出力する。

【0112】

位相設定回路802は、タイミング信号が入力されると分周器103のカウンタ103Aの値を所定の値に設定する。

【0113】

図19は、位相同期回路800の動作を説明する図である。

【0114】

図19のDiv counter は分周器103のカウンタ103Aの値を示す。周波数差検出回路107から検出信号が入力されると、タイミング調整回路801は、基準信号Ref の立ち上がりでタイミング信号を出力する。位相設定回路802は、タイミング調整回路801からタイミング信号が入力されると、分周器103のカウンタ103Aの値を「0」にリセットする。

【0115】

図19の点線は、カウンタ103Aの値をリセットしない場合のカウンタ103Aの値の一例を示す。カウンタ103Aの値をリセットすると、カウンタ103Aの値は、図19の点線から実線のように変化する。位相設定回路802は、基準信号Ref の立ち上がりのタイミングに合わせてカウンタ103Aの値を「0」にリセットすることで、分周信号及び基準信号の周波数、位相が同期する。

【0116】

差分検出回路202が検出信号を出力すると、位相調整回路808は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0117】

本実施形態にかかる位相同期回路800によれば、周波数が一致したタイミングで位相を同期させるため、図19に示すように、オーバーシュートを減少し、セトリング時間を短縮することができる。

【0118】

<第9の実施形態>

図20は、第9 の実施形態に係る位相同期回路900を示すブロック図である。第9の実施形態にかかる位相同期回路900は、位相調整回路908の構成が、第1の実施形態で示した位相同期回路100の位相調整回路108の構成と異なる。

【0119】

位相調整回路908は、遅延回路901を備える。

【0120】

本実施形態の位相調整回路908は、検出信号が入力されると基準信号の位相を分周信号の位相と合わせることで、分周信号及び基準信号の周波数、位相を同期させる。

【0121】

具体的には、遅延回路901が、分周信号の位相と基準信号Refの位相を等しくするように基準信号Ref2の位相を遅延量だけ遅延させる。遅延回路901は、基準信号Ref2 の位相を遅延させる複数の遅延段902と、遅延段902 の複数の出力から信号を選択する選択回路903 を備える。ここで、選択回路903が出力した信号が基準信号Refとなる。遅延回路901は、選択回路903がどの遅延段902の出力を選択するか制御することで、分周信号Divの位相と基準信号Refの位相との差分が小さく(ゼロも含む。)なるように遅延量を調整する。

【0122】

選択回路903には、周波数差検出回路107から検出信号が入力され、分周器103から分周信号が入力される。選択回路902は、検出信号が入力された後、分周信号Div の出力がHI になったタイミングで、遅延段902の出力のうち分周信号Div に最も位相の近い出力を選択し、基準信号Ref として出力する。これにより分周信号は基準信号に対して周波数、位相とも同期する。

【0123】

本実施形態にかかる位相同期回路900によれば、周波数が一致したタイミングで位相を同期させるため、オーバーシュートを減少し、セトリング時間を短縮することができる。

【0124】

<第10の実施形態>

図21は、第10の実施形態に係る位相同期回路1000を示すブロック図である。第10の実施形態にかかる位相同期回路1000は、位相調整回路1008の構成が、第1 の実施形態で示した位相同期回路100の位相調整回路108の構成と異なる。

【0125】

位相調整回路1008は、分周器(MUX)1001を備える構成である。

【0126】

本実施形態の位相調整回路1008は、検出信号が入力されると基準信号の位相を分周信号の位相と合わせることにより、基準信号の位相と分周信号の位相を同期させる。位相調整回路1008は、分周信号の位相と基準信号の位相を同期させることで分周信号の位相と基準信号の位相との差分を小さくする。

【0127】

分周器1001は、基準信号Ref より周波数の高い基準信号Ref2 を入力とし,基準信号Ref2 を分周し、基準信号Refを出力する。

【0128】

周波数差検出回路107から検出信号が入力されると、分周信号Div の出力がHI になったタイミングで、分周器1001 のカウンタ(図示せず)をリセットする。これにより分周信号は基準信号に対して周波数、位相とも同期する。

【0129】

これにより分周信号は基準信号に対して周波数、位相とも同期する.

本実施形態にかかる位相同期回路によれば、周波数が一致したタイミングで位相を同期させるため、オーバーシュートを減少し、セトリング時間を短縮することができる。

【0130】

<第11の実施形態>

図22は、第11の実施形態に係る位相同期回路1100について説明する。位相同期回路1100は、第1の実施形態に係る位相同期回路100と同様の構成である。位相同期回路1100は、ループフィルタ1106の構成、機能が位相同期回路100のループフィルタ106と異なる。

【0131】

図22に、第11の実施形態に係る位相同期回路1100のループフィルタ1106を示す。

【0132】

図22に示すように、ループフィルタ1106は、一端がチャージポンプ105に接続され、他端が電圧制御発振器102に接続された接続部1805と、一端が接続部1805に接続され、他端が第1電源電位(本実施形態では、グランド)に接続された第1コンデンサ1803と、第1コンデンサ1803と並列に配置され、一端が接続部1805に接続された抵抗1801と、一端が抵抗1801と直列に接続され、他端が第1電源電位に接続された第2コンデンサ1802と、抵抗1801に並列に配置され、一端が第2コンデンサ1802の一端と接続され、ONのときは他端が接続部1805に接続され、OFFのときは、他端が接続部1805に接続されないスイッチ1804とを備え、周波数差検出回路107が検出信号を生成前は、スイッチ1804がONとなり、周波数差検出回路107が検出信号を生成すると、スイッチ1804がOFFとなる。

【0133】

図22のループフィルタ1106において、抵抗1801 と第2コンデンサ1802 の間の端子Vb は、制御電圧端子Va に比べて応答が遅い。図23に一般的なPLLにおけるループフィルタの動作を説明する。図23(a)に示すように、位相比較器104がUP 信号を出力している間、ループフィルタ106に電流が供給される。このとき、Vb はVa より応答が遅く、VbとVaの間で電圧差が生じる。周波数差検出回路107が検出信号を出力し、分周信号と基準信号の周波数、位相ともに同期した場合において、ループフィルタのVa とVb に電圧差が生じている場合、図23(b)に示すように、第1コンデンサ1801から第2コンデンサ1803へと電流が流れ、Va はVb に近付いていく。その結果、電圧制御発振器102の周波数が下がってしまう。これによって、図23(c)に示すように、分周信号を基準信号の周波数と位相に合わせるために、UP信号が再び流れる。このように、VbはVaより応答が遅いため、Vaの電圧が安定しない。その結果、セトリング時間が増加してしまう。

【0134】

本実施形態のループフィルタ1106では、これを防ぐために、周波数差検出回路107が検出信号を出力されるまで、スイッチ1804 をONとし、検出信号が出力されたらスイッチ1804をOFFとする。スイッチ1804をONとしている間、第2コンデンサ1802の一端はスイッチ1804を介して接続部1805に接続される。したがって、VaとVbに電圧差が生じないため、VaとVbとが変化することがなくなる。その結果、分周信号を基準信号の周波数と位相に合わせるためのセトリング時間を減少させることが出来る。

【0135】

<第12の実施形態>

次に、第12の実施形態にかかる位相同期回路1200を説明する。位相同期回路1200は、図18に示す第8の実施形態に係る位相同期回路800と同様の構成である。位相同期回路1200は、位相比較器1204の機能が、位相同期回路800の位相比較器104の機能と異なる。

【0136】

本実施形態に係る位相比較器1204は、周波数差検出回路107 により検出信号が出力されると、一定時間の間、位相比較器1204 の動作を停止させる。

【0137】

図24は、本実施形態の位相同期回路1200の動作を説明する図である。図24に示すように、位相同期回路1200は、分周器103のカウンタをリセットすることにより分周信号の位相を基準信号の位相に合わせる。このとき、基準信号Ref の信号はHI になっているため、位相比較器を停止させる機能を有さない場合、位相比較器はUP 信号を出力してしまう。これを防ぐため、周波数差検出回路108 が検出信号を出力してから一定時間の間位相比較器1204の動作を停止させる。位相比較器1204は、少なくとも周波数差検出回路107が検出信号を生成してから、位相調整回路808が前記分周信号と前記基準信号との位相を同期させるまでの間、比較信号を生成しないことが好ましい。そのため、周波数差検出回路107が検出信号を生成してから、次に基準信号が立ち上がるタイミングまでを含む一定時間の間、位相比較器1204の動作を停止させる。

【0138】

<第13の実施形態>

次に、第13の実施形態にかかる位相同期回路1300を説明する。位相同期回路1300は、図18に示す第8の実施形態に係る位相同期回路800と同様の構成である。位相同期回路1300は、チャージポンプ1305の機能が、位相同期回路800のチャージポンプ105の機能と異なる。

【0139】

第13の実施形態にかかるチャージポンプ1305 は、周波数差検出回路107 により検出信号が出力されると、一定時間の間、チャージポンプ1305の動作を停止させる。

【0140】

位相同期回路1300の動作において、分周器103のカウンタをリセットすることにより分周信号の位相を基準信号の位相に合わせる。このとき、基準信号Ref の信号はHI になっているため、位相比較器104はUP 信号を出力してしまう。このとき、位相比較器104がUP 信号を出力してもチャージポンプ1305 が動作しないよう動作を停止させる。チャージポンプ1305は、少なくとも周波数差検出回路107が検出信号を生成してから、位相調整回路108が前記分周信号と前記基準信号との位相を同期させるまでの間、電流を供給しないことが好ましい。そのため、周波数差検出回路107が検出信号を生成してから、次に基準信号が立ち上がるタイミングまでを含む一定時間の間、チャージポンプ1305の動作を停止させる。

【0141】

<第14の実施形態>

図25は、第14の実施形態に係る位相同期回路1400を示すブロック図である。図26は、位相同期回路1400の動作を説明する図である。

【0142】

図25に示すように、位相同期回路1400は、実施形態1の位相同期回路と比べて、ミスエッジカウンタ1401を更に備える構成である。

【0143】

図26に示すように、ミスエッジカウンタ1401は、基準信号と分周信号の位相差が2πを越えた回数をカウントする。チャージポンプ105 は、ミスエッジカウンタ1401の値に応じてチャージポンプの電流を調整する。

【0144】

周波数差検出回路108により検出信号が出力されたときにミスエッジカウンタ1401のカウンタを0にリセットする。これにより、チャージポンプの電流は通常の値となる。

【0145】

<第15の実施形態>

図27は、第15の実施形態にかかる無線機2000である。

【0146】

無線機2000は、無線信号を送信および受信するアンテナ2001 と,アンテナ2001により受信した無線信号を増幅し,増幅信号を生成する第1増幅器2002 と、発振信号を生成する位相同期回路100と、増幅信号と発振信号とを乗算し、受信ベースバンド信号を生成する第1ミキサ回路2004 と、送信ベースバンド信号と発振信号とを乗算し、送信信号を生成する第2ミキサ回路2005 と、送信信号を増幅し無線信号を出力する第2増幅器2006 とを有する。

【0147】

本実施形態にかかる無線機2000では、位相同期回路100が、発振信号の周波数の切り替え時に、セトリング時間を短縮することができる。

【0148】

なお、本発明は上記の実施形態のそのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記の実施形態に開示されている複数の構成要素の適宜な組み合わせにより、種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施形態にわたる構成要素を適宜組み合わせてもよい。

【符号の説明】

【0149】

100、200、300、400、500、600、700、800、900、1000、1100、1200、1300、1400・・・位相同期回路、102・・・電圧制御発振器、103、1001・・・分周器、103A・・・カウンタ、104、1204・・・位相比較器、105、1305・・・チャージポンプ、106、1106・・・ループフィルタ、107、207、307、407、507、607・・・周波数差検出回路、108、808、908、1008・・・位相調整回路、109、209、309、409、509、609・・・算出部、110・・・保持部、201・・・カウンタ、202、302、402、702・・・差分検出回路、301・・・モニタ、401・・・TDC、401A、501B1、503B1、602B1・・・入力端子、401B、501B2、503B2、602B2・・・クロック入力端子、401C、501B3、503B3、602B3、901・・・遅延回路、402A・・・差分出力回路、402B、505・・・符号反転検出回路、501・・・第1パルス幅検出回路、502・・・第1差分出力回路、503・・・第2パルス幅検出回路、504・・・第2差分出力回路、501A・・・第1インバータ、501B・・・第1TDC、503A・・・第2インバータ、503B・・・第2TDC、601・・・論理回路、602・・・パルス幅検出回路、603・・・差分出力回路、604・・・符号反転検出回路、602A・・・インバータ、602B・・・TDC、801・・・タイミング調整回路、802・・・位相設定回路、902・・・遅延段、903・・・選択回路、1801・・・抵抗、1802・・・第2コンデンサ、1803・・・第1コンデンサ、1804・・・スイッチ、1805・・・接続部、1401・・・ミスエッジカウンタ、2000・・・無線機、2001・・・アンテナ、2002・・・第1増幅器、2004・・・第1ミキサ回路、2005・・・第2ミキサ回路、2006・・・第2増幅器。

【特許請求の範囲】

【請求項1】

制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、

前記発振信号を分周して分周信号を生成する分周器と、

前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、

前記比較信号に応じた電流を生成するチャージポンプと、

前記電流をフィルタリングし、前記制御信号を生成するフィルタと、

前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する検出回路と、

前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路と、

を備えることを特徴とする位相同期回路。

【請求項2】

前記検出回路は、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出する算出部と、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を保持する保持部とを有し、前記保持部が保持する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分の符号が正であり、前記算出部が算出する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分の符号が負である場合に前記検出信号を生成することを特徴とする請求項1記載の位相同期回路。

【請求項3】

前記検出回路は、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出する算出部と、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を保持する保持部とを有し、前記保持部が保持する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分の符号が負であり、前記算出部が算出する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分の符号が正である場合に前記検出信号を生成することを特徴とする請求項1記載の位相同期回路。

【請求項4】

前記検出回路は、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出する算出部を有し、前記算出部が算出する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分がゼロである場合に前記検出信号を生成することを特徴とする請求項1記載の位相同期回路。

【請求項5】

前記位相調整回路は、前記検出信号が生成されると、前記分周信号の位相を前記基準信号の位相に同期させることを特徴とする請求項1記載の位相同期回路。

【請求項6】

前記位相調整回路は、前記検出信号が生成されると、前記基準信号の位相を前記分周信号の位相に同期させることを特徴とする請求項1記載の位相同期回路。

【請求項7】

前記算出部は、前記分周器の分周数と、前記基準信号の1周期中に含まれる前記発振信号のサイクル数との差から前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出することを特徴とする請求項2記載の位相同期回路。

【請求項8】

前記分周器は、発振信号のサイクル数をカウントするカウンタを備え、

前記算出部は、前記カウンタの値と基準信号の1周期前の前記カウンタの値との差から前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出することを特徴とする請求項2記載の位相同期回路。

【請求項9】

前記算出部は、前記基準信号の位相と前記分周信号の位相との位相差を検出する位相差検出器を備え、前記位相差検出器が検出した位相差と当該検出1周期前の位相差とから前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出することを特徴とする請求項2記載の位相同期回路。

【請求項10】

前記位相比較器は、

前記基準信号の位相が前記分周信号の位相より早い場合、前記基準信号の立ち上がりから前記分周信号の立ち上がりまでと等しい第1パルス幅を有する第1の比較信号を生成し、前記基準信号の位相が前記分周信号の位相より遅い場合、前記分周信号の立ち上がりから前記基準信号の立ち上がりまでと等しい第2パルス幅を有する第2の比較信号を生成し、

前記検出回路の前記算出部は、前記第1又は前記第2パルス幅と、1つ前の比較信号の第1又は第2パルス幅との差から前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出することを特徴とする請求項2記載の位相同期回路。

【請求項11】

前記分周器は、前記サイクル数をカウントするカウンタを備え、

前記位相調整回路は、前記検出信号が生成されると、前記カウンタの値をリセットするように前記カウンタを制御する

ことを特徴とする請求項5記載の位相同期回路。

【請求項12】

前記位相調整回路は、前記基準信号の位相を遅延量だけ遅延させる遅延回路を備え、

前記遅延回路は、前記検出信号が生成されると、前記分周信号の位相と前記基準信号の位相との差分が小さくなるよう前記遅延量を調整することを特徴とする請求項6記載の位相同期回路。

【請求項13】

前記位相調整回路は、第1基準信号を分周し、前記基準信号を生成する第2分周器を備え、前記第2分周器は、前記第1基準信号のサイクル数をカウントするカウンタを備え、前記第2分周器は、前記検出信号が生成されると、前記カウンタの値をリセットすることを特徴とする請求項6記載の位相同期回路。

【請求項14】

前記検出回路は、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分と前記保持部が保持する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分との差と前記前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分とから1周期後に検出される分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を予測し、当該予測した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が極小となった場合に、前記検出信号を生成することを特徴とする請求項2記載の位相同期回路。

【請求項15】

前記フィルタは、一端が前記チャージポンプに接続され、他端が前記電圧制御発振器に接続された接続部と、

一端が前記接続部に接続された抵抗と、

一端が前記抵抗と直列に接続され、他端が第1電源電位に接続されたコンデンサと、

前記抵抗に並列に配置され、一端が前記コンデンサの一端と接続され、ONのときは他端が前記接続部に接続され、OFFのときは、他端が前記接続部に接続されないスイッチと、

前記検出回路が検出信号を生成前は、前記スイッチがONとなり、前記検出回路が検出信号を生成すると、前記スイッチがOFFとなることを特徴とする請求項1記載の位相同期回路。

【請求項16】

前記位相比較器は、前記検出回路が前記検出信号を生成してから、一定時間、前記比較信号を生成しないことを特徴とする請求項1記載の位相同期回路。

【請求項17】

前記チャージポンプは,前記検出回路が前記検出信号を生成してから、一定時間、前記電流を出力しないことを特徴とする請求項1記載の位相同期回路。

【請求項18】

前記基準信号と前記分周信号の位相差が2πを超えた回数をカウントし、カウント数に応じた大きさの信号を出力するカウンタを備え、

前記チャージポンプは、前記信号に応じた電流を出力し、

前記検出回路が、検出信号を生成すると、前記カウンタの値をリセットすることを特徴とする請求項1記載の位相同期回路。

【請求項19】

無線信号を送信および受信するアンテナと、

前記アンテナより受信した無線信号を増幅し、増幅信号を生成する第1増幅器と、

送信信号を増幅し、無線信号を生成する第2増幅器と、

前記発振信号を生成する請求項1 記載の位相同期回路と、

前記増幅信号と前記発振信号とを乗算し、受信ベースバンド信号を生成する第1ミキサ回路と、

送信ベースバンド信号と前記発振信号とを乗算し、前記送信信号を生成する第2ミキサ回路とを備えることを特徴とする無線機。

【請求項1】

制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、

前記発振信号を分周して分周信号を生成する分周器と、

前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、

前記比較信号に応じた電流を生成するチャージポンプと、

前記電流をフィルタリングし、前記制御信号を生成するフィルタと、

前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する検出回路と、

前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路と、

を備えることを特徴とする位相同期回路。

【請求項2】

前記検出回路は、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出する算出部と、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を保持する保持部とを有し、前記保持部が保持する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分の符号が正であり、前記算出部が算出する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分の符号が負である場合に前記検出信号を生成することを特徴とする請求項1記載の位相同期回路。

【請求項3】

前記検出回路は、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出する算出部と、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を保持する保持部とを有し、前記保持部が保持する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分の符号が負であり、前記算出部が算出する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分の符号が正である場合に前記検出信号を生成することを特徴とする請求項1記載の位相同期回路。

【請求項4】

前記検出回路は、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出する算出部を有し、前記算出部が算出する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分がゼロである場合に前記検出信号を生成することを特徴とする請求項1記載の位相同期回路。

【請求項5】

前記位相調整回路は、前記検出信号が生成されると、前記分周信号の位相を前記基準信号の位相に同期させることを特徴とする請求項1記載の位相同期回路。

【請求項6】

前記位相調整回路は、前記検出信号が生成されると、前記基準信号の位相を前記分周信号の位相に同期させることを特徴とする請求項1記載の位相同期回路。

【請求項7】

前記算出部は、前記分周器の分周数と、前記基準信号の1周期中に含まれる前記発振信号のサイクル数との差から前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出することを特徴とする請求項2記載の位相同期回路。

【請求項8】

前記分周器は、発振信号のサイクル数をカウントするカウンタを備え、

前記算出部は、前記カウンタの値と基準信号の1周期前の前記カウンタの値との差から前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出することを特徴とする請求項2記載の位相同期回路。

【請求項9】

前記算出部は、前記基準信号の位相と前記分周信号の位相との位相差を検出する位相差検出器を備え、前記位相差検出器が検出した位相差と当該検出1周期前の位相差とから前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出することを特徴とする請求項2記載の位相同期回路。

【請求項10】

前記位相比較器は、

前記基準信号の位相が前記分周信号の位相より早い場合、前記基準信号の立ち上がりから前記分周信号の立ち上がりまでと等しい第1パルス幅を有する第1の比較信号を生成し、前記基準信号の位相が前記分周信号の位相より遅い場合、前記分周信号の立ち上がりから前記基準信号の立ち上がりまでと等しい第2パルス幅を有する第2の比較信号を生成し、

前記検出回路の前記算出部は、前記第1又は前記第2パルス幅と、1つ前の比較信号の第1又は第2パルス幅との差から前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分を算出することを特徴とする請求項2記載の位相同期回路。

【請求項11】

前記分周器は、前記サイクル数をカウントするカウンタを備え、

前記位相調整回路は、前記検出信号が生成されると、前記カウンタの値をリセットするように前記カウンタを制御する

ことを特徴とする請求項5記載の位相同期回路。

【請求項12】

前記位相調整回路は、前記基準信号の位相を遅延量だけ遅延させる遅延回路を備え、

前記遅延回路は、前記検出信号が生成されると、前記分周信号の位相と前記基準信号の位相との差分が小さくなるよう前記遅延量を調整することを特徴とする請求項6記載の位相同期回路。

【請求項13】

前記位相調整回路は、第1基準信号を分周し、前記基準信号を生成する第2分周器を備え、前記第2分周器は、前記第1基準信号のサイクル数をカウントするカウンタを備え、前記第2分周器は、前記検出信号が生成されると、前記カウンタの値をリセットすることを特徴とする請求項6記載の位相同期回路。

【請求項14】

前記検出回路は、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分と前記保持部が保持する前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分との差と前記前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分とから1周期後に検出される分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分を予測し、当該予測した分周信号の周波数の定数倍の値と基準信号の周波数の定数倍の値との差分が極小となった場合に、前記検出信号を生成することを特徴とする請求項2記載の位相同期回路。

【請求項15】

前記フィルタは、一端が前記チャージポンプに接続され、他端が前記電圧制御発振器に接続された接続部と、

一端が前記接続部に接続された抵抗と、

一端が前記抵抗と直列に接続され、他端が第1電源電位に接続されたコンデンサと、

前記抵抗に並列に配置され、一端が前記コンデンサの一端と接続され、ONのときは他端が前記接続部に接続され、OFFのときは、他端が前記接続部に接続されないスイッチと、

前記検出回路が検出信号を生成前は、前記スイッチがONとなり、前記検出回路が検出信号を生成すると、前記スイッチがOFFとなることを特徴とする請求項1記載の位相同期回路。

【請求項16】

前記位相比較器は、前記検出回路が前記検出信号を生成してから、一定時間、前記比較信号を生成しないことを特徴とする請求項1記載の位相同期回路。

【請求項17】

前記チャージポンプは,前記検出回路が前記検出信号を生成してから、一定時間、前記電流を出力しないことを特徴とする請求項1記載の位相同期回路。

【請求項18】

前記基準信号と前記分周信号の位相差が2πを超えた回数をカウントし、カウント数に応じた大きさの信号を出力するカウンタを備え、

前記チャージポンプは、前記信号に応じた電流を出力し、

前記検出回路が、検出信号を生成すると、前記カウンタの値をリセットすることを特徴とする請求項1記載の位相同期回路。

【請求項19】

無線信号を送信および受信するアンテナと、

前記アンテナより受信した無線信号を増幅し、増幅信号を生成する第1増幅器と、

送信信号を増幅し、無線信号を生成する第2増幅器と、

前記発振信号を生成する請求項1 記載の位相同期回路と、

前記増幅信号と前記発振信号とを乗算し、受信ベースバンド信号を生成する第1ミキサ回路と、

送信ベースバンド信号と前記発振信号とを乗算し、前記送信信号を生成する第2ミキサ回路とを備えることを特徴とする無線機。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【公開番号】特開2012−75000(P2012−75000A)

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願番号】特願2010−219269(P2010−219269)

【出願日】平成22年9月29日(2010.9.29)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願日】平成22年9月29日(2010.9.29)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]