位相同期発振器及びそれを用いたマルチレーダシステム

【課題】与えられた周波数帯域をより効率的に利用することができるマルチレーダシステムを提供する。

【解決手段】周波数が周期的に増減する信号を生成して出力する複数のレーダを含んで構成されるマルチレーダシステムであって、各レーダは、周期的に増減する周波数の上限値及び下限値が各レーダの信号毎に互いに異なり且つ当該上限値及び下限値になるタイミングが各信号毎に互いにほぼ一致するように所定の同期信号に同期して信号を生成し、出力する。これにより、電波干渉を生じさせずに、各信号の周波数間隔を詰めることができ、より多くのチャネルを設定することができる。

【解決手段】周波数が周期的に増減する信号を生成して出力する複数のレーダを含んで構成されるマルチレーダシステムであって、各レーダは、周期的に増減する周波数の上限値及び下限値が各レーダの信号毎に互いに異なり且つ当該上限値及び下限値になるタイミングが各信号毎に互いにほぼ一致するように所定の同期信号に同期して信号を生成し、出力する。これにより、電波干渉を生じさせずに、各信号の周波数間隔を詰めることができ、より多くのチャネルを設定することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、位相同期発振器及びそれを用いたマルチレーダシステムに関する。本発明は、特に、FM−CWレーダ等のRF帯発振部に用いて好適なる位相同期発振器及びそれを用いたマルチレーダシステムに用いると好適である。

【背景技術】

【0002】

図35は従来技術を説明する図で、図35(A)は従来のFM−CWレーダの周波数変調部分を示している。FM−CW方式の基本構成は、ファンクションジェネレータ(FG)等で三角波の変調信号を発生し、この変調信号により電圧制御発振器(VCO)に周波数変調をかけるものである。FM−CW方式で重要なことは、正確な三角波の周波数変調をかけることであり、このためには、例えば中心周波数を基準にして、その最大及び最小周波数偏移が変化しないこと、周波数が時間とともに直線的(リニア)に変化すること、すなわちその傾き(周波数変化速度)が変化しないこと、が必要である。FM−CWレーダの出力周波数は、VCOの外部条件(温度、電源等)の安定度に依存し、また出力周波数の周波数偏移については、VCOの変調感度、出力周波数に依存するため、高安定なVCOが必要となる。また、周波数が直線的に増加するためにはVCOの良好なリニアリティーが必要となる。

【0003】

図35(B)は従来のFM−CWレーダ送信部の典型的な構成を示している。発振周波数の温度変化に対してはCPUが温度センサで検出した温度によりデータテーブルを参照し、三角波の中心電圧を補正する。また、発振周波数のリニアリティーについてはCPUが同じくデータテーブルを参照することで三角波電圧の補正を行う。

【0004】

図35(C)は、従来のFM−CWレーダ送信部の他の構成例を示す図で、PLL(Phase Locked Loop)回路に三角波を重畳する方法を示している。この方法では、PLLを中心周波数で位相同期させることにより中心周波数を安定化する。一方、この中心周波数に加える周波数変移のリニアリティーについては、CPUがデータテーブルを参照することにより三角波電圧を補正する。

【0005】

また従来は、変調信号として水晶発振器6aに位相同期した三角波を用いることで発振周波数を安定化させると共に、出力のRF信号を周波数検波することで周波数偏移の上限や下限を超えないように制御を行う発振回路が知られている(特許文献1)。

【特許文献1】特開平6−120735

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかし、上記データテーブルを使用して発振周波数の温度変化やリニアリティーを補正する方式であると、別途に大きなデータテーブルを持つ必要があるばかりか、回路素子のバラツキに応じて装置毎に個別のデータテーブルを作成する必要があり、試験工数が大幅に増えてしまう。また、上記図35(C)の構成では、三角波で変調したVCO出力に対してPLLによるフィードバックがかかってしまうため、VCO出力の変調特性が悪化してしまう。また、特許文献1のVCOの変調特性はリニアであることが前提であり、もしリニアで無い場合は、データテーブル等を使用してリニアリティー補正する必要がある。

【0007】

また、マルチレーダシステムは、FM−CWレーダを複数個配置して構成され、各レーダに異なる検知エリアを割り当てることで、より広範囲なエリアをより精度良く検知することができる。マルチレーダシステムは、複数のレーダを搭載した一つの装置であってよいし、また、少なくとも一つのレーダを搭載した複数の装置であってもよい。例えば、自動車のような車両にレーダが搭載される場合、各車両に搭載されるレーダがマルチレーダシステムを構成する。

【0008】

図36は、従来におけるマルチレーダシステムにおける複数のレーダそれぞれの周波数割り当てを説明する図である。図36(A)は、レーダから送信される電波が干渉する場合を示し、同一の周波数帯域を用いて、複数のレーダから三角波変調された送信信号を送信すると、送信信号の周波数が同一になるタイミングが生じ、どちらのレーダからの送信信号であるか区別がつかず、正しい測定ができなくなる。そのため、複数のレーダを配置する場合、各レーダの送信信号の周波数が互いに干渉しないようにする必要があるため、図36(B)に示すように、周波数帯域が互いに重ならないように、少なくとも周波数の変動幅分の周波数帯域を各レーダに割り当てる必要がある。

【0009】

一方で、使用可能な周波数帯域が制限される場合には、一つのレーダあたりに割り当てる帯域を広く確保することができない。すなわち、送信信号の周波数偏移を大きく取ることができない。送信信号の周波数偏移が大きいほど、感度・分解能も上がるので、割り当てる帯域が十分に広くない場合、感度・分解能が低下する。

【0010】

また、温度変化や経時変化などにより、送信信号の中心周波数や周波数偏移の変動分を考慮して、隣接する送信信号間に所定の間隔をあける必要がある。この変動分が大きいと、干渉を防ぐために間隔を広く確保しなければならず、送信信号の周波数偏移量又はレーダ数(チャネル数)が犠牲となる。

【0011】

図37は、三角波で周波数変調された送信信号の中心周波数や周波数偏移の変動を説明する図である。図37(A)は、送信信号の中心周波数が変動する場合を示し、図37(B)は、送信信号の周波数偏移が変動する場合を示す。また、図37(C)は、周波数の変動分を考慮した周波数の割り当て例を示す図である。図37(C)では、1GHzの帯域に対して、周波数偏移を200MHz、変動分を50MHzとすると、2つのレーダしか配置することができず(2チャネルしか確保できず)、周波数帯域が効率的に利用されていない。

【0012】

本発明は上記従来技術の問題点に鑑みなされたもので、その目的とするところは、VCO回路の特性バラツキや温度変動によらず、簡単な構成及び制御で常に高安定なVCO出力が得られる位相同期発振器を提供することにある。

【0013】

また、本発明の目的は、常に高安定なVCO出力が得られる位相同期発振器を用いて、与えられた周波数帯域をより効率的に利用することができるマルチレーダシステムを提供することにある。

【課題を解決するための手段】

【0014】

本発明の第1の態様(VCOの校正)による位相同期発振器は、基準信号と比較信号の位相を比較する位相比較器と、該位相比較器の位相誤差信号を積分するローパスフィルタと、該ローパスフィルタの後段に介在して本器の主制御を行う制御部と、該制御部出力の制御電圧に応じた周波数の信号を発生するVCO回路と、該VCO回路の出力信号を分周して前記比較信号を形成する可変分周器とからなるPLLループを備える位相同期発振器であって、前記制御部は、PLLループを複数の周波数でロックさせて各ロック時の制御電圧を測定する制御電圧測定手段と、前記測定された各制御電圧に基づき、前記各周波数を結ぶ区間の周波数変化を代表する変調感度を求めるリニアリティー校正手段とを備えたものである。

【0015】

本発明によれば、PLLループを複数の周波数でロックさせる構成により、VCOの変調感度にバラツキや温度依存性があっても、該VCOを所要周波数で発振させるための制御電圧が容易かつ正確に得られる。

【0016】

本発明の第2の態様(VCOの駆動)による位相同期発振器は、前記PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を生成し、出力するVCO駆動手段を更に備えたものである。

【0017】

本発明によれば、VCO回路をリニアリティー校正された電圧信号で駆動する構成により、VCO回路の特性バラツキや温度変動によらず、常に安定した発振特性が得られる。

【0018】

本発明の第3の態様(間欠的なPLL制御)では、VCO駆動手段は、VCO回路が中心周波数を出力するタイミングに同期してローパスフィルタの出力をサンプリングし、検出した位相誤差信号が所定範囲を超える場合は、該位相誤差信号を小さくする方向に制御電圧をオフセットする。従って、間欠的なPLL制御により、中心周波数を一定に維持できる。

【0019】

本発明の第4の態様(間欠的なFLL制御)による位相同期発振器は、基準信号を分周する第1の分周器と、VCO回路の出力を分周して前記比較信号を形成する第2の分周器とを備え、前記VCO駆動手段は、前記第1,第2の分周器のカウンタをVCO回路に加える信号周期の整数倍周期で定期的にリセットすると共に、前記VCO回路が中心周波数を出力するタイミングに同期してサンプリングしたローパスフィルタ出力の位相誤差信号が所定範囲を超える場合は、該位相誤差信号を小さくする方向に制御電圧をオフセットする。

【0020】

本発明においては、第1,第2の分周器のカウンタを定期的にリセットする構成により、両分周信号を強制的に位相あわせする。しかし、もしVCO出力の周波数がずれていると、両分周信号間の位相は速やかに広がってしまう。そこで、本発明では、ローパスフィルタ出力の位相誤差信号を定期的に検出することで、該位相誤差信号の変化速度を監視し、VCO出力の周波数がずれているか否かを検出する。本発明では、第1,第2の分周器のカウンタを定期的にリセットすることで特定の絶対位相へ引き込まないので、位相引き込みが速い。なお、周波数のみ揃っていればロック状態にあると判定する制御を本明細書ではFLL(Frequency Locked Loop)制御と呼ぶ。

【0021】

本発明の第5の態様(PLLの高速引き込み)による位相同期発振器は、基準信号を分周する第1の可変分周器と、VCO回路の出力を分周して前記比較信号を形成する第2の可変分周器とを備え、前記制御部は、前記第1,第2の可変分周器に所定の分周比を設定後、PLLループを形成して基準信号と比較信号間の位相引き込みを開始する際に、前記VCO回路に前記所定の分周比に対応する制御電圧を加えると共に、前記第1,第2の可変分周器のカウンタをリセットするものである。

【0022】

本発明によれば、VCO回路に当初から設定分周比に対応する制御電圧を加えることで当初から所要周波数に近いVCO出力が得られる。また、第1,第2の可変分周器のカウンタをリセットすることにより、両分周信号の初期位相が強制的に揃う。この場合に、両分周信号の周波数は既に略一致しており、両分周信号の初期位相が合っているため、PLLループは速やかにロック状態に収束する。

【0023】

本発明の第6の態様(温度により変調感度が変化しないVCO回路を備える)による位相同期発振器は、基準信号と比較信号の位相を比較する位相比較器と、該位相比較器の位相誤差信号を積分するローパスフィルタと、該ローパスフィルタの後段に介在して本器の主制御を行う制御部と、該制御部出力の制御電圧に応じた周波数の信号を発生するVCO回路と、前記VCO回路の出力信号を分周して前記比較信号を形成する可変分周器とからなるPLLループを備える位相同期発振器であって、前記制御部は、PLLのロック周波数を所定間隔で変化させ、所定の周波数範囲をカバーする範囲につき各ロック時の制御電圧を測定する制御電圧測定手段と、前記測定した制御電圧の変動範囲を複数区間に分割して、各区間を代表する変調感度を求めるリニアリティー校正手段と、PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、VCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を、前記ロック時の制御電圧と前記求めた各区間を代表する変調感度に基づき生成し、出力するVCO駆動手段とを備えたものである。

【0024】

本発明によれば、予め所要周波数範囲の変調感度を一旦求めておけば、該変調感度は温度によりあまり変化しないので、任意温度におけるVCO駆動時には、VCO駆動手段は、PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、VCO回路に所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を、前記ロック時の制御電圧(基準電圧)と前記求めた各区間を代表する変調感度に基づき生成し、出力することで、温度によらず、VCO回路を常に正しい周波数で駆動できる。

【0025】

本発明の第7の態様によるマルチレーダシステムは、上記本発明の第1乃至第6の態様いずれかに記載の位相同期発振器を有する複数のFM−CWレーダを備えて構成されるマルチレーダシステムであって、各FM−CWレーダの前記制御部は、周期的に増減する制御電圧であって且つ前記制御電圧の増減方向及び増減速度が互いに一致するように所定の同期信号に同期した前記制御電圧を生成し、各FM−CWレーダの前記VCO回路は、前記制御電圧の増減に応じて、中心周波数に対して所定の周波数偏移量分周波数が周期的に増減する信号であって且つ各信号の中心周波数は互いに異なりさらに当該信号の周波数の増減方向及び増減速度が互いに一致する前記信号を出力する。

【0026】

本発明によれば、電波干渉を生じさせずに、各信号の周波数間隔を詰めることができ、より多くのチャネルを設定することができる。

【0027】

本発明の第8の態様によるマルチレーダシステムは、上記第7の態様において、各FM−CWレーダの前記制御部のうちの一つが前記同期信号を生成し、残りの前記制御部に出力する。

【0028】

本発明の第9の態様によるマルチレーダシステムは、上記第7の態様において、各FM−CWレーダの前記制御部のうちの一つが外部から供給される同期信号を受信し、残りの前記制御部に出力する。

【0029】

本発明の第10の態様によるマルチレーダシステムは、上記第7の態様において、各FM−CWレーダの前記制御部は、それぞれ外部から供給される同期信号を受信する。

【0030】

本発明の第11の態様によるマルチレーダシステムは、周波数が周期的に増減する信号を生成して出力する複数のレーダを含んで構成されるマルチレーダシステムにおいて、各レーダは、周期的に増減する周波数の上限値及び下限値が各レーダの信号毎に互いに異なり且つ当該上限値及び下限値になるタイミングが各信号毎に互いにほぼ一致するように所定の同期信号に同期して前記信号を生成することを特徴とする。

【0031】

本発明の第12の態様によるマルチレーダシステムは、上記第11の態様において、各レーダは、当該信号の周波数の増減方向及び増減速度が互いに一致するように所定の同期信号に同期して当該信号を生成する。

【0032】

本発明の第13の態様によるマルチレーダシステムは、上記第11の態様において、前記複数のレーダのうちの一つが前記同期信号を生成し、残りのレーダに出力する。

【0033】

本発明の第14の態様によるマルチレーダシステムは、上記第11の態様において、前記複数のレーダのうちの一つが外部から供給される同期信号を受信し、残りのレーダに出力する。

【0034】

本発明の第15の態様によるマルチレーダ異捨て無は、上記第11の態様において、前記複数のレーダは、外部から供給される同期信号を受信する。

【0035】

本発明の第16の態様によるマルチレーダシステムは、上記第11の態様において、前記複数のレーダは複数の車両それぞれに搭載されており、第1の方向に進行している車両に搭載されるレーダは、第1の周波数帯域に含まれる周波数の信号を生成し、第1の方向と異なる第2の方向に進行している車両に搭載されるレーダは、第1の周波数帯域と異なる第2の周波数帯域に含まれる周波数の信号を生成する。

【発明の効果】

【0036】

以上述べた如く本発明の位相同期発振器によれば、特性のバラツキや温度変化を有するVCO回路を使用しても、PLL制御による出力周波数の安定化、PLL開放下でのVCO駆動による出力周波数変化のリニアリティー向上が図れ、よって位相同期発振器の信頼性向上、更には、該発振器を使用したFM−CWレーダ等の普及に寄与するところが極めて大きい。

【0037】

また、本発明のマルチレーダシステムによれば、利用可能な周波数帯域に割り当てられるチャネルの周波数偏移量が従来と同程度であっても、電波干渉を生じさせずに、チャネルの周波数間隔を狭めることができ、従来と比較して多数のチャネルを当該周波数帯域に設定することができるようになり、周波数の利用効率が格段に向上する。

【発明を実施するための最良の形態】

【0038】

以下、添付図面に従って本発明に好適なる実施の形態を詳細に説明する。なお、全図を通して同一符号は同一又は相当部分を示すものとする。

【0039】

(位相同期発振器)

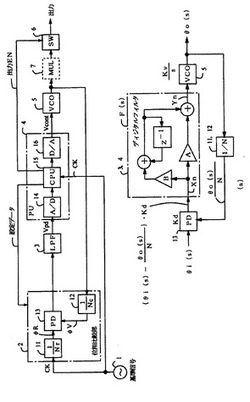

図1は第1の実施の形態による位相同期発振器のブロック図である。図において、1はPLLの基準クロック信号CKを発生するクロック発振器、2はPLLループを構成する位相比較部、11はクロック信号CKの可変分周器、12はVCO出力の可変分周器、13は両分周器出力φR,φVの位相を比較する位相比較器(PD)、3はPD13出力の位相誤差信号を積分するローパスフィルタ(LPF)、4は本発明の制御部に相当するプロセッサユニット(PU)、14はLPF3出力の位相誤差信号VpdをサンプリングするA/D変換器、15は本発振器の主制御・処理を行うCPU、16はCPU15出力の制御電圧をアナログの制御電圧Vcontに変換するD/A変換器、5は制御電圧Vcontに対応する周波数の発振信号を出力する電圧制御発振器(VCO)、6はVCO5の出力を通過/遮断するRFスイッチ(SW)である。

【0040】

CPU15は、VCO5の特性バラツキや温度変動によらず、PLLループを連続して又は周期的に構成することでVCO5の発振周波数を安定化させる制御と、レーダ動作時にPLLループを開放した状態で三角波信号を生成してVCO5にリニアリティー補正された周波数変調出力を出力させる制御とを行う。具体的には、後述の図2,図4,図6の各種処理を実行することにより、本発明の制御電圧測定手段、リニアリティー校正手段、VCO駆動手段(レーダ送信処理)等の各種機能を実現することもできる。

【0041】

制御電圧測定手段は、PLLループを複数の周波数でロックさせることで、各ロック時の制御電圧Vcontを測定する。その際には、位相比較部2に設定データを出力して、可変分周器11,12の分周比を所望に設定する。更に、LPF5出力の位相誤差信号Vpdを定期的にサンプリングすると共に、公知のPLL処理に従って位相誤差信号Vpdを小さくする方向に制御電圧Vcontを更新し、PLLループを複数の周波数で順次ロックさせる。各ロック時に取得した制御電圧Vcontは、VCO5の特性バラツキや温度変動によらず、該VCO5を各所定の周波数で発振させるに必要な制御電圧Vcontである。

【0042】

図1の挿入図(a)に一例のPLLループの概念構成図を示す。ここでは、LPF3とCPU15とが実現するループフィルタの機能を伝達特性F(s)を有するディジタルフィルタで表している。CPU15でディジタルフィルタを構成することにより、ゲインやクロック周期でフィルタ特性を変化させることができる。今、ディジタルフィルタの入力をX(n)、出力をY(n)とすると、差分方程式は、

Y(n)=(A+B)・X(n)+Y(n−1)−A・X(n−1)

で表される。これをZ変換すると、

Y(z)=(A+B)・X(z)+z−1・Y(z)−A・z−1・X(z)

で表され、フィルタの伝達特性F(z)は、

F(z)=Y(z)/X(z)=A+B/(1−Z−1)

で表される。これをF(s)で表すと、

F(s)=A+B/(1−e−j2πfT)

となる。

【0043】

更に、PLLとした場合の入力の位相をθi(s)、出力の位相をθo(s)とすると、ループの伝達特性H(s)は、

H(s)=θo(s)/θi(s)

=K・F(s)/{s+K・F(s)}

但し、K=Kd・Kv/N

で表される。

【0044】

次に、リニアリティー校正手段は、前記測定された各制御電圧Vcontに基づき、前記各周波数を結ぶ区間の周波数変化を代表(例えば直線近似)するような変調感度を求める。そして、VCO駆動(レーダ送信)手段は 前記PLLループを所定周波数(例えば送信信号の中心周波数)でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を生成し、出力する。このレーダ送信時には、ループ制御を開放しているため、VCO5の周波数変化を抑制するようなループのフィードバックはかからず、よって周波数変化の高い忠実性を維持できる。更に、該レーダ送信の例えば1周期毎にレーダ送信の中心周波数を安定化するためのループ制御を間欠的に行うことで、レーダ送信波の周波数も安定化する。以下、これらの制御・処理を詳細に説明する。

【0045】

図2は実施の形態による制御電圧測定処理のフローチャートで、PLLの分周比を変化させることでVCO出力に中心周波数f0、下限変調周波数f1、上限変調周波数f2を得るための各制御電圧V0,V1,V2を測定する場合を示している。ステップS11では、制御電圧Vcontの測定時に不要波を出力しないようRFスイッチSW6に対する出力ENをディセーブルし、無線波(RF)の出力を遮断する。ステップS12では測定シーケンスを保持するレジスタiの内容を初期化(例えばi=1に)する。ステップS13ではPLLが周波数fi(最初は下限周波数f1)でロックするように分周器11,12の分周比Nr,Ncを設定する。これによりPD13は両分周信号φR,φVの位相誤差に応じた位相誤差信号を出力し、これをLPF3で積分(フィルタ)する。

【0046】

ステップS14ではCPU15がLPF3出力の位相誤差出力Vpdを定期的に取得し、ステップS15では該信号Vpdが所要のセンター値(例えば2.5V)を中心とする所定範囲内にあるか否かを判別する。所定範囲内にない場合はPLLループがロック状態に無いため、ステップS16に進み、通常のPLLモードに従ってVpdがセンター値に近づく方向に制御電圧Vcontを更新する。

【0047】

こうして、やがて、ステップS15の判別で位相誤差出力Vpd ≒ センター値になると、PLLループがロック状態にあるので処理はステップS17に進み、その時点の制御電圧VcontをVi(最初は下限周波数f1に対する制御電圧V1)としてメモリに記憶する。ステップS18ではレジスタiの内容を更新し、次の測定対象を例えば中心周波数f0とする。ステップS19ではレジスタiの内容が測定終了か否かを判別し、測定終了でない場合はステップS13に戻る。こうして、続く中心周波数f0(V0)及び上限周波数f2(V2)についての測定を行い、やがて、ステップS19の判別で測定終了になると、この処理を抜ける。

【0048】

図3に第1の実施の形態による制御電圧測定動作のタイミングチャートを示す。一例の位相誤差出力Vpdは0〜5Vの範囲で変化し、中間の2.5V付近でロック状態と判定される。最初は、PLLは例えば下限周波数f1でロックするように分周比Nr,Ncを設定し、所定時間間隔でPLLループ制御を行う。CPU15は定期的にVpdを取得すると共に、通常のPLLループ制御に従って位相誤差出力Vpdが2.5Vに近づく方向に制御電圧Vcontを更新する。こうして、ループ制御を継続し、やがて、Vpd ≒2.5Vになると、ロック状態であり、この時、VCO5の発振周波数fは、VCO5の特性バラツキや温度による変動によらず、正確に下限周波数f1となっている。CPU15はこの時点の制御電圧Vcontを取得し、これをVCO5に下限周波数f1を発生させるための制御電圧V1としてメモリに記憶する。

【0049】

次に、PLLを中心周波数f0でロックさせ、その時点のVcontをVCO5に中心周波数f0を発生させるるための制御電圧V0としてメモリに記憶する。最後に、PLLを上限周波数f2でロックさせ、その時点のVcontをVCO5に上限周波数f2を発生させるための制御電圧V2としてメモリに記憶する。

【0050】

本実施の形態によれば、PLLループを各所定周波数(所定分周比)f0,f1,f2でロックさせる構成により、VCO5の特性バラツキや温度変化によらず、VCO5を所定周波数f0,f1,f2で発振させるための制御電圧V0,V1,V2を自動的に、かつ正確に求めることが可能である。

【0051】

図4は第1の実施の形態によるリニアリティー校正処理のフローチャートで、上記求めた(f1,V1),(f0,V0),(f2,V2)の組の情報に基づき、各周波数を結ぶ区間A〜DにおけるVCO出力を一定の周波数Δfづつリニアに変化させるための制御電圧Vcontを求める処理を示している。なお、この処理で求められた制御電圧Vcontを実際にVCO5に出力すれば、図5(b)に示すような出力の周波数特性が得られる。

【0052】

ステップS31では上記図2の処理で取得した制御電圧V0〜V2及び周波数f0〜f2の各情報を使用し、三角周期T0を例えば4分割した各区間j(=A〜D)におけるVCO5の変調感度を特性a(j)により直線近似する。図5(c)にリニアリティー校正動作のタイミングチャートを示す。

・区間Aの周波数変化f1→f0、制御電圧変化V1→V0により、

変調感度a(A)=(f0−f1)/(V0−V1)

・区間Bの周波数変化f0→f2、制御電圧変化V0→V2により、

変調感度a(B)=(f2−f0)/(V2−V0)

・区間Cの周波数変化f2→f0、制御電圧変化V2→V0により、

変調感度a(C)=−(f2−f0)/(V2−V0)=−a(B)

・区間Dの周波数変化f0→f1、制御電圧変化V0→V1により、

変調感度a(D)=−(f0−f1)/(V0−V1)=−a(A)

となる。

【0053】

ステップS32では、三角波条件(例えば、三角周期:10ms,中心周波数f0からの周波数偏移:±25MHz)とCPU条件(例えば、Vcontの時間分解能50μs,電圧分解能:0.005V)とに従い、各時点における周波数変化Δf(例えば、50μs当たり0.5MHz一定)を求める。ステップS33ではタイミングカウンタk=0,領域レジスタj=Aに初期化する。ステップS34では制御電圧Vcontに例えば下限周波数f1を生成させるための制御電圧V1をセットする。

【0054】

ステップS35では制御電圧の増分ΔVcont(k)を、

ΔVcont(k)=Δf/a(j)

により求める。ステップS36では、次の時点の制御電圧Vcont(k+1)を、

Vcont(k+1)=Vcont(k)+ΔVcont(k)

により求める。これにより、出力周波数をΔfづつ変化させるに必要な制御電圧Vcontが更新される。なお、レーダ動作時には更新した制御電圧VcontをVCO5に出力すると共に、この演算処理は50μs周期で定期的に行われる。

【0055】

ステップS37ではカウンタkに+1し、ステップS38ではk≧(T0/4)*jか否かを判別する。ここで、j=A〜Dは数1〜4に対応するものとする。k≧(T0/4)*jでない場合は、ステップS35に戻り、次のタイミングの制御電圧を求める。

【0056】

こうして、やがて、ステップS38の判別でk≧(T0/4)*jを満足すると、ステップS39では領域カウンタjに+1し、ステップS40ではj>4(=D)か否かを判別する。j>4でない場合は、ステップS35に戻り、次の領域の変調感度を使用して上記同様の処理を行う。こうして、やがてステップS40の判別でj>4になると、1周期T0分の制御電圧Vcontを求めたことになるので、この処理を抜ける。本実施の形態では、上記PLL動作と、VCOのリニアリティー校正処理を行うことにより、機器毎に固有の補正テーブルを設けなくても、VCO5のリニアリティーを自動的に高い精度で校正し、使用可能となる。

【0057】

図5は第1の実施の形態によるリニアリティー校正動作のタイミングチャートで、図5(a)にVCO5のもとの周波数変調特性を示す。横軸は制御電圧Vcont、縦軸は発振周波数である。VCO5の変調感度(Δf/ΔVcont)は非直線的に変化しており、中心周波数f0を境に見ると、低周波側では変調感度が高く、高周波側では低くなっている。この様な変調特性に対しては、図5(c)に示す様な制御電圧Vcontを加えることで、図5(b)に示す如く周波数が直線的に変化する特性が得られる。

【0058】

図5(b)にFM−CWレーダとしての好ましい周波数変化を示す。VCO5の出力周波数は下限f1と上限f2との間で直線的に変化している。リニアリティー校正処理は、図5(a)のVCO5に、図5(b)に示す如くリニア変化する周波数を出力させるための制御電圧Vcontを、図5(c)に従って求める処理である。

【0059】

図6は第1の実施の形態によるレーダ送信処理のフローチャートで、PLLを開放した状態で、CPU15がV0を基準にして連続した三角波を発生すると共に、1又は2以上の三角周期毎にその中心周波数をf0に維持するためのループ制御を間欠的に行う場合を示している。ステップS51ではPLLを一旦中心周波数f0でロックさせる。これにより、Vpd≒2.5V、Vcont≒V0(この時点のV0)に安定する。ステップS52ではCPU15が該V0を基準としてT0周期のリニアリティー補正された三角波を発生し、VCO5に加える。三角波の区間は、PLLループを開放しているため、VCO出力の周波数は図5(b)に示す如くリニアに変化する。PLLループの開放はCPU15がこの区間のループ制御を行わないことで容易に実現できる。

【0060】

一方、PD13はVCO出力の周波数変化に伴い位相誤差信号を変化させるが、LPF3は三角波周期よりも十分大きい時定数(例えば10倍程度)を有しているため、VCO5に三角波を加えてもこの区間の位相誤差信号はLPF3で平均化され、出力の位相誤差信号Vpdには三角波周期毎に僅かな変動が生じることになる。

【0061】

ステップS53では3T0/4(中心周波数)のタイミングでLPF3の位相誤差信号Vpdを取得する。VCO5の特性に変動が無い場合はこの区間の位相誤差信号は平均化されてVpd≒2.5Vの付近にあるが、VCO特性が変化すると、これに伴いVpdも徐々に変化する。ステップS54ではVpd≒Vref(=2.5V)か否かを判別する。Vpd≒Vrefの場合はf0が所要範囲内にあるので処理はステップS58に進む。またVpd≒Vrefでない場合は、更にステップS55でVpd>Vrefか否かを判別する。

【0062】

Vpd>Vrefでない場合はステップS56に進み、次のT0/4におけるVpdを増やすべく、例えば次の時点のVcont(例えばV1)を−側にオフセットする。また、Vpd>Vrefの場合はステップS57で次のT0/4におけるVpdを減らすべく、次の時点のVcont(例えばV1)を+側にオフセットする。CPU15は図1(a)のディジタルフィルタに従ってオフセット量を決定する。なお、制御電圧にオフセットを加えるタイミングは、上記VCO5にV1を加えるタイミングでも良いが、他のタイミングでも良い。ここで注目することは、三角波の周期内ではオープンループ動作となり、VCO出力の三角波特性を変形することはないことである。そして、三角波周期のある時点に同期して周期的(間欠的)にフィードバックしPLLをかけることである。ステップS58以降では何周期の三角波ごとにフィードバックを入れるかを設定するため、フィードバック制御のない三角波を所定数出力する。即ち、ステップS58ではフィードバック制御のない三角波の数が所定回数分出力したか否かを判別し、実行してない場合はステップS59でフィードバック制御のない三角波を一周期出力する。また実行した場合はこの処理を抜ける。

【0063】

図7は第1の実施の形態によるレーダ送信動作のタイミングチャートで、3角波周期毎にVcont(V1)にオフセットを加える場合を示している。本実施の形態によれば、3角波の終わった瞬間にフィードバックをかけるため、VCO5の出力周波数の三角形状はなまらない。なお、フィードバックする周期とPLLのループゲインとは反比例するため、ループゲインを落とし、制御の応答を遅くしたいような場合には、フィードバック周期を長くする方法がある。例えば制御電圧Vcontは三角波の10周期ごとにフィードバックし、V1の値をオフセットするとか、または三角波の1000周期ごとにフィードバックし、V1の値をオフセットすることが可能である。

【0064】

図8は第1の実施の形態によるレーダ運用動作のタイミングチャートで、一連のレーダ動作の合間に、VCOのリニアリティー校正動作を割り込ませることで、常に安定したレーダ動作を維持可能な場合を示している。VCO5は温度特性を有するため、レーダ動作中に温度が変化すると、中心周波数f0を出力させるための制御電圧V0も変化する。本実施の形態では、定期的にリニアリティーの再校正を行うことで常に安定したレーダ動作を維持できる。

【0065】

図8(A)は、一連のレーダ動作の合間に制御電圧V1,V0,V2の測定及びこれに伴うリニアリティー校正を行う場合を示している。なお、別途に温度変化を検出して温度が所定以上変化した場合に制御電圧V1,V0,V2の測定及びリニアリティー校正を行うように構成しても良い。また、制御電圧の測定順序は任意であり、例えば中心周波数f0の測定を最後にできる。こうすれば、PLLループは既に周波数f0でロックしているので、続くレーダ動作に移る際には、上記図6で述べたステップS51の処理を省略できる。

【0066】

図8(B)は、各一連のレーダ動作の合間に、各制御電圧V1,V0,V2の測定を順々に行い、最後のV2の測定と共にVCO5のリニアリティー校正を行う場合を示している。こうすれば、一制御電圧当たりの測定時間は短いので、レーダ動作のデッドタイムを小さくできるメリットがある。なお、この方法は、図示しないが、上記3点の制御電圧V1,V0,V2のみでなく、制御電圧の測定ポイントをもっと増やして、よりきめ細かいリニアリティー校正を行う場合に特に有利である。

【0067】

図9は第2の実施の形態による位相同期発振器のブロック図で、LPFをレーダ用とVCO校正用の2系統備え、各動作におけるPLLの高速引き込みを可能にした場合を示している。図において、PD3の出力はスイッチ17a,17bを介してLPF3a,3bにそれぞれ入力している。LPF3aは専らVCO駆動時の中心周波数出力タイミングにサンプリングした位相誤差信号を積分し、LPF3bは専ら制御電圧測定時の位相誤差信号を積分する目的で使用される。好ましくは、LPF3bの時定数をLPF3aの時定数よりも小さくすることで、各周波数に対する制御電圧の測定時間を短縮できる。

【0068】

また、この例の可変分周器11,12はCPU15からカウンタをリセット可能に構成されており、両カウンタを一斉にリセットすることで両分周信号φR、φVの初期位相を強制的に揃えることが可能である。また、スイッチSW7aは信号の通過をON/OFF可能に構成されており、LPF3aは、SW7aがONしている区間の位相誤差信号を積分し、SW7aがOFFすると、それまでに蓄積した積分値(コンデンサのチャージ)をそのまま保持可能である。スイッチSW7bとLPF3bとについても同様である。本実施の形態では、このような構成を有効活用することでPLLループの引き込み時間を大幅に短縮可能である。以下、詳細に説明する。

【0069】

図10は第2の実施の形態による位相同期発振器の高速引き込み処理のフローチャートで、この処理は、前半の例えば制御電圧V1の測定処理と、後半のレーダ動作処理とからなっている。例えば直前のレーダ動作終了後、この処理に入力する。ステップS61では可変分周器11,12の分周比をf1に設定する。ステップS62では制御電圧Vcontに前回のV1の測定で取得し、記憶しておいたV1を設定する。これによりVCO5は、温度変動によらず、当初より前回のV1の測定でロックした時の下限周波数f1を発生することになる。ステップS63では可変分周器11,12のカウンタをリセットし、これにより両分周信号φR,φVの初期位相が速やかに揃う。

【0070】

ステップS64では、上記V1測定の準備ができたことにより、スイッチ制御信号SW2をONにし、LPF3bを介したPLL動作を可能とする。この時、LPF3bでは内部コンデンサが前回の制御電圧の測定でロック状態に至った際の位相誤差電圧Vpd2(≒2.5V)を保持しており、この位相誤差電圧Vpd2は、前回の測定電圧がV1,V0又はV2によらず、そのロック状態では約Vref(例えば約2,5V)になっている。従って、今回のPLLループもロックに近い状態から開始できるため、ループの時定数によらず、より早い時点でロック状態に収束できることになる。ステップS65ではVpd2を取得する。ステップS66ではVpd2≒Vrefか否かを判別し、NOの場合はステップS67でVpd2がVrefに近づく方向にVcontを更新し、ステップS65に戻る。

【0071】

こうして、やがて、上記ステップS66の判別でVpd2≒Vrefになると、ステップS68ではその時点のVcontを取得し、制御電圧V1の記憶用のメモリに記憶する。ステップS69ではスイッチ制御信号SW2をOFFにし、これにより今回ロックした際の位相誤差電圧Vpd2がLPF3b内のコンデンサに保持される。

【0072】

次にレーダ動作に移り、ステップS71では可変分周器11,12の分周比を中心周波数f0に設定する。ステップS72ではVcontにV0を中心とする三角波信号を重畳する。ステップS73では可変分周器11,12のカウンタをリセットし、速やかに両分周信号φR,φV間の初期位相を合わせる。ステップS74では、レーダ動作の準備ができたことにより、スイッチ制御信号SW1をONにし、LPF3aを介したPLL動作を可能とする。この時、LPF3aでは内部コンデンサが前回のレーダ動作で略ロック状態に維持された際の位相誤差電圧Vpd1(約2,5V)を保持している。

【0073】

ステップS75では上記図6で述べた様なレーダ送信制御を行い、ステップS76では所定サイクル数分の三角波送信を行ったか否かを判別する。終了してない場合はステップS77でフィードバック制御のない三角波を一周期出力する。こうして、やがて、ステップS76の判別で所定サイクル数分の送信を終了するとステップS78ではスイッチ制御信号SW1をOFFにし、これにより今回のレーダ動作でロック維持した際の位相誤差電圧Vpd1がLPF3a内のコンデンサに保持される。

【0074】

図11は第2の実施の形態による位相同期発振器の高速引き込み動作のタイミングチャートで、各一連のレーダ動作の間に、制御電圧V1の測定処理を割り込ませた場合を示している。前回のレーダ動作が完了すると、スイッチ制御信号SW1がOFF(L)となり、LPF3aのVpd1を保持する。CPU15は可変分周器11,12にf1を得るための分周比を設定し、前回測定したV1をVcontとして出力する。更に、可変分周器11,12のカウンタをリセットして初期位相を合わせる。以上で測定動作の準備ができたので、スイッチ制御信号SW2をON(H)とし、LPF3bの位相誤差信号Vpd2に従ってPLL動作を行う。こうして、やがて、Vpd2がロック範囲内にあることを確認すると、CPU15はその時点のVcontを新たなV1として記憶する。V1の測定を完了すると、スイッチ制御信号SW2をOFFにし、その時点のVpd2を保持する。

【0075】

次のレーダ動作に移ると、可変分周器11,12にf0を得るための分周比を設定する。更に、CPU15からV0を中心とした三角波波形を出力する。なお、この例の三角波の校正はV2の測定後に行われる。更に可変分周器のカウンタをリセットして初期位相を合わせる。そして、レーダ動作の準備ができたので、スイッチ制御信号SW1をONにし、レーダ用のVpd1でPLLを動作させる。以下、同様にしてV0,V2を取得し、リニアリティー構成データの更新を行う。

【0076】

図12は第3の実施の形態による位相同期発振器のブロック図で、2系統のPLL回路を備え、これらを単独のCPU15で制御すると共に、一方のループを使用してレーダ動作を実行すると同時に、他方のループを使用してVCO回路のリニアリティー校正を行い、これらを両系統のPLL回路で交互に行う場合を示している。これにより、レーダ動作のデッドタイムを無くすことが可能である。

【0077】

図13に第3の実施の形態による位相同期発振器の動作タイミングチャートを示す。PLLaによりレーダ動作すると共に、PLLbではV1,V0,V2の測定及びVCO5bのリニアリティー校正を行う。次いで、PLLbによりレーダ動作すると共に、PLLaではV1,V0,V2の測定及びVCO5aのリニアリティー校正を行う。切換えは、例えば5分毎のように定期的に切換えても良く、あるいは外気の温度変化がある範囲を超えた場合に行っても良い。

【0078】

図14は第4の実施の形態による位相同期発振器を説明する図で、VCO回路の発振周波数は温度変化によってドリフトするが、その変調感度は温度によってあまり変化しないようなVCO回路に適用して好適なる場合を示している。実際上、このような特性を有するVCO回路は少なくない。なお、PLL回路については上記図1、図9又は図12で述べたものと同様でよい。図14(A)にこの種のVCO回路の変調特性を示す。常温時の変調カーブをaとすると、高温時にはカーブb側にシフトし、また低温時にはカーブc側にシフトする関係にある。このようなVCO回路では、同一の制御電圧V0を加えた場合でも、その発振周波数は温度によりf0'〜f0''に変化するが、V0近傍の変調感度は変わらないので、周波数をΔf変化させるためのΔVcontも温度により変化しない。このことは全制御電圧範囲Vmin〜Vmaxについて言えることである。

【0079】

図14(B)にこのVCO回路に対するリニアリティー校正処理のフローチャートを示す。ステップS81では可変分周器PLLの分周比Nr,Ncを変化させることで、ロック周波数を徐々に高くしてスイープさせ、その都度制御電圧Vcontを測定する。ステップS82では、前記測定した各制御電圧Vcontについて、制御電圧の可能な変動範囲Vmin〜Vmaxを例えば1V毎に分割し、各区間を代表するような変調感度a01、a12、a23,…を求める。ステップS83では三角波条件とCPU条件とに基づき、各時点における周波数変化Δf(この例では一定)を求める。こうして、温度変動によらず共通して使用可能な感度テーブルが得られる。

【0080】

なお、図示しないが、レーダ送信時には、まずPLLをf0にロックさせることで、その時点の制御電圧V0が求まる。以後は、例えば該V0を起点にして上限周波数f2までΔf分づつVcontを増加する。その際には、各時点のVcontがどの電圧区間にあるかを判別し、各対応する区間の変調感度を利用することで当該区間の各電圧変化を求める。こうして、やがてf2に達すると、次に下限周波数f1までVcontを減少させ、次にf0まで増加させる。そして、このような制御を繰り返す。従って、本実施の形態によれば、温度変動によらず、常に適正な周波数範囲のレーダ波を送信できる。また、温度変動ではリニアリティー校正処理を行う必要が無いため、レーダ動作を中断せずに運用できる。

【0081】

図15,図16は第5の実施の形態による位相同期発振器を説明する図(1),(2)で、図15は、両分周信号φR,φV間の位相までを揃えるPLL制御に代えて、周波数のみ揃っていれば位相までは揃わなくても良いとする所謂FLL(frequency Locked Loop)制御を行う場合を示している。一般に、制御電圧VcontをD/A変換してVCO5に加えると、VCO5の出力周波数は、最小でもD/A16の1ビット電圧分解能×変調感度の大きさで段階的に変化することになる。一方、PLLループ(即ち、LPF3)は三角波駆動によるレーダ送信波の平均周波数がf0となるようアナログ的に動作するので、位相誤差信号Vpdのロック検出幅をあまり狭くすると、制御電圧V0に対するオフセット補正が頻繁に発生してしまうことになる。本第5の実施の形態では、この問題を解決すべく、PLL制御に代えて、FLL制御を行う。なお、回路構成については例えば図1と同様のものでも良いが、CPU15から可変分周器11,12のカウンタをリセット可能に構成されているものとする。

【0082】

一般に、両分周信号φR,φV間の位相は、VCO5をフリーランさせている(即ち、PLLループをオープンにしている)状態では、例え両分周信号φR,φVの周波数が揃っていても、これらの位相は徐々にずれる(スリップする)ことになるが、本第5の実施の形態により可変分周器11,12のカウンタを毎周期毎にリセットすることで、三角波の1周期内に大幅な位相差が生じることを有効に回避できる。しかし、もしVCO5の発振周波数が所要からずれている場合には、両信号φR,φV間の位相差も短時間で速やかに広がるため、このような状態は位相誤差信号Vpdを毎周期観測することで確実に検出できる。

【0083】

図15において、FLL制御に基づく本実施の形態では、両分周信号φR,φV間の位相までは揃わなくても、VCO5出力の周波数が所定範囲内に入っていれば良いので、可変分周器11,12のカウンタを例えば三角波の1周期毎にリセットすると共に、単位区間(例えば1周期)内にVpdが所定以上変化したことを検出した場合は、出力周波数が所定範囲外にあるとして、制御電圧Vcontをオフセットする。図16に位相比較部2の動作を示す。FLL制御の実現方法としては、可変分周器11,12のカウンタを定期的(3角波の1又は2周期以上)にリセットすることにより、容易に実現できる。

【0084】

図17は第6の実施の形態による位相同期発振器を説明する図で、CPU15が三角波信号を発生する代わりに、リニアリティー校正された2値波信号を発生する場合を示している。なお、位相同期発振器の構成については上記図1,図9又は図12に示したものと同様で良い。図において、この例のVCO5は時間tの進行に伴い定期的に周波数f1とf2とを交互に出力している。中心周波数はf0である。このような位相同期発振器は2周波CW方式のレーダ装置に適用して好適である。

【0085】

図18,図19は実施の形態による故障検出動作を説明する図(1),(2)で、図18(A)は通常動作時における位相誤差信号Vpdが異常レベルにある場合を示している。本装置を車載用として用いる場合、人命に係わるため、常に動作の状態を監視する必要がある。本実施の形態では、通常動作時に位相誤差信号VpdがPLL引き込み可能な正常電圧範囲から外れたことにより、ロック異常を検出する。

【0086】

図18(B)は通常動作時における中心の制御電圧V0が異常レベルにある場合を示している。過酷な使用環境下では、例えば、筐体内への水の侵入や、結露等によって中心周波数f0(即ち、制御電圧V0)が大幅に変動する場合がある。本実施の形態では、通常動作時に制御電圧V0が正常範囲から外れたことにより、VCO動作の異常を検出する。

【0087】

図19は電源ON時のリニアリティー校正結果が異常の場合を示している。VCO特性は経時変化によっても劣化する。本実施の形態では、装置の電源投入時又は定期的にPLLループを構成してリニアリティー校正すると共に、例えば電源ON時におけるf0,f2,f1に対する各Vcont測定値V0,V2,V1と、工場出荷時のこれらの値とを比較することで、これらの内の何れか1つ以上が所定以上外れていることを検出すると、異常と判定する。なお、この例では絶対電圧が指定範囲内であるかを比較しているが、各電圧間の相対的な電圧値が指定範囲内であるかを比較しても良い。

【0088】

なお、上記図1,図9又は図12において、本回路をミリ波帯のFM−CWレーダ等に使用する場合は、ミリ波帯の可変分周器12を使用するが、このような可変分周器が入手困難又は高価な場合には、より低い周波数の可変分周器12を使用すると共に、VCO5の出力を周波数逓倍器(MULTI)7によってミリ波帯に逓倍して出力しても良い。

【0089】

また、CPU15が発生する信号は、上記三角波信号や2値波信号以外にも様々な信号波形(正弦波、ノコギリ波等)を発生可能である。

【0090】

また、上記実施の形態ではVCO5の変調感度を3つの測定ポイントf1,f0,f2に渡って直線近似したが、これに限らない。測定ポイント数を増やすことで、より高精度な近似が可能となり、リニアリティー校正の精度を上げることができる。

【0091】

また、上記実施の形態では、複数区間における変調感度を各区間における直線近似で代表したが、これに限らない。各区間におけるカーブをより忠実に近似可能な高次の関数や指数関数等により近似しても良い。

【0092】

また、上記実施の形態では位相比較部2とCPU15のクロック信号CKを共通にしたが、CPU15に別系統のクロック信号を使用しても良い。

(マルチレーダシステム)

以下、上述した位相同期発振器を用いたレーダを複数個配備したマルチレーダシステムについて説明する。

【0093】

図20は、第7の実施の形態によるマルチレーダシステムの概略構成例を示す図である。マルチレーダシステムは、複数のFM−CWレーダ(以下、単にレーダと称する)100−1、100−2、100−3、100−4を備える(以下、各レーダを区別しない場合は、レーダ100と称する)。以下の説明では、一例として、4つのレーダを備えるマルチレーダシステムについて説明するが、レーダの数は4つに限らず、必要に応じた複数個のレーダを配備可能である。また、図20の構成は、複数のレーダを搭載する一つの装置としてのマルチレーダシステムである。

【0094】

複数のレーダのうちの一つ(例えば、レーダ100−1)は、マスターレーダMとして機能し、後述するように、三角波の出力に応じて同期信号を生成、当該同期信号を出力する。残りのレーダ(例えば、レーダ100−2〜100−4)は、マスターレーダMからの同期信号が入力され、当該同期信号に応じて三角波を出力するスレーブレーダS(S1〜S3)として機能する。

【0095】

図21は、各レーダの概略構成例を示す図である。マルチレーダシステムを構成する各レーダ100では、発振部101が三角波で周波数変調された送信信号を生成し、送信信号はアンテナから放射される。この発振部101は、上述した本発明の実施の形態による位相同期発振器である。目標物に当たって反射した信号は受信信号としてアンテナで受信され、ミキサ102で送信信号とミキシングされることでビート信号が得られる。三角波で周波数変調された送信信号は時間ともに周波数が変化しており、受信信号は往復時間だけ前に放射された送信信号の反射波であるため、現在の送信信号と周波数がずれていることを利用して、目標物までの距離を算出する。また、目標物との相対速度を算出するには、ドップラー効果により反射波が周波数偏移することを利用する。目標物までの距離及び目標物との相対速度は、ビート信号を解析し、既知の計算方法によって求められる。

【0096】

図22は、第7の実施の形態によるマルチレーダシステムにおける各レーダ100の発振部101の構成を示す図である。なお、発振部101−1はレーダ100−1の発振部、発振部101−2はレーダ100−2の発振部、発振部101−3はレーダ100−3の発振部、発振部101−4はレーダ100−4の発振部を示す(各発振部を区別しない場合は、発振部101と称する)。各発振部101は、例えば、図1に示す第1の実施の形態による位相同期発振器により構成される。マスターレーダとして機能するレーダ100−1の発振部101−1のCPU15−1は、三角波を生成する所定のタイミングで同期信号を出力する。

【0097】

図23は、同期信号の出力を説明する図である。図示されるように、例えば、同期信号は、三角波の1周期毎に出力される。

【0098】

図22において、CPU15−1から出力される同期信号は、スレーブレーダとして機能するレーダ100−2、100−3、100−4の各発振部101−2、101−3、101−4のCPU15−2、15−3、15−4に入力される。そして、CPU15−2、15−3、15−4も、同期信号に同期して三角波を出力する。

【0099】

図23において、各CPU15−1〜15−4(各CPUを区別しない場合は、CPU15と称する)は、入力された同期信号の立ち上がりエッジを検知すると、三角波形状の制御電圧Vcont出力を開始し、結果、送信信号に1周期の三角波形状で周波数変調する。同期信号を三角波の周期で入力し続けることにより、送信信号は三角波の周波数変調が連続してかかる。

【0100】

以上にように、同期した複数の三角波を生成する三角波生成部の例としてCPU15−1〜15−4等を備え、かつ、この複数の三角波のそれぞれを制御信号として、それぞれの制御信号に応じて周波数変調された信号を出力する複数のVCOを備え、複数の電圧制御発信器は、互いに中心周波数が異なる、周波数変調された信号を出力するとともに、少なくとも1つの三角波に基いて生成される周波数変調された信号の下限周波数に対して、少なくとも他の1つの三角波に基いて生成される周波数変調された信号の上限周波数が大きくなるように出力周波数が設定することで、周波数変調された各信号の周波数間隔を縮めることができる。

【0101】

このとき、図24のように、1つの周波数変調された信号の下限周波数に対してマルチレーダとして送信する他の全て(1つ(中心周波数が最も近いもの)、2つ(中心周波数が最も近いもの及び次に近いもの)、又は、それ以上)の周波数変調された信号の上限周波数が高い周波数になるように設定することもできる。

【0102】

図24は各発振部101において周波数変調された送信信号の周波数変化を示す図である。各送信信号の三角波状の周波数変化が同期信号に同期しているので、各送信信号の周波数は同期して変化する。すなわち、各送信信号の周波数変調による上限周波数及び下限周波数となるタイミングは一致する。また、周波数の増減方向も一致する。

【0103】

さらに図24の周波数領域では、各発振部101の中心周波数は所定の周波数間隔(チャネル間隔)ずらして割り当て、各レーダの三角波変調の周波数偏移量を一定とするように制御電圧Vcontを制御することで、周波数の増減速度が一致し、どのタイミングでも常に一定の周波数間隔となる。

【0104】

従って、隣接する送信信号同士において、従来、中心周波数の高い方の下限周波数が、中心周波数の低い方の上限周波数より低くなり問題となるような場合でも、送信信号の周波数は重ならず、干渉は生じない。例えば、発振部101−1の送信信号の下限周波数は、それに隣接する発振部101−2の送信信号の上限周波数より低くなるが、そのタイミングが重ならず、発振部101−1の送信信号と発振部101−2の送信信号が干渉することはない。他の送信信号同士も同様に干渉することはない。

【0105】

本発明の実施の形態におけるマルチレーダシステムでは、互いに同期した三角波で周波数変調を行い、変調の周波数偏移量を合わせることで、所定の周波数間隔(チャネル間隔)を、周波数偏移量に依存しないでチャネル設定が可能となる。

【0106】

すなわち、送信信号の周波数偏移量を変えずに、一定の周波数帯域により多くのチャネルを設定することができるようになり、周波数帯域をより有効に利用することができる。なお、本明細書では、配備されたレーダの送信信号に割り当てられる周波数をチャネルと呼ぶ場合がある。

【0107】

チャネル間隔は、次の表1に示す項目を考慮して、決定される。

【0108】

【表1】

【0109】

具体的には、利用可能な周波数帯域が76GHz〜77GHzの1GHz幅である場合(項目1)、各レーダの送信信号の周波数誤差となる基準信号間の周波数偏差(項目2)、PLL回路の定常周波数誤差(項目3)、周波数偏移の校正誤差(項目5)、ドップラー偏移(項目7)、往復時間による周波数ずれ(項目11)などを考慮し、これらの周波数変動幅を合計した値の2倍(中心周波数から上下方向にそれぞれの変動幅が生じるため)が必要なチャネル間隔となる。表1の例では、項目2、3、5、7及び11の各変動幅の合計(3.7225MHz)の2倍の値、すなわち、約7.45MHzとなる。

【0110】

周波数偏移量は200MHz(項目4)に設定されているので、周波数帯域76GHz〜77GHzにおいて、中心周波数が設定できる帯域は、76.2GHz〜76.8GHzの600MHzの帯域となり、チャネル間隔を7.45MHzとすると、この帯域に81本のチャネルを設定することができる。

【0111】

図25は、周波数帯域76GHz〜77GHzに81チャネルが設定された例を示す図である。図22(c)に示した従来の場合では、帯域1GHz、周波数偏移量200MHzとした場合、2チャネルした設定できなかったが、本発明の実施の形態例では、ほぼ同様の条件にて81チャネルが設定可能であり、チャネル数を大幅に増加させることができる。

【0112】

図26は、第8の実施の形態によるマルチレーダシステムの概略構成例を示す図である。第8の実施の形態によるマルチレーダシステムは、図20における第7の実施の形態の変形例であり、同期信号が外部から供給される場合を示す。具体的には、三角波の周期を有する同期信号を例えばAM放送又はFM放送の電波を用いて、外部の電波発信源から放射する。マルチレーダシステムの受信機110がその電波を受信し、電波に含まれる所定周波数の同期信号が各レーダ100−1〜100−4に供給される。同期信号は、図示されるように、マスターレーダ100−1を通じて各スレーブレーダ100−2〜100−4に供給されてもよいし、受信機110から並列にマスターレーダ100−1〜100−4に供給される構成であってもよい。また、各レーダ100が受信機110を備え、各レーダが同期信号を受信する構成であってもよい。同期信号を外部から供給することにより、同期信号を生成する個々のマスターレーダの個体差による同期信号のずれをなくし、複数のマルチレーダシステム間でも、三角波の同期を取ることができる。

【0113】

特に、複数の車両それぞれに少なくとも一つのレーダが搭載されて、マルチレーダシステムが構成される場合、各車両ごとに受信機110を搭載し、各車両のレーダは、受信機110で受信された同期信号に基づいて三角波を出力する。これにより、離間する複数のレーダで構成されるマルチレーダシステムにおける各レーダの三角波も同期を取ることができる。また、GPSを利用したカーナビゲーションシステムの車両への搭載が普及しており、車両でGPS信号を入手することが容易にできるようになってきている。このGPS信号で、例えば1秒間隔で出力される1pps信号を同期信号とすることもできる。この場合、1pps信号は1秒間に1パルス出力なので、三角波の周波数が100Hzである場合は、1pps信号が入力されると、三角波100パルス出力すればよい。

【0114】

図27は、第9の実施の形態によるマルチレーダシステムの各レーダにおける発振部101の構成例を示す図である。第9の実施の形態によるマルチレーダシステムは、図22における第7の実施の形態の変形例であり、基準信号を各レーダで共通化する場合を示す。具体的には、基準信号を生成するクロック発振器1を各レーダの発振器で共通化している。これにより、基準信号の周波数偏差(表1の項目2)を考慮する必要がなくなり、さらにチャネルの周波数間隔を詰めることができる。具体的には、表1の場合、約7.45MHzを約5.93MHz((3.7225MHz−0.76MHz)×2=5.9225MHz)に詰めることができる。

【0115】

図28は、第9の実施の形態におけるマルチレーダシステムにおける各レーダの送信信号の周波数割り当て例を示す図である。図28では、一例として、4台の車両A、B、C、Dそれぞれに4つのレーダを搭載している場合であって、1台の車両における4つのレーダのクロック発振器1を共通化することで、各車両内における周波数間隔は5.93MHzとすることができ、車両間の周波数間隔は約7.45MHzとする。

【0116】

図29は、第10の実施の形態によるマルチレーダシステムの各レーダにおける発振部101の構成例を示す図である。第10の実施の形態によるマルチレーダシステムは、図22における第7の実施の形態の変形例であり、マスターレーダとスレーブレーダの区分をなくし、CPU15とは独立して同期信号を生成、出力する同期信号制御部(同期信号生成手段)111が設けられる。同期信号制御部111により生成された同期信号は、各レーダ100−1〜100−4に供給される。また、同期信号の入出力停止など同期信号に関する何らか異常、故障の検出も、同期信号制御部111が一元的に行う。

【0117】

図30は、車両の進行方向によってチャネルの周波数帯域を分割する適用例を示す図である。本発明の実施の形態によるマルチレーダシステムを自動車の車両に適用した場合において、2つの車両がすれ違う場合に、各車両のレーダに割り当てられたチャネルが同一であると、互いに他方のレーダからの送信信号を受信していまい、正しい測定が行えない。そこで、一例として、図30に示すように、周波数帯域を上り用帯域と下り用帯域に分け、車両の進行方向に対応する帯域のチャネルを割り当てる。車両の進行方向は、例えば、車両に搭載されるGPSシステムにより検知される方位の情報を用いて取得される。上り方向に進行する車両には、上り用帯域のチャネルを割り当て、下り方向に進行する車両には、下り用帯域のチャネルを割り当てる。これにより、すれ違うことにより近接する2つの車両のチャネルが同一になることない。なお、仮に同一方向に進行する2つの車両に、同一のチャネルが割り当てられている場合、2つの車両に搭載されるレーダの電波が互いに干渉するほどに近接する可能性は、すれ違う場合と比較して十分に低い。従って、図30のように、チャネルを割り当てる周波数帯域を分割し、車両の進行方向が異なり、すれ違いなど車両同士が近接する可能性が高い場合は、車両の進行方向により異なる周波数帯域のチャネルを割り当て、車両同士が近接する可能性が低い場合は、実質的に、同一のチャネルを複数の車両で用いることも可能となる。

【0118】

図31は、車両の進行方向によってチャネルの周波数帯域を分割する別の適用例を示す図である。図31は、図30における2方向ではなく、4方向に分割する例であり、例えば東西南北の4方向について、周波数帯域を分割し、車両の進行方向によって異なる周波数帯域のチャネルを割り当てる。分割する方向は、2方向や4方向に限らず、例えば8方向などさらに細かく分割されてもよい。

【0119】

本発明の実施の形態におけるマルチレーダシステムを構成する各レーダは、FM−CWレーダに限られない。例えば、各レーダは2周波CWレーダであってもよく、2周波CWレーダの場合、各レーダに割り当てられた2つの周波数はレーダ毎に異なっており、周波数の切り替えタイミングをレーダ毎に一致させることで、送信信号同士の干渉を抑えることができる。

【0120】

図32は、2周波CWレーダによるマルチレーダシステムにおける周波数割り当て例を示す図である。以下では、2周波CWレーダも単にレーダと称し、参照番号100を用いる。図32(A)では、各レーダの送信信号の周波数切り替えタイミングを一致させる。これにより、各レーダ100に割り当てられる周波数は、他のレーダに割り当てられる2つの周波数間の帯域内であっても、互いの周波数は重ならない。なお、周波数切り替えタイミングにおいては、各レーダの周波数は瞬間的に重なるが、この切り替えタイミングの信号はマスクし、信号処理の対象としない。図32(B)は、周波数切り替えタイミングにおいても、干渉が生じない周波数割り当て例である。周波数が重ならないように、切り替えタイミングをレーダ毎にずらす。これにより周波数切り替えタイミングにおけるマスク処理を不要とする。また、図32(C)は、複数のレーダ100−1〜100−4において、周波数切り替えタイミングにおけるレーダ100−1と100−2の周波数切り替え方向と、レーダ100−3と100−4の周波数切り替え方向を互いに逆方向になるように異ならせる例である。これにより、周波数帯域に割り当て可能なチャネル数をさらに増やすことができ、周波数利用効率が向上する。同方向にのみ周波数が切り替わる図32(A)、(B)に比べて、チャネル数を最大2倍増とすることができる。

【0121】

図33は、2周波CWレーダによるマルチレーダシステムの大規模な周波数配置例を示す図である。周波数帯域を複数のグループに分割し、各グループにおいて、図32(C)に示した周波数配置例を適用する。すなわち、各グループにおいて、周波数切り替えタイミングは同時だが周波数切り替え方向が異なる複数のチャネルが設定される。

【0122】

図34は、2周波CWレーダによるマルチレーダシステムの概略構成例を示す図である。図34の構成例は、図20の構成例と同様に、周波数切り替えタイミングにおいて、マスターレーダからスレーブレーダに同期信号が出力され、スレーブレーダは、同期信号に同期して周波数を切り替えることで、各レーダが同期して周波数を切り替えることができる。また、マスターレーダは、周波数切り替え方向を決定する極性信号POLをスレーブレーダに供給する。極性信号は、周波数の切り替え周期でH/Lレベル変化する信号であって、極性信号のレベルに応じて周波数の切り替え方向が決定される。例えば、各スレーブレーダは、Hレベルの極性信号が供給されている間に、同期信号を受信すると、2周波数のうちの高い周波数に切り替わり、Lレベルの極性信号が供給されている間に、同期信号を受信すると、低周波数に切り替わる。FM−CWレーダにおける実施の形態例と同様に、極性信号及び同期信号は、外部から供給され、マスターレーダがそれを受信して、スレーブレーダに供給する構成であってもよいし、さらに、マスターレーダ及びスレーブレーダの区別なく、各レーダがそれぞれ外部からの極性信号及び同期信号を受信する構成であってもよい。

【0123】

上記本発明に好適なる複数の実施の形態を述べたが、本発明の思想を逸脱しない範囲内で各部の構成、制御、処理及びこれらの組合せの様々な変更が行えることは言うまでもない。

【0124】

(付記1)

基準信号と比較信号の位相を比較する位相比較器と、該位相比較器の位相誤差信号を積分するローパスフィルタと、該ローパスフィルタの後段に介在して本器の主制御を行う制御部と、該制御部出力の制御電圧に応じた周波数の信号を発生するVCO回路と、該VCO回路の出力信号を分周して前記比較信号を形成する可変分周器とからなるPLLループを備える位相同期発振器であって、前記制御部は、

PLLループを複数の周波数でロックさせて各ロック時の制御電圧を測定する制御電圧測定手段と、

前記測定された各制御電圧に基づき、前記各周波数を結ぶ区間の周波数変化を代表する変調感度を求めるリニアリティー校正手段とを備えたことを特徴とする位相同期発振器。

【0125】

(付記2)

前記PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を生成し、出力するVCO駆動手段を備えたことを特徴とする請求項1記載の位相同期発振器

(付記3)

VCO駆動手段は、VCO回路が中心周波数を出力するタイミングに同期してローパスフィルタの出力をサンプリングし、検出した位相誤差信号が所定範囲を超える場合は、該位相誤差信号を小さくする方向に制御電圧をオフセットすることを特徴とする請求項2記載の位相同期発振器。

【0126】

(付記4)

基準信号を分周する第1の分周器と、VCO回路の出力を分周して前記比較信号を形成する第2の分周器とを備え、

前記VCO駆動手段は、前記第1,第2の分周器のカウンタをVCO回路に加える信号周期の整数倍周期で定期的にリセットすると共に、前記VCO回路が中心周波数を出力するタイミングに同期してサンプリングしたローパスフィルタ出力の位相誤差信号が所定範囲を超える場合は、該位相誤差信号を小さくする方向に制御電圧をオフセットすることを特徴とする請求項2記載の位相同期発振器。

【0127】

(付記5)

基準信号を分周する第1の可変分周器と、VCO回路の出力を分周して前記比較信号を形成する第2の可変分周器とを備え、前記制御部は、前記第1,第2の可変分周器に所定の分周比を設定後、PLLループを形成して基準信号と比較信号間の位相引き込みを開始する際に、前記VCO回路に前記所定の分周比に対応する制御電圧を加えると共に、前記第1,第2の可変分周器のカウンタをリセットすることを特徴とする請求項1又は2記載の位相同期発振器。

【0128】

(付記6)

基準信号と比較信号の位相を比較する位相比較器と、該位相比較器の位相誤差信号を積分するローパスフィルタと、該ローパスフィルタの後段に介在して本器の主制御を行う制御部と、該制御部出力の制御電圧に応じた周波数の信号を発生するVCO回路と、前記VCO回路の出力信号を分周して前記比較信号を形成する可変分周器とからなるPLLループを備える位相同期発振器であって、前記制御部は、

PLLのロック周波数を所定間隔で変化させ、所定の周波数範囲をカバーする範囲につき各ロック時の制御電圧を測定する制御電圧測定手段と、

前記測定した制御電圧の変動範囲を複数区間に分割して、各区間を代表する変調感度を求めるリニアリティー校正手段と、

PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、VCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を、前記ロック時の制御電圧と前記求めた各区間を代表する変調感度に基づき生成し、出力するVCO駆動手段とを備えたことを特徴とする位相同期発振器。

【0129】

(付記7)

付記1乃至6のいずれかに記載の位相同期発振器を有する複数のFM−CWレーダを備えて構成されるマルチレーダシステムにおいて、

各FM−CWレーダの前記制御部は、周期的に増減する制御電圧であって且つ前記制御電圧の増減方向及び増減速度が互いに一致するように所定の同期信号に同期した前記制御電圧を生成し、

各FM−CWレーダの前記VCO回路は、前記制御電圧の増減に応じて、中心周波数に対して所定の周波数偏移量分周波数が周期的に増減する信号であって且つ各信号の中心周波数は互いに異なりさらに当該信号の周波数の増減方向及び増減速度が互いに一致する前記信号を出力することを特徴とするマルチレーダシステム。

【0130】

(付記8)

付記7において、

各FM−CWレーダの前記制御部のうちの一つが前記同期信号を生成し、残りの前記制御部に出力することを特徴とするマルチレーダシステム。

【0131】

(付記9)

付記7において、

各FM−CWレーダの前記制御部のうちの一つが外部から供給される同期信号を受信し、残りの前記制御部に出力することを特徴とするマルチレーダシステム。

【0132】

(付記10)

付記7において、

各FM−CWレーダの前記制御部は、それぞれ外部から供給される同期信号を受信することを特徴とするマルチレーダシステム。

【0133】

(付記11)

付記7において、

前記基準信号は、各FM−CWレーダで共通であることを特徴とするマルチレーダシステム。

【0134】

(付記12)

付記7において、

前記同期信号を生成する同期信号生成手段を備え、当該同期信号生成手段が生成された同期信号が各制御部に供給されることを特徴とするマルチレーダシステム。

【0135】

(付記13)

周波数が周期的に増減する信号を生成して出力する複数のレーダを含んで構成されるマルチレーダシステムにおいて、

各レーダは、周期的に増減する周波数の上限値及び下限値が各レーダの信号毎に互いに異なり且つ当該上限値及び下限値になるタイミングが各信号毎に互いにほぼ一致するように所定の同期信号に同期して前記信号を生成することを特徴とするマルチレーダシステム。

【0136】

(付記14)

付記13において、

各レーダは、当該信号の周波数の増減方向及び増減速度が互いに一致するように所定の同期信号に同期して当該信号を生成することを特徴とするマルチレーダシステム。

【0137】

(付記15)

付記13において、

前記複数のレーダのうちの一つが前記同期信号を生成し、残りのレーダに出力することを特徴とするマルチレーダシステム。

【0138】

(付記16)

付記13において、

前記複数のレーダのうちの一つが外部から供給される同期信号を受信し、残りのレーダに出力することを特徴とするマルチレーダシステム。

【0139】

(付記17)

付記13において、

前記複数のレーダは、外部から供給される同期信号を受信することを特徴とするマルチレーダシステム。

【0140】

(付記18)

付記13において、

前記複数のレーダは複数の車両それぞれに搭載されており、第1の方向に進行している車両に搭載されるレーダは、第1の周波数帯域に含まれる周波数の信号を生成し、第1の方向と異なる第2の方向に進行している車両に搭載されるレーダは、第1の周波数帯域と異なる第2の周波数帯域に含まれる周波数の信号を生成することを特徴とするマルチレーダシステム。

【0141】

(付記19)

同期した複数の三角波を生成する三角波生成部と、

該複数の三角波のそれぞれを制御信号として、該それぞれの制御信号に応じて周波数変調された信号を出力する複数の電圧制御発信器と、

を備え、前記複数の電圧制御発信器は、互いに中心周波数が異なる、周波数変調された信号を出力するとともに、少なくとも1つの三角波に基いて生成される周波数変調された信号の下限周波数に対して、少なくとも他の1つの三角波に基いて生成される周波数変調された信号の上限周波数が大きくなるように出力周波数が設定された、

ことを特徴とするマルチレーダシステム。

【図面の簡単な説明】

【0142】

【図1】第1の実施の形態による位相同期発振器のブロック図である。

【図2】第1の実施の形態による制御電圧測定処理のフローチャートである。

【図3】第1の実施の形態による制御電圧測定動作のタイミングチャートである。

【図4】第1の実施の形態によるリニアリティー校正処理のフローチャートである。

【図5】第1の実施の形態によるリニアリティー校正動作のタイミングチャートである。

【図6】第1の実施の形態によるレーダ送信処理のフローチャートである。

【図7】第1の実施の形態によるレーダ送信動作のタイミングチャートである。

【図8】第1の実施の形態によるレーダ運用動作のタイミングチャートである。

【図9】第2の実施の形態による位相同期発振器のブロック図である。

【図10】第2の実施の形態による位相同期発振器の高速引き込み処理のフローチャートである。

【図11】第2の実施の形態による位相同期発振器の高速引き込み動作のタイミングチャートである。

【図12】第3の実施の形態による位相同期発振器のブロック図である。

【図13】第3の実施の形態による位相同期発振器の動作のタイミングチャートである。

【図14】第4の実施の形態による位相同期発振器を説明する図である。

【図15】第5の実施の形態による位相同期発振器を説明する図(1)である。

【図16】第5の実施の形態による位相同期発振器を説明する図(2)である。

【図17】第6の実施の形態による位相同期発振器を説明する図である。

【図18】実施の形態による故障検出動作を説明する図(1)である。

【図19】実施の形態による故障検出動作を説明する図(2)である。

【図20】第7の実施の形態によるマルチレーダシステムの概略構成例を示す図である。

【図21】各レーダの概略構成例を示す図である。

【図22】第7の実施の形態によるマルチレーダシステムにおける各レーダ100の発振部101の構成を示す図である。

【図23】同期信号の出力を説明する図である。

【図24】各発振部101において周波数変調された送信信号の周波数変化を示す図である。

【図25】周波数帯域76GHz〜77GHzに81チャネルが設定された例を示す図である。

【図26】第8の実施の形態によるマルチレーダシステムの概略構成例を示す図である。

【図27】第9の実施の形態によるマルチレーダシステムの各レーダにおける発振部101の構成例を示す図である。

【図28】第9の実施の形態におけるマルチレーダシステムにおける各レーダの送信信号の周波数割り当て例を示す図である。

【図29】第10の実施の形態によるマルチレーダシステムの各レーダにおける発振部101の構成例を示す図である。

【図30】車両の進行方向によってチャネルの周波数帯域を分割する適用例を示す図である。

【図31】車両の進行方向によってチャネルの周波数帯域を分割する別の適用例を示す図である。

【図32】2周波CWレーダによるマルチレーダシステムにおける周波数割り当て例を示す図である。

【図33】2周波CWレーダによるマルチレーダシステムの大規模な周波数配置例を示す図である。

【図34】2周波CWレーダによるマルチレーダシステムの概略構成例を示す図である。

【図35】従来技術を説明する図である。

【図36】従来におけるマルチレーダシステムにおける複数のレーダそれぞれの周波数割り当てを説明する図である。

【図37】送信信号の中心周波数や周波数偏移の変動を説明する図である。

【符号の説明】

【0143】

1 クロック発振器

2 位相比較部

3 ローパスフィルタ(LPF)

4 プロセッサユニット(PU)

5 電圧制御発振器(VCO)

6 RFスイッチ(SW)

7 周波数逓倍器

11,12 可変分周器

13 位相比較器(PD)

14 A/D変換器

15 CPU

16 D/A変換器

100 レーダ

101 発振部

102 ミキサ

110 受信機

111 同期信号制御部

【技術分野】

【0001】

本発明は、位相同期発振器及びそれを用いたマルチレーダシステムに関する。本発明は、特に、FM−CWレーダ等のRF帯発振部に用いて好適なる位相同期発振器及びそれを用いたマルチレーダシステムに用いると好適である。

【背景技術】

【0002】

図35は従来技術を説明する図で、図35(A)は従来のFM−CWレーダの周波数変調部分を示している。FM−CW方式の基本構成は、ファンクションジェネレータ(FG)等で三角波の変調信号を発生し、この変調信号により電圧制御発振器(VCO)に周波数変調をかけるものである。FM−CW方式で重要なことは、正確な三角波の周波数変調をかけることであり、このためには、例えば中心周波数を基準にして、その最大及び最小周波数偏移が変化しないこと、周波数が時間とともに直線的(リニア)に変化すること、すなわちその傾き(周波数変化速度)が変化しないこと、が必要である。FM−CWレーダの出力周波数は、VCOの外部条件(温度、電源等)の安定度に依存し、また出力周波数の周波数偏移については、VCOの変調感度、出力周波数に依存するため、高安定なVCOが必要となる。また、周波数が直線的に増加するためにはVCOの良好なリニアリティーが必要となる。

【0003】

図35(B)は従来のFM−CWレーダ送信部の典型的な構成を示している。発振周波数の温度変化に対してはCPUが温度センサで検出した温度によりデータテーブルを参照し、三角波の中心電圧を補正する。また、発振周波数のリニアリティーについてはCPUが同じくデータテーブルを参照することで三角波電圧の補正を行う。

【0004】

図35(C)は、従来のFM−CWレーダ送信部の他の構成例を示す図で、PLL(Phase Locked Loop)回路に三角波を重畳する方法を示している。この方法では、PLLを中心周波数で位相同期させることにより中心周波数を安定化する。一方、この中心周波数に加える周波数変移のリニアリティーについては、CPUがデータテーブルを参照することにより三角波電圧を補正する。

【0005】

また従来は、変調信号として水晶発振器6aに位相同期した三角波を用いることで発振周波数を安定化させると共に、出力のRF信号を周波数検波することで周波数偏移の上限や下限を超えないように制御を行う発振回路が知られている(特許文献1)。

【特許文献1】特開平6−120735

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかし、上記データテーブルを使用して発振周波数の温度変化やリニアリティーを補正する方式であると、別途に大きなデータテーブルを持つ必要があるばかりか、回路素子のバラツキに応じて装置毎に個別のデータテーブルを作成する必要があり、試験工数が大幅に増えてしまう。また、上記図35(C)の構成では、三角波で変調したVCO出力に対してPLLによるフィードバックがかかってしまうため、VCO出力の変調特性が悪化してしまう。また、特許文献1のVCOの変調特性はリニアであることが前提であり、もしリニアで無い場合は、データテーブル等を使用してリニアリティー補正する必要がある。

【0007】

また、マルチレーダシステムは、FM−CWレーダを複数個配置して構成され、各レーダに異なる検知エリアを割り当てることで、より広範囲なエリアをより精度良く検知することができる。マルチレーダシステムは、複数のレーダを搭載した一つの装置であってよいし、また、少なくとも一つのレーダを搭載した複数の装置であってもよい。例えば、自動車のような車両にレーダが搭載される場合、各車両に搭載されるレーダがマルチレーダシステムを構成する。

【0008】

図36は、従来におけるマルチレーダシステムにおける複数のレーダそれぞれの周波数割り当てを説明する図である。図36(A)は、レーダから送信される電波が干渉する場合を示し、同一の周波数帯域を用いて、複数のレーダから三角波変調された送信信号を送信すると、送信信号の周波数が同一になるタイミングが生じ、どちらのレーダからの送信信号であるか区別がつかず、正しい測定ができなくなる。そのため、複数のレーダを配置する場合、各レーダの送信信号の周波数が互いに干渉しないようにする必要があるため、図36(B)に示すように、周波数帯域が互いに重ならないように、少なくとも周波数の変動幅分の周波数帯域を各レーダに割り当てる必要がある。

【0009】

一方で、使用可能な周波数帯域が制限される場合には、一つのレーダあたりに割り当てる帯域を広く確保することができない。すなわち、送信信号の周波数偏移を大きく取ることができない。送信信号の周波数偏移が大きいほど、感度・分解能も上がるので、割り当てる帯域が十分に広くない場合、感度・分解能が低下する。

【0010】

また、温度変化や経時変化などにより、送信信号の中心周波数や周波数偏移の変動分を考慮して、隣接する送信信号間に所定の間隔をあける必要がある。この変動分が大きいと、干渉を防ぐために間隔を広く確保しなければならず、送信信号の周波数偏移量又はレーダ数(チャネル数)が犠牲となる。

【0011】

図37は、三角波で周波数変調された送信信号の中心周波数や周波数偏移の変動を説明する図である。図37(A)は、送信信号の中心周波数が変動する場合を示し、図37(B)は、送信信号の周波数偏移が変動する場合を示す。また、図37(C)は、周波数の変動分を考慮した周波数の割り当て例を示す図である。図37(C)では、1GHzの帯域に対して、周波数偏移を200MHz、変動分を50MHzとすると、2つのレーダしか配置することができず(2チャネルしか確保できず)、周波数帯域が効率的に利用されていない。

【0012】

本発明は上記従来技術の問題点に鑑みなされたもので、その目的とするところは、VCO回路の特性バラツキや温度変動によらず、簡単な構成及び制御で常に高安定なVCO出力が得られる位相同期発振器を提供することにある。

【0013】

また、本発明の目的は、常に高安定なVCO出力が得られる位相同期発振器を用いて、与えられた周波数帯域をより効率的に利用することができるマルチレーダシステムを提供することにある。

【課題を解決するための手段】

【0014】

本発明の第1の態様(VCOの校正)による位相同期発振器は、基準信号と比較信号の位相を比較する位相比較器と、該位相比較器の位相誤差信号を積分するローパスフィルタと、該ローパスフィルタの後段に介在して本器の主制御を行う制御部と、該制御部出力の制御電圧に応じた周波数の信号を発生するVCO回路と、該VCO回路の出力信号を分周して前記比較信号を形成する可変分周器とからなるPLLループを備える位相同期発振器であって、前記制御部は、PLLループを複数の周波数でロックさせて各ロック時の制御電圧を測定する制御電圧測定手段と、前記測定された各制御電圧に基づき、前記各周波数を結ぶ区間の周波数変化を代表する変調感度を求めるリニアリティー校正手段とを備えたものである。

【0015】

本発明によれば、PLLループを複数の周波数でロックさせる構成により、VCOの変調感度にバラツキや温度依存性があっても、該VCOを所要周波数で発振させるための制御電圧が容易かつ正確に得られる。

【0016】

本発明の第2の態様(VCOの駆動)による位相同期発振器は、前記PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を生成し、出力するVCO駆動手段を更に備えたものである。

【0017】

本発明によれば、VCO回路をリニアリティー校正された電圧信号で駆動する構成により、VCO回路の特性バラツキや温度変動によらず、常に安定した発振特性が得られる。

【0018】

本発明の第3の態様(間欠的なPLL制御)では、VCO駆動手段は、VCO回路が中心周波数を出力するタイミングに同期してローパスフィルタの出力をサンプリングし、検出した位相誤差信号が所定範囲を超える場合は、該位相誤差信号を小さくする方向に制御電圧をオフセットする。従って、間欠的なPLL制御により、中心周波数を一定に維持できる。

【0019】

本発明の第4の態様(間欠的なFLL制御)による位相同期発振器は、基準信号を分周する第1の分周器と、VCO回路の出力を分周して前記比較信号を形成する第2の分周器とを備え、前記VCO駆動手段は、前記第1,第2の分周器のカウンタをVCO回路に加える信号周期の整数倍周期で定期的にリセットすると共に、前記VCO回路が中心周波数を出力するタイミングに同期してサンプリングしたローパスフィルタ出力の位相誤差信号が所定範囲を超える場合は、該位相誤差信号を小さくする方向に制御電圧をオフセットする。

【0020】

本発明においては、第1,第2の分周器のカウンタを定期的にリセットする構成により、両分周信号を強制的に位相あわせする。しかし、もしVCO出力の周波数がずれていると、両分周信号間の位相は速やかに広がってしまう。そこで、本発明では、ローパスフィルタ出力の位相誤差信号を定期的に検出することで、該位相誤差信号の変化速度を監視し、VCO出力の周波数がずれているか否かを検出する。本発明では、第1,第2の分周器のカウンタを定期的にリセットすることで特定の絶対位相へ引き込まないので、位相引き込みが速い。なお、周波数のみ揃っていればロック状態にあると判定する制御を本明細書ではFLL(Frequency Locked Loop)制御と呼ぶ。

【0021】

本発明の第5の態様(PLLの高速引き込み)による位相同期発振器は、基準信号を分周する第1の可変分周器と、VCO回路の出力を分周して前記比較信号を形成する第2の可変分周器とを備え、前記制御部は、前記第1,第2の可変分周器に所定の分周比を設定後、PLLループを形成して基準信号と比較信号間の位相引き込みを開始する際に、前記VCO回路に前記所定の分周比に対応する制御電圧を加えると共に、前記第1,第2の可変分周器のカウンタをリセットするものである。

【0022】

本発明によれば、VCO回路に当初から設定分周比に対応する制御電圧を加えることで当初から所要周波数に近いVCO出力が得られる。また、第1,第2の可変分周器のカウンタをリセットすることにより、両分周信号の初期位相が強制的に揃う。この場合に、両分周信号の周波数は既に略一致しており、両分周信号の初期位相が合っているため、PLLループは速やかにロック状態に収束する。

【0023】

本発明の第6の態様(温度により変調感度が変化しないVCO回路を備える)による位相同期発振器は、基準信号と比較信号の位相を比較する位相比較器と、該位相比較器の位相誤差信号を積分するローパスフィルタと、該ローパスフィルタの後段に介在して本器の主制御を行う制御部と、該制御部出力の制御電圧に応じた周波数の信号を発生するVCO回路と、前記VCO回路の出力信号を分周して前記比較信号を形成する可変分周器とからなるPLLループを備える位相同期発振器であって、前記制御部は、PLLのロック周波数を所定間隔で変化させ、所定の周波数範囲をカバーする範囲につき各ロック時の制御電圧を測定する制御電圧測定手段と、前記測定した制御電圧の変動範囲を複数区間に分割して、各区間を代表する変調感度を求めるリニアリティー校正手段と、PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、VCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を、前記ロック時の制御電圧と前記求めた各区間を代表する変調感度に基づき生成し、出力するVCO駆動手段とを備えたものである。

【0024】

本発明によれば、予め所要周波数範囲の変調感度を一旦求めておけば、該変調感度は温度によりあまり変化しないので、任意温度におけるVCO駆動時には、VCO駆動手段は、PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、VCO回路に所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を、前記ロック時の制御電圧(基準電圧)と前記求めた各区間を代表する変調感度に基づき生成し、出力することで、温度によらず、VCO回路を常に正しい周波数で駆動できる。

【0025】

本発明の第7の態様によるマルチレーダシステムは、上記本発明の第1乃至第6の態様いずれかに記載の位相同期発振器を有する複数のFM−CWレーダを備えて構成されるマルチレーダシステムであって、各FM−CWレーダの前記制御部は、周期的に増減する制御電圧であって且つ前記制御電圧の増減方向及び増減速度が互いに一致するように所定の同期信号に同期した前記制御電圧を生成し、各FM−CWレーダの前記VCO回路は、前記制御電圧の増減に応じて、中心周波数に対して所定の周波数偏移量分周波数が周期的に増減する信号であって且つ各信号の中心周波数は互いに異なりさらに当該信号の周波数の増減方向及び増減速度が互いに一致する前記信号を出力する。

【0026】

本発明によれば、電波干渉を生じさせずに、各信号の周波数間隔を詰めることができ、より多くのチャネルを設定することができる。

【0027】

本発明の第8の態様によるマルチレーダシステムは、上記第7の態様において、各FM−CWレーダの前記制御部のうちの一つが前記同期信号を生成し、残りの前記制御部に出力する。

【0028】

本発明の第9の態様によるマルチレーダシステムは、上記第7の態様において、各FM−CWレーダの前記制御部のうちの一つが外部から供給される同期信号を受信し、残りの前記制御部に出力する。

【0029】

本発明の第10の態様によるマルチレーダシステムは、上記第7の態様において、各FM−CWレーダの前記制御部は、それぞれ外部から供給される同期信号を受信する。

【0030】

本発明の第11の態様によるマルチレーダシステムは、周波数が周期的に増減する信号を生成して出力する複数のレーダを含んで構成されるマルチレーダシステムにおいて、各レーダは、周期的に増減する周波数の上限値及び下限値が各レーダの信号毎に互いに異なり且つ当該上限値及び下限値になるタイミングが各信号毎に互いにほぼ一致するように所定の同期信号に同期して前記信号を生成することを特徴とする。

【0031】

本発明の第12の態様によるマルチレーダシステムは、上記第11の態様において、各レーダは、当該信号の周波数の増減方向及び増減速度が互いに一致するように所定の同期信号に同期して当該信号を生成する。

【0032】

本発明の第13の態様によるマルチレーダシステムは、上記第11の態様において、前記複数のレーダのうちの一つが前記同期信号を生成し、残りのレーダに出力する。

【0033】

本発明の第14の態様によるマルチレーダシステムは、上記第11の態様において、前記複数のレーダのうちの一つが外部から供給される同期信号を受信し、残りのレーダに出力する。

【0034】

本発明の第15の態様によるマルチレーダ異捨て無は、上記第11の態様において、前記複数のレーダは、外部から供給される同期信号を受信する。

【0035】

本発明の第16の態様によるマルチレーダシステムは、上記第11の態様において、前記複数のレーダは複数の車両それぞれに搭載されており、第1の方向に進行している車両に搭載されるレーダは、第1の周波数帯域に含まれる周波数の信号を生成し、第1の方向と異なる第2の方向に進行している車両に搭載されるレーダは、第1の周波数帯域と異なる第2の周波数帯域に含まれる周波数の信号を生成する。

【発明の効果】

【0036】

以上述べた如く本発明の位相同期発振器によれば、特性のバラツキや温度変化を有するVCO回路を使用しても、PLL制御による出力周波数の安定化、PLL開放下でのVCO駆動による出力周波数変化のリニアリティー向上が図れ、よって位相同期発振器の信頼性向上、更には、該発振器を使用したFM−CWレーダ等の普及に寄与するところが極めて大きい。

【0037】

また、本発明のマルチレーダシステムによれば、利用可能な周波数帯域に割り当てられるチャネルの周波数偏移量が従来と同程度であっても、電波干渉を生じさせずに、チャネルの周波数間隔を狭めることができ、従来と比較して多数のチャネルを当該周波数帯域に設定することができるようになり、周波数の利用効率が格段に向上する。

【発明を実施するための最良の形態】

【0038】

以下、添付図面に従って本発明に好適なる実施の形態を詳細に説明する。なお、全図を通して同一符号は同一又は相当部分を示すものとする。

【0039】

(位相同期発振器)

図1は第1の実施の形態による位相同期発振器のブロック図である。図において、1はPLLの基準クロック信号CKを発生するクロック発振器、2はPLLループを構成する位相比較部、11はクロック信号CKの可変分周器、12はVCO出力の可変分周器、13は両分周器出力φR,φVの位相を比較する位相比較器(PD)、3はPD13出力の位相誤差信号を積分するローパスフィルタ(LPF)、4は本発明の制御部に相当するプロセッサユニット(PU)、14はLPF3出力の位相誤差信号VpdをサンプリングするA/D変換器、15は本発振器の主制御・処理を行うCPU、16はCPU15出力の制御電圧をアナログの制御電圧Vcontに変換するD/A変換器、5は制御電圧Vcontに対応する周波数の発振信号を出力する電圧制御発振器(VCO)、6はVCO5の出力を通過/遮断するRFスイッチ(SW)である。

【0040】

CPU15は、VCO5の特性バラツキや温度変動によらず、PLLループを連続して又は周期的に構成することでVCO5の発振周波数を安定化させる制御と、レーダ動作時にPLLループを開放した状態で三角波信号を生成してVCO5にリニアリティー補正された周波数変調出力を出力させる制御とを行う。具体的には、後述の図2,図4,図6の各種処理を実行することにより、本発明の制御電圧測定手段、リニアリティー校正手段、VCO駆動手段(レーダ送信処理)等の各種機能を実現することもできる。

【0041】

制御電圧測定手段は、PLLループを複数の周波数でロックさせることで、各ロック時の制御電圧Vcontを測定する。その際には、位相比較部2に設定データを出力して、可変分周器11,12の分周比を所望に設定する。更に、LPF5出力の位相誤差信号Vpdを定期的にサンプリングすると共に、公知のPLL処理に従って位相誤差信号Vpdを小さくする方向に制御電圧Vcontを更新し、PLLループを複数の周波数で順次ロックさせる。各ロック時に取得した制御電圧Vcontは、VCO5の特性バラツキや温度変動によらず、該VCO5を各所定の周波数で発振させるに必要な制御電圧Vcontである。

【0042】

図1の挿入図(a)に一例のPLLループの概念構成図を示す。ここでは、LPF3とCPU15とが実現するループフィルタの機能を伝達特性F(s)を有するディジタルフィルタで表している。CPU15でディジタルフィルタを構成することにより、ゲインやクロック周期でフィルタ特性を変化させることができる。今、ディジタルフィルタの入力をX(n)、出力をY(n)とすると、差分方程式は、

Y(n)=(A+B)・X(n)+Y(n−1)−A・X(n−1)

で表される。これをZ変換すると、

Y(z)=(A+B)・X(z)+z−1・Y(z)−A・z−1・X(z)

で表され、フィルタの伝達特性F(z)は、

F(z)=Y(z)/X(z)=A+B/(1−Z−1)

で表される。これをF(s)で表すと、

F(s)=A+B/(1−e−j2πfT)

となる。

【0043】

更に、PLLとした場合の入力の位相をθi(s)、出力の位相をθo(s)とすると、ループの伝達特性H(s)は、

H(s)=θo(s)/θi(s)

=K・F(s)/{s+K・F(s)}

但し、K=Kd・Kv/N

で表される。

【0044】

次に、リニアリティー校正手段は、前記測定された各制御電圧Vcontに基づき、前記各周波数を結ぶ区間の周波数変化を代表(例えば直線近似)するような変調感度を求める。そして、VCO駆動(レーダ送信)手段は 前記PLLループを所定周波数(例えば送信信号の中心周波数)でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を生成し、出力する。このレーダ送信時には、ループ制御を開放しているため、VCO5の周波数変化を抑制するようなループのフィードバックはかからず、よって周波数変化の高い忠実性を維持できる。更に、該レーダ送信の例えば1周期毎にレーダ送信の中心周波数を安定化するためのループ制御を間欠的に行うことで、レーダ送信波の周波数も安定化する。以下、これらの制御・処理を詳細に説明する。

【0045】

図2は実施の形態による制御電圧測定処理のフローチャートで、PLLの分周比を変化させることでVCO出力に中心周波数f0、下限変調周波数f1、上限変調周波数f2を得るための各制御電圧V0,V1,V2を測定する場合を示している。ステップS11では、制御電圧Vcontの測定時に不要波を出力しないようRFスイッチSW6に対する出力ENをディセーブルし、無線波(RF)の出力を遮断する。ステップS12では測定シーケンスを保持するレジスタiの内容を初期化(例えばi=1に)する。ステップS13ではPLLが周波数fi(最初は下限周波数f1)でロックするように分周器11,12の分周比Nr,Ncを設定する。これによりPD13は両分周信号φR,φVの位相誤差に応じた位相誤差信号を出力し、これをLPF3で積分(フィルタ)する。

【0046】

ステップS14ではCPU15がLPF3出力の位相誤差出力Vpdを定期的に取得し、ステップS15では該信号Vpdが所要のセンター値(例えば2.5V)を中心とする所定範囲内にあるか否かを判別する。所定範囲内にない場合はPLLループがロック状態に無いため、ステップS16に進み、通常のPLLモードに従ってVpdがセンター値に近づく方向に制御電圧Vcontを更新する。

【0047】

こうして、やがて、ステップS15の判別で位相誤差出力Vpd ≒ センター値になると、PLLループがロック状態にあるので処理はステップS17に進み、その時点の制御電圧VcontをVi(最初は下限周波数f1に対する制御電圧V1)としてメモリに記憶する。ステップS18ではレジスタiの内容を更新し、次の測定対象を例えば中心周波数f0とする。ステップS19ではレジスタiの内容が測定終了か否かを判別し、測定終了でない場合はステップS13に戻る。こうして、続く中心周波数f0(V0)及び上限周波数f2(V2)についての測定を行い、やがて、ステップS19の判別で測定終了になると、この処理を抜ける。

【0048】

図3に第1の実施の形態による制御電圧測定動作のタイミングチャートを示す。一例の位相誤差出力Vpdは0〜5Vの範囲で変化し、中間の2.5V付近でロック状態と判定される。最初は、PLLは例えば下限周波数f1でロックするように分周比Nr,Ncを設定し、所定時間間隔でPLLループ制御を行う。CPU15は定期的にVpdを取得すると共に、通常のPLLループ制御に従って位相誤差出力Vpdが2.5Vに近づく方向に制御電圧Vcontを更新する。こうして、ループ制御を継続し、やがて、Vpd ≒2.5Vになると、ロック状態であり、この時、VCO5の発振周波数fは、VCO5の特性バラツキや温度による変動によらず、正確に下限周波数f1となっている。CPU15はこの時点の制御電圧Vcontを取得し、これをVCO5に下限周波数f1を発生させるための制御電圧V1としてメモリに記憶する。

【0049】

次に、PLLを中心周波数f0でロックさせ、その時点のVcontをVCO5に中心周波数f0を発生させるるための制御電圧V0としてメモリに記憶する。最後に、PLLを上限周波数f2でロックさせ、その時点のVcontをVCO5に上限周波数f2を発生させるための制御電圧V2としてメモリに記憶する。

【0050】

本実施の形態によれば、PLLループを各所定周波数(所定分周比)f0,f1,f2でロックさせる構成により、VCO5の特性バラツキや温度変化によらず、VCO5を所定周波数f0,f1,f2で発振させるための制御電圧V0,V1,V2を自動的に、かつ正確に求めることが可能である。

【0051】

図4は第1の実施の形態によるリニアリティー校正処理のフローチャートで、上記求めた(f1,V1),(f0,V0),(f2,V2)の組の情報に基づき、各周波数を結ぶ区間A〜DにおけるVCO出力を一定の周波数Δfづつリニアに変化させるための制御電圧Vcontを求める処理を示している。なお、この処理で求められた制御電圧Vcontを実際にVCO5に出力すれば、図5(b)に示すような出力の周波数特性が得られる。

【0052】

ステップS31では上記図2の処理で取得した制御電圧V0〜V2及び周波数f0〜f2の各情報を使用し、三角周期T0を例えば4分割した各区間j(=A〜D)におけるVCO5の変調感度を特性a(j)により直線近似する。図5(c)にリニアリティー校正動作のタイミングチャートを示す。

・区間Aの周波数変化f1→f0、制御電圧変化V1→V0により、

変調感度a(A)=(f0−f1)/(V0−V1)

・区間Bの周波数変化f0→f2、制御電圧変化V0→V2により、

変調感度a(B)=(f2−f0)/(V2−V0)

・区間Cの周波数変化f2→f0、制御電圧変化V2→V0により、

変調感度a(C)=−(f2−f0)/(V2−V0)=−a(B)

・区間Dの周波数変化f0→f1、制御電圧変化V0→V1により、

変調感度a(D)=−(f0−f1)/(V0−V1)=−a(A)

となる。

【0053】

ステップS32では、三角波条件(例えば、三角周期:10ms,中心周波数f0からの周波数偏移:±25MHz)とCPU条件(例えば、Vcontの時間分解能50μs,電圧分解能:0.005V)とに従い、各時点における周波数変化Δf(例えば、50μs当たり0.5MHz一定)を求める。ステップS33ではタイミングカウンタk=0,領域レジスタj=Aに初期化する。ステップS34では制御電圧Vcontに例えば下限周波数f1を生成させるための制御電圧V1をセットする。

【0054】

ステップS35では制御電圧の増分ΔVcont(k)を、

ΔVcont(k)=Δf/a(j)

により求める。ステップS36では、次の時点の制御電圧Vcont(k+1)を、

Vcont(k+1)=Vcont(k)+ΔVcont(k)

により求める。これにより、出力周波数をΔfづつ変化させるに必要な制御電圧Vcontが更新される。なお、レーダ動作時には更新した制御電圧VcontをVCO5に出力すると共に、この演算処理は50μs周期で定期的に行われる。

【0055】

ステップS37ではカウンタkに+1し、ステップS38ではk≧(T0/4)*jか否かを判別する。ここで、j=A〜Dは数1〜4に対応するものとする。k≧(T0/4)*jでない場合は、ステップS35に戻り、次のタイミングの制御電圧を求める。

【0056】

こうして、やがて、ステップS38の判別でk≧(T0/4)*jを満足すると、ステップS39では領域カウンタjに+1し、ステップS40ではj>4(=D)か否かを判別する。j>4でない場合は、ステップS35に戻り、次の領域の変調感度を使用して上記同様の処理を行う。こうして、やがてステップS40の判別でj>4になると、1周期T0分の制御電圧Vcontを求めたことになるので、この処理を抜ける。本実施の形態では、上記PLL動作と、VCOのリニアリティー校正処理を行うことにより、機器毎に固有の補正テーブルを設けなくても、VCO5のリニアリティーを自動的に高い精度で校正し、使用可能となる。

【0057】

図5は第1の実施の形態によるリニアリティー校正動作のタイミングチャートで、図5(a)にVCO5のもとの周波数変調特性を示す。横軸は制御電圧Vcont、縦軸は発振周波数である。VCO5の変調感度(Δf/ΔVcont)は非直線的に変化しており、中心周波数f0を境に見ると、低周波側では変調感度が高く、高周波側では低くなっている。この様な変調特性に対しては、図5(c)に示す様な制御電圧Vcontを加えることで、図5(b)に示す如く周波数が直線的に変化する特性が得られる。

【0058】

図5(b)にFM−CWレーダとしての好ましい周波数変化を示す。VCO5の出力周波数は下限f1と上限f2との間で直線的に変化している。リニアリティー校正処理は、図5(a)のVCO5に、図5(b)に示す如くリニア変化する周波数を出力させるための制御電圧Vcontを、図5(c)に従って求める処理である。

【0059】

図6は第1の実施の形態によるレーダ送信処理のフローチャートで、PLLを開放した状態で、CPU15がV0を基準にして連続した三角波を発生すると共に、1又は2以上の三角周期毎にその中心周波数をf0に維持するためのループ制御を間欠的に行う場合を示している。ステップS51ではPLLを一旦中心周波数f0でロックさせる。これにより、Vpd≒2.5V、Vcont≒V0(この時点のV0)に安定する。ステップS52ではCPU15が該V0を基準としてT0周期のリニアリティー補正された三角波を発生し、VCO5に加える。三角波の区間は、PLLループを開放しているため、VCO出力の周波数は図5(b)に示す如くリニアに変化する。PLLループの開放はCPU15がこの区間のループ制御を行わないことで容易に実現できる。

【0060】

一方、PD13はVCO出力の周波数変化に伴い位相誤差信号を変化させるが、LPF3は三角波周期よりも十分大きい時定数(例えば10倍程度)を有しているため、VCO5に三角波を加えてもこの区間の位相誤差信号はLPF3で平均化され、出力の位相誤差信号Vpdには三角波周期毎に僅かな変動が生じることになる。

【0061】

ステップS53では3T0/4(中心周波数)のタイミングでLPF3の位相誤差信号Vpdを取得する。VCO5の特性に変動が無い場合はこの区間の位相誤差信号は平均化されてVpd≒2.5Vの付近にあるが、VCO特性が変化すると、これに伴いVpdも徐々に変化する。ステップS54ではVpd≒Vref(=2.5V)か否かを判別する。Vpd≒Vrefの場合はf0が所要範囲内にあるので処理はステップS58に進む。またVpd≒Vrefでない場合は、更にステップS55でVpd>Vrefか否かを判別する。

【0062】

Vpd>Vrefでない場合はステップS56に進み、次のT0/4におけるVpdを増やすべく、例えば次の時点のVcont(例えばV1)を−側にオフセットする。また、Vpd>Vrefの場合はステップS57で次のT0/4におけるVpdを減らすべく、次の時点のVcont(例えばV1)を+側にオフセットする。CPU15は図1(a)のディジタルフィルタに従ってオフセット量を決定する。なお、制御電圧にオフセットを加えるタイミングは、上記VCO5にV1を加えるタイミングでも良いが、他のタイミングでも良い。ここで注目することは、三角波の周期内ではオープンループ動作となり、VCO出力の三角波特性を変形することはないことである。そして、三角波周期のある時点に同期して周期的(間欠的)にフィードバックしPLLをかけることである。ステップS58以降では何周期の三角波ごとにフィードバックを入れるかを設定するため、フィードバック制御のない三角波を所定数出力する。即ち、ステップS58ではフィードバック制御のない三角波の数が所定回数分出力したか否かを判別し、実行してない場合はステップS59でフィードバック制御のない三角波を一周期出力する。また実行した場合はこの処理を抜ける。

【0063】

図7は第1の実施の形態によるレーダ送信動作のタイミングチャートで、3角波周期毎にVcont(V1)にオフセットを加える場合を示している。本実施の形態によれば、3角波の終わった瞬間にフィードバックをかけるため、VCO5の出力周波数の三角形状はなまらない。なお、フィードバックする周期とPLLのループゲインとは反比例するため、ループゲインを落とし、制御の応答を遅くしたいような場合には、フィードバック周期を長くする方法がある。例えば制御電圧Vcontは三角波の10周期ごとにフィードバックし、V1の値をオフセットするとか、または三角波の1000周期ごとにフィードバックし、V1の値をオフセットすることが可能である。

【0064】

図8は第1の実施の形態によるレーダ運用動作のタイミングチャートで、一連のレーダ動作の合間に、VCOのリニアリティー校正動作を割り込ませることで、常に安定したレーダ動作を維持可能な場合を示している。VCO5は温度特性を有するため、レーダ動作中に温度が変化すると、中心周波数f0を出力させるための制御電圧V0も変化する。本実施の形態では、定期的にリニアリティーの再校正を行うことで常に安定したレーダ動作を維持できる。

【0065】

図8(A)は、一連のレーダ動作の合間に制御電圧V1,V0,V2の測定及びこれに伴うリニアリティー校正を行う場合を示している。なお、別途に温度変化を検出して温度が所定以上変化した場合に制御電圧V1,V0,V2の測定及びリニアリティー校正を行うように構成しても良い。また、制御電圧の測定順序は任意であり、例えば中心周波数f0の測定を最後にできる。こうすれば、PLLループは既に周波数f0でロックしているので、続くレーダ動作に移る際には、上記図6で述べたステップS51の処理を省略できる。

【0066】

図8(B)は、各一連のレーダ動作の合間に、各制御電圧V1,V0,V2の測定を順々に行い、最後のV2の測定と共にVCO5のリニアリティー校正を行う場合を示している。こうすれば、一制御電圧当たりの測定時間は短いので、レーダ動作のデッドタイムを小さくできるメリットがある。なお、この方法は、図示しないが、上記3点の制御電圧V1,V0,V2のみでなく、制御電圧の測定ポイントをもっと増やして、よりきめ細かいリニアリティー校正を行う場合に特に有利である。

【0067】

図9は第2の実施の形態による位相同期発振器のブロック図で、LPFをレーダ用とVCO校正用の2系統備え、各動作におけるPLLの高速引き込みを可能にした場合を示している。図において、PD3の出力はスイッチ17a,17bを介してLPF3a,3bにそれぞれ入力している。LPF3aは専らVCO駆動時の中心周波数出力タイミングにサンプリングした位相誤差信号を積分し、LPF3bは専ら制御電圧測定時の位相誤差信号を積分する目的で使用される。好ましくは、LPF3bの時定数をLPF3aの時定数よりも小さくすることで、各周波数に対する制御電圧の測定時間を短縮できる。

【0068】

また、この例の可変分周器11,12はCPU15からカウンタをリセット可能に構成されており、両カウンタを一斉にリセットすることで両分周信号φR、φVの初期位相を強制的に揃えることが可能である。また、スイッチSW7aは信号の通過をON/OFF可能に構成されており、LPF3aは、SW7aがONしている区間の位相誤差信号を積分し、SW7aがOFFすると、それまでに蓄積した積分値(コンデンサのチャージ)をそのまま保持可能である。スイッチSW7bとLPF3bとについても同様である。本実施の形態では、このような構成を有効活用することでPLLループの引き込み時間を大幅に短縮可能である。以下、詳細に説明する。

【0069】

図10は第2の実施の形態による位相同期発振器の高速引き込み処理のフローチャートで、この処理は、前半の例えば制御電圧V1の測定処理と、後半のレーダ動作処理とからなっている。例えば直前のレーダ動作終了後、この処理に入力する。ステップS61では可変分周器11,12の分周比をf1に設定する。ステップS62では制御電圧Vcontに前回のV1の測定で取得し、記憶しておいたV1を設定する。これによりVCO5は、温度変動によらず、当初より前回のV1の測定でロックした時の下限周波数f1を発生することになる。ステップS63では可変分周器11,12のカウンタをリセットし、これにより両分周信号φR,φVの初期位相が速やかに揃う。

【0070】

ステップS64では、上記V1測定の準備ができたことにより、スイッチ制御信号SW2をONにし、LPF3bを介したPLL動作を可能とする。この時、LPF3bでは内部コンデンサが前回の制御電圧の測定でロック状態に至った際の位相誤差電圧Vpd2(≒2.5V)を保持しており、この位相誤差電圧Vpd2は、前回の測定電圧がV1,V0又はV2によらず、そのロック状態では約Vref(例えば約2,5V)になっている。従って、今回のPLLループもロックに近い状態から開始できるため、ループの時定数によらず、より早い時点でロック状態に収束できることになる。ステップS65ではVpd2を取得する。ステップS66ではVpd2≒Vrefか否かを判別し、NOの場合はステップS67でVpd2がVrefに近づく方向にVcontを更新し、ステップS65に戻る。

【0071】

こうして、やがて、上記ステップS66の判別でVpd2≒Vrefになると、ステップS68ではその時点のVcontを取得し、制御電圧V1の記憶用のメモリに記憶する。ステップS69ではスイッチ制御信号SW2をOFFにし、これにより今回ロックした際の位相誤差電圧Vpd2がLPF3b内のコンデンサに保持される。

【0072】

次にレーダ動作に移り、ステップS71では可変分周器11,12の分周比を中心周波数f0に設定する。ステップS72ではVcontにV0を中心とする三角波信号を重畳する。ステップS73では可変分周器11,12のカウンタをリセットし、速やかに両分周信号φR,φV間の初期位相を合わせる。ステップS74では、レーダ動作の準備ができたことにより、スイッチ制御信号SW1をONにし、LPF3aを介したPLL動作を可能とする。この時、LPF3aでは内部コンデンサが前回のレーダ動作で略ロック状態に維持された際の位相誤差電圧Vpd1(約2,5V)を保持している。

【0073】

ステップS75では上記図6で述べた様なレーダ送信制御を行い、ステップS76では所定サイクル数分の三角波送信を行ったか否かを判別する。終了してない場合はステップS77でフィードバック制御のない三角波を一周期出力する。こうして、やがて、ステップS76の判別で所定サイクル数分の送信を終了するとステップS78ではスイッチ制御信号SW1をOFFにし、これにより今回のレーダ動作でロック維持した際の位相誤差電圧Vpd1がLPF3a内のコンデンサに保持される。

【0074】

図11は第2の実施の形態による位相同期発振器の高速引き込み動作のタイミングチャートで、各一連のレーダ動作の間に、制御電圧V1の測定処理を割り込ませた場合を示している。前回のレーダ動作が完了すると、スイッチ制御信号SW1がOFF(L)となり、LPF3aのVpd1を保持する。CPU15は可変分周器11,12にf1を得るための分周比を設定し、前回測定したV1をVcontとして出力する。更に、可変分周器11,12のカウンタをリセットして初期位相を合わせる。以上で測定動作の準備ができたので、スイッチ制御信号SW2をON(H)とし、LPF3bの位相誤差信号Vpd2に従ってPLL動作を行う。こうして、やがて、Vpd2がロック範囲内にあることを確認すると、CPU15はその時点のVcontを新たなV1として記憶する。V1の測定を完了すると、スイッチ制御信号SW2をOFFにし、その時点のVpd2を保持する。

【0075】

次のレーダ動作に移ると、可変分周器11,12にf0を得るための分周比を設定する。更に、CPU15からV0を中心とした三角波波形を出力する。なお、この例の三角波の校正はV2の測定後に行われる。更に可変分周器のカウンタをリセットして初期位相を合わせる。そして、レーダ動作の準備ができたので、スイッチ制御信号SW1をONにし、レーダ用のVpd1でPLLを動作させる。以下、同様にしてV0,V2を取得し、リニアリティー構成データの更新を行う。

【0076】

図12は第3の実施の形態による位相同期発振器のブロック図で、2系統のPLL回路を備え、これらを単独のCPU15で制御すると共に、一方のループを使用してレーダ動作を実行すると同時に、他方のループを使用してVCO回路のリニアリティー校正を行い、これらを両系統のPLL回路で交互に行う場合を示している。これにより、レーダ動作のデッドタイムを無くすことが可能である。

【0077】

図13に第3の実施の形態による位相同期発振器の動作タイミングチャートを示す。PLLaによりレーダ動作すると共に、PLLbではV1,V0,V2の測定及びVCO5bのリニアリティー校正を行う。次いで、PLLbによりレーダ動作すると共に、PLLaではV1,V0,V2の測定及びVCO5aのリニアリティー校正を行う。切換えは、例えば5分毎のように定期的に切換えても良く、あるいは外気の温度変化がある範囲を超えた場合に行っても良い。

【0078】

図14は第4の実施の形態による位相同期発振器を説明する図で、VCO回路の発振周波数は温度変化によってドリフトするが、その変調感度は温度によってあまり変化しないようなVCO回路に適用して好適なる場合を示している。実際上、このような特性を有するVCO回路は少なくない。なお、PLL回路については上記図1、図9又は図12で述べたものと同様でよい。図14(A)にこの種のVCO回路の変調特性を示す。常温時の変調カーブをaとすると、高温時にはカーブb側にシフトし、また低温時にはカーブc側にシフトする関係にある。このようなVCO回路では、同一の制御電圧V0を加えた場合でも、その発振周波数は温度によりf0'〜f0''に変化するが、V0近傍の変調感度は変わらないので、周波数をΔf変化させるためのΔVcontも温度により変化しない。このことは全制御電圧範囲Vmin〜Vmaxについて言えることである。

【0079】

図14(B)にこのVCO回路に対するリニアリティー校正処理のフローチャートを示す。ステップS81では可変分周器PLLの分周比Nr,Ncを変化させることで、ロック周波数を徐々に高くしてスイープさせ、その都度制御電圧Vcontを測定する。ステップS82では、前記測定した各制御電圧Vcontについて、制御電圧の可能な変動範囲Vmin〜Vmaxを例えば1V毎に分割し、各区間を代表するような変調感度a01、a12、a23,…を求める。ステップS83では三角波条件とCPU条件とに基づき、各時点における周波数変化Δf(この例では一定)を求める。こうして、温度変動によらず共通して使用可能な感度テーブルが得られる。

【0080】

なお、図示しないが、レーダ送信時には、まずPLLをf0にロックさせることで、その時点の制御電圧V0が求まる。以後は、例えば該V0を起点にして上限周波数f2までΔf分づつVcontを増加する。その際には、各時点のVcontがどの電圧区間にあるかを判別し、各対応する区間の変調感度を利用することで当該区間の各電圧変化を求める。こうして、やがてf2に達すると、次に下限周波数f1までVcontを減少させ、次にf0まで増加させる。そして、このような制御を繰り返す。従って、本実施の形態によれば、温度変動によらず、常に適正な周波数範囲のレーダ波を送信できる。また、温度変動ではリニアリティー校正処理を行う必要が無いため、レーダ動作を中断せずに運用できる。

【0081】

図15,図16は第5の実施の形態による位相同期発振器を説明する図(1),(2)で、図15は、両分周信号φR,φV間の位相までを揃えるPLL制御に代えて、周波数のみ揃っていれば位相までは揃わなくても良いとする所謂FLL(frequency Locked Loop)制御を行う場合を示している。一般に、制御電圧VcontをD/A変換してVCO5に加えると、VCO5の出力周波数は、最小でもD/A16の1ビット電圧分解能×変調感度の大きさで段階的に変化することになる。一方、PLLループ(即ち、LPF3)は三角波駆動によるレーダ送信波の平均周波数がf0となるようアナログ的に動作するので、位相誤差信号Vpdのロック検出幅をあまり狭くすると、制御電圧V0に対するオフセット補正が頻繁に発生してしまうことになる。本第5の実施の形態では、この問題を解決すべく、PLL制御に代えて、FLL制御を行う。なお、回路構成については例えば図1と同様のものでも良いが、CPU15から可変分周器11,12のカウンタをリセット可能に構成されているものとする。

【0082】

一般に、両分周信号φR,φV間の位相は、VCO5をフリーランさせている(即ち、PLLループをオープンにしている)状態では、例え両分周信号φR,φVの周波数が揃っていても、これらの位相は徐々にずれる(スリップする)ことになるが、本第5の実施の形態により可変分周器11,12のカウンタを毎周期毎にリセットすることで、三角波の1周期内に大幅な位相差が生じることを有効に回避できる。しかし、もしVCO5の発振周波数が所要からずれている場合には、両信号φR,φV間の位相差も短時間で速やかに広がるため、このような状態は位相誤差信号Vpdを毎周期観測することで確実に検出できる。

【0083】

図15において、FLL制御に基づく本実施の形態では、両分周信号φR,φV間の位相までは揃わなくても、VCO5出力の周波数が所定範囲内に入っていれば良いので、可変分周器11,12のカウンタを例えば三角波の1周期毎にリセットすると共に、単位区間(例えば1周期)内にVpdが所定以上変化したことを検出した場合は、出力周波数が所定範囲外にあるとして、制御電圧Vcontをオフセットする。図16に位相比較部2の動作を示す。FLL制御の実現方法としては、可変分周器11,12のカウンタを定期的(3角波の1又は2周期以上)にリセットすることにより、容易に実現できる。

【0084】

図17は第6の実施の形態による位相同期発振器を説明する図で、CPU15が三角波信号を発生する代わりに、リニアリティー校正された2値波信号を発生する場合を示している。なお、位相同期発振器の構成については上記図1,図9又は図12に示したものと同様で良い。図において、この例のVCO5は時間tの進行に伴い定期的に周波数f1とf2とを交互に出力している。中心周波数はf0である。このような位相同期発振器は2周波CW方式のレーダ装置に適用して好適である。

【0085】

図18,図19は実施の形態による故障検出動作を説明する図(1),(2)で、図18(A)は通常動作時における位相誤差信号Vpdが異常レベルにある場合を示している。本装置を車載用として用いる場合、人命に係わるため、常に動作の状態を監視する必要がある。本実施の形態では、通常動作時に位相誤差信号VpdがPLL引き込み可能な正常電圧範囲から外れたことにより、ロック異常を検出する。

【0086】

図18(B)は通常動作時における中心の制御電圧V0が異常レベルにある場合を示している。過酷な使用環境下では、例えば、筐体内への水の侵入や、結露等によって中心周波数f0(即ち、制御電圧V0)が大幅に変動する場合がある。本実施の形態では、通常動作時に制御電圧V0が正常範囲から外れたことにより、VCO動作の異常を検出する。

【0087】

図19は電源ON時のリニアリティー校正結果が異常の場合を示している。VCO特性は経時変化によっても劣化する。本実施の形態では、装置の電源投入時又は定期的にPLLループを構成してリニアリティー校正すると共に、例えば電源ON時におけるf0,f2,f1に対する各Vcont測定値V0,V2,V1と、工場出荷時のこれらの値とを比較することで、これらの内の何れか1つ以上が所定以上外れていることを検出すると、異常と判定する。なお、この例では絶対電圧が指定範囲内であるかを比較しているが、各電圧間の相対的な電圧値が指定範囲内であるかを比較しても良い。

【0088】

なお、上記図1,図9又は図12において、本回路をミリ波帯のFM−CWレーダ等に使用する場合は、ミリ波帯の可変分周器12を使用するが、このような可変分周器が入手困難又は高価な場合には、より低い周波数の可変分周器12を使用すると共に、VCO5の出力を周波数逓倍器(MULTI)7によってミリ波帯に逓倍して出力しても良い。

【0089】

また、CPU15が発生する信号は、上記三角波信号や2値波信号以外にも様々な信号波形(正弦波、ノコギリ波等)を発生可能である。

【0090】

また、上記実施の形態ではVCO5の変調感度を3つの測定ポイントf1,f0,f2に渡って直線近似したが、これに限らない。測定ポイント数を増やすことで、より高精度な近似が可能となり、リニアリティー校正の精度を上げることができる。

【0091】

また、上記実施の形態では、複数区間における変調感度を各区間における直線近似で代表したが、これに限らない。各区間におけるカーブをより忠実に近似可能な高次の関数や指数関数等により近似しても良い。

【0092】

また、上記実施の形態では位相比較部2とCPU15のクロック信号CKを共通にしたが、CPU15に別系統のクロック信号を使用しても良い。

(マルチレーダシステム)

以下、上述した位相同期発振器を用いたレーダを複数個配備したマルチレーダシステムについて説明する。

【0093】

図20は、第7の実施の形態によるマルチレーダシステムの概略構成例を示す図である。マルチレーダシステムは、複数のFM−CWレーダ(以下、単にレーダと称する)100−1、100−2、100−3、100−4を備える(以下、各レーダを区別しない場合は、レーダ100と称する)。以下の説明では、一例として、4つのレーダを備えるマルチレーダシステムについて説明するが、レーダの数は4つに限らず、必要に応じた複数個のレーダを配備可能である。また、図20の構成は、複数のレーダを搭載する一つの装置としてのマルチレーダシステムである。

【0094】

複数のレーダのうちの一つ(例えば、レーダ100−1)は、マスターレーダMとして機能し、後述するように、三角波の出力に応じて同期信号を生成、当該同期信号を出力する。残りのレーダ(例えば、レーダ100−2〜100−4)は、マスターレーダMからの同期信号が入力され、当該同期信号に応じて三角波を出力するスレーブレーダS(S1〜S3)として機能する。

【0095】

図21は、各レーダの概略構成例を示す図である。マルチレーダシステムを構成する各レーダ100では、発振部101が三角波で周波数変調された送信信号を生成し、送信信号はアンテナから放射される。この発振部101は、上述した本発明の実施の形態による位相同期発振器である。目標物に当たって反射した信号は受信信号としてアンテナで受信され、ミキサ102で送信信号とミキシングされることでビート信号が得られる。三角波で周波数変調された送信信号は時間ともに周波数が変化しており、受信信号は往復時間だけ前に放射された送信信号の反射波であるため、現在の送信信号と周波数がずれていることを利用して、目標物までの距離を算出する。また、目標物との相対速度を算出するには、ドップラー効果により反射波が周波数偏移することを利用する。目標物までの距離及び目標物との相対速度は、ビート信号を解析し、既知の計算方法によって求められる。

【0096】

図22は、第7の実施の形態によるマルチレーダシステムにおける各レーダ100の発振部101の構成を示す図である。なお、発振部101−1はレーダ100−1の発振部、発振部101−2はレーダ100−2の発振部、発振部101−3はレーダ100−3の発振部、発振部101−4はレーダ100−4の発振部を示す(各発振部を区別しない場合は、発振部101と称する)。各発振部101は、例えば、図1に示す第1の実施の形態による位相同期発振器により構成される。マスターレーダとして機能するレーダ100−1の発振部101−1のCPU15−1は、三角波を生成する所定のタイミングで同期信号を出力する。

【0097】

図23は、同期信号の出力を説明する図である。図示されるように、例えば、同期信号は、三角波の1周期毎に出力される。

【0098】

図22において、CPU15−1から出力される同期信号は、スレーブレーダとして機能するレーダ100−2、100−3、100−4の各発振部101−2、101−3、101−4のCPU15−2、15−3、15−4に入力される。そして、CPU15−2、15−3、15−4も、同期信号に同期して三角波を出力する。

【0099】

図23において、各CPU15−1〜15−4(各CPUを区別しない場合は、CPU15と称する)は、入力された同期信号の立ち上がりエッジを検知すると、三角波形状の制御電圧Vcont出力を開始し、結果、送信信号に1周期の三角波形状で周波数変調する。同期信号を三角波の周期で入力し続けることにより、送信信号は三角波の周波数変調が連続してかかる。

【0100】

以上にように、同期した複数の三角波を生成する三角波生成部の例としてCPU15−1〜15−4等を備え、かつ、この複数の三角波のそれぞれを制御信号として、それぞれの制御信号に応じて周波数変調された信号を出力する複数のVCOを備え、複数の電圧制御発信器は、互いに中心周波数が異なる、周波数変調された信号を出力するとともに、少なくとも1つの三角波に基いて生成される周波数変調された信号の下限周波数に対して、少なくとも他の1つの三角波に基いて生成される周波数変調された信号の上限周波数が大きくなるように出力周波数が設定することで、周波数変調された各信号の周波数間隔を縮めることができる。

【0101】

このとき、図24のように、1つの周波数変調された信号の下限周波数に対してマルチレーダとして送信する他の全て(1つ(中心周波数が最も近いもの)、2つ(中心周波数が最も近いもの及び次に近いもの)、又は、それ以上)の周波数変調された信号の上限周波数が高い周波数になるように設定することもできる。

【0102】

図24は各発振部101において周波数変調された送信信号の周波数変化を示す図である。各送信信号の三角波状の周波数変化が同期信号に同期しているので、各送信信号の周波数は同期して変化する。すなわち、各送信信号の周波数変調による上限周波数及び下限周波数となるタイミングは一致する。また、周波数の増減方向も一致する。

【0103】

さらに図24の周波数領域では、各発振部101の中心周波数は所定の周波数間隔(チャネル間隔)ずらして割り当て、各レーダの三角波変調の周波数偏移量を一定とするように制御電圧Vcontを制御することで、周波数の増減速度が一致し、どのタイミングでも常に一定の周波数間隔となる。

【0104】

従って、隣接する送信信号同士において、従来、中心周波数の高い方の下限周波数が、中心周波数の低い方の上限周波数より低くなり問題となるような場合でも、送信信号の周波数は重ならず、干渉は生じない。例えば、発振部101−1の送信信号の下限周波数は、それに隣接する発振部101−2の送信信号の上限周波数より低くなるが、そのタイミングが重ならず、発振部101−1の送信信号と発振部101−2の送信信号が干渉することはない。他の送信信号同士も同様に干渉することはない。

【0105】

本発明の実施の形態におけるマルチレーダシステムでは、互いに同期した三角波で周波数変調を行い、変調の周波数偏移量を合わせることで、所定の周波数間隔(チャネル間隔)を、周波数偏移量に依存しないでチャネル設定が可能となる。

【0106】

すなわち、送信信号の周波数偏移量を変えずに、一定の周波数帯域により多くのチャネルを設定することができるようになり、周波数帯域をより有効に利用することができる。なお、本明細書では、配備されたレーダの送信信号に割り当てられる周波数をチャネルと呼ぶ場合がある。

【0107】

チャネル間隔は、次の表1に示す項目を考慮して、決定される。

【0108】

【表1】

【0109】

具体的には、利用可能な周波数帯域が76GHz〜77GHzの1GHz幅である場合(項目1)、各レーダの送信信号の周波数誤差となる基準信号間の周波数偏差(項目2)、PLL回路の定常周波数誤差(項目3)、周波数偏移の校正誤差(項目5)、ドップラー偏移(項目7)、往復時間による周波数ずれ(項目11)などを考慮し、これらの周波数変動幅を合計した値の2倍(中心周波数から上下方向にそれぞれの変動幅が生じるため)が必要なチャネル間隔となる。表1の例では、項目2、3、5、7及び11の各変動幅の合計(3.7225MHz)の2倍の値、すなわち、約7.45MHzとなる。

【0110】

周波数偏移量は200MHz(項目4)に設定されているので、周波数帯域76GHz〜77GHzにおいて、中心周波数が設定できる帯域は、76.2GHz〜76.8GHzの600MHzの帯域となり、チャネル間隔を7.45MHzとすると、この帯域に81本のチャネルを設定することができる。

【0111】

図25は、周波数帯域76GHz〜77GHzに81チャネルが設定された例を示す図である。図22(c)に示した従来の場合では、帯域1GHz、周波数偏移量200MHzとした場合、2チャネルした設定できなかったが、本発明の実施の形態例では、ほぼ同様の条件にて81チャネルが設定可能であり、チャネル数を大幅に増加させることができる。

【0112】

図26は、第8の実施の形態によるマルチレーダシステムの概略構成例を示す図である。第8の実施の形態によるマルチレーダシステムは、図20における第7の実施の形態の変形例であり、同期信号が外部から供給される場合を示す。具体的には、三角波の周期を有する同期信号を例えばAM放送又はFM放送の電波を用いて、外部の電波発信源から放射する。マルチレーダシステムの受信機110がその電波を受信し、電波に含まれる所定周波数の同期信号が各レーダ100−1〜100−4に供給される。同期信号は、図示されるように、マスターレーダ100−1を通じて各スレーブレーダ100−2〜100−4に供給されてもよいし、受信機110から並列にマスターレーダ100−1〜100−4に供給される構成であってもよい。また、各レーダ100が受信機110を備え、各レーダが同期信号を受信する構成であってもよい。同期信号を外部から供給することにより、同期信号を生成する個々のマスターレーダの個体差による同期信号のずれをなくし、複数のマルチレーダシステム間でも、三角波の同期を取ることができる。

【0113】

特に、複数の車両それぞれに少なくとも一つのレーダが搭載されて、マルチレーダシステムが構成される場合、各車両ごとに受信機110を搭載し、各車両のレーダは、受信機110で受信された同期信号に基づいて三角波を出力する。これにより、離間する複数のレーダで構成されるマルチレーダシステムにおける各レーダの三角波も同期を取ることができる。また、GPSを利用したカーナビゲーションシステムの車両への搭載が普及しており、車両でGPS信号を入手することが容易にできるようになってきている。このGPS信号で、例えば1秒間隔で出力される1pps信号を同期信号とすることもできる。この場合、1pps信号は1秒間に1パルス出力なので、三角波の周波数が100Hzである場合は、1pps信号が入力されると、三角波100パルス出力すればよい。

【0114】

図27は、第9の実施の形態によるマルチレーダシステムの各レーダにおける発振部101の構成例を示す図である。第9の実施の形態によるマルチレーダシステムは、図22における第7の実施の形態の変形例であり、基準信号を各レーダで共通化する場合を示す。具体的には、基準信号を生成するクロック発振器1を各レーダの発振器で共通化している。これにより、基準信号の周波数偏差(表1の項目2)を考慮する必要がなくなり、さらにチャネルの周波数間隔を詰めることができる。具体的には、表1の場合、約7.45MHzを約5.93MHz((3.7225MHz−0.76MHz)×2=5.9225MHz)に詰めることができる。

【0115】

図28は、第9の実施の形態におけるマルチレーダシステムにおける各レーダの送信信号の周波数割り当て例を示す図である。図28では、一例として、4台の車両A、B、C、Dそれぞれに4つのレーダを搭載している場合であって、1台の車両における4つのレーダのクロック発振器1を共通化することで、各車両内における周波数間隔は5.93MHzとすることができ、車両間の周波数間隔は約7.45MHzとする。

【0116】

図29は、第10の実施の形態によるマルチレーダシステムの各レーダにおける発振部101の構成例を示す図である。第10の実施の形態によるマルチレーダシステムは、図22における第7の実施の形態の変形例であり、マスターレーダとスレーブレーダの区分をなくし、CPU15とは独立して同期信号を生成、出力する同期信号制御部(同期信号生成手段)111が設けられる。同期信号制御部111により生成された同期信号は、各レーダ100−1〜100−4に供給される。また、同期信号の入出力停止など同期信号に関する何らか異常、故障の検出も、同期信号制御部111が一元的に行う。

【0117】

図30は、車両の進行方向によってチャネルの周波数帯域を分割する適用例を示す図である。本発明の実施の形態によるマルチレーダシステムを自動車の車両に適用した場合において、2つの車両がすれ違う場合に、各車両のレーダに割り当てられたチャネルが同一であると、互いに他方のレーダからの送信信号を受信していまい、正しい測定が行えない。そこで、一例として、図30に示すように、周波数帯域を上り用帯域と下り用帯域に分け、車両の進行方向に対応する帯域のチャネルを割り当てる。車両の進行方向は、例えば、車両に搭載されるGPSシステムにより検知される方位の情報を用いて取得される。上り方向に進行する車両には、上り用帯域のチャネルを割り当て、下り方向に進行する車両には、下り用帯域のチャネルを割り当てる。これにより、すれ違うことにより近接する2つの車両のチャネルが同一になることない。なお、仮に同一方向に進行する2つの車両に、同一のチャネルが割り当てられている場合、2つの車両に搭載されるレーダの電波が互いに干渉するほどに近接する可能性は、すれ違う場合と比較して十分に低い。従って、図30のように、チャネルを割り当てる周波数帯域を分割し、車両の進行方向が異なり、すれ違いなど車両同士が近接する可能性が高い場合は、車両の進行方向により異なる周波数帯域のチャネルを割り当て、車両同士が近接する可能性が低い場合は、実質的に、同一のチャネルを複数の車両で用いることも可能となる。

【0118】

図31は、車両の進行方向によってチャネルの周波数帯域を分割する別の適用例を示す図である。図31は、図30における2方向ではなく、4方向に分割する例であり、例えば東西南北の4方向について、周波数帯域を分割し、車両の進行方向によって異なる周波数帯域のチャネルを割り当てる。分割する方向は、2方向や4方向に限らず、例えば8方向などさらに細かく分割されてもよい。

【0119】

本発明の実施の形態におけるマルチレーダシステムを構成する各レーダは、FM−CWレーダに限られない。例えば、各レーダは2周波CWレーダであってもよく、2周波CWレーダの場合、各レーダに割り当てられた2つの周波数はレーダ毎に異なっており、周波数の切り替えタイミングをレーダ毎に一致させることで、送信信号同士の干渉を抑えることができる。

【0120】

図32は、2周波CWレーダによるマルチレーダシステムにおける周波数割り当て例を示す図である。以下では、2周波CWレーダも単にレーダと称し、参照番号100を用いる。図32(A)では、各レーダの送信信号の周波数切り替えタイミングを一致させる。これにより、各レーダ100に割り当てられる周波数は、他のレーダに割り当てられる2つの周波数間の帯域内であっても、互いの周波数は重ならない。なお、周波数切り替えタイミングにおいては、各レーダの周波数は瞬間的に重なるが、この切り替えタイミングの信号はマスクし、信号処理の対象としない。図32(B)は、周波数切り替えタイミングにおいても、干渉が生じない周波数割り当て例である。周波数が重ならないように、切り替えタイミングをレーダ毎にずらす。これにより周波数切り替えタイミングにおけるマスク処理を不要とする。また、図32(C)は、複数のレーダ100−1〜100−4において、周波数切り替えタイミングにおけるレーダ100−1と100−2の周波数切り替え方向と、レーダ100−3と100−4の周波数切り替え方向を互いに逆方向になるように異ならせる例である。これにより、周波数帯域に割り当て可能なチャネル数をさらに増やすことができ、周波数利用効率が向上する。同方向にのみ周波数が切り替わる図32(A)、(B)に比べて、チャネル数を最大2倍増とすることができる。

【0121】

図33は、2周波CWレーダによるマルチレーダシステムの大規模な周波数配置例を示す図である。周波数帯域を複数のグループに分割し、各グループにおいて、図32(C)に示した周波数配置例を適用する。すなわち、各グループにおいて、周波数切り替えタイミングは同時だが周波数切り替え方向が異なる複数のチャネルが設定される。

【0122】

図34は、2周波CWレーダによるマルチレーダシステムの概略構成例を示す図である。図34の構成例は、図20の構成例と同様に、周波数切り替えタイミングにおいて、マスターレーダからスレーブレーダに同期信号が出力され、スレーブレーダは、同期信号に同期して周波数を切り替えることで、各レーダが同期して周波数を切り替えることができる。また、マスターレーダは、周波数切り替え方向を決定する極性信号POLをスレーブレーダに供給する。極性信号は、周波数の切り替え周期でH/Lレベル変化する信号であって、極性信号のレベルに応じて周波数の切り替え方向が決定される。例えば、各スレーブレーダは、Hレベルの極性信号が供給されている間に、同期信号を受信すると、2周波数のうちの高い周波数に切り替わり、Lレベルの極性信号が供給されている間に、同期信号を受信すると、低周波数に切り替わる。FM−CWレーダにおける実施の形態例と同様に、極性信号及び同期信号は、外部から供給され、マスターレーダがそれを受信して、スレーブレーダに供給する構成であってもよいし、さらに、マスターレーダ及びスレーブレーダの区別なく、各レーダがそれぞれ外部からの極性信号及び同期信号を受信する構成であってもよい。

【0123】

上記本発明に好適なる複数の実施の形態を述べたが、本発明の思想を逸脱しない範囲内で各部の構成、制御、処理及びこれらの組合せの様々な変更が行えることは言うまでもない。

【0124】

(付記1)

基準信号と比較信号の位相を比較する位相比較器と、該位相比較器の位相誤差信号を積分するローパスフィルタと、該ローパスフィルタの後段に介在して本器の主制御を行う制御部と、該制御部出力の制御電圧に応じた周波数の信号を発生するVCO回路と、該VCO回路の出力信号を分周して前記比較信号を形成する可変分周器とからなるPLLループを備える位相同期発振器であって、前記制御部は、

PLLループを複数の周波数でロックさせて各ロック時の制御電圧を測定する制御電圧測定手段と、

前記測定された各制御電圧に基づき、前記各周波数を結ぶ区間の周波数変化を代表する変調感度を求めるリニアリティー校正手段とを備えたことを特徴とする位相同期発振器。

【0125】

(付記2)

前記PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を生成し、出力するVCO駆動手段を備えたことを特徴とする請求項1記載の位相同期発振器

(付記3)

VCO駆動手段は、VCO回路が中心周波数を出力するタイミングに同期してローパスフィルタの出力をサンプリングし、検出した位相誤差信号が所定範囲を超える場合は、該位相誤差信号を小さくする方向に制御電圧をオフセットすることを特徴とする請求項2記載の位相同期発振器。

【0126】

(付記4)

基準信号を分周する第1の分周器と、VCO回路の出力を分周して前記比較信号を形成する第2の分周器とを備え、

前記VCO駆動手段は、前記第1,第2の分周器のカウンタをVCO回路に加える信号周期の整数倍周期で定期的にリセットすると共に、前記VCO回路が中心周波数を出力するタイミングに同期してサンプリングしたローパスフィルタ出力の位相誤差信号が所定範囲を超える場合は、該位相誤差信号を小さくする方向に制御電圧をオフセットすることを特徴とする請求項2記載の位相同期発振器。

【0127】

(付記5)

基準信号を分周する第1の可変分周器と、VCO回路の出力を分周して前記比較信号を形成する第2の可変分周器とを備え、前記制御部は、前記第1,第2の可変分周器に所定の分周比を設定後、PLLループを形成して基準信号と比較信号間の位相引き込みを開始する際に、前記VCO回路に前記所定の分周比に対応する制御電圧を加えると共に、前記第1,第2の可変分周器のカウンタをリセットすることを特徴とする請求項1又は2記載の位相同期発振器。

【0128】

(付記6)

基準信号と比較信号の位相を比較する位相比較器と、該位相比較器の位相誤差信号を積分するローパスフィルタと、該ローパスフィルタの後段に介在して本器の主制御を行う制御部と、該制御部出力の制御電圧に応じた周波数の信号を発生するVCO回路と、前記VCO回路の出力信号を分周して前記比較信号を形成する可変分周器とからなるPLLループを備える位相同期発振器であって、前記制御部は、

PLLのロック周波数を所定間隔で変化させ、所定の周波数範囲をカバーする範囲につき各ロック時の制御電圧を測定する制御電圧測定手段と、

前記測定した制御電圧の変動範囲を複数区間に分割して、各区間を代表する変調感度を求めるリニアリティー校正手段と、

PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、VCO回路に前記所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための電圧信号を、前記ロック時の制御電圧と前記求めた各区間を代表する変調感度に基づき生成し、出力するVCO駆動手段とを備えたことを特徴とする位相同期発振器。

【0129】

(付記7)

付記1乃至6のいずれかに記載の位相同期発振器を有する複数のFM−CWレーダを備えて構成されるマルチレーダシステムにおいて、

各FM−CWレーダの前記制御部は、周期的に増減する制御電圧であって且つ前記制御電圧の増減方向及び増減速度が互いに一致するように所定の同期信号に同期した前記制御電圧を生成し、

各FM−CWレーダの前記VCO回路は、前記制御電圧の増減に応じて、中心周波数に対して所定の周波数偏移量分周波数が周期的に増減する信号であって且つ各信号の中心周波数は互いに異なりさらに当該信号の周波数の増減方向及び増減速度が互いに一致する前記信号を出力することを特徴とするマルチレーダシステム。

【0130】

(付記8)

付記7において、

各FM−CWレーダの前記制御部のうちの一つが前記同期信号を生成し、残りの前記制御部に出力することを特徴とするマルチレーダシステム。

【0131】

(付記9)

付記7において、

各FM−CWレーダの前記制御部のうちの一つが外部から供給される同期信号を受信し、残りの前記制御部に出力することを特徴とするマルチレーダシステム。

【0132】

(付記10)

付記7において、

各FM−CWレーダの前記制御部は、それぞれ外部から供給される同期信号を受信することを特徴とするマルチレーダシステム。

【0133】

(付記11)

付記7において、

前記基準信号は、各FM−CWレーダで共通であることを特徴とするマルチレーダシステム。

【0134】

(付記12)

付記7において、

前記同期信号を生成する同期信号生成手段を備え、当該同期信号生成手段が生成された同期信号が各制御部に供給されることを特徴とするマルチレーダシステム。

【0135】

(付記13)

周波数が周期的に増減する信号を生成して出力する複数のレーダを含んで構成されるマルチレーダシステムにおいて、

各レーダは、周期的に増減する周波数の上限値及び下限値が各レーダの信号毎に互いに異なり且つ当該上限値及び下限値になるタイミングが各信号毎に互いにほぼ一致するように所定の同期信号に同期して前記信号を生成することを特徴とするマルチレーダシステム。

【0136】

(付記14)

付記13において、

各レーダは、当該信号の周波数の増減方向及び増減速度が互いに一致するように所定の同期信号に同期して当該信号を生成することを特徴とするマルチレーダシステム。

【0137】

(付記15)

付記13において、

前記複数のレーダのうちの一つが前記同期信号を生成し、残りのレーダに出力することを特徴とするマルチレーダシステム。

【0138】

(付記16)

付記13において、

前記複数のレーダのうちの一つが外部から供給される同期信号を受信し、残りのレーダに出力することを特徴とするマルチレーダシステム。

【0139】

(付記17)

付記13において、

前記複数のレーダは、外部から供給される同期信号を受信することを特徴とするマルチレーダシステム。

【0140】

(付記18)

付記13において、

前記複数のレーダは複数の車両それぞれに搭載されており、第1の方向に進行している車両に搭載されるレーダは、第1の周波数帯域に含まれる周波数の信号を生成し、第1の方向と異なる第2の方向に進行している車両に搭載されるレーダは、第1の周波数帯域と異なる第2の周波数帯域に含まれる周波数の信号を生成することを特徴とするマルチレーダシステム。

【0141】

(付記19)

同期した複数の三角波を生成する三角波生成部と、

該複数の三角波のそれぞれを制御信号として、該それぞれの制御信号に応じて周波数変調された信号を出力する複数の電圧制御発信器と、

を備え、前記複数の電圧制御発信器は、互いに中心周波数が異なる、周波数変調された信号を出力するとともに、少なくとも1つの三角波に基いて生成される周波数変調された信号の下限周波数に対して、少なくとも他の1つの三角波に基いて生成される周波数変調された信号の上限周波数が大きくなるように出力周波数が設定された、

ことを特徴とするマルチレーダシステム。

【図面の簡単な説明】

【0142】

【図1】第1の実施の形態による位相同期発振器のブロック図である。

【図2】第1の実施の形態による制御電圧測定処理のフローチャートである。

【図3】第1の実施の形態による制御電圧測定動作のタイミングチャートである。

【図4】第1の実施の形態によるリニアリティー校正処理のフローチャートである。

【図5】第1の実施の形態によるリニアリティー校正動作のタイミングチャートである。

【図6】第1の実施の形態によるレーダ送信処理のフローチャートである。

【図7】第1の実施の形態によるレーダ送信動作のタイミングチャートである。

【図8】第1の実施の形態によるレーダ運用動作のタイミングチャートである。

【図9】第2の実施の形態による位相同期発振器のブロック図である。

【図10】第2の実施の形態による位相同期発振器の高速引き込み処理のフローチャートである。

【図11】第2の実施の形態による位相同期発振器の高速引き込み動作のタイミングチャートである。

【図12】第3の実施の形態による位相同期発振器のブロック図である。

【図13】第3の実施の形態による位相同期発振器の動作のタイミングチャートである。

【図14】第4の実施の形態による位相同期発振器を説明する図である。

【図15】第5の実施の形態による位相同期発振器を説明する図(1)である。

【図16】第5の実施の形態による位相同期発振器を説明する図(2)である。

【図17】第6の実施の形態による位相同期発振器を説明する図である。

【図18】実施の形態による故障検出動作を説明する図(1)である。

【図19】実施の形態による故障検出動作を説明する図(2)である。

【図20】第7の実施の形態によるマルチレーダシステムの概略構成例を示す図である。

【図21】各レーダの概略構成例を示す図である。

【図22】第7の実施の形態によるマルチレーダシステムにおける各レーダ100の発振部101の構成を示す図である。

【図23】同期信号の出力を説明する図である。

【図24】各発振部101において周波数変調された送信信号の周波数変化を示す図である。

【図25】周波数帯域76GHz〜77GHzに81チャネルが設定された例を示す図である。

【図26】第8の実施の形態によるマルチレーダシステムの概略構成例を示す図である。

【図27】第9の実施の形態によるマルチレーダシステムの各レーダにおける発振部101の構成例を示す図である。

【図28】第9の実施の形態におけるマルチレーダシステムにおける各レーダの送信信号の周波数割り当て例を示す図である。

【図29】第10の実施の形態によるマルチレーダシステムの各レーダにおける発振部101の構成例を示す図である。

【図30】車両の進行方向によってチャネルの周波数帯域を分割する適用例を示す図である。

【図31】車両の進行方向によってチャネルの周波数帯域を分割する別の適用例を示す図である。

【図32】2周波CWレーダによるマルチレーダシステムにおける周波数割り当て例を示す図である。

【図33】2周波CWレーダによるマルチレーダシステムの大規模な周波数配置例を示す図である。

【図34】2周波CWレーダによるマルチレーダシステムの概略構成例を示す図である。

【図35】従来技術を説明する図である。

【図36】従来におけるマルチレーダシステムにおける複数のレーダそれぞれの周波数割り当てを説明する図である。

【図37】送信信号の中心周波数や周波数偏移の変動を説明する図である。

【符号の説明】

【0143】

1 クロック発振器

2 位相比較部

3 ローパスフィルタ(LPF)

4 プロセッサユニット(PU)

5 電圧制御発振器(VCO)

6 RFスイッチ(SW)

7 周波数逓倍器

11,12 可変分周器

13 位相比較器(PD)

14 A/D変換器

15 CPU

16 D/A変換器

100 レーダ

101 発振部

102 ミキサ

110 受信機

111 同期信号制御部

【特許請求の範囲】

【請求項1】

周波数が周期的に増減する信号を生成して出力する複数のレーダを含むマルチレーダシステムにおいて、

各レーダは、周期的に増減する周波数の上限値及び下限値が各レーダの信号毎に互いに異なり且つ当該上限値及び下限値になるタイミングが各信号毎に互いにほぼ一致するように所定の同期信号に同期して前記信号を生成することを特徴とするマルチレーダシステム。

【請求項2】

請求項1において、

各レーダは、当該信号の周波数の増減方向及び増減速度が互いに一致するように所定の同期信号に同期して当該信号を生成することを特徴とするマルチレーダシステム。

【請求項3】

請求項1において、

前記複数のレーダのうちの一つが前記同期信号を生成し、残りのレーダに出力することを特徴とするマルチレーダシステム。

【請求項4】

請求項1において、

前記複数のレーダのうちの一つが外部から供給される同期信号を受信し、残りのレーダに出力することを特徴とするマルチレーダシステム。

【請求項5】

請求項1において、

前記複数のレーダは複数の車両それぞれに搭載されており、第1の方向に進行している車両に搭載されるレーダは、第1の周波数帯域に含まれる周波数の信号を生成し、第1の方向と異なる第2の方向に進行している車両に搭載されるレーダは、第1の周波数帯域と異なる第2の周波数帯域に含まれる周波数の信号を生成することを特徴とするマルチレーダシステム。

【請求項6】

同期した複数の三角波を生成する三角波生成部と、

該複数の三角波のそれぞれを制御信号として、該それぞれの制御信号に応じて周波数変調された信号を出力する複数の電圧制御発信器と、

を備え、前記複数の電圧制御発信器は、互いに中心周波数が異なる、周波数変調された信号を出力するとともに、少なくとも1つの三角波に基いて生成される周波数変調された信号の下限周波数に対して、少なくとも他の1つの三角波に基いて生成される周波数変調された信号の上限周波数が大きくなるように出力周波数が設定された、

ことを特徴とするマルチレーダシステム。

【請求項1】

周波数が周期的に増減する信号を生成して出力する複数のレーダを含むマルチレーダシステムにおいて、

各レーダは、周期的に増減する周波数の上限値及び下限値が各レーダの信号毎に互いに異なり且つ当該上限値及び下限値になるタイミングが各信号毎に互いにほぼ一致するように所定の同期信号に同期して前記信号を生成することを特徴とするマルチレーダシステム。

【請求項2】

請求項1において、

各レーダは、当該信号の周波数の増減方向及び増減速度が互いに一致するように所定の同期信号に同期して当該信号を生成することを特徴とするマルチレーダシステム。

【請求項3】

請求項1において、

前記複数のレーダのうちの一つが前記同期信号を生成し、残りのレーダに出力することを特徴とするマルチレーダシステム。

【請求項4】

請求項1において、

前記複数のレーダのうちの一つが外部から供給される同期信号を受信し、残りのレーダに出力することを特徴とするマルチレーダシステム。

【請求項5】

請求項1において、

前記複数のレーダは複数の車両それぞれに搭載されており、第1の方向に進行している車両に搭載されるレーダは、第1の周波数帯域に含まれる周波数の信号を生成し、第1の方向と異なる第2の方向に進行している車両に搭載されるレーダは、第1の周波数帯域と異なる第2の周波数帯域に含まれる周波数の信号を生成することを特徴とするマルチレーダシステム。

【請求項6】

同期した複数の三角波を生成する三角波生成部と、

該複数の三角波のそれぞれを制御信号として、該それぞれの制御信号に応じて周波数変調された信号を出力する複数の電圧制御発信器と、

を備え、前記複数の電圧制御発信器は、互いに中心周波数が異なる、周波数変調された信号を出力するとともに、少なくとも1つの三角波に基いて生成される周波数変調された信号の下限周波数に対して、少なくとも他の1つの三角波に基いて生成される周波数変調された信号の上限周波数が大きくなるように出力周波数が設定された、

ことを特徴とするマルチレーダシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【公開番号】特開2008−298736(P2008−298736A)

【公開日】平成20年12月11日(2008.12.11)

【国際特許分類】

【出願番号】特願2007−148188(P2007−148188)

【出願日】平成19年6月4日(2007.6.4)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成20年12月11日(2008.12.11)

【国際特許分類】

【出願日】平成19年6月4日(2007.6.4)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]