位相周波数比較回路

【課題】雑音特性及び高速動作を維持しながら、消費電力を削減することができる位相周波数比較回路を得ることを目的とする。

【解決手段】出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

【解決手段】出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、2つの入力信号の位相を比較する位相周波数比較回路に関するものである。

【背景技術】

【0002】

位相周波数比較回路は、PLL(Phase Locked Loop)を構成する主要回路の1つであり、その雑音特性は、PLLの出力信号の位相雑音特性に大きな影響を与える。

このため、低雑音のPLLにおいては、位相周波数比較回路の低雑音化が重要である。

特に、フリッカ雑音が大きいMOSトランジスタを用いて、位相周波数比較回路を構成する場合、バイポーラトランジスタを用いて構成する場合と比べて、PLLの出力信号の低離調周波数領域の位相雑音が劣化する。

【0003】

このため、低離調周波数領域の位相雑音を抑える必要がある場合には、バイポーラトランジスタを用いた論理回路(ECL(Emitter Coupled Logic)、もしくは、CML(Current Mode Logic))によって位相周波数比較回路が構成されることがある。

また、位相周波数比較回路に高速動作が要求される場合にも、バイポーラトランジスタを用いた論理回路によって位相周波数比較回路が構成されることがある。

【0004】

ここで、図6は以下の非特許文献1に開示されている位相周波数比較回路を示す構成図であり、この位相周波数比較回路はバイポーラトランジスタを用いている。

図6では、差動増幅回路で構成されている出力バッファ回路のみをトランジスタレベルの回路図で表しているが、位相周波数比較コア回路においても同様に、ECL回路(エミッタ結合論理回路)で構成されている。

【先行技術文献】

【非特許文献】

【0005】

【非特許文献1】Hittite社 位相周波数比較IC 439QS16G データシート

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の位相周波数比較回路は以上のように構成されているので、ECL回路が内部の定流源によって常に電流を流す必要がある。このため、入力信号の信号レベルが遷移するときだけ電流が流れるCMOSロジック回路と比べて、消費電力が大きくなってしまう課題があった。

【0007】

この発明は上記のような課題を解決するためになされたもので、雑音特性及び高速動作を維持しながら、消費電力を削減することができる位相周波数比較回路を得ることを目的とする。

【課題を解決するための手段】

【0008】

この発明に係る位相周波数比較回路は、第1の入力信号の立ち上がりエッジを検出するとともに、第2の入力信号の立ち上がりエッジを検出し、第1の入力信号の立ち上がりエッジの検出タイミングが第2の入力信号の立ち上がりエッジの検出タイミングより早ければ、第1の入力信号の立ち上がりエッジを検出してから第2の入力信号の立ち上がりエッジを検出するまでの間、第1のエッジ検出信号を出力し、第2の入力信号の立ち上がりエッジの検出タイミングが第1の入力信号の立ち上がりエッジの検出タイミングより早ければ、第2の入力信号の立ち上がりエッジを検出してから第1の入力信号の立ち上がりエッジを検出するまでの間、第2のエッジ検出信号を出力する位相比較手段と、第1の入力信号又は第2の入力信号における立ち上がりエッジに同期して、第1のエッジ検出信号及び第2のエッジ検出信号よりもパルス幅が広い電流制御信号を出力する電流制御信号出力手段とを設け、論理信号出力手段が、電流制御信号出力手段から電流制御信号が出力されている期間中、位相比較手段から第1のエッジ検出信号が出力された場合、第1の論理信号を出力し、電流制御信号出力手段から電流制御信号が出力されている期間中、位相比較手段から第2のエッジ検出信号が出力された場合、第2の論理信号を出力するようにしたものである。

【発明の効果】

【0009】

この発明によれば、第1の入力信号の立ち上がりエッジを検出するとともに、第2の入力信号の立ち上がりエッジを検出し、第1の入力信号の立ち上がりエッジの検出タイミングが第2の入力信号の立ち上がりエッジの検出タイミングより早ければ、第1の入力信号の立ち上がりエッジを検出してから第2の入力信号の立ち上がりエッジを検出するまでの間、第1のエッジ検出信号を出力し、第2の入力信号の立ち上がりエッジの検出タイミングが第1の入力信号の立ち上がりエッジの検出タイミングより早ければ、第2の入力信号の立ち上がりエッジを検出してから第1の入力信号の立ち上がりエッジを検出するまでの間、第2のエッジ検出信号を出力する位相比較手段と、第1の入力信号又は第2の入力信号における立ち上がりエッジに同期して、第1のエッジ検出信号及び第2のエッジ検出信号よりもパルス幅が広い電流制御信号を出力する電流制御信号出力手段とを設け、論理信号出力手段が、電流制御信号出力手段から電流制御信号が出力されている期間中、位相比較手段から第1のエッジ検出信号が出力された場合、第1の論理信号を出力し、電流制御信号出力手段から電流制御信号が出力されている期間中、位相比較手段から第2のエッジ検出信号が出力された場合、第2の論理信号を出力するように構成したので、雑音特性及び高速動作を維持しながら、消費電力を削減することができる効果がある。

【図面の簡単な説明】

【0010】

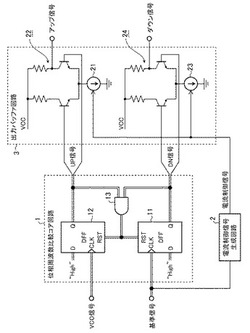

【図1】この発明の実施の形態1による位相周波数比較回路を示す構成図である。

【図2】図1の位相周波数比較回路における各種信号のタイミングを示すタイミングチャートである。

【図3】図1の位相周波数比較回路における各種信号のタイミングを示すタイミングチャートである。

【図4】この発明の実施の形態3による位相周波数比較回路を示す構成図である。

【図5】この発明の実施の形態4による位相周波数比較回路を示す構成図である。

【図6】非特許文献1に開示されている位相周波数比較回路を示す構成図である。

【発明を実施するための形態】

【0011】

実施の形態1.

図1はこの発明の実施の形態1による位相周波数比較回路を示す構成図である。

図1において、位相周波数比較コア回路1はD−フリップフロップ11,12及び論理回路13から構成されており、基準信号(第1の入力信号)の立ち上がりエッジを検出するとともに、電圧制御発振器から出力されるVCO信号(第2の入力信号)の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早ければ、その基準信号の立ち上がりエッジを検出してからVCO信号の立ち上がりエッジを検出するまでの間、UP信号(第1のエッジ検出信号)を出力し、そのVCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早ければ、そのVCO信号の立ち上がりエッジを検出してから基準信号の立ち上がりエッジを検出するまでの間、DN信号(第2のエッジ検出信号)を出力する回路である。なお、位相周波数比較コア回路1は位相比較手段を構成している。

【0012】

電流制御信号生成回路2は基準信号における立ち上がりエッジ(または、VCO信号における立ち上がりエッジ)に同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3に出力する回路である。なお、電流制御信号生成回路2は電流制御信号出力手段を構成している。

【0013】

出力バッファ回路3は電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号(第1の論理信号)を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号(第2の論理信号)を出力する回路である。なお、出力バッファ回路3は論理信号出力手段を構成している。

【0014】

出力バッファ回路3の定電流源21は電流制御信号生成回路2から電流制御信号が出力されている期間中、電流を出力する電流源である。なお、定電流源21は第1の定電流源を構成している。

差動増幅回路22はバイポーラトランジスタと負荷抵抗(抵抗値Rの抵抗)からなる直列回路が2つ並列に接続されて構成されており、位相周波数比較コア回路1からUP信号が出力された場合、定電流源21の出力電流によってアップ信号を出力する回路である。なお、差動増幅回路22は第1の差動増幅回路を構成している。

【0015】

定電流源23は電流制御信号生成回路2から電流制御信号が出力されている期間中、電流を出力する電流源である。なお、定電流源23は第2の定電流源を構成している。

差動増幅回路24はバイポーラトランジスタと負荷抵抗(抵抗値Rの抵抗)からなる直列回路が2つ並列に接続されて構成されており、位相周波数比較コア回路1からDN信号が出力された場合、定電流源23の出力電流によってダウン信号を出力する回路である。なお、差動増幅回路24は第2の差動増幅回路を構成している。

【0016】

次に動作について説明する。

図2は図1の位相周波数比較回路における各種信号のタイミングを示すタイミングチャートである。

位相周波数比較コア回路1は、基準信号の立ち上がりエッジを検出するとともに、電圧制御発振器から出力されるVCO信号の立ち上がりエッジを検出する。

図2のタイミングチャートは、PLLの位相同期が確立している状態を示しており、基準信号とVCO信号の立ち上がりエッジは概ね揃っているが、VCO信号のジッタによって若干の揺らぎが生じているために、両者の立ち上がりエッジがずれている。

位相周波数比較コア回路1は、この揺らぎを含めて、基準信号とVCO信号の立ち上がりエッジを検出している。

【0017】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早ければ、その基準信号の立ち上がりエッジを検出してからVCO信号の立ち上がりエッジを検出するまでの間、UP信号を出力バッファ回路2の差動増幅回路22に出力する。

図2の例では、左から1番目及び2番目の信号において、基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早いため、UP信号を出力バッファ回路2の差動増幅回路22に出力している。

【0018】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち上がりエッジを検出し、そのVCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早ければ、そのVCO信号の立ち上がりエッジを検出してから基準信号の立ち上がりエッジを検出するまでの間、DN信号を出力バッファ回路2の差動増幅回路24に出力する。

図2の例では、左から3番目及び4番目の信号において、VCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早いため、DN信号を出力バッファ回路2の差動増幅回路24に出力している。

【0019】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングとVCO信号の立ち上がりエッジの検出タイミングが一致していれば、UP信号とDN信号の出力を行わない。

図2の例では、左から5番目の信号において、基準信号の立ち上がりエッジの検出タイミングとVCO信号の立ち上がりエッジの検出タイミングが一致しているため、UP信号とDN信号の出力を行っていない。

【0020】

電流制御信号生成回路2は、基準信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3の定電流源21,23に出力する。

即ち、電流制御信号生成回路2は、予め基準信号の周期を認識しており、基準信号の立ち上がりエッジを検出する毎に、当該立ち上がりエッジの検出タイミングと基準信号の周期を考慮して、電流制御信号の出力開始タイミングが、次の立ち上がりエッジの検出タイミングより時間tcだけ前になり、その電流制御信号の出力終了タイミングが、次の立ち上がりエッジの検出タイミングより時間tcだけ後になるようにする。

【0021】

なお、tcはUP信号及びDN信号におけるパルス幅の最大値より大きい値に設定される。

ここでは、電流制御信号生成回路2が、基準信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成するものを示したが、VCO信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3の定電流源21,23に出力するようにしてもよい。

【0022】

出力バッファ回路3は、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

即ち、出力バッファ回路3の差動増幅回路22には、電源電圧VCCが印加されており、電流制御信号生成回路2から電流制御信号が出力されている期間中(電流制御信号の信号レベルがHである期間中)、定電流源21から電流値I0の電流Itailが出力される。

このため、位相周波数比較コア回路1からUP信号が出力されることで、差動増幅回路22の2つのバイポーラトランジスタがオンになると、差動増幅回路22から電圧値がVCC−R×I0のアップ信号が出力される。

なお、電流制御信号生成回路2から電流制御信号が出力されていない期間中(電流制御信号の信号レベルがLである期間中)は、定電流源21から出力される電流Itailの電流値が0になり、差動増幅回路22から電圧値がVCCの信号が出力される。

【0023】

また、出力バッファ回路3の差動増幅回路24には、電源電圧VCCが印加されており、電流制御信号生成回路2から電流制御信号が出力されている期間中(電流制御信号の信号レベルがHである期間中)、定電流源23から電流値I0の電流Itailが出力される。

このため、位相周波数比較コア回路1からDN信号が出力されることで、差動増幅回路24の2つのバイポーラトランジスタがオンになると、差動増幅回路24から電圧値がVCC−R×I0のダウン信号が出力される。

なお、電流制御信号生成回路2から電流制御信号が出力されていない期間中(電流制御信号の信号レベルがLである期間中)は、定電流源23から出力される電流Itailの電流値が0になり、差動増幅回路24から電圧値がVCCの信号が出力される。

【0024】

以上で明らかなように、この実施の形態1によれば、基準信号の立ち上がりエッジを検出するとともに、VCO信号の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早ければ、その基準信号の立ち上がりエッジを検出してからVCO信号の立ち上がりエッジを検出するまでの間、UP信号を出力し、そのVCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早ければ、そのVCO信号の立ち上がりエッジを検出してから基準信号の立ち上がりエッジを検出するまでの間、DN信号を出力する位相周波数比較コア回路1と、基準信号における立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力する電流制御信号生成回路2とを設け、出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力するように構成したので、雑音特性及び高速動作を維持しながら、消費電力を削減することができる効果を奏する。

即ち、出力バッファ回路2の出力信号の波形に影響を与えることなく、出力バッファ回路2の定電流源21,23の電流値を間欠的にON/OFFすることが可能となり、消費電力を削減することができる。

【0025】

この実施の形態1では、差動増幅回路22,24がバイポーラトランジスタを用いて構成されているものを示したが、バイポーラトランジスタに限るものではなく、例えば、FETなどの他のトランジスタを用いて、差動増幅回路22,24を構成してもよい。

【0026】

実施の形態2.

上記実施の形態1では、位相周波数比較コア回路1が、基準信号及びVCO信号の立ち上がりエッジを検出するものを示したが、位相周波数比較コア回路1が、基準信号の立ち下がりエッジを検出するとともに、VCO信号の立ち下がりエッジを検出し、その基準信号の立ち下がりエッジの検出タイミングがVCO信号の立ち下がりエッジの検出タイミングより早ければ、その基準信号の立ち下がりエッジを検出してからVCO信号の立ち下がりエッジを検出するまでの間、UP信号を出力し、そのVCO信号の立ち下がりエッジの検出タイミングが基準信号の立ち下がりエッジの検出タイミングより早ければ、そのVCO信号の立ち下がりエッジを検出してから基準信号の立ち下がりエッジを検出するまでの間、DN信号を出力するようにしてもよい。

この場合、電流制御信号生成回路2は、基準信号における立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力するようにする。

図3は図1の位相周波数比較回路における各種信号のタイミングを示すタイミングチャートである。

【0027】

以下、図3を参照しながら、位相周波数比較回路の動作を具体的に説明する。

位相周波数比較コア回路1は、基準信号の立ち下がりエッジを検出するとともに、電圧制御発振器から出力されるVCO信号の立ち下がりエッジを検出する。

図3のタイミングチャートは、PLLの位相同期が確立している状態を示しており、基準信号とVCO信号の立ち下がりエッジは概ね揃っているが、VCO信号のジッタによって若干の揺らぎが生じているために、両者の立ち下がりエッジがずれている。

位相周波数比較コア回路1は、この揺らぎを含めて、基準信号とVCO信号の立ち下がりエッジを検出している。

【0028】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち下がりエッジを検出し、その基準信号の立ち下がりエッジの検出タイミングがVCO信号の立ち下がりエッジの検出タイミングより早ければ、その基準信号の立ち下がりエッジを検出してからVCO信号の立ち下がりエッジを検出するまでの間、UP信号を出力バッファ回路2の差動増幅回路22に出力する。

図3の例では、左から1番目及び2番目の信号において、基準信号の立ち下がりエッジの検出タイミングがVCO信号の立ち下がりエッジの検出タイミングより早いため、UP信号を出力バッファ回路2の差動増幅回路22に出力している。

【0029】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち下がりエッジを検出し、そのVCO信号の立ち下がりエッジの検出タイミングが基準信号の立ち下がりエッジの検出タイミングより早ければ、そのVCO信号の立ち下がりエッジを検出してから基準信号の立ち下がりエッジを検出するまでの間、DN信号を出力バッファ回路2の差動増幅回路24に出力する。

図3の例では、左から3番目及び4番目の信号において、VCO信号の立ち下がりエッジの検出タイミングが基準信号の立ち下がりエッジの検出タイミングより早いため、DN信号を出力バッファ回路2の差動増幅回路24に出力している。

【0030】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち下がりエッジを検出し、その基準信号の立ち下がりエッジの検出タイミングとVCO信号の立ち下がりエッジの検出タイミングが一致していれば、UP信号とDN信号の出力を行わない。

図3の例では、左から5番目の信号において、基準信号の立ち下がりエッジの検出タイミングとVCO信号の立ち下がりエッジの検出タイミングが一致しているため、UP信号とDN信号の出力を行っていない。

【0031】

電流制御信号生成回路2は、基準信号の立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3の定電流源21,23に出力する。

即ち、電流制御信号生成回路2は、予め基準信号の周期を認識しており、基準信号の立ち下がりエッジを検出する毎に、当該立ち下がりエッジの検出タイミングと基準信号の周期を考慮して、電流制御信号の出力開始タイミングが、次の立ち下がりエッジの検出タイミングより時間tcだけ前になり、その電流制御信号の出力終了タイミングが、次の立ち下がりエッジの検出タイミングより時間tcだけ後になるようにする。

【0032】

なお、tcはUP信号及びDN信号におけるパルス幅の最大値より大きい値に設定される。

ここでは、電流制御信号生成回路2が、基準信号の立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成するものを示したが、VCO信号の立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3の定電流源21,23に出力するようにしてもよい。

【0033】

出力バッファ回路3は、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

即ち、出力バッファ回路3の差動増幅回路22には、電源電圧VCCが印加されており、電流制御信号生成回路2から電流制御信号が出力されている期間中(電流制御信号の信号レベルがHである期間中)、定電流源21から電流値I0の電流Itailが出力される。

このため、位相周波数比較コア回路1からUP信号が出力されることで、差動増幅回路22の2つのバイポーラトランジスタがオンになると、差動増幅回路22から電圧値がVCC−R×I0のアップ信号が出力される。

なお、電流制御信号生成回路2から電流制御信号が出力されていない期間中(電流制御信号の信号レベルがLである期間中)は、定電流源21から出力される電流Itailの電流値が0になり、差動増幅回路22から電圧値がVCCの信号が出力される。

【0034】

また、出力バッファ回路3の差動増幅回路24には、電源電圧VCCが印加されており、電流制御信号生成回路2から電流制御信号が出力されている期間中(電流制御信号の信号レベルがHである期間中)、定電流源23から電流値I0の電流Itailが出力される。

このため、位相周波数比較コア回路1からDN信号が出力されることで、差動増幅回路24の2つのバイポーラトランジスタがオンになると、差動増幅回路24から電圧値がVCC−R×I0のダウン信号が出力される。

なお、電流制御信号生成回路2から電流制御信号が出力されていない期間中(電流制御信号の信号レベルがLである期間中)は、定電流源23から出力される電流Itailの電流値が0になり、差動増幅回路24から電圧値がVCCの信号が出力される。

【0035】

以上で明らかなように、この実施の形態2によれば、基準信号の立ち下がりエッジを検出するとともに、VCO信号の立ち下がりエッジを検出し、その基準信号の立ち下がりエッジの検出タイミングがVCO信号の立ち下がりエッジの検出タイミングより早ければ、その基準信号の立ち下がりエッジを検出してからVCO信号の立ち下がりエッジを検出するまでの間、UP信号を出力し、そのVCO信号の立ち下がりエッジの検出タイミングが基準信号の立ち下がりエッジの検出タイミングより早ければ、そのVCO信号の立ち下がりエッジを検出してから基準信号の立ち下がりエッジを検出するまでの間、DN信号を出力する位相周波数比較コア回路1と、基準信号における立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力する電流制御信号生成回路2とを設け、出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力するように構成したので、雑音特性及び高速動作を維持しながら、消費電力を削減することができる効果を奏する。

即ち、出力バッファ回路2の出力信号の波形に影響を与えることなく、出力バッファ回路2の定電流源21,23の電流値を間欠的にON/OFFすることが可能となり、消費電力を削減することができる。

【0036】

この実施の形態2では、差動増幅回路22,24がバイポーラトランジスタを用いて構成されているものを示したが、バイポーラトランジスタに限るものではなく、例えば、FETなどの他のトランジスタを用いて、差動増幅回路22,24を構成してもよい。

【0037】

この実施の形態2では、位相周波数比較コア回路1が、基準信号及びVCO信号の立ち下がりエッジを検出するものを示したが、基準信号及びVCO信号の立ち上がりエッジと立ち下がりエッジの双方を検出するようにしてもよい。

この場合、電流制御信号生成回路2は、基準信号における立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力するとともに、立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力するようにする。

【0038】

実施の形態3.

上記実施の形態1,2では、電流制御信号生成回路2から出力される電流制御信号によって、定電流源21,23から電流Itailが出力される期間を制限することで、消費電力を削減するものを示したが、電流制御信号生成回路2から出力される電流制御信号によって、更に、位相周波数比較コア回路1におけるUP信号とDN信号の出力処理等に制限を加えることで、消費電力を削減するようにしてもよい。

【0039】

図4はこの発明の実施の形態3による位相周波数比較回路を示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

位相周波数比較コア回路4はD−フリップフロップ31,32及び論理回路33から構成されており、図1の位相周波数比較コア回路1と同様に、基準信号の立ち上がりエッジを検出するとともに、電圧制御発振器から出力されるVCO信号の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早ければ、その基準信号の立ち上がりエッジを検出してからVCO信号の立ち上がりエッジを検出するまでの間、UP信号を出力し、そのVCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早ければ、そのVCO信号の立ち上がりエッジを検出してから基準信号の立ち上がりエッジを検出するまでの間、DN信号を出力する回路である。

ただし、位相周波数比較コア回路4は、図1の位相周波数比較コア回路1と異なり、電流制御信号生成回路5から電流制御信号が出力されている期間中は、基準信号及びVCO信号の立ち上がりエッジの検出処理や、UP信号とDN信号の出力処理を実施しない。

なお、位相周波数比較コア回路4は位相比較手段を構成している。

【0040】

電流制御信号生成回路5は基準信号における立ち上がりエッジ(または、VCO信号における立ち上がりエッジ)に同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を位相周波数比較コア回路4及び出力バッファ回路3に出力する回路である。なお、電流制御信号生成回路5は電流制御信号出力手段を構成している。

【0041】

次に動作について説明する。

電流制御信号生成回路5は、図1の電流制御信号生成回路2と同様に、基準信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成する。

ただし、電流制御信号生成回路5は、図1の電流制御信号生成回路2と異なり、その電流制御信号を出力バッファ回路3に出力するだけでなく、位相周波数比較コア回路4にも出力する。

ここでは、電流制御信号生成回路5が、基準信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成するものを示したが、VCO信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3及び位相周波数比較コア回路4に出力するようにしてもよい。

【0042】

位相周波数比較コア回路4は、電流制御信号生成回路5から電流制御信号が出力されている期間中は、図1の位相周波数比較コア回路1と同様に、基準信号及びVCO信号の立ち上がりエッジの検出処理や、UP信号とDN信号の出力処理を実施する。

一方、電流制御信号生成回路5から電流制御信号が出力されていない期間中は、基準信号及びVCO信号の立ち上がりエッジの検出処理や、UP信号とDN信号の出力処理を実施しない。

【0043】

これにより、出力バッファ回路3だけでなく、位相周波数比較コア回路4の消費電力も削除することができる。

位相周波数比較コア回路4で発生する雑音は、信号の立ち上がり、もしくは、立ち上がり時の動作のみに依存するため、このような電流制御を行うことで、出力雑音が劣化することはない。

ただし、D−フリップフロップ31,32のような論理状態を記憶する回路が位相周波数比較コア回路4に含まれている場合、D−フリップフロップ31,32に供給する電流値を0にすると正常な動作ができなくなるため、電流制御信号が出力されていない期間中でも、D−フリップフロップ31,32に供給する電流値を0にせず、論理状態を保持できる程度の最低限の電流を供給する必要がある。

【0044】

以上で明らかなように、この実施の形態3によれば、電流制御信号生成回路5から電流制御信号が出力されている期間中に限り、位相周波数比較コア回路4が、基準信号及びVCO信号の立ち上がりエッジの検出処理や、UP信号とDN信号の出力処理を実施するように構成したので、上記実施の形態1,2よりも更に、消費電力を削減することができる効果を奏する。

【0045】

この実施の形態3では、位相周波数比較コア回路4が、基準信号及びVCO信号の立ち上がりエッジを検出するものを示したが、基準信号及びVCO信号の立下りエッジを検出するようにしてもよい。

この場合、電流制御信号生成回路5は、基準信号における立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力するようにする。

【0046】

実施の形態4.

図5はこの発明の実施の形態4による位相周波数比較回路を示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

ロック検出回路6は基準信号とVCO信号の位相同期が確立しているか否かを判定し、位相同期が確立していれば、ロック検出信号を論理回路7に出力する処理を実施する。

論理回路7はロック検出回路6からロック検出信号が出力されている期間中は、電流制御信号生成回路2から出力された電流制御信号を出力バッファ回路3に出力し、ロック検出回路6からロック検出信号が出力されていない期間中は、信号レベルがHレベルの信号を連続的に出力バッファ回路3に出力する処理を実施する。

なお、電流制御信号生成回路2、ロック検出回路6及び論理回路7から電流制御信号出力手段が構成されている。

【0047】

次に動作について説明する。

上記実施の形態1〜3の位相周波数比較回路の場合、PLLの位相同期時の動作には問題が生じないが、位相同期確立までの過渡状態が通常のPLLと異なる。

即ち、アップ信号とダウン信号のパルス幅が2×tcに制限されるため、基準信号とVCO信号の立ち上がりエッジ(または、立ち下がりエッジ)が大きく異なる場合、基準信号とVCO信号における立ち上がりエッジの検出タイミングの時間差を正確に出力することができない。

これにより、例えば、PLLの出力周波数を、ある値から別の値に切り替える場合、切り替え時間が長くなることがある。

【0048】

この実施の形態4では、切り替え時間が長くなることを防止するために、ロック検出回路6と論理回路7を追加している。

ロック検出回路6は、基準信号とVCO信号の位相同期が確立しているか否かを判定し、位相同期が確立していれば、ロック検出信号を論理回路7に出力する。

論理回路7は、ロック検出回路6からロック検出信号が出力されている期間中は、電流制御信号生成回路2から出力された電流制御信号を出力バッファ回路3に出力する。

したがって、基準信号とVCO信号の位相同期が確立していれば、上記実施の形態1〜3と同様に、電流制御信号生成回路2から出力された電流制御信号が出力バッファ回路3に出力されるため、出力バッファ回路3では、上記実施の形態1〜3と同様に、アップ信号とダウン信号の出力処理が行われ、消費電力が削減される。

【0049】

論理回路7は、ロック検出回路6からロック検出信号が出力されていない期間中は、信号レベルがHレベルの信号を連続的に出力バッファ回路3に出力する。

出力バッファ回路3は、ロック検出回路6からロック検出信号が出力されていない期間中(位相同期が確立していない期間中)、論理回路7から信号レベルがHレベルの信号を連続的に受けることで(電流制御信号を連続的に受けることに相当する)、定電流源21,23から電流値I0の電流Itailが常時出力される。

この場合、定電流源21,23の消費電力が増えるが、PLLの出力周波数を、ある値から別の値に切り替える場合の切り替え時間が長くなることを防止することができる。

【0050】

なお、本願発明はその発明の範囲内において、各実施の形態の自由な組み合わせ、あるいは各実施の形態の任意の構成要素の変形、もしくは各実施の形態において任意の構成要素の省略が可能である。

【符号の説明】

【0051】

1 位相周波数比較コア回路(位相比較手段)、2 電流制御信号生成回路(電流制御信号出力手段)、3 出力バッファ回路(論理信号出力手段)、4 位相周波数比較コア回路(位相比較手段)、5 電流制御信号生成回路(電流制御信号出力手段)、6 ロック検出回路(電流制御信号出力手段)、7 論理回路(電流制御信号出力手段)、11,12,31,32 D−フリップフロップ、13,33 論理回路、21 定電流源(第1の定電流源)、22 差動増幅回路(第1の差動増幅回路)、23 定電流源(第2の定電流源)、24 差動増幅回路(第2の差動増幅回路)。

【技術分野】

【0001】

この発明は、2つの入力信号の位相を比較する位相周波数比較回路に関するものである。

【背景技術】

【0002】

位相周波数比較回路は、PLL(Phase Locked Loop)を構成する主要回路の1つであり、その雑音特性は、PLLの出力信号の位相雑音特性に大きな影響を与える。

このため、低雑音のPLLにおいては、位相周波数比較回路の低雑音化が重要である。

特に、フリッカ雑音が大きいMOSトランジスタを用いて、位相周波数比較回路を構成する場合、バイポーラトランジスタを用いて構成する場合と比べて、PLLの出力信号の低離調周波数領域の位相雑音が劣化する。

【0003】

このため、低離調周波数領域の位相雑音を抑える必要がある場合には、バイポーラトランジスタを用いた論理回路(ECL(Emitter Coupled Logic)、もしくは、CML(Current Mode Logic))によって位相周波数比較回路が構成されることがある。

また、位相周波数比較回路に高速動作が要求される場合にも、バイポーラトランジスタを用いた論理回路によって位相周波数比較回路が構成されることがある。

【0004】

ここで、図6は以下の非特許文献1に開示されている位相周波数比較回路を示す構成図であり、この位相周波数比較回路はバイポーラトランジスタを用いている。

図6では、差動増幅回路で構成されている出力バッファ回路のみをトランジスタレベルの回路図で表しているが、位相周波数比較コア回路においても同様に、ECL回路(エミッタ結合論理回路)で構成されている。

【先行技術文献】

【非特許文献】

【0005】

【非特許文献1】Hittite社 位相周波数比較IC 439QS16G データシート

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の位相周波数比較回路は以上のように構成されているので、ECL回路が内部の定流源によって常に電流を流す必要がある。このため、入力信号の信号レベルが遷移するときだけ電流が流れるCMOSロジック回路と比べて、消費電力が大きくなってしまう課題があった。

【0007】

この発明は上記のような課題を解決するためになされたもので、雑音特性及び高速動作を維持しながら、消費電力を削減することができる位相周波数比較回路を得ることを目的とする。

【課題を解決するための手段】

【0008】

この発明に係る位相周波数比較回路は、第1の入力信号の立ち上がりエッジを検出するとともに、第2の入力信号の立ち上がりエッジを検出し、第1の入力信号の立ち上がりエッジの検出タイミングが第2の入力信号の立ち上がりエッジの検出タイミングより早ければ、第1の入力信号の立ち上がりエッジを検出してから第2の入力信号の立ち上がりエッジを検出するまでの間、第1のエッジ検出信号を出力し、第2の入力信号の立ち上がりエッジの検出タイミングが第1の入力信号の立ち上がりエッジの検出タイミングより早ければ、第2の入力信号の立ち上がりエッジを検出してから第1の入力信号の立ち上がりエッジを検出するまでの間、第2のエッジ検出信号を出力する位相比較手段と、第1の入力信号又は第2の入力信号における立ち上がりエッジに同期して、第1のエッジ検出信号及び第2のエッジ検出信号よりもパルス幅が広い電流制御信号を出力する電流制御信号出力手段とを設け、論理信号出力手段が、電流制御信号出力手段から電流制御信号が出力されている期間中、位相比較手段から第1のエッジ検出信号が出力された場合、第1の論理信号を出力し、電流制御信号出力手段から電流制御信号が出力されている期間中、位相比較手段から第2のエッジ検出信号が出力された場合、第2の論理信号を出力するようにしたものである。

【発明の効果】

【0009】

この発明によれば、第1の入力信号の立ち上がりエッジを検出するとともに、第2の入力信号の立ち上がりエッジを検出し、第1の入力信号の立ち上がりエッジの検出タイミングが第2の入力信号の立ち上がりエッジの検出タイミングより早ければ、第1の入力信号の立ち上がりエッジを検出してから第2の入力信号の立ち上がりエッジを検出するまでの間、第1のエッジ検出信号を出力し、第2の入力信号の立ち上がりエッジの検出タイミングが第1の入力信号の立ち上がりエッジの検出タイミングより早ければ、第2の入力信号の立ち上がりエッジを検出してから第1の入力信号の立ち上がりエッジを検出するまでの間、第2のエッジ検出信号を出力する位相比較手段と、第1の入力信号又は第2の入力信号における立ち上がりエッジに同期して、第1のエッジ検出信号及び第2のエッジ検出信号よりもパルス幅が広い電流制御信号を出力する電流制御信号出力手段とを設け、論理信号出力手段が、電流制御信号出力手段から電流制御信号が出力されている期間中、位相比較手段から第1のエッジ検出信号が出力された場合、第1の論理信号を出力し、電流制御信号出力手段から電流制御信号が出力されている期間中、位相比較手段から第2のエッジ検出信号が出力された場合、第2の論理信号を出力するように構成したので、雑音特性及び高速動作を維持しながら、消費電力を削減することができる効果がある。

【図面の簡単な説明】

【0010】

【図1】この発明の実施の形態1による位相周波数比較回路を示す構成図である。

【図2】図1の位相周波数比較回路における各種信号のタイミングを示すタイミングチャートである。

【図3】図1の位相周波数比較回路における各種信号のタイミングを示すタイミングチャートである。

【図4】この発明の実施の形態3による位相周波数比較回路を示す構成図である。

【図5】この発明の実施の形態4による位相周波数比較回路を示す構成図である。

【図6】非特許文献1に開示されている位相周波数比較回路を示す構成図である。

【発明を実施するための形態】

【0011】

実施の形態1.

図1はこの発明の実施の形態1による位相周波数比較回路を示す構成図である。

図1において、位相周波数比較コア回路1はD−フリップフロップ11,12及び論理回路13から構成されており、基準信号(第1の入力信号)の立ち上がりエッジを検出するとともに、電圧制御発振器から出力されるVCO信号(第2の入力信号)の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早ければ、その基準信号の立ち上がりエッジを検出してからVCO信号の立ち上がりエッジを検出するまでの間、UP信号(第1のエッジ検出信号)を出力し、そのVCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早ければ、そのVCO信号の立ち上がりエッジを検出してから基準信号の立ち上がりエッジを検出するまでの間、DN信号(第2のエッジ検出信号)を出力する回路である。なお、位相周波数比較コア回路1は位相比較手段を構成している。

【0012】

電流制御信号生成回路2は基準信号における立ち上がりエッジ(または、VCO信号における立ち上がりエッジ)に同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3に出力する回路である。なお、電流制御信号生成回路2は電流制御信号出力手段を構成している。

【0013】

出力バッファ回路3は電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号(第1の論理信号)を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号(第2の論理信号)を出力する回路である。なお、出力バッファ回路3は論理信号出力手段を構成している。

【0014】

出力バッファ回路3の定電流源21は電流制御信号生成回路2から電流制御信号が出力されている期間中、電流を出力する電流源である。なお、定電流源21は第1の定電流源を構成している。

差動増幅回路22はバイポーラトランジスタと負荷抵抗(抵抗値Rの抵抗)からなる直列回路が2つ並列に接続されて構成されており、位相周波数比較コア回路1からUP信号が出力された場合、定電流源21の出力電流によってアップ信号を出力する回路である。なお、差動増幅回路22は第1の差動増幅回路を構成している。

【0015】

定電流源23は電流制御信号生成回路2から電流制御信号が出力されている期間中、電流を出力する電流源である。なお、定電流源23は第2の定電流源を構成している。

差動増幅回路24はバイポーラトランジスタと負荷抵抗(抵抗値Rの抵抗)からなる直列回路が2つ並列に接続されて構成されており、位相周波数比較コア回路1からDN信号が出力された場合、定電流源23の出力電流によってダウン信号を出力する回路である。なお、差動増幅回路24は第2の差動増幅回路を構成している。

【0016】

次に動作について説明する。

図2は図1の位相周波数比較回路における各種信号のタイミングを示すタイミングチャートである。

位相周波数比較コア回路1は、基準信号の立ち上がりエッジを検出するとともに、電圧制御発振器から出力されるVCO信号の立ち上がりエッジを検出する。

図2のタイミングチャートは、PLLの位相同期が確立している状態を示しており、基準信号とVCO信号の立ち上がりエッジは概ね揃っているが、VCO信号のジッタによって若干の揺らぎが生じているために、両者の立ち上がりエッジがずれている。

位相周波数比較コア回路1は、この揺らぎを含めて、基準信号とVCO信号の立ち上がりエッジを検出している。

【0017】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早ければ、その基準信号の立ち上がりエッジを検出してからVCO信号の立ち上がりエッジを検出するまでの間、UP信号を出力バッファ回路2の差動増幅回路22に出力する。

図2の例では、左から1番目及び2番目の信号において、基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早いため、UP信号を出力バッファ回路2の差動増幅回路22に出力している。

【0018】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち上がりエッジを検出し、そのVCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早ければ、そのVCO信号の立ち上がりエッジを検出してから基準信号の立ち上がりエッジを検出するまでの間、DN信号を出力バッファ回路2の差動増幅回路24に出力する。

図2の例では、左から3番目及び4番目の信号において、VCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早いため、DN信号を出力バッファ回路2の差動増幅回路24に出力している。

【0019】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングとVCO信号の立ち上がりエッジの検出タイミングが一致していれば、UP信号とDN信号の出力を行わない。

図2の例では、左から5番目の信号において、基準信号の立ち上がりエッジの検出タイミングとVCO信号の立ち上がりエッジの検出タイミングが一致しているため、UP信号とDN信号の出力を行っていない。

【0020】

電流制御信号生成回路2は、基準信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3の定電流源21,23に出力する。

即ち、電流制御信号生成回路2は、予め基準信号の周期を認識しており、基準信号の立ち上がりエッジを検出する毎に、当該立ち上がりエッジの検出タイミングと基準信号の周期を考慮して、電流制御信号の出力開始タイミングが、次の立ち上がりエッジの検出タイミングより時間tcだけ前になり、その電流制御信号の出力終了タイミングが、次の立ち上がりエッジの検出タイミングより時間tcだけ後になるようにする。

【0021】

なお、tcはUP信号及びDN信号におけるパルス幅の最大値より大きい値に設定される。

ここでは、電流制御信号生成回路2が、基準信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成するものを示したが、VCO信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3の定電流源21,23に出力するようにしてもよい。

【0022】

出力バッファ回路3は、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

即ち、出力バッファ回路3の差動増幅回路22には、電源電圧VCCが印加されており、電流制御信号生成回路2から電流制御信号が出力されている期間中(電流制御信号の信号レベルがHである期間中)、定電流源21から電流値I0の電流Itailが出力される。

このため、位相周波数比較コア回路1からUP信号が出力されることで、差動増幅回路22の2つのバイポーラトランジスタがオンになると、差動増幅回路22から電圧値がVCC−R×I0のアップ信号が出力される。

なお、電流制御信号生成回路2から電流制御信号が出力されていない期間中(電流制御信号の信号レベルがLである期間中)は、定電流源21から出力される電流Itailの電流値が0になり、差動増幅回路22から電圧値がVCCの信号が出力される。

【0023】

また、出力バッファ回路3の差動増幅回路24には、電源電圧VCCが印加されており、電流制御信号生成回路2から電流制御信号が出力されている期間中(電流制御信号の信号レベルがHである期間中)、定電流源23から電流値I0の電流Itailが出力される。

このため、位相周波数比較コア回路1からDN信号が出力されることで、差動増幅回路24の2つのバイポーラトランジスタがオンになると、差動増幅回路24から電圧値がVCC−R×I0のダウン信号が出力される。

なお、電流制御信号生成回路2から電流制御信号が出力されていない期間中(電流制御信号の信号レベルがLである期間中)は、定電流源23から出力される電流Itailの電流値が0になり、差動増幅回路24から電圧値がVCCの信号が出力される。

【0024】

以上で明らかなように、この実施の形態1によれば、基準信号の立ち上がりエッジを検出するとともに、VCO信号の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早ければ、その基準信号の立ち上がりエッジを検出してからVCO信号の立ち上がりエッジを検出するまでの間、UP信号を出力し、そのVCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早ければ、そのVCO信号の立ち上がりエッジを検出してから基準信号の立ち上がりエッジを検出するまでの間、DN信号を出力する位相周波数比較コア回路1と、基準信号における立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力する電流制御信号生成回路2とを設け、出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力するように構成したので、雑音特性及び高速動作を維持しながら、消費電力を削減することができる効果を奏する。

即ち、出力バッファ回路2の出力信号の波形に影響を与えることなく、出力バッファ回路2の定電流源21,23の電流値を間欠的にON/OFFすることが可能となり、消費電力を削減することができる。

【0025】

この実施の形態1では、差動増幅回路22,24がバイポーラトランジスタを用いて構成されているものを示したが、バイポーラトランジスタに限るものではなく、例えば、FETなどの他のトランジスタを用いて、差動増幅回路22,24を構成してもよい。

【0026】

実施の形態2.

上記実施の形態1では、位相周波数比較コア回路1が、基準信号及びVCO信号の立ち上がりエッジを検出するものを示したが、位相周波数比較コア回路1が、基準信号の立ち下がりエッジを検出するとともに、VCO信号の立ち下がりエッジを検出し、その基準信号の立ち下がりエッジの検出タイミングがVCO信号の立ち下がりエッジの検出タイミングより早ければ、その基準信号の立ち下がりエッジを検出してからVCO信号の立ち下がりエッジを検出するまでの間、UP信号を出力し、そのVCO信号の立ち下がりエッジの検出タイミングが基準信号の立ち下がりエッジの検出タイミングより早ければ、そのVCO信号の立ち下がりエッジを検出してから基準信号の立ち下がりエッジを検出するまでの間、DN信号を出力するようにしてもよい。

この場合、電流制御信号生成回路2は、基準信号における立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力するようにする。

図3は図1の位相周波数比較回路における各種信号のタイミングを示すタイミングチャートである。

【0027】

以下、図3を参照しながら、位相周波数比較回路の動作を具体的に説明する。

位相周波数比較コア回路1は、基準信号の立ち下がりエッジを検出するとともに、電圧制御発振器から出力されるVCO信号の立ち下がりエッジを検出する。

図3のタイミングチャートは、PLLの位相同期が確立している状態を示しており、基準信号とVCO信号の立ち下がりエッジは概ね揃っているが、VCO信号のジッタによって若干の揺らぎが生じているために、両者の立ち下がりエッジがずれている。

位相周波数比較コア回路1は、この揺らぎを含めて、基準信号とVCO信号の立ち下がりエッジを検出している。

【0028】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち下がりエッジを検出し、その基準信号の立ち下がりエッジの検出タイミングがVCO信号の立ち下がりエッジの検出タイミングより早ければ、その基準信号の立ち下がりエッジを検出してからVCO信号の立ち下がりエッジを検出するまでの間、UP信号を出力バッファ回路2の差動増幅回路22に出力する。

図3の例では、左から1番目及び2番目の信号において、基準信号の立ち下がりエッジの検出タイミングがVCO信号の立ち下がりエッジの検出タイミングより早いため、UP信号を出力バッファ回路2の差動増幅回路22に出力している。

【0029】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち下がりエッジを検出し、そのVCO信号の立ち下がりエッジの検出タイミングが基準信号の立ち下がりエッジの検出タイミングより早ければ、そのVCO信号の立ち下がりエッジを検出してから基準信号の立ち下がりエッジを検出するまでの間、DN信号を出力バッファ回路2の差動増幅回路24に出力する。

図3の例では、左から3番目及び4番目の信号において、VCO信号の立ち下がりエッジの検出タイミングが基準信号の立ち下がりエッジの検出タイミングより早いため、DN信号を出力バッファ回路2の差動増幅回路24に出力している。

【0030】

位相周波数比較コア回路1は、基準信号とVCO信号の立ち下がりエッジを検出し、その基準信号の立ち下がりエッジの検出タイミングとVCO信号の立ち下がりエッジの検出タイミングが一致していれば、UP信号とDN信号の出力を行わない。

図3の例では、左から5番目の信号において、基準信号の立ち下がりエッジの検出タイミングとVCO信号の立ち下がりエッジの検出タイミングが一致しているため、UP信号とDN信号の出力を行っていない。

【0031】

電流制御信号生成回路2は、基準信号の立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3の定電流源21,23に出力する。

即ち、電流制御信号生成回路2は、予め基準信号の周期を認識しており、基準信号の立ち下がりエッジを検出する毎に、当該立ち下がりエッジの検出タイミングと基準信号の周期を考慮して、電流制御信号の出力開始タイミングが、次の立ち下がりエッジの検出タイミングより時間tcだけ前になり、その電流制御信号の出力終了タイミングが、次の立ち下がりエッジの検出タイミングより時間tcだけ後になるようにする。

【0032】

なお、tcはUP信号及びDN信号におけるパルス幅の最大値より大きい値に設定される。

ここでは、電流制御信号生成回路2が、基準信号の立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成するものを示したが、VCO信号の立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3の定電流源21,23に出力するようにしてもよい。

【0033】

出力バッファ回路3は、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

即ち、出力バッファ回路3の差動増幅回路22には、電源電圧VCCが印加されており、電流制御信号生成回路2から電流制御信号が出力されている期間中(電流制御信号の信号レベルがHである期間中)、定電流源21から電流値I0の電流Itailが出力される。

このため、位相周波数比較コア回路1からUP信号が出力されることで、差動増幅回路22の2つのバイポーラトランジスタがオンになると、差動増幅回路22から電圧値がVCC−R×I0のアップ信号が出力される。

なお、電流制御信号生成回路2から電流制御信号が出力されていない期間中(電流制御信号の信号レベルがLである期間中)は、定電流源21から出力される電流Itailの電流値が0になり、差動増幅回路22から電圧値がVCCの信号が出力される。

【0034】

また、出力バッファ回路3の差動増幅回路24には、電源電圧VCCが印加されており、電流制御信号生成回路2から電流制御信号が出力されている期間中(電流制御信号の信号レベルがHである期間中)、定電流源23から電流値I0の電流Itailが出力される。

このため、位相周波数比較コア回路1からDN信号が出力されることで、差動増幅回路24の2つのバイポーラトランジスタがオンになると、差動増幅回路24から電圧値がVCC−R×I0のダウン信号が出力される。

なお、電流制御信号生成回路2から電流制御信号が出力されていない期間中(電流制御信号の信号レベルがLである期間中)は、定電流源23から出力される電流Itailの電流値が0になり、差動増幅回路24から電圧値がVCCの信号が出力される。

【0035】

以上で明らかなように、この実施の形態2によれば、基準信号の立ち下がりエッジを検出するとともに、VCO信号の立ち下がりエッジを検出し、その基準信号の立ち下がりエッジの検出タイミングがVCO信号の立ち下がりエッジの検出タイミングより早ければ、その基準信号の立ち下がりエッジを検出してからVCO信号の立ち下がりエッジを検出するまでの間、UP信号を出力し、そのVCO信号の立ち下がりエッジの検出タイミングが基準信号の立ち下がりエッジの検出タイミングより早ければ、そのVCO信号の立ち下がりエッジを検出してから基準信号の立ち下がりエッジを検出するまでの間、DN信号を出力する位相周波数比較コア回路1と、基準信号における立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力する電流制御信号生成回路2とを設け、出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力するように構成したので、雑音特性及び高速動作を維持しながら、消費電力を削減することができる効果を奏する。

即ち、出力バッファ回路2の出力信号の波形に影響を与えることなく、出力バッファ回路2の定電流源21,23の電流値を間欠的にON/OFFすることが可能となり、消費電力を削減することができる。

【0036】

この実施の形態2では、差動増幅回路22,24がバイポーラトランジスタを用いて構成されているものを示したが、バイポーラトランジスタに限るものではなく、例えば、FETなどの他のトランジスタを用いて、差動増幅回路22,24を構成してもよい。

【0037】

この実施の形態2では、位相周波数比較コア回路1が、基準信号及びVCO信号の立ち下がりエッジを検出するものを示したが、基準信号及びVCO信号の立ち上がりエッジと立ち下がりエッジの双方を検出するようにしてもよい。

この場合、電流制御信号生成回路2は、基準信号における立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力するとともに、立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力するようにする。

【0038】

実施の形態3.

上記実施の形態1,2では、電流制御信号生成回路2から出力される電流制御信号によって、定電流源21,23から電流Itailが出力される期間を制限することで、消費電力を削減するものを示したが、電流制御信号生成回路2から出力される電流制御信号によって、更に、位相周波数比較コア回路1におけるUP信号とDN信号の出力処理等に制限を加えることで、消費電力を削減するようにしてもよい。

【0039】

図4はこの発明の実施の形態3による位相周波数比較回路を示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

位相周波数比較コア回路4はD−フリップフロップ31,32及び論理回路33から構成されており、図1の位相周波数比較コア回路1と同様に、基準信号の立ち上がりエッジを検出するとともに、電圧制御発振器から出力されるVCO信号の立ち上がりエッジを検出し、その基準信号の立ち上がりエッジの検出タイミングがVCO信号の立ち上がりエッジの検出タイミングより早ければ、その基準信号の立ち上がりエッジを検出してからVCO信号の立ち上がりエッジを検出するまでの間、UP信号を出力し、そのVCO信号の立ち上がりエッジの検出タイミングが基準信号の立ち上がりエッジの検出タイミングより早ければ、そのVCO信号の立ち上がりエッジを検出してから基準信号の立ち上がりエッジを検出するまでの間、DN信号を出力する回路である。

ただし、位相周波数比較コア回路4は、図1の位相周波数比較コア回路1と異なり、電流制御信号生成回路5から電流制御信号が出力されている期間中は、基準信号及びVCO信号の立ち上がりエッジの検出処理や、UP信号とDN信号の出力処理を実施しない。

なお、位相周波数比較コア回路4は位相比較手段を構成している。

【0040】

電流制御信号生成回路5は基準信号における立ち上がりエッジ(または、VCO信号における立ち上がりエッジ)に同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を位相周波数比較コア回路4及び出力バッファ回路3に出力する回路である。なお、電流制御信号生成回路5は電流制御信号出力手段を構成している。

【0041】

次に動作について説明する。

電流制御信号生成回路5は、図1の電流制御信号生成回路2と同様に、基準信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成する。

ただし、電流制御信号生成回路5は、図1の電流制御信号生成回路2と異なり、その電流制御信号を出力バッファ回路3に出力するだけでなく、位相周波数比較コア回路4にも出力する。

ここでは、電流制御信号生成回路5が、基準信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成するものを示したが、VCO信号の立ち上がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を生成し、その電流制御信号を出力バッファ回路3及び位相周波数比較コア回路4に出力するようにしてもよい。

【0042】

位相周波数比較コア回路4は、電流制御信号生成回路5から電流制御信号が出力されている期間中は、図1の位相周波数比較コア回路1と同様に、基準信号及びVCO信号の立ち上がりエッジの検出処理や、UP信号とDN信号の出力処理を実施する。

一方、電流制御信号生成回路5から電流制御信号が出力されていない期間中は、基準信号及びVCO信号の立ち上がりエッジの検出処理や、UP信号とDN信号の出力処理を実施しない。

【0043】

これにより、出力バッファ回路3だけでなく、位相周波数比較コア回路4の消費電力も削除することができる。

位相周波数比較コア回路4で発生する雑音は、信号の立ち上がり、もしくは、立ち上がり時の動作のみに依存するため、このような電流制御を行うことで、出力雑音が劣化することはない。

ただし、D−フリップフロップ31,32のような論理状態を記憶する回路が位相周波数比較コア回路4に含まれている場合、D−フリップフロップ31,32に供給する電流値を0にすると正常な動作ができなくなるため、電流制御信号が出力されていない期間中でも、D−フリップフロップ31,32に供給する電流値を0にせず、論理状態を保持できる程度の最低限の電流を供給する必要がある。

【0044】

以上で明らかなように、この実施の形態3によれば、電流制御信号生成回路5から電流制御信号が出力されている期間中に限り、位相周波数比較コア回路4が、基準信号及びVCO信号の立ち上がりエッジの検出処理や、UP信号とDN信号の出力処理を実施するように構成したので、上記実施の形態1,2よりも更に、消費電力を削減することができる効果を奏する。

【0045】

この実施の形態3では、位相周波数比較コア回路4が、基準信号及びVCO信号の立ち上がりエッジを検出するものを示したが、基準信号及びVCO信号の立下りエッジを検出するようにしてもよい。

この場合、電流制御信号生成回路5は、基準信号における立ち下がりエッジに同期して、UP信号及びDN信号よりもパルス幅が広い電流制御信号を出力するようにする。

【0046】

実施の形態4.

図5はこの発明の実施の形態4による位相周波数比較回路を示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

ロック検出回路6は基準信号とVCO信号の位相同期が確立しているか否かを判定し、位相同期が確立していれば、ロック検出信号を論理回路7に出力する処理を実施する。

論理回路7はロック検出回路6からロック検出信号が出力されている期間中は、電流制御信号生成回路2から出力された電流制御信号を出力バッファ回路3に出力し、ロック検出回路6からロック検出信号が出力されていない期間中は、信号レベルがHレベルの信号を連続的に出力バッファ回路3に出力する処理を実施する。

なお、電流制御信号生成回路2、ロック検出回路6及び論理回路7から電流制御信号出力手段が構成されている。

【0047】

次に動作について説明する。

上記実施の形態1〜3の位相周波数比較回路の場合、PLLの位相同期時の動作には問題が生じないが、位相同期確立までの過渡状態が通常のPLLと異なる。

即ち、アップ信号とダウン信号のパルス幅が2×tcに制限されるため、基準信号とVCO信号の立ち上がりエッジ(または、立ち下がりエッジ)が大きく異なる場合、基準信号とVCO信号における立ち上がりエッジの検出タイミングの時間差を正確に出力することができない。

これにより、例えば、PLLの出力周波数を、ある値から別の値に切り替える場合、切り替え時間が長くなることがある。

【0048】

この実施の形態4では、切り替え時間が長くなることを防止するために、ロック検出回路6と論理回路7を追加している。

ロック検出回路6は、基準信号とVCO信号の位相同期が確立しているか否かを判定し、位相同期が確立していれば、ロック検出信号を論理回路7に出力する。

論理回路7は、ロック検出回路6からロック検出信号が出力されている期間中は、電流制御信号生成回路2から出力された電流制御信号を出力バッファ回路3に出力する。

したがって、基準信号とVCO信号の位相同期が確立していれば、上記実施の形態1〜3と同様に、電流制御信号生成回路2から出力された電流制御信号が出力バッファ回路3に出力されるため、出力バッファ回路3では、上記実施の形態1〜3と同様に、アップ信号とダウン信号の出力処理が行われ、消費電力が削減される。

【0049】

論理回路7は、ロック検出回路6からロック検出信号が出力されていない期間中は、信号レベルがHレベルの信号を連続的に出力バッファ回路3に出力する。

出力バッファ回路3は、ロック検出回路6からロック検出信号が出力されていない期間中(位相同期が確立していない期間中)、論理回路7から信号レベルがHレベルの信号を連続的に受けることで(電流制御信号を連続的に受けることに相当する)、定電流源21,23から電流値I0の電流Itailが常時出力される。

この場合、定電流源21,23の消費電力が増えるが、PLLの出力周波数を、ある値から別の値に切り替える場合の切り替え時間が長くなることを防止することができる。

【0050】

なお、本願発明はその発明の範囲内において、各実施の形態の自由な組み合わせ、あるいは各実施の形態の任意の構成要素の変形、もしくは各実施の形態において任意の構成要素の省略が可能である。

【符号の説明】

【0051】

1 位相周波数比較コア回路(位相比較手段)、2 電流制御信号生成回路(電流制御信号出力手段)、3 出力バッファ回路(論理信号出力手段)、4 位相周波数比較コア回路(位相比較手段)、5 電流制御信号生成回路(電流制御信号出力手段)、6 ロック検出回路(電流制御信号出力手段)、7 論理回路(電流制御信号出力手段)、11,12,31,32 D−フリップフロップ、13,33 論理回路、21 定電流源(第1の定電流源)、22 差動増幅回路(第1の差動増幅回路)、23 定電流源(第2の定電流源)、24 差動増幅回路(第2の差動増幅回路)。

【特許請求の範囲】

【請求項1】

第1の入力信号の立ち上がりエッジを検出するとともに、第2の入力信号の立ち上がりエッジを検出し、上記第1の入力信号の立ち上がりエッジの検出タイミングが上記第2の入力信号の立ち上がりエッジの検出タイミングより早ければ、上記第1の入力信号の立ち上がりエッジを検出してから上記第2の入力信号の立ち上がりエッジを検出するまでの間、第1のエッジ検出信号を出力し、上記第2の入力信号の立ち上がりエッジの検出タイミングが上記第1の入力信号の立ち上がりエッジの検出タイミングより早ければ、上記第2の入力信号の立ち上がりエッジを検出してから上記第1の入力信号の立ち上がりエッジを検出するまでの間、第2のエッジ検出信号を出力する位相比較手段と、上記第1の入力信号又は上記第2の入力信号における立ち上がりエッジに同期して、上記第1のエッジ検出信号及び上記第2のエッジ検出信号よりもパルス幅が広い電流制御信号を出力する電流制御信号出力手段と、上記電流制御信号出力手段から電流制御信号が出力されている期間中、上記位相比較手段から第1のエッジ検出信号が出力された場合、第1の論理信号を出力し、上記電流制御信号出力手段から電流制御信号が出力されている期間中、上記位相比較手段から第2のエッジ検出信号が出力された場合、第2の論理信号を出力する論理信号出力手段とを備えた位相周波数比較回路。

【請求項2】

第1の入力信号の立ち下がりエッジを検出するとともに、第2の入力信号の立ち下がりエッジを検出し、上記第1の入力信号の立ち下がりエッジの検出タイミングが上記第2の入力信号の立ち下がりエッジの検出タイミングより早ければ、上記第1の入力信号の立ち下がりエッジを検出してから上記第2の入力信号の立ち下がりエッジを検出するまでの間、第1のエッジ検出信号を出力し、上記第2の入力信号の立ち下がりエッジの検出タイミングが上記第1の入力信号の立ち下がりエッジの検出タイミングより早ければ、上記第2の入力信号の立ち下がりエッジを検出してから上記第1の入力信号の立ち下がりエッジを検出するまでの間、第2のエッジ検出信号を出力する位相比較手段と、上記第1の入力信号又は上記第2の入力信号における立ち下がりエッジに同期して、上記第1のエッジ検出信号及び上記第2のエッジ検出信号よりもパルス幅が広い電流制御信号を出力する電流制御信号出力手段と、上記電流制御信号出力手段から電流制御信号が出力されている期間中、上記位相比較手段から第1のエッジ検出信号が出力された場合、第1の論理信号を出力し、上記電流制御信号出力手段から電流制御信号が出力されている期間中、上記位相比較手段から第2のエッジ検出信号が出力された場合、第2の論理信号を出力する論理信号出力手段とを備えた位相周波数比較回路。

【請求項3】

論理信号出力手段は、電流制御信号出力手段から電流制御信号が出力されている期間中、電流を出力する第1の定電流源と、上記第1の定電流源と接続されており、位相比較手段から第1のエッジ検出信号が出力された場合、上記第1の定電流源の出力電流によって第1の論理信号を出力する第1の差動増幅回路と、上記電流制御信号出力手段から電流制御信号が出力されている期間中、電流を出力する第2の定電流源と、上記第2の定電流源と接続されており、上記位相比較手段から第2のエッジ検出信号が出力された場合、上記第2の定電流源の出力電流によって第2の論理信号を出力する第2の差動増幅回路とから構成されていることを特徴とする請求項1または請求項2記載の位相周波数比較回路。

【請求項4】

位相比較手段は、電流制御信号出力手段から電流制御信号が出力されている期間に限り、第1のエッジ検出信号又は第2のエッジ検出信号の出力処理を実施することを特徴とする請求項1から請求項3のうちのいずれか1項記載の位相周波数比較回路。

【請求項5】

電流制御信号出力手段は、第1の入力信号と第2の入力信号における位相同期が確立しているか否かを判定し、位相同期が確立していれば、上記第1の入力信号又は上記第2の入力信号における立ち上がりエッジに同期して、第1のエッジ検出信号及び第2のエッジ検出信号よりもパルス幅が広い電流制御信号を論理信号出力手段に出力し、位相同期が確立していなければ、位相同期が確立するまでの期間、電流制御信号を連続的に論理信号出力手段に出力することを特徴とする請求項1記載の位相周波数比較回路。

【請求項6】

電流制御信号出力手段は、第1の入力信号と第2の入力信号における位相同期が確立しているか否かを判定し、位相同期が確立していれば、上記第1の入力信号又は上記第2の入力信号における立ち下がりエッジに同期して、第1のエッジ検出信号及び第2のエッジ検出信号よりもパルス幅が広い電流制御信号を論理信号出力手段に出力し、位相同期が確立していなければ、位相同期が確立するまでの期間、電流制御信号を連続的に論理信号出力手段に出力することを特徴とする請求項2記載の位相周波数比較回路。

【請求項1】

第1の入力信号の立ち上がりエッジを検出するとともに、第2の入力信号の立ち上がりエッジを検出し、上記第1の入力信号の立ち上がりエッジの検出タイミングが上記第2の入力信号の立ち上がりエッジの検出タイミングより早ければ、上記第1の入力信号の立ち上がりエッジを検出してから上記第2の入力信号の立ち上がりエッジを検出するまでの間、第1のエッジ検出信号を出力し、上記第2の入力信号の立ち上がりエッジの検出タイミングが上記第1の入力信号の立ち上がりエッジの検出タイミングより早ければ、上記第2の入力信号の立ち上がりエッジを検出してから上記第1の入力信号の立ち上がりエッジを検出するまでの間、第2のエッジ検出信号を出力する位相比較手段と、上記第1の入力信号又は上記第2の入力信号における立ち上がりエッジに同期して、上記第1のエッジ検出信号及び上記第2のエッジ検出信号よりもパルス幅が広い電流制御信号を出力する電流制御信号出力手段と、上記電流制御信号出力手段から電流制御信号が出力されている期間中、上記位相比較手段から第1のエッジ検出信号が出力された場合、第1の論理信号を出力し、上記電流制御信号出力手段から電流制御信号が出力されている期間中、上記位相比較手段から第2のエッジ検出信号が出力された場合、第2の論理信号を出力する論理信号出力手段とを備えた位相周波数比較回路。

【請求項2】

第1の入力信号の立ち下がりエッジを検出するとともに、第2の入力信号の立ち下がりエッジを検出し、上記第1の入力信号の立ち下がりエッジの検出タイミングが上記第2の入力信号の立ち下がりエッジの検出タイミングより早ければ、上記第1の入力信号の立ち下がりエッジを検出してから上記第2の入力信号の立ち下がりエッジを検出するまでの間、第1のエッジ検出信号を出力し、上記第2の入力信号の立ち下がりエッジの検出タイミングが上記第1の入力信号の立ち下がりエッジの検出タイミングより早ければ、上記第2の入力信号の立ち下がりエッジを検出してから上記第1の入力信号の立ち下がりエッジを検出するまでの間、第2のエッジ検出信号を出力する位相比較手段と、上記第1の入力信号又は上記第2の入力信号における立ち下がりエッジに同期して、上記第1のエッジ検出信号及び上記第2のエッジ検出信号よりもパルス幅が広い電流制御信号を出力する電流制御信号出力手段と、上記電流制御信号出力手段から電流制御信号が出力されている期間中、上記位相比較手段から第1のエッジ検出信号が出力された場合、第1の論理信号を出力し、上記電流制御信号出力手段から電流制御信号が出力されている期間中、上記位相比較手段から第2のエッジ検出信号が出力された場合、第2の論理信号を出力する論理信号出力手段とを備えた位相周波数比較回路。

【請求項3】

論理信号出力手段は、電流制御信号出力手段から電流制御信号が出力されている期間中、電流を出力する第1の定電流源と、上記第1の定電流源と接続されており、位相比較手段から第1のエッジ検出信号が出力された場合、上記第1の定電流源の出力電流によって第1の論理信号を出力する第1の差動増幅回路と、上記電流制御信号出力手段から電流制御信号が出力されている期間中、電流を出力する第2の定電流源と、上記第2の定電流源と接続されており、上記位相比較手段から第2のエッジ検出信号が出力された場合、上記第2の定電流源の出力電流によって第2の論理信号を出力する第2の差動増幅回路とから構成されていることを特徴とする請求項1または請求項2記載の位相周波数比較回路。

【請求項4】

位相比較手段は、電流制御信号出力手段から電流制御信号が出力されている期間に限り、第1のエッジ検出信号又は第2のエッジ検出信号の出力処理を実施することを特徴とする請求項1から請求項3のうちのいずれか1項記載の位相周波数比較回路。

【請求項5】

電流制御信号出力手段は、第1の入力信号と第2の入力信号における位相同期が確立しているか否かを判定し、位相同期が確立していれば、上記第1の入力信号又は上記第2の入力信号における立ち上がりエッジに同期して、第1のエッジ検出信号及び第2のエッジ検出信号よりもパルス幅が広い電流制御信号を論理信号出力手段に出力し、位相同期が確立していなければ、位相同期が確立するまでの期間、電流制御信号を連続的に論理信号出力手段に出力することを特徴とする請求項1記載の位相周波数比較回路。

【請求項6】

電流制御信号出力手段は、第1の入力信号と第2の入力信号における位相同期が確立しているか否かを判定し、位相同期が確立していれば、上記第1の入力信号又は上記第2の入力信号における立ち下がりエッジに同期して、第1のエッジ検出信号及び第2のエッジ検出信号よりもパルス幅が広い電流制御信号を論理信号出力手段に出力し、位相同期が確立していなければ、位相同期が確立するまでの期間、電流制御信号を連続的に論理信号出力手段に出力することを特徴とする請求項2記載の位相周波数比較回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−30887(P2013−30887A)

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願番号】特願2011−164211(P2011−164211)

【出願日】平成23年7月27日(2011.7.27)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願日】平成23年7月27日(2011.7.27)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]