位相差検出方法、位相制御方法、位相差検出回路、位相制御回路及び無線電力伝送装置

【課題】二信号間の検出位相差の範囲の拡大とともに連続的な位相差出力特性を実現することにある。

【解決手段】 位相差検出部(24)を備えて二信号間(信号入力In1、In2)の位相差DPを検出し、この検出位相差をオフセット値によりシフトして出力する。出力された検出位相差が所定の下限値(PL )以上、上限値(PH )以下の位相差範囲となるように、前記オフセット値が制御される。検出位相差のオフセット値によるシフトは、検出位相差にオフセット値の加算又は減算により行う。

【解決手段】 位相差検出部(24)を備えて二信号間(信号入力In1、In2)の位相差DPを検出し、この検出位相差をオフセット値によりシフトして出力する。出力された検出位相差が所定の下限値(PL )以上、上限値(PH )以下の位相差範囲となるように、前記オフセット値が制御される。検出位相差のオフセット値によるシフトは、検出位相差にオフセット値の加算又は減算により行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、信号間の位相差を検出する技術、信号間の位相を制御する技術に関する。

【背景技術】

【0002】

二信号間の位相差を検出する位相差検出回路は、PLL(Phase-Locked Loop :位相同期ループ)回路等、位相差制御FB(Feedback:フィードバック)系回路の位相差検出や位相制御に用いられる。

【0003】

信号間の位相差検出に関し、PLL回路において、信号間の位相差を−2π(−360度)から+2π(+360度)の範囲(4π)で検出することが知られている(例えば、特許文献1)。

【0004】

位相調整に関し、ループフィルタの出力からダイナミックレンジを検出し、ループフィルタの出力のダイナミックレンジを所定範囲内になるように、位相シフト回路を制御することが知られている(例えば、特許文献2)。また、動作点がダイナミックレンジの端に移動した場合には、ダイナミックレンジの中央値にリセットすることが知られている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−120515号公報

【特許文献2】特開平9−009285号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、信号間の位相差の検出範囲を例えば、0〜360〔度〕程度に広く設定しても、検出位相差で位相を制御する制御対象に揺らぎがあると、検出位相差が大きく変動する。例えば、検出位相差が+180〔度〕と−180〔度〕に変動すると、検出位相差を表すレベル出力は大きく変動する。このように変動を伴ったレベル出力は、位相差出力が大きく変動していても、フィルタリングすると、出力の中間値付近の位相差出力即ち、位相差0〔度〕の位相差出力となってしまう。このような位相差出力では変動する位相差に応じた位相制御が得られない。

【0007】

斯かる要求や課題について、特許文献1、2にはその開示や示唆はなく、それを解決する構成等についての開示や示唆もない。

【0008】

そこで、本開示の位相差検出方法、位相制御方法、位相差検出回路、位相制御回路又は無線電力伝送装置の目的は、上記課題に鑑み、二信号間の検出位相差の範囲の拡大とともに連続的な位相差出力特性を実現することにある。

【課題を解決するための手段】

【0009】

上記目的を達成するため、本開示の位相差検出方法、位相制御方法、位相差検出回路、位相制御回路又は無線電力伝送装置は、二信号間の位相差を検出し、検出位相差をオフセット値によりシフトして出力する。出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように、前記オフセット値が制御される。

【発明の効果】

【0010】

本開示の位相差検出方法、位相制御方法、位相差検出回路、位相制御回路又は無線電力伝送装置によれば、次の何れかの効果が得られる。

【0011】

(1) 検出位相差の範囲を拡大でき、連続した位相差出力特性を実現できる。

【0012】

(2) 検出位相差が大きく変動しても、下限値以上、上限値以下の検出範囲に検出位相差を制御でき、連続した位相差出力特性を得ることができる。

【0013】

(3) 位相差の検出範囲は、その範囲内に下限値及び上限値の設定により、任意の範囲を設定できる。

【0014】

そして、本発明の他の目的、特徴及び利点は、添付図面及び各実施の形態を参照することにより、一層明確になるであろう。

【図面の簡単な説明】

【0015】

【図1】第1の実施の形態に係る位相差検出回路を示す図である。

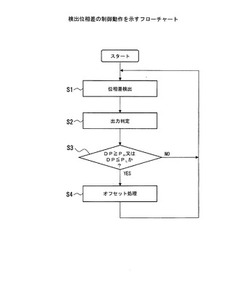

【図2】検出位相差の制御動作を示すフローチャートである。

【図3】位相差出力特性を示す図である。

【図4】第2の実施の形態に係る位相差検出回路を示す図である。

【図5】位相差出力特性を示す図である。

【図6】第3の実施の形態に係る位相差検出回路の構成例を示す回路図である。

【図7】エクスクルーシブOR論理ゲートの真理値表を示す図である。

【図8】位相差検出部の動作を示すタイムチャートである。

【図9】出力判定部及びリセット信号生成部の一例を示す図である。

【図10】出力判定部の動作を示すタイミングチャートである。

【図11】出力判定部のエクスクルーシブOR論理ゲートの真理値表を示す図である。

【図12】リセット信号生成部のマイクロコンピュータの構成例を示す図である。

【図13】位相差検出回路の動作を示すタイムチャートである。

【図14】位相差検出回路の動作を示すタイムチャートである。

【図15】第4の実施の形態に係るマイクロ波電力伝送装置を示す図である。

【図16】位相制御回路の構成例を示す回路図である。

【図17】制御用コンピュータの構成例を示す図である。

【図18】位相制御の制御動作を示すフローチャートである。

【図19】比較例を示す位相比較器の入出力特性を示す図である。

【図20】検出位相差の揺らぎを示す図である。

【発明を実施するための形態】

【0016】

〔第1の実施の形態〕

【0017】

第1の実施の形態について、図1を参照する。図1に示す位相差検出回路は一例であり、係る構成に本発明は限定されない。

【0018】

この位相差検出回路2は、本開示の位相差検出回路の一例である。図1に示す位相差検出回路2には、位相差検出部4と、オフセット制御部6とが備えられている。

【0019】

位相差検出部4は、二信号間の位相差を検出する位相検出手段の一例である。信号入力In1は前記二信号の一方である第1の信号の一例である。また、信号入力In2は前記二信号の他方である第2の信号の一例である。

【0020】

この位相差検出部4は位相差検出機能とオフセット機能を備える。位相差検出機能は、一例として、0〔度〕ないし720〔度〕の広い範囲で位相差を検出する。この位相差検出機能により、信号入力In1、In2間の位相差が検出される。この結果、検出位相差DPを表す位相差出力Opが得られる。この位相差出力Opは検出位相差DPを表す電気信号である。この位相差出力Opがオフセット制御部6に加えられる。

【0021】

オフセット機能は、信号入力In1、In2間の検出位相差をオフセット値によりシフトして出力する機能である。一例であるオフセット機能は、広い範囲の位相差検出機能を維持しながら、検出位相差を所定の範囲にシフトさせるためのオフセット値を加算又は減算する。即ち、オフセット制御部6からのオフセット制御信号OFCにより既述のオフセット値の加算又は減算が行われる。

【0022】

オフセット制御部6は、既述のオフセット値を制御する制御手段の一例である。このオフセット制御部6では、位相差出力Opに基づき、検出位相DPが所定の下限値PL 以上、上限値PH 以下になるように既述のオフセット値を制御する。この制御のため、オフセット制御部6では、位相差出力Opに基づき、検出位相DPが上限値PH 又は下限値PL に到達したか否かを判定する。検出位相DPが上限値PH 又は下限値PL に到達していれば、オフセット制御部6からオフセット制御信号OFCが得られる。上限値PH 及び下限値PL は位相差検出部4の位相差検出可能な範囲内に設定される。上限値PH はその位相差範囲の上端より小さい値である。下限値PL はその位相差範囲の下端より大きい値である。

【0023】

斯かる構成では、次のような位相差検出及び検出制御が行われる。位相差検出部4では、オフセット値+OF又は−OFで位相差検出が行われる。検出位相差DPが上限値PH 又は下限値PL に到達すれば、オフセット制御部6からオフセット制御信号OFCが出力される。このオフセット制御信号OFCは連続した信号でもよいし、検出位相差DPが上限値PH 又は下限値PL に到達したことを契機とする瞬間的な信号でもよい。

【0024】

この場合、オフセット値+OFで、検出位相差DPが上限値PH 又は下限値PL に到達すれば、オフセット値+OFからオフセット値−OFに変更される。その場合、その到達時点で、現行のオフセット値が−OFであれば、オフセット値+OFに変更される。即ち、検出位相差DPに応じてオフセット値の加算又は減算により、検出位相差DPが下限値PL 以上、上限値PH 以下の位相差範囲に制御される。

【0025】

この位相差検出及び制御の動作について、図2を参照する。図2に示す処理手順は一例であって、係る手順に限定されない。

【0026】

この動作手順は、本開示の位相差検出方法の一例である。図2に示す処理手順では、位相差検出(ステップS1)、出力判定(ステップS2、S3)、オフセット処理(ステップS4)を含んでいる。

【0027】

位相差検出(ステップS1)は、少なくとも二信号間の位相差を検出する処理である。この処理は、位相差検出部4で実行される。既述の二信号の一例として、信号入力In1と信号入力In2が位相差検出部4に加えられる。位相差検出部4では、既述の位相差検出機能により、信号入力In1、In2間の位相差が検出される。この処理により、検出位相差DPを表す位相差出力Opが得られる。

【0028】

出力判定(ステップS2、S3)では、検出位相差DPが上限値PH 又は下限値PL に到達したことを判定する。この出力判定は、検出位相差DPが上限値以上(DP≧PH )又は下限値以下(DP≦PL )に到達したことを判定する(ステップS3)。検出位相差DPが上限値以上(DP≧PH )又は下限値以下(DP≦PL )に到達した場合には(ステップS3のYES)、オフセット処理(ステップS4)に移行する。

【0029】

オフセット処理(ステップS4)は、位相差検出部4に対して既述のオフセット値OFの加算又は減算を行う処理である。検出位相差DPが上限値以上(DP≧PH )又は下限値以下(DP≦PL )に到達すれば、既述の位相差範囲に検出位相差DPがシフトするようにオフセット値OFの減算(又は加算)を行う。例えば、位相差検出部4の検出位相差DPが上限値PH に到達した時点で、設定中のオフセット値が+OFであれば、オフセット値−OFに変更する。また、設定中のオフセット値が−OFであれば、リセット信号RESETに基づき、オフセット値+OFに変更する。

【0030】

次に、オフセット処理の後、再び位相差検出(ステップS1)に戻り、同様の位相差検出を行う。ステップS3(出力判定)において、検出位相差DPが上限値以上(DP≧PH )又は下限値以下(DP≦PL )に到達していなければ(ステップS3のNO)、オフセット処理(ステップS4)に移行することなく、ステップS1に戻る。つまり、検出位相差DPが検出可能な位相差範囲Pr(PL <DP<PH )内にあれば、現状のオフセット値が維持される。

【0031】

このような位相差検出では、次のような利点がある。

【0032】

(1) 位相差検出において、連続的な位相差出力特性が得られる。

【0033】

この位相差出力特性について、図3を参照する。図3に示す位相差出力特性は、検出位相差(横軸)に対して位相差出力レベル(縦軸)を示している。検出位相差DPに応じて直線的な位相差出力レベルが得られている。検出位相差DPが上限値PH に到達すると、既述のオフセット値OFの加算又は減算により、位相差D1にシフトされる。また、検出位相差DPが下限値PL に到達すると、既述のオフセット値OFの加算又は減算により、位相差D2にシフトされる。つまり、検出位相差DPが上限値PH に到達すると、所定の位相差D1にシフトされ(即ち、シフト量=PH −D1)、また、下限値PL に到達すると、所定の位相差D2(>D1)にシフトされる(シフト量=PL +D2)。この結果、検出位相差を所定位相差だけ増加又は減少させるので、あらゆる位相差で連続的な位相差出力特性が得られる。

【0034】

(2) 検出位相差DPを位相差範囲Prにシフトさせるには、オフセット値に例えば、360〔度〕程度の任意の値を設定することができる。

【0035】

(3) 位相差検出部4の位相差検出機能において、位相検出可能な範囲は、既述の位相差範囲Prを超えて任意の値にできる。その検出可能な範囲において、連続的な位相差検出出力を得ることができる。

【0036】

〔第2の実施の形態〕

【0037】

第2の実施の形態について、図4を参照する。図4に示す位相差検出回路は一例であり、係る構成に本発明は限定されない。図4において、図1と同一部分には同一符号を付してある。

【0038】

この位相差検出回路22は、本開示の位相差検出回路の一例である。この位相差検出回路22は、例えば、0〜720〔度〕の位相差を検出する機能を備え、検出位相差DPの上限値PH 及び下限値PL を判定する。検出位相差DPの値が上限値PH 又は下限値PL に到達すれば、360〔度〕だけ加減させ、これにより、あらゆる位相差に対して連続的な位相差出力特性を実現する。

【0039】

図4に示す位相差検出回路22の位相差検出部24は信号間の位相差を検出する位相差検出手段の一例であり、位相比較部26と、オフセット部28とが備えられている。この位相差検出部24には位相差検出対象の一例である二信号として信号入力In1、In2が加えられている。位相差検出部24の出力側にはローパスフィルタ(Low-Pass Filter :LPF)部30が設置されている。そして、オフセット制御部6には上限/下限判定部32と、リセット信号生成部34とが設置されている。

【0040】

位相比較部26は、例えば、0ないし720〔度〕の位相差範囲で位相差を検出する機能を備えている。この位相比較部26には信号入力In1が入力され、信号入力In2がオフセット部28を介して入力されている。オフセット部28は、二信号の一方である信号入力In2側に設置されており、信号入力In2に対し、既述のオフセット値を設定する。位相比較部26は、信号入力In1と、オフセット値が設定された信号入力In2とを比較し、両者の位相差を0〜720〔度〕の範囲で検出する。従って、位相比較部26には検出位相差DPを表す位相差パルスPPが得られる。この位相差パルスPPのパルス幅が、検出位相差DPの大きさを表す。

【0041】

LPF部30は、位相差パルスPPを直流レベルに変換する信号変換手段の一例である。このLPF部30には位相差パルスPPが直流レベルに変換された既述の位相差出力Opが得られる。この位相差出力Opは、検出位相差DPの大きさに比例したレベルを持つ信号である。この位相差出力Opは、上限/下限判定部32に入力される。

【0042】

上限/下限判定部32は、検出位相差DPが上限値に到達したか又は下限値に到達したかの出力レベル判定手段の一例である。この上限/下限判定部32には予め基準値として、上限値Vth−HIと下限値Vth−LOが設定されている。上限値Vth−HIと下限値Vth−LOは、位相差出力Opと比較する直流電圧値である。そこで、位相差出力Opが上限値Vth−HI又は下限値Vth−LOに到達していれば、その判定出力が得られる。この判定出力はリセット信号生成部34に入力される。

【0043】

リセット信号生成部34は、上限/下限判定部32の判定出力に基づき、リセット信号RESETを生成する。このリセット信号RESETは、位相差検出部24のオフセット部28に入力される。

【0044】

斯かる構成では、リセット信号RESETがオフセット部28に加えられると、オフセット処理が実行される。即ち、リセット信号RESETの入力前に設定されていたオフセット値は、リセット信号RESETを受けて新たなオフセット値に変更される。つまり、オフセット値の変更により、リセット信号RESETの入力前の状態から例えば、オフセット値として例えば、180〔度〕の加算又は減算が行われる(後述のパルス反転)。これにより、信号入力In1、In2の位相差がいかなる値においても、位相差検出回路22の位相差出力Opが連続的に変化することとなる。

【0045】

この位相差検出回路22の位相差出力特性について、図5を参照する。図5に示す位相差出力特性は一例であり、係る特性に本発明が限定されない。

【0046】

図5は、一例として検出位相差DPの上限値PH を630〔度〕、下限値PL を90〔度〕に設定した場合の位相差出力特性である。横軸が検出位相差DP〔deg(=度)〕、縦軸が位相差出力レベル〔%〕である。この出力特性は、検出位相差DPに応じて位相差出力レベルの変化を示している。図5において、湾曲した矢印は位相シフト、双方向矢印は位相差変化を示す。

【0047】

検出位相差DPが630〔度〕を超える位相差出力Op(出力電圧)に到達すると、リセット信号生成部34にリセット信号RESETが発生する。これにより、検出位相差DPは−360〔度〕だけシフトされ、270〔度〕となる。この場合、検出位相差DPは270〔度〕より増減する。

【0048】

また、検出位相差DPが90〔度〕に到達すると、同様に、リセット信号生成部34にはリセット信号RESETが発生する。リセット信号RESETは、オフセット値を切り替える制御信号の一例であり、リセット信号生成部34は制御信号生成手段の一例である。これにより、検出位相差DPは+360〔度〕だけシフトされ、450〔度〕となる。この場合、検出位相差DPは450〔度〕より増減することになる。

【0049】

〔第3の実施の形態〕

【0050】

第3の実施の形態について、図6を参照する。図6に示す位相差検出回路22は一例であり、係る構成に本発明は限定されない。図6において、図4と同一部分には同一符号を付してある。

【0051】

図6に示す位相差検出回路22の位相差検出部24では、信号入力In1を位相差検出の基準(マスタ)側に、信号入力In2をスレーブ側に設定されている。信号入力In1側に設置されたこの分周回路36には、一例としてD形フリップフロップ(D−FF)41、42が設置されている。信号入力In1は、D−FF41にクロックとして入力され、このD−FF41で2分周される。D−FF41の出力A2は、D−FF42のクロックとして入力され、D−FF42で2分周される。この結果、分周回路36では、信号入力In1の4分周出力A4が得られる。この分周出力A4が位相比較部26のD−FF44及びエクスクルーシブOR(Exclusive:EXOR、排他的論理和)論理ゲート46に入力されている。

【0052】

オフセット部28は、信号入力In2側に設置されている。このオフセット部28は、一例としてD−FF43及び選択回路(Selector:SEL)48を備える。D−FF43は分周手段の一例である。信号入力In2は、D−FF43にクロックとして入力され、D−FF43で2分周される。D−FF43には非反転出力B2及び反転出力B2Xが得られる。SEL48は、非反転出力B2又は反転出力B2Xの選択手段の一例である。SEL48は、リセット信号RESETを受けることにより、非反転出力B2又は反転出力B2Xを出力する。例えば、リセット信号RESET=Hのとき、非反転出力B2から反転出力B2Xに切り替えられる。また、リセット信号RESET=Lのとき、反転出力B2Xから非反転出力B2に切り替えられる。非反転出力B2又は反転出力B2Xは、位相比較部26のD−FF44のCLK入力に加えられる。

【0053】

位相比較部26は、一例としてD−FF44及びEXOR論理ゲート46を備えている。D−FF44には、D−FF43の反転出力B2X又は非反転出力B2がクロックとして入力される。従って、D−FF44では、D−FF42の出力が反転出力B2X又は非反転出力B2によりゲーティングされる。そして、EXOR論理ゲート46には、D−FF42の出力A4と、D−FF44の出力が加えられている。従って、EXOR論理ゲート46には、信号入力In1を基準にして信号入力In2の位相差が検出され、検出位相差DPを表す位相差パルスPPが得られる。

【0054】

D−FF42、44の出力とEXOR論理ゲート46の出力について、図7を参照する。図7は、EXOR論理ゲート46の真理値表を示している。各D−FF42、44の出力が共にL(低レベル)出力又はH(高レベル)出力の場合、両者の排他的論理和により、EXOR論理ゲート46の出力はL出力となる。D−FF42、44の出力の一方がL出力又は他方がH出力の場合、両者の排他的論理和により、EXOR論理ゲート46の出力はH出力となる。即ち、EXOR論理ゲート46のH出力区間が検出位相差DPを示している。

【0055】

この位相差検出部24の論理動作について、図8を参照する。図8に示すタイムチャートは、位相差検出部24の各部の論理動作を示しており、この論理動作に本発明が限定されない。

【0056】

図8のAは信号入力In1、図8のDは信号入力In2を示している。この例では、信号入力In1、In2の1周期の区間がθB =360〔度〕に設定され、そのH出力区間がθA =180〔度〕、そのL出力区間が180〔度〕である。従って、信号入力In1、In2の2周期の区間がθC =720〔度〕である。

【0057】

信号入力In1がクロックとして入力されたD−FF41には、図8のBに示す出力A2が得られる。出力A2は、1周期がθC =720〔度〕であり、そのH出力区間がθB =360〔度〕、そのL出力区間が360〔度〕である。この出力A2がクロックとして入力されたD−FF42には、図8のCに示す出力A4が得られる。出力A4は、1周期が1440〔度〕であり、そのH出力区間が720〔度〕、そのL出力区間が720〔度〕である。

【0058】

信号入力In2がクロックとして入力されたD−FF43には、720〔度〕を1周期とする非反転出力B2及び反転出力B2Xが得られる。リセット信号RESETがRESET=Hであれば、図8のEに示すように、SEL48で非反転出力B2が選択される。リセット信号RESETがRESET=Lであれば、図8のFに示すように、SEL48で反転出力B2Xが選択される。つまり、リセット信号RESETのH/Lが切り替わると、SEL48の出力が非反転出力B2又は反転出力B2X出力に切り替えられる。

【0059】

RESET=Hのとき、D−FF44では出力A4が非反転出力B2でゲーティングされ、図8のGに示す出力が得られる。EXOR論理ゲート46では、出力A4とD−FF44の出力との排他的論理和(一方がH出力、他方がL出力)により、図8のHに示す出力(位相差パルスPP)が得られる。

【0060】

RESET=Lのとき、D−FF44では出力A4が反転出力B2Xでゲーティングされ、図8のIに示す出力が得られる。EXOR論理ゲート46では、出力A4とD−FF44の出力との排他的論理和(一方がH出力、他方がL出力)により、図8のJに示す出力が得られる(位相差パルスPP)。この場合、図8のH及びJに示す位相差パルスPPのH出力区間は180〔度〕相当のパルス幅差分である。

【0061】

次に、上限/下限判定部32、リセット信号生成部34及びこれらの動作について、図9、図10及び図11を参照する。図9は上限/下限判定部32及びリセット信号生成部34の構成例を示し、図10は上限/下限判定部32の動作を示し、図11は上限/下限判定部32のEXOR論理ゲートの真理値表を示している。係る構成及び動作に本発明は限定されない。図9において、図4と同一部分には同一符号を付してある。

【0062】

図9に示す上限/下限判定部32では一例として上限判定部32Hと、下限判定部32Lと、EXOR論理ゲート50とが含まれる。即ち、上限/下限判定部32は、検出位相差が上限値以上又は下限値以下を判定するウインドコンパレータを構成している。

【0063】

上限判定部32Hにはコンパレータ52が設置され、下限判定部32Lにはコンパレータ53が設置されている。コンパレータ52には、基準入力として上限電圧Vth−HIが設定され、コンパレータ53には、基準入力として下限電圧Vth−LOが設定されている。上限電圧Vth−HIの生成には、抵抗54、56の分圧回路58が用いられている。この場合、直流電圧を抵抗54、56の抵抗比で分圧することにより、上限基準電圧Vth−HIが設定される。また、下限電圧Vth−LOの生成には、抵抗60、62の分圧回路64が用いられている。この場合、直流電圧を抵抗60、62の抵抗比で分圧することにより、下限電圧Vth−LOが設定される。

【0064】

この上限/下限判定部32では、図10のAに示すように、コンパレータ52は、位相差出力Opのレベルが上限電圧Vth−HI以上では、図10のBに示すH出力、またVth−HI以下ではL出力となる。また、コンパレータ53は、位相差出力Opが下限電圧Vth−LO以下では図10のCに示すL出力、下限電圧Vth−LO以上ではH出力となる。

【0065】

各コンパレータ52、53の各出力が入力されるEXOR論理ゲート50では、図11に示す真理値表に記載された論理動作となる。各コンパレータ52、53で得られる各出力H/Lが相違しているとき、図10のDに示すように、EXOR論理ゲート50はH出力を発生する。また、各コンパレータ52、53の各出力がH又はLで一致していれば、EXOR論理ゲート50はL出力(図10のDのL)を発生する。即ち、検出位相差が下限値以下、上限値以上でL出力となり、検出位相差が下限値以上、上限値以下でH出力となる。

【0066】

そして、EXOR論理ゲート50の出力側に設置されたリセット信号生成部34は、一例としてマイコン(UPC)66で構成される。このマイコン66は、EXOR論理ゲート50の出力即ち、上限/下限判定部32の判定出力がL出力であれば、リセット信号RESETを現状出力から反転値に切り替える。即ち、現状出力がH出力であれば反転出力Lに切り替えられ、又は現状出力がLであればその反転値である非反転出力Hに切り替えられる。

【0067】

このマイクロコンピュータ66について、図12を参照する。図12に示すマイクロコンピュータの構成は一例であり、係る構成に本発明は限定されない。

【0068】

図12に示すマイクロコンピュータ66では、プロセッサ68、メモリ部70及び入出力部(I/O)72を備えている。メモリ部70にはプログラムを格納するROM(Read-Only Memory)や、データを格納するRAM(Random-Access Memory)を備えている。斯かる構成では、I/O72にEXOR論理ゲート50の出力が取り込まれ、EXOR論理ゲート50の出力がLからHに遷移したとき、出力中のリセット信号RESETを現状出力からその反転値に切り替えて出力する。

【0069】

この実施の形態の位相差検出回路22(図6)の動作について、図13及び図14を参照する。図13は、LPF部30の出力が下限電圧Vth−LOに到達する過程の動作を示している。また、図14は、LPF部30の出力が上限電圧Vth−HIに到達する過程の動作を示している。

【0070】

図13のAに示す信号入力In1は既述したように、分周回路36で4分周され、D−FF42には、図13のDに示す出力A4が得られる。図13のBに示す信号入力In2は既述したように、D−FF43で2分周される。このとき、RESET=Lであれば、SEL48では、D−FF43の非反転出力B2が選択され、図13のCに示す非反転出力B2が得られる。

【0071】

D−FF44では、クロックにD−FF43の非反転出力B2が加えられ、D−FF42の出力がゲーティングされ、図13のEに示す出力が得られる。EXOR論理ゲート46では、D−FF42の出力A4とD−FF44の出力の排他的論理和により、図13のFに示す出力が得られる。

【0072】

この場合、EXOR論理ゲート46の出力パルスのH区間が徐々に小さくなると、LPF部30の出力は図13のGに示すように、徐々に低下する。LPF部30の出力(位相差出力Op)が下限電圧Vth−LOに到達すると、EXOR論理ゲート50がL出力(図10のD)を発生する。このL出力により、リセット信号生成部34のマイコン66が図13のHに示すリセット信号RESETを発生する。この場合、現行のリセット信号がRESET=Lとすれば、その反転値として、RESET=Hに切り替わる。

【0073】

この時点からSEL48の出力が、RESET=Hへの遷移を契機に、即ち、その時点で図13のCに示すように、非反転出力B2から反転出力B2Xに切り替えられる。これにより、検出位相差がシフトし、LPF部30の出力は、図13のGに示すように、時点t1以降では下限電圧Vth−LOより高い値に回復する。

【0074】

この場合も、図14のAに示す信号入力In1は分周回路36で4分周され、D−FF42には図14のDに示す出力A4が得られる。また、図14のBに示す信号入力In2がD−FF43で2分周され、このとき、RESET=Hであるので、SEL48では、D−FF43の反転出力B2Xが選択され、図14のCに示す反転出力B2Xが得られる。

【0075】

D−FF44では、クロックにD−FF43の反転出力B2Xが加えられ、D−FF42の出力がゲーティングされ、図14のEに示す出力が得られる。EXOR論理ゲート46では、D−FF42の出力A4とD−FF44の出力の排他的論理和により、図14のFに示す出力が得られる。

【0076】

この場合、EXOR論理ゲート46の出力パルスのH区間が徐々に大きくなると、LPF部30の出力は図14のGに示すように、徐々に上昇する。LPF部30の出力(位相差出力Op)が上限電圧Vth−HIに到達すると、EXOR論理ゲート50が出力L(図10のD)を発生する。この出力Lにより、リセット信号生成部34のマイコン66が図14のHに示すリセット信号RESETを発生する。この場合、現行のリセット信号がRESET=Hとすれば、その反転値として、RESET=Lに切り替えられる。

【0077】

この時点からSEL48の出力が、RESET=Lへの遷移を契機に、図14のCに示すように、非反転出力B2から反転出力B2Xに切り替えられる。これにより、検出位相差がシフトし、LPF部30の出力は、図14のGに示すように、時点t2以降では上限電圧Vth−HIより低い値に回復する。

【0078】

このような動作により、検出位相差が下限値未満となり又は上限値を超えても、下限値以上、上限値以下の位相検出範囲に制御され、連続した位相差検出を行うことができる。

【0079】

以上述べた第3の実施の形態について、利点や特徴事項を以下に列挙する。

【0080】

(1) 一例として0〜720〔度〕の位相差検出機能を備え、検出位相差が上限値及び下限値に到達したことを判定し、位相差検出値を一定位相差として例えば、180〔度〕だけを加減させる。この結果、信号入力のあらゆる位相差に対し、連続的な位相差出力特性を実現できる。従って、位相差を検出する二信号の入力位相差が0〜360〔度〕のいかなる値でも、連続的な出力が得られる。

【0081】

(2) 上記位相差検出回路22では、0〜720度の位相差と、位相差検出値を位相差検出範囲の上限及び下限で180〔度〕だけ加減する構成を備える。

【0082】

(3) 位相差検出回路22では、上限及び下限で位相差検出値を180〔度〕だけを加減する処理に、検出位相差に相当するパルス信号を直流信号に変換するLPF部30の出力と、コンパレータ52、53とを含む構成で実現している。

【0083】

(4) 位相差検出回路22では、上限及び下限で位相差検出値を180〔度〕だけ加減する処理に、D−FF43の反転出力と非反転出力を、リセット信号生成部34が発生するリセット信号RESETで切り替える構成を備えている。

【0084】

(5) 二信号の位相差検出において、一方の信号入力In1側を二つのD−FF41、42の分周出力と、他方の信号入力In2側を一つのD−FF43の分周出力(反転出力及び非反転出力)とを用いることにより、位相差を検出している。

【0085】

(6) 位相差の検出では、D−FF44とEXOR論理ゲート46とを用いている。D−FF44では、D−FF42の分周出力をD−FF43の反転出力及び非反転出力でゲーティングし、EXOR論理ゲート46で、D−FF42の出力と、D−FF44の出力との排他的論理和により、検出位相差をパルス幅に変換して出力させている。

【0086】

(7) リセット信号生成部34では一例として、マイクロコンピュータ66を用いることにより、上限/下限判定出力部32の出力値がHになった場合、リセット信号RESETを生成する。現状出力がRESET=Hであれば、上限/下限判定出力部32の出力値がHになった場合に、リセット信号RESETは反転値に切り替えられる。つまり現状出力がRESET=Hであれば、RESET=Lに切り替えている。これにより、位相差の連続的な検出出力を得ることができる。

【0087】

〔第4の実施の形態〕

【0088】

第4の実施の形態について、図15を参照する。図15に示すマイクロ波電力伝送装置は一例であり、係る構成に本発明は限定されない。

【0089】

図15に示すマイクロ波電力伝送装置70は、本開示の無線電力伝送装置の一例であり、宇宙太陽光発電の出力をマイクロ波伝送する。このマイクロ波電力伝送装置70には、電力源74が設置され、この電力源74には一例として、太陽電池75が用いられている。太陽電池75は、太陽光により発電する。この電力源74は、例えば、宇宙空間に設置されるが、地球上に設置されてもよい。

【0090】

この電力源74の出力側には複数の電力/マイクロ波変換器76が設置され、この電力/マイクロ波変換器76の出力側には位相制御送信部780、781、782・・78Nが個別に設置されている。各電力/マイクロ波変換器76は電力を送信可能な無線信号の一例として、6〔GHz〕程度の周波数のマイクロ波に変換する。位相制御送信部780、781、782・・・78Nは、本開示の位相制御方法及び位相制御回路の一例である。

【0091】

電力源74で得られた電力は、各電力/マイクロ波変換器76により各マイクロ波M0 、M1 、M2 、M3 ・・・MN に変換され、各マイクロ波M0 、M1 、M2 、M3 ・・・MN は、位相制御送信部780、781、782・・78Nに加えられる。位相制御送信部780、781、782・・78Nでは、電力/マイクロ波変換器76からのマイクロ波出力を送信する際、電力伝送効率が最大となるように、マイクロ波出力位相を任意の値に制御する。出力位相が制御されたマイクロ波出力は、各アンテナ80により個別に電力受給先に送信される。

【0092】

このマイクロ波電力伝送装置70の位相制御回路について、図16を参照する。図16に示す位相制御回路は一例であり、斯かる構成に本発明が限定されない。図16において、図15と同一部分には同一符号を付してある。

【0093】

図16に示す位相制御回路82は、本開示の位相制御方法及び位相制御回路の一例である。この位相制御回路82は、既述のマイクロ波電力伝送装置70において、位相差制御フィードバック系を構成している。この位相制御回路82では、複数の位相制御送信部780、781、782・・78Nの一つである例えば、位相制御送信部780を基準(マスタ)側に他の位相制御送信部781、782・・78Nをスレーブ側に設定する。

【0094】

各位相制御送信部780、781、782・・78Nのそれぞれには移相器84及び増幅器(AMP)86が設置されている。各移相器84には既述の電力/マイクロ波変換器76からマイクロ波M0 、M1 、M2 、M3 ・・・MN が入力される。AMP86は既述の位相制御送信部780、781・・・78Nの例えば、終段増幅器である。このAMP86にはアンテナ80が接続され、既述のマイクロ波が送信される。この実施の形態では、各AMP86からマイクロ波M0 、M1 、M2 、M3 ・・・MN の各信号から位相θ0 、θ1 、θ2 、θ3 ・・・θN が検出される。従って、各AMP86は各位相θ0 、θ1 、θ2 、θ3 ・・・θN の検出手段の一例である。

【0095】

各AMP86で検出された各位相θi(=θ1 、θ2 、θ3 ・・・θN )は、第1のセレクタ90により選択されて制御部94の位相差検出部102に加えられる。セレクタ90は、各位相θ1 、θ2 、θ3 ・・・θN の選択手段の一例である。セレクタ90は、制御用パーソナルコンピュータ(制御PC)98からセレクト信号により制御され、位相θ1 、θ2 、θ3 ・・・θN の何れかが順次に選択される。

【0096】

制御PC98は、セレクタ90に対するセレクト信号を出力するとともに、第2のセレクタ100に対するセレクト信号を同期して出力する。制御PC98は、基準位相φ0及び目標位相差Δφを出力する。セレクタ100は位相制御の対象であるスレーブ側の移相器84を選択する。

【0097】

制御部94では、基準側AMP86の検出位相θ0 と、セレクタ90で選択された既述の位相θiとの位相差Δθ(=θi−θ0 )を検出する。この制御部94では、この検出位相差Δθを目標位相差Δφと比較し、誤差を求める。一例である制御部94は、位相差検出部102と誤差検出部104とを備えている。

【0098】

位相差検出部102は、既述の位相差検出回路2(図1)又は位相差検出回路22(図4)で構成される。セレクタ90では、既述の位相θiから、例えば、位相θi=θ1 が選択される。基準側のAMP86から基準位相φ0に設定された位相出力θ0 が得られる。

【0099】

位相差検出部102では、位相θ0 と位相θ1 が比較され、検出位相差Δθ=θi−θ0 =θ1 −θ0 が求められる。この検出位相差Δθが誤差検出部104に加えられる。誤差検出部104では、検出位相差Δθと、制御PC98で設定された目標位相差Δφとが比較され、位相差誤差が求められる。この位相差誤差が位相制御信号としてのセレクタ100に加えられる。セレクタ90、100は、この場合、位相出力θ1 に関する一つの制御対象を選択するので、位相θ1 を取り出した移相器84に位相制御信号が加えられ、マイクロ波M1 の位相θ1 が制御される。この場合、制御PC98に設定された目標位相差Δφに検出位相差Δθが到達するように、位相θ1 が制御される。

【0100】

この位相制御回路82の制御PC98には、例えば、パーソナルコンピュータで構成すればよい。図17に示す制御PC98は一例であり、係る構成に本発明が限定されない。図17に示す制御PC98では、プロセッサ106と、メモリ部108と、RAM110と、入出力部112とをバス114で接続している。プロセッサ106は、メモリ部108にあるプログラムを実行し、既述のセレクタ90、100に対するセレクト信号を生成する。

【0101】

メモリ部108は、プログラム記憶部116と、データ記憶部118を備える。プログラム記憶部116にはOS(Operating System)や既述の位相制御のための位相制御プログラム等の各種アプリケーションプログラムが記録される。データ記憶部118には目標位相差Δφ、基準位相φ0、検出されたデータや演算途上のデータが格納される。従って、メモリ部108には、ハードディスクドライブ、CD、DVD等のROM、半導体メモリ等の各種の記録媒体を用いることができる。RAM110は一時的にデータを格納し、実行するプログラムのワークエリアを構成する。

【0102】

入出力部112では、プロセッサ106の制御により、制御部94からの誤差検出信号を受け、また、既述の基準位相φ0、目標位相差Δφが設定され、セレクタ90に対するセレクト信号S1 、セレクタ100に対するセレクト信号S2 が出力される。

【0103】

この位相制御回路82の位相差制御について、図18を参照する。図18に示す位相差制御の処理手順は一例であり、係る手順に本発明は限定されない。

【0104】

この処理手順は、本開示の位相制御方法の一例である。図18に示す処理手順では、セレクタ90により制御対象である位相θi(=θ1 、θ2 ・・・θN )の何れかが選択される(ステップS11)。これに対応してセレクタ100によりマイクロ波M1 〜M4 の何れかが選択され、例えば、位相θ1 の場合には、その入力側のマイクロ波M1 が選択される。

【0105】

検出位相θiとマスタ側の基準位相θ0 とが比較され、この場合、Δθ=θi−θ0 により位相差Δθが検出される(ステップS12)。この検出位相差Δθは、制御PC98の目標位相差Δφと比較され、検出位相差Δθの目標位相差Δφに対する誤差が求められる(ステップS13)。

【0106】

この誤差により位相制御が行われる(ステップS14)。この場合、セレクタ100を通じて位相制御送信部781の移相器84が選択され、その制御入力となる。これにより、マイクロ波M1の位相がシフトされる。

【0107】

検出位相差Δθが目標位相差Δφに一致したか否かを判断する(ステップS15)。検出位相差Δθが目標位相差Δφに一致していなければ(ステップS15のNO)、ステップS12に戻り、継続して位相制御を行う。

【0108】

そして、検出位相差Δθが目標位相差Δφに一致すれば(ステップS15のYES)、ステップS11に戻り、次の位相θ2 ・・・θN の何れかを選択し、同様に制御する位相制御送信部782〜78Nの移相器84の何れかが選択される。既述の位相制御が継続的に実行される。

【0109】

従って、マイクロ波送信中、マイクロ波出力の位相が設定位相に制御され、その結果、最大の電力伝送効率を得られ、維持される。

【0110】

この第4の実施の形態について、以下に特徴事項や利点を列挙する。

【0111】

(1) マイクロ波出力位相の制御は、複数の位相制御送信部780、781、782・・・78Nの中から何れか一つの例えば、位相制御送信部780を基準送信部、その他の位相制御送信部780、781、782・・・78Nをスレーブ送信部とし、これらの位相差を検出することにより位相制御を行っている。

【0112】

(2) 制御PC98から各位相制御送信部780、781、782・・・78Nに対する目標位相差Δφが出力される。誤差検出器104では、目標位相差Δφ(設定位相差)と検出位相差Δθとを比較して誤差が算出される。この誤差出力をスレーブ側の対応する位相制御送信部781、782・・・78Nの移相器84に位相制御値として入力し、目標位相差Δφに制御している。

【0113】

(3) このような位相差制御FB系を構成する位相制御回路82では、目標位相差Δφが270〔度〕(=−90〔度〕)に設定された場合、制御対象(例えば、位相制御送信部780、781、782・・・78N)に揺らぎが発生しても位相差検出部102の出力は連続的な区間にあるため、出力信号のばたつきは生じない。

【0114】

(4) 位相差が90〔度〕以下になる出力電圧となると、位相差検出部102では、第2の実施の形態で述べた通り、リセット信号RESETが発生し、検出位相差が450〔度〕に制御される。この結果、この位相差制御FB系即ち、位相制御回路82では、目標位相差が90〔度〕(=−90〔度〕)に設定された場合でも、連続的な位相差検出特性の区間で制御することができる。

【0115】

(5) マイクロ波無線電力伝送装置等、複数の出力信号の位相差をある一定値に保つための位相差FB制御装置において、あらゆる位相差において連続的な入出力特性を実現できる。

【0116】

(6) 宇宙太陽光発電のマイクロ波電力伝送装置において、マイクロ波出力を送信する際に、マイクロ波出力の位相を制御することができ、電力伝送効率を最大に制御することができる。

【0117】

〔他の実施の形態〕

【0118】

(1) 上記実施の形態では、宇宙太陽光発電システムを例示したが、本発明は上記実施の形態に限定されない。例えば、電気自動車充電システム等のマイクロ波電力伝送装置にも適用でき、複数のマイクロ波信号の位相差を任意に設定する位相差制御フィードバック系の位相差検出及び位相制御に広く利用できる。

【0119】

(2) 本発明は上記実施の形態だけでなく、移動通信や映像伝送、ディジタルTV放送等の無線装置や光伝送装置、その他各種民生機器等に用いられる広帯域出力PLL回路に利用できる。

【0120】

(3) 第3の実施の形態では、信号入力In1側に二つのD−FFを設置して分周しているが、これに限定されない。即ち、一又は三以上のD−FFを設置してもよい。また、信号入力In2側に一つのD−FFを設置しているが、これに限定されない。即ち、信号入力In1側のD−FFによる分周段数をnとすれば、信号入力In2側のD−FFによる分周段数をn/2としてもよい。このような構成によれば、位相の検出範囲を上記実施の形態の720〔度〕から更に拡大し、位相差を求める構成としてもよい。この検出位相差により、位相制御を行う構成としてもよい。

【0121】

(4) 上記実施の形態では、ハードウェア構成について、ディスクリート素子を明示した論理回路等を示したが、本発明は係る構成に限定されない。記録媒体に格納されたプログラムの実行により、ディスクリート素子と同等の機能を実現するソフトウェアで構成された回路を用いてもよい。

【0122】

〔比較例〕

【0123】

上記実施の形態の比較例について図19及び図20を参照する。図19は位相比較器の入出力特性の一例を示す。また、図20は検出位相差の揺らぎを示している。

【0124】

従来のマイクロ波電力伝送装置における位相差制御FB系では、通常のPLL回路に用いられる位相比較器を利用し、対象となる送信マイクロ波の位相差を検出している。係る位相比較器では図19に示す入出力特性を持っている。この入出力特性例では、入力信号位相差−180〔度〕ないし+180〔度〕の位相差範囲に対し、位相差出力電圧〔V〕は、0〔V〕ないし5〔V〕である。

【0125】

そして、通常PLL回路では、図19に示す入出力特性で得た位相比較器出力をフィルタリングし、制御対象(VCO)にフィードバックすることにより、位相比較器出力電圧の中心値の付近即ち、位相差=0〔度〕、比較器出力電圧=2.5〔V〕に位相を制御している。

【0126】

これに対し、マイクロ波電力伝送装置の位相差制御FB系では、0〔度〕〜360〔度〕の任意の位相差に制御することが必要である。このような位相差制御FB系に、図19に示す入出力特性を持つ位相比較器を用いる場合には、次のような問題が生じる。

【0127】

位相差制御FB系の目標位相差に例えば、180〔度〕の位相差が設定されると、位相比較器出力は、最大値(Vmax=5〔V〕)付近に制御される。しかしながら、実際には制御対象の揺らぎがあるため、図20に示すように、検出位相差は、+180〔度〕ないし−180〔度〕の範囲でばたつき(位相差変動)を生じる。このため、位相比較器出力にも最大値(Vmax=+5〔V〕)と最小値(Vmin=0〔V〕)の範囲の大きなばたつき(電圧変動)を生じる。このような電圧変動を伴う電圧をフィルタリングした場合、得られる位相差検出出力信号は最大値(Vmax=+5〔V〕)と最小値(Vmin=0〔V〕)の中間値(Vmean=+2.5〔V〕)付近、即ち、位相差が0〔度〕となる。このため、所望の位相差(=180〔度〕)に制御することができない。このような課題は、上記実施の形態により解決されている。

【0128】

次に、以上述べた実施例を含む実施の形態に関し、更に以下の付記を開示する。以下の付記に本発明が限定されるものではない。

【0129】

(付記1) 二信号間の位相差を検出する位相差検出方法において、

前記二信号間の検出位相差をオフセット値によりシフトして出力し、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御する

ことを特徴とする位相差検出方法。

【0130】

(付記2) 前記オフセット値は、前記二信号の一方に対して加算し又は減算されることを特徴とする付記1に記載の位相差検出方法。

【0131】

(付記3) 前記二信号が第1の信号と第2の信号であり、

前記第1の信号の分周信号、前記第2の信号の反転信号及び非反転信号を生成し、

前記第1の信号の前記分周信号と、前記第2の信号の前記反転信号又は前記非反転信号とを比較して位相差を検出し、

該検出位相差が前記上限値又は前記下限値に到達したか否かを判定し、

該検出位相差が前記上限値又は前記下限値に到達した時点で前記反転信号を用いていれば前記非反転信号に切り替え、又は前記時点で前記非反転信号を用いていれば前記反転信号に切り替える

ことを特徴とする付記1に記載の位相差検出方法。

【0132】

(付記4) 二信号間の位相差を制御する位相制御方法において、

前記二信号間の検出位相差をオフセット値によりシフトして出力し、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御し、

前記位相差範囲内に制御された前記検出位相差と設定位相差との誤差を検出し、

該検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する

ことを特徴とする位相制御方法。

【0133】

(付記5) 二信号間の位相差を検出する位相差検出回路において、

前記二信号間の検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記位相差検出手段より出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

を備えることを特徴とする位相差検出回路。

【0134】

(付記6) 前記オフセット制御手段は、前記二信号の一方に前記オフセット値の加算又は減算を行う

ことを特徴とする付記5に記載の位相差検出回路。

【0135】

(付記7) 前記位相差検出手段は、前記二信号が第1の信号と第2の信号であり、前記第1の信号を分周するとともに、前記第2の信号の反転信号及び非反転信号を生成し、前記第1の信号の前記分周信号と、前記第2の信号の前記反転信号又は非反転信号とを比較して位相差を検出し、

前記オフセット制御手段は、前記検出位相差が前記上限値又は前記下限値に到達したか否かを判定する判定手段を含み、該判定手段の前記検出位相差の前記判定に基づき、前記検出位相差が前記上限値又は前記下限値に到達した時点で前記反転信号を用いていれば前記非反転信号に切り替え、又は前記時点で前記非反転信号を用いていれば前記反転信号に切り替える

ことを特徴とする付記5に記載の位相差検出回路。

【0136】

(付記8) 前記オフセット制御手段は、

前記位相検出手段で検出された前記検出位相を表す位相差パルスを直流信号に変換する信号変換手段と、

前記直流信号のレベルが上限レベル以上又は下限レベル以下で出力を発生する比較手段と、

前記比較手段の出力に基づき、前記オフセット値を切り替える制御信号を発生する制御信号生成部と、

を備えることを特徴とする付記5に記載の位相差検出回路。

【0137】

(付記9) 二信号間の位相差を制御する位相制御回路において、

前記二信号間の位相差を検出し、前記二信号間の検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

前記位相差検出手段より出力された前記検出位相差と、設定位相差との誤差を検出する誤差検出手段と、

前記誤差検出手段の検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する位相制御手段と、

を備えることを特徴とする位相制御回路。

【0138】

(付記10) 電力源と、

前記電力源の出力を無線信号に変換する複数の変換手段と、

これら変換手段の複数の無線信号から選択された二信号間の位相差を検出し、該検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

前記位相差検出手段より出力された前記検出位相差と、設定位相差との誤差を検出する誤差検出手段と、

前記誤差検出手段の検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する位相制御手段と、

を備えることを特徴とする無線電力伝送装置。

【0139】

以上説明したように、位相差検出方法、位相制御方法、位相差検出回路、位相制御回路及び無線電力伝送装置の最も好ましい実施の形態等について説明したが、本発明は、上記記載に限定されるものではなく、特許請求の範囲に記載され、又は発明を実施するための形態に開示された発明の要旨に基づき、当業者において様々な変形や変更が可能であることは勿論であり、斯かる変形や変更が、本発明の範囲に含まれることは言うまでもない。

【符号の説明】

【0140】

2、22 位相差検出回路

4、24 位相差検出部

6 オフセット制御部

26 位相比較部

28 オフセット部

30 LPF部

32 上限/下限判定部

34 リセット信号生成部

36 分周回路

41、42、43、44 D−FF

46、50 EXOR論理ゲート

48 SEL

52、53 コンパレータ

32H 上限判定部

32L 下限判定部

66 マイクロコンピュータ

74 電力源

75 太陽電池

76 電力/マイクロ波変換器

780、781、782・・・78N 位相制御送信部

82 位相制御回路

84 移相器

86 AMP

90、100 セレクタ

94 制御部

98 制御PC

102 位相差検出部

104 誤差検出部

106 プロセッサ

【技術分野】

【0001】

本発明は、信号間の位相差を検出する技術、信号間の位相を制御する技術に関する。

【背景技術】

【0002】

二信号間の位相差を検出する位相差検出回路は、PLL(Phase-Locked Loop :位相同期ループ)回路等、位相差制御FB(Feedback:フィードバック)系回路の位相差検出や位相制御に用いられる。

【0003】

信号間の位相差検出に関し、PLL回路において、信号間の位相差を−2π(−360度)から+2π(+360度)の範囲(4π)で検出することが知られている(例えば、特許文献1)。

【0004】

位相調整に関し、ループフィルタの出力からダイナミックレンジを検出し、ループフィルタの出力のダイナミックレンジを所定範囲内になるように、位相シフト回路を制御することが知られている(例えば、特許文献2)。また、動作点がダイナミックレンジの端に移動した場合には、ダイナミックレンジの中央値にリセットすることが知られている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−120515号公報

【特許文献2】特開平9−009285号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、信号間の位相差の検出範囲を例えば、0〜360〔度〕程度に広く設定しても、検出位相差で位相を制御する制御対象に揺らぎがあると、検出位相差が大きく変動する。例えば、検出位相差が+180〔度〕と−180〔度〕に変動すると、検出位相差を表すレベル出力は大きく変動する。このように変動を伴ったレベル出力は、位相差出力が大きく変動していても、フィルタリングすると、出力の中間値付近の位相差出力即ち、位相差0〔度〕の位相差出力となってしまう。このような位相差出力では変動する位相差に応じた位相制御が得られない。

【0007】

斯かる要求や課題について、特許文献1、2にはその開示や示唆はなく、それを解決する構成等についての開示や示唆もない。

【0008】

そこで、本開示の位相差検出方法、位相制御方法、位相差検出回路、位相制御回路又は無線電力伝送装置の目的は、上記課題に鑑み、二信号間の検出位相差の範囲の拡大とともに連続的な位相差出力特性を実現することにある。

【課題を解決するための手段】

【0009】

上記目的を達成するため、本開示の位相差検出方法、位相制御方法、位相差検出回路、位相制御回路又は無線電力伝送装置は、二信号間の位相差を検出し、検出位相差をオフセット値によりシフトして出力する。出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように、前記オフセット値が制御される。

【発明の効果】

【0010】

本開示の位相差検出方法、位相制御方法、位相差検出回路、位相制御回路又は無線電力伝送装置によれば、次の何れかの効果が得られる。

【0011】

(1) 検出位相差の範囲を拡大でき、連続した位相差出力特性を実現できる。

【0012】

(2) 検出位相差が大きく変動しても、下限値以上、上限値以下の検出範囲に検出位相差を制御でき、連続した位相差出力特性を得ることができる。

【0013】

(3) 位相差の検出範囲は、その範囲内に下限値及び上限値の設定により、任意の範囲を設定できる。

【0014】

そして、本発明の他の目的、特徴及び利点は、添付図面及び各実施の形態を参照することにより、一層明確になるであろう。

【図面の簡単な説明】

【0015】

【図1】第1の実施の形態に係る位相差検出回路を示す図である。

【図2】検出位相差の制御動作を示すフローチャートである。

【図3】位相差出力特性を示す図である。

【図4】第2の実施の形態に係る位相差検出回路を示す図である。

【図5】位相差出力特性を示す図である。

【図6】第3の実施の形態に係る位相差検出回路の構成例を示す回路図である。

【図7】エクスクルーシブOR論理ゲートの真理値表を示す図である。

【図8】位相差検出部の動作を示すタイムチャートである。

【図9】出力判定部及びリセット信号生成部の一例を示す図である。

【図10】出力判定部の動作を示すタイミングチャートである。

【図11】出力判定部のエクスクルーシブOR論理ゲートの真理値表を示す図である。

【図12】リセット信号生成部のマイクロコンピュータの構成例を示す図である。

【図13】位相差検出回路の動作を示すタイムチャートである。

【図14】位相差検出回路の動作を示すタイムチャートである。

【図15】第4の実施の形態に係るマイクロ波電力伝送装置を示す図である。

【図16】位相制御回路の構成例を示す回路図である。

【図17】制御用コンピュータの構成例を示す図である。

【図18】位相制御の制御動作を示すフローチャートである。

【図19】比較例を示す位相比較器の入出力特性を示す図である。

【図20】検出位相差の揺らぎを示す図である。

【発明を実施するための形態】

【0016】

〔第1の実施の形態〕

【0017】

第1の実施の形態について、図1を参照する。図1に示す位相差検出回路は一例であり、係る構成に本発明は限定されない。

【0018】

この位相差検出回路2は、本開示の位相差検出回路の一例である。図1に示す位相差検出回路2には、位相差検出部4と、オフセット制御部6とが備えられている。

【0019】

位相差検出部4は、二信号間の位相差を検出する位相検出手段の一例である。信号入力In1は前記二信号の一方である第1の信号の一例である。また、信号入力In2は前記二信号の他方である第2の信号の一例である。

【0020】

この位相差検出部4は位相差検出機能とオフセット機能を備える。位相差検出機能は、一例として、0〔度〕ないし720〔度〕の広い範囲で位相差を検出する。この位相差検出機能により、信号入力In1、In2間の位相差が検出される。この結果、検出位相差DPを表す位相差出力Opが得られる。この位相差出力Opは検出位相差DPを表す電気信号である。この位相差出力Opがオフセット制御部6に加えられる。

【0021】

オフセット機能は、信号入力In1、In2間の検出位相差をオフセット値によりシフトして出力する機能である。一例であるオフセット機能は、広い範囲の位相差検出機能を維持しながら、検出位相差を所定の範囲にシフトさせるためのオフセット値を加算又は減算する。即ち、オフセット制御部6からのオフセット制御信号OFCにより既述のオフセット値の加算又は減算が行われる。

【0022】

オフセット制御部6は、既述のオフセット値を制御する制御手段の一例である。このオフセット制御部6では、位相差出力Opに基づき、検出位相DPが所定の下限値PL 以上、上限値PH 以下になるように既述のオフセット値を制御する。この制御のため、オフセット制御部6では、位相差出力Opに基づき、検出位相DPが上限値PH 又は下限値PL に到達したか否かを判定する。検出位相DPが上限値PH 又は下限値PL に到達していれば、オフセット制御部6からオフセット制御信号OFCが得られる。上限値PH 及び下限値PL は位相差検出部4の位相差検出可能な範囲内に設定される。上限値PH はその位相差範囲の上端より小さい値である。下限値PL はその位相差範囲の下端より大きい値である。

【0023】

斯かる構成では、次のような位相差検出及び検出制御が行われる。位相差検出部4では、オフセット値+OF又は−OFで位相差検出が行われる。検出位相差DPが上限値PH 又は下限値PL に到達すれば、オフセット制御部6からオフセット制御信号OFCが出力される。このオフセット制御信号OFCは連続した信号でもよいし、検出位相差DPが上限値PH 又は下限値PL に到達したことを契機とする瞬間的な信号でもよい。

【0024】

この場合、オフセット値+OFで、検出位相差DPが上限値PH 又は下限値PL に到達すれば、オフセット値+OFからオフセット値−OFに変更される。その場合、その到達時点で、現行のオフセット値が−OFであれば、オフセット値+OFに変更される。即ち、検出位相差DPに応じてオフセット値の加算又は減算により、検出位相差DPが下限値PL 以上、上限値PH 以下の位相差範囲に制御される。

【0025】

この位相差検出及び制御の動作について、図2を参照する。図2に示す処理手順は一例であって、係る手順に限定されない。

【0026】

この動作手順は、本開示の位相差検出方法の一例である。図2に示す処理手順では、位相差検出(ステップS1)、出力判定(ステップS2、S3)、オフセット処理(ステップS4)を含んでいる。

【0027】

位相差検出(ステップS1)は、少なくとも二信号間の位相差を検出する処理である。この処理は、位相差検出部4で実行される。既述の二信号の一例として、信号入力In1と信号入力In2が位相差検出部4に加えられる。位相差検出部4では、既述の位相差検出機能により、信号入力In1、In2間の位相差が検出される。この処理により、検出位相差DPを表す位相差出力Opが得られる。

【0028】

出力判定(ステップS2、S3)では、検出位相差DPが上限値PH 又は下限値PL に到達したことを判定する。この出力判定は、検出位相差DPが上限値以上(DP≧PH )又は下限値以下(DP≦PL )に到達したことを判定する(ステップS3)。検出位相差DPが上限値以上(DP≧PH )又は下限値以下(DP≦PL )に到達した場合には(ステップS3のYES)、オフセット処理(ステップS4)に移行する。

【0029】

オフセット処理(ステップS4)は、位相差検出部4に対して既述のオフセット値OFの加算又は減算を行う処理である。検出位相差DPが上限値以上(DP≧PH )又は下限値以下(DP≦PL )に到達すれば、既述の位相差範囲に検出位相差DPがシフトするようにオフセット値OFの減算(又は加算)を行う。例えば、位相差検出部4の検出位相差DPが上限値PH に到達した時点で、設定中のオフセット値が+OFであれば、オフセット値−OFに変更する。また、設定中のオフセット値が−OFであれば、リセット信号RESETに基づき、オフセット値+OFに変更する。

【0030】

次に、オフセット処理の後、再び位相差検出(ステップS1)に戻り、同様の位相差検出を行う。ステップS3(出力判定)において、検出位相差DPが上限値以上(DP≧PH )又は下限値以下(DP≦PL )に到達していなければ(ステップS3のNO)、オフセット処理(ステップS4)に移行することなく、ステップS1に戻る。つまり、検出位相差DPが検出可能な位相差範囲Pr(PL <DP<PH )内にあれば、現状のオフセット値が維持される。

【0031】

このような位相差検出では、次のような利点がある。

【0032】

(1) 位相差検出において、連続的な位相差出力特性が得られる。

【0033】

この位相差出力特性について、図3を参照する。図3に示す位相差出力特性は、検出位相差(横軸)に対して位相差出力レベル(縦軸)を示している。検出位相差DPに応じて直線的な位相差出力レベルが得られている。検出位相差DPが上限値PH に到達すると、既述のオフセット値OFの加算又は減算により、位相差D1にシフトされる。また、検出位相差DPが下限値PL に到達すると、既述のオフセット値OFの加算又は減算により、位相差D2にシフトされる。つまり、検出位相差DPが上限値PH に到達すると、所定の位相差D1にシフトされ(即ち、シフト量=PH −D1)、また、下限値PL に到達すると、所定の位相差D2(>D1)にシフトされる(シフト量=PL +D2)。この結果、検出位相差を所定位相差だけ増加又は減少させるので、あらゆる位相差で連続的な位相差出力特性が得られる。

【0034】

(2) 検出位相差DPを位相差範囲Prにシフトさせるには、オフセット値に例えば、360〔度〕程度の任意の値を設定することができる。

【0035】

(3) 位相差検出部4の位相差検出機能において、位相検出可能な範囲は、既述の位相差範囲Prを超えて任意の値にできる。その検出可能な範囲において、連続的な位相差検出出力を得ることができる。

【0036】

〔第2の実施の形態〕

【0037】

第2の実施の形態について、図4を参照する。図4に示す位相差検出回路は一例であり、係る構成に本発明は限定されない。図4において、図1と同一部分には同一符号を付してある。

【0038】

この位相差検出回路22は、本開示の位相差検出回路の一例である。この位相差検出回路22は、例えば、0〜720〔度〕の位相差を検出する機能を備え、検出位相差DPの上限値PH 及び下限値PL を判定する。検出位相差DPの値が上限値PH 又は下限値PL に到達すれば、360〔度〕だけ加減させ、これにより、あらゆる位相差に対して連続的な位相差出力特性を実現する。

【0039】

図4に示す位相差検出回路22の位相差検出部24は信号間の位相差を検出する位相差検出手段の一例であり、位相比較部26と、オフセット部28とが備えられている。この位相差検出部24には位相差検出対象の一例である二信号として信号入力In1、In2が加えられている。位相差検出部24の出力側にはローパスフィルタ(Low-Pass Filter :LPF)部30が設置されている。そして、オフセット制御部6には上限/下限判定部32と、リセット信号生成部34とが設置されている。

【0040】

位相比較部26は、例えば、0ないし720〔度〕の位相差範囲で位相差を検出する機能を備えている。この位相比較部26には信号入力In1が入力され、信号入力In2がオフセット部28を介して入力されている。オフセット部28は、二信号の一方である信号入力In2側に設置されており、信号入力In2に対し、既述のオフセット値を設定する。位相比較部26は、信号入力In1と、オフセット値が設定された信号入力In2とを比較し、両者の位相差を0〜720〔度〕の範囲で検出する。従って、位相比較部26には検出位相差DPを表す位相差パルスPPが得られる。この位相差パルスPPのパルス幅が、検出位相差DPの大きさを表す。

【0041】

LPF部30は、位相差パルスPPを直流レベルに変換する信号変換手段の一例である。このLPF部30には位相差パルスPPが直流レベルに変換された既述の位相差出力Opが得られる。この位相差出力Opは、検出位相差DPの大きさに比例したレベルを持つ信号である。この位相差出力Opは、上限/下限判定部32に入力される。

【0042】

上限/下限判定部32は、検出位相差DPが上限値に到達したか又は下限値に到達したかの出力レベル判定手段の一例である。この上限/下限判定部32には予め基準値として、上限値Vth−HIと下限値Vth−LOが設定されている。上限値Vth−HIと下限値Vth−LOは、位相差出力Opと比較する直流電圧値である。そこで、位相差出力Opが上限値Vth−HI又は下限値Vth−LOに到達していれば、その判定出力が得られる。この判定出力はリセット信号生成部34に入力される。

【0043】

リセット信号生成部34は、上限/下限判定部32の判定出力に基づき、リセット信号RESETを生成する。このリセット信号RESETは、位相差検出部24のオフセット部28に入力される。

【0044】

斯かる構成では、リセット信号RESETがオフセット部28に加えられると、オフセット処理が実行される。即ち、リセット信号RESETの入力前に設定されていたオフセット値は、リセット信号RESETを受けて新たなオフセット値に変更される。つまり、オフセット値の変更により、リセット信号RESETの入力前の状態から例えば、オフセット値として例えば、180〔度〕の加算又は減算が行われる(後述のパルス反転)。これにより、信号入力In1、In2の位相差がいかなる値においても、位相差検出回路22の位相差出力Opが連続的に変化することとなる。

【0045】

この位相差検出回路22の位相差出力特性について、図5を参照する。図5に示す位相差出力特性は一例であり、係る特性に本発明が限定されない。

【0046】

図5は、一例として検出位相差DPの上限値PH を630〔度〕、下限値PL を90〔度〕に設定した場合の位相差出力特性である。横軸が検出位相差DP〔deg(=度)〕、縦軸が位相差出力レベル〔%〕である。この出力特性は、検出位相差DPに応じて位相差出力レベルの変化を示している。図5において、湾曲した矢印は位相シフト、双方向矢印は位相差変化を示す。

【0047】

検出位相差DPが630〔度〕を超える位相差出力Op(出力電圧)に到達すると、リセット信号生成部34にリセット信号RESETが発生する。これにより、検出位相差DPは−360〔度〕だけシフトされ、270〔度〕となる。この場合、検出位相差DPは270〔度〕より増減する。

【0048】

また、検出位相差DPが90〔度〕に到達すると、同様に、リセット信号生成部34にはリセット信号RESETが発生する。リセット信号RESETは、オフセット値を切り替える制御信号の一例であり、リセット信号生成部34は制御信号生成手段の一例である。これにより、検出位相差DPは+360〔度〕だけシフトされ、450〔度〕となる。この場合、検出位相差DPは450〔度〕より増減することになる。

【0049】

〔第3の実施の形態〕

【0050】

第3の実施の形態について、図6を参照する。図6に示す位相差検出回路22は一例であり、係る構成に本発明は限定されない。図6において、図4と同一部分には同一符号を付してある。

【0051】

図6に示す位相差検出回路22の位相差検出部24では、信号入力In1を位相差検出の基準(マスタ)側に、信号入力In2をスレーブ側に設定されている。信号入力In1側に設置されたこの分周回路36には、一例としてD形フリップフロップ(D−FF)41、42が設置されている。信号入力In1は、D−FF41にクロックとして入力され、このD−FF41で2分周される。D−FF41の出力A2は、D−FF42のクロックとして入力され、D−FF42で2分周される。この結果、分周回路36では、信号入力In1の4分周出力A4が得られる。この分周出力A4が位相比較部26のD−FF44及びエクスクルーシブOR(Exclusive:EXOR、排他的論理和)論理ゲート46に入力されている。

【0052】

オフセット部28は、信号入力In2側に設置されている。このオフセット部28は、一例としてD−FF43及び選択回路(Selector:SEL)48を備える。D−FF43は分周手段の一例である。信号入力In2は、D−FF43にクロックとして入力され、D−FF43で2分周される。D−FF43には非反転出力B2及び反転出力B2Xが得られる。SEL48は、非反転出力B2又は反転出力B2Xの選択手段の一例である。SEL48は、リセット信号RESETを受けることにより、非反転出力B2又は反転出力B2Xを出力する。例えば、リセット信号RESET=Hのとき、非反転出力B2から反転出力B2Xに切り替えられる。また、リセット信号RESET=Lのとき、反転出力B2Xから非反転出力B2に切り替えられる。非反転出力B2又は反転出力B2Xは、位相比較部26のD−FF44のCLK入力に加えられる。

【0053】

位相比較部26は、一例としてD−FF44及びEXOR論理ゲート46を備えている。D−FF44には、D−FF43の反転出力B2X又は非反転出力B2がクロックとして入力される。従って、D−FF44では、D−FF42の出力が反転出力B2X又は非反転出力B2によりゲーティングされる。そして、EXOR論理ゲート46には、D−FF42の出力A4と、D−FF44の出力が加えられている。従って、EXOR論理ゲート46には、信号入力In1を基準にして信号入力In2の位相差が検出され、検出位相差DPを表す位相差パルスPPが得られる。

【0054】

D−FF42、44の出力とEXOR論理ゲート46の出力について、図7を参照する。図7は、EXOR論理ゲート46の真理値表を示している。各D−FF42、44の出力が共にL(低レベル)出力又はH(高レベル)出力の場合、両者の排他的論理和により、EXOR論理ゲート46の出力はL出力となる。D−FF42、44の出力の一方がL出力又は他方がH出力の場合、両者の排他的論理和により、EXOR論理ゲート46の出力はH出力となる。即ち、EXOR論理ゲート46のH出力区間が検出位相差DPを示している。

【0055】

この位相差検出部24の論理動作について、図8を参照する。図8に示すタイムチャートは、位相差検出部24の各部の論理動作を示しており、この論理動作に本発明が限定されない。

【0056】

図8のAは信号入力In1、図8のDは信号入力In2を示している。この例では、信号入力In1、In2の1周期の区間がθB =360〔度〕に設定され、そのH出力区間がθA =180〔度〕、そのL出力区間が180〔度〕である。従って、信号入力In1、In2の2周期の区間がθC =720〔度〕である。

【0057】

信号入力In1がクロックとして入力されたD−FF41には、図8のBに示す出力A2が得られる。出力A2は、1周期がθC =720〔度〕であり、そのH出力区間がθB =360〔度〕、そのL出力区間が360〔度〕である。この出力A2がクロックとして入力されたD−FF42には、図8のCに示す出力A4が得られる。出力A4は、1周期が1440〔度〕であり、そのH出力区間が720〔度〕、そのL出力区間が720〔度〕である。

【0058】

信号入力In2がクロックとして入力されたD−FF43には、720〔度〕を1周期とする非反転出力B2及び反転出力B2Xが得られる。リセット信号RESETがRESET=Hであれば、図8のEに示すように、SEL48で非反転出力B2が選択される。リセット信号RESETがRESET=Lであれば、図8のFに示すように、SEL48で反転出力B2Xが選択される。つまり、リセット信号RESETのH/Lが切り替わると、SEL48の出力が非反転出力B2又は反転出力B2X出力に切り替えられる。

【0059】

RESET=Hのとき、D−FF44では出力A4が非反転出力B2でゲーティングされ、図8のGに示す出力が得られる。EXOR論理ゲート46では、出力A4とD−FF44の出力との排他的論理和(一方がH出力、他方がL出力)により、図8のHに示す出力(位相差パルスPP)が得られる。

【0060】

RESET=Lのとき、D−FF44では出力A4が反転出力B2Xでゲーティングされ、図8のIに示す出力が得られる。EXOR論理ゲート46では、出力A4とD−FF44の出力との排他的論理和(一方がH出力、他方がL出力)により、図8のJに示す出力が得られる(位相差パルスPP)。この場合、図8のH及びJに示す位相差パルスPPのH出力区間は180〔度〕相当のパルス幅差分である。

【0061】

次に、上限/下限判定部32、リセット信号生成部34及びこれらの動作について、図9、図10及び図11を参照する。図9は上限/下限判定部32及びリセット信号生成部34の構成例を示し、図10は上限/下限判定部32の動作を示し、図11は上限/下限判定部32のEXOR論理ゲートの真理値表を示している。係る構成及び動作に本発明は限定されない。図9において、図4と同一部分には同一符号を付してある。

【0062】

図9に示す上限/下限判定部32では一例として上限判定部32Hと、下限判定部32Lと、EXOR論理ゲート50とが含まれる。即ち、上限/下限判定部32は、検出位相差が上限値以上又は下限値以下を判定するウインドコンパレータを構成している。

【0063】

上限判定部32Hにはコンパレータ52が設置され、下限判定部32Lにはコンパレータ53が設置されている。コンパレータ52には、基準入力として上限電圧Vth−HIが設定され、コンパレータ53には、基準入力として下限電圧Vth−LOが設定されている。上限電圧Vth−HIの生成には、抵抗54、56の分圧回路58が用いられている。この場合、直流電圧を抵抗54、56の抵抗比で分圧することにより、上限基準電圧Vth−HIが設定される。また、下限電圧Vth−LOの生成には、抵抗60、62の分圧回路64が用いられている。この場合、直流電圧を抵抗60、62の抵抗比で分圧することにより、下限電圧Vth−LOが設定される。

【0064】

この上限/下限判定部32では、図10のAに示すように、コンパレータ52は、位相差出力Opのレベルが上限電圧Vth−HI以上では、図10のBに示すH出力、またVth−HI以下ではL出力となる。また、コンパレータ53は、位相差出力Opが下限電圧Vth−LO以下では図10のCに示すL出力、下限電圧Vth−LO以上ではH出力となる。

【0065】

各コンパレータ52、53の各出力が入力されるEXOR論理ゲート50では、図11に示す真理値表に記載された論理動作となる。各コンパレータ52、53で得られる各出力H/Lが相違しているとき、図10のDに示すように、EXOR論理ゲート50はH出力を発生する。また、各コンパレータ52、53の各出力がH又はLで一致していれば、EXOR論理ゲート50はL出力(図10のDのL)を発生する。即ち、検出位相差が下限値以下、上限値以上でL出力となり、検出位相差が下限値以上、上限値以下でH出力となる。

【0066】

そして、EXOR論理ゲート50の出力側に設置されたリセット信号生成部34は、一例としてマイコン(UPC)66で構成される。このマイコン66は、EXOR論理ゲート50の出力即ち、上限/下限判定部32の判定出力がL出力であれば、リセット信号RESETを現状出力から反転値に切り替える。即ち、現状出力がH出力であれば反転出力Lに切り替えられ、又は現状出力がLであればその反転値である非反転出力Hに切り替えられる。

【0067】

このマイクロコンピュータ66について、図12を参照する。図12に示すマイクロコンピュータの構成は一例であり、係る構成に本発明は限定されない。

【0068】

図12に示すマイクロコンピュータ66では、プロセッサ68、メモリ部70及び入出力部(I/O)72を備えている。メモリ部70にはプログラムを格納するROM(Read-Only Memory)や、データを格納するRAM(Random-Access Memory)を備えている。斯かる構成では、I/O72にEXOR論理ゲート50の出力が取り込まれ、EXOR論理ゲート50の出力がLからHに遷移したとき、出力中のリセット信号RESETを現状出力からその反転値に切り替えて出力する。

【0069】

この実施の形態の位相差検出回路22(図6)の動作について、図13及び図14を参照する。図13は、LPF部30の出力が下限電圧Vth−LOに到達する過程の動作を示している。また、図14は、LPF部30の出力が上限電圧Vth−HIに到達する過程の動作を示している。

【0070】

図13のAに示す信号入力In1は既述したように、分周回路36で4分周され、D−FF42には、図13のDに示す出力A4が得られる。図13のBに示す信号入力In2は既述したように、D−FF43で2分周される。このとき、RESET=Lであれば、SEL48では、D−FF43の非反転出力B2が選択され、図13のCに示す非反転出力B2が得られる。

【0071】

D−FF44では、クロックにD−FF43の非反転出力B2が加えられ、D−FF42の出力がゲーティングされ、図13のEに示す出力が得られる。EXOR論理ゲート46では、D−FF42の出力A4とD−FF44の出力の排他的論理和により、図13のFに示す出力が得られる。

【0072】

この場合、EXOR論理ゲート46の出力パルスのH区間が徐々に小さくなると、LPF部30の出力は図13のGに示すように、徐々に低下する。LPF部30の出力(位相差出力Op)が下限電圧Vth−LOに到達すると、EXOR論理ゲート50がL出力(図10のD)を発生する。このL出力により、リセット信号生成部34のマイコン66が図13のHに示すリセット信号RESETを発生する。この場合、現行のリセット信号がRESET=Lとすれば、その反転値として、RESET=Hに切り替わる。

【0073】

この時点からSEL48の出力が、RESET=Hへの遷移を契機に、即ち、その時点で図13のCに示すように、非反転出力B2から反転出力B2Xに切り替えられる。これにより、検出位相差がシフトし、LPF部30の出力は、図13のGに示すように、時点t1以降では下限電圧Vth−LOより高い値に回復する。

【0074】

この場合も、図14のAに示す信号入力In1は分周回路36で4分周され、D−FF42には図14のDに示す出力A4が得られる。また、図14のBに示す信号入力In2がD−FF43で2分周され、このとき、RESET=Hであるので、SEL48では、D−FF43の反転出力B2Xが選択され、図14のCに示す反転出力B2Xが得られる。

【0075】

D−FF44では、クロックにD−FF43の反転出力B2Xが加えられ、D−FF42の出力がゲーティングされ、図14のEに示す出力が得られる。EXOR論理ゲート46では、D−FF42の出力A4とD−FF44の出力の排他的論理和により、図14のFに示す出力が得られる。

【0076】

この場合、EXOR論理ゲート46の出力パルスのH区間が徐々に大きくなると、LPF部30の出力は図14のGに示すように、徐々に上昇する。LPF部30の出力(位相差出力Op)が上限電圧Vth−HIに到達すると、EXOR論理ゲート50が出力L(図10のD)を発生する。この出力Lにより、リセット信号生成部34のマイコン66が図14のHに示すリセット信号RESETを発生する。この場合、現行のリセット信号がRESET=Hとすれば、その反転値として、RESET=Lに切り替えられる。

【0077】

この時点からSEL48の出力が、RESET=Lへの遷移を契機に、図14のCに示すように、非反転出力B2から反転出力B2Xに切り替えられる。これにより、検出位相差がシフトし、LPF部30の出力は、図14のGに示すように、時点t2以降では上限電圧Vth−HIより低い値に回復する。

【0078】

このような動作により、検出位相差が下限値未満となり又は上限値を超えても、下限値以上、上限値以下の位相検出範囲に制御され、連続した位相差検出を行うことができる。

【0079】

以上述べた第3の実施の形態について、利点や特徴事項を以下に列挙する。

【0080】

(1) 一例として0〜720〔度〕の位相差検出機能を備え、検出位相差が上限値及び下限値に到達したことを判定し、位相差検出値を一定位相差として例えば、180〔度〕だけを加減させる。この結果、信号入力のあらゆる位相差に対し、連続的な位相差出力特性を実現できる。従って、位相差を検出する二信号の入力位相差が0〜360〔度〕のいかなる値でも、連続的な出力が得られる。

【0081】

(2) 上記位相差検出回路22では、0〜720度の位相差と、位相差検出値を位相差検出範囲の上限及び下限で180〔度〕だけ加減する構成を備える。

【0082】

(3) 位相差検出回路22では、上限及び下限で位相差検出値を180〔度〕だけを加減する処理に、検出位相差に相当するパルス信号を直流信号に変換するLPF部30の出力と、コンパレータ52、53とを含む構成で実現している。

【0083】

(4) 位相差検出回路22では、上限及び下限で位相差検出値を180〔度〕だけ加減する処理に、D−FF43の反転出力と非反転出力を、リセット信号生成部34が発生するリセット信号RESETで切り替える構成を備えている。

【0084】

(5) 二信号の位相差検出において、一方の信号入力In1側を二つのD−FF41、42の分周出力と、他方の信号入力In2側を一つのD−FF43の分周出力(反転出力及び非反転出力)とを用いることにより、位相差を検出している。

【0085】

(6) 位相差の検出では、D−FF44とEXOR論理ゲート46とを用いている。D−FF44では、D−FF42の分周出力をD−FF43の反転出力及び非反転出力でゲーティングし、EXOR論理ゲート46で、D−FF42の出力と、D−FF44の出力との排他的論理和により、検出位相差をパルス幅に変換して出力させている。

【0086】

(7) リセット信号生成部34では一例として、マイクロコンピュータ66を用いることにより、上限/下限判定出力部32の出力値がHになった場合、リセット信号RESETを生成する。現状出力がRESET=Hであれば、上限/下限判定出力部32の出力値がHになった場合に、リセット信号RESETは反転値に切り替えられる。つまり現状出力がRESET=Hであれば、RESET=Lに切り替えている。これにより、位相差の連続的な検出出力を得ることができる。

【0087】

〔第4の実施の形態〕

【0088】

第4の実施の形態について、図15を参照する。図15に示すマイクロ波電力伝送装置は一例であり、係る構成に本発明は限定されない。

【0089】

図15に示すマイクロ波電力伝送装置70は、本開示の無線電力伝送装置の一例であり、宇宙太陽光発電の出力をマイクロ波伝送する。このマイクロ波電力伝送装置70には、電力源74が設置され、この電力源74には一例として、太陽電池75が用いられている。太陽電池75は、太陽光により発電する。この電力源74は、例えば、宇宙空間に設置されるが、地球上に設置されてもよい。

【0090】

この電力源74の出力側には複数の電力/マイクロ波変換器76が設置され、この電力/マイクロ波変換器76の出力側には位相制御送信部780、781、782・・78Nが個別に設置されている。各電力/マイクロ波変換器76は電力を送信可能な無線信号の一例として、6〔GHz〕程度の周波数のマイクロ波に変換する。位相制御送信部780、781、782・・・78Nは、本開示の位相制御方法及び位相制御回路の一例である。

【0091】

電力源74で得られた電力は、各電力/マイクロ波変換器76により各マイクロ波M0 、M1 、M2 、M3 ・・・MN に変換され、各マイクロ波M0 、M1 、M2 、M3 ・・・MN は、位相制御送信部780、781、782・・78Nに加えられる。位相制御送信部780、781、782・・78Nでは、電力/マイクロ波変換器76からのマイクロ波出力を送信する際、電力伝送効率が最大となるように、マイクロ波出力位相を任意の値に制御する。出力位相が制御されたマイクロ波出力は、各アンテナ80により個別に電力受給先に送信される。

【0092】

このマイクロ波電力伝送装置70の位相制御回路について、図16を参照する。図16に示す位相制御回路は一例であり、斯かる構成に本発明が限定されない。図16において、図15と同一部分には同一符号を付してある。

【0093】

図16に示す位相制御回路82は、本開示の位相制御方法及び位相制御回路の一例である。この位相制御回路82は、既述のマイクロ波電力伝送装置70において、位相差制御フィードバック系を構成している。この位相制御回路82では、複数の位相制御送信部780、781、782・・78Nの一つである例えば、位相制御送信部780を基準(マスタ)側に他の位相制御送信部781、782・・78Nをスレーブ側に設定する。

【0094】

各位相制御送信部780、781、782・・78Nのそれぞれには移相器84及び増幅器(AMP)86が設置されている。各移相器84には既述の電力/マイクロ波変換器76からマイクロ波M0 、M1 、M2 、M3 ・・・MN が入力される。AMP86は既述の位相制御送信部780、781・・・78Nの例えば、終段増幅器である。このAMP86にはアンテナ80が接続され、既述のマイクロ波が送信される。この実施の形態では、各AMP86からマイクロ波M0 、M1 、M2 、M3 ・・・MN の各信号から位相θ0 、θ1 、θ2 、θ3 ・・・θN が検出される。従って、各AMP86は各位相θ0 、θ1 、θ2 、θ3 ・・・θN の検出手段の一例である。

【0095】

各AMP86で検出された各位相θi(=θ1 、θ2 、θ3 ・・・θN )は、第1のセレクタ90により選択されて制御部94の位相差検出部102に加えられる。セレクタ90は、各位相θ1 、θ2 、θ3 ・・・θN の選択手段の一例である。セレクタ90は、制御用パーソナルコンピュータ(制御PC)98からセレクト信号により制御され、位相θ1 、θ2 、θ3 ・・・θN の何れかが順次に選択される。

【0096】

制御PC98は、セレクタ90に対するセレクト信号を出力するとともに、第2のセレクタ100に対するセレクト信号を同期して出力する。制御PC98は、基準位相φ0及び目標位相差Δφを出力する。セレクタ100は位相制御の対象であるスレーブ側の移相器84を選択する。

【0097】

制御部94では、基準側AMP86の検出位相θ0 と、セレクタ90で選択された既述の位相θiとの位相差Δθ(=θi−θ0 )を検出する。この制御部94では、この検出位相差Δθを目標位相差Δφと比較し、誤差を求める。一例である制御部94は、位相差検出部102と誤差検出部104とを備えている。

【0098】

位相差検出部102は、既述の位相差検出回路2(図1)又は位相差検出回路22(図4)で構成される。セレクタ90では、既述の位相θiから、例えば、位相θi=θ1 が選択される。基準側のAMP86から基準位相φ0に設定された位相出力θ0 が得られる。

【0099】

位相差検出部102では、位相θ0 と位相θ1 が比較され、検出位相差Δθ=θi−θ0 =θ1 −θ0 が求められる。この検出位相差Δθが誤差検出部104に加えられる。誤差検出部104では、検出位相差Δθと、制御PC98で設定された目標位相差Δφとが比較され、位相差誤差が求められる。この位相差誤差が位相制御信号としてのセレクタ100に加えられる。セレクタ90、100は、この場合、位相出力θ1 に関する一つの制御対象を選択するので、位相θ1 を取り出した移相器84に位相制御信号が加えられ、マイクロ波M1 の位相θ1 が制御される。この場合、制御PC98に設定された目標位相差Δφに検出位相差Δθが到達するように、位相θ1 が制御される。

【0100】

この位相制御回路82の制御PC98には、例えば、パーソナルコンピュータで構成すればよい。図17に示す制御PC98は一例であり、係る構成に本発明が限定されない。図17に示す制御PC98では、プロセッサ106と、メモリ部108と、RAM110と、入出力部112とをバス114で接続している。プロセッサ106は、メモリ部108にあるプログラムを実行し、既述のセレクタ90、100に対するセレクト信号を生成する。

【0101】

メモリ部108は、プログラム記憶部116と、データ記憶部118を備える。プログラム記憶部116にはOS(Operating System)や既述の位相制御のための位相制御プログラム等の各種アプリケーションプログラムが記録される。データ記憶部118には目標位相差Δφ、基準位相φ0、検出されたデータや演算途上のデータが格納される。従って、メモリ部108には、ハードディスクドライブ、CD、DVD等のROM、半導体メモリ等の各種の記録媒体を用いることができる。RAM110は一時的にデータを格納し、実行するプログラムのワークエリアを構成する。

【0102】

入出力部112では、プロセッサ106の制御により、制御部94からの誤差検出信号を受け、また、既述の基準位相φ0、目標位相差Δφが設定され、セレクタ90に対するセレクト信号S1 、セレクタ100に対するセレクト信号S2 が出力される。

【0103】

この位相制御回路82の位相差制御について、図18を参照する。図18に示す位相差制御の処理手順は一例であり、係る手順に本発明は限定されない。

【0104】

この処理手順は、本開示の位相制御方法の一例である。図18に示す処理手順では、セレクタ90により制御対象である位相θi(=θ1 、θ2 ・・・θN )の何れかが選択される(ステップS11)。これに対応してセレクタ100によりマイクロ波M1 〜M4 の何れかが選択され、例えば、位相θ1 の場合には、その入力側のマイクロ波M1 が選択される。

【0105】

検出位相θiとマスタ側の基準位相θ0 とが比較され、この場合、Δθ=θi−θ0 により位相差Δθが検出される(ステップS12)。この検出位相差Δθは、制御PC98の目標位相差Δφと比較され、検出位相差Δθの目標位相差Δφに対する誤差が求められる(ステップS13)。

【0106】

この誤差により位相制御が行われる(ステップS14)。この場合、セレクタ100を通じて位相制御送信部781の移相器84が選択され、その制御入力となる。これにより、マイクロ波M1の位相がシフトされる。

【0107】

検出位相差Δθが目標位相差Δφに一致したか否かを判断する(ステップS15)。検出位相差Δθが目標位相差Δφに一致していなければ(ステップS15のNO)、ステップS12に戻り、継続して位相制御を行う。

【0108】

そして、検出位相差Δθが目標位相差Δφに一致すれば(ステップS15のYES)、ステップS11に戻り、次の位相θ2 ・・・θN の何れかを選択し、同様に制御する位相制御送信部782〜78Nの移相器84の何れかが選択される。既述の位相制御が継続的に実行される。

【0109】

従って、マイクロ波送信中、マイクロ波出力の位相が設定位相に制御され、その結果、最大の電力伝送効率を得られ、維持される。

【0110】

この第4の実施の形態について、以下に特徴事項や利点を列挙する。

【0111】

(1) マイクロ波出力位相の制御は、複数の位相制御送信部780、781、782・・・78Nの中から何れか一つの例えば、位相制御送信部780を基準送信部、その他の位相制御送信部780、781、782・・・78Nをスレーブ送信部とし、これらの位相差を検出することにより位相制御を行っている。

【0112】

(2) 制御PC98から各位相制御送信部780、781、782・・・78Nに対する目標位相差Δφが出力される。誤差検出器104では、目標位相差Δφ(設定位相差)と検出位相差Δθとを比較して誤差が算出される。この誤差出力をスレーブ側の対応する位相制御送信部781、782・・・78Nの移相器84に位相制御値として入力し、目標位相差Δφに制御している。

【0113】

(3) このような位相差制御FB系を構成する位相制御回路82では、目標位相差Δφが270〔度〕(=−90〔度〕)に設定された場合、制御対象(例えば、位相制御送信部780、781、782・・・78N)に揺らぎが発生しても位相差検出部102の出力は連続的な区間にあるため、出力信号のばたつきは生じない。

【0114】

(4) 位相差が90〔度〕以下になる出力電圧となると、位相差検出部102では、第2の実施の形態で述べた通り、リセット信号RESETが発生し、検出位相差が450〔度〕に制御される。この結果、この位相差制御FB系即ち、位相制御回路82では、目標位相差が90〔度〕(=−90〔度〕)に設定された場合でも、連続的な位相差検出特性の区間で制御することができる。

【0115】

(5) マイクロ波無線電力伝送装置等、複数の出力信号の位相差をある一定値に保つための位相差FB制御装置において、あらゆる位相差において連続的な入出力特性を実現できる。

【0116】

(6) 宇宙太陽光発電のマイクロ波電力伝送装置において、マイクロ波出力を送信する際に、マイクロ波出力の位相を制御することができ、電力伝送効率を最大に制御することができる。

【0117】

〔他の実施の形態〕

【0118】

(1) 上記実施の形態では、宇宙太陽光発電システムを例示したが、本発明は上記実施の形態に限定されない。例えば、電気自動車充電システム等のマイクロ波電力伝送装置にも適用でき、複数のマイクロ波信号の位相差を任意に設定する位相差制御フィードバック系の位相差検出及び位相制御に広く利用できる。

【0119】

(2) 本発明は上記実施の形態だけでなく、移動通信や映像伝送、ディジタルTV放送等の無線装置や光伝送装置、その他各種民生機器等に用いられる広帯域出力PLL回路に利用できる。

【0120】

(3) 第3の実施の形態では、信号入力In1側に二つのD−FFを設置して分周しているが、これに限定されない。即ち、一又は三以上のD−FFを設置してもよい。また、信号入力In2側に一つのD−FFを設置しているが、これに限定されない。即ち、信号入力In1側のD−FFによる分周段数をnとすれば、信号入力In2側のD−FFによる分周段数をn/2としてもよい。このような構成によれば、位相の検出範囲を上記実施の形態の720〔度〕から更に拡大し、位相差を求める構成としてもよい。この検出位相差により、位相制御を行う構成としてもよい。

【0121】

(4) 上記実施の形態では、ハードウェア構成について、ディスクリート素子を明示した論理回路等を示したが、本発明は係る構成に限定されない。記録媒体に格納されたプログラムの実行により、ディスクリート素子と同等の機能を実現するソフトウェアで構成された回路を用いてもよい。

【0122】

〔比較例〕

【0123】

上記実施の形態の比較例について図19及び図20を参照する。図19は位相比較器の入出力特性の一例を示す。また、図20は検出位相差の揺らぎを示している。

【0124】

従来のマイクロ波電力伝送装置における位相差制御FB系では、通常のPLL回路に用いられる位相比較器を利用し、対象となる送信マイクロ波の位相差を検出している。係る位相比較器では図19に示す入出力特性を持っている。この入出力特性例では、入力信号位相差−180〔度〕ないし+180〔度〕の位相差範囲に対し、位相差出力電圧〔V〕は、0〔V〕ないし5〔V〕である。

【0125】

そして、通常PLL回路では、図19に示す入出力特性で得た位相比較器出力をフィルタリングし、制御対象(VCO)にフィードバックすることにより、位相比較器出力電圧の中心値の付近即ち、位相差=0〔度〕、比較器出力電圧=2.5〔V〕に位相を制御している。

【0126】

これに対し、マイクロ波電力伝送装置の位相差制御FB系では、0〔度〕〜360〔度〕の任意の位相差に制御することが必要である。このような位相差制御FB系に、図19に示す入出力特性を持つ位相比較器を用いる場合には、次のような問題が生じる。

【0127】

位相差制御FB系の目標位相差に例えば、180〔度〕の位相差が設定されると、位相比較器出力は、最大値(Vmax=5〔V〕)付近に制御される。しかしながら、実際には制御対象の揺らぎがあるため、図20に示すように、検出位相差は、+180〔度〕ないし−180〔度〕の範囲でばたつき(位相差変動)を生じる。このため、位相比較器出力にも最大値(Vmax=+5〔V〕)と最小値(Vmin=0〔V〕)の範囲の大きなばたつき(電圧変動)を生じる。このような電圧変動を伴う電圧をフィルタリングした場合、得られる位相差検出出力信号は最大値(Vmax=+5〔V〕)と最小値(Vmin=0〔V〕)の中間値(Vmean=+2.5〔V〕)付近、即ち、位相差が0〔度〕となる。このため、所望の位相差(=180〔度〕)に制御することができない。このような課題は、上記実施の形態により解決されている。

【0128】

次に、以上述べた実施例を含む実施の形態に関し、更に以下の付記を開示する。以下の付記に本発明が限定されるものではない。

【0129】

(付記1) 二信号間の位相差を検出する位相差検出方法において、

前記二信号間の検出位相差をオフセット値によりシフトして出力し、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御する

ことを特徴とする位相差検出方法。

【0130】

(付記2) 前記オフセット値は、前記二信号の一方に対して加算し又は減算されることを特徴とする付記1に記載の位相差検出方法。

【0131】

(付記3) 前記二信号が第1の信号と第2の信号であり、

前記第1の信号の分周信号、前記第2の信号の反転信号及び非反転信号を生成し、

前記第1の信号の前記分周信号と、前記第2の信号の前記反転信号又は前記非反転信号とを比較して位相差を検出し、

該検出位相差が前記上限値又は前記下限値に到達したか否かを判定し、

該検出位相差が前記上限値又は前記下限値に到達した時点で前記反転信号を用いていれば前記非反転信号に切り替え、又は前記時点で前記非反転信号を用いていれば前記反転信号に切り替える

ことを特徴とする付記1に記載の位相差検出方法。

【0132】

(付記4) 二信号間の位相差を制御する位相制御方法において、

前記二信号間の検出位相差をオフセット値によりシフトして出力し、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御し、

前記位相差範囲内に制御された前記検出位相差と設定位相差との誤差を検出し、

該検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する

ことを特徴とする位相制御方法。

【0133】

(付記5) 二信号間の位相差を検出する位相差検出回路において、

前記二信号間の検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記位相差検出手段より出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

を備えることを特徴とする位相差検出回路。

【0134】

(付記6) 前記オフセット制御手段は、前記二信号の一方に前記オフセット値の加算又は減算を行う

ことを特徴とする付記5に記載の位相差検出回路。

【0135】

(付記7) 前記位相差検出手段は、前記二信号が第1の信号と第2の信号であり、前記第1の信号を分周するとともに、前記第2の信号の反転信号及び非反転信号を生成し、前記第1の信号の前記分周信号と、前記第2の信号の前記反転信号又は非反転信号とを比較して位相差を検出し、

前記オフセット制御手段は、前記検出位相差が前記上限値又は前記下限値に到達したか否かを判定する判定手段を含み、該判定手段の前記検出位相差の前記判定に基づき、前記検出位相差が前記上限値又は前記下限値に到達した時点で前記反転信号を用いていれば前記非反転信号に切り替え、又は前記時点で前記非反転信号を用いていれば前記反転信号に切り替える

ことを特徴とする付記5に記載の位相差検出回路。

【0136】

(付記8) 前記オフセット制御手段は、

前記位相検出手段で検出された前記検出位相を表す位相差パルスを直流信号に変換する信号変換手段と、

前記直流信号のレベルが上限レベル以上又は下限レベル以下で出力を発生する比較手段と、

前記比較手段の出力に基づき、前記オフセット値を切り替える制御信号を発生する制御信号生成部と、

を備えることを特徴とする付記5に記載の位相差検出回路。

【0137】

(付記9) 二信号間の位相差を制御する位相制御回路において、

前記二信号間の位相差を検出し、前記二信号間の検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

前記位相差検出手段より出力された前記検出位相差と、設定位相差との誤差を検出する誤差検出手段と、

前記誤差検出手段の検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する位相制御手段と、

を備えることを特徴とする位相制御回路。

【0138】

(付記10) 電力源と、

前記電力源の出力を無線信号に変換する複数の変換手段と、

これら変換手段の複数の無線信号から選択された二信号間の位相差を検出し、該検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

前記位相差検出手段より出力された前記検出位相差と、設定位相差との誤差を検出する誤差検出手段と、

前記誤差検出手段の検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する位相制御手段と、

を備えることを特徴とする無線電力伝送装置。

【0139】

以上説明したように、位相差検出方法、位相制御方法、位相差検出回路、位相制御回路及び無線電力伝送装置の最も好ましい実施の形態等について説明したが、本発明は、上記記載に限定されるものではなく、特許請求の範囲に記載され、又は発明を実施するための形態に開示された発明の要旨に基づき、当業者において様々な変形や変更が可能であることは勿論であり、斯かる変形や変更が、本発明の範囲に含まれることは言うまでもない。

【符号の説明】

【0140】

2、22 位相差検出回路

4、24 位相差検出部

6 オフセット制御部

26 位相比較部

28 オフセット部

30 LPF部

32 上限/下限判定部

34 リセット信号生成部

36 分周回路

41、42、43、44 D−FF

46、50 EXOR論理ゲート

48 SEL

52、53 コンパレータ

32H 上限判定部

32L 下限判定部

66 マイクロコンピュータ

74 電力源

75 太陽電池

76 電力/マイクロ波変換器

780、781、782・・・78N 位相制御送信部

82 位相制御回路

84 移相器

86 AMP

90、100 セレクタ

94 制御部

98 制御PC

102 位相差検出部

104 誤差検出部

106 プロセッサ

【特許請求の範囲】

【請求項1】

二信号間の位相差を検出する位相差検出方法において、

前記二信号間の検出位相差をオフセット値によりシフトして出力し、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御する

ことを特徴とする位相差検出方法。

【請求項2】

前記二信号が第1の信号と第2の信号であり、

前記第1の信号の分周信号、前記第2の信号の反転信号及び非反転信号を生成し、

前記第1の信号の前記分周信号と、前記第2の信号の前記反転信号又は前記非反転信号とを比較して位相差を検出し、

該検出位相差が前記上限値又は前記下限値に到達したか否かを判定し、

該検出位相差が前記上限値又は前記下限値に到達した時点で前記反転信号を用いていれば前記非反転信号に切り替え、又は前記時点で前記非反転信号を用いていれば前記反転信号に切り替える

ことを特徴とする請求項1に記載の位相差検出方法。

【請求項3】

二信号間の位相差を制御する位相制御方法において、

前記二信号間の検出位相差をオフセット値によりシフトして出力し、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御し、

前記位相差範囲内に制御された前記検出位相差と設定位相差との誤差を検出し、

該検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する

ことを特徴とする位相制御方法。

【請求項4】

二信号間の位相差を検出する位相差検出回路において、

前記二信号間の検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記位相差検出手段より出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

を備えることを特徴とする位相差検出回路。

【請求項5】

前記位相差検出手段は、前記二信号が第1の信号と第2の信号であり、前記第1の信号を分周するとともに、前記第2の信号の反転信号及び非反転信号を生成し、前記第1の信号の前記分周信号と、前記第2の信号の前記反転信号又は非反転信号とを比較して位相差を検出し、

前記オフセット制御手段は、前記検出位相差が前記上限値又は前記下限値に到達したか否かを判定する判定手段を含み、該判定手段の前記検出位相差の前記判定に基づき、前記検出位相差が前記上限値又は前記下限値に到達した時点で前記反転信号を用いていれば前記非反転信号に切り替え、又は前記時点で前記非反転信号を用いていれば前記反転信号に切り替える

ことを特徴とする請求項4に記載の位相差検出回路。

【請求項6】

前記オフセット制御手段は、

前記位相検出手段で検出された前記検出位相を表す位相差パルスを直流信号に変換する信号変換手段と、

前記直流信号のレベルが上限レベル以上又は下限レベル以下で出力を発生する比較手段と、

前記比較手段の出力に基づき、前記オフセット値を切り替える制御信号を発生する制御信号生成部と、

を備えることを特徴とする請求項4に記載の位相差検出回路。

【請求項7】

二信号間の位相差を制御する位相制御回路において、

前記二信号間の位相差を検出し、前記二信号間の検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

前記位相差検出手段より出力された前記検出位相差と、設定位相差との誤差を検出する誤差検出手段と、

前記誤差検出手段の検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する位相制御手段と、

を備えることを特徴とする位相制御回路。

【請求項8】

電力源と、

前記電力源の出力を無線信号に変換する複数の変換手段と、

これら変換手段の複数の無線信号から選択された二信号間の位相差を検出し、該検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

前記位相差検出手段より出力された前記検出位相差と、設定位相差との誤差を検出する誤差検出手段と、

前記誤差検出手段の検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する位相制御手段と、

を備えることを特徴とする無線電力伝送装置。

【請求項1】

二信号間の位相差を検出する位相差検出方法において、

前記二信号間の検出位相差をオフセット値によりシフトして出力し、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御する

ことを特徴とする位相差検出方法。

【請求項2】

前記二信号が第1の信号と第2の信号であり、

前記第1の信号の分周信号、前記第2の信号の反転信号及び非反転信号を生成し、

前記第1の信号の前記分周信号と、前記第2の信号の前記反転信号又は前記非反転信号とを比較して位相差を検出し、

該検出位相差が前記上限値又は前記下限値に到達したか否かを判定し、

該検出位相差が前記上限値又は前記下限値に到達した時点で前記反転信号を用いていれば前記非反転信号に切り替え、又は前記時点で前記非反転信号を用いていれば前記反転信号に切り替える

ことを特徴とする請求項1に記載の位相差検出方法。

【請求項3】

二信号間の位相差を制御する位相制御方法において、

前記二信号間の検出位相差をオフセット値によりシフトして出力し、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御し、

前記位相差範囲内に制御された前記検出位相差と設定位相差との誤差を検出し、

該検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する

ことを特徴とする位相制御方法。

【請求項4】

二信号間の位相差を検出する位相差検出回路において、

前記二信号間の検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記位相差検出手段より出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

を備えることを特徴とする位相差検出回路。

【請求項5】

前記位相差検出手段は、前記二信号が第1の信号と第2の信号であり、前記第1の信号を分周するとともに、前記第2の信号の反転信号及び非反転信号を生成し、前記第1の信号の前記分周信号と、前記第2の信号の前記反転信号又は非反転信号とを比較して位相差を検出し、

前記オフセット制御手段は、前記検出位相差が前記上限値又は前記下限値に到達したか否かを判定する判定手段を含み、該判定手段の前記検出位相差の前記判定に基づき、前記検出位相差が前記上限値又は前記下限値に到達した時点で前記反転信号を用いていれば前記非反転信号に切り替え、又は前記時点で前記非反転信号を用いていれば前記反転信号に切り替える

ことを特徴とする請求項4に記載の位相差検出回路。

【請求項6】

前記オフセット制御手段は、

前記位相検出手段で検出された前記検出位相を表す位相差パルスを直流信号に変換する信号変換手段と、

前記直流信号のレベルが上限レベル以上又は下限レベル以下で出力を発生する比較手段と、

前記比較手段の出力に基づき、前記オフセット値を切り替える制御信号を発生する制御信号生成部と、

を備えることを特徴とする請求項4に記載の位相差検出回路。

【請求項7】

二信号間の位相差を制御する位相制御回路において、

前記二信号間の位相差を検出し、前記二信号間の検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

前記位相差検出手段より出力された前記検出位相差と、設定位相差との誤差を検出する誤差検出手段と、

前記誤差検出手段の検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する位相制御手段と、

を備えることを特徴とする位相制御回路。

【請求項8】

電力源と、

前記電力源の出力を無線信号に変換する複数の変換手段と、

これら変換手段の複数の無線信号から選択された二信号間の位相差を検出し、該検出位相差をオフセット値によりシフトして出力する位相差検出手段と、

前記出力された検出位相差が所定の下限値以上、上限値以下の位相差範囲となるように前記オフセット値を制御するオフセット制御手段と、

前記位相差検出手段より出力された前記検出位相差と、設定位相差との誤差を検出する誤差検出手段と、

前記誤差検出手段の検出誤差に応じて前記二信号の少なくとも一方の信号位相を制御する位相制御手段と、

を備えることを特徴とする無線電力伝送装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2012−114600(P2012−114600A)

【公開日】平成24年6月14日(2012.6.14)

【国際特許分類】

【出願番号】特願2010−260648(P2010−260648)

【出願日】平成22年11月22日(2010.11.22)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成24年6月14日(2012.6.14)

【国際特許分類】

【出願日】平成22年11月22日(2010.11.22)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]