位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、PLL(Phase Locked Loop)回路に適用される位相比較回路に関する。

【背景技術】

【0002】

共通の基準信号が入力される複数のPLL回路を有するシステムでは、各PLL回路の出力信号間の位相差の精度が問題となる場合がある。

【0003】

PLL回路は、入力された基準信号と電圧制御発振器(VCO:Voltage Controlled Oscilator)出力の分周信号との位相を比較し、その比較結果を電圧制御発振器の周波数制御端子にフィードバックすることで、VCO出力信号(=PLL出力信号)を基準信号に位相同期させ、基準信号を正確に逓倍した信号を得る回路である。

【0004】

ここで、PLL回路を構成するバッファアンプや分周器の遅延時間、位相比較回路の特性にばらつきがある場合、基準信号に対するPLL出力信号の位相差がばらついてしまう。

【0005】

例えば、下記特許文献1では、基準信号が同一の複数のPLL回路に対して出力信号間の位相差を自動的に調整する方法が開示されている。

【0006】

また、下記特許文献2では、図6に示すように、基準信号とPLL出力信号との位相差を比較する回路が開示されている。

【0007】

図6はフリップフロップを用いたホッジ位相比較回路(Hogge Phase Detecor)である。この回路は、ランダムなデータ信号と連続的なクロック信号との位相差を測定するのに使われることが多い。しかし、ランダムなデータ信号を周波数の異なるクロック信号に置き換えると、上述した基準信号とPLL出力信号との位相比較にも使用することができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−229020号公報

【特許文献2】特開2002−252560号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

図6に示したホッジ位相比較回路で、周波数の異なる信号をRF信号と基準信号とし、位相比較を行った場合の特性を以下に述べる。

【0010】

まず、RF信号と基準信号との周波数比が整数である場合(ここでは周波数比を2とする)の位相比較回路のタイミングチャートを図7に示す。

【0011】

このホッジ位相比較回路は、基準信号の立ち上がりエッジと、その直後のRF信号の立ち上がりエッジを検出し、両立ち上がりエッジの時間差と等しいパルス幅のアップ信号を出力する。また、ダウン信号は常にRF信号の半周期分のパルス幅の信号となる。これによりアップ信号のパルス幅とダウン信号のパルス幅の差分が、基準信号とRF信号との立ち上がりエッジの時間差(位相差)を示すこととなる。

【0012】

入力信号の位相差に対する出力信号(アップ信号―ダウン信号の積分値)特性を図8に示す。

【0013】

ここで入力信号の位相差は、RF信号の周期を基準として表している。入力信号の位相差が2π、すなわち、RF信号の周期を超えると、次のRF信号の立ち上がりエッジを検出するため、前の2πの範囲の特性と同じとなる。つまりこの場合、入力信号の位相差に対する出力信号の特性は、2π、すなわち、360度の周期を持っている。言い換えると±180度の範囲の位相差を検出することが可能である。RF信号と基準信号との周波数比が整数の場合は、基準信号の立ち上がりエッジと次のRF信号の立ち上がりエッジの時間差は常に一定となるため、周波数比の値によらず図8の特性が得られる。

【0014】

次に、RF信号と基準信号との周波数比が整数でない場合(ここでは周波数比を2.5とする)の位相比較回路のタイミングチャートを図9に示す。

【0015】

RF信号と基準信号との周波数比が整数でない場合は、基準信号の立ち上がりエッジと次のRF信号の立ち上がりエッジの時間差は一定とはならない。ここで示した例の場合は2種類の時間差が交互に繰り返される。このためアップ信号も、2種類の幅のパルスが交互に出力されることとなる。

【0016】

この場合の、入力信号の位相差に対する出力信号特性を図10に示す。出力信号には、2種類のアップ信号の平均値が使われるため、出力信号特性の周期が1/2となる。つまり、入力信号の位相差に対する出力信号の特性は、π、すなわち180度の周期を持っており、位相差の検出範囲は±90度であることが分かる。

【0017】

このような、RF信号と基準信号との周波数比が整数でない条件が想定されるのは、基準信号を入力としたフラクショナルPLLでRF信号を生成した場合や、基準信号の分周信号を用いたPLLでRF信号を生成した場合等である。

【0018】

従来の位相比較回路は以上のように構成されているので、RF信号と基準信号との周波数比が整数でない場合には、位相差の検出範囲が±180度より狭くなる課題があった。

【0019】

本発明は、従来の課題を解消するためになされたものであり、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得ることを目的とするものである。

【課題を解決するための手段】

【0020】

本発明に係る位相比較回路は、高周波信号と基準信号との立ち上がりエッジもしくは立ち下がりエッジの時刻を比較し、比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する位相比較コア回路と、高周波信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、高周波信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前の高周波信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号を生成するマスク信号生成回路と、位相比較コア回路により生成されたアップ信号およびダウン信号を、マスク信号生成回路により生成されたマスク制御信号に従いマスクする信号マスク回路とを備えたものである。

【発明の効果】

【0021】

本発明によれば、位相比較コア回路により生成されたアップ信号およびダウン信号を、信号マスク回路によりマスク制御信号に従いマスクすることで、高周波信号と基準信号との周波数比が整数あるいは整数でないに関わらず、信号マスク回路から出力されるアップ信号のパルス幅が毎回変化せず一定値になる。言い換えれば、基準信号と高周波信号との立ち上がりタイミング関係が等しい部分のみの比較結果を出力することになる。よって、この場合、入力信号の位相差に対する出力信号の特性は、2π、すなわち360度の周期を持っており、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路が得られる効果がある。

【図面の簡単な説明】

【0022】

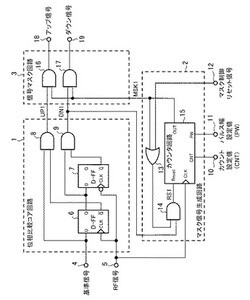

【図1】この発明の実施の形態1による位相比較回路を示す回路図である。

【図2】この発明の実施の形態1による位相比較回路でRF信号と基準信号との周波数比が整数でない場合の動作を示すタイミングチャートである。

【図3】この発明の実施の形態1による位相比較回路でRF信号と基準信号との周波数比が整数でない場合の入力信号の位相差に対する出力信号特性を示す特性図である。

【図4】この発明の実施の形態2による位相比較回路を示す回路図である。

【図5】この発明の実施の形態2による位相比較回路でRF信号と基準信号との周波数比が整数でない場合の動作を示すタイミングチャートである。

【図6】従来の位相比較回路を示す回路図である。

【図7】従来の位相比較回路でRF信号と基準信号との周波数比が整数である場合の動作を示すタイミングチャートである。

【図8】従来の位相比較回路でRF信号と基準信号との周波数比が整数である場合の入力信号の位相差に対する出力信号特性を示す特性図である。

【図9】従来の位相比較回路でRF信号と基準信号との周波数比が整数でない場合の動作を示すタイミングチャートである。

【図10】従来の位相比較回路でRF信号と基準信号との周波数比が整数でない場合の入力信号の位相差に対する出力信号特性を示す特性図である。

【発明を実施するための形態】

【0023】

実施の形態1.

図1はこの発明の実施の形態1による位相比較回路を示す回路図である。

図1において、この位相比較回路は、大きく分類して、位相比較コア回路1、マスク信号生成回路2、および信号マスク回路3から構成される。

【0024】

位相比較コア回路1は、図6で示したホッジ位相比較回路と同一の構成である。すなわち、Dフリップフロップ回路(DFFと言う)6は、端子5から入力されるRF信号の立ち上がりエッジで、端子4から入力される基準信号をラッチし、DFF7は、端子5から入力されるRF信号の立ち下がりエッジで、DFF6の出力信号をラッチする。

【0025】

アンド回路8は、端子4から入力される基準信号とDFF6の反転出力信号との論理積を演算し、その出力信号が位相比較コア回路1の出力であるアップ信号UP1となる。

また、アンド回路9は、DFF6の出力信号とDFF7の反転出力信号との論理積を演算し、その出力信号が位相比較コア回路1のもう一つの出力であるダウン信号DN1となる。

【0026】

マスク信号生成回路2は、マスク制御信号MSK1を生成するものであり、オア回路13、アンド回路14、およびカウンタ回路15から構成される。

【0027】

オア回路13は、端子12から入力されるマスク制御リセット信号とカウンタ回路15から出力されるマスク制御信号MSK1との論理和を演算する。アンド回路14は、位相比較コア回路1から出力されるダウン信号DN1とオア回路13からの出力信号との論理積を演算し、その出力信号がカウンタ回路15をリセットするカウンタリセット信号RS1となる。

【0028】

カウンタ回路15は、カウンタリセット信号RS1でリセットされた後、入力されるクロック、すなわち、RF信号の立ち上がりをカウントし、端子10より設定されたカウント設定値(CNT)に達すると、マスク制御信号MSK1を出力する。

【0029】

ここで、マスク制御信号MSK1は、RF信号に同期した信号であり、この信号の立ち上がりは、アップ信号の立ち上がりの直前のRF信号の立ち上がりと一致している。また、マスク制御信号MSK1のパルス幅は、基準信号の1周期分とほぼ等しく、周期は、RF信号と基準信号との周波数比を、N+K/M(但し、N,K,Mは任意の自然数)とすると、(M×N+K)/frfである(但し、frfはRF信号の周波数)。

【0030】

端子11よりパルス幅設定値(PW)を設定すると、マスク制御信号MSK1のパルス幅は、パルス幅設定値(PW)を用いてPW/frfとなる。ここで、前記カウント設定値(CNT)を(M×N+K−1)に、パルス幅設定値(PW)をNとすれば、前記定義したマスク制御信号MSK1が得られる。

【0031】

信号マスク回路3は、位相比較コア回路1から出力されるアップ信号UP1およびダウン信号DN1を、マスク信号生成回路2から出力されるマスク制御信号MSK1によりマスクするものである。

【0032】

アンド回路16は、位相比較コア回路1から出力されるアップ信号UP1とマスク信号生成回路2から出力されるマスク制御信号MSK1との論理積をアップ信号として端子18から出力する。

また、アンド回路17は、位相比較コア回路1から出力されるダウン信号DN1とマスク信号生成回路2から出力されるマスク制御信号MSK1との論理積をダウン信号として端子19から出力する。

【0033】

次に動作について説明する。

図2に示すのは、RF信号と基準信号との周波数比が整数でない場合(ここでは周波数比を2.5とする)のタイミングチャートである。N=2,M=2,K=1なので、マスク信号生成回路2に設定されるカウント設定値(CNT)は4、パルス幅設定値(PW)は2となる。

【0034】

まず、マスク制御リセット信号が“H”の場合、カウンタリセット信号RS1としてダウン信号DN1がそのまま出力される。

このダウン信号DN1は、図6で示したホッジ位相比較回路のダウン信号であるため、基準信号の周期毎にパルスが出力されている。このため、カウンタ回路15は、RF信号の2周期もしくは3周期毎にリセットされるため、カウント値が4まで届かず、マスク制御信号MSK1は出力されない。

【0035】

次に、マスク制御リセット信号を“L”にして、マスク信号生成回路2のリセットを解除すると、オア回路13の出力が“L”になるため、カウンタリセット信号RS1は“L”のままである。すなわち、カウンタ回路15がリセットされないためカウントアップし、カウント値が4になった時点でマスク制御信号MSK1が“H”となる。

【0036】

マスク制御信号MSK1のパルス幅は、PW=2であるため、RF信号の2周期分の長さとなる。ここで、マスク制御信号MSK1が“H”である間に、ダウン信号DN1が出力され、このパルスはアンド回路14を通過してカウンタ回路15をリセットする。その後は前記の動作を繰り返す。

【0037】

よって、このマスク信号生成回路2では、RF信号に同期して、アップ信号UP1の立ち上がりの直前のRF信号の立ち上がりと一致して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成できることが分かる。

【0038】

このマスク制御信号MSK1を用いて、位相比較コア回路1から出力されるアップ信号UP1およびダウン信号DN1をマスクすることで、出力されるアップ信号のパルス幅が毎回変化せず一定値になる。この原理は以下の通りである。

【0039】

RF信号と基準信号との周波数比がN+K/Mの場合、RF信号の(M×N+K)サイクル分と基準信号のMサイクル分の時間の時間が等しくなる。つまり、(M×N+K)/frf=M/frefの関係が成り立つ。また、位相比較コア回路1から出力されるアップ信号は、(M×N+K)/frf(=M/fref)の周期でパルス幅が変動していることになる。よって、アップ信号を(M×N+K)/frfの時間に1回だけ選択することで、選択されたパルスの幅は一定となる。

【0040】

図3にこの場合の位相比較器の入力信号の位相差に対する出力信号特性を示す。

図3によれば、2π、すなわち、360度の周期を持っており、±180度の範囲の位相差を検出できることが分かる。

【0041】

なお、この実施の形態1では、位相比較コア回路1としてホッジ位相比較回路を用いたが、入力されるRF信号と基準信号との立ち上がりもしくは立ち下がりエッジの時刻を比較し、その比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する回路であれば、他の回路であっても良い。

【0042】

また、マスク信号生成回路2についても、RF信号に同期して、アップ信号UP1の立ち上がりの直前のRF信号の立ち上がりと一致して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成できる回路であれば、他の回路であっても良い。

【0043】

以上のように、この実施の形態1によれば、位相比較コア回路1により生成されたアップ信号UP1およびダウン信号DN1を、信号マスク回路3によりマスク制御信号MSK1に従いマスクすることで、RF信号と基準信号との周波数比が整数あるいは整数でないに関わらず、信号マスク回路3から出力されるアップ信号のパルス幅が毎回変化せず一定値になる。言い換えれば、基準信号とRF信号との立ち上がりタイミング関係が等しい部分のみの比較結果を出力することになる。よって、この場合、入力信号の位相差に対する出力信号の特性は、2π、すなわち360度の周期を持っており、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路が得られる効果がある。

【0044】

実施の形態2.

前記実施の形態1では、位相比較コア回路1により生成されたアップ信号UP1およびダウン信号DN1を、信号マスク回路3によりマスク制御信号MSK1に従いマスクしたが、この実施の形態2では、位相比較コア回路1の入力である基準信号を、信号マスク回路によりマスク制御信号に従いマスクすることで、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができるようにするものである。

【0045】

図4はこの発明の実施の形態2による位相比較回路を示す回路図である。

図4において、この位相比較回路は、大きく分類して、マスク信号生成回路21、信号マスク回路22、および位相比較コア回路1から構成される。

【0046】

マスク信号生成回路21は、マスク制御信号MSK2を生成するものであり、オア回路23、およびカウンタ回路24から構成される。

【0047】

オア回路23は、端子12から入力されるマスク制御リセット信号とカウンタ回路24から出力されるマスク制御信号MSK2との論理和を演算し、その出力信号がカウンタ回路24をリセットするカウンタリセット信号RS2となる。

【0048】

カウンタ回路24は、カウンタリセット信号RS2でリセットされた後、入力されるクロック、すなわち、基準信号の立ち下がりをカウントし、端子10より設定されたカウント設定値(CNT)に達すると、マスク制御信号MSK2を出力する。

【0049】

ここで、マスク制御信号MSK2は、基準信号に同期した信号であり、基準信号の立ち下がりに一致して立ち上がる。また、マスク制御信号MSK2のパルス幅は、基準信号の1周期分とほぼ等しく、周期は、M/frefである。但し、RF信号と基準信号との周波数比はN+K/M、frefは基準信号の周波数である。

【0050】

ここで、前記カウント設定値(CNT)を(M−1)にすれば、前記定義したマスク制御信号MSK2が得られる。

【0051】

信号マスク回路22は、端子4から入力される基準信号をマスク信号生成回路21により生成されたマスク制御信号MSK2によりマスクするものである。

信号マスク回路22において、アンド回路25は、基準信号とマスク制御信号MSK2との論理積を信号マスク回路出力信号REF2として出力する。

【0052】

位相比較コア回路1は、図1で示したホッジ位相比較回路と同一の構成である。但し、DFF6は、端子5から入力されるRF信号の立ち上がりエッジで、信号マスク回路22から入力される信号マスク回路出力信号REF2をラッチする。

【0053】

次に動作について説明する。

図5に示すのは、RF信号と基準信号との周波数比が整数でない場合(ここでは周波数比を2.5とする)のタイミングチャートである。N=2,M=2,K=1なので、マスク信号生成回路21に設定されるカウント設定値(CNT)は1となる。

【0054】

まず、マスク制御リセット信号が“H”の場合、カウンタ回路24は、常にリセットされるため、マスク制御信号MSK2は“L”のままである。

すなわち、基準信号は信号マスク回路22によってマスクされるため、位相比較コア回路1には基準信号が入力されず、アップ信号もダウン信号も出力されない。

【0055】

次に、マスク制御リセット信号を“L”にして、マスク信号生成回路21のリセットを解除すると、オア回路23の出力であるカウンタリセット信号RS1が“L”となる。すなわち、カウンタ回路24がカウントを始めるが、カウント設定値(CNT)が1であるので、次の基準信号の立ち下がりでマスク制御信号MSK2が“H”となる。また、これと同時に、マスク制御信号MSK2の“H”によりカウンタ回路24がリセットされる。

【0056】

その後、基準信号の1周期分の時間だけマスク制御信号MSK2が“H”を継続した後、マスク制御信号MSK2は“L”になり、カウンタ回路24のリセットが解除されて、再びカウントを始める。その後は前記の動作を繰り返す。

【0057】

よって、このマスク信号生成回路21では、基準信号に同期して、基準信号の立ち下がりに一致して立ち上がり、パルス幅は基準信号の1周期分と等しく、周期はM/frefとなるマスク制御信号MSK2を生成できることが分かる。

【0058】

このマスク制御信号MSK2を用いて、位相比較コア回路1の入力である基準信号をマスクすることで、位相比較コア回路1から出力されるアップ信号のパルス幅が毎回変化せず一定値になる。この原理は、前記実施の形態1と同様である。

【0059】

この場合の位相比較器の入力信号の位相差に対する出力信号特性は、図3と同じものとなる。

図3によれば、2π、すなわち、360度の周期を持っており、±180度の範囲の位相差を検出できることが分かる。

【0060】

なお、この実施の形態2では、位相比較コア回路1としてホッジ位相比較回路を用いたが、入力されるRF信号と基準信号との立ち上がりもしくは立ち下がりエッジの時刻を比較し、その比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する回路であれば、他の回路であっても良い。

【0061】

また、マスク信号生成回路21についても、基準信号に同期して、基準信号の立ち下がりに一致して立ち上がり、パルス幅は基準信号の1周期分と等しく、周期はM/frefとなるマスク制御信号MSK2を生成できる回路であれば、他の回路であっても良い。

【0062】

以上のように、この実施の形態2によれば、位相比較コア回路1の入力である基準信号を、信号マスク回路22によりマスク制御信MSK2に従いマスクすることで、RF信号と基準信号との周波数比が整数あるいは整数でないに関わらず、位相比較コア回路1から出力されるアップ信号のパルス幅が毎回変化せず一定値になる。言い換えれば、基準信号とRF信号との立ち上がりタイミング関係が等しい部分のみの比較結果を出力することになる。よって、この場合、入力信号の位相差に対する出力信号の特性は、2π、すなわち360度の周期を持っており、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路が得られる効果がある。

【0063】

なお、本願発明はその発明の範囲内において、各実施の形態の自由な組み合わせ、あるいは各実施の形態の任意な構成要素の変形、もしくは各実施の形態において任意な構成要素の省略が可能である。

【符号の説明】

【0064】

1 位相比較コア回路、2,21 マスク信号生成回路、3,22 信号マスク回路、4,5,10〜12,18,19 端子、6,7 Dフリップフロップ回路、8,9,14,16,17,25 アンド回路、13,23 オア回路、15,24 カウンタ回路。

【技術分野】

【0001】

本発明は、PLL(Phase Locked Loop)回路に適用される位相比較回路に関する。

【背景技術】

【0002】

共通の基準信号が入力される複数のPLL回路を有するシステムでは、各PLL回路の出力信号間の位相差の精度が問題となる場合がある。

【0003】

PLL回路は、入力された基準信号と電圧制御発振器(VCO:Voltage Controlled Oscilator)出力の分周信号との位相を比較し、その比較結果を電圧制御発振器の周波数制御端子にフィードバックすることで、VCO出力信号(=PLL出力信号)を基準信号に位相同期させ、基準信号を正確に逓倍した信号を得る回路である。

【0004】

ここで、PLL回路を構成するバッファアンプや分周器の遅延時間、位相比較回路の特性にばらつきがある場合、基準信号に対するPLL出力信号の位相差がばらついてしまう。

【0005】

例えば、下記特許文献1では、基準信号が同一の複数のPLL回路に対して出力信号間の位相差を自動的に調整する方法が開示されている。

【0006】

また、下記特許文献2では、図6に示すように、基準信号とPLL出力信号との位相差を比較する回路が開示されている。

【0007】

図6はフリップフロップを用いたホッジ位相比較回路(Hogge Phase Detecor)である。この回路は、ランダムなデータ信号と連続的なクロック信号との位相差を測定するのに使われることが多い。しかし、ランダムなデータ信号を周波数の異なるクロック信号に置き換えると、上述した基準信号とPLL出力信号との位相比較にも使用することができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−229020号公報

【特許文献2】特開2002−252560号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

図6に示したホッジ位相比較回路で、周波数の異なる信号をRF信号と基準信号とし、位相比較を行った場合の特性を以下に述べる。

【0010】

まず、RF信号と基準信号との周波数比が整数である場合(ここでは周波数比を2とする)の位相比較回路のタイミングチャートを図7に示す。

【0011】

このホッジ位相比較回路は、基準信号の立ち上がりエッジと、その直後のRF信号の立ち上がりエッジを検出し、両立ち上がりエッジの時間差と等しいパルス幅のアップ信号を出力する。また、ダウン信号は常にRF信号の半周期分のパルス幅の信号となる。これによりアップ信号のパルス幅とダウン信号のパルス幅の差分が、基準信号とRF信号との立ち上がりエッジの時間差(位相差)を示すこととなる。

【0012】

入力信号の位相差に対する出力信号(アップ信号―ダウン信号の積分値)特性を図8に示す。

【0013】

ここで入力信号の位相差は、RF信号の周期を基準として表している。入力信号の位相差が2π、すなわち、RF信号の周期を超えると、次のRF信号の立ち上がりエッジを検出するため、前の2πの範囲の特性と同じとなる。つまりこの場合、入力信号の位相差に対する出力信号の特性は、2π、すなわち、360度の周期を持っている。言い換えると±180度の範囲の位相差を検出することが可能である。RF信号と基準信号との周波数比が整数の場合は、基準信号の立ち上がりエッジと次のRF信号の立ち上がりエッジの時間差は常に一定となるため、周波数比の値によらず図8の特性が得られる。

【0014】

次に、RF信号と基準信号との周波数比が整数でない場合(ここでは周波数比を2.5とする)の位相比較回路のタイミングチャートを図9に示す。

【0015】

RF信号と基準信号との周波数比が整数でない場合は、基準信号の立ち上がりエッジと次のRF信号の立ち上がりエッジの時間差は一定とはならない。ここで示した例の場合は2種類の時間差が交互に繰り返される。このためアップ信号も、2種類の幅のパルスが交互に出力されることとなる。

【0016】

この場合の、入力信号の位相差に対する出力信号特性を図10に示す。出力信号には、2種類のアップ信号の平均値が使われるため、出力信号特性の周期が1/2となる。つまり、入力信号の位相差に対する出力信号の特性は、π、すなわち180度の周期を持っており、位相差の検出範囲は±90度であることが分かる。

【0017】

このような、RF信号と基準信号との周波数比が整数でない条件が想定されるのは、基準信号を入力としたフラクショナルPLLでRF信号を生成した場合や、基準信号の分周信号を用いたPLLでRF信号を生成した場合等である。

【0018】

従来の位相比較回路は以上のように構成されているので、RF信号と基準信号との周波数比が整数でない場合には、位相差の検出範囲が±180度より狭くなる課題があった。

【0019】

本発明は、従来の課題を解消するためになされたものであり、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得ることを目的とするものである。

【課題を解決するための手段】

【0020】

本発明に係る位相比較回路は、高周波信号と基準信号との立ち上がりエッジもしくは立ち下がりエッジの時刻を比較し、比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する位相比較コア回路と、高周波信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、高周波信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前の高周波信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号を生成するマスク信号生成回路と、位相比較コア回路により生成されたアップ信号およびダウン信号を、マスク信号生成回路により生成されたマスク制御信号に従いマスクする信号マスク回路とを備えたものである。

【発明の効果】

【0021】

本発明によれば、位相比較コア回路により生成されたアップ信号およびダウン信号を、信号マスク回路によりマスク制御信号に従いマスクすることで、高周波信号と基準信号との周波数比が整数あるいは整数でないに関わらず、信号マスク回路から出力されるアップ信号のパルス幅が毎回変化せず一定値になる。言い換えれば、基準信号と高周波信号との立ち上がりタイミング関係が等しい部分のみの比較結果を出力することになる。よって、この場合、入力信号の位相差に対する出力信号の特性は、2π、すなわち360度の周期を持っており、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路が得られる効果がある。

【図面の簡単な説明】

【0022】

【図1】この発明の実施の形態1による位相比較回路を示す回路図である。

【図2】この発明の実施の形態1による位相比較回路でRF信号と基準信号との周波数比が整数でない場合の動作を示すタイミングチャートである。

【図3】この発明の実施の形態1による位相比較回路でRF信号と基準信号との周波数比が整数でない場合の入力信号の位相差に対する出力信号特性を示す特性図である。

【図4】この発明の実施の形態2による位相比較回路を示す回路図である。

【図5】この発明の実施の形態2による位相比較回路でRF信号と基準信号との周波数比が整数でない場合の動作を示すタイミングチャートである。

【図6】従来の位相比較回路を示す回路図である。

【図7】従来の位相比較回路でRF信号と基準信号との周波数比が整数である場合の動作を示すタイミングチャートである。

【図8】従来の位相比較回路でRF信号と基準信号との周波数比が整数である場合の入力信号の位相差に対する出力信号特性を示す特性図である。

【図9】従来の位相比較回路でRF信号と基準信号との周波数比が整数でない場合の動作を示すタイミングチャートである。

【図10】従来の位相比較回路でRF信号と基準信号との周波数比が整数でない場合の入力信号の位相差に対する出力信号特性を示す特性図である。

【発明を実施するための形態】

【0023】

実施の形態1.

図1はこの発明の実施の形態1による位相比較回路を示す回路図である。

図1において、この位相比較回路は、大きく分類して、位相比較コア回路1、マスク信号生成回路2、および信号マスク回路3から構成される。

【0024】

位相比較コア回路1は、図6で示したホッジ位相比較回路と同一の構成である。すなわち、Dフリップフロップ回路(DFFと言う)6は、端子5から入力されるRF信号の立ち上がりエッジで、端子4から入力される基準信号をラッチし、DFF7は、端子5から入力されるRF信号の立ち下がりエッジで、DFF6の出力信号をラッチする。

【0025】

アンド回路8は、端子4から入力される基準信号とDFF6の反転出力信号との論理積を演算し、その出力信号が位相比較コア回路1の出力であるアップ信号UP1となる。

また、アンド回路9は、DFF6の出力信号とDFF7の反転出力信号との論理積を演算し、その出力信号が位相比較コア回路1のもう一つの出力であるダウン信号DN1となる。

【0026】

マスク信号生成回路2は、マスク制御信号MSK1を生成するものであり、オア回路13、アンド回路14、およびカウンタ回路15から構成される。

【0027】

オア回路13は、端子12から入力されるマスク制御リセット信号とカウンタ回路15から出力されるマスク制御信号MSK1との論理和を演算する。アンド回路14は、位相比較コア回路1から出力されるダウン信号DN1とオア回路13からの出力信号との論理積を演算し、その出力信号がカウンタ回路15をリセットするカウンタリセット信号RS1となる。

【0028】

カウンタ回路15は、カウンタリセット信号RS1でリセットされた後、入力されるクロック、すなわち、RF信号の立ち上がりをカウントし、端子10より設定されたカウント設定値(CNT)に達すると、マスク制御信号MSK1を出力する。

【0029】

ここで、マスク制御信号MSK1は、RF信号に同期した信号であり、この信号の立ち上がりは、アップ信号の立ち上がりの直前のRF信号の立ち上がりと一致している。また、マスク制御信号MSK1のパルス幅は、基準信号の1周期分とほぼ等しく、周期は、RF信号と基準信号との周波数比を、N+K/M(但し、N,K,Mは任意の自然数)とすると、(M×N+K)/frfである(但し、frfはRF信号の周波数)。

【0030】

端子11よりパルス幅設定値(PW)を設定すると、マスク制御信号MSK1のパルス幅は、パルス幅設定値(PW)を用いてPW/frfとなる。ここで、前記カウント設定値(CNT)を(M×N+K−1)に、パルス幅設定値(PW)をNとすれば、前記定義したマスク制御信号MSK1が得られる。

【0031】

信号マスク回路3は、位相比較コア回路1から出力されるアップ信号UP1およびダウン信号DN1を、マスク信号生成回路2から出力されるマスク制御信号MSK1によりマスクするものである。

【0032】

アンド回路16は、位相比較コア回路1から出力されるアップ信号UP1とマスク信号生成回路2から出力されるマスク制御信号MSK1との論理積をアップ信号として端子18から出力する。

また、アンド回路17は、位相比較コア回路1から出力されるダウン信号DN1とマスク信号生成回路2から出力されるマスク制御信号MSK1との論理積をダウン信号として端子19から出力する。

【0033】

次に動作について説明する。

図2に示すのは、RF信号と基準信号との周波数比が整数でない場合(ここでは周波数比を2.5とする)のタイミングチャートである。N=2,M=2,K=1なので、マスク信号生成回路2に設定されるカウント設定値(CNT)は4、パルス幅設定値(PW)は2となる。

【0034】

まず、マスク制御リセット信号が“H”の場合、カウンタリセット信号RS1としてダウン信号DN1がそのまま出力される。

このダウン信号DN1は、図6で示したホッジ位相比較回路のダウン信号であるため、基準信号の周期毎にパルスが出力されている。このため、カウンタ回路15は、RF信号の2周期もしくは3周期毎にリセットされるため、カウント値が4まで届かず、マスク制御信号MSK1は出力されない。

【0035】

次に、マスク制御リセット信号を“L”にして、マスク信号生成回路2のリセットを解除すると、オア回路13の出力が“L”になるため、カウンタリセット信号RS1は“L”のままである。すなわち、カウンタ回路15がリセットされないためカウントアップし、カウント値が4になった時点でマスク制御信号MSK1が“H”となる。

【0036】

マスク制御信号MSK1のパルス幅は、PW=2であるため、RF信号の2周期分の長さとなる。ここで、マスク制御信号MSK1が“H”である間に、ダウン信号DN1が出力され、このパルスはアンド回路14を通過してカウンタ回路15をリセットする。その後は前記の動作を繰り返す。

【0037】

よって、このマスク信号生成回路2では、RF信号に同期して、アップ信号UP1の立ち上がりの直前のRF信号の立ち上がりと一致して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成できることが分かる。

【0038】

このマスク制御信号MSK1を用いて、位相比較コア回路1から出力されるアップ信号UP1およびダウン信号DN1をマスクすることで、出力されるアップ信号のパルス幅が毎回変化せず一定値になる。この原理は以下の通りである。

【0039】

RF信号と基準信号との周波数比がN+K/Mの場合、RF信号の(M×N+K)サイクル分と基準信号のMサイクル分の時間の時間が等しくなる。つまり、(M×N+K)/frf=M/frefの関係が成り立つ。また、位相比較コア回路1から出力されるアップ信号は、(M×N+K)/frf(=M/fref)の周期でパルス幅が変動していることになる。よって、アップ信号を(M×N+K)/frfの時間に1回だけ選択することで、選択されたパルスの幅は一定となる。

【0040】

図3にこの場合の位相比較器の入力信号の位相差に対する出力信号特性を示す。

図3によれば、2π、すなわち、360度の周期を持っており、±180度の範囲の位相差を検出できることが分かる。

【0041】

なお、この実施の形態1では、位相比較コア回路1としてホッジ位相比較回路を用いたが、入力されるRF信号と基準信号との立ち上がりもしくは立ち下がりエッジの時刻を比較し、その比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する回路であれば、他の回路であっても良い。

【0042】

また、マスク信号生成回路2についても、RF信号に同期して、アップ信号UP1の立ち上がりの直前のRF信号の立ち上がりと一致して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成できる回路であれば、他の回路であっても良い。

【0043】

以上のように、この実施の形態1によれば、位相比較コア回路1により生成されたアップ信号UP1およびダウン信号DN1を、信号マスク回路3によりマスク制御信号MSK1に従いマスクすることで、RF信号と基準信号との周波数比が整数あるいは整数でないに関わらず、信号マスク回路3から出力されるアップ信号のパルス幅が毎回変化せず一定値になる。言い換えれば、基準信号とRF信号との立ち上がりタイミング関係が等しい部分のみの比較結果を出力することになる。よって、この場合、入力信号の位相差に対する出力信号の特性は、2π、すなわち360度の周期を持っており、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路が得られる効果がある。

【0044】

実施の形態2.

前記実施の形態1では、位相比較コア回路1により生成されたアップ信号UP1およびダウン信号DN1を、信号マスク回路3によりマスク制御信号MSK1に従いマスクしたが、この実施の形態2では、位相比較コア回路1の入力である基準信号を、信号マスク回路によりマスク制御信号に従いマスクすることで、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができるようにするものである。

【0045】

図4はこの発明の実施の形態2による位相比較回路を示す回路図である。

図4において、この位相比較回路は、大きく分類して、マスク信号生成回路21、信号マスク回路22、および位相比較コア回路1から構成される。

【0046】

マスク信号生成回路21は、マスク制御信号MSK2を生成するものであり、オア回路23、およびカウンタ回路24から構成される。

【0047】

オア回路23は、端子12から入力されるマスク制御リセット信号とカウンタ回路24から出力されるマスク制御信号MSK2との論理和を演算し、その出力信号がカウンタ回路24をリセットするカウンタリセット信号RS2となる。

【0048】

カウンタ回路24は、カウンタリセット信号RS2でリセットされた後、入力されるクロック、すなわち、基準信号の立ち下がりをカウントし、端子10より設定されたカウント設定値(CNT)に達すると、マスク制御信号MSK2を出力する。

【0049】

ここで、マスク制御信号MSK2は、基準信号に同期した信号であり、基準信号の立ち下がりに一致して立ち上がる。また、マスク制御信号MSK2のパルス幅は、基準信号の1周期分とほぼ等しく、周期は、M/frefである。但し、RF信号と基準信号との周波数比はN+K/M、frefは基準信号の周波数である。

【0050】

ここで、前記カウント設定値(CNT)を(M−1)にすれば、前記定義したマスク制御信号MSK2が得られる。

【0051】

信号マスク回路22は、端子4から入力される基準信号をマスク信号生成回路21により生成されたマスク制御信号MSK2によりマスクするものである。

信号マスク回路22において、アンド回路25は、基準信号とマスク制御信号MSK2との論理積を信号マスク回路出力信号REF2として出力する。

【0052】

位相比較コア回路1は、図1で示したホッジ位相比較回路と同一の構成である。但し、DFF6は、端子5から入力されるRF信号の立ち上がりエッジで、信号マスク回路22から入力される信号マスク回路出力信号REF2をラッチする。

【0053】

次に動作について説明する。

図5に示すのは、RF信号と基準信号との周波数比が整数でない場合(ここでは周波数比を2.5とする)のタイミングチャートである。N=2,M=2,K=1なので、マスク信号生成回路21に設定されるカウント設定値(CNT)は1となる。

【0054】

まず、マスク制御リセット信号が“H”の場合、カウンタ回路24は、常にリセットされるため、マスク制御信号MSK2は“L”のままである。

すなわち、基準信号は信号マスク回路22によってマスクされるため、位相比較コア回路1には基準信号が入力されず、アップ信号もダウン信号も出力されない。

【0055】

次に、マスク制御リセット信号を“L”にして、マスク信号生成回路21のリセットを解除すると、オア回路23の出力であるカウンタリセット信号RS1が“L”となる。すなわち、カウンタ回路24がカウントを始めるが、カウント設定値(CNT)が1であるので、次の基準信号の立ち下がりでマスク制御信号MSK2が“H”となる。また、これと同時に、マスク制御信号MSK2の“H”によりカウンタ回路24がリセットされる。

【0056】

その後、基準信号の1周期分の時間だけマスク制御信号MSK2が“H”を継続した後、マスク制御信号MSK2は“L”になり、カウンタ回路24のリセットが解除されて、再びカウントを始める。その後は前記の動作を繰り返す。

【0057】

よって、このマスク信号生成回路21では、基準信号に同期して、基準信号の立ち下がりに一致して立ち上がり、パルス幅は基準信号の1周期分と等しく、周期はM/frefとなるマスク制御信号MSK2を生成できることが分かる。

【0058】

このマスク制御信号MSK2を用いて、位相比較コア回路1の入力である基準信号をマスクすることで、位相比較コア回路1から出力されるアップ信号のパルス幅が毎回変化せず一定値になる。この原理は、前記実施の形態1と同様である。

【0059】

この場合の位相比較器の入力信号の位相差に対する出力信号特性は、図3と同じものとなる。

図3によれば、2π、すなわち、360度の周期を持っており、±180度の範囲の位相差を検出できることが分かる。

【0060】

なお、この実施の形態2では、位相比較コア回路1としてホッジ位相比較回路を用いたが、入力されるRF信号と基準信号との立ち上がりもしくは立ち下がりエッジの時刻を比較し、その比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する回路であれば、他の回路であっても良い。

【0061】

また、マスク信号生成回路21についても、基準信号に同期して、基準信号の立ち下がりに一致して立ち上がり、パルス幅は基準信号の1周期分と等しく、周期はM/frefとなるマスク制御信号MSK2を生成できる回路であれば、他の回路であっても良い。

【0062】

以上のように、この実施の形態2によれば、位相比較コア回路1の入力である基準信号を、信号マスク回路22によりマスク制御信MSK2に従いマスクすることで、RF信号と基準信号との周波数比が整数あるいは整数でないに関わらず、位相比較コア回路1から出力されるアップ信号のパルス幅が毎回変化せず一定値になる。言い換えれば、基準信号とRF信号との立ち上がりタイミング関係が等しい部分のみの比較結果を出力することになる。よって、この場合、入力信号の位相差に対する出力信号の特性は、2π、すなわち360度の周期を持っており、入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路が得られる効果がある。

【0063】

なお、本願発明はその発明の範囲内において、各実施の形態の自由な組み合わせ、あるいは各実施の形態の任意な構成要素の変形、もしくは各実施の形態において任意な構成要素の省略が可能である。

【符号の説明】

【0064】

1 位相比較コア回路、2,21 マスク信号生成回路、3,22 信号マスク回路、4,5,10〜12,18,19 端子、6,7 Dフリップフロップ回路、8,9,14,16,17,25 アンド回路、13,23 オア回路、15,24 カウンタ回路。

【特許請求の範囲】

【請求項1】

高周波信号と基準信号との立ち上がりエッジもしくは立ち下がりエッジの時刻を比較し、該比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する位相比較コア回路と、

高周波信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、高周波信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前の高周波信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号を生成するマスク信号生成回路と、

前記位相比較コア回路により生成されたアップ信号およびダウン信号を、前記マスク信号生成回路により生成されたマスク制御信号に従いマスクする信号マスク回路とを備えた位相比較回路。

【請求項2】

前記位相比較コア回路は、

高周波信号の立ち上がりエッジで基準信号をラッチする第1のDフリップフロップ回路と、

高周波信号の立ち下がりエッジで前記第1のDフリップフロップ回路の出力信号をラッチする第2のDフリップフロップ回路と、

基準信号と前記第1のDフリップフロップ回路の反転出力信号との論理積を演算し、アップ信号を生成する第1のアンド回路と、

前記第1のDフリップフロップ回路の出力信号と前記第2のDフリップフロップ回路の反転出力信号との論理積を演算し、ダウン信号を生成する第2のアンド回路とを備えたことを特徴とする請求項1記載の位相比較回路。

【請求項3】

前記マスク信号生成回路は、

外部より入力されるマスク制御リセット信号と当該マスク信号生成回路により生成されるマスク制御信号との論理和を演算するオア回路と、

前記位相比較コア回路により生成されたダウン信号と前記オア回路により演算された論理和による信号との論理積を演算する第3のアンド回路と、

高周波信号をクロックとして動作し、前記第3のアンド回路により演算された論理積による信号でリセットされ、クロックの立ち上がりをカウントし、カウント値がM×N+K−1に達すると、パルス幅がN/frfのマスク制御信号を出力するカウンタ回路とを備えたことを特徴とする請求項1記載の位相比較回路。

【請求項4】

前記信号マスク回路は、

前記位相比較コア回路により生成されたアップ信号と前記マスク信号生成回路により生成されたマスク制御信号との論理積を演算する第4のアンド回路と、

前記位相比較コア回路により生成されたダウン信号と前記マスク信号生成回路により生成されたマスク制御信号との論理積を演算する第5のアンド回路とを備えたことを特徴とする請求項1記載の位相比較回路。

【請求項5】

高周波信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、基準信号の周波数をfrefとしたとき、基準信号の立ち下がりに同期して立ち上がり、パルス幅は基準信号の1周期分と等しく、周期はM/frefとなるマスク制御信号を生成するマスク信号生成回路と、

基準信号を前記マスク信号生成回路により生成されたマスク制御信号に従いマスクする信号マスク回路と、

高周波信号と前記信号マスク回路から出力される基準信号の立ち上がりエッジもしくは立ち下がりエッジの時刻を比較し、該比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する位相比較コア回路とを備えた位相比較回路。

【請求項6】

前記マスク信号生成回路は、

外部より入力されるマスク制御リセット信号と当該マスク信号生成回路により生成されるマスク制御信号との論理和を演算するオア回路と、

基準信号をクロックとして動作し、前記オア回路により演算された論理和による信号でリセットされ、クロックの立ち下がりをカウントし、カウント値がM−1に達すると、パルス幅が1/frefのマスク制御信号を出力するカウンタ回路とを備えたことを特徴とする請求項5記載の位相比較回路。

【請求項7】

前記信号マスク回路は、

基準信号と前記マスク信号生成回路により生成されたマスク制御信号との論理積を演算する第1のアンド回路を備えたことを特徴とする請求項5記載の位相比較回路。

【請求項8】

前記位相比較コア回路は、

高周波信号の立ち上がりエッジで前記信号マスク回路から出力される基準信号をラッチする第1のDフリップフロップ回路と、

高周波信号の立ち下がりエッジで前記第1のDフリップフロップ回路の出力信号をラッチする第2のDフリップフロップ回路と、

前記信号マスク回路から出力される基準信号と前記第1のDフリップフロップ回路の反転出力信号との論理積を演算し、アップ信号を生成する第2のアンド回路と、

前記第1のDフリップフロップ回路の出力信号と前記第2のDフリップフロップ回路の反転出力信号との論理積を演算し、ダウン信号を生成する第3のアンド回路とを備えたことを特徴とする請求項5記載の位相比較回路。

【請求項1】

高周波信号と基準信号との立ち上がりエッジもしくは立ち下がりエッジの時刻を比較し、該比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する位相比較コア回路と、

高周波信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、高周波信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前の高周波信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号を生成するマスク信号生成回路と、

前記位相比較コア回路により生成されたアップ信号およびダウン信号を、前記マスク信号生成回路により生成されたマスク制御信号に従いマスクする信号マスク回路とを備えた位相比較回路。

【請求項2】

前記位相比較コア回路は、

高周波信号の立ち上がりエッジで基準信号をラッチする第1のDフリップフロップ回路と、

高周波信号の立ち下がりエッジで前記第1のDフリップフロップ回路の出力信号をラッチする第2のDフリップフロップ回路と、

基準信号と前記第1のDフリップフロップ回路の反転出力信号との論理積を演算し、アップ信号を生成する第1のアンド回路と、

前記第1のDフリップフロップ回路の出力信号と前記第2のDフリップフロップ回路の反転出力信号との論理積を演算し、ダウン信号を生成する第2のアンド回路とを備えたことを特徴とする請求項1記載の位相比較回路。

【請求項3】

前記マスク信号生成回路は、

外部より入力されるマスク制御リセット信号と当該マスク信号生成回路により生成されるマスク制御信号との論理和を演算するオア回路と、

前記位相比較コア回路により生成されたダウン信号と前記オア回路により演算された論理和による信号との論理積を演算する第3のアンド回路と、

高周波信号をクロックとして動作し、前記第3のアンド回路により演算された論理積による信号でリセットされ、クロックの立ち上がりをカウントし、カウント値がM×N+K−1に達すると、パルス幅がN/frfのマスク制御信号を出力するカウンタ回路とを備えたことを特徴とする請求項1記載の位相比較回路。

【請求項4】

前記信号マスク回路は、

前記位相比較コア回路により生成されたアップ信号と前記マスク信号生成回路により生成されたマスク制御信号との論理積を演算する第4のアンド回路と、

前記位相比較コア回路により生成されたダウン信号と前記マスク信号生成回路により生成されたマスク制御信号との論理積を演算する第5のアンド回路とを備えたことを特徴とする請求項1記載の位相比較回路。

【請求項5】

高周波信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、基準信号の周波数をfrefとしたとき、基準信号の立ち下がりに同期して立ち上がり、パルス幅は基準信号の1周期分と等しく、周期はM/frefとなるマスク制御信号を生成するマスク信号生成回路と、

基準信号を前記マスク信号生成回路により生成されたマスク制御信号に従いマスクする信号マスク回路と、

高周波信号と前記信号マスク回路から出力される基準信号の立ち上がりエッジもしくは立ち下がりエッジの時刻を比較し、該比較結果に応じて位相を進めるアップ信号または位相を遅らせるダウン信号を生成する位相比較コア回路とを備えた位相比較回路。

【請求項6】

前記マスク信号生成回路は、

外部より入力されるマスク制御リセット信号と当該マスク信号生成回路により生成されるマスク制御信号との論理和を演算するオア回路と、

基準信号をクロックとして動作し、前記オア回路により演算された論理和による信号でリセットされ、クロックの立ち下がりをカウントし、カウント値がM−1に達すると、パルス幅が1/frefのマスク制御信号を出力するカウンタ回路とを備えたことを特徴とする請求項5記載の位相比較回路。

【請求項7】

前記信号マスク回路は、

基準信号と前記マスク信号生成回路により生成されたマスク制御信号との論理積を演算する第1のアンド回路を備えたことを特徴とする請求項5記載の位相比較回路。

【請求項8】

前記位相比較コア回路は、

高周波信号の立ち上がりエッジで前記信号マスク回路から出力される基準信号をラッチする第1のDフリップフロップ回路と、

高周波信号の立ち下がりエッジで前記第1のDフリップフロップ回路の出力信号をラッチする第2のDフリップフロップ回路と、

前記信号マスク回路から出力される基準信号と前記第1のDフリップフロップ回路の反転出力信号との論理積を演算し、アップ信号を生成する第2のアンド回路と、

前記第1のDフリップフロップ回路の出力信号と前記第2のDフリップフロップ回路の反転出力信号との論理積を演算し、ダウン信号を生成する第3のアンド回路とを備えたことを特徴とする請求項5記載の位相比較回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−244290(P2012−244290A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−110488(P2011−110488)

【出願日】平成23年5月17日(2011.5.17)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月17日(2011.5.17)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]