位相比較装置

【課題】ステップ応答収束時間だけ待つ必要なく積分値を抽出し、また、入力信号の周波数が既知でなくても抽出した積分値に応じて位相差を演算する位相比較装置を得る。

【解決手段】分周器4が入力信号の周波数を2分周し、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分し、基準積分器7が既知の一定レベルの基準信号を分周器4により設定された周期分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、入力信号の周波数の1/2倍の周波数の整数倍の周波数にヌル点のできるsyncフィルタ特性が形成されることを利用し、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。また、2つの入力信号の周波数が既知でなくても、2つの入力信号の位相差を演算することができる。

【解決手段】分周器4が入力信号の周波数を2分周し、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分し、基準積分器7が既知の一定レベルの基準信号を分周器4により設定された周期分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、入力信号の周波数の1/2倍の周波数の整数倍の周波数にヌル点のできるsyncフィルタ特性が形成されることを利用し、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。また、2つの入力信号の周波数が既知でなくても、2つの入力信号の位相差を演算することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、2つの入力信号の位相差を演算する位相比較装置に関する。

【背景技術】

【0002】

従来の位相比較器として、2つの入力信号の位相差に応じたパルスを生成する排他的倫理和回路と、排他的倫理和回路の後段に接続され、2つの入力信号の位相差に応じた信号を出力するローパスフィルタとを備えたものがある(下記特許文献1の第1図)。

【0003】

また、従来の位相比較器として、2つの入力信号のうちの一方の入力信号の立ち上がりに応じて充電を開始し、他方の入力信号の立ち上がりに応じて充電を停止する積分器と、積分器の充電停止後の積分電圧を抽出し、その積分電圧を2つの入力信号の立ち上がり時間差の時間情報として出力するサンプルホールド回路とを備えたものがある(下記特許文献1の第5図)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭59−161119号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来の位相比較器は以上のように構成されているので、以下の課題がある。

排他的倫理和回路の後段にローパスフィルタを接続した位相比較器は、2つの入力信号がパルス波の場合に、排他的倫理和回路の出力信号がステップ応答的に立ち上がる。よって、ローパスフィルタの出力信号が安定するためには、ローパスフィルタの時定数に起因するステップ応答が収束する時間だけ待つ必要があり、高調波の影響の抑圧量が多ければ多いほど、ステップ応答収束時間が長くなる。また、あまりステップ応答時間が長くなると出力信号が立ち下がり、位相比較できなくなってしまう課題がある。

【0006】

積分器の後段にサンプルホールド回路を接続した位相比較器は、積分電圧を2つの入力信号の立ち上がり時間差の時間情報として出力する。よって、2つの入力信号の周波数が既知であれば、立ち上がり時間差の時間情報と、既知の周波数とにより、2つの入力信号の位相差を演算することができるが、2つの入力信号の周波数が既知でなかったり、周波数が変動する場合には、2つの入力信号の位相差を演算することができない課題がある。

また、2つの異なる入力信号の立ち上がりに応じて、積分器の充電開始および充電停止を制御するので、充電開始の際の遅延と、充電停止の際の遅延とが個別に発生し、抽出される積分値の誤差変動が大きくなる課題がある。

【0007】

本発明は、以上のような課題を解消するためになされたものであり、ステップ応答収束時間だけ待つ必要なく積分値を抽出し、また、入力信号の周波数が既知でなくても抽出した積分値に応じて位相差を演算し、さらに、積分値の誤差変動も小さい位相比較装置を得ることを目的とする。

【課題を解決するための手段】

【0008】

本発明の位相比較装置は、第一の入力信号と第二の入力信号との位相差に応じたパルスを生成する位相比較手段と、第一の入力信号の周期のN倍の時間を設定する時間設定手段と、位相比較手段により生成されたパルスを時間設定手段により設定された時間分積分する第一の積分手段と、既知の一定レベルの基準信号を時間設定手段により設定された時間分積分する第二の積分手段と、第一の積分手段による第一の積分値および第二の積分手段による第二の積分値を抽出し、第一の積分値および第二の積分値に応じて位相差を演算する位相差演算手段とを備えたものである。

【発明の効果】

【0009】

本発明によれば、時間設定手段が第一の入力信号の周期のN倍の時間を設定し、第一の積分手段が位相比較手段により生成されたパルスを時間設定手段により設定された時間分積分するように構成したので、第一の入力信号の周波数の1/N倍の周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0010】

また、第一の積分手段が位相比較手段により生成されたパルスを時間設定手段により設定された時間分積分し、第二の積分手段が既知の一定レベルの基準信号を時間設定手段により設定された時間分積分し、位相差演算手段が第一の積分手段による第一の積分値および第二の積分手段による第二の積分値に応じて位相差を演算するように構成したので、2つの入力信号の周波数が既知でなかったり、周波数が変動する場合であっても、2つの入力信号の位相差を演算することができる。

【0011】

さらに、位相比較手段が第一の入力信号と第二の入力信号との位相差に応じたパルスを生成し、第一の積分手段が位相比較手段により生成されたパルスを積分するように構成したので、第一の積分手段は、位相比較手段により生成されたパルスを積分するだけで良く、抽出される積分値の誤差変動を小さくすることができる効果がある。

【図面の簡単な説明】

【0012】

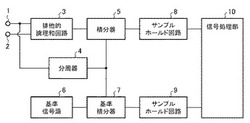

【図1】この発明の実施の形態1による位相比較装置を示す構成図である。

【図2】この発明の実施の形態1による位相比較装置の動作を示すタイミングチャートである。

【図3】この発明の実施の形態1による位相比較装置の出力信号スペクトラムを示す特性図である。

【図4】この発明の実施の形態1による位相比較装置の位相比較出力特性を示す特性図である。

【図5】この発明の実施の形態2による位相比較装置を示す構成図である。

【図6】この発明の実施の形態2による位相比較装置の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0013】

実施の形態1.

図1はこの発明の実施の形態1による位相比較装置を示す構成図である。

図1において、排他的論理和回路(位相比較手段、位相比較回路)3は、入力信号端子1,2からの入力信号の排他的論理和を取る。

分周器(時間設定手段)4は、入力信号端子1からの入力信号の周波数を2分周する。

【0014】

積分器(第一の積分手段)5は、排他的論理和回路3により生成されたパルスを分周器4により2分周された周期分積分する。

基準信号源6は、既知の一定レベルの基準信号を発生する。

基準積分器(第二の積分手段)7は、基準信号源6により発生された基準信号を分周器4により2分周された周期分積分する。

【0015】

サンプルホールド回路(位相差演算手段)8は、積分器5による停止後の積分値をサンプルホールドする。

サンプルホールド回路(位相差演算手段)9は、基準積分器7による停止後の積分値をサンプルホールドする。

信号処理部(位相差演算手段)10は、サンプルホールド回路8によりサンプルホールドされた積分値およびサンプルホールド回路9によりサンプルホールドされた積分値に応じて位相差を演算する。

【0016】

なお、図1の例では、位相比較装置の構成要素である排他的論理和回路3、分周器4、積分器5、基準信号源6、基準積分器7、サンプルホールド回路8,9、および信号処理部10が、例えば、半導体回路基板等のハードウエアで構成されていることを想定している。しかし、信号処理部10は、半導体回路基板等のソフトウエアで構成されていても良く、この場合は、信号処理部10の処理内容が記述されているプログラムをメモリに格納し、マイコンのCPUがメモリに格納されているプログラムを実行することにより、信号処理部10の機能を実現する。

【0017】

次に動作について説明する。

図2は位相比較装置の動作を示すタイミングチャートである。

以下、図1および図2を参照しながら説明する。

【0018】

入力信号端子1および入力信号端子2からの2つの入力信号は、排他的論理和回路3において位相比較される。排他的論理和回路3は、2つの入力信号の排他的論理和を取り、入力信号の立ち上がりおよび立ち下がりにおいて、位相差分のパルスを生成する。

【0019】

入力信号端子1からの入力信号は、分周器4にも供給され、分周器4は、入力信号端子1からの入力信号の周波数を2分周する。よって、分周器4は、入力信号端子1からの入力信号の周期の2倍の周期の信号を生成する。

【0020】

排他的論理和回路3により生成されたパルスは、積分器5に供給される。積分器5は、分周器4により出力されるパルスの立ち上がりで積分が開始され、排他的論理和回路3により生成されたパルスを積分し、2分周された周期後に積分を停止する。

【0021】

また、基準信号源6は、一定レベルの基準信号を発生し、基準積分器7に供給される。基準積分器7は、分周器4により出力されるパルスの立ち上がりで積分が開始され、基準信号源6により生成された一定レベルの基準信号を積分し、2分周された周期後に積分を停止する。

【0022】

サンプルホールド回路8は、積分器5による停止後の積分値をサンプルホールドし、サンプルホールド回路9は、基準積分器7による停止後の積分値をサンプルホールドする。例えば、積分器5および基準積分器7の積分停止後に、A/D変換器等により積分器5および基準積分器7の積分値(積分電圧)をサンプルホールドする。

【0023】

サンプルホールド回路8,9によりサンプルホールドされた各積分値は、信号処理部10に供給される。信号処理部10は、サンプルホールドされた各積分値に応じて位相差を演算する。

信号処理部10では、各積分値に応じて、例えば、以下のように位相差を演算する。

排他的論理和回路3の出力のHighレベルと基準信号源6の出力レベルとが同じであれば、サンプルホールド回路8の積分値をVp、サンプルホールド回路9の積分値をVrとすると、位相差φは、下記式(1)により演算することができる。

【0024】

その後、積分器5、基準積分器7、およびサンプルホールド回路8,9に保持された値はリセットされる。

次の位相差演算の際には、同様に、積分器5および基準積分器7が、分周器4により出力されるパルスの立ち上がりで積分を開始し、2分周された周期後に積分を停止し、信号処理部10では、各積分値に応じて位相差が演算される。

【0025】

次に実施の形態1の構成が効果を奏する原理について説明する。

図1および図2において、排他的論理和回路3は、2つの入力信号の排他的論理和を取り、入力信号1,2の立ち上がりおよび立ち下がりにおいて、位相差に応じたパルスを生成する。

この位相差に応じたパルスは、入力信号1,2の高調波成分を有し、0次成分が入力信号1,2に相当する。

【0026】

そのため、位相差に応じたパルスは、図3に実線および破線で示すように、直流成分0、基本周波数成分fin、基本周波数成分の高調波成分2finのスペクトラムを有する。

このまま何の処理もせずにサンプリングすると、サンプリングするタイミングにより出力レベルが変動し、測定値が自ら発生する信号成分により値が安定せず、雑音に見える。

【0027】

よって、上記特許文献1の第1図のように、ローパスフィルタを用いて高調波を抑圧し、直流電圧で表される位相差情報を正確にサンプリングできるようにするのが一般的である。しかし、ローパスフィルタは、排他的論理和回路3の出力信号がステップ応答的に立ち上がるので、ローパスフィルタの時定数に起因するステップ応答が収束する時間だけ待つ必要があり、ステップ応答が安定しないと正確なサンプリングが行えないという欠点が有る。

【0028】

この実施の形態1では、入力信号1の入力周波数finの周期の2倍の周期で区間積分することで、fin/2の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、fin,2fin,・・・の高調波成分を抑圧する。

よって、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0029】

図4に実施の形態1による位相比較装置の位相比較出力特性を示す。基準積分器7の出力レベルをフルスケールとし、位相に対しπラジアンの区間において線形な出力特性を有する。

【0030】

この実施の形態1によれば、分周器4が入力信号の周波数を2分周し、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分するように構成したので、入力信号の周波数の1/2倍の周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0031】

また、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分し、基準積分器7が既知の一定レベルの基準信号を分周器4により設定された周期分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、2つの入力信号の周波数が既知でなかったり、周波数が変動する場合であっても、2つの入力信号の位相差を演算することができる。

【0032】

さらに、排他的論理和回路3が2つの入力信号の位相差に応じたパルスを生成し、積分器5が排他的論理和回路3により生成されたパルスを積分するように構成したので、積分器5は、排他的論理和回路3により生成されたパルスを積分するだけで良く、抽出される積分値の誤差変動を小さくすることができる。

【0033】

なお、上記実施の形態1によれば、位相比較回路として排他的論理和回路3を適用したものを示したが、位相比較回路としてその他、アナログ乗算器またはRSフリップフロップを適用しても良く、それぞれの位相比較回路が持っている位相比較出力特性になるだけで、基本的に同様な動作になる。

【0034】

また、上記実施の形態1によれば、分周器4は、入力信号端子1からの入力信号の周波数を2分周するものとしたが、N(Nは任意の自然数)分周するものであっても良く、fin/Nの周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、同様にfin,2fin,・・・の高調波成分を抑圧することができる。

【0035】

実施の形態2.

図5はこの発明の実施の形態2による位相比較装置を示す構成図である。

図5において、コンパレータ(比較手段)11は、基準積分器7による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生する。

カウンタ(時間設定手段)12は、入力信号端子1からの入力信号の波数をカウントし、コンパレータ11によりトリガ信号が発生された場合に、トリガ信号の発生時の次の波のエッジでカウントを終了する。

なお、その他の構成については、分周器4を削除した以外は、図1に示した構成と同様である。

【0036】

次に動作について説明する。

図6は位相比較装置の動作を示すタイミングチャートである。

以下、図5および図6を参照しながら説明する。

【0037】

入力信号端子1および入力信号端子2からの2つの入力信号は、排他的論理和回路3において位相比較される。排他的論理和回路3は、2つの入力信号の排他的論理和を取り、入力信号の立ち上がりおよび立ち下がりにおいて、位相差分のパルスを生成する。

【0038】

入力信号端子1からの入力信号は、カウンタ12にも供給され、カウンタ12は、入力信号端子1からの入力信号の波数をカウントする。

【0039】

排他的論理和回路3により生成されたパルスは、積分器5に供給される。積分器5は、カウンタ12によるカウント開始により積分が開始され、排他的論理和回路3により生成されたパルスを積分する。

【0040】

また、基準信号源6は、一定レベルの基準信号を発生し、基準積分器7に供給される。基準積分器7は、カウンタ12によるカウント開始により積分が開始され、基準信号源6により生成された一定レベルの基準信号を積分する。

【0041】

コンパレータ11には、予め閾値が設定されており、基準積分器7による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生する。

カウンタ12は、コンパレータ11によりトリガ信号が発生された場合に、トリガ信号発生時の次の入力信号の波のエッジでカウントを終了する。図6では、カウント3でカウントを終了している。

積分器5および基準積分器7は、カウンタ12によるカウント終了により積分を停止する。

【0042】

サンプルホールド回路8は、積分器5による停止後の積分値をサンプルホールドし、サンプルホールド回路9は、基準積分器7による停止後の積分値をサンプルホールドする。

【0043】

サンプルホールド回路8,9によりサンプルホールドされた各積分値は、信号処理部10に供給される。信号処理部10は、サンプルホールドされた各積分値に応じて位相差を演算する。演算法は、実施の形態1の式(1)と同様である。

【0044】

その後、積分器5、基準積分器7、サンプルホールド回路8,9、およびカウンタ12に保持された値はリセットされる。

次の位相差演算の際には、同様に、積分器5および基準積分器7が、カウンタ12によるカウント開始により積分が開始され、カウント終了により積分を停止し、信号処理部10では、各積分値に応じて位相差が演算される。

【0045】

次に実施の形態2の構成が効果を奏する原理について説明する。

この実施の形態2においても、入力信号1の入力周波数finの周期の3倍の周期で区間積分することで、fin/3の周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、fin,2fin,・・・の高調波成分を抑圧する。

よって、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0046】

また、この実施の形態2による位相比較装置の位相比較出力特性は、図4と同様である。

【0047】

さらに、上記実施の形態1による位相比較装置では、入力信号の周波数が大きく変化する場合に、周波数により位相分解能が大きく変わってしまう場合がある。

これは、出力Vrは、1/finに比例するため、入力信号の周波数が高くなるほど出力Vrが低下し、位相分解能が低下するからである。

【0048】

これに対して、この実施の形態2による位相比較装置では、出力Vrが少なくともコンパレータ11に予め設定された閾値以上になるので、入力信号の周波数が高くなっても、カウント数が増えるだけであり、出力Vrをほぼ一定に保ち、位相分解能もほぼ一定に保つことができる。

【0049】

この実施の形態2によれば、カウンタ12が入力信号の波数を3カウントし、積分器5が排他的論理和回路3により生成されたパルスをカウンタ12により設定された時間分積分するように構成したので、入力信号の周波数の3倍の周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0050】

また、積分器5が排他的論理和回路3により生成されたパルスをカウンタ12により設定された時間分積分し、基準積分器7が既知の一定レベルの基準信号をカウンタ12により設定された時間分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、2つの入力信号の周波数が既知でなかったり、周波数が変動する場合であっても、2つの入力信号の位相差を演算することができる。

【0051】

さらに、排他的論理和回路3が2つの入力信号の位相差に応じたパルスを生成し、積分器5が排他的論理和回路3により生成されたパルスを積分するように構成したので、積分器5は、排他的論理和回路3により生成されたパルスを積分するだけで良く、抽出される積分値の誤差変動を小さくすることができる。

【0052】

さらに、コンパレータ11が基準積分器7による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生し、カウンタ12がコンパレータ11によりトリガ信号が発生された場合に、トリガ信号の発生時の次の波のエッジでカウントを終了するように構成したので、基準積分器7による積分値である出力Vrが少なくともコンパレータ11に予め設定された閾値以上になるので、入力信号の周波数が高くなっても、位相分解能もほぼ一定に保つことができる。

【0053】

なお、上記実施の形態2によれば、コンパレータ11には、予め閾値が設定されたものとしたが、コンパレータ11における閾値を可変設定自在にするものであっても良く、位相分解能を可変設定自在にすることができる。

【0054】

また、上記実施の形態2によれば、コンパレータ11およびカウンタ12を備え、カウンタ12は、コンパレータ11によりトリガ信号が発生された場合に、トリガ信号の発生時の次の波のエッジでカウントを終了するようにした。

しかし、カウンタ12は、入力信号端子1からの入力信号の波数をカウントし、予め設定されたN(Nは任意の自然数)波数だけカウントした場合に、次の波のエッジでカウントを終了するようにしても良い。この場合、コンパレータ11を備える必要が無く、構成を容易にすることができる。

【0055】

なお、本願発明は、その発明の範囲内において、各実施の形態の自由な組み合わせ、あるいは各実施の形態の任意の構成要素の変形、もしくは各実施の形態において任意の構成要素の省略が可能である。

【符号の説明】

【0056】

1,2 入力信号端子、3 排他的論理和回路、4 分周器、5 積分器、6 基準信号源、7 基準積分器、8,9 サンプルホールド回路、10 信号処理部、11 コンパレータ、12 カウンタ。

【技術分野】

【0001】

本発明は、2つの入力信号の位相差を演算する位相比較装置に関する。

【背景技術】

【0002】

従来の位相比較器として、2つの入力信号の位相差に応じたパルスを生成する排他的倫理和回路と、排他的倫理和回路の後段に接続され、2つの入力信号の位相差に応じた信号を出力するローパスフィルタとを備えたものがある(下記特許文献1の第1図)。

【0003】

また、従来の位相比較器として、2つの入力信号のうちの一方の入力信号の立ち上がりに応じて充電を開始し、他方の入力信号の立ち上がりに応じて充電を停止する積分器と、積分器の充電停止後の積分電圧を抽出し、その積分電圧を2つの入力信号の立ち上がり時間差の時間情報として出力するサンプルホールド回路とを備えたものがある(下記特許文献1の第5図)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭59−161119号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来の位相比較器は以上のように構成されているので、以下の課題がある。

排他的倫理和回路の後段にローパスフィルタを接続した位相比較器は、2つの入力信号がパルス波の場合に、排他的倫理和回路の出力信号がステップ応答的に立ち上がる。よって、ローパスフィルタの出力信号が安定するためには、ローパスフィルタの時定数に起因するステップ応答が収束する時間だけ待つ必要があり、高調波の影響の抑圧量が多ければ多いほど、ステップ応答収束時間が長くなる。また、あまりステップ応答時間が長くなると出力信号が立ち下がり、位相比較できなくなってしまう課題がある。

【0006】

積分器の後段にサンプルホールド回路を接続した位相比較器は、積分電圧を2つの入力信号の立ち上がり時間差の時間情報として出力する。よって、2つの入力信号の周波数が既知であれば、立ち上がり時間差の時間情報と、既知の周波数とにより、2つの入力信号の位相差を演算することができるが、2つの入力信号の周波数が既知でなかったり、周波数が変動する場合には、2つの入力信号の位相差を演算することができない課題がある。

また、2つの異なる入力信号の立ち上がりに応じて、積分器の充電開始および充電停止を制御するので、充電開始の際の遅延と、充電停止の際の遅延とが個別に発生し、抽出される積分値の誤差変動が大きくなる課題がある。

【0007】

本発明は、以上のような課題を解消するためになされたものであり、ステップ応答収束時間だけ待つ必要なく積分値を抽出し、また、入力信号の周波数が既知でなくても抽出した積分値に応じて位相差を演算し、さらに、積分値の誤差変動も小さい位相比較装置を得ることを目的とする。

【課題を解決するための手段】

【0008】

本発明の位相比較装置は、第一の入力信号と第二の入力信号との位相差に応じたパルスを生成する位相比較手段と、第一の入力信号の周期のN倍の時間を設定する時間設定手段と、位相比較手段により生成されたパルスを時間設定手段により設定された時間分積分する第一の積分手段と、既知の一定レベルの基準信号を時間設定手段により設定された時間分積分する第二の積分手段と、第一の積分手段による第一の積分値および第二の積分手段による第二の積分値を抽出し、第一の積分値および第二の積分値に応じて位相差を演算する位相差演算手段とを備えたものである。

【発明の効果】

【0009】

本発明によれば、時間設定手段が第一の入力信号の周期のN倍の時間を設定し、第一の積分手段が位相比較手段により生成されたパルスを時間設定手段により設定された時間分積分するように構成したので、第一の入力信号の周波数の1/N倍の周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0010】

また、第一の積分手段が位相比較手段により生成されたパルスを時間設定手段により設定された時間分積分し、第二の積分手段が既知の一定レベルの基準信号を時間設定手段により設定された時間分積分し、位相差演算手段が第一の積分手段による第一の積分値および第二の積分手段による第二の積分値に応じて位相差を演算するように構成したので、2つの入力信号の周波数が既知でなかったり、周波数が変動する場合であっても、2つの入力信号の位相差を演算することができる。

【0011】

さらに、位相比較手段が第一の入力信号と第二の入力信号との位相差に応じたパルスを生成し、第一の積分手段が位相比較手段により生成されたパルスを積分するように構成したので、第一の積分手段は、位相比較手段により生成されたパルスを積分するだけで良く、抽出される積分値の誤差変動を小さくすることができる効果がある。

【図面の簡単な説明】

【0012】

【図1】この発明の実施の形態1による位相比較装置を示す構成図である。

【図2】この発明の実施の形態1による位相比較装置の動作を示すタイミングチャートである。

【図3】この発明の実施の形態1による位相比較装置の出力信号スペクトラムを示す特性図である。

【図4】この発明の実施の形態1による位相比較装置の位相比較出力特性を示す特性図である。

【図5】この発明の実施の形態2による位相比較装置を示す構成図である。

【図6】この発明の実施の形態2による位相比較装置の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0013】

実施の形態1.

図1はこの発明の実施の形態1による位相比較装置を示す構成図である。

図1において、排他的論理和回路(位相比較手段、位相比較回路)3は、入力信号端子1,2からの入力信号の排他的論理和を取る。

分周器(時間設定手段)4は、入力信号端子1からの入力信号の周波数を2分周する。

【0014】

積分器(第一の積分手段)5は、排他的論理和回路3により生成されたパルスを分周器4により2分周された周期分積分する。

基準信号源6は、既知の一定レベルの基準信号を発生する。

基準積分器(第二の積分手段)7は、基準信号源6により発生された基準信号を分周器4により2分周された周期分積分する。

【0015】

サンプルホールド回路(位相差演算手段)8は、積分器5による停止後の積分値をサンプルホールドする。

サンプルホールド回路(位相差演算手段)9は、基準積分器7による停止後の積分値をサンプルホールドする。

信号処理部(位相差演算手段)10は、サンプルホールド回路8によりサンプルホールドされた積分値およびサンプルホールド回路9によりサンプルホールドされた積分値に応じて位相差を演算する。

【0016】

なお、図1の例では、位相比較装置の構成要素である排他的論理和回路3、分周器4、積分器5、基準信号源6、基準積分器7、サンプルホールド回路8,9、および信号処理部10が、例えば、半導体回路基板等のハードウエアで構成されていることを想定している。しかし、信号処理部10は、半導体回路基板等のソフトウエアで構成されていても良く、この場合は、信号処理部10の処理内容が記述されているプログラムをメモリに格納し、マイコンのCPUがメモリに格納されているプログラムを実行することにより、信号処理部10の機能を実現する。

【0017】

次に動作について説明する。

図2は位相比較装置の動作を示すタイミングチャートである。

以下、図1および図2を参照しながら説明する。

【0018】

入力信号端子1および入力信号端子2からの2つの入力信号は、排他的論理和回路3において位相比較される。排他的論理和回路3は、2つの入力信号の排他的論理和を取り、入力信号の立ち上がりおよび立ち下がりにおいて、位相差分のパルスを生成する。

【0019】

入力信号端子1からの入力信号は、分周器4にも供給され、分周器4は、入力信号端子1からの入力信号の周波数を2分周する。よって、分周器4は、入力信号端子1からの入力信号の周期の2倍の周期の信号を生成する。

【0020】

排他的論理和回路3により生成されたパルスは、積分器5に供給される。積分器5は、分周器4により出力されるパルスの立ち上がりで積分が開始され、排他的論理和回路3により生成されたパルスを積分し、2分周された周期後に積分を停止する。

【0021】

また、基準信号源6は、一定レベルの基準信号を発生し、基準積分器7に供給される。基準積分器7は、分周器4により出力されるパルスの立ち上がりで積分が開始され、基準信号源6により生成された一定レベルの基準信号を積分し、2分周された周期後に積分を停止する。

【0022】

サンプルホールド回路8は、積分器5による停止後の積分値をサンプルホールドし、サンプルホールド回路9は、基準積分器7による停止後の積分値をサンプルホールドする。例えば、積分器5および基準積分器7の積分停止後に、A/D変換器等により積分器5および基準積分器7の積分値(積分電圧)をサンプルホールドする。

【0023】

サンプルホールド回路8,9によりサンプルホールドされた各積分値は、信号処理部10に供給される。信号処理部10は、サンプルホールドされた各積分値に応じて位相差を演算する。

信号処理部10では、各積分値に応じて、例えば、以下のように位相差を演算する。

排他的論理和回路3の出力のHighレベルと基準信号源6の出力レベルとが同じであれば、サンプルホールド回路8の積分値をVp、サンプルホールド回路9の積分値をVrとすると、位相差φは、下記式(1)により演算することができる。

【0024】

その後、積分器5、基準積分器7、およびサンプルホールド回路8,9に保持された値はリセットされる。

次の位相差演算の際には、同様に、積分器5および基準積分器7が、分周器4により出力されるパルスの立ち上がりで積分を開始し、2分周された周期後に積分を停止し、信号処理部10では、各積分値に応じて位相差が演算される。

【0025】

次に実施の形態1の構成が効果を奏する原理について説明する。

図1および図2において、排他的論理和回路3は、2つの入力信号の排他的論理和を取り、入力信号1,2の立ち上がりおよび立ち下がりにおいて、位相差に応じたパルスを生成する。

この位相差に応じたパルスは、入力信号1,2の高調波成分を有し、0次成分が入力信号1,2に相当する。

【0026】

そのため、位相差に応じたパルスは、図3に実線および破線で示すように、直流成分0、基本周波数成分fin、基本周波数成分の高調波成分2finのスペクトラムを有する。

このまま何の処理もせずにサンプリングすると、サンプリングするタイミングにより出力レベルが変動し、測定値が自ら発生する信号成分により値が安定せず、雑音に見える。

【0027】

よって、上記特許文献1の第1図のように、ローパスフィルタを用いて高調波を抑圧し、直流電圧で表される位相差情報を正確にサンプリングできるようにするのが一般的である。しかし、ローパスフィルタは、排他的論理和回路3の出力信号がステップ応答的に立ち上がるので、ローパスフィルタの時定数に起因するステップ応答が収束する時間だけ待つ必要があり、ステップ応答が安定しないと正確なサンプリングが行えないという欠点が有る。

【0028】

この実施の形態1では、入力信号1の入力周波数finの周期の2倍の周期で区間積分することで、fin/2の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、fin,2fin,・・・の高調波成分を抑圧する。

よって、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0029】

図4に実施の形態1による位相比較装置の位相比較出力特性を示す。基準積分器7の出力レベルをフルスケールとし、位相に対しπラジアンの区間において線形な出力特性を有する。

【0030】

この実施の形態1によれば、分周器4が入力信号の周波数を2分周し、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分するように構成したので、入力信号の周波数の1/2倍の周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0031】

また、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分し、基準積分器7が既知の一定レベルの基準信号を分周器4により設定された周期分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、2つの入力信号の周波数が既知でなかったり、周波数が変動する場合であっても、2つの入力信号の位相差を演算することができる。

【0032】

さらに、排他的論理和回路3が2つの入力信号の位相差に応じたパルスを生成し、積分器5が排他的論理和回路3により生成されたパルスを積分するように構成したので、積分器5は、排他的論理和回路3により生成されたパルスを積分するだけで良く、抽出される積分値の誤差変動を小さくすることができる。

【0033】

なお、上記実施の形態1によれば、位相比較回路として排他的論理和回路3を適用したものを示したが、位相比較回路としてその他、アナログ乗算器またはRSフリップフロップを適用しても良く、それぞれの位相比較回路が持っている位相比較出力特性になるだけで、基本的に同様な動作になる。

【0034】

また、上記実施の形態1によれば、分周器4は、入力信号端子1からの入力信号の周波数を2分周するものとしたが、N(Nは任意の自然数)分周するものであっても良く、fin/Nの周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、同様にfin,2fin,・・・の高調波成分を抑圧することができる。

【0035】

実施の形態2.

図5はこの発明の実施の形態2による位相比較装置を示す構成図である。

図5において、コンパレータ(比較手段)11は、基準積分器7による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生する。

カウンタ(時間設定手段)12は、入力信号端子1からの入力信号の波数をカウントし、コンパレータ11によりトリガ信号が発生された場合に、トリガ信号の発生時の次の波のエッジでカウントを終了する。

なお、その他の構成については、分周器4を削除した以外は、図1に示した構成と同様である。

【0036】

次に動作について説明する。

図6は位相比較装置の動作を示すタイミングチャートである。

以下、図5および図6を参照しながら説明する。

【0037】

入力信号端子1および入力信号端子2からの2つの入力信号は、排他的論理和回路3において位相比較される。排他的論理和回路3は、2つの入力信号の排他的論理和を取り、入力信号の立ち上がりおよび立ち下がりにおいて、位相差分のパルスを生成する。

【0038】

入力信号端子1からの入力信号は、カウンタ12にも供給され、カウンタ12は、入力信号端子1からの入力信号の波数をカウントする。

【0039】

排他的論理和回路3により生成されたパルスは、積分器5に供給される。積分器5は、カウンタ12によるカウント開始により積分が開始され、排他的論理和回路3により生成されたパルスを積分する。

【0040】

また、基準信号源6は、一定レベルの基準信号を発生し、基準積分器7に供給される。基準積分器7は、カウンタ12によるカウント開始により積分が開始され、基準信号源6により生成された一定レベルの基準信号を積分する。

【0041】

コンパレータ11には、予め閾値が設定されており、基準積分器7による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生する。

カウンタ12は、コンパレータ11によりトリガ信号が発生された場合に、トリガ信号発生時の次の入力信号の波のエッジでカウントを終了する。図6では、カウント3でカウントを終了している。

積分器5および基準積分器7は、カウンタ12によるカウント終了により積分を停止する。

【0042】

サンプルホールド回路8は、積分器5による停止後の積分値をサンプルホールドし、サンプルホールド回路9は、基準積分器7による停止後の積分値をサンプルホールドする。

【0043】

サンプルホールド回路8,9によりサンプルホールドされた各積分値は、信号処理部10に供給される。信号処理部10は、サンプルホールドされた各積分値に応じて位相差を演算する。演算法は、実施の形態1の式(1)と同様である。

【0044】

その後、積分器5、基準積分器7、サンプルホールド回路8,9、およびカウンタ12に保持された値はリセットされる。

次の位相差演算の際には、同様に、積分器5および基準積分器7が、カウンタ12によるカウント開始により積分が開始され、カウント終了により積分を停止し、信号処理部10では、各積分値に応じて位相差が演算される。

【0045】

次に実施の形態2の構成が効果を奏する原理について説明する。

この実施の形態2においても、入力信号1の入力周波数finの周期の3倍の周期で区間積分することで、fin/3の周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、fin,2fin,・・・の高調波成分を抑圧する。

よって、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0046】

また、この実施の形態2による位相比較装置の位相比較出力特性は、図4と同様である。

【0047】

さらに、上記実施の形態1による位相比較装置では、入力信号の周波数が大きく変化する場合に、周波数により位相分解能が大きく変わってしまう場合がある。

これは、出力Vrは、1/finに比例するため、入力信号の周波数が高くなるほど出力Vrが低下し、位相分解能が低下するからである。

【0048】

これに対して、この実施の形態2による位相比較装置では、出力Vrが少なくともコンパレータ11に予め設定された閾値以上になるので、入力信号の周波数が高くなっても、カウント数が増えるだけであり、出力Vrをほぼ一定に保ち、位相分解能もほぼ一定に保つことができる。

【0049】

この実施の形態2によれば、カウンタ12が入力信号の波数を3カウントし、積分器5が排他的論理和回路3により生成されたパルスをカウンタ12により設定された時間分積分するように構成したので、入力信号の周波数の3倍の周波数の整数倍の周波数にヌル(Null)点のできるsyncフィルタ特性が形成されることを利用し、簡単な構成で短時間で高周波のフィルタリングができ、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。

【0050】

また、積分器5が排他的論理和回路3により生成されたパルスをカウンタ12により設定された時間分積分し、基準積分器7が既知の一定レベルの基準信号をカウンタ12により設定された時間分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、2つの入力信号の周波数が既知でなかったり、周波数が変動する場合であっても、2つの入力信号の位相差を演算することができる。

【0051】

さらに、排他的論理和回路3が2つの入力信号の位相差に応じたパルスを生成し、積分器5が排他的論理和回路3により生成されたパルスを積分するように構成したので、積分器5は、排他的論理和回路3により生成されたパルスを積分するだけで良く、抽出される積分値の誤差変動を小さくすることができる。

【0052】

さらに、コンパレータ11が基準積分器7による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生し、カウンタ12がコンパレータ11によりトリガ信号が発生された場合に、トリガ信号の発生時の次の波のエッジでカウントを終了するように構成したので、基準積分器7による積分値である出力Vrが少なくともコンパレータ11に予め設定された閾値以上になるので、入力信号の周波数が高くなっても、位相分解能もほぼ一定に保つことができる。

【0053】

なお、上記実施の形態2によれば、コンパレータ11には、予め閾値が設定されたものとしたが、コンパレータ11における閾値を可変設定自在にするものであっても良く、位相分解能を可変設定自在にすることができる。

【0054】

また、上記実施の形態2によれば、コンパレータ11およびカウンタ12を備え、カウンタ12は、コンパレータ11によりトリガ信号が発生された場合に、トリガ信号の発生時の次の波のエッジでカウントを終了するようにした。

しかし、カウンタ12は、入力信号端子1からの入力信号の波数をカウントし、予め設定されたN(Nは任意の自然数)波数だけカウントした場合に、次の波のエッジでカウントを終了するようにしても良い。この場合、コンパレータ11を備える必要が無く、構成を容易にすることができる。

【0055】

なお、本願発明は、その発明の範囲内において、各実施の形態の自由な組み合わせ、あるいは各実施の形態の任意の構成要素の変形、もしくは各実施の形態において任意の構成要素の省略が可能である。

【符号の説明】

【0056】

1,2 入力信号端子、3 排他的論理和回路、4 分周器、5 積分器、6 基準信号源、7 基準積分器、8,9 サンプルホールド回路、10 信号処理部、11 コンパレータ、12 カウンタ。

【特許請求の範囲】

【請求項1】

第一の入力信号と第二の入力信号との位相差に応じたパルスを生成する位相比較手段と、

上記第一の入力信号の周期のN(Nは任意の自然数)倍の時間を設定する時間設定手段と、

上記位相比較手段により生成されたパルスを上記時間設定手段により設定された時間分積分する第一の積分手段と、

既知の一定レベルの基準信号を上記時間設定手段により設定された時間分積分する第二の積分手段と、

上記第一の積分手段による第一の積分値および上記第二の積分手段による第二の積分値を抽出し、それら第一の積分値および第二の積分値に応じて位相差を演算する位相差演算手段とを備えた位相比較装置。

【請求項2】

上記第二の積分手段による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生する比較手段とを備え、

上記時間設定手段は、

上記比較手段によりトリガ信号が発生された場合に上記第一の入力信号の周期のN倍の時間の終了時を設定することを特徴とする請求項1記載の位相比較装置。

【請求項3】

第一の入力信号と第二の入力信号との位相差に応じたパルスを生成する位相比較回路と、

上記第一の入力信号の周波数をN(Nは任意の自然数)分周する分周器と、

上記位相比較回路により生成されたパルスを上記分周器によりN分周された周期分積分する第一の積分器と、

一定レベルの基準信号を発生する基準信号源と、

上記基準信号源により発生された基準信号を上記分周器によりN分周された周期分積分する第二の積分器と、

上記第一の積分器による停止後の第一の積分値を抽出する第一のサンプルホールド回路と、

上記第二の積分器による停止後の第二の積分値を抽出する第二のサンプルホールド回路と、

上記第一のサンプルホールド回路により抽出された第一の積分値および上記第二のサンプルホールド回路により抽出された第二の積分値に応じて位相差を演算する信号処理部とを備えた位相比較装置。

【請求項4】

第一の入力信号と第二の入力信号との位相差に応じたパルスを生成する位相比較回路と、

上記第一の入力信号の波数をN(Nは任意の自然数)カウントした場合にカウントを終了するカウンタと、

上記カウンタによるカウントの開始時に上記位相比較回路により生成されたパルスの積分を開始し、上記カウンタによるカウントの終了時に積分を停止する第一の積分器と、

一定レベルの基準信号を発生する基準信号源と、

上記カウンタによるカウントの開始時に上記基準信号源により発生された基準信号の積分を開始し、上記カウンタによるカウントの終了時に積分を停止する第二の積分器と、

上記第一の積分器による停止後の第一の積分値を抽出する第一のサンプルホールド回路と、

上記第二の積分器による停止後の第二の積分値を抽出する第二のサンプルホールド回路と、

上記第一のサンプルホールド回路により抽出された第一の積分値および上記第二のサンプルホールド回路により抽出された第二の積分値に応じて位相差を演算する信号処理部とを備えた位相比較装置。

【請求項5】

上記第二の積分手段による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生するコンパレータとを備え、

上記カウンタは、

上記第一の入力信号の波数をカウントし、上記コンパレータによりトリガ信号が発生された場合に、トリガ信号の発生時の次の波のエッジでカウントを終了することを特徴とする請求項4記載の位相比較装置。

【請求項1】

第一の入力信号と第二の入力信号との位相差に応じたパルスを生成する位相比較手段と、

上記第一の入力信号の周期のN(Nは任意の自然数)倍の時間を設定する時間設定手段と、

上記位相比較手段により生成されたパルスを上記時間設定手段により設定された時間分積分する第一の積分手段と、

既知の一定レベルの基準信号を上記時間設定手段により設定された時間分積分する第二の積分手段と、

上記第一の積分手段による第一の積分値および上記第二の積分手段による第二の積分値を抽出し、それら第一の積分値および第二の積分値に応じて位相差を演算する位相差演算手段とを備えた位相比較装置。

【請求項2】

上記第二の積分手段による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生する比較手段とを備え、

上記時間設定手段は、

上記比較手段によりトリガ信号が発生された場合に上記第一の入力信号の周期のN倍の時間の終了時を設定することを特徴とする請求項1記載の位相比較装置。

【請求項3】

第一の入力信号と第二の入力信号との位相差に応じたパルスを生成する位相比較回路と、

上記第一の入力信号の周波数をN(Nは任意の自然数)分周する分周器と、

上記位相比較回路により生成されたパルスを上記分周器によりN分周された周期分積分する第一の積分器と、

一定レベルの基準信号を発生する基準信号源と、

上記基準信号源により発生された基準信号を上記分周器によりN分周された周期分積分する第二の積分器と、

上記第一の積分器による停止後の第一の積分値を抽出する第一のサンプルホールド回路と、

上記第二の積分器による停止後の第二の積分値を抽出する第二のサンプルホールド回路と、

上記第一のサンプルホールド回路により抽出された第一の積分値および上記第二のサンプルホールド回路により抽出された第二の積分値に応じて位相差を演算する信号処理部とを備えた位相比較装置。

【請求項4】

第一の入力信号と第二の入力信号との位相差に応じたパルスを生成する位相比較回路と、

上記第一の入力信号の波数をN(Nは任意の自然数)カウントした場合にカウントを終了するカウンタと、

上記カウンタによるカウントの開始時に上記位相比較回路により生成されたパルスの積分を開始し、上記カウンタによるカウントの終了時に積分を停止する第一の積分器と、

一定レベルの基準信号を発生する基準信号源と、

上記カウンタによるカウントの開始時に上記基準信号源により発生された基準信号の積分を開始し、上記カウンタによるカウントの終了時に積分を停止する第二の積分器と、

上記第一の積分器による停止後の第一の積分値を抽出する第一のサンプルホールド回路と、

上記第二の積分器による停止後の第二の積分値を抽出する第二のサンプルホールド回路と、

上記第一のサンプルホールド回路により抽出された第一の積分値および上記第二のサンプルホールド回路により抽出された第二の積分値に応じて位相差を演算する信号処理部とを備えた位相比較装置。

【請求項5】

上記第二の積分手段による積分値と予め設定された閾値とを比較し、積分値が閾値を越えた場合にトリガ信号を発生するコンパレータとを備え、

上記カウンタは、

上記第一の入力信号の波数をカウントし、上記コンパレータによりトリガ信号が発生された場合に、トリガ信号の発生時の次の波のエッジでカウントを終了することを特徴とする請求項4記載の位相比較装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−34119(P2013−34119A)

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願番号】特願2011−169378(P2011−169378)

【出願日】平成23年8月2日(2011.8.2)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願日】平成23年8月2日(2011.8.2)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]