位置検出装置

【課題】ホール効果を利用した位置検出装置において、従来よりも部品点数および部品コストを低減する。

【解決手段】制御回路20が実装された回路基板14上に、導電素子21〜25をパターン配線し、制御回路20は、導電素子21〜25のそれぞれに対して、所定の第1の方向に電流を供給すると共に、電流が流れている導電素子21〜29において、第1の方向と交差する第2の方向の電位差を検出し、導電素子21〜25のそれぞれについて検出した電位差に基づいて、導電素子21〜25に対する磁石の相対位置を検出する。

【解決手段】制御回路20が実装された回路基板14上に、導電素子21〜25をパターン配線し、制御回路20は、導電素子21〜25のそれぞれに対して、所定の第1の方向に電流を供給すると共に、電流が流れている導電素子21〜29において、第1の方向と交差する第2の方向の電位差を検出し、導電素子21〜25のそれぞれについて検出した電位差に基づいて、導電素子21〜25に対する磁石の相対位置を検出する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ホール効果を利用した位置検出装置に関するものである。

【背景技術】

【0002】

従来、ホール効果を利用して、電磁変換素子に対する磁石の相対位置を検出する位置検出装置が知られている(例えば、特許文献1参照)。

【0003】

このような位置検出装置においては、磁石と電磁変換素子の相対位置に応じて電磁変換素子における電位差が変化することを利用し、上記電位差に応じた信号を電磁変換素子が出力し、制御部が、電磁変換素子の上記出力に応じて、磁石と電磁変換素子の相対位置を特定するようになっている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−209651号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、従来の位置検出装置は、電磁変換素子として、専用のICを採用しているので、制御部を実装する回路基板に加え、電磁変換素子用のICを用意しなければならず、部品点数および部品コストが増大する。

【0006】

本発明は上記点に鑑み、ホール効果を利用した位置検出装置において、従来よりも部品点数および部品コストを低減することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するための請求項1に記載の発明は、回路基板(14)と、発生する磁界が前記回路基板(14)を貫くような配置で前記回路基板(14)に対して相対的に移動する磁石(13)と、前記回路基板(14)上にパターン配線された1個以上の導電素子(21〜29)と、前記回路基板(14)上に実装された制御回路(20)と、前記制御回路(20)から前記1個以上の導電素子(21〜29)のそれぞれに対して、対象の導電素子上の第1の点(P)から対象の導電素子上の第2の点(Q)への電流が発生するよう電流を供給するための配線であると共に、前記第1の点(P)から前記第2の点(Q)への方向を第1の方向とし、対象の導電素子上の第3の点(R)から見て前記第1の方向と交差する方向を第2の方向とすると、前記第3の点(R)と、対象の導電素子において前記第3の点(R)から見て前記第2の方向にある第4の点(S)と、の間の電位差を検出するための位置検出用配線(61〜65)と、を備え、前記制御回路(20)は、前記1個以上の導電素子(21〜29)のそれぞれに対して、対象の導電素子の前記第1の点(P)から前記第2の点(Q)まで電流が流れるよう、対象の導電素子に電流を供給すると共に、対象の導電素子(21〜29)の前記第3の点(R)と第4の点(S)との間の電位差を検出し、前記1個以上の導電素子(21〜29)のそれぞれについて検出した前記電位差に基づいて、前記1個以上の導電素子(21〜29)に対する前記磁石(13)の相対位置に応じた作動を行う位置検出装置である。

【0008】

このように、電磁変換素子として、1個以上の導電素子が、制御回路(20)と共に回路基板(14)上にパターン配線され、この導電素子に発生する電位差に基づいて、1個以上の導電素子(21〜29)に対する磁石(13)の相対位置を検出することができる。このように、電磁変換素子をパターン配線することで、ICとして電磁変換素子を構成するよりも、部品点数が減り、かつ、部品コストが低減される。

【0009】

また、請求項2に記載の発明は、請求項1に記載の位置検出装置において、前記回路基板(14)には、前記位置検出用配線(61〜65)以外の他の配線および回路部品(51)も配置されていることを特徴とする。

【0010】

このように、他の配線および回路部品(51)が実装されている回路基板(14)に、位置検出用配線(61〜65)および導電素子を配置することで、既存の回路基板(14)を有効に利用して位置検出を行うことができる。

【0011】

また、請求項3に記載の発明は、請求項1または2に記載の位置検出装置において、前記回路基板(14)に設けられた回路部品のうち、所定の高さよりも低い回路部品は、前記回路基板(14)の前記磁石(13)側の面に実装され、所定の高さ以上の回路部品は、そのすべてが、前記回路基板(14)の前記磁石(13)側とは反対側の面に実装されていることを特徴とする。

【0012】

このように、所定の高さ以上の回路部品は、そのすべてが、回路基板(14)の磁石(13)側とは反対側の面に実装されていることで、磁石(13)を回路基板(14)に近づけ易くなる。

【0013】

また、請求項4に記載の発明は、請求項1ないし3のいずれか1つに記載の位置検出装置前記1個以上の導電素子(21〜29)は、複数個の導電素子(21〜29)であることを特徴とする。

【0014】

また、請求項5に記載の発明は、請求項1ないし4のいずれか1つに記載の位置検出装置において、前記1個以上の導電素子(21〜29)のそれぞれは、前記位置検出用配線(61〜65)よりも太くパターン配線されていることを特徴とする。このようにすることで、導電素子を貫く磁束を大きくすることができるので、位置検出の感度を向上することができる。

【0015】

なお、上記および特許請求の範囲における括弧内の符号は、特許請求の範囲に記載された用語と後述の実施形態に記載される当該用語を例示する具体物等との対応関係を示すものである。

【図面の簡単な説明】

【0016】

【図1】本発明の実施形態に係る位置検出装置1の斜視図である。

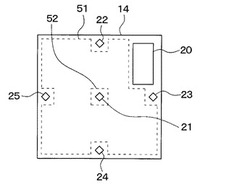

【図2】位置検出装置1の平面図である。

【図3】図2のA−A断面図である。

【図4】回路基板14の磁石側の面を示す図である。

【図5】回路基板14の

【図6】導電素子21、位置検出用配線61〜65、マイクロコントローラ20の電気的接続関係を示す図である。

【図7】磁石13の位置の一例を示す図である。

【図8】磁石13の磁束13a、13bが導電素子25を貫く状態を示す図である。

【図9】導電素子25に電位差が発生する状態を示す図である。

【図10】各導電素子のベース電圧を特定する手順のフローチャートである。

【図11】各導電素子の電流を均一にするための処理のフローチャートである。

【図12】磁石の位置検出のためのマイクロコントローラの処理を示すフローチャートである。

【図13】回路基板14が多層基板になっている場合の導電素子25から28の配置を示す図である。

【図14】導電素子21〜29の配置例を示す図である。

【図15】導電素子23、35の配置例を示す図である。

【図16】導電素子21〜28の配置例を示す図である。

【図17】導電素子21の配置例を示す図である。

【発明を実施するための形態】

【0017】

以下、本発明の一実施形態について説明する。図1、図2に、本実施形態に係る位置検出装置1の外観を斜視図および平面図で示し、図3に、図2のA−A断面図を示す。これら図1〜3に示すように、位置検出装置1は、筐体11と、操作部12と、磁石13と、回路基板14とを備えている。

【0018】

操作部12は、ユーザの操作を直接受ける部材であり、ユーザの操作に応じて、筐体11の上面に設けられた十字型のスリット11aに沿って前後方向(図2の上下方向)および左右方向(図2の左右方向)に移動するようになっている。磁石13は、筐体11内に収容されると共に、操作部12の下端に固定され、操作部12と共に移動するようになっている。そして、この磁石13は、両極が磁石13の上端(図3の上方向を上とする)および下端に位置するように配置されている。

【0019】

プリント基板である回路基板14は、筐体11内に収容されると共に、筐体11に対して固定されている。また回路基板14は、磁石13の下側において、磁石13に対向して配置されると共に、回路基板14と磁石13の距離は、磁石13の発生する磁界が回路基板14を貫くようになっている。

【0020】

なお、筐体11は操作部12に対して移動し、磁石13は操作部12と共に移動し、回路基板14は筐体11に固定されているので、磁石13は回路基板14に対して相対的に移動する。

【0021】

次に、回路基板14について詳細に説明する。図4に、回路基板14の磁石13側の表面(以下、単に回路基板14の上面という)を示す。回路基板14の上面には、マイクロコントローラ20(制御部の一例に相当する)が実装されている。

【0022】

また、回路基板14の上面には、5つの導電素子21〜25がパターン配線されている。また、回路基板14には、導電素子21〜25以外にも、破線51で囲まれた範囲内に他の線がパターン配線されており、また、回路部品(コンデンサ、抵抗、IC等)が実装されている。

【0023】

導電素子21〜25は、回路基板14の上面の中央にプリントされた導電素子21、前端部中央にプリントされた導電素子22、右端部中央にプリントされた導電素子23、後端部中央に配置された導電素子24、左端部中央に配置された導電素子25から成り、それぞれ、導電性材料(例えばアルミニウム、銅)によってパターン配線された矩形板形状の部材である。

【0024】

これら導電素子21〜25のそれぞれとマイクロコントローラ20とは、後述するように、各導電素子21〜25の2点(第1の点および第2の点に相当する)間に電流を流すと共に各導電素子の他の2点(第3の点および第4の点に相当する)における電位差を検出するための位置検出用配線によって接続されている。これら位置検出用配線も、回路基板14の破線51で囲まれた範囲内にパターン配線されている。

【0025】

なお、導電素子21〜25の回路基板14に対するサイズ比率は、図4のように、1:数十程度でもよいし、1:1000程度でもよい。例えば、回路基板14が1辺10cmの正方形形状を有している場合、導電素子21〜25の全長が0.1mm程度であってもよい。

【0026】

ここで、回路基板14に実装される回路部品の高さについて説明する。本実施形態では、磁石13の磁束が回路基板14を貫くようになっている必要があるので、磁石13をできる限り回路基板14に近づけたい。そのために、図5の側面図に示すように、回路基板14に設けられた回路部品のうち、所定の高さよりも低い回路部品は、回路基板14の上面に実装され、所定の高さ以上の回路部品は、そのすべてが、回路基板14の磁石13側とは反対側の面(以下、下面という)に実装されている。ここで、所定の高さは、磁石13から回路基板14の上面までの最短距離hよりも小さい値(例えばhの0.8倍)とする。なお、この所定の高さよりも低い回路部品は、回路基板14の上面のみならず下面に実装されていてもよい。このように、所定の高さ以上の回路部品は、そのすべてが、回路基板14の下面に実装されていることで、磁石13を回路基板14に近づけ易くなる。

【0027】

次に、図6を参照して、導電素子21〜25のそれぞれをマイクロコントローラ20に接続する位置検出用配線61〜65について説明する。

【0028】

まず、導電素子21および導電素子21用の位置検出用配線61について説明する。位置検出用配線61は、チップ抵抗31、スイッチ41a〜41d、およびパターン配線を含んでいる。

【0029】

この位置検出用配線61により、導電素子21の矩形の頂点の1つである点P(第1の点に相当する)は、チップ抵抗31の一端に接続され、チップ抵抗31の他端が、マイクロコントローラ20のDA端子20aに接続される。また、導電素子21の矩形の別の頂点の1つである点Q(第2の点に相当する)は、マイクロコントローラ20のGND端子20hに接続される。これらの配線により、DA端子20aから電圧を印加することで、点Pから点Qへの電流が発生する。

【0030】

また、導電素子21の矩形の別の頂点の1つである点R(第3の点に相当する)は、スイッチ41dを介してマイクロコントローラ20のAD端子20gに接続される。また、導電素子21の矩形の別の頂点の1つである点S(第4の点に相当する)は、スイッチ41cを介してマイクロコントローラ20の他のAD端子20fに接続される。これらの配線により、点Rと点Sの間の電位差をマイクロコントローラ20が検出することができる。

【0031】

また、導電素子21とチップ抵抗31とを繋ぐ配線から、スイッチ41bを介してマイクロコントローラ20のAD端子20gに接続する配線が伸びている。また、チップ抵抗31とマイクロコントローラ20のDA端子20aとを繋ぐ配線から、スイッチ41aを介してマイクロコントローラ20のAD端子20fに接続する配線が伸びている。これら、チップ抵抗31の両端の電位差をマイクロコントローラ20が検出することができる。

【0032】

なお、位置検出用配線61のうち、導電素子21の点P、Q、R、Sに接続している配線よりも、導電素子21の方が太くパターン配線されている。このようにすることで、導電素子を貫く磁束を大きくすることができるので、位置検出の感度を向上することができる。

【0033】

また、導電素子22および導電素子22用の位置検出用配線62も、同様に、マイクロコントローラ20から導電素子22上の点P(第1の点に相当する)から導電素子22の点Q(第2の点に相当する)への電流が発生するよう電流を供給するための配線を有し、さらに、点R(第3の点に相当する)と点S(第4の点に相当する)との間の電位差を検出するための配線とを備えている。具体的には、上記の位置検出用配線61の説明において、導電素子21を導電素子22に読み替え、チップ抵抗31をチップ抵抗32に読み替え、スイッチ41a、41b、41c、41dをそれぞれスイッチ42a、42b、43c、44dに読み替え、DA端子20aをDA端子20bに読み替え、位置検出用配線61を位置検出用配線62に読み替えれば、位置検出用配線62の説明として成立する。

【0034】

また、導電素子23および導電素子23用の位置検出用配線63も、同様に、マイクロコントローラ20から導電素子23上の点P(第1の点に相当する)から点Q(第2の点に相当する)への電流が発生するよう電流を供給するための配線を有し、さらに、点R(第3の点に相当する)と点S(第4の点に相当する)との間の電位差を検出するための配線とを備えている。具体的には、上記の位置検出用配線61の説明において、導電素子21を導電素子23に読み替え、チップ抵抗31をチップ抵抗33に読み替え、スイッチ41a、41b、41c、41dをそれぞれスイッチ43a、43b、43c、43dに読み替え、DA端子20aをDA端子20cに読み替え、位置検出用配線61を位置検出用配線63に読み替えれば、位置検出用配線63の説明として成立する。

【0035】

また、導電素子24および導電素子24用の位置検出用配線64も、同様に、マイクロコントローラ20から導電素子24上の点P(第1の点に相当する)から点Q(第2の点に相当する)への電流が発生するよう電流を供給するための配線を有し、さらに、点R(第3の点に相当する)と点S(第4の点に相当する)との間の電位差を検出するための配線とを備えている。具体的には、上記の位置検出用配線61の説明において、導電素子21を導電素子24に読み替え、チップ抵抗31をチップ抵抗34に読み替え、スイッチ41a、41b、41c、41dをそれぞれスイッチ44a、44b、44c、44dに読み替え、DA端子20aをDA端子20dに読み替え、位置検出用配線61を位置検出用配線64に読み替えれば、位置検出用配線64の説明として成立する。

【0036】

また、導電素子25および導電素子25用の位置検出用配線65も、同様に、マイクロコントローラ20から導電素子25上の点P(第1の点に相当する)から点Q(第2の点に相当する)への電流が発生するよう電流を供給するための配線を有し、さらに、点R(第3の点に相当する)と点S(第4の点に相当する)との間の電位差を検出するための配線とを備えている。具体的には、上記の位置検出用配線61の説明において、導電素子21を導電素子25に読み替え、チップ抵抗31をチップ抵抗35に読み替え、スイッチ41a、41b、41c、41dをそれぞれスイッチ45a、45b、45c、45dに読み替え、DA端子20aをDA端子20eに読み替え、位置検出用配線61を位置検出用配線65に読み替えれば、位置検出用配線65の説明として成立する。

【0037】

なお、スイッチ41a〜41d、42a〜42d、43a〜43d、44a〜44d、45a〜45dは、回路基板14上の図示しないパターン配線より、それぞれマイクロコントローラ20の各ポートに接続されている。それにより、マイクロコントローラ20は、スイッチ41a〜41d、42a〜42d、43a〜43d、44a〜44d、45a〜45dのオン(接続)およびオフ(切断)を独立に制御することができる。

【0038】

また、回路基板14の破線51(図2参照)で囲まれた範囲には、上述の位置検出用配線61〜65以外の他の配線および回路部品も配置されている。他の配線および回路部品としては、例えば、車内LAN用のインターフェース回路、車両内の各電子部品へ電力供給するための電源回路としては、例えば、、キーレスエントリまたはスマートエントリのための車載ECU、ボデーECU、車室内のドライバを撮影するためのカメラ用の各種回路、加速度センサ、ヨーレートセンサ等ががある。このように、他の配線および回路部品が実装されている回路基板14に、位置検出用配線61〜65および導電素子21〜25を配置することで、既存の回路基板14を有効に利用して位置検出を行うことができる。

【0039】

次に、上記のような構成の位置検出装置1による位置検出の原理について説明する。ユーザ操作部12を操作して、操作部12と共に磁石13が移動し、図7に示すように、磁石13が導電素子25の直上に位置したとする。このとき、図8の側面図に示すように、導電素子25を貫く磁束13a、13bは、他の導電素子21〜24よりも強くなる。したがって、図9に示すように、導電素子25を磁束70が貫いている状態で、点Pから点Qに流れる電流を発生させると、ホール効果により、点Rと点Sの間に電位差が発生する。したがって、導電素子21〜25の電位差を検出することで、回路基板14に対する磁石13の相対位置を検出することができる。

【0040】

次に、位置検出装置1の具体的な作動について説明する。まず、位置検出装置1の設置時における第1の調整用作動について、図10のフローチャートを参照して説明する。この図10のフローチャートに示す手順は、磁石13による磁界が存在しない状況で各導電素子21〜25に発生する電位差を検出するための手順である。

【0041】

まず、ステップ110で、位置検出装置1の取り付け作業者が、位置検出装置1を所定の位置(例えば、車両内のダッシュボード等)に取り付ける。ただしこの際、磁石13は位置検出装置1から外した状態とする。

【0042】

続いてステップ120で、作業者が、位置検出装置1の電源を投入(オン)する。するとマイクロコントローラ20は、初めて起動したことに基づいて、導電素子21〜25のそれぞれについて、点Rと点Sの間の電位差を計測する。

【0043】

具体的には、まずスイッチ41c、41dをオンにすると共に他のスイッチ42c、42d、43c、43d、44c、44d、45c、45dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子21の点RS間の電位差とする。次に、スイッチ42c、42dをオンにすると共に他のスイッチ41c、41d、43c、43d、44c、44d、45c、45dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子22の点RS間の電位差とする。次に、スイッチ43c、43dをオンにすると共に他のスイッチ41c、41d、42c、42d、44c、44d、45c、45dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子23の点RS間の電位差とする。次に、スイッチ44c、44dをオンにすると共に他のスイッチ41c、41d、42c、42d、43c、43d、45c、45dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子24の点RS間の電位差とする。最後に、スイッチ45c、45dをオンにすると共に他のスイッチ41c、41d、42c、42d、43c、43d、44c、44dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子25の点RS間の電位差とする。

【0044】

続いてステップ140では、マイクロコントローラ20が、ステップ130で検出した各導電素子21〜25の点RS間の電圧を、ベース電位差として、記憶媒体(例えば、回路基板14に実装されたフラッシュメモリ)に記録する。このようにして記録された電位差は、後述するように、磁石13の位置検出時に、各導電素子21〜25の電位差を補正するために用いられる。

【0045】

次に、位置検出装置1の設置時における第2の調整用作動について、図11のフローチャートを図11のフローチャートを参照して説明する。この図11のフローチャートに示す手順は、各導電素子21〜25に流れる電流を、導電素子21〜25間で均一にするための手順である。各導電素子21〜25に流れる電流が、導電素子21〜25間で均一になれば、各導電素子21〜25のホール効果の影響も均一となる。

【0046】

まず、マイクロコントローラ20は、起動する度に、図11の処理を開始し、5個の導電素子21〜25のそれぞれを対象として、対象の導電素子についてステップ210、220の処理を行う。例えば対象の導電素子を導電素子21とする場合は、ステップ210で、導電素子21および導電素子21に接続するチップ抵抗31に所定の電圧を印加し、続いて、ステップ220で、導電素子21の点Pから点Qに流れる電流を計測する。

【0047】

より具体的には、ステップ210では、DA端子20aから所定の電圧を印加することで、DA端子20aとGND端子20hとの間に所定の電位差を発生させる。

【0048】

そして、ステップ210では、スイッチ41a、41bをオンにし、他の図6中のスイッチすべてをオフとすることで、チップ抵抗31の両端の電位差V0(AD端子20f、20g間の電位差)を検出する。この検出した電位差V0を、あらかじめ位置検出装置1の記憶媒体(例えばROM、フラッシュメモリ)に記録されたチップ抵抗31の抵抗値で除算することで、チップ抵抗31に流れる電流値を算出する。そして、この検出した電流値を、導電素子21の点Pから点Qに流れる電流として特定する。なお、チップ抵抗31とAD端子20f、20gとの間には電流は流れない。

【0049】

他の導電素子22〜25を対象の導電素子としてステップ210、220を実行する場合も同様である。導電素子22を対象とする場合は、上述の説明において、導電素子21を導電素子22に読み替え、DA端子20aをDA端子20bに読み替え、チップ抵抗31をチップ抵抗32に読み替え、スイッチ41a、41bをスイッチ42a、42bに読み替えればよい。また、導電素子23を対象とする場合は、上述の説明において、導電素子21を導電素子23に読み替え、DA端子20aをDA端子20cに読み替え、チップ抵抗31をチップ抵抗33に読み替え、スイッチ41a、41bをスイッチ43a、43bに読み替えればよい。また、導電素子24を対象とする場合は、上述の説明において、導電素子21を導電素子24に読み替え、DA端子20aをDA端子20dに読み替え、チップ抵抗31をチップ抵抗34に読み替え、スイッチ41a、41bをスイッチ44a、44bに読み替えればよい。また、導電素子24を対象とする場合は、上述の説明において、導電素子21を導電素子25に読み替え、DA端子20aをDA端子20eに読み替え、チップ抵抗31をチップ抵抗35に読み替え、スイッチ41a、41bをスイッチ45a、45bに読み替えればよい。

【0050】

続いてステップ230では、マイクロコントローラ20は、上述のように特定した各導電素子21〜25に流れる電流に基づいて、各電素子21〜25に流れる電流を電素子21〜25間で均一になるよう、各電素子21〜25に各DA端子20a〜20eから印加する電圧を補正する。例えば、ステップ210で各DA端子20a〜20eから印加した電圧がV0と等しくなっており、導電素子21〜25について特定した電流値の平均値がI0で、導電素子21、22、23、24、25について特定した電流値がそれぞれI1、I2、I3、I4、I5であったとする。この場合、導電素子21〜25に等しく電流値I0の電流が流れるよう、DA端子20a、20b、20c、20d、20eから印加する印加電圧として、それぞれ、I0/I1×V0、I0/I2×V0、I0/I3×V0、I0/I4×V0、I0/I4×V0の値を、それぞれDA端子20a、20b、20c、20d、20e用の調整済印加電圧として、記憶媒体(例えばマイクロコントローラ20のRAM)に記録する。

【0051】

次に、回路基板14に固定された導電素子21〜25に対する磁石13の相対位置検出のための処理について説明する。マイクロコントローラ20は、起動し、図11(および初回起動時には図10)の処理を行った後に、図12の処理を実行する。

【0052】

この図12の処理では、まずステップ305で、点RS間の電位差を検出する対象の導電素子を導電素子21に切り替えるため、スイッチ41c、41dをオンにし、スイッチ42c、42d、43c、43d、44c、44d、45c、45dをオフにする。また、ステップ305では、スイッチ41a、41b、42a、42b、43a、43b、44a、44b、45a、45bもオフにする。

【0053】

続いてステップ310では、導電素子21用の調整済み印加電圧を読み出し、読み出した調整済み印加電圧をDA端子20aから印加する。このとき、導電素子21上のP点からQ点には上述の電流I0が流れるので、磁石13が導電素子21を貫く磁束に応じたRS点間の電位差を、AD端子20f、20g間の電位差として検出できる。なおこのとき、導電素子21とAD端子20f、20gとの間には電流は流れない。

【0054】

例えば、磁石13が導電素子21の真上にあれば、ホール効果によって、導電素子21上のRS点間に最大の電位差が発生するが、磁石13が導電素子21から遠く離れた位置(例えば、導電素子25の真上)にあれば、導電素子21上のRS点間に発生する電位差が非常に小さくなるか、または電位差が発生しない。

【0055】

ステップ310では、このように検出した導電素子21上のRS点間の電位差から、図10の処理で記憶した導電素子21のベース電位差を減算し、その減算結果の値を、導電素子21上のRS点間の調整後電位差としてRAMに記録する。

【0056】

続いてステップ315では、ステップ310以降、導電素子21〜25のすべての導電素子について、RS点間の電位差検出を行ったか否かを判定する。本例では、まだ導電素子21しか電位差検出を行っていないので、判定結果は否定的なものになり、処理をステップ320に進める。

【0057】

ステップ320では、点RS間の電位差を検出する対象の導電素子を次の導電素子22に切り替えるため、スイッチ42c、42dをオンにし、スイッチ41c、41d、43c、43d、44c、44d、45c、45dをオフにする。そして、処理をステップ310に戻す。

【0058】

ステップ310では、前回のステップ310の処理に対して、対象を導電素子21から導電素子22に代えた処理を行う。すなわち、導電素子22用の調整済み印加電圧をDA端子20aから印加することで、導電素子22上のP点からQ点に上述の電流I0を発生させ、導電素子22上のRS点間の電位差を、AD端子20f、20g間の電位差として検出する。そして、検出した導電素子22上のRS点間の電位差から、図10の処理で記憶した導電素子22のベース電位差を減算し、その減算結果の値を、導電素子22上のRS点間の調整後電位差としてRAMに記録する。

【0059】

続くステップ315では、本例では、まだ導電素子21、22しか電位差検出を行っていないので、まだRS点間の電位差検出を行っていない導電素子があると判定し、処理をステップ320に進める。

【0060】

ステップ320では、点RS間の電位差を検出する対象の導電素子を次の導電素子23に切り替えるため、スイッチ43c、43dをオンにし、スイッチ41c、41d、42c、42d、44c、44d、45c、45dをオフにする。そして、処理をステップ310に戻す。

【0061】

そして、ステップ310で、前回のステップ310の処理に対して、対象を導電素子22から導電素子23に代えた処理を行うことで、導電素子23上のRS点間の調整後電位差としてRAMに記録し、ステップ315で、まだRS点間の電位差検出を行っていない導電素子があると判定し処理をステップ320に進め、点RS間の電位差を検出する対象の導電素子を次の導電素子24に切り替えるため、スイッチ44c、44dをオンにし、スイッチ41c、41d、42c、42d、43c、43d、45c、45dをオフにする。そして、処理をステップ310に戻す。

【0062】

そして、ステップ310で、前回のステップ310の処理に対して、対象を導電素子23から導電素子24に代えた処理を行うことで、導電素子24上のRS点間の調整後電位差としてRAMに記録し、ステップ315で、まだRS点間の電位差検出を行っていない導電素子があると判定し処理をステップ320に進め、点RS間の電位差を検出する対象の導電素子を次の導電素子25に切り替えるため、スイッチ45c、45dをオンにし、スイッチ41c、41d、42c、42d、43c、43d、44c、44dをオフにする。そして、処理をステップ310に戻す。

【0063】

そして、ステップ310で、前回のステップ310の処理に対して、対象を導電素子24から導電素子25に代えた処理を行うことで、導電素子25上のRS点間の調整後電位差としてRAMに記録する。

【0064】

そしてステップ315では、ステップ305の実行以降、既に導電素子21〜25すべてについてRS点間の電位差検出を行ったと判定し、処理をステップ325に進める。

【0065】

このように、導電素子21〜25のRS点間の調整後電位差を検出するために、1個ずつ順番に導電素子21〜25のPQ点間に電流を発生させることで、一度にすべての導電素子21〜25に電流を発生させる場合に比べ、電力消費量が低減されると共に、マイクロコントローラ20のAD端子の数も2個使用すれば済むという利点がある。

【0066】

なお、ステップ310、315、320の繰り返しにおいて、310、315、320の一巡に要する時間は、例えば20ミリ秒から200ミリ秒までの範囲内のいずれかであってもよい。したがって、すべての導電素子21〜25の調整後電位差を取得するのに、100ミリ秒から1秒程度かかってもよい。そして、1回のステップ310の処理において、DA端子20aから電圧を印加する時間も、10ミリ秒から100ミリ秒までの範囲内のいずれかであってもよい。

【0067】

ステップ320では、ステップ310の繰り返しによって取得した導電素子21〜25の調整後電位差に基づいて、導電素子21〜25に対する磁石13の位置を特定する。特定の方法および特定する位置の分解能は、種々のものを採用することができる。

【0068】

例えば、導電素子21〜25の調整後電位差の絶対値のうち、特定の導電素子の調整後電位差の絶対値が最も大きい場合は、当該特定の導電素子の直上の位置に磁石13があると判定してもよい。より具体的には、例えば導電素子25の調整後電位差の絶対値が一番大きい場合、磁石13の位置は回路基板14の中央よりも左であると特定し、また例えば導電素子21の調整後電位差の絶対値が一番大きい場合、磁石13の位置は回路基板14の中央あると特定してもよい。

【0069】

また例えば、導電素子21〜25の調整後電位差の絶対値W1〜W5で重み付けした、導電素子21〜25の位置X1〜X5(ただしX1〜X5は2次元ベクトル)の重み付き平均M=W1×X1+W2×X2+W3×X3+W4×X4+W5×X5を、磁石13の位置としてもよい。

【0070】

続いてステップ330では、ステップ325で特定した磁石13の位置を示す情報を、位置検出装置1の外部(例えば、位置検出装置1に接続された車載ナビゲーション装置)に出力する。ステップ330の後、処理はステップ305に戻る。

【0071】

このようなマイクロコントローラ20の処理により、各導電素子21〜25のそれぞれに対して、対象の導電素子の点Pから点Qまで電流が流れるよう、対象の導電素子に電流を供給すると共に、対象の導電素子の点Rと点Sとの間の電位差を検出し、導電素子21〜25のそれぞれについて検出した調整後電位差に基づいて、導電素子21〜25に対する磁石13の相対位置を特定して出力する。

【0072】

このように、電磁変換素子として、5個の導電素子21〜25が、制御回路20と共に回路基板14上にパターン配線され(すなわち、プリントされ)、この導電素子21〜25に発生する電位差に基づいて、導電素子21〜25に対する磁石13の相対位置を検出することができる。このように、電磁変換素子をパターン配線することで、ICとして電磁変換素子を構成するよりも、部品点数が減り、かつ、部品コストが低減される。

【0073】

また、導電素子21〜25のそれぞれは、位置検出用配線61〜65よりも太くパターン配線されているので、導電素子25を貫く磁束を大きくすることができるので、位置検出の感度を向上することができる。

【0074】

なお、位置検出用配線61の配線に用いる材料と、導電素子21〜25の配線に用いる材料は、同じであっても違っていても良いが、同じにした方が、回路基板14にパターン配線を行うときの手間および位置検出装置1の製造コストが低減されるという利点がある。

【0075】

(他の実施形態)

以上、本発明の実施形態について説明したが、本発明の範囲は、上記実施形態のみに限定されるものではなく、本発明の各発明特定事項の機能を実現し得る種々の形態を包含するものである。例えば、以下のような形態も許容される。

【0076】

(1)上記実施形態では、回路基板14は、上面と下面にのみパターン配線される基板であったが、回路基板14は、3層以上にパターン配線可能な多層基板であってもよい。その場合、回路基板14において、導電素子21〜25と重なるように、他の導電素子を各層にパターン配線するようになっていてもよい。例えば、図13に示すように、導電素子25に重なるように、複数の導電素子26〜28を配置してもよい。この場合、複数の導電素子26〜28も、それぞれ導電素子25と同様に、点P、Q、R、Sを有し、位置検出用配線62と同様の位置検出用配線でマイクロコントローラ20と接続されていてもよい。

【0077】

このようにすることで、この導電素子25〜28の各PQ点間に電流を発生させ、導電素子25〜28の各RQ点間の電位差を検出し、それを、磁石13の位置(回路基板14に平行な面内の位置)の検出に用いることで、導電素子25〜28付近における磁石13の位置の特定精度が向上する。

【0078】

(2)また、図14に示すように、回路基板14の同じ層(例えば上面)において、導電素子の数を増やし、9個の導電素子21〜29を配置し、新たに配置した導電素子26〜29についても、他の導電素子21〜26と同様に、マイクロコントローラ20がPQ点間に電流を流し、RQ点間の電位差を検出することで、より高い精度で磁石13の位置検出を行うことができる。

【0079】

(3)また、磁石13が左右方向にしか移動しないような位置検出装置1の場合、図15に示すように、導電素子21、22、24を廃し、導電素子としては回路基板14に導電素子23と導電素子25のみをパターン配線するようになっていてもよい。この場合でも、磁石13の左右方向(図15中の左右方向)の位置を検出することは可能である。このような動きをする磁石13の応用例としては、オン時に左に移動し、オフ時に右に移動するオフスイッチがある。

【0080】

(4)また、磁石13が回路基板14上を円環状にしか移動しない位置検出装置1の場合、図16に示すように、導電素子21〜28を円環状の並びでパターン配線するようになっていてもよい。この場合、新たに配置した導電素子26〜28についても、他の導電素子21〜26と同様に、マイクロコントローラ20がPQ点間に電流を流し、RQ点間の電位差を検出する。

【0081】

(5)また、磁石13が上下方向(図3の上下方向)にしか移動しないような位置検出装置1の場合、図17に示すように、導電素子22〜25を廃し、導電素子としては回路基板14に導電素子21のみをパターン配線するようになっていてもよい。この場合でも、磁石13の上下方向(図17の紙面に垂直な方向)の位置を検出することは可能である。このような動きをする磁石13の応用例としては、オン時に回路基板14(および導電素子21)に近づく方向に移動し、オフ時に回路基板14(および導電素子21)から離れる方向に移動するオフスイッチがある。

【0082】

(6)また、上記実施形態では、導電素子21〜25に流す電流を均一化させるために、チップ抵抗31〜35を配置している。導電素子21〜25に流す電流を均一化させることは、磁石13の位置検出の精度を高めることに繋がるが、磁石13の位置検出の精度を高める必要がない場合は、そもそもチップ抵抗31〜35もスイッチ41a〜45a、41b〜45bも配置する必要はなく、プリントされた配線のみを介してDA端子20a〜20eのそれぞれを導電素子21〜25に接続させればよい。

【0083】

(7)また、上記実施形態では、磁石13は、その位置によらず、回路基板14に対して垂直になっているが、磁石13の回路基板14に対する傾きは、磁石13の位置の変化に応じて変化してもよい。例えば、磁石13が、所定の始点を中心に回転して移動するようになっていてもよい。

【0084】

(8)また、上記実施形態では、制御回路としてマイクロコントローラ20が例示されているが、制御回路としてマイクロコントローラ以外を採用してもよい。

【0085】

(9)また、上記実施形態では、1つの導電素子内において、点P、Q、R、Sがそれぞれ異なる位置にある。しかし、点P、Qのうちいずれか一方が、点R、Sのうちいずれかと共通であってもよい。ただし、第1の点Pおよび第2の点Qの両方が、第2の点Rおよび第3の点Sのうちいずれかと共通であるようになってはいけない。

【0086】

P、Q、R、Sの配置は、以下のようになっていれば、ホール効果によって発生する電位差を検出することができる。導電素子の点Pから点Qへの方向を第1の方向とし、当該導電素子上の点Rから見て第1の方向と交差(上記実施形態では直交)する方向を第2の方向とすると、点Rと、点Rから見て当該第2の方向にある点を点Sとすればよい。

【0087】

(10)また、上記実施形態では、マイクロコンピュータ20は、検出した導電素子のRS点間の電位差に基づいて、導電素子に対する磁石13の相対位置に応じた作動を行ううようになっている。そして、相対位置に応じた作動としては、相対位置の特定および出力を行っている。しかし、相対位置に応じた作動は、相対位置の特定および出力に限らない。

【符号の説明】

【0088】

1 位置検出装置

11 筐体

11a スリット

12 操作部

13 磁石

14 回路基板

20 マイクロコントローラ

20a〜20e DA端子

20f、20g AD端子

20h GND端子

21〜29 導電素子

52〜58 回路部品

31〜35 チップ抵抗

61〜65 位置検出用配線

【技術分野】

【0001】

本発明は、ホール効果を利用した位置検出装置に関するものである。

【背景技術】

【0002】

従来、ホール効果を利用して、電磁変換素子に対する磁石の相対位置を検出する位置検出装置が知られている(例えば、特許文献1参照)。

【0003】

このような位置検出装置においては、磁石と電磁変換素子の相対位置に応じて電磁変換素子における電位差が変化することを利用し、上記電位差に応じた信号を電磁変換素子が出力し、制御部が、電磁変換素子の上記出力に応じて、磁石と電磁変換素子の相対位置を特定するようになっている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−209651号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、従来の位置検出装置は、電磁変換素子として、専用のICを採用しているので、制御部を実装する回路基板に加え、電磁変換素子用のICを用意しなければならず、部品点数および部品コストが増大する。

【0006】

本発明は上記点に鑑み、ホール効果を利用した位置検出装置において、従来よりも部品点数および部品コストを低減することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するための請求項1に記載の発明は、回路基板(14)と、発生する磁界が前記回路基板(14)を貫くような配置で前記回路基板(14)に対して相対的に移動する磁石(13)と、前記回路基板(14)上にパターン配線された1個以上の導電素子(21〜29)と、前記回路基板(14)上に実装された制御回路(20)と、前記制御回路(20)から前記1個以上の導電素子(21〜29)のそれぞれに対して、対象の導電素子上の第1の点(P)から対象の導電素子上の第2の点(Q)への電流が発生するよう電流を供給するための配線であると共に、前記第1の点(P)から前記第2の点(Q)への方向を第1の方向とし、対象の導電素子上の第3の点(R)から見て前記第1の方向と交差する方向を第2の方向とすると、前記第3の点(R)と、対象の導電素子において前記第3の点(R)から見て前記第2の方向にある第4の点(S)と、の間の電位差を検出するための位置検出用配線(61〜65)と、を備え、前記制御回路(20)は、前記1個以上の導電素子(21〜29)のそれぞれに対して、対象の導電素子の前記第1の点(P)から前記第2の点(Q)まで電流が流れるよう、対象の導電素子に電流を供給すると共に、対象の導電素子(21〜29)の前記第3の点(R)と第4の点(S)との間の電位差を検出し、前記1個以上の導電素子(21〜29)のそれぞれについて検出した前記電位差に基づいて、前記1個以上の導電素子(21〜29)に対する前記磁石(13)の相対位置に応じた作動を行う位置検出装置である。

【0008】

このように、電磁変換素子として、1個以上の導電素子が、制御回路(20)と共に回路基板(14)上にパターン配線され、この導電素子に発生する電位差に基づいて、1個以上の導電素子(21〜29)に対する磁石(13)の相対位置を検出することができる。このように、電磁変換素子をパターン配線することで、ICとして電磁変換素子を構成するよりも、部品点数が減り、かつ、部品コストが低減される。

【0009】

また、請求項2に記載の発明は、請求項1に記載の位置検出装置において、前記回路基板(14)には、前記位置検出用配線(61〜65)以外の他の配線および回路部品(51)も配置されていることを特徴とする。

【0010】

このように、他の配線および回路部品(51)が実装されている回路基板(14)に、位置検出用配線(61〜65)および導電素子を配置することで、既存の回路基板(14)を有効に利用して位置検出を行うことができる。

【0011】

また、請求項3に記載の発明は、請求項1または2に記載の位置検出装置において、前記回路基板(14)に設けられた回路部品のうち、所定の高さよりも低い回路部品は、前記回路基板(14)の前記磁石(13)側の面に実装され、所定の高さ以上の回路部品は、そのすべてが、前記回路基板(14)の前記磁石(13)側とは反対側の面に実装されていることを特徴とする。

【0012】

このように、所定の高さ以上の回路部品は、そのすべてが、回路基板(14)の磁石(13)側とは反対側の面に実装されていることで、磁石(13)を回路基板(14)に近づけ易くなる。

【0013】

また、請求項4に記載の発明は、請求項1ないし3のいずれか1つに記載の位置検出装置前記1個以上の導電素子(21〜29)は、複数個の導電素子(21〜29)であることを特徴とする。

【0014】

また、請求項5に記載の発明は、請求項1ないし4のいずれか1つに記載の位置検出装置において、前記1個以上の導電素子(21〜29)のそれぞれは、前記位置検出用配線(61〜65)よりも太くパターン配線されていることを特徴とする。このようにすることで、導電素子を貫く磁束を大きくすることができるので、位置検出の感度を向上することができる。

【0015】

なお、上記および特許請求の範囲における括弧内の符号は、特許請求の範囲に記載された用語と後述の実施形態に記載される当該用語を例示する具体物等との対応関係を示すものである。

【図面の簡単な説明】

【0016】

【図1】本発明の実施形態に係る位置検出装置1の斜視図である。

【図2】位置検出装置1の平面図である。

【図3】図2のA−A断面図である。

【図4】回路基板14の磁石側の面を示す図である。

【図5】回路基板14の

【図6】導電素子21、位置検出用配線61〜65、マイクロコントローラ20の電気的接続関係を示す図である。

【図7】磁石13の位置の一例を示す図である。

【図8】磁石13の磁束13a、13bが導電素子25を貫く状態を示す図である。

【図9】導電素子25に電位差が発生する状態を示す図である。

【図10】各導電素子のベース電圧を特定する手順のフローチャートである。

【図11】各導電素子の電流を均一にするための処理のフローチャートである。

【図12】磁石の位置検出のためのマイクロコントローラの処理を示すフローチャートである。

【図13】回路基板14が多層基板になっている場合の導電素子25から28の配置を示す図である。

【図14】導電素子21〜29の配置例を示す図である。

【図15】導電素子23、35の配置例を示す図である。

【図16】導電素子21〜28の配置例を示す図である。

【図17】導電素子21の配置例を示す図である。

【発明を実施するための形態】

【0017】

以下、本発明の一実施形態について説明する。図1、図2に、本実施形態に係る位置検出装置1の外観を斜視図および平面図で示し、図3に、図2のA−A断面図を示す。これら図1〜3に示すように、位置検出装置1は、筐体11と、操作部12と、磁石13と、回路基板14とを備えている。

【0018】

操作部12は、ユーザの操作を直接受ける部材であり、ユーザの操作に応じて、筐体11の上面に設けられた十字型のスリット11aに沿って前後方向(図2の上下方向)および左右方向(図2の左右方向)に移動するようになっている。磁石13は、筐体11内に収容されると共に、操作部12の下端に固定され、操作部12と共に移動するようになっている。そして、この磁石13は、両極が磁石13の上端(図3の上方向を上とする)および下端に位置するように配置されている。

【0019】

プリント基板である回路基板14は、筐体11内に収容されると共に、筐体11に対して固定されている。また回路基板14は、磁石13の下側において、磁石13に対向して配置されると共に、回路基板14と磁石13の距離は、磁石13の発生する磁界が回路基板14を貫くようになっている。

【0020】

なお、筐体11は操作部12に対して移動し、磁石13は操作部12と共に移動し、回路基板14は筐体11に固定されているので、磁石13は回路基板14に対して相対的に移動する。

【0021】

次に、回路基板14について詳細に説明する。図4に、回路基板14の磁石13側の表面(以下、単に回路基板14の上面という)を示す。回路基板14の上面には、マイクロコントローラ20(制御部の一例に相当する)が実装されている。

【0022】

また、回路基板14の上面には、5つの導電素子21〜25がパターン配線されている。また、回路基板14には、導電素子21〜25以外にも、破線51で囲まれた範囲内に他の線がパターン配線されており、また、回路部品(コンデンサ、抵抗、IC等)が実装されている。

【0023】

導電素子21〜25は、回路基板14の上面の中央にプリントされた導電素子21、前端部中央にプリントされた導電素子22、右端部中央にプリントされた導電素子23、後端部中央に配置された導電素子24、左端部中央に配置された導電素子25から成り、それぞれ、導電性材料(例えばアルミニウム、銅)によってパターン配線された矩形板形状の部材である。

【0024】

これら導電素子21〜25のそれぞれとマイクロコントローラ20とは、後述するように、各導電素子21〜25の2点(第1の点および第2の点に相当する)間に電流を流すと共に各導電素子の他の2点(第3の点および第4の点に相当する)における電位差を検出するための位置検出用配線によって接続されている。これら位置検出用配線も、回路基板14の破線51で囲まれた範囲内にパターン配線されている。

【0025】

なお、導電素子21〜25の回路基板14に対するサイズ比率は、図4のように、1:数十程度でもよいし、1:1000程度でもよい。例えば、回路基板14が1辺10cmの正方形形状を有している場合、導電素子21〜25の全長が0.1mm程度であってもよい。

【0026】

ここで、回路基板14に実装される回路部品の高さについて説明する。本実施形態では、磁石13の磁束が回路基板14を貫くようになっている必要があるので、磁石13をできる限り回路基板14に近づけたい。そのために、図5の側面図に示すように、回路基板14に設けられた回路部品のうち、所定の高さよりも低い回路部品は、回路基板14の上面に実装され、所定の高さ以上の回路部品は、そのすべてが、回路基板14の磁石13側とは反対側の面(以下、下面という)に実装されている。ここで、所定の高さは、磁石13から回路基板14の上面までの最短距離hよりも小さい値(例えばhの0.8倍)とする。なお、この所定の高さよりも低い回路部品は、回路基板14の上面のみならず下面に実装されていてもよい。このように、所定の高さ以上の回路部品は、そのすべてが、回路基板14の下面に実装されていることで、磁石13を回路基板14に近づけ易くなる。

【0027】

次に、図6を参照して、導電素子21〜25のそれぞれをマイクロコントローラ20に接続する位置検出用配線61〜65について説明する。

【0028】

まず、導電素子21および導電素子21用の位置検出用配線61について説明する。位置検出用配線61は、チップ抵抗31、スイッチ41a〜41d、およびパターン配線を含んでいる。

【0029】

この位置検出用配線61により、導電素子21の矩形の頂点の1つである点P(第1の点に相当する)は、チップ抵抗31の一端に接続され、チップ抵抗31の他端が、マイクロコントローラ20のDA端子20aに接続される。また、導電素子21の矩形の別の頂点の1つである点Q(第2の点に相当する)は、マイクロコントローラ20のGND端子20hに接続される。これらの配線により、DA端子20aから電圧を印加することで、点Pから点Qへの電流が発生する。

【0030】

また、導電素子21の矩形の別の頂点の1つである点R(第3の点に相当する)は、スイッチ41dを介してマイクロコントローラ20のAD端子20gに接続される。また、導電素子21の矩形の別の頂点の1つである点S(第4の点に相当する)は、スイッチ41cを介してマイクロコントローラ20の他のAD端子20fに接続される。これらの配線により、点Rと点Sの間の電位差をマイクロコントローラ20が検出することができる。

【0031】

また、導電素子21とチップ抵抗31とを繋ぐ配線から、スイッチ41bを介してマイクロコントローラ20のAD端子20gに接続する配線が伸びている。また、チップ抵抗31とマイクロコントローラ20のDA端子20aとを繋ぐ配線から、スイッチ41aを介してマイクロコントローラ20のAD端子20fに接続する配線が伸びている。これら、チップ抵抗31の両端の電位差をマイクロコントローラ20が検出することができる。

【0032】

なお、位置検出用配線61のうち、導電素子21の点P、Q、R、Sに接続している配線よりも、導電素子21の方が太くパターン配線されている。このようにすることで、導電素子を貫く磁束を大きくすることができるので、位置検出の感度を向上することができる。

【0033】

また、導電素子22および導電素子22用の位置検出用配線62も、同様に、マイクロコントローラ20から導電素子22上の点P(第1の点に相当する)から導電素子22の点Q(第2の点に相当する)への電流が発生するよう電流を供給するための配線を有し、さらに、点R(第3の点に相当する)と点S(第4の点に相当する)との間の電位差を検出するための配線とを備えている。具体的には、上記の位置検出用配線61の説明において、導電素子21を導電素子22に読み替え、チップ抵抗31をチップ抵抗32に読み替え、スイッチ41a、41b、41c、41dをそれぞれスイッチ42a、42b、43c、44dに読み替え、DA端子20aをDA端子20bに読み替え、位置検出用配線61を位置検出用配線62に読み替えれば、位置検出用配線62の説明として成立する。

【0034】

また、導電素子23および導電素子23用の位置検出用配線63も、同様に、マイクロコントローラ20から導電素子23上の点P(第1の点に相当する)から点Q(第2の点に相当する)への電流が発生するよう電流を供給するための配線を有し、さらに、点R(第3の点に相当する)と点S(第4の点に相当する)との間の電位差を検出するための配線とを備えている。具体的には、上記の位置検出用配線61の説明において、導電素子21を導電素子23に読み替え、チップ抵抗31をチップ抵抗33に読み替え、スイッチ41a、41b、41c、41dをそれぞれスイッチ43a、43b、43c、43dに読み替え、DA端子20aをDA端子20cに読み替え、位置検出用配線61を位置検出用配線63に読み替えれば、位置検出用配線63の説明として成立する。

【0035】

また、導電素子24および導電素子24用の位置検出用配線64も、同様に、マイクロコントローラ20から導電素子24上の点P(第1の点に相当する)から点Q(第2の点に相当する)への電流が発生するよう電流を供給するための配線を有し、さらに、点R(第3の点に相当する)と点S(第4の点に相当する)との間の電位差を検出するための配線とを備えている。具体的には、上記の位置検出用配線61の説明において、導電素子21を導電素子24に読み替え、チップ抵抗31をチップ抵抗34に読み替え、スイッチ41a、41b、41c、41dをそれぞれスイッチ44a、44b、44c、44dに読み替え、DA端子20aをDA端子20dに読み替え、位置検出用配線61を位置検出用配線64に読み替えれば、位置検出用配線64の説明として成立する。

【0036】

また、導電素子25および導電素子25用の位置検出用配線65も、同様に、マイクロコントローラ20から導電素子25上の点P(第1の点に相当する)から点Q(第2の点に相当する)への電流が発生するよう電流を供給するための配線を有し、さらに、点R(第3の点に相当する)と点S(第4の点に相当する)との間の電位差を検出するための配線とを備えている。具体的には、上記の位置検出用配線61の説明において、導電素子21を導電素子25に読み替え、チップ抵抗31をチップ抵抗35に読み替え、スイッチ41a、41b、41c、41dをそれぞれスイッチ45a、45b、45c、45dに読み替え、DA端子20aをDA端子20eに読み替え、位置検出用配線61を位置検出用配線65に読み替えれば、位置検出用配線65の説明として成立する。

【0037】

なお、スイッチ41a〜41d、42a〜42d、43a〜43d、44a〜44d、45a〜45dは、回路基板14上の図示しないパターン配線より、それぞれマイクロコントローラ20の各ポートに接続されている。それにより、マイクロコントローラ20は、スイッチ41a〜41d、42a〜42d、43a〜43d、44a〜44d、45a〜45dのオン(接続)およびオフ(切断)を独立に制御することができる。

【0038】

また、回路基板14の破線51(図2参照)で囲まれた範囲には、上述の位置検出用配線61〜65以外の他の配線および回路部品も配置されている。他の配線および回路部品としては、例えば、車内LAN用のインターフェース回路、車両内の各電子部品へ電力供給するための電源回路としては、例えば、、キーレスエントリまたはスマートエントリのための車載ECU、ボデーECU、車室内のドライバを撮影するためのカメラ用の各種回路、加速度センサ、ヨーレートセンサ等ががある。このように、他の配線および回路部品が実装されている回路基板14に、位置検出用配線61〜65および導電素子21〜25を配置することで、既存の回路基板14を有効に利用して位置検出を行うことができる。

【0039】

次に、上記のような構成の位置検出装置1による位置検出の原理について説明する。ユーザ操作部12を操作して、操作部12と共に磁石13が移動し、図7に示すように、磁石13が導電素子25の直上に位置したとする。このとき、図8の側面図に示すように、導電素子25を貫く磁束13a、13bは、他の導電素子21〜24よりも強くなる。したがって、図9に示すように、導電素子25を磁束70が貫いている状態で、点Pから点Qに流れる電流を発生させると、ホール効果により、点Rと点Sの間に電位差が発生する。したがって、導電素子21〜25の電位差を検出することで、回路基板14に対する磁石13の相対位置を検出することができる。

【0040】

次に、位置検出装置1の具体的な作動について説明する。まず、位置検出装置1の設置時における第1の調整用作動について、図10のフローチャートを参照して説明する。この図10のフローチャートに示す手順は、磁石13による磁界が存在しない状況で各導電素子21〜25に発生する電位差を検出するための手順である。

【0041】

まず、ステップ110で、位置検出装置1の取り付け作業者が、位置検出装置1を所定の位置(例えば、車両内のダッシュボード等)に取り付ける。ただしこの際、磁石13は位置検出装置1から外した状態とする。

【0042】

続いてステップ120で、作業者が、位置検出装置1の電源を投入(オン)する。するとマイクロコントローラ20は、初めて起動したことに基づいて、導電素子21〜25のそれぞれについて、点Rと点Sの間の電位差を計測する。

【0043】

具体的には、まずスイッチ41c、41dをオンにすると共に他のスイッチ42c、42d、43c、43d、44c、44d、45c、45dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子21の点RS間の電位差とする。次に、スイッチ42c、42dをオンにすると共に他のスイッチ41c、41d、43c、43d、44c、44d、45c、45dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子22の点RS間の電位差とする。次に、スイッチ43c、43dをオンにすると共に他のスイッチ41c、41d、42c、42d、44c、44d、45c、45dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子23の点RS間の電位差とする。次に、スイッチ44c、44dをオンにすると共に他のスイッチ41c、41d、42c、42d、43c、43d、45c、45dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子24の点RS間の電位差とする。最後に、スイッチ45c、45dをオンにすると共に他のスイッチ41c、41d、42c、42d、43c、43d、44c、44dをオフとする。その上で、AD端子20f、20g間の電位差を検出し、検出した電位差を、導電素子25の点RS間の電位差とする。

【0044】

続いてステップ140では、マイクロコントローラ20が、ステップ130で検出した各導電素子21〜25の点RS間の電圧を、ベース電位差として、記憶媒体(例えば、回路基板14に実装されたフラッシュメモリ)に記録する。このようにして記録された電位差は、後述するように、磁石13の位置検出時に、各導電素子21〜25の電位差を補正するために用いられる。

【0045】

次に、位置検出装置1の設置時における第2の調整用作動について、図11のフローチャートを図11のフローチャートを参照して説明する。この図11のフローチャートに示す手順は、各導電素子21〜25に流れる電流を、導電素子21〜25間で均一にするための手順である。各導電素子21〜25に流れる電流が、導電素子21〜25間で均一になれば、各導電素子21〜25のホール効果の影響も均一となる。

【0046】

まず、マイクロコントローラ20は、起動する度に、図11の処理を開始し、5個の導電素子21〜25のそれぞれを対象として、対象の導電素子についてステップ210、220の処理を行う。例えば対象の導電素子を導電素子21とする場合は、ステップ210で、導電素子21および導電素子21に接続するチップ抵抗31に所定の電圧を印加し、続いて、ステップ220で、導電素子21の点Pから点Qに流れる電流を計測する。

【0047】

より具体的には、ステップ210では、DA端子20aから所定の電圧を印加することで、DA端子20aとGND端子20hとの間に所定の電位差を発生させる。

【0048】

そして、ステップ210では、スイッチ41a、41bをオンにし、他の図6中のスイッチすべてをオフとすることで、チップ抵抗31の両端の電位差V0(AD端子20f、20g間の電位差)を検出する。この検出した電位差V0を、あらかじめ位置検出装置1の記憶媒体(例えばROM、フラッシュメモリ)に記録されたチップ抵抗31の抵抗値で除算することで、チップ抵抗31に流れる電流値を算出する。そして、この検出した電流値を、導電素子21の点Pから点Qに流れる電流として特定する。なお、チップ抵抗31とAD端子20f、20gとの間には電流は流れない。

【0049】

他の導電素子22〜25を対象の導電素子としてステップ210、220を実行する場合も同様である。導電素子22を対象とする場合は、上述の説明において、導電素子21を導電素子22に読み替え、DA端子20aをDA端子20bに読み替え、チップ抵抗31をチップ抵抗32に読み替え、スイッチ41a、41bをスイッチ42a、42bに読み替えればよい。また、導電素子23を対象とする場合は、上述の説明において、導電素子21を導電素子23に読み替え、DA端子20aをDA端子20cに読み替え、チップ抵抗31をチップ抵抗33に読み替え、スイッチ41a、41bをスイッチ43a、43bに読み替えればよい。また、導電素子24を対象とする場合は、上述の説明において、導電素子21を導電素子24に読み替え、DA端子20aをDA端子20dに読み替え、チップ抵抗31をチップ抵抗34に読み替え、スイッチ41a、41bをスイッチ44a、44bに読み替えればよい。また、導電素子24を対象とする場合は、上述の説明において、導電素子21を導電素子25に読み替え、DA端子20aをDA端子20eに読み替え、チップ抵抗31をチップ抵抗35に読み替え、スイッチ41a、41bをスイッチ45a、45bに読み替えればよい。

【0050】

続いてステップ230では、マイクロコントローラ20は、上述のように特定した各導電素子21〜25に流れる電流に基づいて、各電素子21〜25に流れる電流を電素子21〜25間で均一になるよう、各電素子21〜25に各DA端子20a〜20eから印加する電圧を補正する。例えば、ステップ210で各DA端子20a〜20eから印加した電圧がV0と等しくなっており、導電素子21〜25について特定した電流値の平均値がI0で、導電素子21、22、23、24、25について特定した電流値がそれぞれI1、I2、I3、I4、I5であったとする。この場合、導電素子21〜25に等しく電流値I0の電流が流れるよう、DA端子20a、20b、20c、20d、20eから印加する印加電圧として、それぞれ、I0/I1×V0、I0/I2×V0、I0/I3×V0、I0/I4×V0、I0/I4×V0の値を、それぞれDA端子20a、20b、20c、20d、20e用の調整済印加電圧として、記憶媒体(例えばマイクロコントローラ20のRAM)に記録する。

【0051】

次に、回路基板14に固定された導電素子21〜25に対する磁石13の相対位置検出のための処理について説明する。マイクロコントローラ20は、起動し、図11(および初回起動時には図10)の処理を行った後に、図12の処理を実行する。

【0052】

この図12の処理では、まずステップ305で、点RS間の電位差を検出する対象の導電素子を導電素子21に切り替えるため、スイッチ41c、41dをオンにし、スイッチ42c、42d、43c、43d、44c、44d、45c、45dをオフにする。また、ステップ305では、スイッチ41a、41b、42a、42b、43a、43b、44a、44b、45a、45bもオフにする。

【0053】

続いてステップ310では、導電素子21用の調整済み印加電圧を読み出し、読み出した調整済み印加電圧をDA端子20aから印加する。このとき、導電素子21上のP点からQ点には上述の電流I0が流れるので、磁石13が導電素子21を貫く磁束に応じたRS点間の電位差を、AD端子20f、20g間の電位差として検出できる。なおこのとき、導電素子21とAD端子20f、20gとの間には電流は流れない。

【0054】

例えば、磁石13が導電素子21の真上にあれば、ホール効果によって、導電素子21上のRS点間に最大の電位差が発生するが、磁石13が導電素子21から遠く離れた位置(例えば、導電素子25の真上)にあれば、導電素子21上のRS点間に発生する電位差が非常に小さくなるか、または電位差が発生しない。

【0055】

ステップ310では、このように検出した導電素子21上のRS点間の電位差から、図10の処理で記憶した導電素子21のベース電位差を減算し、その減算結果の値を、導電素子21上のRS点間の調整後電位差としてRAMに記録する。

【0056】

続いてステップ315では、ステップ310以降、導電素子21〜25のすべての導電素子について、RS点間の電位差検出を行ったか否かを判定する。本例では、まだ導電素子21しか電位差検出を行っていないので、判定結果は否定的なものになり、処理をステップ320に進める。

【0057】

ステップ320では、点RS間の電位差を検出する対象の導電素子を次の導電素子22に切り替えるため、スイッチ42c、42dをオンにし、スイッチ41c、41d、43c、43d、44c、44d、45c、45dをオフにする。そして、処理をステップ310に戻す。

【0058】

ステップ310では、前回のステップ310の処理に対して、対象を導電素子21から導電素子22に代えた処理を行う。すなわち、導電素子22用の調整済み印加電圧をDA端子20aから印加することで、導電素子22上のP点からQ点に上述の電流I0を発生させ、導電素子22上のRS点間の電位差を、AD端子20f、20g間の電位差として検出する。そして、検出した導電素子22上のRS点間の電位差から、図10の処理で記憶した導電素子22のベース電位差を減算し、その減算結果の値を、導電素子22上のRS点間の調整後電位差としてRAMに記録する。

【0059】

続くステップ315では、本例では、まだ導電素子21、22しか電位差検出を行っていないので、まだRS点間の電位差検出を行っていない導電素子があると判定し、処理をステップ320に進める。

【0060】

ステップ320では、点RS間の電位差を検出する対象の導電素子を次の導電素子23に切り替えるため、スイッチ43c、43dをオンにし、スイッチ41c、41d、42c、42d、44c、44d、45c、45dをオフにする。そして、処理をステップ310に戻す。

【0061】

そして、ステップ310で、前回のステップ310の処理に対して、対象を導電素子22から導電素子23に代えた処理を行うことで、導電素子23上のRS点間の調整後電位差としてRAMに記録し、ステップ315で、まだRS点間の電位差検出を行っていない導電素子があると判定し処理をステップ320に進め、点RS間の電位差を検出する対象の導電素子を次の導電素子24に切り替えるため、スイッチ44c、44dをオンにし、スイッチ41c、41d、42c、42d、43c、43d、45c、45dをオフにする。そして、処理をステップ310に戻す。

【0062】

そして、ステップ310で、前回のステップ310の処理に対して、対象を導電素子23から導電素子24に代えた処理を行うことで、導電素子24上のRS点間の調整後電位差としてRAMに記録し、ステップ315で、まだRS点間の電位差検出を行っていない導電素子があると判定し処理をステップ320に進め、点RS間の電位差を検出する対象の導電素子を次の導電素子25に切り替えるため、スイッチ45c、45dをオンにし、スイッチ41c、41d、42c、42d、43c、43d、44c、44dをオフにする。そして、処理をステップ310に戻す。

【0063】

そして、ステップ310で、前回のステップ310の処理に対して、対象を導電素子24から導電素子25に代えた処理を行うことで、導電素子25上のRS点間の調整後電位差としてRAMに記録する。

【0064】

そしてステップ315では、ステップ305の実行以降、既に導電素子21〜25すべてについてRS点間の電位差検出を行ったと判定し、処理をステップ325に進める。

【0065】

このように、導電素子21〜25のRS点間の調整後電位差を検出するために、1個ずつ順番に導電素子21〜25のPQ点間に電流を発生させることで、一度にすべての導電素子21〜25に電流を発生させる場合に比べ、電力消費量が低減されると共に、マイクロコントローラ20のAD端子の数も2個使用すれば済むという利点がある。

【0066】

なお、ステップ310、315、320の繰り返しにおいて、310、315、320の一巡に要する時間は、例えば20ミリ秒から200ミリ秒までの範囲内のいずれかであってもよい。したがって、すべての導電素子21〜25の調整後電位差を取得するのに、100ミリ秒から1秒程度かかってもよい。そして、1回のステップ310の処理において、DA端子20aから電圧を印加する時間も、10ミリ秒から100ミリ秒までの範囲内のいずれかであってもよい。

【0067】

ステップ320では、ステップ310の繰り返しによって取得した導電素子21〜25の調整後電位差に基づいて、導電素子21〜25に対する磁石13の位置を特定する。特定の方法および特定する位置の分解能は、種々のものを採用することができる。

【0068】

例えば、導電素子21〜25の調整後電位差の絶対値のうち、特定の導電素子の調整後電位差の絶対値が最も大きい場合は、当該特定の導電素子の直上の位置に磁石13があると判定してもよい。より具体的には、例えば導電素子25の調整後電位差の絶対値が一番大きい場合、磁石13の位置は回路基板14の中央よりも左であると特定し、また例えば導電素子21の調整後電位差の絶対値が一番大きい場合、磁石13の位置は回路基板14の中央あると特定してもよい。

【0069】

また例えば、導電素子21〜25の調整後電位差の絶対値W1〜W5で重み付けした、導電素子21〜25の位置X1〜X5(ただしX1〜X5は2次元ベクトル)の重み付き平均M=W1×X1+W2×X2+W3×X3+W4×X4+W5×X5を、磁石13の位置としてもよい。

【0070】

続いてステップ330では、ステップ325で特定した磁石13の位置を示す情報を、位置検出装置1の外部(例えば、位置検出装置1に接続された車載ナビゲーション装置)に出力する。ステップ330の後、処理はステップ305に戻る。

【0071】

このようなマイクロコントローラ20の処理により、各導電素子21〜25のそれぞれに対して、対象の導電素子の点Pから点Qまで電流が流れるよう、対象の導電素子に電流を供給すると共に、対象の導電素子の点Rと点Sとの間の電位差を検出し、導電素子21〜25のそれぞれについて検出した調整後電位差に基づいて、導電素子21〜25に対する磁石13の相対位置を特定して出力する。

【0072】

このように、電磁変換素子として、5個の導電素子21〜25が、制御回路20と共に回路基板14上にパターン配線され(すなわち、プリントされ)、この導電素子21〜25に発生する電位差に基づいて、導電素子21〜25に対する磁石13の相対位置を検出することができる。このように、電磁変換素子をパターン配線することで、ICとして電磁変換素子を構成するよりも、部品点数が減り、かつ、部品コストが低減される。

【0073】

また、導電素子21〜25のそれぞれは、位置検出用配線61〜65よりも太くパターン配線されているので、導電素子25を貫く磁束を大きくすることができるので、位置検出の感度を向上することができる。

【0074】

なお、位置検出用配線61の配線に用いる材料と、導電素子21〜25の配線に用いる材料は、同じであっても違っていても良いが、同じにした方が、回路基板14にパターン配線を行うときの手間および位置検出装置1の製造コストが低減されるという利点がある。

【0075】

(他の実施形態)

以上、本発明の実施形態について説明したが、本発明の範囲は、上記実施形態のみに限定されるものではなく、本発明の各発明特定事項の機能を実現し得る種々の形態を包含するものである。例えば、以下のような形態も許容される。

【0076】

(1)上記実施形態では、回路基板14は、上面と下面にのみパターン配線される基板であったが、回路基板14は、3層以上にパターン配線可能な多層基板であってもよい。その場合、回路基板14において、導電素子21〜25と重なるように、他の導電素子を各層にパターン配線するようになっていてもよい。例えば、図13に示すように、導電素子25に重なるように、複数の導電素子26〜28を配置してもよい。この場合、複数の導電素子26〜28も、それぞれ導電素子25と同様に、点P、Q、R、Sを有し、位置検出用配線62と同様の位置検出用配線でマイクロコントローラ20と接続されていてもよい。

【0077】

このようにすることで、この導電素子25〜28の各PQ点間に電流を発生させ、導電素子25〜28の各RQ点間の電位差を検出し、それを、磁石13の位置(回路基板14に平行な面内の位置)の検出に用いることで、導電素子25〜28付近における磁石13の位置の特定精度が向上する。

【0078】

(2)また、図14に示すように、回路基板14の同じ層(例えば上面)において、導電素子の数を増やし、9個の導電素子21〜29を配置し、新たに配置した導電素子26〜29についても、他の導電素子21〜26と同様に、マイクロコントローラ20がPQ点間に電流を流し、RQ点間の電位差を検出することで、より高い精度で磁石13の位置検出を行うことができる。

【0079】

(3)また、磁石13が左右方向にしか移動しないような位置検出装置1の場合、図15に示すように、導電素子21、22、24を廃し、導電素子としては回路基板14に導電素子23と導電素子25のみをパターン配線するようになっていてもよい。この場合でも、磁石13の左右方向(図15中の左右方向)の位置を検出することは可能である。このような動きをする磁石13の応用例としては、オン時に左に移動し、オフ時に右に移動するオフスイッチがある。

【0080】

(4)また、磁石13が回路基板14上を円環状にしか移動しない位置検出装置1の場合、図16に示すように、導電素子21〜28を円環状の並びでパターン配線するようになっていてもよい。この場合、新たに配置した導電素子26〜28についても、他の導電素子21〜26と同様に、マイクロコントローラ20がPQ点間に電流を流し、RQ点間の電位差を検出する。

【0081】

(5)また、磁石13が上下方向(図3の上下方向)にしか移動しないような位置検出装置1の場合、図17に示すように、導電素子22〜25を廃し、導電素子としては回路基板14に導電素子21のみをパターン配線するようになっていてもよい。この場合でも、磁石13の上下方向(図17の紙面に垂直な方向)の位置を検出することは可能である。このような動きをする磁石13の応用例としては、オン時に回路基板14(および導電素子21)に近づく方向に移動し、オフ時に回路基板14(および導電素子21)から離れる方向に移動するオフスイッチがある。

【0082】

(6)また、上記実施形態では、導電素子21〜25に流す電流を均一化させるために、チップ抵抗31〜35を配置している。導電素子21〜25に流す電流を均一化させることは、磁石13の位置検出の精度を高めることに繋がるが、磁石13の位置検出の精度を高める必要がない場合は、そもそもチップ抵抗31〜35もスイッチ41a〜45a、41b〜45bも配置する必要はなく、プリントされた配線のみを介してDA端子20a〜20eのそれぞれを導電素子21〜25に接続させればよい。

【0083】

(7)また、上記実施形態では、磁石13は、その位置によらず、回路基板14に対して垂直になっているが、磁石13の回路基板14に対する傾きは、磁石13の位置の変化に応じて変化してもよい。例えば、磁石13が、所定の始点を中心に回転して移動するようになっていてもよい。

【0084】

(8)また、上記実施形態では、制御回路としてマイクロコントローラ20が例示されているが、制御回路としてマイクロコントローラ以外を採用してもよい。

【0085】

(9)また、上記実施形態では、1つの導電素子内において、点P、Q、R、Sがそれぞれ異なる位置にある。しかし、点P、Qのうちいずれか一方が、点R、Sのうちいずれかと共通であってもよい。ただし、第1の点Pおよび第2の点Qの両方が、第2の点Rおよび第3の点Sのうちいずれかと共通であるようになってはいけない。

【0086】

P、Q、R、Sの配置は、以下のようになっていれば、ホール効果によって発生する電位差を検出することができる。導電素子の点Pから点Qへの方向を第1の方向とし、当該導電素子上の点Rから見て第1の方向と交差(上記実施形態では直交)する方向を第2の方向とすると、点Rと、点Rから見て当該第2の方向にある点を点Sとすればよい。

【0087】

(10)また、上記実施形態では、マイクロコンピュータ20は、検出した導電素子のRS点間の電位差に基づいて、導電素子に対する磁石13の相対位置に応じた作動を行ううようになっている。そして、相対位置に応じた作動としては、相対位置の特定および出力を行っている。しかし、相対位置に応じた作動は、相対位置の特定および出力に限らない。

【符号の説明】

【0088】

1 位置検出装置

11 筐体

11a スリット

12 操作部

13 磁石

14 回路基板

20 マイクロコントローラ

20a〜20e DA端子

20f、20g AD端子

20h GND端子

21〜29 導電素子

52〜58 回路部品

31〜35 チップ抵抗

61〜65 位置検出用配線

【特許請求の範囲】

【請求項1】

回路基板(14)と、

発生する磁界が前記回路基板(14)を貫くような配置で前記回路基板(14)に対して相対的に移動する磁石(13)と、

前記回路基板(14)上にパターン配線された1個以上の導電素子(21〜29)と、

前記回路基板(14)上に実装された制御回路(20)と、

前記制御回路(20)から前記1個以上の導電素子(21〜29)のそれぞれに対して、対象の導電素子上の第1の点(P)から対象の導電素子上の第2の点(Q)への電流が発生するよう電流を供給するための配線であると共に、前記第1の点(P)から前記第2の点(Q)への方向を第1の方向とし、対象の導電素子上の第3の点(R)から見て前記第1の方向と交差する方向を第2の方向とすると、前記第3の点(R)と、対象の導電素子において前記第3の点(R)から見て前記第2の方向にある第4の点(S)と、の間の電位差を検出するための位置検出用配線(61〜65)と、を備え、

前記制御回路(20)は、前記1個以上の導電素子(21〜29)のそれぞれに対して、対象の導電素子の前記第1の点(P)から前記第2の点(Q)まで電流が流れるよう、対象の導電素子に電流を供給すると共に、対象の導電素子(21〜29)の前記第3の点(R)と第4の点(S)との間の電位差を検出し、前記1個以上の導電素子(21〜29)のそれぞれについて検出した前記電位差に基づいて、前記1個以上の導電素子(21〜29)に対する前記磁石(13)の相対位置に応じた作動を行う位置検出装置。

【請求項2】

前記回路基板(14)には、前記位置検出用配線(61〜65)以外の他の配線および回路部品(51)も配置されていることを特徴とする請求項1に記載の位置検出装置。

【請求項3】

前記回路基板(14)に設けられた回路部品のうち、所定の高さよりも低い回路部品は、前記回路基板(14)の前記磁石(13)側の面に実装され、所定の高さ以上の回路部品は、そのすべてが、前記回路基板(14)の前記磁石(13)側とは反対側の面に実装されていることを特徴とする請求項1または2に記載の位置検出装置。

【請求項4】

前記1個以上の導電素子(21〜29)は、複数個の導電素子(21〜29)であることを特徴とする請求項1ないし3のいずれか1つに記載の位置検出装置。

【請求項5】

前記1個以上の導電素子(21〜29)のそれぞれは、前記位置検出用配線(61〜65)よりも太くパターン配線されていることを特徴とする請求項1ないし4のいずれか1つに記載の位置検出装置。

【請求項1】

回路基板(14)と、

発生する磁界が前記回路基板(14)を貫くような配置で前記回路基板(14)に対して相対的に移動する磁石(13)と、

前記回路基板(14)上にパターン配線された1個以上の導電素子(21〜29)と、

前記回路基板(14)上に実装された制御回路(20)と、

前記制御回路(20)から前記1個以上の導電素子(21〜29)のそれぞれに対して、対象の導電素子上の第1の点(P)から対象の導電素子上の第2の点(Q)への電流が発生するよう電流を供給するための配線であると共に、前記第1の点(P)から前記第2の点(Q)への方向を第1の方向とし、対象の導電素子上の第3の点(R)から見て前記第1の方向と交差する方向を第2の方向とすると、前記第3の点(R)と、対象の導電素子において前記第3の点(R)から見て前記第2の方向にある第4の点(S)と、の間の電位差を検出するための位置検出用配線(61〜65)と、を備え、

前記制御回路(20)は、前記1個以上の導電素子(21〜29)のそれぞれに対して、対象の導電素子の前記第1の点(P)から前記第2の点(Q)まで電流が流れるよう、対象の導電素子に電流を供給すると共に、対象の導電素子(21〜29)の前記第3の点(R)と第4の点(S)との間の電位差を検出し、前記1個以上の導電素子(21〜29)のそれぞれについて検出した前記電位差に基づいて、前記1個以上の導電素子(21〜29)に対する前記磁石(13)の相対位置に応じた作動を行う位置検出装置。

【請求項2】

前記回路基板(14)には、前記位置検出用配線(61〜65)以外の他の配線および回路部品(51)も配置されていることを特徴とする請求項1に記載の位置検出装置。

【請求項3】

前記回路基板(14)に設けられた回路部品のうち、所定の高さよりも低い回路部品は、前記回路基板(14)の前記磁石(13)側の面に実装され、所定の高さ以上の回路部品は、そのすべてが、前記回路基板(14)の前記磁石(13)側とは反対側の面に実装されていることを特徴とする請求項1または2に記載の位置検出装置。

【請求項4】

前記1個以上の導電素子(21〜29)は、複数個の導電素子(21〜29)であることを特徴とする請求項1ないし3のいずれか1つに記載の位置検出装置。

【請求項5】

前記1個以上の導電素子(21〜29)のそれぞれは、前記位置検出用配線(61〜65)よりも太くパターン配線されていることを特徴とする請求項1ないし4のいずれか1つに記載の位置検出装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−83577(P2013−83577A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−224223(P2011−224223)

【出願日】平成23年10月11日(2011.10.11)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月11日(2011.10.11)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]