低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子に係り、特に、素子パフォーマンスを向上させるために機械的なストレスエンジニアリングを採用したMOS(metal−oxide−silicon)トランジスタのようなLSI(Large Scale Integration)半導体素子に関する。

【背景技術】

【0002】

MOSトランジスタのキャリア移動度は、素子の電力消耗及びスイッチングパフォーマンスに大きな影響力を有する。キャリア移動度を向上させることによって、スイッチング速度を速めることができ、低電圧での動作が可能となって、電力消耗を減少させうる。

【0003】

MOSトランジスタでキャリア移動度を向上させるために機械的ストレスエンジニアリングが採用された(例えば、特許文献1参照)。チャンネル領域での引張応力は、NMOSトランジスタでは、電流増加を招くが、PMOSトランジスタでは電流減少を招くことになる。チャンネル領域での圧縮応力は、PMOSトランジスタでは電流増加を招くが、NMOSトランジスタでは電流減少を招くことになる。

【0004】

図1は、素子でのキャリア移動度を向上させるために、機械的ストレスを導入するための方法を説明するNOS素子の概略的な断面図である。基板10に形成された素子は、基板10内に形成された素子分離領域12によって素子分離されている。トランジスタ素子は、基板10に形成されたソース/ドレーン領域22、26を含み、これらの間にチャンネル領域18が限定される。ゲート構造は、基板10上に形成されたゲート絶縁膜14と、前記ゲート絶縁膜14上にある導電性ゲート層20と、前記導電性ゲート層20上に形成されたシリサイド層30と、を含む。ゲート構造の両側壁には、絶縁側壁スペーサ24が形成されている。

【0005】

前記ゲート構造の上と前記ソース/ドレーン領域26及び基板10の上面に形成されたストレスコントロール層40によって前記チャンネル18に機械的ストレスが導入される。特に、図1に矢印で表示したように、MOSトランジスタ構造に引張応力が導入される。図1に矢印で表示されたような引張応力を前記チャンネル18に導入するための他の方法は、ソース/ドレーン領域22、26にシリサイド領域30を形成することである。シリサイド化工程を進行させた後、シリサイド領域30はシリサイドにより置換される前の元のソース/ドレーン材料より小さい体積を占めるためにチャンネル18に引張応力が導入される。

【0006】

機械的ストレスをMOSトランジスタに導入すれば、キャリア移動度を向上させる以外に、電気的ノイズ、特にフリッカノイズが導入されることによって、素子のパフォーマンスが劣化するということが分かった。通常、“1/fノイズ”とも称されるフリッカノイズは、そのパワースペクトルP(f)が、P(f)=1/fa(式中、aは1に非常に近い)によって挙動する周波数fの関数で表示されるノイズの一種である。また、フリッカノイズは、大部分のノイズパワーが周波数スペクトルの下端に集中するので、“ピンクノイズ”とも称される。フリッカノイズは、キャリアのトラッピング及びデトラッピング(detrapping)だけでなく、トラップされた電荷によるキャリア分散を通じた移動度変調により引き起こされると見なされている。フリッカノイズ劣化は、低周波アナログ回路及び高性能デジタル回路のいずれについても重要な因子となりうる。フリッカノイズは相対的に低周波で発生するが、そのノイズは、高周波スペクトルまでアップコンバータ(up−converter)に変換されて振動のコヒーレンシを劣化させうるので、一部のRF回路については非常に重要な因子である。

【0007】

図2A及び図2Bは、MOS素子でのストレスエンジニアリングとノイズとの関係を表すグラフである。図2Aは、ストレスが付加されたトランジスタとストレスが減少したトランジスタのノイズパワーSvg分布グラフである。この測定は、NMOS素子に対しては、Vd=0.05V及びVg=0.85Vで、そしてPMOS素子についてはVd=−0.05V及びVg=−0.85Vでなされた。図2Bは、CMOS素子のノイズパワー比対最大トランスコンダクタンス(Gmmax)改善率のグラフである。図2Bのグラフィックは、MOS素子での引張応力及び圧縮応力は、何れもフリッカノイズの観点でパフォーマンスを劣化させることを表す。

【0008】

したがって、MOSトランジスタにストレスエンジニアリングを与えれれば、MOSトランジスタのパフォーマンスが向上するが、フリッカノイズ特性は劣化する。すなわち、NMOS及びPMOS素子のいずれにおいても、引張応力及び圧縮応力は、素子のパフォーマンスを向上させるが、これら二素子のフリッカノイズ特性は劣化する。したがって、フリッカノイズ特性が考慮される場合、特にアナログ用、RF用及び混合信号用、例えばシステムLSI用などにおいては、ストレスエンジニアリングがあらゆる回路のパフォーマンスを向上させるに当って、常に許容されうる手段ではない。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許第6,573,172号明細書

【特許文献2】特開2003−086708号公報

【特許文献3】特開昭62−013061号公報

【特許文献4】特開平11−238799号公報

【特許文献5】特開2000−216377号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の特徴は、混合信号応用素子を有するLSI素子のような半導体素子、前記半導体素子のレイアウト、及びその素子を製造するための方法を提供することであり、ここで、引張応力及び/または圧縮応力を素子の他の領域、すなわち、アナログ領域及びデジタル領域に選択的に印加して素子のパフォーマンスを向上させると同時に、素子のパフォーマンスに及ぼすフリッカノイズの影響を減少させる。

【課題を解決するための手段】

【0011】

一態様において、本発明は、回路製造方法に関するものである。複数の回路領域内に複数の導電型を有し、複数の動作モードで動作する複数の素子を形成する。前記素子の動作モードに基づいて選択された少なくとも1つの素子に機械的ストレスを印加する。

【0012】

前記動作モードは、アナログモード及びデジタルモードを含みうる。また、前記動作モードは、ノイズに敏感なモード及びノイズに敏感でないモード、低速動作モード及び高速動作モード、そして高電圧動作モード及び低電圧動作モードを含みうる。

【0013】

一実施例において、前記素子は、少なくとも1つのPMOS素子及び/または少なくとも1つのNMOS素子を含む。前記素子は、少なくとも1つのCMOS素子を含みうる。

【0014】

一実施例において、前記機械的ストレスはデジタルモードのNMOS素子のチャンネルに印加される。一実施例において、前記機械的ストレスは、デジタルモードのPMOS素子のチャンネルに印加される。

【0015】

一実施例において、電気的なノイズ増加を防止するためにアナログモードで動作する素子にはストレスを印加しない。前記電気的なノイズはフリッカノイズでありうる。

【0016】

一実施例において、前記少なくとも1つの選択された素子に機械的ストレスを印加する段階は、前記素子に近接して前記回路にストレスコントロール膜を形成する段階を含む。前記ストレスコントロール膜は、引張応力及び/または圧縮応力を印加しうる。一実施例において、ストレスが印加されていない素子に近接して、前記ストレスコントロール膜でストレスを緩和する。前記ストレスコントロール膜でストレスを緩和するために、前記ストレスコントロール膜にイオン注入を行う。前記ストレスコントロール膜でストレスを緩和するために、前記ストレスコントロール膜の一部を選択的に除去することもある。前記ストレスコントロール膜は、SiN、SiONまたはSiO2を含みうる。前記ストレスコントロール膜形成段階は、アニーリング段階を含みうる。前記ストレスコントロール膜は、PECVD(plasma−enhanced chemical vapor deposition)及び/またはLPCVD(low−pressure chemical vapor deposition)方法で形成しうる。

【0017】

一実施例において、前記少なくとも1つの選択された素子に機械的ストレスを印加する段階は、前記回路上でシリサイド化工程を行う段階を含みうる。一実施例において、前記少なくとも1つの選択された素子に機械的ストレスを印加する段階は、前記回路上にキャッピング層を形成する段階と、ストレスが印加される素子に近接して前記キャッピング層を選択的に除去する段階と、ストレスが印加される素子にストレスを印加するために第2シリサイド化工程を行う段階とをさらに含む。

【0018】

一実施例において、前記少なくとも1つの選択された素子に機械的ストレスを印加する段階は、ストレスが印加される素子にソース/ドレーン構造をエピタキシャル成長させる段階を含む。

【0019】

一実施例において、第1CMOS構造の第1素子と、第1CMOS構造の第2素子とにストレスが印加される。第2CMOS構造の第1素子と、第2CMOS構造の第2素子とにストレスが印加されない。一実施例において、前記第1CMOS構造はデジタルモードで動作し、前記第2CMOS構造はアナログモードで動作する。一実施例において、前記第1CMOS構造の第1素子はPMOS素子であり、前記第1CMOS構造の第2素子はNMOS素子であり、前記PMOS素子は、そのチャンネルに印加される圧縮応力を有し、前記NMOS素子はそのチャンネルに印加される引張応力を有する。一実施例において、前記第1CMOS構造及び第2CMOS構造において、前記第1素子は何れもPMOS素子である。一実施例において、前記第1CMOS構造及び第2CMOS構造において、前記第2素子は何れもNMOS素子である。

【0020】

一実施例において、前記機械的ストレスを印加する段階は、前記素子に引張応力を印加する第1ストレスコントロール膜を前記回路上に形成する段階と、引張応力が印加されていない素子に近接して前記第1ストレスコントロール膜を選択的に除去する段階と、前記素子に圧縮応力を与える第2ストレスコントロール膜を前記素子上に形成する段階と、前記素子の選択された部分に近接して前記第2ストレスコントロール膜上にストレス緩和膜を形成する段階と、前記ストレス緩和膜を用いて圧縮応力が印加されていない素子でストレスを緩和させる段階と、を含む。前記圧縮応力が印加されない素子でストレスを緩和する段階は、前記ストレス緩和膜内にイオンを注入する段階を含む。

【0021】

一実施例において、前記機械的ストレスを印加する段階は、前記素子に引張応力を印加する第1ストレスコントロール膜を前記回路上に形成する段階と、引張応力が印加されない素子に近接して前記第1ストレスコントロール膜を選択的に除去する段階と、前記素子に圧縮応力を印加する第2ストレスコントロール膜を前記素子上に形成する段階と、圧縮応力が印加されない素子に近接して前記第2ストレスコントロール膜を選択的に除去する段階と、を含む。

【0022】

本発明の他の態様によれば、本発明は回路に関するものである。本発明に係る回路は、複数の回路領域内で複数の導電型を有して複数の動作モードで動作する複数の素子が形成された基板を含む。前記複数の素子のうち、選択される少なくとも1つの素子はその素子に印加された機械的ストレスを有し、前記選択された素子はその動作モードに基づいて選択される。

【0023】

前記動作モードは、アナログモード及びデジタルモードを含みうる。また、前記動作モードは、ノイズに敏感なモード及びノイズに敏感でないモード、低速動作モード及び高速動作モード、そして高電圧動作モード及び低電圧動作モードを含みうる。

【0024】

一実施例において、前記素子は少なくとも1つのPMOS素子及び/または少なくとも1つのNMOS素子を含む。前記素子は少なくとも1つのCMOS素子を含みうる。

【0025】

一実施例において、前記機械的ストレスはデジタルモードのNMOS素子のチャンネルに印加される。一実施例において、前記機械的ストレスはデジタルモードのPMOS素子のチャンネルに印加される。

【0026】

一実施例において、電気的なノイズ増加を防止するためにアナログモードで動作する素子にはストレスが印加されない。前記電気的なノイズはフリッカノイズでありうる。

【0027】

一実施例において、前記機械的ストレスは、前記素子に近接して前記回路上に形成されたストレスコントロール膜を用いて前記選択された素子に印加される。前記ストレスコントロール膜は、引張応力及び/または圧縮応力を印加しうる。一実施例において、ストレスが印加されていない素子に近接して前記ストレスコントロール膜でストレスが緩和される。前記ストレスコントロール膜のうち、ストレスが緩和された部分は追加で注入されたイオンを含みうる。一実施例において、前記ストレスコントロール膜はストレスが印加されていない素子に近接して存在しない。前記ストレスコントロール膜は、SiN、SiON及び/またはSiO2を含みうる。一実施例において、前記ストレスコントロール膜は、アニーリングされる。一実施例において、前記ストレスコントロール膜はPECVDまたはLPCVDによって形成される膜である。

【0028】

一実施例において、前記機械的ストレスを印加する手段はシリサイドを含む。

【0029】

一実施例において、前記機械的ストレスを印加する手段はエピタキシャル成長されたソース/ドレーン構造を含む。

【0030】

一実施例において、第1CMOS構造の第1素子と、第1CMOS構造の第2素子にストレスが印加されており、第2CMOS構造の第1素子と、第2CMOS構造の第2素子にストレスが印加されていない。一実施例において、前記第1CMOS構造は、デジタルモードで動作し、前記第2CMOS構造はアナログモードで動作する。一実施例において、前記第1CMOS構造の第1素子はPMOS素子であり、前記第1CMOS構造の第2素子はNMOS素子であり、前記PMOS素子はそのチャンネルに印加される圧縮応力を有し、前記NMOS素子はそのチャンネルに印加される引張応力を有する。一実施例において、前記第1CMOS構造及び第2CMOS構造において前記第1素子は何れもPMOS素子である。一実施例において、前記第1CMOS構造及び第2CMOS構造において前記第2素子は何れもNMOS素子である。

【0031】

一実施例において、前記機械的ストレスを印加する手段は、前記素子に引張応力を印加し、前記引張応力が印加される素子に近接した位置にのみ存在するように前記回路上に形成されている第1ストレスコントロール膜と、前記素子に圧縮応力を与えるように前記素子上に形成されている第2ストレスコントロール膜と、前記素子の選択された部分に近接して前記第2ストレスコントロール膜上に形成されており、圧縮応力を必要としない素子でストレスを緩和するストレス緩和膜とを含む。一実施例において、前記ストレス緩和膜は追加で注入されたイオンを含む。

【0032】

一実施例において、前記機械的ストレスを印加する手段は、前記素子に引張応力を印加し、前記引張応力が印加される素子に近接した位置にのみ存在するように前記回路上に形成されている第1ストレスコントロール膜と、前記素子に圧縮応力を印加し、前記圧縮応力が印加される素子に近接した位置にのみ存在するように前記素子上に形成されている第2ストレスコントロール膜と、を含む。

【0033】

本発明の他の態様によれば、本発明は回路製造方法に関するものである。本発明に係る方法では回路の第1領域に第1導電型の第1MOS素子を形成する。前記回路の第2領域に第1導電型の第2MOS素子を形成する。前記第1及び第2MOS素子のチャンネルにストレスを印加する。前記第2MOS素子のチャンネルでストレスを緩和する。

【0034】

一実施例において、前記第1及び第2MOS素子に近接して前記回路上にストレスコントロール膜が形成される。前記ストレスコントロール膜は、前記第1及び第2MOS素子にストレスを印加する。前記ストレスコントロール膜はLPCVD方法によって形成しうる。また、前記ストレスコントロール膜は、PECVD方法によって形成しても良い。前記ストレスコントロール膜は、低温で形成されたSiNを含みうる。一実施例において、前記ストレスを緩和する段階は、前記ストレスコントロール膜にイオンを注入する段階を含む。前記ストレスコントロール膜はSiNを含みうる。

【0035】

一実施例において、前記ストレスは圧縮応力である。一実施例において、前記ストレスは引張応力である。

【0036】

本発明の他の態様によれば、本発明は回路製造方法に関するものである。本発明に係る方法では、回路の第1領域に第1導電型の第1MOS素子を形成する。前記回路の第2領域に第1導電型の第2MOS素子を形成する。前記第1MOS素子のチャンネルにストレスを印加する。

【0037】

一実施例において、前記第1MOS素子のチャンネルにストレスを印加する段階は、前記第1及び第2MOS素子に近接して前記回路上にストレスコントロール膜を形成する。前記ストレスコントロール膜はPECVDによって形成しうる。前記ストレスコントロール膜はSiONを含みうる。前記ストレスコントロール膜はSiO2よりなりうる。

【0038】

一実施例において、本発明に係る方法は、前記第2MOS素子からストレスコントロール膜を除去し、前記第1MOS素子上に前記ストレスコントロール膜の一部を残す段階をさらに含む。一実施例において、前記第1MOS素子上のストレスコントロール膜部分をアニーリングする段階をさらに含む。

【0039】

一実施例において、本発明に係る方法は、前記第1及び第2MOS素子に近接して第1相のシリサイドを形成するために第1熱処理を行う段階をさらに含む。前記第1及び第2MOS素子と前記第1相のシリサイド上にキャッピング層が形成されうる。前記第1MOS素子及び第1相のシリサイド上で前記キャッピング層の一部を除去しうる。前記第1相のシリサイドを第2相のシリサイドに転換させるために第2熱処理を行える。

【0040】

一実施例において、前記ストレスは圧縮応力である。一実施例において、前記ストレスは引張応力である。

【0041】

本発明の他の態様によれば、本発明は回路製造方法に関するものである。本発明の方法によれば、回路の第1領域に第1導電型の第1MOS素子及び第2導電型の第2MOS素子を含む第1CMOS素子を形成する。前記回路の第2領域に第1導電型の第3MOS素子及び第2導電型の第4MOS素子を含む第2CMOS素子を形成する。前記第1及び第2MOS素子のうち、何れか1つのチャンネルに引張応力を印加し、前記第1及び第2MOS素子のうち、他の1つに圧縮応力を印加する。前記第1領域でMOS素子のチャンネルにストレスが印加されたならば、前記第2領域でMOS素子のチャンネルに印加されたストレスを除去する。

【0042】

一実施例において、本発明による方法は、前記第1及び第2MOS素子のうち、何れか1つのソース/ドレーン領域とゲート上に半導体層をエピタキシャル成長させ、前記第1及び第2MOS素子のうち、何れか1つに圧縮応力を印加する段階をさらに含む。前記第1及び第2MOS素子のうち、他の1つの上にストレスコントロール膜を形成して前記第1及び第2MOS素子のうち、他の1つに引張応力を印加する。

【0043】

一実施例において、前記第1及び第2MOS素子のうち、何れか1つに引張応力を印加する第1ストレスコントロール膜を前記第1及び第2MOS素子のうち、何れか1つの上に形成する。一実施例において、前記第1ストレスコントロール膜はSiN、SiON、及びSiO2のうち、少なくとも何れか1つを含む。前記第1及び第2MOS素子のうち、他の1つに圧縮応力を印加する第2ストレスコントロール膜を前記第1及び第2MOS素子のうち、他の1つの上に形成しうる。一実施例において、前記第2ストレスコントロール膜はSiN及びSiO2のうち、少なくとも何れか1つを含む。

【0044】

本発明の他の態様によれば、本発明は回路に関するものである。本発明に係る回路は回路の第1領域に形成された第1導電型の第1MOS素子と、前記回路の第2領域に形成された第1導電型の第2MOS素子とを含む。前記第1MOS素子のチャンネルにはストレスが印加されており、前記第2MOS素子にはストレスが印加されていない。

【0045】

一実施例において、前記第1MOS素子上にストレスコントロール膜が形成されており、前記ストレスコントロール膜は前記第1MOS素子にストレスを印加する。一実施例において、前記ストレスコントロール膜はその内部に注入されているイオンをさらに含む。一実施例において、前記ストレスコントロール膜はSiNよりなる。一実施例において、前記ストレスコントロール膜はSiONよりなる。一実施例において、前記ストレスコントロール膜はSiO2よりなる。一実施例において、前記ストレスは圧縮応力である。一実施例において、前記ストレスは引張応力である。

【0046】

一実施例において、本発明に係る回路は、前記第1MOS素子のソース/ドレーン構造に近接した第2相のシリサイドをさらに含む。

【0047】

本発明の他の態様によれば、本発明は回路に関するものである。本発明に係る回路は、回路の第1領域に形成され、第1導電型の第1MOS素子及び第2導電型の第2MOS素子を含む第1CMOS素子と、前記回路の第2領域に形成されて第1導電型の第3MOS素子及び第2導電型の第4MOS素子を含む第2CMOS素子を含む。前記第1及び第2MOS素子のうち、何れか1つのチャンネルには引張応力が印加されており、前記第1及び第2MOS素子のうち、他の1つには圧縮応力が印加されている。

【0048】

一実施例において、本発明に係る回路は、前記第1及び第2MOS素子のうち、何れか1つに圧縮応力を印加できるように、前記第1及び第2MOS素子のうち、何れか1つのソース/ドレーン領域とゲート上とにエピタキシャル成長されている半導体層をさらに含む。

【0049】

一実施例において、本発明に係る回路は、前記第1及び第2MOS素子のうち、他の1つに引張応力を印加できるように前記第1及び第2MOS素子のうち、他の1つの上に形成されたストレスコントロール膜をさらに含む。

【0050】

一実施例において、前記第1及び第2MOS素子のうち、何れか1つの上に形成されている第1ストレスコントロール膜をさらに含む。前記第1ストレスコントロール膜は前記第1及び第2MOS素子のうち、何れか1つに引張応力を印加する。一実施例において、前記第1ストレスコントロール膜は、SiN、SiON、及びSiO2のうち、少なくとも何れか1つを含む。一実施例において、本発明に係る回路は、前記第1及び第2MOS素子のうち、他の1つの上に形成されている第2ストレスコントロール膜をさらに含む。前記第2ストレスコントロール膜は、前記第1及び第2MOS素子のうち、他の1つに圧縮応力を印加する。前記第2ストレスコントロール膜はSiN及びSiO2のうち、少なくとも何れか1つを含みうる。

【発明の効果】

【0051】

本発明によれば、特定の素子の要求される動作構成によって前記素子にストレスエンジニアリングを選択的に適用する。すなわち、素子の導電型、すなわちn型またはp型はもとより、それらの動作による役割、例えばアナログ/デジタル、低電圧/高電圧、高速/低速、ノイズ敏感如何などに基づいて素子、すなわちNMOS及び/またはPMOS素子で適切な応力、すなわち引張応力または圧縮応力を印加及び/または除去しうる。

【図面の簡単な説明】

【0052】

【図1】素子でキャリア移動度を向上させるために機械的ストレスを導入する方法を説明するMOS素子の概略的な断面図である。

【図2A】MOS素子でのストレスエンジニアリングとノイズとの関係を説明するグラフである。

【図2B】MOS素子でのストレスエンジニアリングとノイズとの関係を説明するグラフである。

【図3】本発明によって素子を形成する一方法を説明するフローチャートであって、素子に及ぼすノイズの影響は減少させつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に適用する方法を説明するフローチャートである。

【図4】本発明によって素子を形成する他の方法を説明するフローチャートであって、素子に及ぼすノイズの影響は減少させつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に適用する方法を説明するフローチャートである。

【図5】本発明によって素子を形成するさらに他の方法を説明するフローチャートであって、素子に及ぼすノイズの影響は減少させつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に適用する方法を説明するフローチャートである。

【図6】本発明の一実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図7】本発明の一実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図8】本発明の一実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図9】本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図10】本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図11】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図12】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図13】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図14】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図15】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図16】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図17】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図18】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図19】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図20】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図21】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図22】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図23】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図24】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図25】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図26】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図27】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図28】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図29】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図30】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図31】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図32】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【発明を実施するための形態】

【0053】

本発明の前記及び他の特徴及び利点は添付図面に示されたような本発明の望ましい実施例のさらに具体的な説明からさらに明白になる。添付図面は、本発明の原理を説明するために必要に応じて強調して示した。図面において同じ符号は同じ要素を示す。

【0054】

本発明によれば、混合信号応用素子、例えばアナログ及びデジタル応用素子を有するLSI素子のような半導体素子、その半導体素子のレイアウト、及びその素子の製造方法を提供し、ここで引張応力及び/または圧縮応力を素子の異なる領域、すなわちアナログ領域及びデジタル領域に選択的に印加して素子のパフォーマンスを向上させると同時に、素子のパフォーマンスに及ぼすフリッカノイズの影響を減少させる。

【0055】

次いで、本発明の実施例を詳細に説明する。次の実施例は3つの実施例カテゴリーのうち、何れか1つに属すると考慮されうる。ここで、各カテゴリーは、素子に及ぼすノイズの影響を制限しつつ、パフォーマンスを向上させるように素子にストレスエンジニアリングを選択的に適用する方法で区分される。図3ないし図5は、各々本発明の実施例の3つのカテゴリーを説明するフローチャートである。これらカテゴリーは、本発明を制限するものと解釈されてはならない。これらカテゴリーは、説明をさらに明確にし、かつ本発明の理解を容易にするためのものでのみ理解されねばならない。

【0056】

図3は、本発明によって素子を形成する1つの方法を説明するフローチャートであって、ここでは素子に及ぼすノイズの影響は減らしつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に印加する。

【0057】

図3を参照すれば、段階52で、第1導電型、すなわちn型またはp型の第1MOS素子を素子の第1領域、例えば、デジタル領域、すなわちデジタル回路が形成される素子領域に形成する。第1導電型、すなわちn型またはp型の第2MOS素子を素子の第2領域、例えばアナログ領域、すなわちアナログ回路が形成される素子領域に形成する。段階54で、第1及び第2領域に第1及び第2MOS素子のチャンネルに局部的応力を選択的に印加するためにストレスエンジニアリングを印加する。段階56において、前記第2領域で第2MOS素子のチャンネルから応力を解除または緩和する。

【0058】

前記方法によって第1MOS素子のチャンネルにのみ応力が印加される。応力が与えられた第1MOS素子は印加された応力の結果としてパフォーマンスが向上されうるが、ノイズが増加されることもある。一方、第2MOS素子は、局部的応力が印加されていないために、フリッカノイズによる効果が減少しうる回路が得られる。この方法は、前記第1領域が前記第2領域に比べてノイズに対して敏感でない場合のような状況で適用されうる。例えば、前記第1領域は、デジタル回路、低電圧動作用回路及び/またはノイズに敏感でない回路を含むことができ、前記第2領域はアナログ回路、高電圧動作用回路及び/またはノイズに敏感な回路を含みうる。

【0059】

一実施例において、ストレスコントロール膜を形成することによって局部的応力を前記第1領域及び第2領域の両側に何れも印加しうる。前記第1MOS素子での応力を緩和するために、イオン注入を用いるか、前記ストレスコントロール膜の一部を前記第2MOS素子上で除去する。次いで、本発明に係る前記第1カテゴリーまたは第1グループの特定実施例をさらに詳細に説明する。

【0060】

図4は、本発明によって素子を形成する他の方法を説明するフローチャートであって、ここでは、素子に及ぼすノイズの影響は減らしつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に印加する。図4は本発明の第2カテゴリーを説明する。

【0061】

図4を参照すれば、段階62で、第1導電型、すなわちn型またはp型の第1MOS素子を素子の第1領域、例えばデジタル領域、すなわちデジタル回路が形成される領域に形成する。前記第1導電型、すなわちn型またはp型の第2MOS素子を素子の第2領域、例えばアナログ領域、すなわち、アナログ回路が形成される領域に形成する。段階64において、前記第1領域で前記第1MOS素子のチャンネルに局部的応力を選択的に印加するためにストレスエンジニアリングを適用する。

【0062】

前記方法によって前記第1MOS素子のチャンネルにのみ応力が印加される。応力が印加された前記第1MOS素子は、印加された応力によって向上したパフォーマンス特性を有するが、これに伴って増加したノイズを有することもある。一方、前記第2MOS素子は、局部的応力が印加されていないためにフリッカノイズによる影響を減らしうる。この方法は、前記第1領域が第2領域よりノイズに敏感ではない場合に適用しうる。例えば、前記第1領域はデジタル回路、低電圧動作用回路及び/またはノイズに敏感でない回路を含み、前記第2領域はアナログ回路、高電圧動作用回路及び/またはノイズに敏感な回路を含みうる。

【0063】

本発明に係る前記第2カテゴリーまたは第2グループの特定実施例を次にさらに詳細に説明する。

【0064】

図5は、本発明によって素子を形成する他の方法を説明するフローチャートであって、ここでは素子に及ぼすノイズの影響は減らしつつ、素子パフォーマンスを向上させるために、素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に印加する。図5は本発明の第3カテゴリーを説明する図面である。

【0065】

図5を参照すれば、段階66で、第1導電型、すなわちn型またはp型の第1MOS素子と、第2導電型、すなわちp型またはn型の第2MOS素子を含む第1CMOS素子を素子の第1領域、例えばデジタル領域、すなわちデジタル回路が形成される領域に形成する。第1導電型、すなわちn型またはp型の第1(第3)MOS素子と、第2導電型、すなわちp型またはn型の第2(第4)MOS素子を含む第2CMOS素子を素子の第2領域、例えばアナログ領域、すなわち、アナログ回路が形成される領域に形成する。段階68で、前記第1及び第2CMOS領域で前記第1及び第2MOS素子の少なくとも1チャンネルに局部的引張応力及び局部的圧縮応力を選択的に印加するためにストレスエンジニアリングを適用する。段階70で、第2CMOS素子のMOS素子のチャンネルで応力を解除または緩和する。

【0066】

前記方法によって、前記第1CMOS素子の第1及び/または第2MOS素子のチャンネルにのみ応力が印加される。応力が印加された前記第1CMOS素子は印加された応力によって向上したパフォーマンス特性を有するが、これに伴って増加したノイズを有することもある。一方、前記第2CMOS素子は、局部的応力が印加されていないために、フリッカノイズによる影響を減らしうる。この方法は、前記第1領域が第2領域よりノイズに敏感ではない場合に適用しうる。例えば、前記第1領域はデジタル回路、低電圧動作用回路及び/またはノイズに敏感でない回路を含み、前記第2領域はアナログ回路、高電圧動作用回路及び/またはノイズに敏感な回路を含みうる。

【0067】

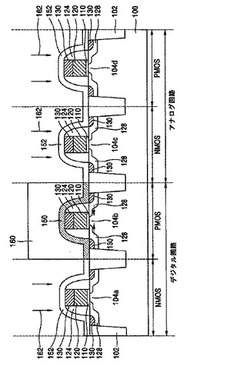

図6ないし図8は、本発明の一実施例に係る半導体素子の形成方法を説明する概略的な断面図である。本実施例は前述した実施例の第1カテゴリーに属するものである。

【0068】

図6を参照すれば、例えばシリコンよりなる基板100を準備する。素子はデジタル回路領域及びアナログ回路領域を含む。デジタル回路領域及びアナログ回路領域は各々第1NMOSトランジスタ及び第1PMOSトランジスタを含む。素子分離のためにSTI(shallow trench isolation)102が基板100に形成されている。各トランジスタは、ソース/ドレーン領域128を含み、これらは各々低濃度ソース/ドレーン領域122及び高濃度ソース/ドレーン領域126を含む。各トランジスタの基板上にはゲート絶縁膜パターン110が形成されている。各トランジスタで各ゲート絶縁膜パターン110上には導電性ゲートパターン120が形成されており、各導電性ゲートパターン120及びソース/ドレーン領域128、特に高濃度ソース/ドレーン領域126の露出領域上には各々シリサイドパターン130が形成されている。前記シリサイドパターン130は、例えばコバルトシリサイド、ニッケルシリサイド、チタンシリサイド、またはタングステンシリサイドで形成しうる。前記ゲート絶縁膜パターン110、導電性ゲートパターン120及びシリサイドパターン130を含むあらゆるゲート構造の両側壁には側壁スペーサ124が形成されている。一実施例において、アナログ回路領域ではトランジスタゲート構造とSTI102との距離、すなわちd1、d2、d3及びd4は1.5μm以上になることが望ましい。

【0069】

図7を参照すれば、前記構造上にストレスコントロール膜150を形成する。図面に矢印で表示されたように、前記ストレスコントロール膜150は、トランジスタのチャンネル104a、104b、104c、104dに圧縮応力を印加する。前記ストレスコントロール膜150はPECVD(plasma enhanced chemical vapor deposition)により約20−150nmの厚さに形成されたシリコン窒化膜(SiN膜)よりなりうる。また、200−400℃の低温条件下で形成されたシリコン窒化膜、または圧縮応力を有するシリコン酸化膜を使用しても良い。

【0070】

図8を参照すれば、デジタル回路領域のNMOSトランジスタとアナログ回路領域のNMOS及びPMOSトランジスタ上で圧縮応力を選択的に緩和する。フォトレジストマスク160をデジタル回路領域のPMOSトランジスタだけを覆うように形成する。前記フォトレジストマスク160をイオン注入マスクとして使用して参照符号“162”で表示したように、Ge、Si、As、In、Sbなどのイオンをストレスコントロール膜150内に注入する。一実施例において、前記ストレスコントロール膜150の厚さを考慮して、イオン注入エネルギーを20−100KeVの範囲に調節し、注入されたイオンが実質的に前記シリサイドパターン130内に注入されることを防止することが望ましい。

【0071】

イオン注入の結果、デジタル回路領域のPMOSトランジスタを除外したあらゆる領域で前記ストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換される。したがって、デジタル回路領域のPMOSトランジスタのチャンネル104bにだけ圧縮応力が印加される状態に残る。その結果、デジタル回路領域のPMOSトランジスタでは、パフォーマンスが向上する。デジタル回路領域のNMOSトランジスタ及びアナログ回路領域のNMOS及びPMOSトランジスタ領域上には応力が残っていないために、これら素子のフリッカノイズ特性が劣化されない。すなわち、本実施例ではデジタル回路領域でのPMOS素子でのみパフォーマンスの向上のためにPECVDシリコン窒化膜よりなるストレスコントロール膜が使われる。

【0072】

図9及び図10は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第1カテゴリーに属するものである。図9及び図10の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、シリサイドパターン130及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。

【0073】

図9を参照すれば、前記構造上に引張応力を印加するストレスコントロール膜250を形成する。前記ストレスコントロール膜250は、LPCVDによって約20−150nmの厚さに形成されたシリコン窒化膜よりなりうる。他の例として、前記ストレスコントロール膜250は、400−800℃の高温条件下で形成されたシリコン窒化膜で形成されることもある。また、前記ストレスコントロール膜250はPECVDによってシリコン酸化窒化膜(SiON膜)を形成した後、アニーリング段階を経て得られる。他の方法として、前記ストレスコントロール膜250は引張力を印加するシリコン酸化膜で形成しうる。結果的に、得られる引張応力は、図9で矢印で示したように、トランジスタのチャンネル204a、204b、204c、204dに局部的に影響が及ぼす。

【0074】

図10を参照すれば、デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のPMOS及びNMOSトランジスタ上で引張応力を選択的に緩和する。フォトレジストマスク260をデジタル回路領域のNMOSトランジスタだけ覆うように形成する。前記フォトレジストマスク260をイオン注入マスクとして使用して参照符号“262”と表示したように、Ge、Si、As、In、Sbなどのイオンをストレスコントロール膜250内に注入する。一実施例において、前記ストレスコントロール膜250の厚さを考慮し、イオン注入エネルギーを20−100KeVの範囲に調節し、注入されたイオンが実質的に前記シリサイドパターン130内に注入されることを防止することが望ましい。

【0075】

イオン注入の結果、デジタル回路領域のNMOSトランジスタを除外したあらゆる領域で前記ストレスコントロール膜250はストレス解除膜またはストレス緩和膜252に変換される。したがって、デジタル回路領域のNMOSトランジスタのチャンネル204bにだけ引張応力が印加される状態に残る。その結果、デジタル回路領域のNMOSトランジスタでは、パフォーマンスが向上する。デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のNMOS及びPMOSトランジスタ領域上には応力が残っていないために、これら素子のフリッカノイズ特性が劣化されない。すなわち、本実施例ではデジタル回路領域でのNMOS素子でのみパフォーマンス向上のためにLPCVDシリコン窒化膜よりなるストレスコントロール膜が使われる。

【0076】

図11及び図13は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は前記実施例のうち、第2カテゴリーに属するものである。図11ないし図13の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、シリサイドパターン130及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。

【0077】

図11を参照すれば、前記構造上に応力を持たないストレスコントロール膜350を形成する。前記ストレスコントロール膜350は、PECVDによって約20−150nmの厚さに形成されたシリコン酸化窒化膜よりなりうる。

【0078】

図12を参照すれば、デジタル回路領域でNMOSトランジスタ上にのみフォトレジストパターン360を形成する。次いで、前記フォトレジストパターン360をマスクとして使用してデジタル回路領域のNMOSトランジスタを除外したあらゆる領域で前記ストレスコントロール膜350を除去する。

【0079】

次いで、図13を参照すれば、前記フォトレジストパターン360を除去し、前記ストレスコントロール膜350の残余部分をアニーリングする。アニーリングの結果、前記ストレスコントロール膜350は引張応力膜352に変換され、これは図面で矢印で表示したようにデジタル回路領域でNMOSトランジスタのチャンネル304aに引張応力を印加する。残りのトランジスタのチャンネル304b、304c、304dは、それらの各トランジスタ領域に引張応力膜352がないので、何らの応力も受けない。

【0080】

このように、本実施例ではデジタル回路領域でNMOSトランジスタのチャンネル304aに引張応力が局部的に付与される。その結果、デジタル回路領域のNMOSトランジスタではパフォーマンスが向上する。デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のNMOS及びPMOSトランジスタ領域上には応力が残っていないために、これら素子のフリッカノイズ特性が劣化されない。すなわち、本実施例ではデジタル回路領域でのNMOS素子でのみパフォーマンスの向上のために引張応力を有するアニーリングされたPECVDシリコン酸化窒化膜を使用する。

【0081】

図14ないし図16は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は前記実施例のうち、第2カテゴリーに属するものである。図14ないし図16の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。図14ないし図16の実施例では、NMOSパフォーマンスを向上させるために引張応力を有するアニーリングされたPECVDシリコン二酸化膜(SiO2膜)が形成される。

【0082】

図14を参照すれば、前記構造上にSiO2膜450を形成する。前記SiO2膜450は約600℃以下の温度下でPECVD方法によって約20−100nmの厚さに形成しうる。

【0083】

図15を参照すれば、アナログ回路領域のNMOSトランジスタ上のSiO2膜450部分を除去する。次いで、前記SiO2膜450を900−1150℃の温度でアニーリングして前記SiO2膜450から引張応力を誘導し、それにより、デジタル回路領域のNMOSトランジスタから引張応力を誘導する。ここで、注意すべき点は、アナログ回路領域のNMOSトランジスタには応力印加を防止することが望ましいので、アナログ回路領域のNMOSトランジスタでは前記SiO2膜450を除去する。PMOSトランジスタ上にあるSiO2膜450は除去する必要がない。その理由は、SiO2膜をアニーリングすれば、PMOSトランジスタには影響を及ぼさないからである。例えば、高い引張応力を有するCVD SiO2膜の高温アニーリングの影響によってAsイオン注入されたポーリシリコン(典型的にNMOSゲートに使われる)には圧縮応力が誘導されると知られている。したがって、アニーリング後には図面で矢印で表示したように、デジタル回路領域で、NMOSトランジスタのチャンネル404aに印加された引張応力と、ゲート120に印加された圧縮応力とが存在する。

【0084】

次いで、図16を参照すれば、後続工程、例えば素子のソース/ドレーン領域のシリサイド化のような工程を進行するように、前記SiO2膜450の残りの部分を除去しうる。しかし、前記SiO2膜450の残りの部分は必ずしも除去する必要はない。前記SiO2膜450が完全に除去されるか、またはデジタル回路領域のNMOSトランジスタ上に残っているかに関係なく、前記ゲート120での圧縮応力及び前記チャンネル404aでの引張応力は保持されうる。

【0085】

前述したように、本実施例ではデジタル回路領域のNMOSトランジスタのチャンネル404aには局部的に引張応力が与えられ、そのゲートには圧縮応力が与えられる。その結果、デジタル回路領域のNMOSトランジスタでは、パフォーマンスが向上する。デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のNMOS及びPMOSトランジスタ領域上には、応力が残っていないために、これら素子のフリッカノイズ特性が劣化されない。ここで、注意すべき点は、本実施例において、追加的な高温アニーリング工程を導入しなくても、ソース/ドレーン活性化のための熱的負担を引張応力を誘導するのに利用することもできるということである。

【0086】

図17ないし図20は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第2カテゴリーに属するものである。本実施例では、NMOSトランジスタのパフォーマンスを向上させるためにシリサイド化工程を利用する。図17ないし図20の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。しかし、図17ないし図20の実施例において、シリサイドパターン130の代わりにシリサイドパターン830が図示されている。本実施例ではこれらシリサイドパターン830を、次の説明するようにNMOSパフォーマンスを向上させるのに利用する。

【0087】

図17を参照すれば、前記構造上に金属層パターンを蒸着して前記シリサイドパターン830を形成する。ここで、前記シリサイドパターン830は、ソース/ドレーン領域128及び導電性ゲート120のシリコン上に形成される。前記金属層は、例えばコバルトよりなりうる。その後、約450℃で第1RTA(rapid thermal annealing)工程を行なってコバルトモノシリサイド(CoSi)よりなるシリサイドパターン830を形成する。すなわち、第1熱処理によって第1相の金属シリサイドが形成される。前記第1RTAが行なわれた後、残りのコバルトは除去する。

【0088】

図18を参照すれば、前記第1RTAが行なわれた結果物上にキャッピング層840を形成する。前記キャッピング層840は、約5−20nmの厚さに形成されたチタン窒化膜(TiN膜)よりなりうる。

【0089】

図19を参照すれば、前記構造上にフォトレジストパターン860を形成してデジタル回路領域のNMOSトランジスタ上に形成された前記キャッピング層840部分のみを露出させる。次いで、前記キャッピング層840の露出された部分を除去する。次いで、約700−1100℃の温度下で第2RTA工程を行う。前記第2RTA工程の結果として、前記シリサイドパターン830が第2相の金属シリサイドに相転移する。例えば、CoSiがコバルトジシリサイド(CoSi2)に相転移する。その結果、ゲート及びソース/ドレーン領域上には、新たなシリサイドパターン830aが形成される。第1相の金属シリサイド、例えばCoSiから第2相の金属シリサイド、例えばCoSi2の相転移が行われる間、デジタル回路領域のNMOSトランジスタにチャンネル804aには引張応力が与えられる。他のチャンネル804b、804c、804dにはその上にキャッピング層840が形成されているので、これらがストレスを緩和する役割を行い、前記チャンネル804b、804c、804dには引張応力が、ほとんどまたは全く印加されない。すなわち、デジタル回路領域のNMOSトランジスタのチャンネル804aには引張応力が局部的に与えられが、残りのトランジスタのチャンネル804b、804c、804dにはその上に応力を緩和するためのキャッピング層840があるので、アニーリングによる影響を受けない。

【0090】

図20を参照すれば、キャッピング層840の残りの部分を除去する。その結果、デジタル回路領域のNMOSトランジスタのチャンネル804aには引張応力を与え、残りのトランジスタには応力を与えないシリサイドパターン830aを有する素子が得られる。

【0091】

図21ないし図27は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第3カテゴリーに属するものである。本実施例では、PMOSトランジスタのパフォーマンスを向上させるために、PMOSトランジスタに圧縮応力を誘導できるように、エピタキシャル成長されたソース/ドレーン構造を利用する。

【0092】

図21を参照すれば、各々NMOSトランジスタ及びPMOSトランジスタを含むCMOS構造をデジタル回路領域及びアナログ回路領域を含む素子の前記デジタル回路領域及びアナログ回路領域に形成する。前記デジタル回路領域及びアナログ回路領域は、各々第1NMOSトランジスタ及び第1PMOSトランジスタを含む。例えば、シリコンよりなる基板100を準備する。素子分離のために前記基板100にSTI102を形成する。各トランジスタは、ソース/ドレーン領域128を含み、これらは各々低濃度ソース/ドレーン領域122及び高濃度ソース/ドレーン領域126を含む。前記基板100上には各トランジスタを構成するゲート絶縁膜パターン110が形成されている。前記ゲート絶縁膜パターン110上には各トランジスタを構成するための導電性ゲートパターン120が形成され、前記ゲート絶縁膜パターン110及び導電性ゲートパターン120を含むあらゆるゲート構造の両側壁には側壁スペーサ124が形成される。

【0093】

図22を参照すれば、図21の構造上にマスク層510を形成する。前記マスク層510は、例えばシリコン酸化物、シリコン窒化物、またはこれらと類似した材料よりなりうる。

【0094】

図23を参照すれば、デジタル回路領域のPMOSトランジスタ上にあるマスク層510部分を少なくとも部分的に除去し、側壁スペーサ124上に少量のマスク層510だけを残す。その後、露出されたPMOSトランジスタのソース/ドレーン領域128の一部をそのゲート構造の側で自己整列方式で垂直方向に異方性エッチングによって一部除去する。その結果、約10−100nmの深さを有する溝520が形成される。

【0095】

図24を参照すれば、前記溝520及び導電性ゲート120の上面に半導体層522を選択的にエピタキシャル成長させる。前記エピタキシャル成長された半導体層522はSiGe、SiCまたはその他の物質よりなりうる。図面で矢印で表示したように、前記半導体層522はデジタル回路領域のPMOSトランジスタのチャンネル504bに圧縮応力を与える。この圧縮応力は、エピタキシャル成長された前記半導体層522のさらに大きな格子定数に起因する。さらに大きな格子定数を有する材料はチャンネル504b材料に圧力を与え、チャンネル504bで圧出応力が引き起こされる。すなわち、エピタキシャル成長された半導体層522と前記基板100は、相異なる格子定数及び/または相異なる熱膨張係数を有し、これにより、トランジスタのチャンネルで機械的応力が発生し、前記チャンネルでのキャリア移動度に影響を及ぼす。

【0096】

図25を参照すれば、前記構造から前記マスク層510の残りの部分を除去する。次いで、前記導電性ゲートパターン120及び露出されたソース/ドレーン領域128の上と、デジタル回路領域のPMOSトランジスタにエピタキシャル成長されている前記半導体層522の上面上に金属シリサイド層530を形成する。前記金属シリサイド層530は、例えばニッケルシリサイド、コバルトシリサイド、または他の類似した材料よりなりる。

【0097】

次いで、図26を参照すれば、前記構造上に引張応力を有するストレスコントロール膜550を形成する。前記ストレスコントロール膜550はLPCVD方法によって約20−150nmの厚さを有するように形成されたシリコン窒化膜よりなりうる。前記ストレスコントロール膜550は400−800℃の高温条件下で形成されたシリコン窒化膜で形成されることもある。他の方法として、前記ストレスコントロール膜550はアニーリングされたPECVD SiON膜、または引張応力を有するシリコン酸化膜よりなりうる。その結果、チャンネル504a、504b、504c、504dには局部的に引張応力が与えられる。

【0098】

次いで、図27を参照すれば、デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のPMOS及びNMOSトランジスタで引張応力を選択的に緩和させる。デジタル回路領域のNMOSトランジスタ上にフォトレジストマスクパターン560を形成する。次いで、デジタル回路領域のNMOSトランジスタのみを除き、前記構造のあらゆる領域にGe、Si、As、In、Snなどのイオン、または他の類似したイオンを注入する。その結果、デジタル回路領域のPMOSトランジスタとアナログ回路領域のPMOS及びNMOSトランジスタで引張応力が緩和される。図面に矢印で示したように、イオン注入後にはデジタル回路領域のNMOSトランジスタのチャンネル504a上には引張応力が局部的に与えられ、デジタル回路領域のPMOSトランジスタのチャンネル504bには圧縮応力が局部的に与えられる。アナログ回路領域のチャンネル504c、504d上には何らの応力も与えられない。

【0099】

図28ないし図31は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第3カテゴリーに属するものである。本実施例では、デジタルトランジスタのNMOS及びPMOSトランジスタの何れにも応力を導入するために、引張応力層及び圧縮応力層を別途に形成する。図28ないし図31の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、シリサイドパターン130及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。

【0100】

図28を参照すれば、引張応力を有する第1ストレスコントロール膜650を前記構造上に形成する。前記第1ストレスコントロール膜650はLPCVDによって約20−150nmの厚さに形成されたシリコン窒化膜よりなりうる。前記第1ストレスコントロール膜650は400−800℃の高温条件下で形成されたシリコン窒化膜よりなりうる。他の方法として、前記第1ストレスコントロール膜650は、アニーリングされたPECVD SiON膜または引張応力を有するシリコン酸化膜よりなりうる。前記第1ストレスコントロール膜650を形成した結果、デジタル回路領域及びアナログ回路領域のチャンネル604a、604b、604c、604dには、図面に矢印で示したように引張応力が局部的に形成される。

【0101】

図29を参照すれば、前記第1ストレスコントロール膜650のうち、デジタル回路領域のPMOSトランジスタと、アナログ回路領域のPMOS及びNMOSトランジスタ上にある部分を除去する。デジタル回路領域のNMOSトランジスタのみを覆うフォトレジストパターン654を形成し、前記第1ストレスコントロール膜650の露出された部分を除去する。ここで、注意すべき点は、前記第1ストレスコントロール膜650としてPECVD SiON膜を使用した場合には、前記第1ストレスコントロール膜650のうち、デジタル回路領域のPMOSトランジスタと、アナログ回路領域のPMOS及びNMOSトランジスタ上にある部分を除去した後、アニーリング工程を行うことが望ましいということである。前記第1ストレスコントロール膜650を選択的に除去した結果、図面に矢印で示したように、デジタル回路領域のNMOSトランジスタのチャンネル604aにのみ引張応力が印加される状態で残る。

【0102】

図30を参照すれば、前記構造上に圧縮応力を有する第2ストレスコントロール膜660を形成する。前記第2ストレスコントロール膜660は、例えばPECVD方法によって約20−150nmの厚さに形成されたシリコン窒化膜で形成しうる。前記第2ストレスコントロール膜660は、200−400℃の低温条件下で形成されたシリコン窒化膜よりなりうる。他の方法として、前記第2ストレスコントロール膜660は、圧縮応力を有するシリコン酸化膜よりなりうる。前記第2ストレスコントロール膜660を形成した結果、図面に矢印で示したように、前記あらゆるチャンネル604a、604b、604c、604dには圧縮応力が印加され、前記チャンネル604aには圧縮応力及び引張応力が何れも印加される。

【0103】

図31を参照すれば、デジタル回路領域のPMOSトランジスタのみ除き、あらゆるトランジスタ上で前記第2ストレスコントロール膜660をストレス解除膜またはストレス緩和膜662に選択的に変換させる。デジタル回路領域のPMOSトランジスタ上にのみフォトレジストマスクパターン670を形成する。デジタル回路領域のPMOSトランジスタを覆っている前記第2ストレスコントロール膜660は除き、参照符号“672”で表示したように、Ge、Si、As、In、Snなどのイオン、または他の類似したイオンを前記第2ストレスコントロール膜660に注入する。前記イオン注入によって前記第2ストレスコントロール膜660の露出部分で圧縮応力が緩和され、前記第2ストレスコントロール膜660の露出部分がストレス解除膜またはストレス緩和膜662になる。その結果、図面に矢印で表示されたように、引張応力はデジタル回路領域のNMOSトランジスタのチャンネル604aにのみ局部的に与えられ、圧縮応力はデジタル回路領域のPMOSトランジスタのチャンネル604bにだけ局部的に与えられる。したがって、アナログ回路領域のトランジスタは印加されたストレスによる影響を受けずに、デジタル回路領域でNMOSトランジスタ及びPMOSトランジスタのパフォーマンスを何れも向上させうる。したがって、アナログ回路領域のトランジスタは、トランジスタのストレス印加によって引き起こされうるノイズにより劣化されない。

【0104】

図32は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第3カテゴリーに属するものである。図32の実施例は、図28ないし図31の実施例の変形例である。図32の実施例では、図28ないし図30に示した段階を同一に適用する。したがって、これら段階についての詳細な説明は省略する。

【0105】

図32を参照すれば、圧縮応力を有する第2ストレスコントロール膜660を形成した後、デジタル回路領域のPMOSトランジスタのみを除いてあらゆる領域で前記第2ストレスコントロール膜660を除去する。その結果、図面に矢印で表示されたように、引張応力がデジタル回路領域のNMOSトランジスタのチャンネル704aに局部的に与えられ、圧縮応力がデジタル回路領域のPMOSトランジスタのチャンネル704bに局部的に与えられる。

【0106】

以上、本発明を例示的な実施例を挙げて詳細に説明したが、本発明は前記実施例に限定されず、本発明の技術的思想及び範囲を逸脱せずに、当業者によって多様な変形が可能である。

【産業上の利用可能性】

【0107】

本発明は、デジタル、アナログ及び混合モード機能を含む回路に適用可能である。例えば、本発明はDRAM及びエンベデッドDRAMのようなメモリLSIに適用可能である。本発明の方法は、DRAMセル及び/またはノイズに敏感なアナログ回路のDRAMセンスアンプに適用可能である。本発明は、個別メモリチップまたはSRAM、フラッシュメモリ、MRAM、PRAM、及びその他の素子で構成されたエンベデッドメモリチップ構成でメモリ回路のセンスアンプ回路などの回路に適用可能である。前記回路でセンスアンプは、電流の非常に小さな差を感知せねばならず、よってこれらのパフォーマンスがフリッカノイズなどのノイズによって実質的に劣化されうるので、本発明は前記回路に特に適するように適用されうる。

【符号の説明】

【0108】

100 基板

102 STI

104a、104b、104c、104d トランジスタのチャンネル

110 ゲート絶縁膜パターン

120 導電性ゲートパターン

122 低濃度ソース/ドレーン領域

124 側壁スペーサ

126 高濃度ソース/ドレーン領域

128 ソース/ドレーン領域

130 シリサイドパターン

150 ストレスコントロール膜

152 ストレス解除膜またはストレス緩和膜

160 フォトレジストマスク

162 Ge、Si、As、In、Sbなどのイオンストレスコトロール膜

【技術分野】

【0001】

本発明は、半導体素子に係り、特に、素子パフォーマンスを向上させるために機械的なストレスエンジニアリングを採用したMOS(metal−oxide−silicon)トランジスタのようなLSI(Large Scale Integration)半導体素子に関する。

【背景技術】

【0002】

MOSトランジスタのキャリア移動度は、素子の電力消耗及びスイッチングパフォーマンスに大きな影響力を有する。キャリア移動度を向上させることによって、スイッチング速度を速めることができ、低電圧での動作が可能となって、電力消耗を減少させうる。

【0003】

MOSトランジスタでキャリア移動度を向上させるために機械的ストレスエンジニアリングが採用された(例えば、特許文献1参照)。チャンネル領域での引張応力は、NMOSトランジスタでは、電流増加を招くが、PMOSトランジスタでは電流減少を招くことになる。チャンネル領域での圧縮応力は、PMOSトランジスタでは電流増加を招くが、NMOSトランジスタでは電流減少を招くことになる。

【0004】

図1は、素子でのキャリア移動度を向上させるために、機械的ストレスを導入するための方法を説明するNOS素子の概略的な断面図である。基板10に形成された素子は、基板10内に形成された素子分離領域12によって素子分離されている。トランジスタ素子は、基板10に形成されたソース/ドレーン領域22、26を含み、これらの間にチャンネル領域18が限定される。ゲート構造は、基板10上に形成されたゲート絶縁膜14と、前記ゲート絶縁膜14上にある導電性ゲート層20と、前記導電性ゲート層20上に形成されたシリサイド層30と、を含む。ゲート構造の両側壁には、絶縁側壁スペーサ24が形成されている。

【0005】

前記ゲート構造の上と前記ソース/ドレーン領域26及び基板10の上面に形成されたストレスコントロール層40によって前記チャンネル18に機械的ストレスが導入される。特に、図1に矢印で表示したように、MOSトランジスタ構造に引張応力が導入される。図1に矢印で表示されたような引張応力を前記チャンネル18に導入するための他の方法は、ソース/ドレーン領域22、26にシリサイド領域30を形成することである。シリサイド化工程を進行させた後、シリサイド領域30はシリサイドにより置換される前の元のソース/ドレーン材料より小さい体積を占めるためにチャンネル18に引張応力が導入される。

【0006】

機械的ストレスをMOSトランジスタに導入すれば、キャリア移動度を向上させる以外に、電気的ノイズ、特にフリッカノイズが導入されることによって、素子のパフォーマンスが劣化するということが分かった。通常、“1/fノイズ”とも称されるフリッカノイズは、そのパワースペクトルP(f)が、P(f)=1/fa(式中、aは1に非常に近い)によって挙動する周波数fの関数で表示されるノイズの一種である。また、フリッカノイズは、大部分のノイズパワーが周波数スペクトルの下端に集中するので、“ピンクノイズ”とも称される。フリッカノイズは、キャリアのトラッピング及びデトラッピング(detrapping)だけでなく、トラップされた電荷によるキャリア分散を通じた移動度変調により引き起こされると見なされている。フリッカノイズ劣化は、低周波アナログ回路及び高性能デジタル回路のいずれについても重要な因子となりうる。フリッカノイズは相対的に低周波で発生するが、そのノイズは、高周波スペクトルまでアップコンバータ(up−converter)に変換されて振動のコヒーレンシを劣化させうるので、一部のRF回路については非常に重要な因子である。

【0007】

図2A及び図2Bは、MOS素子でのストレスエンジニアリングとノイズとの関係を表すグラフである。図2Aは、ストレスが付加されたトランジスタとストレスが減少したトランジスタのノイズパワーSvg分布グラフである。この測定は、NMOS素子に対しては、Vd=0.05V及びVg=0.85Vで、そしてPMOS素子についてはVd=−0.05V及びVg=−0.85Vでなされた。図2Bは、CMOS素子のノイズパワー比対最大トランスコンダクタンス(Gmmax)改善率のグラフである。図2Bのグラフィックは、MOS素子での引張応力及び圧縮応力は、何れもフリッカノイズの観点でパフォーマンスを劣化させることを表す。

【0008】

したがって、MOSトランジスタにストレスエンジニアリングを与えれれば、MOSトランジスタのパフォーマンスが向上するが、フリッカノイズ特性は劣化する。すなわち、NMOS及びPMOS素子のいずれにおいても、引張応力及び圧縮応力は、素子のパフォーマンスを向上させるが、これら二素子のフリッカノイズ特性は劣化する。したがって、フリッカノイズ特性が考慮される場合、特にアナログ用、RF用及び混合信号用、例えばシステムLSI用などにおいては、ストレスエンジニアリングがあらゆる回路のパフォーマンスを向上させるに当って、常に許容されうる手段ではない。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許第6,573,172号明細書

【特許文献2】特開2003−086708号公報

【特許文献3】特開昭62−013061号公報

【特許文献4】特開平11−238799号公報

【特許文献5】特開2000−216377号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の特徴は、混合信号応用素子を有するLSI素子のような半導体素子、前記半導体素子のレイアウト、及びその素子を製造するための方法を提供することであり、ここで、引張応力及び/または圧縮応力を素子の他の領域、すなわち、アナログ領域及びデジタル領域に選択的に印加して素子のパフォーマンスを向上させると同時に、素子のパフォーマンスに及ぼすフリッカノイズの影響を減少させる。

【課題を解決するための手段】

【0011】

一態様において、本発明は、回路製造方法に関するものである。複数の回路領域内に複数の導電型を有し、複数の動作モードで動作する複数の素子を形成する。前記素子の動作モードに基づいて選択された少なくとも1つの素子に機械的ストレスを印加する。

【0012】

前記動作モードは、アナログモード及びデジタルモードを含みうる。また、前記動作モードは、ノイズに敏感なモード及びノイズに敏感でないモード、低速動作モード及び高速動作モード、そして高電圧動作モード及び低電圧動作モードを含みうる。

【0013】

一実施例において、前記素子は、少なくとも1つのPMOS素子及び/または少なくとも1つのNMOS素子を含む。前記素子は、少なくとも1つのCMOS素子を含みうる。

【0014】

一実施例において、前記機械的ストレスはデジタルモードのNMOS素子のチャンネルに印加される。一実施例において、前記機械的ストレスは、デジタルモードのPMOS素子のチャンネルに印加される。

【0015】

一実施例において、電気的なノイズ増加を防止するためにアナログモードで動作する素子にはストレスを印加しない。前記電気的なノイズはフリッカノイズでありうる。

【0016】

一実施例において、前記少なくとも1つの選択された素子に機械的ストレスを印加する段階は、前記素子に近接して前記回路にストレスコントロール膜を形成する段階を含む。前記ストレスコントロール膜は、引張応力及び/または圧縮応力を印加しうる。一実施例において、ストレスが印加されていない素子に近接して、前記ストレスコントロール膜でストレスを緩和する。前記ストレスコントロール膜でストレスを緩和するために、前記ストレスコントロール膜にイオン注入を行う。前記ストレスコントロール膜でストレスを緩和するために、前記ストレスコントロール膜の一部を選択的に除去することもある。前記ストレスコントロール膜は、SiN、SiONまたはSiO2を含みうる。前記ストレスコントロール膜形成段階は、アニーリング段階を含みうる。前記ストレスコントロール膜は、PECVD(plasma−enhanced chemical vapor deposition)及び/またはLPCVD(low−pressure chemical vapor deposition)方法で形成しうる。

【0017】

一実施例において、前記少なくとも1つの選択された素子に機械的ストレスを印加する段階は、前記回路上でシリサイド化工程を行う段階を含みうる。一実施例において、前記少なくとも1つの選択された素子に機械的ストレスを印加する段階は、前記回路上にキャッピング層を形成する段階と、ストレスが印加される素子に近接して前記キャッピング層を選択的に除去する段階と、ストレスが印加される素子にストレスを印加するために第2シリサイド化工程を行う段階とをさらに含む。

【0018】

一実施例において、前記少なくとも1つの選択された素子に機械的ストレスを印加する段階は、ストレスが印加される素子にソース/ドレーン構造をエピタキシャル成長させる段階を含む。

【0019】

一実施例において、第1CMOS構造の第1素子と、第1CMOS構造の第2素子とにストレスが印加される。第2CMOS構造の第1素子と、第2CMOS構造の第2素子とにストレスが印加されない。一実施例において、前記第1CMOS構造はデジタルモードで動作し、前記第2CMOS構造はアナログモードで動作する。一実施例において、前記第1CMOS構造の第1素子はPMOS素子であり、前記第1CMOS構造の第2素子はNMOS素子であり、前記PMOS素子は、そのチャンネルに印加される圧縮応力を有し、前記NMOS素子はそのチャンネルに印加される引張応力を有する。一実施例において、前記第1CMOS構造及び第2CMOS構造において、前記第1素子は何れもPMOS素子である。一実施例において、前記第1CMOS構造及び第2CMOS構造において、前記第2素子は何れもNMOS素子である。

【0020】

一実施例において、前記機械的ストレスを印加する段階は、前記素子に引張応力を印加する第1ストレスコントロール膜を前記回路上に形成する段階と、引張応力が印加されていない素子に近接して前記第1ストレスコントロール膜を選択的に除去する段階と、前記素子に圧縮応力を与える第2ストレスコントロール膜を前記素子上に形成する段階と、前記素子の選択された部分に近接して前記第2ストレスコントロール膜上にストレス緩和膜を形成する段階と、前記ストレス緩和膜を用いて圧縮応力が印加されていない素子でストレスを緩和させる段階と、を含む。前記圧縮応力が印加されない素子でストレスを緩和する段階は、前記ストレス緩和膜内にイオンを注入する段階を含む。

【0021】

一実施例において、前記機械的ストレスを印加する段階は、前記素子に引張応力を印加する第1ストレスコントロール膜を前記回路上に形成する段階と、引張応力が印加されない素子に近接して前記第1ストレスコントロール膜を選択的に除去する段階と、前記素子に圧縮応力を印加する第2ストレスコントロール膜を前記素子上に形成する段階と、圧縮応力が印加されない素子に近接して前記第2ストレスコントロール膜を選択的に除去する段階と、を含む。

【0022】

本発明の他の態様によれば、本発明は回路に関するものである。本発明に係る回路は、複数の回路領域内で複数の導電型を有して複数の動作モードで動作する複数の素子が形成された基板を含む。前記複数の素子のうち、選択される少なくとも1つの素子はその素子に印加された機械的ストレスを有し、前記選択された素子はその動作モードに基づいて選択される。

【0023】

前記動作モードは、アナログモード及びデジタルモードを含みうる。また、前記動作モードは、ノイズに敏感なモード及びノイズに敏感でないモード、低速動作モード及び高速動作モード、そして高電圧動作モード及び低電圧動作モードを含みうる。

【0024】

一実施例において、前記素子は少なくとも1つのPMOS素子及び/または少なくとも1つのNMOS素子を含む。前記素子は少なくとも1つのCMOS素子を含みうる。

【0025】

一実施例において、前記機械的ストレスはデジタルモードのNMOS素子のチャンネルに印加される。一実施例において、前記機械的ストレスはデジタルモードのPMOS素子のチャンネルに印加される。

【0026】

一実施例において、電気的なノイズ増加を防止するためにアナログモードで動作する素子にはストレスが印加されない。前記電気的なノイズはフリッカノイズでありうる。

【0027】

一実施例において、前記機械的ストレスは、前記素子に近接して前記回路上に形成されたストレスコントロール膜を用いて前記選択された素子に印加される。前記ストレスコントロール膜は、引張応力及び/または圧縮応力を印加しうる。一実施例において、ストレスが印加されていない素子に近接して前記ストレスコントロール膜でストレスが緩和される。前記ストレスコントロール膜のうち、ストレスが緩和された部分は追加で注入されたイオンを含みうる。一実施例において、前記ストレスコントロール膜はストレスが印加されていない素子に近接して存在しない。前記ストレスコントロール膜は、SiN、SiON及び/またはSiO2を含みうる。一実施例において、前記ストレスコントロール膜は、アニーリングされる。一実施例において、前記ストレスコントロール膜はPECVDまたはLPCVDによって形成される膜である。

【0028】

一実施例において、前記機械的ストレスを印加する手段はシリサイドを含む。

【0029】

一実施例において、前記機械的ストレスを印加する手段はエピタキシャル成長されたソース/ドレーン構造を含む。

【0030】

一実施例において、第1CMOS構造の第1素子と、第1CMOS構造の第2素子にストレスが印加されており、第2CMOS構造の第1素子と、第2CMOS構造の第2素子にストレスが印加されていない。一実施例において、前記第1CMOS構造は、デジタルモードで動作し、前記第2CMOS構造はアナログモードで動作する。一実施例において、前記第1CMOS構造の第1素子はPMOS素子であり、前記第1CMOS構造の第2素子はNMOS素子であり、前記PMOS素子はそのチャンネルに印加される圧縮応力を有し、前記NMOS素子はそのチャンネルに印加される引張応力を有する。一実施例において、前記第1CMOS構造及び第2CMOS構造において前記第1素子は何れもPMOS素子である。一実施例において、前記第1CMOS構造及び第2CMOS構造において前記第2素子は何れもNMOS素子である。

【0031】

一実施例において、前記機械的ストレスを印加する手段は、前記素子に引張応力を印加し、前記引張応力が印加される素子に近接した位置にのみ存在するように前記回路上に形成されている第1ストレスコントロール膜と、前記素子に圧縮応力を与えるように前記素子上に形成されている第2ストレスコントロール膜と、前記素子の選択された部分に近接して前記第2ストレスコントロール膜上に形成されており、圧縮応力を必要としない素子でストレスを緩和するストレス緩和膜とを含む。一実施例において、前記ストレス緩和膜は追加で注入されたイオンを含む。

【0032】

一実施例において、前記機械的ストレスを印加する手段は、前記素子に引張応力を印加し、前記引張応力が印加される素子に近接した位置にのみ存在するように前記回路上に形成されている第1ストレスコントロール膜と、前記素子に圧縮応力を印加し、前記圧縮応力が印加される素子に近接した位置にのみ存在するように前記素子上に形成されている第2ストレスコントロール膜と、を含む。

【0033】

本発明の他の態様によれば、本発明は回路製造方法に関するものである。本発明に係る方法では回路の第1領域に第1導電型の第1MOS素子を形成する。前記回路の第2領域に第1導電型の第2MOS素子を形成する。前記第1及び第2MOS素子のチャンネルにストレスを印加する。前記第2MOS素子のチャンネルでストレスを緩和する。

【0034】

一実施例において、前記第1及び第2MOS素子に近接して前記回路上にストレスコントロール膜が形成される。前記ストレスコントロール膜は、前記第1及び第2MOS素子にストレスを印加する。前記ストレスコントロール膜はLPCVD方法によって形成しうる。また、前記ストレスコントロール膜は、PECVD方法によって形成しても良い。前記ストレスコントロール膜は、低温で形成されたSiNを含みうる。一実施例において、前記ストレスを緩和する段階は、前記ストレスコントロール膜にイオンを注入する段階を含む。前記ストレスコントロール膜はSiNを含みうる。

【0035】

一実施例において、前記ストレスは圧縮応力である。一実施例において、前記ストレスは引張応力である。

【0036】

本発明の他の態様によれば、本発明は回路製造方法に関するものである。本発明に係る方法では、回路の第1領域に第1導電型の第1MOS素子を形成する。前記回路の第2領域に第1導電型の第2MOS素子を形成する。前記第1MOS素子のチャンネルにストレスを印加する。

【0037】

一実施例において、前記第1MOS素子のチャンネルにストレスを印加する段階は、前記第1及び第2MOS素子に近接して前記回路上にストレスコントロール膜を形成する。前記ストレスコントロール膜はPECVDによって形成しうる。前記ストレスコントロール膜はSiONを含みうる。前記ストレスコントロール膜はSiO2よりなりうる。

【0038】

一実施例において、本発明に係る方法は、前記第2MOS素子からストレスコントロール膜を除去し、前記第1MOS素子上に前記ストレスコントロール膜の一部を残す段階をさらに含む。一実施例において、前記第1MOS素子上のストレスコントロール膜部分をアニーリングする段階をさらに含む。

【0039】

一実施例において、本発明に係る方法は、前記第1及び第2MOS素子に近接して第1相のシリサイドを形成するために第1熱処理を行う段階をさらに含む。前記第1及び第2MOS素子と前記第1相のシリサイド上にキャッピング層が形成されうる。前記第1MOS素子及び第1相のシリサイド上で前記キャッピング層の一部を除去しうる。前記第1相のシリサイドを第2相のシリサイドに転換させるために第2熱処理を行える。

【0040】

一実施例において、前記ストレスは圧縮応力である。一実施例において、前記ストレスは引張応力である。

【0041】

本発明の他の態様によれば、本発明は回路製造方法に関するものである。本発明の方法によれば、回路の第1領域に第1導電型の第1MOS素子及び第2導電型の第2MOS素子を含む第1CMOS素子を形成する。前記回路の第2領域に第1導電型の第3MOS素子及び第2導電型の第4MOS素子を含む第2CMOS素子を形成する。前記第1及び第2MOS素子のうち、何れか1つのチャンネルに引張応力を印加し、前記第1及び第2MOS素子のうち、他の1つに圧縮応力を印加する。前記第1領域でMOS素子のチャンネルにストレスが印加されたならば、前記第2領域でMOS素子のチャンネルに印加されたストレスを除去する。

【0042】

一実施例において、本発明による方法は、前記第1及び第2MOS素子のうち、何れか1つのソース/ドレーン領域とゲート上に半導体層をエピタキシャル成長させ、前記第1及び第2MOS素子のうち、何れか1つに圧縮応力を印加する段階をさらに含む。前記第1及び第2MOS素子のうち、他の1つの上にストレスコントロール膜を形成して前記第1及び第2MOS素子のうち、他の1つに引張応力を印加する。

【0043】

一実施例において、前記第1及び第2MOS素子のうち、何れか1つに引張応力を印加する第1ストレスコントロール膜を前記第1及び第2MOS素子のうち、何れか1つの上に形成する。一実施例において、前記第1ストレスコントロール膜はSiN、SiON、及びSiO2のうち、少なくとも何れか1つを含む。前記第1及び第2MOS素子のうち、他の1つに圧縮応力を印加する第2ストレスコントロール膜を前記第1及び第2MOS素子のうち、他の1つの上に形成しうる。一実施例において、前記第2ストレスコントロール膜はSiN及びSiO2のうち、少なくとも何れか1つを含む。

【0044】

本発明の他の態様によれば、本発明は回路に関するものである。本発明に係る回路は回路の第1領域に形成された第1導電型の第1MOS素子と、前記回路の第2領域に形成された第1導電型の第2MOS素子とを含む。前記第1MOS素子のチャンネルにはストレスが印加されており、前記第2MOS素子にはストレスが印加されていない。

【0045】

一実施例において、前記第1MOS素子上にストレスコントロール膜が形成されており、前記ストレスコントロール膜は前記第1MOS素子にストレスを印加する。一実施例において、前記ストレスコントロール膜はその内部に注入されているイオンをさらに含む。一実施例において、前記ストレスコントロール膜はSiNよりなる。一実施例において、前記ストレスコントロール膜はSiONよりなる。一実施例において、前記ストレスコントロール膜はSiO2よりなる。一実施例において、前記ストレスは圧縮応力である。一実施例において、前記ストレスは引張応力である。

【0046】

一実施例において、本発明に係る回路は、前記第1MOS素子のソース/ドレーン構造に近接した第2相のシリサイドをさらに含む。

【0047】

本発明の他の態様によれば、本発明は回路に関するものである。本発明に係る回路は、回路の第1領域に形成され、第1導電型の第1MOS素子及び第2導電型の第2MOS素子を含む第1CMOS素子と、前記回路の第2領域に形成されて第1導電型の第3MOS素子及び第2導電型の第4MOS素子を含む第2CMOS素子を含む。前記第1及び第2MOS素子のうち、何れか1つのチャンネルには引張応力が印加されており、前記第1及び第2MOS素子のうち、他の1つには圧縮応力が印加されている。

【0048】

一実施例において、本発明に係る回路は、前記第1及び第2MOS素子のうち、何れか1つに圧縮応力を印加できるように、前記第1及び第2MOS素子のうち、何れか1つのソース/ドレーン領域とゲート上とにエピタキシャル成長されている半導体層をさらに含む。

【0049】

一実施例において、本発明に係る回路は、前記第1及び第2MOS素子のうち、他の1つに引張応力を印加できるように前記第1及び第2MOS素子のうち、他の1つの上に形成されたストレスコントロール膜をさらに含む。

【0050】

一実施例において、前記第1及び第2MOS素子のうち、何れか1つの上に形成されている第1ストレスコントロール膜をさらに含む。前記第1ストレスコントロール膜は前記第1及び第2MOS素子のうち、何れか1つに引張応力を印加する。一実施例において、前記第1ストレスコントロール膜は、SiN、SiON、及びSiO2のうち、少なくとも何れか1つを含む。一実施例において、本発明に係る回路は、前記第1及び第2MOS素子のうち、他の1つの上に形成されている第2ストレスコントロール膜をさらに含む。前記第2ストレスコントロール膜は、前記第1及び第2MOS素子のうち、他の1つに圧縮応力を印加する。前記第2ストレスコントロール膜はSiN及びSiO2のうち、少なくとも何れか1つを含みうる。

【発明の効果】

【0051】

本発明によれば、特定の素子の要求される動作構成によって前記素子にストレスエンジニアリングを選択的に適用する。すなわち、素子の導電型、すなわちn型またはp型はもとより、それらの動作による役割、例えばアナログ/デジタル、低電圧/高電圧、高速/低速、ノイズ敏感如何などに基づいて素子、すなわちNMOS及び/またはPMOS素子で適切な応力、すなわち引張応力または圧縮応力を印加及び/または除去しうる。

【図面の簡単な説明】

【0052】

【図1】素子でキャリア移動度を向上させるために機械的ストレスを導入する方法を説明するMOS素子の概略的な断面図である。

【図2A】MOS素子でのストレスエンジニアリングとノイズとの関係を説明するグラフである。

【図2B】MOS素子でのストレスエンジニアリングとノイズとの関係を説明するグラフである。

【図3】本発明によって素子を形成する一方法を説明するフローチャートであって、素子に及ぼすノイズの影響は減少させつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に適用する方法を説明するフローチャートである。

【図4】本発明によって素子を形成する他の方法を説明するフローチャートであって、素子に及ぼすノイズの影響は減少させつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に適用する方法を説明するフローチャートである。

【図5】本発明によって素子を形成するさらに他の方法を説明するフローチャートであって、素子に及ぼすノイズの影響は減少させつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に適用する方法を説明するフローチャートである。

【図6】本発明の一実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図7】本発明の一実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図8】本発明の一実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図9】本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図10】本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図11】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図12】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図13】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図14】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図15】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図16】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図17】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図18】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図19】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図20】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図21】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図22】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図23】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図24】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図25】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図26】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図27】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図28】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図29】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図30】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図31】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【図32】本発明のさらに他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。

【発明を実施するための形態】

【0053】

本発明の前記及び他の特徴及び利点は添付図面に示されたような本発明の望ましい実施例のさらに具体的な説明からさらに明白になる。添付図面は、本発明の原理を説明するために必要に応じて強調して示した。図面において同じ符号は同じ要素を示す。

【0054】

本発明によれば、混合信号応用素子、例えばアナログ及びデジタル応用素子を有するLSI素子のような半導体素子、その半導体素子のレイアウト、及びその素子の製造方法を提供し、ここで引張応力及び/または圧縮応力を素子の異なる領域、すなわちアナログ領域及びデジタル領域に選択的に印加して素子のパフォーマンスを向上させると同時に、素子のパフォーマンスに及ぼすフリッカノイズの影響を減少させる。

【0055】

次いで、本発明の実施例を詳細に説明する。次の実施例は3つの実施例カテゴリーのうち、何れか1つに属すると考慮されうる。ここで、各カテゴリーは、素子に及ぼすノイズの影響を制限しつつ、パフォーマンスを向上させるように素子にストレスエンジニアリングを選択的に適用する方法で区分される。図3ないし図5は、各々本発明の実施例の3つのカテゴリーを説明するフローチャートである。これらカテゴリーは、本発明を制限するものと解釈されてはならない。これらカテゴリーは、説明をさらに明確にし、かつ本発明の理解を容易にするためのものでのみ理解されねばならない。

【0056】

図3は、本発明によって素子を形成する1つの方法を説明するフローチャートであって、ここでは素子に及ぼすノイズの影響は減らしつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に印加する。

【0057】

図3を参照すれば、段階52で、第1導電型、すなわちn型またはp型の第1MOS素子を素子の第1領域、例えば、デジタル領域、すなわちデジタル回路が形成される素子領域に形成する。第1導電型、すなわちn型またはp型の第2MOS素子を素子の第2領域、例えばアナログ領域、すなわちアナログ回路が形成される素子領域に形成する。段階54で、第1及び第2領域に第1及び第2MOS素子のチャンネルに局部的応力を選択的に印加するためにストレスエンジニアリングを印加する。段階56において、前記第2領域で第2MOS素子のチャンネルから応力を解除または緩和する。

【0058】

前記方法によって第1MOS素子のチャンネルにのみ応力が印加される。応力が与えられた第1MOS素子は印加された応力の結果としてパフォーマンスが向上されうるが、ノイズが増加されることもある。一方、第2MOS素子は、局部的応力が印加されていないために、フリッカノイズによる効果が減少しうる回路が得られる。この方法は、前記第1領域が前記第2領域に比べてノイズに対して敏感でない場合のような状況で適用されうる。例えば、前記第1領域は、デジタル回路、低電圧動作用回路及び/またはノイズに敏感でない回路を含むことができ、前記第2領域はアナログ回路、高電圧動作用回路及び/またはノイズに敏感な回路を含みうる。

【0059】

一実施例において、ストレスコントロール膜を形成することによって局部的応力を前記第1領域及び第2領域の両側に何れも印加しうる。前記第1MOS素子での応力を緩和するために、イオン注入を用いるか、前記ストレスコントロール膜の一部を前記第2MOS素子上で除去する。次いで、本発明に係る前記第1カテゴリーまたは第1グループの特定実施例をさらに詳細に説明する。

【0060】

図4は、本発明によって素子を形成する他の方法を説明するフローチャートであって、ここでは、素子に及ぼすノイズの影響は減らしつつ、素子パフォーマンスを向上させるために素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に印加する。図4は本発明の第2カテゴリーを説明する。

【0061】

図4を参照すれば、段階62で、第1導電型、すなわちn型またはp型の第1MOS素子を素子の第1領域、例えばデジタル領域、すなわちデジタル回路が形成される領域に形成する。前記第1導電型、すなわちn型またはp型の第2MOS素子を素子の第2領域、例えばアナログ領域、すなわち、アナログ回路が形成される領域に形成する。段階64において、前記第1領域で前記第1MOS素子のチャンネルに局部的応力を選択的に印加するためにストレスエンジニアリングを適用する。

【0062】

前記方法によって前記第1MOS素子のチャンネルにのみ応力が印加される。応力が印加された前記第1MOS素子は、印加された応力によって向上したパフォーマンス特性を有するが、これに伴って増加したノイズを有することもある。一方、前記第2MOS素子は、局部的応力が印加されていないためにフリッカノイズによる影響を減らしうる。この方法は、前記第1領域が第2領域よりノイズに敏感ではない場合に適用しうる。例えば、前記第1領域はデジタル回路、低電圧動作用回路及び/またはノイズに敏感でない回路を含み、前記第2領域はアナログ回路、高電圧動作用回路及び/またはノイズに敏感な回路を含みうる。

【0063】

本発明に係る前記第2カテゴリーまたは第2グループの特定実施例を次にさらに詳細に説明する。

【0064】

図5は、本発明によって素子を形成する他の方法を説明するフローチャートであって、ここでは素子に及ぼすノイズの影響は減らしつつ、素子パフォーマンスを向上させるために、素子の1つまたはそれ以上の選択された領域にストレスエンジニアリングを選択的に印加する。図5は本発明の第3カテゴリーを説明する図面である。

【0065】

図5を参照すれば、段階66で、第1導電型、すなわちn型またはp型の第1MOS素子と、第2導電型、すなわちp型またはn型の第2MOS素子を含む第1CMOS素子を素子の第1領域、例えばデジタル領域、すなわちデジタル回路が形成される領域に形成する。第1導電型、すなわちn型またはp型の第1(第3)MOS素子と、第2導電型、すなわちp型またはn型の第2(第4)MOS素子を含む第2CMOS素子を素子の第2領域、例えばアナログ領域、すなわち、アナログ回路が形成される領域に形成する。段階68で、前記第1及び第2CMOS領域で前記第1及び第2MOS素子の少なくとも1チャンネルに局部的引張応力及び局部的圧縮応力を選択的に印加するためにストレスエンジニアリングを適用する。段階70で、第2CMOS素子のMOS素子のチャンネルで応力を解除または緩和する。

【0066】

前記方法によって、前記第1CMOS素子の第1及び/または第2MOS素子のチャンネルにのみ応力が印加される。応力が印加された前記第1CMOS素子は印加された応力によって向上したパフォーマンス特性を有するが、これに伴って増加したノイズを有することもある。一方、前記第2CMOS素子は、局部的応力が印加されていないために、フリッカノイズによる影響を減らしうる。この方法は、前記第1領域が第2領域よりノイズに敏感ではない場合に適用しうる。例えば、前記第1領域はデジタル回路、低電圧動作用回路及び/またはノイズに敏感でない回路を含み、前記第2領域はアナログ回路、高電圧動作用回路及び/またはノイズに敏感な回路を含みうる。

【0067】

図6ないし図8は、本発明の一実施例に係る半導体素子の形成方法を説明する概略的な断面図である。本実施例は前述した実施例の第1カテゴリーに属するものである。

【0068】

図6を参照すれば、例えばシリコンよりなる基板100を準備する。素子はデジタル回路領域及びアナログ回路領域を含む。デジタル回路領域及びアナログ回路領域は各々第1NMOSトランジスタ及び第1PMOSトランジスタを含む。素子分離のためにSTI(shallow trench isolation)102が基板100に形成されている。各トランジスタは、ソース/ドレーン領域128を含み、これらは各々低濃度ソース/ドレーン領域122及び高濃度ソース/ドレーン領域126を含む。各トランジスタの基板上にはゲート絶縁膜パターン110が形成されている。各トランジスタで各ゲート絶縁膜パターン110上には導電性ゲートパターン120が形成されており、各導電性ゲートパターン120及びソース/ドレーン領域128、特に高濃度ソース/ドレーン領域126の露出領域上には各々シリサイドパターン130が形成されている。前記シリサイドパターン130は、例えばコバルトシリサイド、ニッケルシリサイド、チタンシリサイド、またはタングステンシリサイドで形成しうる。前記ゲート絶縁膜パターン110、導電性ゲートパターン120及びシリサイドパターン130を含むあらゆるゲート構造の両側壁には側壁スペーサ124が形成されている。一実施例において、アナログ回路領域ではトランジスタゲート構造とSTI102との距離、すなわちd1、d2、d3及びd4は1.5μm以上になることが望ましい。

【0069】

図7を参照すれば、前記構造上にストレスコントロール膜150を形成する。図面に矢印で表示されたように、前記ストレスコントロール膜150は、トランジスタのチャンネル104a、104b、104c、104dに圧縮応力を印加する。前記ストレスコントロール膜150はPECVD(plasma enhanced chemical vapor deposition)により約20−150nmの厚さに形成されたシリコン窒化膜(SiN膜)よりなりうる。また、200−400℃の低温条件下で形成されたシリコン窒化膜、または圧縮応力を有するシリコン酸化膜を使用しても良い。

【0070】

図8を参照すれば、デジタル回路領域のNMOSトランジスタとアナログ回路領域のNMOS及びPMOSトランジスタ上で圧縮応力を選択的に緩和する。フォトレジストマスク160をデジタル回路領域のPMOSトランジスタだけを覆うように形成する。前記フォトレジストマスク160をイオン注入マスクとして使用して参照符号“162”で表示したように、Ge、Si、As、In、Sbなどのイオンをストレスコントロール膜150内に注入する。一実施例において、前記ストレスコントロール膜150の厚さを考慮して、イオン注入エネルギーを20−100KeVの範囲に調節し、注入されたイオンが実質的に前記シリサイドパターン130内に注入されることを防止することが望ましい。

【0071】

イオン注入の結果、デジタル回路領域のPMOSトランジスタを除外したあらゆる領域で前記ストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換される。したがって、デジタル回路領域のPMOSトランジスタのチャンネル104bにだけ圧縮応力が印加される状態に残る。その結果、デジタル回路領域のPMOSトランジスタでは、パフォーマンスが向上する。デジタル回路領域のNMOSトランジスタ及びアナログ回路領域のNMOS及びPMOSトランジスタ領域上には応力が残っていないために、これら素子のフリッカノイズ特性が劣化されない。すなわち、本実施例ではデジタル回路領域でのPMOS素子でのみパフォーマンスの向上のためにPECVDシリコン窒化膜よりなるストレスコントロール膜が使われる。

【0072】

図9及び図10は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第1カテゴリーに属するものである。図9及び図10の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、シリサイドパターン130及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。

【0073】

図9を参照すれば、前記構造上に引張応力を印加するストレスコントロール膜250を形成する。前記ストレスコントロール膜250は、LPCVDによって約20−150nmの厚さに形成されたシリコン窒化膜よりなりうる。他の例として、前記ストレスコントロール膜250は、400−800℃の高温条件下で形成されたシリコン窒化膜で形成されることもある。また、前記ストレスコントロール膜250はPECVDによってシリコン酸化窒化膜(SiON膜)を形成した後、アニーリング段階を経て得られる。他の方法として、前記ストレスコントロール膜250は引張力を印加するシリコン酸化膜で形成しうる。結果的に、得られる引張応力は、図9で矢印で示したように、トランジスタのチャンネル204a、204b、204c、204dに局部的に影響が及ぼす。

【0074】

図10を参照すれば、デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のPMOS及びNMOSトランジスタ上で引張応力を選択的に緩和する。フォトレジストマスク260をデジタル回路領域のNMOSトランジスタだけ覆うように形成する。前記フォトレジストマスク260をイオン注入マスクとして使用して参照符号“262”と表示したように、Ge、Si、As、In、Sbなどのイオンをストレスコントロール膜250内に注入する。一実施例において、前記ストレスコントロール膜250の厚さを考慮し、イオン注入エネルギーを20−100KeVの範囲に調節し、注入されたイオンが実質的に前記シリサイドパターン130内に注入されることを防止することが望ましい。

【0075】

イオン注入の結果、デジタル回路領域のNMOSトランジスタを除外したあらゆる領域で前記ストレスコントロール膜250はストレス解除膜またはストレス緩和膜252に変換される。したがって、デジタル回路領域のNMOSトランジスタのチャンネル204bにだけ引張応力が印加される状態に残る。その結果、デジタル回路領域のNMOSトランジスタでは、パフォーマンスが向上する。デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のNMOS及びPMOSトランジスタ領域上には応力が残っていないために、これら素子のフリッカノイズ特性が劣化されない。すなわち、本実施例ではデジタル回路領域でのNMOS素子でのみパフォーマンス向上のためにLPCVDシリコン窒化膜よりなるストレスコントロール膜が使われる。

【0076】

図11及び図13は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は前記実施例のうち、第2カテゴリーに属するものである。図11ないし図13の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、シリサイドパターン130及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。

【0077】

図11を参照すれば、前記構造上に応力を持たないストレスコントロール膜350を形成する。前記ストレスコントロール膜350は、PECVDによって約20−150nmの厚さに形成されたシリコン酸化窒化膜よりなりうる。

【0078】

図12を参照すれば、デジタル回路領域でNMOSトランジスタ上にのみフォトレジストパターン360を形成する。次いで、前記フォトレジストパターン360をマスクとして使用してデジタル回路領域のNMOSトランジスタを除外したあらゆる領域で前記ストレスコントロール膜350を除去する。

【0079】

次いで、図13を参照すれば、前記フォトレジストパターン360を除去し、前記ストレスコントロール膜350の残余部分をアニーリングする。アニーリングの結果、前記ストレスコントロール膜350は引張応力膜352に変換され、これは図面で矢印で表示したようにデジタル回路領域でNMOSトランジスタのチャンネル304aに引張応力を印加する。残りのトランジスタのチャンネル304b、304c、304dは、それらの各トランジスタ領域に引張応力膜352がないので、何らの応力も受けない。

【0080】

このように、本実施例ではデジタル回路領域でNMOSトランジスタのチャンネル304aに引張応力が局部的に付与される。その結果、デジタル回路領域のNMOSトランジスタではパフォーマンスが向上する。デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のNMOS及びPMOSトランジスタ領域上には応力が残っていないために、これら素子のフリッカノイズ特性が劣化されない。すなわち、本実施例ではデジタル回路領域でのNMOS素子でのみパフォーマンスの向上のために引張応力を有するアニーリングされたPECVDシリコン酸化窒化膜を使用する。

【0081】

図14ないし図16は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は前記実施例のうち、第2カテゴリーに属するものである。図14ないし図16の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。図14ないし図16の実施例では、NMOSパフォーマンスを向上させるために引張応力を有するアニーリングされたPECVDシリコン二酸化膜(SiO2膜)が形成される。

【0082】

図14を参照すれば、前記構造上にSiO2膜450を形成する。前記SiO2膜450は約600℃以下の温度下でPECVD方法によって約20−100nmの厚さに形成しうる。

【0083】

図15を参照すれば、アナログ回路領域のNMOSトランジスタ上のSiO2膜450部分を除去する。次いで、前記SiO2膜450を900−1150℃の温度でアニーリングして前記SiO2膜450から引張応力を誘導し、それにより、デジタル回路領域のNMOSトランジスタから引張応力を誘導する。ここで、注意すべき点は、アナログ回路領域のNMOSトランジスタには応力印加を防止することが望ましいので、アナログ回路領域のNMOSトランジスタでは前記SiO2膜450を除去する。PMOSトランジスタ上にあるSiO2膜450は除去する必要がない。その理由は、SiO2膜をアニーリングすれば、PMOSトランジスタには影響を及ぼさないからである。例えば、高い引張応力を有するCVD SiO2膜の高温アニーリングの影響によってAsイオン注入されたポーリシリコン(典型的にNMOSゲートに使われる)には圧縮応力が誘導されると知られている。したがって、アニーリング後には図面で矢印で表示したように、デジタル回路領域で、NMOSトランジスタのチャンネル404aに印加された引張応力と、ゲート120に印加された圧縮応力とが存在する。

【0084】

次いで、図16を参照すれば、後続工程、例えば素子のソース/ドレーン領域のシリサイド化のような工程を進行するように、前記SiO2膜450の残りの部分を除去しうる。しかし、前記SiO2膜450の残りの部分は必ずしも除去する必要はない。前記SiO2膜450が完全に除去されるか、またはデジタル回路領域のNMOSトランジスタ上に残っているかに関係なく、前記ゲート120での圧縮応力及び前記チャンネル404aでの引張応力は保持されうる。

【0085】

前述したように、本実施例ではデジタル回路領域のNMOSトランジスタのチャンネル404aには局部的に引張応力が与えられ、そのゲートには圧縮応力が与えられる。その結果、デジタル回路領域のNMOSトランジスタでは、パフォーマンスが向上する。デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のNMOS及びPMOSトランジスタ領域上には、応力が残っていないために、これら素子のフリッカノイズ特性が劣化されない。ここで、注意すべき点は、本実施例において、追加的な高温アニーリング工程を導入しなくても、ソース/ドレーン活性化のための熱的負担を引張応力を誘導するのに利用することもできるということである。

【0086】

図17ないし図20は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第2カテゴリーに属するものである。本実施例では、NMOSトランジスタのパフォーマンスを向上させるためにシリサイド化工程を利用する。図17ないし図20の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。しかし、図17ないし図20の実施例において、シリサイドパターン130の代わりにシリサイドパターン830が図示されている。本実施例ではこれらシリサイドパターン830を、次の説明するようにNMOSパフォーマンスを向上させるのに利用する。

【0087】

図17を参照すれば、前記構造上に金属層パターンを蒸着して前記シリサイドパターン830を形成する。ここで、前記シリサイドパターン830は、ソース/ドレーン領域128及び導電性ゲート120のシリコン上に形成される。前記金属層は、例えばコバルトよりなりうる。その後、約450℃で第1RTA(rapid thermal annealing)工程を行なってコバルトモノシリサイド(CoSi)よりなるシリサイドパターン830を形成する。すなわち、第1熱処理によって第1相の金属シリサイドが形成される。前記第1RTAが行なわれた後、残りのコバルトは除去する。

【0088】

図18を参照すれば、前記第1RTAが行なわれた結果物上にキャッピング層840を形成する。前記キャッピング層840は、約5−20nmの厚さに形成されたチタン窒化膜(TiN膜)よりなりうる。

【0089】

図19を参照すれば、前記構造上にフォトレジストパターン860を形成してデジタル回路領域のNMOSトランジスタ上に形成された前記キャッピング層840部分のみを露出させる。次いで、前記キャッピング層840の露出された部分を除去する。次いで、約700−1100℃の温度下で第2RTA工程を行う。前記第2RTA工程の結果として、前記シリサイドパターン830が第2相の金属シリサイドに相転移する。例えば、CoSiがコバルトジシリサイド(CoSi2)に相転移する。その結果、ゲート及びソース/ドレーン領域上には、新たなシリサイドパターン830aが形成される。第1相の金属シリサイド、例えばCoSiから第2相の金属シリサイド、例えばCoSi2の相転移が行われる間、デジタル回路領域のNMOSトランジスタにチャンネル804aには引張応力が与えられる。他のチャンネル804b、804c、804dにはその上にキャッピング層840が形成されているので、これらがストレスを緩和する役割を行い、前記チャンネル804b、804c、804dには引張応力が、ほとんどまたは全く印加されない。すなわち、デジタル回路領域のNMOSトランジスタのチャンネル804aには引張応力が局部的に与えられが、残りのトランジスタのチャンネル804b、804c、804dにはその上に応力を緩和するためのキャッピング層840があるので、アニーリングによる影響を受けない。

【0090】

図20を参照すれば、キャッピング層840の残りの部分を除去する。その結果、デジタル回路領域のNMOSトランジスタのチャンネル804aには引張応力を与え、残りのトランジスタには応力を与えないシリサイドパターン830aを有する素子が得られる。

【0091】

図21ないし図27は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第3カテゴリーに属するものである。本実施例では、PMOSトランジスタのパフォーマンスを向上させるために、PMOSトランジスタに圧縮応力を誘導できるように、エピタキシャル成長されたソース/ドレーン構造を利用する。

【0092】

図21を参照すれば、各々NMOSトランジスタ及びPMOSトランジスタを含むCMOS構造をデジタル回路領域及びアナログ回路領域を含む素子の前記デジタル回路領域及びアナログ回路領域に形成する。前記デジタル回路領域及びアナログ回路領域は、各々第1NMOSトランジスタ及び第1PMOSトランジスタを含む。例えば、シリコンよりなる基板100を準備する。素子分離のために前記基板100にSTI102を形成する。各トランジスタは、ソース/ドレーン領域128を含み、これらは各々低濃度ソース/ドレーン領域122及び高濃度ソース/ドレーン領域126を含む。前記基板100上には各トランジスタを構成するゲート絶縁膜パターン110が形成されている。前記ゲート絶縁膜パターン110上には各トランジスタを構成するための導電性ゲートパターン120が形成され、前記ゲート絶縁膜パターン110及び導電性ゲートパターン120を含むあらゆるゲート構造の両側壁には側壁スペーサ124が形成される。

【0093】

図22を参照すれば、図21の構造上にマスク層510を形成する。前記マスク層510は、例えばシリコン酸化物、シリコン窒化物、またはこれらと類似した材料よりなりうる。

【0094】

図23を参照すれば、デジタル回路領域のPMOSトランジスタ上にあるマスク層510部分を少なくとも部分的に除去し、側壁スペーサ124上に少量のマスク層510だけを残す。その後、露出されたPMOSトランジスタのソース/ドレーン領域128の一部をそのゲート構造の側で自己整列方式で垂直方向に異方性エッチングによって一部除去する。その結果、約10−100nmの深さを有する溝520が形成される。

【0095】

図24を参照すれば、前記溝520及び導電性ゲート120の上面に半導体層522を選択的にエピタキシャル成長させる。前記エピタキシャル成長された半導体層522はSiGe、SiCまたはその他の物質よりなりうる。図面で矢印で表示したように、前記半導体層522はデジタル回路領域のPMOSトランジスタのチャンネル504bに圧縮応力を与える。この圧縮応力は、エピタキシャル成長された前記半導体層522のさらに大きな格子定数に起因する。さらに大きな格子定数を有する材料はチャンネル504b材料に圧力を与え、チャンネル504bで圧出応力が引き起こされる。すなわち、エピタキシャル成長された半導体層522と前記基板100は、相異なる格子定数及び/または相異なる熱膨張係数を有し、これにより、トランジスタのチャンネルで機械的応力が発生し、前記チャンネルでのキャリア移動度に影響を及ぼす。

【0096】

図25を参照すれば、前記構造から前記マスク層510の残りの部分を除去する。次いで、前記導電性ゲートパターン120及び露出されたソース/ドレーン領域128の上と、デジタル回路領域のPMOSトランジスタにエピタキシャル成長されている前記半導体層522の上面上に金属シリサイド層530を形成する。前記金属シリサイド層530は、例えばニッケルシリサイド、コバルトシリサイド、または他の類似した材料よりなりる。

【0097】

次いで、図26を参照すれば、前記構造上に引張応力を有するストレスコントロール膜550を形成する。前記ストレスコントロール膜550はLPCVD方法によって約20−150nmの厚さを有するように形成されたシリコン窒化膜よりなりうる。前記ストレスコントロール膜550は400−800℃の高温条件下で形成されたシリコン窒化膜で形成されることもある。他の方法として、前記ストレスコントロール膜550はアニーリングされたPECVD SiON膜、または引張応力を有するシリコン酸化膜よりなりうる。その結果、チャンネル504a、504b、504c、504dには局部的に引張応力が与えられる。

【0098】

次いで、図27を参照すれば、デジタル回路領域のPMOSトランジスタ及びアナログ回路領域のPMOS及びNMOSトランジスタで引張応力を選択的に緩和させる。デジタル回路領域のNMOSトランジスタ上にフォトレジストマスクパターン560を形成する。次いで、デジタル回路領域のNMOSトランジスタのみを除き、前記構造のあらゆる領域にGe、Si、As、In、Snなどのイオン、または他の類似したイオンを注入する。その結果、デジタル回路領域のPMOSトランジスタとアナログ回路領域のPMOS及びNMOSトランジスタで引張応力が緩和される。図面に矢印で示したように、イオン注入後にはデジタル回路領域のNMOSトランジスタのチャンネル504a上には引張応力が局部的に与えられ、デジタル回路領域のPMOSトランジスタのチャンネル504bには圧縮応力が局部的に与えられる。アナログ回路領域のチャンネル504c、504d上には何らの応力も与えられない。

【0099】

図28ないし図31は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第3カテゴリーに属するものである。本実施例では、デジタルトランジスタのNMOS及びPMOSトランジスタの何れにも応力を導入するために、引張応力層及び圧縮応力層を別途に形成する。図28ないし図31の実施例において、基板100、STI102、ソース/ドレーン領域128、ゲート絶縁膜パターン110、導電性ゲートパターン120、シリサイドパターン130及び側壁スペーサ124を含む素子部分の形成は、図6ないし図8の実施例と同一である。したがって、本例では詳細な説明は省略する。

【0100】

図28を参照すれば、引張応力を有する第1ストレスコントロール膜650を前記構造上に形成する。前記第1ストレスコントロール膜650はLPCVDによって約20−150nmの厚さに形成されたシリコン窒化膜よりなりうる。前記第1ストレスコントロール膜650は400−800℃の高温条件下で形成されたシリコン窒化膜よりなりうる。他の方法として、前記第1ストレスコントロール膜650は、アニーリングされたPECVD SiON膜または引張応力を有するシリコン酸化膜よりなりうる。前記第1ストレスコントロール膜650を形成した結果、デジタル回路領域及びアナログ回路領域のチャンネル604a、604b、604c、604dには、図面に矢印で示したように引張応力が局部的に形成される。

【0101】

図29を参照すれば、前記第1ストレスコントロール膜650のうち、デジタル回路領域のPMOSトランジスタと、アナログ回路領域のPMOS及びNMOSトランジスタ上にある部分を除去する。デジタル回路領域のNMOSトランジスタのみを覆うフォトレジストパターン654を形成し、前記第1ストレスコントロール膜650の露出された部分を除去する。ここで、注意すべき点は、前記第1ストレスコントロール膜650としてPECVD SiON膜を使用した場合には、前記第1ストレスコントロール膜650のうち、デジタル回路領域のPMOSトランジスタと、アナログ回路領域のPMOS及びNMOSトランジスタ上にある部分を除去した後、アニーリング工程を行うことが望ましいということである。前記第1ストレスコントロール膜650を選択的に除去した結果、図面に矢印で示したように、デジタル回路領域のNMOSトランジスタのチャンネル604aにのみ引張応力が印加される状態で残る。

【0102】

図30を参照すれば、前記構造上に圧縮応力を有する第2ストレスコントロール膜660を形成する。前記第2ストレスコントロール膜660は、例えばPECVD方法によって約20−150nmの厚さに形成されたシリコン窒化膜で形成しうる。前記第2ストレスコントロール膜660は、200−400℃の低温条件下で形成されたシリコン窒化膜よりなりうる。他の方法として、前記第2ストレスコントロール膜660は、圧縮応力を有するシリコン酸化膜よりなりうる。前記第2ストレスコントロール膜660を形成した結果、図面に矢印で示したように、前記あらゆるチャンネル604a、604b、604c、604dには圧縮応力が印加され、前記チャンネル604aには圧縮応力及び引張応力が何れも印加される。

【0103】

図31を参照すれば、デジタル回路領域のPMOSトランジスタのみ除き、あらゆるトランジスタ上で前記第2ストレスコントロール膜660をストレス解除膜またはストレス緩和膜662に選択的に変換させる。デジタル回路領域のPMOSトランジスタ上にのみフォトレジストマスクパターン670を形成する。デジタル回路領域のPMOSトランジスタを覆っている前記第2ストレスコントロール膜660は除き、参照符号“672”で表示したように、Ge、Si、As、In、Snなどのイオン、または他の類似したイオンを前記第2ストレスコントロール膜660に注入する。前記イオン注入によって前記第2ストレスコントロール膜660の露出部分で圧縮応力が緩和され、前記第2ストレスコントロール膜660の露出部分がストレス解除膜またはストレス緩和膜662になる。その結果、図面に矢印で表示されたように、引張応力はデジタル回路領域のNMOSトランジスタのチャンネル604aにのみ局部的に与えられ、圧縮応力はデジタル回路領域のPMOSトランジスタのチャンネル604bにだけ局部的に与えられる。したがって、アナログ回路領域のトランジスタは印加されたストレスによる影響を受けずに、デジタル回路領域でNMOSトランジスタ及びPMOSトランジスタのパフォーマンスを何れも向上させうる。したがって、アナログ回路領域のトランジスタは、トランジスタのストレス印加によって引き起こされうるノイズにより劣化されない。

【0104】

図32は、本発明の他の実施例に係る半導体素子を形成する方法を説明する概略的な断面図である。本実施例は、前記実施例のうち、第3カテゴリーに属するものである。図32の実施例は、図28ないし図31の実施例の変形例である。図32の実施例では、図28ないし図30に示した段階を同一に適用する。したがって、これら段階についての詳細な説明は省略する。

【0105】

図32を参照すれば、圧縮応力を有する第2ストレスコントロール膜660を形成した後、デジタル回路領域のPMOSトランジスタのみを除いてあらゆる領域で前記第2ストレスコントロール膜660を除去する。その結果、図面に矢印で表示されたように、引張応力がデジタル回路領域のNMOSトランジスタのチャンネル704aに局部的に与えられ、圧縮応力がデジタル回路領域のPMOSトランジスタのチャンネル704bに局部的に与えられる。

【0106】

以上、本発明を例示的な実施例を挙げて詳細に説明したが、本発明は前記実施例に限定されず、本発明の技術的思想及び範囲を逸脱せずに、当業者によって多様な変形が可能である。

【産業上の利用可能性】

【0107】

本発明は、デジタル、アナログ及び混合モード機能を含む回路に適用可能である。例えば、本発明はDRAM及びエンベデッドDRAMのようなメモリLSIに適用可能である。本発明の方法は、DRAMセル及び/またはノイズに敏感なアナログ回路のDRAMセンスアンプに適用可能である。本発明は、個別メモリチップまたはSRAM、フラッシュメモリ、MRAM、PRAM、及びその他の素子で構成されたエンベデッドメモリチップ構成でメモリ回路のセンスアンプ回路などの回路に適用可能である。前記回路でセンスアンプは、電流の非常に小さな差を感知せねばならず、よってこれらのパフォーマンスがフリッカノイズなどのノイズによって実質的に劣化されうるので、本発明は前記回路に特に適するように適用されうる。

【符号の説明】

【0108】

100 基板

102 STI

104a、104b、104c、104d トランジスタのチャンネル

110 ゲート絶縁膜パターン

120 導電性ゲートパターン

122 低濃度ソース/ドレーン領域

124 側壁スペーサ

126 高濃度ソース/ドレーン領域

128 ソース/ドレーン領域

130 シリサイドパターン

150 ストレスコントロール膜

152 ストレス解除膜またはストレス緩和膜

160 フォトレジストマスク

162 Ge、Si、As、In、Sbなどのイオンストレスコトロール膜

【特許請求の範囲】

【請求項1】

回路の第1領域に第1導電型の第1MOS素子を形成する段階と、

前記回路の第2領域に前記第1MOS素子と同一導電型である第1導電型の第2MOS素子を形成する段階と、

前記第1MOS素子及び第2MOS素子のうち前記第1MOS素子のチャンネルにストレスを印加する段階と、を含み、

前記第1MOS素子のチャンネルにのみストレスを印加する段階前に、

前記第1及び第2MOS素子に近接して第1相のシリサイドを形成するために第1熱処理を行う段階と、

前記第1及び第2MOS素子と前記第1相のシリサイド上にキャッピング層を形成する段階をさらに含む

ことを特徴とする回路製造方法。

【請求項2】

前記第1MOS素子及び第1相のシリサイド上で前記キャッピング層の一部を除去する段階をさらに含む

ことを特徴とする請求項1に記載の回路製造方法。

【請求項3】

前記第1MOS素子のチャンネルにストレスを印加する前に前記第1MOS素子と前記第2相のシリサイドを露出させるように前記キャッピング層の一部を除去し、

前記第1MOS素子のチャンネルにストレスを印加する段階は、前記第2MOS素子が前記キャッピング層で覆われている状態で前記第1相のシリサイドを第2相のシリサイドに転換させるために第2熱処理を行う段階をさらに含む

ことを特徴とする請求項2に記載の回路製造方法。

【請求項4】

回路の第1領域に形成された第1導電型の第1MOS素子と、

前記回路の第2領域に形成された前記第1MOS素子と同一導電型である第1導電型の第2MOS素子と、を含み、

前記第1MOS素子のチャンネルにはストレスが印加されており、前記第2MOS素子にはストレスが印加されておらず、

前記第1MOS素子のチャンネルにストレスを印加するために前記第1MOS素子のソース/ドレーン領域上に形成された第2相のシリサイドをさらに含む

ことを特徴とする回路。

【請求項1】

回路の第1領域に第1導電型の第1MOS素子を形成する段階と、

前記回路の第2領域に前記第1MOS素子と同一導電型である第1導電型の第2MOS素子を形成する段階と、

前記第1MOS素子及び第2MOS素子のうち前記第1MOS素子のチャンネルにストレスを印加する段階と、を含み、

前記第1MOS素子のチャンネルにのみストレスを印加する段階前に、

前記第1及び第2MOS素子に近接して第1相のシリサイドを形成するために第1熱処理を行う段階と、

前記第1及び第2MOS素子と前記第1相のシリサイド上にキャッピング層を形成する段階をさらに含む

ことを特徴とする回路製造方法。

【請求項2】

前記第1MOS素子及び第1相のシリサイド上で前記キャッピング層の一部を除去する段階をさらに含む

ことを特徴とする請求項1に記載の回路製造方法。

【請求項3】

前記第1MOS素子のチャンネルにストレスを印加する前に前記第1MOS素子と前記第2相のシリサイドを露出させるように前記キャッピング層の一部を除去し、

前記第1MOS素子のチャンネルにストレスを印加する段階は、前記第2MOS素子が前記キャッピング層で覆われている状態で前記第1相のシリサイドを第2相のシリサイドに転換させるために第2熱処理を行う段階をさらに含む

ことを特徴とする請求項2に記載の回路製造方法。

【請求項4】

回路の第1領域に形成された第1導電型の第1MOS素子と、

前記回路の第2領域に形成された前記第1MOS素子と同一導電型である第1導電型の第2MOS素子と、を含み、

前記第1MOS素子のチャンネルにはストレスが印加されており、前記第2MOS素子にはストレスが印加されておらず、

前記第1MOS素子のチャンネルにストレスを印加するために前記第1MOS素子のソース/ドレーン領域上に形成された第2相のシリサイドをさらに含む

ことを特徴とする回路。

【図1】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【公開番号】特開2013−30780(P2013−30780A)

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願番号】特願2012−183974(P2012−183974)

【出願日】平成24年8月23日(2012.8.23)

【分割の表示】特願2005−99739(P2005−99739)の分割

【原出願日】平成17年3月30日(2005.3.30)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願日】平成24年8月23日(2012.8.23)

【分割の表示】特願2005−99739(P2005−99739)の分割

【原出願日】平成17年3月30日(2005.3.30)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]