低電力無線周波数デジタル受信機

【課題】無線周波数受信機における消費電力の低減。

【解決手段】無線周波数デジタル受信機100は、第1のレートで信号をサンプリングする変調器104を有する。この受信機は、少なくとも1つの処理ユニット110を有する。この処理ユニットは、信号を分離し、第1のレートよりも低いレートで信号を再結合する複数のデジタルバンドパスフィルタ120を有する。この処理ユニットは、周波数オフセットを調整する、または第1のレートよりも低いレートで信号をセンタリングするデジタルダウンコンバータ108を有する。この受信機は、受信機内に2つ以上の処理ユニットがある場合に、隣接する処理ユニットに結合される少なくとも1つのレート制御バッファを有する。

【解決手段】無線周波数デジタル受信機100は、第1のレートで信号をサンプリングする変調器104を有する。この受信機は、少なくとも1つの処理ユニット110を有する。この処理ユニットは、信号を分離し、第1のレートよりも低いレートで信号を再結合する複数のデジタルバンドパスフィルタ120を有する。この処理ユニットは、周波数オフセットを調整する、または第1のレートよりも低いレートで信号をセンタリングするデジタルダウンコンバータ108を有する。この受信機は、受信機内に2つ以上の処理ユニットがある場合に、隣接する処理ユニットに結合される少なくとも1つのレート制御バッファを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本開示の実施形態は、一般に通信システムに関し、より詳細には、無線周波数(RF)領域において任意のバンドパスフィルタリングを実施し、フィルタリングしたRF信号をデジタル領域にダウンコンバートすることができる、低電力無線周波数デジタル受信機に関する。

【背景技術】

【0002】

無線受信機は、無線アンテナからの信号を使用可能な形に変換することができる。アンテナから受け取った信号を変換する設計アーキテクチャは、低雑音増幅器(LNA)、ダウンコンバートミキサ、電圧制御器オシレータ(VCO)、低域フィルタ(LPF)、シンセサイザループ、基準発生器、アナログデジタルコンバータ(ADC)、および復調器を有し得るデジタル信号処理装置(DSP)を含むことができる。アーキテクチャ内のこうしたRFユニットのブロック、およびアナログベースバンド、および混合信号回路には、一体型受信機設計の設計努力、および実装費用の大部分が費やされることがある。非デジタル回路の使用はまた、プロセス技術が進化し、供給電圧が低減するにつれて、電圧(振幅)ヘッドルームが限られるという問題を生じ得る。

【0003】

大部分のRF、およびアナログベースバンド回路を排除することによって、複雑性を低減させ、ヘッドルーム問題を軽減するように設計された一アーキテクチャでは、アンテナからの入力信号を、LNAによって増幅し、ADCによって直接サンプリングすることができる。アナログ信号処理の大部分は、DSPに委ねられることになり得る。このアーキテクチャでは、ADCに厳格な要件が求められることがある。ADCのサンプリング周波数は、RF搬送周波数のナイキストレートでよく、この周波数は、信号帯域幅よりも高くなり得る。そのため、ADCの設計複雑性、および同期サンプリングクロックの消費電力にオーバーヘッドが生じる結果となり得る。アンダーサンプリング策を採用できる場合でも、余分の雑音がベースバンドに折り込まれることがあり、これによって受信機の信号対雑音比(SNR)が劣化するおそれがある。

【発明の概要】

【発明が解決しようとする課題】

【0004】

したがって、上記の問題を解決するシステムおよび方法を提供することが望ましい。

【課題を解決するための手段】

【0005】

無線周波数デジタル受信機は、第1のレートで信号をサンプリングする変調器を有する。この受信機は、少なくとも1つの処理ユニットを有する。この処理ユニットは、信号を分離し、第1のレートよりも低いレートで信号を再結合する複数のデジタルバンドパスフィルタを有する。この処理ユニットは、周波数オフセットを調整する、または第1のレートよりも低いレートで信号をセンタリングするデジタルダウンコンバータを有する。この受信機は、受信機内に2つ以上の処理ユニットがある場合に、隣接する処理ユニットに結合される少なくとも1つのレート制御バッファを有する。

【0006】

マルチトーンアップコンバータは、信号を受け取るように構成されたデジタルアップコンバータを有する。信号を分離するように構成された複数のデジタルバンドパスフィルタが、デジタルアップコンバータに結合されている。信号を結合するデジタルルータが、複数のバンドパスフィルタに結合されている。信号をアナログ信号に変換するデジタルアナログコンバータが、デジタルルータに結合されている。

【0007】

無線周波数受信機における消費電力を低減させる方法は、信号を受信するステップと、信号をフィルタリングするステップと、第1のレートで信号をサンプリングするステップと、少なくとも1つの処理ユニットにおいて、第1のレートよりも低い処理レートで信号をサブバンドに分離するステップと、サブバンドからの信号を処理レートで再結合するステップと、周波数オフセットを補正する、または処理レートで信号をセンタリングするステップとを含む。

【0008】

上記の特徴、機能、および利点は、本開示の様々な実施形態において独立に実現することも、またはさらに他の実施形態と組み合わせることもできる。

【0009】

本開示の実施形態は、詳細な説明、および添付の図面からより完全に理解されよう。

【図面の簡単な説明】

【0010】

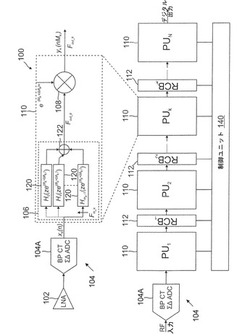

【図1】均質な処理を有する受信機の概略的なアーキテクチャのブロック図である。

【図2】搬送周波数からの信号を、それぞれが処理ユニットによって行われる複数の段階を経てベースバンドに変換する工程を示すグラフである。

【図3】受信機の特定の例のブロック図である。

【図4】受信機の等価な組合せのブロック図である。

【図5】受信機の特定の例のシミュレーション結果のグラフである。

【図6】受信機の動作を示す工程図である。

【図7】RFトーン発生器のブロック図である。

【図8】RFトーン発生器の動作を示す工程図である。

【図9】RFトーン発生器のシミュレーション結果のグラフである。

【発明を実施するための形態】

【0011】

図1を参照すると、均質な処理を有する受信機100の概略的なアーキテクチャのブロック図を示すことができる。受信機100は、低電力無線周波数(RF)デジタルベースバンド設計を有することができる。受信機100について、モバイルプラットフォームに関して以下で説明することができる。受信機100は、入来したRF通信を処理するスマートフォン、携帯電話などの中に配置することができる。受信機100はまた、ソフトウェア無線(SDR)、スマート無線、車載通信、車両用インフォテインメント(infotainment)などに使用することができる。

【0012】

受信機100は、バンドパスフィルタリング、サンプリング、ダウンコンバート、およびデシメーションの工程を、複雑性が低く、かつ電力効率が良い形で実施することができる。RF、デジタル領域、およびアナログ領域にわたる、いくつかのビルディングブロックからなり、デジタル回路において非常に高速のクロックレートで作動し得る既存の手法とは異なり、受信機100は、マルチレートデジタル信号処理(MDSP)と、バンドパス連続時間デルタシグマアナログデジタルコンバータ(BP−CT−ΔΣ−ADC)との組合せを利用して、上記の工程を、対象となる信号帯域幅のクロックレートで作動するストリームライン、およびトランスペアレントな機構において実行することができる。上記により、従来のアーキテクチャに比べて、信号の入力からデータの出力までの待ち時間がより短く、必要となるビルディングブロックの数がより少数に、かつ消費電力をより低減させることができる。さらに、この設計によって、アナログデジタルコンバータ(ADC)に課される厳格な要件を除去することができる。受信機100は、アナログ回路、またはデジタル回路のいずれかのビルディングブロックを有することができ、したがってRF回路が減少し、その結果受信機100は、現代の超大規模集積回路(VLSI)技術におけるプロセス変動に耐えるものとなる。

【0013】

受信機100は、RF領域において任意のバンドパスフィルタリング(BPF)を実施することができる。図1に示す実施形態では、受信機100は、フィルタリングしたRF信号をデジタル領域にダウンコンバートすることができる。受信機100は、混合信号回路設計策を使用し、信号をナイキストレートで処理することができる。受信機100は、低消費電力、および低複雑性設計という重要な利点を実現することができる。受信機100は、MDSP、およびBP−CT−ΔΣ−ADC104の技術に基づくことができる。

【0014】

受信機100は、搬送周波数の倍数のレートで信号を処理するのではなく、信号帯域幅をカバーするレートで信号を取り扱うことができる。処理レートのこうした低減によって、処理帯域幅を節減し、全体的な消費電力を低減させることができる。低電力RFデジタルベースバンド受信機100はまた、ソフトウェア定義のモジュールによって、所望の入力周波数領域、および出力データレートにプログラミングし、かつ調整することができるビルディングブロックを有することができる。受信機100のMDSP部分は、マルチトーンアップコンバータになるように構成変更することができ、このコンバータは、受信機100の動作の始めの較正工程用のトーン発生器として働くことができる。

【0015】

図1に示す実施形態では、入来したRF信号は、アンテナを介して導入することができ、アンテナは図示されていない。アンテナは、電波を受信し、それらの電波を電流に変換することができる。アンテナは、増幅器102に結合することができる。増幅器102は、低雑音増幅器(LNA)102でよく、受信機100のアンテナによって受信した信号の出力を増大させることができる。

【0016】

LNA102は、変調器104に結合することができる。変調器104は、増幅器102から信号を受け取ることができる。図1に示す実施形態では、変調器104は、BP−CT−ΔΣ−ADC104Aでよく、信号をフィルタリングし、サンプリングすることによって、信号を処理することができる。信号をデジタル領域に持ち込むことによって、BP−CT−ΔΣ−ADC104Aは、雑音排除性、堅牢性、および融通性を実現することができ、性能、消費電力、およびコスト削減を向上させる可能性をもたらすことができる。BP−CT−ΔΣ−ADC104Aは、消費電力、およびチップ面積を低く保持しながら、高速動作を可能とすることができる。フィルタリングした信号のサンプルを、BP−CT−ΔΣ−ADC104Aの出力で、レートFin_kで生成することができ、Xk(n)として示す。この出力は、高度のプログラミング性を提供することができ、マルチスタンダードRF受信機100にとって理想的となり得る。

【0017】

BP−CT−ΔΣ−ADC104Aは、LNA102が受け取った入来信号をベースバンドにダウンコンバートすることができる。変調器104は、狭帯域信号に対してバンドパスADCを実施するのに適し得る。フィルタリングした信号を、変調器104の連続時間デルタシグマ(CT−ΔΣ)部分によってデジタル化することができる。BP−CT−ΔΣ−ADC104Aは、入力信号を混合し、デジタル化することができ、この信号にはLNA102による増幅が必要となり得る。BP−CT−ΔΣ−ADC104Aは、フィードバックに正弦波パルスの整数を利用することができる。フィードバックベースの関数は、本質的にバンドパスとなり得る。上記によって、時間遅延ジッタ、およびパルス幅ジッタの存在下でも、変調器104の性能を大幅に改善することができる。また、変調器104のサンプリング周波数は、変調器104を同調させる中央周波数よりも低くてよい。

【0018】

図1の実施形態に示すように、変調器104は、デジタル多相フィルタ(DPF)106に結合することができる。DPF106は、BP−CT−ΔΣ−ADC104Aの出力を受け取ることができ、この出力はXk(n)であった。DPF106は、信号をダウンコンバートし、かつデシメーションするMDSPを実施することができる。フィルタ106は、入力信号Xk(n)を、係数Mでサブサンプリングされたいくつかの等間隔サブバンド120に分割することができ、したがってクリティカルにサンプリングすることができる。サブバンド120は、入力信号Xk(n)を複数の成分に分離するバンドパス有限長フィルタ(FLF)120のアレイでよく、これらのフィルタはそれぞれ、元の信号を異なるフィルタ係数でフィルタリングする。例えば、フィルタ係数は、Hn(zej(θk+...))とすることができる。図1に示すように、第1のフィルタ係数は、H0(zej(θk+...))とすることができる。DPF106は、結合器122を介して、サブバンド120からの信号をレートFout_kで再結合することができる。Fout_kは、Fin_kとは異ならせることができ、Fout_kは、Fin_kよりも低いレートにすることができる。

【0019】

DPF106のバンドパスフィルタ120はそれぞれ、レートFout_kで動作することができる。Fout_kは、対象となる信号帯域幅よりも大きくてよい。Fout_kは通常、Fin_kよりも遙かに小さくすることができ、Fin_kは、Fout_kの倍数となるように選択することができる。FLF120の個数は、Mによって示され、Fin_kのFout_kに対する比として定義することができる。DPF106には、総数M個のサブFLF120があってもよく、それぞれがレートFout_kで作動する。BP−CT−ΔΣ−ADC104Aの出力Xk(n)は、信号の分離を示す点線によって示されるように、各サブバンド120に時間多重化される。図2は、搬送周波数からの信号を、それぞれが処理ユニット(PU)110によって行われる複数の段階を(上から下へと)経てベースバンドに変換する工程を示すグラフである。DPF106によって有限インパルス応答(FIR)を使用して、入来信号Xk(n)からサンプルを取ることができる。次いで、FLF120からの出力を、結合器122で、レートFout_kで結合することができる。

【0020】

図1に示す実施形態では、DPF106をデジタルダウンコンバータ(DDC)108に結合することができ、どちらもレートFout_kで動作することができる。DDC108は、DPF106の出力を、中間周波数(IF)でセンタリングされたデジタル化実信号、またはゼロ周波数でセンタリングされたベースバンド複素信号に変換することができる。次いで、受信機100のDDC108は、レートFout_kで出力yk(nMk)を供給することができる。

【0021】

受信機100は、デバイス自体の中に配置することも、または複数のDPF106、およびDDC108が、増幅器102、および変調器104とともに直列に存在し得る均質なPU110ベースのアーキテクチャの一部とすることもできる。図示の一実施形態では、BP−CT−ΔΣ−ADC104Aは、第1のPU110、すなわちPU1に結合し、次いで多数の他のPU110に結合することができる。各PU110は、信号を処理することができる。レート変換バッファ(RCB)112を、受信機100内のPU110間に結合することができる。RCB112を用いて、あるサンプルレートの信号を操作し、その信号を新しいサンプルレートに変換することができる。PU110の個数と、RCB112の個数とは、調整することができる。PU110とRCB112との組合せによって、デジタル出力を供給することができる。

【0022】

図1に示すように、受信機100は、1つのPU110、または多数のPU110を有することができる。PU110はそれぞれ、複数のデジタルバンドパスフィルタ120をDPF106内に有することができる。複数のデジタルバンドパスフィルタ120は、レートFin_kで入来した信号を分離し、入来信号のレートFin_kよりも低いレートFout_kで、その信号を再結合することができる。Fin_kとFout_kとは、PU110ごとに異なってもよい。PU110内のDDC108は、周波数オフセットを調整する、または入来信号のレートFout_kよりも低いレートで信号をセンタリングすることができる。受信機100内に2つ以上のPU110がある場合、少なくとも1つのRCB112を、隣接するPU110に結合することができる。

【0023】

受信機100は、制御器140を含むことができる。制御器140は、2つ以上のPU110が動作している場合に、受信機100に組み込むことができる。図1内に示すように、制御器140は、受信機100内の各PU110、および各RCB112に結合することができる。この接続によって、PU110、およびRCB112の構成が可能となる。構成時に、信号を処理するレートを調整することができる。

【0024】

制御器140は、ソフトウェア、ハードウェア、または両方の組合せでプログラミングすることができる。ソフトウェア実装では、コードを、非一時的コンピュータ可読記憶媒体に実装することができる。制御器140の非一時的コンピュータ可読記憶媒体には、以下に限られるものではないが、揮発性メモリ、不揮発性メモリ、磁気および光記憶装置、あるいは現時点で既知の、または後に開発される、コードおよび/またはデータを記憶することが可能な他の媒体が含まれ得る。コードは、データ構造およびコードとして具体化され、非一時的コンピュータ可読記憶媒体内に記憶される方法および工程を実施するコンピュータシステムによって読み取り、実行することができる。さらに、制御器140用の方法および工程は、ハードウェアモジュール内に含めることができる。これらのハードウェアモジュールには、特定用途向け集積回路(ASIC)チップ、フィールドプログラマブルゲートアレイ(FPGA)、および現時点で既知の、または後に開発される他のプログラマブルロジックデバイスが含まれ得る。

【0025】

制御器140は、デジタルバンドパスフィルタ120、およびDDC108をセットアップすることによって、各PU110を構成することができる。一実施形態では、PU110、およびRCB112は、別の方法、例えば配線によって構成することができる。制御器140は、現在のPU110が変調器104に結合されている場合、入来レートを現在のPU110の処理レートの倍数として調整し、搬送周波数を現在のPU110の処理レートの倍数として調整することによって、PU110内のDDC108を迂回することができる。あるいは、制御器140は、前のPU110の処理レートを現在のPU110の処理レートの倍数として調整し、中間周波数を現在のPU110の処理レートの倍数として調整することができる。

【0026】

受け取った信号は、各PU110内で時間多重化によって分離することができる。PU110が変調器104と結合されている場合、変調器104からのサンプリング信号を、DPF106の各サブバンド120に供給することができる。そうでない場合は、前のPU110の出力を、現在のPU110のDPF106のサブバンド120に時間多重化することができる。

【0027】

受信機100内に複数のPU110が使用されている場合、総数M個のサブ有限長フィルタ120は、入来レートFin_kよりも低いレートFout_kで作動することができる。Mは、PU110が変調器104の次にある場合、第1のレートの、現在のPU110の処理レートに対する比とすることができる。PU110が変調器104に結合されていない場合、例えばPU2110、PUk110、またはPUN110では、Mは、前のPU110の処理レートの、現在のPU110の処理レートに対する比とすることができる。

【0028】

上述のように、変調器104は、第1のレートで信号を処理することができる。第1のレートは、搬送周波数よりも高くてよい。複数のデジタルバンドパスフィルタ120、およびDDC108を有するPU110は、信号の帯域幅のナイキストレート以上のレートで信号を処理することができる。典型的には、このレートは、搬送周波数よりも低くてよい。

【0029】

各PU110内のDDC108は、同じPU110内のM個のサブ有限長フィルタ120と同じレートで作動し、出力を生成することができる。一実施形態では、処理ユニットが、最後に最終出力を生成する場合、各PU110内のDDC108は、ゼロ周波数で信号をセンタリングすることができる。そうでない場合、DDC108は、周波数オフセットを所望の中間周波数に補正することができる。第1のレートは、搬送周波数よりも大きくてよい。各PU110の処理レートは、信号の帯域幅をカバーすることができ、かつ搬送周波数よりも低くすることができる。

【0030】

次に、図3に移ると、受信機100の特定の例のブロック図を表すことができる。受信機100は、1つのPU110で動作することができる。RF信号は、アンテナによって受信することができ、アンテナは図示されていない。アンテナにLNA102を結合することができる。LNA102は、アンテナから受け取った信号を増大させることができる。変調器104をLNA102に結合することができる。BP−CT−ΔΣ−ADC104Aは、LNA102からの信号をフィルタリングし、サンプリングすることによって、その信号を処理することができる。信号は、第1のレートFSで処理することができる。FSは、搬送周波数の倍数でよい。

【0031】

信号は、変調器104によって処理した後、DPF106に供給することができる。変調器104の出力は、x(n)とすることができる。図3に示す実施形態では、信号は、FLF120によって処理することができる。FLF120は、サブバンドを表すことができ、これらのサブバンドはそれぞれ、元の信号を異なるフィルタ係数でフィルタリングする。例えば、フィルタ係数は、Hn(zej(θk+...))とすることができる。図3に示すように、第1のフィルタ係数は、H0(zej(θk+...))とすることができる。この実施形態では、サブバンド120は、64個の離散ユニットとして表すことができる。例えば、各サブバンド120は、クリティカルサンプリング(critical sampling)として係数64でサンプリングを行うことができる。64個のサブバンド120からの信号を、結合器122によって第2のレートFOUTで再結合することができる。サブバンド120の個数64は、第1のレートFSの、第2のレートFOUTに対する比と同等、またはその比に比例した数とすることができる。再結合した信号をDDC108に供給し、出力y(nM、k)として送信することができる。FSは、搬送周波数の倍数とすることができ、FOUTは、信号の帯域幅をカバーすることができる。

【0032】

DPF106の全体的な動作は、図4の実施形態に示すデジタルバンドパスフィルタ(DBF)402と、M−to−1デジタルデシメータ(DDEC)404との組合せと等価とすることができる。図示のように、信号は、LNA102によってアンテナから受け取ることができる。BP−CT−ΔΣ−ADC104Aは、信号をデジタル化し、PU110のDBF402にその信号を供給することができる。信号x(n)は、上述のレートFSで供給することができる。

【0033】

DBF402は、規定されたパスバンドで信号をフィルタリングする動作を実施することができる。DBF402にDDEC404を結合することができる。DDEC404は、DBF402から受け取った離散時間信号のサンプル数を減少させることができる。DDEC404は、DBF402から受け取った信号をベースバンドに持ち込むことができる。こうした減少はMに比例させることができ、MはFSのFOUTに対する比として規定された数である。次いで、DDEC404に結合されたDDC108によって、信号をレートFOUTでダウンコンバートすることができる。その後、DDC108は、出力y(nM、k)を供給することができる。DBF402とDDEC404との組合せは、DPF106に等価となり得る。DBF402、およびDDEC404は、レートFSで作動することができる。しかし、どちらともより高速のレートFSで作動しているので、レートFOUTで作動している図3のDPF106は、図4のDBF402とDDEC404との組合せよりも消費電力が少ない。

【0034】

各サブバンドまたはFLF120に対するフィルタ係数は、対応するDBF402係数の時間多重化値とすることができる。一実施形態では、DBF402係数は、デジタルローパスフィルタ(DLF)係数を回転させたバージョン、またはアップコンバートしたバージョンとすることができる。DLFは、DBF402と同じフィルタ帯域幅を有することができるが、ベースバンドでダウンコンバートしたサンプルを処理する。回転角度は、θk+Δθとすることができ、θkは、2π×k×FS/Mに等しく、Δθは、搬送周波数(FC)とθkとの差とすることができる。図5は、受信機100のシミュレーション結果のグラフである。このグラフは、BP−CT−ΔΣ−ADC104Aの工程と、DPF106の工程との組合せを示している。

【0035】

図6を参照すると、受信機100の動作を示す工程図を表すことができる。受信機100の工程は、ブロック600から開始することができる。ブロック602で、受信機100のアンテナは、RF信号を受信することができる。ブロック604で、RF信号をLNA102によって増幅することができる。ブロック606で、信号をフィルタリングすることができる。ブロック608で、信号をサンプリングすることができる。信号のフィルタリング、およびサンプリングは、BP−CT−ΔΣ−ADC104Aによって処理することができる。

【0036】

ブロック610で、信号をデジタル多相フィルタで時間多重化することができる。DPF106は、変調器104から受け取ったデジタル化信号をサブバンド120に分離することができる。それらのサブバンド120から、DPF106の結合器122を介して信号を生成することができる。ブロック612で、再結合した信号をダウンコンバートすることができる。次いで、DDC108の出力をさらに処理する、またはデバイスのアプリケーションによって使用することができる。ブロック614で、工程を終了することができる。

【0037】

図7に移ると、RFトーン発生器700を表すことができる。先に説明した受信機100の信号経路を構成変更して、発生器700を設けることができる。RFトーン発生器700は、デジタルアップコンバータ(DUC)702、DPF106、およびデジタルルータ(DR)704を含むことができる。補助デジタルアナログコンバータ(AUX DAC)706を、DR704を介して発生器700に結合することができる。デジタル信号x(nM、k)を、DUC702に供給することができる。DUC702によって、この信号を複素信号と混合し、DPF106にレートFinで供給することができる。

【0038】

図7の実施形態では、受信機100のDPF106、およびDDC108の信号経路を、反対方向に容易に構成変更することができ、したがって受信機100全体を、デジタルアナログコンバータ(DAC)の助けを得て、RFトーン発生器700とすることができる。DPF106の各サブバンド120は、入来信号の一部分を取ることができる。サブバンド120は、DR704に結合することができる。DR704は、サブバンドの出力を単一の信号に多重化することができる。DR704に、AUX DAC706を結合することができる。AUX DAC706は、信号を取り、その信号をアナログの形に変換することができる。この信号を、送信機に供給することができる。送信機は、電気信号をRF通信に変換することができる。レートFinは、RFトーン周波数よりも小さく、したがって消費電力を低減させることができる。

【0039】

図8は、RFトーン発生器700のシミュレーション結果のグラフである。このトーン発生器700の出力は、受信機100の動作の始めの較正工程用の、LNA102またはBP−CT−ΔΣ−ADC104への入力のテスト信号として働くことができる。

【0040】

図9を参照すると、RFトーン発生器700の動作を示す工程図を表すことができる。発生器700の工程は、ブロック900から開始することができる。ブロック902で、発生器700のDUC702は、デジタル信号を受け取ることができる。ブロック904で、DUC702は、そのデジタル化された信号をアップコンバートすることによって、その信号を適切にフォーマットすることができる。ブロック906で、DPF106によって信号を時間多重化することができる。DPF106は、発生器700向けに目的変更することができ、信号をレートFinで分離することができる。

【0041】

ブロック908で、DR704のデジタル多相フィルタを介して、信号をデジタル式にルートすることができる。DR704によって、Finよりも高いレートで信号の再結合を行うことができる。最初の処理段階における処理速度が低速であるため、電力を節減することができる。ブロック910で、AUX DAC706によって信号をアナログ信号に変換することができる。ブロック912で、工程を終了することができる。

【0042】

上記の明細書および図には、第1のレートで信号をサンプリングする変調器104と、少なくとも1つの処理ユニット110であって、信号を分離し、第1のレートよりも低いレートで信号を再結合する複数のデジタルバンドパスフィルタ120と、周波数オフセットを調整する、または第1のレートよりも低いレートで信号をセンタリングするデジタルダウンコンバータ108とを含む少なくとも1つの処理ユニット110と、受信機100内に2つ以上の処理ユニット110がある場合に、隣接する処理ユニット110に結合される少なくとも1つのレート制御バッファとを含む、無線周波数デジタル受信機100が開示されている。

【0043】

一変形形態では、無線周波数デジタル受信機100は、受信機100内に2つ以上の処理ユニット110がある場合に、少なくとも1つの処理ユニット110と、少なくとも1つのレート制御バッファとの間の接続部を構成する制御器140を含む。さらに別の変形形態では、無線周波数デジタル受信機100は、変調器104が信号を受け取る前に、信号を受け取り、増幅する増幅器102を含む。さらに別の変形形態では、変調器104は、バンドパス連続時間デルタシグマアナログデジタルコンバータである。さらに別の変形形態では、各処理ユニット110内の複数のデジタルバンドパスフィルタ120は、デジタル多相フィルタ106の形で設けられる。

【0044】

一代替形態では、各処理ユニット110内の複数のデジタルバンドパスフィルタ120は、それぞれが第1のレートよりも低いレートで作動する総数M個のサブ有限長フィルタを含み、現在の処理ユニット110が変調器104の次にある場合、Mは、第1のレートの、現在の処理ユニット110の処理レートに対する比であり、そうでない場合、Mは、前の処理ユニット110の処理レートの、現在の処理ユニット110の処理レートに対する比である。別の代替形態では、各処理ユニット110内のM個のサブ有限長フィルタに対する入力は、現在の処理ユニット110が変調器104の次にある場合、変調器104の時間多重化出力によって供給され、そうでない場合、前の処理ユニット110の時間多重化出力によって供給される。

【0045】

別の変形形態では、変調器104は、搬送周波数よりも高い第1のレートで信号を処理し、各処理ユニット110内の複数のデジタルバンドパスフィルタ120、およびデジタルダウンコンバータ108は、信号の帯域幅のナイキストレート以上であるが、搬送周波数よりも低いレートで信号を処理する。さらに別の変形形態では、各処理ユニット110内のデジタルダウンコンバータ108は、同じ処理ユニット110内のM個のサブ有限長フィルタと同じレートで作動し、処理ユニット110の出力を生成する。一例では、各処理ユニット110内のデジタルダウンコンバータ108は、処理ユニット110が最後に最終出力を生成する場合、ゼロ周波数で信号をセンタリングし、そうでない場合、周波数オフセットを所望の中間周波数に補正する。さらに別の代替形態では、第1のレートは、搬送周波数よりも大きく、各処理ユニット110の処理レートは、信号の帯域幅をカバーし、かつ搬送周波数よりも低い。

【0046】

一態様では、信号を受け取るデジタルアップコンバータ702と、デジタルアップコンバータ702に結合され、信号を分離する複数のデジタルバンドパスフィルタ120と、複数のデジタルバンドパスフィルタ120に結合され、信号を結合するデジタルルータと、デジタルルータに結合され、信号をアナログ信号に変換するデジタルアナログコンバータ706とを含む、マルチトーンアップコンバータが開示されている。一変形形態では、較正のために、信号が、無線周波数デジタル受信機100内の低雑音増幅器102、または変調器104にテスト信号として供給される。別の変形形態では、マルチトーンアップコンバータは、無線周波数デジタル受信機100を含む。一変形形態では、デジタルアップコンバータ702、および複数のデジタルバンドパスフィルタ120が、無線周波数デジタル受信機100内の処理ユニット110として再利用される。一代替形態では、無線周波数デジタル受信機100は、第1のレートで信号をサンプリングする変調器104と、複数の処理ユニット110であって、それぞれが信号を分離し、第1のレートよりも低いレートで信号を再結合する複数のデジタルバンドパスフィルタ120と、周波数オフセットを調整する、または信号をセンタリングするデジタルダウンコンバータ108とを含む複数の処理ユニット110と、隣接する処理ユニット110に結合される少なくとも1つのレート制御バッファと、各処理ユニット110とレート制御バッファとの間の接続部を構成する制御器140とを含む。

【0047】

一態様では、無線周波数デジタル受信機100における消費電力を低減させる方法であって、信号を受信するステップと、信号をフィルタリングするステップと、第1のレートで信号をサンプリングするステップと、少なくとも1つの処理ユニット110において、第1のレートよりも低い処理レートで、信号をサブバンド120に分離するステップと、サブバンド120からの信号を処理レートで再結合するステップと、周波数オフセットを補正する、または処理レートで信号をセンタリングするステップとを含む、方法が開示されている。

【0048】

一変形形態では、この方法は、処理ユニット110内のデジタルダウンコンバータ108を迂回するステップであって、現在の処理ユニット110が変調器104に結合されている場合、第1のレートを現在の処理ユニット110の処理レートの倍数として調整し、搬送周波数を現在の処理ユニット110の処理レートの倍数として調整することによって迂回し、そうでない場合、前の処理ユニット110の処理レートを現在の処理ユニット110の処理レートの倍数として調整し、中間周波数を現在の処理ユニット110の処理レートの倍数として調整することによって迂回するステップを含む。

【0049】

一変形形態では、信号を分離するステップは、現在の処理ユニット110が変調器104に結合されている場合、サンプリングした信号を、各サブバンド120に時間多重化するステップを含み、そうでない場合、前の処理ユニット110の出力を、現在の処理ユニット110内の各サブバンド120に時間多重化するステップを含む。さらに別の変形形態では、この方法は、処理ユニット110内の複数のデジタルバンドパスフィルタ120、およびデジタルダウンコンバータ108を、制御器140を介してセットアップすることによって各処理ユニット110を構成するステップ、または処理ユニット110内の複数のデジタルバンドパスフィルタ120、およびデジタルダウンコンバータ108を、制御器140を介して迂回するステップを含むことができる。

【0050】

本開示の実施形態を、様々な特定の実施形態に関して説明してきたが、本開示の実施形態は、特許請求の範囲の趣旨および範囲に包含される改変形態で実践できることが当業者には認識されよう。

【符号の説明】

【0051】

100 無線周波数デジタル受信機

102 増幅器

104 変調器

106 デジタル多相フィルタ

108 デジタルダウンコンバータ

110 処理ユニット

112 レート変換バッファ

120 デジタルバンドパスフィルタ

122 結合器

140 制御器

402 デジタルバンドパスフィルタ

404 デジタルデシメータ

700 RFトーン発生器

702 デジタルアップコンバータ

704 デジタルルータ

706 補助デジタルアナログコンバータ

【技術分野】

【0001】

本開示の実施形態は、一般に通信システムに関し、より詳細には、無線周波数(RF)領域において任意のバンドパスフィルタリングを実施し、フィルタリングしたRF信号をデジタル領域にダウンコンバートすることができる、低電力無線周波数デジタル受信機に関する。

【背景技術】

【0002】

無線受信機は、無線アンテナからの信号を使用可能な形に変換することができる。アンテナから受け取った信号を変換する設計アーキテクチャは、低雑音増幅器(LNA)、ダウンコンバートミキサ、電圧制御器オシレータ(VCO)、低域フィルタ(LPF)、シンセサイザループ、基準発生器、アナログデジタルコンバータ(ADC)、および復調器を有し得るデジタル信号処理装置(DSP)を含むことができる。アーキテクチャ内のこうしたRFユニットのブロック、およびアナログベースバンド、および混合信号回路には、一体型受信機設計の設計努力、および実装費用の大部分が費やされることがある。非デジタル回路の使用はまた、プロセス技術が進化し、供給電圧が低減するにつれて、電圧(振幅)ヘッドルームが限られるという問題を生じ得る。

【0003】

大部分のRF、およびアナログベースバンド回路を排除することによって、複雑性を低減させ、ヘッドルーム問題を軽減するように設計された一アーキテクチャでは、アンテナからの入力信号を、LNAによって増幅し、ADCによって直接サンプリングすることができる。アナログ信号処理の大部分は、DSPに委ねられることになり得る。このアーキテクチャでは、ADCに厳格な要件が求められることがある。ADCのサンプリング周波数は、RF搬送周波数のナイキストレートでよく、この周波数は、信号帯域幅よりも高くなり得る。そのため、ADCの設計複雑性、および同期サンプリングクロックの消費電力にオーバーヘッドが生じる結果となり得る。アンダーサンプリング策を採用できる場合でも、余分の雑音がベースバンドに折り込まれることがあり、これによって受信機の信号対雑音比(SNR)が劣化するおそれがある。

【発明の概要】

【発明が解決しようとする課題】

【0004】

したがって、上記の問題を解決するシステムおよび方法を提供することが望ましい。

【課題を解決するための手段】

【0005】

無線周波数デジタル受信機は、第1のレートで信号をサンプリングする変調器を有する。この受信機は、少なくとも1つの処理ユニットを有する。この処理ユニットは、信号を分離し、第1のレートよりも低いレートで信号を再結合する複数のデジタルバンドパスフィルタを有する。この処理ユニットは、周波数オフセットを調整する、または第1のレートよりも低いレートで信号をセンタリングするデジタルダウンコンバータを有する。この受信機は、受信機内に2つ以上の処理ユニットがある場合に、隣接する処理ユニットに結合される少なくとも1つのレート制御バッファを有する。

【0006】

マルチトーンアップコンバータは、信号を受け取るように構成されたデジタルアップコンバータを有する。信号を分離するように構成された複数のデジタルバンドパスフィルタが、デジタルアップコンバータに結合されている。信号を結合するデジタルルータが、複数のバンドパスフィルタに結合されている。信号をアナログ信号に変換するデジタルアナログコンバータが、デジタルルータに結合されている。

【0007】

無線周波数受信機における消費電力を低減させる方法は、信号を受信するステップと、信号をフィルタリングするステップと、第1のレートで信号をサンプリングするステップと、少なくとも1つの処理ユニットにおいて、第1のレートよりも低い処理レートで信号をサブバンドに分離するステップと、サブバンドからの信号を処理レートで再結合するステップと、周波数オフセットを補正する、または処理レートで信号をセンタリングするステップとを含む。

【0008】

上記の特徴、機能、および利点は、本開示の様々な実施形態において独立に実現することも、またはさらに他の実施形態と組み合わせることもできる。

【0009】

本開示の実施形態は、詳細な説明、および添付の図面からより完全に理解されよう。

【図面の簡単な説明】

【0010】

【図1】均質な処理を有する受信機の概略的なアーキテクチャのブロック図である。

【図2】搬送周波数からの信号を、それぞれが処理ユニットによって行われる複数の段階を経てベースバンドに変換する工程を示すグラフである。

【図3】受信機の特定の例のブロック図である。

【図4】受信機の等価な組合せのブロック図である。

【図5】受信機の特定の例のシミュレーション結果のグラフである。

【図6】受信機の動作を示す工程図である。

【図7】RFトーン発生器のブロック図である。

【図8】RFトーン発生器の動作を示す工程図である。

【図9】RFトーン発生器のシミュレーション結果のグラフである。

【発明を実施するための形態】

【0011】

図1を参照すると、均質な処理を有する受信機100の概略的なアーキテクチャのブロック図を示すことができる。受信機100は、低電力無線周波数(RF)デジタルベースバンド設計を有することができる。受信機100について、モバイルプラットフォームに関して以下で説明することができる。受信機100は、入来したRF通信を処理するスマートフォン、携帯電話などの中に配置することができる。受信機100はまた、ソフトウェア無線(SDR)、スマート無線、車載通信、車両用インフォテインメント(infotainment)などに使用することができる。

【0012】

受信機100は、バンドパスフィルタリング、サンプリング、ダウンコンバート、およびデシメーションの工程を、複雑性が低く、かつ電力効率が良い形で実施することができる。RF、デジタル領域、およびアナログ領域にわたる、いくつかのビルディングブロックからなり、デジタル回路において非常に高速のクロックレートで作動し得る既存の手法とは異なり、受信機100は、マルチレートデジタル信号処理(MDSP)と、バンドパス連続時間デルタシグマアナログデジタルコンバータ(BP−CT−ΔΣ−ADC)との組合せを利用して、上記の工程を、対象となる信号帯域幅のクロックレートで作動するストリームライン、およびトランスペアレントな機構において実行することができる。上記により、従来のアーキテクチャに比べて、信号の入力からデータの出力までの待ち時間がより短く、必要となるビルディングブロックの数がより少数に、かつ消費電力をより低減させることができる。さらに、この設計によって、アナログデジタルコンバータ(ADC)に課される厳格な要件を除去することができる。受信機100は、アナログ回路、またはデジタル回路のいずれかのビルディングブロックを有することができ、したがってRF回路が減少し、その結果受信機100は、現代の超大規模集積回路(VLSI)技術におけるプロセス変動に耐えるものとなる。

【0013】

受信機100は、RF領域において任意のバンドパスフィルタリング(BPF)を実施することができる。図1に示す実施形態では、受信機100は、フィルタリングしたRF信号をデジタル領域にダウンコンバートすることができる。受信機100は、混合信号回路設計策を使用し、信号をナイキストレートで処理することができる。受信機100は、低消費電力、および低複雑性設計という重要な利点を実現することができる。受信機100は、MDSP、およびBP−CT−ΔΣ−ADC104の技術に基づくことができる。

【0014】

受信機100は、搬送周波数の倍数のレートで信号を処理するのではなく、信号帯域幅をカバーするレートで信号を取り扱うことができる。処理レートのこうした低減によって、処理帯域幅を節減し、全体的な消費電力を低減させることができる。低電力RFデジタルベースバンド受信機100はまた、ソフトウェア定義のモジュールによって、所望の入力周波数領域、および出力データレートにプログラミングし、かつ調整することができるビルディングブロックを有することができる。受信機100のMDSP部分は、マルチトーンアップコンバータになるように構成変更することができ、このコンバータは、受信機100の動作の始めの較正工程用のトーン発生器として働くことができる。

【0015】

図1に示す実施形態では、入来したRF信号は、アンテナを介して導入することができ、アンテナは図示されていない。アンテナは、電波を受信し、それらの電波を電流に変換することができる。アンテナは、増幅器102に結合することができる。増幅器102は、低雑音増幅器(LNA)102でよく、受信機100のアンテナによって受信した信号の出力を増大させることができる。

【0016】

LNA102は、変調器104に結合することができる。変調器104は、増幅器102から信号を受け取ることができる。図1に示す実施形態では、変調器104は、BP−CT−ΔΣ−ADC104Aでよく、信号をフィルタリングし、サンプリングすることによって、信号を処理することができる。信号をデジタル領域に持ち込むことによって、BP−CT−ΔΣ−ADC104Aは、雑音排除性、堅牢性、および融通性を実現することができ、性能、消費電力、およびコスト削減を向上させる可能性をもたらすことができる。BP−CT−ΔΣ−ADC104Aは、消費電力、およびチップ面積を低く保持しながら、高速動作を可能とすることができる。フィルタリングした信号のサンプルを、BP−CT−ΔΣ−ADC104Aの出力で、レートFin_kで生成することができ、Xk(n)として示す。この出力は、高度のプログラミング性を提供することができ、マルチスタンダードRF受信機100にとって理想的となり得る。

【0017】

BP−CT−ΔΣ−ADC104Aは、LNA102が受け取った入来信号をベースバンドにダウンコンバートすることができる。変調器104は、狭帯域信号に対してバンドパスADCを実施するのに適し得る。フィルタリングした信号を、変調器104の連続時間デルタシグマ(CT−ΔΣ)部分によってデジタル化することができる。BP−CT−ΔΣ−ADC104Aは、入力信号を混合し、デジタル化することができ、この信号にはLNA102による増幅が必要となり得る。BP−CT−ΔΣ−ADC104Aは、フィードバックに正弦波パルスの整数を利用することができる。フィードバックベースの関数は、本質的にバンドパスとなり得る。上記によって、時間遅延ジッタ、およびパルス幅ジッタの存在下でも、変調器104の性能を大幅に改善することができる。また、変調器104のサンプリング周波数は、変調器104を同調させる中央周波数よりも低くてよい。

【0018】

図1の実施形態に示すように、変調器104は、デジタル多相フィルタ(DPF)106に結合することができる。DPF106は、BP−CT−ΔΣ−ADC104Aの出力を受け取ることができ、この出力はXk(n)であった。DPF106は、信号をダウンコンバートし、かつデシメーションするMDSPを実施することができる。フィルタ106は、入力信号Xk(n)を、係数Mでサブサンプリングされたいくつかの等間隔サブバンド120に分割することができ、したがってクリティカルにサンプリングすることができる。サブバンド120は、入力信号Xk(n)を複数の成分に分離するバンドパス有限長フィルタ(FLF)120のアレイでよく、これらのフィルタはそれぞれ、元の信号を異なるフィルタ係数でフィルタリングする。例えば、フィルタ係数は、Hn(zej(θk+...))とすることができる。図1に示すように、第1のフィルタ係数は、H0(zej(θk+...))とすることができる。DPF106は、結合器122を介して、サブバンド120からの信号をレートFout_kで再結合することができる。Fout_kは、Fin_kとは異ならせることができ、Fout_kは、Fin_kよりも低いレートにすることができる。

【0019】

DPF106のバンドパスフィルタ120はそれぞれ、レートFout_kで動作することができる。Fout_kは、対象となる信号帯域幅よりも大きくてよい。Fout_kは通常、Fin_kよりも遙かに小さくすることができ、Fin_kは、Fout_kの倍数となるように選択することができる。FLF120の個数は、Mによって示され、Fin_kのFout_kに対する比として定義することができる。DPF106には、総数M個のサブFLF120があってもよく、それぞれがレートFout_kで作動する。BP−CT−ΔΣ−ADC104Aの出力Xk(n)は、信号の分離を示す点線によって示されるように、各サブバンド120に時間多重化される。図2は、搬送周波数からの信号を、それぞれが処理ユニット(PU)110によって行われる複数の段階を(上から下へと)経てベースバンドに変換する工程を示すグラフである。DPF106によって有限インパルス応答(FIR)を使用して、入来信号Xk(n)からサンプルを取ることができる。次いで、FLF120からの出力を、結合器122で、レートFout_kで結合することができる。

【0020】

図1に示す実施形態では、DPF106をデジタルダウンコンバータ(DDC)108に結合することができ、どちらもレートFout_kで動作することができる。DDC108は、DPF106の出力を、中間周波数(IF)でセンタリングされたデジタル化実信号、またはゼロ周波数でセンタリングされたベースバンド複素信号に変換することができる。次いで、受信機100のDDC108は、レートFout_kで出力yk(nMk)を供給することができる。

【0021】

受信機100は、デバイス自体の中に配置することも、または複数のDPF106、およびDDC108が、増幅器102、および変調器104とともに直列に存在し得る均質なPU110ベースのアーキテクチャの一部とすることもできる。図示の一実施形態では、BP−CT−ΔΣ−ADC104Aは、第1のPU110、すなわちPU1に結合し、次いで多数の他のPU110に結合することができる。各PU110は、信号を処理することができる。レート変換バッファ(RCB)112を、受信機100内のPU110間に結合することができる。RCB112を用いて、あるサンプルレートの信号を操作し、その信号を新しいサンプルレートに変換することができる。PU110の個数と、RCB112の個数とは、調整することができる。PU110とRCB112との組合せによって、デジタル出力を供給することができる。

【0022】

図1に示すように、受信機100は、1つのPU110、または多数のPU110を有することができる。PU110はそれぞれ、複数のデジタルバンドパスフィルタ120をDPF106内に有することができる。複数のデジタルバンドパスフィルタ120は、レートFin_kで入来した信号を分離し、入来信号のレートFin_kよりも低いレートFout_kで、その信号を再結合することができる。Fin_kとFout_kとは、PU110ごとに異なってもよい。PU110内のDDC108は、周波数オフセットを調整する、または入来信号のレートFout_kよりも低いレートで信号をセンタリングすることができる。受信機100内に2つ以上のPU110がある場合、少なくとも1つのRCB112を、隣接するPU110に結合することができる。

【0023】

受信機100は、制御器140を含むことができる。制御器140は、2つ以上のPU110が動作している場合に、受信機100に組み込むことができる。図1内に示すように、制御器140は、受信機100内の各PU110、および各RCB112に結合することができる。この接続によって、PU110、およびRCB112の構成が可能となる。構成時に、信号を処理するレートを調整することができる。

【0024】

制御器140は、ソフトウェア、ハードウェア、または両方の組合せでプログラミングすることができる。ソフトウェア実装では、コードを、非一時的コンピュータ可読記憶媒体に実装することができる。制御器140の非一時的コンピュータ可読記憶媒体には、以下に限られるものではないが、揮発性メモリ、不揮発性メモリ、磁気および光記憶装置、あるいは現時点で既知の、または後に開発される、コードおよび/またはデータを記憶することが可能な他の媒体が含まれ得る。コードは、データ構造およびコードとして具体化され、非一時的コンピュータ可読記憶媒体内に記憶される方法および工程を実施するコンピュータシステムによって読み取り、実行することができる。さらに、制御器140用の方法および工程は、ハードウェアモジュール内に含めることができる。これらのハードウェアモジュールには、特定用途向け集積回路(ASIC)チップ、フィールドプログラマブルゲートアレイ(FPGA)、および現時点で既知の、または後に開発される他のプログラマブルロジックデバイスが含まれ得る。

【0025】

制御器140は、デジタルバンドパスフィルタ120、およびDDC108をセットアップすることによって、各PU110を構成することができる。一実施形態では、PU110、およびRCB112は、別の方法、例えば配線によって構成することができる。制御器140は、現在のPU110が変調器104に結合されている場合、入来レートを現在のPU110の処理レートの倍数として調整し、搬送周波数を現在のPU110の処理レートの倍数として調整することによって、PU110内のDDC108を迂回することができる。あるいは、制御器140は、前のPU110の処理レートを現在のPU110の処理レートの倍数として調整し、中間周波数を現在のPU110の処理レートの倍数として調整することができる。

【0026】

受け取った信号は、各PU110内で時間多重化によって分離することができる。PU110が変調器104と結合されている場合、変調器104からのサンプリング信号を、DPF106の各サブバンド120に供給することができる。そうでない場合は、前のPU110の出力を、現在のPU110のDPF106のサブバンド120に時間多重化することができる。

【0027】

受信機100内に複数のPU110が使用されている場合、総数M個のサブ有限長フィルタ120は、入来レートFin_kよりも低いレートFout_kで作動することができる。Mは、PU110が変調器104の次にある場合、第1のレートの、現在のPU110の処理レートに対する比とすることができる。PU110が変調器104に結合されていない場合、例えばPU2110、PUk110、またはPUN110では、Mは、前のPU110の処理レートの、現在のPU110の処理レートに対する比とすることができる。

【0028】

上述のように、変調器104は、第1のレートで信号を処理することができる。第1のレートは、搬送周波数よりも高くてよい。複数のデジタルバンドパスフィルタ120、およびDDC108を有するPU110は、信号の帯域幅のナイキストレート以上のレートで信号を処理することができる。典型的には、このレートは、搬送周波数よりも低くてよい。

【0029】

各PU110内のDDC108は、同じPU110内のM個のサブ有限長フィルタ120と同じレートで作動し、出力を生成することができる。一実施形態では、処理ユニットが、最後に最終出力を生成する場合、各PU110内のDDC108は、ゼロ周波数で信号をセンタリングすることができる。そうでない場合、DDC108は、周波数オフセットを所望の中間周波数に補正することができる。第1のレートは、搬送周波数よりも大きくてよい。各PU110の処理レートは、信号の帯域幅をカバーすることができ、かつ搬送周波数よりも低くすることができる。

【0030】

次に、図3に移ると、受信機100の特定の例のブロック図を表すことができる。受信機100は、1つのPU110で動作することができる。RF信号は、アンテナによって受信することができ、アンテナは図示されていない。アンテナにLNA102を結合することができる。LNA102は、アンテナから受け取った信号を増大させることができる。変調器104をLNA102に結合することができる。BP−CT−ΔΣ−ADC104Aは、LNA102からの信号をフィルタリングし、サンプリングすることによって、その信号を処理することができる。信号は、第1のレートFSで処理することができる。FSは、搬送周波数の倍数でよい。

【0031】

信号は、変調器104によって処理した後、DPF106に供給することができる。変調器104の出力は、x(n)とすることができる。図3に示す実施形態では、信号は、FLF120によって処理することができる。FLF120は、サブバンドを表すことができ、これらのサブバンドはそれぞれ、元の信号を異なるフィルタ係数でフィルタリングする。例えば、フィルタ係数は、Hn(zej(θk+...))とすることができる。図3に示すように、第1のフィルタ係数は、H0(zej(θk+...))とすることができる。この実施形態では、サブバンド120は、64個の離散ユニットとして表すことができる。例えば、各サブバンド120は、クリティカルサンプリング(critical sampling)として係数64でサンプリングを行うことができる。64個のサブバンド120からの信号を、結合器122によって第2のレートFOUTで再結合することができる。サブバンド120の個数64は、第1のレートFSの、第2のレートFOUTに対する比と同等、またはその比に比例した数とすることができる。再結合した信号をDDC108に供給し、出力y(nM、k)として送信することができる。FSは、搬送周波数の倍数とすることができ、FOUTは、信号の帯域幅をカバーすることができる。

【0032】

DPF106の全体的な動作は、図4の実施形態に示すデジタルバンドパスフィルタ(DBF)402と、M−to−1デジタルデシメータ(DDEC)404との組合せと等価とすることができる。図示のように、信号は、LNA102によってアンテナから受け取ることができる。BP−CT−ΔΣ−ADC104Aは、信号をデジタル化し、PU110のDBF402にその信号を供給することができる。信号x(n)は、上述のレートFSで供給することができる。

【0033】

DBF402は、規定されたパスバンドで信号をフィルタリングする動作を実施することができる。DBF402にDDEC404を結合することができる。DDEC404は、DBF402から受け取った離散時間信号のサンプル数を減少させることができる。DDEC404は、DBF402から受け取った信号をベースバンドに持ち込むことができる。こうした減少はMに比例させることができ、MはFSのFOUTに対する比として規定された数である。次いで、DDEC404に結合されたDDC108によって、信号をレートFOUTでダウンコンバートすることができる。その後、DDC108は、出力y(nM、k)を供給することができる。DBF402とDDEC404との組合せは、DPF106に等価となり得る。DBF402、およびDDEC404は、レートFSで作動することができる。しかし、どちらともより高速のレートFSで作動しているので、レートFOUTで作動している図3のDPF106は、図4のDBF402とDDEC404との組合せよりも消費電力が少ない。

【0034】

各サブバンドまたはFLF120に対するフィルタ係数は、対応するDBF402係数の時間多重化値とすることができる。一実施形態では、DBF402係数は、デジタルローパスフィルタ(DLF)係数を回転させたバージョン、またはアップコンバートしたバージョンとすることができる。DLFは、DBF402と同じフィルタ帯域幅を有することができるが、ベースバンドでダウンコンバートしたサンプルを処理する。回転角度は、θk+Δθとすることができ、θkは、2π×k×FS/Mに等しく、Δθは、搬送周波数(FC)とθkとの差とすることができる。図5は、受信機100のシミュレーション結果のグラフである。このグラフは、BP−CT−ΔΣ−ADC104Aの工程と、DPF106の工程との組合せを示している。

【0035】

図6を参照すると、受信機100の動作を示す工程図を表すことができる。受信機100の工程は、ブロック600から開始することができる。ブロック602で、受信機100のアンテナは、RF信号を受信することができる。ブロック604で、RF信号をLNA102によって増幅することができる。ブロック606で、信号をフィルタリングすることができる。ブロック608で、信号をサンプリングすることができる。信号のフィルタリング、およびサンプリングは、BP−CT−ΔΣ−ADC104Aによって処理することができる。

【0036】

ブロック610で、信号をデジタル多相フィルタで時間多重化することができる。DPF106は、変調器104から受け取ったデジタル化信号をサブバンド120に分離することができる。それらのサブバンド120から、DPF106の結合器122を介して信号を生成することができる。ブロック612で、再結合した信号をダウンコンバートすることができる。次いで、DDC108の出力をさらに処理する、またはデバイスのアプリケーションによって使用することができる。ブロック614で、工程を終了することができる。

【0037】

図7に移ると、RFトーン発生器700を表すことができる。先に説明した受信機100の信号経路を構成変更して、発生器700を設けることができる。RFトーン発生器700は、デジタルアップコンバータ(DUC)702、DPF106、およびデジタルルータ(DR)704を含むことができる。補助デジタルアナログコンバータ(AUX DAC)706を、DR704を介して発生器700に結合することができる。デジタル信号x(nM、k)を、DUC702に供給することができる。DUC702によって、この信号を複素信号と混合し、DPF106にレートFinで供給することができる。

【0038】

図7の実施形態では、受信機100のDPF106、およびDDC108の信号経路を、反対方向に容易に構成変更することができ、したがって受信機100全体を、デジタルアナログコンバータ(DAC)の助けを得て、RFトーン発生器700とすることができる。DPF106の各サブバンド120は、入来信号の一部分を取ることができる。サブバンド120は、DR704に結合することができる。DR704は、サブバンドの出力を単一の信号に多重化することができる。DR704に、AUX DAC706を結合することができる。AUX DAC706は、信号を取り、その信号をアナログの形に変換することができる。この信号を、送信機に供給することができる。送信機は、電気信号をRF通信に変換することができる。レートFinは、RFトーン周波数よりも小さく、したがって消費電力を低減させることができる。

【0039】

図8は、RFトーン発生器700のシミュレーション結果のグラフである。このトーン発生器700の出力は、受信機100の動作の始めの較正工程用の、LNA102またはBP−CT−ΔΣ−ADC104への入力のテスト信号として働くことができる。

【0040】

図9を参照すると、RFトーン発生器700の動作を示す工程図を表すことができる。発生器700の工程は、ブロック900から開始することができる。ブロック902で、発生器700のDUC702は、デジタル信号を受け取ることができる。ブロック904で、DUC702は、そのデジタル化された信号をアップコンバートすることによって、その信号を適切にフォーマットすることができる。ブロック906で、DPF106によって信号を時間多重化することができる。DPF106は、発生器700向けに目的変更することができ、信号をレートFinで分離することができる。

【0041】

ブロック908で、DR704のデジタル多相フィルタを介して、信号をデジタル式にルートすることができる。DR704によって、Finよりも高いレートで信号の再結合を行うことができる。最初の処理段階における処理速度が低速であるため、電力を節減することができる。ブロック910で、AUX DAC706によって信号をアナログ信号に変換することができる。ブロック912で、工程を終了することができる。

【0042】

上記の明細書および図には、第1のレートで信号をサンプリングする変調器104と、少なくとも1つの処理ユニット110であって、信号を分離し、第1のレートよりも低いレートで信号を再結合する複数のデジタルバンドパスフィルタ120と、周波数オフセットを調整する、または第1のレートよりも低いレートで信号をセンタリングするデジタルダウンコンバータ108とを含む少なくとも1つの処理ユニット110と、受信機100内に2つ以上の処理ユニット110がある場合に、隣接する処理ユニット110に結合される少なくとも1つのレート制御バッファとを含む、無線周波数デジタル受信機100が開示されている。

【0043】

一変形形態では、無線周波数デジタル受信機100は、受信機100内に2つ以上の処理ユニット110がある場合に、少なくとも1つの処理ユニット110と、少なくとも1つのレート制御バッファとの間の接続部を構成する制御器140を含む。さらに別の変形形態では、無線周波数デジタル受信機100は、変調器104が信号を受け取る前に、信号を受け取り、増幅する増幅器102を含む。さらに別の変形形態では、変調器104は、バンドパス連続時間デルタシグマアナログデジタルコンバータである。さらに別の変形形態では、各処理ユニット110内の複数のデジタルバンドパスフィルタ120は、デジタル多相フィルタ106の形で設けられる。

【0044】

一代替形態では、各処理ユニット110内の複数のデジタルバンドパスフィルタ120は、それぞれが第1のレートよりも低いレートで作動する総数M個のサブ有限長フィルタを含み、現在の処理ユニット110が変調器104の次にある場合、Mは、第1のレートの、現在の処理ユニット110の処理レートに対する比であり、そうでない場合、Mは、前の処理ユニット110の処理レートの、現在の処理ユニット110の処理レートに対する比である。別の代替形態では、各処理ユニット110内のM個のサブ有限長フィルタに対する入力は、現在の処理ユニット110が変調器104の次にある場合、変調器104の時間多重化出力によって供給され、そうでない場合、前の処理ユニット110の時間多重化出力によって供給される。

【0045】

別の変形形態では、変調器104は、搬送周波数よりも高い第1のレートで信号を処理し、各処理ユニット110内の複数のデジタルバンドパスフィルタ120、およびデジタルダウンコンバータ108は、信号の帯域幅のナイキストレート以上であるが、搬送周波数よりも低いレートで信号を処理する。さらに別の変形形態では、各処理ユニット110内のデジタルダウンコンバータ108は、同じ処理ユニット110内のM個のサブ有限長フィルタと同じレートで作動し、処理ユニット110の出力を生成する。一例では、各処理ユニット110内のデジタルダウンコンバータ108は、処理ユニット110が最後に最終出力を生成する場合、ゼロ周波数で信号をセンタリングし、そうでない場合、周波数オフセットを所望の中間周波数に補正する。さらに別の代替形態では、第1のレートは、搬送周波数よりも大きく、各処理ユニット110の処理レートは、信号の帯域幅をカバーし、かつ搬送周波数よりも低い。

【0046】

一態様では、信号を受け取るデジタルアップコンバータ702と、デジタルアップコンバータ702に結合され、信号を分離する複数のデジタルバンドパスフィルタ120と、複数のデジタルバンドパスフィルタ120に結合され、信号を結合するデジタルルータと、デジタルルータに結合され、信号をアナログ信号に変換するデジタルアナログコンバータ706とを含む、マルチトーンアップコンバータが開示されている。一変形形態では、較正のために、信号が、無線周波数デジタル受信機100内の低雑音増幅器102、または変調器104にテスト信号として供給される。別の変形形態では、マルチトーンアップコンバータは、無線周波数デジタル受信機100を含む。一変形形態では、デジタルアップコンバータ702、および複数のデジタルバンドパスフィルタ120が、無線周波数デジタル受信機100内の処理ユニット110として再利用される。一代替形態では、無線周波数デジタル受信機100は、第1のレートで信号をサンプリングする変調器104と、複数の処理ユニット110であって、それぞれが信号を分離し、第1のレートよりも低いレートで信号を再結合する複数のデジタルバンドパスフィルタ120と、周波数オフセットを調整する、または信号をセンタリングするデジタルダウンコンバータ108とを含む複数の処理ユニット110と、隣接する処理ユニット110に結合される少なくとも1つのレート制御バッファと、各処理ユニット110とレート制御バッファとの間の接続部を構成する制御器140とを含む。

【0047】

一態様では、無線周波数デジタル受信機100における消費電力を低減させる方法であって、信号を受信するステップと、信号をフィルタリングするステップと、第1のレートで信号をサンプリングするステップと、少なくとも1つの処理ユニット110において、第1のレートよりも低い処理レートで、信号をサブバンド120に分離するステップと、サブバンド120からの信号を処理レートで再結合するステップと、周波数オフセットを補正する、または処理レートで信号をセンタリングするステップとを含む、方法が開示されている。

【0048】

一変形形態では、この方法は、処理ユニット110内のデジタルダウンコンバータ108を迂回するステップであって、現在の処理ユニット110が変調器104に結合されている場合、第1のレートを現在の処理ユニット110の処理レートの倍数として調整し、搬送周波数を現在の処理ユニット110の処理レートの倍数として調整することによって迂回し、そうでない場合、前の処理ユニット110の処理レートを現在の処理ユニット110の処理レートの倍数として調整し、中間周波数を現在の処理ユニット110の処理レートの倍数として調整することによって迂回するステップを含む。

【0049】

一変形形態では、信号を分離するステップは、現在の処理ユニット110が変調器104に結合されている場合、サンプリングした信号を、各サブバンド120に時間多重化するステップを含み、そうでない場合、前の処理ユニット110の出力を、現在の処理ユニット110内の各サブバンド120に時間多重化するステップを含む。さらに別の変形形態では、この方法は、処理ユニット110内の複数のデジタルバンドパスフィルタ120、およびデジタルダウンコンバータ108を、制御器140を介してセットアップすることによって各処理ユニット110を構成するステップ、または処理ユニット110内の複数のデジタルバンドパスフィルタ120、およびデジタルダウンコンバータ108を、制御器140を介して迂回するステップを含むことができる。

【0050】

本開示の実施形態を、様々な特定の実施形態に関して説明してきたが、本開示の実施形態は、特許請求の範囲の趣旨および範囲に包含される改変形態で実践できることが当業者には認識されよう。

【符号の説明】

【0051】

100 無線周波数デジタル受信機

102 増幅器

104 変調器

106 デジタル多相フィルタ

108 デジタルダウンコンバータ

110 処理ユニット

112 レート変換バッファ

120 デジタルバンドパスフィルタ

122 結合器

140 制御器

402 デジタルバンドパスフィルタ

404 デジタルデシメータ

700 RFトーン発生器

702 デジタルアップコンバータ

704 デジタルルータ

706 補助デジタルアナログコンバータ

【特許請求の範囲】

【請求項1】

第1のレートで信号をサンプリングする変調器(104)と、

少なくとも1つの処理ユニット(110)であって、

前記信号を分離し、前記第1のレートよりも低いレートで前記信号を再結合する、複数のデジタルバンドパスフィルタ(120)と、

周波数オフセットを調整する、または前記第1のレートよりも低いレートで前記信号をセンタリングするデジタルダウンコンバータ(108)と

を備える、少なくとも1つの処理ユニット(110)と、

前記受信機(100)内に2つ以上の処理ユニット(110)がある場合に、隣接する処理ユニット(110)に結合される少なくとも1つのレート制御バッファと

を備える、無線周波数デジタル受信機(100)。

【請求項2】

前記受信機(100)内に2つ以上の処理ユニット(110)がある場合に、前記少なくとも1つの処理ユニット(110)と、前記少なくとも1つのレート制御バッファとの間の接続部を構成する制御器(140)を備える、請求項1に記載の無線周波数デジタル受信機(100)。

【請求項3】

前記変調器(104)が前記信号を受け取る前に、前記信号を受け取り、増幅する増幅器(102)をさらに備える、請求項1または2に記載の無線周波数デジタル受信機(100)。

【請求項4】

前記変調器(104)が、バンドパス連続時間デルタシグマアナログデジタルコンバータである、請求項1ないし3のいずれか一項に記載の無線周波数デジタル受信機(100)。

【請求項5】

各処理ユニット(110)内の前記複数のデジタルバンドパスフィルタ(120)が、デジタル多相フィルタ(106)の形で設けられる、請求項1ないし4のいずれか一項に記載の無線周波数デジタル受信機(100)。

【請求項6】

各処理ユニット(110)内の前記複数のデジタルバンドパスフィルタ(120)が、それぞれが前記第1のレートよりも低いレートで作動する総数M個のサブ有限長フィルタを備え、現在の処理ユニット(110)が前記変調器(104)の次にある場合、Mは、前記第1のレートの、前記現在の処理ユニット(110)の処理レートに対する比であり、そうでない場合、Mは、前の処理ユニット(110)の処理レートの、前記現在の処理ユニット(110)の前記処理レートに対する比である、請求項1ないし5のいずれか一項に記載の無線周波数デジタル受信機(100)。

【請求項7】

無線周波数デジタル受信機(100)における消費電力を低減させる方法であって、

信号を受信するステップと、

前記信号をフィルタリングするステップと、

第1のレートで前記信号をサンプリングするステップと、

少なくとも1つの処理ユニット(110)において、

前記第1のレートよりも低い処理レートで前記信号をサブバンド(120)に分離するステップと、

前記サブバンド(120)からの前記信号を前記処理レートで再結合するステップと、

波数オフセットを補正する、または前記処理レートで前記信号をセンタリングするステップと

を含む、方法。

【請求項8】

処理ユニット(110)内のデジタルダウンコンバータ(108)を迂回するステップであって、現在の処理ユニット(110)が変調器(104)に結合されている場合、前記第1のレートを前記現在の処理ユニット(110)の処理レートの倍数として調整し、搬送周波数を前記現在の処理ユニット(110)の前記処理レートの倍数として調整することによって迂回し、そうでない場合、前の処理ユニット(110)の処理レートを前記現在の処理ユニット(110)の前記処理レートの倍数として調整し、中間周波数を前記現在の処理ユニット(110)の前記処理レートの倍数として調整することによって迂回するステップを含む、請求項7に記載の、無線周波数デジタル受信機(100)における消費電力を低減させる方法。

【請求項9】

前記信号を分離するステップが、現在の処理ユニット(110)が変調器(104)に結合されている場合、前記サンプリングした信号を、各サブバンド(120)に時間多重化し、そうでない場合、前の処理ユニット(110)の出力を、前記現在の処理ユニット(110)内の各サブバンド(120)に時間多重化するステップを含む、請求項7に記載の、無線周波数デジタル受信機(100)における消費電力を低減させる方法。

【請求項10】

処理ユニット(110)内の複数のデジタルバンドパスフィルタ(120)、およびデジタルダウンコンバータ(108)を、制御器(140)を介してセットアップすることによって各処理ユニット(110)を構成するステップ、または前記処理ユニット(110)内の前記複数のデジタルバンドパスフィルタ(120)、および前記デジタルダウンコンバータ(108)を、前記制御器(140)を介して迂回するステップを含む、請求項7ないし9のいずれか一項に記載の、無線周波数デジタル受信機(100)における消費電力を低減させる方法。

【請求項1】

第1のレートで信号をサンプリングする変調器(104)と、

少なくとも1つの処理ユニット(110)であって、

前記信号を分離し、前記第1のレートよりも低いレートで前記信号を再結合する、複数のデジタルバンドパスフィルタ(120)と、

周波数オフセットを調整する、または前記第1のレートよりも低いレートで前記信号をセンタリングするデジタルダウンコンバータ(108)と

を備える、少なくとも1つの処理ユニット(110)と、

前記受信機(100)内に2つ以上の処理ユニット(110)がある場合に、隣接する処理ユニット(110)に結合される少なくとも1つのレート制御バッファと

を備える、無線周波数デジタル受信機(100)。

【請求項2】

前記受信機(100)内に2つ以上の処理ユニット(110)がある場合に、前記少なくとも1つの処理ユニット(110)と、前記少なくとも1つのレート制御バッファとの間の接続部を構成する制御器(140)を備える、請求項1に記載の無線周波数デジタル受信機(100)。

【請求項3】

前記変調器(104)が前記信号を受け取る前に、前記信号を受け取り、増幅する増幅器(102)をさらに備える、請求項1または2に記載の無線周波数デジタル受信機(100)。

【請求項4】

前記変調器(104)が、バンドパス連続時間デルタシグマアナログデジタルコンバータである、請求項1ないし3のいずれか一項に記載の無線周波数デジタル受信機(100)。

【請求項5】

各処理ユニット(110)内の前記複数のデジタルバンドパスフィルタ(120)が、デジタル多相フィルタ(106)の形で設けられる、請求項1ないし4のいずれか一項に記載の無線周波数デジタル受信機(100)。

【請求項6】

各処理ユニット(110)内の前記複数のデジタルバンドパスフィルタ(120)が、それぞれが前記第1のレートよりも低いレートで作動する総数M個のサブ有限長フィルタを備え、現在の処理ユニット(110)が前記変調器(104)の次にある場合、Mは、前記第1のレートの、前記現在の処理ユニット(110)の処理レートに対する比であり、そうでない場合、Mは、前の処理ユニット(110)の処理レートの、前記現在の処理ユニット(110)の前記処理レートに対する比である、請求項1ないし5のいずれか一項に記載の無線周波数デジタル受信機(100)。

【請求項7】

無線周波数デジタル受信機(100)における消費電力を低減させる方法であって、

信号を受信するステップと、

前記信号をフィルタリングするステップと、

第1のレートで前記信号をサンプリングするステップと、

少なくとも1つの処理ユニット(110)において、

前記第1のレートよりも低い処理レートで前記信号をサブバンド(120)に分離するステップと、

前記サブバンド(120)からの前記信号を前記処理レートで再結合するステップと、

波数オフセットを補正する、または前記処理レートで前記信号をセンタリングするステップと

を含む、方法。

【請求項8】

処理ユニット(110)内のデジタルダウンコンバータ(108)を迂回するステップであって、現在の処理ユニット(110)が変調器(104)に結合されている場合、前記第1のレートを前記現在の処理ユニット(110)の処理レートの倍数として調整し、搬送周波数を前記現在の処理ユニット(110)の前記処理レートの倍数として調整することによって迂回し、そうでない場合、前の処理ユニット(110)の処理レートを前記現在の処理ユニット(110)の前記処理レートの倍数として調整し、中間周波数を前記現在の処理ユニット(110)の前記処理レートの倍数として調整することによって迂回するステップを含む、請求項7に記載の、無線周波数デジタル受信機(100)における消費電力を低減させる方法。

【請求項9】

前記信号を分離するステップが、現在の処理ユニット(110)が変調器(104)に結合されている場合、前記サンプリングした信号を、各サブバンド(120)に時間多重化し、そうでない場合、前の処理ユニット(110)の出力を、前記現在の処理ユニット(110)内の各サブバンド(120)に時間多重化するステップを含む、請求項7に記載の、無線周波数デジタル受信機(100)における消費電力を低減させる方法。

【請求項10】

処理ユニット(110)内の複数のデジタルバンドパスフィルタ(120)、およびデジタルダウンコンバータ(108)を、制御器(140)を介してセットアップすることによって各処理ユニット(110)を構成するステップ、または前記処理ユニット(110)内の前記複数のデジタルバンドパスフィルタ(120)、および前記デジタルダウンコンバータ(108)を、前記制御器(140)を介して迂回するステップを含む、請求項7ないし9のいずれか一項に記載の、無線周波数デジタル受信機(100)における消費電力を低減させる方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−81162(P2013−81162A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−200461(P2012−200461)

【出願日】平成24年9月12日(2012.9.12)

【出願人】(500520743)ザ・ボーイング・カンパニー (773)

【氏名又は名称原語表記】The Boeing Company

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2012−200461(P2012−200461)

【出願日】平成24年9月12日(2012.9.12)

【出願人】(500520743)ザ・ボーイング・カンパニー (773)

【氏名又は名称原語表記】The Boeing Company

【Fターム(参考)】

[ Back to top ]