保護回路の実装構造

【目的】 実装面積が小さく、配線インダクタンスが小さく、かつ、放熱性が良好な保護回路の実装手段を提供する。

【構成】 主プリント配線板1と補助プリント配線板2を平行に配置し、プリント配線板1,2とほぼ垂直にして両プリント配線板1,2間にダイオード3及び複数個のツェナーダイオード4〜8を実装し、プリント配線板1,2のプリント配線によってダイオード3及びツェナーダイオード4〜8を直列に接続する。このダイオード3及びツェナーダイオード4〜8によりスナバ回路を構成する。

【構成】 主プリント配線板1と補助プリント配線板2を平行に配置し、プリント配線板1,2とほぼ垂直にして両プリント配線板1,2間にダイオード3及び複数個のツェナーダイオード4〜8を実装し、プリント配線板1,2のプリント配線によってダイオード3及びツェナーダイオード4〜8を直列に接続する。このダイオード3及びツェナーダイオード4〜8によりスナバ回路を構成する。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、保護回路の実装構造に関する。具体的にいうと、本発明は、電力用半導体素子を保護するための保護回路の実装構造に関する。

【0002】

【背景技術とその問題点】従来より、スイッチング電源やDC/DCコンバーター等の小型の電源装置においては、スイッチング素子を保護するためのスナバ回路(サージ吸収回路)が使用されている。

【0003】図2は抵抗33、コンデンサ34及びダイオード35によって構成されたスナバ回路を備えたDC/DCコンバータを示す回路図である。このスナバ回路は、抵抗33とコンデンサ34の並列体にダイオード35を直列に接続したものであり、変圧器32の一次側の端子間に接続されている。また、ダイオード35は直流電源(図示せず)に対し逆バイアス方向に接続されている。この回路にあっては、MOSFET31がターンオフした瞬間に変圧器32に蓄積されていたエネルギーはコンデンサ34に移され、抵抗33で消費される。これにより、MOSFET31がターンオフした瞬間におけるドレイン−ソース間電圧の急激な上昇が防止され、MOSFET31が保護される。

【0004】このようなスナバ回路を具体化してプリント配線板に実装する場合、従来にあっては、1枚のプリント配線板上に平面的あるいは2次元的に実装されていた。しかも、装置の小型化を目的としてチップ抵抗を用いてスナバ回路を構成する場合には、チップ抵抗の定格電力が小さいために複数個のチップ抵抗を用いる必要があり、図3(a)に示すようにプリント配線板39の配線パターン間40,41に多数のチップ抵抗38を配列し、例えば図3(b)のような回路となるようにチップ抵抗38を接続していた。例えば、電気抵抗R(Ω),定格電力P(W)の2個の抵抗33を定格電力P/5(W)のチップ抵抗38で実装する場合には、図3(b)に示すように、電気抵抗5R(Ω)のチップ抵抗38を5個並列に接続した並列体を2組直列に接続しなければならなかった。

【0005】このため、チップ抵抗を用いた場合には、抵抗の実装面積が増大するという不都合があった。また、このように多くのチップ抵抗を直列及び並列に接続すると、配線距離が長くなるために配線インダクタンスが増大し、高周波・高速スイッチング素子の保護には適さなかった。さらには、チップ抵抗の熱を1枚のプリント配線板から放熱させなければならないので、放熱効率が悪いという問題もあった。

【0006】また、図4はツェナーダイオード36とダイオード37によって構成されたスナバ回路を備えたDC/DCコンバーターを示す回路図である。このスナバ回路は、ツェナーダイオード36とダイオード37の直列体であり、ツェナーダイオード36は直流電源(図示せず)に対し順バイアス方向に接続されており、ダイオード37は直流電源(図示せず)に対し逆バイアス方向に接続されている。このスナバ回路を用いることにより、変圧器32の一次側の端子間の電圧はツェナーダイオード36の動作電圧以下に制限される。これにより、MOSFET31のドレイン−ソース間に掛かる電圧は安全動作領域に制限され、MOSFET31が保護される。

【0007】つぎに、DC/DCコンバータに用いた場合の上記スナバ回路の働きを具体的に説明する。図5はDC/DCコンバータの一例を示す回路図、図6(a)(b)(c)はそれぞれ図5のDC/DCコンバータ(スナバ回路を設けられていないもの)における一次側回路に設けられたMOSFET31の電圧、一次側回路に流れる電流IPおよび二次側回路ISに流れる電流を示すタイムチャートである。まず、図5のような構成のDC/DCコンバータにおけるスナバ回路を設けられていない場合の動作を説明する。一次側回路のMOSFET31がオンになる(時間T1)と、一次側回路に電流IPが流れ出す。この後、MOSFET31がオフになると、MOSFET31のソース−ドレイン間電圧VDSが急上昇し、同時に一次側回路の電流IPが減少する(時間T2)。一次側回路の電流IPが減少すると、相互インダクタンスによって二次側回路に電流ISが流れ、同時に、自己インダクタンスによって一次側のMOSFET31のソース−ドレイン間電圧VDSにスパイク電圧VPKが発生する。

【0008】これに対し、図5に想像線によって示したように、一次側回路にダイオード37とツェナーダイオード36からなるスナバ回路を設けると、スナバ回路を通ってMOSFET31のドレイン側から直流電源側へ電流が流れてスパイク電圧VPKがカットされる。

【0009】しかしながら、このようなスナバ回路を具体化して配線基板に実装する場合も、従来にあっては、1枚の配線基板上に平面的あるいは2次元的に実装されていた。このため、電力用のパワーツェナーダイオードを使用しなければならない場合には、部品形状が大きくなり、実装面積が大きくなるという問題があった。

【0010】

【発明が解決しようとする課題】本発明は、叙上の従来例の欠点に鑑みてなされたものであり、その目的とするところは、実装面積が著しく小さく、配線インダクタンスが小さく、かつ、放熱性の良好な保護回路の実装構造を提供することにある。

【0011】

【課題を解決するための手段】本発明の保護回路の実装構造は、電力用半導体素子を保護するための保護回路の実装構造であって、第1のプリント配線板に対向させて第2のプリント配線板を配置し、前記保護回路を構成するための部品を両プリント配線板間に略垂直に配設し、第1及び第2のプリント配線板の配線パターンによって前記部品を接続して保護回路を形成したことを特徴としている。

【0012】

【作用】本発明の保護回路の実装構造にあっては、対向させた第1及び第2のプリント配線板間に略垂直に保護回路部品を配設しているので、保護回路部品の実装面積を小さくすることができる。

【0013】また、保護回路部品の両端に設けられた2枚のプリント配線板に保護回路の配線を分離して形成することができるので、保護回路の配線の長さを短くすることができ、配線インダクタンスを減少させることができる。従って、高周波・高速スイッチング素子の保護回路としても好適となる。

【0014】さらに、保護回路部品の両端にそれぞれプリント配線板が配置されているので、双方のプリント配線板から放熱させることができ、保護回路を構成する部品の放熱性が良好となり、保護回路の熱設計が容易になる。

【0015】

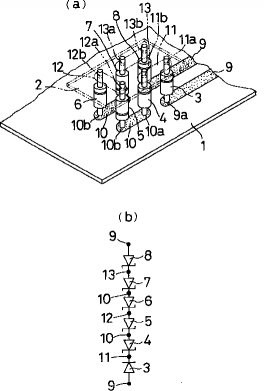

【実施例】図1(a)は本発明の一実施例による保護回路の実装構造を示す斜視図、図1(b)は図1(a)の電気回路図である。本実施例の保護回路の実装構造にあっては、主プリント配線板1に補助プリント配線板2を平行に配置し、ダイオード3と複数個のツェナーダイオード4,5,6,7,8を2枚のプリント配線板1,2の間に垂直に立てて実装してある。複数個のツェナーダイオード4〜8は配線パターンによって全て同方向に直列に接続してあり、ダイオード3はこれらと逆方向に直列に接続してある。ここで、複数個のツェナーダイオード4〜8を直列に接続して用いているのは、大電力用のパワーツェナーダイオードを1個使用するよりも、小容量のツェナーダイオードを複数個使用するほうが、全体としての実装面積を小さくできるからである。したがって、例えば定格電力P(W),動作電圧VZD(V)のパワーツェナーダイオードを1個使用する場合には、定格電力P/n(W)以上,動作電圧VZD/n(V)の小容量のツェナーダイオードをn個直列に接続して使用する。以下、この実施例を図面に基づき、さらに詳細に説明する。

【0016】主プリント配線板1の表面には、帯状をした端子電極9と短冊状をした接続電極10を一直線上に形成してあり、これらを2列平行に形成してある。端子電極9,9の端部には端子孔9a,9aを形成してあり、接続電極10,10の両端部には端子孔10a,10b,10a,10bを形成してある。

【0017】一方、補助プリント配線板2には短冊状をした3個の接続電極11,12,13を形成してある。接続電極11,13は端子電極9,9の間隔と同じ間隔で平行に形成してあり、接続電極12は接続電極11,13の端部から一定の距離を隔てて接続電極11,13と直角に形成してある。また、接続電極11,12,13の両端部には端子孔11a,11b;12a,12b;13a,13bを形成してある。

【0018】ここで、接続電極11の端子孔11a,11b間の距離は端子電極9の端子孔9aと接続電極10の端子孔10aの間の距離に等しくしてあり、接続電極12の端子孔12a,12b間の距離は接続電極10,10の端子孔10b,10b間の距離に等しくしてある。また、接続電極13の端子孔13a,13b間の距離は接続電極10の端子孔10aと端子電極9の端子孔9aの間の距離に等しくしてある。

【0019】しかして、端子孔11aと端子孔9aには、ダイオ−ド3のカソード側の端子とアノード側の端子をそれぞれ挿入して半田付けしてある。

【0020】端子孔11bと端子孔10aには、ツェナーダイオード4のカソード側の端子とアノード側の端子をそれぞれ挿入して半田付けしてある。

【0021】端子孔12aと端子孔10bには、ツェナーダイオード5のアノード側の端子とカソード側の端子をそれぞれ挿入して半田付けしてある。

【0022】端子孔12bと端子孔10bには、ツェナーダイオード6のカソード側の端子とアノード側の端子をそれぞれ挿入して半田付けしてある。

【0023】端子孔13aと端子孔10aには、ツェナーダイオード7のアノード側の端子とカソード側の端子をそれぞれ挿入して半田付けしてある。

【0024】端子孔13bと端子孔9aには、ツェナーダイオード8のカソード側の端子とアノード側の端子をそれぞれ挿入して半田付けしてある。

【0025】こうして主プリント配線板1と補助プリント配線板2との間に実装されたダイオード3及び各ツェナーダイオード4〜8は、両プリント配線板1,2の端子電極9及び接続電極10〜13によって図1(b)に示すように直列に接続される。しかも、ダイオード3及び各ツェナーダイオード4〜8は、両プリント配線板1,2間に略垂直に立てた状態で実装されているので、プリント配線板1,2上における実装面積(占有面積)を小さくできる。

【0026】また、回路配線(配線パターン)を主プリント配線板1と補助プリント配線板2とに分けて立体的に構成することができるので、回路配線の長さを最短にすることができ、配線インダクタンスを小さくすることができる。さらに、ダイオード3やツェナーダイオード4〜8で発生した熱は、プリント配線板1,2へ伝わり、両側のプリント配線板1,2から放熱されるので、放熱面積が大きくなり、放熱性が良好となる。

【0027】

【発明の効果】本発明によれば、第1及び第2のプリント配線板間に略垂直に保護回路部品を実装することにより保護回路部品の実装面積を小さくすることができる。また、2枚のプリント配線板に回路配線を分離して形成できるので、回路配線の長さを短くして配線インダクタンスを減少させることができ、高周波・高速スイッチング素子の保護回路としても好適となる。さらに、放熱面積の増大により保護回路を構成する部品の放熱性が良好となり、保護回路の熱設計を容易にすることができる。

【図面の簡単な説明】

【図1】(a)は本発明の一実施例によるスナバ回路の実装構造を示す斜視図、(b)は(a)のスナバ回路を表わした電気回路図である。

【図2】スナバ回路の一例を示す電気回路図である。

【図3】(a)(b)は従来例によるスナバ回路の抵抗の実装方法を示す平面図及びその回路図である。

【図4】別な構成のスナバ回路を示す電気回路図である。

【図5】同上のスナバ回路のDC/DCコンバーターへの適用例を示す電気回路図である。

【図6】(a)は図5のMOSFETに掛かるドレイン−ソース間電圧VDSの時間変化を示す図、(b)は図2の1次側の電流IPの時間変化を示す図、(c)は図2の2次側の電流ISの時間変化を示す図である。

【符号の説明】

1,2 プリント配線板

3 ダイオード

4〜8 ツェナーダイオード

9 端子電極

10〜13 接続電極

【0001】

【産業上の利用分野】本発明は、保護回路の実装構造に関する。具体的にいうと、本発明は、電力用半導体素子を保護するための保護回路の実装構造に関する。

【0002】

【背景技術とその問題点】従来より、スイッチング電源やDC/DCコンバーター等の小型の電源装置においては、スイッチング素子を保護するためのスナバ回路(サージ吸収回路)が使用されている。

【0003】図2は抵抗33、コンデンサ34及びダイオード35によって構成されたスナバ回路を備えたDC/DCコンバータを示す回路図である。このスナバ回路は、抵抗33とコンデンサ34の並列体にダイオード35を直列に接続したものであり、変圧器32の一次側の端子間に接続されている。また、ダイオード35は直流電源(図示せず)に対し逆バイアス方向に接続されている。この回路にあっては、MOSFET31がターンオフした瞬間に変圧器32に蓄積されていたエネルギーはコンデンサ34に移され、抵抗33で消費される。これにより、MOSFET31がターンオフした瞬間におけるドレイン−ソース間電圧の急激な上昇が防止され、MOSFET31が保護される。

【0004】このようなスナバ回路を具体化してプリント配線板に実装する場合、従来にあっては、1枚のプリント配線板上に平面的あるいは2次元的に実装されていた。しかも、装置の小型化を目的としてチップ抵抗を用いてスナバ回路を構成する場合には、チップ抵抗の定格電力が小さいために複数個のチップ抵抗を用いる必要があり、図3(a)に示すようにプリント配線板39の配線パターン間40,41に多数のチップ抵抗38を配列し、例えば図3(b)のような回路となるようにチップ抵抗38を接続していた。例えば、電気抵抗R(Ω),定格電力P(W)の2個の抵抗33を定格電力P/5(W)のチップ抵抗38で実装する場合には、図3(b)に示すように、電気抵抗5R(Ω)のチップ抵抗38を5個並列に接続した並列体を2組直列に接続しなければならなかった。

【0005】このため、チップ抵抗を用いた場合には、抵抗の実装面積が増大するという不都合があった。また、このように多くのチップ抵抗を直列及び並列に接続すると、配線距離が長くなるために配線インダクタンスが増大し、高周波・高速スイッチング素子の保護には適さなかった。さらには、チップ抵抗の熱を1枚のプリント配線板から放熱させなければならないので、放熱効率が悪いという問題もあった。

【0006】また、図4はツェナーダイオード36とダイオード37によって構成されたスナバ回路を備えたDC/DCコンバーターを示す回路図である。このスナバ回路は、ツェナーダイオード36とダイオード37の直列体であり、ツェナーダイオード36は直流電源(図示せず)に対し順バイアス方向に接続されており、ダイオード37は直流電源(図示せず)に対し逆バイアス方向に接続されている。このスナバ回路を用いることにより、変圧器32の一次側の端子間の電圧はツェナーダイオード36の動作電圧以下に制限される。これにより、MOSFET31のドレイン−ソース間に掛かる電圧は安全動作領域に制限され、MOSFET31が保護される。

【0007】つぎに、DC/DCコンバータに用いた場合の上記スナバ回路の働きを具体的に説明する。図5はDC/DCコンバータの一例を示す回路図、図6(a)(b)(c)はそれぞれ図5のDC/DCコンバータ(スナバ回路を設けられていないもの)における一次側回路に設けられたMOSFET31の電圧、一次側回路に流れる電流IPおよび二次側回路ISに流れる電流を示すタイムチャートである。まず、図5のような構成のDC/DCコンバータにおけるスナバ回路を設けられていない場合の動作を説明する。一次側回路のMOSFET31がオンになる(時間T1)と、一次側回路に電流IPが流れ出す。この後、MOSFET31がオフになると、MOSFET31のソース−ドレイン間電圧VDSが急上昇し、同時に一次側回路の電流IPが減少する(時間T2)。一次側回路の電流IPが減少すると、相互インダクタンスによって二次側回路に電流ISが流れ、同時に、自己インダクタンスによって一次側のMOSFET31のソース−ドレイン間電圧VDSにスパイク電圧VPKが発生する。

【0008】これに対し、図5に想像線によって示したように、一次側回路にダイオード37とツェナーダイオード36からなるスナバ回路を設けると、スナバ回路を通ってMOSFET31のドレイン側から直流電源側へ電流が流れてスパイク電圧VPKがカットされる。

【0009】しかしながら、このようなスナバ回路を具体化して配線基板に実装する場合も、従来にあっては、1枚の配線基板上に平面的あるいは2次元的に実装されていた。このため、電力用のパワーツェナーダイオードを使用しなければならない場合には、部品形状が大きくなり、実装面積が大きくなるという問題があった。

【0010】

【発明が解決しようとする課題】本発明は、叙上の従来例の欠点に鑑みてなされたものであり、その目的とするところは、実装面積が著しく小さく、配線インダクタンスが小さく、かつ、放熱性の良好な保護回路の実装構造を提供することにある。

【0011】

【課題を解決するための手段】本発明の保護回路の実装構造は、電力用半導体素子を保護するための保護回路の実装構造であって、第1のプリント配線板に対向させて第2のプリント配線板を配置し、前記保護回路を構成するための部品を両プリント配線板間に略垂直に配設し、第1及び第2のプリント配線板の配線パターンによって前記部品を接続して保護回路を形成したことを特徴としている。

【0012】

【作用】本発明の保護回路の実装構造にあっては、対向させた第1及び第2のプリント配線板間に略垂直に保護回路部品を配設しているので、保護回路部品の実装面積を小さくすることができる。

【0013】また、保護回路部品の両端に設けられた2枚のプリント配線板に保護回路の配線を分離して形成することができるので、保護回路の配線の長さを短くすることができ、配線インダクタンスを減少させることができる。従って、高周波・高速スイッチング素子の保護回路としても好適となる。

【0014】さらに、保護回路部品の両端にそれぞれプリント配線板が配置されているので、双方のプリント配線板から放熱させることができ、保護回路を構成する部品の放熱性が良好となり、保護回路の熱設計が容易になる。

【0015】

【実施例】図1(a)は本発明の一実施例による保護回路の実装構造を示す斜視図、図1(b)は図1(a)の電気回路図である。本実施例の保護回路の実装構造にあっては、主プリント配線板1に補助プリント配線板2を平行に配置し、ダイオード3と複数個のツェナーダイオード4,5,6,7,8を2枚のプリント配線板1,2の間に垂直に立てて実装してある。複数個のツェナーダイオード4〜8は配線パターンによって全て同方向に直列に接続してあり、ダイオード3はこれらと逆方向に直列に接続してある。ここで、複数個のツェナーダイオード4〜8を直列に接続して用いているのは、大電力用のパワーツェナーダイオードを1個使用するよりも、小容量のツェナーダイオードを複数個使用するほうが、全体としての実装面積を小さくできるからである。したがって、例えば定格電力P(W),動作電圧VZD(V)のパワーツェナーダイオードを1個使用する場合には、定格電力P/n(W)以上,動作電圧VZD/n(V)の小容量のツェナーダイオードをn個直列に接続して使用する。以下、この実施例を図面に基づき、さらに詳細に説明する。

【0016】主プリント配線板1の表面には、帯状をした端子電極9と短冊状をした接続電極10を一直線上に形成してあり、これらを2列平行に形成してある。端子電極9,9の端部には端子孔9a,9aを形成してあり、接続電極10,10の両端部には端子孔10a,10b,10a,10bを形成してある。

【0017】一方、補助プリント配線板2には短冊状をした3個の接続電極11,12,13を形成してある。接続電極11,13は端子電極9,9の間隔と同じ間隔で平行に形成してあり、接続電極12は接続電極11,13の端部から一定の距離を隔てて接続電極11,13と直角に形成してある。また、接続電極11,12,13の両端部には端子孔11a,11b;12a,12b;13a,13bを形成してある。

【0018】ここで、接続電極11の端子孔11a,11b間の距離は端子電極9の端子孔9aと接続電極10の端子孔10aの間の距離に等しくしてあり、接続電極12の端子孔12a,12b間の距離は接続電極10,10の端子孔10b,10b間の距離に等しくしてある。また、接続電極13の端子孔13a,13b間の距離は接続電極10の端子孔10aと端子電極9の端子孔9aの間の距離に等しくしてある。

【0019】しかして、端子孔11aと端子孔9aには、ダイオ−ド3のカソード側の端子とアノード側の端子をそれぞれ挿入して半田付けしてある。

【0020】端子孔11bと端子孔10aには、ツェナーダイオード4のカソード側の端子とアノード側の端子をそれぞれ挿入して半田付けしてある。

【0021】端子孔12aと端子孔10bには、ツェナーダイオード5のアノード側の端子とカソード側の端子をそれぞれ挿入して半田付けしてある。

【0022】端子孔12bと端子孔10bには、ツェナーダイオード6のカソード側の端子とアノード側の端子をそれぞれ挿入して半田付けしてある。

【0023】端子孔13aと端子孔10aには、ツェナーダイオード7のアノード側の端子とカソード側の端子をそれぞれ挿入して半田付けしてある。

【0024】端子孔13bと端子孔9aには、ツェナーダイオード8のカソード側の端子とアノード側の端子をそれぞれ挿入して半田付けしてある。

【0025】こうして主プリント配線板1と補助プリント配線板2との間に実装されたダイオード3及び各ツェナーダイオード4〜8は、両プリント配線板1,2の端子電極9及び接続電極10〜13によって図1(b)に示すように直列に接続される。しかも、ダイオード3及び各ツェナーダイオード4〜8は、両プリント配線板1,2間に略垂直に立てた状態で実装されているので、プリント配線板1,2上における実装面積(占有面積)を小さくできる。

【0026】また、回路配線(配線パターン)を主プリント配線板1と補助プリント配線板2とに分けて立体的に構成することができるので、回路配線の長さを最短にすることができ、配線インダクタンスを小さくすることができる。さらに、ダイオード3やツェナーダイオード4〜8で発生した熱は、プリント配線板1,2へ伝わり、両側のプリント配線板1,2から放熱されるので、放熱面積が大きくなり、放熱性が良好となる。

【0027】

【発明の効果】本発明によれば、第1及び第2のプリント配線板間に略垂直に保護回路部品を実装することにより保護回路部品の実装面積を小さくすることができる。また、2枚のプリント配線板に回路配線を分離して形成できるので、回路配線の長さを短くして配線インダクタンスを減少させることができ、高周波・高速スイッチング素子の保護回路としても好適となる。さらに、放熱面積の増大により保護回路を構成する部品の放熱性が良好となり、保護回路の熱設計を容易にすることができる。

【図面の簡単な説明】

【図1】(a)は本発明の一実施例によるスナバ回路の実装構造を示す斜視図、(b)は(a)のスナバ回路を表わした電気回路図である。

【図2】スナバ回路の一例を示す電気回路図である。

【図3】(a)(b)は従来例によるスナバ回路の抵抗の実装方法を示す平面図及びその回路図である。

【図4】別な構成のスナバ回路を示す電気回路図である。

【図5】同上のスナバ回路のDC/DCコンバーターへの適用例を示す電気回路図である。

【図6】(a)は図5のMOSFETに掛かるドレイン−ソース間電圧VDSの時間変化を示す図、(b)は図2の1次側の電流IPの時間変化を示す図、(c)は図2の2次側の電流ISの時間変化を示す図である。

【符号の説明】

1,2 プリント配線板

3 ダイオード

4〜8 ツェナーダイオード

9 端子電極

10〜13 接続電極

【特許請求の範囲】

【請求項1】 電力用半導体素子を保護するための保護回路の実装構造であって、第1のプリント配線板に対向させて第2のプリント配線板を配置し、前記保護回路を構成するための部品を両プリント配線板間に略垂直に配設し、第1及び第2のプリント配線板の配線パターンによって前記部品を接続して保護回路を形成した保護回路の実装構造。

【請求項1】 電力用半導体素子を保護するための保護回路の実装構造であって、第1のプリント配線板に対向させて第2のプリント配線板を配置し、前記保護回路を構成するための部品を両プリント配線板間に略垂直に配設し、第1及び第2のプリント配線板の配線パターンによって前記部品を接続して保護回路を形成した保護回路の実装構造。

【図1】

【図2】

【図4】

【図5】

【図3】

【図6】

【図2】

【図4】

【図5】

【図3】

【図6】

【公開番号】特開平6−5887

【公開日】平成6年(1994)1月14日

【国際特許分類】

【出願番号】特願平4−186019

【出願日】平成4年(1992)6月18日

【出願人】(000002945)オムロン株式会社 (3,542)

【公開日】平成6年(1994)1月14日

【国際特許分類】

【出願日】平成4年(1992)6月18日

【出願人】(000002945)オムロン株式会社 (3,542)

[ Back to top ]