信号および電力の伝送装置

【課題】3相インバータを構成するスイッチング素子の操作信号の伝送と駆動回路への電力の供給とをトランス1つで行なうことが困難なこと。

【解決手段】マイクロプロセッサ50から出力される操作信号g¥#は、エンコーダ41にてマンチェスタ符号にて符号化され、1次側コイルW1の印加電圧信号となる。2次側コイルW2uには、電源回路60およびデコードユニット70が並列接続されている。電源回路60は、スイッチング素子Supの駆動部20の電源を生成する。これに対し、デコードユニット70は、2次側コイルW2uに伝送された電圧信号の復号処理をすることで、スイッチング素子Supの操作信号gupを抽出し、駆動部20に出力する。

【解決手段】マイクロプロセッサ50から出力される操作信号g¥#は、エンコーダ41にてマンチェスタ符号にて符号化され、1次側コイルW1の印加電圧信号となる。2次側コイルW2uには、電源回路60およびデコードユニット70が並列接続されている。電源回路60は、スイッチング素子Supの駆動部20の電源を生成する。これに対し、デコードユニット70は、2次側コイルW2uに伝送された電圧信号の復号処理をすることで、スイッチング素子Supの操作信号gupを抽出し、駆動部20に出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、伝送対象となる信号の伝送と該伝送先への電力の伝送とを行なう信号および電力の伝送装置に関する。

【背景技術】

【0002】

この種の伝送装置としては、たとえば下記特許文献1に見られるように、駆動対象とするスイッチング素子の操作信号をトランスを介して駆動回路に出力するに際し、このトランスの2次側コイルの出力を、スイッチング素子のゲートを充電するための電力として利用するものも提案されている。詳しくは、トランスの2次側コイルに並列接続された一対のコンデンサの電荷をスイッチング素子のゲートに充電するために利用して且つ、一対のコンデンサの接続点の電位によってスイッチング素子のオン指令、オフ指令を識別する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許第3417127号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ただし、上記装置は、たとえば3相インバータを構成するスイッチング素子の操作信号の伝送装置として利用される場合、各レッグ毎にトランスを備える必要が生じる等、伝送対象とする信号の伝送先の数が増加する際に回路規模の大型化や部品点数の増大を招きやすい。

【0005】

また、上記一対のコンデンサの電圧がオン・オフの指令に応じて変動するため、上記装置では、スイッチング素子のゲートの充電以外の電源が必要であっても上記一対のコンデンサを利用することが困難であり、別途電源を用意する必要が生じる。

【0006】

さらに、スイッチング素子のオン指令期間やオフ指令期間が長くなる場合、トランスの1次側コイルや2次側コイルを鎖交する磁束が過度に大きくなるおそれがある。このため、トランスを大型化する要求が生じやすい。

【0007】

本発明は、上記課題を解決する過程でなされたものであり、その目的は、伝送対象となる信号の伝送と該伝送先への電力の伝送とを行なう新たな信号および電力の伝送装置を提供することにある。

【課題を解決するための手段】

【0008】

以下、上記課題を解決するための手段、およびその作用効果について記載する。

【0009】

請求項1記載の発明は、互いに磁気結合した1次側コイルおよび2次側コイルと、伝送対象となる対象信号をパルス符号化する符号化手段と、前記符号化手段の出力に応じた電圧信号である入力側電圧信号を前記1次側コイルに印加する電圧印加手段と、前記入力側電圧信号によって前記2次側コイルに誘起される電圧信号である出力側電圧信号の変化に基づき、前記出力側電圧信号を復号する復号手段と、前記入力側電圧信号によって前記2次側コイルに誘起される電圧信号に応じて前記2次側コイルに接続される電気経路に流れる電流を整流する整流回路と、を備えることを特徴とする。

【0010】

上記発明では、対象信号をパルス符号化することで、磁気結合した1次側コイルおよび2次側コイルを介して対象信号を伝送させることが容易となる。また、出力側電圧信号は、パルス信号であるため、その変化に基づきパルス符号化された信号を検出することができ、ひいてはこれを復号することで対象信号を抽出することができる。また、2次側コイルから出力側電圧信号が出力されることで流れる電流を整流する整流回路を備えることで、整流回路を、対象信号の出力側における直流電源として利用することができる。

【0011】

請求項2記載の発明は、請求項1記載の発明において、前記復号手段は、第1出力経路を介して前記2次側コイルに接続され、前記整流回路は、前記第1出力経路とは相違する第2出力経路を介して前記2次側コイルに接続されていることを特徴とする。

【0012】

上記発明では、復号手段と整流回路とが互いに相違する経路を介して同一の2次側コイルに接続されるため、復号手段の入力電圧と整流回路の出力電圧とを各別とする設定等が容易となる。

【0013】

請求項3記載の発明は、請求項1または2記載の発明において、前記対象信号は、情報信号と、該情報信号の更新の都度、該情報信号に先立って情報信号が伝送される旨を示す同期信号とを含むことを特徴とする。

【0014】

上記発明では、対象信号に同期信号を含めることで、情報信号が更新される都度、更新された情報信号である旨を復号手段側で把握することが容易となる。

【0015】

請求項4記載の発明は、請求項3記載の発明において、前記符号化手段による符号化処理は、前記入力側電圧信号が前記1次側コイルに印加されることによる前記1次側コイルおよび前記2次側コイルの鎖交磁束についての前記同期信号と前記情報信号との1周期に対応する期間にわたる変化量をゼロとするものであることを特徴とする。

【0016】

上記発明では、鎖交磁束が過度に大きくなることを好適に回避することができ、ひいては、磁気部品を小型化することができる。

【0017】

請求項5記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記パルス符号は、バイフェーズ符号であることを特徴とする。

【0018】

DMI符号やマンチェスタ符号等のバイフェーズ符号は、2値のそれぞれの継続時間が短い符号であるため、1次側コイルや2次側コイルの鎖交磁束の増大を抑制しやすい。このため、上記発明では、磁気部品を小型化することができる。

【0019】

請求項6記載の発明は、請求項1〜5のいずれか1項に記載の発明において、前記復号手段は、前記出力側電圧信号に基づきクロック信号を生成するクロック生成手段を備えることを特徴とする。

【0020】

上記発明では、出力側電圧信号がパルス符号化された信号であることに鑑み、パルスを利用してクロックを生成することで、復号処理を容易に行なうことができる。

【0021】

請求項7記載の発明は、請求項1〜6のいずれか1項に記載の発明において、前記整流回路には、前記整流回路の出力電流を平滑化するフィルタ回路が接続されており、前記フィルタ回路の時定数は、前記出力側電圧信号の電圧値が一定となる最長時間よりも長く設定されていることを特徴とする。

【0022】

出力側電圧信号の電圧値が一定となる最長時間と比較して上記時定数が小さい場合、フィルタ回路の平滑化機能が復号手段の入力信号に干渉することで、復号手段による復号処理に支障が生じることが懸念される。上記発明では、この点に鑑み、上記設定とした。

【0023】

請求項8記載の発明は、請求項1〜7のいずれか1項に記載の発明において、前記2次側コイルは、互いに電位の相違しうる部材のそれぞれに接続される複数のコイルからなり、前記復号手段は、前記複数のコイルのそれぞれ毎に備えられることを特徴とする。

【0024】

上記発明では、互いに電位の相違しうる部材のそれぞれに対象信号と電力とを伝送することができる。

【0025】

請求項9記載の発明は、請求項8記載の発明において、前記2次側コイルは、直列接続された一対のスイッチング素子である高電位側のスイッチング素子および低電位側のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれに接続されるコイルを含み、前記対象信号は、前記スイッチング素子のオン・オフの指令信号を含むことを特徴とする。

【0026】

上記発明では、駆動回路に、スイッチング素子のオン・オフの指令信号と電力とを伝送することができる。

【0027】

請求項10記載の発明は、請求項9記載の発明において、前記2次側コイルに接続される駆動回路は、直列接続された一対のスイッチング素子の複数組のそれぞれの高電位側のスイッチング素子を駆動対象とする各別の駆動回路を備え、前記対象信号は、前記複数組の一対のスイッチング素子のそれぞれのオン・オフの指令信号と、該指令信号の更新の都度、該指令信号に先立って指令信号が伝送される旨を示す同期信号とを含み、前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、前記高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない信号であり、前記復号手段は、前記直列接続された一対のスイッチング素子のオン・オフの指令信号が、双方ともオン指令であることを異常として検出する異常検出手段を備え、該異常検出手段によって異常が検出されることに基づき、該異常に対処する異常対処処理を実行する実行手段をさらに備えることを特徴とする。

【0028】

上記発明では、実行手段を備えることで、双方ともオン指令である異常時に、異常な信号を正常としてスイッチング素子が駆動され続ける事態を回避することができる。

【0029】

請求項11記載の発明は、請求項9または10記載の発明において、前記2次側コイルに接続される駆動回路は、直列接続された一対のスイッチング素子の複数組のそれぞれの高電位側のスイッチング素子を駆動対象とする各別の駆動回路を備え、前記対象信号は、前記複数組の一対のスイッチング素子のそれぞれのオン・オフの指令信号と、該指令信号の更新の都度、該指令信号に先立って指令信号が伝送される旨を示す同期信号とを含み、前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、前記高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない信号であり、前記同期信号は、前記オン指令に対応する信号と同一の信号が3つ以上連続する信号であることを特徴とする。

【0030】

高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない場合、指令信号の配列によって、オン指令に対応する符号と同一符号が3つ以上連続しないようにすることができる。このため、上記設定とすることで、同期信号を、指令信号と識別可能な信号とすることができる。

【0031】

請求項12記載の発明は、請求項9〜11のいずれか1項に記載の発明において、前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、高電位側のスイッチング素子のオン指令および低電位側のスイッチング素子のオフ指令、高電位側のスイッチング素子のオフ指令および低電位側のスイッチング素子のオン指令、ならびに高電位側のスイッチング素子のオフ指令および低電位側のスイッチング素子のオフ指令の3つの指令パターンのいずれかであることを特徴とする。

【0032】

上記発明では、高電位側のスイッチング素子と低電位側のスイッチング素子との双方がオン状態となるものを除き、全てのスイッチングパターンを指令することができる。

【0033】

請求項13記載の発明は、請求項12記載の発明において、前記直列接続された高電位側のスイッチング素子および低電位側のスイッチング素子は、交互にオン状態となるように相補駆動されるものであって且つ、それら高電位側のスイッチング素子および低電位側のスイッチング素子のいずれか一方および他方のそれぞれがオン、オフとなる状態からオフ、オンとなる状態に移行するに先立ち、前記指令信号が双方のオフ状態を指令することを特徴とする。

【0034】

上記発明では、駆動回路側にデッドタイムを生成する手段を備えることなく、デッドタイムを対象信号によって指令することができる。

【0035】

請求項14記載の発明は、請求項9〜13のいずれか1項に記載の発明において、前記駆動回路は、前記スイッチング素子の駆動状態を監視する監視手段を備え、前記監視手段は、前記整流回路に電気的に接続されていることを特徴とする。

【0036】

上記発明では、監視手段に電源が必要となる。このため、整流回路を備えるメリットが特に大きい。これに対し、こうしたものを備えることなく、スイッチング素子を駆動する用途の場合には、通常のパルストランスを用いることも可能となり得る。

【0037】

請求項15記載の発明は、請求項8〜14のいずれか1項に記載の発明において、前記複数のコイルには、複数のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれが接続され、前記対象信号は、前記複数のスイッチング素子のそれぞれのオン・オフの指令信号を含み、前記複数のスイッチング素子のうち互いに相違する部類に属するスイッチング素子のそれぞれに対応する前記駆動回路同士で前記オン・オフ指令の入力から駆動対象とするスイッチング素子が操作されるまでの遅延時間を相違させる設定がなされていることを特徴とする。

【0038】

上記発明では、互いに相違する部類に属するスイッチング素子同士で同時にスイッチング状態の切り替え指令信号が出力されたとしても、これら互いに相違する部類に属するスイッチング素子同士でスイッチング状態の切り替えタイミングを相違させることができる。

【0039】

請求項16記載の発明は、請求項8〜14のいずれか1項に記載の発明において、前記複数のコイルには、複数のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれが接続され、前記対象信号は、前記複数のスイッチング素子のそれぞれのオン・オフの指令信号を含み、前記対象信号は、前記1次側コイルおよび前記2次側コイルを介して周期的に伝送されるものであり、周期的な伝送の1周期の間に前記複数のスイッチング素子の全てのオン・オフを指令する信号が含まれて且つ、前記複数のスイッチング素子のうちの互いに相違する部類に属するスイッチング素子のそれぞれで互いに相違する周期で前記オン・オフを指令する信号が更新されることを特徴とする。

【0040】

上記発明では、互いに相違する部類に属するスイッチング素子同士でオン・オフの指令信号の更新タイミングが相違するため、これら互いに相違する部類に属するスイッチング素子同士でスイッチング状態の切り替えタイミングを相違させることができる。

【0041】

請求項17記載の発明は、請求項8〜14のいずれか1項に記載の発明において、前記複数のコイルには、複数のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれが接続され、前記対象信号は、前記複数のスイッチング素子のそれぞれのオン・オフの指令信号を含み、前記対象信号は、前記1次側コイルおよび前記2次側コイルを介して周期的に伝送されるものであり、周期的な伝送の1周期の間に前記複数のスイッチング素子のうちの互いに相違する部類のいずれかに属するスイッチング素子のオン・オフを指令する信号に加えて、該いずれかを指定する信号が伝送されることを特徴とする。

【0042】

上記発明では、伝送の周期毎にいずれか1つの部類が指定されるため、互いに相違する部類に属するスイッチング素子同士でスイッチング状態の切り替えタイミングを相違させることができる。

【0043】

請求項18記載の発明は、請求項15〜17のいずれか1項に記載の発明において、前記複数のスイッチング素子は、互いに相違する回転機に接続されて且つ共通の直流電圧源に接続された複数の直流交流変換回路を構成するものであって且つ、互いに相違する直流交流変換回路を構成するもの同士が互いに相違する部類とされるものであることを特徴とする。

【0044】

請求項19記載の発明は、請求項1〜18のいずれか1項に記載の発明において、前記1次側コイルと前記2次側コイルとは互いに絶縁されていることを特徴とする。

【0045】

上記発明では、1次側に接続される部材と2次側に接続される部材との動作電位が相違する場合であっても、これに適切に対処することができる。

【0046】

請求項20記載の発明は、請求項1〜19のいずれか1項に記載の発明において、前記出力側電圧信号の変動量を縮小変換して、前記復号手段に入力する変換手段をさらに備えることを特徴とする。

【0047】

上記発明では、出力側電圧信号の変動量を整流回路の出力電圧の要求に応じて設定しつつも、復号手段の入力電圧を適切な値とすることができる。

【図面の簡単な説明】

【0048】

【図1】第1の実施形態にかかるシステム構成図。

【図2】同実施形態にかかるスイッチング素子のオン・オフ操作手法を示すタイムチ ャート。

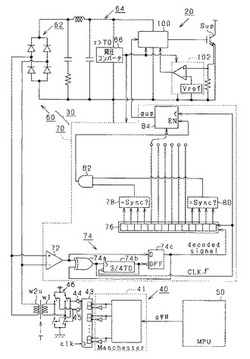

【図3】同実施形態にかかる伝送装置の構成を示す図。

【図4】同実施形態にかかる符号化信号を示すタイムチャート。

【図5】同実施形態にかかる復号処理を示すタイムチャート。

【図6】同実施形態にかかる性能評価結果を示すタイムチャート。

【図7】同実施形態にかかる性能評価結果を示すタイムチャート。

【図8】同実施形態にかかる性能評価結果を示す図。

【図9】第2の実施形態にかかる伝送装置の構成を示す図。

【図10】第3の実施形態にかかるシステム構成図。

【図11】同実施形態にかかるスイッチング状態の切り替えタイミングの設定手法を 示す図。

【図12】同実施形態の効果を示す図。

【図13】第4の実施形態にかかる情報信号の伝送手法を示すタイムチャート。

【図14】第5の実施形態にかかる情報信号の伝送手法を示すタイムチャート。

【図15】第6の実施形態にかかるスイッチングモードの更新可能周期を示すタイムチャート。

【図16】第7の実施形態にかかるシステム構成図。

【図17】同実施形態にかかるフレーム出力処理の手順を示す流れ図。

【図18】同実施形態にかかるフレーム出力処理態様を示すタイムチャート。

【図19】第8の実施形態にかかるフレーム出力処理の手順を示す流れ図。

【図20】第9の実施形態にかかるフレーム出力処理の手順を示す流れ図。

【図21】同実施形態にかかるフレーム出力処理態様を示すタイムチャート。

【図22】第10の実施形態にかかるフレーム出力停止期間の1次側コイルの電圧印加処理の手順を示す流れ図。

【図23】第11の実施形態にかかるシステム構成図。

【図24】上記各実施形態の変形例にかかる回路図。

【発明を実施するための形態】

【0049】

<第1の実施形態>

以下、本発明にかかる信号および電力の伝送装置をスイッチング素子の駆動回路への信号および電力の伝送装置に適用した第1の実施形態について、図面を参照しつつ説明する。

【0050】

図1に、本実施形態にかかるシステム構成を示す。

【0051】

図示されるように、車載主機としてのモータジェネレータ10は、3相の同期機である。モータジェネレータ10には、インバータINVを介して直流電圧源(高電圧バッテリ12)が接続されている。高電圧バッテリ12は、端子電圧がたとえば100V以上となる2次電池である。高電圧バッテリ12の正極電位および負極電位の中央値が車体電位となる設定とするなどして、高電圧バッテリ12の負極電位は、車体電位とは相違するように設定されている。この設定は、たとえば高電圧バッテリ12の電圧を分圧する複数のコンデンサの接続点を車体に接続することで実現することができる。

【0052】

インバータINVは、高電位側のスイッチング素子S¥p(¥=u,v,w)および低電位側のスイッチング素子S¥nの直列接続体を3組備え、これら各直列接続体を構成する高電位側のスイッチング素子S¥pおよび低電位側のスイッチング素子S¥nの接続点がモータジェネレータ10の各端子に接続されている。そして、スイッチング素子S¥#(¥=u,v,w:#=p,n)のそれぞれには、ダイオードD¥#のそれぞれが逆並列に接続されている。

【0053】

また、上記各スイッチング素子S¥#の開閉制御端子(ゲート)には、ドライブユニットDUが接続されている。ドライブユニットDUは、スイッチング素子S¥#のゲートの電圧を制御する機能が搭載された駆動部20を備えている。また、上側アームのスイッチング素子S¥pのドライブユニットDUとU相下側アームのスイッチング素子SunのドライブユニットDUとは、スイッチング素子S¥#のオン・オフの操作指令を受信する受信ユニット30を備えている。なお、V相およびW相の下側アームのスイッチング素子Svn,SwnのドライブユニットDUには、U相下側アームのスイッチング素子SunのドライブユニットDUによって受信された信号が取り込まれる。これは、下側アームのスイッチング素子Sun,Svn,SwnのそれぞれのドライブユニットDUの動作電位が等しいことに鑑みた設定である。

【0054】

上記モータジェネレータ10を流れる電流は電流センサ14によって検出される。そして、電流センサ14の検出値等、モータジェネレータ10の制御量(トルク等)を制御する上で必要な検出値は、マイクロプロセッサユニット50に入力される。マイクロプロセッサユニット50は、メモリに格納されたプログラムを中央処理装置によって実行するソフトウェア手段である。

【0055】

マイクロプロセッサユニット50では、電流センサ14の検出値等に基づき、モータジェネレータ10を流れる電流を、モータジェネレータ10のトルクを指令トルクとするうえで要求される指令電流に制御する。ここでは、たとえば特開2008−228419号公報等に記載されるモデル予測制御(MPC:Model Predictive Control)が用いられる。すなわち、インバータINVのスイッチングモードを仮設定した場合についてのそれぞれの電流を予測し、予測される電流と指令電流との差が最も小さくなるスイッチングモードを採用する。ここで、スイッチングモードは、インバータINVの6つのスイッチング素子S¥#(¥=u,v,w;#=p,n)のそれぞれがオンであるかオフであるかによって定まるものであり、8つのスイッチングモードが存在する。それらのうち、スイッチングモード1〜6は、インバータINVの出力電圧を図に示す有効電圧ベクトルV1〜V6とするものである。

【0056】

マイクロプロセッサユニット50では、スイッチングモードが決定されると、これに応じたスイッチング素子S¥#の操作信号g¥#を送信ユニット40に出力する。ここで、操作信号g¥#は、基本的にはスイッチングモードを表現するものであるが、スイッチングモードの切り代わり時には、上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方をオフ指令とすることで、図2に示すデッドタイムDTを表現する。ここで、デッドタイムDTは、スイッチングモードの切り替えに際して上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオンとなることがないように、スイッチング素子S¥#のスイッチング状態の切り替わり速度に基づき設定されるものである。

【0057】

送信ユニット40では、マイクロプロセッサユニット50から出力された操作信号g¥#をデジタルベースバンド符号にて符号化し、符号化された信号であるパルス信号に応じてトランスTの1次側コイルW1に電圧を印加する。これにより、トランスTの2次側コイルW2n,W2u,W2v,W2wにパルス状の電圧信号が出力される。

【0058】

ここで、2次側コイルW2nは、U相下側アームのスイッチング素子SunのドライブユニットDUに搭載された受信ユニット30に接続されている。また、2次側コイルW2u,v,wのそれぞれは、U,V,W相の上側アームのスイッチング素子Sup,Svp,SwpのそれぞれのドライブユニットDUに搭載された受信ユニット30に接続されている。

【0059】

以下、送信ユニット40、トランスTおよび受信ユニット30を備える伝送装置の構成について、図3に基づきさらに説明する。図3では、便宜上、U相の上側アームのスイッチング素子SupのドライブユニットDUに信号および電力を伝送する経路を、他の経路を代表して示している。

【0060】

マイクロプロセッサユニット50から出力された操作信号g¥#は、送信ユニット40内のエンコーダ41によってデジタルベースバンド符号化処理がなされ、パルス信号に符号化される。ここでは、パルス符号として、マンチェスタ符号が用いられる。図4に、マンチェスタ符号によって符号化されたパルス符号化信号を示す。図示されるように、マンチェスタ符号は、1ビットに対応する期間(単位期間T0)の中央で論理が反転するものであり、特に論理「0」と論理「1」とで、中央での反転極性が相違するものである。本実施形態では、同期信号(図中、Sync)を4ビットの信号とし、これに続いて各1ビットで操作信号gup,gun,gvp,gvn,gwp,gwnのそれぞれを順次表現する。これにより、操作信号gup,gun,gvp,gvn,gwp,gwnの出力周期である1フレームが、10ビットとなる。

【0061】

本実施形態では、同期信号を「0111」とする。これは、上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオンとなることがないために、操作信号g¥#を表現する6ビットのデータが、オン指令に対応する論理値「1」が3連続するデータを含み得ないことに鑑みた設定である。これにより、操作信号g¥#を表現するデータと同期信号とを識別することができる。ちなみに、同期信号の先頭データを「0」としたのは、操作信号g¥#と確実に識別するためである。

【0062】

なお、本実施形態では、単位期間T0の10倍の期間である1フレームの期間の整数N倍をデッドタイムDTとする。すなわち、スイッチングモードの切り替えに際しては、スイッチング状態の切り替わるレッグについて、Nフレームの期間にわたって、上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方をオフ指令とする。なお、1フレーム期間は、スイッチング状態の切り替えに際して双方がオン状態となることがない下限時間以下に設定することが望ましい。

【0063】

先の図3に示したエンコーダ41の出力信号は、シフトレジスタ43に入力される。シフトレジスタ43は、クロック信号clkに同期してパルス符号化された信号を1次側コイルW1に出力する。

【0064】

詳しくは、1次側コイルW1には、フルブリッジ回路46が接続されており、シフトレジスタ43の出力信号は、フルブリッジ回路46の各スイッチング素子を駆動するドライバ44,45に入力される。これにより、1次側コイルW1には、パルス符号化された信号に応じた電圧信号(入力側電圧信号)が印加される。

【0065】

1次側コイルW1に電圧信号が印加されると、2次側コイルW2uには、1次側コイルW1と2次側コイルW2uとの巻数比に応じた倍率で変動する電圧信号が誘起される。2次側コイルW2uに接続された受信ユニット30は、電源回路60とデコードユニット70とを備える。

【0066】

電源回路60は、2次側コイルW2uに誘起された電圧に応じて流れる電流を整流する整流回路62と、整流回路62から出力される電流を平滑化するフィルタ回路64と、フィルタ回路64の出力電圧を降圧する降圧コンバータ66とを備える。ここで、フィルタ回路64の出力電圧は、降圧コンバータ66に入力されるのに加えて、駆動部20に入力される。駆動部20は、デコードユニット70の出力する操作信号gupに応じてスイッチング素子Supを駆動する駆動IC100と、過電流保護回路102とを備える。ここで、過電流保護回路102は、スイッチング素子Supを流れる電流を監視し、この電流が閾値電流以上となることで、駆動IC100にスイッチング素子Supを強制的にオフ操作する指令を出力するものである。スイッチング素子Supを流れる電流が閾値以上であるか否かの判断は、スイッチング素子Supの入力端子(コレクタ)および出力端子(エミッタ)間を流れる電流と相関を有する微小電流を出力するセンス端子Stの出力電流が閾値以上であるか否かの判断処理となる。

【0067】

なお、上記降圧コンバータ66は、スイッチング素子Supの駆動用の電圧と、駆動IC100や、過電流保護回路102、デコードユニット70の電源電圧との相違に鑑み、電源電圧を生成するためのものであり、たとえば「20V」の入力電圧を5V程度に降圧する。

【0068】

一方、デコードユニット70は、2次側コイルW2uの電圧の変動量を縮小変換するデータスライサ72を備えている。データスライサ72は、2次側コイルW2uの電圧を、論理回路の動作電圧範囲に変換するための変換手段である。データスライサ72の出力電圧は、デコーダ74に入力される。デコーダ74は、XOR回路74aと、ワンショットパルス回路74bと、復号された信号を出力するDフリップフロップ74cとを備えている。

【0069】

ここで、XOR回路74aは、データスライサ72の出力電圧とDフリップフロップ74cの出力電圧との排他的論理和信号を出力する。ワンショットパルス回路74bは、ワンショットパルスの出力期間でないことを条件に、XOR回路74aの出力電圧の立ち上がりに同期して、予め定められた長さのパルス幅を有するパルス信号を出力する。ここで、パルス幅は、「3・T0/4」に設定される。これは、クロック信号CLKを容易に生成するための一設定である。そして、Dフリップフロップ74cでは、データ端子の出力信号を、ワンショットパルス信号の立ち下がりエッジのタイミングで、そのタイミングにおけるデータスライサ72の出力信号に更新する。

【0070】

図5に、デコーダ74の処理を示す。詳しくは、図5(a)に、デコーダ74の入力信号の推移を示し、図5(b)に、ワンショットパルス回路74bの出力信号の推移を示し、図5(c)に、復号された信号(Dフリップフロップ74cの出力信号)の推移を示し、図5(d)に、デコーダ74の入力信号から生成されるクロック信号CLK(XOR回路74aの出力信号)の推移を示す。

【0071】

先の図3に示すように、復号された信号は、シフトレジスタ76に入力される。シフトレジスタ76では、XOR回路74aの出力信号の立ち上がりエッジをクロック信号CLKとして用いて、Dフリップフロップ74cの出力信号を順次格納する。ここで、本実施形態では、シフトレジスタ76の記憶容量を14ビットとする。これは、1フレーム分のデータと次の1フレームの同期信号とを格納可能とするための設定である。

【0072】

同期信号識別回路78では、シフトレジスタ76の先頭の4ビットのデータが同期信号であるか否かを判断し、同期信号識別回路80では、シフトレジスタ76の最後の4ビットのデータが同期信号であるか否かを判断する。一方、AND回路82では、同期信号識別回路78,80の双方が同期信号を検出することで、操作信号出力回路84にイネーブル信号を出力する。操作信号出力回路84では、イネーブル信号に同期して、シフトレジスタ76の先頭から5ビット目の信号を操作信号gupとして、駆動IC100に出力する。

【0073】

なお、スイッチング素子Svp,SwpのそれぞれのドライブユニットDU内の操作信号出力回路84では、シフトレジスタ76の先頭から7番目、9番目の信号を操作信号gvp,gwpとしてそれぞれ出力する。また、スイッチング素子Sunのドライブユニット内の操作信号出力回路84では、シフトレジスタ76の先頭から6番目の信号を操作信号gupとして出力するとともに、8番目および10番目の信号を操作信号gvn,gwnとして、対応するドライブユニットDU内の駆動部20のそれぞれに出力する。

【0074】

ちなみに、上記フィルタ回路64の時定数τは、2次側コイルW2uの電圧値が固定される最長期間(ここでは、単位期間T0)よりも長く設定される。これは、フィルタ回路64によって、デコーダ74の入力電圧が方形波とならなくなる事態を回避するための設定である。ちなみに、ここでの時定数τとは、ステップ状の入力電圧の変化に対する平滑化される電圧の変化の割合が規定割合(たとえば37%)まで低下するのに要する時間として定義されるものである。時定数τは、応答性を定量化するためのパラメータであり、これが短いほど応答性が速いことを意味する。そして、フィルタ回路64の時定数τが2次側コイルW2uの電圧値が固定される最長期間よりも長いということは、フィルタ回路64の入力電圧の変動に伴ってフィルタ回路64がこれを平滑化するに際し、変動が規定割合以下に減衰するまでに要する時間が最長時間よりも長いことを意味する。

【0075】

図6〜図8に、本実施形態にかかる構成の性能評価結果を示す。

【0076】

図6は、伝送レートを「2.1Mpbs」とした場合について、操作信号gwpの伝送態様を示すものである。詳しくは、図6(a)は、マイクロプロセッサユニット50の出力する操作信号gwpの推移を示し、図6(b)は、1次側コイルW1の電圧の推移を示し、図6(c)は、2次側コイルW2wの電圧の推移を示し、図6(d)は、駆動IC100に出力される操作信号gwpの推移を示す。

【0077】

図7は、伝送レートを「2.1Mpbs」とした場合について、デコーダ74の処理を示す。詳しくは、図7(a)は、2次側コイルW2wの電圧の推移を示し、図7(b)は、クロック信号CLK(XOR回路74aの出力信号)の推移を示し、図7(c)は、デコードされた信号(Dフリップフロップ74c)の推移を示す。

【0078】

なお、伝送レートを「10Mpbs」以上とした場合であっても、図6、図7と同様、良好な信号伝送が実現可能であることが確認されている。

【0079】

図8は、伝送レートを「2.1Mpbs」,「5Mpbs」,「7.5Mpbs」,「10Mpbs」のそれぞれとした場合の伝送電力と2次側コイルW2wの出力電圧との関係を示す。図示されるように、伝送レートを「10Mpbs」としても電力の伝送は良好である。

【0080】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0081】

(1)2次側コイルW2n,W2u,W2v,W2wにデコードユニット70と電源回路60とを接続した。これにより、スイッチング素子S¥#の操作信号g¥#を伝送することおよびドライブユニットDUの電源電力を伝送することができる。

【0082】

(2)2次側コイルW2n,W2u,W2v,W2wに、電源回路60とデコードユニと70とを並列接続した。これにより、デコードユニット70内の動作電圧(たとえば5V)と、電源回路60の入力電圧(たとえば20V)とを相違させることが容易となる。

【0083】

(3)伝送対象となる信号を、操作信号g¥#と同期信号とによって構成した。これにより、操作信号g¥#が更新される都度、更新された操作信号g¥#である旨を容易に把握することができる。

【0084】

(4)マンチェスタ符号を用いて伝送対象となる信号をパルス符号化した。これにより、1フレーム(さらには、1ビット)に渡る1次側コイルの印加電圧の平均値をゼロとすることができ、ひいては、1次側コイルW1の鎖交磁束が過度に大きくなることを好適に回避することができる。

【0085】

(5)2次側コイルW2n,W2u,W2v,W2wに誘起される電圧に基づき、クロック信号CLKを生成した。これにより、復号処理を容易に行なうことができる。

【0086】

(6)フィルタ回路64の時定数τを、2次側コイルW2n,W2u,W2v,W2wの電圧値が一定となる最長時間よりも長く設定した。これにより、フィルタ回路64の平滑化処理によってデコードユニット70による復号処理に支障が生じることを好適に回避することができる。

【0087】

(7)トランスTの2次側コイルを、複数のコイル(2次側コイルW2n,W2u,W2v,W2w)とした。これにより、互いに動作電位の相違しうるドライブユニットDUへの信号および電力の伝送に際して1つのトランスTで対処することができる。

【0088】

(8)同期信号を、オン指令に対応する論理値が3つ継続する信号とした。これにより、操作信号g¥#と識別可能な信号とするうえで同期信号を極力短い信号とすることができる。

【0089】

(9)操作信号g¥p,g¥nを、高電位側のスイッチング素子S¥pのオン指令および低電位側のスイッチング素子S¥nのオフ指令、高電位側のスイッチング素子S¥pのオフ指令および低電位側のスイッチング素子S¥nのオン指令、ならびに高電位側のスイッチング素子S¥pのオフ指令および低電位側のスイッチング素子S¥nのオフ指令の3つの指令パターンのいずれかを示す信号とした。これにより、高電位側のスイッチング素子S¥pと低電位側のスイッチング素子S¥nとの双方がオン状態となるものを除き、全てのスイッチングパターンを指令することができる。

【0090】

(10)スイッチングモードの切り替えに際して、スイッチング状態の切り替えがなされるレッグにおける高電位側のスイッチング素子S¥pの操作信号g¥pおよび低電位側のスイッチング素子S¥nの操作信号g¥nの双方をオフ指令とした。これにより、ドライブユニットDU側にデッドタイムを生成する手段を備えることなく、デッドタイムDTをマイクロプロセッサユニット50から出力される操作信号g¥#によって指令することができる。

【0091】

(11)降圧コンバータ66を、過電流保護回路102の電源とした。これにより、過電流保護回路102の電源を確保することができる。

【0092】

(12)1次側コイルW1と2次側コイルW2n,W2u,W2v,W2wとを互いに絶縁した。これにより、1次側コイルW1に接続される部材(マイクロプロセッサユニット50、送信ユニット40)と2次側に接続される部材(ドライブユニットDU)との動作電位が相違する場合であっても、これに適切に対処することができる。

【0093】

(13)2次側コイルW2n,W2u,W2v,W2wの変動量を縮小変換してデコーダ74に入力するデータスライサ72を備えた。これにより、2次側コイルW2n,W2u,W2v,W2wの電圧の変動量を整流回路62の出力電圧(たとえば20V程度)の要求に応じて設定しつつも、デコーダ74の入力電圧を適切な値(たとえば5V)とすることができる。

【0094】

(14)モータジェネレータ10の制御量の制御手法として、モデル予測制御を採用した。これにより、その制御周期よりも1フレーム周期(10・T0)を短くすることで、信号の伝送に起因して制御の応答遅れが生じる事態を好適に回避することができる。

<第2の実施形態>

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0095】

図9に、本実施形態にかかる送信ユニット40、トランスTおよび受信ユニット30を備える伝送装置の構成を示す。なお、図9において、先の図3に示した部材に対応するものについては、便宜上同一の符号を付している。

【0096】

本実施形態では、デコードされた信号(シフトレジスタ76に格納された信号)について、同一レッグの上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオン指令である場合、操作信号g¥#の更新を禁止し、所定周期に渡ってそうした事態が継続することでインバータINVを構成する全スイッチング素子S¥#を強制的にオフ操作する。

【0097】

すなわち、AND回路86では、シフトレジスタ76の5番目および6番目のデータがともにオン指令を示すか否かを判断し、AND回路88では、シフトレジスタ76の7番目および8番目のデータがともにオン指令を示すか否かを判断し、AND回路90では、シフトレジスタ76の9番目および10番目のデータがともにオン指令を示すか否かを判断する。一方、NOR回路92では、AND回路86,88,90の出力信号に基づき、少なくとも1レッグで上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオン指令となっているか否かを判断する。そして、AND回路82では、同期信号識別回路78,80の双方が同期信号を検出して且つ、上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオン指令となるレッグが存在しないと判断される場合、操作信号出力回路84にイネーブル信号を出力する。

【0098】

また、AND回路94では、AND回路82の出力信号とクロック信号CLKとの論理積信号を生成し、ウォッチドッグタイマ96に入力する。ウォッチドッグタイマ96では、規定の長さを有する時間に渡ってイネーブル信号およびクロック信号CLKが入力されない場合、操作信号出力回路84をリセットする。本実施形態では、この規定の長さを有する時間を3フレーム分の時間とし、CR回路等のアナログ回路によってこの時間を定める。これにより、操作信号gupがリセットされる。こうした処理は、V相、W相の上側アームやU相の下側アームのドライブユニットDU内の受信ユニット30でも同様に行われるため、インバータINVの全スイッチング素子S¥#がオフ操作されることとなる。<第3の実施形態>

以下、第3の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0099】

図10に、本実施形態にかかる信号および電力の伝送対象を示す。なお、図10において、先の図1に示した部材に対応するものについては、便宜上同一の符号を付している。

【0100】

図示されるように、本実施形態では、パラレルシリーズハイブリッド車を想定しており、第1モータジェネレータ10aおよび第2モータジェネレータ10bを備える。これら第1モータジェネレータ10aおよび第2モータジェネレータ10bは、それぞれインバータINVa,INVbを介してコンバータCNVに接続されている。コンバータCNVは、一対のスイッチング素子Scp,Scnの接続点にリアクトルLを介して高電圧バッテリ12の正極が接続されたものである。

【0101】

本実施形態では、図示されるように、コンバータCNVのスイッチング素子Scp,ScnのそれぞれのドライブユニットDUに受信ユニット30aが搭載されている。また、インバータINVaの高電位側のスイッチング素子S¥pとU相の低電位側のスイッチング素子SunとのそれぞれのドライブユニットDUに受信ユニット30bが搭載されている。さらに、インバータINVbの高電位側のスイッチング素子S¥pと低電位側のスイッチング素子SunとのそれぞれのドライブユニットDUに受信ユニット30cが搭載されている。

【0102】

図11に、受信ユニット30a,30b,30cのそれぞれの一部構成を示す。図示されるように、受信ユニット30aのAND回路82からのイネーブル信号は、操作信号出力回路84に直接入力される。これに対し、受信ユニット30b,30cのAND回路82からのイネーブル信号は、遅延回路83b,83cのそれぞれを介して操作信号出力回路84に入力される。ここで、遅延回路83bと遅延回路83cとでは、遅延時間が互いに相違する。

【0103】

これにより、図12に示すように、コンバータCNVとインバータINVaとインバータINVbとで、スイッチング状態の切り替え可能タイミングを相違させることができる(ここで、切り替え可能タイミングとは、フレームデータに応じた操作信号の更新タイミングのことであり、必ずしもスイッチング状態が切り替えられるタイミングとはならない)。

【0104】

このように、スイッチング状態の切り替え可能タイミングを互いに相違させることで、サージ電圧を低減することができる。

<第4の実施形態>

以下、第4の実施形態について、先の第3の実施形態との相違点を中心に図面を参照しつつ説明する。

【0105】

本実施形態では、先の図10に示した受信ユニット30a,30b,30cを同一構成とする。

【0106】

図13に、本実施形態にかかるフレームデータの伝送態様を示す。図示されるように、本実施形態では、1フレームにおいてインバータINVa,INVbの双方の操作信号とコンバータCNVの操作信号とを含みつつも、それらの更新周期を3フレームとして、順次更新する。図では、インバータINVaの操作信号g¥#が更新(サンプリング番号n)された次のフレームで、インバータINVbの操作信号g¥#が更新され、その次のフレームでコンバータCNVの操作信号gcp、gcnが更新される例を示している。

【0107】

こうした設定によっても、コンバータCNVとインバータINVaとインバータINVbとで、スイッチング状態の切り替え可能タイミングを相違させることができる。

<第5の実施形態>

以下、第5の実施形態について、先の第3の実施形態との相違点を中心に図面を参照しつつ説明する。

【0108】

本実施形態では、先の図10に示した受信ユニット30a,30b,30cを同一構成とする。

【0109】

図14に、本実施形態にかかるフレームデータの伝送態様を示す。図示されるように、本実施形態では、1フレームにおいて、インバータINVaとインバータINVbとコンバータCNVとのいずれか1つの操作信号を含め、且ついずれの操作信号かを指定する信号を含める。そして、3フレームに1度ずつインバータINVaとインバータINVbとコンバータCNVとのそれぞれの操作信号を伝送する。

【0110】

こうした設定によっても、コンバータCNVとインバータINVaとインバータINVbとで、スイッチング状態の切り替え可能タイミングを相違させることができる。

<第6の実施形態>

以下、第6の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0111】

図15に、本実施形態にかかるスイッチングモードの更新可能タイミングを示す。図中、時刻t1,t2,t3,t4が更新可能タイミングである。ここで、更新可能タイミングとは、スイッチングモードを変更することが可能なタイミングを意味し、必ずしも変更がなされるタイミングを意味しない。

【0112】

図示されるように、本実施形態では、更新可能タイミング間の周期を、1フレーム(ここでは、1フレームを10ビットとする例を想定しているため、単位期間T0の10倍の期間)とする。これは、スイッチングモードの変更タイミングの遅延ばらつきを低減するための設定である。すなわち、モデル予測制御では、更新可能タイミングにおいてスイッチングモードを更新した場合の制御性を予測評価することで、実際のスイッチングモードを決定する。このため、スイッチングモードの実際の更新タイミングがばらつく場合には、モデル予測制御の制御性が低下する懸念が生じる。ここで、上記設定によれば、スイッチングモードの決定から実際にスイッチングモードが変更されるまでの遅延時間を略固定することができるため、遅延時間のばらつきを好適に低減することができる。

【0113】

これに対し、スイッチングモードの更新可能周期の整数分の1が1フレームとならない場合には、マイクロプロセッサユニット50の規定するスイッチングモードの更新可能タイミングに対する実際の更新タイミングの遅延時間がばらつくこととなる。

<第7の実施形態>

以下、第7の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0114】

本実施形態では、モータジェネレータ10を流れる電流を指令値にフィードバック制御するための操作量としての指令電圧がインバータINVの出力電圧となるように、3角波比較PWM処理によって操作信号を生成する周知の電流フィードバック制御を行なう。

【0115】

図16に、本実施形態にかかるシステム構成を示す。なお、図16において、先の図1に示した部材に対応するものについては、便宜上同一の符号を付している。

【0116】

図中、マイクロプロセッサユニット50の内部には、周知の電流フィードバック制御の概要のブロック図を記載してある。すなわち、指令電圧vd*,vq*は、モータジェネレータ10を流れるd軸電流idおよびq軸電流iqのそれぞれを指令電流id*,iq*のそれぞれにフィードバック制御するための操作量であり、3相の指令電圧vu*,vv*,vw*は、指令電圧vd*,vq*を3相変換したものである。そして、3相の指令電圧v¥*(¥=u,v,w)をインバータINVの入力電圧で規格化したDuty信号D¥と三角波形状のキャリア信号Scとの大小比較に基づき、PWM信号g¥を生成する。このPWM信号g¥の立ち上がりエッジをデッドタイムだけ遅延させた信号が上側アームの操作信号g¥pであり、PWM信号g¥の論理反転信号の立ち上がりエッジをデッドタイムだけ遅延させた信号が下側アームの操作信号g¥nである。

【0117】

この場合、基本的に、操作信号g¥#の指令が変化するタイミングは、キャリア信号Scの変化の分解能に依存するものの、略任意のタイミングとなり得る。たとえば、キャリア信号Scの周期を「50μs」とし、キャリア信号Scの変化を「10MHz」のクロックで生成する場合、操作信号g¥#の切り替わり自体は、「50μs」に1度であるものの、そのタイミングは、「0.1μs」の時間分解能を有する。

【0118】

ここで、上記時間分解能に対応する時間間隔よりも長い周期毎にフレームを出力したのでは、マイクロプロセッサユニット50によって規定される操作信号g¥#の変化タイミングに対するドライブユニットDU側での操作信号g¥#の変化タイミングの遅延時間が大きくばらつくこととなる。そして、これは指令電圧v¥#の制御性の低下をもたらし、ひいてはインバータINVの出力線間電圧の基本波成分の制御性の低下をもたらす。

【0119】

これに対し、上記時間分解能に対応する時間間隔でフレームを出力することは、伝送レートを極めて大きくする必要があり、伝送装置の高速性能に対する要求が過大となるおそれがある。

【0120】

そこで本実施形態では、フレームの出力タイミングを操作信号g¥#の変化に同期させる。

【0121】

図17に、本実施形態にかかる1次側コイルw1への電圧印加処理の手順を示す。この処理は、送信ユニット40によって実行される。

【0122】

この一連の処理では、まずステップS10において、操作信号g¥#の中に、オン操作指令からオフ操作指令に変化したものや、オフ操作指令からオン操作指令に変化したものがあるか否かを判断する。

【0123】

ステップS10において肯定判断される場合、ステップS12において、フレームの出力中であるか否かを判断する。そして、フレームの出力中である場合には、フレームの出力終了まで待機する一方、フレームの出力中でない場合には、ステップS14に移行する。ステップS14においては、操作信号g¥#の符号化処理を行なう。そして、ステップS16においては、符号化処理された操作信号g¥#を含むフレームを出力する。なお、ステップS14、S16の処理は、本実施形態において、同期手段を構成する。

【0124】

一方、ステップS10において否定判断される場合、ステップS17において、フレームの出力中であるか否かを判断する。そして、フレームの出力中である場合には、フレームの出力終了まで待機する一方、フレームの出力中でない場合には、ステップS18において、マンチェスタ符号における「0」を継続して出力する。ここで、フレーム出力停止時であっても1次側コイルw1に電圧を印加するのは、ドライブユニットDUに対する給電のためである。また、「0」を出力するのは、ドライブユニットDUの給電のための電圧印加処理に起因してトランスTの磁気飽和が生じる事態を回避するためである。ちなみに、「0」は、先の図4に示す同期信号の冒頭の符号である「0」と同一であるため、フレームの出力への切り替え時には、「1」からはじめればよく、フレームの出力を迅速に行なうことが可能となるというメリットもある。

【0125】

なお、上記ステップS16、S18の処理が完了する場合には、この一連の処理を一旦終了する。

【0126】

図18に、本実施形態の効果を示す。なお、図では、ドライブユニットDU側での操作信号g¥#の変化を、スイッチング素子S¥#の状態変化として模式的に示している。

【0127】

図示されるように、U相上側アームの操作信号gupのオン操作指令への切り替わりタイミングから、ドライブユニットDU側での操作信号gupのオン操作指令への切り替わりタイミング(スイッチング素子Supのオン状態への切り替え開始タイミング)までには遅延が生じる。ただし、この遅延時間は、V相上側アームの操作信号gvpのオン操作指令への切り替わりタイミングから、ドライブユニットDU側での操作信号gvpのオン操作指令への切り替わりタイミング(スイッチング素子Svpのオン状態への切り替え開始タイミング)までの遅延時間と略等しい。このため、操作信号gupのオン操作指令への切り替わりタイミングから操作信号gvpのオン操作指令への切り替わりタイミングまでの時間間隔T1と、スイッチング素子Supのオン状態への切り替わり開始タイミングからスイッチング素子Svpのオン状態への切り替わり開始タイミングまでの時間間隔T2とは略等しい。このため、インバータINVの出力線間電圧の基本波成分を、指令電圧vu*,vv*,vw*によって定まるものに好適に制御することができる。

<第8の実施形態>

以下、第8の実施形態について、先の第2の実施形態との相違点を中心に図面を参照しつつ説明する。

【0128】

図19に、本実施形態にかかる1次側コイルw1への電圧印加処理の手順を示す。この処理は、送信ユニット40によって実行される。なお、図19に示す処理において、先の図17に示した処理に対応するものについては、便宜上、同一のステップ番号を付している。

【0129】

図示されるように、本実施形態では、ステップS17において否定判断される場合、ステップS20において、フレーム出力後所定時間が経過したか否かを判断する。この処理は、操作信号g¥#についての情報が前回のものと同一である情報を有するフレームを再送するか否かを判断するためのものである。これは、フレームの伝送に際してエラーが生じた場合に、エラーからの復帰を早期に行なうためのものである。

【0130】

特に、本実施形態では、先の図9に示したウォッチドッグタイマ96において、規定時間に渡ってイネーブル信号およびクロック信号CLKが入力されない場合、対応するスイッチング素子S¥#がオフ操作されるため、ステップS10において肯定判断されることで出力されたフレームの伝送にエラーが生じる場合には、インバータINVが停止制御されるおそれがある。このため、上記所定時間を、ウォッチドッグタイマ96における上記規定時間未満に設定することで、インバータINVの停止制御がなされる事態が生じることを極力回避する。なお、この規定時間は、上記第2の実施形態のように3フレーム分の長さとする代わりに、それよりも長い時間としてもよい。ちなみに、ステップS20、S14,S16の処理は、本実施形態において、再送手段を構成する。

<第9の実施形態>

以下、第9の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0131】

本実施形態では、インバータINVの出力電圧を指令電圧v¥*とするための処理として、三角波比較PWM処理に代えて、空間ベクトル変調処理を採用する。ここで空間ベクトル変調処理は、所定時間におけるインバータINVの出力電圧の平均値を指令電圧v¥*とするための処理の1つであるが、所定時間において採用されるスイッチングモードの順序や時間が三角波PWM処理による制約を受けないものである。すなわち所定時間において採用される各スイッチングモードに対応する電圧ベクトルの平均値が指令電圧v¥*となるとの条件で、スイッチングモードの選択やその採用時間の自由度を向上させることができるものである。

【0132】

この場合、スイッチング状態の切り替えのなされるモータジェネレータ10の端子数が複数となるおそれがある。そこで本実施形態では、図20に記載する処理を行なう。

【0133】

図20は、本実施形態にかかる1次側コイルw1への電圧印加処理の手順を示す。この処理は、送信ユニット40によって実行される。なお、図20に示す処理において、先の図17に示した処理に対応するものについては、便宜上、同一のステップ番号を付している。

【0134】

図示されるように、本実施形態では、ステップS10において肯定判断される場合、ステップS22において、操作信号g¥#のうち、指令が変化する信号が複数あることを条件に、それらの変化の情報を同時に出力するか、一部の出力を遅延するかを選択する。この選択は、マイクロプロセッサユニット50の記憶手段に、同時のスイッチング状態の切り替えを許容するスイッチングパターンと許容しないスイッチングパターンとを記憶しておき、これらスイッチングパターンと操作信号g¥#の変化前後のパターンとの照合に基づき行われる。以下、記憶手段に記憶されるスイッチングパターンの概念について、図21に基づき説明する。

【0135】

図21は、スイッチング素子Supのオフ状態への切り替え指令と、スイッチング素子Svpのオン状態への切り替え指令とを同時に伝送することを許容して(図21(A))且つ、スイッチング素子Supのオフ状態への切り替え指令と、スイッチング素子Swpのオン状態への切り替え指令とについて、それらの同時伝送を禁止する(図21(B))例を示す。

【0136】

これは、図21(A)に示すケースの方が、図21(B)に示すケースと比較して、スイッチング状態の切り替えに起因してサージ電圧が小さくなると想定されることに基づくものである。すなわち、スイッチング素子Supがオフ状態となると同時にスイッチング素子Svpがオン状態となる場合、正極側直流母線Lpにおいて電流量が変化する領域は、U相およびV相間である。これに対し、スイッチング素子Supがオフ状態となると同時にスイッチング素子Swpがオン状態となる場合、正極側直流母線Lpにおいて電流量が変化する領域は、U相およびW相間である。図からわかるように、U相およびV相間で電流量が変化する場合と比較して、U相およびW相間で電流量が変化する場合の方が、電流量が変化する電気経路が長い。このため、電流量が変化する部分の寄生インダクタも大きくなり、ひいてはサージが大きくなると想定される。

【0137】

なお、先の図20のステップS22の処理は、本実施形態において、延期手段を構成する。

<第10の実施形態>

以下、第10の実施形態について、先の第8の実施形態との相違点を中心に図面を参照しつつ説明する。

【0138】

本実施形態では、フレームの出力停止期間において、互いに極性の相違する電圧値(以下、H電圧、L電圧)のいずれか一方を選択的に印加する。ここで、H電圧は、バイフェーズ符号の論理「0」を構成する後半部分の電圧値であり、L電圧は、バイフェーズ符号の論理「0」を構成する前半部分の電圧値である。

【0139】

図22に、本実施形態にかかるフレーム出力停止期間における電圧印加処理の手順を示す。この処理は、送信ユニット40によって実行される。

【0140】

この一連の処理では、まずステップS30において、フレーム出力が完了した直後であるか否かを判断する。そして、ステップS30において肯定判断される場合、ステップS32において、積分値Inが上限側閾値InthH以上であるか否かを判断する。ここで、積分値Inは、トランスTの磁束と正の相関を有するパラメータである。詳しくは、後述する処理によって1次側コイルw1の印加電圧の時間積分値とされるものである。なお、上限側閾値InthHは、トランスTが磁気飽和しない上限値に基づき設定される。ステップS32において肯定判断される場合、ステップS34において、コイルw1にL電圧を印加する。なお、ステップS32、S34の処理は、本実施形態において、所定電圧印加手段および反転手段を構成する。

【0141】

一方、ステップS32において否定判断される場合、ステップS36において、積分値Inが下限側閾値InthL以下であるか否かを判断する。ここで、下限側閾値InthLは、トランスTが磁気飽和しない上限値に基づき設定される。そして、ステップS36において肯定判断される場合、ステップS38において、コイルw1にH電圧を印加する。なお、ステップS36、S38の処理は、本実施形態において、所定電圧印加手段および反転手段を構成する。

【0142】

これに対し、ステップS30において否定判断される場合や、ステップS36において否定判断される場合には、ステップS40に移行する。ステップS40においては、積分値Inを更新する。ここでは、ステップS34の処理がなされた後、ステップS30またはステップS36において否定判断されている場合には、積分値Inをデクリメントする。また、ステップS38の処理がなされた後、ステップS30またはステップS36において否定判断されている場合には、積分値Inをインクリメントする。ただし、フレームの転送中においては、積分値Inの更新をしない。これは、フレームの転送時において1次側コイルw1に印加される電圧の平均値がゼロとなることによる。なお、ステップS40の処理は、本実施形態において、磁束算出手段を構成する。

【0143】

なお、ステップS34,S38,S40の処理が完了する場合には、この一連の処理を一旦終了する。

<第11の実施形態>

以下、第11の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0144】

本実施形態は、燃料電池の状態監視装置に対する信号および電力の伝送装置である。

【0145】

図23に、本実施形態にかかるシステム構成を示す。

【0146】

図示される組電池110は、車載主機としてのモータジェネレータ(図示略)に対する電力供給源であり、その端子電圧がたとえば100V以上となるものである。組電池110は、燃料電池によって構成される電池セルCij(i=1〜m、j=1〜n)の直列接続体である。電池セルCijは、全て同一仕様であり、個体差や経年変化を除き端子電圧が等しくなるものである。電池セルCijは、隣接するn個ずつでグループ化され、ブロックBiを構成している。各ブロックBiの状態は、監視ユニットUiによって監視される。

【0147】

上記組電池110の負極電位は、車体電位と相違するように設定されている。監視ユニットUiは、マイクロプロセッサユニット50からの指令に基づき、ブロックBi内の電池セルCi1〜Cinの電圧異常の有無を診断し、診断結果信号DSiをフォトカプラ112を介してマイクロプロセッサユニット50に出力する。

【0148】

ここで、マイクロプロセッサユニット50は、監視指令信号を送信ユニット40に出力する。送信ユニット40では、監視指令信号をデジタルベースバンド符号化処理し、パルス符号化された電圧信号を1次側コイルW1に印加する。これにより、1次側コイルW1に磁気結合されて且つ監視ユニットUiのそれぞれに接続された2次側コイルW2にパルス電圧が誘起される。監視ユニットUiは、2次側コイルW2に接続された受信ユニット30を備え、ここで、2次側コイルW2に誘起される電圧信号を復号処理し、監視指令信号を取り出すとともに、2次側コイルW2に誘起される電圧によって流れる電流を整流することで電力を取り出す。

【0149】

このように、本実施形態では、各監視ユニットUiに対する監視指令信号の送信や監視ユニットUiに対する電力の送信を単一のトランスTを用いて行なうことができる。特に、監視ユニットUiは、ブロックBiを電源とする必要がないため、電池セルC11の発電停止時においても動作可能となる。

<その他の実施形態>

なお、上記各実施形態は、以下のように変更して実施してもよい。

【0150】

「パルス符号化について」

2値のそれぞれを示すパルスの論理「H」期間と論理「L」期間とが等しい(時比率が50%)である符号としては、マンチェスタ符号に限らず、たとえば差分マンチェスタ符号であってもよい。もっとも、バイフェーズ符号としては、2値のそれぞれを示すパルスの論理「H」期間と論理「L」期間とが等しい(時比率が50%である符号)にも限らず、バイフェーズNRZ符号や、CMI等であってもよい。また、パルス符号としては、2値的なものに限らず、たとえばAMI符号等であってもよい。そのほか、8b10b符号や、6b8b符号、PR4符号等であってもよい。

【0151】

「符号化手段について」

上記実施形態では、操作信号g¥#を生成するソフトウェア処理手段(マイクロプロセッサユニット50)とは別に専用のハードウェア手段(エンコーダ41)によって構成したが、これに限らず、ソフトウェア処理手段によって構成してもよい。

【0152】

「電圧印加手段について」

フルブリッジ回路46を備えるものに限らず、たとえば図24(a)に示すように、プッシュプル回路を備えて構成してもよく、また、図24(b)に示すように、1次側コイルW1と電源との間のループ経路を単一のスイッチング素子にて開閉するものであってもよい。

【0153】

「復号手段について」

たとえば上記第1の実施形態(図1)や第2の実施形態(図9)において、下側アームのドライブユニットDUのそれぞれに受信ユニット30を搭載してもよい。この場合、これらに接続される2次側コイル同士を各別の部材とすることで、インバータINVの負極側の直流母線における電圧降下に起因した下側アームの各ドライブユニットDUのグランド電位の変動の影響を受けることなく、スイッチング素子S¥nを駆動することができる。

【0154】

上記第4の実施形態(図13)や第5の実施形態(図14)において、下側アームのドライブユニットDUについては、いずれか1つのみに受信ユニット30を搭載するようにしてもよい。

【0155】

「同期信号について」

上記のものに限らない。特に、上下アームの双方がオンとなり得る構成の場合、同期信号の設定変更が特に重要である。こうした構成とは、たとえば、米国特許第7130205号明細書や特開2009−141989号公報に記載されているように、インバータとバッテリとの間にインピーダンスネットワークを接続し、上下アームをオン操作(シュートスルー)することでインバータの入力電圧を昇圧する構成の場合等である。この場合、たとえば、デッドタイム期間を受信ユニット30側で生成する設定とし、上下アームの双方がオフとなることがないように操作信号g¥p,g¥nを定めることで、オフに対応する符号が3つ以上連続するように同期信号を生成してもよい。もっとも、オン指令およびオフ指令を表現する2値の論理値のいずれをも表現しないパルスとして同期信号を符号化してもよい。

【0156】

なお、伝送対象となる対象信号として、同期信号を含むものに限らない。これを含まない場合であっても、たとえばクロック用のトランスを別途備え、クロック用のトランスによってフレームの先頭を指示する信号を伝送するようにするなら、復号処理を容易に実行することができる。

【0157】

「情報信号について」

上記第1の実施形態(図1)等において、符号化対象とする情報信号を、スイッチングモードを表現する操作信号のみとして且つ、受信ユニット30においてデッドタイム生成機能を搭載するようにしてもよい。

【0158】

「実行手段について」

上記第2の実施形態(図9)では、正常データが連続3周期以上受信できない場合にスイッチング素子S¥#を強制的にオフ状態としたが、これに限らず、たとえば連続2周期以上、または1周期受信できない場合であってもよい。また、スイッチング素子S¥#を強制的にオフ状態とするものに限らず、正常であったときのスイッチングを維持して且つ、異常がある旨を外部(マイクロプロセッサユニット50等)に通知するものであってもよい。

【0159】

「監視手段について」

スイッチング素子S¥#を流れる電流が過度に大きいか否かを判断する手段に限らない。たとえば、スイッチング素子S¥#の温度を監視する手段や、スイッチング素子S¥#の温度情報を外部に出力する手段等であってもよい。

【0160】

「整流回路について」

フルブリッジ方式の整流回路62に限らず、周知の整流回路を適宜利用してよい。

【0161】

「変換手段について」

たとえば、2次側コイルW2n,W2u,W2v,W2wに中点タップを備え、2次側コイルW2n,W2u,W2v,W2wの中点タップと一方の端部との間の電圧をデコーダ74の入力とするなら、出力側電圧信号の変動量を縮小変換する変換手段を備えなくてもよい。また、たとえば要求される電源の電圧が低い場合や、整流回路62の出力側に昇圧回路を備える場合等にあっても、変換手段を備えない構成としてもよい。

【0162】

「整流回路および復号手段の接続について」

並列接続に限らず、たとえば復号手段の出力側に整流回路を直列接続してもよい。また、これ以外の接続手法としては、「変換手段について」の欄に記載した手法もある。

【0163】

「フィルタ回路について」

2次遅れ回路に限らず、たとえば1次遅れ回路であってもよい。

【0164】

「スイッチングモードを所定周期で更新する制御について」

モデル予測制御に限らず、DTC(Direct Torque Control)等であってもよい。

【0165】

「符号化処理タイミングについて」

上記第6の実施形態(図15)では、スイッチングモードの更新可能周期をフレーム周期としたが、これに限らず、更新可能周期の整数分の1の周期をフレーム周期としてもよい。

【0166】

もっとも、モデル予測制御等の場合であっても、フレームを所定周期で出力することは必須ではない。たとえば上記第7の実施形態(図18)の要領で、スイッチングモードの変更タイミングに同期してフレームを出力するものであってもよい。なお、この場合、実際には、スイッチングモードの変更に伴って、2度、フレームを出力することとなる。これは、スイッチングモードの変更に伴って、上下アームのスイッチング状態がデッドタイムDTだけ離間して変更されるためである。

【0167】

「再送手段(ステップS20)について」

上記第1の実施形態(図3)のように、ウォッチドッグタイマ96を備えない構成の場合、所定時間を、たとえば上下アームのスイッチング素子S¥p,S¥nが双方オンとなる短絡状態の許容上限時間未満に設定することが望ましい。

【0168】

「指令変化検出手段(S10)について」

上記実施形態では、操作信号g¥#を入力してその変化を検出する専用のハードウェア処理手段としたが、これに限らない。たとえば、前回のサンプリング周期と今回のサンプリング周期とで操作信号g¥#に指令が相違するものの有無を判断するソフトウェア処理手段としてもよい。ただし、ここでのサンプリング周期は、1フレームよりも短い時間間隔とすることが望ましい。

【0169】

「同期手段(S12〜S16)について」

ハードウェア処理手段に限らないことについては、「指令変化検出手段」と同様である。

【0170】

「延期手段(S22)について」

上記第9の実施形態(図20、図21)では、同時のスイッチングを許可するパターンと禁止するパターンとの双方を記憶手段に記憶したが、いずれか一方であってもよい。

【0171】

上記第9の実施形態(図20、図21)では、同時のスイッチングを許可する旨が記憶手段に記憶されたスイッチングパターンについては、同時のスイッチングを許可するようにしたがこれに限らない。たとえば、スイッチング状態の切り替えを伴うモータジェネレータ10の端子数を固定値として一律制限してもよい。

【0172】

「所定電圧印加手段(S36,S40)について」

パルス符号化された信号を構成する電圧値の電圧を1次側コイルw1に印加する手段に限らず、これとは別の電圧値の電圧を印加する手段であってもよい。このほか、たとえば「磁束算出手段(S38,S42,S44)について」の欄に記載したものであってもよい。

【0173】

「磁束算出手段(S38,S42,S44)について」

上記第10の実施形態(図22)において例示したように、同一の極性を有する電圧の印加時間によって、磁束量を定量化するものに限らない。たとえば、所定電圧印加手段が印加電圧の極性が同一であって且つその絶対値を変化させるものである場合、電圧の積分値によって磁束量を定量化することが望ましい。

【0174】

またたとえば、トランスTの磁束のゼロ点を検出する手段を備え、ゼロ点の検出タイミングから所定時間経過することで、印加電圧の極性を反転させるものであってもよい。ここで、ゼロ点検出手段としては、たとえば、2次側コイルw2u,w2v,w2w,w2nに誘起される電流の極性の変化や、整流回路62のうちオンとなるダイオードの切り替わりを検出する手段として構成することができる。

【0175】

「反転手段(S32〜S40)について」

上記第10の実施形態(図22)では、フレームの出力直後を、印加電圧の極性の変更を許可するタイミングとしたが、これに限らず、所定電圧印加手段による電圧の印加時間が長くなる場合に極性を反転させてもよい。

【0176】

「同期手段によるフレーム出力がなされない期間について」

上記第7の実施形態(図18)等では、フレーム出力がなされない期間において、「0」に対応する電圧信号を印加したが、これに限らず、「1」に対応する電圧信号を印加してもよい。

【0177】

フレーム出力がなされない期間において、フレームとは相違する電圧信号を1次側コイルw1に印加するものに限らない。たとえば上記第8の実施形態(図19)に例示されるようにフレームの出力がなされない時間が制限される場合等にあっては、1次側コイルw1への電圧の印加自体を停止したとしてもドライブユニットDUへの電力供給停止期間が過度に長くならないため、1次側コイルw1への電圧の印加自体を停止することも可能ではある。

【0178】

「対象信号について」

電力変換回路を構成するスイッチング素子の操作信号や、燃料電池の監視指令信号に限らない。ただし、対象信号の入力側(伝送先)として電源を備えないものにおいて、指令に応じて所定の処理を実行するものに対する指令信号であることが望ましい。

【0179】

もっとも、これは、電源を備えうるシステムへの出力信号を対象信号とすることが有効でないことを意味しない。たとえば、上記第11の実施形態(図23)において、電池セルCijをリチウムイオン2次電池やニッケル水素2次電池等の2次電池とする場合、監視ユニットUiが電池セルCi1〜Cinを電源とすることも可能ではある。ただし、この場合、監視ユニットUiの個体差等に起因して監視ユニットU1〜Umの消費電力にばらつきが生じる場合、電池セルCi1〜Cinの消費電力がばらつき、ひいては充電率や端子電圧にばらつきが生じやすくなる。これに対し、上記第11の実施形態と同様の構成を採用することで、こうした問題を回避することができる。

【0180】

「2次側コイルについて」

たとえば高電圧システムの基準電位(高電圧バッテリ12の負極電位)と低電圧システムの基準電位(車体電位)とが同一であるなら、上記第1の実施形態(図1)等において、1次側コイルW1と下側アーム用の2次側コイルW2nとを接続してもよい。もっとも、下側アームのスイッチング素子の駆動に際してインバータINVの直流母線における電圧降下によって影響を受けないようにするためには、これらを接続しないことが望ましい。

【0181】

なお、対象信号の伝送先の構成によっては、2次側コイルが1つとなってもよい。

【0182】

「スイッチング状態の切り替え可能タイミングを相違させる部類分けについて」

・上記第5の実施形態(図10)等において、コンバータCNVと、インバータINVa,INVbとのスイッチング状態の切り替えタイミングを相違させて且つ、インバータINVa,INVb同士のスイッチング状態の切り替えタイミングの一致を許可する設定としてもよい。

【0183】

またたとえば、インバータINVの各相(レッグ)を1つの部類として、それら部類同士でスイッチング状態の切り替え可能タイミングを相違させてもよい。これは、上記第3〜第5の実施形態の手法によって行なうことができる。なお、この場合、各レッグを構成する高電位側のスイッチング素子S¥pと低電位側のスイッチング素子S¥nが1つずつであるなら、それら一対のスイッチング素子S¥p,S¥nのみが同一の部類の構成要素となる。

【0184】

さらに、部類分けの適用対象としては、高電位側のスイッチング素子と低電位側のスイッチング素子とからなる一対のスイッチング素子を構成要素とするものに限らず、また、スイッチング状態の切り替え可能タイミングを部類毎で相違させる目的はサージ低減に限らない。たとえば、低電位側のスイッチング素子と高電位側のダイオードとの直列接続体を備える周知の昇圧チョッパ回路を複数並列駆動する場合に、マルチフェーズ処理を行なうべくスイッチング状態の切り替えタイミングをずらしてもよい。

【0185】

「そのほか」

インバータの各相を構成する高電位側のスイッチング素子S¥pと低電位側のスイッチング素子S¥#とを複数並列接続してもよい。この場合、高電位側のスイッチング素子S¥pのうちこれら同一相のものでは受信ユニット30を共有できる。

【符号の説明】

【0186】

10…モータジェネレータ、30…受信ユニット、40…送信ユニット、41…エンコーダ、43…シフトレジスタ、72…データスライサ(変換手段の一実施形態)、74…デコーダ、W1…1次側コイル、W2n,W2u,Swv,W2w…2次側コイル。

【技術分野】

【0001】

本発明は、伝送対象となる信号の伝送と該伝送先への電力の伝送とを行なう信号および電力の伝送装置に関する。

【背景技術】

【0002】

この種の伝送装置としては、たとえば下記特許文献1に見られるように、駆動対象とするスイッチング素子の操作信号をトランスを介して駆動回路に出力するに際し、このトランスの2次側コイルの出力を、スイッチング素子のゲートを充電するための電力として利用するものも提案されている。詳しくは、トランスの2次側コイルに並列接続された一対のコンデンサの電荷をスイッチング素子のゲートに充電するために利用して且つ、一対のコンデンサの接続点の電位によってスイッチング素子のオン指令、オフ指令を識別する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許第3417127号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ただし、上記装置は、たとえば3相インバータを構成するスイッチング素子の操作信号の伝送装置として利用される場合、各レッグ毎にトランスを備える必要が生じる等、伝送対象とする信号の伝送先の数が増加する際に回路規模の大型化や部品点数の増大を招きやすい。

【0005】

また、上記一対のコンデンサの電圧がオン・オフの指令に応じて変動するため、上記装置では、スイッチング素子のゲートの充電以外の電源が必要であっても上記一対のコンデンサを利用することが困難であり、別途電源を用意する必要が生じる。

【0006】

さらに、スイッチング素子のオン指令期間やオフ指令期間が長くなる場合、トランスの1次側コイルや2次側コイルを鎖交する磁束が過度に大きくなるおそれがある。このため、トランスを大型化する要求が生じやすい。

【0007】

本発明は、上記課題を解決する過程でなされたものであり、その目的は、伝送対象となる信号の伝送と該伝送先への電力の伝送とを行なう新たな信号および電力の伝送装置を提供することにある。

【課題を解決するための手段】

【0008】

以下、上記課題を解決するための手段、およびその作用効果について記載する。

【0009】

請求項1記載の発明は、互いに磁気結合した1次側コイルおよび2次側コイルと、伝送対象となる対象信号をパルス符号化する符号化手段と、前記符号化手段の出力に応じた電圧信号である入力側電圧信号を前記1次側コイルに印加する電圧印加手段と、前記入力側電圧信号によって前記2次側コイルに誘起される電圧信号である出力側電圧信号の変化に基づき、前記出力側電圧信号を復号する復号手段と、前記入力側電圧信号によって前記2次側コイルに誘起される電圧信号に応じて前記2次側コイルに接続される電気経路に流れる電流を整流する整流回路と、を備えることを特徴とする。

【0010】

上記発明では、対象信号をパルス符号化することで、磁気結合した1次側コイルおよび2次側コイルを介して対象信号を伝送させることが容易となる。また、出力側電圧信号は、パルス信号であるため、その変化に基づきパルス符号化された信号を検出することができ、ひいてはこれを復号することで対象信号を抽出することができる。また、2次側コイルから出力側電圧信号が出力されることで流れる電流を整流する整流回路を備えることで、整流回路を、対象信号の出力側における直流電源として利用することができる。

【0011】

請求項2記載の発明は、請求項1記載の発明において、前記復号手段は、第1出力経路を介して前記2次側コイルに接続され、前記整流回路は、前記第1出力経路とは相違する第2出力経路を介して前記2次側コイルに接続されていることを特徴とする。

【0012】

上記発明では、復号手段と整流回路とが互いに相違する経路を介して同一の2次側コイルに接続されるため、復号手段の入力電圧と整流回路の出力電圧とを各別とする設定等が容易となる。

【0013】

請求項3記載の発明は、請求項1または2記載の発明において、前記対象信号は、情報信号と、該情報信号の更新の都度、該情報信号に先立って情報信号が伝送される旨を示す同期信号とを含むことを特徴とする。

【0014】

上記発明では、対象信号に同期信号を含めることで、情報信号が更新される都度、更新された情報信号である旨を復号手段側で把握することが容易となる。

【0015】

請求項4記載の発明は、請求項3記載の発明において、前記符号化手段による符号化処理は、前記入力側電圧信号が前記1次側コイルに印加されることによる前記1次側コイルおよび前記2次側コイルの鎖交磁束についての前記同期信号と前記情報信号との1周期に対応する期間にわたる変化量をゼロとするものであることを特徴とする。

【0016】

上記発明では、鎖交磁束が過度に大きくなることを好適に回避することができ、ひいては、磁気部品を小型化することができる。

【0017】

請求項5記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記パルス符号は、バイフェーズ符号であることを特徴とする。

【0018】

DMI符号やマンチェスタ符号等のバイフェーズ符号は、2値のそれぞれの継続時間が短い符号であるため、1次側コイルや2次側コイルの鎖交磁束の増大を抑制しやすい。このため、上記発明では、磁気部品を小型化することができる。

【0019】

請求項6記載の発明は、請求項1〜5のいずれか1項に記載の発明において、前記復号手段は、前記出力側電圧信号に基づきクロック信号を生成するクロック生成手段を備えることを特徴とする。

【0020】

上記発明では、出力側電圧信号がパルス符号化された信号であることに鑑み、パルスを利用してクロックを生成することで、復号処理を容易に行なうことができる。

【0021】

請求項7記載の発明は、請求項1〜6のいずれか1項に記載の発明において、前記整流回路には、前記整流回路の出力電流を平滑化するフィルタ回路が接続されており、前記フィルタ回路の時定数は、前記出力側電圧信号の電圧値が一定となる最長時間よりも長く設定されていることを特徴とする。

【0022】

出力側電圧信号の電圧値が一定となる最長時間と比較して上記時定数が小さい場合、フィルタ回路の平滑化機能が復号手段の入力信号に干渉することで、復号手段による復号処理に支障が生じることが懸念される。上記発明では、この点に鑑み、上記設定とした。

【0023】

請求項8記載の発明は、請求項1〜7のいずれか1項に記載の発明において、前記2次側コイルは、互いに電位の相違しうる部材のそれぞれに接続される複数のコイルからなり、前記復号手段は、前記複数のコイルのそれぞれ毎に備えられることを特徴とする。

【0024】

上記発明では、互いに電位の相違しうる部材のそれぞれに対象信号と電力とを伝送することができる。

【0025】

請求項9記載の発明は、請求項8記載の発明において、前記2次側コイルは、直列接続された一対のスイッチング素子である高電位側のスイッチング素子および低電位側のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれに接続されるコイルを含み、前記対象信号は、前記スイッチング素子のオン・オフの指令信号を含むことを特徴とする。

【0026】

上記発明では、駆動回路に、スイッチング素子のオン・オフの指令信号と電力とを伝送することができる。

【0027】

請求項10記載の発明は、請求項9記載の発明において、前記2次側コイルに接続される駆動回路は、直列接続された一対のスイッチング素子の複数組のそれぞれの高電位側のスイッチング素子を駆動対象とする各別の駆動回路を備え、前記対象信号は、前記複数組の一対のスイッチング素子のそれぞれのオン・オフの指令信号と、該指令信号の更新の都度、該指令信号に先立って指令信号が伝送される旨を示す同期信号とを含み、前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、前記高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない信号であり、前記復号手段は、前記直列接続された一対のスイッチング素子のオン・オフの指令信号が、双方ともオン指令であることを異常として検出する異常検出手段を備え、該異常検出手段によって異常が検出されることに基づき、該異常に対処する異常対処処理を実行する実行手段をさらに備えることを特徴とする。

【0028】

上記発明では、実行手段を備えることで、双方ともオン指令である異常時に、異常な信号を正常としてスイッチング素子が駆動され続ける事態を回避することができる。

【0029】

請求項11記載の発明は、請求項9または10記載の発明において、前記2次側コイルに接続される駆動回路は、直列接続された一対のスイッチング素子の複数組のそれぞれの高電位側のスイッチング素子を駆動対象とする各別の駆動回路を備え、前記対象信号は、前記複数組の一対のスイッチング素子のそれぞれのオン・オフの指令信号と、該指令信号の更新の都度、該指令信号に先立って指令信号が伝送される旨を示す同期信号とを含み、前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、前記高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない信号であり、前記同期信号は、前記オン指令に対応する信号と同一の信号が3つ以上連続する信号であることを特徴とする。

【0030】

高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない場合、指令信号の配列によって、オン指令に対応する符号と同一符号が3つ以上連続しないようにすることができる。このため、上記設定とすることで、同期信号を、指令信号と識別可能な信号とすることができる。

【0031】

請求項12記載の発明は、請求項9〜11のいずれか1項に記載の発明において、前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、高電位側のスイッチング素子のオン指令および低電位側のスイッチング素子のオフ指令、高電位側のスイッチング素子のオフ指令および低電位側のスイッチング素子のオン指令、ならびに高電位側のスイッチング素子のオフ指令および低電位側のスイッチング素子のオフ指令の3つの指令パターンのいずれかであることを特徴とする。

【0032】

上記発明では、高電位側のスイッチング素子と低電位側のスイッチング素子との双方がオン状態となるものを除き、全てのスイッチングパターンを指令することができる。

【0033】

請求項13記載の発明は、請求項12記載の発明において、前記直列接続された高電位側のスイッチング素子および低電位側のスイッチング素子は、交互にオン状態となるように相補駆動されるものであって且つ、それら高電位側のスイッチング素子および低電位側のスイッチング素子のいずれか一方および他方のそれぞれがオン、オフとなる状態からオフ、オンとなる状態に移行するに先立ち、前記指令信号が双方のオフ状態を指令することを特徴とする。

【0034】

上記発明では、駆動回路側にデッドタイムを生成する手段を備えることなく、デッドタイムを対象信号によって指令することができる。

【0035】

請求項14記載の発明は、請求項9〜13のいずれか1項に記載の発明において、前記駆動回路は、前記スイッチング素子の駆動状態を監視する監視手段を備え、前記監視手段は、前記整流回路に電気的に接続されていることを特徴とする。

【0036】

上記発明では、監視手段に電源が必要となる。このため、整流回路を備えるメリットが特に大きい。これに対し、こうしたものを備えることなく、スイッチング素子を駆動する用途の場合には、通常のパルストランスを用いることも可能となり得る。

【0037】

請求項15記載の発明は、請求項8〜14のいずれか1項に記載の発明において、前記複数のコイルには、複数のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれが接続され、前記対象信号は、前記複数のスイッチング素子のそれぞれのオン・オフの指令信号を含み、前記複数のスイッチング素子のうち互いに相違する部類に属するスイッチング素子のそれぞれに対応する前記駆動回路同士で前記オン・オフ指令の入力から駆動対象とするスイッチング素子が操作されるまでの遅延時間を相違させる設定がなされていることを特徴とする。

【0038】

上記発明では、互いに相違する部類に属するスイッチング素子同士で同時にスイッチング状態の切り替え指令信号が出力されたとしても、これら互いに相違する部類に属するスイッチング素子同士でスイッチング状態の切り替えタイミングを相違させることができる。

【0039】

請求項16記載の発明は、請求項8〜14のいずれか1項に記載の発明において、前記複数のコイルには、複数のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれが接続され、前記対象信号は、前記複数のスイッチング素子のそれぞれのオン・オフの指令信号を含み、前記対象信号は、前記1次側コイルおよび前記2次側コイルを介して周期的に伝送されるものであり、周期的な伝送の1周期の間に前記複数のスイッチング素子の全てのオン・オフを指令する信号が含まれて且つ、前記複数のスイッチング素子のうちの互いに相違する部類に属するスイッチング素子のそれぞれで互いに相違する周期で前記オン・オフを指令する信号が更新されることを特徴とする。

【0040】

上記発明では、互いに相違する部類に属するスイッチング素子同士でオン・オフの指令信号の更新タイミングが相違するため、これら互いに相違する部類に属するスイッチング素子同士でスイッチング状態の切り替えタイミングを相違させることができる。

【0041】

請求項17記載の発明は、請求項8〜14のいずれか1項に記載の発明において、前記複数のコイルには、複数のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれが接続され、前記対象信号は、前記複数のスイッチング素子のそれぞれのオン・オフの指令信号を含み、前記対象信号は、前記1次側コイルおよび前記2次側コイルを介して周期的に伝送されるものであり、周期的な伝送の1周期の間に前記複数のスイッチング素子のうちの互いに相違する部類のいずれかに属するスイッチング素子のオン・オフを指令する信号に加えて、該いずれかを指定する信号が伝送されることを特徴とする。

【0042】

上記発明では、伝送の周期毎にいずれか1つの部類が指定されるため、互いに相違する部類に属するスイッチング素子同士でスイッチング状態の切り替えタイミングを相違させることができる。

【0043】

請求項18記載の発明は、請求項15〜17のいずれか1項に記載の発明において、前記複数のスイッチング素子は、互いに相違する回転機に接続されて且つ共通の直流電圧源に接続された複数の直流交流変換回路を構成するものであって且つ、互いに相違する直流交流変換回路を構成するもの同士が互いに相違する部類とされるものであることを特徴とする。

【0044】

請求項19記載の発明は、請求項1〜18のいずれか1項に記載の発明において、前記1次側コイルと前記2次側コイルとは互いに絶縁されていることを特徴とする。

【0045】

上記発明では、1次側に接続される部材と2次側に接続される部材との動作電位が相違する場合であっても、これに適切に対処することができる。

【0046】

請求項20記載の発明は、請求項1〜19のいずれか1項に記載の発明において、前記出力側電圧信号の変動量を縮小変換して、前記復号手段に入力する変換手段をさらに備えることを特徴とする。

【0047】

上記発明では、出力側電圧信号の変動量を整流回路の出力電圧の要求に応じて設定しつつも、復号手段の入力電圧を適切な値とすることができる。

【図面の簡単な説明】

【0048】

【図1】第1の実施形態にかかるシステム構成図。

【図2】同実施形態にかかるスイッチング素子のオン・オフ操作手法を示すタイムチ ャート。

【図3】同実施形態にかかる伝送装置の構成を示す図。

【図4】同実施形態にかかる符号化信号を示すタイムチャート。

【図5】同実施形態にかかる復号処理を示すタイムチャート。

【図6】同実施形態にかかる性能評価結果を示すタイムチャート。

【図7】同実施形態にかかる性能評価結果を示すタイムチャート。

【図8】同実施形態にかかる性能評価結果を示す図。

【図9】第2の実施形態にかかる伝送装置の構成を示す図。

【図10】第3の実施形態にかかるシステム構成図。

【図11】同実施形態にかかるスイッチング状態の切り替えタイミングの設定手法を 示す図。

【図12】同実施形態の効果を示す図。

【図13】第4の実施形態にかかる情報信号の伝送手法を示すタイムチャート。

【図14】第5の実施形態にかかる情報信号の伝送手法を示すタイムチャート。

【図15】第6の実施形態にかかるスイッチングモードの更新可能周期を示すタイムチャート。

【図16】第7の実施形態にかかるシステム構成図。

【図17】同実施形態にかかるフレーム出力処理の手順を示す流れ図。

【図18】同実施形態にかかるフレーム出力処理態様を示すタイムチャート。

【図19】第8の実施形態にかかるフレーム出力処理の手順を示す流れ図。

【図20】第9の実施形態にかかるフレーム出力処理の手順を示す流れ図。

【図21】同実施形態にかかるフレーム出力処理態様を示すタイムチャート。

【図22】第10の実施形態にかかるフレーム出力停止期間の1次側コイルの電圧印加処理の手順を示す流れ図。

【図23】第11の実施形態にかかるシステム構成図。

【図24】上記各実施形態の変形例にかかる回路図。

【発明を実施するための形態】

【0049】

<第1の実施形態>

以下、本発明にかかる信号および電力の伝送装置をスイッチング素子の駆動回路への信号および電力の伝送装置に適用した第1の実施形態について、図面を参照しつつ説明する。

【0050】

図1に、本実施形態にかかるシステム構成を示す。

【0051】

図示されるように、車載主機としてのモータジェネレータ10は、3相の同期機である。モータジェネレータ10には、インバータINVを介して直流電圧源(高電圧バッテリ12)が接続されている。高電圧バッテリ12は、端子電圧がたとえば100V以上となる2次電池である。高電圧バッテリ12の正極電位および負極電位の中央値が車体電位となる設定とするなどして、高電圧バッテリ12の負極電位は、車体電位とは相違するように設定されている。この設定は、たとえば高電圧バッテリ12の電圧を分圧する複数のコンデンサの接続点を車体に接続することで実現することができる。

【0052】

インバータINVは、高電位側のスイッチング素子S¥p(¥=u,v,w)および低電位側のスイッチング素子S¥nの直列接続体を3組備え、これら各直列接続体を構成する高電位側のスイッチング素子S¥pおよび低電位側のスイッチング素子S¥nの接続点がモータジェネレータ10の各端子に接続されている。そして、スイッチング素子S¥#(¥=u,v,w:#=p,n)のそれぞれには、ダイオードD¥#のそれぞれが逆並列に接続されている。

【0053】

また、上記各スイッチング素子S¥#の開閉制御端子(ゲート)には、ドライブユニットDUが接続されている。ドライブユニットDUは、スイッチング素子S¥#のゲートの電圧を制御する機能が搭載された駆動部20を備えている。また、上側アームのスイッチング素子S¥pのドライブユニットDUとU相下側アームのスイッチング素子SunのドライブユニットDUとは、スイッチング素子S¥#のオン・オフの操作指令を受信する受信ユニット30を備えている。なお、V相およびW相の下側アームのスイッチング素子Svn,SwnのドライブユニットDUには、U相下側アームのスイッチング素子SunのドライブユニットDUによって受信された信号が取り込まれる。これは、下側アームのスイッチング素子Sun,Svn,SwnのそれぞれのドライブユニットDUの動作電位が等しいことに鑑みた設定である。

【0054】

上記モータジェネレータ10を流れる電流は電流センサ14によって検出される。そして、電流センサ14の検出値等、モータジェネレータ10の制御量(トルク等)を制御する上で必要な検出値は、マイクロプロセッサユニット50に入力される。マイクロプロセッサユニット50は、メモリに格納されたプログラムを中央処理装置によって実行するソフトウェア手段である。

【0055】

マイクロプロセッサユニット50では、電流センサ14の検出値等に基づき、モータジェネレータ10を流れる電流を、モータジェネレータ10のトルクを指令トルクとするうえで要求される指令電流に制御する。ここでは、たとえば特開2008−228419号公報等に記載されるモデル予測制御(MPC:Model Predictive Control)が用いられる。すなわち、インバータINVのスイッチングモードを仮設定した場合についてのそれぞれの電流を予測し、予測される電流と指令電流との差が最も小さくなるスイッチングモードを採用する。ここで、スイッチングモードは、インバータINVの6つのスイッチング素子S¥#(¥=u,v,w;#=p,n)のそれぞれがオンであるかオフであるかによって定まるものであり、8つのスイッチングモードが存在する。それらのうち、スイッチングモード1〜6は、インバータINVの出力電圧を図に示す有効電圧ベクトルV1〜V6とするものである。

【0056】

マイクロプロセッサユニット50では、スイッチングモードが決定されると、これに応じたスイッチング素子S¥#の操作信号g¥#を送信ユニット40に出力する。ここで、操作信号g¥#は、基本的にはスイッチングモードを表現するものであるが、スイッチングモードの切り代わり時には、上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方をオフ指令とすることで、図2に示すデッドタイムDTを表現する。ここで、デッドタイムDTは、スイッチングモードの切り替えに際して上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオンとなることがないように、スイッチング素子S¥#のスイッチング状態の切り替わり速度に基づき設定されるものである。

【0057】

送信ユニット40では、マイクロプロセッサユニット50から出力された操作信号g¥#をデジタルベースバンド符号にて符号化し、符号化された信号であるパルス信号に応じてトランスTの1次側コイルW1に電圧を印加する。これにより、トランスTの2次側コイルW2n,W2u,W2v,W2wにパルス状の電圧信号が出力される。

【0058】

ここで、2次側コイルW2nは、U相下側アームのスイッチング素子SunのドライブユニットDUに搭載された受信ユニット30に接続されている。また、2次側コイルW2u,v,wのそれぞれは、U,V,W相の上側アームのスイッチング素子Sup,Svp,SwpのそれぞれのドライブユニットDUに搭載された受信ユニット30に接続されている。

【0059】

以下、送信ユニット40、トランスTおよび受信ユニット30を備える伝送装置の構成について、図3に基づきさらに説明する。図3では、便宜上、U相の上側アームのスイッチング素子SupのドライブユニットDUに信号および電力を伝送する経路を、他の経路を代表して示している。

【0060】

マイクロプロセッサユニット50から出力された操作信号g¥#は、送信ユニット40内のエンコーダ41によってデジタルベースバンド符号化処理がなされ、パルス信号に符号化される。ここでは、パルス符号として、マンチェスタ符号が用いられる。図4に、マンチェスタ符号によって符号化されたパルス符号化信号を示す。図示されるように、マンチェスタ符号は、1ビットに対応する期間(単位期間T0)の中央で論理が反転するものであり、特に論理「0」と論理「1」とで、中央での反転極性が相違するものである。本実施形態では、同期信号(図中、Sync)を4ビットの信号とし、これに続いて各1ビットで操作信号gup,gun,gvp,gvn,gwp,gwnのそれぞれを順次表現する。これにより、操作信号gup,gun,gvp,gvn,gwp,gwnの出力周期である1フレームが、10ビットとなる。

【0061】

本実施形態では、同期信号を「0111」とする。これは、上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオンとなることがないために、操作信号g¥#を表現する6ビットのデータが、オン指令に対応する論理値「1」が3連続するデータを含み得ないことに鑑みた設定である。これにより、操作信号g¥#を表現するデータと同期信号とを識別することができる。ちなみに、同期信号の先頭データを「0」としたのは、操作信号g¥#と確実に識別するためである。

【0062】

なお、本実施形態では、単位期間T0の10倍の期間である1フレームの期間の整数N倍をデッドタイムDTとする。すなわち、スイッチングモードの切り替えに際しては、スイッチング状態の切り替わるレッグについて、Nフレームの期間にわたって、上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方をオフ指令とする。なお、1フレーム期間は、スイッチング状態の切り替えに際して双方がオン状態となることがない下限時間以下に設定することが望ましい。

【0063】

先の図3に示したエンコーダ41の出力信号は、シフトレジスタ43に入力される。シフトレジスタ43は、クロック信号clkに同期してパルス符号化された信号を1次側コイルW1に出力する。

【0064】

詳しくは、1次側コイルW1には、フルブリッジ回路46が接続されており、シフトレジスタ43の出力信号は、フルブリッジ回路46の各スイッチング素子を駆動するドライバ44,45に入力される。これにより、1次側コイルW1には、パルス符号化された信号に応じた電圧信号(入力側電圧信号)が印加される。

【0065】

1次側コイルW1に電圧信号が印加されると、2次側コイルW2uには、1次側コイルW1と2次側コイルW2uとの巻数比に応じた倍率で変動する電圧信号が誘起される。2次側コイルW2uに接続された受信ユニット30は、電源回路60とデコードユニット70とを備える。

【0066】

電源回路60は、2次側コイルW2uに誘起された電圧に応じて流れる電流を整流する整流回路62と、整流回路62から出力される電流を平滑化するフィルタ回路64と、フィルタ回路64の出力電圧を降圧する降圧コンバータ66とを備える。ここで、フィルタ回路64の出力電圧は、降圧コンバータ66に入力されるのに加えて、駆動部20に入力される。駆動部20は、デコードユニット70の出力する操作信号gupに応じてスイッチング素子Supを駆動する駆動IC100と、過電流保護回路102とを備える。ここで、過電流保護回路102は、スイッチング素子Supを流れる電流を監視し、この電流が閾値電流以上となることで、駆動IC100にスイッチング素子Supを強制的にオフ操作する指令を出力するものである。スイッチング素子Supを流れる電流が閾値以上であるか否かの判断は、スイッチング素子Supの入力端子(コレクタ)および出力端子(エミッタ)間を流れる電流と相関を有する微小電流を出力するセンス端子Stの出力電流が閾値以上であるか否かの判断処理となる。

【0067】

なお、上記降圧コンバータ66は、スイッチング素子Supの駆動用の電圧と、駆動IC100や、過電流保護回路102、デコードユニット70の電源電圧との相違に鑑み、電源電圧を生成するためのものであり、たとえば「20V」の入力電圧を5V程度に降圧する。

【0068】

一方、デコードユニット70は、2次側コイルW2uの電圧の変動量を縮小変換するデータスライサ72を備えている。データスライサ72は、2次側コイルW2uの電圧を、論理回路の動作電圧範囲に変換するための変換手段である。データスライサ72の出力電圧は、デコーダ74に入力される。デコーダ74は、XOR回路74aと、ワンショットパルス回路74bと、復号された信号を出力するDフリップフロップ74cとを備えている。

【0069】

ここで、XOR回路74aは、データスライサ72の出力電圧とDフリップフロップ74cの出力電圧との排他的論理和信号を出力する。ワンショットパルス回路74bは、ワンショットパルスの出力期間でないことを条件に、XOR回路74aの出力電圧の立ち上がりに同期して、予め定められた長さのパルス幅を有するパルス信号を出力する。ここで、パルス幅は、「3・T0/4」に設定される。これは、クロック信号CLKを容易に生成するための一設定である。そして、Dフリップフロップ74cでは、データ端子の出力信号を、ワンショットパルス信号の立ち下がりエッジのタイミングで、そのタイミングにおけるデータスライサ72の出力信号に更新する。

【0070】

図5に、デコーダ74の処理を示す。詳しくは、図5(a)に、デコーダ74の入力信号の推移を示し、図5(b)に、ワンショットパルス回路74bの出力信号の推移を示し、図5(c)に、復号された信号(Dフリップフロップ74cの出力信号)の推移を示し、図5(d)に、デコーダ74の入力信号から生成されるクロック信号CLK(XOR回路74aの出力信号)の推移を示す。

【0071】

先の図3に示すように、復号された信号は、シフトレジスタ76に入力される。シフトレジスタ76では、XOR回路74aの出力信号の立ち上がりエッジをクロック信号CLKとして用いて、Dフリップフロップ74cの出力信号を順次格納する。ここで、本実施形態では、シフトレジスタ76の記憶容量を14ビットとする。これは、1フレーム分のデータと次の1フレームの同期信号とを格納可能とするための設定である。

【0072】

同期信号識別回路78では、シフトレジスタ76の先頭の4ビットのデータが同期信号であるか否かを判断し、同期信号識別回路80では、シフトレジスタ76の最後の4ビットのデータが同期信号であるか否かを判断する。一方、AND回路82では、同期信号識別回路78,80の双方が同期信号を検出することで、操作信号出力回路84にイネーブル信号を出力する。操作信号出力回路84では、イネーブル信号に同期して、シフトレジスタ76の先頭から5ビット目の信号を操作信号gupとして、駆動IC100に出力する。

【0073】

なお、スイッチング素子Svp,SwpのそれぞれのドライブユニットDU内の操作信号出力回路84では、シフトレジスタ76の先頭から7番目、9番目の信号を操作信号gvp,gwpとしてそれぞれ出力する。また、スイッチング素子Sunのドライブユニット内の操作信号出力回路84では、シフトレジスタ76の先頭から6番目の信号を操作信号gupとして出力するとともに、8番目および10番目の信号を操作信号gvn,gwnとして、対応するドライブユニットDU内の駆動部20のそれぞれに出力する。

【0074】

ちなみに、上記フィルタ回路64の時定数τは、2次側コイルW2uの電圧値が固定される最長期間(ここでは、単位期間T0)よりも長く設定される。これは、フィルタ回路64によって、デコーダ74の入力電圧が方形波とならなくなる事態を回避するための設定である。ちなみに、ここでの時定数τとは、ステップ状の入力電圧の変化に対する平滑化される電圧の変化の割合が規定割合(たとえば37%)まで低下するのに要する時間として定義されるものである。時定数τは、応答性を定量化するためのパラメータであり、これが短いほど応答性が速いことを意味する。そして、フィルタ回路64の時定数τが2次側コイルW2uの電圧値が固定される最長期間よりも長いということは、フィルタ回路64の入力電圧の変動に伴ってフィルタ回路64がこれを平滑化するに際し、変動が規定割合以下に減衰するまでに要する時間が最長時間よりも長いことを意味する。

【0075】

図6〜図8に、本実施形態にかかる構成の性能評価結果を示す。

【0076】

図6は、伝送レートを「2.1Mpbs」とした場合について、操作信号gwpの伝送態様を示すものである。詳しくは、図6(a)は、マイクロプロセッサユニット50の出力する操作信号gwpの推移を示し、図6(b)は、1次側コイルW1の電圧の推移を示し、図6(c)は、2次側コイルW2wの電圧の推移を示し、図6(d)は、駆動IC100に出力される操作信号gwpの推移を示す。

【0077】

図7は、伝送レートを「2.1Mpbs」とした場合について、デコーダ74の処理を示す。詳しくは、図7(a)は、2次側コイルW2wの電圧の推移を示し、図7(b)は、クロック信号CLK(XOR回路74aの出力信号)の推移を示し、図7(c)は、デコードされた信号(Dフリップフロップ74c)の推移を示す。

【0078】

なお、伝送レートを「10Mpbs」以上とした場合であっても、図6、図7と同様、良好な信号伝送が実現可能であることが確認されている。

【0079】

図8は、伝送レートを「2.1Mpbs」,「5Mpbs」,「7.5Mpbs」,「10Mpbs」のそれぞれとした場合の伝送電力と2次側コイルW2wの出力電圧との関係を示す。図示されるように、伝送レートを「10Mpbs」としても電力の伝送は良好である。

【0080】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0081】

(1)2次側コイルW2n,W2u,W2v,W2wにデコードユニット70と電源回路60とを接続した。これにより、スイッチング素子S¥#の操作信号g¥#を伝送することおよびドライブユニットDUの電源電力を伝送することができる。

【0082】

(2)2次側コイルW2n,W2u,W2v,W2wに、電源回路60とデコードユニと70とを並列接続した。これにより、デコードユニット70内の動作電圧(たとえば5V)と、電源回路60の入力電圧(たとえば20V)とを相違させることが容易となる。

【0083】

(3)伝送対象となる信号を、操作信号g¥#と同期信号とによって構成した。これにより、操作信号g¥#が更新される都度、更新された操作信号g¥#である旨を容易に把握することができる。

【0084】

(4)マンチェスタ符号を用いて伝送対象となる信号をパルス符号化した。これにより、1フレーム(さらには、1ビット)に渡る1次側コイルの印加電圧の平均値をゼロとすることができ、ひいては、1次側コイルW1の鎖交磁束が過度に大きくなることを好適に回避することができる。

【0085】

(5)2次側コイルW2n,W2u,W2v,W2wに誘起される電圧に基づき、クロック信号CLKを生成した。これにより、復号処理を容易に行なうことができる。

【0086】

(6)フィルタ回路64の時定数τを、2次側コイルW2n,W2u,W2v,W2wの電圧値が一定となる最長時間よりも長く設定した。これにより、フィルタ回路64の平滑化処理によってデコードユニット70による復号処理に支障が生じることを好適に回避することができる。

【0087】

(7)トランスTの2次側コイルを、複数のコイル(2次側コイルW2n,W2u,W2v,W2w)とした。これにより、互いに動作電位の相違しうるドライブユニットDUへの信号および電力の伝送に際して1つのトランスTで対処することができる。

【0088】

(8)同期信号を、オン指令に対応する論理値が3つ継続する信号とした。これにより、操作信号g¥#と識別可能な信号とするうえで同期信号を極力短い信号とすることができる。

【0089】

(9)操作信号g¥p,g¥nを、高電位側のスイッチング素子S¥pのオン指令および低電位側のスイッチング素子S¥nのオフ指令、高電位側のスイッチング素子S¥pのオフ指令および低電位側のスイッチング素子S¥nのオン指令、ならびに高電位側のスイッチング素子S¥pのオフ指令および低電位側のスイッチング素子S¥nのオフ指令の3つの指令パターンのいずれかを示す信号とした。これにより、高電位側のスイッチング素子S¥pと低電位側のスイッチング素子S¥nとの双方がオン状態となるものを除き、全てのスイッチングパターンを指令することができる。

【0090】

(10)スイッチングモードの切り替えに際して、スイッチング状態の切り替えがなされるレッグにおける高電位側のスイッチング素子S¥pの操作信号g¥pおよび低電位側のスイッチング素子S¥nの操作信号g¥nの双方をオフ指令とした。これにより、ドライブユニットDU側にデッドタイムを生成する手段を備えることなく、デッドタイムDTをマイクロプロセッサユニット50から出力される操作信号g¥#によって指令することができる。

【0091】

(11)降圧コンバータ66を、過電流保護回路102の電源とした。これにより、過電流保護回路102の電源を確保することができる。

【0092】

(12)1次側コイルW1と2次側コイルW2n,W2u,W2v,W2wとを互いに絶縁した。これにより、1次側コイルW1に接続される部材(マイクロプロセッサユニット50、送信ユニット40)と2次側に接続される部材(ドライブユニットDU)との動作電位が相違する場合であっても、これに適切に対処することができる。

【0093】

(13)2次側コイルW2n,W2u,W2v,W2wの変動量を縮小変換してデコーダ74に入力するデータスライサ72を備えた。これにより、2次側コイルW2n,W2u,W2v,W2wの電圧の変動量を整流回路62の出力電圧(たとえば20V程度)の要求に応じて設定しつつも、デコーダ74の入力電圧を適切な値(たとえば5V)とすることができる。

【0094】

(14)モータジェネレータ10の制御量の制御手法として、モデル予測制御を採用した。これにより、その制御周期よりも1フレーム周期(10・T0)を短くすることで、信号の伝送に起因して制御の応答遅れが生じる事態を好適に回避することができる。

<第2の実施形態>

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0095】

図9に、本実施形態にかかる送信ユニット40、トランスTおよび受信ユニット30を備える伝送装置の構成を示す。なお、図9において、先の図3に示した部材に対応するものについては、便宜上同一の符号を付している。

【0096】

本実施形態では、デコードされた信号(シフトレジスタ76に格納された信号)について、同一レッグの上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオン指令である場合、操作信号g¥#の更新を禁止し、所定周期に渡ってそうした事態が継続することでインバータINVを構成する全スイッチング素子S¥#を強制的にオフ操作する。

【0097】

すなわち、AND回路86では、シフトレジスタ76の5番目および6番目のデータがともにオン指令を示すか否かを判断し、AND回路88では、シフトレジスタ76の7番目および8番目のデータがともにオン指令を示すか否かを判断し、AND回路90では、シフトレジスタ76の9番目および10番目のデータがともにオン指令を示すか否かを判断する。一方、NOR回路92では、AND回路86,88,90の出力信号に基づき、少なくとも1レッグで上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオン指令となっているか否かを判断する。そして、AND回路82では、同期信号識別回路78,80の双方が同期信号を検出して且つ、上側アームの操作信号g¥pと下側アームの操作信号g¥nとの双方がオン指令となるレッグが存在しないと判断される場合、操作信号出力回路84にイネーブル信号を出力する。

【0098】

また、AND回路94では、AND回路82の出力信号とクロック信号CLKとの論理積信号を生成し、ウォッチドッグタイマ96に入力する。ウォッチドッグタイマ96では、規定の長さを有する時間に渡ってイネーブル信号およびクロック信号CLKが入力されない場合、操作信号出力回路84をリセットする。本実施形態では、この規定の長さを有する時間を3フレーム分の時間とし、CR回路等のアナログ回路によってこの時間を定める。これにより、操作信号gupがリセットされる。こうした処理は、V相、W相の上側アームやU相の下側アームのドライブユニットDU内の受信ユニット30でも同様に行われるため、インバータINVの全スイッチング素子S¥#がオフ操作されることとなる。<第3の実施形態>

以下、第3の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0099】

図10に、本実施形態にかかる信号および電力の伝送対象を示す。なお、図10において、先の図1に示した部材に対応するものについては、便宜上同一の符号を付している。

【0100】

図示されるように、本実施形態では、パラレルシリーズハイブリッド車を想定しており、第1モータジェネレータ10aおよび第2モータジェネレータ10bを備える。これら第1モータジェネレータ10aおよび第2モータジェネレータ10bは、それぞれインバータINVa,INVbを介してコンバータCNVに接続されている。コンバータCNVは、一対のスイッチング素子Scp,Scnの接続点にリアクトルLを介して高電圧バッテリ12の正極が接続されたものである。

【0101】

本実施形態では、図示されるように、コンバータCNVのスイッチング素子Scp,ScnのそれぞれのドライブユニットDUに受信ユニット30aが搭載されている。また、インバータINVaの高電位側のスイッチング素子S¥pとU相の低電位側のスイッチング素子SunとのそれぞれのドライブユニットDUに受信ユニット30bが搭載されている。さらに、インバータINVbの高電位側のスイッチング素子S¥pと低電位側のスイッチング素子SunとのそれぞれのドライブユニットDUに受信ユニット30cが搭載されている。

【0102】

図11に、受信ユニット30a,30b,30cのそれぞれの一部構成を示す。図示されるように、受信ユニット30aのAND回路82からのイネーブル信号は、操作信号出力回路84に直接入力される。これに対し、受信ユニット30b,30cのAND回路82からのイネーブル信号は、遅延回路83b,83cのそれぞれを介して操作信号出力回路84に入力される。ここで、遅延回路83bと遅延回路83cとでは、遅延時間が互いに相違する。

【0103】

これにより、図12に示すように、コンバータCNVとインバータINVaとインバータINVbとで、スイッチング状態の切り替え可能タイミングを相違させることができる(ここで、切り替え可能タイミングとは、フレームデータに応じた操作信号の更新タイミングのことであり、必ずしもスイッチング状態が切り替えられるタイミングとはならない)。

【0104】

このように、スイッチング状態の切り替え可能タイミングを互いに相違させることで、サージ電圧を低減することができる。

<第4の実施形態>

以下、第4の実施形態について、先の第3の実施形態との相違点を中心に図面を参照しつつ説明する。

【0105】

本実施形態では、先の図10に示した受信ユニット30a,30b,30cを同一構成とする。

【0106】

図13に、本実施形態にかかるフレームデータの伝送態様を示す。図示されるように、本実施形態では、1フレームにおいてインバータINVa,INVbの双方の操作信号とコンバータCNVの操作信号とを含みつつも、それらの更新周期を3フレームとして、順次更新する。図では、インバータINVaの操作信号g¥#が更新(サンプリング番号n)された次のフレームで、インバータINVbの操作信号g¥#が更新され、その次のフレームでコンバータCNVの操作信号gcp、gcnが更新される例を示している。

【0107】

こうした設定によっても、コンバータCNVとインバータINVaとインバータINVbとで、スイッチング状態の切り替え可能タイミングを相違させることができる。

<第5の実施形態>

以下、第5の実施形態について、先の第3の実施形態との相違点を中心に図面を参照しつつ説明する。

【0108】

本実施形態では、先の図10に示した受信ユニット30a,30b,30cを同一構成とする。

【0109】

図14に、本実施形態にかかるフレームデータの伝送態様を示す。図示されるように、本実施形態では、1フレームにおいて、インバータINVaとインバータINVbとコンバータCNVとのいずれか1つの操作信号を含め、且ついずれの操作信号かを指定する信号を含める。そして、3フレームに1度ずつインバータINVaとインバータINVbとコンバータCNVとのそれぞれの操作信号を伝送する。

【0110】

こうした設定によっても、コンバータCNVとインバータINVaとインバータINVbとで、スイッチング状態の切り替え可能タイミングを相違させることができる。

<第6の実施形態>

以下、第6の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0111】

図15に、本実施形態にかかるスイッチングモードの更新可能タイミングを示す。図中、時刻t1,t2,t3,t4が更新可能タイミングである。ここで、更新可能タイミングとは、スイッチングモードを変更することが可能なタイミングを意味し、必ずしも変更がなされるタイミングを意味しない。

【0112】

図示されるように、本実施形態では、更新可能タイミング間の周期を、1フレーム(ここでは、1フレームを10ビットとする例を想定しているため、単位期間T0の10倍の期間)とする。これは、スイッチングモードの変更タイミングの遅延ばらつきを低減するための設定である。すなわち、モデル予測制御では、更新可能タイミングにおいてスイッチングモードを更新した場合の制御性を予測評価することで、実際のスイッチングモードを決定する。このため、スイッチングモードの実際の更新タイミングがばらつく場合には、モデル予測制御の制御性が低下する懸念が生じる。ここで、上記設定によれば、スイッチングモードの決定から実際にスイッチングモードが変更されるまでの遅延時間を略固定することができるため、遅延時間のばらつきを好適に低減することができる。

【0113】

これに対し、スイッチングモードの更新可能周期の整数分の1が1フレームとならない場合には、マイクロプロセッサユニット50の規定するスイッチングモードの更新可能タイミングに対する実際の更新タイミングの遅延時間がばらつくこととなる。

<第7の実施形態>

以下、第7の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0114】

本実施形態では、モータジェネレータ10を流れる電流を指令値にフィードバック制御するための操作量としての指令電圧がインバータINVの出力電圧となるように、3角波比較PWM処理によって操作信号を生成する周知の電流フィードバック制御を行なう。

【0115】

図16に、本実施形態にかかるシステム構成を示す。なお、図16において、先の図1に示した部材に対応するものについては、便宜上同一の符号を付している。

【0116】

図中、マイクロプロセッサユニット50の内部には、周知の電流フィードバック制御の概要のブロック図を記載してある。すなわち、指令電圧vd*,vq*は、モータジェネレータ10を流れるd軸電流idおよびq軸電流iqのそれぞれを指令電流id*,iq*のそれぞれにフィードバック制御するための操作量であり、3相の指令電圧vu*,vv*,vw*は、指令電圧vd*,vq*を3相変換したものである。そして、3相の指令電圧v¥*(¥=u,v,w)をインバータINVの入力電圧で規格化したDuty信号D¥と三角波形状のキャリア信号Scとの大小比較に基づき、PWM信号g¥を生成する。このPWM信号g¥の立ち上がりエッジをデッドタイムだけ遅延させた信号が上側アームの操作信号g¥pであり、PWM信号g¥の論理反転信号の立ち上がりエッジをデッドタイムだけ遅延させた信号が下側アームの操作信号g¥nである。

【0117】

この場合、基本的に、操作信号g¥#の指令が変化するタイミングは、キャリア信号Scの変化の分解能に依存するものの、略任意のタイミングとなり得る。たとえば、キャリア信号Scの周期を「50μs」とし、キャリア信号Scの変化を「10MHz」のクロックで生成する場合、操作信号g¥#の切り替わり自体は、「50μs」に1度であるものの、そのタイミングは、「0.1μs」の時間分解能を有する。

【0118】

ここで、上記時間分解能に対応する時間間隔よりも長い周期毎にフレームを出力したのでは、マイクロプロセッサユニット50によって規定される操作信号g¥#の変化タイミングに対するドライブユニットDU側での操作信号g¥#の変化タイミングの遅延時間が大きくばらつくこととなる。そして、これは指令電圧v¥#の制御性の低下をもたらし、ひいてはインバータINVの出力線間電圧の基本波成分の制御性の低下をもたらす。

【0119】

これに対し、上記時間分解能に対応する時間間隔でフレームを出力することは、伝送レートを極めて大きくする必要があり、伝送装置の高速性能に対する要求が過大となるおそれがある。

【0120】

そこで本実施形態では、フレームの出力タイミングを操作信号g¥#の変化に同期させる。

【0121】

図17に、本実施形態にかかる1次側コイルw1への電圧印加処理の手順を示す。この処理は、送信ユニット40によって実行される。

【0122】

この一連の処理では、まずステップS10において、操作信号g¥#の中に、オン操作指令からオフ操作指令に変化したものや、オフ操作指令からオン操作指令に変化したものがあるか否かを判断する。

【0123】

ステップS10において肯定判断される場合、ステップS12において、フレームの出力中であるか否かを判断する。そして、フレームの出力中である場合には、フレームの出力終了まで待機する一方、フレームの出力中でない場合には、ステップS14に移行する。ステップS14においては、操作信号g¥#の符号化処理を行なう。そして、ステップS16においては、符号化処理された操作信号g¥#を含むフレームを出力する。なお、ステップS14、S16の処理は、本実施形態において、同期手段を構成する。

【0124】

一方、ステップS10において否定判断される場合、ステップS17において、フレームの出力中であるか否かを判断する。そして、フレームの出力中である場合には、フレームの出力終了まで待機する一方、フレームの出力中でない場合には、ステップS18において、マンチェスタ符号における「0」を継続して出力する。ここで、フレーム出力停止時であっても1次側コイルw1に電圧を印加するのは、ドライブユニットDUに対する給電のためである。また、「0」を出力するのは、ドライブユニットDUの給電のための電圧印加処理に起因してトランスTの磁気飽和が生じる事態を回避するためである。ちなみに、「0」は、先の図4に示す同期信号の冒頭の符号である「0」と同一であるため、フレームの出力への切り替え時には、「1」からはじめればよく、フレームの出力を迅速に行なうことが可能となるというメリットもある。

【0125】

なお、上記ステップS16、S18の処理が完了する場合には、この一連の処理を一旦終了する。

【0126】

図18に、本実施形態の効果を示す。なお、図では、ドライブユニットDU側での操作信号g¥#の変化を、スイッチング素子S¥#の状態変化として模式的に示している。

【0127】

図示されるように、U相上側アームの操作信号gupのオン操作指令への切り替わりタイミングから、ドライブユニットDU側での操作信号gupのオン操作指令への切り替わりタイミング(スイッチング素子Supのオン状態への切り替え開始タイミング)までには遅延が生じる。ただし、この遅延時間は、V相上側アームの操作信号gvpのオン操作指令への切り替わりタイミングから、ドライブユニットDU側での操作信号gvpのオン操作指令への切り替わりタイミング(スイッチング素子Svpのオン状態への切り替え開始タイミング)までの遅延時間と略等しい。このため、操作信号gupのオン操作指令への切り替わりタイミングから操作信号gvpのオン操作指令への切り替わりタイミングまでの時間間隔T1と、スイッチング素子Supのオン状態への切り替わり開始タイミングからスイッチング素子Svpのオン状態への切り替わり開始タイミングまでの時間間隔T2とは略等しい。このため、インバータINVの出力線間電圧の基本波成分を、指令電圧vu*,vv*,vw*によって定まるものに好適に制御することができる。

<第8の実施形態>

以下、第8の実施形態について、先の第2の実施形態との相違点を中心に図面を参照しつつ説明する。

【0128】

図19に、本実施形態にかかる1次側コイルw1への電圧印加処理の手順を示す。この処理は、送信ユニット40によって実行される。なお、図19に示す処理において、先の図17に示した処理に対応するものについては、便宜上、同一のステップ番号を付している。

【0129】

図示されるように、本実施形態では、ステップS17において否定判断される場合、ステップS20において、フレーム出力後所定時間が経過したか否かを判断する。この処理は、操作信号g¥#についての情報が前回のものと同一である情報を有するフレームを再送するか否かを判断するためのものである。これは、フレームの伝送に際してエラーが生じた場合に、エラーからの復帰を早期に行なうためのものである。

【0130】

特に、本実施形態では、先の図9に示したウォッチドッグタイマ96において、規定時間に渡ってイネーブル信号およびクロック信号CLKが入力されない場合、対応するスイッチング素子S¥#がオフ操作されるため、ステップS10において肯定判断されることで出力されたフレームの伝送にエラーが生じる場合には、インバータINVが停止制御されるおそれがある。このため、上記所定時間を、ウォッチドッグタイマ96における上記規定時間未満に設定することで、インバータINVの停止制御がなされる事態が生じることを極力回避する。なお、この規定時間は、上記第2の実施形態のように3フレーム分の長さとする代わりに、それよりも長い時間としてもよい。ちなみに、ステップS20、S14,S16の処理は、本実施形態において、再送手段を構成する。

<第9の実施形態>

以下、第9の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0131】

本実施形態では、インバータINVの出力電圧を指令電圧v¥*とするための処理として、三角波比較PWM処理に代えて、空間ベクトル変調処理を採用する。ここで空間ベクトル変調処理は、所定時間におけるインバータINVの出力電圧の平均値を指令電圧v¥*とするための処理の1つであるが、所定時間において採用されるスイッチングモードの順序や時間が三角波PWM処理による制約を受けないものである。すなわち所定時間において採用される各スイッチングモードに対応する電圧ベクトルの平均値が指令電圧v¥*となるとの条件で、スイッチングモードの選択やその採用時間の自由度を向上させることができるものである。

【0132】

この場合、スイッチング状態の切り替えのなされるモータジェネレータ10の端子数が複数となるおそれがある。そこで本実施形態では、図20に記載する処理を行なう。

【0133】

図20は、本実施形態にかかる1次側コイルw1への電圧印加処理の手順を示す。この処理は、送信ユニット40によって実行される。なお、図20に示す処理において、先の図17に示した処理に対応するものについては、便宜上、同一のステップ番号を付している。

【0134】

図示されるように、本実施形態では、ステップS10において肯定判断される場合、ステップS22において、操作信号g¥#のうち、指令が変化する信号が複数あることを条件に、それらの変化の情報を同時に出力するか、一部の出力を遅延するかを選択する。この選択は、マイクロプロセッサユニット50の記憶手段に、同時のスイッチング状態の切り替えを許容するスイッチングパターンと許容しないスイッチングパターンとを記憶しておき、これらスイッチングパターンと操作信号g¥#の変化前後のパターンとの照合に基づき行われる。以下、記憶手段に記憶されるスイッチングパターンの概念について、図21に基づき説明する。

【0135】

図21は、スイッチング素子Supのオフ状態への切り替え指令と、スイッチング素子Svpのオン状態への切り替え指令とを同時に伝送することを許容して(図21(A))且つ、スイッチング素子Supのオフ状態への切り替え指令と、スイッチング素子Swpのオン状態への切り替え指令とについて、それらの同時伝送を禁止する(図21(B))例を示す。

【0136】

これは、図21(A)に示すケースの方が、図21(B)に示すケースと比較して、スイッチング状態の切り替えに起因してサージ電圧が小さくなると想定されることに基づくものである。すなわち、スイッチング素子Supがオフ状態となると同時にスイッチング素子Svpがオン状態となる場合、正極側直流母線Lpにおいて電流量が変化する領域は、U相およびV相間である。これに対し、スイッチング素子Supがオフ状態となると同時にスイッチング素子Swpがオン状態となる場合、正極側直流母線Lpにおいて電流量が変化する領域は、U相およびW相間である。図からわかるように、U相およびV相間で電流量が変化する場合と比較して、U相およびW相間で電流量が変化する場合の方が、電流量が変化する電気経路が長い。このため、電流量が変化する部分の寄生インダクタも大きくなり、ひいてはサージが大きくなると想定される。

【0137】

なお、先の図20のステップS22の処理は、本実施形態において、延期手段を構成する。

<第10の実施形態>

以下、第10の実施形態について、先の第8の実施形態との相違点を中心に図面を参照しつつ説明する。

【0138】

本実施形態では、フレームの出力停止期間において、互いに極性の相違する電圧値(以下、H電圧、L電圧)のいずれか一方を選択的に印加する。ここで、H電圧は、バイフェーズ符号の論理「0」を構成する後半部分の電圧値であり、L電圧は、バイフェーズ符号の論理「0」を構成する前半部分の電圧値である。

【0139】

図22に、本実施形態にかかるフレーム出力停止期間における電圧印加処理の手順を示す。この処理は、送信ユニット40によって実行される。

【0140】

この一連の処理では、まずステップS30において、フレーム出力が完了した直後であるか否かを判断する。そして、ステップS30において肯定判断される場合、ステップS32において、積分値Inが上限側閾値InthH以上であるか否かを判断する。ここで、積分値Inは、トランスTの磁束と正の相関を有するパラメータである。詳しくは、後述する処理によって1次側コイルw1の印加電圧の時間積分値とされるものである。なお、上限側閾値InthHは、トランスTが磁気飽和しない上限値に基づき設定される。ステップS32において肯定判断される場合、ステップS34において、コイルw1にL電圧を印加する。なお、ステップS32、S34の処理は、本実施形態において、所定電圧印加手段および反転手段を構成する。

【0141】

一方、ステップS32において否定判断される場合、ステップS36において、積分値Inが下限側閾値InthL以下であるか否かを判断する。ここで、下限側閾値InthLは、トランスTが磁気飽和しない上限値に基づき設定される。そして、ステップS36において肯定判断される場合、ステップS38において、コイルw1にH電圧を印加する。なお、ステップS36、S38の処理は、本実施形態において、所定電圧印加手段および反転手段を構成する。

【0142】

これに対し、ステップS30において否定判断される場合や、ステップS36において否定判断される場合には、ステップS40に移行する。ステップS40においては、積分値Inを更新する。ここでは、ステップS34の処理がなされた後、ステップS30またはステップS36において否定判断されている場合には、積分値Inをデクリメントする。また、ステップS38の処理がなされた後、ステップS30またはステップS36において否定判断されている場合には、積分値Inをインクリメントする。ただし、フレームの転送中においては、積分値Inの更新をしない。これは、フレームの転送時において1次側コイルw1に印加される電圧の平均値がゼロとなることによる。なお、ステップS40の処理は、本実施形態において、磁束算出手段を構成する。

【0143】

なお、ステップS34,S38,S40の処理が完了する場合には、この一連の処理を一旦終了する。

<第11の実施形態>

以下、第11の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0144】

本実施形態は、燃料電池の状態監視装置に対する信号および電力の伝送装置である。

【0145】

図23に、本実施形態にかかるシステム構成を示す。

【0146】

図示される組電池110は、車載主機としてのモータジェネレータ(図示略)に対する電力供給源であり、その端子電圧がたとえば100V以上となるものである。組電池110は、燃料電池によって構成される電池セルCij(i=1〜m、j=1〜n)の直列接続体である。電池セルCijは、全て同一仕様であり、個体差や経年変化を除き端子電圧が等しくなるものである。電池セルCijは、隣接するn個ずつでグループ化され、ブロックBiを構成している。各ブロックBiの状態は、監視ユニットUiによって監視される。

【0147】

上記組電池110の負極電位は、車体電位と相違するように設定されている。監視ユニットUiは、マイクロプロセッサユニット50からの指令に基づき、ブロックBi内の電池セルCi1〜Cinの電圧異常の有無を診断し、診断結果信号DSiをフォトカプラ112を介してマイクロプロセッサユニット50に出力する。

【0148】

ここで、マイクロプロセッサユニット50は、監視指令信号を送信ユニット40に出力する。送信ユニット40では、監視指令信号をデジタルベースバンド符号化処理し、パルス符号化された電圧信号を1次側コイルW1に印加する。これにより、1次側コイルW1に磁気結合されて且つ監視ユニットUiのそれぞれに接続された2次側コイルW2にパルス電圧が誘起される。監視ユニットUiは、2次側コイルW2に接続された受信ユニット30を備え、ここで、2次側コイルW2に誘起される電圧信号を復号処理し、監視指令信号を取り出すとともに、2次側コイルW2に誘起される電圧によって流れる電流を整流することで電力を取り出す。

【0149】

このように、本実施形態では、各監視ユニットUiに対する監視指令信号の送信や監視ユニットUiに対する電力の送信を単一のトランスTを用いて行なうことができる。特に、監視ユニットUiは、ブロックBiを電源とする必要がないため、電池セルC11の発電停止時においても動作可能となる。

<その他の実施形態>

なお、上記各実施形態は、以下のように変更して実施してもよい。

【0150】

「パルス符号化について」

2値のそれぞれを示すパルスの論理「H」期間と論理「L」期間とが等しい(時比率が50%)である符号としては、マンチェスタ符号に限らず、たとえば差分マンチェスタ符号であってもよい。もっとも、バイフェーズ符号としては、2値のそれぞれを示すパルスの論理「H」期間と論理「L」期間とが等しい(時比率が50%である符号)にも限らず、バイフェーズNRZ符号や、CMI等であってもよい。また、パルス符号としては、2値的なものに限らず、たとえばAMI符号等であってもよい。そのほか、8b10b符号や、6b8b符号、PR4符号等であってもよい。

【0151】

「符号化手段について」

上記実施形態では、操作信号g¥#を生成するソフトウェア処理手段(マイクロプロセッサユニット50)とは別に専用のハードウェア手段(エンコーダ41)によって構成したが、これに限らず、ソフトウェア処理手段によって構成してもよい。

【0152】

「電圧印加手段について」

フルブリッジ回路46を備えるものに限らず、たとえば図24(a)に示すように、プッシュプル回路を備えて構成してもよく、また、図24(b)に示すように、1次側コイルW1と電源との間のループ経路を単一のスイッチング素子にて開閉するものであってもよい。

【0153】

「復号手段について」

たとえば上記第1の実施形態(図1)や第2の実施形態(図9)において、下側アームのドライブユニットDUのそれぞれに受信ユニット30を搭載してもよい。この場合、これらに接続される2次側コイル同士を各別の部材とすることで、インバータINVの負極側の直流母線における電圧降下に起因した下側アームの各ドライブユニットDUのグランド電位の変動の影響を受けることなく、スイッチング素子S¥nを駆動することができる。

【0154】

上記第4の実施形態(図13)や第5の実施形態(図14)において、下側アームのドライブユニットDUについては、いずれか1つのみに受信ユニット30を搭載するようにしてもよい。

【0155】

「同期信号について」

上記のものに限らない。特に、上下アームの双方がオンとなり得る構成の場合、同期信号の設定変更が特に重要である。こうした構成とは、たとえば、米国特許第7130205号明細書や特開2009−141989号公報に記載されているように、インバータとバッテリとの間にインピーダンスネットワークを接続し、上下アームをオン操作(シュートスルー)することでインバータの入力電圧を昇圧する構成の場合等である。この場合、たとえば、デッドタイム期間を受信ユニット30側で生成する設定とし、上下アームの双方がオフとなることがないように操作信号g¥p,g¥nを定めることで、オフに対応する符号が3つ以上連続するように同期信号を生成してもよい。もっとも、オン指令およびオフ指令を表現する2値の論理値のいずれをも表現しないパルスとして同期信号を符号化してもよい。

【0156】

なお、伝送対象となる対象信号として、同期信号を含むものに限らない。これを含まない場合であっても、たとえばクロック用のトランスを別途備え、クロック用のトランスによってフレームの先頭を指示する信号を伝送するようにするなら、復号処理を容易に実行することができる。

【0157】

「情報信号について」

上記第1の実施形態(図1)等において、符号化対象とする情報信号を、スイッチングモードを表現する操作信号のみとして且つ、受信ユニット30においてデッドタイム生成機能を搭載するようにしてもよい。

【0158】

「実行手段について」

上記第2の実施形態(図9)では、正常データが連続3周期以上受信できない場合にスイッチング素子S¥#を強制的にオフ状態としたが、これに限らず、たとえば連続2周期以上、または1周期受信できない場合であってもよい。また、スイッチング素子S¥#を強制的にオフ状態とするものに限らず、正常であったときのスイッチングを維持して且つ、異常がある旨を外部(マイクロプロセッサユニット50等)に通知するものであってもよい。

【0159】

「監視手段について」

スイッチング素子S¥#を流れる電流が過度に大きいか否かを判断する手段に限らない。たとえば、スイッチング素子S¥#の温度を監視する手段や、スイッチング素子S¥#の温度情報を外部に出力する手段等であってもよい。

【0160】

「整流回路について」

フルブリッジ方式の整流回路62に限らず、周知の整流回路を適宜利用してよい。

【0161】

「変換手段について」

たとえば、2次側コイルW2n,W2u,W2v,W2wに中点タップを備え、2次側コイルW2n,W2u,W2v,W2wの中点タップと一方の端部との間の電圧をデコーダ74の入力とするなら、出力側電圧信号の変動量を縮小変換する変換手段を備えなくてもよい。また、たとえば要求される電源の電圧が低い場合や、整流回路62の出力側に昇圧回路を備える場合等にあっても、変換手段を備えない構成としてもよい。

【0162】

「整流回路および復号手段の接続について」

並列接続に限らず、たとえば復号手段の出力側に整流回路を直列接続してもよい。また、これ以外の接続手法としては、「変換手段について」の欄に記載した手法もある。

【0163】

「フィルタ回路について」

2次遅れ回路に限らず、たとえば1次遅れ回路であってもよい。

【0164】

「スイッチングモードを所定周期で更新する制御について」

モデル予測制御に限らず、DTC(Direct Torque Control)等であってもよい。

【0165】

「符号化処理タイミングについて」

上記第6の実施形態(図15)では、スイッチングモードの更新可能周期をフレーム周期としたが、これに限らず、更新可能周期の整数分の1の周期をフレーム周期としてもよい。

【0166】

もっとも、モデル予測制御等の場合であっても、フレームを所定周期で出力することは必須ではない。たとえば上記第7の実施形態(図18)の要領で、スイッチングモードの変更タイミングに同期してフレームを出力するものであってもよい。なお、この場合、実際には、スイッチングモードの変更に伴って、2度、フレームを出力することとなる。これは、スイッチングモードの変更に伴って、上下アームのスイッチング状態がデッドタイムDTだけ離間して変更されるためである。

【0167】

「再送手段(ステップS20)について」

上記第1の実施形態(図3)のように、ウォッチドッグタイマ96を備えない構成の場合、所定時間を、たとえば上下アームのスイッチング素子S¥p,S¥nが双方オンとなる短絡状態の許容上限時間未満に設定することが望ましい。

【0168】

「指令変化検出手段(S10)について」

上記実施形態では、操作信号g¥#を入力してその変化を検出する専用のハードウェア処理手段としたが、これに限らない。たとえば、前回のサンプリング周期と今回のサンプリング周期とで操作信号g¥#に指令が相違するものの有無を判断するソフトウェア処理手段としてもよい。ただし、ここでのサンプリング周期は、1フレームよりも短い時間間隔とすることが望ましい。

【0169】

「同期手段(S12〜S16)について」

ハードウェア処理手段に限らないことについては、「指令変化検出手段」と同様である。

【0170】

「延期手段(S22)について」

上記第9の実施形態(図20、図21)では、同時のスイッチングを許可するパターンと禁止するパターンとの双方を記憶手段に記憶したが、いずれか一方であってもよい。

【0171】

上記第9の実施形態(図20、図21)では、同時のスイッチングを許可する旨が記憶手段に記憶されたスイッチングパターンについては、同時のスイッチングを許可するようにしたがこれに限らない。たとえば、スイッチング状態の切り替えを伴うモータジェネレータ10の端子数を固定値として一律制限してもよい。

【0172】

「所定電圧印加手段(S36,S40)について」

パルス符号化された信号を構成する電圧値の電圧を1次側コイルw1に印加する手段に限らず、これとは別の電圧値の電圧を印加する手段であってもよい。このほか、たとえば「磁束算出手段(S38,S42,S44)について」の欄に記載したものであってもよい。

【0173】

「磁束算出手段(S38,S42,S44)について」

上記第10の実施形態(図22)において例示したように、同一の極性を有する電圧の印加時間によって、磁束量を定量化するものに限らない。たとえば、所定電圧印加手段が印加電圧の極性が同一であって且つその絶対値を変化させるものである場合、電圧の積分値によって磁束量を定量化することが望ましい。

【0174】

またたとえば、トランスTの磁束のゼロ点を検出する手段を備え、ゼロ点の検出タイミングから所定時間経過することで、印加電圧の極性を反転させるものであってもよい。ここで、ゼロ点検出手段としては、たとえば、2次側コイルw2u,w2v,w2w,w2nに誘起される電流の極性の変化や、整流回路62のうちオンとなるダイオードの切り替わりを検出する手段として構成することができる。

【0175】

「反転手段(S32〜S40)について」

上記第10の実施形態(図22)では、フレームの出力直後を、印加電圧の極性の変更を許可するタイミングとしたが、これに限らず、所定電圧印加手段による電圧の印加時間が長くなる場合に極性を反転させてもよい。

【0176】

「同期手段によるフレーム出力がなされない期間について」

上記第7の実施形態(図18)等では、フレーム出力がなされない期間において、「0」に対応する電圧信号を印加したが、これに限らず、「1」に対応する電圧信号を印加してもよい。

【0177】

フレーム出力がなされない期間において、フレームとは相違する電圧信号を1次側コイルw1に印加するものに限らない。たとえば上記第8の実施形態(図19)に例示されるようにフレームの出力がなされない時間が制限される場合等にあっては、1次側コイルw1への電圧の印加自体を停止したとしてもドライブユニットDUへの電力供給停止期間が過度に長くならないため、1次側コイルw1への電圧の印加自体を停止することも可能ではある。

【0178】

「対象信号について」

電力変換回路を構成するスイッチング素子の操作信号や、燃料電池の監視指令信号に限らない。ただし、対象信号の入力側(伝送先)として電源を備えないものにおいて、指令に応じて所定の処理を実行するものに対する指令信号であることが望ましい。

【0179】

もっとも、これは、電源を備えうるシステムへの出力信号を対象信号とすることが有効でないことを意味しない。たとえば、上記第11の実施形態(図23)において、電池セルCijをリチウムイオン2次電池やニッケル水素2次電池等の2次電池とする場合、監視ユニットUiが電池セルCi1〜Cinを電源とすることも可能ではある。ただし、この場合、監視ユニットUiの個体差等に起因して監視ユニットU1〜Umの消費電力にばらつきが生じる場合、電池セルCi1〜Cinの消費電力がばらつき、ひいては充電率や端子電圧にばらつきが生じやすくなる。これに対し、上記第11の実施形態と同様の構成を採用することで、こうした問題を回避することができる。

【0180】

「2次側コイルについて」

たとえば高電圧システムの基準電位(高電圧バッテリ12の負極電位)と低電圧システムの基準電位(車体電位)とが同一であるなら、上記第1の実施形態(図1)等において、1次側コイルW1と下側アーム用の2次側コイルW2nとを接続してもよい。もっとも、下側アームのスイッチング素子の駆動に際してインバータINVの直流母線における電圧降下によって影響を受けないようにするためには、これらを接続しないことが望ましい。

【0181】

なお、対象信号の伝送先の構成によっては、2次側コイルが1つとなってもよい。

【0182】

「スイッチング状態の切り替え可能タイミングを相違させる部類分けについて」

・上記第5の実施形態(図10)等において、コンバータCNVと、インバータINVa,INVbとのスイッチング状態の切り替えタイミングを相違させて且つ、インバータINVa,INVb同士のスイッチング状態の切り替えタイミングの一致を許可する設定としてもよい。

【0183】

またたとえば、インバータINVの各相(レッグ)を1つの部類として、それら部類同士でスイッチング状態の切り替え可能タイミングを相違させてもよい。これは、上記第3〜第5の実施形態の手法によって行なうことができる。なお、この場合、各レッグを構成する高電位側のスイッチング素子S¥pと低電位側のスイッチング素子S¥nが1つずつであるなら、それら一対のスイッチング素子S¥p,S¥nのみが同一の部類の構成要素となる。

【0184】

さらに、部類分けの適用対象としては、高電位側のスイッチング素子と低電位側のスイッチング素子とからなる一対のスイッチング素子を構成要素とするものに限らず、また、スイッチング状態の切り替え可能タイミングを部類毎で相違させる目的はサージ低減に限らない。たとえば、低電位側のスイッチング素子と高電位側のダイオードとの直列接続体を備える周知の昇圧チョッパ回路を複数並列駆動する場合に、マルチフェーズ処理を行なうべくスイッチング状態の切り替えタイミングをずらしてもよい。

【0185】

「そのほか」

インバータの各相を構成する高電位側のスイッチング素子S¥pと低電位側のスイッチング素子S¥#とを複数並列接続してもよい。この場合、高電位側のスイッチング素子S¥pのうちこれら同一相のものでは受信ユニット30を共有できる。

【符号の説明】

【0186】

10…モータジェネレータ、30…受信ユニット、40…送信ユニット、41…エンコーダ、43…シフトレジスタ、72…データスライサ(変換手段の一実施形態)、74…デコーダ、W1…1次側コイル、W2n,W2u,Swv,W2w…2次側コイル。

【特許請求の範囲】

【請求項1】

互いに磁気結合した1次側コイル(W1)および2次側コイル(W2n,W2u,W2v,W2w)と、

伝送対象となる対象信号をパルス符号化する符号化手段(41)と、

前記符号化手段の出力に応じた電圧信号である入力側電圧信号を前記1次側コイルに印加する電圧印加手段(46)と、

前記入力側電圧信号によって前記2次側コイルに誘起される電圧信号である出力側電圧信号の変化に基づき、前記出力側電圧信号を復号する復号手段(74)と、

前記入力側電圧信号によって前記2次側コイルに誘起される電圧信号に応じて前記2次側コイルに接続される電気経路に流れる電流を整流する整流回路(62)と、

を備えることを特徴とする信号および電力の伝送装置。

【請求項2】

前記復号手段は、第1出力経路を介して前記2次側コイルに接続され、

前記整流回路は、前記第1出力経路とは相違する第2出力経路を介して前記2次側コイルに接続されていることを特徴とする請求項1記載の信号および電力の伝送装置。

【請求項3】

前記対象信号は、情報信号と、該情報信号の更新の都度、該情報信号に先立って情報信号が伝送される旨を示す同期信号とを含むことを特徴とする請求項1または2記載の信号および電力の伝送装置。

【請求項4】

前記符号化手段による符号化処理は、前記入力側電圧信号が前記1次側コイルに印加されることによる前記1次側コイルおよび前記2次側コイルの鎖交磁束についての前記同期信号と前記情報信号との1周期に対応する期間にわたる変化量をゼロとするものであることを特徴とする請求項3記載の信号および電力の伝送装置。

【請求項5】

前記パルス符号は、バイフェーズ符号であることを特徴とする請求項1〜4のいずれか1項に記載の信号および電力の伝送装置。

【請求項6】

前記復号手段は、前記出力側電圧信号に基づきクロック信号を生成するクロック生成手段を備えることを特徴とする請求項1〜5のいずれか1項に記載の信号および電力の伝送装置。

【請求項7】

前記整流回路には、前記整流回路の出力電流を平滑化するフィルタ回路(64)が接続されており、

前記フィルタ回路の時定数は、前記出力側電圧信号の電圧値が一定となる最長時間よりも長く設定されていることを特徴とする請求項1〜6のいずれか1項に記載の信号および電力の伝送装置。

【請求項8】

前記2次側コイルは、互いに電位の相違しうる部材のそれぞれに接続される複数のコイルからなり、

前記復号手段は、前記複数のコイルのそれぞれ毎に備えられることを特徴とする請求項1〜7のいずれか1項に記載の信号および電力の伝送装置。

【請求項9】

前記2次側コイルは、直列接続された一対のスイッチング素子である高電位側のスイッチング素子(Sup,Svp,Swp)および低電位側のスイッチング素子(Sun,Svn,Swn)のそれぞれを駆動対象とする各別の駆動回路のそれぞれに接続されるコイルを含み、

前記対象信号は、前記スイッチング素子のオン・オフの指令信号を含むことを特徴とする請求項8記載の信号および電力の伝送装置。

【請求項10】

前記2次側コイルに接続される駆動回路は、直列接続された一対のスイッチング素子の複数組のそれぞれの高電位側のスイッチング素子を駆動対象とする各別の駆動回路を備え、

前記対象信号は、前記複数組の一対のスイッチング素子のそれぞれのオン・オフの指令信号と、該指令信号の更新の都度、該指令信号に先立って指令信号が伝送される旨を示す同期信号とを含み、

前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、前記高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない信号であり、

前記復号手段は、前記直列接続された一対のスイッチング素子のオン・オフの指令信号が、双方ともオン指令であることを異常として検出する異常検出手段(86,88,90)を備え、

該異常検出手段によって異常が検出されることに基づき、該異常に対処する異常対処処理を実行する実行手段(96)をさらに備えることを特徴とする請求項9記載の信号および電力の伝送装置。

【請求項11】

前記2次側コイルに接続される駆動回路は、直列接続された一対のスイッチング素子の複数組のそれぞれの高電位側のスイッチング素子を駆動対象とする各別の駆動回路を備え、

前記対象信号は、前記複数組の一対のスイッチング素子のそれぞれのオン・オフの指令信号と、該指令信号の更新の都度、該指令信号に先立って指令信号が伝送される旨を示す同期信号とを含み、

前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、前記高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない信号であり、

前記同期信号は、前記オン指令に対応する信号と同一の信号が3つ以上連続する信号であることを特徴とする請求項9または10記載の信号および電力の伝送装置。

【請求項12】

前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、高電位側のスイッチング素子のオン指令および低電位側のスイッチング素子のオフ指令、高電位側のスイッチング素子のオフ指令および低電位側のスイッチング素子のオン指令、ならびに高電位側のスイッチング素子のオフ指令および低電位側のスイッチング素子のオフ指令の3つの指令パターンのいずれかであることを特徴とする請求項9〜11のいずれか1項に記載の信号および電力の伝送装置。

【請求項13】

前記直列接続された高電位側のスイッチング素子および低電位側のスイッチング素子は、交互にオン状態となるように相補駆動されるものであって且つ、それら高電位側のスイッチング素子および低電位側のスイッチング素子のいずれか一方および他方のそれぞれがオン、オフとなる状態からオフ、オンとなる状態に移行するに先立ち、前記指令信号が双方のオフ状態を指令することを特徴とする請求項12記載の信号および電力の伝送装置。

【請求項14】

前記駆動回路は、前記スイッチング素子の駆動状態を監視する監視手段(102)を備え、

前記監視手段は、前記整流回路に電気的に接続されていることを特徴とする請求項9〜13のいずれか1項に記載の信号および電力の伝送装置。

【請求項15】

前記複数のコイルには、複数のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれが接続され、

前記対象信号は、前記複数のスイッチング素子のそれぞれのオン・オフの指令信号を含み、

前記複数のスイッチング素子のうち互いに相違する部類に属するスイッチング素子のそれぞれに対応する前記駆動回路同士で前記オン・オフ指令の入力から駆動対象とするスイッチング素子が操作されるまでの遅延時間を相違させる設定がなされていることを特徴とする請求項8〜14のいずれか1項に記載の信号および電力の伝送装置。

【請求項16】

前記複数のコイルには、複数のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれが接続され、

前記対象信号は、前記複数のスイッチング素子のそれぞれのオン・オフの指令信号を含み、

前記対象信号は、前記1次側コイルおよび前記2次側コイルを介して周期的に伝送されるものであり、周期的な伝送の1周期の間に前記複数のスイッチング素子の全てのオン・オフを指令する信号が含まれて且つ、前記複数のスイッチング素子のうちの互いに相違する部類に属するスイッチング素子のそれぞれで互いに相違する周期で前記オン・オフを指令する信号が更新されることを特徴とする請求項8〜14のいずれか1項に記載の信号および電力の伝送装置。

【請求項17】

前記複数のコイルには、複数のスイッチング素子のそれぞれを駆動対象とする各別の駆動回路のそれぞれが接続され、

前記対象信号は、前記複数のスイッチング素子のそれぞれのオン・オフの指令信号を含み、

前記対象信号は、前記1次側コイルおよび前記2次側コイルを介して周期的に伝送されるものであり、周期的な伝送の1周期の間に前記複数のスイッチング素子のうちの互いに相違する部類のいずれかに属するスイッチング素子のオン・オフを指令する信号に加えて、該いずれかを指定する信号が伝送されることを特徴とする請求項8〜14のいずれか1項に記載の信号および電力の伝送装置。

【請求項18】

前記複数のスイッチング素子は、互いに相違する回転機に接続されて且つ共通の直流電圧源に接続された複数の直流交流変換回路(INVa,INVb)を構成するものであって且つ、互いに相違する直流交流変換回路を構成するもの同士が互いに相違する部類とされるものであることを特徴とする請求項15〜17のいずれか1項に記載の信号および電力の伝送装置。

【請求項19】

前記1次側コイルと前記2次側コイルとは互いに絶縁されていることを特徴とする請求項1〜18のいずれか1項に記載の信号および電力の伝送装置。

【請求項20】

前記出力側電圧信号の変動量を縮小変換して、前記復号手段に入力する変換手段(72)をさらに備えることを特徴とする請求項1〜19のいずれか1項に記載の信号および電力の伝送装置。

【請求項21】

前記スイッチング素子は、回転機に接続された直流交流変換回路を構成するものであり、

前記スイッチング素子のオン・オフの指令信号は、前記直流交流変換回路を構成するスイッチング素子のそれぞれがオンであるかオフであるかを表現するスイッチングモードが所定周期で更新可能なものであり、

前記符号化手段によるパルス符号化の周期を、前記所定周期の整数分の1に設定することを特徴とする請求項9〜14のいずれか1項に記載の信号および電力の伝送装置。

【請求項22】

前記2次側コイルは、スイッチング素子(Sup,Svp,Swp,Sun,Svn,Swn)を駆動対象とする駆動回路に接続されるコイルを含み、

前記対象信号は、前記スイッチング素子のオン・オフの指令信号を含み、

前記指令信号の変化を検出する指令変化検出手段(S10)と、

前記符号化手段によるパルス符号化処理および前記入力側電圧信号を前記1次側コイルに印加する処理を、前記指令信号の変化に同期させる同期手段(14,S16)と、

を備えることを特徴とする請求項1〜14のいずれか1項に記載の信号および電力の伝送装置。

【請求項23】

前記電圧印加手段は、前記指令変化検出手段によって前記指令信号の変化が検出されない期間が規定の長さを有する時間に達する場合、前記符号化手段の前回の出力に応じた前記入力側電圧信号を再送する再送手段(S20)を備えることを特徴とする請求項22記載の信号および電力の伝送装置。

【請求項24】

前記対象信号は、複数のスイッチング素子の指令信号を含み、

前記電圧印加手段によって前記パルス符号化された対象信号が前記2次側コイルに伝送されている期間において、前記指令変化検出手段が前記指令信号の変化を検出する場合、前記伝送されている期間の終了後、前記変化が検出された前記指令信号を含む前記対象信号を前記2次側コイルに伝送することを特徴とする請求項22または23記載の信号および電力の伝送装置。

【請求項25】

前記対象信号は、複数のスイッチング素子の指令信号を含み、

前記対象信号が、前記複数のスイッチング素子の指令信号の中に前回伝送されたものから変化するものを複数含む場合、前記電圧印加手段による前記1次側コイルへの電圧の印加による前記対象信号の今回の伝送に際し、前記変化する指令信号のうちの一部について変化前のものを再送することで、変化後の信号の伝送を延期する延期手段(S22)を備えることを特徴とする請求項22〜24のいずれか1項に記載の信号および電力の伝送装置。

【請求項26】

前記延期手段は、

前記変化する指令信号の同時の伝送を許可する条件および禁止する条件の少なくとも一方を記憶する記憶手段を備え、

前記許可する条件が成立する場合には、前記伝送の延期処理を行なわないことを特徴とする請求項25記載の信号および電力の伝送装置。

【請求項27】

前記電圧印加手段は、前記符号化手段によってパルス符号化された信号に対応する前記入力側電圧信号が前記1次側コイルに印加された後、前記対象信号が新たにパルス符号化されるまでの期間において、前記1次側コイルに、所定の条件で極性が反転する電圧を印加することを特徴とする請求項23〜26のいずれか1項に記載の信号および電力の伝送装置。

【請求項28】

前記パルス符号は、バイフェーズ符号であり、

前記所定の条件で極性が反転する電圧は、前記バイフェーズ符号のうちの特定の1つの符号に対応する電圧を前記1次側コイルに継続的に出力することによって生成されることを特徴とする請求項27記載の信号および電力の伝送装置。

【請求項29】

前記電圧印加手段は、

前記符号化手段によってパルス符号化された信号に対応する前記入力側電圧信号が前記1次側コイルに印加された後、前記対象信号が新たにパルス符号化されるまでの期間において、前記2次側コイルに所定の電圧を印加する所定電圧印加手段(S34,S38)と、

前記所定電圧印加手段による電圧の印加に伴う前記1次側コイルおよび前記2次側コイルの双方を貫く磁気経路の磁束量を算出する磁束算出手段(S40)と、

前記磁束算出手段による算出結果に基づき、前記所定電圧印加手段によって印加する電圧の極性を反転させる反転手段(S32,S36)と、

を備えることを特徴とする請求項27記載の信号および電力の伝送装置。

【請求項1】

互いに磁気結合した1次側コイル(W1)および2次側コイル(W2n,W2u,W2v,W2w)と、

伝送対象となる対象信号をパルス符号化する符号化手段(41)と、

前記符号化手段の出力に応じた電圧信号である入力側電圧信号を前記1次側コイルに印加する電圧印加手段(46)と、

前記入力側電圧信号によって前記2次側コイルに誘起される電圧信号である出力側電圧信号の変化に基づき、前記出力側電圧信号を復号する復号手段(74)と、

前記入力側電圧信号によって前記2次側コイルに誘起される電圧信号に応じて前記2次側コイルに接続される電気経路に流れる電流を整流する整流回路(62)と、

を備えることを特徴とする信号および電力の伝送装置。

【請求項2】

前記復号手段は、第1出力経路を介して前記2次側コイルに接続され、

前記整流回路は、前記第1出力経路とは相違する第2出力経路を介して前記2次側コイルに接続されていることを特徴とする請求項1記載の信号および電力の伝送装置。

【請求項3】

前記対象信号は、情報信号と、該情報信号の更新の都度、該情報信号に先立って情報信号が伝送される旨を示す同期信号とを含むことを特徴とする請求項1または2記載の信号および電力の伝送装置。

【請求項4】

前記符号化手段による符号化処理は、前記入力側電圧信号が前記1次側コイルに印加されることによる前記1次側コイルおよび前記2次側コイルの鎖交磁束についての前記同期信号と前記情報信号との1周期に対応する期間にわたる変化量をゼロとするものであることを特徴とする請求項3記載の信号および電力の伝送装置。

【請求項5】

前記パルス符号は、バイフェーズ符号であることを特徴とする請求項1〜4のいずれか1項に記載の信号および電力の伝送装置。

【請求項6】

前記復号手段は、前記出力側電圧信号に基づきクロック信号を生成するクロック生成手段を備えることを特徴とする請求項1〜5のいずれか1項に記載の信号および電力の伝送装置。

【請求項7】

前記整流回路には、前記整流回路の出力電流を平滑化するフィルタ回路(64)が接続されており、

前記フィルタ回路の時定数は、前記出力側電圧信号の電圧値が一定となる最長時間よりも長く設定されていることを特徴とする請求項1〜6のいずれか1項に記載の信号および電力の伝送装置。

【請求項8】

前記2次側コイルは、互いに電位の相違しうる部材のそれぞれに接続される複数のコイルからなり、

前記復号手段は、前記複数のコイルのそれぞれ毎に備えられることを特徴とする請求項1〜7のいずれか1項に記載の信号および電力の伝送装置。

【請求項9】

前記2次側コイルは、直列接続された一対のスイッチング素子である高電位側のスイッチング素子(Sup,Svp,Swp)および低電位側のスイッチング素子(Sun,Svn,Swn)のそれぞれを駆動対象とする各別の駆動回路のそれぞれに接続されるコイルを含み、

前記対象信号は、前記スイッチング素子のオン・オフの指令信号を含むことを特徴とする請求項8記載の信号および電力の伝送装置。

【請求項10】

前記2次側コイルに接続される駆動回路は、直列接続された一対のスイッチング素子の複数組のそれぞれの高電位側のスイッチング素子を駆動対象とする各別の駆動回路を備え、

前記対象信号は、前記複数組の一対のスイッチング素子のそれぞれのオン・オフの指令信号と、該指令信号の更新の都度、該指令信号に先立って指令信号が伝送される旨を示す同期信号とを含み、

前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、前記高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない信号であり、

前記復号手段は、前記直列接続された一対のスイッチング素子のオン・オフの指令信号が、双方ともオン指令であることを異常として検出する異常検出手段(86,88,90)を備え、

該異常検出手段によって異常が検出されることに基づき、該異常に対処する異常対処処理を実行する実行手段(96)をさらに備えることを特徴とする請求項9記載の信号および電力の伝送装置。

【請求項11】

前記2次側コイルに接続される駆動回路は、直列接続された一対のスイッチング素子の複数組のそれぞれの高電位側のスイッチング素子を駆動対象とする各別の駆動回路を備え、

前記対象信号は、前記複数組の一対のスイッチング素子のそれぞれのオン・オフの指令信号と、該指令信号の更新の都度、該指令信号に先立って指令信号が伝送される旨を示す同期信号とを含み、

前記直列接続された一対のスイッチング素子のオン・オフの指令信号は、前記高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン指令となることのない信号であり、

前記同期信号は、前記オン指令に対応する信号と同一の信号が3つ以上連続する信号であることを特徴とする請求項9または10記載の信号および電力の伝送装置。

【請求項12】