信号伝送回路

【課題】低コストかつ実装密度が高い回路基板を用いて、信号線間のクロストークノイズを低減するとともに、スタブによる反射ノイズを低減することのできる信号伝送回路を提供する。

【解決手段】本発明に係る信号伝送回路において、電子部品のリード端子と貫通ビアは表層配線で接続され、貫通ビアの途中に分岐を設けないように構成されている。さらに、第2電子部品を接続する第2配線間に、第1電子部品を接続する第1配線を配置し、第1配線と第2配線の間で信号をインターリーブ送信する。

【解決手段】本発明に係る信号伝送回路において、電子部品のリード端子と貫通ビアは表層配線で接続され、貫通ビアの途中に分岐を設けないように構成されている。さらに、第2電子部品を接続する第2配線間に、第1電子部品を接続する第1配線を配置し、第1配線と第2配線の間で信号をインターリーブ送信する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子部品を実装した基板上に形成される信号伝送回路に関する。

【背景技術】

【0002】

近年、低コストかつ高速・大容量の計算機、ストレージ装置などに対する需要が高まっている。これら装置において、高速な信号処理を低コストで実現するため、安価な半導体パッケージ(TSOP:Thin Small Outline Packageなど)のメモリを高密度に実装する場合がある。

【0003】

かかる構成の下では、信号配線間の間隔が狭くなり、クロストークノイズが増大する。また、低コストの基板においては、ビアは基板を貫通する貫通ビアとして形成されており、スタブ(ビアの途中で信号経路が分岐すること)が生じやすい。スタブにおいて生じる信号反射は、信号伝送速度が低速である場合は影響が小さいが、信号伝送速度が高速になると、スタブによって生じる反射ノイズに起因する信号品質の劣化が顕著になる。

【0004】

下記特許文献1には、信号線間のクロストークノイズを低減する技術として、異なるバスはそれぞれ異なるタイミングで変化する信号を伝達するようにする手法が記載されている。

【0005】

下記特許文献2には、メモリコントローラとメモリをスタブレス接続する回路構成が記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−7823号公報

【特許文献2】特開2004−62725号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

回路基板上の信号線間で生じるクロストークノイズを抑制するためには、信号線間の配置間隔を広げることが望ましい。そのための手法として、信号線を回路基板内に埋め込んだ内層配線を用いることが考えられる。内層配線は、回路基板の厚さ方向に設けられたビアに基板内部で信号線を接続することによって設けられる。

【0008】

しかし、コストを低減するため安価な半導体パッケージを実装した回路基板は、ビアを形成するコストを抑制する観点から、基板を貫通した貫通ビアを採用している。そのためビアの途中に内層配線を接続すると、分岐経路が生じてスタブが形成されてしまう。

【0009】

本発明は、上記のような課題を解決するためになされたものであり、低コストかつ実装密度が高い回路基板を用いて、信号線間のクロストークノイズを低減するとともに、スタブによる反射ノイズを低減することのできる信号伝送回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明に係る信号伝送回路において、電子部品のリード端子と貫通ビアは表層配線で接続され、貫通ビアの途中に分岐を設けないように構成されている。さらに、第2電子部品と送信回路を接続する第2配線間に、第1電子部品と送信回路を接続する第1配線を配置し、第1配線と第2配線の間で信号をインターリーブ送信する。

【発明の効果】

【0011】

本発明に係る信号伝送回路によれば、貫通ビアの途中に分岐経路を設けないようにすることにより、スタブにおける反射ノイズを抑制することができる。また、信号をインターリーブ送信することにより、信号線間のクロストークノイズを抑制することができる。これらにより、低コストで実装密度が高く、信号品質の良い信号伝送回路を提供することができる。

【図面の簡単な説明】

【0012】

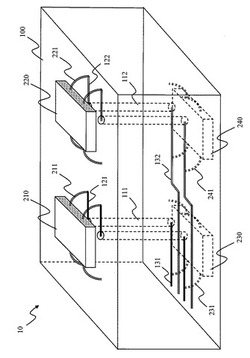

【図1】実施形態1に係る信号伝送回路10の構成図である。

【図2】実施形態1に係る信号伝送回路10の上面透視図および側断面図である。

【図3】従来の信号伝送回路の側断面図である。

【図4】信号伝送回路の解析モデルを示す図である。

【図5】図4に示した解析モデルを用いて信号波形を解析した結果を示す図である。

【図6】実施形態2に係る信号伝送回路10の上面透視図である。

【図7】実施形態2に係る信号伝送回路10の別構成例を示す上面透視図である。

【図8】実施形態3に係る信号伝送回路10の側断面図である。

【図9】実施形態4に係る信号伝送回路10の側断面図である。

【図10】実施形態5に係る信号伝送回路10の側断面図である。

【図11】実施形態6における信号送信回路300の構成例を示す図である。

【図12】実施形態7に係る信号伝送回路10の構成図である。

【発明を実施するための形態】

【0013】

<実施の形態1>

図1は、本発明の実施形態1に係る信号伝送回路10の構成図である。信号伝送回路10は、基板100、電子部品210、220、230、および240、貫通ビア111および112、表層配線121、122、131、132を備える。

【0014】

電子部品210と220は基板100の表面に実装されており、それぞれリード端子211、221を備える。電子部品230と240は基板100の裏面に実装されており、それぞれリード端子231、241を備える。記載の簡易のため、リード端子の本数はそれぞれ4本とした。

【0015】

貫通ビア111と112は、それぞれ基板100を貫通している。貫通ビア111は表層配線121とリード端子211を介して電子部品210に接続され、貫通ビア112は表層配線122とリード端子221を介して電子部品220に接続されている。

【0016】

電子部品230は、リード端子231と表層配線131を介して貫通ビア111に接続されている。電子部品240は、リード端子241と表層配線132を介して貫通ビア112に接続されている。

【0017】

表層配線131と132は、基板100の裏面において集約され、後述する信号送信回路300に接続されている。電子部品210、220、230、および240は、表層配線131と132を介して、信号送信回路300から信号を受信する。

【0018】

図2は、本実施形態1に係る信号伝送回路10の上面透視図および側断面図である。上面透視図は、信号伝送回路10を上方から透過して見た図である。上方から見て同じ位置にある部品は、図面中の符号を併記して記載した。

【0019】

表層配線132は、電子部品210のリード端子211の間を通過して、信号伝送回路300に接続されている。リード端子211は表層配線121および表層配線131に接続されているので、結果として表層配線131と132は交互に配置されることになる。

【0020】

貫通ビア111は、基板100の表面と裏面で、それぞれ表層配線121と131に接続され、途中で分岐経路を有さない。これにより、貫通ビア111にはスタブ部分が生じないので、スタブによって生じる反射ノイズを低減することができる。

【0021】

信号送信回路300が送信した信号は、表層配線131を介して電子部品230に到達し、さらに貫通ビア111と表層配線121を介して電子部品210に到達する。電子部品210と230は、信号送信回路300からの信号線路を終端する終端抵抗212および232(例えば、ODT:On Die Termination)をそれぞれ内蔵している。

【0022】

電子部品220と240、貫通ビア112についても、上記と同様の構成を備える。ただし表層配線131と132は交互に配置されているので、信号伝送回路300が信号をそのまま送信すると、表層配線131と132の間でクロストークノイズが生じる。そこで信号送信回路300は、信号を表層配線131と132の間でインターリーブ送信する。これにより、クロストークノイズを低減することができる。

【0023】

図3は、従来の信号伝送回路の側断面図である。本発明に係る信号伝送回路10と比較するために従来の構成を示した。従来の信号伝送回路は、基板100の内部に埋め込まれた内層配線141が貫通ビア111の途中に接続されており、これによって貫通ビア111が分岐してスタブ1111が形成される。

【0024】

図4は、信号伝送回路の解析モデルを示す図である。図4(a)は本実施形態1に係る信号伝送回路10の解析モデル、図4(b)は図3に示した従来の信号伝送回路の解析モデルを示す。

【0025】

本実施形態1に係る信号伝送回路10において、信号送信回路300は、抵抗301と波形生成器302によってモデル化することができる。電子部品210〜240は、抵抗251とコンデンサ252を備えた受信素子250としてモデル化することができる。リード端子はインダクタ402でモデル化する。各表層配線は信号線路401でモデル化する。貫通ビア111と112は信号線路403でモデル化する。

【0026】

従来の信号伝送回路も同様にモデル化することができるが、スタブ1111を信号線路404でモデル化している点が、本実施形態1に係る信号伝送回路10とは異なる。

【0027】

図5は、図4に示した解析モデルを用いて信号波形を解析した結果を示す図である。図5(a)は電子部品230におけるアイパターン、図5(b)は電子部品210におけるアイパターンを示す。それぞれ左図は従来の信号伝送回路におけるアイパターン、右図は本実施形態1にかかる信号伝送回路10のアイパターンを示す。信号伝送速度は800Mbps、信号線路401、403、404の特性インピーダンスは50Ω、抵抗251は50Ωとした。図5に示すように、本実施形態1に係る信号伝送回路10では、ノイズを低減し、信号の有効ウィンドウ幅が広くなっていることがわかる。

【0028】

<実施の形態1:まとめ>

以上のように、本実施形態1に係る信号伝送回路10において、貫通ビア111および112は途中で分岐しないように構成されており、電子部品と貫通ビアは表層配線のみで接続される。これにより、貫通ビアの途中で信号経路が分岐せず、スタブを形成しないようにすることができる。

【0029】

また、本実施形態1に係る信号伝送回路10は、貫通ビアの途中で信号経路を分岐させずに基板100の実装面で表層配線を集約し、各表層配線間で信号をインターリーブ送信する。これにより、表層配線を高密度で実装しつつ、クロストークノイズを低減することができる。

【0030】

また、本実施形態1に係る信号伝送回路10において、表層配線131と132は交互に配置されており、信号送信回路300はこれら表層配線の間で信号をインターリーブ送信する。これにより、同時に信号が送信される配線の間隔が大きく、かつシールド線が入るので、インターリーブ送信の効果と併せてクロストークノイズをより効果的に低減することができる。

【0031】

<実施の形態2>

実施形態1では、表層配線132をリード端子間に通し、表層配線131と132を交互に配置することとした。この配置は、リード端子の間隔が十分であれば特に支障はないが、表層配線の幅に対してリード端子の間隔が十分に大きくない場合には、配線を形成する工程の制約上、支障が生じる。そこで本発明の実施形態2では、電子部品230を迂回するように表層配線132を配置することとした。

【0032】

図6は、本実施形態2に係る信号伝送回路10の上面透視図である。本実施形態2において、表層配線132は、電子部品230を迂回するように配置されている。

【0033】

表層配線131については、必ずしも表層配線132の配置に合わせる必要はないが、配線密度を高める観点からは、表層配線131と132をできる限り交互に配置することが望ましい。そこで本実施形態2では、表層配線131を表層配線132の配置位置に向かって延ばし、両者が合流した位置からこれらを交互に配置することとした。

【0034】

ただし、表層配線131と表層配線132が交差しないように、2つ目の貫通ビア113と114を設けて配線を基板100の表面に改めて延ばし、図6における貫通ビア113よりも左側の領域においてのみ、表層配線131と表層配線132を交互に配置することとした。

【0035】

図6に示す構成の下では、貫通ビア113よりも左側の領域において表層配線131と132が交互に配置されているため、この領域においてインターリーブ送信の効果を発揮することができる。

【0036】

図7は、本実施形態2に係る信号伝送回路10の別構成例を示す上面透視図である。図7に示す構成では、電子部品210と220を、信号伝送回路300に向かって互いに横方向に隣接して配置している。電子部品230と240についても同様である。

【0037】

図7に示す構成により、表層配線132は電子部品210と230を迂回して配置されることになるので、図6と同様の効果を発揮することができる。さらには、信号伝送回路300から電子部品220と240までの間の信号線路が短くなり、その結果としてインターリーブ送信を実施しない区間が図6よりも短くなるので、信号をより安定して送信することができる。

【0038】

<実施の形態3>

本発明の実施形態3では、表層配線131または132を全て表層配線として形成するだけの実装スペースが取れないような場合において、これら表層配線の一部を内層配線として構成した例を説明する。

【0039】

図8は、本実施形態3に係る信号伝送回路10の側断面図である。本実施形態3に係る信号伝送回路10の構成は、実施形態1〜2で説明した構成と概ね同様であるが、表層配線131の一部が基板100に埋め込まれた内層配線133として構成されている点が異なる。表層配線132についても同様に配置することもできるが、説明は省略する。

【0040】

図8において、表層配線131のうち、信号送信回路300と電子部品230の間の区間の一部は、内層配線133となっている。内層配線133と表層配線131の間は、貫通ビア115で接続されている。貫通ビア115と内層配線133によって分岐経路が生じ、スタブが形成される。スタブの影響をできる限り抑えるため、内層配線133はできる限り基板100の表面に近い位置に配置することが望ましい。

【0041】

図8に示す構成によれば、表層配線131の一部を内層配線133として構成することにより、実施形態1〜2と概ね同等の効果を発揮しつつ、表層配線131を実装する面積を低減することができる。また、貫通ビア115と内層配線133によって生じるスタブの長さをできる限り短く抑えることにより、実施形態1〜2と同等の効果に近づけることができる。

【0042】

<実施の形態4>

本発明の実施形態4では、電子部品を基板100の表面のみに実装する場合における構成を説明する。

【0043】

図9は、本実施形態4に係る信号伝送回路10の側断面図である。本実施形態4では、基板100の表面のみに電子部品210と220が実装され、これらは信号伝送回路300から同じ信号を受信するものとする。

【0044】

図9において、電子部品220は信号伝送回路300から見て奥側に配置されているので、信号伝送回路300から電子部品220に至る信号線は、電子部品210を迂回するか、または電子部品210のリード端子211の間を通過するなどして、電子部品210を回避する必要がある。

【0045】

実装面積などの都合上、これら手法をいずれも採用することができない場合には、図9に示すように貫通ビア111を介して表層配線131をいったん基板100の裏面に延ばし、裏面の表層配線132、貫通ビア112、表面の表層配線122を介して電子部品220に信号を送信するようにすればよい。信号送信回路300が信号をインターリーブ送信する点は、実施形態1〜3と同様である。

【0046】

以上のように、本実施形態4に係る信号伝送回路10によれば、リード端子間に表層配線を通すことが難しい場合でも、貫通ビアを介して電子部品を迂回することができる。貫通ビア111と112が分岐経路を有さない点については、実施形態1〜3と同様であるので、同様の効果を発揮することができる。

【0047】

<実施の形態5>

図10は、本発明の実施形態5に係る信号伝送回路10の側断面図である。本実施形態5において、電子部品210は終端抵抗212を内蔵していないため、外付け終端抵抗213を新たに設け、リード端子211に接続した。その他の構成は実施形態1〜4と同様である。なお図10では、実施形態1と同様の構成を前提とした。

【0048】

本実施形態5に係る信号伝送回路10も、実施形態1〜4と同様の効果を発揮することができる。

【0049】

<実施の形態6>

本発明の実施形態6では、信号送信回路300の具体例について説明する。その他の構成は実施形態1〜5と同様である。以下では実施形態1で説明した構成を前提として説明する。

【0050】

図11は、本実施形態6における信号送信回路300の構成例を示す図である。信号送信回路300は、送信器303、受信器304、抵抗素子305、スイッチ306を備える。

【0051】

送信器303が送信する信号は、スイッチ306がOFFのときは表層配線131と132を介して各電子部品に送信される。スイッチ306がONのときは、抵抗素子305を介して信号線を終端する。抵抗素子305の抵抗値は基板配線の特性インピーダンスに整合させておくことが望ましい。

【0052】

抵抗素子305の抵抗値をインピーダンス整合させておくことにより、インターリーブ送信の過程で使用していない信号線にクロストークノイズが生じたとしても、抵抗素子305において信号反射が生じず、ノイズがグラウンドに流れ出る。これにより、インターリーブ送信において使用している信号線間におけるクロストークノイズを低減することができる。

【0053】

<実施の形態7>

図12は、本発明の実施形態7に係る信号伝送回路10の構成図である。本実施形態7に係る信号伝送回路10の構成は、信号送信回路300の構成を除いて、実施形態6と同様である。

【0054】

本実施形態7において、信号送信回路300は、送信器303、受信器304、バススイッチ310を備える。送信器303と受信器304については実施形態6と同様である。バススイッチ310は、抵抗素子311、スイッチ312を備える。

【0055】

表層配線131または132に接続されたスイッチ312がONのときは、送信器303が送信する信号は各表層配線を介して各電子部品に送信される。抵抗素子311に接続されたスイッチ312がONのときは、表層配線131または132に接続されたスイッチ312はOFFとなり、信号線は抵抗素子312を介して終端する。

【0056】

本実施形態7によれば、信号送信回路300自身がインターリーブ送信機能を備えていない場合でも、バススイッチ310を新たに追加することにより、実施形態1〜6と同様の効果を発揮することができる。

【0057】

本発明は上記した実施例に限定されるものではなく、様々な変形例が含まれる。例えば、上記した実施例は本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施形態の構成の一部を他の実施形態の構成に置き換えることもできる。また、ある実施形態の構成に他の実施形態の構成を加えることもできる。また、各実施形態の構成の一部について、他の構成の追加・削除・置換をすることができる。

【0058】

また、上記各構成は、それらの一部または全部を、多段構成にすることにより性能を改善してもよい。例えば、信号バス数の増加による接続する半導体素子の多段化がある。

【0059】

また、信号配線や各構成の素子は説明上必要と考えられるものを示しており、製品上必ずしも全ての信号配線や各構成の素子を示しているとは限らない。実際には各構成を結ぶ信号配線トポロジーの種類や各構成の素子数が複数になる場合があると考えてもよい。

【符号の説明】

【0060】

100:基板

111〜115:貫通ビア

1111:スタブ

121、122、131、132:表層配線

133、141:内層配線

210、220、230、240:電子部品

211、221、231、241:リード端子

250:受信回路

212、222、232、251:抵抗

252:コンデンサ

300:信号送信回路

301:抵抗

302:波形生成器

303:送信器

304: 受信器

305:抵抗素子

306:スイッチ

310:バススイッチ

311:抵抗素子

312:スイッチ

401、403、404:信号線路

402:インダクタ

【技術分野】

【0001】

本発明は、電子部品を実装した基板上に形成される信号伝送回路に関する。

【背景技術】

【0002】

近年、低コストかつ高速・大容量の計算機、ストレージ装置などに対する需要が高まっている。これら装置において、高速な信号処理を低コストで実現するため、安価な半導体パッケージ(TSOP:Thin Small Outline Packageなど)のメモリを高密度に実装する場合がある。

【0003】

かかる構成の下では、信号配線間の間隔が狭くなり、クロストークノイズが増大する。また、低コストの基板においては、ビアは基板を貫通する貫通ビアとして形成されており、スタブ(ビアの途中で信号経路が分岐すること)が生じやすい。スタブにおいて生じる信号反射は、信号伝送速度が低速である場合は影響が小さいが、信号伝送速度が高速になると、スタブによって生じる反射ノイズに起因する信号品質の劣化が顕著になる。

【0004】

下記特許文献1には、信号線間のクロストークノイズを低減する技術として、異なるバスはそれぞれ異なるタイミングで変化する信号を伝達するようにする手法が記載されている。

【0005】

下記特許文献2には、メモリコントローラとメモリをスタブレス接続する回路構成が記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−7823号公報

【特許文献2】特開2004−62725号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

回路基板上の信号線間で生じるクロストークノイズを抑制するためには、信号線間の配置間隔を広げることが望ましい。そのための手法として、信号線を回路基板内に埋め込んだ内層配線を用いることが考えられる。内層配線は、回路基板の厚さ方向に設けられたビアに基板内部で信号線を接続することによって設けられる。

【0008】

しかし、コストを低減するため安価な半導体パッケージを実装した回路基板は、ビアを形成するコストを抑制する観点から、基板を貫通した貫通ビアを採用している。そのためビアの途中に内層配線を接続すると、分岐経路が生じてスタブが形成されてしまう。

【0009】

本発明は、上記のような課題を解決するためになされたものであり、低コストかつ実装密度が高い回路基板を用いて、信号線間のクロストークノイズを低減するとともに、スタブによる反射ノイズを低減することのできる信号伝送回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明に係る信号伝送回路において、電子部品のリード端子と貫通ビアは表層配線で接続され、貫通ビアの途中に分岐を設けないように構成されている。さらに、第2電子部品と送信回路を接続する第2配線間に、第1電子部品と送信回路を接続する第1配線を配置し、第1配線と第2配線の間で信号をインターリーブ送信する。

【発明の効果】

【0011】

本発明に係る信号伝送回路によれば、貫通ビアの途中に分岐経路を設けないようにすることにより、スタブにおける反射ノイズを抑制することができる。また、信号をインターリーブ送信することにより、信号線間のクロストークノイズを抑制することができる。これらにより、低コストで実装密度が高く、信号品質の良い信号伝送回路を提供することができる。

【図面の簡単な説明】

【0012】

【図1】実施形態1に係る信号伝送回路10の構成図である。

【図2】実施形態1に係る信号伝送回路10の上面透視図および側断面図である。

【図3】従来の信号伝送回路の側断面図である。

【図4】信号伝送回路の解析モデルを示す図である。

【図5】図4に示した解析モデルを用いて信号波形を解析した結果を示す図である。

【図6】実施形態2に係る信号伝送回路10の上面透視図である。

【図7】実施形態2に係る信号伝送回路10の別構成例を示す上面透視図である。

【図8】実施形態3に係る信号伝送回路10の側断面図である。

【図9】実施形態4に係る信号伝送回路10の側断面図である。

【図10】実施形態5に係る信号伝送回路10の側断面図である。

【図11】実施形態6における信号送信回路300の構成例を示す図である。

【図12】実施形態7に係る信号伝送回路10の構成図である。

【発明を実施するための形態】

【0013】

<実施の形態1>

図1は、本発明の実施形態1に係る信号伝送回路10の構成図である。信号伝送回路10は、基板100、電子部品210、220、230、および240、貫通ビア111および112、表層配線121、122、131、132を備える。

【0014】

電子部品210と220は基板100の表面に実装されており、それぞれリード端子211、221を備える。電子部品230と240は基板100の裏面に実装されており、それぞれリード端子231、241を備える。記載の簡易のため、リード端子の本数はそれぞれ4本とした。

【0015】

貫通ビア111と112は、それぞれ基板100を貫通している。貫通ビア111は表層配線121とリード端子211を介して電子部品210に接続され、貫通ビア112は表層配線122とリード端子221を介して電子部品220に接続されている。

【0016】

電子部品230は、リード端子231と表層配線131を介して貫通ビア111に接続されている。電子部品240は、リード端子241と表層配線132を介して貫通ビア112に接続されている。

【0017】

表層配線131と132は、基板100の裏面において集約され、後述する信号送信回路300に接続されている。電子部品210、220、230、および240は、表層配線131と132を介して、信号送信回路300から信号を受信する。

【0018】

図2は、本実施形態1に係る信号伝送回路10の上面透視図および側断面図である。上面透視図は、信号伝送回路10を上方から透過して見た図である。上方から見て同じ位置にある部品は、図面中の符号を併記して記載した。

【0019】

表層配線132は、電子部品210のリード端子211の間を通過して、信号伝送回路300に接続されている。リード端子211は表層配線121および表層配線131に接続されているので、結果として表層配線131と132は交互に配置されることになる。

【0020】

貫通ビア111は、基板100の表面と裏面で、それぞれ表層配線121と131に接続され、途中で分岐経路を有さない。これにより、貫通ビア111にはスタブ部分が生じないので、スタブによって生じる反射ノイズを低減することができる。

【0021】

信号送信回路300が送信した信号は、表層配線131を介して電子部品230に到達し、さらに貫通ビア111と表層配線121を介して電子部品210に到達する。電子部品210と230は、信号送信回路300からの信号線路を終端する終端抵抗212および232(例えば、ODT:On Die Termination)をそれぞれ内蔵している。

【0022】

電子部品220と240、貫通ビア112についても、上記と同様の構成を備える。ただし表層配線131と132は交互に配置されているので、信号伝送回路300が信号をそのまま送信すると、表層配線131と132の間でクロストークノイズが生じる。そこで信号送信回路300は、信号を表層配線131と132の間でインターリーブ送信する。これにより、クロストークノイズを低減することができる。

【0023】

図3は、従来の信号伝送回路の側断面図である。本発明に係る信号伝送回路10と比較するために従来の構成を示した。従来の信号伝送回路は、基板100の内部に埋め込まれた内層配線141が貫通ビア111の途中に接続されており、これによって貫通ビア111が分岐してスタブ1111が形成される。

【0024】

図4は、信号伝送回路の解析モデルを示す図である。図4(a)は本実施形態1に係る信号伝送回路10の解析モデル、図4(b)は図3に示した従来の信号伝送回路の解析モデルを示す。

【0025】

本実施形態1に係る信号伝送回路10において、信号送信回路300は、抵抗301と波形生成器302によってモデル化することができる。電子部品210〜240は、抵抗251とコンデンサ252を備えた受信素子250としてモデル化することができる。リード端子はインダクタ402でモデル化する。各表層配線は信号線路401でモデル化する。貫通ビア111と112は信号線路403でモデル化する。

【0026】

従来の信号伝送回路も同様にモデル化することができるが、スタブ1111を信号線路404でモデル化している点が、本実施形態1に係る信号伝送回路10とは異なる。

【0027】

図5は、図4に示した解析モデルを用いて信号波形を解析した結果を示す図である。図5(a)は電子部品230におけるアイパターン、図5(b)は電子部品210におけるアイパターンを示す。それぞれ左図は従来の信号伝送回路におけるアイパターン、右図は本実施形態1にかかる信号伝送回路10のアイパターンを示す。信号伝送速度は800Mbps、信号線路401、403、404の特性インピーダンスは50Ω、抵抗251は50Ωとした。図5に示すように、本実施形態1に係る信号伝送回路10では、ノイズを低減し、信号の有効ウィンドウ幅が広くなっていることがわかる。

【0028】

<実施の形態1:まとめ>

以上のように、本実施形態1に係る信号伝送回路10において、貫通ビア111および112は途中で分岐しないように構成されており、電子部品と貫通ビアは表層配線のみで接続される。これにより、貫通ビアの途中で信号経路が分岐せず、スタブを形成しないようにすることができる。

【0029】

また、本実施形態1に係る信号伝送回路10は、貫通ビアの途中で信号経路を分岐させずに基板100の実装面で表層配線を集約し、各表層配線間で信号をインターリーブ送信する。これにより、表層配線を高密度で実装しつつ、クロストークノイズを低減することができる。

【0030】

また、本実施形態1に係る信号伝送回路10において、表層配線131と132は交互に配置されており、信号送信回路300はこれら表層配線の間で信号をインターリーブ送信する。これにより、同時に信号が送信される配線の間隔が大きく、かつシールド線が入るので、インターリーブ送信の効果と併せてクロストークノイズをより効果的に低減することができる。

【0031】

<実施の形態2>

実施形態1では、表層配線132をリード端子間に通し、表層配線131と132を交互に配置することとした。この配置は、リード端子の間隔が十分であれば特に支障はないが、表層配線の幅に対してリード端子の間隔が十分に大きくない場合には、配線を形成する工程の制約上、支障が生じる。そこで本発明の実施形態2では、電子部品230を迂回するように表層配線132を配置することとした。

【0032】

図6は、本実施形態2に係る信号伝送回路10の上面透視図である。本実施形態2において、表層配線132は、電子部品230を迂回するように配置されている。

【0033】

表層配線131については、必ずしも表層配線132の配置に合わせる必要はないが、配線密度を高める観点からは、表層配線131と132をできる限り交互に配置することが望ましい。そこで本実施形態2では、表層配線131を表層配線132の配置位置に向かって延ばし、両者が合流した位置からこれらを交互に配置することとした。

【0034】

ただし、表層配線131と表層配線132が交差しないように、2つ目の貫通ビア113と114を設けて配線を基板100の表面に改めて延ばし、図6における貫通ビア113よりも左側の領域においてのみ、表層配線131と表層配線132を交互に配置することとした。

【0035】

図6に示す構成の下では、貫通ビア113よりも左側の領域において表層配線131と132が交互に配置されているため、この領域においてインターリーブ送信の効果を発揮することができる。

【0036】

図7は、本実施形態2に係る信号伝送回路10の別構成例を示す上面透視図である。図7に示す構成では、電子部品210と220を、信号伝送回路300に向かって互いに横方向に隣接して配置している。電子部品230と240についても同様である。

【0037】

図7に示す構成により、表層配線132は電子部品210と230を迂回して配置されることになるので、図6と同様の効果を発揮することができる。さらには、信号伝送回路300から電子部品220と240までの間の信号線路が短くなり、その結果としてインターリーブ送信を実施しない区間が図6よりも短くなるので、信号をより安定して送信することができる。

【0038】

<実施の形態3>

本発明の実施形態3では、表層配線131または132を全て表層配線として形成するだけの実装スペースが取れないような場合において、これら表層配線の一部を内層配線として構成した例を説明する。

【0039】

図8は、本実施形態3に係る信号伝送回路10の側断面図である。本実施形態3に係る信号伝送回路10の構成は、実施形態1〜2で説明した構成と概ね同様であるが、表層配線131の一部が基板100に埋め込まれた内層配線133として構成されている点が異なる。表層配線132についても同様に配置することもできるが、説明は省略する。

【0040】

図8において、表層配線131のうち、信号送信回路300と電子部品230の間の区間の一部は、内層配線133となっている。内層配線133と表層配線131の間は、貫通ビア115で接続されている。貫通ビア115と内層配線133によって分岐経路が生じ、スタブが形成される。スタブの影響をできる限り抑えるため、内層配線133はできる限り基板100の表面に近い位置に配置することが望ましい。

【0041】

図8に示す構成によれば、表層配線131の一部を内層配線133として構成することにより、実施形態1〜2と概ね同等の効果を発揮しつつ、表層配線131を実装する面積を低減することができる。また、貫通ビア115と内層配線133によって生じるスタブの長さをできる限り短く抑えることにより、実施形態1〜2と同等の効果に近づけることができる。

【0042】

<実施の形態4>

本発明の実施形態4では、電子部品を基板100の表面のみに実装する場合における構成を説明する。

【0043】

図9は、本実施形態4に係る信号伝送回路10の側断面図である。本実施形態4では、基板100の表面のみに電子部品210と220が実装され、これらは信号伝送回路300から同じ信号を受信するものとする。

【0044】

図9において、電子部品220は信号伝送回路300から見て奥側に配置されているので、信号伝送回路300から電子部品220に至る信号線は、電子部品210を迂回するか、または電子部品210のリード端子211の間を通過するなどして、電子部品210を回避する必要がある。

【0045】

実装面積などの都合上、これら手法をいずれも採用することができない場合には、図9に示すように貫通ビア111を介して表層配線131をいったん基板100の裏面に延ばし、裏面の表層配線132、貫通ビア112、表面の表層配線122を介して電子部品220に信号を送信するようにすればよい。信号送信回路300が信号をインターリーブ送信する点は、実施形態1〜3と同様である。

【0046】

以上のように、本実施形態4に係る信号伝送回路10によれば、リード端子間に表層配線を通すことが難しい場合でも、貫通ビアを介して電子部品を迂回することができる。貫通ビア111と112が分岐経路を有さない点については、実施形態1〜3と同様であるので、同様の効果を発揮することができる。

【0047】

<実施の形態5>

図10は、本発明の実施形態5に係る信号伝送回路10の側断面図である。本実施形態5において、電子部品210は終端抵抗212を内蔵していないため、外付け終端抵抗213を新たに設け、リード端子211に接続した。その他の構成は実施形態1〜4と同様である。なお図10では、実施形態1と同様の構成を前提とした。

【0048】

本実施形態5に係る信号伝送回路10も、実施形態1〜4と同様の効果を発揮することができる。

【0049】

<実施の形態6>

本発明の実施形態6では、信号送信回路300の具体例について説明する。その他の構成は実施形態1〜5と同様である。以下では実施形態1で説明した構成を前提として説明する。

【0050】

図11は、本実施形態6における信号送信回路300の構成例を示す図である。信号送信回路300は、送信器303、受信器304、抵抗素子305、スイッチ306を備える。

【0051】

送信器303が送信する信号は、スイッチ306がOFFのときは表層配線131と132を介して各電子部品に送信される。スイッチ306がONのときは、抵抗素子305を介して信号線を終端する。抵抗素子305の抵抗値は基板配線の特性インピーダンスに整合させておくことが望ましい。

【0052】

抵抗素子305の抵抗値をインピーダンス整合させておくことにより、インターリーブ送信の過程で使用していない信号線にクロストークノイズが生じたとしても、抵抗素子305において信号反射が生じず、ノイズがグラウンドに流れ出る。これにより、インターリーブ送信において使用している信号線間におけるクロストークノイズを低減することができる。

【0053】

<実施の形態7>

図12は、本発明の実施形態7に係る信号伝送回路10の構成図である。本実施形態7に係る信号伝送回路10の構成は、信号送信回路300の構成を除いて、実施形態6と同様である。

【0054】

本実施形態7において、信号送信回路300は、送信器303、受信器304、バススイッチ310を備える。送信器303と受信器304については実施形態6と同様である。バススイッチ310は、抵抗素子311、スイッチ312を備える。

【0055】

表層配線131または132に接続されたスイッチ312がONのときは、送信器303が送信する信号は各表層配線を介して各電子部品に送信される。抵抗素子311に接続されたスイッチ312がONのときは、表層配線131または132に接続されたスイッチ312はOFFとなり、信号線は抵抗素子312を介して終端する。

【0056】

本実施形態7によれば、信号送信回路300自身がインターリーブ送信機能を備えていない場合でも、バススイッチ310を新たに追加することにより、実施形態1〜6と同様の効果を発揮することができる。

【0057】

本発明は上記した実施例に限定されるものではなく、様々な変形例が含まれる。例えば、上記した実施例は本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施形態の構成の一部を他の実施形態の構成に置き換えることもできる。また、ある実施形態の構成に他の実施形態の構成を加えることもできる。また、各実施形態の構成の一部について、他の構成の追加・削除・置換をすることができる。

【0058】

また、上記各構成は、それらの一部または全部を、多段構成にすることにより性能を改善してもよい。例えば、信号バス数の増加による接続する半導体素子の多段化がある。

【0059】

また、信号配線や各構成の素子は説明上必要と考えられるものを示しており、製品上必ずしも全ての信号配線や各構成の素子を示しているとは限らない。実際には各構成を結ぶ信号配線トポロジーの種類や各構成の素子数が複数になる場合があると考えてもよい。

【符号の説明】

【0060】

100:基板

111〜115:貫通ビア

1111:スタブ

121、122、131、132:表層配線

133、141:内層配線

210、220、230、240:電子部品

211、221、231、241:リード端子

250:受信回路

212、222、232、251:抵抗

252:コンデンサ

300:信号送信回路

301:抵抗

302:波形生成器

303:送信器

304: 受信器

305:抵抗素子

306:スイッチ

310:バススイッチ

311:抵抗素子

312:スイッチ

401、403、404:信号線路

402:インダクタ

【特許請求の範囲】

【請求項1】

第1電子部品および第2電子部品を実装する基板と、

前記基板を貫通するビアと、

前記第1電子部品および前記第2電子部品に信号を送信する送信回路と、

前記第1電子部品を前記送信回路に接続する第1配線と、

前記第2電子部品を前記送信回路に接続する第2配線と、

を備え、

前記第1電子部品に電気的に接続されている前記ビアと、前記第2電子部品に電気的に接続されている前記ビアは、前記基板内部で分岐して各分岐経路がそれぞれ異なる電子部品に電気的に接続されることがないように構成されており、

前記第1電子部品のリード端子と前記第2電子部品のリード端子は、前記基板上の表層配線のみで前記ビアに接続されており、

前記第1配線は、複数の前記第2配線の間に配置されており、

前記送信回路は、前記第1配線と前記第2配線の間で前記信号をインターリーブ送信する

ことを特徴とする信号伝送回路。

【請求項2】

前記第2配線は、前記第1電子部品が備える複数のリード端子の間に配置されている

ことを特徴とする請求項1記載の信号伝送回路。

【請求項3】

前記第2配線は、前記第1電子部品を迂回して配置されている

ことを特徴とする請求項1記載の信号伝送回路。

【請求項4】

前記第1電子部品と前記第2電子部品は、前記送信回路が配置されている方向に向かって互いに横に隣接して配置されている

ことを特徴とする請求項3記載の信号伝送回路。

【請求項5】

前記第1配線の一部または前記第2配線の一部は、前記基板内の内層配線として構成されている

ことを特徴とする請求項1記載の信号伝送回路。

【請求項6】

前記第1電子部品のリード端子または前記第2電子部品のリード端子に接続された外付け終端抵抗を備えた

ことを特徴とする請求項1記載の信号伝送回路。

【請求項7】

前記送信回路は、

前記第1配線と前記第2配線に前記信号を送信するか否かを切り替えるスイッチと、

前記第1配線および前記第2配線を終端する終端抵抗と、

を備え、

前記終端抵抗は、

抵抗値が前記第1配線の特性インピーダンスおよび前記第2配線の特性インピーダンスに整合するように構成されている

ことを特徴とする請求項1記載の信号伝送回路。

【請求項1】

第1電子部品および第2電子部品を実装する基板と、

前記基板を貫通するビアと、

前記第1電子部品および前記第2電子部品に信号を送信する送信回路と、

前記第1電子部品を前記送信回路に接続する第1配線と、

前記第2電子部品を前記送信回路に接続する第2配線と、

を備え、

前記第1電子部品に電気的に接続されている前記ビアと、前記第2電子部品に電気的に接続されている前記ビアは、前記基板内部で分岐して各分岐経路がそれぞれ異なる電子部品に電気的に接続されることがないように構成されており、

前記第1電子部品のリード端子と前記第2電子部品のリード端子は、前記基板上の表層配線のみで前記ビアに接続されており、

前記第1配線は、複数の前記第2配線の間に配置されており、

前記送信回路は、前記第1配線と前記第2配線の間で前記信号をインターリーブ送信する

ことを特徴とする信号伝送回路。

【請求項2】

前記第2配線は、前記第1電子部品が備える複数のリード端子の間に配置されている

ことを特徴とする請求項1記載の信号伝送回路。

【請求項3】

前記第2配線は、前記第1電子部品を迂回して配置されている

ことを特徴とする請求項1記載の信号伝送回路。

【請求項4】

前記第1電子部品と前記第2電子部品は、前記送信回路が配置されている方向に向かって互いに横に隣接して配置されている

ことを特徴とする請求項3記載の信号伝送回路。

【請求項5】

前記第1配線の一部または前記第2配線の一部は、前記基板内の内層配線として構成されている

ことを特徴とする請求項1記載の信号伝送回路。

【請求項6】

前記第1電子部品のリード端子または前記第2電子部品のリード端子に接続された外付け終端抵抗を備えた

ことを特徴とする請求項1記載の信号伝送回路。

【請求項7】

前記送信回路は、

前記第1配線と前記第2配線に前記信号を送信するか否かを切り替えるスイッチと、

前記第1配線および前記第2配線を終端する終端抵抗と、

を備え、

前記終端抵抗は、

抵抗値が前記第1配線の特性インピーダンスおよび前記第2配線の特性インピーダンスに整合するように構成されている

ことを特徴とする請求項1記載の信号伝送回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−227617(P2012−227617A)

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願番号】特願2011−91408(P2011−91408)

【出願日】平成23年4月15日(2011.4.15)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願日】平成23年4月15日(2011.4.15)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]