信号分配器及びその設計方法

【課題】回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることを目的とする。

【解決手段】信号分配器1は、複数の出力端子21と各出力端子21間を接続する複数の伝送線路22とを有する出力部20と、等価回路において多段に直列接続する複数の1/4波長伝送線路により入力端子10と出力部20とを接続する変成器部30と、を備え、等価回路における複数の出力端子21のそれぞれについて、入力端子10の方向から一の出力端子21に接続する伝送線路22の特性インピーダンスと、該一の出力端子21を含む、該伝送線路22よりも入力端子10から離れる方向に位置する一以上の出力端子21の合成インピーダンスとが等しい、ことを特徴とする。

【解決手段】信号分配器1は、複数の出力端子21と各出力端子21間を接続する複数の伝送線路22とを有する出力部20と、等価回路において多段に直列接続する複数の1/4波長伝送線路により入力端子10と出力部20とを接続する変成器部30と、を備え、等価回路における複数の出力端子21のそれぞれについて、入力端子10の方向から一の出力端子21に接続する伝送線路22の特性インピーダンスと、該一の出力端子21を含む、該伝送線路22よりも入力端子10から離れる方向に位置する一以上の出力端子21の合成インピーダンスとが等しい、ことを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マイクロ波信号を分配する信号分配器及びその設計方法に関する。

【背景技術】

【0002】

マイクロ波ミリ波信号をN方向に分配する回路としてウィルキンソン電力分配器が良く知られている(下記非特許文献1参照)。ウィルキンソン電力分配器では、どの入出力端子から見ても整合が取れており、出力端子間のアイソレーションも取れている。しかしながら、3方向以上に分配する場合には回路が立体構造になるので、回路を平面状に構成したり集積回路を製作したりすることは困難である。この課題を解決する技術として、下記特許文献1に記載の電力合成器及び電力分配器が知られている。

【0003】

入力信号を分配する際には、入力信号に対して反射成分を生じないことが要求される。平面構成の回路でこの要求を満たすものとして、下記非特許文献2及び3に記載の変成器付き多分配回路や、下記非特許文献4に記載のバグレー・ポリゴン電力分配器が知られている。また、基板の裏面から同軸ケーブルにより給電し、基板の表面上で放射状に信号を多分配する回路も知られている(下記非特許文献5)。

【0004】

入力信号を2n+1分割(nは整数)する従来のバグレー・ポリゴン電力分配器では、隣り合う出力端子間の伝送路長が半波長と決まっているので、回路が大型化する傾向があった。この点を改善するものとして、特願2006−313003号明細書に記載の電力分配器がある。この電力分配器により回路の小型化が実現できると共に分配特性を改善できる。

【非特許文献1】http://www.microwaves101.com/encyclopedia/wilkinson_nway.cfm

【非特許文献2】M. Kishihara, K. Yamane and I.Ohta,“Design of broadband microstrip-type multi-waypower dividers”、Asia-Pacific Microwave Conference, Proc., vol.3, pp.1688-1691, Nov.2003.

【非特許文献3】M. Kishihara, K. Yamane and I.Ohta,“DParallel processing of powell’s optimization algorithmand its application to design of multi-way power dividers,” Asia-Pacific MicrowaveConference, Proc., 2005.

【非特許文献4】http://www.dc2light.pwp.blueyonder.co.uk/Webpage/Hybridcouplers.htm#bagley

【非特許文献5】E.L.Holzman, “An eiginvalue equation analysis of a symmetrical coax line to N-waywaveguide power divider, “ IEEE Trans. on MTT, Vol.42, No7, July 1994.

【特許文献1】特開平9−289405号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特願2006−313003明細書に記載の電力分配器では、入力端子における反射損が所定のレベル以下である帯域(入力端子における反射特性が良い帯域)が狭い。

【0006】

本発明は、上記課題を解決するためになされたものであり、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることが可能な信号分配器及びその設計方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の信号分配器は、複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、等価回路において多段に直列接続する複数の1/4波長伝送線路により入力端子と出力部とを接続する変成器部と、を備え、等価回路における複数の出力端子のそれぞれについて、入力端子の方向から一の出力端子に接続する伝送線路の特性インピーダンスと、該一の出力端子を含む、該伝送線路よりも入力端子から離れる方向に位置する一以上の出力端子の合成インピーダンスとが等しい、ことを特徴とする。

【0008】

このような信号分配器によれば、変成器部が、複数の1/4波長伝送線路が直列に接続された多段変成器であるので、1段変成器の場合と比較して、入力端子における反射損が広帯域に亘って低減される(入力端子における反射特性(入力反射特性)が広帯域に亘って向上する)。また、各出力端子について、入力端子の方向から一の出力端子に接続する伝送線路の特性インピーダンスが、その伝送線路よりも入力端子から離れる方向に位置する一以上の出力端子の合成インピーダンスと等しくなるように、出力端子間の伝送線路を設けることで、出力端子間の伝送線路の長さを任意に選択できる。その結果、出力端子間の伝送線路長を短くして回路を小型化できる。すなわち、このような信号分配器により、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることが可能となる。

【0009】

本発明の信号分配器では、変成器部が、一端が入力端子と接続する第1の1/4波長伝送線路と、該第1の1/4波長伝送線路の他端と出力部とを接続する第2の1/4波長伝送線路とを有する2段変成器であり、第1の1/4波長伝送線路及び第2の1/4波長伝送線路の線幅が互いに等しいことが好ましい。

【0010】

この場合、変成器部を構成する1/4波長伝送線路の線幅が一定であるので、信号分配器を容易に製作することが可能になる。

【0011】

本発明の信号分配器の設計方法は、複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、入力端子と出力部とを接続する変成器部とを備える信号分配器を設計する情報処理装置における、信号分配器の設計方法であって、入力端子での入力端子インピーダンス、出力端子の個数、及び信号分配器の通過域内許容反射量に対応する許容反射係数の入力を受け付ける受付ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(1)

Z1=2Z0,Z2=2Z0/3,…,Zk=2Z0/(N−2) …(1)

ただし、k=(N−1)/2

(式中、Z0は入力端子インピーダンスを表し、Nは出力端子の個数を表す。)

により、各出力端子間を接続する複数の伝送線路の特性インピーダンスZkを算出する第1算出ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(2)

Zin=Z0/(2n+1) …(2)

ただし、n=(N−1)/2

(式中、Z0は入力端子インピーダンスを表し、Nは出力端子の個数を表す。)

により、変成器部と出力部との接続点における負荷Zinを算出する第2算出ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び許容反射係数と、第2算出ステップにおいて算出された負荷とに基づいて、下記式(3)及び(4)

ρm2={(K0L−K122)/(K0L+K122)}2 …(3)

(式中、ρmは許容反射係数を表し、K0Lは負荷と入力端子インピーダンスとの比を表し、K12は変成器部を構成する第1の1/4波長伝送線路の特性インピーダンスと第2の1/4波長伝送線路の特性インピーダンスの1/2との比を表す。すなわち、K0L=Zin/Z0,K12=(Zm2/2)/Zm1)

Zm1(Zm2/2)=Z0Zin …(4)

(式中、Z0は入力端子インピーダンスを表し、Zinは負荷を表す。)

により、第1の1/4波長伝送線路の特性インピーダンスZm1と第2の1/4波長伝送線路の特性インピーダンスZm2とを算出する第3算出ステップと、第1算出ステップ及び第3算出ステップにおいて算出された特性インピーダンスを出力する出力ステップと、を含むことを特徴とする。

【0012】

このような信号分配器の設計方法によれば、入力端子での入力端子インピーダンス、出力端子の個数、及び信号分配器の通過域内許容反射量に対応する許容反射係数を入力することにより、上記信号分配器を構成する各伝送線路の特性インピーダンスを算出できる。すなわち、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることが可能な信号分配器を設計できる。

【0013】

本発明の信号分配器の設計方法は、複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、入力端子と出力部とを接続する変成器部とを備える信号分配器を設計する情報処理装置における、信号分配器の設計方法であって、入力端子での入力端子インピーダンス、出力端子の個数、及び線路パラメータ比の入力を受け付ける受付ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(5)

Z1=2Z0,Z2=2Z0/3,…,Zk=2Z0/(N−2) …(5)

ただし、k=(N−1)/2

(式中、Z0は入力端子インピーダンスを表し、Nは出力端子の個数を表す。)

により、各出力端子間を接続する複数の伝送線路の特性インピーダンスZkを算出する第1算出ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(6)

Zin=Z0/(2n+1) …(6)

ただし、n=(N−1)/2

(式中、Z0は入力端子インピーダンスを表し、Nは出力端子の個数を表す。)

により、変成器部と出力部との接続点における負荷Zinを算出する第2算出ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び線路パラメータ比と、第2算出ステップにおいて算出された負荷とに基づいて、下記式(7)及び(8)

(Zm2/2)=K12Zm1 …(7)

(式中、K12は線路パラメータ比を表す。)

Zm1(Zm2/2)=Z0Zin …(8)

(式中、Z0は入力端子インピーダンスを表し、Zinは負荷を表す。)

により、第1の1/4波長伝送線路の特性インピーダンスZm1と第2の1/4波長伝送線路の特性インピーダンスZm2とを算出する第3算出ステップと、第1算出ステップ及び第3算出ステップにおいて算出された特性インピーダンスを出力する出力ステップと、を含むことを特徴とする。

【0014】

このような信号分配器の設計方法によれば、入力端子での入力端子インピーダンス、出力端子の個数、及び線路パラメータ比を入力することにより、上記信号分配器を構成する各伝送線路の特性インピーダンスを算出できる。すなわち、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることができ、且つ、第1の1/4波長伝送線路の幅と第2の1/4波長伝送線路の幅とが等しい信号分配器を設計できる。

【発明の効果】

【0015】

このような信号分配器及びその設計方法によれば、多段変成器が導入されると共に、出力端子間の伝送線路の長さではなくその特性インピーダンスが指定されるので、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることが可能になる。

【発明を実施するための最良の形態】

【0016】

以下、添付図面を参照しながら本発明の実施形態を詳細に説明する。なお、図面の説明において同一又は同等の要素には同一の符号を付し、重複する説明を省略する。

【0017】

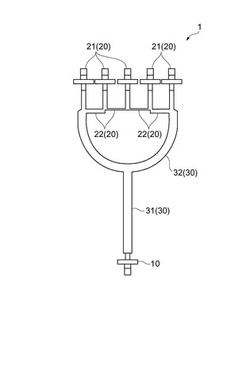

まず、図1を用いて、実施形態に係る信号分配器1の構成を説明する。図1は、実施形態に係る信号分配器1の平面図である。信号分配器1は、マイクロ波信号が入力される入力端子10と、信号分配器の幅方向に沿って一列に並ぶように設けられた5個の出力端子21と各出力端子21間を接続する複数の伝送線路22とを有する出力部20と、入力端子10と出力部20とを接続する変成器部30とを備えている。信号分配器1の形状は、入力端子10から見て左右対称である。なお、出力端子21の個数は、奇数である限り限定されることはない。

【0018】

変成器部30は、一端が入力端子10と接続する直線状の伝送線路(第1の1/4波長伝送線路)31と、その伝送線路31の他端に接続された、円弧状の伝送線路(第2の1/4波長伝送線路)32とを備えている。伝送線路31の他端は伝送線路32の中心部と接続しており、伝送線路32の端部(出力部20との接続部)はその中心部から見て入力端子10とは反対方向に配置されている。すなわち、変成器部30は、伝送線路32において二方向に分岐している。伝送線路31の長さ、及び伝送線路32の中心部から端部までの長さは、共に中心周波数(1GHz)の1/4波長であり、それらの幅は互いに等しくなるように設計されている。このように、信号分配器1は2段1/4波長変成器を用いた信号分配器である。

【0019】

図2は、信号分配器1の回路パターンを示す図である。伝送線路22、31及び32はマイクロストリップ線路である。基板厚は0.965mmであり、基板の比誘電率は2.6である。伝送線路の厚さ(銅箔厚)は0.018mmである。図2に示すように、伝送線路部分は、入力端子10から出力端子21にかけての長さが115.4mm、全体幅が59.12mmである。伝送線路31の長さ及び幅は、それぞれ50.04mm、5mmであり、伝送線路32が描く円弧の内径及び外径は、それぞれ24.25mm、29.25mmであり、伝送線路32の幅は5mmである。もっとも、信号分配器1の設計は上記各値に縛られること無く、必要に応じて各寸法を変更してよい。

【0020】

なお、以下では、説明の便宜のため、入力端子10を入力端子#1ともいい、出力端子21を図2の右方から順に出力端子#2,#3,…,#6ともいう(図2参照)。また、出力端子#3及び#4を接続する伝送線路を22a,出力端子#4及び#5を接続する伝送線路を22b,出力端子#2及び#3を接続する伝送線路を22c,出力端子#5及び#6を接続する伝送線路を22dともいう。伝送線路22a及び22bの長さは13.26mmであり、伝送線路22c及び22dの長さは12.54mmである。

【0021】

図3は、信号分配器1の等価回路を一般化したものを示す図である。信号分配器1のような、入力端子から見て左右対称である分配器の等価回路は、その形状の対称性を考慮して図3のように示される。図3の位置P0は出力端子#4に対応し、位置P1は出力端子#3,#5に対応する。図3には現れていないが、位置P2が図2における出力端子#2,6に対応する。

【0022】

入力端子インピーダンス及び出力端子#2〜#6の負荷インピーダンスはZ0(Ω)である。このとき、伝送線路22a,22bの特性インピーダンスZ1は、

Z1=2Z0

で示される。すなわち、入力端子#1の方向から出力端子#4に接続する伝送線路22a及び22bの特性インピーダンスは、出力端子#3の負荷インピーダンスの2倍と等しい。伝送線路22a及び22bの長さL1は信号分配器1では13.26mmであるが、これに限定されずに任意に決定できる。

【0023】

また、伝送線路22c及び22dの特性インピーダンスZ2は、

Z2=2Z0/3

で示される。すなわち、入力端子#1の方向から出力端子#3(#5)に接続する伝送線路22c及び22dの特性インピーダンスは、出力端子#3,#4,#5の合成インピーダンスの2倍と等しい。伝送線路22c及び22dの長さL2は信号分配器1では12.54mmであるが、この長さも任意に決定できる。

【0024】

出力端子21間の伝送線路22の特性インピーダンスを示す一般式は上記式(1)で示される(上記式(5)も同様である)。また、図3における位置Pn(変成器部30と出力部20との接続点)での負荷Zinは上記式(2)で示される(上記式(6)も同様である)。

【0025】

次に、変成器部30を構成する伝送線路31及び伝送線路32の特性インピーダンスZm1,Zm2の決定方法、すなわち変成器部30の決定方法を説明する。なお、2段目の伝送線路である伝送線路32の製作時の特性インピーダンスはZm2であるが、伝送線路32は伝送線路31との接続部から二方向に分かれるため、等価回路上での伝送線路32の特性インピーダンスはZm2/2で示される。

【0026】

図4は、チェビシェフ型2段1/4波長変成器の反射特性を示すグラフであり、縦軸は反射損、横軸は電気長である。比帯域幅をwT=(π−2θm)/(π/2)、通過域(反射損が所定のレベル以下である区間)の下限及び上限の電気長をそれぞれθm,π−θm、無反射となる下側及び上側の電気長をそれぞれθz,π−θzとする。また、θ=0,πにおける反射損をGroとし、通過域内許容反射量をGrmとする。伝送線路31及び32の長さLa,Lbは、それぞれλ0/4(λ0は中心周波数波長)である。

【0027】

まず、インピーダンス比K0L及びK12をそれぞれ以下のように定義する。すなわち、K0Lは、上記位置Pnでの負荷の、入力端子インピーダンスZ0に対する比であり、K12は、伝送線路32の特性インピーダンスの1/2の、伝送線路31の特性インピーダンスに対する比である。

K0L=Zin/Z0,K12=(Zm2/2)/Zm1

【0028】

また、入力端子10から図3における位置Pnへの伝送特性を下記式で定義する。

|S12|2=1/{1+hm2T22(x)}

ただし、T2(x)=2x2−1, x=cosθ/cosθm

【0029】

更に、反射係数の絶対値をρとし、Gro,Grmのそれぞれに対応する反射係数の絶対値をρ0,ρmとすると、値ρmは上記式(3)により示され、値ρ,ρ0はそれぞれ以下のように定義される。

ρ2=1−|S12|2

ρ02={(K0L−1)/(K0L+1)}2

【0030】

θ=θmのときにはρ=ρmとなるので、

hm2=ρm2/(1−ρm2)

【0031】

θ=0又はπのときに

h02=hm2T22(x0), x0=±1/cosθm

とおくと、ρ=ρ0より

h02=ρ02/(1−ρ02)=(K0L−1)2/4K0L

【0032】

θ=θz、すなわち完全整合のときの実部・虚部条件から、下記式と上記式(4)(上記式(8)も同様)が導かれる。

tan2(θz)=K12(K0L−1)/(K0L−K122) …(9)

【0033】

また、完全整合時はT2(x)=0でなければならないので、

【数1】

であり、このとき次式が成立する。

hm2=h02cot4θz

【0034】

上述した一連の理論に基づいて、通過域内許容反射量(又は比帯域幅)に着目した設計方法(以下「第1の設計方法」という)を説明する。

【0035】

まず、許容反射係数ρm、入力端子インピーダンスZ0及び位置Pnでの負荷Zinが与えられた場合には、上記式(3)よりインピーダンス比K12が定まり、更に上記式(4)を用いることで、伝送線路31の特性インピーダンスZm1と伝送線路32の特性インピーダンスZm2とを決定できる。これに加えて、h0,hmよりθz,θmが定まるので、下記式により比帯域幅wTが導かれる。

wT=2−4θm/π

【0036】

また、比帯域幅wT、入力端子インピーダンスZ0及び位置Pnでの負荷Zinが与えられた場合には、θm,θz,h02,hm2,ρmの順に値が定まるので、やはり、伝送線路31の特性インピーダンスZm1と伝送線路32の特性インピーダンスZm2とを決定できる。

【0037】

次に、二つの周波数f1及びf2(f2=uf1)に着目した設計方法(以下「第2の設計方法」という)を説明する。ここでは、周波数f1及びf2で無反射になるとする。参考文献(C.Monzon, "A small dual-frequency transformer in twosections," IEEE Trans. Microwave Theory Tech., vol.51, no.4, pp.1157-1161,Apr. 2003)によれば、伝送線路31及び32の長さLa,Lbは互いに等しくなり、周波数f1,f2での電気長θz1=β1La,θz2=β2Lbについては、θz1+θz2=πが成立する。f2=uf1のときにはθz2=uθz1であるから、θz1=π/(1+u),θz2=uπ/(1+u)となる。これらより下記式が成立する。

La=Lb=λ1/{2(1+u)}

なお、λ1は、無反射となる下側の波長である。u=2であればLa+Lb=λ1/3となり、伝送線路31及び32の全長は、無反射となる下側の周波数に対して1/3波長となる。

【0038】

(La+Lb)/λ1=β1/(β1+β2)=f1/(f1+f2)

であるので、f0=(f1+f2)/2とすると、

La=Lb=λ0/4

となる。

【0039】

したがって、第2の設計方法は、無反射となる下側及び上側の周波数の平均を中心周波数とすると、伝送線路31,32は中心周波数f0に対して1/4波長線路となり、θz=β1La=πf1/2f0によりθzが定まり、結局、第1の設計方法に帰着する。

【0040】

次に、伝送線路31及び32の線路パラメータに着目した設計方法(以下「第3の設計方法」という)を説明する。この場合には、まず、中心周波数f0を設定し、線路パラメータ比K12が与えられるとして上記式(7)を上記式(8)に適用して下記式

Zm12=Z0Zin/K12 …(11)

が得られ、これにより直ちにZm1,Zm2が定まる。

【0041】

また、上記式(3)よりρm2が決定し、通過域内許容反射量Grmが定まる。また、周波数f0に対して1/4波長伝送線路を用いるので、

θz1=0.5π(f1/f0)

θz2=π−θz1=0.5π(f2/f0) …(12)

が導かれ、上記式(9)より、無反射となる下側周波数及び上側周波数が定まり、更に上記式(10)により比帯域幅wTが定まる。このように、線路パラメータにZm2/2=Zm1K12なる条件を与えることで、通過域内許容反射量Grm、無反射となる下側周波数及び上側周波数、並びに比帯域幅wTが一意に定まる。

【0042】

例えば、K12=1/2,Z0=50,Zin=Z0/5とすると、上記式(11)よりZm1=31.62,Zm2=31.62となる。また、K0L=1/5,K12=1/2よりρm2が定まり、Grm=−19.1(dB)となる。更に、上記式(9)よりtan2θz1=8となり、上記式群(12)よりf1/f0=0.784,f2/f0=1.216と定まる。

【0043】

次に、図5〜10を用いて信号分配器1の特性を説明する。ここでは特に、下記の三点について説明する。

(1)入力端子における反射特性を広帯域に亘って向上させること(入力反射特性の広帯域化)

(2)多周波共用(マルチバンド化)の実現

(3)回路製作の容易化

【0044】

まず、図5及び6を用いて、入力反射特性の広帯域化について説明する。図5は信号分配器1及び従来の(特願2006−313003明細書に記載の)信号分配器の反射特性及び分配特性の理論値を示すグラフであり、縦軸はそれら各特性、横軸は規格化周波数である。図6は信号分配器1及び従来の(特願2006−313003明細書に記載の)信号分配器の位相特性の理論値を示すグラフであり、縦軸は位相差、横軸は規格化周波数である。図5では、信号分配器1の反射特性(S11)及び分配特性(S21,S31,S41)を実線で示している。また、1段1/4波長変成器を用いた信号分配器(従来例)の反射特性(S11)及び分配特性(S21,S31,S41)を一点鎖線で示している。

【0045】

なお、SパラメータS21は、入力端子#1から出力端子#2(#6)に流れる信号の分配特性を示し、SパラメータS31は、入力端子#1から出力端子#3(#5)に流れる信号の分配特性を示し、SパラメータS41は、入力端子#1から出力端子#4に流れる信号の分配特性を示す。

【0046】

入力反射特性の広帯域化を実現するに当たっては、入力端子インピーダンスをZ0=50Ω、等価回路上における全体の負荷端インピーダンスをZ0/5とし、通過域における反射損を−20dB以下にするために、伝送線路31の特性インピーダンスをZm1=31.80Ωとし、伝送線路32の特性インピーダンスをZm2=31.45Ω(等価回路上では15.72Ω)とした。なお、反射損−20dBは、マイクロ波信号の分配器において一般的によく使用されている仕様である。

【0047】

この場合、図5に示すように、2段1/4波長変成器を用いた信号分配器1の通過域における周波数領域Daは、1段1/4波長変成器を用いた信号分配器のそれ(Db)よりも拡大されている。すなわち、入力反射特性が広帯域に亘って向上している。また、分配特性についても、信号分配器1の方が従来のものよりも広帯域に亘って一定レベルを保っており、改善されている。一方、位相差については、図6に示すように、位相差Arg(S21/S41)及びArg(S21/S31)共に信号分配器1と従来のものとで変化はなく、線形に推移する。

【0048】

次に、図7を用いて、多周波共用の実現について説明する。図7は信号分配器1の反射特性及び分配特性の理論値を示すグラフであり、縦軸はそれら各特性、横軸は規格化周波数である。図7では、信号分配器1の反射特性(S11)を実線で示し、分配特性(S21,S31,S41)を破線で示している。

【0049】

多周波共用の実現に当たっては、入力端子インピーダンスをZ0=50Ω、等価回路上における全体の負荷端インピーダンスをZ0/5とした。また、無反射となる下側周波数がf1=2/3になり、上側周波数がf2=2f1=4/3になるように、伝送線路31の特性インピーダンスをZm1=28.87Ωとし、伝送線路32の特性インピーダンスをZm2=34.64Ω(等価回路上では17.32Ω)とした。なお、中心周波数をf0=(f1+f2)/2=1としている。

【0050】

この場合、図7に示すように、信号分配器1は二つの周波数f1,f2の信号を無反射で分配できる(マルチバンド化を実現できる)。周波数f1,f2における挿入損S21,S31,S41は−6.99dBである。

【0051】

次に、図8〜10を用いて、回路製作の容易化について説明する。図8は信号分配器1の反射特性(S11)の理論値及び測定値を示すグラフであり、縦軸は反射特性、横軸は周波数である。図9(a)〜(c)は信号分配器1の分配特性(S12,S13,S14)の理論値及び測定値を示すグラフであり、各グラフにおいて縦軸は分配特性、横軸は周波数である。図10は信号分配器1の位相特性の理論値及び測定値を示すグラフであり、縦軸は位相差、横軸は周波数である。なお、図8〜10では、理論値を実線で示し、測定値を破線で示している。

【0052】

製作した信号分配器1の大きさは図2に示すものと同様である。入力端子インピーダンスはZ0=50Ω、等価回路上における全体の負荷端インピーダンスはZ0/5である。このとき、伝送線路22a,22bの特性インピーダンスは100Ωであり、伝送線路22c,22dの特性インピーダンスは33.3Ωである。また、伝送線路31の特性インピーダンスZm1及び伝送線路32の特性インピーダンスZm2は、それぞれ31.62Ωである(等価回路上では、伝送線路32の特性インピーダンスは15.81Ω)。このとき、中心周波数1GHzでの反射損は−19.03dBであった。このように、図2に示すように伝送線路31及び32の線幅を等しくして双方の特性インピーダンスを同じにした場合でも反射損を抑制できるので、入力反射特性の広帯域化を実現する信号分配器1を容易に製作することが可能になる。

【0053】

次に、図11及び12を用いて、実施形態に係る信号分配器の設計方法について説明する。図11は、実施形態に係る信号分配器の設計に用いる情報処理装置40の構成を示す図である。図12は、信号分配器1の設計手順を示すフローチャートである。

【0054】

図1に示されるような信号分配器1の設計は、ワークステーションやPC(Personal Computer)等の情報処理装置40により実行される。情報処理装置40は、中央処理装置(Central Processing Unit:CPU)41と、プログラムやデータを格納するためのハードディスク装置42と、主メモリ43と、キーボードやマウス等の入力装置44と、CRT(Cathode Ray Tube)等の表示装置45と、磁気テープやROM等の記録媒体46を読み取る読取装置47とを含んで構成されている。ハードディスク装置42、主メモリ43、入力装置44、表示装置45、及び読取装置47は、何れも中央処理装置41に接続されている。

【0055】

この情報処理装置40では、プログラムを格納した記録媒体46が読取装置47に装着され、記録媒体46からプログラムが読み出されてハードディスク装置42に格納される。続いて、ハードディスク装置42に格納されたプログラムが、中央処理装置41により主メモリ43上に展開して実行されて、本実施形態に係る信号分配器の設計方法が実行される。なお、本実施形態に係る設計方法は、上記のようにプログラムによるものでなく装置のみで実行されるものであってもよい。また、以下に述べる一連の処理全てが情報処理装置にて実行されるとしてもよいし、一連の処理のうちの一部が情報処理装置にて実行されるとしてもよい。

【0056】

このような情報処理装置40により実行される信号分配器の設計について説明する。まず、入力装置44や読取装置47により、入力端子インピーダンスZ0、出力端子21の個数Nが受け付けられると共に、許容反射係数ρm、上側下側周波数比u又は線路インピーダンス比K12の入力が受け付けられる(ステップS11、受付ステップ)。もちろん、データの受付は、予めハードディスク装置42に記憶されているデータを読み出すことで実現されてもよい。例えば、通過域内許容反射量Grmや比帯域幅wTから算出されてハードディスク装置42に記憶された許容反射係数ρmが受け付けられてもよい。

【0057】

続いて、受け付けられたデータに基づいて、出力端子21間の伝送線路22の特性インピーダンスZkと、変成器部30と出力部20との接続点(図3における位置Pn)での負荷Zinが算出される(ステップS12、第1算出ステップ、第2算出ステップ)。この演算は、上記式(1)及び(2)などを実装したプログラムが中央処理装置41上で実行されることで行われる。

【0058】

続いて、変成器部30を構成する伝送線路31及び32の特性インピーダンスが算出される(ステップS13、第3算出ステップ)。例えば、上記式(3)及び(4)などを実装したプログラムに、入力端子インピーダンスZ0、許容反射係数ρm、負荷Zinを与えることで伝送線路31及び32の特性インピーダンスが算出される。また、上記式(7)及び(8)などを実装したプログラムに、入力端子インピーダンスZ0、線路パラメータ比K12、負荷Zinを与えることで伝送線路31及び32の特性インピーダンスが算出される。更にまた、上記式(9)などを実装したプログラムに入力端子インピーダンスZ0、上側下側周波数比u、負荷Zinを与えることで、θz=π/(1+u)の関係よりK12が定まり、上記算出手順に繋げることができる。

【0059】

そして、上記ステップS12及びS13で算出されたデータが表示装置45やハードディスク装置42などに出力される(ステップS14、出力ステップ)。これにより、情報処理装置40の利用者は、信号分配器の構成を決定する各伝送線路の特性インピーダンスを取得できる。

【0060】

以上説明したように、本実施形態によれば、変成器部30が、複数の1/4波長伝送線路31,32が直列に接続された多段変成器であるので、1段変成器の場合と比較して、入力端子10における反射損が広帯域に亘って低減される(入力端子における反射特性(入力反射特性)が広帯域に亘って向上する)。また、各出力端子21について、入力端子10の方向から一の出力端子21に接続する伝送線路22の特性インピーダンスが、その伝送線路22よりも入力端子10から離れる方向に位置する一以上の出力端子21の合成インピーダンスと等しくなるように、出力端子21間の伝送線路22を設けることで、出力端子21間の伝送線路22の長さを任意に選択できる。その結果、出力端子21間の伝送線路長を短くして回路を小型化できる。すなわち、信号分配器1によれば、回路の小型化を実現すると共に、入力端子10における反射特性を広帯域に亘って向上させることが可能となる。

【0061】

また、本実施形態によれば、変成器部30を構成する伝送線路31及び32の線幅を一定にしてもよい。この場合、信号分配器1を容易に製作できる。

【0062】

また、本実施形態によれば、入力端子インピーダンスZ0及び出力端子の個数Nと共に、許容反射係数ρm、上側下側周波数比u又は線路パラメータ比K12を入力することにより、信号分配器1を構成する各伝送線路の特性インピーダンスを算出できる。すなわち、回路の小型化を実現すると共に製作の容易化や2周波対応回路の実現が図られ、あるいはまた、入力端子における反射特性を広帯域に亘って向上させることが可能な信号分配器を設計できる。

【0063】

以上、本発明をその実施形態に基づいて詳細に説明した。しかし、本発明は上記実施形態に限定されるものではない。本発明は、その要旨を逸脱しない範囲で以下のような様々な変形が可能である。

【0064】

上記実施形態では、信号分配器1が2段1/4波長変成器(変成器部30)を備えていたが、互いに異なる線路パラメータを有する3以上の伝送線路を多段接続して変成器部を構成してもよい。例えば、図13に示すように、信号分配器が3種の伝送線路を有する変成器部を備えてもよい。図13に示す信号分配器2は、入力端子#11と5個の出力端子#12〜#16とを備え、変成器部50は、一端が入力端子#11と接続する直線状の伝送線路51と、一端がその伝送線路51の他端に接続し伝送線路51と同じ方向に延びる直線状の伝送線路52と、その伝送線路52の他端に接続された円弧状の伝送線路53とを備えている。伝送線路51〜53の特性インピーダンスは、それぞれ33.27Ω、22.36Ω、30.06Ωと設定した。また、下側周波数f1における伝送線路51〜53の電気角は、それぞれ1.13,0.44,1.13と設定した。

【0065】

図14は、信号分配器2の反射特性S11及び分配特性S21,S31,S41を示すグラフであり、縦軸は反射特性及び分配特性、横軸は規格化周波数である。図14に示すように、信号分配器2では、周波数f1,f2=1.4f1,f3=3f1に対するマルチバンド化を実現できる。これに対して、半波長線路を構成要素とする従来の信号分配器(下記参考文献1〜4参照)は、単一周波数対応の半波長線路のインピーダンス無変換機能を使っているため、複数の周波数で無反射と成る回路には向かない。

(参考文献1)I.Sakagami,T.Wuren, M.Fujii and Y.Tomoda, "A new type of multi-way microwave powerdivider based on bagley polygon power divider," 2006 Asia-PacificMicrowave Conf., Vol.2, pp.1353-1356, Yokohama, Japan (Dec.2006)

(参考文献2)http://www.dec2light.pwp.blueyonder.co.uk/Webpage/Hybridcouplers.htm#baglay

(参考文献3)田原、枡田、佐々木、大橋、“プローブ結合部にアイリスを設けた導波管直列電力分配器” 2006年電子情報通信学会エレクトロニクスソサイエティ大会、C-2-39、p.58、2006

(参考文献4)安部、田原、米田、大橋、“基盤を用いた狭壁面プローブ挿入型導波管電力分配器” 電子情報通信学会技術研究報告、MW2007-131、pp.29-34、Dec.2007

【0066】

なお、図13に示す信号分配器2では、伝送線路53が伝送線路52との接続点から二方向に分岐しているが、伝送線路52から二方向に分岐するように変成器部を設計してもよい。

【図面の簡単な説明】

【0067】

【図1】実施形態に係る信号分配器の平面図である。

【図2】図1に示す信号分配器の回路パターンを示す図である。

【図3】信号分配器の等価回路を一般化したものを示す図である。

【図4】チェビシェフ型2段1/4波長変成器の反射特性を示すグラフである。

【図5】信号分配器と従来のものとで反射特性及び分配特性を比較するためのグラフである。

【図6】信号分配器と従来のものとで位相特性を比較するためのグラフである。

【図7】2周波対応信号分配器の反射特性及び分配特性の理論値を示すグラフである。

【図8】信号分配器の反射特性の理論値及び測定値を示すグラフである。

【図9】信号分配器の分配特性の理論値及び測定値を示すグラフである。

【図10】信号分配器の位相特性の理論値及び測定値を示すグラフである。

【図11】情報処理装置の構成を示す図である。

【図12】図11に示す情報処理装置による信号分配器の設計手順を示すフローチャートである。

【図13】変形例に係る信号分配器の回路パターンを示す図である。

【図14】図13に示す3周波対応信号分配器の反射特性及び分配特性の理論値を示すグラフである。

【符号の説明】

【0068】

1,2…信号分配器、10…入力端子、20…出力部、21…出力端子、22…出力端子間を接続する伝送線路、30,50…変成器部、31…伝送線路(第1の1/4波長伝送線路)、32…伝送線路(第2の1/4波長伝送線路)、40…情報処理装置、51〜53…伝送線路(1/4波長伝送線路)。

【技術分野】

【0001】

本発明は、マイクロ波信号を分配する信号分配器及びその設計方法に関する。

【背景技術】

【0002】

マイクロ波ミリ波信号をN方向に分配する回路としてウィルキンソン電力分配器が良く知られている(下記非特許文献1参照)。ウィルキンソン電力分配器では、どの入出力端子から見ても整合が取れており、出力端子間のアイソレーションも取れている。しかしながら、3方向以上に分配する場合には回路が立体構造になるので、回路を平面状に構成したり集積回路を製作したりすることは困難である。この課題を解決する技術として、下記特許文献1に記載の電力合成器及び電力分配器が知られている。

【0003】

入力信号を分配する際には、入力信号に対して反射成分を生じないことが要求される。平面構成の回路でこの要求を満たすものとして、下記非特許文献2及び3に記載の変成器付き多分配回路や、下記非特許文献4に記載のバグレー・ポリゴン電力分配器が知られている。また、基板の裏面から同軸ケーブルにより給電し、基板の表面上で放射状に信号を多分配する回路も知られている(下記非特許文献5)。

【0004】

入力信号を2n+1分割(nは整数)する従来のバグレー・ポリゴン電力分配器では、隣り合う出力端子間の伝送路長が半波長と決まっているので、回路が大型化する傾向があった。この点を改善するものとして、特願2006−313003号明細書に記載の電力分配器がある。この電力分配器により回路の小型化が実現できると共に分配特性を改善できる。

【非特許文献1】http://www.microwaves101.com/encyclopedia/wilkinson_nway.cfm

【非特許文献2】M. Kishihara, K. Yamane and I.Ohta,“Design of broadband microstrip-type multi-waypower dividers”、Asia-Pacific Microwave Conference, Proc., vol.3, pp.1688-1691, Nov.2003.

【非特許文献3】M. Kishihara, K. Yamane and I.Ohta,“DParallel processing of powell’s optimization algorithmand its application to design of multi-way power dividers,” Asia-Pacific MicrowaveConference, Proc., 2005.

【非特許文献4】http://www.dc2light.pwp.blueyonder.co.uk/Webpage/Hybridcouplers.htm#bagley

【非特許文献5】E.L.Holzman, “An eiginvalue equation analysis of a symmetrical coax line to N-waywaveguide power divider, “ IEEE Trans. on MTT, Vol.42, No7, July 1994.

【特許文献1】特開平9−289405号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特願2006−313003明細書に記載の電力分配器では、入力端子における反射損が所定のレベル以下である帯域(入力端子における反射特性が良い帯域)が狭い。

【0006】

本発明は、上記課題を解決するためになされたものであり、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることが可能な信号分配器及びその設計方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の信号分配器は、複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、等価回路において多段に直列接続する複数の1/4波長伝送線路により入力端子と出力部とを接続する変成器部と、を備え、等価回路における複数の出力端子のそれぞれについて、入力端子の方向から一の出力端子に接続する伝送線路の特性インピーダンスと、該一の出力端子を含む、該伝送線路よりも入力端子から離れる方向に位置する一以上の出力端子の合成インピーダンスとが等しい、ことを特徴とする。

【0008】

このような信号分配器によれば、変成器部が、複数の1/4波長伝送線路が直列に接続された多段変成器であるので、1段変成器の場合と比較して、入力端子における反射損が広帯域に亘って低減される(入力端子における反射特性(入力反射特性)が広帯域に亘って向上する)。また、各出力端子について、入力端子の方向から一の出力端子に接続する伝送線路の特性インピーダンスが、その伝送線路よりも入力端子から離れる方向に位置する一以上の出力端子の合成インピーダンスと等しくなるように、出力端子間の伝送線路を設けることで、出力端子間の伝送線路の長さを任意に選択できる。その結果、出力端子間の伝送線路長を短くして回路を小型化できる。すなわち、このような信号分配器により、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることが可能となる。

【0009】

本発明の信号分配器では、変成器部が、一端が入力端子と接続する第1の1/4波長伝送線路と、該第1の1/4波長伝送線路の他端と出力部とを接続する第2の1/4波長伝送線路とを有する2段変成器であり、第1の1/4波長伝送線路及び第2の1/4波長伝送線路の線幅が互いに等しいことが好ましい。

【0010】

この場合、変成器部を構成する1/4波長伝送線路の線幅が一定であるので、信号分配器を容易に製作することが可能になる。

【0011】

本発明の信号分配器の設計方法は、複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、入力端子と出力部とを接続する変成器部とを備える信号分配器を設計する情報処理装置における、信号分配器の設計方法であって、入力端子での入力端子インピーダンス、出力端子の個数、及び信号分配器の通過域内許容反射量に対応する許容反射係数の入力を受け付ける受付ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(1)

Z1=2Z0,Z2=2Z0/3,…,Zk=2Z0/(N−2) …(1)

ただし、k=(N−1)/2

(式中、Z0は入力端子インピーダンスを表し、Nは出力端子の個数を表す。)

により、各出力端子間を接続する複数の伝送線路の特性インピーダンスZkを算出する第1算出ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(2)

Zin=Z0/(2n+1) …(2)

ただし、n=(N−1)/2

(式中、Z0は入力端子インピーダンスを表し、Nは出力端子の個数を表す。)

により、変成器部と出力部との接続点における負荷Zinを算出する第2算出ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び許容反射係数と、第2算出ステップにおいて算出された負荷とに基づいて、下記式(3)及び(4)

ρm2={(K0L−K122)/(K0L+K122)}2 …(3)

(式中、ρmは許容反射係数を表し、K0Lは負荷と入力端子インピーダンスとの比を表し、K12は変成器部を構成する第1の1/4波長伝送線路の特性インピーダンスと第2の1/4波長伝送線路の特性インピーダンスの1/2との比を表す。すなわち、K0L=Zin/Z0,K12=(Zm2/2)/Zm1)

Zm1(Zm2/2)=Z0Zin …(4)

(式中、Z0は入力端子インピーダンスを表し、Zinは負荷を表す。)

により、第1の1/4波長伝送線路の特性インピーダンスZm1と第2の1/4波長伝送線路の特性インピーダンスZm2とを算出する第3算出ステップと、第1算出ステップ及び第3算出ステップにおいて算出された特性インピーダンスを出力する出力ステップと、を含むことを特徴とする。

【0012】

このような信号分配器の設計方法によれば、入力端子での入力端子インピーダンス、出力端子の個数、及び信号分配器の通過域内許容反射量に対応する許容反射係数を入力することにより、上記信号分配器を構成する各伝送線路の特性インピーダンスを算出できる。すなわち、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることが可能な信号分配器を設計できる。

【0013】

本発明の信号分配器の設計方法は、複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、入力端子と出力部とを接続する変成器部とを備える信号分配器を設計する情報処理装置における、信号分配器の設計方法であって、入力端子での入力端子インピーダンス、出力端子の個数、及び線路パラメータ比の入力を受け付ける受付ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(5)

Z1=2Z0,Z2=2Z0/3,…,Zk=2Z0/(N−2) …(5)

ただし、k=(N−1)/2

(式中、Z0は入力端子インピーダンスを表し、Nは出力端子の個数を表す。)

により、各出力端子間を接続する複数の伝送線路の特性インピーダンスZkを算出する第1算出ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(6)

Zin=Z0/(2n+1) …(6)

ただし、n=(N−1)/2

(式中、Z0は入力端子インピーダンスを表し、Nは出力端子の個数を表す。)

により、変成器部と出力部との接続点における負荷Zinを算出する第2算出ステップと、受付ステップにおいて受け付けられた入力端子インピーダンス及び線路パラメータ比と、第2算出ステップにおいて算出された負荷とに基づいて、下記式(7)及び(8)

(Zm2/2)=K12Zm1 …(7)

(式中、K12は線路パラメータ比を表す。)

Zm1(Zm2/2)=Z0Zin …(8)

(式中、Z0は入力端子インピーダンスを表し、Zinは負荷を表す。)

により、第1の1/4波長伝送線路の特性インピーダンスZm1と第2の1/4波長伝送線路の特性インピーダンスZm2とを算出する第3算出ステップと、第1算出ステップ及び第3算出ステップにおいて算出された特性インピーダンスを出力する出力ステップと、を含むことを特徴とする。

【0014】

このような信号分配器の設計方法によれば、入力端子での入力端子インピーダンス、出力端子の個数、及び線路パラメータ比を入力することにより、上記信号分配器を構成する各伝送線路の特性インピーダンスを算出できる。すなわち、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることができ、且つ、第1の1/4波長伝送線路の幅と第2の1/4波長伝送線路の幅とが等しい信号分配器を設計できる。

【発明の効果】

【0015】

このような信号分配器及びその設計方法によれば、多段変成器が導入されると共に、出力端子間の伝送線路の長さではなくその特性インピーダンスが指定されるので、回路の小型化を実現すると共に、入力端子における反射特性を広帯域に亘って向上させることが可能になる。

【発明を実施するための最良の形態】

【0016】

以下、添付図面を参照しながら本発明の実施形態を詳細に説明する。なお、図面の説明において同一又は同等の要素には同一の符号を付し、重複する説明を省略する。

【0017】

まず、図1を用いて、実施形態に係る信号分配器1の構成を説明する。図1は、実施形態に係る信号分配器1の平面図である。信号分配器1は、マイクロ波信号が入力される入力端子10と、信号分配器の幅方向に沿って一列に並ぶように設けられた5個の出力端子21と各出力端子21間を接続する複数の伝送線路22とを有する出力部20と、入力端子10と出力部20とを接続する変成器部30とを備えている。信号分配器1の形状は、入力端子10から見て左右対称である。なお、出力端子21の個数は、奇数である限り限定されることはない。

【0018】

変成器部30は、一端が入力端子10と接続する直線状の伝送線路(第1の1/4波長伝送線路)31と、その伝送線路31の他端に接続された、円弧状の伝送線路(第2の1/4波長伝送線路)32とを備えている。伝送線路31の他端は伝送線路32の中心部と接続しており、伝送線路32の端部(出力部20との接続部)はその中心部から見て入力端子10とは反対方向に配置されている。すなわち、変成器部30は、伝送線路32において二方向に分岐している。伝送線路31の長さ、及び伝送線路32の中心部から端部までの長さは、共に中心周波数(1GHz)の1/4波長であり、それらの幅は互いに等しくなるように設計されている。このように、信号分配器1は2段1/4波長変成器を用いた信号分配器である。

【0019】

図2は、信号分配器1の回路パターンを示す図である。伝送線路22、31及び32はマイクロストリップ線路である。基板厚は0.965mmであり、基板の比誘電率は2.6である。伝送線路の厚さ(銅箔厚)は0.018mmである。図2に示すように、伝送線路部分は、入力端子10から出力端子21にかけての長さが115.4mm、全体幅が59.12mmである。伝送線路31の長さ及び幅は、それぞれ50.04mm、5mmであり、伝送線路32が描く円弧の内径及び外径は、それぞれ24.25mm、29.25mmであり、伝送線路32の幅は5mmである。もっとも、信号分配器1の設計は上記各値に縛られること無く、必要に応じて各寸法を変更してよい。

【0020】

なお、以下では、説明の便宜のため、入力端子10を入力端子#1ともいい、出力端子21を図2の右方から順に出力端子#2,#3,…,#6ともいう(図2参照)。また、出力端子#3及び#4を接続する伝送線路を22a,出力端子#4及び#5を接続する伝送線路を22b,出力端子#2及び#3を接続する伝送線路を22c,出力端子#5及び#6を接続する伝送線路を22dともいう。伝送線路22a及び22bの長さは13.26mmであり、伝送線路22c及び22dの長さは12.54mmである。

【0021】

図3は、信号分配器1の等価回路を一般化したものを示す図である。信号分配器1のような、入力端子から見て左右対称である分配器の等価回路は、その形状の対称性を考慮して図3のように示される。図3の位置P0は出力端子#4に対応し、位置P1は出力端子#3,#5に対応する。図3には現れていないが、位置P2が図2における出力端子#2,6に対応する。

【0022】

入力端子インピーダンス及び出力端子#2〜#6の負荷インピーダンスはZ0(Ω)である。このとき、伝送線路22a,22bの特性インピーダンスZ1は、

Z1=2Z0

で示される。すなわち、入力端子#1の方向から出力端子#4に接続する伝送線路22a及び22bの特性インピーダンスは、出力端子#3の負荷インピーダンスの2倍と等しい。伝送線路22a及び22bの長さL1は信号分配器1では13.26mmであるが、これに限定されずに任意に決定できる。

【0023】

また、伝送線路22c及び22dの特性インピーダンスZ2は、

Z2=2Z0/3

で示される。すなわち、入力端子#1の方向から出力端子#3(#5)に接続する伝送線路22c及び22dの特性インピーダンスは、出力端子#3,#4,#5の合成インピーダンスの2倍と等しい。伝送線路22c及び22dの長さL2は信号分配器1では12.54mmであるが、この長さも任意に決定できる。

【0024】

出力端子21間の伝送線路22の特性インピーダンスを示す一般式は上記式(1)で示される(上記式(5)も同様である)。また、図3における位置Pn(変成器部30と出力部20との接続点)での負荷Zinは上記式(2)で示される(上記式(6)も同様である)。

【0025】

次に、変成器部30を構成する伝送線路31及び伝送線路32の特性インピーダンスZm1,Zm2の決定方法、すなわち変成器部30の決定方法を説明する。なお、2段目の伝送線路である伝送線路32の製作時の特性インピーダンスはZm2であるが、伝送線路32は伝送線路31との接続部から二方向に分かれるため、等価回路上での伝送線路32の特性インピーダンスはZm2/2で示される。

【0026】

図4は、チェビシェフ型2段1/4波長変成器の反射特性を示すグラフであり、縦軸は反射損、横軸は電気長である。比帯域幅をwT=(π−2θm)/(π/2)、通過域(反射損が所定のレベル以下である区間)の下限及び上限の電気長をそれぞれθm,π−θm、無反射となる下側及び上側の電気長をそれぞれθz,π−θzとする。また、θ=0,πにおける反射損をGroとし、通過域内許容反射量をGrmとする。伝送線路31及び32の長さLa,Lbは、それぞれλ0/4(λ0は中心周波数波長)である。

【0027】

まず、インピーダンス比K0L及びK12をそれぞれ以下のように定義する。すなわち、K0Lは、上記位置Pnでの負荷の、入力端子インピーダンスZ0に対する比であり、K12は、伝送線路32の特性インピーダンスの1/2の、伝送線路31の特性インピーダンスに対する比である。

K0L=Zin/Z0,K12=(Zm2/2)/Zm1

【0028】

また、入力端子10から図3における位置Pnへの伝送特性を下記式で定義する。

|S12|2=1/{1+hm2T22(x)}

ただし、T2(x)=2x2−1, x=cosθ/cosθm

【0029】

更に、反射係数の絶対値をρとし、Gro,Grmのそれぞれに対応する反射係数の絶対値をρ0,ρmとすると、値ρmは上記式(3)により示され、値ρ,ρ0はそれぞれ以下のように定義される。

ρ2=1−|S12|2

ρ02={(K0L−1)/(K0L+1)}2

【0030】

θ=θmのときにはρ=ρmとなるので、

hm2=ρm2/(1−ρm2)

【0031】

θ=0又はπのときに

h02=hm2T22(x0), x0=±1/cosθm

とおくと、ρ=ρ0より

h02=ρ02/(1−ρ02)=(K0L−1)2/4K0L

【0032】

θ=θz、すなわち完全整合のときの実部・虚部条件から、下記式と上記式(4)(上記式(8)も同様)が導かれる。

tan2(θz)=K12(K0L−1)/(K0L−K122) …(9)

【0033】

また、完全整合時はT2(x)=0でなければならないので、

【数1】

であり、このとき次式が成立する。

hm2=h02cot4θz

【0034】

上述した一連の理論に基づいて、通過域内許容反射量(又は比帯域幅)に着目した設計方法(以下「第1の設計方法」という)を説明する。

【0035】

まず、許容反射係数ρm、入力端子インピーダンスZ0及び位置Pnでの負荷Zinが与えられた場合には、上記式(3)よりインピーダンス比K12が定まり、更に上記式(4)を用いることで、伝送線路31の特性インピーダンスZm1と伝送線路32の特性インピーダンスZm2とを決定できる。これに加えて、h0,hmよりθz,θmが定まるので、下記式により比帯域幅wTが導かれる。

wT=2−4θm/π

【0036】

また、比帯域幅wT、入力端子インピーダンスZ0及び位置Pnでの負荷Zinが与えられた場合には、θm,θz,h02,hm2,ρmの順に値が定まるので、やはり、伝送線路31の特性インピーダンスZm1と伝送線路32の特性インピーダンスZm2とを決定できる。

【0037】

次に、二つの周波数f1及びf2(f2=uf1)に着目した設計方法(以下「第2の設計方法」という)を説明する。ここでは、周波数f1及びf2で無反射になるとする。参考文献(C.Monzon, "A small dual-frequency transformer in twosections," IEEE Trans. Microwave Theory Tech., vol.51, no.4, pp.1157-1161,Apr. 2003)によれば、伝送線路31及び32の長さLa,Lbは互いに等しくなり、周波数f1,f2での電気長θz1=β1La,θz2=β2Lbについては、θz1+θz2=πが成立する。f2=uf1のときにはθz2=uθz1であるから、θz1=π/(1+u),θz2=uπ/(1+u)となる。これらより下記式が成立する。

La=Lb=λ1/{2(1+u)}

なお、λ1は、無反射となる下側の波長である。u=2であればLa+Lb=λ1/3となり、伝送線路31及び32の全長は、無反射となる下側の周波数に対して1/3波長となる。

【0038】

(La+Lb)/λ1=β1/(β1+β2)=f1/(f1+f2)

であるので、f0=(f1+f2)/2とすると、

La=Lb=λ0/4

となる。

【0039】

したがって、第2の設計方法は、無反射となる下側及び上側の周波数の平均を中心周波数とすると、伝送線路31,32は中心周波数f0に対して1/4波長線路となり、θz=β1La=πf1/2f0によりθzが定まり、結局、第1の設計方法に帰着する。

【0040】

次に、伝送線路31及び32の線路パラメータに着目した設計方法(以下「第3の設計方法」という)を説明する。この場合には、まず、中心周波数f0を設定し、線路パラメータ比K12が与えられるとして上記式(7)を上記式(8)に適用して下記式

Zm12=Z0Zin/K12 …(11)

が得られ、これにより直ちにZm1,Zm2が定まる。

【0041】

また、上記式(3)よりρm2が決定し、通過域内許容反射量Grmが定まる。また、周波数f0に対して1/4波長伝送線路を用いるので、

θz1=0.5π(f1/f0)

θz2=π−θz1=0.5π(f2/f0) …(12)

が導かれ、上記式(9)より、無反射となる下側周波数及び上側周波数が定まり、更に上記式(10)により比帯域幅wTが定まる。このように、線路パラメータにZm2/2=Zm1K12なる条件を与えることで、通過域内許容反射量Grm、無反射となる下側周波数及び上側周波数、並びに比帯域幅wTが一意に定まる。

【0042】

例えば、K12=1/2,Z0=50,Zin=Z0/5とすると、上記式(11)よりZm1=31.62,Zm2=31.62となる。また、K0L=1/5,K12=1/2よりρm2が定まり、Grm=−19.1(dB)となる。更に、上記式(9)よりtan2θz1=8となり、上記式群(12)よりf1/f0=0.784,f2/f0=1.216と定まる。

【0043】

次に、図5〜10を用いて信号分配器1の特性を説明する。ここでは特に、下記の三点について説明する。

(1)入力端子における反射特性を広帯域に亘って向上させること(入力反射特性の広帯域化)

(2)多周波共用(マルチバンド化)の実現

(3)回路製作の容易化

【0044】

まず、図5及び6を用いて、入力反射特性の広帯域化について説明する。図5は信号分配器1及び従来の(特願2006−313003明細書に記載の)信号分配器の反射特性及び分配特性の理論値を示すグラフであり、縦軸はそれら各特性、横軸は規格化周波数である。図6は信号分配器1及び従来の(特願2006−313003明細書に記載の)信号分配器の位相特性の理論値を示すグラフであり、縦軸は位相差、横軸は規格化周波数である。図5では、信号分配器1の反射特性(S11)及び分配特性(S21,S31,S41)を実線で示している。また、1段1/4波長変成器を用いた信号分配器(従来例)の反射特性(S11)及び分配特性(S21,S31,S41)を一点鎖線で示している。

【0045】

なお、SパラメータS21は、入力端子#1から出力端子#2(#6)に流れる信号の分配特性を示し、SパラメータS31は、入力端子#1から出力端子#3(#5)に流れる信号の分配特性を示し、SパラメータS41は、入力端子#1から出力端子#4に流れる信号の分配特性を示す。

【0046】

入力反射特性の広帯域化を実現するに当たっては、入力端子インピーダンスをZ0=50Ω、等価回路上における全体の負荷端インピーダンスをZ0/5とし、通過域における反射損を−20dB以下にするために、伝送線路31の特性インピーダンスをZm1=31.80Ωとし、伝送線路32の特性インピーダンスをZm2=31.45Ω(等価回路上では15.72Ω)とした。なお、反射損−20dBは、マイクロ波信号の分配器において一般的によく使用されている仕様である。

【0047】

この場合、図5に示すように、2段1/4波長変成器を用いた信号分配器1の通過域における周波数領域Daは、1段1/4波長変成器を用いた信号分配器のそれ(Db)よりも拡大されている。すなわち、入力反射特性が広帯域に亘って向上している。また、分配特性についても、信号分配器1の方が従来のものよりも広帯域に亘って一定レベルを保っており、改善されている。一方、位相差については、図6に示すように、位相差Arg(S21/S41)及びArg(S21/S31)共に信号分配器1と従来のものとで変化はなく、線形に推移する。

【0048】

次に、図7を用いて、多周波共用の実現について説明する。図7は信号分配器1の反射特性及び分配特性の理論値を示すグラフであり、縦軸はそれら各特性、横軸は規格化周波数である。図7では、信号分配器1の反射特性(S11)を実線で示し、分配特性(S21,S31,S41)を破線で示している。

【0049】

多周波共用の実現に当たっては、入力端子インピーダンスをZ0=50Ω、等価回路上における全体の負荷端インピーダンスをZ0/5とした。また、無反射となる下側周波数がf1=2/3になり、上側周波数がf2=2f1=4/3になるように、伝送線路31の特性インピーダンスをZm1=28.87Ωとし、伝送線路32の特性インピーダンスをZm2=34.64Ω(等価回路上では17.32Ω)とした。なお、中心周波数をf0=(f1+f2)/2=1としている。

【0050】

この場合、図7に示すように、信号分配器1は二つの周波数f1,f2の信号を無反射で分配できる(マルチバンド化を実現できる)。周波数f1,f2における挿入損S21,S31,S41は−6.99dBである。

【0051】

次に、図8〜10を用いて、回路製作の容易化について説明する。図8は信号分配器1の反射特性(S11)の理論値及び測定値を示すグラフであり、縦軸は反射特性、横軸は周波数である。図9(a)〜(c)は信号分配器1の分配特性(S12,S13,S14)の理論値及び測定値を示すグラフであり、各グラフにおいて縦軸は分配特性、横軸は周波数である。図10は信号分配器1の位相特性の理論値及び測定値を示すグラフであり、縦軸は位相差、横軸は周波数である。なお、図8〜10では、理論値を実線で示し、測定値を破線で示している。

【0052】

製作した信号分配器1の大きさは図2に示すものと同様である。入力端子インピーダンスはZ0=50Ω、等価回路上における全体の負荷端インピーダンスはZ0/5である。このとき、伝送線路22a,22bの特性インピーダンスは100Ωであり、伝送線路22c,22dの特性インピーダンスは33.3Ωである。また、伝送線路31の特性インピーダンスZm1及び伝送線路32の特性インピーダンスZm2は、それぞれ31.62Ωである(等価回路上では、伝送線路32の特性インピーダンスは15.81Ω)。このとき、中心周波数1GHzでの反射損は−19.03dBであった。このように、図2に示すように伝送線路31及び32の線幅を等しくして双方の特性インピーダンスを同じにした場合でも反射損を抑制できるので、入力反射特性の広帯域化を実現する信号分配器1を容易に製作することが可能になる。

【0053】

次に、図11及び12を用いて、実施形態に係る信号分配器の設計方法について説明する。図11は、実施形態に係る信号分配器の設計に用いる情報処理装置40の構成を示す図である。図12は、信号分配器1の設計手順を示すフローチャートである。

【0054】

図1に示されるような信号分配器1の設計は、ワークステーションやPC(Personal Computer)等の情報処理装置40により実行される。情報処理装置40は、中央処理装置(Central Processing Unit:CPU)41と、プログラムやデータを格納するためのハードディスク装置42と、主メモリ43と、キーボードやマウス等の入力装置44と、CRT(Cathode Ray Tube)等の表示装置45と、磁気テープやROM等の記録媒体46を読み取る読取装置47とを含んで構成されている。ハードディスク装置42、主メモリ43、入力装置44、表示装置45、及び読取装置47は、何れも中央処理装置41に接続されている。

【0055】

この情報処理装置40では、プログラムを格納した記録媒体46が読取装置47に装着され、記録媒体46からプログラムが読み出されてハードディスク装置42に格納される。続いて、ハードディスク装置42に格納されたプログラムが、中央処理装置41により主メモリ43上に展開して実行されて、本実施形態に係る信号分配器の設計方法が実行される。なお、本実施形態に係る設計方法は、上記のようにプログラムによるものでなく装置のみで実行されるものであってもよい。また、以下に述べる一連の処理全てが情報処理装置にて実行されるとしてもよいし、一連の処理のうちの一部が情報処理装置にて実行されるとしてもよい。

【0056】

このような情報処理装置40により実行される信号分配器の設計について説明する。まず、入力装置44や読取装置47により、入力端子インピーダンスZ0、出力端子21の個数Nが受け付けられると共に、許容反射係数ρm、上側下側周波数比u又は線路インピーダンス比K12の入力が受け付けられる(ステップS11、受付ステップ)。もちろん、データの受付は、予めハードディスク装置42に記憶されているデータを読み出すことで実現されてもよい。例えば、通過域内許容反射量Grmや比帯域幅wTから算出されてハードディスク装置42に記憶された許容反射係数ρmが受け付けられてもよい。

【0057】

続いて、受け付けられたデータに基づいて、出力端子21間の伝送線路22の特性インピーダンスZkと、変成器部30と出力部20との接続点(図3における位置Pn)での負荷Zinが算出される(ステップS12、第1算出ステップ、第2算出ステップ)。この演算は、上記式(1)及び(2)などを実装したプログラムが中央処理装置41上で実行されることで行われる。

【0058】

続いて、変成器部30を構成する伝送線路31及び32の特性インピーダンスが算出される(ステップS13、第3算出ステップ)。例えば、上記式(3)及び(4)などを実装したプログラムに、入力端子インピーダンスZ0、許容反射係数ρm、負荷Zinを与えることで伝送線路31及び32の特性インピーダンスが算出される。また、上記式(7)及び(8)などを実装したプログラムに、入力端子インピーダンスZ0、線路パラメータ比K12、負荷Zinを与えることで伝送線路31及び32の特性インピーダンスが算出される。更にまた、上記式(9)などを実装したプログラムに入力端子インピーダンスZ0、上側下側周波数比u、負荷Zinを与えることで、θz=π/(1+u)の関係よりK12が定まり、上記算出手順に繋げることができる。

【0059】

そして、上記ステップS12及びS13で算出されたデータが表示装置45やハードディスク装置42などに出力される(ステップS14、出力ステップ)。これにより、情報処理装置40の利用者は、信号分配器の構成を決定する各伝送線路の特性インピーダンスを取得できる。

【0060】

以上説明したように、本実施形態によれば、変成器部30が、複数の1/4波長伝送線路31,32が直列に接続された多段変成器であるので、1段変成器の場合と比較して、入力端子10における反射損が広帯域に亘って低減される(入力端子における反射特性(入力反射特性)が広帯域に亘って向上する)。また、各出力端子21について、入力端子10の方向から一の出力端子21に接続する伝送線路22の特性インピーダンスが、その伝送線路22よりも入力端子10から離れる方向に位置する一以上の出力端子21の合成インピーダンスと等しくなるように、出力端子21間の伝送線路22を設けることで、出力端子21間の伝送線路22の長さを任意に選択できる。その結果、出力端子21間の伝送線路長を短くして回路を小型化できる。すなわち、信号分配器1によれば、回路の小型化を実現すると共に、入力端子10における反射特性を広帯域に亘って向上させることが可能となる。

【0061】

また、本実施形態によれば、変成器部30を構成する伝送線路31及び32の線幅を一定にしてもよい。この場合、信号分配器1を容易に製作できる。

【0062】

また、本実施形態によれば、入力端子インピーダンスZ0及び出力端子の個数Nと共に、許容反射係数ρm、上側下側周波数比u又は線路パラメータ比K12を入力することにより、信号分配器1を構成する各伝送線路の特性インピーダンスを算出できる。すなわち、回路の小型化を実現すると共に製作の容易化や2周波対応回路の実現が図られ、あるいはまた、入力端子における反射特性を広帯域に亘って向上させることが可能な信号分配器を設計できる。

【0063】

以上、本発明をその実施形態に基づいて詳細に説明した。しかし、本発明は上記実施形態に限定されるものではない。本発明は、その要旨を逸脱しない範囲で以下のような様々な変形が可能である。

【0064】

上記実施形態では、信号分配器1が2段1/4波長変成器(変成器部30)を備えていたが、互いに異なる線路パラメータを有する3以上の伝送線路を多段接続して変成器部を構成してもよい。例えば、図13に示すように、信号分配器が3種の伝送線路を有する変成器部を備えてもよい。図13に示す信号分配器2は、入力端子#11と5個の出力端子#12〜#16とを備え、変成器部50は、一端が入力端子#11と接続する直線状の伝送線路51と、一端がその伝送線路51の他端に接続し伝送線路51と同じ方向に延びる直線状の伝送線路52と、その伝送線路52の他端に接続された円弧状の伝送線路53とを備えている。伝送線路51〜53の特性インピーダンスは、それぞれ33.27Ω、22.36Ω、30.06Ωと設定した。また、下側周波数f1における伝送線路51〜53の電気角は、それぞれ1.13,0.44,1.13と設定した。

【0065】

図14は、信号分配器2の反射特性S11及び分配特性S21,S31,S41を示すグラフであり、縦軸は反射特性及び分配特性、横軸は規格化周波数である。図14に示すように、信号分配器2では、周波数f1,f2=1.4f1,f3=3f1に対するマルチバンド化を実現できる。これに対して、半波長線路を構成要素とする従来の信号分配器(下記参考文献1〜4参照)は、単一周波数対応の半波長線路のインピーダンス無変換機能を使っているため、複数の周波数で無反射と成る回路には向かない。

(参考文献1)I.Sakagami,T.Wuren, M.Fujii and Y.Tomoda, "A new type of multi-way microwave powerdivider based on bagley polygon power divider," 2006 Asia-PacificMicrowave Conf., Vol.2, pp.1353-1356, Yokohama, Japan (Dec.2006)

(参考文献2)http://www.dec2light.pwp.blueyonder.co.uk/Webpage/Hybridcouplers.htm#baglay

(参考文献3)田原、枡田、佐々木、大橋、“プローブ結合部にアイリスを設けた導波管直列電力分配器” 2006年電子情報通信学会エレクトロニクスソサイエティ大会、C-2-39、p.58、2006

(参考文献4)安部、田原、米田、大橋、“基盤を用いた狭壁面プローブ挿入型導波管電力分配器” 電子情報通信学会技術研究報告、MW2007-131、pp.29-34、Dec.2007

【0066】

なお、図13に示す信号分配器2では、伝送線路53が伝送線路52との接続点から二方向に分岐しているが、伝送線路52から二方向に分岐するように変成器部を設計してもよい。

【図面の簡単な説明】

【0067】

【図1】実施形態に係る信号分配器の平面図である。

【図2】図1に示す信号分配器の回路パターンを示す図である。

【図3】信号分配器の等価回路を一般化したものを示す図である。

【図4】チェビシェフ型2段1/4波長変成器の反射特性を示すグラフである。

【図5】信号分配器と従来のものとで反射特性及び分配特性を比較するためのグラフである。

【図6】信号分配器と従来のものとで位相特性を比較するためのグラフである。

【図7】2周波対応信号分配器の反射特性及び分配特性の理論値を示すグラフである。

【図8】信号分配器の反射特性の理論値及び測定値を示すグラフである。

【図9】信号分配器の分配特性の理論値及び測定値を示すグラフである。

【図10】信号分配器の位相特性の理論値及び測定値を示すグラフである。

【図11】情報処理装置の構成を示す図である。

【図12】図11に示す情報処理装置による信号分配器の設計手順を示すフローチャートである。

【図13】変形例に係る信号分配器の回路パターンを示す図である。

【図14】図13に示す3周波対応信号分配器の反射特性及び分配特性の理論値を示すグラフである。

【符号の説明】

【0068】

1,2…信号分配器、10…入力端子、20…出力部、21…出力端子、22…出力端子間を接続する伝送線路、30,50…変成器部、31…伝送線路(第1の1/4波長伝送線路)、32…伝送線路(第2の1/4波長伝送線路)、40…情報処理装置、51〜53…伝送線路(1/4波長伝送線路)。

【特許請求の範囲】

【請求項1】

複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、

等価回路において多段に直列接続する複数の1/4波長伝送線路により入力端子と前記出力部とを接続する変成器部と、

を備え、

等価回路における前記複数の出力端子のそれぞれについて、前記入力端子の方向から一の出力端子に接続する伝送線路の特性インピーダンスと、該一の出力端子を含む、該伝送線路よりも前記入力端子から離れる方向に位置する一以上の出力端子の合成インピーダンスとが等しい、

ことを特徴とする信号分配器。

【請求項2】

前記変成器部が、一端が前記入力端子と接続する第1の1/4波長伝送線路と、該第1の1/4波長伝送線路の他端と前記出力部とを接続する第2の1/4波長伝送線路とを有する2段変成器であり、

前記第1の1/4波長伝送線路及び前記第2の1/4波長伝送線路の線幅が互いに等しい、

ことを特徴とする請求項1に記載の信号分配器。

【請求項3】

複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、入力端子と前記出力部とを接続する変成器部とを備える信号分配器を設計する情報処理装置における、信号分配器の設計方法であって、

前記入力端子での入力端子インピーダンス、前記出力端子の個数、及び前記信号分配器の通過域内許容反射量に対応する許容反射係数の入力を受け付ける受付ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(1)

Z1=2Z0,Z2=2Z0/3,…,Zk=2Z0/(N−2) …(1)

ただし、k=(N−1)/2

(式中、Z0は前記入力端子インピーダンスを表し、Nは前記出力端子の個数を表す。)

により、各出力端子間を接続する複数の伝送線路の特性インピーダンスZkを算出する第1算出ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(2)

Zin=Z0/(2n+1) …(2)

ただし、n=(N−1)/2

(式中、Z0は前記入力端子インピーダンスを表し、Nは前記出力端子の個数を表す。)

により、前記変成器部と前記出力部との接続点における負荷Zinを算出する第2算出ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び許容反射係数と、前記第2算出ステップにおいて算出された負荷とに基づいて、下記式(3)及び(4)

ρm2={(K0L−K122)/(K0L+K122)}2 …(3)

(式中、ρmは前記許容反射係数を表し、K0Lは前記負荷と前記入力端子インピーダンスとの比を表し、K12は前記変成器部を構成する第1の1/4波長伝送線路の特性インピーダンスと第2の1/4波長伝送線路の特性インピーダンスの1/2との比を表す。すなわち、K0L=Zin/Z0,K12=(Zm2/2)/Zm1)

Zm1(Zm2/2)=Z0Zin …(4)

(式中、Z0は前記入力端子インピーダンスを表し、Zinは前記負荷を表す。)

により、前記第1の1/4波長伝送線路の特性インピーダンスZm1と前記第2の1/4波長伝送線路の特性インピーダンスZm2とを算出する第3算出ステップと、

前記第1算出ステップ及び前記第3算出ステップにおいて算出された特性インピーダンスを出力する出力ステップと、

を含むことを特徴とする信号分配器の設計方法。

【請求項4】

複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、入力端子と前記出力部とを接続する変成器部とを備える信号分配器を設計する情報処理装置における、信号分配器の設計方法であって、

前記入力端子での入力端子インピーダンス、前記出力端子の個数、及び線路パラメータ比の入力を受け付ける受付ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(5)

Z1=2Z0,Z2=2Z0/3,…,Zk=2Z0/(N−2) …(5)

ただし、k=(N−1)/2

(式中、Z0は前記入力端子インピーダンスを表し、Nは前記出力端子の個数を表す。)

により、各出力端子間を接続する複数の伝送線路の特性インピーダンスZkを算出する第1算出ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(6)

Zin=Z0/(2n+1) …(6)

ただし、n=(N−1)/2

(式中、Z0は前記入力端子インピーダンスを表し、Nは前記出力端子の個数を表す。)

により、前記変成器部と前記出力部との接続点における負荷Zinを算出する第2算出ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び線路パラメータ比と、前記第2算出ステップにおいて算出された負荷とに基づいて、下記式(7)及び(8)

(Zm2/2)=K12Zm1 …(7)

(式中、K12は前記線路パラメータ比を表す。)

Zm1(Zm2/2)=Z0Zin …(8)

(式中、Z0は前記入力端子インピーダンスを表し、Zinは前記負荷を表す。)

により、前記第1の1/4波長伝送線路の特性インピーダンスZm1と前記第2の1/4波長伝送線路の特性インピーダンスZm2とを算出する第3算出ステップと、

前記第1算出ステップ及び前記第3算出ステップにおいて算出された特性インピーダンスを出力する出力ステップと、

を含むことを特徴とする信号分配器の設計方法。

【請求項1】

複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、

等価回路において多段に直列接続する複数の1/4波長伝送線路により入力端子と前記出力部とを接続する変成器部と、

を備え、

等価回路における前記複数の出力端子のそれぞれについて、前記入力端子の方向から一の出力端子に接続する伝送線路の特性インピーダンスと、該一の出力端子を含む、該伝送線路よりも前記入力端子から離れる方向に位置する一以上の出力端子の合成インピーダンスとが等しい、

ことを特徴とする信号分配器。

【請求項2】

前記変成器部が、一端が前記入力端子と接続する第1の1/4波長伝送線路と、該第1の1/4波長伝送線路の他端と前記出力部とを接続する第2の1/4波長伝送線路とを有する2段変成器であり、

前記第1の1/4波長伝送線路及び前記第2の1/4波長伝送線路の線幅が互いに等しい、

ことを特徴とする請求項1に記載の信号分配器。

【請求項3】

複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、入力端子と前記出力部とを接続する変成器部とを備える信号分配器を設計する情報処理装置における、信号分配器の設計方法であって、

前記入力端子での入力端子インピーダンス、前記出力端子の個数、及び前記信号分配器の通過域内許容反射量に対応する許容反射係数の入力を受け付ける受付ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(1)

Z1=2Z0,Z2=2Z0/3,…,Zk=2Z0/(N−2) …(1)

ただし、k=(N−1)/2

(式中、Z0は前記入力端子インピーダンスを表し、Nは前記出力端子の個数を表す。)

により、各出力端子間を接続する複数の伝送線路の特性インピーダンスZkを算出する第1算出ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(2)

Zin=Z0/(2n+1) …(2)

ただし、n=(N−1)/2

(式中、Z0は前記入力端子インピーダンスを表し、Nは前記出力端子の個数を表す。)

により、前記変成器部と前記出力部との接続点における負荷Zinを算出する第2算出ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び許容反射係数と、前記第2算出ステップにおいて算出された負荷とに基づいて、下記式(3)及び(4)

ρm2={(K0L−K122)/(K0L+K122)}2 …(3)

(式中、ρmは前記許容反射係数を表し、K0Lは前記負荷と前記入力端子インピーダンスとの比を表し、K12は前記変成器部を構成する第1の1/4波長伝送線路の特性インピーダンスと第2の1/4波長伝送線路の特性インピーダンスの1/2との比を表す。すなわち、K0L=Zin/Z0,K12=(Zm2/2)/Zm1)

Zm1(Zm2/2)=Z0Zin …(4)

(式中、Z0は前記入力端子インピーダンスを表し、Zinは前記負荷を表す。)

により、前記第1の1/4波長伝送線路の特性インピーダンスZm1と前記第2の1/4波長伝送線路の特性インピーダンスZm2とを算出する第3算出ステップと、

前記第1算出ステップ及び前記第3算出ステップにおいて算出された特性インピーダンスを出力する出力ステップと、

を含むことを特徴とする信号分配器の設計方法。

【請求項4】

複数の出力端子と各出力端子間を接続する複数の伝送線路とを有する出力部と、入力端子と前記出力部とを接続する変成器部とを備える信号分配器を設計する情報処理装置における、信号分配器の設計方法であって、

前記入力端子での入力端子インピーダンス、前記出力端子の個数、及び線路パラメータ比の入力を受け付ける受付ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(5)

Z1=2Z0,Z2=2Z0/3,…,Zk=2Z0/(N−2) …(5)

ただし、k=(N−1)/2

(式中、Z0は前記入力端子インピーダンスを表し、Nは前記出力端子の個数を表す。)

により、各出力端子間を接続する複数の伝送線路の特性インピーダンスZkを算出する第1算出ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び出力端子の個数に基づいて、下記式(6)

Zin=Z0/(2n+1) …(6)

ただし、n=(N−1)/2

(式中、Z0は前記入力端子インピーダンスを表し、Nは前記出力端子の個数を表す。)

により、前記変成器部と前記出力部との接続点における負荷Zinを算出する第2算出ステップと、

前記受付ステップにおいて受け付けられた入力端子インピーダンス及び線路パラメータ比と、前記第2算出ステップにおいて算出された負荷とに基づいて、下記式(7)及び(8)

(Zm2/2)=K12Zm1 …(7)

(式中、K12は前記線路パラメータ比を表す。)

Zm1(Zm2/2)=Z0Zin …(8)

(式中、Z0は前記入力端子インピーダンスを表し、Zinは前記負荷を表す。)

により、前記第1の1/4波長伝送線路の特性インピーダンスZm1と前記第2の1/4波長伝送線路の特性インピーダンスZm2とを算出する第3算出ステップと、

前記第1算出ステップ及び前記第3算出ステップにおいて算出された特性インピーダンスを出力する出力ステップと、

を含むことを特徴とする信号分配器の設計方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2009−200609(P2009−200609A)

【公開日】平成21年9月3日(2009.9.3)

【国際特許分類】

【出願番号】特願2008−37679(P2008−37679)

【出願日】平成20年2月19日(2008.2.19)

【出願人】(305060567)国立大学法人富山大学 (194)

【公開日】平成21年9月3日(2009.9.3)

【国際特許分類】

【出願日】平成20年2月19日(2008.2.19)

【出願人】(305060567)国立大学法人富山大学 (194)

[ Back to top ]