信号整形回路および光送信装置

【課題】柔軟な信号整形を行うこと。

【解決手段】演算回路112は、第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する。分岐部113は、演算回路112によって出力された信号を分岐し、分岐した各信号の一方を第二入力部へ入力する。また、分岐部113は、分岐した各信号の他方を出力する。遅延回路114は、演算回路112から出力されて分岐部113へ入力される信号または分岐部113から出力されて第二入力部へ入力される信号を遅延させる。

【解決手段】演算回路112は、第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する。分岐部113は、演算回路112によって出力された信号を分岐し、分岐した各信号の一方を第二入力部へ入力する。また、分岐部113は、分岐した各信号の他方を出力する。遅延回路114は、演算回路112から出力されて分岐部113へ入力される信号または分岐部113から出力されて第二入力部へ入力される信号を遅延させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、信号を整形する信号整形回路および光送信装置に関する。

【背景技術】

【0002】

近年の通信分野においては、データ通信量の増大に伴い、ひとつの信号で大量のデータを送信するため、データレートの高速化が進んでいる。高速なデータは、ケーブル、ボード、出力デバイスなどで符号間干渉などの劣化をしやすいため、帯域不足による劣化分を考慮し、信号の符号間干渉を生じやすい部分をあらかじめ強調したエンファシス信号(プリエンファシス信号)が用いられることがある。

【0003】

エンファシス信号の生成手法の一例として、信号を分岐し、分岐した各信号に遅延差を与えて加減算するFIR(Finite Impulse Response:有限インパルス応答)方式が知られている(たとえば、下記特許文献1参照。)。一方、無線通信装置において、IIR(Infinite Impulse Response:無限インパルス応答)方式のフィルタによってバンドパスフィルタを実現する技術が知られている(たとえば、下記非特許文献1参照。)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−88693号公報

【非特許文献】

【0005】

【非特許文献1】Stefan Andersson,Peter Caputa,and Christer Svensson、“A tuned,inductorless,recursive filter LNA in CMOS”、ESSCIRC2002 P.351−354

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述した従来技術では、実現可能なエンファシスの強さが小さいため、要求される信号波形に応じて柔軟な信号整形を行うことが困難であるという問題がある。

【0007】

本発明は、上述した従来技術による問題点を解消するため、柔軟な信号整形を行うことができる信号整形回路および信号整形回路を用いた光送信装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上述した課題を解決し、目的を達成するため、本発明の一側面によれば、第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、を備える信号整形回路および信号整形回路を用いた光送信装置が提案される。

【0009】

また、本発明の別の側面によれば、第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算して出力する演算部と、前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号に対して、所定比率を乗じて遅延させる遅延部と、前記遅延部の前記所定比率を調整可能にする調整部と、を備える信号整形回路および信号整形回路を用いた光送信装置が提案される。

【0010】

また、本発明の別の側面によれば、第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算した信号を出力する演算部と、前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタと、を備える信号整形回路および信号整形回路を用いた光送信装置が提案される。

【発明の効果】

【0011】

本発明の一側面によれば、柔軟な信号整形を行うことができるという効果を奏する。

【図面の簡単な説明】

【0012】

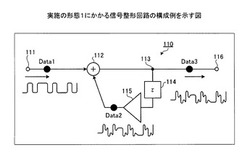

【図1−1】図1−1は、実施の形態1にかかる信号整形回路の構成例を示す図である。

【図1−2】図1−2は、FIR方式の信号整形回路の構成例を参考として示す図である。

【図2】図2は、各方式の信号整形回路における信号の一例を示す図である。

【図3】図3は、各方式の信号整形回路におけるエンファシス特性の一例を示す図である。

【図4】図4は、図1に示した演算回路の構成例を示す図である。

【図5】図5は、図1に示した遅延回路およびバッファ回路の構成例を示す図である。

【図6】図6は、実施の形態1にかかる光送信装置の構成例を示す図である。

【図7】図7は、実施の形態2にかかる信号整形回路の構成例を示す図である。

【図8−1】図8−1は、図7に示した演算回路の構成例を示す図である。

【図8−2】図8−2は、図7に示した演算回路の変形例を示す図である。

【図9】図9は、実施の形態2にかかる信号整形回路の変形例1を示す図である。

【図10】図10は、図9に示した遅延回路およびバッファ回路の構成例を示す図である。

【図11−1】図11−1は、図10に示した遅延バッファ回路の調整前の入出力特性の一例を示す図である。

【図11−2】図11−2は、図10に示した遅延バッファ回路の調整前の信号の一例を示す図である。

【図12−1】図12−1は、図10に示した遅延バッファ回路の調整後の入出力特性の一例を示す図である。

【図12−2】図12−2は、図10に示した遅延バッファ回路の調整後の信号の一例を示す図である。

【図13】図13は、実施の形態2にかかる信号整形回路の変形例2を示す図である。

【図14−1】図14−1は、調整前の帰還信号のシミュレーション結果の一例を示す図である。

【図14−2】図14−2は、調整前の出力信号のシミュレーション結果の一例を示す図である。

【図15−1】図15−1は、調整後の帰還信号のシミュレーション結果の一例を示す図である。

【図15−2】図15−2は、調整後の出力信号のシミュレーション結果の一例を示す図である。

【図16】図16は、実施の形態3にかかる信号整形回路の構成例を示す図である。

【図17】図17は、図16に示したハイパスフィルタの構成例を示す図である。

【図18】図18は、図16に示すハイパスフィルタ通過後の信号を遅延バッファ回路に入力した場合の遅延バッファ回路の入出力特性の一例を示す図である。

【図19】図19は、調整後の帰還信号のシミュレーション結果の一例を示す図である。

【図20】図20は、調整後の出力信号のシミュレーション結果の一例を示す図である。

【図21−1】図21−1は、実施の形態4にかかる信号整形回路の構成例を示す図である。

【図21−2】図21−2は、図21−1に示した信号整形回路からハイパスフィルタを省いた構成を参考として示す図である。

【図22−1】図22−1は、図1−1に示した信号整形回路の出力信号のアイパターンの一例を示す図である。

【図22−2】図22−2は、図1−1に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。

【図23−1】図23−1は、図16に示した信号整形回路の出力信号のアイパターンの一例を示す図である。

【図23−2】図23−2は、図16に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。

【図24−1】図24−1は、図21−2に示した信号整形回路の出力信号のアイパターンの一例を参考として示す図である。

【図24−2】図24−2は、図21−2に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を参考として示す図である。

【図25−1】図25−1は、図21−1に示した信号整形回路の出力信号のアイパターンの一例を示す図である。

【図25−2】図25−2は、図21−1に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。

【発明を実施するための形態】

【0013】

以下に添付図面を参照して、本発明にかかる信号整形回路および光送信装置の実施の形態を詳細に説明する。

【0014】

(実施の形態1)

(信号整形回路の構成)

図1−1は、実施の形態1にかかる信号整形回路の構成例を示す図である。図1−1に示す信号整形回路110は、入力された信号を整形して出力する信号整形回路である。たとえば、信号整形回路110は、VCSEL(Vertical Cavity Surface Emitting Laser:垂直共振器面発光レーザ)などの発光素子へ入力する駆動信号を整形する。ただし、信号整形回路110による整形対象の信号は発光素子の駆動信号に限らない。

【0015】

図1−1に示すように、信号整形回路110は、入力部111と、演算回路112と、分岐部113と、遅延回路114と、バッファ回路115と、出力部116と、を備えている。入力部111には、整形対象の信号が入力される。入力部111へ入力される信号は、たとえば正相信号および逆相信号を含む差動信号である。入力部111は、入力された信号を入力信号Data1として演算回路112へ出力する。

【0016】

演算回路112は、第一入力部と第二入力部を有する。演算回路112の第一入力部には、入力部111から出力された入力信号Data1(第一信号)が入力される。演算回路112の第二入力部には、バッファ回路115から出力された帰還信号Data2(第二信号)が入力される。演算回路112は、入力された入力信号Data1と帰還信号Data2をそれぞれ重み付けして加算または減算する演算部である。そして、演算回路112は、加算または減算した信号を出力信号Data3として分岐部113へ出力する。

【0017】

分岐部113は、演算回路112から出力された出力信号Data3を分岐する。そして、分岐部113は、分岐した出力信号Data3の一方を出力部116へ出力する。また、分岐部113は、分岐した出力信号Data3の他方を帰還信号Data2として遅延回路114へ出力する。

【0018】

遅延回路114は、分岐部113から出力された帰還信号Data2を遅延させる遅延部である。そして、遅延回路114は、遅延させた帰還信号Data2をバッファ回路115へ出力する。バッファ回路115は、遅延回路114から出力された帰還信号Data2を出力調整する。そして、バッファ回路115は、出力調整した信号を帰還信号Data2として演算回路112へ出力する。

【0019】

演算回路112へ出力された帰還信号Data2は、演算回路112の第二入力部へ入力される。このように、遅延回路114、バッファ回路115および出力部116は、分岐部113から出力された帰還信号Data2を演算回路112の第二入力部へ帰還させる帰還部である。出力部116は、分岐部113から出力された出力信号Data3を信号整形回路110の後段へ出力する。

【0020】

これにより、出力信号Data3を帰還信号Data2として帰還させて入力信号Data1に加算または減算するIIR方式によって入力信号Data1を信号整形し、信号整形した信号を出力信号Data3として出力することができる。たとえば、入力信号Data1の特定の高周波成分を強調(エンファシス)したり、入力信号Data1の特定の高周波成分を抑制したりすることができる。以下、信号整形回路110が、入力信号Data1の特定の高周波成分を強調(エンファシス)する例について主に説明する。

【0021】

図1−1においては、バッファ回路115を遅延回路114の後段に設ける構成について図示したが、バッファ回路115を遅延回路114の前段に設ける構成とすることもできる。また、遅延回路114を分岐部113の後段かつバッファ回路115の前段に設ける構成について図示したが、遅延回路114を演算回路112の後段かつ分岐部113の前段に設ける構成とすることもできる。また、バッファ回路115を分岐部113の後段かつ遅延回路114の後段に設ける構成について図示したが、バッファ回路115を演算回路112の後段かつ分岐部113の前段に設ける構成とすることもできる。

【0022】

(FIR方式の信号整形回路の構成例)

図1−2は、FIR方式の信号整形回路の構成例を参考として示す図である。図1−2に示すように、FIR方式の信号整形回路120は、入力部121と、分岐部122と、遅延回路123と、バッファ回路124,125と、演算回路126と、出力部127と、を備えている。

【0023】

入力部121には、整形対象の信号が入力される。入力部121は、入力された信号を分岐部122へ出力する。分岐部122は、入力部121から出力された信号を分岐する。そして、分岐部122は、分岐した各信号の一方を分岐信号D1としてバッファ回路124へ出力する。また、分岐部122は、分岐した各信号の他方を分岐信号D2として遅延回路123へ出力する。

【0024】

遅延回路123は、分岐部122から出力された分岐信号D2を遅延させる。そして、遅延回路123は、遅延させた分岐信号D2をバッファ回路125へ出力する。遅延回路123における遅延時間τは、たとえば図1−1に示した遅延回路114における遅延時間τと同じである。

【0025】

バッファ回路124は、分岐部122から出力された分岐信号D1を出力調整する。そして、バッファ回路124は、出力調整した分岐信号D1を演算回路126へ出力する。バッファ回路125は、遅延回路123から出力された分岐信号D2を出力調整する。そして、バッファ回路125は、出力調整した分岐信号D2を演算回路126へ出力する。

【0026】

演算回路126は、バッファ回路124から出力された分岐信号D1と、バッファ回路125から出力された分岐信号D2と、を加算または減算する。そして、演算回路126は、加算または減算した信号を出力信号D3として出力部127へ出力する。演算回路126における加算または減算の重み付け(加算比)は、たとえば図1−1に示した演算回路112と同じである。出力部127は、演算回路126から出力された信号出力信号D3を出力する。

【0027】

(各方式の信号整形回路における信号)

図2は、各方式の信号整形回路における信号の一例を示す図である。図2において、横軸は時間を示している。波形211〜213は、図1−1に示したIIR方式の信号整形回路110における入力信号Data1、帰還信号Data2および出力信号Data3の各波形を示している。図2では、演算回路112が、入力信号Data1から帰還信号Data2を減算した結果を出力信号Data3として出力する例を示している。

【0028】

波形221〜223は、図1−2に示したFIR方式の信号整形回路120における分岐信号D1、分岐信号D2および出力信号D3の各波形を参考として示している。なお、図2では、演算回路126が、分岐信号D1から分岐信号D2を減算した結果を出力信号D3として出力する例を示している。

【0029】

波形211〜213および波形221〜223に示すように、図1−1に示したIIR方式の信号整形回路110は、図1−2に示したFIR方式の信号整形回路120よりもより高周波成分の強度の大きいエンファシスを信号にかけることができる。これにより、たとえば信号の立ち上がり部分などをより急峻に強調することができる。

【0030】

(各方式の信号整形回路におけるエンファシス特性)

図3は、各方式の信号整形回路におけるエンファシス特性の一例を示す図である。図3において、横軸は信号の周波数[GHz]を示している。縦軸は信号の強度を示している。エンファシス特性301は、図1−1に示したIIR方式の信号整形回路110から出力される出力信号Data3の周波数に対する強度の特性を示している。エンファシス特性302は、図1−2に示したFIR方式の信号整形回路120から出力される出力信号D3の周波数に対する強度の特性を参考として示している。

【0031】

エンファシス特性301,302に示すように、図1−1に示したIIR方式の信号整形回路110は、FIR方式の信号整形回路120よりも特定の高周波成分(たとえば22[GHz]付近の成分)を強調したエンファシス信号を得ることができる。

【0032】

(演算回路の構成)

図4は、図1に示した演算回路の構成例を示す図である。図4に示した演算回路112は、たとえば図4に示す演算回路400によって実現することができる。演算回路400は、入力部411,412と、トランジスタ421,422と、電流源431,432と、グランド440と、を備えている。また、演算回路400は、入力部451,452と、トランジスタ461,462と、抵抗471,472と、電源480と、出力部481,482と、を備えている。

【0033】

入力部411,412(IN1P,IN1N)は、それぞれ入力部111から出力された入力信号Data1の正相信号および逆相信号が入力される第一入力部である。入力部411は、トランジスタ421のゲートに接続されている。入力部412は、トランジスタ422のゲートに接続されている。

【0034】

トランジスタ421のゲートは入力部411に接続されている。トランジスタ421のソースは電流源431に接続されている。トランジスタ421のドレインは抵抗471および出力部482に接続されている。トランジスタ422のゲートは入力部412に接続されている。トランジスタ422のソースは電流源431に接続されている。トランジスタ422のドレインは抵抗472および出力部481に接続されている。電流源431は、一端がトランジスタ421,422の各ソースに接続され、他端がグランド440(VSS)に接続されている。

【0035】

入力部451,452(IN2P,IN2N)は、それぞれバッファ回路115から出力された帰還信号Data2の正相信号および逆相信号が入力される第二入力部である。入力部451は、トランジスタ461のゲートに接続されている。入力部452は、トランジスタ462のゲートに接続されている。

【0036】

トランジスタ461のゲートは入力部451に接続されている。トランジスタ461のソースは電流源432に接続されている。トランジスタ461のドレインは抵抗471および出力部482に接続されている。トランジスタ462のゲートは入力部452に接続されている。トランジスタ462のソースは電流源432に接続されている。トランジスタ462のドレインは抵抗472および出力部481に接続されている。

【0037】

電流源432は、一端がトランジスタ461,462の各ソースに接続され、他端がグランド440(VSS)に接続されている。抵抗471は、一端がトランジスタ421,461の各ドレインに接続され、他端が電源480(VDD)に接続されている。抵抗472は、一端がトランジスタ422,462の各ドレインに接続され、他端が電源480(VDD)に接続されている。

【0038】

出力部481(OUTP)は、トランジスタ422,462からの信号を正相信号として出力する。出力部482(OUTN)は、トランジスタ421,461からの信号を逆相信号として出力する。これにより、入力部111から出力された入力信号Data1と、バッファ回路115から出力された帰還信号Data2と、を加算した信号を出力信号Data3として出力することができる。

【0039】

また、正相信号と逆相信号とを入れ替えることで、入力信号Data1と帰還信号Data2とを減算することもできる。たとえば、入力部451に帰還信号Data2の逆相信号を入力し、入力部452に帰還信号Data2の正相信号を入力することで、入力信号Data1から帰還信号Data2を減算することができる。

【0040】

また、加算または減算における入力信号Data1の重みは、たとえば電流源431の電流値などによって決まる。また、加算または減算における帰還信号Data2との重みは、たとえば電流源432の電流値などによって決まる。トランジスタ421,422,461,462のそれぞれはたとえばFET(Field Effect Transistor:電界効果トランジスタ)である。

【0041】

(遅延回路およびバッファ回路の構成)

図5は、図1に示した遅延回路およびバッファ回路の構成例を示す図である。図4に示した遅延回路114およびバッファ回路115のそれぞれは、たとえば図5に示す遅延バッファ回路500によって実現することができる。遅延バッファ回路500は、入力部511,512と、トランジスタ521,522と、電流源530と、グランド540と、抵抗551,552と、電源560と、出力部571,572と、を備えている。

【0042】

入力部511,512(INP,INN)には、それぞれ遅延バッファ回路500へ入力された帰還信号Data2の正相信号および逆相信号が入力される。入力部511は、トランジスタ521のゲートに接続されている。入力部512は、トランジスタ522のゲートに接続されている。

【0043】

トランジスタ521,522のそれぞれはたとえばFETである。トランジスタ521のゲートは入力部511に接続されている。トランジスタ521のソースは電流源530に接続されている。トランジスタ521のドレインは抵抗551および出力部572に接続されている。トランジスタ522のゲートは入力部512に接続されている。トランジスタ522のソースは電流源530に接続されている。トランジスタ522のドレインは抵抗552および出力部571に接続されている。

【0044】

電流源530は、一端がトランジスタ521,522の各ソースに接続され、他端がグランド540(VSS)に接続されている。抵抗551は、一端がトランジスタ521のドレインに接続され、他端が電源560(VDD)に接続されている。抵抗552は、一端がトランジスタ522のドレインに接続され、他端が電源560に接続されている。

【0045】

出力部571は、トランジスタ522からの信号を正相信号として出力する。出力部572は、トランジスタ521からの信号を逆相信号として出力する。これにより、遅延バッファ回路500へ入力された帰還信号Data2に遅延と利得を与えて出力することができる。遅延バッファ回路500による帰還信号Data2の利得は、たとえば電流源530における電流の大きさによって決まる。

【0046】

(光送信装置の構成)

図6は、実施の形態1にかかる光送信装置の構成例を示す図である。図6に示す光送信装置600は、入力された駆動信号に基づく信号光を送信する。具体的には、光送信装置600は、図1−1に示した信号整形回路110と、発光素子610と、を備えている。信号整形回路110は、光送信装置600へ入力された駆動信号を整形し、整形した駆動信号を発光素子610へ出力する。

【0047】

発光素子610は、たとえばVCSELなどのLD(Laser Diode:レーザダイオード)である。発光素子610は、一端が信号整形回路110に接続され、他端が接地されている。発光素子610は、信号整形回路110から出力された駆動信号に基づいて強度変調(直接変調)した信号光を出射する。これにより、光送信装置600は、入力された駆動信号に基づく信号光を送信することができる。

【0048】

このように、実施の形態1にかかる信号整形回路110によれば、出力信号を分岐して帰還させた信号を入力信号に加算または減算するIIRフィルタを用いることで、より柔軟な信号整形が可能になる。また、実施の形態1にかかる光送信装置600によれば、信号整形回路110によって駆動信号を柔軟に整形することができる。このため、要求される信号光の波形や発光素子610の特性に応じて駆動信号を柔軟に整形し、品質の高い信号光を送信することができる。

【0049】

(実施の形態2)

実施の形態2について、実施の形態1と異なる部分について説明する。

【0050】

(信号整形回路の構成)

図7は、実施の形態2にかかる信号整形回路の構成例を示す図である。図7において、図1−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図7に示すように、実施の形態2にかかる信号整形回路110は、図1−1に示した演算回路112に代えて可変演算回路701を備えている。

【0051】

可変演算回路701は、図1−1に示した演算回路112に、加算または減算における入力信号Data1(第一信号)および帰還信号Data2(第二信号)の各重みの少なくとも一方を調整可能にする調整部を設けた演算回路(たとえば図8−1,図8−2参照)である。たとえば、可変演算回路701は、入力信号Data1に第一比率を乗じた信号と、帰還信号Data2に第二比率を乗じた信号と、を加算また減算した信号を出力し、第一比率および第二比率の少なくとも一方を調整可能にした演算回路である。

【0052】

(演算回路の構成)

図8−1は、図7に示した演算回路の構成例を示す図である。図8−1において、図4に示した部分と同様の部分については同一の符号を付して説明を省略する。図8−1に示すように、実施の形態2にかかる可変演算回路701は、図4に示した電流源432に代えて、可変電流源811,812および可変抵抗813を備えている。

【0053】

可変電流源811,812は、それぞれ電流の大きさが可変の電流源である。可変電流源811は、一端がトランジスタ461のソースに接続され、他端がグランド440に接続されている。可変電流源812は、一端がトランジスタ462のソースに接続され、他端がグランド440に接続されている。これにより、トランジスタ461,462のソース電流を可変にすることができる。可変抵抗813は、抵抗値が可変の抵抗である。また、可変抵抗813は、一端がトランジスタ461のソースに接続されており、一端がトランジスタ462のソースに接続されている。

【0054】

ここで、演算回路400のエンファシス加算利得(帰還信号Data2の加算または減算の重み)は、たとえば(Gm×Ra)/(1+Gm×Rb)によって示すことができる。Gmはトランジスタ461,462のコンダクタンスである。Raは抵抗471,472の抵抗値である。Rbはトランジスタ461,462のソースの合成インピーダンス(可変抵抗813の抵抗値)である。

【0055】

したがって、エンファシス加算利得は、差動回路のトランジスタ461,462のソースの合成インピーダンスRbおよびトランジスタ461,462のコンダクタンスGmの大きさに依存する。そして、コンダクタンスGmはトランジスタ461,462のソース電流に依存する。このため、可変電流源811,812によってトランジスタ461,462のソース電流を可変にすることでエンファシス加算利得を調整することができる。

【0056】

また、可変抵抗813によりトランジスタ461,462のソースの合成インピーダンスRbを可変にすることでエンファシス加算利得を調整することができる。たとえば、可変抵抗813の抵抗値Rbを大きくすればエンファシス加算利得が小さくなり、抵抗値Rbを小さくすればエンファシス加算利得が大きくなる。

【0057】

図8−2は、図7に示した演算回路の変形例を示す図である。図8−2において、図8−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図8−2に示すように、実施の形態2にかかる可変演算回路701は、図8−1に示した電流源431に代えて、可変電流源821,822および可変抵抗823を備えている。

【0058】

可変電流源821,822は、それぞれ電流の大きさが可変の電流源である。可変電流源821は、一端がトランジスタ421のソースに接続され、他端がグランド440に接続されている。可変電流源822は、一端がトランジスタ422のソースに接続され、他端がグランド440に接続されている。これにより、トランジスタ421,422のソース電流を可変にすることができる。可変抵抗823は、抵抗値が可変の抵抗である。また、可変抵抗823は、一端がトランジスタ421のソースに接続されており、一端がトランジスタ422のソースに接続されている。

【0059】

これにより、帰還信号Data2の加算または減算の重みだけでなく、入力信号Data1の加算または減算の重みも調整することができる。また、演算回路400は、図4に示した構成において、電流源431に代えて、可変電流源821,822および可変抵抗823を備える構成としてもよい。この場合は、入力信号Data1の加算または減算の重みを調整することができる。このように、実施の形態2にかかる可変演算回路701は、加算または減算における入力信号Data1および帰還信号Data2の各重みの少なくとも一方を調整可能である。

【0060】

(信号整形回路の変形例1)

図9は、実施の形態2にかかる信号整形回路の変形例1を示す図である。図9に示すように、実施の形態2にかかる信号整形回路110は、図1−1に示した遅延回路114に代えて利得可変遅延回路901を備えている。

【0061】

利得可変遅延回路901は、図1−1に示した遅延回路114に、帰還信号Data2に対する利得を調整可能にする調整部を設けた演算回路(たとえば図10参照)である。たとえば、利得可変遅延回路901は、帰還信号Data2に対して、所定比率を乗じて遅延させて出力し、所定比率を調整可能にした遅延回路である。また、バッファ回路115に代えて、帰還信号Data2に対する利得を調整可能にする調整部を設けたバッファ回路を設けてもよい。

【0062】

(遅延回路およびバッファ回路の構成)

図10は、図9に示した遅延回路およびバッファ回路の構成例を示す図である。図10において、図5に示した部分と同様の部分については同一の符号を付して説明を省略する。図9に示した利得可変遅延回路901は、図10に示す遅延バッファ回路500によって実現することができる。図10に示す遅延バッファ回路500は、図5に示した電流源530に代えて、可変電流源1011,1012、可変抵抗1021,1022およびスイッチ1030を備えている。

【0063】

可変電流源1011,1012のそれぞれは、電流の大きさが可変の電流源である。可変電流源1011は、一端がトランジスタ521のソースに接続され、他端がグランド540に接続されている。可変電流源1012は、一端がトランジスタ522のソースに接続され、他端がグランド540に接続されている。

【0064】

可変抵抗1021,1022のそれぞれは、抵抗値が可変の抵抗である。可変抵抗1021は、一端がトランジスタ521のソースに接続され、他端がトランジスタ522のソースに接続されている。可変抵抗1022は、一端がスイッチ1030に接続され、他端がトランジスタ522のソースに接続されている。スイッチ1030は、オン状態においては可変抵抗1022と可変電流源1011とを接続し、オフ状態においては可変抵抗1022と可変電流源1011とを切断する。

【0065】

可変電流源1011,1012の電流を変化させることで、遅延バッファ回路500における帰還信号Data2への利得を調整することができる。また、スイッチ1030のオン/オフを切り替えることによっても遅延バッファ回路500における帰還信号Data2への利得を調整することができる。

【0066】

なお、遅延バッファ回路500において、可変抵抗1021,1022およびスイッチ1030に代えて、抵抗値が固定の抵抗を設けてもよい。この場合も、可変電流源1011,1012の電流を変化させることで、遅延バッファ回路500における帰還信号Data2への利得を調整することができる。

【0067】

また、遅延バッファ回路500において、可変電流源1011,1012に代えて、電流の大きさが固定の電流源を設けてもよい。この場合も、スイッチ1030のオン/オフを切り替えることによっても遅延バッファ回路500における帰還信号Data2への利得を調整することができる。

【0068】

(遅延バッファ回路の調整前の入出力特性)

図11−1は、図10に示した遅延バッファ回路の調整前の入出力特性の一例を示す図である。図11−1において、横軸は、遅延バッファ回路500への入力信号1101の振幅(入力振幅)を示している。縦軸は、遅延バッファ回路500からの出力信号1102の振幅(出力振幅)を示している。入出力特性1110は、遅延バッファ回路500における入力振幅に対する出力振幅の特性を示している。

【0069】

入出力特性1110は、入力振幅の増加に対して出力振幅がほぼ線形に増加する線形領域1111を有する。また、入出力特性1110における線形領域1111よりそれぞれ低振幅側および高振幅側の非線形領域1112,1113は、入力振幅の増加に対して出力振幅がほぼ一定となる領域である。このように、遅延バッファ回路500には、出力する信号の振幅に上限がある。

【0070】

線形領域1111における利得(入力振幅に対する出力振幅の変化量)は、たとえば可変電流源1011,1012の電流の大きさやスイッチ1030のオン/オフの状態によって決まる。図11−1に示す例では、線形領域1111における利得が比較的大きく設定されている。この場合は、線形領域1111の幅が相対的に小さくなる。

【0071】

このため、入力信号1101の振幅が線形領域1111に収まらなくなっている。したがって、入力信号1101の高周波成分が非線形領域1112,1113に現れてリミッタがかかり、出力信号1102には高周波成分が含まれなくなる。このように、入力信号1101の振幅に対して線形領域1111が狭い場合は、出力信号1102(帰還信号Data2)の高周波成分が失われ、エンファシスが十分に効かなくなる。

【0072】

一方、線形領域1111における利得が小さくなり過ぎると、入力信号1101の振幅は線形領域1111に収まるが、出力信号1102の振幅が小さくなる。このため、たとえば、入力信号Data1に対する帰還信号Data2の加算または減算の比率が小さくなり、十分なエンファシスの強度が得られなくなる。また、たとえば、出力信号Data3の信号強度(振幅)を十分に大きくすることができなくなる。

【0073】

図11−1においては、遅延バッファ回路500について説明したが、演算回路400にも同様に出力する信号の振幅に上限がある。したがって、演算回路400においても、たとえば帰還信号Data2が線形領域1111に収まらなくなると、十分なエンファシスの強度が得られなくなったり、出力信号Data3の信号強度(振幅)を十分に大きくすることができなくなったりする。

【0074】

なお、従来の無線通信装置でバンドパスフィルタとして用いられるIIR方式のフィルタにおいては、フィルタとして用いられているため、エンファシスの強度や出力信号の強度を調整することが求められない。このため、従来のIIR方式のフィルタにおいては、たとえば、演算回路や遅延回路が入出力特性の線形領域のみで動作するように設計すればよく、上記のような信号が線形領域に収まらなくなるという問題がなかった。

【0075】

(遅延バッファ回路の調整前の信号)

図11−2は、図10に示した遅延バッファ回路の調整前の信号の一例を示す図である。図11−2において、図2に示した部分と同様の部分については同一の符号を付して説明を省略する。図11−1に示したように入力信号1101の振幅が線形領域1111に収まっていない場合は、波形212に示すように出力信号1102(帰還信号Data2)の高周波成分が失われる。このため、波形213に示すように、出力信号Data3に対してエンファシスが十分に効かなくなることがある。

【0076】

このように、IIR方式のフィルタをエンファシスに用いた場合においては、エンファシス信号を遅延して帰還させる際、演算回路112、遅延回路114、バッファ回路115などの出力のリミッタにより高周波成分が失われることがある。その結果、IIR方式ならではの特定の周波数で急峻なエンファシス信号(たとえば図2に示した波形213)が得られないことがある。これに対して、実施の形態2にかかる信号整形回路110は、演算回路400や遅延バッファ回路500における利得等を可変にする。

【0077】

(遅延バッファ回路の調整後の入出力特性)

図12−1は、図10に示した遅延バッファ回路の調整後の入出力特性の一例を示す図である。図12−1において、図11−1に示した部分と同様の部分については同一の符号を付して説明を省略する。実施の形態2にかかる遅延バッファ回路500は、たとえば可変電流源1011,1012の電流の大きさやスイッチ1030の状態によって、線形領域1111における利得を調整することができる。

【0078】

図12−1に示す例では、線形領域1111における利得が図11−1の場合より小さく設定されている。この場合は、線形領域1111の幅が相対的に大きくなる。これにより、入力信号1101の振幅が線形領域1111に収まっている。したがって、入力信号1101の高周波成分が線形領域1111に含まれるためリミッタがかからず、出力信号1102に高周波成分が含まれるようになる。

【0079】

このように、可変電流源1011,1012の電流の大きさやスイッチ1030の状態によって、入力信号1101の振幅が線形領域1111に収まるようにすることで、出力信号1102(帰還信号Data2)の高周波成分を維持することができる。このため、信号に対して強いエンファシスをかけることができる。たとえば、入力信号1101の振幅が線形領域1111の90%程度の振幅になるように調整することで、効率よく信号にエンファシスをかけることができる。

【0080】

また、可変電流源1011,1012の電流の大きさやスイッチ1030の状態によって、線形領域1111における利得が小さくなり過ぎないようにすることで、出力信号1102の振幅が小さくなり過ぎることを回避することができる。このため、十分なエンファシスの強度が得られなかったり、信号強度(振幅)を十分に大きくすることができなかったりすることを回避することができる。

【0081】

(遅延バッファ回路の調整後の信号)

図12−2は、図10に示した遅延バッファ回路の調整後の信号の一例を示す図である。図12−2において、図2に示した部分と同様の部分については同一の符号を付して説明を省略する。図12−1に示したように入力信号1101の振幅が線形領域1111に収まっている場合は、波形212に示すように出力信号1102(帰還信号Data2)の高周波成分が維持される。このため、波形213に示すように、出力信号Data3に対して強いエンファシスが効くようになる。

【0082】

(信号整形回路の変形例2)

図13は、実施の形態2にかかる信号整形回路の変形例2を示す図である。図13において、図1−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図13に示すように、実施の形態2にかかる信号整形回路110は、図1−1に示したバッファ回路115に代えて、スイッチ1311およびバッファ回路1321,1322を備えていてもよい。

【0083】

遅延回路114は、遅延させた信号をスイッチ1311へ出力する。スイッチ1311は、遅延回路114から出力された信号をバッファ回路1321へ出力する第一状態と、遅延回路114から出力された信号をバッファ回路1322へ出力する第二状態と、に切替可能な経路切替スイッチである。

【0084】

バッファ回路1321,1322のそれぞれは、スイッチ1311から出力された信号を出力調整して演算回路112へ出力する。また、バッファ回路1321,1322は、互いに異なる利得によって信号を増幅する。バッファ回路1321,1322の各構成例は、たとえば図5に示した遅延バッファ回路500と同様である。これにより、スイッチ1311の切替により、帰還信号Data2に対する出力を変化させることができる。

【0085】

(調整前の各信号のシミュレーション結果)

図14−1は、調整前の帰還信号のシミュレーション結果の一例を示す図である。図14−2は、調整前の出力信号のシミュレーション結果の一例を示す図である。図14−1,図14−2において、横軸は時間[ns]を示し、縦軸は信号の強度を示している。

【0086】

図14−1に示す波形1411は、可変演算回路701や利得可変遅延回路901における利得の調整前の帰還信号Data2の波形である。図14−2に示す波形1412は、可変演算回路701や利得可変遅延回路901における利得の調整前の出力信号Data3の波形である。波形1411,1412に示すように、可変演算回路701や利得可変遅延回路901における利得の調整前は、帰還信号Data2および出力信号Data3の高周波成分が小さくなっていることが分かる。

【0087】

(調整後の各信号のシミュレーション結果)

図15−1は、調整後の帰還信号のシミュレーション結果の一例を示す図である。図15−2は、調整後の出力信号のシミュレーション結果の一例を示す図である。図15−1,図15−2において、横軸は時間[ns]を示し、縦軸は信号の強度を示している。

【0088】

図15−1に示す波形1511は、可変演算回路701や利得可変遅延回路901における利得の調整後の帰還信号Data2の波形である。図15−2に示す波形1512は、可変演算回路701や利得可変遅延回路901における利得の調整後の出力信号Data3の波形である。波形1511,1512に示すように、可変演算回路701や利得可変遅延回路901における利得の調整後は、帰還信号Data2および出力信号Data3の高周波成分が大きくなり、強いエンファシスがかかっていることが分かる。

【0089】

このように、実施の形態2にかかる信号整形回路110によれば、IIRフィルタの加算器等の利得を調整可能にすることで、加算器等のリミッタによる高周波成分の減衰を抑えつつ、要求されるエンファシス強度や信号強度を実現することが可能になる。これにより、より柔軟な信号整形を行うことができる。

【0090】

(実施の形態3)

実施の形態3について、実施の形態1,2と異なる部分について説明する。

【0091】

(信号整形回路の構成)

図16は、実施の形態3にかかる信号整形回路の構成例を示す図である。図16において、図1−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図16に示すように、実施の形態3にかかる信号整形回路110は、図1−1に示した構成に加えてハイパスフィルタ1601(HPF:High Pass Filter)を備えている。ハイパスフィルタ1601は、たとえば分岐部113と遅延回路114との間に設けられている。

【0092】

ハイパスフィルタ1601は、分岐部113から出力された帰還信号Data2の所定の周波数以下の低周波成分を減衰させるフィルタである。ハイパスフィルタ1601は、低周波成分を減衰させた帰還信号Data2を遅延回路114へ出力する。遅延回路114は、ハイパスフィルタ1601から出力された帰還信号Data2を遅延させる。

【0093】

なお、図16においてはハイパスフィルタ1601を分岐部113と遅延回路114との間に設ける構成を図示したが、ハイパスフィルタ1601を遅延回路114とバッファ回路115の間に設ける構成としてもよい。また、ハイパスフィルタ1601をバッファ回路115と演算回路112との間に設ける構成としてもよい。

【0094】

(ハイパスフィルタの構成)

図17は、図16に示したハイパスフィルタの構成例を示す図である。図17に示すように、ハイパスフィルタ1601は、たとえば、入力部1701と、コンデンサ1702と、抵抗1703と、グランド1704と、出力部1705と、を備えている。入力部1701には、分岐部113から出力された出力信号Data3が入力される。

【0095】

入力部1701(IN)には、ハイパスフィルタ1601へ入力された帰還信号Data2が入力される。コンデンサ1702は、一端が入力部1701に接続され、他端が抵抗1703および出力部1705に接続されている。抵抗1703は、一端が出力部1705に接続され、他端がグランド1704(VSS)に接続されている。

【0096】

出力部1705(OUT)は、入力された信号をハイパスフィルタ1601の後段へ出力する。これにより、入力部1701へ入力された帰還信号Data2に含まれる低周波成分を減衰させ、低周波成分を減衰させた帰還信号Data2を出力することができる。

【0097】

(遅延バッファ回路の入出力特性)

図18は、図16に示すハイパスフィルタ通過後の信号を遅延バッファ回路に入力した場合の遅延バッファ回路の入出力特性の一例を示す図である。図18において、図11−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図16に示したように、ハイパスフィルタ1601によって帰還信号Data2の低周波成分を減衰させることで、帰還信号Data2の振幅が小さくなる。

【0098】

このため、図18に示すように、入力信号1101(帰還信号Data2)の高周波成分が線形領域1111に収まりやすくなる。このため、入力信号1101の高周波成分が線形領域1111に収まるようにしつつ、線形領域1111の利得をより大きくすることが可能になる。

【0099】

このように、ハイパスフィルタ1601を設けることで、線形性の高い線形領域1111に高周波エンファシス信号を割り当てることができるため、入力信号1101の振幅依存および出力信号1102の振幅依存が小さくなる。このため、効率よく高周波エンファシス成分を遅延させて帰還させることができる。

【0100】

(調整後の帰還信号のシミュレーション結果)

図19は、調整後の帰還信号のシミュレーション結果の一例を示す図である。図20は、調整後の出力信号のシミュレーション結果の一例を示す図である。図19,図20において、横軸は時間[ns]を示し、縦軸は信号の強度を示している。

【0101】

図19に示す波形1901は、可変演算回路701や利得可変遅延回路901における利得の調整後の帰還信号Data2の波形である。図20に示す波形2001は、可変演算回路701や利得可変遅延回路901における利得の調整後の出力信号Data3の波形である。波形1901,2001に示すように、ハイパスフィルタ1601を設けることで、図15−1,図15−2に示した例よりも帰還信号Data2および出力信号Data3の高周波成分がさらに大きくなり、より強いエンファシスがかかっていることが分かる。

【0102】

このように、実施の形態3にかかる信号整形回路110によれば、帰還信号Data2の低周波成分を減衰させるハイパスフィルタ1601を設けることで、帰還信号Data2の振幅を小さくすることができる。これにより、帰還信号Data2の振幅が加算回路等の入出力特性の線形領域に収まりやすくなり、より柔軟な信号整形が可能になる。

【0103】

さらに、実施の形態3にかかる信号整形回路110において、実施の形態2にかかる信号整形回路110のように、IIRフィルタの演算回路112、遅延回路114、バッファ回路115などの利得等を調整可能にしてもよい。これにより、加算器等のリミッタによる高周波成分の減衰を抑えつつ、要求されるエンファシス強度や信号強度を実現することがより容易になる。

【0104】

(実施の形態4)

実施の形態4について、実施の形態1〜3と異なる部分について説明する。

【0105】

図21−1は、実施の形態4にかかる信号整形回路の構成例を示す図である。図21−1において、図16に示した部分と同様の部分については同一の符号を付して説明を省略する。図21−1に示すように、実施の形態4にかかる信号整形回路110は、図16に示した構成に加えて、分岐部2101と、バッファ回路2102と、遅延回路2103と、を備えている。分岐部2101、バッファ回路2102、遅延回路2103および演算回路112は、FIRフィルタになっている。

【0106】

したがって、実施の形態4にかかる信号整形回路110は、IIR方式の信号整形回路の前段にFIRフィルタを設けた構成となっている。具体的には、分岐部2101、バッファ回路2102および遅延回路2103は、入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を演算回路112の第一入力部へ入力する分岐遅延回路である。

【0107】

分岐部2101は、入力部111から出力された信号を分岐する。そして、分岐部2101は、分岐した各信号の一方を分岐信号data1としてバッファ回路2102へ出力する。また、分岐部2101は、分岐した各信号の他方を分岐信号data2として遅延回路2103へ出力する。

【0108】

バッファ回路2102は、分岐部2101から出力された分岐信号data1を出力調整する。バッファ回路2102は、出力調整した分岐信号data1を演算回路112へ出力する。遅延回路2103は、分岐部2101から出力された分岐信号data2を遅延させる。遅延回路2103は、遅延させた分岐信号data2を演算回路112へ出力する。

【0109】

演算回路112は、バッファ回路2102から出力された分岐信号data1と、バッファ回路2102から出力された分岐信号data2と、バッファ回路115から出力された帰還信号data3と、を加算または減算する。演算回路112は、加算または減算した信号を出力信号data4として分岐部113へ出力する。

【0110】

分岐部113は、演算回路112から出力された出力信号data4を分岐し、分岐した出力信号data4の一方を出力部116へ出力する。また、分岐部113は、分岐した出力信号data4の他方を帰還信号data3としてハイパスフィルタ1601へ出力する。ハイパスフィルタ1601は、分岐部113から出力された帰還信号data3の低周波成分を減衰させて遅延回路114へ出力する。

【0111】

遅延回路114は、ハイパスフィルタ1601から出力された帰還信号data3を遅延させてバッファ回路115へ出力する。バッファ回路115は、遅延回路114から出力された帰還信号data3を出力調整して演算回路112へ出力する。

【0112】

(信号整形回路からハイパスフィルタを省いた構成)

図21−2は、図21−1に示した信号整形回路からハイパスフィルタを省いた構成を参考として示す図である。図21−2に参考として示す信号整形回路110は、図21−1に示した信号整形回路110においてハイパスフィルタ1601を省いた構成である。

【0113】

(IIR方式でハイパスフィルタなしの信号整形回路の位相特性)

図22−1は、図1−1に示した信号整形回路の出力信号のアイパターンの一例を示す図である。図22−2は、図1−1に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。図22−1,図22−2において、横軸は繰り返しの時間[ns]を示し、縦軸は信号の強度を示している(以下のアイパターンの図でも同様)。

【0114】

図22−1に示すアイパターン2210は、図1−1に示した信号整形回路110(IIR方式,ハイパスフィルタなし)における出力信号Data3のアイパターンを示している。図22−2に示すアイパターン2220は、図1−1に示した信号整形回路110(IIR方式,ハイパスフィルタなし)における出力信号Data3を用いて発光素子を駆動した場合の光出力のアイパターンを示している。

【0115】

(IIR方式でハイパスフィルタありの信号整形回路の位相特性)

図23−1は、図16に示した信号整形回路の出力信号のアイパターンの一例を示す図である。図23−2は、図16に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。図23−1に示すアイパターン2310は、図16に示した信号整形回路110(IIR方式,ハイパスフィルタあり)における出力信号Data3のアイパターンを示している。図23−2に示すアイパターン2320は、図16に示した信号整形回路110(IIR方式,ハイパスフィルタあり)における出力信号Data3を用いて発光素子を駆動した場合の光出力のアイパターンを示している。

【0116】

(FIR方式とIIR方式でハイパスフィルタなしの信号整形回路の位相特性)

図24−1は、図21−2に示した信号整形回路の出力信号のアイパターンの一例を参考として示す図である。図24−2は、図21−2に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を参考として示す図である。

【0117】

図24−1に示すアイパターン2410は、図21−2に示した信号整形回路110(FIR+IIR方式,ハイパスフィルタなし)における出力信号data4のアイパターンを参考として示している。図24−2に示すアイパターン2420は、図21−2に示した信号整形回路110(FIR+IIR方式,ハイパスフィルタなし)における出力信号data4を用いて発光素子を駆動した場合の光出力のアイパターンを参考として示している。

【0118】

(FIR方式とIIR方式でハイパスフィルタありの信号整形回路の位相特性)

図25−1は、図21−1に示した信号整形回路の出力信号のアイパターンの一例を示す図である。図25−2は、図21−1に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。図25−1に示すアイパターン2510は、図21−1に示した信号整形回路110(FIR+IIR方式,ハイパスフィルタあり)における出力信号data4のアイパターンを示している。図25−2に示すアイパターン2520は、図21−1に示した信号整形回路110(FIR+IIR方式,ハイパスフィルタあり)における出力信号data4を用いて発光素子を駆動した場合の光出力のアイパターンを示している。

【0119】

図22−1,図22−2と図23−1,図23−2とを比較すると、IIR方式の信号整形回路110においてハイパスフィルタ1601を設けても、出力信号Data3および出力信号Data3を用いて発光素子を駆動した場合の光出力の位相特性は特に向上しない。

【0120】

一方、図24−1,図24−2と図25−1,図25−2とを比較すると、FIR方式とIIR方式を組み合わせた信号整形回路110においては、ハイパスフィルタ1601を設けることで各信号の位相特性が向上することが分かる。具体的には、出力信号data4および出力信号data4を用いて発光素子を駆動した場合の光出力の位相特性が向上する。

【0121】

このように、実施の形態4にかかる信号整形回路110によれば、FIR方式とIIR方式を組み合わせ、帰還信号data3の低周波成分を減衰させるフィルタを設ける構成とすることができる。これにより、出力信号data4を用いて発光素子を駆動した場合の光出力の位相特性を向上させることができる。また、実施の形態4にかかる光送信装置600によれば、発光素子610の出力信号の位相特性を向上させることができるため、発光素子610によって送信される信号光の品質をさらに向上させることができる。

【0122】

さらに、実施の形態4にかかる信号整形回路110において、実施の形態2にかかる信号整形回路110のように、IIRフィルタの演算回路112、遅延回路114、バッファ回路115などの利得等を調整可能にしてもよい。これにより、出力信号data4の位相特性を向上させつつ、要求されるエンファシス強度や信号強度を実現することが容易になる。

【0123】

以上説明したように、信号整形回路および光送信装置によれば、柔軟な信号整形を行うことができる。上述した各実施の形態に関し、さらに以下の付記を開示する。

【0124】

(付記1)第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、

を備えることを特徴とする信号整形回路。

【0125】

(付記2)前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタを備えることを特徴とする付記1に記載の信号整形回路。

【0126】

(付記3)入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を前記第一入力部へ入力する分岐遅延回路を備え、

前記演算部は、前記分岐遅延回路によって前記第一入力部へ入力された各信号と、前記フィルタによって前記低周波成分が減衰した第二信号と、を加算または減算することを特徴とする付記2に記載の信号整形回路。

【0127】

(付記4)前記分岐部から出力された信号によって強度変調した信号光を出射する発光素子へ前記各信号の他方を入力することを特徴とする付記1〜3のいずれか一つに記載の信号整形回路。

【0128】

(付記5)前記演算部は、出力する信号の振幅に上限があることを特徴とする付記1〜4のいずれか一つに記載の信号整形回路。

【0129】

(付記6)第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、

前記分岐部によって分岐された各信号の他方によって強度変調した信号光を出射する発光素子と、

を備えることを特徴とする光送信装置。

【0130】

(付記7)第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算して出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号に対して、所定比率を乗じて遅延させる遅延部と、

前記遅延部の前記所定比率を調整可能にする調整部と、

を備えることを特徴とする信号整形回路。

【0131】

(付記8)前記遅延部は、出力する信号の振幅に上限があることを特徴とする付記7に記載の信号整形回路。

【0132】

(付記9)第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタと、

を備えることを特徴とする信号整形回路。

【0133】

(付記10)前記演算部は、前記第一信号と前記第二信号とをそれぞれ重み付けして加算または減算し、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部を備えることを特徴とする付記9に記載の信号整形回路。

【0134】

(付記11)前記遅延部は、前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号に対して、所定比率を乗じて遅延させ、

前記遅延部の前記所定比率を調整可能にする調整部を備えることを特徴とする付記9に記載の信号整形回路。

【0135】

(付記12)入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を前記第一入力部へ入力する分岐遅延回路を備え、

前記演算部は、前記分岐遅延回路によって前記第一入力部へ入力された各信号と、前記フィルタによって前記低周波成分が減衰した第二信号と、を加算または減算することを特徴とする付記9〜11のいずれか一つに記載の信号整形回路。

【符号の説明】

【0136】

Data1 入力信号

Data2,data3 帰還信号

Data3,data4 出力信号

data1,data2 分岐信号

110,120 信号整形回路

111,121,411,412,451,452,511,512,1701 入力部

112,126,400 演算回路

113,122,2101 分岐部

114,123,2103 遅延回路

115,124,125,1321,1322,2102 バッファ回路

116,127,481,482,571,572,1705 出力部

211〜213,221〜223,1411,1412,1511,1512,1901,2001 波形

301,302 エンファシス特性

421,422,461,462,521,522 トランジスタ

431,432,530 電流源

440,540,1704 グランド

471,472,551,552,1703 抵抗

480,560 電源

500 遅延バッファ回路

600 光送信装置

610 発光素子

701 可変演算回路

811,812,821,822,1011,1012 可変電流源

813,823,1021,1022 可変抵抗

901 利得可変遅延回路

1030,1311 スイッチ

1101 入力信号

1102 出力信号

1110 入出力特性

1111 線形領域

1112,1113 非線形領域

1601 ハイパスフィルタ

1702 コンデンサ

2210,2220,2310,2320,2410,2420,2510,2520 アイパターン

【技術分野】

【0001】

本発明は、信号を整形する信号整形回路および光送信装置に関する。

【背景技術】

【0002】

近年の通信分野においては、データ通信量の増大に伴い、ひとつの信号で大量のデータを送信するため、データレートの高速化が進んでいる。高速なデータは、ケーブル、ボード、出力デバイスなどで符号間干渉などの劣化をしやすいため、帯域不足による劣化分を考慮し、信号の符号間干渉を生じやすい部分をあらかじめ強調したエンファシス信号(プリエンファシス信号)が用いられることがある。

【0003】

エンファシス信号の生成手法の一例として、信号を分岐し、分岐した各信号に遅延差を与えて加減算するFIR(Finite Impulse Response:有限インパルス応答)方式が知られている(たとえば、下記特許文献1参照。)。一方、無線通信装置において、IIR(Infinite Impulse Response:無限インパルス応答)方式のフィルタによってバンドパスフィルタを実現する技術が知られている(たとえば、下記非特許文献1参照。)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−88693号公報

【非特許文献】

【0005】

【非特許文献1】Stefan Andersson,Peter Caputa,and Christer Svensson、“A tuned,inductorless,recursive filter LNA in CMOS”、ESSCIRC2002 P.351−354

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述した従来技術では、実現可能なエンファシスの強さが小さいため、要求される信号波形に応じて柔軟な信号整形を行うことが困難であるという問題がある。

【0007】

本発明は、上述した従来技術による問題点を解消するため、柔軟な信号整形を行うことができる信号整形回路および信号整形回路を用いた光送信装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上述した課題を解決し、目的を達成するため、本発明の一側面によれば、第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、を備える信号整形回路および信号整形回路を用いた光送信装置が提案される。

【0009】

また、本発明の別の側面によれば、第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算して出力する演算部と、前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号に対して、所定比率を乗じて遅延させる遅延部と、前記遅延部の前記所定比率を調整可能にする調整部と、を備える信号整形回路および信号整形回路を用いた光送信装置が提案される。

【0010】

また、本発明の別の側面によれば、第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算した信号を出力する演算部と、前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタと、を備える信号整形回路および信号整形回路を用いた光送信装置が提案される。

【発明の効果】

【0011】

本発明の一側面によれば、柔軟な信号整形を行うことができるという効果を奏する。

【図面の簡単な説明】

【0012】

【図1−1】図1−1は、実施の形態1にかかる信号整形回路の構成例を示す図である。

【図1−2】図1−2は、FIR方式の信号整形回路の構成例を参考として示す図である。

【図2】図2は、各方式の信号整形回路における信号の一例を示す図である。

【図3】図3は、各方式の信号整形回路におけるエンファシス特性の一例を示す図である。

【図4】図4は、図1に示した演算回路の構成例を示す図である。

【図5】図5は、図1に示した遅延回路およびバッファ回路の構成例を示す図である。

【図6】図6は、実施の形態1にかかる光送信装置の構成例を示す図である。

【図7】図7は、実施の形態2にかかる信号整形回路の構成例を示す図である。

【図8−1】図8−1は、図7に示した演算回路の構成例を示す図である。

【図8−2】図8−2は、図7に示した演算回路の変形例を示す図である。

【図9】図9は、実施の形態2にかかる信号整形回路の変形例1を示す図である。

【図10】図10は、図9に示した遅延回路およびバッファ回路の構成例を示す図である。

【図11−1】図11−1は、図10に示した遅延バッファ回路の調整前の入出力特性の一例を示す図である。

【図11−2】図11−2は、図10に示した遅延バッファ回路の調整前の信号の一例を示す図である。

【図12−1】図12−1は、図10に示した遅延バッファ回路の調整後の入出力特性の一例を示す図である。

【図12−2】図12−2は、図10に示した遅延バッファ回路の調整後の信号の一例を示す図である。

【図13】図13は、実施の形態2にかかる信号整形回路の変形例2を示す図である。

【図14−1】図14−1は、調整前の帰還信号のシミュレーション結果の一例を示す図である。

【図14−2】図14−2は、調整前の出力信号のシミュレーション結果の一例を示す図である。

【図15−1】図15−1は、調整後の帰還信号のシミュレーション結果の一例を示す図である。

【図15−2】図15−2は、調整後の出力信号のシミュレーション結果の一例を示す図である。

【図16】図16は、実施の形態3にかかる信号整形回路の構成例を示す図である。

【図17】図17は、図16に示したハイパスフィルタの構成例を示す図である。

【図18】図18は、図16に示すハイパスフィルタ通過後の信号を遅延バッファ回路に入力した場合の遅延バッファ回路の入出力特性の一例を示す図である。

【図19】図19は、調整後の帰還信号のシミュレーション結果の一例を示す図である。

【図20】図20は、調整後の出力信号のシミュレーション結果の一例を示す図である。

【図21−1】図21−1は、実施の形態4にかかる信号整形回路の構成例を示す図である。

【図21−2】図21−2は、図21−1に示した信号整形回路からハイパスフィルタを省いた構成を参考として示す図である。

【図22−1】図22−1は、図1−1に示した信号整形回路の出力信号のアイパターンの一例を示す図である。

【図22−2】図22−2は、図1−1に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。

【図23−1】図23−1は、図16に示した信号整形回路の出力信号のアイパターンの一例を示す図である。

【図23−2】図23−2は、図16に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。

【図24−1】図24−1は、図21−2に示した信号整形回路の出力信号のアイパターンの一例を参考として示す図である。

【図24−2】図24−2は、図21−2に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を参考として示す図である。

【図25−1】図25−1は、図21−1に示した信号整形回路の出力信号のアイパターンの一例を示す図である。

【図25−2】図25−2は、図21−1に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。

【発明を実施するための形態】

【0013】

以下に添付図面を参照して、本発明にかかる信号整形回路および光送信装置の実施の形態を詳細に説明する。

【0014】

(実施の形態1)

(信号整形回路の構成)

図1−1は、実施の形態1にかかる信号整形回路の構成例を示す図である。図1−1に示す信号整形回路110は、入力された信号を整形して出力する信号整形回路である。たとえば、信号整形回路110は、VCSEL(Vertical Cavity Surface Emitting Laser:垂直共振器面発光レーザ)などの発光素子へ入力する駆動信号を整形する。ただし、信号整形回路110による整形対象の信号は発光素子の駆動信号に限らない。

【0015】

図1−1に示すように、信号整形回路110は、入力部111と、演算回路112と、分岐部113と、遅延回路114と、バッファ回路115と、出力部116と、を備えている。入力部111には、整形対象の信号が入力される。入力部111へ入力される信号は、たとえば正相信号および逆相信号を含む差動信号である。入力部111は、入力された信号を入力信号Data1として演算回路112へ出力する。

【0016】

演算回路112は、第一入力部と第二入力部を有する。演算回路112の第一入力部には、入力部111から出力された入力信号Data1(第一信号)が入力される。演算回路112の第二入力部には、バッファ回路115から出力された帰還信号Data2(第二信号)が入力される。演算回路112は、入力された入力信号Data1と帰還信号Data2をそれぞれ重み付けして加算または減算する演算部である。そして、演算回路112は、加算または減算した信号を出力信号Data3として分岐部113へ出力する。

【0017】

分岐部113は、演算回路112から出力された出力信号Data3を分岐する。そして、分岐部113は、分岐した出力信号Data3の一方を出力部116へ出力する。また、分岐部113は、分岐した出力信号Data3の他方を帰還信号Data2として遅延回路114へ出力する。

【0018】

遅延回路114は、分岐部113から出力された帰還信号Data2を遅延させる遅延部である。そして、遅延回路114は、遅延させた帰還信号Data2をバッファ回路115へ出力する。バッファ回路115は、遅延回路114から出力された帰還信号Data2を出力調整する。そして、バッファ回路115は、出力調整した信号を帰還信号Data2として演算回路112へ出力する。

【0019】

演算回路112へ出力された帰還信号Data2は、演算回路112の第二入力部へ入力される。このように、遅延回路114、バッファ回路115および出力部116は、分岐部113から出力された帰還信号Data2を演算回路112の第二入力部へ帰還させる帰還部である。出力部116は、分岐部113から出力された出力信号Data3を信号整形回路110の後段へ出力する。

【0020】

これにより、出力信号Data3を帰還信号Data2として帰還させて入力信号Data1に加算または減算するIIR方式によって入力信号Data1を信号整形し、信号整形した信号を出力信号Data3として出力することができる。たとえば、入力信号Data1の特定の高周波成分を強調(エンファシス)したり、入力信号Data1の特定の高周波成分を抑制したりすることができる。以下、信号整形回路110が、入力信号Data1の特定の高周波成分を強調(エンファシス)する例について主に説明する。

【0021】

図1−1においては、バッファ回路115を遅延回路114の後段に設ける構成について図示したが、バッファ回路115を遅延回路114の前段に設ける構成とすることもできる。また、遅延回路114を分岐部113の後段かつバッファ回路115の前段に設ける構成について図示したが、遅延回路114を演算回路112の後段かつ分岐部113の前段に設ける構成とすることもできる。また、バッファ回路115を分岐部113の後段かつ遅延回路114の後段に設ける構成について図示したが、バッファ回路115を演算回路112の後段かつ分岐部113の前段に設ける構成とすることもできる。

【0022】

(FIR方式の信号整形回路の構成例)

図1−2は、FIR方式の信号整形回路の構成例を参考として示す図である。図1−2に示すように、FIR方式の信号整形回路120は、入力部121と、分岐部122と、遅延回路123と、バッファ回路124,125と、演算回路126と、出力部127と、を備えている。

【0023】

入力部121には、整形対象の信号が入力される。入力部121は、入力された信号を分岐部122へ出力する。分岐部122は、入力部121から出力された信号を分岐する。そして、分岐部122は、分岐した各信号の一方を分岐信号D1としてバッファ回路124へ出力する。また、分岐部122は、分岐した各信号の他方を分岐信号D2として遅延回路123へ出力する。

【0024】

遅延回路123は、分岐部122から出力された分岐信号D2を遅延させる。そして、遅延回路123は、遅延させた分岐信号D2をバッファ回路125へ出力する。遅延回路123における遅延時間τは、たとえば図1−1に示した遅延回路114における遅延時間τと同じである。

【0025】

バッファ回路124は、分岐部122から出力された分岐信号D1を出力調整する。そして、バッファ回路124は、出力調整した分岐信号D1を演算回路126へ出力する。バッファ回路125は、遅延回路123から出力された分岐信号D2を出力調整する。そして、バッファ回路125は、出力調整した分岐信号D2を演算回路126へ出力する。

【0026】

演算回路126は、バッファ回路124から出力された分岐信号D1と、バッファ回路125から出力された分岐信号D2と、を加算または減算する。そして、演算回路126は、加算または減算した信号を出力信号D3として出力部127へ出力する。演算回路126における加算または減算の重み付け(加算比)は、たとえば図1−1に示した演算回路112と同じである。出力部127は、演算回路126から出力された信号出力信号D3を出力する。

【0027】

(各方式の信号整形回路における信号)

図2は、各方式の信号整形回路における信号の一例を示す図である。図2において、横軸は時間を示している。波形211〜213は、図1−1に示したIIR方式の信号整形回路110における入力信号Data1、帰還信号Data2および出力信号Data3の各波形を示している。図2では、演算回路112が、入力信号Data1から帰還信号Data2を減算した結果を出力信号Data3として出力する例を示している。

【0028】

波形221〜223は、図1−2に示したFIR方式の信号整形回路120における分岐信号D1、分岐信号D2および出力信号D3の各波形を参考として示している。なお、図2では、演算回路126が、分岐信号D1から分岐信号D2を減算した結果を出力信号D3として出力する例を示している。

【0029】

波形211〜213および波形221〜223に示すように、図1−1に示したIIR方式の信号整形回路110は、図1−2に示したFIR方式の信号整形回路120よりもより高周波成分の強度の大きいエンファシスを信号にかけることができる。これにより、たとえば信号の立ち上がり部分などをより急峻に強調することができる。

【0030】

(各方式の信号整形回路におけるエンファシス特性)

図3は、各方式の信号整形回路におけるエンファシス特性の一例を示す図である。図3において、横軸は信号の周波数[GHz]を示している。縦軸は信号の強度を示している。エンファシス特性301は、図1−1に示したIIR方式の信号整形回路110から出力される出力信号Data3の周波数に対する強度の特性を示している。エンファシス特性302は、図1−2に示したFIR方式の信号整形回路120から出力される出力信号D3の周波数に対する強度の特性を参考として示している。

【0031】

エンファシス特性301,302に示すように、図1−1に示したIIR方式の信号整形回路110は、FIR方式の信号整形回路120よりも特定の高周波成分(たとえば22[GHz]付近の成分)を強調したエンファシス信号を得ることができる。

【0032】

(演算回路の構成)

図4は、図1に示した演算回路の構成例を示す図である。図4に示した演算回路112は、たとえば図4に示す演算回路400によって実現することができる。演算回路400は、入力部411,412と、トランジスタ421,422と、電流源431,432と、グランド440と、を備えている。また、演算回路400は、入力部451,452と、トランジスタ461,462と、抵抗471,472と、電源480と、出力部481,482と、を備えている。

【0033】

入力部411,412(IN1P,IN1N)は、それぞれ入力部111から出力された入力信号Data1の正相信号および逆相信号が入力される第一入力部である。入力部411は、トランジスタ421のゲートに接続されている。入力部412は、トランジスタ422のゲートに接続されている。

【0034】

トランジスタ421のゲートは入力部411に接続されている。トランジスタ421のソースは電流源431に接続されている。トランジスタ421のドレインは抵抗471および出力部482に接続されている。トランジスタ422のゲートは入力部412に接続されている。トランジスタ422のソースは電流源431に接続されている。トランジスタ422のドレインは抵抗472および出力部481に接続されている。電流源431は、一端がトランジスタ421,422の各ソースに接続され、他端がグランド440(VSS)に接続されている。

【0035】

入力部451,452(IN2P,IN2N)は、それぞれバッファ回路115から出力された帰還信号Data2の正相信号および逆相信号が入力される第二入力部である。入力部451は、トランジスタ461のゲートに接続されている。入力部452は、トランジスタ462のゲートに接続されている。

【0036】

トランジスタ461のゲートは入力部451に接続されている。トランジスタ461のソースは電流源432に接続されている。トランジスタ461のドレインは抵抗471および出力部482に接続されている。トランジスタ462のゲートは入力部452に接続されている。トランジスタ462のソースは電流源432に接続されている。トランジスタ462のドレインは抵抗472および出力部481に接続されている。

【0037】

電流源432は、一端がトランジスタ461,462の各ソースに接続され、他端がグランド440(VSS)に接続されている。抵抗471は、一端がトランジスタ421,461の各ドレインに接続され、他端が電源480(VDD)に接続されている。抵抗472は、一端がトランジスタ422,462の各ドレインに接続され、他端が電源480(VDD)に接続されている。

【0038】

出力部481(OUTP)は、トランジスタ422,462からの信号を正相信号として出力する。出力部482(OUTN)は、トランジスタ421,461からの信号を逆相信号として出力する。これにより、入力部111から出力された入力信号Data1と、バッファ回路115から出力された帰還信号Data2と、を加算した信号を出力信号Data3として出力することができる。

【0039】

また、正相信号と逆相信号とを入れ替えることで、入力信号Data1と帰還信号Data2とを減算することもできる。たとえば、入力部451に帰還信号Data2の逆相信号を入力し、入力部452に帰還信号Data2の正相信号を入力することで、入力信号Data1から帰還信号Data2を減算することができる。

【0040】

また、加算または減算における入力信号Data1の重みは、たとえば電流源431の電流値などによって決まる。また、加算または減算における帰還信号Data2との重みは、たとえば電流源432の電流値などによって決まる。トランジスタ421,422,461,462のそれぞれはたとえばFET(Field Effect Transistor:電界効果トランジスタ)である。

【0041】

(遅延回路およびバッファ回路の構成)

図5は、図1に示した遅延回路およびバッファ回路の構成例を示す図である。図4に示した遅延回路114およびバッファ回路115のそれぞれは、たとえば図5に示す遅延バッファ回路500によって実現することができる。遅延バッファ回路500は、入力部511,512と、トランジスタ521,522と、電流源530と、グランド540と、抵抗551,552と、電源560と、出力部571,572と、を備えている。

【0042】

入力部511,512(INP,INN)には、それぞれ遅延バッファ回路500へ入力された帰還信号Data2の正相信号および逆相信号が入力される。入力部511は、トランジスタ521のゲートに接続されている。入力部512は、トランジスタ522のゲートに接続されている。

【0043】

トランジスタ521,522のそれぞれはたとえばFETである。トランジスタ521のゲートは入力部511に接続されている。トランジスタ521のソースは電流源530に接続されている。トランジスタ521のドレインは抵抗551および出力部572に接続されている。トランジスタ522のゲートは入力部512に接続されている。トランジスタ522のソースは電流源530に接続されている。トランジスタ522のドレインは抵抗552および出力部571に接続されている。

【0044】

電流源530は、一端がトランジスタ521,522の各ソースに接続され、他端がグランド540(VSS)に接続されている。抵抗551は、一端がトランジスタ521のドレインに接続され、他端が電源560(VDD)に接続されている。抵抗552は、一端がトランジスタ522のドレインに接続され、他端が電源560に接続されている。

【0045】

出力部571は、トランジスタ522からの信号を正相信号として出力する。出力部572は、トランジスタ521からの信号を逆相信号として出力する。これにより、遅延バッファ回路500へ入力された帰還信号Data2に遅延と利得を与えて出力することができる。遅延バッファ回路500による帰還信号Data2の利得は、たとえば電流源530における電流の大きさによって決まる。

【0046】

(光送信装置の構成)

図6は、実施の形態1にかかる光送信装置の構成例を示す図である。図6に示す光送信装置600は、入力された駆動信号に基づく信号光を送信する。具体的には、光送信装置600は、図1−1に示した信号整形回路110と、発光素子610と、を備えている。信号整形回路110は、光送信装置600へ入力された駆動信号を整形し、整形した駆動信号を発光素子610へ出力する。

【0047】

発光素子610は、たとえばVCSELなどのLD(Laser Diode:レーザダイオード)である。発光素子610は、一端が信号整形回路110に接続され、他端が接地されている。発光素子610は、信号整形回路110から出力された駆動信号に基づいて強度変調(直接変調)した信号光を出射する。これにより、光送信装置600は、入力された駆動信号に基づく信号光を送信することができる。

【0048】

このように、実施の形態1にかかる信号整形回路110によれば、出力信号を分岐して帰還させた信号を入力信号に加算または減算するIIRフィルタを用いることで、より柔軟な信号整形が可能になる。また、実施の形態1にかかる光送信装置600によれば、信号整形回路110によって駆動信号を柔軟に整形することができる。このため、要求される信号光の波形や発光素子610の特性に応じて駆動信号を柔軟に整形し、品質の高い信号光を送信することができる。

【0049】

(実施の形態2)

実施の形態2について、実施の形態1と異なる部分について説明する。

【0050】

(信号整形回路の構成)

図7は、実施の形態2にかかる信号整形回路の構成例を示す図である。図7において、図1−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図7に示すように、実施の形態2にかかる信号整形回路110は、図1−1に示した演算回路112に代えて可変演算回路701を備えている。

【0051】

可変演算回路701は、図1−1に示した演算回路112に、加算または減算における入力信号Data1(第一信号)および帰還信号Data2(第二信号)の各重みの少なくとも一方を調整可能にする調整部を設けた演算回路(たとえば図8−1,図8−2参照)である。たとえば、可変演算回路701は、入力信号Data1に第一比率を乗じた信号と、帰還信号Data2に第二比率を乗じた信号と、を加算また減算した信号を出力し、第一比率および第二比率の少なくとも一方を調整可能にした演算回路である。

【0052】

(演算回路の構成)

図8−1は、図7に示した演算回路の構成例を示す図である。図8−1において、図4に示した部分と同様の部分については同一の符号を付して説明を省略する。図8−1に示すように、実施の形態2にかかる可変演算回路701は、図4に示した電流源432に代えて、可変電流源811,812および可変抵抗813を備えている。

【0053】

可変電流源811,812は、それぞれ電流の大きさが可変の電流源である。可変電流源811は、一端がトランジスタ461のソースに接続され、他端がグランド440に接続されている。可変電流源812は、一端がトランジスタ462のソースに接続され、他端がグランド440に接続されている。これにより、トランジスタ461,462のソース電流を可変にすることができる。可変抵抗813は、抵抗値が可変の抵抗である。また、可変抵抗813は、一端がトランジスタ461のソースに接続されており、一端がトランジスタ462のソースに接続されている。

【0054】

ここで、演算回路400のエンファシス加算利得(帰還信号Data2の加算または減算の重み)は、たとえば(Gm×Ra)/(1+Gm×Rb)によって示すことができる。Gmはトランジスタ461,462のコンダクタンスである。Raは抵抗471,472の抵抗値である。Rbはトランジスタ461,462のソースの合成インピーダンス(可変抵抗813の抵抗値)である。

【0055】

したがって、エンファシス加算利得は、差動回路のトランジスタ461,462のソースの合成インピーダンスRbおよびトランジスタ461,462のコンダクタンスGmの大きさに依存する。そして、コンダクタンスGmはトランジスタ461,462のソース電流に依存する。このため、可変電流源811,812によってトランジスタ461,462のソース電流を可変にすることでエンファシス加算利得を調整することができる。

【0056】

また、可変抵抗813によりトランジスタ461,462のソースの合成インピーダンスRbを可変にすることでエンファシス加算利得を調整することができる。たとえば、可変抵抗813の抵抗値Rbを大きくすればエンファシス加算利得が小さくなり、抵抗値Rbを小さくすればエンファシス加算利得が大きくなる。

【0057】

図8−2は、図7に示した演算回路の変形例を示す図である。図8−2において、図8−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図8−2に示すように、実施の形態2にかかる可変演算回路701は、図8−1に示した電流源431に代えて、可変電流源821,822および可変抵抗823を備えている。

【0058】

可変電流源821,822は、それぞれ電流の大きさが可変の電流源である。可変電流源821は、一端がトランジスタ421のソースに接続され、他端がグランド440に接続されている。可変電流源822は、一端がトランジスタ422のソースに接続され、他端がグランド440に接続されている。これにより、トランジスタ421,422のソース電流を可変にすることができる。可変抵抗823は、抵抗値が可変の抵抗である。また、可変抵抗823は、一端がトランジスタ421のソースに接続されており、一端がトランジスタ422のソースに接続されている。

【0059】

これにより、帰還信号Data2の加算または減算の重みだけでなく、入力信号Data1の加算または減算の重みも調整することができる。また、演算回路400は、図4に示した構成において、電流源431に代えて、可変電流源821,822および可変抵抗823を備える構成としてもよい。この場合は、入力信号Data1の加算または減算の重みを調整することができる。このように、実施の形態2にかかる可変演算回路701は、加算または減算における入力信号Data1および帰還信号Data2の各重みの少なくとも一方を調整可能である。

【0060】

(信号整形回路の変形例1)

図9は、実施の形態2にかかる信号整形回路の変形例1を示す図である。図9に示すように、実施の形態2にかかる信号整形回路110は、図1−1に示した遅延回路114に代えて利得可変遅延回路901を備えている。

【0061】

利得可変遅延回路901は、図1−1に示した遅延回路114に、帰還信号Data2に対する利得を調整可能にする調整部を設けた演算回路(たとえば図10参照)である。たとえば、利得可変遅延回路901は、帰還信号Data2に対して、所定比率を乗じて遅延させて出力し、所定比率を調整可能にした遅延回路である。また、バッファ回路115に代えて、帰還信号Data2に対する利得を調整可能にする調整部を設けたバッファ回路を設けてもよい。

【0062】

(遅延回路およびバッファ回路の構成)

図10は、図9に示した遅延回路およびバッファ回路の構成例を示す図である。図10において、図5に示した部分と同様の部分については同一の符号を付して説明を省略する。図9に示した利得可変遅延回路901は、図10に示す遅延バッファ回路500によって実現することができる。図10に示す遅延バッファ回路500は、図5に示した電流源530に代えて、可変電流源1011,1012、可変抵抗1021,1022およびスイッチ1030を備えている。

【0063】

可変電流源1011,1012のそれぞれは、電流の大きさが可変の電流源である。可変電流源1011は、一端がトランジスタ521のソースに接続され、他端がグランド540に接続されている。可変電流源1012は、一端がトランジスタ522のソースに接続され、他端がグランド540に接続されている。

【0064】

可変抵抗1021,1022のそれぞれは、抵抗値が可変の抵抗である。可変抵抗1021は、一端がトランジスタ521のソースに接続され、他端がトランジスタ522のソースに接続されている。可変抵抗1022は、一端がスイッチ1030に接続され、他端がトランジスタ522のソースに接続されている。スイッチ1030は、オン状態においては可変抵抗1022と可変電流源1011とを接続し、オフ状態においては可変抵抗1022と可変電流源1011とを切断する。

【0065】

可変電流源1011,1012の電流を変化させることで、遅延バッファ回路500における帰還信号Data2への利得を調整することができる。また、スイッチ1030のオン/オフを切り替えることによっても遅延バッファ回路500における帰還信号Data2への利得を調整することができる。

【0066】

なお、遅延バッファ回路500において、可変抵抗1021,1022およびスイッチ1030に代えて、抵抗値が固定の抵抗を設けてもよい。この場合も、可変電流源1011,1012の電流を変化させることで、遅延バッファ回路500における帰還信号Data2への利得を調整することができる。

【0067】

また、遅延バッファ回路500において、可変電流源1011,1012に代えて、電流の大きさが固定の電流源を設けてもよい。この場合も、スイッチ1030のオン/オフを切り替えることによっても遅延バッファ回路500における帰還信号Data2への利得を調整することができる。

【0068】

(遅延バッファ回路の調整前の入出力特性)

図11−1は、図10に示した遅延バッファ回路の調整前の入出力特性の一例を示す図である。図11−1において、横軸は、遅延バッファ回路500への入力信号1101の振幅(入力振幅)を示している。縦軸は、遅延バッファ回路500からの出力信号1102の振幅(出力振幅)を示している。入出力特性1110は、遅延バッファ回路500における入力振幅に対する出力振幅の特性を示している。

【0069】

入出力特性1110は、入力振幅の増加に対して出力振幅がほぼ線形に増加する線形領域1111を有する。また、入出力特性1110における線形領域1111よりそれぞれ低振幅側および高振幅側の非線形領域1112,1113は、入力振幅の増加に対して出力振幅がほぼ一定となる領域である。このように、遅延バッファ回路500には、出力する信号の振幅に上限がある。

【0070】

線形領域1111における利得(入力振幅に対する出力振幅の変化量)は、たとえば可変電流源1011,1012の電流の大きさやスイッチ1030のオン/オフの状態によって決まる。図11−1に示す例では、線形領域1111における利得が比較的大きく設定されている。この場合は、線形領域1111の幅が相対的に小さくなる。

【0071】

このため、入力信号1101の振幅が線形領域1111に収まらなくなっている。したがって、入力信号1101の高周波成分が非線形領域1112,1113に現れてリミッタがかかり、出力信号1102には高周波成分が含まれなくなる。このように、入力信号1101の振幅に対して線形領域1111が狭い場合は、出力信号1102(帰還信号Data2)の高周波成分が失われ、エンファシスが十分に効かなくなる。

【0072】

一方、線形領域1111における利得が小さくなり過ぎると、入力信号1101の振幅は線形領域1111に収まるが、出力信号1102の振幅が小さくなる。このため、たとえば、入力信号Data1に対する帰還信号Data2の加算または減算の比率が小さくなり、十分なエンファシスの強度が得られなくなる。また、たとえば、出力信号Data3の信号強度(振幅)を十分に大きくすることができなくなる。

【0073】

図11−1においては、遅延バッファ回路500について説明したが、演算回路400にも同様に出力する信号の振幅に上限がある。したがって、演算回路400においても、たとえば帰還信号Data2が線形領域1111に収まらなくなると、十分なエンファシスの強度が得られなくなったり、出力信号Data3の信号強度(振幅)を十分に大きくすることができなくなったりする。

【0074】

なお、従来の無線通信装置でバンドパスフィルタとして用いられるIIR方式のフィルタにおいては、フィルタとして用いられているため、エンファシスの強度や出力信号の強度を調整することが求められない。このため、従来のIIR方式のフィルタにおいては、たとえば、演算回路や遅延回路が入出力特性の線形領域のみで動作するように設計すればよく、上記のような信号が線形領域に収まらなくなるという問題がなかった。

【0075】

(遅延バッファ回路の調整前の信号)

図11−2は、図10に示した遅延バッファ回路の調整前の信号の一例を示す図である。図11−2において、図2に示した部分と同様の部分については同一の符号を付して説明を省略する。図11−1に示したように入力信号1101の振幅が線形領域1111に収まっていない場合は、波形212に示すように出力信号1102(帰還信号Data2)の高周波成分が失われる。このため、波形213に示すように、出力信号Data3に対してエンファシスが十分に効かなくなることがある。

【0076】

このように、IIR方式のフィルタをエンファシスに用いた場合においては、エンファシス信号を遅延して帰還させる際、演算回路112、遅延回路114、バッファ回路115などの出力のリミッタにより高周波成分が失われることがある。その結果、IIR方式ならではの特定の周波数で急峻なエンファシス信号(たとえば図2に示した波形213)が得られないことがある。これに対して、実施の形態2にかかる信号整形回路110は、演算回路400や遅延バッファ回路500における利得等を可変にする。

【0077】

(遅延バッファ回路の調整後の入出力特性)

図12−1は、図10に示した遅延バッファ回路の調整後の入出力特性の一例を示す図である。図12−1において、図11−1に示した部分と同様の部分については同一の符号を付して説明を省略する。実施の形態2にかかる遅延バッファ回路500は、たとえば可変電流源1011,1012の電流の大きさやスイッチ1030の状態によって、線形領域1111における利得を調整することができる。

【0078】

図12−1に示す例では、線形領域1111における利得が図11−1の場合より小さく設定されている。この場合は、線形領域1111の幅が相対的に大きくなる。これにより、入力信号1101の振幅が線形領域1111に収まっている。したがって、入力信号1101の高周波成分が線形領域1111に含まれるためリミッタがかからず、出力信号1102に高周波成分が含まれるようになる。

【0079】

このように、可変電流源1011,1012の電流の大きさやスイッチ1030の状態によって、入力信号1101の振幅が線形領域1111に収まるようにすることで、出力信号1102(帰還信号Data2)の高周波成分を維持することができる。このため、信号に対して強いエンファシスをかけることができる。たとえば、入力信号1101の振幅が線形領域1111の90%程度の振幅になるように調整することで、効率よく信号にエンファシスをかけることができる。

【0080】

また、可変電流源1011,1012の電流の大きさやスイッチ1030の状態によって、線形領域1111における利得が小さくなり過ぎないようにすることで、出力信号1102の振幅が小さくなり過ぎることを回避することができる。このため、十分なエンファシスの強度が得られなかったり、信号強度(振幅)を十分に大きくすることができなかったりすることを回避することができる。

【0081】

(遅延バッファ回路の調整後の信号)

図12−2は、図10に示した遅延バッファ回路の調整後の信号の一例を示す図である。図12−2において、図2に示した部分と同様の部分については同一の符号を付して説明を省略する。図12−1に示したように入力信号1101の振幅が線形領域1111に収まっている場合は、波形212に示すように出力信号1102(帰還信号Data2)の高周波成分が維持される。このため、波形213に示すように、出力信号Data3に対して強いエンファシスが効くようになる。

【0082】

(信号整形回路の変形例2)

図13は、実施の形態2にかかる信号整形回路の変形例2を示す図である。図13において、図1−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図13に示すように、実施の形態2にかかる信号整形回路110は、図1−1に示したバッファ回路115に代えて、スイッチ1311およびバッファ回路1321,1322を備えていてもよい。

【0083】

遅延回路114は、遅延させた信号をスイッチ1311へ出力する。スイッチ1311は、遅延回路114から出力された信号をバッファ回路1321へ出力する第一状態と、遅延回路114から出力された信号をバッファ回路1322へ出力する第二状態と、に切替可能な経路切替スイッチである。

【0084】

バッファ回路1321,1322のそれぞれは、スイッチ1311から出力された信号を出力調整して演算回路112へ出力する。また、バッファ回路1321,1322は、互いに異なる利得によって信号を増幅する。バッファ回路1321,1322の各構成例は、たとえば図5に示した遅延バッファ回路500と同様である。これにより、スイッチ1311の切替により、帰還信号Data2に対する出力を変化させることができる。

【0085】

(調整前の各信号のシミュレーション結果)

図14−1は、調整前の帰還信号のシミュレーション結果の一例を示す図である。図14−2は、調整前の出力信号のシミュレーション結果の一例を示す図である。図14−1,図14−2において、横軸は時間[ns]を示し、縦軸は信号の強度を示している。

【0086】

図14−1に示す波形1411は、可変演算回路701や利得可変遅延回路901における利得の調整前の帰還信号Data2の波形である。図14−2に示す波形1412は、可変演算回路701や利得可変遅延回路901における利得の調整前の出力信号Data3の波形である。波形1411,1412に示すように、可変演算回路701や利得可変遅延回路901における利得の調整前は、帰還信号Data2および出力信号Data3の高周波成分が小さくなっていることが分かる。

【0087】

(調整後の各信号のシミュレーション結果)

図15−1は、調整後の帰還信号のシミュレーション結果の一例を示す図である。図15−2は、調整後の出力信号のシミュレーション結果の一例を示す図である。図15−1,図15−2において、横軸は時間[ns]を示し、縦軸は信号の強度を示している。

【0088】

図15−1に示す波形1511は、可変演算回路701や利得可変遅延回路901における利得の調整後の帰還信号Data2の波形である。図15−2に示す波形1512は、可変演算回路701や利得可変遅延回路901における利得の調整後の出力信号Data3の波形である。波形1511,1512に示すように、可変演算回路701や利得可変遅延回路901における利得の調整後は、帰還信号Data2および出力信号Data3の高周波成分が大きくなり、強いエンファシスがかかっていることが分かる。

【0089】

このように、実施の形態2にかかる信号整形回路110によれば、IIRフィルタの加算器等の利得を調整可能にすることで、加算器等のリミッタによる高周波成分の減衰を抑えつつ、要求されるエンファシス強度や信号強度を実現することが可能になる。これにより、より柔軟な信号整形を行うことができる。

【0090】

(実施の形態3)

実施の形態3について、実施の形態1,2と異なる部分について説明する。

【0091】

(信号整形回路の構成)

図16は、実施の形態3にかかる信号整形回路の構成例を示す図である。図16において、図1−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図16に示すように、実施の形態3にかかる信号整形回路110は、図1−1に示した構成に加えてハイパスフィルタ1601(HPF:High Pass Filter)を備えている。ハイパスフィルタ1601は、たとえば分岐部113と遅延回路114との間に設けられている。

【0092】

ハイパスフィルタ1601は、分岐部113から出力された帰還信号Data2の所定の周波数以下の低周波成分を減衰させるフィルタである。ハイパスフィルタ1601は、低周波成分を減衰させた帰還信号Data2を遅延回路114へ出力する。遅延回路114は、ハイパスフィルタ1601から出力された帰還信号Data2を遅延させる。

【0093】

なお、図16においてはハイパスフィルタ1601を分岐部113と遅延回路114との間に設ける構成を図示したが、ハイパスフィルタ1601を遅延回路114とバッファ回路115の間に設ける構成としてもよい。また、ハイパスフィルタ1601をバッファ回路115と演算回路112との間に設ける構成としてもよい。

【0094】

(ハイパスフィルタの構成)

図17は、図16に示したハイパスフィルタの構成例を示す図である。図17に示すように、ハイパスフィルタ1601は、たとえば、入力部1701と、コンデンサ1702と、抵抗1703と、グランド1704と、出力部1705と、を備えている。入力部1701には、分岐部113から出力された出力信号Data3が入力される。

【0095】

入力部1701(IN)には、ハイパスフィルタ1601へ入力された帰還信号Data2が入力される。コンデンサ1702は、一端が入力部1701に接続され、他端が抵抗1703および出力部1705に接続されている。抵抗1703は、一端が出力部1705に接続され、他端がグランド1704(VSS)に接続されている。

【0096】

出力部1705(OUT)は、入力された信号をハイパスフィルタ1601の後段へ出力する。これにより、入力部1701へ入力された帰還信号Data2に含まれる低周波成分を減衰させ、低周波成分を減衰させた帰還信号Data2を出力することができる。

【0097】

(遅延バッファ回路の入出力特性)

図18は、図16に示すハイパスフィルタ通過後の信号を遅延バッファ回路に入力した場合の遅延バッファ回路の入出力特性の一例を示す図である。図18において、図11−1に示した部分と同様の部分については同一の符号を付して説明を省略する。図16に示したように、ハイパスフィルタ1601によって帰還信号Data2の低周波成分を減衰させることで、帰還信号Data2の振幅が小さくなる。

【0098】

このため、図18に示すように、入力信号1101(帰還信号Data2)の高周波成分が線形領域1111に収まりやすくなる。このため、入力信号1101の高周波成分が線形領域1111に収まるようにしつつ、線形領域1111の利得をより大きくすることが可能になる。

【0099】

このように、ハイパスフィルタ1601を設けることで、線形性の高い線形領域1111に高周波エンファシス信号を割り当てることができるため、入力信号1101の振幅依存および出力信号1102の振幅依存が小さくなる。このため、効率よく高周波エンファシス成分を遅延させて帰還させることができる。

【0100】

(調整後の帰還信号のシミュレーション結果)

図19は、調整後の帰還信号のシミュレーション結果の一例を示す図である。図20は、調整後の出力信号のシミュレーション結果の一例を示す図である。図19,図20において、横軸は時間[ns]を示し、縦軸は信号の強度を示している。

【0101】

図19に示す波形1901は、可変演算回路701や利得可変遅延回路901における利得の調整後の帰還信号Data2の波形である。図20に示す波形2001は、可変演算回路701や利得可変遅延回路901における利得の調整後の出力信号Data3の波形である。波形1901,2001に示すように、ハイパスフィルタ1601を設けることで、図15−1,図15−2に示した例よりも帰還信号Data2および出力信号Data3の高周波成分がさらに大きくなり、より強いエンファシスがかかっていることが分かる。

【0102】

このように、実施の形態3にかかる信号整形回路110によれば、帰還信号Data2の低周波成分を減衰させるハイパスフィルタ1601を設けることで、帰還信号Data2の振幅を小さくすることができる。これにより、帰還信号Data2の振幅が加算回路等の入出力特性の線形領域に収まりやすくなり、より柔軟な信号整形が可能になる。

【0103】

さらに、実施の形態3にかかる信号整形回路110において、実施の形態2にかかる信号整形回路110のように、IIRフィルタの演算回路112、遅延回路114、バッファ回路115などの利得等を調整可能にしてもよい。これにより、加算器等のリミッタによる高周波成分の減衰を抑えつつ、要求されるエンファシス強度や信号強度を実現することがより容易になる。

【0104】

(実施の形態4)

実施の形態4について、実施の形態1〜3と異なる部分について説明する。

【0105】

図21−1は、実施の形態4にかかる信号整形回路の構成例を示す図である。図21−1において、図16に示した部分と同様の部分については同一の符号を付して説明を省略する。図21−1に示すように、実施の形態4にかかる信号整形回路110は、図16に示した構成に加えて、分岐部2101と、バッファ回路2102と、遅延回路2103と、を備えている。分岐部2101、バッファ回路2102、遅延回路2103および演算回路112は、FIRフィルタになっている。

【0106】

したがって、実施の形態4にかかる信号整形回路110は、IIR方式の信号整形回路の前段にFIRフィルタを設けた構成となっている。具体的には、分岐部2101、バッファ回路2102および遅延回路2103は、入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を演算回路112の第一入力部へ入力する分岐遅延回路である。

【0107】

分岐部2101は、入力部111から出力された信号を分岐する。そして、分岐部2101は、分岐した各信号の一方を分岐信号data1としてバッファ回路2102へ出力する。また、分岐部2101は、分岐した各信号の他方を分岐信号data2として遅延回路2103へ出力する。

【0108】

バッファ回路2102は、分岐部2101から出力された分岐信号data1を出力調整する。バッファ回路2102は、出力調整した分岐信号data1を演算回路112へ出力する。遅延回路2103は、分岐部2101から出力された分岐信号data2を遅延させる。遅延回路2103は、遅延させた分岐信号data2を演算回路112へ出力する。

【0109】

演算回路112は、バッファ回路2102から出力された分岐信号data1と、バッファ回路2102から出力された分岐信号data2と、バッファ回路115から出力された帰還信号data3と、を加算または減算する。演算回路112は、加算または減算した信号を出力信号data4として分岐部113へ出力する。

【0110】

分岐部113は、演算回路112から出力された出力信号data4を分岐し、分岐した出力信号data4の一方を出力部116へ出力する。また、分岐部113は、分岐した出力信号data4の他方を帰還信号data3としてハイパスフィルタ1601へ出力する。ハイパスフィルタ1601は、分岐部113から出力された帰還信号data3の低周波成分を減衰させて遅延回路114へ出力する。

【0111】

遅延回路114は、ハイパスフィルタ1601から出力された帰還信号data3を遅延させてバッファ回路115へ出力する。バッファ回路115は、遅延回路114から出力された帰還信号data3を出力調整して演算回路112へ出力する。

【0112】

(信号整形回路からハイパスフィルタを省いた構成)

図21−2は、図21−1に示した信号整形回路からハイパスフィルタを省いた構成を参考として示す図である。図21−2に参考として示す信号整形回路110は、図21−1に示した信号整形回路110においてハイパスフィルタ1601を省いた構成である。

【0113】

(IIR方式でハイパスフィルタなしの信号整形回路の位相特性)

図22−1は、図1−1に示した信号整形回路の出力信号のアイパターンの一例を示す図である。図22−2は、図1−1に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。図22−1,図22−2において、横軸は繰り返しの時間[ns]を示し、縦軸は信号の強度を示している(以下のアイパターンの図でも同様)。

【0114】

図22−1に示すアイパターン2210は、図1−1に示した信号整形回路110(IIR方式,ハイパスフィルタなし)における出力信号Data3のアイパターンを示している。図22−2に示すアイパターン2220は、図1−1に示した信号整形回路110(IIR方式,ハイパスフィルタなし)における出力信号Data3を用いて発光素子を駆動した場合の光出力のアイパターンを示している。

【0115】

(IIR方式でハイパスフィルタありの信号整形回路の位相特性)

図23−1は、図16に示した信号整形回路の出力信号のアイパターンの一例を示す図である。図23−2は、図16に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。図23−1に示すアイパターン2310は、図16に示した信号整形回路110(IIR方式,ハイパスフィルタあり)における出力信号Data3のアイパターンを示している。図23−2に示すアイパターン2320は、図16に示した信号整形回路110(IIR方式,ハイパスフィルタあり)における出力信号Data3を用いて発光素子を駆動した場合の光出力のアイパターンを示している。

【0116】

(FIR方式とIIR方式でハイパスフィルタなしの信号整形回路の位相特性)

図24−1は、図21−2に示した信号整形回路の出力信号のアイパターンの一例を参考として示す図である。図24−2は、図21−2に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を参考として示す図である。

【0117】

図24−1に示すアイパターン2410は、図21−2に示した信号整形回路110(FIR+IIR方式,ハイパスフィルタなし)における出力信号data4のアイパターンを参考として示している。図24−2に示すアイパターン2420は、図21−2に示した信号整形回路110(FIR+IIR方式,ハイパスフィルタなし)における出力信号data4を用いて発光素子を駆動した場合の光出力のアイパターンを参考として示している。

【0118】

(FIR方式とIIR方式でハイパスフィルタありの信号整形回路の位相特性)

図25−1は、図21−1に示した信号整形回路の出力信号のアイパターンの一例を示す図である。図25−2は、図21−1に示した信号整形回路の出力信号を用いて発光素子を駆動した場合の光出力のアイパターンの一例を示す図である。図25−1に示すアイパターン2510は、図21−1に示した信号整形回路110(FIR+IIR方式,ハイパスフィルタあり)における出力信号data4のアイパターンを示している。図25−2に示すアイパターン2520は、図21−1に示した信号整形回路110(FIR+IIR方式,ハイパスフィルタあり)における出力信号data4を用いて発光素子を駆動した場合の光出力のアイパターンを示している。

【0119】

図22−1,図22−2と図23−1,図23−2とを比較すると、IIR方式の信号整形回路110においてハイパスフィルタ1601を設けても、出力信号Data3および出力信号Data3を用いて発光素子を駆動した場合の光出力の位相特性は特に向上しない。

【0120】

一方、図24−1,図24−2と図25−1,図25−2とを比較すると、FIR方式とIIR方式を組み合わせた信号整形回路110においては、ハイパスフィルタ1601を設けることで各信号の位相特性が向上することが分かる。具体的には、出力信号data4および出力信号data4を用いて発光素子を駆動した場合の光出力の位相特性が向上する。

【0121】

このように、実施の形態4にかかる信号整形回路110によれば、FIR方式とIIR方式を組み合わせ、帰還信号data3の低周波成分を減衰させるフィルタを設ける構成とすることができる。これにより、出力信号data4を用いて発光素子を駆動した場合の光出力の位相特性を向上させることができる。また、実施の形態4にかかる光送信装置600によれば、発光素子610の出力信号の位相特性を向上させることができるため、発光素子610によって送信される信号光の品質をさらに向上させることができる。

【0122】

さらに、実施の形態4にかかる信号整形回路110において、実施の形態2にかかる信号整形回路110のように、IIRフィルタの演算回路112、遅延回路114、バッファ回路115などの利得等を調整可能にしてもよい。これにより、出力信号data4の位相特性を向上させつつ、要求されるエンファシス強度や信号強度を実現することが容易になる。

【0123】

以上説明したように、信号整形回路および光送信装置によれば、柔軟な信号整形を行うことができる。上述した各実施の形態に関し、さらに以下の付記を開示する。

【0124】

(付記1)第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、

を備えることを特徴とする信号整形回路。

【0125】

(付記2)前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタを備えることを特徴とする付記1に記載の信号整形回路。

【0126】

(付記3)入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を前記第一入力部へ入力する分岐遅延回路を備え、

前記演算部は、前記分岐遅延回路によって前記第一入力部へ入力された各信号と、前記フィルタによって前記低周波成分が減衰した第二信号と、を加算または減算することを特徴とする付記2に記載の信号整形回路。

【0127】

(付記4)前記分岐部から出力された信号によって強度変調した信号光を出射する発光素子へ前記各信号の他方を入力することを特徴とする付記1〜3のいずれか一つに記載の信号整形回路。

【0128】

(付記5)前記演算部は、出力する信号の振幅に上限があることを特徴とする付記1〜4のいずれか一つに記載の信号整形回路。

【0129】

(付記6)第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、

前記分岐部によって分岐された各信号の他方によって強度変調した信号光を出射する発光素子と、

を備えることを特徴とする光送信装置。

【0130】

(付記7)第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算して出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号に対して、所定比率を乗じて遅延させる遅延部と、

前記遅延部の前記所定比率を調整可能にする調整部と、

を備えることを特徴とする信号整形回路。

【0131】

(付記8)前記遅延部は、出力する信号の振幅に上限があることを特徴とする付記7に記載の信号整形回路。

【0132】

(付記9)第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタと、

を備えることを特徴とする信号整形回路。

【0133】

(付記10)前記演算部は、前記第一信号と前記第二信号とをそれぞれ重み付けして加算または減算し、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部を備えることを特徴とする付記9に記載の信号整形回路。

【0134】

(付記11)前記遅延部は、前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号に対して、所定比率を乗じて遅延させ、

前記遅延部の前記所定比率を調整可能にする調整部を備えることを特徴とする付記9に記載の信号整形回路。

【0135】

(付記12)入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を前記第一入力部へ入力する分岐遅延回路を備え、

前記演算部は、前記分岐遅延回路によって前記第一入力部へ入力された各信号と、前記フィルタによって前記低周波成分が減衰した第二信号と、を加算または減算することを特徴とする付記9〜11のいずれか一つに記載の信号整形回路。

【符号の説明】

【0136】

Data1 入力信号

Data2,data3 帰還信号

Data3,data4 出力信号

data1,data2 分岐信号

110,120 信号整形回路

111,121,411,412,451,452,511,512,1701 入力部

112,126,400 演算回路

113,122,2101 分岐部

114,123,2103 遅延回路

115,124,125,1321,1322,2102 バッファ回路

116,127,481,482,571,572,1705 出力部

211〜213,221〜223,1411,1412,1511,1512,1901,2001 波形

301,302 エンファシス特性

421,422,461,462,521,522 トランジスタ

431,432,530 電流源

440,540,1704 グランド

471,472,551,552,1703 抵抗

480,560 電源

500 遅延バッファ回路

600 光送信装置

610 発光素子

701 可変演算回路

811,812,821,822,1011,1012 可変電流源

813,823,1021,1022 可変抵抗

901 利得可変遅延回路

1030,1311 スイッチ

1101 入力信号

1102 出力信号

1110 入出力特性

1111 線形領域

1112,1113 非線形領域

1601 ハイパスフィルタ

1702 コンデンサ

2210,2220,2310,2320,2410,2420,2510,2520 アイパターン

【特許請求の範囲】

【請求項1】

第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、

を備えることを特徴とする信号整形回路。

【請求項2】

前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタを備えることを特徴とする請求項1に記載の信号整形回路。

【請求項3】

入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を前記第一入力部へ入力する分岐遅延回路を備え、

前記演算部は、前記分岐遅延回路によって前記第一入力部へ入力された各信号と、前記フィルタによって前記低周波成分が減衰した第二信号と、を加算または減算することを特徴とする請求項2に記載の信号整形回路。

【請求項4】

第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、

前記分岐部によって分岐された各信号の他方によって強度変調した信号光を出射する発光素子と、

を備えることを特徴とする光送信装置。

【請求項5】

第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算して出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号に対して、所定比率を乗じて遅延させる遅延部と、

前記遅延部の前記所定比率を調整可能にする調整部と、

を備えることを特徴とする信号整形回路。

【請求項6】

第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタと、

を備えることを特徴とする信号整形回路。

【請求項7】

入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を前記第一入力部へ入力する分岐遅延回路を備え、

前記演算部は、前記分岐遅延回路によって前記第一入力部へ入力された各信号と、前記フィルタによって前記低周波成分が減衰した第二信号と、を加算または減算することを特徴とする請求項6に記載の信号整形回路。

【請求項1】

第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、

を備えることを特徴とする信号整形回路。

【請求項2】

前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタを備えることを特徴とする請求項1に記載の信号整形回路。

【請求項3】

入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を前記第一入力部へ入力する分岐遅延回路を備え、

前記演算部は、前記分岐遅延回路によって前記第一入力部へ入力された各信号と、前記フィルタによって前記低周波成分が減衰した第二信号と、を加算または減算することを特徴とする請求項2に記載の信号整形回路。

【請求項4】

第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、をそれぞれ重み付けして加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記演算部による加算または減算における前記第一信号および前記第二信号の各重みの少なくとも一方を調整可能にする調整部と、

前記分岐部によって分岐された各信号の他方によって強度変調した信号光を出射する発光素子と、

を備えることを特徴とする光送信装置。

【請求項5】

第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算して出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号に対して、所定比率を乗じて遅延させる遅延部と、

前記遅延部の前記所定比率を調整可能にする調整部と、

を備えることを特徴とする信号整形回路。

【請求項6】

第一入力部へ入力された第一信号と、第二入力部へ入力された第二信号と、を加算または減算した信号を出力する演算部と、

前記演算部によって出力された信号を分岐し、分岐された各信号の一方を前記第二入力部へ入力し、分岐された各信号の他方を出力する分岐部と、

前記演算部から出力されて前記分岐部へ入力される信号または前記分岐部から出力されて前記第二入力部へ入力される信号を遅延させる遅延部と、

前記分岐部から出力されて前記第二入力部へ入力される信号の所定の低周波成分を減衰させるフィルタと、

を備えることを特徴とする信号整形回路。

【請求項7】

入力された信号を分岐し、分岐した各信号に遅延差を与え、遅延差を与えた各信号を前記第一入力部へ入力する分岐遅延回路を備え、

前記演算部は、前記分岐遅延回路によって前記第一入力部へ入力された各信号と、前記フィルタによって前記低周波成分が減衰した第二信号と、を加算または減算することを特徴とする請求項6に記載の信号整形回路。

【図1−1】

【図1−2】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8−1】

【図8−2】

【図9】

【図10】

【図11−1】

【図11−2】

【図12−1】

【図12−2】

【図13】

【図14−1】

【図14−2】

【図15−1】

【図15−2】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21−1】

【図21−2】

【図22−1】

【図22−2】

【図23−1】

【図23−2】

【図24−1】

【図24−2】

【図25−1】

【図25−2】

【図1−2】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8−1】

【図8−2】

【図9】

【図10】

【図11−1】

【図11−2】

【図12−1】

【図12−2】

【図13】

【図14−1】

【図14−2】

【図15−1】

【図15−2】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21−1】

【図21−2】

【図22−1】

【図22−2】

【図23−1】

【図23−2】

【図24−1】

【図24−2】

【図25−1】

【図25−2】

【公開番号】特開2013−74438(P2013−74438A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−211619(P2011−211619)

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]