信号生成装置及び信号生成方法

【課題】任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置を提供する。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ジッタを付加した信号を生成する信号生成装置及び信号生成方法に関する。

【背景技術】

【0002】

受信デバイスの負荷試験の1つとして、ジッタ耐力(Jitter Tolerance)試験がある。ジッタ耐力試験は、ジッタを付加した信号を対象デバイスに与えて動作が正常であるかを確認する試験であり、付加するジッタの成分を変化させて対象デバイスがどのようなジッタに耐えられるかを評価する。通常、ジッタ耐力試験では試験用測定器を用いて測定を行うが、ジッタ変調についての制約があったり、機材が高額であったりした。

【0003】

対象デバイスに与えるジッタが付加された信号は、一般に、高周波のキャリア信号(主信号)に1kHz〜10MHz程度の変調信号をミキサによりミキシングすることで生成する。すなわち、図10に示すように、第1のシンセサイザ101により生成したキャリア信号SIG1と第2のシンセサイザ102により生成した変調信号SIG2とをミキサ103によりミキシングする。そして、ミキサ103から出力される変調された信号SIG3を被測定物である対象デバイス104に供給し、ジッタ耐力試験が実施される。

【0004】

下記特許文献1には、入力信号が分配される複数の系の各系に可変シフトレジスタ(VSR)及びデジタルアナログ変換器(DAC)を有し、各DACの入力クロックを制御するダイレクトデジタルシンセサイザ(DDS)を設けた電力増幅装置が開示されている。DDSが入力クロックの周波数を変更せずに初期位相をサンプリング周波数に対して変更し、サンプリング周波数に対する程度の大まかな遅延調整はVSRの段数制御により行い、微調整はDDSの位相制御により行うことが記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−60451号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

前述のようにミキサを用いてキャリア信号に変調信号をミキシングしジッタを付加した信号を生成すると、ミキサでのキャリア信号と変調信号とのミキシングにより、信号波形の歪みが発生したり信号の増幅に多大な電力が必要になったりする。例えば、ミキサを用いて変調周波数の高い変調を実施する際には、変調成分の減衰が大きくなるためにアンプなどにより変調成分の出力を増幅したりする必要があった。また、付加されたジッタの量は、変調された信号をオシロスコープ等の測定器により直接計測して確認しているため、所望の量のジッタを付加するための確認及び調整を行う作業が必要であった。そのため、多種のジッタ周波数やジッタ深度(ジッタの大きさ)の切り替えを行い試験を実施することは、多大な労力を要し煩雑であった。

【0007】

本発明の目的は、任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置及び信号生成方法を提供することにある。

【課題を解決するための手段】

【0008】

信号生成装置の一態様は、基準クロックに基づいて制御データに応じた周波数の出力信号を生成し出力するダイレクトデジタルシンセサイザと、基準クロックに同期させてダイレクトデジタルシンセサイザに制御データを供給する制御部とを備える。制御部は、設定されるジッタの周波数及び大きさに応じてダイレクトデジタルシンセサイザの出力周波数を制御するための一連の設定データが格納された制御テーブルを有し、基準クロックに同期したタイミングで制御データを制御テーブルに格納されている設定データで順次書き替える。

【発明の効果】

【0009】

開示の信号生成装置は、制御テーブルに従って、ダイレクトデジタルシンセサイザに供給する制御データを短時間かつ一定の時間間隔で切り替えて出力周波数を制御するので、出力信号の周波数を周期的に変化させることができる。したがって、ダイレクトデジタルシンセサイザに供給する制御データを適宜制御することにより、任意のジッタを付加でき、歪みのない良好な信号波形を有する信号を容易に生成することができる。

【図面の簡単な説明】

【0010】

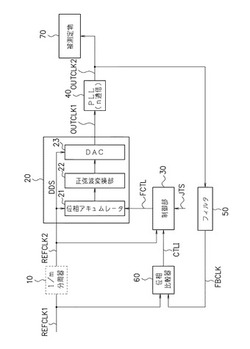

【図1】本発明の実施形態における信号生成装置の構成例を示す図である。

【図2】本実施形態におけるフィルタの周波数特性を示す図である。

【図3】本実施形態における制御部の構成例を示す図である。

【図4】本実施形態におけるジッタ制御テーブルの例を示す図である。

【図5】本実施形態におけるジッタ制御テーブルの第1例を示す図である。

【図6】図5に示したジッタ制御テーブルによる周波数変化を説明するための図である。

【図7】本実施形態におけるジッタ制御テーブルの第2例を説明するための図である。

【図8】本実施形態におけるジッタ制御テーブルの第3例を説明するための図である。

【図9A】本実施形態における信号生成装置を用いたジッタ付加試験の例を示すフローチャートである。

【図9B】図9Aに続くジッタ付加試験の例を示すフローチャートである。

【図10】ミキサを使用した信号生成回路の構成を示す図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施形態を図面に基づいて説明する。

【0012】

図1は、本発明の実施形態における信号生成装置の構成例を示すブロック図である。本実施形態における信号生成装置は、分周器10、ダイレクトデジタルシンセサイザ(Direct Digital Synthesizer:DDS)20、制御部30、位相ロックループ(Phase Locked Loop:PLL)回路40、フィルタ50、及び位相比較器60を有する。また、図1において、70は被測定物(試験対象デバイス)であり、例えば受信デバイスである。

【0013】

分周器10は、入力されるリファレンスクロックREFCLK1を分周し、周波数が(1/m)倍のリファレンスクロックREFCLK2を出力する。分周器10から出力されるリファレンスクロックREFCLK2は、DDS20及び制御部30に供給される。なお、DDS20や制御部30の仕様において不都合がない場合には、分周器10を設けずに、リファレンスクロックREFCLK1をDDS20及び制御部30に対して供給するようにしても良い。

【0014】

DDS20は、入力されるリファレンスクロックREFCLK2を基準クロックとして動作し、基準クロックの周波数に基づいて、制御データ(チューニングワード)FCTLによって指定される周波数の出力クロックOUTCLK1を生成し出力する。本実施形態においては、DDS20の基準クロックは、リファレンスクロックREFCLK2として説明するが、リファレンスクロックREFCLK2を逓倍又は分周したクロックであっても良い。DDS20は、位相アキュムレータ21、正弦波変換部22、及びデジタルアナログ変換部(DAC)23を有する。また、図示していないが、DDS20は、DAC23の出力をフィルタ処理するローパスフィルタをさらに有していても良い。

【0015】

位相アキュムレータ21は、入力される制御データFCTLによって指定される周波数に応じて位相設定データの増分を決定し、基準クロックであるリファレンスクロックREFCLK2に基づいて位相設定データを積算していく。積算された位相設定データは、正弦波変換部22に出力される。正弦波変換部22には、正弦波の振幅データに係るルックアップテーブルが格納されている。位相アキュムレータ21から出力された位相設定データは、それに対応した正弦波の振幅データに正弦波変換部22により変換されてDAC23に出力される。DAC23は、リファレンスクロックREFCLK2に基づいて、正弦波変換部22から出力された正弦波の振幅データをデジタルアナログ変換し、出力クロックOUTCLK1として出力する。

【0016】

制御部30は、ジッタ周波数における1周期分の出力周波数の変動量をマッピングしたジッタ制御テーブルを有する。ジッタ制御テーブルには、ジッタを付加した信号を生成するために制御データ(チューニングワード)FCTLとしてDDS20に供給する1周期分の一連の設定データが書き込みタイミング毎に格納されている。制御部30は、入力されるジッタ設定情報JTSに基づいて、それにより指定されるジッタの周波数及び深度(大きさ)に応じたジッタ制御テーブルを選択し、そのジッタ制御テーブルに格納されている設定データを制御データFCTLとしてDDS20に出力する。制御部30からDDS20への制御データFCTLの出力は、DDS20の基準クロック(ここでは、リファレンスクロックREFCLK2)に同期したタイミングで行われ、そのタイミング毎に設定データが1つずつ順に出力される。言い換えれば、制御部30から出力される制御データFCTLが、DDS20の基準クロックに同期したタイミングでジッタ制御テーブルに格納されている設定データに順次書き替えられてDDS20へ供給される。また、制御部30には、位相比較器60から出力される制御情報CTLIが入力される。制御部30は、制御情報CTLIに基づいて制御データFCTLに対する補正処理を必要に応じて行い、補正処理された制御データFCTLをDDS20に出力する。

【0017】

PLL回路40は、DDS20から出力される出力クロックOUTCLK1を逓倍し、周波数がn倍された高周波のクロックを出力クロックOUTCLK2として出力する。PLL回路40から出力される出力クロックOUTCLK2は、フィルタ50及び被測定物70に供給される。

【0018】

フィルタ50は、図2に示すように周波数FJ1〜FJ2のジッタ周波数設定範囲の成分は遮断し、周波数FJ2よりも高い周波数成分は透過させる周波数特性HPFを有するハイパスフィルタである。すなわち、フィルタ50は、カットオフ周波数が周波数FJ2と出力クロックOUTCLK2の基本周波数との間にあるハイパスフィルタである。フィルタ50は、入力される出力クロックOUTCLK2から付加されているジッタ成分を除去してフィードバッククロックFBCLKとして出力する。

【0019】

位相比較器60は、入力されるリファレンスクロックREFCLK1とフィードバッククロックFBCLK(ジッタ成分が除去された出力クロックOUTCLK2)との位相(周波数)を比較し、比較結果を制御情報CTLIとして出力する。

【0020】

図3は、図1に示した制御部30の構成例を示すブロック図である。制御部30は、デコーダ31、テーブル読み出し部32、メモリ33、テーブル保持部34、補正処理部35、及び出力部36を有する。メモリ33には、付加するジッタに応じた複数のジッタ制御テーブル37A、37B、37C、…が格納されている。

【0021】

デコーダ31は、入力されるジッタ設定情報JTSをデコードし、そのジッタ設定情報JTSに応じたジッタ制御テーブルをメモリ33から読み出すための読み出しアドレスRADを出力する。テーブル読み出し部32は、デコーダ31から読み出しアドレスRADが供給され、供給された読み出しアドレスRADを用いて、メモリ33からジッタ制御テーブルを読み出す。テーブル保持部34は、テーブル読み出し部32により読み出されたジッタ制御テーブルTD1が供給され、それを保持する。

【0022】

補正処理部35は、テーブル保持部34から保持しているジッタ制御テーブルの設定データTD2及び位相比較器60からの制御情報CTLIが供給され、制御情報CTLIに基づいて設定データTD2に補正処理を施す。なお、補正処理部35による補正処理は、必ず実行されるのではなく、制御情報CTLIに基づき必要に応じて実行される。出力部36は、補正処理後の設定データTD3が供給され、それを設定データTD4としてDDS20の基準クロックに同期したタイミングでDDS20に送る。

【0023】

図4は、ジッタ制御テーブルの一例を示す図である。基本周波数BASEの信号に対して、ジッタ周波数が(1×106)/(12Tc)〔kHz〕でジッタ深度(ジッタの大きさ)が±3Fd(基本周波数BASEを中心に±3Fdの幅で周波数を変動させる)であるジッタを付加する場合を一例として示す。また、DDS20の基準クロックの周波数は(8×103)/Tc〔MHz〕であるとする。

【0024】

このようなジッタが付加された信号を生成するには、例えば図4(A)に示すように、期間a(0〜1Tc〔ns〕)において、制御部30は、出力周波数(BASE−3Fd)に対応する設定値(BASE−3Vd)を制御データFCTLとしてDDS20に出力する。続く、期間b(1Tc〜2Tc〔ns〕)において、制御部30は、出力周波数(BASE−2Fd)に対応する設定値(BASE−2Vd)を制御データFCTLとしてDDS20に出力する。また、期間c(2Tc〜3Tc〔ns〕)において、制御部30は、出力周波数(BASE−1Fd)に対応する設定値(BASE−1Vd)を制御データFCTLとしてDDS20に出力する。以下、同様に制御部30は、図4(A)に示すように時間Tcが経過する毎にVdずつ設定値を変動させ、その設定値を制御データFCTLとしてDDS20に出力する。

【0025】

制御部30からDDS20への設定値の書き込みは8/Tc〔ns〕毎に行うので、図4(A)に示したようにしてDDS20へ設定値を送るには、図4(B)に示すようなジッタ制御テーブルとなる。すなわち、まず8/Tc〔ns〕毎に設定値(BASE−3Vd)の書き込みを8回行い、続いて8/Tc〔ns〕毎に設定値(BASE−2Vd)の書き込みを8回行い、その後同様に8回毎に設定値の切り替えを行う。

【0026】

ここで、DDSは、一般にPLL回路用の発振器など周波数調整等に使用されており、通常は単一周波数の信号を出力するために用いられるので、DDSに与える制御データ(チューニングワード)は固定である。

【0027】

それに対して、本実施形態では、制御部30が、前述のジッタ制御テーブルを用いて、ナノ秒あるいはピコ秒といった短時間(高速)かつ一定の間隔でDDS20に与える制御データFCTLを更新するよう制御する。このようにDDS20に与える制御ビットの切り替えを高速かつ一定時間毎に行って、出力クロックOUTCLK1に係る周波数制御をし周期的に周波数を変化させることにより、周波数変調と同様の効果が得られ、ジッタを付加した信号を生成することができる。

【0028】

また、本実施形態では、ジッタ制御テーブルに格納する設定データの繰り返し数や値の変化量によりジッタ周波数やジッタ深度を自由に設定することができ、任意のジッタを容易に付加することができる。また、DDS20に対する制御データ(設定データ)でジッタの量を制御できるので、微小なジッタの付加が可能になり、またジッタの量の確認及び調整を行う作業が不要、あるいは著しく簡易になる。例えば、容易に多種のジッタ周波数やジッタ深度の切り替えを行って試験を実施することができたり、付加するジッタの量を線形的に変化させたりして試験を実施することができる。また、例えば、瞬時にジッタ周波数やジッタ深度の切り替えを行うことが可能になり、瞬時のジッタ付加耐力やジッタ急変耐力等の計測が可能になる。

【0029】

また、ジッタ制御テーブルにはジッタ周波数における1周期分の出力周波数の変動量だけをマッピングし、その繰り返し制御を行うことにより、ジッタ制御テーブルを記憶するためのメモリ容量の増大を抑制しジッタを付加した信号を生成することができる。また、本実施形態においてはミキサを用いずにDDS20がジッタの成分を含む信号を生成するので、歪みのない良好な信号波形の信号が得られるとともに、ノイズが発生することもない。

【0030】

以下、本実施形態での具体例について説明する。以下の説明では、図1に示した構成において、ジッタを付加していない状態での各クロックの周波数は、次のとおりであるとする。クロックREFCLK1、OUTCLK2、及びFBCLKの周波数が622.08〔MHz〕であり、クロックREFCLK2の周波数が311.04〔MHz〕であり、クロックOUTCLK1の周波数が19.44〔MHz〕であるとする。また、DDS20の基準クロックは、クロックREFCLK2と同じであるとし、その周波数は311.04〔MHz〕であるとする。

【0031】

図5は、本実施形態におけるジッタ制御テーブルの第1例を示す図である。第1例は、基本周波数19.44〔MHz〕の信号に対して、ジッタ周波数が810〔kHz〕でジッタ深度が±57.0〔ppm〕であるジッタを付加した信号をDDS20から出力する例である。ここで、DDS20における制御データのビット数を24ビットとすると、1/(224)=0.06〔ppm〕ステップでの周波数偏差の制御が可能である。したがって、1回の制御での変動幅を9.5〔ppm〕とすると、図5(A)に示すように、9.5/0.06=160ステップ(32×5)単位で24回制御すれば良い。

【0032】

図5(A)に示すDDS20からの出力クロックOUTCLK1の周波数制御は、図5(B)に示すジッタ制御テーブルにより実現される。すなわち、DDS20における制御データの書き込みは3.2〔ns〕(=1/311.04MHz)毎に行われるので、期間aである0〔ns〕から48.2〔ns〕まで(a1〜a16の書き込み)は、設定データ“0000 1111 1111 1111 1110 0010”を書き込み続ける。同様に、期間bである51.4〔ns〕から99.6〔ns〕まで(b1〜b16の書き込み)は、設定データ“0000 1111 1111 1111 1110 0111”を書き込み続ける。以下、期間c〜期間xまで同様に出力周波数に応じた設定データをDDS20に書き込むこととなる。

【0033】

図6は、図5(B)に示したジッタ制御テーブルによるDDS20から出力される出力クロックOUTCLK1の周波数変化を説明するための図である。図6に示すように、時間間隔Jtd(本例では、51.44〔ns〕)の間隔で周波数変調が切り替えられ、変動幅Jfd(本例では、9.5〔ppm〕)の間隔でジッタの大きさが制御される。図5(B)に示したジッタ制御テーブルを用いることで、時間間隔Jtの間に出力クロックOUTCLK1の周波数は、基本周波数F0である19.44〔MHz〕を中心に±57.0〔ppm〕の範囲で変化することとなる。

【0034】

ここで、ジッタ制御テーブルに格納されている設定データに基づいてDDS20からの出力クロックOUTCLK1の周波数制御を行うと、実際の制御では同期にずれが生じることがある。本実施形態では、リファレンスクロックREFCLK1とフィードバッククロックFBCLKとの位相(周波数)を位相比較器60で比較し、比較結果に基づいて制御部30がDDS20に与える制御データを適宜加減し同位相となるように位相(周波数)を調整する。

【0035】

図7は、本実施形態におけるジッタ制御テーブルの第2例を示す図である。第2例は、基本周波数19.44〔MHz〕の信号に対して、ジッタ周波数が810〔kHz〕でジッタ深度が±114.0〔ppm〕であるジッタを付加した信号をDDS20から出力する例である。すなわち、図7(A)に示すように、周波数変化を破線で示した第1例でのジッタ深度Jw1(±57.0〔ppm〕)に対して、実線で示すように2倍のジッタ深度Jw2のジッタを付加するようにするものである。

【0036】

このようにジッタ深度(ジッタの大きさ)を2倍にする場合には、図7(B)に示すように設定データにおける変動量を2倍にすれば良い。同様に、ジッタ深度(ジッタの大きさ)を3倍にする場合には、設定データにおける変動量を3倍にすれば良い。すなわち、本実施形態では、ジッタ深度(ジッタの大きさ)をN倍(Nは任意の値)にする場合には、設定データにおける変動量をN倍にすれば良く、N倍のジッタを付加した信号を容易に生成することができる。

【0037】

図8は、本実施形態におけるジッタ制御テーブルの第3例を示す図である。第3例は、基本周波数19.44〔MHz〕の信号に対して、ジッタ周波数が405〔kHz〕でジッタ深度が±57.0〔ppm〕であるジッタを付加した信号をDDS20から出力する例である。すなわち、図8(A)に示すように、周波数変化を破線で示した第1例でのジッタ周波数JF1(810〔kHz〕)に対して、実線で示すように1/2倍のジッタ周波数JF2のジッタを付加するようにするものである。

【0038】

このようにジッタ周波数を1/2倍にする場合には、図8(B)に示すように設定データの制御速度を2倍に遅くすれば良い(例えば、DDS20の基準クロックの周波数は変更せずに、同じ設定データの書き込み回数を2倍にする)。同様に、ジッタ周波数を(1/10)倍にする場合には、設定データの制御速度を10倍に遅くすれば良い。すなわち、本実施形態では、ジッタ周波数を(1/M)倍(Mは任意の値)にする場合には、設定データの制御速度をM倍に遅くすれば良く、(1/M)倍のジッタ周波数でのジッタを付加した信号を容易に生成することができる。

【0039】

なお、前述した図7及び図8に示した例を組み合わせても良い。ジッタ深度(ジッタの大きさ)をX倍(Xは任意の値)にし、かつジッタ周波数を(1/Y)倍(Yは任意の値)にする場合には、設定データにおける変動量をX倍にし、かつ設定データの制御速度をY倍に遅くすれば良い。このように、ジッタ制御テーブルにおける設定データの変動量、及び設定ビットの切り替えタイミングの制御により、容易に任意のジッタを付加することができる。

【0040】

次に、図9A及び図9Bを参照して、本実施形態における信号生成装置を用いたジッタ付加試験の例を説明する。図9Aは、本実施形態における信号生成装置を用いたジッタ付加試験の例を示すフローチャートであり、図9Bは、図9Aに続くジッタ付加試験の例を示すフローチャートである。

【0041】

ジッタ付加試験が開始されると、まず、ステップS101にて、信号生成装置(DDS20及び制御部30)の初期化が実行される。初期化が完了すると、ステップS102にて、制御部30は、基本周波数の信号が出力されるようにDDS20に制御データFCTLを設定する。ステップS102において制御データFCTLの設定が行われた後、基本周波数の信号がDDS20から出力されているか(S103)、及び同期したクロックがDDS20及び制御部30に入力されているか(S104)が判定される。判定の結果、基本周波数の信号がDDS20から出力されていない、又は同期したクロックがDDS20及び制御部30に入力されていないと判定された場合には、ステップS101に戻る。一方、基本周波数の信号がDDS20から出力されていると判定され、かつ同期したクロックがDDS20及び制御部30に入力されていると判定された場合には、ステップS105へ進む。

【0042】

ステップS105にて、制御部30は、入力されるジッタ設定情報JTSに基づいて、保持しているジッタ制御テーブルの内からジッタ設定に応じたジッタ制御テーブルを選択する。そして、制御部30は、ステップS106〜S108の処理を実行し、DDS20の基準クロックに同期したタイミングで、選択したジッタ制御テーブルに格納されている設定データを1つずつ順にDDS20制御データFCTLとして書き込む。これにより、DDS20では、その基準クロックに同期した書き込みタイミング毎に制御データが更新され、制御データの値に応じた周波数の出力クロックが生成され出力される。このようにして、DDS20は、ジッタの成分を含む信号を生成し出力クロックOUTCLK1として出力し、DDS20から出力された出力クロックOUTCLK1はPLL回路40によりn逓倍されて被測定物70に供給される。

【0043】

ステップS106〜S108の処理が選択したジッタ制御テーブルに格納されている設定データの数と同じ回数繰り返される、すなわち選択したジッタ制御テーブルに格納されている最終の設定データがDDS20に書き込まれるとステップS109へ進む。ステップS109では、DDS20からの出力クロックの周波数が、選択されたジッタ制御テーブルに合わせて変動しているか否かが判定される。ステップS109での判定の結果、出力クロックの周波数がジッタ制御テーブルに合わせて変動していない場合には、ステップS106に戻る。

【0044】

一方、ステップS109での判定の結果、出力クロックの周波数がジッタ制御テーブルに合わせて変動している場合には、ステップS110へ進む。ステップS110にて、位相比較器60は、入力クロックに対応するリファレンスクロックREFCLK1と出力クロックに対応するフィードバッククロックFBCLK(ジッタ成分が除去された出力クロックOUTCLK2)との周波数を比較する。

【0045】

ステップS110での比較の結果、入力クロックと出力クロックとの周波数が異なり(S111のNO)、かつ出力クロックの周波数が入力クロックの周波数より高い(S112のYES)ときには、制御部30は、制御データから“1”を減算しステップS110に戻る(S113)。また、入力クロックと出力クロックとの周波数が異なり(S111のNO)、かつ出力クロックの周波数が入力クロックの周波数より高くない(S112のNO)ときには、制御部30は、制御データに“1”を加算しステップS110に戻る(S114)。

【0046】

前述したステップS110〜S114の処理を入力クロックと出力クロックとの周波数が同じになるまで繰り返し行う。そして、入力クロックと出力クロックとの周波数が同じになると(S111のYES)、ステップS115にて、制御部30は、すべてのジッタ設定に対するテストが完了したか否かを判断する。その結果、実施していないテストがある場合には、ステップS105に戻り、未実施のジッタ設定でステップS105以降の処理を再び行う。一方、すべてのジッタ設定に対するテストが完了している場合には、ジッタ付加試験を終了する。

【0047】

なお、本実施形態においてDDS20は、制御データFCTLに応じた周波数の正弦波を出力する例を示したが、DDS20の出力信号は正弦波に限定されるものではない。DDS20が、正弦波とは異なる他の周期性を有する信号の振幅データに係るルックアップテーブルを持ち、それに応じた出力信号を出力可能であっても良い。

【0048】

また、本実施形態においてジッタ制御テーブルには、同じ設定データが連続する場合でもそれぞれの設定データが分けて格納されているが、ジッタ制御テーブルはこの形式に限定されるものではない。例えば、設定データとその設定データが連続する個数とを組にしてジッタ制御テーブルに格納し、制御部30が、格納された個数の情報に従って、対応する設定データを繰り返し出力するように制御しても良い。

【0049】

なお、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

【符号の説明】

【0050】

10 分周器

20 ダイレクトデジタルシンセサイザ(DDS)

21 位相アキュムレータ

22 正弦波変換部

23 デジタルアナログ変換部(DAC)

30 制御部

31 デコーダ

32 テーブル読み出し部

33 メモリ

34 テーブル保持部

35 補正処理部

36 出力部

37A、37B、37C ジッタ制御テーブル

40 PLL回路

50 フィルタ

60 位相比較器

【技術分野】

【0001】

本発明は、ジッタを付加した信号を生成する信号生成装置及び信号生成方法に関する。

【背景技術】

【0002】

受信デバイスの負荷試験の1つとして、ジッタ耐力(Jitter Tolerance)試験がある。ジッタ耐力試験は、ジッタを付加した信号を対象デバイスに与えて動作が正常であるかを確認する試験であり、付加するジッタの成分を変化させて対象デバイスがどのようなジッタに耐えられるかを評価する。通常、ジッタ耐力試験では試験用測定器を用いて測定を行うが、ジッタ変調についての制約があったり、機材が高額であったりした。

【0003】

対象デバイスに与えるジッタが付加された信号は、一般に、高周波のキャリア信号(主信号)に1kHz〜10MHz程度の変調信号をミキサによりミキシングすることで生成する。すなわち、図10に示すように、第1のシンセサイザ101により生成したキャリア信号SIG1と第2のシンセサイザ102により生成した変調信号SIG2とをミキサ103によりミキシングする。そして、ミキサ103から出力される変調された信号SIG3を被測定物である対象デバイス104に供給し、ジッタ耐力試験が実施される。

【0004】

下記特許文献1には、入力信号が分配される複数の系の各系に可変シフトレジスタ(VSR)及びデジタルアナログ変換器(DAC)を有し、各DACの入力クロックを制御するダイレクトデジタルシンセサイザ(DDS)を設けた電力増幅装置が開示されている。DDSが入力クロックの周波数を変更せずに初期位相をサンプリング周波数に対して変更し、サンプリング周波数に対する程度の大まかな遅延調整はVSRの段数制御により行い、微調整はDDSの位相制御により行うことが記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−60451号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

前述のようにミキサを用いてキャリア信号に変調信号をミキシングしジッタを付加した信号を生成すると、ミキサでのキャリア信号と変調信号とのミキシングにより、信号波形の歪みが発生したり信号の増幅に多大な電力が必要になったりする。例えば、ミキサを用いて変調周波数の高い変調を実施する際には、変調成分の減衰が大きくなるためにアンプなどにより変調成分の出力を増幅したりする必要があった。また、付加されたジッタの量は、変調された信号をオシロスコープ等の測定器により直接計測して確認しているため、所望の量のジッタを付加するための確認及び調整を行う作業が必要であった。そのため、多種のジッタ周波数やジッタ深度(ジッタの大きさ)の切り替えを行い試験を実施することは、多大な労力を要し煩雑であった。

【0007】

本発明の目的は、任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置及び信号生成方法を提供することにある。

【課題を解決するための手段】

【0008】

信号生成装置の一態様は、基準クロックに基づいて制御データに応じた周波数の出力信号を生成し出力するダイレクトデジタルシンセサイザと、基準クロックに同期させてダイレクトデジタルシンセサイザに制御データを供給する制御部とを備える。制御部は、設定されるジッタの周波数及び大きさに応じてダイレクトデジタルシンセサイザの出力周波数を制御するための一連の設定データが格納された制御テーブルを有し、基準クロックに同期したタイミングで制御データを制御テーブルに格納されている設定データで順次書き替える。

【発明の効果】

【0009】

開示の信号生成装置は、制御テーブルに従って、ダイレクトデジタルシンセサイザに供給する制御データを短時間かつ一定の時間間隔で切り替えて出力周波数を制御するので、出力信号の周波数を周期的に変化させることができる。したがって、ダイレクトデジタルシンセサイザに供給する制御データを適宜制御することにより、任意のジッタを付加でき、歪みのない良好な信号波形を有する信号を容易に生成することができる。

【図面の簡単な説明】

【0010】

【図1】本発明の実施形態における信号生成装置の構成例を示す図である。

【図2】本実施形態におけるフィルタの周波数特性を示す図である。

【図3】本実施形態における制御部の構成例を示す図である。

【図4】本実施形態におけるジッタ制御テーブルの例を示す図である。

【図5】本実施形態におけるジッタ制御テーブルの第1例を示す図である。

【図6】図5に示したジッタ制御テーブルによる周波数変化を説明するための図である。

【図7】本実施形態におけるジッタ制御テーブルの第2例を説明するための図である。

【図8】本実施形態におけるジッタ制御テーブルの第3例を説明するための図である。

【図9A】本実施形態における信号生成装置を用いたジッタ付加試験の例を示すフローチャートである。

【図9B】図9Aに続くジッタ付加試験の例を示すフローチャートである。

【図10】ミキサを使用した信号生成回路の構成を示す図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施形態を図面に基づいて説明する。

【0012】

図1は、本発明の実施形態における信号生成装置の構成例を示すブロック図である。本実施形態における信号生成装置は、分周器10、ダイレクトデジタルシンセサイザ(Direct Digital Synthesizer:DDS)20、制御部30、位相ロックループ(Phase Locked Loop:PLL)回路40、フィルタ50、及び位相比較器60を有する。また、図1において、70は被測定物(試験対象デバイス)であり、例えば受信デバイスである。

【0013】

分周器10は、入力されるリファレンスクロックREFCLK1を分周し、周波数が(1/m)倍のリファレンスクロックREFCLK2を出力する。分周器10から出力されるリファレンスクロックREFCLK2は、DDS20及び制御部30に供給される。なお、DDS20や制御部30の仕様において不都合がない場合には、分周器10を設けずに、リファレンスクロックREFCLK1をDDS20及び制御部30に対して供給するようにしても良い。

【0014】

DDS20は、入力されるリファレンスクロックREFCLK2を基準クロックとして動作し、基準クロックの周波数に基づいて、制御データ(チューニングワード)FCTLによって指定される周波数の出力クロックOUTCLK1を生成し出力する。本実施形態においては、DDS20の基準クロックは、リファレンスクロックREFCLK2として説明するが、リファレンスクロックREFCLK2を逓倍又は分周したクロックであっても良い。DDS20は、位相アキュムレータ21、正弦波変換部22、及びデジタルアナログ変換部(DAC)23を有する。また、図示していないが、DDS20は、DAC23の出力をフィルタ処理するローパスフィルタをさらに有していても良い。

【0015】

位相アキュムレータ21は、入力される制御データFCTLによって指定される周波数に応じて位相設定データの増分を決定し、基準クロックであるリファレンスクロックREFCLK2に基づいて位相設定データを積算していく。積算された位相設定データは、正弦波変換部22に出力される。正弦波変換部22には、正弦波の振幅データに係るルックアップテーブルが格納されている。位相アキュムレータ21から出力された位相設定データは、それに対応した正弦波の振幅データに正弦波変換部22により変換されてDAC23に出力される。DAC23は、リファレンスクロックREFCLK2に基づいて、正弦波変換部22から出力された正弦波の振幅データをデジタルアナログ変換し、出力クロックOUTCLK1として出力する。

【0016】

制御部30は、ジッタ周波数における1周期分の出力周波数の変動量をマッピングしたジッタ制御テーブルを有する。ジッタ制御テーブルには、ジッタを付加した信号を生成するために制御データ(チューニングワード)FCTLとしてDDS20に供給する1周期分の一連の設定データが書き込みタイミング毎に格納されている。制御部30は、入力されるジッタ設定情報JTSに基づいて、それにより指定されるジッタの周波数及び深度(大きさ)に応じたジッタ制御テーブルを選択し、そのジッタ制御テーブルに格納されている設定データを制御データFCTLとしてDDS20に出力する。制御部30からDDS20への制御データFCTLの出力は、DDS20の基準クロック(ここでは、リファレンスクロックREFCLK2)に同期したタイミングで行われ、そのタイミング毎に設定データが1つずつ順に出力される。言い換えれば、制御部30から出力される制御データFCTLが、DDS20の基準クロックに同期したタイミングでジッタ制御テーブルに格納されている設定データに順次書き替えられてDDS20へ供給される。また、制御部30には、位相比較器60から出力される制御情報CTLIが入力される。制御部30は、制御情報CTLIに基づいて制御データFCTLに対する補正処理を必要に応じて行い、補正処理された制御データFCTLをDDS20に出力する。

【0017】

PLL回路40は、DDS20から出力される出力クロックOUTCLK1を逓倍し、周波数がn倍された高周波のクロックを出力クロックOUTCLK2として出力する。PLL回路40から出力される出力クロックOUTCLK2は、フィルタ50及び被測定物70に供給される。

【0018】

フィルタ50は、図2に示すように周波数FJ1〜FJ2のジッタ周波数設定範囲の成分は遮断し、周波数FJ2よりも高い周波数成分は透過させる周波数特性HPFを有するハイパスフィルタである。すなわち、フィルタ50は、カットオフ周波数が周波数FJ2と出力クロックOUTCLK2の基本周波数との間にあるハイパスフィルタである。フィルタ50は、入力される出力クロックOUTCLK2から付加されているジッタ成分を除去してフィードバッククロックFBCLKとして出力する。

【0019】

位相比較器60は、入力されるリファレンスクロックREFCLK1とフィードバッククロックFBCLK(ジッタ成分が除去された出力クロックOUTCLK2)との位相(周波数)を比較し、比較結果を制御情報CTLIとして出力する。

【0020】

図3は、図1に示した制御部30の構成例を示すブロック図である。制御部30は、デコーダ31、テーブル読み出し部32、メモリ33、テーブル保持部34、補正処理部35、及び出力部36を有する。メモリ33には、付加するジッタに応じた複数のジッタ制御テーブル37A、37B、37C、…が格納されている。

【0021】

デコーダ31は、入力されるジッタ設定情報JTSをデコードし、そのジッタ設定情報JTSに応じたジッタ制御テーブルをメモリ33から読み出すための読み出しアドレスRADを出力する。テーブル読み出し部32は、デコーダ31から読み出しアドレスRADが供給され、供給された読み出しアドレスRADを用いて、メモリ33からジッタ制御テーブルを読み出す。テーブル保持部34は、テーブル読み出し部32により読み出されたジッタ制御テーブルTD1が供給され、それを保持する。

【0022】

補正処理部35は、テーブル保持部34から保持しているジッタ制御テーブルの設定データTD2及び位相比較器60からの制御情報CTLIが供給され、制御情報CTLIに基づいて設定データTD2に補正処理を施す。なお、補正処理部35による補正処理は、必ず実行されるのではなく、制御情報CTLIに基づき必要に応じて実行される。出力部36は、補正処理後の設定データTD3が供給され、それを設定データTD4としてDDS20の基準クロックに同期したタイミングでDDS20に送る。

【0023】

図4は、ジッタ制御テーブルの一例を示す図である。基本周波数BASEの信号に対して、ジッタ周波数が(1×106)/(12Tc)〔kHz〕でジッタ深度(ジッタの大きさ)が±3Fd(基本周波数BASEを中心に±3Fdの幅で周波数を変動させる)であるジッタを付加する場合を一例として示す。また、DDS20の基準クロックの周波数は(8×103)/Tc〔MHz〕であるとする。

【0024】

このようなジッタが付加された信号を生成するには、例えば図4(A)に示すように、期間a(0〜1Tc〔ns〕)において、制御部30は、出力周波数(BASE−3Fd)に対応する設定値(BASE−3Vd)を制御データFCTLとしてDDS20に出力する。続く、期間b(1Tc〜2Tc〔ns〕)において、制御部30は、出力周波数(BASE−2Fd)に対応する設定値(BASE−2Vd)を制御データFCTLとしてDDS20に出力する。また、期間c(2Tc〜3Tc〔ns〕)において、制御部30は、出力周波数(BASE−1Fd)に対応する設定値(BASE−1Vd)を制御データFCTLとしてDDS20に出力する。以下、同様に制御部30は、図4(A)に示すように時間Tcが経過する毎にVdずつ設定値を変動させ、その設定値を制御データFCTLとしてDDS20に出力する。

【0025】

制御部30からDDS20への設定値の書き込みは8/Tc〔ns〕毎に行うので、図4(A)に示したようにしてDDS20へ設定値を送るには、図4(B)に示すようなジッタ制御テーブルとなる。すなわち、まず8/Tc〔ns〕毎に設定値(BASE−3Vd)の書き込みを8回行い、続いて8/Tc〔ns〕毎に設定値(BASE−2Vd)の書き込みを8回行い、その後同様に8回毎に設定値の切り替えを行う。

【0026】

ここで、DDSは、一般にPLL回路用の発振器など周波数調整等に使用されており、通常は単一周波数の信号を出力するために用いられるので、DDSに与える制御データ(チューニングワード)は固定である。

【0027】

それに対して、本実施形態では、制御部30が、前述のジッタ制御テーブルを用いて、ナノ秒あるいはピコ秒といった短時間(高速)かつ一定の間隔でDDS20に与える制御データFCTLを更新するよう制御する。このようにDDS20に与える制御ビットの切り替えを高速かつ一定時間毎に行って、出力クロックOUTCLK1に係る周波数制御をし周期的に周波数を変化させることにより、周波数変調と同様の効果が得られ、ジッタを付加した信号を生成することができる。

【0028】

また、本実施形態では、ジッタ制御テーブルに格納する設定データの繰り返し数や値の変化量によりジッタ周波数やジッタ深度を自由に設定することができ、任意のジッタを容易に付加することができる。また、DDS20に対する制御データ(設定データ)でジッタの量を制御できるので、微小なジッタの付加が可能になり、またジッタの量の確認及び調整を行う作業が不要、あるいは著しく簡易になる。例えば、容易に多種のジッタ周波数やジッタ深度の切り替えを行って試験を実施することができたり、付加するジッタの量を線形的に変化させたりして試験を実施することができる。また、例えば、瞬時にジッタ周波数やジッタ深度の切り替えを行うことが可能になり、瞬時のジッタ付加耐力やジッタ急変耐力等の計測が可能になる。

【0029】

また、ジッタ制御テーブルにはジッタ周波数における1周期分の出力周波数の変動量だけをマッピングし、その繰り返し制御を行うことにより、ジッタ制御テーブルを記憶するためのメモリ容量の増大を抑制しジッタを付加した信号を生成することができる。また、本実施形態においてはミキサを用いずにDDS20がジッタの成分を含む信号を生成するので、歪みのない良好な信号波形の信号が得られるとともに、ノイズが発生することもない。

【0030】

以下、本実施形態での具体例について説明する。以下の説明では、図1に示した構成において、ジッタを付加していない状態での各クロックの周波数は、次のとおりであるとする。クロックREFCLK1、OUTCLK2、及びFBCLKの周波数が622.08〔MHz〕であり、クロックREFCLK2の周波数が311.04〔MHz〕であり、クロックOUTCLK1の周波数が19.44〔MHz〕であるとする。また、DDS20の基準クロックは、クロックREFCLK2と同じであるとし、その周波数は311.04〔MHz〕であるとする。

【0031】

図5は、本実施形態におけるジッタ制御テーブルの第1例を示す図である。第1例は、基本周波数19.44〔MHz〕の信号に対して、ジッタ周波数が810〔kHz〕でジッタ深度が±57.0〔ppm〕であるジッタを付加した信号をDDS20から出力する例である。ここで、DDS20における制御データのビット数を24ビットとすると、1/(224)=0.06〔ppm〕ステップでの周波数偏差の制御が可能である。したがって、1回の制御での変動幅を9.5〔ppm〕とすると、図5(A)に示すように、9.5/0.06=160ステップ(32×5)単位で24回制御すれば良い。

【0032】

図5(A)に示すDDS20からの出力クロックOUTCLK1の周波数制御は、図5(B)に示すジッタ制御テーブルにより実現される。すなわち、DDS20における制御データの書き込みは3.2〔ns〕(=1/311.04MHz)毎に行われるので、期間aである0〔ns〕から48.2〔ns〕まで(a1〜a16の書き込み)は、設定データ“0000 1111 1111 1111 1110 0010”を書き込み続ける。同様に、期間bである51.4〔ns〕から99.6〔ns〕まで(b1〜b16の書き込み)は、設定データ“0000 1111 1111 1111 1110 0111”を書き込み続ける。以下、期間c〜期間xまで同様に出力周波数に応じた設定データをDDS20に書き込むこととなる。

【0033】

図6は、図5(B)に示したジッタ制御テーブルによるDDS20から出力される出力クロックOUTCLK1の周波数変化を説明するための図である。図6に示すように、時間間隔Jtd(本例では、51.44〔ns〕)の間隔で周波数変調が切り替えられ、変動幅Jfd(本例では、9.5〔ppm〕)の間隔でジッタの大きさが制御される。図5(B)に示したジッタ制御テーブルを用いることで、時間間隔Jtの間に出力クロックOUTCLK1の周波数は、基本周波数F0である19.44〔MHz〕を中心に±57.0〔ppm〕の範囲で変化することとなる。

【0034】

ここで、ジッタ制御テーブルに格納されている設定データに基づいてDDS20からの出力クロックOUTCLK1の周波数制御を行うと、実際の制御では同期にずれが生じることがある。本実施形態では、リファレンスクロックREFCLK1とフィードバッククロックFBCLKとの位相(周波数)を位相比較器60で比較し、比較結果に基づいて制御部30がDDS20に与える制御データを適宜加減し同位相となるように位相(周波数)を調整する。

【0035】

図7は、本実施形態におけるジッタ制御テーブルの第2例を示す図である。第2例は、基本周波数19.44〔MHz〕の信号に対して、ジッタ周波数が810〔kHz〕でジッタ深度が±114.0〔ppm〕であるジッタを付加した信号をDDS20から出力する例である。すなわち、図7(A)に示すように、周波数変化を破線で示した第1例でのジッタ深度Jw1(±57.0〔ppm〕)に対して、実線で示すように2倍のジッタ深度Jw2のジッタを付加するようにするものである。

【0036】

このようにジッタ深度(ジッタの大きさ)を2倍にする場合には、図7(B)に示すように設定データにおける変動量を2倍にすれば良い。同様に、ジッタ深度(ジッタの大きさ)を3倍にする場合には、設定データにおける変動量を3倍にすれば良い。すなわち、本実施形態では、ジッタ深度(ジッタの大きさ)をN倍(Nは任意の値)にする場合には、設定データにおける変動量をN倍にすれば良く、N倍のジッタを付加した信号を容易に生成することができる。

【0037】

図8は、本実施形態におけるジッタ制御テーブルの第3例を示す図である。第3例は、基本周波数19.44〔MHz〕の信号に対して、ジッタ周波数が405〔kHz〕でジッタ深度が±57.0〔ppm〕であるジッタを付加した信号をDDS20から出力する例である。すなわち、図8(A)に示すように、周波数変化を破線で示した第1例でのジッタ周波数JF1(810〔kHz〕)に対して、実線で示すように1/2倍のジッタ周波数JF2のジッタを付加するようにするものである。

【0038】

このようにジッタ周波数を1/2倍にする場合には、図8(B)に示すように設定データの制御速度を2倍に遅くすれば良い(例えば、DDS20の基準クロックの周波数は変更せずに、同じ設定データの書き込み回数を2倍にする)。同様に、ジッタ周波数を(1/10)倍にする場合には、設定データの制御速度を10倍に遅くすれば良い。すなわち、本実施形態では、ジッタ周波数を(1/M)倍(Mは任意の値)にする場合には、設定データの制御速度をM倍に遅くすれば良く、(1/M)倍のジッタ周波数でのジッタを付加した信号を容易に生成することができる。

【0039】

なお、前述した図7及び図8に示した例を組み合わせても良い。ジッタ深度(ジッタの大きさ)をX倍(Xは任意の値)にし、かつジッタ周波数を(1/Y)倍(Yは任意の値)にする場合には、設定データにおける変動量をX倍にし、かつ設定データの制御速度をY倍に遅くすれば良い。このように、ジッタ制御テーブルにおける設定データの変動量、及び設定ビットの切り替えタイミングの制御により、容易に任意のジッタを付加することができる。

【0040】

次に、図9A及び図9Bを参照して、本実施形態における信号生成装置を用いたジッタ付加試験の例を説明する。図9Aは、本実施形態における信号生成装置を用いたジッタ付加試験の例を示すフローチャートであり、図9Bは、図9Aに続くジッタ付加試験の例を示すフローチャートである。

【0041】

ジッタ付加試験が開始されると、まず、ステップS101にて、信号生成装置(DDS20及び制御部30)の初期化が実行される。初期化が完了すると、ステップS102にて、制御部30は、基本周波数の信号が出力されるようにDDS20に制御データFCTLを設定する。ステップS102において制御データFCTLの設定が行われた後、基本周波数の信号がDDS20から出力されているか(S103)、及び同期したクロックがDDS20及び制御部30に入力されているか(S104)が判定される。判定の結果、基本周波数の信号がDDS20から出力されていない、又は同期したクロックがDDS20及び制御部30に入力されていないと判定された場合には、ステップS101に戻る。一方、基本周波数の信号がDDS20から出力されていると判定され、かつ同期したクロックがDDS20及び制御部30に入力されていると判定された場合には、ステップS105へ進む。

【0042】

ステップS105にて、制御部30は、入力されるジッタ設定情報JTSに基づいて、保持しているジッタ制御テーブルの内からジッタ設定に応じたジッタ制御テーブルを選択する。そして、制御部30は、ステップS106〜S108の処理を実行し、DDS20の基準クロックに同期したタイミングで、選択したジッタ制御テーブルに格納されている設定データを1つずつ順にDDS20制御データFCTLとして書き込む。これにより、DDS20では、その基準クロックに同期した書き込みタイミング毎に制御データが更新され、制御データの値に応じた周波数の出力クロックが生成され出力される。このようにして、DDS20は、ジッタの成分を含む信号を生成し出力クロックOUTCLK1として出力し、DDS20から出力された出力クロックOUTCLK1はPLL回路40によりn逓倍されて被測定物70に供給される。

【0043】

ステップS106〜S108の処理が選択したジッタ制御テーブルに格納されている設定データの数と同じ回数繰り返される、すなわち選択したジッタ制御テーブルに格納されている最終の設定データがDDS20に書き込まれるとステップS109へ進む。ステップS109では、DDS20からの出力クロックの周波数が、選択されたジッタ制御テーブルに合わせて変動しているか否かが判定される。ステップS109での判定の結果、出力クロックの周波数がジッタ制御テーブルに合わせて変動していない場合には、ステップS106に戻る。

【0044】

一方、ステップS109での判定の結果、出力クロックの周波数がジッタ制御テーブルに合わせて変動している場合には、ステップS110へ進む。ステップS110にて、位相比較器60は、入力クロックに対応するリファレンスクロックREFCLK1と出力クロックに対応するフィードバッククロックFBCLK(ジッタ成分が除去された出力クロックOUTCLK2)との周波数を比較する。

【0045】

ステップS110での比較の結果、入力クロックと出力クロックとの周波数が異なり(S111のNO)、かつ出力クロックの周波数が入力クロックの周波数より高い(S112のYES)ときには、制御部30は、制御データから“1”を減算しステップS110に戻る(S113)。また、入力クロックと出力クロックとの周波数が異なり(S111のNO)、かつ出力クロックの周波数が入力クロックの周波数より高くない(S112のNO)ときには、制御部30は、制御データに“1”を加算しステップS110に戻る(S114)。

【0046】

前述したステップS110〜S114の処理を入力クロックと出力クロックとの周波数が同じになるまで繰り返し行う。そして、入力クロックと出力クロックとの周波数が同じになると(S111のYES)、ステップS115にて、制御部30は、すべてのジッタ設定に対するテストが完了したか否かを判断する。その結果、実施していないテストがある場合には、ステップS105に戻り、未実施のジッタ設定でステップS105以降の処理を再び行う。一方、すべてのジッタ設定に対するテストが完了している場合には、ジッタ付加試験を終了する。

【0047】

なお、本実施形態においてDDS20は、制御データFCTLに応じた周波数の正弦波を出力する例を示したが、DDS20の出力信号は正弦波に限定されるものではない。DDS20が、正弦波とは異なる他の周期性を有する信号の振幅データに係るルックアップテーブルを持ち、それに応じた出力信号を出力可能であっても良い。

【0048】

また、本実施形態においてジッタ制御テーブルには、同じ設定データが連続する場合でもそれぞれの設定データが分けて格納されているが、ジッタ制御テーブルはこの形式に限定されるものではない。例えば、設定データとその設定データが連続する個数とを組にしてジッタ制御テーブルに格納し、制御部30が、格納された個数の情報に従って、対応する設定データを繰り返し出力するように制御しても良い。

【0049】

なお、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

【符号の説明】

【0050】

10 分周器

20 ダイレクトデジタルシンセサイザ(DDS)

21 位相アキュムレータ

22 正弦波変換部

23 デジタルアナログ変換部(DAC)

30 制御部

31 デコーダ

32 テーブル読み出し部

33 メモリ

34 テーブル保持部

35 補正処理部

36 出力部

37A、37B、37C ジッタ制御テーブル

40 PLL回路

50 フィルタ

60 位相比較器

【特許請求の範囲】

【請求項1】

基準クロックに基づいて、入力される制御データに応じた周波数の出力信号を生成し出力するダイレクトデジタルシンセサイザと、

前記基準クロックに同期させて前記ダイレクトデジタルシンセサイザに前記制御データを供給する制御部とを備え、

前記制御部は、設定されるジッタの周波数及び大きさに応じて前記ダイレクトデジタルシンセサイザの出力周波数を制御するための一連の設定データが格納された制御テーブルを有し、前記基準クロックに同期したタイミングで前記制御データを前記制御テーブルに格納されている前記設定データで順次書き替えることを特徴とする信号生成装置。

【請求項2】

前記制御テーブルは、1周期分の前記設定データが格納されていることを特徴とする請求項1記載の信号生成装置。

【請求項3】

前記制御部は、前記制御テーブルを複数有し、前記ダイレクトデジタルシンセサイザの出力周波数の制御に用いる前記制御テーブルを、設定されるジッタの周波数及び大きさに応じて選択することを特徴とする請求項1又は2記載の信号生成装置。

【請求項4】

入力される2つの信号の位相を比較する位相比較器を備え、

前記制御部は、前記位相比較器による前記基準クロックと前記ダイレクトデジタルシンセサイザの出力信号とに係る位相比較の結果に基づいて、前記ダイレクトデジタルシンセサイザに供給する前記制御データに補正処理を施すことを特徴とする請求項1〜3の何れか1項に記載の信号生成装置。

【請求項5】

前記ダイレクトデジタルシンセサイザの出力信号を逓倍する位相ロックループ回路を備えることを特徴とする請求項1〜4の何れか1項に記載の信号生成装置。

【請求項6】

前記制御テーブルは、前記基準クロックの周期毎に、1周期に対して1つの前記設定データが格納されていることを特徴とする請求項1〜5の何れか1項に記載の信号生成装置。

【請求項7】

基準クロックに基づいて、入力される制御データに応じた周波数の出力信号を生成し出力するダイレクトデジタルシンセサイザを用いた信号生成方法であって、

設定されるジッタの周波数及び大きさに応じて前記ダイレクトデジタルシンセサイザの出力周波数を制御するための制御テーブルに格納されている一連の設定データで前記制御データを前記基準クロックに同期したタイミングで順次書き替えて、前記制御データを前記ダイレクトデジタルシンセサイザに供給することを特徴とする信号生成方法。

【請求項8】

前記基準クロックと前記ダイレクトデジタルシンセサイザの出力信号とに係る位相比較を行い、前記位相比較の結果に基づいて、前記ダイレクトデジタルシンセサイザに供給する前記制御データに補正処理を施すことを特徴とする請求項7記載の信号生成方法。

【請求項1】

基準クロックに基づいて、入力される制御データに応じた周波数の出力信号を生成し出力するダイレクトデジタルシンセサイザと、

前記基準クロックに同期させて前記ダイレクトデジタルシンセサイザに前記制御データを供給する制御部とを備え、

前記制御部は、設定されるジッタの周波数及び大きさに応じて前記ダイレクトデジタルシンセサイザの出力周波数を制御するための一連の設定データが格納された制御テーブルを有し、前記基準クロックに同期したタイミングで前記制御データを前記制御テーブルに格納されている前記設定データで順次書き替えることを特徴とする信号生成装置。

【請求項2】

前記制御テーブルは、1周期分の前記設定データが格納されていることを特徴とする請求項1記載の信号生成装置。

【請求項3】

前記制御部は、前記制御テーブルを複数有し、前記ダイレクトデジタルシンセサイザの出力周波数の制御に用いる前記制御テーブルを、設定されるジッタの周波数及び大きさに応じて選択することを特徴とする請求項1又は2記載の信号生成装置。

【請求項4】

入力される2つの信号の位相を比較する位相比較器を備え、

前記制御部は、前記位相比較器による前記基準クロックと前記ダイレクトデジタルシンセサイザの出力信号とに係る位相比較の結果に基づいて、前記ダイレクトデジタルシンセサイザに供給する前記制御データに補正処理を施すことを特徴とする請求項1〜3の何れか1項に記載の信号生成装置。

【請求項5】

前記ダイレクトデジタルシンセサイザの出力信号を逓倍する位相ロックループ回路を備えることを特徴とする請求項1〜4の何れか1項に記載の信号生成装置。

【請求項6】

前記制御テーブルは、前記基準クロックの周期毎に、1周期に対して1つの前記設定データが格納されていることを特徴とする請求項1〜5の何れか1項に記載の信号生成装置。

【請求項7】

基準クロックに基づいて、入力される制御データに応じた周波数の出力信号を生成し出力するダイレクトデジタルシンセサイザを用いた信号生成方法であって、

設定されるジッタの周波数及び大きさに応じて前記ダイレクトデジタルシンセサイザの出力周波数を制御するための制御テーブルに格納されている一連の設定データで前記制御データを前記基準クロックに同期したタイミングで順次書き替えて、前記制御データを前記ダイレクトデジタルシンセサイザに供給することを特徴とする信号生成方法。

【請求項8】

前記基準クロックと前記ダイレクトデジタルシンセサイザの出力信号とに係る位相比較を行い、前記位相比較の結果に基づいて、前記ダイレクトデジタルシンセサイザに供給する前記制御データに補正処理を施すことを特徴とする請求項7記載の信号生成方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図10】

【公開番号】特開2013−61278(P2013−61278A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−200697(P2011−200697)

【出願日】平成23年9月14日(2011.9.14)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月14日(2011.9.14)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]