信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、信号生成装置及び周波数シンセサイザに関する。

【背景技術】

【0002】

標準信号発生器の一つとしてPLL(Phase Locked Loop)を用いた周波数シンセサイザが知られており、その応用としては例えば移動局における局発振部や無線通信機器の試験用信号源、放送機器などが挙げられる。通信分野において周波数シンセサイザを適用する場合には、他のチャンネルとの混信を避けるためにノイズが少ないことが要求され、電波が過密化している状況下では周波数をできるだけ細かく設定できることが望ましい。

【0003】

そこで本件出願人は、このような要請を充足しつつ、回路構成が簡素な周波数シンセサイザを開発し、その技術は既に特許文献1などに開示されている。例えば特許文献1の手法では、電圧制御発振器の出力信号をA/D(アナログ/ディジタル)変換し、そのディジタル信号を処理してD/A変換し、得られたアナログ信号を電圧制御発振器に制御電圧として入力している。

【0004】

しかしながらこのような装置は、A/D(アナログ/ディジタル)変換し、そのディジタル信号を処理してD/A変換しているため、スプリアス特性を良好化するには限界があり、またA/D、D/Aの両変換を行うことから、十分な回路の簡素化が図られているとは言い難いという課題がある。

特許文献2には、ディジタルデータに応じた周波数の三角波を生成し、コンパレータを用いてアナログの三角波のゼロクロスタイミングを求めて三角波の周波数に対応した周波数のパルス信号を得る手法が開示されている。この技術ではディジタルデータをD/A変換した後、アナログの三角波を直線補間している。直線補間する目的は、アナログの三角波がゼロ点をクロスするタイミングがディジタル信号のサンプルタイミングよりも高い精度にできないことから、ゼロクロスタイミングを周波数に応じたタイミングに固定するためである(段落0019〜0023)。しかしながら、この信号発生器を用いてリファレンス信号を生成し、PLLを組んだ場合、三角波のゼロクロスを正確に検出できないことから、位相雑音を低下させるには十分とはいえない。

【0005】

以上のことをまとめると、回路構成が簡素な周波数シンセサイザを制作することが要求されている共に、例えばこの要求に応える周波数シンセサイザを構築するにあたって、リファレンス信号などに用いられる基準信号例えばクロック信号について低ノイズな良質な信号を簡易な回路構成で生成することも要求されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−74291号公報

【特許文献2】特開平5−206732号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明はこのような事情の下になされたものであり、本発明の目的は、例えば周波数シンセサイザのリファレンス信号などに利用できる低ノイズの周波数信号を生成できる技術を提供することにある。本発明の他の目的はPLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好な周波数シンセサイザを提供することにある。

【課題を解決するための手段】

【0008】

本発明の信号生成装置は、鋸歯状の積分波形が予め設定したしきい値を跨ぐタイミングに基づいてパルス信号を出力する装置において、

クロック信号を出力するクロック源と、

設定周波数に応じたディジタル値を有するディジタル信号が入力され、このディジタル値を前記クロック信号に基づいて積分することにより、鋸歯状の積分波形を生成する積分波形生成部と、

前記積分波形生成部から出力される前記ディジタル値が一方向に変化する領域において、予め設定したしきい値の前後のディジタル値を含む、等間隔の奇数個のディジタル値列の先頭のディジタル値及び最後部のディジタル値を夫々読み出した先頭クロック信号及び後方クロック信号を出力するクロック情報出力部と、

前記先頭のディジタル値としきい値との差分と、最後部のディジタル値と前記しきい値との差分と、の比率に応じた係数値を出力する回路部と、

前記係数値に基づいて、予め設定した時間だけ前記積分波形のディジタル値が前記しきい値になっている時点とみなす先頭クロック信号及び後方クロック信号の使用比率に対応する信号を出力する使用比率決定部と、

前記クロック情報出力部から出力された先頭クロック信号及び後方クロック信号の一方を、予め設定された時間だけ、前記使用比率決定部から出力される使用比率に対応する信号により選択して出力するクロック選択部と、

このクロック選択部から出力されたクロック信号毎にトグルされ、トグルされて得られたパルス信号を出力する信号出力部と、を備えたことを特徴とする。

【0009】

前記予め設定したしきい値は例えばゼロである。

【0010】

具体例を挙げれば、 先頭のディジタル値及び最後部のディジタル値を読み出したクロック信号を夫々P1及びP3とし、奇数個のディジタル値列の中央のディジタル値を読み出したクロック信号をP2とすると、

前記クロック情報出力部は、クロック信号P1及びP3を出力するように構成され、

前記使用比率決定部において、予め設定した時間だけ前記積分波形のディジタル値が前記しきい値になっている時点とみなす先頭クロック信号及び後方クロック信号は、夫々クロック信号P1及びP3である。

【0011】

また前記クロック選択部は、選択信号であるパルス信号の信号レベルが「H」及び「L」の一方により先頭クロック信号が選択され、他方により後方クロック信号が選択されるように構成され、

前記使用比率決定部は、デューティ比の平均が前記しきい値の直前のディジタル値及び直後のディジタル値の比率に対応する値となる、前記選択信号をなすPWMパルス列を出力するΔΣ回路である。

【0012】

本発明の周波数シンセサイザは、電圧制御発振器から出力される周波数信号を分周器を介して位相比較部に帰還し、帰還された周波数信号と設定周波数に対応する参照周波数信号とを位相比較部にて比較し、その比較結果を前記電圧制御発振器に入力する周波数シンセサイザにおいて、

前記参照周波数信号として、本発明の信号生成装置から出力される信号を用いることを特徴とする。

【発明の効果】

【0013】

本発明は、例えばPLLを用いた周波数シンセサイザに用いられる参照周波数信号を、ディジタル信号からなる鋸波の予め設定したしきい値例えばゼロクロスポイントを検出したときのクロックに基づいて生成するにあたって、ディジタル値が飛び飛びの値であることからディジタル値が前記しきい値になるとは限らない点に着目している。このため前記ディジタル値が徐々に変化する領域においてディジタル値が前記しきい値を跨ぐ直前のディジタル値及び直後のディジタル値の比率に対応する比率で前記しきい値の前後の2つのクロック信号を使用している。従って前記しきい値の直前または直後のクロック信号を一律に用いる手法と比較すれば低ノイズの周波数信号を得ることができる。そしてこの周波数信号を利用して周波数シンセサイザを構成すれば、スプリアス特性が改善されるという効果がある。

【図面の簡単な説明】

【0014】

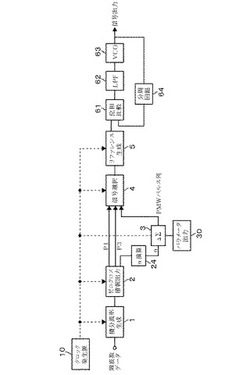

【図1】本発明に係る周波数シンセサイザの実施形態の全体構成を示すブロック図である。

【図2】積分波形生成部の回路を示すブロック図である。

【図3】積分波形生成部の動作を示す説明図である。

【図4】積分波形生成部の出力波形を示す波形図である。

【図5】ゼロクロス情報出力部を示すブロック図である。

【図6】積分波形である鋸波がゼロ点をクロスする様子を示す説明図である。

【図7】積分波形である鋸波がゼロ点をクロスする様子を示す説明図である。

【図8】積分波形である鋸波のゼロクロス時の直前のディジタル値及び直後のディジタル値の比率に対応する係数値を説明するための説明図である。

【図9】図1に示す一部の回路要素を鋸波を構成するディジタルデータと関連付けて示す説明図である。

【図10】クロック選択部を示す回路図である。

【図11】積分波形である鋸波のゼロクロス時の直前のディジタル値及び直後のディジタル値の比率に対応する係数値に応じてクロック信号P1、P3が選択される様子を示すタイムチャートである。

【図12】クロック信号P1のみをゼロクロスのタイミングとして捕らえた場合の周波数特性と本発明における周波数特性とを比較して示す特性図である。

【発明を実施するための形態】

【0015】

本発明に係る信号生成装置を周波数シンセサイザに適用した実施形態について説明すると、図1はこの実施の全体構成を示すブロック図であり、1は積分波形生成回路部である。この積分波形生成回路部1は、入力されたディジタル値(周波数データ)に応じた周波数の鋸波をディジタルデータで出力する機能を有し、図2に示すように加算部11の後段にフリップフロップ回路12を設け、フリップフロップ回路12の出力を加算部11にて入力値と加算するように構成されている。フリップフロップ回路12には、クロック発生源10からクロック信号が入力され、クロック信号の入力のタイミングにより加算部11からの入力データが出力される。クロック信号の周波数は、出力されるディジタル値群により特定される鋸波の周波数として例えば5MHzを得たい場合には、例えば20MHz程度とされる。

【0016】

積分波形生成回路部1の動作について、説明の便宜上4ビットのディジタル値により動作する場合を例に挙げて図3を参照しながら説明する。ディジタル値は「2」の補数として取り扱われており、例えば当該回路部1に入力される周波数データである入力値が例えば「0001」であるとすると、入力値と加算部11とが加算されて加算値が増えていくが、加算値が「0111」となり、次に「0001」が入力されると、「1000」となって十進値は負の値に変わる。従ってフリップフロップ回路12に入力されるクロック信号のパルス番号(便宜上の番号である)と、周波数データ(入力値)と、出力値との関係は図3に示すようになり、図4に示すように出力波形は入力値の積分波形である鋸波となる。そしてこの鋸波の周波数は、設定される周波数データである入力値に応じて決まることから、この周波数データは後述のように信号発生器の設定周波数を決定するデータとなる。なお積分波形生成回路部1のディジタル信号は、4ビットで説明しているが、実際には例えば32ビットの信号が用いられる

積分波形生成回路部1の後段には、ゼロクロス情報出力部2が設けられ、このゼロクロス情報出力部2の後段には、使用比率決定部であるΔΣ回路3と信号選択部4とが設けられている。理解の容易さを優先するために、ゼロクロス情報出力部2、ΔΣ回路3及び信号選択部4の構成を説明する前に、これらの回路を使用する目的、役割について述べておく。

【0017】

積分波形生成回路部1から出力される鋸波を構成するディジタル値が徐々に変化する領域においてディジタル値の符号が負から正に反転するゼロクロス時の直前のディジタル値を読み出したクロック信号をP1とし、ゼロクロス時の直後のディジタル値を読み出したクロック信号をP2とし、前記クロック信号P1よりも2クロック遅れたクロック信号をP3とすると、クロック信号P1〜P3と鋸波のディジタル値との関係は図6に示すように表される。なお、前記鋸波の実際の波形図は各ディジタル値毎に階段状になっている。

【0018】

図3に示す例における鋸波は、積分波形生成回路部1に入力される周波数設定データである入力値(ディジタル値)が「1」(0001)であることから、十進値で「1」ずつインクリメントされ、このため鋸波が繰り返される度にディジタル値が第1のしきい値である「0」となるタイミングが存在する。しかし前記入力値が「3」(0011)である場合には、例えば「−7」、「−4」、「−1」、「2」という具合にディジタル値が増加していくことから、正確なゼロクロスポイント、つまり「0」を検出するクロック信号が存在しなくなる。

【0019】

一方、積分波形生成回路部1に入力される周波数設定データは、最終的に後述の電圧制御発振器から出力される周波数を設定するための設定信号である。例えばクロック発生源10から出力されるクロック信号の周波数が16MHzであるとすると、周波数設定データを「1」とすれば、鋸波の周波数は1MHzとなり(図3参照)、周波数設定データを「2」とすれば、2MHzとなる。図3の例は説明用の模式的な一例であり、実際にはディジタル信号は例えば32ビットで構成され、ディジタル値が「0」をとることは稀である。

【0020】

このためほとんどの場合、ディジタル値が負から正に移行するときには「0」を跨ぐことになるので、正確なゼロクロスポイントを検出することができない。この場合、ゼロクロスする直前のディジタル値を読み取るクロック信号であるP1をゼロクロスポイントとみなすことが考えられるが、そうすると周波数シンセサイザのスプリアス特性について良好な特性を得ることが困難である。そこでこの実施形態では、クロック信号P1とP3との一方をゼロクロスポイントとみなし、P1におけるディジタル値(P1で読み出されるディジタル値)とP2におけるディジタル値とに基づいて、ゼロクロスポイントとして取り扱うクロック信号P1とP3との使用比率、つまりクロック信号P1をゼロクロスポイントとして使用する態様と、クロック信号P2をゼロクロスポイントとして使用する態様と、の選択比率を決定するようにしている。なお以下の説明ではクロック信号P1(P2、P3)に対応するディジタル値という表現を「P1(P2、P3)の値」と略記する。

【0021】

即ち、周波数設定データが決まっているので、図7においてP2が第1のしきい値である「0」であるときのP1の値は予め分かっている。説明の便宜上このときのP1の値を第2のしきい値である「−50」とすると、P1の値が「−50」であれば、正確なゼロクロスポイントはクロック信号P1とP3との中間位置にあることになる。このときのクロック信号P1とP3との使用比率は50%であり、予め設定された時間内においてゼロクロスパルスとして使用されるクロック信号P1の数とクロック信号P3の数とは1:1となる。より一般的に言えば、図7に示すように前記使用比率をαとすると、P1の値がYであるとき、α=1−(Y/Ym)で表される。YmはP3がゼロクロスポイントであるときのP1の値であり、Yが0.5Ymのとき、αは0.5(50%)である。またYが0のときαは1(100%)となり、この場合は予め設定された時間内においてゼロクロスパルスとして使用されるクロック信号はP1だけとなる。またYがYm/3のときにはαは2/3(66.7%)となり、この場合は予め設定された時間内においてゼロクロスパルスとして使用されるクロック信号P1の数とクロック信号P3の数とは2:1となる。

【0022】

図8は、P1〜P3の値及び時間的位置と、クロック信号P1、P3の使用比率(%)の一例とを対応付けて示した図である。このようにクロック信号P2がゼロクロスポイントであるときには(P2の値が0であるときには)、所定時間内にてクロック信号P1、P3を半分ずつ使用し、この状態からP1の値が0に近づくほどクロック信号P1の使用回数を増やしている。即ち、正確なゼロクロスポイントは得られなくとも、所定時間内においてはP1の値とP2の値との比率はそれ程変動せず、このため所定時間内においてゼロクロスポイントとみなしたディジタル値の値を平均すれば、0に近い値となっているものと推測している。この推測は後述の実験例から適切であることが裏付けられている。

【0023】

このようないわばゼロクロスポイントの擬似処理を行う回路部分について説明すると、ゼロクロス情報検出部2は図5に示すように、P1検出部21を備えている。このP1検出部21は、鋸波を構成するディジタル値が第2のしきい値以上になるタイミングを検出するためのものであり、前記ディジタル値と第2のしきい値とを比較し、ディジタル値が第2のしきい値よりも小さい値から、第2のしきい値以上の値に変わったときにP1検出パルスを出力するように構成される。第2のしきい値は、既述のようにP2が第1のしきい値である「0」であるときのP1の値であり、後述の図7の例ではYm/2に相当する。第2のしきい値をこのように設定する理由は、P1は、第2のしきい値と第1のしきい値との間に存在するからである。

【0024】

図5中22は、ゼロクロスポイントの候補となる2つのクロック信号P1、P3を出力するための回路部であり、ゼロクロス検出パルスとクロック信号とのアンドをとる2つのアンド回路22a、22bと、一方のアンド回路22bに入力されるゼロクロス検出パルスを2クロック分だけ遅延させる遅延回路22cとを備えている。

【0025】

また221は前記ゼロクロス検出パルスをラッチイネーブル信号として鋸波データ(ディジタル値)をP1の値として出力するフリップフロップ回路であり、223は前記ゼロクロス検出パルスを遅延回路222で1クロック分遅延させたパルスをラッチイネーブル信号とし、鋸波データをP2の値として出力するフリップフロップ回路である。この実施形態ではP1の値だけを使用して比率αを求めているが、例えば鋸波の周期が分からない場合つまり互に連続するディジタル値の飛びの値が分からない場合には、P1の値の次のP2の値は分からないため、P2の値も必要になる。

【0026】

図1に戻って、ゼロクロス情報出力部2にて得られたP1の値は、クロック信号P1、P3の使用比率であるαを演算する回路部24に取り込まれ、この回路部24にて既述の演算(α=1−(Y/Ym))が行われる。ΔΣ回路3は、前記使用比率であるαを取り込み、予め設定された時間だけ、デューティ比の平均値がαとなるPWM(パルス幅変調)パルス列を出力する回路部分である。またΔΣ回路3は、使用比率αを取り込み、P1、P3の比率をΔΣ変調によって生成することで、近傍量子化ノイズを低減させる。30はパラメータ出力部であり、前記回路部24及びΔΣ回路3に必要なパラメータ、ΔΣ回路3のフィードバックゲイン(周波数により可変)を出力する部分である。なお、前記回路部24は、ゼロクロス情報出力部2の一部として取り扱うこともできる。

【0027】

信号選択部4は、ゼロクロス情報検出部2から出力されたクロック信号P1、P3のうち、ΔΣ回路3から出力されるP1、P3選択信号により一方が選択されてゼロクロスポイントとみなすクロック信号の列(擬似ゼロクロスポイントの列)を出力する機能を有する。図9は、鋸波を構成するディジタルデータとΔΣ回路3及び信号選択部4とを対応付けて示す説明図である。信号選択部4は、パルス信号P1とΔΣ回路3からの信号とのアンド条件をとるアンド回路41と、パルス信号P3とΔΣ回路3からの信号を否定回路43にて反転した信号とのアンド条件をとるアンド回路42と、これらアンド回路41、42のオア条件をとるオア回路44とを含む。

【0028】

信号選択部4の後段には、後述のPLLにて使用される参照周波数信号であるリファレンス信号を生成するリファレンス信号生成部5が設けられている。このリファレンス信号生成部5は、信号選択部4から出力される、ゼロクロスポイントとみなすパルス信号によりトグルされたパルスをリファレンス信号として出力する機能を有する。

リファレンス生成部5の後段にはPLLを構成する位相比較部61、ローパスフィルタ(LPF)62、電圧制御発振器(VCO)63、及び分周回路64が設けられている。

【0029】

ここで、既に図1の回路の一部の作用については詳述しているが、上述実施形態の全体作用について、簡単にまとめて述べておく。この周波数シンセサイザから得ようとする周波数の設定を図示しない設定部でおこない、この設定部から設定周波数に応じた周波数データが積分波形生成部1に入力され、例えば図4及び図6に模式的な例として示すようにディジタル信号からなる鋸波が生成される。この鋸波は後述のPLLにおける位相を決定するためのものである。そしてクロック発生源10からのクロック信号により、ゼロクロス情報出力部2にて、鋸波を形成するディジタル値が読み出され、前記ディジタル値が徐々に変化する領域において正、負の符号が反転するゼロクロス時、この例では負から正に反転するゼロクロス時の直前のディジタル値を読み出すクロック信号P1と、このクロック信号P1よりも2クロック遅れたクロック信号P3とが出力される。またクロック信号P1により読み出されたディジタル値(P1の値)がゼロクロス情報出力部2から出力される。

【0030】

更にP1の値に基づいて、既に図7及び図8等を用いて詳述したように、ゼロクロスポイントとみなしたクロック信号P1及びP3とを、どれだけの比率で使用するかを決定し、この比率(使用比率)に対応するP1、P3選択信号を出力する。この一連の決定は、回路部24及びΔΣ回路3により行われる。

【0031】

図11は、ゼロクロス情報検出部2から出力されるクロック信号P1及びP3と、ΔΣ回路3から出力されるPWMパルス列と、リファレンス生成部5にて生成されるリファレンス信号と、を対応付けて示すタイムチャートである。なお、紙面の制約から、時間軸の長さについては模式的な大きさである。図10に信号選択部4を示してあるように、クロック信号P1については、ΔΣ回路3の出力の「H」により選択され、クロック信号P3についてはΔΣ回路3の出力の「L」により選択される。従って前記使用比率が50%(αが0.5)のときにはΔΣ回路3の出力からデューティ比50%のパルス列が出力され、クロック信号P1、P2が交互に選択されることになる。

【0032】

また前記使用比率が66、7%のときにおけるクロック信号の選択の様子を実際に沿って示すことが困難なことから、ΔΣ回路3の出力からデューティ比が2/3のパルスが出力されているものとして描いている。この場合、クロック信号P1が2回選択され、クロック信号P2が1回選択される。実際には、PWMパルス列により選択された結果、設定時間内におけるクロック信号P1とP2との選択回数が2:1になる。既述のように、短い設定時間内であれば、正しいゼロクロスポイントがそれ程変化しないであろうという前提でこのような処理を行っている。

【0033】

そして選択されたクロック信号P1またはP2のパルス列によりトグルされてリファレンス信号が得られ、位相比較部61にて、電圧制御発振器63から分周回路64を介して送られた周波数信号と当該リファレンス信号との位相比較が行われ、その結果が電圧制御発振器63の制御電圧となってPLLループが構成され、PLLがロックしたときに、電圧制御発振器63から設定された周波数である周波数信号が得られる。

【0034】

上述実施の形態によれば、PLLを用いた周波数シンセサイザにおいてディジタル信号である周波数設定データに基づいて鋸波を生成し、概略的にはこの鋸波のゼロクロスポイントを検出してリファレンス信号を生成している。従って先の特許文献1の手法のようにA/D変換及びD/A変換を行わなくてよいので、回路構成が簡素化される。そしてPLLを用いた周波数シンセサイザに用いられる参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成するにあたって、ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない点に着目している。

【0035】

このため前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の前後のディジタル値を読み出したクロック信号P1、P3を擬似ゼロクロスポイントの候補とし、ゼロクロス時の直前、直後のディジタル値に基づいて(ただし一方の値が分かれば他方の値も分かる)、クロック信号P1、P3の使用比率を決定している。更にクロック信号P1、P3のタイミングを時間的に平均すれば正確なゼロクロスポイントに近いクロックが取り出せているであろうと推測して、選択されたクロック信号P1、P3によりトグルしてリファレンス信号を得ている。このため周波数シンセサイザの出力におけるスプリアス特性が良好である。

【0036】

本発明では、鋸波のディジタル値が正から負に向かって徐々に減少するように構成してもよく、この場合にはディジタル値が正から負に反転する時点がゼロクロス時となる。またクロック信号P1、P3の使用比率を決定するために、上述の例ではP1の値を用いているが、P2の値を用いてもよいし、P1、P2の両方の値を用いて例えばこれらの比を求めるといった手法であってもよい。

【0037】

更にまたゼロクロスポイントとみなすクロック信号としては、P1、P3に限られるものではなく、例えば鋸波を構成するポイント(符号が反転するポイントは除く)でP1、P3の条件を満たす箇所であればどこでもよい。即ち、鋸波のデータが負から正に変わった後において一定の数だけ後のデータ例えば5個後のデータをP1として取り扱っても、先の実施の形態と実質同じである。この場合例えばデータを構成するディジタル値がゼロであれば、P1、P3のパルスが50%ずつ使用される。またP1に対して奇数個後ろのパルスであれば、両パルスの真ん中にデータが位置するので例えばP1、P5の組を用いても良い。

【0038】

言い換えれば本発明は、鋸波がある値(第1のしきい値)を取るたびに信号出力部からパルス信号を出力する手法であることから、第1のしきい値としてはゼロに限らない。例えば図5に示すP1検出部21をゼロクロス検出部(ディジタル値が負から正に変化したとき、例えばMSBが1から0に変わるときを検出する検出部)として構成してもよい。この場合には、P3のクロックの次のクロックをP4とすると、例えばP2、P3、P4の3つのクロックを用いることになり、P2が先頭クロック信号、P4が最後部クロック信号となる。そして例えば鋸波を形成する前後のディジタル値の差が「50」であるとすると、第1のしきい値は「50」であり、第2のしきい値はゼロである。また例えばP2の値が分かれば、P2と第2のしきい値との差分、及びP4と第2のしきい値との差分が分かるので、比率αを決定することができる。

【0039】

ゼロクロス検出部21として、鋸波データ(鋸波のディジタル値)がゼロ以外のしきい値を越えたときにパルスを出力する回路を用いることができる。この場合においても、時間軸をずらせば、ゼロクロスを検出していることと実質同じである。

【0040】

また例えば40MHzのクロックを用いて上述の実施の形態のように先頭クロック信号であるP1と後方クロック信号であるP3とを用いることと、80MHzのクロックを用いて連続して5個並ぶP1からP5までのクロック信号のうち、P1、P5を夫々先頭クロック信号及び後方クロック信号として用いることとは、実質同じである。従って等間隔の奇数個のディジタル値列の先頭のディジタル値及び最後部のディジタル値を夫々読み出した先頭クロック信号及び後方クロック信号を出力するために、前記ディジタル値列の数は3個に限らず、5個以上であってもよい。

【実施例】

【0041】

本発明の効果の確認を行うために、図1に示した回路を用いた場合(実施例)と、ゼロクロスポイントとしてクロック信号P3だけを用いた場合(比較例)と、の夫々においてリファレンス信号生成部5から得られる周波数信号のスプリアス特性を調べた。リファレンス信号生成部5はDDS(Direct Digital Synthesizer)により構成され、設定出力周波数は、312.5kHzである。なお後者の比較例は図1に示した回路においてΔΣ回路3を停止させて行った。図12は、スプリアス特性を示す図であり、Aは実施例、Bは比較例である。この結果から分かるように、本発明によればスプリアス特性が良好であることが分かる。

【符号の説明】

【0042】

1 積分波形生成回路部

10 クロック発生源

2 ゼロクロス情報出力部

21 ゼロクロス検出部

22 クロック信号P1、P3を出力する回路部

23 P1値出力部

3 ΔΣ回路部

4 信号選択部

5 リファレンス生成部

61 位相比較部

63 電圧制御発振器

【技術分野】

【0001】

本発明は、信号生成装置及び周波数シンセサイザに関する。

【背景技術】

【0002】

標準信号発生器の一つとしてPLL(Phase Locked Loop)を用いた周波数シンセサイザが知られており、その応用としては例えば移動局における局発振部や無線通信機器の試験用信号源、放送機器などが挙げられる。通信分野において周波数シンセサイザを適用する場合には、他のチャンネルとの混信を避けるためにノイズが少ないことが要求され、電波が過密化している状況下では周波数をできるだけ細かく設定できることが望ましい。

【0003】

そこで本件出願人は、このような要請を充足しつつ、回路構成が簡素な周波数シンセサイザを開発し、その技術は既に特許文献1などに開示されている。例えば特許文献1の手法では、電圧制御発振器の出力信号をA/D(アナログ/ディジタル)変換し、そのディジタル信号を処理してD/A変換し、得られたアナログ信号を電圧制御発振器に制御電圧として入力している。

【0004】

しかしながらこのような装置は、A/D(アナログ/ディジタル)変換し、そのディジタル信号を処理してD/A変換しているため、スプリアス特性を良好化するには限界があり、またA/D、D/Aの両変換を行うことから、十分な回路の簡素化が図られているとは言い難いという課題がある。

特許文献2には、ディジタルデータに応じた周波数の三角波を生成し、コンパレータを用いてアナログの三角波のゼロクロスタイミングを求めて三角波の周波数に対応した周波数のパルス信号を得る手法が開示されている。この技術ではディジタルデータをD/A変換した後、アナログの三角波を直線補間している。直線補間する目的は、アナログの三角波がゼロ点をクロスするタイミングがディジタル信号のサンプルタイミングよりも高い精度にできないことから、ゼロクロスタイミングを周波数に応じたタイミングに固定するためである(段落0019〜0023)。しかしながら、この信号発生器を用いてリファレンス信号を生成し、PLLを組んだ場合、三角波のゼロクロスを正確に検出できないことから、位相雑音を低下させるには十分とはいえない。

【0005】

以上のことをまとめると、回路構成が簡素な周波数シンセサイザを制作することが要求されている共に、例えばこの要求に応える周波数シンセサイザを構築するにあたって、リファレンス信号などに用いられる基準信号例えばクロック信号について低ノイズな良質な信号を簡易な回路構成で生成することも要求されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−74291号公報

【特許文献2】特開平5−206732号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明はこのような事情の下になされたものであり、本発明の目的は、例えば周波数シンセサイザのリファレンス信号などに利用できる低ノイズの周波数信号を生成できる技術を提供することにある。本発明の他の目的はPLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好な周波数シンセサイザを提供することにある。

【課題を解決するための手段】

【0008】

本発明の信号生成装置は、鋸歯状の積分波形が予め設定したしきい値を跨ぐタイミングに基づいてパルス信号を出力する装置において、

クロック信号を出力するクロック源と、

設定周波数に応じたディジタル値を有するディジタル信号が入力され、このディジタル値を前記クロック信号に基づいて積分することにより、鋸歯状の積分波形を生成する積分波形生成部と、

前記積分波形生成部から出力される前記ディジタル値が一方向に変化する領域において、予め設定したしきい値の前後のディジタル値を含む、等間隔の奇数個のディジタル値列の先頭のディジタル値及び最後部のディジタル値を夫々読み出した先頭クロック信号及び後方クロック信号を出力するクロック情報出力部と、

前記先頭のディジタル値としきい値との差分と、最後部のディジタル値と前記しきい値との差分と、の比率に応じた係数値を出力する回路部と、

前記係数値に基づいて、予め設定した時間だけ前記積分波形のディジタル値が前記しきい値になっている時点とみなす先頭クロック信号及び後方クロック信号の使用比率に対応する信号を出力する使用比率決定部と、

前記クロック情報出力部から出力された先頭クロック信号及び後方クロック信号の一方を、予め設定された時間だけ、前記使用比率決定部から出力される使用比率に対応する信号により選択して出力するクロック選択部と、

このクロック選択部から出力されたクロック信号毎にトグルされ、トグルされて得られたパルス信号を出力する信号出力部と、を備えたことを特徴とする。

【0009】

前記予め設定したしきい値は例えばゼロである。

【0010】

具体例を挙げれば、 先頭のディジタル値及び最後部のディジタル値を読み出したクロック信号を夫々P1及びP3とし、奇数個のディジタル値列の中央のディジタル値を読み出したクロック信号をP2とすると、

前記クロック情報出力部は、クロック信号P1及びP3を出力するように構成され、

前記使用比率決定部において、予め設定した時間だけ前記積分波形のディジタル値が前記しきい値になっている時点とみなす先頭クロック信号及び後方クロック信号は、夫々クロック信号P1及びP3である。

【0011】

また前記クロック選択部は、選択信号であるパルス信号の信号レベルが「H」及び「L」の一方により先頭クロック信号が選択され、他方により後方クロック信号が選択されるように構成され、

前記使用比率決定部は、デューティ比の平均が前記しきい値の直前のディジタル値及び直後のディジタル値の比率に対応する値となる、前記選択信号をなすPWMパルス列を出力するΔΣ回路である。

【0012】

本発明の周波数シンセサイザは、電圧制御発振器から出力される周波数信号を分周器を介して位相比較部に帰還し、帰還された周波数信号と設定周波数に対応する参照周波数信号とを位相比較部にて比較し、その比較結果を前記電圧制御発振器に入力する周波数シンセサイザにおいて、

前記参照周波数信号として、本発明の信号生成装置から出力される信号を用いることを特徴とする。

【発明の効果】

【0013】

本発明は、例えばPLLを用いた周波数シンセサイザに用いられる参照周波数信号を、ディジタル信号からなる鋸波の予め設定したしきい値例えばゼロクロスポイントを検出したときのクロックに基づいて生成するにあたって、ディジタル値が飛び飛びの値であることからディジタル値が前記しきい値になるとは限らない点に着目している。このため前記ディジタル値が徐々に変化する領域においてディジタル値が前記しきい値を跨ぐ直前のディジタル値及び直後のディジタル値の比率に対応する比率で前記しきい値の前後の2つのクロック信号を使用している。従って前記しきい値の直前または直後のクロック信号を一律に用いる手法と比較すれば低ノイズの周波数信号を得ることができる。そしてこの周波数信号を利用して周波数シンセサイザを構成すれば、スプリアス特性が改善されるという効果がある。

【図面の簡単な説明】

【0014】

【図1】本発明に係る周波数シンセサイザの実施形態の全体構成を示すブロック図である。

【図2】積分波形生成部の回路を示すブロック図である。

【図3】積分波形生成部の動作を示す説明図である。

【図4】積分波形生成部の出力波形を示す波形図である。

【図5】ゼロクロス情報出力部を示すブロック図である。

【図6】積分波形である鋸波がゼロ点をクロスする様子を示す説明図である。

【図7】積分波形である鋸波がゼロ点をクロスする様子を示す説明図である。

【図8】積分波形である鋸波のゼロクロス時の直前のディジタル値及び直後のディジタル値の比率に対応する係数値を説明するための説明図である。

【図9】図1に示す一部の回路要素を鋸波を構成するディジタルデータと関連付けて示す説明図である。

【図10】クロック選択部を示す回路図である。

【図11】積分波形である鋸波のゼロクロス時の直前のディジタル値及び直後のディジタル値の比率に対応する係数値に応じてクロック信号P1、P3が選択される様子を示すタイムチャートである。

【図12】クロック信号P1のみをゼロクロスのタイミングとして捕らえた場合の周波数特性と本発明における周波数特性とを比較して示す特性図である。

【発明を実施するための形態】

【0015】

本発明に係る信号生成装置を周波数シンセサイザに適用した実施形態について説明すると、図1はこの実施の全体構成を示すブロック図であり、1は積分波形生成回路部である。この積分波形生成回路部1は、入力されたディジタル値(周波数データ)に応じた周波数の鋸波をディジタルデータで出力する機能を有し、図2に示すように加算部11の後段にフリップフロップ回路12を設け、フリップフロップ回路12の出力を加算部11にて入力値と加算するように構成されている。フリップフロップ回路12には、クロック発生源10からクロック信号が入力され、クロック信号の入力のタイミングにより加算部11からの入力データが出力される。クロック信号の周波数は、出力されるディジタル値群により特定される鋸波の周波数として例えば5MHzを得たい場合には、例えば20MHz程度とされる。

【0016】

積分波形生成回路部1の動作について、説明の便宜上4ビットのディジタル値により動作する場合を例に挙げて図3を参照しながら説明する。ディジタル値は「2」の補数として取り扱われており、例えば当該回路部1に入力される周波数データである入力値が例えば「0001」であるとすると、入力値と加算部11とが加算されて加算値が増えていくが、加算値が「0111」となり、次に「0001」が入力されると、「1000」となって十進値は負の値に変わる。従ってフリップフロップ回路12に入力されるクロック信号のパルス番号(便宜上の番号である)と、周波数データ(入力値)と、出力値との関係は図3に示すようになり、図4に示すように出力波形は入力値の積分波形である鋸波となる。そしてこの鋸波の周波数は、設定される周波数データである入力値に応じて決まることから、この周波数データは後述のように信号発生器の設定周波数を決定するデータとなる。なお積分波形生成回路部1のディジタル信号は、4ビットで説明しているが、実際には例えば32ビットの信号が用いられる

積分波形生成回路部1の後段には、ゼロクロス情報出力部2が設けられ、このゼロクロス情報出力部2の後段には、使用比率決定部であるΔΣ回路3と信号選択部4とが設けられている。理解の容易さを優先するために、ゼロクロス情報出力部2、ΔΣ回路3及び信号選択部4の構成を説明する前に、これらの回路を使用する目的、役割について述べておく。

【0017】

積分波形生成回路部1から出力される鋸波を構成するディジタル値が徐々に変化する領域においてディジタル値の符号が負から正に反転するゼロクロス時の直前のディジタル値を読み出したクロック信号をP1とし、ゼロクロス時の直後のディジタル値を読み出したクロック信号をP2とし、前記クロック信号P1よりも2クロック遅れたクロック信号をP3とすると、クロック信号P1〜P3と鋸波のディジタル値との関係は図6に示すように表される。なお、前記鋸波の実際の波形図は各ディジタル値毎に階段状になっている。

【0018】

図3に示す例における鋸波は、積分波形生成回路部1に入力される周波数設定データである入力値(ディジタル値)が「1」(0001)であることから、十進値で「1」ずつインクリメントされ、このため鋸波が繰り返される度にディジタル値が第1のしきい値である「0」となるタイミングが存在する。しかし前記入力値が「3」(0011)である場合には、例えば「−7」、「−4」、「−1」、「2」という具合にディジタル値が増加していくことから、正確なゼロクロスポイント、つまり「0」を検出するクロック信号が存在しなくなる。

【0019】

一方、積分波形生成回路部1に入力される周波数設定データは、最終的に後述の電圧制御発振器から出力される周波数を設定するための設定信号である。例えばクロック発生源10から出力されるクロック信号の周波数が16MHzであるとすると、周波数設定データを「1」とすれば、鋸波の周波数は1MHzとなり(図3参照)、周波数設定データを「2」とすれば、2MHzとなる。図3の例は説明用の模式的な一例であり、実際にはディジタル信号は例えば32ビットで構成され、ディジタル値が「0」をとることは稀である。

【0020】

このためほとんどの場合、ディジタル値が負から正に移行するときには「0」を跨ぐことになるので、正確なゼロクロスポイントを検出することができない。この場合、ゼロクロスする直前のディジタル値を読み取るクロック信号であるP1をゼロクロスポイントとみなすことが考えられるが、そうすると周波数シンセサイザのスプリアス特性について良好な特性を得ることが困難である。そこでこの実施形態では、クロック信号P1とP3との一方をゼロクロスポイントとみなし、P1におけるディジタル値(P1で読み出されるディジタル値)とP2におけるディジタル値とに基づいて、ゼロクロスポイントとして取り扱うクロック信号P1とP3との使用比率、つまりクロック信号P1をゼロクロスポイントとして使用する態様と、クロック信号P2をゼロクロスポイントとして使用する態様と、の選択比率を決定するようにしている。なお以下の説明ではクロック信号P1(P2、P3)に対応するディジタル値という表現を「P1(P2、P3)の値」と略記する。

【0021】

即ち、周波数設定データが決まっているので、図7においてP2が第1のしきい値である「0」であるときのP1の値は予め分かっている。説明の便宜上このときのP1の値を第2のしきい値である「−50」とすると、P1の値が「−50」であれば、正確なゼロクロスポイントはクロック信号P1とP3との中間位置にあることになる。このときのクロック信号P1とP3との使用比率は50%であり、予め設定された時間内においてゼロクロスパルスとして使用されるクロック信号P1の数とクロック信号P3の数とは1:1となる。より一般的に言えば、図7に示すように前記使用比率をαとすると、P1の値がYであるとき、α=1−(Y/Ym)で表される。YmはP3がゼロクロスポイントであるときのP1の値であり、Yが0.5Ymのとき、αは0.5(50%)である。またYが0のときαは1(100%)となり、この場合は予め設定された時間内においてゼロクロスパルスとして使用されるクロック信号はP1だけとなる。またYがYm/3のときにはαは2/3(66.7%)となり、この場合は予め設定された時間内においてゼロクロスパルスとして使用されるクロック信号P1の数とクロック信号P3の数とは2:1となる。

【0022】

図8は、P1〜P3の値及び時間的位置と、クロック信号P1、P3の使用比率(%)の一例とを対応付けて示した図である。このようにクロック信号P2がゼロクロスポイントであるときには(P2の値が0であるときには)、所定時間内にてクロック信号P1、P3を半分ずつ使用し、この状態からP1の値が0に近づくほどクロック信号P1の使用回数を増やしている。即ち、正確なゼロクロスポイントは得られなくとも、所定時間内においてはP1の値とP2の値との比率はそれ程変動せず、このため所定時間内においてゼロクロスポイントとみなしたディジタル値の値を平均すれば、0に近い値となっているものと推測している。この推測は後述の実験例から適切であることが裏付けられている。

【0023】

このようないわばゼロクロスポイントの擬似処理を行う回路部分について説明すると、ゼロクロス情報検出部2は図5に示すように、P1検出部21を備えている。このP1検出部21は、鋸波を構成するディジタル値が第2のしきい値以上になるタイミングを検出するためのものであり、前記ディジタル値と第2のしきい値とを比較し、ディジタル値が第2のしきい値よりも小さい値から、第2のしきい値以上の値に変わったときにP1検出パルスを出力するように構成される。第2のしきい値は、既述のようにP2が第1のしきい値である「0」であるときのP1の値であり、後述の図7の例ではYm/2に相当する。第2のしきい値をこのように設定する理由は、P1は、第2のしきい値と第1のしきい値との間に存在するからである。

【0024】

図5中22は、ゼロクロスポイントの候補となる2つのクロック信号P1、P3を出力するための回路部であり、ゼロクロス検出パルスとクロック信号とのアンドをとる2つのアンド回路22a、22bと、一方のアンド回路22bに入力されるゼロクロス検出パルスを2クロック分だけ遅延させる遅延回路22cとを備えている。

【0025】

また221は前記ゼロクロス検出パルスをラッチイネーブル信号として鋸波データ(ディジタル値)をP1の値として出力するフリップフロップ回路であり、223は前記ゼロクロス検出パルスを遅延回路222で1クロック分遅延させたパルスをラッチイネーブル信号とし、鋸波データをP2の値として出力するフリップフロップ回路である。この実施形態ではP1の値だけを使用して比率αを求めているが、例えば鋸波の周期が分からない場合つまり互に連続するディジタル値の飛びの値が分からない場合には、P1の値の次のP2の値は分からないため、P2の値も必要になる。

【0026】

図1に戻って、ゼロクロス情報出力部2にて得られたP1の値は、クロック信号P1、P3の使用比率であるαを演算する回路部24に取り込まれ、この回路部24にて既述の演算(α=1−(Y/Ym))が行われる。ΔΣ回路3は、前記使用比率であるαを取り込み、予め設定された時間だけ、デューティ比の平均値がαとなるPWM(パルス幅変調)パルス列を出力する回路部分である。またΔΣ回路3は、使用比率αを取り込み、P1、P3の比率をΔΣ変調によって生成することで、近傍量子化ノイズを低減させる。30はパラメータ出力部であり、前記回路部24及びΔΣ回路3に必要なパラメータ、ΔΣ回路3のフィードバックゲイン(周波数により可変)を出力する部分である。なお、前記回路部24は、ゼロクロス情報出力部2の一部として取り扱うこともできる。

【0027】

信号選択部4は、ゼロクロス情報検出部2から出力されたクロック信号P1、P3のうち、ΔΣ回路3から出力されるP1、P3選択信号により一方が選択されてゼロクロスポイントとみなすクロック信号の列(擬似ゼロクロスポイントの列)を出力する機能を有する。図9は、鋸波を構成するディジタルデータとΔΣ回路3及び信号選択部4とを対応付けて示す説明図である。信号選択部4は、パルス信号P1とΔΣ回路3からの信号とのアンド条件をとるアンド回路41と、パルス信号P3とΔΣ回路3からの信号を否定回路43にて反転した信号とのアンド条件をとるアンド回路42と、これらアンド回路41、42のオア条件をとるオア回路44とを含む。

【0028】

信号選択部4の後段には、後述のPLLにて使用される参照周波数信号であるリファレンス信号を生成するリファレンス信号生成部5が設けられている。このリファレンス信号生成部5は、信号選択部4から出力される、ゼロクロスポイントとみなすパルス信号によりトグルされたパルスをリファレンス信号として出力する機能を有する。

リファレンス生成部5の後段にはPLLを構成する位相比較部61、ローパスフィルタ(LPF)62、電圧制御発振器(VCO)63、及び分周回路64が設けられている。

【0029】

ここで、既に図1の回路の一部の作用については詳述しているが、上述実施形態の全体作用について、簡単にまとめて述べておく。この周波数シンセサイザから得ようとする周波数の設定を図示しない設定部でおこない、この設定部から設定周波数に応じた周波数データが積分波形生成部1に入力され、例えば図4及び図6に模式的な例として示すようにディジタル信号からなる鋸波が生成される。この鋸波は後述のPLLにおける位相を決定するためのものである。そしてクロック発生源10からのクロック信号により、ゼロクロス情報出力部2にて、鋸波を形成するディジタル値が読み出され、前記ディジタル値が徐々に変化する領域において正、負の符号が反転するゼロクロス時、この例では負から正に反転するゼロクロス時の直前のディジタル値を読み出すクロック信号P1と、このクロック信号P1よりも2クロック遅れたクロック信号P3とが出力される。またクロック信号P1により読み出されたディジタル値(P1の値)がゼロクロス情報出力部2から出力される。

【0030】

更にP1の値に基づいて、既に図7及び図8等を用いて詳述したように、ゼロクロスポイントとみなしたクロック信号P1及びP3とを、どれだけの比率で使用するかを決定し、この比率(使用比率)に対応するP1、P3選択信号を出力する。この一連の決定は、回路部24及びΔΣ回路3により行われる。

【0031】

図11は、ゼロクロス情報検出部2から出力されるクロック信号P1及びP3と、ΔΣ回路3から出力されるPWMパルス列と、リファレンス生成部5にて生成されるリファレンス信号と、を対応付けて示すタイムチャートである。なお、紙面の制約から、時間軸の長さについては模式的な大きさである。図10に信号選択部4を示してあるように、クロック信号P1については、ΔΣ回路3の出力の「H」により選択され、クロック信号P3についてはΔΣ回路3の出力の「L」により選択される。従って前記使用比率が50%(αが0.5)のときにはΔΣ回路3の出力からデューティ比50%のパルス列が出力され、クロック信号P1、P2が交互に選択されることになる。

【0032】

また前記使用比率が66、7%のときにおけるクロック信号の選択の様子を実際に沿って示すことが困難なことから、ΔΣ回路3の出力からデューティ比が2/3のパルスが出力されているものとして描いている。この場合、クロック信号P1が2回選択され、クロック信号P2が1回選択される。実際には、PWMパルス列により選択された結果、設定時間内におけるクロック信号P1とP2との選択回数が2:1になる。既述のように、短い設定時間内であれば、正しいゼロクロスポイントがそれ程変化しないであろうという前提でこのような処理を行っている。

【0033】

そして選択されたクロック信号P1またはP2のパルス列によりトグルされてリファレンス信号が得られ、位相比較部61にて、電圧制御発振器63から分周回路64を介して送られた周波数信号と当該リファレンス信号との位相比較が行われ、その結果が電圧制御発振器63の制御電圧となってPLLループが構成され、PLLがロックしたときに、電圧制御発振器63から設定された周波数である周波数信号が得られる。

【0034】

上述実施の形態によれば、PLLを用いた周波数シンセサイザにおいてディジタル信号である周波数設定データに基づいて鋸波を生成し、概略的にはこの鋸波のゼロクロスポイントを検出してリファレンス信号を生成している。従って先の特許文献1の手法のようにA/D変換及びD/A変換を行わなくてよいので、回路構成が簡素化される。そしてPLLを用いた周波数シンセサイザに用いられる参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成するにあたって、ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない点に着目している。

【0035】

このため前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の前後のディジタル値を読み出したクロック信号P1、P3を擬似ゼロクロスポイントの候補とし、ゼロクロス時の直前、直後のディジタル値に基づいて(ただし一方の値が分かれば他方の値も分かる)、クロック信号P1、P3の使用比率を決定している。更にクロック信号P1、P3のタイミングを時間的に平均すれば正確なゼロクロスポイントに近いクロックが取り出せているであろうと推測して、選択されたクロック信号P1、P3によりトグルしてリファレンス信号を得ている。このため周波数シンセサイザの出力におけるスプリアス特性が良好である。

【0036】

本発明では、鋸波のディジタル値が正から負に向かって徐々に減少するように構成してもよく、この場合にはディジタル値が正から負に反転する時点がゼロクロス時となる。またクロック信号P1、P3の使用比率を決定するために、上述の例ではP1の値を用いているが、P2の値を用いてもよいし、P1、P2の両方の値を用いて例えばこれらの比を求めるといった手法であってもよい。

【0037】

更にまたゼロクロスポイントとみなすクロック信号としては、P1、P3に限られるものではなく、例えば鋸波を構成するポイント(符号が反転するポイントは除く)でP1、P3の条件を満たす箇所であればどこでもよい。即ち、鋸波のデータが負から正に変わった後において一定の数だけ後のデータ例えば5個後のデータをP1として取り扱っても、先の実施の形態と実質同じである。この場合例えばデータを構成するディジタル値がゼロであれば、P1、P3のパルスが50%ずつ使用される。またP1に対して奇数個後ろのパルスであれば、両パルスの真ん中にデータが位置するので例えばP1、P5の組を用いても良い。

【0038】

言い換えれば本発明は、鋸波がある値(第1のしきい値)を取るたびに信号出力部からパルス信号を出力する手法であることから、第1のしきい値としてはゼロに限らない。例えば図5に示すP1検出部21をゼロクロス検出部(ディジタル値が負から正に変化したとき、例えばMSBが1から0に変わるときを検出する検出部)として構成してもよい。この場合には、P3のクロックの次のクロックをP4とすると、例えばP2、P3、P4の3つのクロックを用いることになり、P2が先頭クロック信号、P4が最後部クロック信号となる。そして例えば鋸波を形成する前後のディジタル値の差が「50」であるとすると、第1のしきい値は「50」であり、第2のしきい値はゼロである。また例えばP2の値が分かれば、P2と第2のしきい値との差分、及びP4と第2のしきい値との差分が分かるので、比率αを決定することができる。

【0039】

ゼロクロス検出部21として、鋸波データ(鋸波のディジタル値)がゼロ以外のしきい値を越えたときにパルスを出力する回路を用いることができる。この場合においても、時間軸をずらせば、ゼロクロスを検出していることと実質同じである。

【0040】

また例えば40MHzのクロックを用いて上述の実施の形態のように先頭クロック信号であるP1と後方クロック信号であるP3とを用いることと、80MHzのクロックを用いて連続して5個並ぶP1からP5までのクロック信号のうち、P1、P5を夫々先頭クロック信号及び後方クロック信号として用いることとは、実質同じである。従って等間隔の奇数個のディジタル値列の先頭のディジタル値及び最後部のディジタル値を夫々読み出した先頭クロック信号及び後方クロック信号を出力するために、前記ディジタル値列の数は3個に限らず、5個以上であってもよい。

【実施例】

【0041】

本発明の効果の確認を行うために、図1に示した回路を用いた場合(実施例)と、ゼロクロスポイントとしてクロック信号P3だけを用いた場合(比較例)と、の夫々においてリファレンス信号生成部5から得られる周波数信号のスプリアス特性を調べた。リファレンス信号生成部5はDDS(Direct Digital Synthesizer)により構成され、設定出力周波数は、312.5kHzである。なお後者の比較例は図1に示した回路においてΔΣ回路3を停止させて行った。図12は、スプリアス特性を示す図であり、Aは実施例、Bは比較例である。この結果から分かるように、本発明によればスプリアス特性が良好であることが分かる。

【符号の説明】

【0042】

1 積分波形生成回路部

10 クロック発生源

2 ゼロクロス情報出力部

21 ゼロクロス検出部

22 クロック信号P1、P3を出力する回路部

23 P1値出力部

3 ΔΣ回路部

4 信号選択部

5 リファレンス生成部

61 位相比較部

63 電圧制御発振器

【特許請求の範囲】

【請求項1】

鋸歯状の積分波形が予め設定したしきい値を跨ぐタイミングに基づいてパルス信号を出力する装置において、

クロック信号を出力するクロック源と、

設定周波数に応じたディジタル値を有するディジタル信号が入力され、このディジタル値を前記クロック信号に基づいて積分することにより、鋸歯状の積分波形を生成する積分波形生成部と、

前記積分波形生成部から出力される前記ディジタル値が一方向に変化する領域において、予め設定したしきい値の前後のディジタル値を含む、等間隔の奇数個のディジタル値列の先頭のディジタル値及び最後部のディジタル値を夫々読み出した先頭クロック信号及び後方クロック信号を出力するクロック情報出力部と、

前記先頭のディジタル値としきい値との差分と、最後部のディジタル値と前記しきい値との差分と、の比率に応じた係数値を出力する回路部と、

前記係数値に基づいて、予め設定した時間だけ前記積分波形のディジタル値が前記しきい値になっている時点とみなす先頭クロック信号及び後方クロック信号の使用比率に対応する信号を出力する使用比率決定部と、

前記クロック情報出力部から出力された先頭クロック信号及び後方クロック信号の一方を、予め設定された時間だけ、前記使用比率決定部から出力される使用比率に対応する信号により選択して出力するクロック選択部と、

このクロック選択部から出力されたクロック信号毎にトグルされ、トグルされて得られたパルス信号を出力する信号出力部と、を備えたことを特徴とする信号生成装置。

【請求項2】

前記予め設定したしきい値はゼロであることを特徴とする請求項1記載の信号生成装置。

【請求項3】

先頭のディジタル値及び最後部のディジタル値を読み出したクロック信号を夫々P1及びP3とし、奇数個のディジタル値列の中央のディジタル値を読み出したクロック信号をP2とすると、

前記クロック情報出力部は、クロック信号P1及びP3を出力するように構成され、

前記使用比率決定部において、予め設定した時間だけ前記積分波形のディジタル値が前記しきい値になっている時点とみなす先頭クロック信号及び後方クロック信号は、夫々クロック信号P1及びP3であることを特徴とする請求項1または2記載の信号生成装置。

【請求項4】

前記クロック選択部は、選択信号であるパルス信号の信号レベルが「H」及び「L」の一方により先頭クロック信号が選択され、他方により後方クロック信号が選択されるように構成され、

前記使用比率決定部は、デューティ比の平均が前記しきい値の直前のディジタル値及び直後のディジタル値の比率に対応する値となる、前記選択信号をなすPWMパルス列を出力するΔΣ回路であることを特徴とする請求項1ないし3のいずれか一項に記載の信号生成装置。

【請求項5】

電圧制御発振器から出力される周波数信号を分周器を介して位相比較部に帰還し、帰還された周波数信号と設定周波数に対応する参照周波数信号とを位相比較部にて比較し、その比較結果を前記電圧制御発振器に入力する周波数シンセサイザにおいて、

前記参照周波数信号として、請求項1ないし4のいずれか一項に記載の信号生成装置から出力される信号を用いることを特徴とする周波数シンセサイザ。

【請求項1】

鋸歯状の積分波形が予め設定したしきい値を跨ぐタイミングに基づいてパルス信号を出力する装置において、

クロック信号を出力するクロック源と、

設定周波数に応じたディジタル値を有するディジタル信号が入力され、このディジタル値を前記クロック信号に基づいて積分することにより、鋸歯状の積分波形を生成する積分波形生成部と、

前記積分波形生成部から出力される前記ディジタル値が一方向に変化する領域において、予め設定したしきい値の前後のディジタル値を含む、等間隔の奇数個のディジタル値列の先頭のディジタル値及び最後部のディジタル値を夫々読み出した先頭クロック信号及び後方クロック信号を出力するクロック情報出力部と、

前記先頭のディジタル値としきい値との差分と、最後部のディジタル値と前記しきい値との差分と、の比率に応じた係数値を出力する回路部と、

前記係数値に基づいて、予め設定した時間だけ前記積分波形のディジタル値が前記しきい値になっている時点とみなす先頭クロック信号及び後方クロック信号の使用比率に対応する信号を出力する使用比率決定部と、

前記クロック情報出力部から出力された先頭クロック信号及び後方クロック信号の一方を、予め設定された時間だけ、前記使用比率決定部から出力される使用比率に対応する信号により選択して出力するクロック選択部と、

このクロック選択部から出力されたクロック信号毎にトグルされ、トグルされて得られたパルス信号を出力する信号出力部と、を備えたことを特徴とする信号生成装置。

【請求項2】

前記予め設定したしきい値はゼロであることを特徴とする請求項1記載の信号生成装置。

【請求項3】

先頭のディジタル値及び最後部のディジタル値を読み出したクロック信号を夫々P1及びP3とし、奇数個のディジタル値列の中央のディジタル値を読み出したクロック信号をP2とすると、

前記クロック情報出力部は、クロック信号P1及びP3を出力するように構成され、

前記使用比率決定部において、予め設定した時間だけ前記積分波形のディジタル値が前記しきい値になっている時点とみなす先頭クロック信号及び後方クロック信号は、夫々クロック信号P1及びP3であることを特徴とする請求項1または2記載の信号生成装置。

【請求項4】

前記クロック選択部は、選択信号であるパルス信号の信号レベルが「H」及び「L」の一方により先頭クロック信号が選択され、他方により後方クロック信号が選択されるように構成され、

前記使用比率決定部は、デューティ比の平均が前記しきい値の直前のディジタル値及び直後のディジタル値の比率に対応する値となる、前記選択信号をなすPWMパルス列を出力するΔΣ回路であることを特徴とする請求項1ないし3のいずれか一項に記載の信号生成装置。

【請求項5】

電圧制御発振器から出力される周波数信号を分周器を介して位相比較部に帰還し、帰還された周波数信号と設定周波数に対応する参照周波数信号とを位相比較部にて比較し、その比較結果を前記電圧制御発振器に入力する周波数シンセサイザにおいて、

前記参照周波数信号として、請求項1ないし4のいずれか一項に記載の信号生成装置から出力される信号を用いることを特徴とする周波数シンセサイザ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−217171(P2012−217171A)

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願番号】特願2012−81999(P2012−81999)

【出願日】平成24年3月30日(2012.3.30)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願日】平成24年3月30日(2012.3.30)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

[ Back to top ]