信号送信装置、信号送信方法、信号受信装置、信号受信方法及び信号伝送システム

【課題】4:2:0/10ビット、12ビット信号であるデータ構造を4:4:4/10ビット、12ビット信号に変換して、現行の10Gシリアルインターフェースで伝送する。

【解決手段】マッピング部11は、第1〜第Nのサブイメージのそれぞれの一ラインおきに画素サンプルを間引きインターレース信号に変換する。このとき、第1〜第N/2のサブイメージを、4:2:2/rビット信号に変換する。また、第(N/2)+1〜第Nのサブイメージを、4:0:0/rビット信号に変換する。そして、4:2:2/rビット信号のデータ構造、及び4:0:0/rビット信号のデータ構造を、4:4:4/rビット信号のデータ構造に合わせて変換したデュアルリンクHD−SDIを出力する。

【解決手段】マッピング部11は、第1〜第Nのサブイメージのそれぞれの一ラインおきに画素サンプルを間引きインターレース信号に変換する。このとき、第1〜第N/2のサブイメージを、4:2:2/rビット信号に変換する。また、第(N/2)+1〜第Nのサブイメージを、4:0:0/rビット信号に変換する。そして、4:2:2/rビット信号のデータ構造、及び4:0:0/rビット信号のデータ構造を、4:4:4/rビット信号のデータ構造に合わせて変換したデュアルリンクHD−SDIを出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、1フレームの画素数がHD−SDIフォーマットで規定された画素数を越える映像信号をシリアル伝送する場合に適用して好適な信号送信装置、信号送信方法、信号受信装置、信号受信方法及び信号伝送システムに関する。

【背景技術】

【0002】

従来、1フレームが1920サンプル×1080ラインの映像信号である現行のHD(High Definition)の映像信号を超える、超高精細映像信号の受像システムや撮像システムの開発が進んでいる。例えば、現行のHDで規定される画素数の4倍又は16倍もの画素数を持つ次世代の放送方式であるUHDTV(Ultra High Definition TV)規格が、国際協会によって標準化が行われている。この国際協会には、ITU(International Telecommunication Union)やSMPTE(Society of Motion Picture and Television Engineers)がある。

【0003】

ここで、特許文献1には、4k×2k信号(4k×2kの超高解像度信号)の一種である3840×2160/30P,30/1.001P/4:4:4/12ビット信号を、ビットレート10Gbps以上で伝送する技術が開示されている。なお、mサンプル×nラインで表される映像信号を、「m×n」と略記する。そして、[3840×2160/30P]と示した場合には、[水平方向の画素数]×[垂直方向のライン数]/[1秒当りのフレーム数]を示す。また、[4:4:4]は、原色信号伝送方式である場合、[赤信号R:緑信号G:青信号B]の比率を示し、色差信号伝送方式である場合、[輝度信号Y:第1色差信号Cb:第2色差信号Cr]の比率を示す。

【0004】

以下の説明において、プログレッシブ信号のフレームレートを表す50P,59.94P,60Pを、「50P−60P」、47.95P,48P,50P,59.94P,60Pを「48P−60P」と略記する。また、100P,119.88P,120Pを、「100P−120P」と略記し、95.9P,96P,100P,119.88P,120Pを、「96P−120P」と略記する。また、インターレース信号のフレームレートを表す50I,59.94I,60Iを、「50I−60I」、47.95I,48I,50I,59.94I,60Iを、「48I−60I」と略記する。また、3840×2160/100P−120P/4:2:0/10ビット,12ビット信号を、「3840×2160/100P−120P信号」と略記する場合がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2005−328494号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

近年のSMPTEやITUでは、フレームレートが23.98P−60Pである3840×2160や7680×4320の映像信号規格やインターフェース規格が標準化されつつある。また、映像データを伝送するためにモードD(後述する図8参照)を用いた場合、3840×2160/23.98P−30Pの映像信号を1chの10G−SDIで伝送出来る。しかし、フレームレートが120Pや120Pを超える映像信号を伝送するために対応可能なインターフェースについて議論されたり、標準化がなされたりしていなかった。また、1920×1080や2048×1080に対応する映像信号規格には、フレームレートが60Pまでしか規定されていないため、特許文献1に記載されている技術を用いても、高画素の画素サンプルを既存のインターフェースで伝送できなかった。

【0007】

また、SMPTEでは、4096×2160/23.98P−60Pまでの映像信号規格や標準化されつつあるものの、信号送信装置と信号受信装置が備えるインターフェースの議論や標準化がなされていなかった。このため、4096×2160/23.98P−30Pの映像信号を想定すると、映像データ領域に格納される画素サンプル数が増えるため、モードDのライン構造のままでは画素サンプルを多重し、伝送できなかった。

【0008】

さらに、映像信号が4096×2160である場合に、フレームレートが23.98P,24P,25P,29.97P,30P,47.95P,48P,50P,59.94P,60Pの範囲で規定されている。しかし、将来は現在用いられているフレームレート(例えば30P)の3倍速信号である90P、あるいは90P以上のフレームレートの映像信号を伝送することも考慮しなければならない。このため、様々なフレームレートの映像信号を、現行の伝送インターフェースを利用して伝送する仕様を策定する必要があった。

【0009】

本開示はこのような状況に鑑みて成されたものである。すなわち、1フレームの画素数がHD−SDIフォーマットで規定される画素数を越え、かつ、高いフレームレートである映像信号を、HD−SDIインターフェースや10Gbpsのシリアルインターフェースを利用してシリアル伝送することを目的とする。120P伝送時、特に4:2:0信号伝送時にデータ多重方式を工夫して伝送帯域を削減するものである。

【課題を解決するための手段】

【0010】

本開示は、1フレームの画素数がHD−SDIフォーマットで規定される画素数を越えるm×n(mサンプル、nラインを示すm,nは、正の整数)/a−b(a,bは、プログレッシブ信号のフレームレート)/4:2:0/rビット信号で規定されるクラスイメージから、同一ラインで隣り合う2つの画素サンプルを間引く。そして、m′×n′(m′サンプル、n′ラインを示すm′,n′は、正の整数)/a′−b′(a′,b′は、プログレッシブ信号のフレームレート)/4:2:2および4:0:0/rビット信号で規定される第1〜第N(Nは、2以上の整数)のサブイメージの映像データ領域にマッピングする。

次に、画素サンプルがマッピングされた第1〜第Nのサブイメージのそれぞれの一ラインおきに画素サンプルを間引いてインターレース信号とする。このとき、第1〜第N/2のサブイメージを、4:2:2/rビット信号に変換し、第(N/2)+1〜第Nのサブイメージを、4:0:0/rビット信号に変換する。

そして、4:2:2/rビット信号のデータ構造、及び4:0:0/rビット信号のデータ構造を、4:4:4/rビット信号のデータ構造に合わせて変換したデュアルリンクHD−SDIを出力するものである。

【0011】

また、本開示は、4:4:4/rビット信号のデータ構造としてあるデュアルリンクHD−SDIを、4:2:2/rビット信号及び4:0:0/rビット信号に変換する。

次に、4:2:2/rビット信号を、m′×n′(m′サンプル、n′ラインを示すm′,n′は、正の整数)/a′−b′(a′,b′は、プログレッシブ信号のフレームレート)/4:2:2/rビット信号で規定される第1〜第N/2(Nは、2以上の整数)のサブイメージの一ラインおきに画素サンプルを多重する。また、4:0:0/rビット信号を、第(N/2)+1〜第Nのサブイメージの一ラインおきに画素サンプルを多重する。

そして、第1〜第Nのサブイメージから2画素ずつ抽出した画素サンプルを、1フレームの画素数がHD−SDIフォーマットで規定される画素数を越えるm×n(mサンプル、nラインを示すm,nは、正の整数)/a−b(a,bは、プログレッシブ信号のフレームレート)/4:2:0/rビット信号で規定されるクラスイメージのフレームにおける同一ラインに隣り合わせて多重するものである。

【0012】

また、本開示は、上記の映像信号を送信し、この映像信号を受信する信号伝送システムである。

【0013】

本開示は、入力した映像信号に対して、連続する2フレーム(あるいは2フレーム以上)単位のクラスイメージに含まれる画素サンプルの2画素間引き、ライン間引き及びワード間引きを行い、HD−SDIの映像データ領域に画素サンプルを多重した信号を送信する。一方、受信した信号に対して、HD−SDIの映像データ領域から画素サンプルを抽出し、ワード多重、ライン多重、及び2画素多重を行って、映像信号を再生する。

【発明の効果】

【0014】

本開示によれば、4:2:0/10ビット、12ビット信号のデータ構造を4:4:4/10ビット、12ビット信号に変換して、現行の10Gシリアルインターフェースで伝送することを可能とした。このため、新たな伝送規格を設けることなく、従来用いられていた伝送規格を利用できるので利便性が向上するという効果がある。

【図面の簡単な説明】

【0015】

【図1】本開示の第1の実施の形態に係るテレビジョン放送局用のカメラ伝送システムの全体構成を示す図である。

【図2】本開示の第1の実施の形態に係る放送用カメラの回路構成のうち、信号送信装置の内部構成例を示すブロック図である。

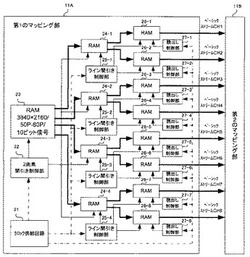

【図3】本開示の第1の実施の形態に係る10ビット信号をマッピングする第1のマッピング部の内部構成例を示すブロック図である。

【図4】本開示の第1の実施の形態に係る第2のマッピング部の内部構成例を示すブロック図である。

【図5】3840×2160におけるUHDTV規格のサンプル構造の例を示す説明図である。

【図6】本開示の第1の実施の形態に係る2画素間引き制御部が第1及び第2のクラスイメージから画素サンプルを2画素ずつ間引いて第1〜第4のサブイメージにマッピングする処理例を示す説明図である。

【図7】24Pの場合における10.692Gbpsのシリアル・デジタルデータの1ライン分のデータ構造例を示す説明図である。

【図8】モードDの例を示す説明図である。

【図9】本開示の第1の実施の形態に係る第1〜第4のサブイメージをライン間引きすることによって、SMPTE372Mの規定に従ってLinkA,Bに分割する例を示す説明図である。

【図10】本開示の第1の実施の形態に係るライン間引きの例を示す説明図である。

【図11】本開示の第1の実施の形態に係る8chの4:2:2/10ビット信号と4:0:0/10ビット信号を4組のHD−SDI LinkA,Bに変換する例を示す説明図である。

【図12】本開示の第1の実施の形態に係る8chの4:2:2/10ビット信号と4:0:0/10ビット信号を4組のHD−SDI LinkA,Bに変換する際のデータ構造の例を示す説明図である。

【図13】本開示の第1の実施の形態に係る4:2:0/12ビット信号をマッピングする第1のマッピング部の内部構成例を示すブロック図である。

【図14】本開示の第1の実施の形態に係る第1〜第4のサブイメージをライン間引きした後、ワード間引きをすることによって、SMPTE372Mの規定に従ってLinkA,Bに分割する例を示す説明図である。

【図15】本開示の第1の実施の形態に係る16chの4:2:2/12ビット信号と4:0:0/12ビット信号を4組のHD−SDI LinkA,Bに変換する例を示す説明図である。

【図16】本開示の第1の実施の形態に係る16chの4:2:2/12ビット信号と4:0:0/12ビット信号を4組のHD−SDI LinkA,Bに変換する際のデータ構造の例を示す説明図である。

【図17】本開示の第1の実施の形態に係る多重部が行うデータの多重処理の例を示す説明図である。

【図18】本開示の第1の実施の形態に係るCCUの回路構成のうち、信号受信装置の内部構成例を示すブロック図である。

【図19】本開示の第1の実施の形態に係る第2の再生部の内部構成例を示すブロック図である。

【図20】本開示の第1の実施の形態に係る10ビット信号を再生する第1の再生部の内部構成例を示すブロック図である。

【図21】本開示の第1の実施の形態に係る12ビット信号を再生する第1の再生部の内部構成例を示すブロック図である。

【図22】本開示の第2の実施の形態に係る第1のマッピング部の内部構成例を示すブロック図である。

【図23】本開示の第2の実施の形態に係るマッピング部が画素サンプルをマッピングする処理イメージを示す説明図である。

【図24】本開示の第2の実施の形態に係る2画素間引き制御部が第1及び第2のクラスイメージから画素サンプルを2画素ずつ間引いて第1〜第8のサブイメージにマッピングする処理例を示す説明図である。

【図25】本開示の第2の実施の形態に係る第1〜第8のサブイメージをライン間引きした後、ワード間引きをすることによって、SMPTE372Mの規定に従ってLinkA,Bに分割する例を示す説明図である。

【図26】本開示の第2の実施の形態に係る第1の再生部の内部構成例を示すブロック図である。

【図27】本開示の第3の実施の形態に係る2画素間引き制御部が第1及び第2のUHDTV2クラスイメージから画素サンプルを2画素ずつ間引いて第1〜第4のUHDTV1クラスイメージにマッピングする処理例を示す説明図である。

【図28】本開示の第3の実施の形態に係る第1のマッピング部の内部構成例を示すブロック図である。

【図29】本開示の第3の実施の形態に係る第1の再生部の内部構成例を示すブロック図である。

【図30】本開示の第4の実施の形態に係る2画素間引き制御部が第1及び第2のUHDTV2クラスイメージから画素サンプルを2画素ずつ間引いて第1〜第4のUHDTV1クラスイメージにマッピングする処理例を示す説明図である。

【発明を実施するための形態】

【0016】

以下、本開示を実施するための最良の形態(以下実施の形態とする。)について説明する。なお、説明は以下の順序で行う。

1.第1の実施の形態(画素サンプルのマッピング制御:3840×2160/50P,59.94P,60P/4:2:0/10ビット,12ビット多重方式を工夫して、伝送するHD−SDIや10G−SDIのch数を半分にする処理の例)

2.第2の実施の形態(3840×2160/100P,119.88P,120P/4:2:0/10ビット,12ビット多重方式を工夫して伝送HD−SDIや10G−SDIのch数を半分にする処理の例)

3.第3の実施の形態(UHDTV2 7680×4320/50P,59.94P,60P/4:2:0/10ビット,12ビット多重方式を工夫して伝送HD−SDIや10G−SDIのch数を半分にする処理の例)

4.第4の実施の形態(UHDTV2 7680×4320/100P,119.88P,120P/4:2:0/10ビット,12ビット多重方式を工夫して伝送HD−SDIや10G−SDIのch数を半分にする処理の例)

5.変形例

【0017】

<1.第1の実施の形態>

[画素サンプルのマッピング制御:3840×2160/50P,59.94P,60P/4:2:0/10ビット,12ビット多重方式を工夫して、伝送するHD−SDIや10G−SDIのch数を半分にする処理の例]

【0018】

以下、本開示の第1の実施形態について、図1〜図21を参照して説明する。

第1の実施の形態に係る伝送システムでは、3840×2160/50P−60P/4:2:0/10ビット,12ビット信号の画素サンプルを間引く方式について説明する。

【0019】

図1は、本実施の形態を適用したテレビジョン放送局用の信号伝送システム10の全体構成を示す図である。この信号伝送システム10は、同一構成としてある複数台の放送用カメラ1及びCCU(カメラコントロールユニット)2で構成されており、各放送用カメラ1が光ファイバーケーブル3でCCU2に接続されている。放送用カメラ1は、シリアル・デジタル信号(映像信号)を送信する信号送信方法を適用した信号送信装置として用いられ、CCU2は、シリアル・デジタル信号を受信する信号受信方法を適用した信号受信装置として用いられる。そして、放送用カメラ1とCCU2を組み合わせた伝送システム10は、シリアル・デジタル信号を送受信する信号伝送システムとして用いられる。また、これらの装置で行われる処理はハードウェアが連携して行うだけでなく、プログラムを実行させることによっても実現することができる。

【0020】

放送用カメラ1は、UHDTV1の4k×2kの超高解像度信号(3840×2160/50P−60P/4:2:0/10ビット,12ビット信号)を生成し、CCU2に送信する。

【0021】

CCU2は、各放送用カメラ1を制御したり、各放送用カメラ1から映像信号を受信したり、各放送用カメラ1のモニタに他の放送用カメラ1で撮影中の映像を表示させるための映像信号(リターンビデオ)を送信したりする。CCU2は、各放送用カメラ1から映像信号を受信する信号受信装置として機能する。

【0022】

[次世代2k、4k、8k映像信号]

ここで、次世代の2k、4k、8k映像信号について説明する。

様々なフレームレートの映像信号を送受信するインターフェースとして、モードD(後述する図7参照)として知られる伝送規格がSMPTE435−2に追加され、SMPTE435−2−2009として標準化が完了した。SMPTE435−2には、10.692Gbpsのシリアルインターフェースに、SMPTE292で規定された10ビットのパラレルストリームである複数chのHD−SDIによってデータを多重処理することについて記載されている。通常、HD−SDIのフィールドは、EAV、水平補助データスペース(HANCデータ、水平ブランキング期間ともいう。)、SAV、映像データの順に構成される。UHDTV規格では、3840×2160/50P−60Pは2chの10Gbpsインターフェースで伝送し、7680×4320/50P−60Pは8chの10Gbpsインターフェースで伝送する方式がSMPTEに提案された。この提案は、SMPTE2036−3として規格の策定が完了した。

【0023】

ITUやSMPTEに提案されている映像規格は、1920×1080の2倍又は4倍のサンプル数及びライン数を持つ3840×2160や7680×4320の映像信号に関する。このうち、ITUで標準化されている映像規格はLSDI(Large screen digital imagery)と呼ばれ、SMPTEに提案しているUHDTVと呼ばれる。UHDTVに関しては次表1の映像信号が規定されている。

【0024】

【表1】

【0025】

また、映画業界におけるディジタルカメラに採用される規格として、次表2,3には、2048×1080や4096×2160の信号規格がSMPTE2048−1,2として標準化されている。

【0026】

【表2】

【0027】

【表3】

【0028】

[DWDM/CWDM波長多重伝送技術]

次に、DWDM/CWDM波長多重伝送技術について説明する。

複数の波長の光を1本の光ファイバーに多重して伝送する方法をWDM(Wavelength Division Multiplexing)と言う。WDMは波長間隔に応じて大まかに以下の3つの方式に分けられる。

【0029】

(1)2波長多重方式

2波長多重方式は、1.3μm、1.55μmといった異なる波長の信号を、2波〜3波程度多重して1本の光ファイバーで伝送する方式である。

【0030】

(2)DWDM(Dense Wavelength Division Multiplexing)方式

DWDMは、特に1.55μm帯にて光の周波数で25GHz、50GHz、100GHz、200GHz..、高密度に光を多重して伝送する方法である。この間隔は、約0.2nm、0.4nm、0.8nm.. 波長の間隔となる。ITU−T(International Telecommunication Union Telecommunication standardization sector)にて中心波長その他の標準化が行われた。DWDMは波長間隔が100GHzと狭いために数十〜百と多くの多重数を取ることが出来、超大容量の通信が可能である。しかし、発振波長幅が波長間隔100GHzより十分狭いことが必要であるとともに中心波長がITU−T規格に一致するよう半導体レーザを温度制御する必要があるため、デバイスが高価であり、システムの消費電力が大きくなる。

【0031】

(3)CWDM(Coarse Wavelength Division Multiplexing)方式

CWDMは、波長間隔を10nm〜20nmとDWDMより一桁以上広く取った波長多重技術である。波長間隔が比較的広いために半導体レーザの発振波長幅がDWDMほど狭帯域である必要が無く、また半導体レーザを温度制御する必要も無いので、システムを低価格、低消費電力化することが可能である。DWDMほどの大容量が必要でないシステムに有効である。中心波長例については、現在のところ4ch構成で以下のものが一般的である。例えば、1.511μm、1.531μm、1.551μm、1.571μm、8ch構成で1.471μm、1.491μm、1.511μm、1.531μm、1.551μm、1.571μm、1.591μm、1.611μmがある。

【0032】

本実施の形態で説明する、3840×2160/50P−60P/4:2:0/10ビット,12ビット信号のフレームレートは、SMPTE S2036−1で規定される信号の倍である。上述したようにSMPTE S2036−1で規定される信号は、3840×2160/50P−60P/4:2:0/10ビット,12ビット信号である。そして、禁止コードなどディジタル信号形式はS2036−1で規定される従来の信号と同じであるとする。

【0033】

図2は、放送用カメラ1の回路構成のうち、本実施の形態に関連する信号送信装置を示すブロック図である。放送用カメラ1内の撮像部及び映像信号処理部(図示略)によって生成された3840×2160/50P−60P/4:2:0/10ビット,12ビット信号が、マッピング部11に送られる。

【0034】

3840×2160/50P−60P/4:2:0/10ビット,12ビット信号は、UHDTV1クラスイメージの1フレームに相当する。そして、この信号は、ワード長が12ビットずつのY′データ系列,C′Bデータ系列,C′Rデータ系列の同期を取って並列配置した、図5に示すようなC′B、C′R信号がY′信号の1/4に間引かれた信号である。この信号の1フレーム期間は1/50、1/59.94、1/60秒であり、1フレーム期間内に2160本の有効ライン期間が含まれている。このため、1フレームの画素数は、HD−SDIフォーマットで規定された画素数を越える映像信号である。

【0035】

S2036−1で規定されるUHDTV1クラスイメージにおけるアクティブラインのサンプル数は3840、ライン数は2160であり、Gデータ系列,Bデータ系列,Rデータ系列のアクティブラインには、それぞれG,B,Rの映像データが配置される。

【0036】

そして、マッピング部11は3840×2160/50P−60P/4:2:0/10ビット,12ビット信号を、HD−SDIフォーマットで規定された8chの伝送ストリームの映像データ領域にマッピングする。

【0037】

ここで、3840×2160/50P−60P/4:2:0/10ビット信号と、3840×2160/50P−60P/4:2:0/12ビット信号の画素サンプルのマッピング処理を分けて説明する。ただし、両者に共通する内容については、単に「4:2:0/10ビット信号」、「4:2:0/12ビット信号」のように略記して説明する場合がある。

【0038】

[1−1.マッピング部の内部構成及び動作例(3840×2160/50P−60P/4:2:0/10ビットの例)]

ここで、マッピング11の内部構成及び動作例を説明する。

始めに、3840×2160/50P−60P/4:2:0/10ビットの例について説明する。

【0039】

図3は、10ビット信号をマッピングするマッピング部11の前段の処理を行う第1のマッピング部11Aの構成例を示す。

本例のマッピング部11(図2を参照)は、第1のマッピング部11Aと第2のマッピング部11Bを備える。

第1のマッピング部11Aは、各部にクロックを供給するクロック供給回路21と、3840×2160/50P−60P/4:2:0/10ビットの映像信号を記憶するRAM23を備える。また、第1のマッピング部11Aは、RAM23から2画素ずつ画素サンプルを読み出す2画素間引き(インタリーブ)を制御する2画素間引き制御部22と、2画素間引きされた画素サンプルを保存するRAM24−1〜24−4と、を備える。

【0040】

また、第1のマッピング部11Aは、RAM24−1〜24−4から読出したデータをライン間引きするライン間引き制御部25−1〜25−4と、ライン間引き制御部25−1〜25−4が間引いたデータを一時的に書き込むRAM26−1〜26−8を備える。

【0041】

また、第1のマッピング部11Aは、RAM26−1〜26−8から読出したデータの画素サンプルを8chのベーシックストリーム(4:2:2/10ビット信号と4:0:0/10ビット信号)として出力する読み出し制御部27−1〜27−8を備える。クロック供給回路21は、2画素間引き制御部22、ライン間引き制御部25−1〜25−4、及び読出し制御部27−1〜27−8にクロックを供給する。このクロックは、画素サンプルの読み出し又は書き込みに用いられ、このクロックにより各部が同期する。

【0042】

次に、第1のマッピング部11Aの各処理ブロックの動作例を説明する。

始めに、不図示のイメージセンサから入力する1フレームの画素数がHD−SDIフォーマットで規定される画素数を越えるm×n(mサンプル、nラインを示すm,nは、正の整数)/a−b(a,bは、プログレッシブ信号のフレームレート)/4:2:0/rビット信号で規定されるUHDTV1クラスイメージの画像信号は、RAM23に書き込まれる。このUHDTV1の画像信号は、3840×2160/50P−60P/4:2:0/10ビット、12ビット信号の画像信号である。そして、この画像信号は、UHDTV1で規定されるクラスイメージである。

【0043】

2画素間引き制御部22は、画像信号で規定される各フレームから抽出した画素サンプルのうち、SMPTE435−1で規定される方式である、同一ライン上で隣り合う2つの画素サンプルを間引く。そして、m′×n′(m′サンプル、n′ラインを示すm′,n′は、正の整数)/a′−b′(a′,b′は、プログレッシブ信号のフレームレート)/4:2:2あるいは4:0:0/rビット信号で規定される第1〜第N(Nは、2以上の整数)のサブイメージの映像データ領域にマッピングする。このサブイメージは、1920×1080/50P−60P/4:2:2あるいは4:0:0/10ビット、12ビット信号であり、N=4である。このため、2画素間引き制御部22は、フレームの同一ライン上で隣り合う2つの画素サンプルを間引いて、SMPTE435−1で規定される第1〜第4のサブイメージの内、フレームの偶数ライン上の画素サンプルを第1のサブイメージと第2のサブイメージに2つの画素サンプルずつマッピングする。そして、フレームの奇数ライン上の画素サンプルを第3のサブイメージと第4のサブイメージにマッピングする。

【0044】

具体的には、2画素間引き制御部22は、3840×2160/50P−60P/4:2:0/10ビット信号の画素サンプルを、隣り合う上下の2ライン毎に、ライン方向に2画素ずつ抽出し、RAM24−1〜24−4に書き込む制御を行う。このとき、2画素間引き制御部22は、RAM24−1〜24−4に、SMPTE435−1で規定される1920×1080/50P−60P相当の第1〜第4のサブイメージを形成する。

【0045】

ライン間引き制御部25−1〜25−4は、RAM24−1〜24−4に書き込まれ、画素サンプルがマッピングされたプログレッシブ信号である第1〜第4のサブイメージをインターレース信号に変換する。このとき、第1〜第N/2のサブイメージ(本例では、第1及び第2のサブイメージ)を、4:2:2/rビット信号に変換する。そして、第(N/2)+1〜第Nのサブイメージ(本例では、第3及び第4のサブイメージ)を、4:0:0/rビット信号に変換する。具体的には、ライン間引き制御部25−1〜25−4は、2画素間引き制御部22によってマッピングされ、RAM24−1〜24−4に書き込まれる第1〜第4のサブイメージをそれぞれ読出す。このとき、ライン間引き制御部25−1〜25−4は、1つのサブイメージを、2chの1920×1080/50I,59.94I,60I/4:2:2/10ビット信号に変換する。以下、50I,59.94I,60Iを、「50I−60I」と略記する。そして、読出した第1〜第4のサブイメージから一ラインおきに間引いてインターレース信号とした1920×1080/50I−60I信号である8chの4:2:2/10ビット信号と4:0:0/10ビット信号をRAM26−1〜26−8に書き込む。

【0046】

その後、読出し制御部27−1〜27−8は、RAM26−1〜26−8から読出した8chの4:2:2/10ビット信号と4:0:0/10ビット信号を出力する。

具体的には、読出し制御部27−1〜27−8は、クロック供給回路21から供給された基準クロックでRAM26−1〜26−8から1920×1080/50I−60I信号を読出す。そして、2本のリンクA、Bを4対で構成した8chの4:2:2/10ビット信号と4:0:0/10ビット信号を、後続の第2のマッピング部11Bに出力する。

【0047】

なお、本例では、2画素間引き及びライン間引きを行うため、2種類のメモリ(RAM24−1〜24−4、RAM26−1〜26−8)を用いた。しかし、一つのメモリを使って、2画素間引きしたデータをライン間引きして8chの4:2:2/10ビット信号と4:0:0/10ビット信号として出力しても良い。

【0048】

図4は、マッピング部11の後段の処理を行う第2のマッピング部11Bの構成例を示す。

第2のマッピング部11Bは、マッピング部11の後段の処理ブロックとして、S/P変換部28−1〜28−16、複合部29−1〜29−4、P/S変換部30−1〜30−8を備える。複合部29−1は、書込みアドレス制御部31−1〜31−4、RAM32−1〜32−4、読み出しアドレス制御部33−1,33−2を備える。複合部29−2〜29−4は、4つのRAMを備える。

【0049】

第2のマッピング部11Bは、第1のマッピング部11Aが出力する4:2:2/rビット信号のデータ構造に合わせて変換したデュアルリンクHD−SDIを出力する機能を有する。また、第2のマッピング部11Bは、第1のマッピング部11Aが出力する4:0:0/rビット信号のデータ構造を、4:4:4/rビット信号のデータ構造に合わせて変換したデュアルリンクHD−SDIを出力する機能も有する。

【0050】

図3に示す読出し制御部27−1〜27−8によって読み出された8chの4:2:2/10ビット信号と4:0:0/10ビット信号が、第2のマッピング部11Bの入力CH1,3,5,7,9,11,13,15にそれぞれ入力する。そして、入力した8CHの4:2:2/10ビット信号と4:0:0/10ビット信号は、それぞれの入力CHに対応するS/P変換部28−1,28−3,…,28−15によってパラレルデータに変換される。なお、S/P変換部28−2,28−4,…,28−16は、後述する3840×2160/50P−60P/4:2:0/12ビットの映像信号の処理に際して、S/P変換部28−1,28−3,…,28−15と共に用いられる。

【0051】

S/P変換部28−1,28−3,…,28−15から出力するパラレルデータは、複合部29−1〜29−4に入力する。ここで、複合部29−1〜29−4の処理ブロックは複雑であるため、複合部29−1についてだけ処理を説明し、残りの複合部29−2〜29−4については記載を省略する。また、複合部29−1〜29−4が行う詳細な処理例については後述する(図12参照)。

【0052】

複合部29−1に含まれる書込みアドレス制御部31−1,31−3は、それぞれS/P変換部28−1,28−9が出力するパラレルデータをRAM32−1,32−3に書き込む。なお、入力CH3に入力し、S/P変換部28−3が出力するパラレルデータは、RAM32−5に書き込まれる。

【0053】

複合部29−1が備える読み出しアドレス制御部33−1,33−3は、それぞれRAM32−1,32−3からパラレルデータを読み出し、P/S変換部30−1,30−2に出力する。そして、P/S変換部30−1,30−2は、RAM32−1,32−3から読み出されたパラレルデータをシリアルデータである2chのHD−SDIとして出力する。

【0054】

また、複合部29−2には、入力CH3,CH11に入力し、S/P変換部28−3,28−11によってSP変換されたパラレルデータがRAM32−5,32−7に書き込まれる。その後、RAM32−5,32−7から読み出されたパラレルデータがP/S変換部30−3,30−4によってシリアルデータに変換された後、2chのHD−SDI(CH3,4)として出力する。

複合部29−3には、入力CH5,CH13に入力し、S/P変換部28−5,28−13によってSP変換されたパラレルデータがRAM32−9,32−11に書き込まれる。その後、RAM32−9,32−11から読み出されたパラレルデータがP/S変換部30−5,30−6によってシリアルデータに変換された後、2chのHD−SDI(CH5,6)として出力する。

複合部29−4には、入力CH7,CH15に入力し、S/P変換部28−7,28−15によってSP変換されたパラレルデータがRAM32−13,32−15に書き込まれる。その後、RAM32−13,32−15から読み出されたパラレルデータがP/S変換部30−7,30−8によってシリアルデータに変換された後、2chのHD−SDI(CH7,8)として出力する。

【0055】

[UHDTV信号規格のサンプル構造の例]

ここで、UHDTV信号規格のサンプル構造の例について、図5を参照して説明する。

図5は、3840×2160におけるUHDTV信号規格のサンプル構造の例を示す説明図である。図5A〜図5Dの説明に用いるフレームは、3840×2160で1フレームを構成する。

【0056】

3840×2160における信号規格のサンプル構造は、以下の4種類がある。なお、SMPTE規格において、R′G′B′のように、ダッシュ「′」をつけた信号は、ガンマ補正などが施された信号を示す。

【0057】

図5Aは、R′G′B′,Y′Cb′Cr′ 4:4:4システムの例である。このシステムでは、全サンプルにRGB又はYCbCrのコンポーネントが含まれる。

図5Bは、Y′Cb′Cr′ 4:2:2システムの例である。このシステムでは、偶数番目の画素サンプルにYCbCr、奇数番目の画素サンプルにYのコンポーネントが含まれる。

図5Cは、Y′Cb′Cr′ 4:2:0システムの例である。このシステムでは、偶数番目の画素サンプルにYCbCr、奇数番目の画素サンプルにY、さらに奇数ラインのCbCrが間引かれたコンポーネントが含まれる。

図5Dは、Y′Cb′Cr′ 4:0:0システムの例である。このシステムでは、全サンプルがYであり、CbCrが間引かれる。

【0058】

図6は、第1のマッピング部11Aが、UHDTV1クラスイメージに含まれる画素サンプルを第1〜第4のサブイメージにマッピングする例を示す図である。

【0059】

始めに、第1のマッピング部11Aが備える2画素間引き制御部22(図3参照)は、3840×2160/50P−60P/4:2:0/10ビット信号の1フレーム(1画面)を4分割する。ここのとき、3840×2160/50P−60P/4:2:0/10ビット信号を、4chの1920×1080/50P−60P/4:2:0/10ビット信号にマッピングする。

【0060】

具体的には、2画素間引き制御部22は、1フレーム(1画面)が3840×2160/50P−60P/4:2:0/10ビット信号であるUHDTV1クラスイメージからライン方向に2画素毎に画素サンプルを間引く。そして、2画素毎に間引いたそれぞれの信号から第1〜第4のサブイメージを作成する。このとき、4chの1920×1080/50P−60P/4:2:2あるいは4:0:0/10ビット信号であるHDイメージフォーマットの映像データ領域である1920サンプルにマッピングして、第1〜第4のサブイメージを作成する。以下の説明で、UHDTV1クラスイメージを「クラスイメージ」と呼ぶ。

【0061】

3840×2160/50P−60P/4:2:0/10ビット信号を2画素サンプルずつ間引くと、偶数ラインを2画素サンプルずつ間引いて得られる第1及び第2のサブイメージは4:2:2のデータ構造になる。一方、奇数ラインを2画素サンプル間引き方式で間引いて得られる第3及び第4の第3及び第4のサブイメージは、C′B/C′Rのサンプルが無いので4:0:0のデータ構造になる。3840×2160/50P−60P/4:2:0/10ビット信号は、SMPTE ST435−1で規定されるSystem2.1の第1〜第4のサブイメージの有効映像領域にマッピングされる。一方、3840×2160/50P−60P/4:2:0/12ビットは、SMPTE ST435−1で規定されるSystem4.1の第1〜第4のサブイメージの有効映像領域にマッピングされる。この時、SMPTE ST435−1,2やSMPTE ST2036−3では、画素サンプルが無い0相当の信号のうち、10ビットの場合には200hが割り当てられ、12ビットの場合には800hを割り当てるよう規定している。そして、3840×2160/50P−60P/4:2:0/10ビット信号がマッピングされた第1〜第4のサブイメージは、SMPTE ST372のFigure2に従ってライン間引きされて8chのHD−SDIに多重される。この多重方法は、SMPTE ST435−1に規定される。

【0062】

[10.692Gbpsのシリアルデータの構成例]

次に、1ラインのHD−SDIフォーマットで規定された10.692Gbpsのシリアルデータの構成例について、図7を参照して説明する。

【0063】

図7は、フレームレートが24Pである場合における10.692Gbpsのシリアル・デジタルデータの1ライン分のデータ構造例を示す。

この図では、ライン番号LN及び誤り検出符号CRCを含めたものをEAV,アクティブライン及びSAVとして示し、付加データの領域を含めたものを水平補助データスペースとして示している。水平補助データスペースには、オーディオ信号がマッピングされており、オーディオ信号に補完データを追加して水平補助データスペースを構成することによって、入力されたHD−SDIと同期を取ることができる。

【0064】

[モードDの説明]

次に、複数チャンネルのHD−SDIに含まれるデータを多重化する例について、図8を参照して説明する。データを多重化する方式は、SMPTE435−2にモードDとして規定される。

【0065】

図8は、モードDの説明図である。

モードDは、8ch(CH1〜CH8)のHD−SDIを多重化する方式であり、10.692Gbpsストリームの映像データ領域と水平補助データスペースのそれぞれにデータが多重されることを規定する。このとき、CH1,CH3,CH5,CH7のHD−SDIの映像/EAV/SAVデータが40ビット抽出され、スクランブルされて40ビットのデータに変換される。一方、CH2,CH4,CH6,CH8のHD−SDIの映像/EAV/SAVデータが32ビット抽出され、8B/10B変換によって、40ビットのデータとされる。各データは足し合わされ、80ビットのデータとされる。このエンコードされた8ワード(80ビット)のデータが10.692Gbpsストリームの映像データ領域に多重される。

【0066】

このとき、80ビットのデータブロックのうち、前半の40ビットのデータブロックには、偶数チャンネルの8B/10B変換された40ビットのデータブロックが割り当てられる。そして、後半の40ビットのデータブロックには、奇数チャンネルのスクランブルされた40ビットのデータブロックが割り当てられる。このため、1つのデータブロックには、例えば、CH2,CH1の順にデータブロックが多重される。このように順番を入れ替えている理由は、使用するモードを識別するためのコンテンツIDが、8B/10B変換された偶数チャンネルの40ビットのデータブロックに含まれるためである。

【0067】

一方、CH1のHD−SDIの水平補助データスペースは、8B/10B変換されて、50ビットのデータブロックにエンコードされる。そして、10.692Gbpsストリームの水平補助データスペースに多重される。ただし、CH2〜CH8のHD−SDIの水平補助データスペースは伝送されない。

【0068】

ここで、図6に説明した第1〜第4のサブイメージを8chのHD−SDIに変換する処理の以降の処理について、図9〜図12を参照して説明する。

【0069】

図9は、第1〜第4のサブイメージの画素サンプルを8CHのHD−SDIにマッピングする例を示す。

上述したように、ライン間引き制御部25−1〜25−4は、第1〜第4のサブイメージをライン間引きして、LinkA,Bの2チャンネルずつ、計8chの4:2:2/10ビット信号と4:0:0/10ビット信号に変換する。ここで、LinkA,Bについて図10を参照して説明する。

【0070】

図10は、SMPTE372によるライン間引きの例を示す。

ここでは、デュアルリンクインタフェースのライン番号とパッケージの例を用いてライン間引きを説明する。

【0071】

マッピング部11は、3840×2160/50P−60P/4:2:0/10ビット信号を第1〜第4のサブイメージに変換した後、複数の処理を経て生成した8chのHD−SDIを作成する。その後、ライン間引き制御部25−1〜25−4は、1920×1080/50P−60P/4:2:0/10ビット信号をLinkA,Bのデータ構造にライン間引きする。これにより、ライン間引きされた信号は、2chの1920×1080/50I−60I/4:2:0/10ビット相当の信号に変換される。

【0072】

次に、図11と図12を説明する。

図11は、第2のマッピング部11Bが8CHの4:2:2/10ビット信号と4:0:0/10ビット信号を4組のLinkA,Bに変換する処理の例を示す。

【0073】

図9に示した8chの4:2:2/10ビット信号と4:0:0/10ビット信号は、それぞれ内容が組み替えられた8CHのHD−SDIに変換される。このとき、HD−SDIのCH1(LinkA)には、元のベーシックストリームのCH1が当てはめられ、HD−SDIのCH2(LinkB)には、元のベーシックストリームのCH5が当てはめられる。

【0074】

ここで、以下の規則に基づいて8chのHD−SDIに4:2:2/10ビット信号と4:0:0/10ビット信号が多重される。

(1)図6に示す第1および第2のサブイメージから作られるベーシックストリームのCH1,2,3,4は、それぞれ4組のデュアルリンクHD−SDI(SMPTEST372)のLinkAであるCH1,3,5,7とする。

(2) 図6に示す第3および第4のサブイメージから作られるベーシックストリームのCH5,6,7,8は、Y′chに多重されたY信号の偶数番目の画素サンプルを、4組のデュアルリンクHD−SDIのLinkBであるCH2,4,6,8の次の奇数番目の画素サンプルのCBchに多重する。

(3)ベーシックストリームのCH5,6,7,8は、Y′chに多重されたY信号の奇数番目の画素サンプルを、4組のデュアルリンクHD−SDIのLinkBであるCH2,4,6,8の同じサンプル番号のC′Rchに多重し直す。

【0075】

このため、第2のマッピング部11Bは、第1及び第2のサブイメージから変換され、4:2:2/10ビット信号のデータ構造である第1〜第4のベーシックストリームをデュアルリンクHD−SDIのLinkAに多重する。また、第3及び第4のサブイメージから変換され、4:0:0/10ビット信号のデータ構造である第5〜第8のベーシックストリームのうち、サンプル番号が偶数であるY信号を、デュアルリンクHD−SDIのLinkBであって、サンプル番号+1番目のC′Bチャンネルに多重する。また、4:0:0/10ビット信号におけるY信号の奇数サンプルを、HD−SDIのLinkBであって、偶数サンプル番目のC′Rチャンネルに多重する。第1〜第8のベーシックストリームを4:4:4/10ビット信号のデータ構造であるHD−SDIに変換する。

【0076】

こうして、第2のマッピング部11Bは、4:2:2/10ビット信号である第1及び第2のサブイメージのCH1〜4と、4:0:0/10ビット信号である第3及び第4のサブイメージのCH5〜8からなる8chのHD−SDIを、4組のLinkA,Bにまとめる。

【0077】

図12は、4:2:2/10ビット信号と4:0:0/10ビット信号を、4:4:4/10ビット信号のデータ構造に変換する処理の例を示す。

本例では、LinkA/Bのデータ転送順序を示す。ここで、Y′Sub1,20等の「sub1,2」とは、第1及び第2のサブイメージを表し、「0」とは、Y′チャンネルにおける0番目の画素サンプルを表す表記規則に従って、LinkA,Bの画素サンプルについて変換処理を示す。

【0078】

LinkA:C′B0,Y′Sub1,20,C′R0,Y′Sub1,21,C′B2:,Y′Sub1,22,C′R2,Y′Sub1,23...

LinkB:Y′Sub3,40,A,Y′Sub3,41,A,Y′Sub3,42,A,Y′Sub3,43,A...

このとき、LinkAは、第1及び第2のサブイメージから得たCH1〜4をそのままとし、LinkBのCchに、第3及び第4のサブイメージから得たCH5〜8のYch(10ビット)を多重する。なお、CH5〜8に含まれる初期値のC′B,C′Rは削除する。

【0079】

LinkA/Bは、デュアルリンクHD−SDI規格であるSMPTEST372の4:4:4(R’G’B’又はY′Cb’Cr’)/10ビットデータ構造と同じデータ構造にすることができる。このため、モードDの10G−SDIは、4:4:4(R’G’B’又はY′Cb’Cr’)/10ビットのデュアルリンク HD−SDI Link A/Bを4組伝送可能である。つまり、4:2:0/10ビット信号を、4:4:4(R’G’B’又はY′Cb’Cr’)/10ビット信号に多重し直したデータ構造では、モードDの10G−SDI 1chで伝送可能である。このことは、現状のSMPTE ST 2036−3の規定に対して半分のch数とした10G−SDIで伝送出来ることを意味する。

【0080】

このようにして、3840×2160/50P−60P/4:2:0/10ビット信号を、4chのモードDで規定される10.692Gbpsの伝送ストリームに多重する。この多重方式には、特開2008−099189号公報に開示された方式が用いられる。ここで、図9に示すように、第1及び第2のサブイメージは、4:2:2/10ビット信号に変換され、第3及び第4のサブイメージは、4:0:0/10ビット信号に変換される。マッピング部11によってマッピングされた8chの4:2:2/10ビット信号と4:0:0/10ビット信号は、第2のマッピング部11B(図3参照)に送られる。

【0081】

SMPTE ST435−1,2やSMPTE ST 2036−3では、この8chのHD−SDIをSMPTE ST435−2で規定されるモードDの10G−SDIの奇数入力CH1,3,5,7に割り当てて伝送するよう規定してある。一方、偶数入力chには信号は割り当てないことが規定してある。そして、合計2chのモードDの10G−SDIで伝送する方式が標準化されている。

【0082】

[1−2.マッピング部の内部構成及び動作例(3840×2160/50P−60P/4:2:0/12ビットの例)]

ここで、入力信号が3840×2160/50P−60P/4:2:0/12ビットである場合に用いられる、マッピング11Cの内部構成及び動作例を説明する。

【0083】

図13は、4:2:0/12ビット信号をマッピングする第1のマッピング部11Cの内部構成例を示す。

第1のマッピング部11Cは、各部にクロックを供給するクロック供給回路41と、3840×2160/50P−60P/4:2:0/12ビットの映像信号を記憶するRAM43を備える。また、第1のマッピング部11Cは、RAM43から読み出したUHDTV1クラスイメージに含まれる画素サンプルを、2画素ずつ読み出す2画素間引き(インタリーブ)を制御する2画素間引き制御部42を備える。また、間引かれた2画素サンプルを第1〜第4のサブイメージとして書き込まれるRAM44−1〜44−4を備える。

【0084】

また、第1のマッピング部11Cは、RAM44−1〜44−4から読み出した第1〜第4のサブイメージをプログレッシブ信号からインターレース信号に変換するライン間引きを制御するライン間引き制御部45−1〜45−4を備える。また、第1のマッピング部11Cは、ライン間引き制御部45−1〜45−4が間引いたインターレース信号をライン毎に書き込まれるRAM46−1〜46−8を備える。

【0085】

また、第1のマッピング部11Cは、RAM46−1〜46−8から読出したデータのワード間引きを制御するワード間引き制御部47−1〜47−8を備える。また、第1のマッピング部11Cは、ワード間引き制御部47−1〜47−8が間引いたワードを書き込むRAM48−1〜48−16と、を備える。また、第1のマッピング部11Cは、RAM48−1〜48−16から読出したワードデータを16chのベーシックストリーム(4:2:2/12ビット信号と4:0:0/12ビット信号)として出力する読出し制御部49−1〜49−16を備える。

【0086】

なお、図13には、4:2:2/12ビット信号であるベーシックストリームのCH1,CH2を生成する処理ブロックを記載したが、ベーシックストリームのCH3〜CH16を生成するブロックも同様の構成例としているため、図示と詳細な説明を省略する。

【0087】

次に、第1のマッピング部11Cの動作例を説明する。

クロック供給回路41は、2画素間引き制御部42、ライン間引き制御部45−1〜45−4、ワード間引き制御部47−1〜47−8、及び読出し制御部49−1〜49−16にクロックを供給する。これらのクロックは、画素サンプルの読み出し又は書き込みに用いられ、これらのクロックにより各部が同期する。

【0088】

不図示のイメージセンサから入力する1フレームの画素数が最大3840×2160である、ベーシックストリームフォーマットで規定される画素数を越えるUHDTV1のクラスイメージによって規定される映像信号は、RAM43に書き込まれる。本例のUHDTV1のクラスイメージは、3840×2160/50P−60P/4:2:0/12ビットの映像信号を表す。本例では、UHDTV1のクラスイメージから2画素毎に間引かれた画素サンプルが、1920×1080/50P−60P/4:2:0/12ビット信号で規定される第1〜第4のサブイメージの映像データ領域にマッピングされることとなる。

【0089】

2画素間引き制御部42は、UHDTV1のクラスイメージから2画素サンプル毎に間引いて1920×1080/50P−60Pに相当する第1〜第4のサブイメージの有効領域にマッピングする。1920×1080/50P−60Pは、SMPTE435−1で規定される。このマッピングの詳細な処理例は後述する。

【0090】

次に、ライン間引き制御部45−1〜45−4は、プログレッシブ信号をインターレース信号に変換する。具体的には、ライン間引き制御部45−1〜45−4は、RAM44−1〜44−4から第1〜第4のサブイメージの映像データ領域にマッピングされた画素サンプルを読出す。このとき、ライン間引き制御部45−1〜45−4は、1つのサブイメージを、2chの1920×1080/50I−60I/4:2:2あるいは4:0:0/12ビット信号に変換する。そして、第1〜第4のサブイメージの映像データ領域から1ラインおきに間引いてインターレース信号とした1920×1080/50I−60I信号をRAM46−1〜46−8に書き込む。

【0091】

次に、ワード間引き制御部47−1〜47−8は、ライン間引き制御部45−1〜45−4によってライン毎に間引かれた画素サンプルをワード毎に間引く。そして、SMPTE435−1に規定されるHD−SDIの映像データ領域にマッピングし、第1〜第16のベーシックストリームを出力する。具体的には、RAM46−1〜46−8から読み出したライン毎に間引かれたインターレース信号をワード毎に間引いて、SMPTE435−1に規定されるベーシックストリームの映像データ領域にマッピングする。このとき、ワード間引き制御部47−1〜47−8は、SMPTE435−1に規定され、第1〜第4のサブイメージ毎に対応する4チャンネルのモードDによって定まる10.692Gbpsストリームの映像データ領域に画素サンプルを多重する。つまり、ワード間引き制御部47−1〜47−8は、1920×1080/50I−60I/4:2:2あるいは4:0:0/12ビット信号を、16chの4:2:2/12ビット信号と4:0:0/12ビット信号に変換する。そして、第1〜第4のサブイメージのそれぞれに対し、SMPTE435−1に規定される4本ずつのベーシックストリームの映像データ領域にマッピングする。

【0092】

具体的には、ワード間引き制御部47−1〜47−8は、RAM44−1〜44−8からSMPTE372のFigure9と同じ方式でワード毎に間引いて画素サンプルを読出す。そして、ワード間引き制御部47−1〜47−8は、読出した画素サンプルを、それぞれ2chの1920×1080/50I−60I信号に変換して、RAM48−1〜48−16に書き込む。

【0093】

そして、読出し制御部49−1〜49−16は、RAM48−1〜48−16から読出した16chのベーシックストリームの伝送ストリームを出力する。具体的には、読出し制御部49−1〜49−16は、クロック供給回路41から供給された基準クロックでRAM48−1〜48−16から画素サンプルを読出す。そして、2本のLinkA、Bを16対で構成した16chのベーシックストリームCH1〜CH16を、後続のマッピング部1Bに出力する。

【0094】

なお、本例では、2画素間引き、ライン間引き、及びワード間引きを行うため、3種類のメモリ(RAM44−1〜44−4、RAM46−1〜46−8、RAM48−1〜48−16)を用いて、3段階の間引き処理を行っている。しかし、一つのメモリに2画素間引き、ライン間引き、及びワード間引きして得たデータを書込み、16chのベーシックストリームとして出力しても良い。

【0095】

図14は、第1のマッピング部11Cが3840×2160/50P−60P/4:2:0/12ビット信号を16chのベーシックストリームにマッピングする例を示す。

上述したように、3840×2160/50P−60P/4:2:0/12ビット信号を多重した第1〜第4のサブイメージの画素サンプルは、ライン間引きに続いてワード間引きされて16chのベーシックストリームに多重される。

【0096】

ここで、ベーシックストリームCH1〜CH8は、4:2:2/10ビット信号と同じサンプル構成であり、モードDの10G−SDIのLink1で伝送可能と言える。同様に、ベーシックストリームCH9〜CH16は、4:0:0/10ビット信号と同じサンプル構成であり、モードDの10G−SDIのLink2で伝送可能と言える。

【0097】

図15は、16chの4:2:2/12ビット信号と4:0:0/12ビット信号を4組のLink A/BであるHD−SDIにマッピングする例を示す。

図16は、16chの4:2:2/12ビット信号と4:0:0/12ビット信号を、4:4:4/12ビット信号に変換する処理の例を示す。

図14に示されるベーシックストリームCH1〜CH16は、図15に示すように以下の順番で多重し直す。

【0098】

(1)ベーシックストリームのCH1,3,5,7はそれぞれ4組のデュアルリンクHD−SDIのLinkAであるCH1,3,5,7とする。ベーシックストリームのCH2,4,6,8,9〜16は、LinkBのYおよびCchにおける第3及び第4のサブイメージのY′信号上位10ビットと、第1及〜第4のサブイメージのY′C′BC′R信号の下位2ビットを多重する。そして、4組のデュアルリンクHD−SDIのLinkBであるCH2,4,6,8のYおよびCchに多重し直す。このとき、ベーシックストリームのCH2,4,6,8,9〜16デフォルト信号は除く。

【0099】

(2)第1及び第2のサブイメージから作られるCH2,4,6,8の偶数番目の画素サンプルのYch信号(6ビット)は、4組のデュアルリンクHD−SDIのLinkBであるCH2,4,6,8のYchの同じ偶数番目の画素サンプルに多重する。

【0100】

(3)第3及び第4のサブイメージから作られるベーシックストリームのCH9,11,13,15のY信号(10ビット)は、以下のように多重する。すなわち、ベーシックストリームのCH9,11,13,15の偶数番目の画素サンプルを4組のデュアルリンクHD−SDIのLinkBであるCH2,4,6,8の次の奇数番目の画素サンプルのC′Bchに多重する。そして、奇数番目の画素サンプルを4組のデュアルリンクHD−SDIのLinkBであるCH2,4,6,8の同じ奇数番目の画素サンプルのC′Rchに多重し直す。

【0101】

(4)第1及び第2のサブイメージから作られるベーシックストリームのCH2,4,6,8の奇数番目の画素サンプルのYch信号(2ビット)と、第3及び第4のサブイメージから作られるベーシックストリームのCH10,12,14,16のY信号の下位2ビットは、4組のデュアルリンクHD−SDIのLinkBであるCH2,4,6,8のYchの奇数番目の画素サンプルに、例えば次表4に示すように、割り当てる。

【0102】

【表4】

・下位2ビットはReserve(0)

・ビット2,3に、第3及び第4のサブイメージのY信号の奇数番目の画素サンプルの下位2ビットを多重する。

・ビット4,5に、第3及び第4のサブイメージのY信号の偶数番目の画素サンプルの下位2ビットを多重する。

・ビット6,7に、第1及び第2のサブイメージのY信号の奇数番目の画素サンプルの下位2ビットを多重する。

・ビット8はイーブン(偶数)パリティ

・ビット9はビット8の反転ビット

とし、このY信号10ビットをY′Sub1−4:0−1と表現する。

【0103】

LinkA/Bのデータ転送順序は図15中に示すように変換される。

LinkA:C′B0:2−11,Y′Sub1,20:2−11,C′R0:2−11,Y′Sub1,21:2−11,C′B2:2−11,Y′Sub1,22:2−11,C′R2:2−11,Y′Sub1,23:2−11...

LinkB:Y′Sub3,40:2−11,Y′C′BC′R0:0−1,Y′Sub3,41:2−11,Y′Sub1−41:0−1,Y′ Sub3,42:2−11,Y′ C′BC′R2:0−1,Y′ Sub3,43:2−11,Y′Sub1−43:0−1...

とする。

【0104】

このとき、第2のマッピング部11Bは、第1および第2のサブイメージから変換され、4:2:2/12ビット信号のデータ構造である第1、3,5,7のベーシックストリームをデュアルリンクHD−SDIのLinkAであるCH1,3,5,7に多重する。

また、第1及び第2のサブイメージから変換され、4:2:2/12ビット信号のデータ構造である第2,4,6,8のベーシックストリームのサンプル番号が偶数であるY信号を、デュアルリンクHD−SDIのLinkBであるCH2,4,6,8の同じサンプル番号のY信号に多重する。また、第3及び第4のサブイメージから変換され、4:0:0/12ビット信号のデータ構造である第9,11,13,15のベーシックストリームのサンプル番号が偶数であるY信号を、デュアルリンクHD−SDIのLinkBであるCH2,4,6,8のサンプル番号+1番目のC′Bチャンネルに多重する。また、第9,11,13,15のベーシックストリームのサンプル番号が奇数であるY信号を、デュアルリンクHD−SDIのLinkBであるCH2,4,6,8の同じサンプル番目のCR′チャンネルに多重する。また、第2,4,6,8のベーシックストリームのサンプル番号が奇数であるY信号、及び第3及び第4のサブイメージから変換され、4:0:0/12ビット信号のデータ構造である第10,12,14,16のベーシックストリームのY信号の下位2ビットを、デュアルリンクHD−SDIのLinkBであるCH2,4,6,8のサンプル番号が奇数であるY信号に多重する。

【0105】

このようにして、4:2:2/12ビット相当である第1のサブイメージのCH1,2と、4:0:0/12ビット相当である第3のサブイメージのCH9,10からなる4つのLinkを、2つのLink(LinkA/B)にまとめる。そして、デュアルLinkHD−SDI(SMPTE ST 372)のR’G’B’(4:4:4/12ビット)と同じデータ構造に合わせる

【0106】

これにより、デュアルリンクHD−SDI規格であるSMPTE ST372の4:4:4(R’G’B’又はY′C′BC′R)/12ビットデータ構造と同じデータ構造にすることができる。この結果、モードDの10G−SDIは4:4:4(R’G’B’又はY′Cb’Cr’)/12ビットのデュアルリンクHD−SDI LinkA/Bを4組で伝送可能である。そして、伝送するHD−SDIのチャンネル数を16chから8chに減らすことができる。また、4:4:4(R’G’B’又はY′Cb’Cr’)/12ビット相当に多重し直したデータ構造では、1chのモードDの10G−SDIで伝送可能である。このため、現状のSMPTE ST2036−3の規定に対して半分のch数の10G−SDIで伝送出来る。

【0107】

ここで、図4に示す第2のマッピング部11Bについて再び説明する。

図中に太線で描かれているCH1,3,5,7,9,11,13,15が、4:2:0/10ビット信号を処理する際の経路であり、太線と細線で書いたCH1〜16が4:2:0/12ビットの信号を処理する際の経路である。4:2:0/10ビット信号の場合は、4:2:0/12ビット信号との上位互換があるので、信号処理回路としては4:2:0/12ビット信号用の一部の回路を使用することで4:2:0/10ビット信号を処理できる。すなわち、図4の入力CH1〜CH16の奇数チャンネルに対して、図3に示される8CHのベーシックストリームの奇数chを割り当てることで、4:2:0/10ビット信号と4:2:0/12ビット信号の上位互換が取れる。このため、S/P変換回路で作成した再生クロックやワード同期信号から、S/P変換したY/C−CH1データのRAMへの書き込み制御信号や、読み出し信号を作成する。画素サンプルの読み出し時には、図12又は図16に示す変換処理に従って入力Y/C−chデータをLinkBに多重し直す。

【0108】

上述したように、第2のマッピング部11Bは、マッピング部11の後段の処理ブロックとして、S/P変換部28−1〜28−16、複合部29−1〜29−4、P/S変換部30−1〜30−8を備える。

【0109】

図13に示す読出し制御部49−1〜49−16によって読み出された16chのベーシックストリームが、第2のマッピング部11Bが備える入力CH1〜16にそれぞれ入力する。そして、入力したベーシックストリームは、各入力CHに対応するS/P変換部28−1〜28−16によってパラレルデータに変換される。

【0110】

S/P変換部28−1〜28−16が出力するデータは、複合部29−1〜29−4に入力する。複合部29−1は、ベーシックストリームCH1,CH2,CH9,CH10に基づいて、HD−SDIのLinkA,B(CH1,2)にまとめる。

複合部29−2は、ベーシックストリームCH3,CH4,CH11,CH12に基づいて、HD−SDIのLinkA,B(CH3,4)にまとめる。

複合部29−3は、ベーシックストリームCH5,CH6,CH13,CH14に基づいて、HD−SDIのLinkA,B(CH5,6)にまとめる。

複合部29−4は、ベーシックストリームCH7,CH8,CH15,CH16に基づいて、HD−SDIのLinkA,B(CH7,8)にまとめる。

【0111】

このように、4:2:0/10ビット信号又は4:2:0/12ビット信号のいずれであっても、マッピング部11が画素サンプルをマッピングし直した後、8chのHD−SDIがS/P・8B/10B変換部12に出力される。このため、8chのHD−SDIのデータ構造を、デュアルLinkHD−SDI(SMPTEST372)のR’G’B’あるいはY′C′BC′R(4:4:4/10ビット、12ビット)と同じデータ構造に合わせることができる。また、モードDの2chの10G−SDIで伝送するために必要なデータ構造を、モードDの10G−SDIの1chで伝送可能なデータ構造に変換できる。

【0112】

そして、8ビット/10ビットエンコーディングされた50ビット幅のパラレル・デジタルデータは、PLL13から受け取る37.125MHzのクロックによって不図示のFIFOメモリに書き込まれる。その後、PLL13から受け取る83.5312MHzのクロックによって50ビット幅のままFIFOメモリから読み出されて、多重部14に送られる。

【0113】

次に多重部14が行う多重処理について説明する。

図17は、多重部14が行うデータの多重処理の例を示す。図17Aは、スクランブルされたCH1〜CH8の各40ビットのデータが、CH1とCH2,CH3とCH4、CH5とCH6、CH7とCH8のペアの順番が入れ替えられて、320ビット幅に多重される様子を示す。図17Bは、8B10B変換された50ビット/サンプルのデータが、200ビット幅の4サンプルに多重される様子を示す。

【0114】

図17Aに示すように、8ビット/10ビットエンコーディングされたデータを、自己同期型スクランブルを掛けたデータで40ビット毎に挟んでいる。これにより、スクランブル方式によるマーク率(0と1の割合)変動や、0−1、1−0の遷移の不安定さを解消し、パソロジカルパターンの発生を防止することができる。

【0115】

また、多重部14は、S/P・スクランブル・8B/10B部12内のFIFOメモリから読み出されたCH1の水平ブランキング期間のみが50ビット幅であるパラレル・デジタルデータを、4サンプル分多重して200ビット幅にする。

【0116】

多重部14によって多重された320ビット幅のパラレル・デジタルデータと200ビット幅のパラレル・デジタルデータは、データ長変換部15に送られる。データ長変換部15は、シフトレジスタを用いて構成されている。そして、320ビット幅のパラレル・デジタルデータを256ビット幅に変換したデータと、200ビット幅のパラレル・デジタルデータを256ビット幅に変換したデータとを用いて、256ビット幅のパラレル・デジタルデータを形成する。さらに、256ビット幅のパラレル・デジタルデータを128ビット幅に変換する。

【0117】

データ長変換部15からFIFOメモリ16を介して送られた64ビット幅のパラレル・デジタルデータは、多チャンネルデータ形成部17で、各々がビットレート668.25Mbpsを有する16ch分のシリアル・デジタルデータとして形成される。多チャンネルデータ形成部17は、例えばXSBI(Ten gigabit Sixteenビット Interface:10ギガビットイーサネット(登録商標)のシステムで使用される16ビットインタフェース)である。多チャンネルデータ形成部17によって形成された16chのシリアル・デジタルデータは、多重・P/S変換部18に送られる。

【0118】

多重・P/S変換部18は、パラレル/シリアル変換部としての機能を有しており、多チャンネルデータ形成部17から受け取る16chのシリアル・デジタルデータを多重し、その多重したパラレル・デジタルデータをパラレル/シリアル変換する。これにより、668.25Mbps×16=10.692Gbpsのシリアル・デジタルデータを生成する。

【0119】

多重・P/S変換部18によって生成されたビットレート10.692Gbpsのシリアル・デジタルデータは、光電変換部19に送られる。光電変換部19は、ビットレート10.692Gbpsのシリアル・デジタルデータをCCU2に出力する出力部として機能する。そして、光電変換部19は、多重部14によって多重された10.692Gbpsの伝送ストリームを出力する。光電変換部19によって光信号に変換されたビットレート10.692Gbpsのシリアル・デジタルデータは、放送用カメラ1から光ファイバーケーブル3経由でCCU2に伝送される。

【0120】

本例の放送用カメラ1を用いることによって、イメージセンサから入力した3840×2160/50P−60Pである、4:2:0/10ビット,12ビット信号をシリアル・デジタルデータとして送信することができる。本例の信号送信装置及び信号送信方法では、3840×2160/50P−60P/4:2:0/10ビット信号をCH1〜CH8のHD−SDI信号に変換する。その後、10.692Gbpsのシリアル・デジタルデータとして出力することが可能となる。

【0121】

なお、各放送用カメラ1からCCU2には、3840×2160/50P−60P/4:2:0/10ビット,12ビット信号が伝送されるだけでない。すなわち、CCU2からも前述のリターンビデオ(他の放送用カメラ1で撮影中の映像を表示させるための映像信号)が光ファイバーケーブル3経由で各放送用カメラ1に伝送される。リターンビデオは周知の技術を用いて生成される(例えば、2チャンネル分のHD−SDI信号を、それぞれ8ビット/10ビットエンコーディングした後、多重してシリアル・デジタルデータに変換する)ので、そのための回路構成の説明は省略する。

【0122】

[CCUの内部構成及び動作例]

次に、CCU2の内部構成例を説明する。

図18は、CCU2の回路構成のうち、本実施の形態に関連する部分を示すブロック図である。CCU2には、このような回路が、各放送用カメラ1に一対一に対応して複数組設けられている。

【0123】

放送用カメラ1から光ファイバーケーブル3を経由して伝送されたビットレート10.692Gbpsのシリアル・デジタルデータは、光電変換部31によって電気信号に変換された後、S/P変換・多チャンネルデータ形成部32に送られる。S/P変換・多チャンネルデータ形成部32は、例えばXSBIである。そして、S/P変換・多チャンネルデータ形成部32は、ビットレート10.692Gbpsのシリアル・デジタルデータを受信する。

【0124】

S/P変換・多チャンネルデータ形成部32は、ビットレート10.692Gbpsのシリアル・デジタルデータをシリアル/パラレル変換する。そして、シリアル/パラレル変換したパラレル・デジタルデータから、各々がビットレート668.25Mbpsを有する16ch分のシリアル・デジタルデータを形成するとともに、668.25MHzのクロックを抽出する。

【0125】

S/P変換・多チャンネルデータ形成部32によって形成された16chのパラレル・デジタルデータは、多重部33に送られる。また、S/P変換・多チャンネルデータ形成部32によって抽出された668.25MHzのクロックは、PLL34に送られる。

【0126】

多重部33は、S/P変換・多チャンネルデータ形成部32から受け取る16chのシリアル・デジタルデータを多重して、64ビット幅のパラレル・デジタルデータをFIFOメモリ35に送る。

【0127】

PLL34は、S/P変換・多チャンネルデータ形成部32から受け取る668.25MHzのクロックを4分の1に分周した167.0625MHzのクロックをFIFOメモリ35に書込みクロックとして送る。

【0128】

またPLL34は、S/P変換・多チャンネルデータ形成部32から受け取る668.25MHzのクロックを8分の1に分周した83.5312MHzのクロックを、FIFOメモリ35に読出しクロックとして送る。さらに、後述するデスクランブル・8B/10B・P/S部38内のFIFOメモリに、83.5312MHzのクロックを書込みクロックとして送る。

【0129】

またPLL34は、S/P変換・多チャンネルデータ形成部32から受け取る668.25MHzのクロックを18分の1に分周した37.125MHzのクロックを、デスクランブル・8B/10B・P/S部38内のFIFOメモリに読出しクロックとして送る。また、PLL34は、デスクランブル・8B/10B・P/S部38内のFIFOメモリに37.125MHzのクロックを書込みクロックとして送る。

【0130】

またPLL34は、S/P変換・多チャンネルデータ形成部32から受け取る668.25MHzのクロックを9分の1に分周した74.25MHzのクロックを、デスクランブル・8B/10B・P/S部38内のFIFOメモリに読出しクロックとして送る。

【0131】

FIFOメモリ35では、多重部33から受け取る64ビット幅のパラレル・デジタルデータが、PLL34から受け取る167.0625MHzのクロックによって書き込まれる。FIFOメモリ35に書き込まれたパラレル・デジタルデータは、PLL34から受け取る83.5312MHzのクロックによって128ビット幅のパラレル・デジタルデータとして読み出されて、データ長変換部36に送られる。

【0132】

データ長変換部36は、シフトレジスタを用いて構成されており、128ビット幅のパラレル・デジタルデータを、256ビット幅に変換する。そして、データ長変換部36は、タイミング基準信号SAVまたはEAVに挿入されているK28.5を検出する。これにより各ライン期間を判別して、タイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータを320ビット幅に変換する。さらに、水平補助データスペースのデータ(8B/10BエンコーディングされたCH1の水平補助データスペースのデータ)を200ビット幅に変換する。データ長変換部36によってデータ長を変換された320ビット幅のパラレル・デジタルデータと200ビット幅のパラレル・デジタルデータとは、分離部37に送られる。

【0133】

分離部37は、データ長変換部36から受け取る320ビット幅のパラレル・デジタルデータを、放送用カメラ1内の多重部14によって多重される前の40ビットずつのCH1〜CH8のデータに分離する。このパラレル・デジタルデータには、タイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータが含まれる。そして、各CH1〜CH8の40ビット幅のパラレル・デジタルデータを、デスクランブル・8B/10B・P/S部38に送る。

【0134】

また、分離部37は、データ長変換部36から受け取る200ビット幅のパラレル・デジタルデータを、多重部14によって多重される前の50ビットずつのデータに分離する。このパラレル・デジタルデータには、8B/10BエンコーディングされたCH1の水平補助データスペースのデータが含まれる。そして、この50ビット幅のパラレル・デジタルデータを、デスクランブル・8B/10B・P/S部38に送る。

【0135】

デスクランブル・8B/10B・P/S部38は、CH1〜CH8に一対一に対応する32個のブロックによって構成される。本例のデスクランブル・8B/10B・P/S部38は、映像信号がマッピングされ、それぞれが第1のリンクチャンネルと第2のリンクチャンネルに分割され、かつ2ラインに分割された第1〜第4のサブイメージを受信する受信部として機能する。

【0136】

デスクランブル・8B/10B・P/S部38は、LinkAであるCH1,CH3,CH5,CH7用のブロックを備え、入力したパラレル・デジタルデータにデスクランブルを掛けて、シリアル・デジタルデータに変換して出力する。

また、デスクランブル・8B/10B・P/S部38は、LinkBであるCH2ch4,CH6,CH8用のブロックを備え、入力したパラレル・デジタルデータを8B/10Bにデコードする。そして、シリアル・デジタルデータに変換して出力する。

【0137】

再生部39は、デスクランブル・8B/10B・P/S部38から送られたCH1〜CH8(LinkA及びLinkB)のHD−SDI信号に、SMPTE 435に従って放送用カメラ1内のマッピング部11の処理と逆の処理を施す。この処理により、再生部39は、3840×2160/50P−60P/4:2:0/10ビット,12ビット信号を再生する。

【0138】

このとき、再生部39は、S/P変換多チャンネルデータ形成部32が受信したHD−SDI1〜32より、ワード多重、ライン多重、2画素多重の処理を順に行うことで第1〜第4のサブイメージを再生する。そして、再生部39は、第1〜第4のサブイメージの映像データ領域に配置された画素サンプルを2画素ずつ取り出して、UHDTV1クラスイメージのフレーム内に順に多重する。

【0139】

再生部39によって再生された3840×2160/50P−60P/4:2:0/10ビット,12ビット信号は、CCU2から出力されて、例えばVTR等(図示略)に送られる。

【0140】

本例においてCCU2は、放送用カメラ1によって生成されたシリアル・デジタルデータを受信する側の信号処理を行う。この信号受信装置,信号受信方法では、このビットレート10.692Gbpsのシリアル・デジタルデータからパラレル・デジタルデータが生成され、このパラレル・デジタルデータが、LinkA,LinkBの各チャンネルのデータに分離される。

【0141】

分離されたLinkAのデータについては、自己同期型デスクランブルが掛けられるが、タイミング基準信号SAVの直前でデスクランブラ内のレジスタの値を全て0にセットしてデコードが開始される。さらに、誤り検出符号CRCに続く少なくとも数ビットのデータにも自己同期型デスクランブルが掛けられる。これにより、タイミング基準信号SAV,アクティブライン,タイミング基準信号EAV,ライン番号LN及び誤り検出符号CRCのデータのみに自己同期型スクランブルが掛けられる。このため、水平補助データスペースのデータには自己同期型スクランブルが掛けられていないにもかかわらず、掛け算回路であるデスクランブラの桁上がりを考慮した正確な計算を行って元のデータを再生することができる。

【0142】

一方、分離されたLinkBのデータについては、8ビット/10ビットデコーディングしたRGBのビットから、LinkBの各サンプルのデータが形成される。そして、自己同期型デスクランブルを掛けられたLinkAのパラレル・デジタルデータと、各サンプルを形成されたLinkBのパラレル・デジタルデータとがそれぞれパラレル/シリアル変換される。そして、マッピングされたCH1〜CH8のHD−SDI信号が再生される。

【0143】

[1−3.再生部の内部構成及び動作例(3840×2160/50P−60P/4:2:0/10ビットの例)]

図19と図20は、再生部39の内部構成例を示す。

始めに、3840×2160/50P−60P/4:2:0/10ビット信号の再生処理の例について説明する。再生部39は、マッピング部11が画素サンプルに行った処理を逆変換するブロックであり、第1の再生部39Aと第2の再生部39Bを備える。

第1の再生部39Aは、第1のマッピング部11Aが行った処理を逆変換し、第2の再生部39Bは、第2のマッピング部11Bが行った処理を逆変換する。なお、再生部39の処理は、第2の再生部39Bと第1の再生部39Aの順に行われるため、以下の説明では、第2の再生部39Bと第1の再生部39Aの順に構成及び動作例を説明する。

【0144】

図19は、8B/10B・P/S部38から入力した8chのHD−SDIより、第1の再生部39Aに出力する8chのベーシックストリームを生成する第2の再生部39Bの内部構成例を示す。

【0145】

上記のように、第2の再生部39Bは、第2のマッピング部11Bと逆の処理を行うものである。

第2の再生部39Bは、4:4:4/rビット信号のデータ構造としてあるデュアルリンクHD−SDIを、4:2:2/rビット信号、及び4:0:0/rビット信号に変換する。

【0146】

第2の再生部39Bは、S/P変換部62−1〜62−8、分離部63−1〜63−4、P/S変換部58−1〜58−16を備える。分離部63−1は、書込みアドレス制御部61−1,61−2、RAM60−1〜60−4、読み出しアドレス制御部59−1〜59−4を備える。

【0147】

8chのHD−SDIは、S/P変換部62−1〜62−8によってパラレルデータに変換された後、分離部63−1〜63−4に入力される。分離部63−1〜63−4は、上述した図12に示す画素サンプルのマッピング処理と逆の処理を行ってHD−SDIからベーシックストリームを生成する。ここで、分離部63−1〜63−4の処理ブロックは複雑であるため、分離部63−1についてだけ処理を説明し、残りの分離部63−2〜29−4については記載を省略する。

【0148】

第2の再生部39Bは、デュアルリンクHD−SDIのLinkAを4:2:2/10ビット信号のデータ構造である第1〜第4のベーシックストリームに多重して、第1及び第2のサブイメージを再生する。デュアルリンクHD−SDIのLinkBであって、サンプル番号+1番目のC′Bチャンネルから読み出したY信号を、4:0:0/10ビット信号のデータ構造である第5〜第8のベーシックストリームのうち、サンプル番号が偶数であるY信号に多重して、第3及び第4のサブイメージを再生する。HD−SDIのLinkBであって、偶数サンプル番目のC′Bチャンネルから読み出したY信号を、4:0:0/10ビット信号のうち、サンプル番号が奇数であるY信号に多重して、4:4:4/10ビット信号のデータ構造であるHD−SDIを第1〜第8のベーシックストリームに変換する。

【0149】

分離部63−1に含まれる書込みアドレス制御部61−1,61−2は、それぞれS/P変換部62−1,62−2が出力するパラレルデータをRAM60−1,60−3に書き込む。分離部63−1が備える読み出しアドレス制御部59−1,59−3は、それぞれRAM60−1,60−3からパラレルデータを読み出し、P/S変換部58−1,58−9に出力する。そして、P/S変換部58−1,58−9は、RAM60−1,60−3から読み出されたパラレルデータをシリアルデータである2chのベーシックストリーム(CH1,9)として第1の再生部39Aに出力する。

【0150】

分離部63−2には、2chのHD−SDI(CH3,4)が入力し、S/P変換部62−3,62−4によってSP変換されたパラレルデータがRAM60−5,60−7に書き込まれる。その後、P/S変換部58−3,58−11は、RAM60−5,60−7から読み出したパラレルデータをシリアルデータに変換した後、2chのベーシックストリーム(CH3,11)として第1の再生部39Aに出力する。

分離部63−3には、2chのHD−SDI(CH5,6)が入力し、S/P変換部62−5,62−6によってSP変換されたパラレルデータがRAM60−9,60−11に書き込まれる。その後、P/S変換部58−5,58−13は、RAM60−9,60−11から読み出されたパラレルデータをシリアルデータに変換した後、2chのベーシックストリーム(CH5,13)として第1の再生部39Aに出力する。

分離部63−4には、2chのHD−SDI(CH7,8)が入力し、S/P変換部62−7,62−8によってSP変換されたパラレルデータがRAM60−13,60−15に書き込まれる。その後、P/S変換部58−7,58−15は、RAM60−13,60−15から読み出したパラレルデータをシリアルデータに変換した後、2chのベーシックストリーム(CH7,15)として第1の再生部39Aに出力する。

【0151】

図20は、第2の再生部39Bから入力した8chのベーシックストリームから、3840×2160/50P−60P/4:2:0/10ビット信号を再生する第1の再生部39Aの内部構成例を示す。

【0152】

第1の再生部39Aは、各部にクロックを供給するクロック供給回路51を備える。クロック供給回路51は、2画素多重制御部52、ライン多重制御部55−1〜55−4、及び書込み制御部57−1〜57−8にクロックを供給する。このクロックにより各部が同期して、画素サンプルの読み出し又は書き込みが制御される。

【0153】

また、第1の再生部39Aは、SMPTE435−2に規定されるモードDの8chのHD−SDIと同じデータ構造としたベーシックストリームをそれぞれ記憶するRAM56−1〜56−8を備える。上述したようにベーシックストリームCH1〜8は、それぞれ1920×1080/50I−60I信号を構成する。そして、ベーシックストリームCH1〜8には、デスクランブル・8B/10B・P/S部38から入力されたLinkAであるCH1,CH3,CH5,CH7と、LinkBであるCH2,CH4,CH6,CH8の画素サンプルを入れ替えた8chのベーシックストリームが用いられる。

【0154】

書込み制御部57−1〜57−8は、クロック供給回路51から供給されるクロックに合わせて、入力した8chのベーシックストリームCH1〜8をRAM56−1〜56−8に保存する書込み制御を行う。

【0155】

ライン多重制御部55−1〜55−4は、RAM56−1〜56−8から読み出したインターレース信号をサブイメージ毎に多重してプログレッシブ信号とする。このとき、ライン多重制御部55−1〜55−4は、4:2:0/rビット信号のベーシックストリームを、m′×n′(m′サンプル、n′ラインを示すm′,n′は、正の整数)/a′−b′(a′,b′は、プログレッシブ信号のフレームレート)/4:2:2/rビット信号で規定される第1〜第N/2(Nは、2以上の整数)のサブイメージの一ラインおきに画素サンプルを多重する。同様に、4:0:0/rビット信号のベーシックストリームを、第(N/2)+1〜第Nのサブイメージの一ラインおきに画素サンプルを多重する。この第1〜第4のサブイメージは、m′×n′が1920×1080であり、a′−b′が50P,59.94P,60Pである。そして、ライン多重制御部55−1〜55−4は、1920×1080/50P−60P/4:2:0/10ビット信号をRAM54−1〜54−4に書き込む。すなわち、RAM54−1〜54−4に保存された信号が第1〜第4のサブイメージを構成する。

【0156】

2画素多重制御部52は、第1〜第4のサブイメージの映像データ領域から抽出した画素サンプルをUHDTV1のクラスイメージにマッピングする。このとき、2画素多重制御部52は、SMPTE435−1で規定される第1〜第4のサブイメージの内、第1のサブイメージと第2のサブイメージから抽出した2つの画素サンプルをフレームの偶数ライン上に多重し、第3のサブイメージと第4のサブイメージから抽出した2つの画素サンプルをフレームの奇数ライン上に多重する場合に、フレームの同一ライン上で2つの画素サンプルを隣り合わせて多重する。すなわち、第1〜第Nのサブイメージから2画素ずつ抽出した画素サンプルを、1フレームの画素数がHD−SDIフォーマットで規定される画素数を越えるm×n(mサンプル、nラインを示すm,nは、正の整数)/a−b(a,bは、プログレッシブ信号のフレームレート)/4:2:0/rビット信号で規定されるクラスイメージのフレームにおける同一ラインに隣り合わせて多重する。このとき、2画素多重制御部52は、RAM54−1〜54−4から読み出した画素サンプルを2画素毎に以下の処理で多重する。すなわち、第1〜第4のサブイメージから2画素ずつ抽出した画素サンプルを、UHDTV1のクラスイメージに併せて多重する。このクラスイメージは、3840×2160/50P−60P/4:2:0/10ビット信号である。

【0157】

なお、図20では、2画素多重、ライン多重を2種類のRAMを用いて2段階で行う例を書いた。しかし、一つのRAMを用いて3840×2160/50P−60P/4:2:0/10ビット信号を再生しても良い。

【0158】

[1−4.再生部の内部構成及び動作例(3840×2160/50P−60P/4:2:0/12ビットの例)]

【0159】

上述した第2の再生部39Bは、rビットが12ビットであって、N=4である場合に以下の処理を行う。すなわち、第2の再生部39Bは、デュアルリンクHD−SDIのLinkAであるCH1,3,5,7から再生した4:2:2/12ビット信号の上位10ビットのデータ構造である第1、3,5,7のベーシックストリームを第1および第2のサブイメージの上位10ビットに変換する。また、デュアルリンクHD−SDIのLinkBであるCH2,4,6,8のサンプル番号が偶数であるY信号から再生した4:2:2/12ビット信号のデータ構造である第2,4,6,8のベーシックストリームの同じサンプル番号のY信号を第1及び第2のサブイメージに変換する。また、デュアルリンクHD−SDIのLinkBであるCH2,4,6,8のサンプル番号+1番目のCB′チャンネルから再生したY信号を、第9,11,13,15のベーシックストリームのサンプル番号が偶数である第3及び第4のサブイメージの上位10ビットに変換する。また、デュアルリンクHD−SDIのLinkBであるCH2,4,6,8のサンプル番目のCR′チャンネルから再生したY信号を、第9,11,13,15のベーシックストリームのサンプル番号が奇数である第3及び第4のサブイメージの上位10ビットに変換する。また、デュアルリンクHD−SDIのLinkBであるCH2,4,6,8のサンプル番号が奇数であるY信号から再生したY信号を、第2,4,6,8のベーシックストリームのサンプル番号が奇数であるY信号に変換する。また、4:0:0/12ビット信号のデータ構造である第10,12,14,16のベーシックストリームのY信号の下位2ビットを第3及び第4のサブイメージに変換する。

【0160】

図21は、第2の再生部39Bから入力した16chのベーシックストリームより、3840×2160/50P−60P/4:2:0/12ビット信号を生成する第1の再生部39Cの内部構成例を示す。

第1の再生部39Cは、第1のマッピング部11Cが画素サンプルに行った処理を逆変換するブロックである。

【0161】

第1の再生部39Cは、各部にクロックを供給するクロック供給回路71を備える。クロック供給回路71は、2画素多重制御部72、ライン多重制御部75−1〜75−4、ワード多重制御部77−1〜77−8、及び書込み制御部79−1〜79−16にクロックを供給する。このクロックにより各部が同期して、画素サンプルの読み出し又は書き込みが制御される。

【0162】

また、第1の再生部39Cは、SMPTE435−2に規定されるモードDの16chのHD−SDIと同じデータ構造としたベーシックストリームをそれぞれ記憶するRAM78−1〜78−16を備える。上述したようにベーシックストリームCH1〜16は、それぞれ1920×1080/50I−60I信号を構成する。そして、ベーシックストリームCH1〜16には、デスクランブル・8B/10B・P/S部38から入力されたLinkAであるCH1,CH3,CH5,CH7,…,CH31と、LinkBであるCH2ch4,CH6,CH8,…,CH16の画素サンプルを入れ替えた16chのベーシックストリームが用いられる。

【0163】

書込み制御部79−1〜79−16は、クロック供給回路71から供給されるクロックに合わせて、入力した16chのベーシックストリームCH1〜16をRAM78−1〜78−16に保存する書込み制御を行う。

【0164】

また、第1の再生部39Cは、ワード多重(デインタリーブ)を制御するワード多重制御部77−1〜77−8と、ワード多重制御部77−1〜77−8が多重したデータを書き込むRAM78−1〜78−16を備える。また、第1の再生部39Cは、ライン多重を制御するライン多重制御部75−1〜75−4と、ライン多重制御部75−1〜75−4が多重したデータを書き込むRAM74−1〜74−4を備える。

【0165】

ワード多重制御部77−1〜77−8は、SMPTE435−2に規定され、第1〜第4のサブイメージ毎に対応する4チャンネルのモードDによって定まる10.692Gbpsストリームの映像データ領域から抽出した画素サンプルをワード毎に多重する。

このとき、ワード多重制御部77−1〜77−8は、RAM78−1〜78−16から読み出したベーシックストリームの映像データ領域から抽出した画素サンプルを、ワードを逆変換したライン毎に画素サンプルを多重する。この多重処理は、SMPTE372のFigure9に従って行われる。具体的には、ワード多重制御部77−1〜77−8は、(RAM78−1,78−2)、(RAM78−3,78−4)、…、(RAM78−31,78−16)毎にタイミングを制御して画素サンプルを多重する。そして、ワード多重制御部77−1〜77−8は、生成した1920×1080/50I−60I/4:2:0/12ビット信号をRAM76−1〜76−8に保存する。

【0166】

ライン多重制御部75−1〜75−4は、RAM76−1〜76−8から読み出したインターレース信号をサブイメージ毎に多重してプログレッシブ信号とする。そして、ライン多重制御部75−1〜75−4は、1920×1080/50P−60P/4:2:0/10ビット信号をRAM74−1〜74−4に書き込む。すなわち、RAM74−1〜74−4に保存された信号が第1〜第4のサブイメージを構成する。

【0167】

2画素多重制御部72は、第1〜第4のサブイメージの映像データ領域から抽出した画素サンプルをUHDTV1のクラスイメージにマッピングする。この第1〜第4のサブイメージは、m′×n′が1920×1080であり、a′−b′が50P,59.94P,60Pである。このとき、2画素多重制御部72は、RAM74−1〜74−4から読み出した画素サンプルを2画素毎に以下の処理で多重する。すなわち、第1〜第4のサブイメージから2画素ずつ抽出した画素サンプルを、UHDTV1のクラスイメージに併せて多重する。このクラスイメージは、3840×2160/50P−60P/4:2:0/12ビット信号である。

【0168】

なお、図21では、2画素多重、ライン多重、ワード多重と、を3種類のRAMを用いて3段階で行う例を書いた。しかし、一つのRAMを用いて3840×2160/50P−60P/4:2:0/12ビット信号を再生しても良い。

【0169】

ここで、SMPTE ST 435−1やSMPTE ST 2036−3で規定される2画素サンプル間引き方式を3840×2160/4:2:0/10ビット,12ビット信号に適用した場合に、偶数ラインは4:2:2信号になる。また、奇数ラインは4:0:0信号になることに着目し、以下の処理を行った。すなわち、偶数ラインを多重した4:2:2信号を組み替える4組のLinkA/BのLinkAとし、以下の様にデータを多重し直す。これにより、10ビット信号と12ビット信号の間で、上位10ビットの互換を取ることができる。さらに、SMPTE ST 372に規定される4:4:4(R’G’B’)/10ビット,12ビットと整合のとれるデータ構造にすることで、多重して伝送するHD−SDIや10G−SDIのch数を従来の半分に削減することを可能となる。

【0170】

<第2の実施の形態>

[UHDTV1 3840×4320/100P,119.88P,120P/4:2:0/10ビット,12ビットの例]

【0171】

次に、本開示の第2の実施の形態に係るマッピング部11と再生部39の動作例について、図22〜図26を参照して説明する。

【0172】

[マッピング部の内部構成及び動作例]

次に、本開示の第2の実施の形態に係る第1のマッピング部11Aと第1の再生部39Aの内部構成例及び動作例について、図22〜図26を参照して説明する。ここでは、3840×2160/100P−120P/4:2:0/10ビット,12ビット信号の画素サンプルを間引く方式について説明する。

【0173】

従来の4:2:0/10ビット信号の場合には16chのHD−SDIに画素サンプルを多重して伝送し、4:2:0信号の0にはデフォルト値を多重して10G−SDI モードDの奇数chのみに割り当てて4chの10G−SDIで伝送する方式が知られていた。そして、10ビット信号の場合には200hがデフォルト値として用いられていた。

【0174】

一方、本実施の形態に係る第1のマッピング部11Aは、第1の実施の形態に示した方式で16chのベーシックストリームに多重された3840×2160/100P−120P/4:2:0/10ビット信号からデフォルト値(200h)を捨てる。このデフォルト値は、4:0:0/10ビット信号形式である8chのベーシックストリームに含まれる。そして、中身のデータを8組の4:4:4(R’G’B’又はY′C′BC′R)/10ビットと同じデータ構造のデュアルリンク HD−SDI LinkA/Bに多重し直すことで、2chの10G−SDI モードDで伝送可能とする。

【0175】

同じく、従来の4:2:0/12ビット信号の場合には、図19に示すように16chのHD−SDIに多重して伝送し、4:2:0信号の0にはデフォルト値を多重して、4chの10G−SDIで伝送する方式が知られていた。そして、12ビット信号の場合には800hがデフォルト値として用いられていた。

【0176】

一方、本実施の形態に係る第1のマッピング部11Aは、第1の実施の形態に示した方式で、32chのベーシックストリームに多重された3840×2160/100P−120P/4:2:0/12ビット信号からデフォルト値(800h)を捨てる。このデフォルト値は、4:0:0/12ビット信号形式である16chのHD−SDIに含まれる。そして、中身のデータを8組の4:4:4(R’G’B’又はY′C′BC′R)/12ビットと同じデータ構造のデュアルリンク HD−SDI LinkA/Bに多重し直すことで、2chの10G−SDI モードDで伝送可能とする。

【0177】

図22は、第1のマッピング部11Aの内部構成例を示す。

第1のマッピング部11Aは、各部にクロックを供給するクロック供給回路81と、3840×2160/100P−120Pの映像信号を記憶するRAM83を備える。また、第1のマッピング部11Aは、RAM83から連続する2フレーム単位のクラスイメージに含まれる画素サンプルを、2画素ずつ読み出す2画素間引き(インタリーブ)を制御する2画素間引き制御部82を備える。また、間引かれた2画素サンプルを第1〜第8のサブイメージとして保存するRAM84−1〜84−8を備える。

【0178】

また、第1のマッピング部11Aは、RAM84−1〜84−8に保存される第1〜第8のサブイメージのライン間引きを制御するライン間引き制御部85−1〜85−8を備える。また、第1のマッピング部11Aは、ライン間引き制御部85−1〜85−8が間引いたラインを書き込むRAM86−1〜86−16と、を備える。

【0179】

また、第1のマッピング部11Aは、RAM86−1〜86−16から読出したデータのワード間引きを制御するワード間引き制御部87−1〜87−16を備える。また、第1のマッピング部11Aは、ワード間引き制御部87−1〜87−16が間引いたワードを書き込むRAM88−1〜88−32と、を備える。

また、第1のマッピング部11Aは、RAM88−1〜88−32から読出したワードを32チャンネルのベーシックストリームとして出力する読出し制御部89−1〜89−32を備える。

【0180】

なお、図22には、ベーシックストリーム1,2を生成する処理ブロックを記載したが、ベーシックストリーム3〜32を生成するブロックも同様の構成例としているため、図示と詳細な説明を省略する。

【0181】

次に、第1のマッピング部11Aの動作例を説明する。

始めに、クロック供給回路81は、2画素間引き制御部82ライン間引き制御部85−1〜85−8、ワード間引き制御部87−1〜87−16、及び読出し制御部89−1〜89−32にクロックを供給する。これらのクロックは、画素サンプルの読み出し又は書き込みに用いられ、これらのクロックにより各部が同期する。

【0182】

不図示のイメージセンサから入力する1フレームの画素数が最大3840×2160である、HD−SDIフォーマットで規定される画素数を越えるUHDTV1のクラスイメージによって規定される映像信号は、RAM83に保存される。UHDTV1のクラスイメージは、3840×2160/100P−120P/4:2:0/10ビット,12ビットの映像信号を表す。本例では、UHDTV1のクラスイメージから2画素毎に間引かれた画素サンプルが第1〜第8のサブイメージの映像データ領域にマッピングされることとなる。

【0183】

2画素間引き制御部82は、UHDTV1のクラスイメージから連続する2フレーム単位で2画素サンプル毎に2フレーム単位で間引く。そして、m′×n′が1920×1080であり、a′−b′が50P,59.94P,60Pである第1〜第8のサブイメージの映像データ領域に画素サンプルをマッピングする。1920×1080/50P−60Pは、SMPTE274で規定される。このとき、2画素間引き制御部82は、第1のクラスイメージの第0ラインの各画素サンプルを第1及び第2のサブイメージの映像データ領域にマッピングし、第1のクラスイメージの第1ラインの各画素サンプルを第3及び第4のサブイメージの映像データ領域にマッピングする。また、第1のクラスイメージの第2ラインの各画素サンプルを第5及び第6のサブイメージの映像データ領域にマッピングし、第1のクラスイメージの第3ラインの各画素サンプルを第7及び第8のサブイメージの映像データ領域にマッピングする。さらに、第2のクラスイメージの第0ラインの各画素サンプルを第1及び第2のサブイメージの映像データ領域にマッピングし、第2のクラスイメージの第1ラインの各画素サンプルを第3及び第4のサブイメージの映像データ領域にマッピングする。また、第2のクラスイメージの第2ラインの各画素サンプルを第5及び第6のサブイメージの映像データ領域にマッピングし、第2のクラスイメージの第3ラインの各画素サンプルを第7及び第8のサブイメージの映像データ領域にマッピングする。

【0184】

次に、ライン間引き制御部85−1〜85−8は、プログレッシブ信号をインターレース信号に変換する。具体的には、ライン間引き制御部85−1〜85−8は、RAM84−1〜84−8から第1〜第8のサブイメージの映像データ領域にマッピングされた画素サンプルを読出す。このとき、ライン間引き制御部85−1〜85−8は、1つのサブイメージを、2chの1920×1080/50I−60I/4:2:0/10ビット,12ビット信号に変換する。そして、第1〜第8のサブイメージの映像データ領域から1ラインおきに間引いてインターレース信号とした1920×1080/50I−60I信号をRAM84−1〜84−8に書き込む。

【0185】

次に、ワード間引き制御部87−1〜87−16は、ライン毎に間引かれた画素サンプルをワード毎に間引いて、SMPTE435−1に規定されるHD−SDIの映像データ領域にマッピングする。このとき、ワード間引き制御部87−1〜87−16は、SMPTE435−1に規定され、第1〜第8のサブイメージ毎に対応する4チャンネルのモードDによって定まる10.692Gbpsストリームの映像データ領域に画素サンプルを多重する。つまり、ワード間引き制御部87−1〜87−16は、1920×1080/50I−60I/4:2:0/10ビット,12ビット信号を、32本のベーシックストリームに変換する。そして、第1〜第8のサブイメージのそれぞれに対し、SMPTE435−1に規定される4本ずつのHD−SDIの映像データ領域にマッピングする。

【0186】

具体的には、ワード間引き制御部87−1〜87−16は、RAM84−1〜84−8からSMPTE372のFigure4,6,7,8,9と同じ方式でワード毎に間引いて画素サンプルを読出す。そして、ワード間引き制御部87−1〜87−16は、読出した画素サンプルを、それぞれ2chの1920×1080/50I−60I信号に変換して、RAM88−1〜88−32に保存する。

【0187】

そして、読出し制御部89−1〜89−32は、RAM88−1〜88−32から読出した32本のベーシックストリームの伝送ストリームを出力する。

具体的には、読出し制御部89−1〜89−32は、クロック供給回路81から供給された基準クロックでRAM88−1〜88−32から画素サンプルを読出す。そして、2本のLinkA/Bを16対で構成した32チャンネルのベーシックストリーム1〜32を、後続の第2のマッピング部11Bに出力する。

【0188】

なお、本例では、2画素間引き、ライン間引き、及びワード間引きを行うため、3種類のメモリ(RAM84−1〜84−8、RAM86−1〜86−16、RAM88−1〜88−32)を用いて、3段階の間引き処理を行っている。しかし、一つのメモリに2画素間引き、ライン間引き、及びワード間引きして得たデータを32chのHD−SDIとして出力しても良い。

【0189】

次に、第1のマッピング部11Aが画素サンプルをマッピングする工程の詳細な処理例を説明する。

図23は、第1のマッピング部11Aが、UHDTV1クラスイメージの連続する第1及び第2フレームに含まれる画素サンプルを第1〜第8のサブイメージにマッピングし、さらに32chのベーシックストリームに画素サンプルをマッピングする例を示す図である。

【0190】

2画素間引き制御部21は、1フレーム(1画面)を8分割する。これにより、3840×2160/100P−120P/4:2:0/10ビット、12ビット信号を、8chの1920×1080/50P−60P/4:2:0/10ビット,12ビット信号にマッピングする。

【0191】

このとき、1フレーム(1画面)が3840×2160/100P−120P/4:2:0/10ビット,12ビット信号である第1フレームのUHDTV1クラスイメージからライン方向に2画素毎に画素サンプルを間引く。そして、2画素毎に間引いたそれぞれの信号を、8chの1920×1080/50P−60P/4:2:0/10ビット,12ビット信号の前半部分(有効領域第1〜540ライン)にマッピングする。

【0192】

その後、第1のマッピング部11Aは、第2フレームのUHDTV1クラスイメージからライン方向に2画素毎に画素サンプルを間引く。そして、2画素毎に間引いたそれぞれの信号を、8chの1920×1080/50P−60P/4:2:0/10ビット,12ビット信号の後半部分(有効領域第541〜1080ライン)にマッピングする。そして、HDイメージフォーマットの映像データ領域である1920サンプルにマッピングさせた、第1〜第8のサブイメージを作成する。以下の説明で、第1フレームのUHDTV1クラスイメージを「第1のクラスイメージ」と呼び、第2フレームのUHDTV1クラスイメージを「第2のクラスイメージ」と呼ぶ。

【0193】

次に、ライン間引き制御部85−1〜85−8がライン間引きを行い、ワード間引き制御部87−1〜87−16がワード間引きを行うことによって、32chの1920×1080/23.98P−30P/4:2:2/10ビット信号を生成する。そして、読出し制御部89−1〜89−32は、ベーシックストリーム1〜32を読み出して第2のマッピング部11Bに出力する。

【0194】

第1のマッピング部11Aが出力するベーシックストリームCH1〜CH32は、16chずつ2組の第2のマッピング部11B−1,11B−2に入力する。第2のマッピング部11B−1,11B−2は、いずれも上述した第2のマッピング部11Bと同様の構成としてあり、同じ動作を行うため詳細な説明を省略する。そして、第2のマッピング部11Bは、第1の実施の形態の図4に示した方式で入力したベーシックストリームを8chずつ、合計8chのHD−SDIにまとめて伝送することができる。

【0195】

次に、第1のマッピング部11A内の各処理ブロックが画素サンプルをマッピングする際の詳細な処理例を説明する。

図24は、2画素間引き制御部82が第1及び第2のクラスイメージから画素サンプルを2画素ずつ間引いて第1〜第8のサブイメージへマッピングする処理の例を示す。

【0196】

第1のマッピング部11Aは、UHDTV1クラスイメージとして定義される3840×2160/100P−120P/4:2:0/10ビット,12ビット信号の画素サンプルを第1〜第8のサブイメージにマッピングする。このとき、第1のマッピング部11Aは、UHDTV1クラスイメージの同一ライン上で隣り合う2つの画素サンプルを2画素サンプルずつ間引いて第1〜第8のサブイメージにマッピングする。このマッピング処理は、第1のマッピング部11Aが備える2画素間引き制御部82の制御によって行われる。

【0197】

2画素間引き制御部82は、3840×2160/100P−120P/4:2:0/10ビット,12ビット信号を2フレーム単位でライン方向に2画素サンプル毎に間引いて第1〜第8のサブイメージの映像データ領域に多重する。第1〜第8のサブイメージは、8chの1920×1080/50P−60P/4:2:0/10ビット,12ビットで規定される。なお、3840×2160/100P−120P/4:2:0/10ビット,12ビット信号は、S2036−1で規定される3840×2160/50P−60P/4:2:0/10ビット,12ビット信号に対してフレームレートを倍とした信号である。1920×1080/50P−60Pは、SMPTE274Mで定義されている。3840×2160/100P−120P/4:2:0/10ビット,12ビット信号の禁止コードなどディジタル信号形式は3840×2160/50P−60Pと同じである。

【0198】

ここで、1フレームの画素数がHD−SDIフォーマットで規定される画素数を越えるUHDTV1のクラスイメージは、以下のように規定される。すなわち、m×n(mサンプル、nラインを示すm,nは、正の整数)/a−b(a,bは、プログレッシブ信号のフレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/10ビット,12ビット信号で規定される。本例では、UHDTV1のクラスイメージにおける、m×nが3840×2160であり、a−bが100P−120Pであり、r:g:bが4:2:0である。UHDTV1クラスイメージには、0ラインから2159ラインにわたって画素サンプルが格納されている。

【0199】

そして、UHDTV1のクラスイメージには、連続する第0ライン、第1ライン、第2ライン、及び第3ラインによってラインが定められる。2画素間引き制御部82は、連続する第1及び第2のUHDTV1クラスイメージ内でそれぞれ連続する4本のラインの1ライン毎に同一ラインで隣り合う2つの画素サンプルを間引く。そして、m′×n′/a′−b′/r′:g′:b′/10ビット,12ビット信号で規定される第1〜第8のサブイメージにマッピングする。ここで、m′サンプル、n′ラインを示すm′,n′は、正の整数であり、a′,b′は、プログレッシブ信号のフレームレートであり、r′,g′,b′は、所定の信号伝送方式である場合における信号比率である。

【0200】

この場合に、2画素間引き制御部21は、m′×n′が1920×1080であり、a′−b′が50P−60Pである第1〜第8のサブイメージの映像データ領域に画素サンプルをマッピングする。このとき、第1のクラスイメージの第0ラインの各画素サンプルを第1及び第2のサブイメージの映像データ領域にマッピングし、第1のクラスイメージの第1ラインの各画素サンプルを第3及び第4のサブイメージの映像データ領域にマッピングする。また、第1のクラスイメージの第2ラインの各画素サンプルを第5及び第6のサブイメージの映像データ領域にマッピングし、第1のクラスイメージの第3ラインの各画素サンプルを第7及び第8のサブイメージの映像データ領域にマッピングする。さらに、第2のクラスイメージの第0ラインの各画素サンプルを第1及び第2のサブイメージの映像データ領域にマッピングし、第2のクラスイメージの第1ラインの各画素サンプルを第3及び第4のサブイメージの映像データ領域にマッピングする。そして、第2のクラスイメージの第2ラインの各画素サンプルを第5及び第6のサブイメージの映像データ領域にマッピングし、第2のクラスイメージの第3ラインの各画素サンプルを第7及び第8のサブイメージの映像データ領域にマッピングする。

【0201】

具体的には、第1のクラスイメージの各ラインから抽出される画素サンプルは以下のように定義される。以下、「第sサンプル」として示される“s”は、第1〜第8のサブイメージのうち、第sのサブイメージに第sサンプルとして規定した画素サンプルがマッピングされることを表している。

(1)第0ライン:第1サンプル、第1サンプル、第2サンプル、第2サンプル、第1サンプル、第1サンプル、第2サンプル、第2サンプル、・・・

(2)第1ライン:第3サンプル、第3サンプル、第4サンプル、第4サンプル、第3サンプル、第3サンプル、第4サンプル、第4サンプル、・・・

(3)第2ライン:第5サンプル、第5サンプル、第6サンプル、第6サンプル、第5サンプル、第5サンプル、第6サンプル、第6サンプル、・・・

(4)第3ライン:第7サンプル、第7サンプル、第8サンプル、第8サンプル、第7サンプル、第7サンプル、第8サンプル、第8サンプル、・・・

(5)第4ライン:第1サンプル、第1サンプル、第2サンプル、第2サンプル、第1サンプル、第1サンプル、第2サンプル、第2サンプル、・・・

(6)第5ライン:第3サンプル、第3サンプル、第4サンプル、第4サンプル、第3サンプル、第3サンプル、第4サンプル、第4サンプル、・・・

(7)第6ライン:第5サンプル、第5サンプル、第6サンプル、第6サンプル、第5サンプル、第5サンプル、第6サンプル、第6サンプル、・・・

(8)第7ライン:第7サンプル、第7サンプル、第8サンプル、第8サンプル、第7サンプル、第7サンプル、第8サンプル、第8サンプル、・・・

.

.

.

【0202】

このように、第1のクラスイメージに含まれる画素を間引いてマッピングする処理が終わると、引き続き第2のクラスイメージに含まれる画素を間引いてマッピングする処理が開始される。このとき、第1のクラスイメージと同様に、第2のクラスイメージにおける、第0ラインにおける隣り合う2つの画素サンプルをそれぞれ第1及び第2のサブイメージの映像データ領域における後半部分のラインにマッピングする。同様に、第1ライン〜第7ラインにおける隣り合う2つの画素サンプルを、それぞれ第3及び第4のサブイメージ、第5及び第6のサブイメージ、第7及び第8のサブイメージの映像データ領域における後半部分のラインにマッピングする。このとき、各画素サンプルがSMPTE274で定義される8chの1920×1080/50P−60P/4:2:2あるいは4:0:0/10ビット,12ビットにマッピングされる。

【0203】

2画素が間引かれ、第1〜第8のサブイメージにマッピングされた画素サンプル数は、3840÷2=1920サンプルである。連続する2フレーム毎に2画素が間引かれた後のライン数は、2×2160÷4=1080ラインである。このため、1920×1080の映像データ領域と、第1及び第2のクラスイメージから間引かれて多重される画素サンプル数及びライン数が一致する。

【0204】

2フレーム単位で2画素サンプル間引き方式で画素サンプルがマッピングされた第1〜第8のサブイメージのうち、第1,2,5,6のサブイメージは4:2:2信号となり、第3,4,7,8のサブイメージは4:0:0信号となる。各サブイメージの“0”の信号成分にはデフォルト値(10ビット信号の場合には200h、12ビット信号の場合には800h)が多重されている。第1のマッピング部11Aは、4:2:0信号の0にはCchのデフォルト値である200h(10ビットシステム)、800h(12ビットシステム)をマッピングすることで、4:2:0を4:2:2と同等に扱っている。そして、第1〜第8のサブイメージは、それぞれRAM84−1〜84−8に保存される。

【0205】

図25は、第1〜第8のサブイメージをライン間引きした後、ワード間引きをすることによって、SMPTE372Mの規定に従ってLinkA又はLinkBに分割する処理の例を示す。

【0206】

上述したように、ライン間引き制御部85−1〜85−8は、画素サンプルがマッピングされた第1〜第8のサブイメージのそれぞれの一ラインおきに画素サンプルを間引いてインターレース信号に変換する。

【0207】

SMPTE435は、10Gインターフェースの規格である。この規格は、複数チャンネルのHD−SDI信号を、2画素(40ビット)単位で8B/10Bエンコーディングして50ビットに変換し、チャンネル毎に多重することを定める。さらに、この規格はビットレート10.692Gbpsまたは10.692Gbps/1.001(以下単に10.692Gbpsと記載する)でシリアル伝送することを定めている。4k×2k信号をHD−SDI信号にマッピングする技術は、SMPTE435 Part1の6.4 Octa Link 1.5Gbps ClassのFigure3及びFigure4に示される。

【0208】

そして、画素サンプルがマッピングされた8chの1920×1080/50P−60P/4:2:0/10ビット,12ビット信号で設定される第1〜第8のサブイメージから、SMPTE435−1のFigure2に定義される方式でライン間引きが行われる。本例では、ライン間引き制御部85−1〜85−8は、第1〜第8のサブイメージを形成する1920×1080/50P−60P信号をライン毎に間引いて2chのインターレース信号(1920×1080/50I−60I信号)を生成する。1920×1080/50I−60I/4:2:0/10ビット,12ビット信号は、SMPTE274Mで定義される信号である。

【0209】

その後、ワード間引き制御部87−1〜87−16は、ライン間引きされた信号が4:4:4の10ビット、12ビットあるいは4:2:2の12ビット信号である場合には更にワード間引きした後、ベーシックストリームを第2のマッピング部11Bに出力する。ここで、従来は、4:4:4信号あるいは4:2:2/12ビット信号の場合には更にワード間引きして、それぞれ4chの1.5Gb/s HD−SDIで伝送する。従って、3840×2160/100P−120P /4:4:4,4:2:2,4:2:0/10ビット,12ビット信号は、図25に示すように合計32chのHD−SDIで伝送される。ただし、4:2:2,4:2:0/10ビット信号の場合には16chのHD−SDIで伝送される。

このように32chのHD−SDIにマッピングされた3840×2160/100P−120P/4:2:0/10ビット,12ビット信号を、4chの10G−SDI モードDに多重して伝送する。(4:2:2,4:2:0の場合にはLinkBは使用せず、CH1,3,5,7のみ使用する。)

【0210】

一方、本実施の形態に係る第2のマッピング部11Bは、ベーシックストリームのデータを置き換える。これにより、4:2:2/10ビット信号形式のHD−SDIと、4:0:0/10ビット信号D形式の8chのHD−SDIを2chの10GbpsのHD−SDI モードDで伝送することができる。同様に、4:2:2/12ビット信号形式のHD−SDIと、4:0:0/12ビット信号D形式の8chのHD−SDIを2chの10G−SDI モードDで伝送することができる。

【0211】

図26は、第1の再生部39Aの内部構成例を示す。

第1の再生部39Aは、第1のマッピング部11Aが画素サンプルに行った処理を逆変換するブロックである。

【0212】

2組の第2の再生部39B−1,39B−2は、合計32本のHD−SDIが入力すると、第1の実施の形態の図19に示した方式でそれぞれベーシックストリームCH1〜CH32に変換して第1の再生部39Aに出力する。

【0213】

第1の再生部39Aは、各部にクロックを供給するクロック供給回路91を備える。クロック供給回路91は、2画素多重制御部92、ライン多重制御部95−1〜95−8、ワード多重制御部97−1〜97−16、及び書込み制御部99−1〜99−32にクロックを供給する。このクロックにより各部が同期して、画素サンプルの読み出し又は書き込みが制御される。

【0214】

また、第1の再生部39Aは、SMPTE435−2に規定されるモードDの32本のベーシックストリーム1〜32をそれぞれ記憶するRAM98−1〜98−32を備える。上述したようにベーシックストリーム1〜32は、それぞれ1920×1080/50I−60I信号を構成する。そして、ベーシックストリームI1〜32には、デスクランブル・8B/10B・P/S部38から入力されたLinkAであるCH1,CH3,CH5,CH7,…,CH31と、LinkBであるCH2,CH4,CH6,CH8,…,CH32が用いられる。

【0215】

書込み制御部99−1〜99−32は、クロック供給回路91から供給されるクロックに合わせて、入力した32本のベーシックストリーム1〜32をRAM98−1〜98−32に保存する書込み制御を行う。

【0216】

また、第1の再生部39Aは、ワード多重(デインタリーブ)を制御するワード多重制御部97−1〜97−16と、ワード多重制御部97−1〜97−16が多重したデータを書き込むRAM96−1〜96−16を備える。また、第1の再生部39Aは、ライン多重を制御するライン多重制御部95−1〜95−8と、ライン多重制御部95−1〜95−8が多重したデータを書き込むRAM94−1〜94−8を備える。

【0217】

ワード多重制御部97−1〜97−16は、SMPTE435−2に規定され、第1〜第8のサブイメージ毎に対応する4チャンネルのモードDによって定まる10.692Gbpsストリームの映像データ領域から抽出した画素サンプルをライン毎に多重する。このとき、ワード多重制御部97−1〜97−16は、RAM98−1〜98−32から読み出したベーシックストリームの映像データ領域から抽出した画素サンプルを、ワードを逆変換したライン毎に画素サンプルを多重する。この多重処理は、SMPTE372のFigure9に従って行われる。具体的には、ワード多重制御部97−1〜97−16は、(RAM98−1,98−2)、(RAM98−3,98−4)、…、(RAM98−31,98−32)毎にタイミングを制御して画素サンプルを多重する。そして、ワード多重制御部97−1〜97−16は、生成した1920×1080/50I−60I/4:2:0/10ビット,12ビット信号をRAM96−1〜96−16に保存する。

【0218】

ライン多重制御部95−1〜95−8は、RAM96−1〜96−16から読み出したライン毎にワード多重された画素サンプルをサブイメージ毎に多重してプログレッシブ信号とする。そして、ライン多重制御部95−1〜95−8は、1920×1080/50P−60P/4:2:0/10ビット,12ビット信号を生成し、RAM94−1〜94−8に保存する。RAM94−1〜94−8に保存された信号が第1〜第8のサブイメージを構成する。

【0219】

2画素多重制御部92は、第1〜第8のサブイメージの映像データ領域から抽出した画素サンプルをUHDTV1のクラスイメージにマッピングする。この第1〜第8のサブイメージは、m′×n′が1920×1080であり、a′−b′が50P−60Pである。このとき、2画素多重制御部92は、RAM94−1〜94−8から読み出した画素サンプルを2画素毎に以下の処理で多重する。そして、第1のサブイメージと第2のサブイメージの前半部分から2画素ずつ抽出した画素サンプルを、UHDTV1のクラスイメージに併せて多重する。このクラスイメージは、3840×2160/100P−120P/4:2:0/10ビット,12ビット信号である。

【0220】

そして、2画素多重制御部92は、UHDTV1クラスイメージが連続する第0ライン、第1ライン、第2ライン、及び第3ラインによってラインが定められ、かつ、連続する第1及び第2のクラスイメージに対して、以下の処理を行って画素サンプルを多重する。すなわち、第1及び第2のサブイメージの映像データ領域から抽出した各画素サンプルを第1のクラスイメージの第0ラインに隣り合わせて多重する。次に、第3及び第4のサブイメージの映像データ領域から抽出した各画素サンプルを第1のクラスイメージの第1ラインに隣り合わせて多重する。次に、第5及び第6のサブイメージの映像データ領域から抽出した各画素サンプルを第1のクラスイメージの第2ラインに隣り合わせて多重する。次に、第7及び第8のサブイメージの映像データ領域から抽出した各画素サンプルを第1のクラスイメージの第3ラインに隣り合わせて多重する。そして、RAM93には、UHDTV1クラスイメージで規定される第1のフレームに3840×2160/100P−120P信号が保存され、適宜、この信号が再生される。

【0221】

さらに、2画素多重制御部92は、第1及び第2のサブイメージの映像データ領域から抽出した各画素サンプルを第2のクラスイメージの第0ラインに隣り合わせて多重する。次に、第3及び第4のサブイメージの映像データ領域から抽出した各画素サンプルを第2のクラスイメージの第1ラインに隣り合わせて多重する。次に、第5及び第6のサブイメージの映像データ領域から抽出した各画素サンプルを第2のクラスイメージの第2ラインに隣り合わせて多重する。次に、第7及び第8のサブイメージの映像データ領域から抽出した各画素サンプルを第2のクラスイメージの第3ラインに隣り合わせて多重する。そして、RAM93には、UHDTV1クラスイメージで規定される第2のフレームに3840×2160/100P−120P信号が保存され、適宜、この信号が再生される。

【0222】

なお、図26では、2画素多重、ライン多重、ワード多重と、を3種類のRAMを用いて3段階で行う例を書いた。しかし、一つのRAMを用いて3840×2160/100P−120P/4:2:0/10ビット,12ビット信号を再生しても良い。

【0223】

以上説明した第2の実施の形態に係る放送用カメラ1の第1のマッピング部11Aは、UHDTV1クラスイメージで規定される画素数の大きい3840×2160/100P−120P信号を、第1〜第8のサブイメージにマッピングする。このマッピング処理は、UHDTV1クラスイメージの連続する2フレーム毎に2画素サンプル単位で間引いて行われる。その後、ライン間引き、ワード間引きを行ってベーシックストリームを出力する。そして、第2のマッピング部11B−1,11B−2は、ベーシックストリームのデータを置き換えて、HD−SDI モードDにより伝送する。この間引き処理は、信号をマッピングする際に必要となるメモリを最小にする方式であると共に、メモリ量が最小になることから信号の伝送遅延も最小に抑えることができる。

【0224】

一方、CCU2の第2の再生部39B−1,39B−2は、受信したHD−SDI モードDのデータを置き換えて32chのベーシックストリームを出力する。第1の再生部39Aは、32chのベーシックストリームを受信した後、ワード多重、ライン多重を行って第1〜第8のサブイメージに画素サンプルを多重する。その後、第1〜第8のサブイメージから抽出した2画素サンプルをUHDTV1クラスイメージで規定される画素数の大きい3840×2160に多重する。このようにして、従来のHD−SDIフォーマットを用いて、UHDTV1クラスイメージで規定される画素サンプルを送受信することが可能となる。

【0225】

<第3の実施の形態>

[UHDTV2 7680×4320/50P,59.94P,60P/4:2:0/10ビット,12ビットの例]

【0226】

次に、本開示の第3の実施の形態に係る第1のマッピング部11Aと第1の再生部39Aの動作例について、図27〜図29を参照して説明する。

【0227】

ここでは、7680×4320/50P−60P/4:2:0/10ビット,12ビット信号の画素サンプルを間引く方式について説明する。

【0228】

図27は、第1のマッピング部11AがUHDTV2クラスイメージに含まれる画素サンプルをUHDTV1クラスイメージにマッピングする処理イメージを示す。

【0229】

本例では、第1のマッピング部11AにUHDTV2クラスイメージとして規定される7680×4320/50P−60P/4:2:0/10ビット,12ビット信号が入力する。7680×4320/50P−60P/4:2:0/10ビット,12ビット信号は、S2036−1で規定される。

【0230】

第1のマッピング部11Aは、始めに7680×4320/50P−60P/4:2:0/10ビット,12ビット信号を、UHDTV1に規定するクラスイメージにマッピングする。このクラスイメージは、3840×2160/50P−60P/4:2:0/10ビット,12ビット信号である。

【0231】

第1のマッピング部11Aは、S2036−3に規定されているように、2サンプル毎に2ライン単位でUHDTV2クラスイメージからUHDTV1クラスイメージに画素サンプルをマッピングする。つまり、7680×4320/50P−60P/4:2:0/10ビット,12ビット信号をライン方向に2画素サンプル毎に2ライン単位で間引く。そして、4chの3840×2160/50P−60P/4:2:0/10ビット,12ビットにマッピングする。

【0232】

従来のマッピング方式では、4chの3840×2160/50P−60P/4:4:4,4:2:2,4:2:0/10ビット,12ビット信号のうち、4:2:0/10ビット信号は、0信号成分にデフォルト値を割り当てていた。なお、10ビット信号の場合には200h、12ビット信号の場合には800hを割り当てられる。これにより、8chのHD−SDIにマッピングして出力され、10G−SDIの奇数chに入力することで2chの10G モードDで伝送できていた。また、4:2:0/12ビット信号は、同様に0信号成分にデフォルト値を割り当てることで16chのHD−SDIにマッピングして出力されるので、2chの10G モードDで伝送できる。従って、7680×4320/50P−60P/4:2:0/10ビット,12ビット信号は、合計8chの10G モードDで伝送可能であった。

【0233】

一方、第3の実施の形態に係る2画素サンプル間引き方式で間引いた後の第1〜第4のUHDTV1クラスイメージの4:2:0信号は、図13のUHDTV1 第1及び第2のクラスイメージは4:2:2信号となる。UHDTV1 第3の第4のクラスイメージは4:0:0信号となり、0の信号成分にはデフォルト値(10ビットの場合には200h、12ビットの場合には800h)が多重されている。

【0234】

7680×4320/50P−60P/4:2:0/10ビット信号の場合には、2画素サンプル間引き方式でマッピングされたそれぞれの第1〜第4のUHDTV1クラスイメージは、第2の実施の形態に示した方式で8chのHD−SDIに多重される。そして、4:2:2信号形式を持つ第1のUHDTV1クラスイメージと4:0:0信号形式を持つ第3のUHDTV1クラスイメージを多重したそれぞれの8chのHD−SDIを、第1の実施の形態の図11,図12を参照して説明した方式で変換する。これにより、4:4:4(R‘G’B‘あるいはY′C′BC′R)/10ビットと同じデータ構造を持つ8組のデュアルリンク HD−SDI LinkA/Bに変換されるため、2chの10G−SDI モードDで伝送することができる。同様に、4:2:2信号形式を持つ第2のUHDTV1クラスイメージと4:0:0信号形式を持つ第4のUHDTV1クラスイメージを多重したそれぞれの8chのHD−SDIを変換する。このとき、第1の実施の形態の図15、図16を参照して説明した方式で4:4:4(R’G’B’又はY′Cb’Cr’)/10ビットと同じデータ構造を持つ8組のデュアルリンク HD−SDI LinkA/Bに変換する。これにより、2chの10G−SDI モードDで伝送することができるので合計4chの10G−SDI モードDで伝送でき、従来方式と比べて伝送容量を半分にすることが可能である。

【0235】

7680×4320/50P−60P/4:2:0/12ビット信号の場合には、2画素サンプル間引き方式でマッピングされたそれぞれの第1〜第4のUHDTV1クラスイメージは、第2の実施の形態に示した方式で16chのHD−SDIに多重される。4:2:2信号形式を持つ第1のUHDTV1クラスイメージと4:0:0信号形式を持つ第3のUHDTV1クラスイメージを多重したそれぞれの16chのHD−SDIを、第1の実施の形態の図15、図16を参照して説明した方式で変換する。これにより、4:4:4(R‘G’B‘あるいはY′C′BC′R)/12ビットと同じデータ構造を持つ8組のデュアルリンク HD−SDI LinkA/Bに変換されるため、2chの10G−SDI モードDで伝送することができる。同様に、4:2:2信号形式を持つ第2のUHDTV1クラスイメージと4:0:0信号形式を持つ第4のUHDTV1クラスイメージを多重したそれぞれの8chのHD−SDIを変換する。このとき、第1の実施の形態の図15、図16を参照して説明した方式で4:4:4(R’G’B’又はY′C′BC′R)/12ビットと同じデータ構造を持つ8組のデュアルリンク HD−SDI LinkA/Bに変換する。これにより、2chの10G−SDI モードDで伝送することができるので合計4chの10G−SDI モードDで伝送でき、従来方式と比べて伝送容量を半分にすることが可能である。

【0236】

図28は、第1のマッピング部11Aの内部構成例を示す。

第1のマッピング部11Aは、各部にクロックを供給するクロック供給回路61と、7680×4320/50P−60Pの映像信号を記憶するRAM103を備える。また、第1のマッピング部11Aは、RAM103に記憶された7680×4320/50P−60Pの映像信号から2画素ずつ画素サンプルを読み出す2画素間引き(インタリーブ)を制御する第2の2画素間引き制御部102を備える。また、2画素間引きされた画素サンプルは、UHDTV1に規定する3840×2160/50P−60P/4:2:0/10ビット,12ビット信号である第1〜第4のクラスイメージとして、RAM104−1〜104−4に保存される。

【0237】

また、第1のマッピング部11Aは、RAM104−1〜104−4から読出した第1〜第4のクラスイメージより、連続する2フレーム毎に2画素ずつ画素サンプルを読み出す2画素間引きを制御する第1の2画素間引き制御部105−1〜105−4を備える。第1の2画素間引き制御部105−1〜105−4が画素サンプルをサブイメージにマッピングする動作は、上述した第2の実施の形態に係る2画素間引き制御部122の動作と同様である。2画素間引きされた画素サンプルは、第1〜第4のクラスイメージ毎に第1〜第8のサブイメージとして、RAM106−1〜106−32に保存される。

【0238】

また、第1のマッピング部11Aは、RAM106−1〜106−32から読出したデータをライン間引きするライン間引き制御部107−1〜107−32を備える。また、ライン間引き制御部107−1〜107−32が間引いたデータを書き込むRAM108−1〜108−64を備える。

【0239】

また、第1のマッピング部11Aは、RAM108−1〜108−64から読出したデータのワード間引きを制御するワード間引き制御部109−1〜109−64を備える。また、第1のマッピング部11Aは、ワード間引き制御部109−1〜109−64が間引いたデータを書き込むRAM110−1〜110−64と、を備える。また、第1のマッピング部11Aは、RAM110−1〜110−64から読出したデータの画素サンプルを64チャンネルのベーシックストリームとして出力する読み出し制御部111−1〜111−64を備える。

【0240】

なお、図28には、ベーシックストリームCH1を生成するブロックについて記載したが、ベーシックストリームCH2〜CH64を生成するブロックも同様の構成例としているため、図示と詳細な説明を省略する。

【0241】

次に、第1のマッピング部11Aの動作例を説明する。

クロック供給回路61は、第2の2画素間引き制御部102、第1の2画素間引き制御部105−1,105−4,ライン間引き制御部107−1〜107−32、ワード間引き制御部109−1〜109−64、及び読出し制御部111−1〜111−64にクロックを供給する。このクロックは、画素サンプルの読み出し又は書き込みに用いられ、このクロックにより各部が同期する。

【0242】

不図示のイメージセンサから入力するUHDTV2の7680×4320/50P−60P/4:2:0/10ビット,12ビット信号で規定されるUHDTV2のクラスイメージは、RAM103に保存される。第2の2画素間引き制御部102は、7680×4320/50P,59.94P,60P/4:2:0/10ビット,12ビットであるUHDTV2のクラスイメージから、同一ラインで隣り合う2つの画素サンプルを間引く。そして、m×nが3840×2160であり、a−bが50P,59.94P,60Pである第1〜第4のUHDTV1のクラスイメージに画素サンプルをマッピングする。

【0243】

具体的には、第2の2画素間引き制御部102は、連続する4本のラインの1ライン毎に同一ラインで隣り合う2つの画素サンプルを間引いた画素サンプルを第1〜第4のUHDTV1のクラスイメージにマッピングする。このとき、UHDTV2のクラスイメージの第0ラインから1ラインおきに含まれる各画素サンプルを、ライン毎に2つの画素サンプルおきに第1のUHDTV1のクラスイメージの映像データ領域における同一ラインにマッピングする。また、UHDTV2のクラスイメージの第0ラインから1ラインおきに含まれる各画素サンプルであって、第1のUHDTV1のクラスイメージにマッピングされた画素サンプルとは異なる画素サンプルをマッピングする。このとき、2つの画素サンプルおきに第2のUHDTV1のクラスイメージの映像データ領域における同一ラインにマッピングする。さらに、UHDTV2のクラスイメージの第1ラインから1ラインおきに含まれる各画素サンプルを、ライン毎に2つの画素サンプルおきに第3のUHDTV1のクラスイメージの映像データ領域における同一ラインにマッピングする。また、UHDTV2のクラスイメージの第1ラインから1ラインおきに含まれる各画素サンプルをマッピングする。このとき、第3のUHDTV1のクラスイメージにマッピングされた画素サンプルとは異なる画素サンプルを、2つの画素サンプルおきに第4のUHDTV1のクラスイメージの映像データ領域における同一ラインにマッピングする。そして、このマッピング処理を、UHDTV2クラスイメージの画素サンプルを全て抽出し終わるまで繰り返す。

【0244】

以降の第1の2画素間引き制御部105−1〜105−4が第1〜第8のサブイメージに画素サンプルをマッピングする処理と、ライン間引き、ワード間引きの処理は、第2の実施の形態に係る画素サンプルの間引き処理と同様に行われるため、詳細な説明を省略する。

【0245】

第1のマッピング部11Aが出力するベーシックストリームCH1〜CH64は、16chずつ8組の第2のマッピング部11Bに入力する。そして、第2のマッピング部11Bは、第1の実施の形態の図4に示した方式で8chずつ、合計64本のHD−SDIにまとめて伝送することができる。

【0246】

図29は、第1の再生部39Aの内部構成例を示す。

第1の再生部39Aは、第1のマッピング部11Aが画素サンプルに行った処理を逆変換するブロックである。

【0247】

8組の第2の再生部39Bは、合計64本のHD−SDIが入力すると、第1の実施の形態の図19に示した方式でそれぞれベーシックストリームCH1〜CH64に変換して第1の再生部39Aに出力する。

【0248】

第1の再生部39Aは、各部にクロックを供給するクロック供給回路121を備える。また、第1の再生部39Aは、1920×1080/50I−60I信号を構成する64本のベーシックストリームCH1〜64をそれぞれ記憶するRAM130−1〜130−64を備える。ベーシックストリームCH1〜64は、デスクランブル・8B/10B・P/S部38から入力されたLinkAであるCH1,CH3,CH5,CH7,…,CH127と、LinkBであるCH2,CH4,CH6,CH8,…,CH64に相当する。書込み制御部131−1〜131−64は、クロック供給回路121から供給されるクロックに合わせて、入力したSMPTE435−2に規定される64本のベーシックストリームCH1〜64をRAM130−1〜130−64に書き込む制御を行う。

【0249】

また、第1の再生部39Aは、ワード多重(デインタリーブ)を制御するワード多重制御部129−1〜129−64と、ワード多重制御部129−1〜129−64が多重したデータを書き込むRAM64−1〜64−64と、を備える。また、ライン多重を制御するライン多重制御部127−1〜127−32と、ライン多重制御部127−1〜127−32が多重したデータを書き込むRAM126−1〜126−32を備える。

【0250】

また、第1の再生部39Aは、RAM126−1〜126−32から抽出した2画素サンプルの多重を制御する第1の2画素多重制御部125−1〜125−4を備える。また、第1の2画素多重制御部125−1〜125−4がUHDTV1クラスイメージに多重した画素サンプルを記憶するRAM124−1〜124−4を備える。また、第1の再生部39Aは、RAM124−1〜124−4から抽出したUHDTV1クラスイメージの画素サンプルをUHDTV2クラスイメージに多重する第2の2画素多重制御部122を備える。また、UHDTV2クラスイメージに多重した画素サンプルを記憶するRAM123を備える。

【0251】

次に、第1の再生部39Aの動作例を説明する。

クロック供給回路121は、第2の2画素多重制御部122、第1の2画素多重制御部125−1〜125−4、ライン多重制御部127−1〜127−32、ワード多重制御部129−1〜129−64及び書込み制御部131−1〜131−64にクロックを供給する。このクロックにより各部が同期して、画素サンプルの読み出し又は書き込みが制御される。

【0252】

第1〜第8のサブイメージから抽出した画素サンプルをUHDTV1クラスイメージにマッピングする処理と、ライン多重、ワード多重の処理は、第2の実施の形態に係る画素サンプルの多重処理と同様に行われるため、詳細な説明を省略する。

【0253】

第2の2画素多重制御部122は、RAM124−1〜124−4から読み出した画素サンプルを2画素毎に以下の処理で多重する。すなわち、m×nが3840×2160であり、a−bが50P,59.94P,60Pである第1〜第4のUHDTV1のクラスイメージから2つの画素サンプルを抽出し、7680×4320/50P,59.94P,60P/4:2:0/10ビット,12ビットであるUHDTV2のクラスイメージの同一ラインに隣り合わせて多重する。

【0254】

ここで、第2の2画素多重制御部122は、第1のUHDTV1のクラスイメージの映像データ領域における同一ラインからライン毎に2つの画素サンプル毎に抽出した画素サンプルを多重する。このとき、UHDTV2のクラスイメージの第0ラインから1ラインおきであって、同一ラインの2つの画素サンプルおきに多重する。また、第2のUHDTV1のクラスイメージの映像データ領域における同一ラインからライン毎に2つの画素サンプル毎に抽出した画素サンプルを多重する。このとき、UHDTV2のクラスイメージの第0ラインから1ラインおきであって、第1のUHDTV1のクラスイメージから多重された画素サンプルとは異なる位置における同一ラインの2つの画素サンプルおきに多重する。

また、第3のUHDTV1のクラスイメージの映像データ領域における同一ラインからライン毎に2つの画素サンプル毎に抽出した画素サンプルを多重する。このとき、UHDTV2のクラスイメージの第1ラインから1ラインおきであって、同一ラインの2つの画素サンプルおきに多重する。また、第4のUHDTV1のクラスイメージの映像データ領域における同一ラインからライン毎に2つの画素サンプル毎に抽出した画素サンプルを多重する。このとき、UHDTV2のクラスイメージの第1ラインから1ラインおきであって、第3のUHDTV1のクラスイメージから多重された画素サンプルとは異なる位置における同一ラインの2つの画素サンプルおきに多重する。

そして、この多重処理を、UHDTV1クラスイメージの画素サンプルを全て抽出し、UHDTV2クラスイメージに多重し終わるまで繰り返す。

【0255】

この結果、RAM123には、UHDTV2で規定されるクラスイメージである7680×4320/100−120P/4:2:0/10ビット,12ビットが保存され、適宜、この信号がVTR等に送って再生される。

【0256】

なお、図29では、第1及び第2の2画素多重、ライン多重、ワード多重と、を4種類のRAMを用いて4段階で行う例を書いた。しかし、一つのRAMを用いて7680×4320/50P−60P/4:2:0/10ビット,12ビット信号を再生しても良い。

【0257】

以上説明した第3の実施の形態に係る放送用カメラ1によれば、以下の間引き処理を行う。すなわち、画素数の大きい7680×4320信号を2画素サンプル単位で2回間引いて複数の1920×1080信号にマッピングした後、ライン間引きする。この間引き処理は、信号をマッピングする際に必要となるメモリを最小にする方式であると共に、メモリ量が最小になることから信号の伝送遅延も最小に抑えることができる。

【0258】

また、第3の実施の形態に係るCCU2は、放送用カメラ1から受け取った64本のHD−SDIに基づいて、ワード多重、ライン多重、2画素多重を行ってUHDTV1クラスイメージを生成する。さらに、UHDTV1クラスイメージからUHDTV2クラスイメージを生成することにより、放送用カメラ1との間で現行の伝送インターフェースを用いてUHDTV2クラスイメージを伝送することが可能となった。

【0259】

また、10G 16chの信号を1本の光ファイバーで伝送する際には、CWDM/DWDM波長多重技術を使うことが出来る。

【0260】

<第4の実施の形態:UHDTV2 7680×4320/100P−120P/4:2:0/10ビット,12ビット多重方式を工夫して伝送HD−SDIや10G−SDIのch数を半分にする>

【0261】

7680×4320/100P−120P/4:2:0/10ビット,12ビット信号は、S2036−1で規定される信号のフレームレートを倍にした信号である。S2036−1で規定される信号とは、7680×4320/50P−60P/4:2:0/10ビット,12ビット信号である。また、7680×4320/100P−120P信号と7680×4320/50P−60Pの禁止コード等のディジタル信号形式は同じであるとする。

図30は、7680×4320/100P−120P/4:2:0/10ビット,12ビット信号を、2フレーム単位でライン方向に2画素サンプル毎に間引く例を示す。

【0262】

このとき、図28に示した第2の2画素間引き制御部102は、7680×4320/100P,119.88P,120P/4:2:0/10ビット,12ビットであるUHDTV2のクラスイメージから、同一ラインで隣り合う2つの画素サンプルを間引く。そして、m×nが3840×2160であり、a−bが100P,119.88P,120Pである第1〜第4のUHDTV1のクラスイメージに画素サンプルをマッピングする。

【0263】

具体的には、7680×4320/100P−120P/4:2:0/10ビット,12ビット信号の画素サンプルを、4chの3840×2160/100P−120P/4:2:0/10ビット,12ビット信号にマッピングする。4chの3840×2160/100P−120P/4:2:0/10ビット,12ビット信号のうち、4:2:0/10ビット信号は、従来方式では0信号成分にデフォルト値を割り当てる。これにより、第2の実施の形態に示した方法で16chのHD−SDIに信号がマッピングして出力され、10G−SDIの奇数chに入力することで4chの10G モードDで伝送できる。

【0264】

また、4:2:0/12ビット信号は、同様に0信号成分にデフォルト値を割り当てる。このデフォルト値は、10ビット信号の場合には200h、12ビット信号の場合には800hが割り当てられる。これにより、32chのHD−SDIに4:2:0/12ビット信号がマッピングして出力されるので、4chの10G モードDで伝送できる。従って、7680×4320/100P−120P/4:2:0/10ビット,12ビット信号は、合計16chの10G モードDで伝送可能である。

【0265】

また、2画素サンプル間引きで間引いた後の第1〜第4のUHDTV1クラスイメージの4:2:0信号のうち、第1及び第2のUHDTV1クラスイメージは4:2:2信号に変換され、第3及び第4のUHDTV1クラスイメージは4:0:0信号に変換される。ここで、0の信号成分には上記のデフォルト値(10ビット信号の場合には200h、12ビット信号の場合には800h)が多重されている。

【0266】

7680×4320/100P−120P/4:2:0/10ビット信号の場合には、2画素サンプル間引きでマッピングされた第1〜第4のUHDTV1クラスイメージは、第2の実施の形態の方式で16chのHD−SDIに多重される。しかし、4:2:2信号形式を持つ第1のUHDTV1クラスイメージと、4:0:0信号形式を持つ第3のUHDTV1クラスイメージを多重したそれぞれのHD−SDIの各16chを変換する。このとき、第1の実施の形態の図11と図12に示した方式で4:4:4(R‘G’B‘あるいはY′C′BC′R)/10ビット信号と同じデータ構造を持つ16組のデュアルリンク HD−SDI LinkA/Bに変換することで、8chの10G−SDI モードDで伝送することができる。

【0267】

同様に、4:2:2信号形式を持つ第2のUHDTV1クラスイメージと4:0:0信号形式を持つUHDTV1/120P 第4のクラスイメージを多重したそれぞれのHD−SDIの各16chを変換する。このとき、第1の実施の形態の方式で4:4:4(R’G’B’又はY′C′BC′R)/10ビット信号と同じデータ構造を持つ16組のデュアルリンク HD−SDI LinkA/Bに変換する。これにより、4chの10G−SDI モードDで伝送することができるので合計8chの10G−SDI モードDで伝送でき、従来方式と比べて伝送容量を半分にすることが可能である。

【0268】

一方、図29に示した第2の2画素多重制御部122は、m×nが3840×2160であり、a−bが100P,119.88P,120Pである第1〜第4のUHDTV1のクラスイメージに2つの画素サンプルを抽出する。そして、7680×4320/50P,59.94P,60P/4:2:0/10ビット,12ビットであるUHDTV2のクラスイメージの同一ラインに隣り合わせて多重する。

【0269】

以上説明した第4の実施の形態に係る放送用カメラ1によれば、7680×4320/100P−120P/4:2:0/12ビット信号の場合には、2画素サンプル間引きによりマッピングされたそれぞれの第1〜第4のUHDTV1クラスイメージは、第2の実施の形態の方式で32chのHD−SDIに多重される。4:2:2信号形式を持つ第1のUHDTV1クラスイメージと、4:0:0信号形式を持つ第3のUHDTV1クラスイメージを多重したそれぞれのHD−SDIの各32chを変換する。このとき、第1の実施の形態の方式で4:4:4(R’G’B’又はY′C′BC′R)/12ビット信号と同じデータ構造を持つ16組のデュアルリンク HD−SDI LinkA/Bに変換する。このため、4chの10G−SDI モードDで伝送することができる。

【0270】

同様に、4:2:2信号形式を持つ第2のUHDTV1クラスイメージと4:0:0信号形式を持つUHDTV1/120P 第4のクラスイメージを多重したそれぞれのHD−SDIの各32chを変換する。このとき、第1の実施の形態図7,8の方式で4:4:4(R’G’B’又はY′C′BC′R)/12ビット信号と同じデータ構造を持つ16組のデュアルリンク HD−SDI LinkA/Bに変換する。このため、4chの10G−SDI モードDで伝送することができるので合計8chの10G−SDI モードDで伝送でき、従来方式と比べて伝送容量を半分にすることが可能である。

【0271】

以上説明した第1〜第4の実施の形態に係る伝送システム10によれば、以下の効果を奏する。

3840×2160/4:2:0/10ビット信号の場合には、偶数ラインをマッピングした4:2:2信号の2組のLinkA/Bを、新しく組み替える4組のLinkA/Bの4chのLinkAとする。また、奇数ラインをマッピングした2組の4:0:0信号のLinkA/BのYchに多重された10ビット信号を、新しく組み替える4組のLinkA/Bの4chのLinkBのCchに多重し直す。これにより、SMPTE ST372に規定される4:4:4(R’G’B’又はY′C′BC′R)/10ビットデータ構造と同じ構造にする。

【0272】

3840×2160/4:2:0/12ビット信号の場合には、以下の処理を行う。すなわち、偶数ラインをマッピングした4:2:2信号の4組のLinkA/Bのうち、12ビット信号の上位10ビットを多重した4chのLinkAを、新しく組み替える4組のLinkA/Bの4chのLinkAとする。また、12ビット信号の下位2ビットを多重した4chのLinkBの、Ychの偶数番目の画素サンプルは新しく組み替える4組のLinkA/Bの4chのLinkBのYchの偶数番目の画素サンプルとする。そして、Ych奇数番目の画素サンプルと、奇数ラインをマッピングした4:0:0信号のLinkA/Bの4chのLinkBのYchに多重された12ビット信号の下位2ビット信号を、奇数番目の画素サンプルに多重し直す。この多重処理は、新しく組み替える4chのLinkA/BのLinkBのYchの画素サンプルに対して行われる。また、Ychに多重された12ビット信号の上位10ビットをCchに多重し直すことで、SMPTE ST372に規定される4:4:4(R’G’B’又はY′C′BC′R)/12ビットデータ構造と同じ構造にする。

【0273】

これにより、ITUやSMPTEで審議されている次世代の映像信号である3840×2160,7680×4320/100P−120P信号を以下のように多重する。すなわち、4:2:0サンプル信号については3840×2160,7680×4320/100P−120P信号を多chのHD−SDIにマッピングした後の2chあるいは4chのHD−SDIの信号の中身を多重し直す。そして、4:4:4(R’G’B’又はY′Cb’Cr’)/10ビットあるいは12ビット信号形式に変換したデュアルリンク HD−SDIのデータ構造とする。こうして、伝送するHD−SDIや10Gインターフェースの伝送ch数を半分にすることができる。

【0274】

また、将来提案される可能性が高い3840×2160/100P−120P、7680×4320/100P−120P信号を、2画素間引きやライン間引き、最終的にはワード間引きをする。これにより、多chの1920×1080/50I−60I信号にマッピングすることができる。上述した第1〜第4の実施の形態におけるマッピング方式が最も必要とするメモリ量が少なく、遅延も少ない。また、SMPTE274Mで規定される1920×1080/50I−60I信号は、現行の測定器で観測可能である。また、3840×2160/100P−120P、7680×4320/100P−120P信号を画素単位あるいは時間単位で間引いて観測することも可能である。また、現行の諸々のSMPTEマッピング規格との整合が取れるので、将来SMPTEにおける標準化においても賛同を得られる可能性が最も高い方式である。

【0275】

また、4k、8kの信号を2画素サンプル毎に間引くことで、画面全体の映像を現行のHD用のモニタや波形モニタ、あるいは8k信号を将来の4k用モニタ等で観測できる。このため、映像機器を開発する際等における不具合の解析に有効である。

【0276】

また、3840×2160/100P−120P、7680×4320/100P−120P信号を、4ch,16chのモードDの10.692Gbpsで伝送する際に、最小の遅延で伝送システムを構築することが出来る。また、SMPTEで審議されているS2036−3規格について、3840×2160、7680×4320のクラスイメージのフレームから2画素サンプル毎に間引く方式の整合を取ることができる。なお、S2036−3は、3840×2160/23.98P−60P、7680×4320/23.98P−60Pの多chの10.692GbpsのモードDへのマッピング規格に関する。

【0277】

また、画素の間引き又は多重に際して抽出される画素数を少なくし、一時領域として用いるメモリ量を抑えることができる。ここで、1920×1080/50P−60P信号をライン間引きして2chの1920×1080/50I−60I信号に変換するライン間引きは、SMPTE372の規格に採用された方式を用いる。この規格には、1920×1080/50P−60P信号を2chの1920×1080/50I−60Iにマッピングする方式が規定されている。このため、上述した実施の形態に係るマッピング方式を用いることによって、SMPTE372の規格で定められたマッピング方式と整合を取ることができる。

【0278】

<6.変形例>

なお、上述した実施の形態例における一連の処理は、ハードウェアにより実行することができるが、ソフトウェアにより実行させることもできる。一連の処理をソフトウェアにより実行させる場合には、そのソフトウェアを構成するプログラムが専用のハードウェアに組み込まれているコンピュータ、または、各種の機能を実行するためのプログラムをインストールしたコンピュータにより、実行可能である。例えば汎用のパーソナルコンピュータなどに所望のソフトウェアを構成するプログラムをインストールして実行させればよい。

【0279】

また、上述した実施の形態の機能を実現するソフトウェアのプログラムコードを記録した記録媒体を、システムあるいは装置に供給してもよい。また、そのシステムあるいは装置のコンピュータ(またはCPU等の制御装置)が記録媒体に格納されたプログラムコードを読み出し実行することによっても、機能が実現されることは言うまでもない。

【0280】

この場合のプログラムコードを供給するための記録媒体としては、例えば、フレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、CD−ROM、CD−R、磁気テープ、不揮発性のメモリカード、ROMなどを用いることができる。

【0281】

また、コンピュータが読み出したプログラムコードを実行することにより、上述した実施の形態の機能が実現される。加えて、そのプログラムコードの指示に基づき、コンピュータ上で稼動しているOSなどが実際の処理の一部又は全部を行う。その処理によって上述した実施の形態の機能が実現される場合も含まれる。

【0282】

また、本開示は上述した実施の形態に限られるものではなく、特許請求の範囲に記載した本開示の要旨を逸脱しない限りその他種々の応用例、変形例を取り得ることは勿論である。

【符号の説明】

【0283】

1…放送用カメラ、2…CCU、3…光ファイバーケーブル、10…信号伝送システム、11…マッピング部、39…再生部

【技術分野】

【0001】

本開示は、1フレームの画素数がHD−SDIフォーマットで規定された画素数を越える映像信号をシリアル伝送する場合に適用して好適な信号送信装置、信号送信方法、信号受信装置、信号受信方法及び信号伝送システムに関する。

【背景技術】

【0002】

従来、1フレームが1920サンプル×1080ラインの映像信号である現行のHD(High Definition)の映像信号を超える、超高精細映像信号の受像システムや撮像システムの開発が進んでいる。例えば、現行のHDで規定される画素数の4倍又は16倍もの画素数を持つ次世代の放送方式であるUHDTV(Ultra High Definition TV)規格が、国際協会によって標準化が行われている。この国際協会には、ITU(International Telecommunication Union)やSMPTE(Society of Motion Picture and Television Engineers)がある。

【0003】

ここで、特許文献1には、4k×2k信号(4k×2kの超高解像度信号)の一種である3840×2160/30P,30/1.001P/4:4:4/12ビット信号を、ビットレート10Gbps以上で伝送する技術が開示されている。なお、mサンプル×nラインで表される映像信号を、「m×n」と略記する。そして、[3840×2160/30P]と示した場合には、[水平方向の画素数]×[垂直方向のライン数]/[1秒当りのフレーム数]を示す。また、[4:4:4]は、原色信号伝送方式である場合、[赤信号R:緑信号G:青信号B]の比率を示し、色差信号伝送方式である場合、[輝度信号Y:第1色差信号Cb:第2色差信号Cr]の比率を示す。

【0004】

以下の説明において、プログレッシブ信号のフレームレートを表す50P,59.94P,60Pを、「50P−60P」、47.95P,48P,50P,59.94P,60Pを「48P−60P」と略記する。また、100P,119.88P,120Pを、「100P−120P」と略記し、95.9P,96P,100P,119.88P,120Pを、「96P−120P」と略記する。また、インターレース信号のフレームレートを表す50I,59.94I,60Iを、「50I−60I」、47.95I,48I,50I,59.94I,60Iを、「48I−60I」と略記する。また、3840×2160/100P−120P/4:2:0/10ビット,12ビット信号を、「3840×2160/100P−120P信号」と略記する場合がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2005−328494号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

近年のSMPTEやITUでは、フレームレートが23.98P−60Pである3840×2160や7680×4320の映像信号規格やインターフェース規格が標準化されつつある。また、映像データを伝送するためにモードD(後述する図8参照)を用いた場合、3840×2160/23.98P−30Pの映像信号を1chの10G−SDIで伝送出来る。しかし、フレームレートが120Pや120Pを超える映像信号を伝送するために対応可能なインターフェースについて議論されたり、標準化がなされたりしていなかった。また、1920×1080や2048×1080に対応する映像信号規格には、フレームレートが60Pまでしか規定されていないため、特許文献1に記載されている技術を用いても、高画素の画素サンプルを既存のインターフェースで伝送できなかった。

【0007】

また、SMPTEでは、4096×2160/23.98P−60Pまでの映像信号規格や標準化されつつあるものの、信号送信装置と信号受信装置が備えるインターフェースの議論や標準化がなされていなかった。このため、4096×2160/23.98P−30Pの映像信号を想定すると、映像データ領域に格納される画素サンプル数が増えるため、モードDのライン構造のままでは画素サンプルを多重し、伝送できなかった。

【0008】

さらに、映像信号が4096×2160である場合に、フレームレートが23.98P,24P,25P,29.97P,30P,47.95P,48P,50P,59.94P,60Pの範囲で規定されている。しかし、将来は現在用いられているフレームレート(例えば30P)の3倍速信号である90P、あるいは90P以上のフレームレートの映像信号を伝送することも考慮しなければならない。このため、様々なフレームレートの映像信号を、現行の伝送インターフェースを利用して伝送する仕様を策定する必要があった。

【0009】

本開示はこのような状況に鑑みて成されたものである。すなわち、1フレームの画素数がHD−SDIフォーマットで規定される画素数を越え、かつ、高いフレームレートである映像信号を、HD−SDIインターフェースや10Gbpsのシリアルインターフェースを利用してシリアル伝送することを目的とする。120P伝送時、特に4:2:0信号伝送時にデータ多重方式を工夫して伝送帯域を削減するものである。

【課題を解決するための手段】

【0010】

本開示は、1フレームの画素数がHD−SDIフォーマットで規定される画素数を越えるm×n(mサンプル、nラインを示すm,nは、正の整数)/a−b(a,bは、プログレッシブ信号のフレームレート)/4:2:0/rビット信号で規定されるクラスイメージから、同一ラインで隣り合う2つの画素サンプルを間引く。そして、m′×n′(m′サンプル、n′ラインを示すm′,n′は、正の整数)/a′−b′(a′,b′は、プログレッシブ信号のフレームレート)/4:2:2および4:0:0/rビット信号で規定される第1〜第N(Nは、2以上の整数)のサブイメージの映像データ領域にマッピングする。

次に、画素サンプルがマッピングされた第1〜第Nのサブイメージのそれぞれの一ラインおきに画素サンプルを間引いてインターレース信号とする。このとき、第1〜第N/2のサブイメージを、4:2:2/rビット信号に変換し、第(N/2)+1〜第Nのサブイメージを、4:0:0/rビット信号に変換する。

そして、4:2:2/rビット信号のデータ構造、及び4:0:0/rビット信号のデータ構造を、4:4:4/rビット信号のデータ構造に合わせて変換したデュアルリンクHD−SDIを出力するものである。

【0011】

また、本開示は、4:4:4/rビット信号のデータ構造としてあるデュアルリンクHD−SDIを、4:2:2/rビット信号及び4:0:0/rビット信号に変換する。

次に、4:2:2/rビット信号を、m′×n′(m′サンプル、n′ラインを示すm′,n′は、正の整数)/a′−b′(a′,b′は、プログレッシブ信号のフレームレート)/4:2:2/rビット信号で規定される第1〜第N/2(Nは、2以上の整数)のサブイメージの一ラインおきに画素サンプルを多重する。また、4:0:0/rビット信号を、第(N/2)+1〜第Nのサブイメージの一ラインおきに画素サンプルを多重する。

そして、第1〜第Nのサブイメージから2画素ずつ抽出した画素サンプルを、1フレームの画素数がHD−SDIフォーマットで規定される画素数を越えるm×n(mサンプル、nラインを示すm,nは、正の整数)/a−b(a,bは、プログレッシブ信号のフレームレート)/4:2:0/rビット信号で規定されるクラスイメージのフレームにおける同一ラインに隣り合わせて多重するものである。

【0012】

また、本開示は、上記の映像信号を送信し、この映像信号を受信する信号伝送システムである。

【0013】

本開示は、入力した映像信号に対して、連続する2フレーム(あるいは2フレーム以上)単位のクラスイメージに含まれる画素サンプルの2画素間引き、ライン間引き及びワード間引きを行い、HD−SDIの映像データ領域に画素サンプルを多重した信号を送信する。一方、受信した信号に対して、HD−SDIの映像データ領域から画素サンプルを抽出し、ワード多重、ライン多重、及び2画素多重を行って、映像信号を再生する。

【発明の効果】

【0014】

本開示によれば、4:2:0/10ビット、12ビット信号のデータ構造を4:4:4/10ビット、12ビット信号に変換して、現行の10Gシリアルインターフェースで伝送することを可能とした。このため、新たな伝送規格を設けることなく、従来用いられていた伝送規格を利用できるので利便性が向上するという効果がある。

【図面の簡単な説明】

【0015】

【図1】本開示の第1の実施の形態に係るテレビジョン放送局用のカメラ伝送システムの全体構成を示す図である。

【図2】本開示の第1の実施の形態に係る放送用カメラの回路構成のうち、信号送信装置の内部構成例を示すブロック図である。

【図3】本開示の第1の実施の形態に係る10ビット信号をマッピングする第1のマッピング部の内部構成例を示すブロック図である。

【図4】本開示の第1の実施の形態に係る第2のマッピング部の内部構成例を示すブロック図である。

【図5】3840×2160におけるUHDTV規格のサンプル構造の例を示す説明図である。

【図6】本開示の第1の実施の形態に係る2画素間引き制御部が第1及び第2のクラスイメージから画素サンプルを2画素ずつ間引いて第1〜第4のサブイメージにマッピングする処理例を示す説明図である。

【図7】24Pの場合における10.692Gbpsのシリアル・デジタルデータの1ライン分のデータ構造例を示す説明図である。

【図8】モードDの例を示す説明図である。

【図9】本開示の第1の実施の形態に係る第1〜第4のサブイメージをライン間引きすることによって、SMPTE372Mの規定に従ってLinkA,Bに分割する例を示す説明図である。

【図10】本開示の第1の実施の形態に係るライン間引きの例を示す説明図である。

【図11】本開示の第1の実施の形態に係る8chの4:2:2/10ビット信号と4:0:0/10ビット信号を4組のHD−SDI LinkA,Bに変換する例を示す説明図である。

【図12】本開示の第1の実施の形態に係る8chの4:2:2/10ビット信号と4:0:0/10ビット信号を4組のHD−SDI LinkA,Bに変換する際のデータ構造の例を示す説明図である。

【図13】本開示の第1の実施の形態に係る4:2:0/12ビット信号をマッピングする第1のマッピング部の内部構成例を示すブロック図である。

【図14】本開示の第1の実施の形態に係る第1〜第4のサブイメージをライン間引きした後、ワード間引きをすることによって、SMPTE372Mの規定に従ってLinkA,Bに分割する例を示す説明図である。

【図15】本開示の第1の実施の形態に係る16chの4:2:2/12ビット信号と4:0:0/12ビット信号を4組のHD−SDI LinkA,Bに変換する例を示す説明図である。

【図16】本開示の第1の実施の形態に係る16chの4:2:2/12ビット信号と4:0:0/12ビット信号を4組のHD−SDI LinkA,Bに変換する際のデータ構造の例を示す説明図である。

【図17】本開示の第1の実施の形態に係る多重部が行うデータの多重処理の例を示す説明図である。

【図18】本開示の第1の実施の形態に係るCCUの回路構成のうち、信号受信装置の内部構成例を示すブロック図である。

【図19】本開示の第1の実施の形態に係る第2の再生部の内部構成例を示すブロック図である。

【図20】本開示の第1の実施の形態に係る10ビット信号を再生する第1の再生部の内部構成例を示すブロック図である。

【図21】本開示の第1の実施の形態に係る12ビット信号を再生する第1の再生部の内部構成例を示すブロック図である。

【図22】本開示の第2の実施の形態に係る第1のマッピング部の内部構成例を示すブロック図である。

【図23】本開示の第2の実施の形態に係るマッピング部が画素サンプルをマッピングする処理イメージを示す説明図である。

【図24】本開示の第2の実施の形態に係る2画素間引き制御部が第1及び第2のクラスイメージから画素サンプルを2画素ずつ間引いて第1〜第8のサブイメージにマッピングする処理例を示す説明図である。