信号送信装置、信号送信方法、信号受信装置、信号受信方法及び信号伝送システム

【課題】2k/23.98P−60P又は47.95I−60I/16ビットの映像信号を伝送するためのインタフェースを設ける。

【解決手段】信号送信装置は、r:g:bが4:4:4である1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号にマッピングする。そして、第1及び第2のマッピング構造に従って、4:2:2である2chの10ビット信号からなる第1〜第3のHD−SDIにマッピングし、出力する。

【解決手段】信号送信装置は、r:g:bが4:4:4である1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号にマッピングする。そして、第1及び第2のマッピング構造に従って、4:2:2である2chの10ビット信号からなる第1〜第3のHD−SDIにマッピングし、出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、例えば、撮像素子から出力される16ビットの映像信号を伝送する場合に適用して好適な信号送信装置、信号送信方法、信号受信装置、信号受信方法及び信号伝送システムに関する。

【背景技術】

【0002】

従来、撮像素子が出力する1フレームの映像信号が1920サンプル×1080ライン(以下、mサンプル×nラインを「m×n」とも略記する。)であるHD(High Definition)信号を伝送するために標準化が行われていた。この標準化を行う国際協会には、ITU(International Telecommunication Union)やSMPTE(Society of Motion Picture and Television Engineers)が知られている。

【0003】

例えば、SMPTE274Mには、1920×1080の映像信号のサンプル構造が規定され、SMPTE292Mには、HDTVシステムのシリアルデジタルインタフェースが規定されている。また、SMPTE372Mには、SMPTE292Mに規定されるデータ構造をベースとして規格化された、LinkA,Bを用いるデュアルリンクHD−SDIインタフェースが規定されている。以下の説明では、1920×1080又は2048×1080のことを、「2k」とも略称し、3840×2160又は4096×2160のことを、「4k」又は「4k×2k」とも略称する。また、1.5Gbpsで映像信号を伝送可能なHD−SDIインタフェースを、「1.5G−SDI」とも呼ぶ。

【0004】

ここで、SMPTE2048−1やSMPTE2036−1(UHDTV)で規定される4096規格や3840規格における画素のサンプル構造は、図14に示す以下の2種類がある。

【0005】

図14は、4k規格のサンプル構造の例を示す説明図である。

図14Aと図14Bの説明に用いるフレームは、4k×2kのサンプル構造で1フレームを構成する。4k規格のサンプル構造は、以下の3種類がある。なお、SMPTE規格において、R′G′B′のように、ダッシュ「′」をつけた信号は、ガンマ補正などが施された信号を示す。

【0006】

図14Aは、R′G′B′,Y′Cb′Cr′ 4:4:4システムにおける画素サンプルの例である。このシステムでは、全サンプルにRGB又はYCbCrのコンポーネントが含まれる。

図14Bは、Y′Cb′Cr′ 4:2:2システムにおける画素サンプルの例である。このシステムでは、偶数サンプルにYCbCr、奇数サンプルにYのコンポーネントが含まれる。

【0007】

また、特許文献1には、4k×2kの超高解像度信号の一種である3840×2160/30P,30/1.001P/4:4:4/12ビット信号を、ビットレート10Gbps以上で伝送する技術が開示されている。なお、[3840×2160/30P]と示した場合には、[水平方向の画素サンプル数]×[垂直方向のライン数]/[1秒当りのフレーム数]を示す。また、[4:4:4]は、原色信号伝送方式である場合、[赤信号R:緑信号G:青信号B]の比率を示し、色差信号伝送方式である場合、[輝度信号Y:第1色差信号Cb:第2色差信号Cr]の比率を示す。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2005−328494号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

ところで、SMPTEによって規定される従来の伝送規格は、10ビット又は12ビットの映像信号を10ビット/ワードのHD−SDIで伝送することを前提としていた。しかし、近年は、撮像素子から出力される16ビットの映像信号を10ビット/ワードのHD−SDIを用いて伝送しようとする要望が高まっている。16ビットの映像信号としては、例えば、2k/4:4:4/16ビット信号があり、この信号は、2kサンプルのG信号、B信号及びR信号から構成される。しかし、このような、2k/23.98P−60P/16ビットの映像信号を伝送するためのインタフェースあるいはインターフェースデータ規格や提案がなかった。

【0010】

本開示はこのような状況に鑑みて成されたものであり、撮像素子から出力される16ビットの映像信号を伝送するためのインタフェースを提供することを目的とする。

【課題を解決するための手段】

【0011】

本開示は、撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号、及びr:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングする。

次に、ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造に従って、r:g:bが4:2:2である2chの10ビット信号からなる第1及び第2のHD−SDIにマッピングすると共に、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造に従って、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIにマッピングし、第1〜第3のHD−SDIを出力するものである。

【0012】

また、本開示は撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:2:2である3chの10ビット信号からなる第1〜第3のHD−SDIを記憶部に書込む。

次に、記憶部から読み出した、2chの10ビット信号からなる第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号を抽出すると共に、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号を抽出する。

そして、r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重することによって、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号を生成するものである。

【0013】

このようにしたことで、撮像素子から出力される16ビットの映像信号を既存のHD−SDIにマッピングして伝送することが可能となった。

【発明の効果】

【0014】

本開示によれば、撮像素子から出力される16ビットの映像信号を、第1及び第2のマッピング構造に基づいて、r:g:bが4:2:2である10ビット信号からなる第1〜第3のHD−SDIとして伝送することが可能となる。このため、既存の伝送規格に準じて16ビットの映像信号を伝送することができる。

【図面の簡単な説明】

【0015】

【図1】本開示の第1の実施の形態に係るテレビジョン放送局用の信号伝送システムの全体構成を示す図である。

【図2】本開示の第1の実施の形態に係る信号送信装置の内部構成例を示すブロック図である。

【図3】通常のベイヤ構造と倍密ベイヤ構造の例を示す説明図である。

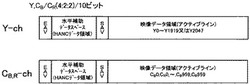

【図4】1.5GbpsのHD−SDI(シリアル・デジタルデータ)の1ライン分のデータ構造例を示す説明図である。

【図5】本開示の第1の実施の形態に係る1chの2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号をワード間引き及びマッピング制御を行う処理の概略例を示す説明図である。

【図6】デュアルリンクの伝送表現の例を示す説明図である。

【図7】本開示の第1の実施の形態に係る30Pあるいは60I/4:2:2/16ビット信号を2ch(デュアルリンク)の1.5G−SDIにマッピングする場合に参照される第1のマッピング構造の例を示す説明図である。

【図8】本開示の第1の実施の形態に係る30Pあるいは60I/0:2:2/16ビット信号を1.5G−SDIにマッピングする場合に参照される第2のマッピング構造の例を示す説明図である。

【図9】本開示の第1の実施の形態に係る信号受信装置の内部構成例を示すブロック図である。

【図10】本開示の第2の実施の形態に係る信号送信装置の内部構成例を示すブロック図である。

【図11】本開示の第2の実施の形態に係る2k/47.95P−60P/4:4:4/16ビット信号をライン間引き、ワード間引き及びマッピング制御を行う処理の概略例を示す説明図である。

【図12】ライン間引きの例を示す説明図である。

【図13】本開示の第2の実施の形態に係る信号受信装置の内部構成例を示すブロック図である。

【図14】UHDTV規格のサンプル構造の例を示す説明図である。

【発明を実施するための形態】

【0016】

以下、本開示を実施するための形態(以下、実施の形態とする。)について説明する。なお、説明は以下の順序で行う。

1.第1の実施の形態(2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を1.5G−SDI 3chにマッピングして伝送する例)

2.第2の実施の形態(2k/47.95P−60P/4:4:4/16ビット信号を1.5G−SDI 6chにマッピングして伝送する例)

3.変形例

【0017】

<1.第1の実施の形態>

[2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を1.5G−SDI 3chにマッピングして伝送する例]

【0018】

始めに、本開示の第1の実施の形態について、図1〜図9を参照して説明する。

本開示の第1の実施の形態に係る信号送信装置10は、プログラムを実行することにより、内部ブロックが連携して行う信号送信方法を実現する。始めに、信号送信装置10の構成例を説明する。

【0019】

ここでは、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を1.5G−SDI 3chにマッピングして伝送する例について説明する。

不図示の撮像素子が出力する映像信号は、m×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビットで規定される。このとき、r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインである。そして、この16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする。

【0020】

また、a−bが23.98P,24P,25P,29.97P,30Pである場合に、「23.98P−30P」と略記することがある。また、a−bが47.95I,48I,50I,59.94I,60Iである場合に、「47.95I−60I」と略記することがある。また、例えば、「2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号」と表記した場合、以下の意味とする。すなわち、撮像素子が1920×1080あるいは2048×1080個の画素で構成され、映像信号のフレームレートが23.98P−30Pあるいはフィールドレートが47.95I−60Iであって、画素が出力する映像信号の量子化ビットが16ビットという意味である。

【0021】

図1は、本実施の形態を適用したテレビジョン放送局用の信号伝送システム5の全体構成を示す図である。

この信号伝送システム5は、複数台の放送用カメラ1とCCU(カメラコントロールユニット)2とで構成されており、各放送用カメラ1が光ファイバーケーブル3でCCU2に接続されている。放送用カメラ1は、シリアル・デジタル信号を送信する信号送信方法を適用した信号送信装置として用いられ、CCU2は、シリアル・デジタル信号を受信する信号受信方法を適用した信号受信装置として用いられる。そして、放送用カメラ1とCCU2を組み合わせた信号伝送システム5は、シリアル・デジタル信号を送受信する信号伝送システムとして用いられる。

【0022】

複数の放送用カメラ1は、同一構成のものである。そして、放送用カメラ1は、デジタルシネマ用の2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を生成し、CCU2に送信する信号送信装置として機能する。

【0023】

CCU2は、各放送用カメラ1を制御したり、各放送用カメラ1から映像信号を受信したり、各放送用カメラ1のモニタに他の放送用カメラ1で撮影中の映像を表示させるための映像信号(リターンビデオ)を送信するユニットである。CCU2は、各放送用カメラ1から映像信号を受信する信号受信装置として機能する。

【0024】

<DWDM/CWDM波長多重伝送技術>

ここで、DWDM/CWDM波長多重伝送技術について説明する。

複数の波長の光を1本の光ファイバーに多重して伝送する方法をWDM(Wavelength Division Multiplexing)と言う。WDMは波長間隔に応じて大まかに以下の3つの方式に分けられる。

【0025】

(1)2波長多重方式

1.3μm、1.55μmといった離れた波長を、2波〜3波程度多重して1本の光ファイバーで伝送する方式である。

【0026】

(2)DWDM(Dense Wavelength Division Multiplexing)方式

特に1.55μm帯において光の周波数で25GHz、50GHz、100GHz、200Ghz..波長で約0.2nm、0.4nm、0.8nm..間隔で高密度に光を多重して伝送する方法をDWDMと言う。ITU−T(International Telecommunication Union Telecommunication standardization sector)にて中心波長他の標準化が行われた。DWDMは波長間隔が100GHzと狭いために数十〜百と多重数を多く取ることが出来、超大容量の通信が可能である。しかし、発振波長幅が波長間隔100GHzより十分狭いことが必要であるとともに中心波長がITU−T規格に一致するよう半導体レーザを温度制御する必要があるため、デバイスが高価であり、システムの消費電力が大きくなる。

【0027】

(3)CWDM(Coarse Wavelength Division Multiplexing)方式

一方で近年CWDMと呼ばれる、波長間隔を10nm〜20nmとDWDMより一桁以上広く取った波長多重技術が注目されるようになってきた。波長間隔が比較的広いために半導体レーザの発振波長幅がDWDMほど狭帯域である必要が無く、また半導体レーザを温度制御する必要も無いので、システムを低価格、低消費電力化することが可能である。DWDMほどの大容量が必要でないシステムに有効である。中心波長例については、現在のところ4ch構成で以下のものが一般的である。例えば、1.511μm、1.531μm、1.551μm、1.571μm、8ch構成で1.471μm、1.491μm、1.511μm、1.531μm、1.551μm、1.571μm、1.591μm、1.611μmがある。

【0028】

<信号送信装置10の内部構成例>

図2は、信号送信装置10の内部構成例を示す。

本開示の第1の実施の形態に係る放送用カメラ1は、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を3chのHD−SDIに多重した後、CCU2が備える信号受信装置20に出力する信号送信装置10を備える。

【0029】

信号送信装置10は、各部にクロックを供給するクロック供給回路11と、不図示の撮像素子が出力する2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を記憶するRAM13を備える。また、信号送信装置10は、RAM13から読出したデータのワード間引きを制御するワード間引き制御部12と、ワード間引き制御部12がワード間引きしたデータを書き込むRAM14−1,14−2とを備える。

【0030】

また、信号送信装置10は、RAM14−1から読出した2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号を、後述する第1のマッピング構造(図7を参照。)に従ってマッピングするマッピング制御部15−1を備える。また、マッピング制御部15−1によってマッピングされた2chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号を記憶するRAM16−1,16−2を備える。

【0031】

また、信号送信装置10は、RAM14−2から読出した2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号を、後述する第2のマッピング構造(図8を参照。)に従ってマッピングするマッピング制御部15−2を備える。また、マッピング制御部15−2によってマッピングされた1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号を記憶するRAM16−3を備える。

【0032】

また、信号送信装置10は、RAM16−1〜16−3から読出したデータの画素サンプルを3chのHD−SDIとして出力する読出し制御部17−1〜17−3を備える。

【0033】

次に、各部の動作例を説明する。

クロック供給回路11は、ワード間引き制御部12、マッピング制御部15−1,15−2及び読出し制御部17−1〜17−3に画素サンプルの読出し又は書き込みに用いるクロックを供給する。各部は、この供給されたクロックにより同期して動作する。

【0034】

ワード間引き制御部12は、RAM13から読出した画素サンプルより、SMPTE372のFigure4,6,7,8,9と同じ方式でワード間引きを行う。このとき、ワード間引き制御部12は、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引く。そして、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングする。同様に、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングする。このとき、RAM14−1には、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号が書き込まれる。一方、RAM14−2には、1chの2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号が書き込まれる。

【0035】

次に、マッピング制御部15−1は、ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造(後述する図7参照)に従って、r:g:bが4:2:2である第1及び第2のHD−SDIにマッピングする。この第1及び第2のHD−SDIは、2chの10ビット信号からなる。

このとき、マッピング制御部15−1は、RAM14−1から読出した2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号を、2chの10ビット信号にマッピングし直してRAM16−1,16−2に書き込む。このとき、RAM16−1には、2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号の奇数ビットから抽出した1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号が書き込まれる。一方、RAM16−2には、2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号の偶数ビットから抽出した1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号が書き込まれる。

【0036】

一方、マッピング制御部15−2は、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造(後述する図8参照)に従って、r:g:bが4:2:2である第3のHD−SDIにマッピングする。この第3のHD−SDIは、1chの10ビット信号からなる。

このとき、マッピング制御部15−2は、RAM14−2から読出した2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号を、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号にマッピングし直してRAM16−3に書き込む。

なお、マッピング制御部15−1,15−2の詳細な動作例については後述する。

【0037】

そして、読出し制御部17−1〜17−3は、クロック供給回路11から供給された基準クロックでRAM16−1〜16−3から読み出した第1〜第3のHD−SDIをHD−SDI ch1〜ch3として出力する。

【0038】

なお、本例では、ワード間引きとマッピング制御を行うため、3種類のメモリ(RAM13,RAM14−1,14−2、RAM16−1〜16−3)を用いて、2段階で間引き制御を行う処理を説明した。しかし、一つのメモリを使って、ワード間引き及びマッピング制御を行った後、3chのHD−SDIとして出力しても良い。

【0039】

ここで、4k×2kの16ビット信号を出力する不図示の撮像素子における構造の通常のベイヤ構造と倍密ベイヤ構造の違いについて説明する。

図3は、倍密ベイヤ構造の4k×2kのサンプル構造とした画素が出力する映像信号の例を示す。

【0040】

従来、ベイヤ構造の撮像素子を用いた撮像装置が一般に知られている。この撮像素子は、色フィルタを介して被写体の像光を取込み、像光の強さに応じて映像信号を出力する。そして、後続の処理部が映像信号に所定の処理を加えることによって、撮像装置がビューファインダや外部の表示装置に映像を表示させることを可能とする。撮像素子には、一般にR,G,B信号のような原色信号をそれぞれ出力可能なR,G,B画素が所定のパターンで配置されており、R,G,B画素をどのように配置するかによって、解像度が異なっている。

【0041】

図3Aは、通常のベイヤ構造の例を示す。

通常のベイヤ構造では、対角線上にそれぞれ2個のG画素を配置し、この対角線に直交する対角線上にR,B画素を配置する構成としている。しかし、通常のベイヤ構造では、一番画素数の多いGchでも4k×2kの半分の画素数しか得られない。

【0042】

図3Bは、倍密ベイヤ構造の例を示す。

倍密ベイヤ構造では、図3Aに示した通常のベイヤ構造とした画素を45度斜めに配列してある。この画素は、通常のベイヤ構造における画素に対して、縦横を半分にしたサイズとしてある。このため、倍密ベイヤにおけるGchは4k×2kの画素数に相当する解像度を持つ。その分、1つの画素のサイズは小さくなるが、斜めにすることで、通常のベイヤ構造でGchに4k×2kの画素数を持たせる場合よりも小さくせずに済む。このため、解像度と感度をバランスよく両立でき、通常のベイヤ構造に対する利点となる。

【0043】

そして、不図示の変換部により、4k×2kの倍密ベイヤ構造とした撮像素子が出力する4k×2kの16ビット信号を2kの16ビット信号に変換した後、本実施の形態に係る信号伝送システム1を用いて映像信号を伝送するようにしている。

【0044】

次に、1ラインのHD−SDIフォーマットで規定されたシリアルデータの構成例について説明する。

図4は、1.5GbpsのHD−SDI(シリアル・デジタルデータ)の1ライン分のデータ構造例である。

【0045】

ここでは、Yチャンネル、CB,CRチャンネルの2種類のチャンネルのデータ構造例を示している。各チャンネルに含まれる、ライン番号LN及び誤り検出符号CRCを含めたものをEAV,映像データ領域(アクティブライン)及びSAVとして示す。そして、付加データの領域を含めたものを水平補助データスペース(HANCデータ領域)として示している。

なお、水平補助データスペースには、オーディオ信号がマッピングされる場合がある。このとき、オーディオ信号に補完データを追加して水平補助データスペースを構成し、入力するHD−SDI信号との同期を取るようにする。

【0046】

図5は、1chの2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号をワード間引き及びマッピング制御を行う処理の概略例を示す。

【0047】

2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号は、SMPTE274やSMPTE2048−2に規定される1920×1080,2048×1080/8ビット,10ビット,12ビット信号と同様のフレーム/ライン構造を持つ。また、サンプル構造はRGB(4:4:4)、量子化ビット数は16ビットである。SMPTE274やSMPTE2048−2では、上位8ビットがall0とall1のデータを、禁止コード(SAV/EAVやANC パケットのヘッダとして使うために映像データとして割り当ててはならないコード)として規定している。

【0048】

10ビットで量子化した場合に、禁止コードは000h〜003hと3FCh〜3FFhであり、12ビットで量子化した場合に、禁止コードは000h〜00FhとFF0h〜FFFhである。このため、16ビットで量子化した16ビット信号にも、10ビット又は12ビットで量子化した場合における禁止コードと同様のものを設けると、0000h〜00FFhとFF00h〜FFFFhが禁止コードとなる。このことは、映像信号として使用できるコードが”512”も制限されることになり好ましくないため、all0〜all1までを使って映像信号を表現可能とすることを検討する。

【0049】

上述したように、ワード間引き制御部12の制御により、RAM13から読み出された1chの2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号が2chの16ビット信号にワード間引きされる。この2chの16ビット信号は、2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号と、2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号である。

【0050】

その後、マッピング制御部15−1は、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号を2chの2k/23.98P−30P/4:2:2又は47.95I−60I/10ビット信号にマッピングする。また、マッピング制御部15−2は、1chの2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号を1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号にマッピングする。

【0051】

図6は、デュアルリンクへのマッピング方法の例を示す。図6Aは、LinkA,Bの伝送表現の例を示し、図6Bは、LinkA,Bの伝送する順番の例を示す。

【0052】

図6Aに示すように、LinkAは、G′チャンネルの全サンプルと、B′及びR′チャンネルの偶数番号のサンプルを伝送し、LinkBは、Aチャンネルの全サンプルと、B′及びR′チャンネルの奇数番号のサンプルを伝送する。

具体的には、LinkA,Bの各データストリームは以下の順序でサンプルを伝送する。なお、上述したように、ダッシュ「′」をつけたR′,G′,B′の信号は、ガンマ補正などが施されたR,G,B信号を示し、各信号に付けられる番号は、サンプル番号を示す。

(1)LinkAデータストリーム:B’0,G’0,R’0,G’1,B’2,G’2,R’2,G’3,・・・

(2)LinkBデータストリーム:B’1,A0,R’1,A1,B’3,A2,R’3,A3,・・・

【0053】

<マッピング構造の例>

次に、1.5G−SDIの2種類のマッピング構造の例について、図7と図8を参照して説明する。

【0054】

<第1のマッピング構造の例>

図7は、1chの30Pあるいは60I/4:2:2/16ビット信号を2ch(デュアルリンク)の1.5G−SDIにマッピングする場合に参照される第1のマッピング構造の例を示す。図7Aは、1.5G−SDIの第1のHD−SDIに含まれるYチャンネル,CBチャンネル,CRチャンネルのマッピング構造の例を示す。図7Bは、1.5G−SDIの第2のHD−SDIに含まれるYch,CBチャンネル,CRチャンネルのマッピング構造の例を示す。

【0055】

上述したように、ワード間引き制御部12は、SMPTE372:2011のFigure3又はFigure5に基づいて、4:4:4/16ビット信号をワード間引きする。ワード間引きされた一方の信号は4:2:2/16ビット信号となり、他方の信号はAchが無いこととし0:2:2/16ビット信号となる。

【0056】

次に、マッピング制御部15−1は、図7に示すように、4:2:2/16ビット信号をch1(1.5G−SDIの1番目のチャンネル)とch2(1.5G−SDIの2番目のチャンネル)に振り分けて、2chの1.5G−SDIにマッピングする。

【0057】

ここで、図7に示す第1のマッピング構造の例は、以下の条件が必要とされる。

(1)画素のMSB(Most Significant ビット:最重要ビット)2ビット(b14,b15)は、1.5G−SDIの第1及び第2リンクが測定器で映像信号として観測できるようにする。このため、1.5G−SDIの第1及び第2リンクの上位2ビットであるb8とb9に、b14,b15を多重する。

(2)1.5G−SDIの禁止コードを回避するため、加えて16ビット信号がall0〜all1の値を取ることを可能にするために、1.5G−SDIの第1及び第2リンクのb2はb3の反転ビットとする。

(3)SAV/EAV,LN,CRCCなどのデータ構造は、SMPTE292−1に規定される有効な画素サンプルが1920あるいは2048であるデータ構造に準拠する。

【0058】

第1のマッピング制御部として用いられるマッピング制御部15−1は、第1のHD−SDIのYチャンネルにG信号でこのYチャンネルと同一サンプル番号の奇数ビットをマッピングし、CBチャンネルにこのCBチャンネルと同じサンプル番号のB信号の奇数ビットをマッピングし、CRチャンネルにこのCRチャンネルと同じサンプル番号のR信号の奇数ビットをマッピングする。そして、多重すべきYチャンネルと同じサンプル番号であるG信号のG14,G15をYチャンネルの上位2ビットに多重し、多重すべきCBチャンネルと同じサンプル番号であるB信号のB14,B15をCBチャンネルの上位2ビットに多重し、多重すべきCRチャンネルと同じサンプル番号であるR信号のR14,R15をCRチャンネルの上位2ビットに多重する。また、第2のHD−SDIのYチャンネルに同じサンプル番号のG信号の偶数ビットをマッピングし、CBチャンネルに同じサンプル番号のB信号の偶数ビットをマッピングし、CRチャンネルに同じサンプル番号のR信号の偶数ビットをマッピングする。そして、多重すべきYチャンネルと同じサンプル番号であるG信号のG14,G15をYチャンネルの上位2ビットに多重し、多重すべきCBチャンネルと同じサンプル番号であるB信号のB14,B15をCBチャンネルの上位2ビットに多重し、多重すべきCRチャンネル同じサンプル番号であるR信号のR14,R15をCRチャンネルの上位2ビットに多重する。その上で、第1及び第2のHD−SDIのYチャンネル、CBチャンネル及びCRチャンネルの各チャンネルに対して、所定位置のビットを反転した反転ビットを多重する。

【0059】

ここで、4:2:2/16ビット信号は、全サンプルのG信号と、偶数サンプルのB,R信号から構成される。これらG,B,R信号それぞれの16ビットを以下のように記述する。例えば、G信号の場合には、G0(LSB:Least Significant bit最下位ビット),G1,G2,G3,G4,G5,G6,G6,G7,G8,G9,G10,G11,G12,G13,G14,G15(MSB: Most Significant bit:最上位ビット)とする。同様に、B信号についてもB0,B1,B2,…,B15とし、R信号についてもR0,R1,R2,…,R15とする。

【0060】

そして、マッピング制御部15−1は、1.5G−SDIの2chのYchに含まれる10ビットに、この4:2:2/16ビット信号のG信号である全サンプルをマッピングする。同様に、CBチャンネルの10ビットに偶数サンプルのB信号をマッピングし、CRチャンネルの10ビットに偶数サンプルのR信号をマッピングする。

【0061】

図7Aに示すように、マッピング制御部15−1は、1.5G−SDIの1番目のchでは、G,B,R信号の上位2ビットである、G15,B15,R15及びG14,B14,R14を、1.5G−SDIのch1とch2のb9,b8に多重する。1.5G−SDIの1番目のchでは、G,B,R信号のG0,B0,R0からG13,B13,R13までの奇数ビットを16ビットの上位から順番に1.5G−SDIの10ビットの上位から下位に多重する。

【0062】

図7Bに示すように、マッピング制御部15−1は、1.5G−SDIの2番目のchでは、G,B,R信号のG0,B0,R0からG13,B13,R13までに含まれる偶数ビットを多重する。この多重は、16ビットの上位から順番に1.5G−SDIの10ビットの上位から下位に対して行われる。この時、16ビット映像信号は、all0〜all1を値として持つ。ここで、1.5G−SDIに禁止コードが発生することを防ぐために、1.5G−SDIの1番目及び2番目のchについては、共にb2の値をb3の反転ビットとする。こうすることで、Ych,CBチャンネル,CRチャンネルに、1.5G−SDIの禁止コード000h〜003hと3FCh〜3FFhを発生させない。

【0063】

<第2のマッピング構造の例>

図8は、30Pあるいは60I/0:2:2/16ビット信号を1.5G−SDIにマッピングする場合に参照される第2のマッピング構造の例を示す。

【0064】

ここで、図8に示す第2のマッピング構造の例は、以下の条件が必要とされる。

(1)CBサンプルは、16ビットの同じサンプル番号のB信号のうち、上位9ビットを多重して伝送する。

(2)CRサンプルは、16ビットの同じサンプル番号のR信号のうち、上位9ビットを多重して伝送する。

(3)Yチャンネルの奇数サンプルは、1.5G−SDIリンクが測定器で映像信号として観測できる様に多重する。例えば、16ビットの同じサンプル番号のG信号のうち、上位2ビット(G15,G14)と、16ビットのB信号のうち、下位7ビットを多重して伝送する。

(4)Yチャンネルの偶数サンプルは、1.5G−SDIリンクが測定器で映像信号として観測できる様に多重する。例えば、16ビットの同じサンプル番号のG信号のうち、上位2ビット(G15,G14)と、16ビットのR信号のうち、下位7ビットを多重して伝送する。

(5)1.5G−SDIの禁止コードを回避するため、加えて画素の16ビット信号がall0〜all1の値を取ることを可能にするために、1.5G−SDI偶数及び奇数リンクのb2はb3の反転ビットとする。

(6)SAV/EAV,LN,CRCCなどのデータ構造は、SMPTE292−1に規定される有効な画素サンプルが1920あるいは2048であるデータ構造に準拠する。

【0065】

第2のマッピング制御部として用いられるマッピング制御部15−2は、第3のHD−SDIにおけるYチャンネルの偶数サンプルにB信号の下位7ビットをマッピングする。また、Yチャンネルと同一サンプル番号(偶数サンプル)であるG信号のG14,G15をYチャンネルの偶数サンプルの上位2ビットに多重し、第3のHD−SDIにおけるYチャンネルの奇数サンプルにR信号の下位7ビットをマッピングすると共に、Yチャンネルと同一サンプル番号(奇数サンプル)であるG信号のG14,G15をYチャンネルの奇数サンプルの上位2ビットに多重する。さらに、CBチャンネルに同じサンプル番号であるB信号の上位9ビットをマッピングし、CRチャンネルに同じサンプル番号であるR信号の上位9ビットをマッピングする。その上で、Yチャンネルの偶数及び奇数サンプル、CBチャンネル及びCRチャンネルの各チャンネルに対して、所定位置のビットを反転した反転ビットを多重する。

【0066】

ここで、0:2:2/16ビット信号は、G信号が無く、奇数サンプルのB,R信号によって構成される。このため、マッピング制御部15−2は、奇数サンプルのB,R信号である16ビットとG信号の上位2ビットを用いて図8に示すように、1chの1.5G−SDIに多重する。

【0067】

また、マッピング制御部15−2は、G信号の上位2ビット(G15及びG14)を、1.5G−SDIの偶数サンプル及び奇数サンプルのYchのb9,b8に多重する。偶数サンプルYchのb7〜b0には、B信号の下位7ビットをB6,B5,B4,B3,B2,B2の反転,B1,B0の順番で多重する。奇数サンプルYchのb7〜b0には、R信号の下位7ビットをR6,R5,R4,R3,R2,R2の反転,R1,R0の順番で多重する。

【0068】

また、マッピング制御部15−2は、B信号及びR信号である16ビットの上位9ビットを第2のマッピング構造に示すようにCBチャンネル及びCRチャンネルへ多重する。この多重する順番は、B15,B14,B13,B12,B11,B10,B9,B9の反転,B8,B7となる。さらに、CRチャンネルにR15,R14,R13,R12,R11,R10,R9,R9の反転,R8,R7の順番で多重する。

【0069】

この時、16ビット映像信号はall0〜all1を値として持つので、1.5G−SDIで禁止コードの発生を防ぐために、1.5G−SDIのYch,CBチャンネル,CRチャンネルともb2をb3の反転ビットとする。こうすることで、1.5G−SDIの禁止コード000h〜003hと3FCh〜3FFhが発生しないようにすることができる。

【0070】

以上の方法で、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を3chの1.5G−SDIにマッピングして伝送することが可能になる。

なお、ANC/オーディオ信号を多重する必要がある場合には、1.5G−SDI用のANC/オーディオ規格であるSMPTE291やSMPTE299に準拠して、例えば1.5G−SDIのch1から順番にデータを多重することとなる。

【0071】

<信号受信装置の内部構成例>

図9は、信号受信装置20の内部構成例を示す。

CCU2は、放送用カメラ1が備える信号送信装置10から入力する3chのHD−SDIから2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を再生する信号受信装置20を備える。本開示の第1の実施の形態に係る信号受信装置20は、プログラムを実行することにより、内部ブロックが連携して行う信号受信方法を実現する。

【0072】

信号受信装置20は、各部にクロックを供給するクロック供給回路21と、ワード多重された2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を一時記憶するRAM23を備える。

【0073】

また、信号受信装置20は、ワード多重を制御するワード多重制御部22を備える。また、ワード多重制御部22が1chの2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号と、1chの2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号を記憶するRAM24−1,24−2を備える。

【0074】

また、信号受信装置20は、上述した第1及び第2のマッピング構造に基づいて、データを抽出する抽出制御部25−1,25−2を備える。また、信号受信装置20は、信号送信装置10から入力する第1のHD−SDIである2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号をRAM26−1に書き込む書込み制御部27−1を備える。同様に、信号送信装置10から入力する第2のHD−SDIである2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号をRAM26−2に書き込む書込み制御部27−2を備える。また、信号送信装置10から入力する第3のHD−SDIである2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号をRAM26−3に書き込む書込み制御部27−3を備える。

【0075】

次に、信号受信装置20の動作例を説明する。

クロック供給回路21は、ワード多重制御部22、抽出制御部25−1,25−2、書込み制御部27−1〜27−3に画素サンプルの読出し又は書き込みに用いるクロックを供給し、このクロックにより各部が同期する。

【0076】

書込み制御部27−1〜27−3は、r:g:bが4:2:2である3chの10ビット信号からなる第1〜第3のHD−SDIをRAM26−1〜26−3に書込む。

【0077】

抽出制御部25−1,25−2は、RAM26−1〜26−3から第1〜第3のHD−SDIを読み出す。このとき、上述した信号送信装置10が備えるマッピング制御部15−1が第1のマッピング構造(図7を参照。)に従ってマッピングした処理の逆変換が行われる。具体的には、抽出制御部25−1は、RAM26−1,26−2から、1chずつ2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、2chの10ビット信号からなる第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号を抽出する。そして、抽出制御部25−1は、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号をRAM24−1に書き込む。

【0078】

ここで、抽出制御部25−1の処理について説明する。

第1の抽出制御部として用いられる抽出制御部25−1は、第1のHD−SDIのYチャンネルからG信号でこのYチャンネルと同一サンプル番号の奇数ビットを抽出し、CBチャンネルからB信号でCBチャンネルと同一サンプル番号の奇数ビットを抽出し、CRチャンネルからR信号でCRチャンネルと同一サンプル番号の奇数ビットを抽出する。そして、Yチャンネルの上位2ビットからYチャンネルと同一サンプル番号であるG信号のG14,G15を抽出し、CBチャンネルの上位2ビットからCBチャンネルと同一サンプル番号であるB信号のB14,B15を抽出し、CRチャンネルの上位2ビットからCRチャンネルと同一サンプル番号であるR信号のR14,R15を抽出する。さらに、第2のHD−SDIのYチャンネルからG信号でYチャンネルと同一サンプル番号の偶数ビットを抽出し、CBチャンネルからB信号でCBチャンネルと同一サンプル番号の偶数ビットを抽出し、CRチャンネルからR信号でCRチャンネルと同一サンプル番号の偶数ビットを抽出する。そして、Yチャンネルの上位2ビットからYチャンネルと同一サンプル番号であるG信号のG14,G15を抽出し、CBチャンネルの上位2ビットからCBチャンネルと同一サンプル番号であるB信号のB14,B15を抽出し、CRチャンネルの上位2ビットからCRチャンネルと同一サンプル番号であるR信号のR14,R15を抽出する。

【0079】

一方、抽出制御部25−2は、RAM26−3から、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置10が備えるマッピング制御部15−2が第2のマッピング構造(図8を参照。)に従ってマッピングした処理の逆変換が行われる。具体的には、抽出制御部25−2は、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、1chの16ビット信号を抽出する。この1chの16ビット信号は、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される。そして、抽出制御部25−2は、1chの2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号をRAM24−2に書き込む。

【0080】

ここで、抽出制御部25−2の処理について説明する。

第2の抽出制御部として用いられる抽出制御部25−2は、第3のHD−SDIにおけるYチャンネルの偶数サンプルからB信号の下位7ビットを抽出する。そして、Yチャンネルと同一サンプル番号(偶数サンプル)であるG信号の上位2ビットからG14,G15を抽出し、第3のHD−SDIにおけるYチャンネルと同一サンプル番号(奇数サンプル)であるG信号からR信号の下位7ビットを抽出する。また、Yチャンネルの奇数サンプルの上位2ビットからG14,G15を抽出し、CBチャンネルからB信号の上位9ビットを抽出し、CRチャンネルからR信号の上位9ビットを抽出する。

【0081】

ワード多重制御部22は、RAM24−1,24−2から読出した2chの16ビット信号をワード多重して、1chの2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号をRAM23に書き込む。具体的には、ワード多重制御部22は、r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重する。これにより、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号を生成する。そして、RAM23から適宜、この信号が再生される。

【0082】

なお、図9では、ワード多重と抽出制御とを2種類のRAMを用いて2段階で行う例を書いたが、一つのRAMを用いて2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を再生しても良い。

【0083】

以上説明した第1の実施の形態に係る伝送システムでは、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号に対して、ワード間引き、マッピングを行う。これにより、3chのHD−SDI信号を生成して出力できる。このため、放送用カメラ1は、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を、ビットレート1.5Gbpsのシリアル・デジタルデータに変換してCCU2に伝送できる。

【0084】

一方、CCU2は、ビットレート1.5Gbpsのシリアル・デジタルデータから2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を再生できる。つまり、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を、従来用いている1.5Gbpsシリアルインタフェースの多chで伝送することが出来る。このため、信号伝送に当たり、既存の設備を有効に活用することができる。

【0085】

<2.第2の実施の形態>

[2k/47.95P−60P/4:4:4/16ビット信号を1.5G−SDI 6chにマッピングして伝送する例]

【0086】

<信号送信装置の内部構成例>

図10は、信号送信装置30の内部構成例を示す。

本開示の第2の実施の形態に係る放送用カメラ1は、2k/47.95P−60P/4:4:4/16ビット信号を3chのHD−SDIによってCCU2が備える信号受信装置40に出力する信号送信装置30を備える。以下の説明では、47.95P,48P,50P,59.94P,60Pを、「47.95P−60P」と略記する場合がある。

【0087】

信号送信装置30は、各部にクロックを供給するクロック供給回路31と、2k/47.95P−60P/4:4:4/16ビット信号を記憶するRAM33を備える。また、信号送信装置30は、上述した第1の実施の形態に係る信号送信装置10におけるワード間引き制御部12、マッピング制御部15−1,15−2、読出し制御部17−1〜17−3を二組備える。このため、各制御ブロックによってマッピングされるHD−SDIを記憶するRAMも二組備える。

【0088】

つまり、信号送信装置30は、RAM33から読出したr:g:bが4:4:4である1chの16ビット信号を一ラインずつ交互に間引いて2チャンネルのインターレース信号(2k/47.95I−60I/4:4:4/16ビット信号)とした映像信号をRAM34−1,34−2に書き込むライン間引き制御部32を備える。また、ライン間引き制御部32がライン間引きしたデータを書き込むRAM34−1,34−2を備える。また、ワード間引きを制御するワード間引き制御部35−1,35−2と、ワード間引き制御部35−1,35−2がワード間引きしたデータを書き込むRAM36−1〜36−4とを備える。

【0089】

また、信号送信装置30は、RAM36−1から読出した2k/47.95I−60I/4:2:2/16ビット信号を、第1のマッピング構造(図7を参照。)に従ってマッピングするマッピング制御部37−1を備える。また、マッピング制御部37−1がマッピングした2chの10ビット信号を記憶するRAM38−1,38−2を備える。

【0090】

また、信号送信装置30は、RAM36−2から読出した2k/47.95I−60I/0:2:2/16ビット信号を、第2のマッピング構造に従ってマッピングするマッピング制御部37−2を備える。また、マッピング制御部37−2がマッピングした1chの10ビット信号を記憶するRAM38−3を備える。

【0091】

また、信号送信装置30は、RAM36−3から読出した2k/47.95I−60I/4:2:2/16ビット信号を、第1のマッピング構造に従ってマッピングするマッピング制御部37−3を備える。また、マッピング制御部37−1がマッピングした2chの10ビット信号を記憶するRAM38−4,38−5を備える。

【0092】

また、信号送信装置30は、RAM36−4から読出した2k/47.95I−60I/0:2:2/16ビット信号を、第2のマッピング構造に従ってマッピングするマッピング制御部37−3を備える。また、マッピング制御部37−4がマッピングした1chの10ビット信号を記憶するRAM38−6を備える。

【0093】

そして、読出し制御部39−1〜39−6は、RAM38−1〜38−6から読み出した二組の第1〜第3のHD−SDIを出力する。このため、信号送信装置30は、RAM38−1〜38−6からそれぞれ読出したデータの画素サンプルを6チャンネルのHD−SDI ch1〜ch6として出力する読出し制御部39−1〜39−6を備える。

【0094】

次に、各部の動作例を説明する。

クロック供給回路31は、ライン間引き制御部32,ワード間引き制御部35−1,35−2、マッピング制御部37−1〜37−4,及び読出し制御部39−1〜39−6に画素サンプルの読出し又は書き込みに用いるクロックを供給する。各部は、この供給されたクロックにより同期して動作する。

【0095】

不図示の撮像素子から入力する2k/47.95P−60P/4:4:4/16ビット信号は、RAM33に保存される。

ライン間引き制御部32は、RAM33に保存された2k/47.95P−60P/4:4:4/16ビット信号を一ラインずつ交互に読み出して、RAM34−1,34−2に保存する。このとき、RAM34−1には、1chの2k/47.95I−60I/4:4:4/16ビット信号が書き込まれる。一方、RAM34−2には、1chの2k/47.95P−60P/4:4:4/16ビット信号が書き込まれる。

【0096】

ワード間引き制御部35−1,35−2は、それぞれRAM34−1,34−2から読出した画素サンプルより、SMPTE372のFigure4,6,7,8,9と同じ方式でワード間引きを行う。このとき、RAM36−1には、2k/47.95I−60I/4:2:2/16ビット信号が書き込まれ、RAM36−2には、2k/47.95I−60I/0:2:2/16ビット信号が書き込まれる。同様に、RAM36−3には、2k/47.95I−60I/4:2:2/16ビット信号が書き込まれ、RAM36−4には、2k/47.95I−60I/0:2:2/16ビット信号が書き込まれる。

【0097】

マッピング制御部37−1は、RAM36−1から読出した2k/47.95I−60I/4:2:2/16ビット信号を、2chの10ビット信号にマッピングし直してRAM38−1,38−2に書き込む。このとき、RAM38−1には、奇数ビットから抽出した1chの2k/47.95I−60I/4:2:2/10ビット信号が書き込まれる。一方、RAM38−2には、偶数ビットから抽出した1chの2k/47.95I−60I/4:2:2/10ビット信号が書き込まれる。

【0098】

マッピング制御部37−2は、RAM36−2から読出した2k/47.95I−60I/0:2:2/16ビット信号を、1chの2k/47.95I−60I/4:2:2/10ビット信号にマッピングし直してRAM38−3に書き込む。

【0099】

マッピング制御部37−3は、RAM36−3から読出した2k/47.95I−60I/4:2:2/16ビット信号を、2chの10ビット信号にマッピングし直してRAM38−4,38−5に書き込む。このとき、RAM38−4には、奇数ビットから抽出した1chの2k/47.95I−60I/4:2:2/10ビット信号が書き込まれる。一方、RAM38−5には、偶数ビットから抽出した1chの2k/47.95I−60I/4:2:2/10ビット信号が書き込まれる。

【0100】

マッピング制御部37−4は、RAM36−4から読出した2k/47.95I−60I/0:2:2/16ビット信号を、1chの2k/47.95I−60I/4:2:2/10ビット信号にマッピングし直してRAM38−6に書き込む。

【0101】

そして、読出し制御部39−1〜39−6は、クロック供給回路31から供給された基準クロックでRAM38−1〜38−6から6chの2k/47.95I−60I/4:2:2/10ビット信号を読出す。そして、6chのHD−SDI ch1〜ch6として出力する。

【0102】

なお、本例では、ライン間引き、ワード間引き及びマッピング制御を行うため、4種類のメモリ(RAM33,RAM34−1,34−2,RAM36−1〜36−4、RAM38−1〜38−6)を用いて、3段階で行う例を示した。しかし、一つのメモリを使って、ライン間引き及びワード間引きしたデータをマッピングし直して、6chのHD−SDIとして出力しても良い。

【0103】

図11は、2k/47.95P−60P/4:4:4/16ビット信号をライン間引き、ワード間引き及びマッピング制御を行う処理の概略例を示す。

【0104】

まず、SMPTE372:2011のFigure2に基づいて2k/47.95P−60P/4:4:4/16ビット信号をライン間引きし、2chの2k/47.95I−60I/4:4:4/16ビット信号に変換する。

【0105】

次にSMPTE372:2011のFigure3又は5に基づいて、4:4:4/16ビット信号をワード間引きする。一方の信号は4:2:2/16ビット信号となり、他方の信号はAchが無いこととし0:2:2/16ビット信号となる。この4:2:2/16ビット信号を、第1及び第2のマッピング構造(図7と図8を参照。)に従って1/5G−SDIに多重することで、合計6chの1/5G−SDIで伝送することが可能となる。

【0106】

なお、ANC/オーディオ信号を多重する必要がある場合には、1.5G−SDI用のANC/オーディオ規格であるSMPTE291やSMPTE299に準拠して、例えば1.5G−SDIのch1から順番にデータを多重する。

【0107】

図12は、ライン間引きの例を示す。

ここでは、デュアルリンクインタフェースのライン番号とパッケージの例を用いてライン間引きを説明する。

【0108】

まず、ライン間引き制御部32は、2k/47.95P−60P/4:4:4/16ビット信号をチャンネル1,2にライン間引きする。これにより、ライン間引きされた信号は、2chの2k/47.95I−60I/4:4:4/16ビット信号に変換される。

その後、上述したようにマッピング制御部37−1〜37−4は、第1及び第2のマッピング構造(図7及び図8参照)に基づいてデータをマッピングして、読出し制御部39−1〜39−6が6chのHD−SDIを出力する。

【0109】

<信号受信装置の内部構成例>

図13は、信号受信装置40の内部構成例を示す。

CCU2は、放送用カメラ1が備える信号送信装置30から入力する6chのHD−SDIから2k/47.95P−60P/4:4:4/16ビット信号を再生する信号受信装置40を備える。

【0110】

信号受信装置40は、各部にクロックを供給するクロック供給回路41と、2k/47.95P−60P/4:4:4/16ビットの映像信号を記憶するRAM43を備える。また、上述した第1の実施の形態に係る信号受信装置20における書込み制御部27−1〜27−3と、抽出制御部25−1,25−2と、ワード多重制御部22を二組備える。このため、各制御ブロックによってマッピングされるHD−SDIを記憶するRAMも二組備える。

【0111】

つまり、信号受信装置40は、信号送信装置30から入力する6本のHD−SDI ch1〜ch6をそれぞれ記憶するRAM48−1〜48−6を備える。このHD−SDI ch1〜ch6は、6chの2k/47.95I−60I/4:2:2/10ビット信号によって構成される。そして、書込み制御部49−1〜49−6は、信号送信装置30から入力する二組の第1〜第3のHD−SDIをRAM48−1〜48−6に書込む。このため、書込み制御部49−1〜49−6は、クロック供給回路41から供給されるクロックに合わせて、入力した6本のHD−SDI ch1〜ch6をRAM48−1〜48−6に書き込む制御を行う。

【0112】

また、信号受信装置40は、上述した第1及び第2のマッピング構造(図7及び図8参照)に基づいて、データを抽出する抽出制御部47−1〜47−4を備える。また、信号受信装置40は、信号送信装置30から入力する第1のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−1に書き込む書込み制御部49−1を備える。同様に、信号送信装置30から入力する第2のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−2に書き込む書込み制御部49−2を備える。また、信号送信装置30から入力する第3のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−3に書き込む書込み制御部49−3を備える。

【0113】

また、信号受信装置40は、信号送信装置30から入力する第4のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−4に書き込む書込み制御部49−4を備える。同様に、信号送信装置30から入力する第5のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−5に書き込む書込み制御部49−5を備える。また、信号送信装置30から入力する第6のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−6に書き込む書込み制御部49−6を備える。

【0114】

また、信号受信装置40は、ワード多重を制御するワード多重制御部45−1,45−2と、ワード多重制御部45−1,45−2が一時的に多重したデータを書き込むRAM44−1,44−2と、を備える。ワード多重制御部45−1,45−2は、所定のタイミングを制御してSMPTE372のFigure4,6,7,8,9の逆変換のワード単位で読み出す。この読出しタイミングは、(RAM46−1,46−2)、(RAM46−3,46−4)毎に定まる。

【0115】

また、信号受信装置40は、ワード多重制御部45−1,45−2によって多重された画素サンプルを、一ラインずつ交互に多重するライン多重制御部42を備える。具体的には、ライン多重制御部42は、RAM44−1,44−2から画素サンプルを読出し、一ラインずつ交互に多重して、多重したデータを書き込むRAM43に書き込む。これにより、RAM43には、2k/47.95P−60P/4:4:4/16ビット信号が保存され、適宜、この信号が再生される。

【0116】

次に、信号受信装置40の動作例を説明する。

クロック供給回路41は、ライン多重制御部42,ワード多重制御部45−1,45−2、抽出制御部47−1〜47−4、及び書込み制御部49−1〜49−6に画素サンプルの読み出し又は書き込みに用いるクロックを供給し、このクロックにより各部が同期する。

【0117】

抽出制御部47−1は、RAM48−1,48−2から、1chずつ2k/47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置30が備えるマッピング制御部37−1が第1のマッピング構造(図7を参照。)に従ってマッピングした処理の逆変換が行われる。そして、抽出制御部47−1は、1chの2k/47.95I−60I/4:2:2/16ビット信号をRAM46−1に書き込む。

【0118】

抽出制御部47−2は、RAM48−3から、1chの2k/47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置10が備えるマッピング制御部37−2が第2のマッピング構造(図8を参照。)に従ってマッピングした処理の逆変換が行われる。そして、抽出制御部47−2は、1chの2k/47.95I−60I/0:2:2/16ビット信号をRAM46−2に書き込む。

【0119】

同様に、抽出制御部47−3は、RAM48−4,48−5から、1chずつ2k/47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置30が備えるマッピング制御部37−3が第1のマッピング構造(図7を参照。)に従ってマッピングした処理の逆変換が行われる。そして、抽出制御部47−3は、1chの2k/47.95I−60I/4:2:2/16ビット信号をRAM46−3に書き込む。

【0120】

抽出制御部47−4は、RAM48−6から、1chの2k/47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置10が備えるマッピング制御部37−4が第2のマッピング構造(図8を参照。)に従ってマッピングした処理の逆変換が行われる。そして、抽出制御部47−4は、1chの2k/47.95I−60I/0:2:2/16ビット信号をRAM46−4に書き込む。

【0121】

ワード多重制御部45−1は、RAM46−1,46−2から読出した2chの2k/47.95I−60I/4:2:2/16ビット信号及び2k/47.95I−60I/0:2:2/16ビット信号をワード多重する。この結果として得た、1chの2k/47.95I−60I/4:4:4/16ビット信号をRAM44−1に書き込む。

【0122】

同様に、ワード多重制御部45−2は、RAM46−3,46−4から読出した2chの2k/47.95I−60I/4:2:2/16ビット信号及び2k/47.95I−60I/0:2:2/16ビット信号をワード多重する。この結果として得た、1chの2k/47.95I−60I/4:4:4/16ビット信号をRAM44−2に書き込む。

【0123】

ライン多重制御部42は、RAM44−1から読み出した2k/47.95I−60I/4:4:4/16ビット信号と、RAM44−2から読み出した2k/47.95I−60I/4:4:4/16ビット信号を一ラインずつ交互にライン多重する。そして、ライン多重して得た、1chの2k/47.95P−60P/4:4:4/16ビット信号をRAM43に書き込む。そして、RAM43から適宜、この信号が再生される。

【0124】

なお、図13では、抽出制御、ワード多重、ライン多重を3種類のRAMを用いて3段階で行う例を書いたが、一つのRAMを用いて2k/47.95P−60P/4:4:4/16ビット/4:4:4/10ビット,12ビット信号を生成しても良い。

【0125】

以上説明した第2の実施の形態によれば、信号送信装置30は、2k/47.95P−60P/4:4:4/16ビット信号の画素サンプルを、ライン間引き、ワード間引き及びマッピング制御を行うことで、6チャンネルのHD−SDIで伝送できる。このため、放送用カメラ1は、2k/47.95P−60P/4:4:4/16ビット信号を、ビットレート1.5Gbpsのシリアル・デジタルデータに変換してCCU2に伝送できる。

【0126】

一方、CCU2は、ビットレート1.5Gbpsのシリアル・デジタルデータから2k/47.95P−60P/4:4:4/16ビット信号を再生できる。つまり、4k×2k信号を、従来用いている1.5Gbpsシリアルインタフェースの多chで伝送することが出来る。このため、信号伝送に当たり、既存の設備を有効に活用することができる。

【0127】

このように上述した第1及び第2の実施の形態に係る信号送信装置及び信号受信装置によれば、1920×1080あるいは2048×1080/23.98P−60P/4:4:4/16ビット信号を3ch又は6chの1.5G−SDIにマッピングして伝送することを可能としている。また、1.5G−SDI3ch又は6chの信号を1本の光ファイバーで伝送する際には、CWDM/DWDM波長多重技術を使うことが出来る。

【0128】

また、3ch又は6chで出力される全てのHD−SDIは、波形モニタ等を用いてユーザが映像又は波形として観測することが可能である。このため、実際の機器開発において映像を確認しながら開発できることは非常に有用である。

【0129】

また、SMPTE274に準じた禁止コードを設けると16ビット信号では、0000h−00FFh及びFF00h−FFFFh信号が禁止コードとなり、512ものコードが使えなくなり映像表現の大きな制限要因となる。しかし、上述した本方式では禁止コードを設ける必要がなく、映像信号としてall0〜all1まで伝送可能であるので非常に有用である。また、RAWデータ(いわゆる、生のデータ)を編集する用途にも有用である。

【0130】

また、SMPTE S292−1に準拠して映像信号を伝送するので、SAV/EAV,LN,CRCCはSMPTE S274,S292−1に準拠して付ける。また、ANC/オーディオデータを多重する場合には、SMPTE S291,S299−1に準拠して、6chの1.5G−SDIのうち、第1chから第6chまで順番に多重することが可能である。すなわち、新たに規定を設けることなく、現状のHD関連規格に準じてANC/オーディオなどのデータを多重することが可能である。

【0131】

また、本開示は上述した実施の形態に限られるものではなく、特許請求の範囲に記載した本開示の要旨を逸脱しない限りその他種々の応用例、変形例を取り得ることは勿論である。

【符号の説明】

【0132】

1…放送用カメラ、2…CCU、5…信号伝送システム、10…信号送信装置、11…クロック供給回路、12…ワード間引き制御部、13…RAM、14−1,14−2…RAM、15−1,15−2…マッピング制御部、16−1〜16−3…RAM、17−1〜17−3…読出し制御部、20…信号受信装置、21…クロック供給回路、22…ワード多重制御部、23…RAM、24−1,24−2…RAM、25−1,25−2…抽出制御部、26−1〜26−3…RAM、27−1〜27−3…書込み制御部、30…信号送信装置、40…信号受信装置

【技術分野】

【0001】

本開示は、例えば、撮像素子から出力される16ビットの映像信号を伝送する場合に適用して好適な信号送信装置、信号送信方法、信号受信装置、信号受信方法及び信号伝送システムに関する。

【背景技術】

【0002】

従来、撮像素子が出力する1フレームの映像信号が1920サンプル×1080ライン(以下、mサンプル×nラインを「m×n」とも略記する。)であるHD(High Definition)信号を伝送するために標準化が行われていた。この標準化を行う国際協会には、ITU(International Telecommunication Union)やSMPTE(Society of Motion Picture and Television Engineers)が知られている。

【0003】

例えば、SMPTE274Mには、1920×1080の映像信号のサンプル構造が規定され、SMPTE292Mには、HDTVシステムのシリアルデジタルインタフェースが規定されている。また、SMPTE372Mには、SMPTE292Mに規定されるデータ構造をベースとして規格化された、LinkA,Bを用いるデュアルリンクHD−SDIインタフェースが規定されている。以下の説明では、1920×1080又は2048×1080のことを、「2k」とも略称し、3840×2160又は4096×2160のことを、「4k」又は「4k×2k」とも略称する。また、1.5Gbpsで映像信号を伝送可能なHD−SDIインタフェースを、「1.5G−SDI」とも呼ぶ。

【0004】

ここで、SMPTE2048−1やSMPTE2036−1(UHDTV)で規定される4096規格や3840規格における画素のサンプル構造は、図14に示す以下の2種類がある。

【0005】

図14は、4k規格のサンプル構造の例を示す説明図である。

図14Aと図14Bの説明に用いるフレームは、4k×2kのサンプル構造で1フレームを構成する。4k規格のサンプル構造は、以下の3種類がある。なお、SMPTE規格において、R′G′B′のように、ダッシュ「′」をつけた信号は、ガンマ補正などが施された信号を示す。

【0006】

図14Aは、R′G′B′,Y′Cb′Cr′ 4:4:4システムにおける画素サンプルの例である。このシステムでは、全サンプルにRGB又はYCbCrのコンポーネントが含まれる。

図14Bは、Y′Cb′Cr′ 4:2:2システムにおける画素サンプルの例である。このシステムでは、偶数サンプルにYCbCr、奇数サンプルにYのコンポーネントが含まれる。

【0007】

また、特許文献1には、4k×2kの超高解像度信号の一種である3840×2160/30P,30/1.001P/4:4:4/12ビット信号を、ビットレート10Gbps以上で伝送する技術が開示されている。なお、[3840×2160/30P]と示した場合には、[水平方向の画素サンプル数]×[垂直方向のライン数]/[1秒当りのフレーム数]を示す。また、[4:4:4]は、原色信号伝送方式である場合、[赤信号R:緑信号G:青信号B]の比率を示し、色差信号伝送方式である場合、[輝度信号Y:第1色差信号Cb:第2色差信号Cr]の比率を示す。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2005−328494号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

ところで、SMPTEによって規定される従来の伝送規格は、10ビット又は12ビットの映像信号を10ビット/ワードのHD−SDIで伝送することを前提としていた。しかし、近年は、撮像素子から出力される16ビットの映像信号を10ビット/ワードのHD−SDIを用いて伝送しようとする要望が高まっている。16ビットの映像信号としては、例えば、2k/4:4:4/16ビット信号があり、この信号は、2kサンプルのG信号、B信号及びR信号から構成される。しかし、このような、2k/23.98P−60P/16ビットの映像信号を伝送するためのインタフェースあるいはインターフェースデータ規格や提案がなかった。

【0010】

本開示はこのような状況に鑑みて成されたものであり、撮像素子から出力される16ビットの映像信号を伝送するためのインタフェースを提供することを目的とする。

【課題を解決するための手段】

【0011】

本開示は、撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号、及びr:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングする。

次に、ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造に従って、r:g:bが4:2:2である2chの10ビット信号からなる第1及び第2のHD−SDIにマッピングすると共に、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造に従って、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIにマッピングし、第1〜第3のHD−SDIを出力するものである。

【0012】

また、本開示は撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:2:2である3chの10ビット信号からなる第1〜第3のHD−SDIを記憶部に書込む。

次に、記憶部から読み出した、2chの10ビット信号からなる第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号を抽出すると共に、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号を抽出する。

そして、r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重することによって、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号を生成するものである。

【0013】

このようにしたことで、撮像素子から出力される16ビットの映像信号を既存のHD−SDIにマッピングして伝送することが可能となった。

【発明の効果】

【0014】

本開示によれば、撮像素子から出力される16ビットの映像信号を、第1及び第2のマッピング構造に基づいて、r:g:bが4:2:2である10ビット信号からなる第1〜第3のHD−SDIとして伝送することが可能となる。このため、既存の伝送規格に準じて16ビットの映像信号を伝送することができる。

【図面の簡単な説明】

【0015】

【図1】本開示の第1の実施の形態に係るテレビジョン放送局用の信号伝送システムの全体構成を示す図である。

【図2】本開示の第1の実施の形態に係る信号送信装置の内部構成例を示すブロック図である。

【図3】通常のベイヤ構造と倍密ベイヤ構造の例を示す説明図である。

【図4】1.5GbpsのHD−SDI(シリアル・デジタルデータ)の1ライン分のデータ構造例を示す説明図である。

【図5】本開示の第1の実施の形態に係る1chの2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号をワード間引き及びマッピング制御を行う処理の概略例を示す説明図である。

【図6】デュアルリンクの伝送表現の例を示す説明図である。

【図7】本開示の第1の実施の形態に係る30Pあるいは60I/4:2:2/16ビット信号を2ch(デュアルリンク)の1.5G−SDIにマッピングする場合に参照される第1のマッピング構造の例を示す説明図である。

【図8】本開示の第1の実施の形態に係る30Pあるいは60I/0:2:2/16ビット信号を1.5G−SDIにマッピングする場合に参照される第2のマッピング構造の例を示す説明図である。

【図9】本開示の第1の実施の形態に係る信号受信装置の内部構成例を示すブロック図である。

【図10】本開示の第2の実施の形態に係る信号送信装置の内部構成例を示すブロック図である。

【図11】本開示の第2の実施の形態に係る2k/47.95P−60P/4:4:4/16ビット信号をライン間引き、ワード間引き及びマッピング制御を行う処理の概略例を示す説明図である。

【図12】ライン間引きの例を示す説明図である。

【図13】本開示の第2の実施の形態に係る信号受信装置の内部構成例を示すブロック図である。

【図14】UHDTV規格のサンプル構造の例を示す説明図である。

【発明を実施するための形態】

【0016】

以下、本開示を実施するための形態(以下、実施の形態とする。)について説明する。なお、説明は以下の順序で行う。

1.第1の実施の形態(2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を1.5G−SDI 3chにマッピングして伝送する例)

2.第2の実施の形態(2k/47.95P−60P/4:4:4/16ビット信号を1.5G−SDI 6chにマッピングして伝送する例)

3.変形例

【0017】

<1.第1の実施の形態>

[2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を1.5G−SDI 3chにマッピングして伝送する例]

【0018】

始めに、本開示の第1の実施の形態について、図1〜図9を参照して説明する。

本開示の第1の実施の形態に係る信号送信装置10は、プログラムを実行することにより、内部ブロックが連携して行う信号送信方法を実現する。始めに、信号送信装置10の構成例を説明する。

【0019】

ここでは、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を1.5G−SDI 3chにマッピングして伝送する例について説明する。

不図示の撮像素子が出力する映像信号は、m×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビットで規定される。このとき、r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインである。そして、この16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする。

【0020】

また、a−bが23.98P,24P,25P,29.97P,30Pである場合に、「23.98P−30P」と略記することがある。また、a−bが47.95I,48I,50I,59.94I,60Iである場合に、「47.95I−60I」と略記することがある。また、例えば、「2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号」と表記した場合、以下の意味とする。すなわち、撮像素子が1920×1080あるいは2048×1080個の画素で構成され、映像信号のフレームレートが23.98P−30Pあるいはフィールドレートが47.95I−60Iであって、画素が出力する映像信号の量子化ビットが16ビットという意味である。

【0021】

図1は、本実施の形態を適用したテレビジョン放送局用の信号伝送システム5の全体構成を示す図である。

この信号伝送システム5は、複数台の放送用カメラ1とCCU(カメラコントロールユニット)2とで構成されており、各放送用カメラ1が光ファイバーケーブル3でCCU2に接続されている。放送用カメラ1は、シリアル・デジタル信号を送信する信号送信方法を適用した信号送信装置として用いられ、CCU2は、シリアル・デジタル信号を受信する信号受信方法を適用した信号受信装置として用いられる。そして、放送用カメラ1とCCU2を組み合わせた信号伝送システム5は、シリアル・デジタル信号を送受信する信号伝送システムとして用いられる。

【0022】

複数の放送用カメラ1は、同一構成のものである。そして、放送用カメラ1は、デジタルシネマ用の2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を生成し、CCU2に送信する信号送信装置として機能する。

【0023】

CCU2は、各放送用カメラ1を制御したり、各放送用カメラ1から映像信号を受信したり、各放送用カメラ1のモニタに他の放送用カメラ1で撮影中の映像を表示させるための映像信号(リターンビデオ)を送信するユニットである。CCU2は、各放送用カメラ1から映像信号を受信する信号受信装置として機能する。

【0024】

<DWDM/CWDM波長多重伝送技術>

ここで、DWDM/CWDM波長多重伝送技術について説明する。

複数の波長の光を1本の光ファイバーに多重して伝送する方法をWDM(Wavelength Division Multiplexing)と言う。WDMは波長間隔に応じて大まかに以下の3つの方式に分けられる。

【0025】

(1)2波長多重方式

1.3μm、1.55μmといった離れた波長を、2波〜3波程度多重して1本の光ファイバーで伝送する方式である。

【0026】

(2)DWDM(Dense Wavelength Division Multiplexing)方式

特に1.55μm帯において光の周波数で25GHz、50GHz、100GHz、200Ghz..波長で約0.2nm、0.4nm、0.8nm..間隔で高密度に光を多重して伝送する方法をDWDMと言う。ITU−T(International Telecommunication Union Telecommunication standardization sector)にて中心波長他の標準化が行われた。DWDMは波長間隔が100GHzと狭いために数十〜百と多重数を多く取ることが出来、超大容量の通信が可能である。しかし、発振波長幅が波長間隔100GHzより十分狭いことが必要であるとともに中心波長がITU−T規格に一致するよう半導体レーザを温度制御する必要があるため、デバイスが高価であり、システムの消費電力が大きくなる。

【0027】

(3)CWDM(Coarse Wavelength Division Multiplexing)方式

一方で近年CWDMと呼ばれる、波長間隔を10nm〜20nmとDWDMより一桁以上広く取った波長多重技術が注目されるようになってきた。波長間隔が比較的広いために半導体レーザの発振波長幅がDWDMほど狭帯域である必要が無く、また半導体レーザを温度制御する必要も無いので、システムを低価格、低消費電力化することが可能である。DWDMほどの大容量が必要でないシステムに有効である。中心波長例については、現在のところ4ch構成で以下のものが一般的である。例えば、1.511μm、1.531μm、1.551μm、1.571μm、8ch構成で1.471μm、1.491μm、1.511μm、1.531μm、1.551μm、1.571μm、1.591μm、1.611μmがある。

【0028】

<信号送信装置10の内部構成例>

図2は、信号送信装置10の内部構成例を示す。

本開示の第1の実施の形態に係る放送用カメラ1は、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を3chのHD−SDIに多重した後、CCU2が備える信号受信装置20に出力する信号送信装置10を備える。

【0029】

信号送信装置10は、各部にクロックを供給するクロック供給回路11と、不図示の撮像素子が出力する2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を記憶するRAM13を備える。また、信号送信装置10は、RAM13から読出したデータのワード間引きを制御するワード間引き制御部12と、ワード間引き制御部12がワード間引きしたデータを書き込むRAM14−1,14−2とを備える。

【0030】

また、信号送信装置10は、RAM14−1から読出した2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号を、後述する第1のマッピング構造(図7を参照。)に従ってマッピングするマッピング制御部15−1を備える。また、マッピング制御部15−1によってマッピングされた2chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号を記憶するRAM16−1,16−2を備える。

【0031】

また、信号送信装置10は、RAM14−2から読出した2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号を、後述する第2のマッピング構造(図8を参照。)に従ってマッピングするマッピング制御部15−2を備える。また、マッピング制御部15−2によってマッピングされた1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号を記憶するRAM16−3を備える。

【0032】

また、信号送信装置10は、RAM16−1〜16−3から読出したデータの画素サンプルを3chのHD−SDIとして出力する読出し制御部17−1〜17−3を備える。

【0033】

次に、各部の動作例を説明する。

クロック供給回路11は、ワード間引き制御部12、マッピング制御部15−1,15−2及び読出し制御部17−1〜17−3に画素サンプルの読出し又は書き込みに用いるクロックを供給する。各部は、この供給されたクロックにより同期して動作する。

【0034】

ワード間引き制御部12は、RAM13から読出した画素サンプルより、SMPTE372のFigure4,6,7,8,9と同じ方式でワード間引きを行う。このとき、ワード間引き制御部12は、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引く。そして、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングする。同様に、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングする。このとき、RAM14−1には、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号が書き込まれる。一方、RAM14−2には、1chの2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号が書き込まれる。

【0035】

次に、マッピング制御部15−1は、ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造(後述する図7参照)に従って、r:g:bが4:2:2である第1及び第2のHD−SDIにマッピングする。この第1及び第2のHD−SDIは、2chの10ビット信号からなる。

このとき、マッピング制御部15−1は、RAM14−1から読出した2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号を、2chの10ビット信号にマッピングし直してRAM16−1,16−2に書き込む。このとき、RAM16−1には、2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号の奇数ビットから抽出した1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号が書き込まれる。一方、RAM16−2には、2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号の偶数ビットから抽出した1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号が書き込まれる。

【0036】

一方、マッピング制御部15−2は、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造(後述する図8参照)に従って、r:g:bが4:2:2である第3のHD−SDIにマッピングする。この第3のHD−SDIは、1chの10ビット信号からなる。

このとき、マッピング制御部15−2は、RAM14−2から読出した2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号を、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号にマッピングし直してRAM16−3に書き込む。

なお、マッピング制御部15−1,15−2の詳細な動作例については後述する。

【0037】

そして、読出し制御部17−1〜17−3は、クロック供給回路11から供給された基準クロックでRAM16−1〜16−3から読み出した第1〜第3のHD−SDIをHD−SDI ch1〜ch3として出力する。

【0038】

なお、本例では、ワード間引きとマッピング制御を行うため、3種類のメモリ(RAM13,RAM14−1,14−2、RAM16−1〜16−3)を用いて、2段階で間引き制御を行う処理を説明した。しかし、一つのメモリを使って、ワード間引き及びマッピング制御を行った後、3chのHD−SDIとして出力しても良い。

【0039】

ここで、4k×2kの16ビット信号を出力する不図示の撮像素子における構造の通常のベイヤ構造と倍密ベイヤ構造の違いについて説明する。

図3は、倍密ベイヤ構造の4k×2kのサンプル構造とした画素が出力する映像信号の例を示す。

【0040】

従来、ベイヤ構造の撮像素子を用いた撮像装置が一般に知られている。この撮像素子は、色フィルタを介して被写体の像光を取込み、像光の強さに応じて映像信号を出力する。そして、後続の処理部が映像信号に所定の処理を加えることによって、撮像装置がビューファインダや外部の表示装置に映像を表示させることを可能とする。撮像素子には、一般にR,G,B信号のような原色信号をそれぞれ出力可能なR,G,B画素が所定のパターンで配置されており、R,G,B画素をどのように配置するかによって、解像度が異なっている。

【0041】

図3Aは、通常のベイヤ構造の例を示す。

通常のベイヤ構造では、対角線上にそれぞれ2個のG画素を配置し、この対角線に直交する対角線上にR,B画素を配置する構成としている。しかし、通常のベイヤ構造では、一番画素数の多いGchでも4k×2kの半分の画素数しか得られない。

【0042】

図3Bは、倍密ベイヤ構造の例を示す。

倍密ベイヤ構造では、図3Aに示した通常のベイヤ構造とした画素を45度斜めに配列してある。この画素は、通常のベイヤ構造における画素に対して、縦横を半分にしたサイズとしてある。このため、倍密ベイヤにおけるGchは4k×2kの画素数に相当する解像度を持つ。その分、1つの画素のサイズは小さくなるが、斜めにすることで、通常のベイヤ構造でGchに4k×2kの画素数を持たせる場合よりも小さくせずに済む。このため、解像度と感度をバランスよく両立でき、通常のベイヤ構造に対する利点となる。

【0043】

そして、不図示の変換部により、4k×2kの倍密ベイヤ構造とした撮像素子が出力する4k×2kの16ビット信号を2kの16ビット信号に変換した後、本実施の形態に係る信号伝送システム1を用いて映像信号を伝送するようにしている。

【0044】

次に、1ラインのHD−SDIフォーマットで規定されたシリアルデータの構成例について説明する。

図4は、1.5GbpsのHD−SDI(シリアル・デジタルデータ)の1ライン分のデータ構造例である。

【0045】

ここでは、Yチャンネル、CB,CRチャンネルの2種類のチャンネルのデータ構造例を示している。各チャンネルに含まれる、ライン番号LN及び誤り検出符号CRCを含めたものをEAV,映像データ領域(アクティブライン)及びSAVとして示す。そして、付加データの領域を含めたものを水平補助データスペース(HANCデータ領域)として示している。

なお、水平補助データスペースには、オーディオ信号がマッピングされる場合がある。このとき、オーディオ信号に補完データを追加して水平補助データスペースを構成し、入力するHD−SDI信号との同期を取るようにする。

【0046】

図5は、1chの2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号をワード間引き及びマッピング制御を行う処理の概略例を示す。

【0047】

2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号は、SMPTE274やSMPTE2048−2に規定される1920×1080,2048×1080/8ビット,10ビット,12ビット信号と同様のフレーム/ライン構造を持つ。また、サンプル構造はRGB(4:4:4)、量子化ビット数は16ビットである。SMPTE274やSMPTE2048−2では、上位8ビットがall0とall1のデータを、禁止コード(SAV/EAVやANC パケットのヘッダとして使うために映像データとして割り当ててはならないコード)として規定している。

【0048】

10ビットで量子化した場合に、禁止コードは000h〜003hと3FCh〜3FFhであり、12ビットで量子化した場合に、禁止コードは000h〜00FhとFF0h〜FFFhである。このため、16ビットで量子化した16ビット信号にも、10ビット又は12ビットで量子化した場合における禁止コードと同様のものを設けると、0000h〜00FFhとFF00h〜FFFFhが禁止コードとなる。このことは、映像信号として使用できるコードが”512”も制限されることになり好ましくないため、all0〜all1までを使って映像信号を表現可能とすることを検討する。

【0049】

上述したように、ワード間引き制御部12の制御により、RAM13から読み出された1chの2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号が2chの16ビット信号にワード間引きされる。この2chの16ビット信号は、2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号と、2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号である。

【0050】

その後、マッピング制御部15−1は、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号を2chの2k/23.98P−30P/4:2:2又は47.95I−60I/10ビット信号にマッピングする。また、マッピング制御部15−2は、1chの2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号を1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号にマッピングする。

【0051】

図6は、デュアルリンクへのマッピング方法の例を示す。図6Aは、LinkA,Bの伝送表現の例を示し、図6Bは、LinkA,Bの伝送する順番の例を示す。

【0052】

図6Aに示すように、LinkAは、G′チャンネルの全サンプルと、B′及びR′チャンネルの偶数番号のサンプルを伝送し、LinkBは、Aチャンネルの全サンプルと、B′及びR′チャンネルの奇数番号のサンプルを伝送する。

具体的には、LinkA,Bの各データストリームは以下の順序でサンプルを伝送する。なお、上述したように、ダッシュ「′」をつけたR′,G′,B′の信号は、ガンマ補正などが施されたR,G,B信号を示し、各信号に付けられる番号は、サンプル番号を示す。

(1)LinkAデータストリーム:B’0,G’0,R’0,G’1,B’2,G’2,R’2,G’3,・・・

(2)LinkBデータストリーム:B’1,A0,R’1,A1,B’3,A2,R’3,A3,・・・

【0053】

<マッピング構造の例>

次に、1.5G−SDIの2種類のマッピング構造の例について、図7と図8を参照して説明する。

【0054】

<第1のマッピング構造の例>

図7は、1chの30Pあるいは60I/4:2:2/16ビット信号を2ch(デュアルリンク)の1.5G−SDIにマッピングする場合に参照される第1のマッピング構造の例を示す。図7Aは、1.5G−SDIの第1のHD−SDIに含まれるYチャンネル,CBチャンネル,CRチャンネルのマッピング構造の例を示す。図7Bは、1.5G−SDIの第2のHD−SDIに含まれるYch,CBチャンネル,CRチャンネルのマッピング構造の例を示す。

【0055】

上述したように、ワード間引き制御部12は、SMPTE372:2011のFigure3又はFigure5に基づいて、4:4:4/16ビット信号をワード間引きする。ワード間引きされた一方の信号は4:2:2/16ビット信号となり、他方の信号はAchが無いこととし0:2:2/16ビット信号となる。

【0056】

次に、マッピング制御部15−1は、図7に示すように、4:2:2/16ビット信号をch1(1.5G−SDIの1番目のチャンネル)とch2(1.5G−SDIの2番目のチャンネル)に振り分けて、2chの1.5G−SDIにマッピングする。

【0057】

ここで、図7に示す第1のマッピング構造の例は、以下の条件が必要とされる。

(1)画素のMSB(Most Significant ビット:最重要ビット)2ビット(b14,b15)は、1.5G−SDIの第1及び第2リンクが測定器で映像信号として観測できるようにする。このため、1.5G−SDIの第1及び第2リンクの上位2ビットであるb8とb9に、b14,b15を多重する。

(2)1.5G−SDIの禁止コードを回避するため、加えて16ビット信号がall0〜all1の値を取ることを可能にするために、1.5G−SDIの第1及び第2リンクのb2はb3の反転ビットとする。

(3)SAV/EAV,LN,CRCCなどのデータ構造は、SMPTE292−1に規定される有効な画素サンプルが1920あるいは2048であるデータ構造に準拠する。

【0058】

第1のマッピング制御部として用いられるマッピング制御部15−1は、第1のHD−SDIのYチャンネルにG信号でこのYチャンネルと同一サンプル番号の奇数ビットをマッピングし、CBチャンネルにこのCBチャンネルと同じサンプル番号のB信号の奇数ビットをマッピングし、CRチャンネルにこのCRチャンネルと同じサンプル番号のR信号の奇数ビットをマッピングする。そして、多重すべきYチャンネルと同じサンプル番号であるG信号のG14,G15をYチャンネルの上位2ビットに多重し、多重すべきCBチャンネルと同じサンプル番号であるB信号のB14,B15をCBチャンネルの上位2ビットに多重し、多重すべきCRチャンネルと同じサンプル番号であるR信号のR14,R15をCRチャンネルの上位2ビットに多重する。また、第2のHD−SDIのYチャンネルに同じサンプル番号のG信号の偶数ビットをマッピングし、CBチャンネルに同じサンプル番号のB信号の偶数ビットをマッピングし、CRチャンネルに同じサンプル番号のR信号の偶数ビットをマッピングする。そして、多重すべきYチャンネルと同じサンプル番号であるG信号のG14,G15をYチャンネルの上位2ビットに多重し、多重すべきCBチャンネルと同じサンプル番号であるB信号のB14,B15をCBチャンネルの上位2ビットに多重し、多重すべきCRチャンネル同じサンプル番号であるR信号のR14,R15をCRチャンネルの上位2ビットに多重する。その上で、第1及び第2のHD−SDIのYチャンネル、CBチャンネル及びCRチャンネルの各チャンネルに対して、所定位置のビットを反転した反転ビットを多重する。

【0059】

ここで、4:2:2/16ビット信号は、全サンプルのG信号と、偶数サンプルのB,R信号から構成される。これらG,B,R信号それぞれの16ビットを以下のように記述する。例えば、G信号の場合には、G0(LSB:Least Significant bit最下位ビット),G1,G2,G3,G4,G5,G6,G6,G7,G8,G9,G10,G11,G12,G13,G14,G15(MSB: Most Significant bit:最上位ビット)とする。同様に、B信号についてもB0,B1,B2,…,B15とし、R信号についてもR0,R1,R2,…,R15とする。

【0060】

そして、マッピング制御部15−1は、1.5G−SDIの2chのYchに含まれる10ビットに、この4:2:2/16ビット信号のG信号である全サンプルをマッピングする。同様に、CBチャンネルの10ビットに偶数サンプルのB信号をマッピングし、CRチャンネルの10ビットに偶数サンプルのR信号をマッピングする。

【0061】

図7Aに示すように、マッピング制御部15−1は、1.5G−SDIの1番目のchでは、G,B,R信号の上位2ビットである、G15,B15,R15及びG14,B14,R14を、1.5G−SDIのch1とch2のb9,b8に多重する。1.5G−SDIの1番目のchでは、G,B,R信号のG0,B0,R0からG13,B13,R13までの奇数ビットを16ビットの上位から順番に1.5G−SDIの10ビットの上位から下位に多重する。

【0062】

図7Bに示すように、マッピング制御部15−1は、1.5G−SDIの2番目のchでは、G,B,R信号のG0,B0,R0からG13,B13,R13までに含まれる偶数ビットを多重する。この多重は、16ビットの上位から順番に1.5G−SDIの10ビットの上位から下位に対して行われる。この時、16ビット映像信号は、all0〜all1を値として持つ。ここで、1.5G−SDIに禁止コードが発生することを防ぐために、1.5G−SDIの1番目及び2番目のchについては、共にb2の値をb3の反転ビットとする。こうすることで、Ych,CBチャンネル,CRチャンネルに、1.5G−SDIの禁止コード000h〜003hと3FCh〜3FFhを発生させない。

【0063】

<第2のマッピング構造の例>

図8は、30Pあるいは60I/0:2:2/16ビット信号を1.5G−SDIにマッピングする場合に参照される第2のマッピング構造の例を示す。

【0064】

ここで、図8に示す第2のマッピング構造の例は、以下の条件が必要とされる。

(1)CBサンプルは、16ビットの同じサンプル番号のB信号のうち、上位9ビットを多重して伝送する。

(2)CRサンプルは、16ビットの同じサンプル番号のR信号のうち、上位9ビットを多重して伝送する。

(3)Yチャンネルの奇数サンプルは、1.5G−SDIリンクが測定器で映像信号として観測できる様に多重する。例えば、16ビットの同じサンプル番号のG信号のうち、上位2ビット(G15,G14)と、16ビットのB信号のうち、下位7ビットを多重して伝送する。

(4)Yチャンネルの偶数サンプルは、1.5G−SDIリンクが測定器で映像信号として観測できる様に多重する。例えば、16ビットの同じサンプル番号のG信号のうち、上位2ビット(G15,G14)と、16ビットのR信号のうち、下位7ビットを多重して伝送する。

(5)1.5G−SDIの禁止コードを回避するため、加えて画素の16ビット信号がall0〜all1の値を取ることを可能にするために、1.5G−SDI偶数及び奇数リンクのb2はb3の反転ビットとする。

(6)SAV/EAV,LN,CRCCなどのデータ構造は、SMPTE292−1に規定される有効な画素サンプルが1920あるいは2048であるデータ構造に準拠する。

【0065】

第2のマッピング制御部として用いられるマッピング制御部15−2は、第3のHD−SDIにおけるYチャンネルの偶数サンプルにB信号の下位7ビットをマッピングする。また、Yチャンネルと同一サンプル番号(偶数サンプル)であるG信号のG14,G15をYチャンネルの偶数サンプルの上位2ビットに多重し、第3のHD−SDIにおけるYチャンネルの奇数サンプルにR信号の下位7ビットをマッピングすると共に、Yチャンネルと同一サンプル番号(奇数サンプル)であるG信号のG14,G15をYチャンネルの奇数サンプルの上位2ビットに多重する。さらに、CBチャンネルに同じサンプル番号であるB信号の上位9ビットをマッピングし、CRチャンネルに同じサンプル番号であるR信号の上位9ビットをマッピングする。その上で、Yチャンネルの偶数及び奇数サンプル、CBチャンネル及びCRチャンネルの各チャンネルに対して、所定位置のビットを反転した反転ビットを多重する。

【0066】

ここで、0:2:2/16ビット信号は、G信号が無く、奇数サンプルのB,R信号によって構成される。このため、マッピング制御部15−2は、奇数サンプルのB,R信号である16ビットとG信号の上位2ビットを用いて図8に示すように、1chの1.5G−SDIに多重する。

【0067】

また、マッピング制御部15−2は、G信号の上位2ビット(G15及びG14)を、1.5G−SDIの偶数サンプル及び奇数サンプルのYchのb9,b8に多重する。偶数サンプルYchのb7〜b0には、B信号の下位7ビットをB6,B5,B4,B3,B2,B2の反転,B1,B0の順番で多重する。奇数サンプルYchのb7〜b0には、R信号の下位7ビットをR6,R5,R4,R3,R2,R2の反転,R1,R0の順番で多重する。

【0068】

また、マッピング制御部15−2は、B信号及びR信号である16ビットの上位9ビットを第2のマッピング構造に示すようにCBチャンネル及びCRチャンネルへ多重する。この多重する順番は、B15,B14,B13,B12,B11,B10,B9,B9の反転,B8,B7となる。さらに、CRチャンネルにR15,R14,R13,R12,R11,R10,R9,R9の反転,R8,R7の順番で多重する。

【0069】

この時、16ビット映像信号はall0〜all1を値として持つので、1.5G−SDIで禁止コードの発生を防ぐために、1.5G−SDIのYch,CBチャンネル,CRチャンネルともb2をb3の反転ビットとする。こうすることで、1.5G−SDIの禁止コード000h〜003hと3FCh〜3FFhが発生しないようにすることができる。

【0070】

以上の方法で、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を3chの1.5G−SDIにマッピングして伝送することが可能になる。

なお、ANC/オーディオ信号を多重する必要がある場合には、1.5G−SDI用のANC/オーディオ規格であるSMPTE291やSMPTE299に準拠して、例えば1.5G−SDIのch1から順番にデータを多重することとなる。

【0071】

<信号受信装置の内部構成例>

図9は、信号受信装置20の内部構成例を示す。

CCU2は、放送用カメラ1が備える信号送信装置10から入力する3chのHD−SDIから2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を再生する信号受信装置20を備える。本開示の第1の実施の形態に係る信号受信装置20は、プログラムを実行することにより、内部ブロックが連携して行う信号受信方法を実現する。

【0072】

信号受信装置20は、各部にクロックを供給するクロック供給回路21と、ワード多重された2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を一時記憶するRAM23を備える。

【0073】

また、信号受信装置20は、ワード多重を制御するワード多重制御部22を備える。また、ワード多重制御部22が1chの2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号と、1chの2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号を記憶するRAM24−1,24−2を備える。

【0074】

また、信号受信装置20は、上述した第1及び第2のマッピング構造に基づいて、データを抽出する抽出制御部25−1,25−2を備える。また、信号受信装置20は、信号送信装置10から入力する第1のHD−SDIである2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号をRAM26−1に書き込む書込み制御部27−1を備える。同様に、信号送信装置10から入力する第2のHD−SDIである2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号をRAM26−2に書き込む書込み制御部27−2を備える。また、信号送信装置10から入力する第3のHD−SDIである2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号をRAM26−3に書き込む書込み制御部27−3を備える。

【0075】

次に、信号受信装置20の動作例を説明する。

クロック供給回路21は、ワード多重制御部22、抽出制御部25−1,25−2、書込み制御部27−1〜27−3に画素サンプルの読出し又は書き込みに用いるクロックを供給し、このクロックにより各部が同期する。

【0076】

書込み制御部27−1〜27−3は、r:g:bが4:2:2である3chの10ビット信号からなる第1〜第3のHD−SDIをRAM26−1〜26−3に書込む。

【0077】

抽出制御部25−1,25−2は、RAM26−1〜26−3から第1〜第3のHD−SDIを読み出す。このとき、上述した信号送信装置10が備えるマッピング制御部15−1が第1のマッピング構造(図7を参照。)に従ってマッピングした処理の逆変換が行われる。具体的には、抽出制御部25−1は、RAM26−1,26−2から、1chずつ2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、2chの10ビット信号からなる第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号を抽出する。そして、抽出制御部25−1は、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/16ビット信号をRAM24−1に書き込む。

【0078】

ここで、抽出制御部25−1の処理について説明する。

第1の抽出制御部として用いられる抽出制御部25−1は、第1のHD−SDIのYチャンネルからG信号でこのYチャンネルと同一サンプル番号の奇数ビットを抽出し、CBチャンネルからB信号でCBチャンネルと同一サンプル番号の奇数ビットを抽出し、CRチャンネルからR信号でCRチャンネルと同一サンプル番号の奇数ビットを抽出する。そして、Yチャンネルの上位2ビットからYチャンネルと同一サンプル番号であるG信号のG14,G15を抽出し、CBチャンネルの上位2ビットからCBチャンネルと同一サンプル番号であるB信号のB14,B15を抽出し、CRチャンネルの上位2ビットからCRチャンネルと同一サンプル番号であるR信号のR14,R15を抽出する。さらに、第2のHD−SDIのYチャンネルからG信号でYチャンネルと同一サンプル番号の偶数ビットを抽出し、CBチャンネルからB信号でCBチャンネルと同一サンプル番号の偶数ビットを抽出し、CRチャンネルからR信号でCRチャンネルと同一サンプル番号の偶数ビットを抽出する。そして、Yチャンネルの上位2ビットからYチャンネルと同一サンプル番号であるG信号のG14,G15を抽出し、CBチャンネルの上位2ビットからCBチャンネルと同一サンプル番号であるB信号のB14,B15を抽出し、CRチャンネルの上位2ビットからCRチャンネルと同一サンプル番号であるR信号のR14,R15を抽出する。

【0079】

一方、抽出制御部25−2は、RAM26−3から、1chの2k/23.98P−30P又は47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置10が備えるマッピング制御部15−2が第2のマッピング構造(図8を参照。)に従ってマッピングした処理の逆変換が行われる。具体的には、抽出制御部25−2は、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、1chの16ビット信号を抽出する。この1chの16ビット信号は、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される。そして、抽出制御部25−2は、1chの2k/23.98P−30P又は47.95I−60I/0:2:2/16ビット信号をRAM24−2に書き込む。

【0080】

ここで、抽出制御部25−2の処理について説明する。

第2の抽出制御部として用いられる抽出制御部25−2は、第3のHD−SDIにおけるYチャンネルの偶数サンプルからB信号の下位7ビットを抽出する。そして、Yチャンネルと同一サンプル番号(偶数サンプル)であるG信号の上位2ビットからG14,G15を抽出し、第3のHD−SDIにおけるYチャンネルと同一サンプル番号(奇数サンプル)であるG信号からR信号の下位7ビットを抽出する。また、Yチャンネルの奇数サンプルの上位2ビットからG14,G15を抽出し、CBチャンネルからB信号の上位9ビットを抽出し、CRチャンネルからR信号の上位9ビットを抽出する。

【0081】

ワード多重制御部22は、RAM24−1,24−2から読出した2chの16ビット信号をワード多重して、1chの2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号をRAM23に書き込む。具体的には、ワード多重制御部22は、r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重する。これにより、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号を生成する。そして、RAM23から適宜、この信号が再生される。

【0082】

なお、図9では、ワード多重と抽出制御とを2種類のRAMを用いて2段階で行う例を書いたが、一つのRAMを用いて2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を再生しても良い。

【0083】

以上説明した第1の実施の形態に係る伝送システムでは、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号に対して、ワード間引き、マッピングを行う。これにより、3chのHD−SDI信号を生成して出力できる。このため、放送用カメラ1は、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を、ビットレート1.5Gbpsのシリアル・デジタルデータに変換してCCU2に伝送できる。

【0084】

一方、CCU2は、ビットレート1.5Gbpsのシリアル・デジタルデータから2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を再生できる。つまり、2k/23.98P−30P又は47.95I−60I/4:4:4/16ビット信号を、従来用いている1.5Gbpsシリアルインタフェースの多chで伝送することが出来る。このため、信号伝送に当たり、既存の設備を有効に活用することができる。

【0085】

<2.第2の実施の形態>

[2k/47.95P−60P/4:4:4/16ビット信号を1.5G−SDI 6chにマッピングして伝送する例]

【0086】

<信号送信装置の内部構成例>

図10は、信号送信装置30の内部構成例を示す。

本開示の第2の実施の形態に係る放送用カメラ1は、2k/47.95P−60P/4:4:4/16ビット信号を3chのHD−SDIによってCCU2が備える信号受信装置40に出力する信号送信装置30を備える。以下の説明では、47.95P,48P,50P,59.94P,60Pを、「47.95P−60P」と略記する場合がある。

【0087】

信号送信装置30は、各部にクロックを供給するクロック供給回路31と、2k/47.95P−60P/4:4:4/16ビット信号を記憶するRAM33を備える。また、信号送信装置30は、上述した第1の実施の形態に係る信号送信装置10におけるワード間引き制御部12、マッピング制御部15−1,15−2、読出し制御部17−1〜17−3を二組備える。このため、各制御ブロックによってマッピングされるHD−SDIを記憶するRAMも二組備える。

【0088】

つまり、信号送信装置30は、RAM33から読出したr:g:bが4:4:4である1chの16ビット信号を一ラインずつ交互に間引いて2チャンネルのインターレース信号(2k/47.95I−60I/4:4:4/16ビット信号)とした映像信号をRAM34−1,34−2に書き込むライン間引き制御部32を備える。また、ライン間引き制御部32がライン間引きしたデータを書き込むRAM34−1,34−2を備える。また、ワード間引きを制御するワード間引き制御部35−1,35−2と、ワード間引き制御部35−1,35−2がワード間引きしたデータを書き込むRAM36−1〜36−4とを備える。

【0089】

また、信号送信装置30は、RAM36−1から読出した2k/47.95I−60I/4:2:2/16ビット信号を、第1のマッピング構造(図7を参照。)に従ってマッピングするマッピング制御部37−1を備える。また、マッピング制御部37−1がマッピングした2chの10ビット信号を記憶するRAM38−1,38−2を備える。

【0090】

また、信号送信装置30は、RAM36−2から読出した2k/47.95I−60I/0:2:2/16ビット信号を、第2のマッピング構造に従ってマッピングするマッピング制御部37−2を備える。また、マッピング制御部37−2がマッピングした1chの10ビット信号を記憶するRAM38−3を備える。

【0091】

また、信号送信装置30は、RAM36−3から読出した2k/47.95I−60I/4:2:2/16ビット信号を、第1のマッピング構造に従ってマッピングするマッピング制御部37−3を備える。また、マッピング制御部37−1がマッピングした2chの10ビット信号を記憶するRAM38−4,38−5を備える。

【0092】

また、信号送信装置30は、RAM36−4から読出した2k/47.95I−60I/0:2:2/16ビット信号を、第2のマッピング構造に従ってマッピングするマッピング制御部37−3を備える。また、マッピング制御部37−4がマッピングした1chの10ビット信号を記憶するRAM38−6を備える。

【0093】

そして、読出し制御部39−1〜39−6は、RAM38−1〜38−6から読み出した二組の第1〜第3のHD−SDIを出力する。このため、信号送信装置30は、RAM38−1〜38−6からそれぞれ読出したデータの画素サンプルを6チャンネルのHD−SDI ch1〜ch6として出力する読出し制御部39−1〜39−6を備える。

【0094】

次に、各部の動作例を説明する。

クロック供給回路31は、ライン間引き制御部32,ワード間引き制御部35−1,35−2、マッピング制御部37−1〜37−4,及び読出し制御部39−1〜39−6に画素サンプルの読出し又は書き込みに用いるクロックを供給する。各部は、この供給されたクロックにより同期して動作する。

【0095】

不図示の撮像素子から入力する2k/47.95P−60P/4:4:4/16ビット信号は、RAM33に保存される。

ライン間引き制御部32は、RAM33に保存された2k/47.95P−60P/4:4:4/16ビット信号を一ラインずつ交互に読み出して、RAM34−1,34−2に保存する。このとき、RAM34−1には、1chの2k/47.95I−60I/4:4:4/16ビット信号が書き込まれる。一方、RAM34−2には、1chの2k/47.95P−60P/4:4:4/16ビット信号が書き込まれる。

【0096】

ワード間引き制御部35−1,35−2は、それぞれRAM34−1,34−2から読出した画素サンプルより、SMPTE372のFigure4,6,7,8,9と同じ方式でワード間引きを行う。このとき、RAM36−1には、2k/47.95I−60I/4:2:2/16ビット信号が書き込まれ、RAM36−2には、2k/47.95I−60I/0:2:2/16ビット信号が書き込まれる。同様に、RAM36−3には、2k/47.95I−60I/4:2:2/16ビット信号が書き込まれ、RAM36−4には、2k/47.95I−60I/0:2:2/16ビット信号が書き込まれる。

【0097】

マッピング制御部37−1は、RAM36−1から読出した2k/47.95I−60I/4:2:2/16ビット信号を、2chの10ビット信号にマッピングし直してRAM38−1,38−2に書き込む。このとき、RAM38−1には、奇数ビットから抽出した1chの2k/47.95I−60I/4:2:2/10ビット信号が書き込まれる。一方、RAM38−2には、偶数ビットから抽出した1chの2k/47.95I−60I/4:2:2/10ビット信号が書き込まれる。

【0098】

マッピング制御部37−2は、RAM36−2から読出した2k/47.95I−60I/0:2:2/16ビット信号を、1chの2k/47.95I−60I/4:2:2/10ビット信号にマッピングし直してRAM38−3に書き込む。

【0099】

マッピング制御部37−3は、RAM36−3から読出した2k/47.95I−60I/4:2:2/16ビット信号を、2chの10ビット信号にマッピングし直してRAM38−4,38−5に書き込む。このとき、RAM38−4には、奇数ビットから抽出した1chの2k/47.95I−60I/4:2:2/10ビット信号が書き込まれる。一方、RAM38−5には、偶数ビットから抽出した1chの2k/47.95I−60I/4:2:2/10ビット信号が書き込まれる。

【0100】

マッピング制御部37−4は、RAM36−4から読出した2k/47.95I−60I/0:2:2/16ビット信号を、1chの2k/47.95I−60I/4:2:2/10ビット信号にマッピングし直してRAM38−6に書き込む。

【0101】

そして、読出し制御部39−1〜39−6は、クロック供給回路31から供給された基準クロックでRAM38−1〜38−6から6chの2k/47.95I−60I/4:2:2/10ビット信号を読出す。そして、6chのHD−SDI ch1〜ch6として出力する。

【0102】

なお、本例では、ライン間引き、ワード間引き及びマッピング制御を行うため、4種類のメモリ(RAM33,RAM34−1,34−2,RAM36−1〜36−4、RAM38−1〜38−6)を用いて、3段階で行う例を示した。しかし、一つのメモリを使って、ライン間引き及びワード間引きしたデータをマッピングし直して、6chのHD−SDIとして出力しても良い。

【0103】

図11は、2k/47.95P−60P/4:4:4/16ビット信号をライン間引き、ワード間引き及びマッピング制御を行う処理の概略例を示す。

【0104】

まず、SMPTE372:2011のFigure2に基づいて2k/47.95P−60P/4:4:4/16ビット信号をライン間引きし、2chの2k/47.95I−60I/4:4:4/16ビット信号に変換する。

【0105】

次にSMPTE372:2011のFigure3又は5に基づいて、4:4:4/16ビット信号をワード間引きする。一方の信号は4:2:2/16ビット信号となり、他方の信号はAchが無いこととし0:2:2/16ビット信号となる。この4:2:2/16ビット信号を、第1及び第2のマッピング構造(図7と図8を参照。)に従って1/5G−SDIに多重することで、合計6chの1/5G−SDIで伝送することが可能となる。

【0106】

なお、ANC/オーディオ信号を多重する必要がある場合には、1.5G−SDI用のANC/オーディオ規格であるSMPTE291やSMPTE299に準拠して、例えば1.5G−SDIのch1から順番にデータを多重する。

【0107】

図12は、ライン間引きの例を示す。

ここでは、デュアルリンクインタフェースのライン番号とパッケージの例を用いてライン間引きを説明する。

【0108】

まず、ライン間引き制御部32は、2k/47.95P−60P/4:4:4/16ビット信号をチャンネル1,2にライン間引きする。これにより、ライン間引きされた信号は、2chの2k/47.95I−60I/4:4:4/16ビット信号に変換される。

その後、上述したようにマッピング制御部37−1〜37−4は、第1及び第2のマッピング構造(図7及び図8参照)に基づいてデータをマッピングして、読出し制御部39−1〜39−6が6chのHD−SDIを出力する。

【0109】

<信号受信装置の内部構成例>

図13は、信号受信装置40の内部構成例を示す。

CCU2は、放送用カメラ1が備える信号送信装置30から入力する6chのHD−SDIから2k/47.95P−60P/4:4:4/16ビット信号を再生する信号受信装置40を備える。

【0110】

信号受信装置40は、各部にクロックを供給するクロック供給回路41と、2k/47.95P−60P/4:4:4/16ビットの映像信号を記憶するRAM43を備える。また、上述した第1の実施の形態に係る信号受信装置20における書込み制御部27−1〜27−3と、抽出制御部25−1,25−2と、ワード多重制御部22を二組備える。このため、各制御ブロックによってマッピングされるHD−SDIを記憶するRAMも二組備える。

【0111】

つまり、信号受信装置40は、信号送信装置30から入力する6本のHD−SDI ch1〜ch6をそれぞれ記憶するRAM48−1〜48−6を備える。このHD−SDI ch1〜ch6は、6chの2k/47.95I−60I/4:2:2/10ビット信号によって構成される。そして、書込み制御部49−1〜49−6は、信号送信装置30から入力する二組の第1〜第3のHD−SDIをRAM48−1〜48−6に書込む。このため、書込み制御部49−1〜49−6は、クロック供給回路41から供給されるクロックに合わせて、入力した6本のHD−SDI ch1〜ch6をRAM48−1〜48−6に書き込む制御を行う。

【0112】

また、信号受信装置40は、上述した第1及び第2のマッピング構造(図7及び図8参照)に基づいて、データを抽出する抽出制御部47−1〜47−4を備える。また、信号受信装置40は、信号送信装置30から入力する第1のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−1に書き込む書込み制御部49−1を備える。同様に、信号送信装置30から入力する第2のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−2に書き込む書込み制御部49−2を備える。また、信号送信装置30から入力する第3のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−3に書き込む書込み制御部49−3を備える。

【0113】

また、信号受信装置40は、信号送信装置30から入力する第4のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−4に書き込む書込み制御部49−4を備える。同様に、信号送信装置30から入力する第5のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−5に書き込む書込み制御部49−5を備える。また、信号送信装置30から入力する第6のHD−SDIである2k/47.95I−60I/4:2:2/10ビット信号をRAM48−6に書き込む書込み制御部49−6を備える。

【0114】

また、信号受信装置40は、ワード多重を制御するワード多重制御部45−1,45−2と、ワード多重制御部45−1,45−2が一時的に多重したデータを書き込むRAM44−1,44−2と、を備える。ワード多重制御部45−1,45−2は、所定のタイミングを制御してSMPTE372のFigure4,6,7,8,9の逆変換のワード単位で読み出す。この読出しタイミングは、(RAM46−1,46−2)、(RAM46−3,46−4)毎に定まる。

【0115】

また、信号受信装置40は、ワード多重制御部45−1,45−2によって多重された画素サンプルを、一ラインずつ交互に多重するライン多重制御部42を備える。具体的には、ライン多重制御部42は、RAM44−1,44−2から画素サンプルを読出し、一ラインずつ交互に多重して、多重したデータを書き込むRAM43に書き込む。これにより、RAM43には、2k/47.95P−60P/4:4:4/16ビット信号が保存され、適宜、この信号が再生される。

【0116】

次に、信号受信装置40の動作例を説明する。

クロック供給回路41は、ライン多重制御部42,ワード多重制御部45−1,45−2、抽出制御部47−1〜47−4、及び書込み制御部49−1〜49−6に画素サンプルの読み出し又は書き込みに用いるクロックを供給し、このクロックにより各部が同期する。

【0117】

抽出制御部47−1は、RAM48−1,48−2から、1chずつ2k/47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置30が備えるマッピング制御部37−1が第1のマッピング構造(図7を参照。)に従ってマッピングした処理の逆変換が行われる。そして、抽出制御部47−1は、1chの2k/47.95I−60I/4:2:2/16ビット信号をRAM46−1に書き込む。

【0118】

抽出制御部47−2は、RAM48−3から、1chの2k/47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置10が備えるマッピング制御部37−2が第2のマッピング構造(図8を参照。)に従ってマッピングした処理の逆変換が行われる。そして、抽出制御部47−2は、1chの2k/47.95I−60I/0:2:2/16ビット信号をRAM46−2に書き込む。

【0119】

同様に、抽出制御部47−3は、RAM48−4,48−5から、1chずつ2k/47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置30が備えるマッピング制御部37−3が第1のマッピング構造(図7を参照。)に従ってマッピングした処理の逆変換が行われる。そして、抽出制御部47−3は、1chの2k/47.95I−60I/4:2:2/16ビット信号をRAM46−3に書き込む。

【0120】

抽出制御部47−4は、RAM48−6から、1chの2k/47.95I−60I/4:2:2/10ビット信号を読み出す。このとき、上述した信号送信装置10が備えるマッピング制御部37−4が第2のマッピング構造(図8を参照。)に従ってマッピングした処理の逆変換が行われる。そして、抽出制御部47−4は、1chの2k/47.95I−60I/0:2:2/16ビット信号をRAM46−4に書き込む。

【0121】

ワード多重制御部45−1は、RAM46−1,46−2から読出した2chの2k/47.95I−60I/4:2:2/16ビット信号及び2k/47.95I−60I/0:2:2/16ビット信号をワード多重する。この結果として得た、1chの2k/47.95I−60I/4:4:4/16ビット信号をRAM44−1に書き込む。

【0122】

同様に、ワード多重制御部45−2は、RAM46−3,46−4から読出した2chの2k/47.95I−60I/4:2:2/16ビット信号及び2k/47.95I−60I/0:2:2/16ビット信号をワード多重する。この結果として得た、1chの2k/47.95I−60I/4:4:4/16ビット信号をRAM44−2に書き込む。

【0123】

ライン多重制御部42は、RAM44−1から読み出した2k/47.95I−60I/4:4:4/16ビット信号と、RAM44−2から読み出した2k/47.95I−60I/4:4:4/16ビット信号を一ラインずつ交互にライン多重する。そして、ライン多重して得た、1chの2k/47.95P−60P/4:4:4/16ビット信号をRAM43に書き込む。そして、RAM43から適宜、この信号が再生される。

【0124】

なお、図13では、抽出制御、ワード多重、ライン多重を3種類のRAMを用いて3段階で行う例を書いたが、一つのRAMを用いて2k/47.95P−60P/4:4:4/16ビット/4:4:4/10ビット,12ビット信号を生成しても良い。

【0125】

以上説明した第2の実施の形態によれば、信号送信装置30は、2k/47.95P−60P/4:4:4/16ビット信号の画素サンプルを、ライン間引き、ワード間引き及びマッピング制御を行うことで、6チャンネルのHD−SDIで伝送できる。このため、放送用カメラ1は、2k/47.95P−60P/4:4:4/16ビット信号を、ビットレート1.5Gbpsのシリアル・デジタルデータに変換してCCU2に伝送できる。

【0126】

一方、CCU2は、ビットレート1.5Gbpsのシリアル・デジタルデータから2k/47.95P−60P/4:4:4/16ビット信号を再生できる。つまり、4k×2k信号を、従来用いている1.5Gbpsシリアルインタフェースの多chで伝送することが出来る。このため、信号伝送に当たり、既存の設備を有効に活用することができる。

【0127】

このように上述した第1及び第2の実施の形態に係る信号送信装置及び信号受信装置によれば、1920×1080あるいは2048×1080/23.98P−60P/4:4:4/16ビット信号を3ch又は6chの1.5G−SDIにマッピングして伝送することを可能としている。また、1.5G−SDI3ch又は6chの信号を1本の光ファイバーで伝送する際には、CWDM/DWDM波長多重技術を使うことが出来る。

【0128】

また、3ch又は6chで出力される全てのHD−SDIは、波形モニタ等を用いてユーザが映像又は波形として観測することが可能である。このため、実際の機器開発において映像を確認しながら開発できることは非常に有用である。

【0129】

また、SMPTE274に準じた禁止コードを設けると16ビット信号では、0000h−00FFh及びFF00h−FFFFh信号が禁止コードとなり、512ものコードが使えなくなり映像表現の大きな制限要因となる。しかし、上述した本方式では禁止コードを設ける必要がなく、映像信号としてall0〜all1まで伝送可能であるので非常に有用である。また、RAWデータ(いわゆる、生のデータ)を編集する用途にも有用である。

【0130】

また、SMPTE S292−1に準拠して映像信号を伝送するので、SAV/EAV,LN,CRCCはSMPTE S274,S292−1に準拠して付ける。また、ANC/オーディオデータを多重する場合には、SMPTE S291,S299−1に準拠して、6chの1.5G−SDIのうち、第1chから第6chまで順番に多重することが可能である。すなわち、新たに規定を設けることなく、現状のHD関連規格に準じてANC/オーディオなどのデータを多重することが可能である。

【0131】

また、本開示は上述した実施の形態に限られるものではなく、特許請求の範囲に記載した本開示の要旨を逸脱しない限りその他種々の応用例、変形例を取り得ることは勿論である。

【符号の説明】

【0132】

1…放送用カメラ、2…CCU、5…信号伝送システム、10…信号送信装置、11…クロック供給回路、12…ワード間引き制御部、13…RAM、14−1,14−2…RAM、15−1,15−2…マッピング制御部、16−1〜16−3…RAM、17−1〜17−3…読出し制御部、20…信号受信装置、21…クロック供給回路、22…ワード多重制御部、23…RAM、24−1,24−2…RAM、25−1,25−2…抽出制御部、26−1〜26−3…RAM、27−1〜27−3…書込み制御部、30…信号送信装置、40…信号受信装置

【特許請求の範囲】

【請求項1】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号、及びr:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングするワード間引き制御部と、

ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造に従って、r:g:bが4:2:2である2chの10ビット信号からなる第1及び第2のHD−SDIにマッピングすると共に、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造に従って、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIにマッピングするマッピング制御部と、

前記第1〜第3のHD−SDIを出力する読出し制御部と、を備える

信号送信装置。

【請求項2】

前記マッピング制御部は、

前記第1のHD−SDIのYチャンネルに前記G信号でYチャンネルと同一サンプル番号の奇数ビットをマッピングし、CBチャンネルに前記B信号でCBチャンネルと同一サンプル番号の奇数ビットをマッピングし、CRチャンネルに前記R信号でCRチャンネルと同一サンプル番号の奇数ビットをマッピングすると共に、Yチャンネルと同一サンプル番号であるG信号のG14,G15をYチャンネルの上位2ビットに多重し、CBチャンネルと同一サンプル番号であるB信号のB14,B15を前記CBチャンネルの上位2ビットに多重し、CRチャンネルと同一サンプル番号であるR信号のR14,R15を前記CRチャンネルの上位2ビットに多重し、前記第2のHD−SDIのYチャンネルに前記G信号でYチャンネルと同一サンプル番号の偶数ビットをマッピングし、CBチャンネルに前記B信号でCBチャンネルと同一サンプル番号の偶数ビットをマッピングし、CRチャンネルに前記R信号でCRチャンネルと同一サンプル番号の偶数ビットをマッピングすると共に、Yチャンネルと同一サンプル番号であるG信号のG14,G15をYチャンネルの上位2ビットに多重し、CBチャンネルと同一サンプル番号であるB信号のB14,B15を前記CBチャンネルの上位2ビットに多重し、CRチャンネルと同一サンプル番号であるR信号のR14,R15を前記CRチャンネルの上位2ビットに多重した上で、前記第1及び第2のHD−SDIのYチャンネル、CBチャンネル及びCRチャンネルの各チャンネルに対して、所定位置のビットを反転した反転ビットを多重する第1のマッピング制御部と、

前記第3のHD−SDIにおけるYチャンネルの偶数サンプルに前記B信号の下位7ビットをマッピングすると共に、Yチャンネルと同一サンプル番号(偶数サンプル)であるG信号のG14,G15をYチャンネルの偶数サンプルの上位2ビットに多重し、前記第3のHD−SDIにおけるYチャンネルの奇数サンプルに前記R信号の下位7ビットをマッピングすると共に、Yチャンネルと同一サンプル番号(奇数サンプル)であるG信号のG14,G15をYチャンネルの奇数サンプルの上位2ビットに多重し、CBチャンネルに同じサンプル番号である前記B信号の上位9ビットをマッピングし、CRチャンネルに同じサンプル番号である前記R信号の上位9ビットをマッピングした上で、Yチャンネルの偶数サンプル及び奇数サンプル、CBチャンネル及びCRチャンネルの各チャンネルに対して、前記所定位置のビットを反転した反転ビットを多重する第2のマッピング制御部と、を備える

請求項1記載の信号送信装置。

【請求項3】

r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインであり、a−bが23.98P−30P又は47.95I−60Iである。

請求項2記載の信号送信装置。

【請求項4】

r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインであり、a−bが47.95P−60Pである場合に、

二組の前記ワード間引き制御部と、

二組の前記マッピング制御部と、

二組の前記読出し制御部と、

r:g:bが4:4:4である1chの16ビット信号を一ラインずつ交互に間引いて2チャンネルのインターレース信号とした映像信号を、二組の前記ワード間引き制御部にそれぞれ出力するライン間引き制御部と、を備え、

二組の前記読出し制御部は、二組の前記第1〜第3のHD−SDIを出力する

請求項2記載の信号送信装置。

【請求項5】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号、及びr:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングすることと、

ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造に従って、r:g:bが4:2:2である2chの10ビット信号からなる第1及び第2のHD−SDIにマッピングすると共に、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造に従って、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIにマッピングすることと、

前記第1〜第3のHD−SDIを出力することと、を含む

信号送信方法。

【請求項6】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:2:2である3chの10ビット信号からなる第1〜第3のHD−SDIを記憶部に書込む書込み制御部と、

前記記憶部から読み出した、2chの10ビット信号からなる前記第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号を抽出すると共に、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号を抽出する抽出制御部と、

r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重することによって、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号を生成するワード多重制御部と、を備える

信号受信装置。

【請求項7】

前記抽出制御部は、

前記第1のHD−SDIのYチャンネルから前記G信号でこのYチャンネルと同一サンプル番号の奇数ビットを抽出し、CBチャンネルから前記B信号でCBチャンネルと同一サンプル番号の奇数ビットを抽出し、CRチャンネルから前記R信号でCRチャンネルと同一サンプル番号の奇数ビットを抽出すると共に、Yチャンネルの上位2ビットからYチャンネルと同一サンプル番号であるG信号のG14,G15を抽出し、前記CBチャンネルの上位2ビットからCBチャンネルと同一サンプル番号であるB信号のB14,B15を抽出し、前記CRチャンネルの上位2ビットからCRチャンネルと同一サンプル番号であるR信号のR14,R15を抽出し、前記第2のHD−SDIのYチャンネルから前記G信号でYチャンネルと同一サンプル番号の偶数ビットを抽出し、CBチャンネルから前記B信号でCBチャンネルと同一サンプル番号の偶数ビットを抽出し、CRチャンネルから前記R信号でCRチャンネルと同一サンプル番号の偶数ビットを抽出すると共に、Yチャンネルの上位2ビットからYチャンネルと同一サンプル番号であるG信号のG14,G15を抽出し、前記CBチャンネルの上位2ビットからCBチャンネルと同一サンプル番号であるB信号のB14,B15を抽出し、前記CRチャンネルの上位2ビットからCRチャンネルと同一サンプル番号であるR信号のR14,R15を抽出する第1の抽出制御部と、前記第3のHD−SDIにおけるYチャンネルの偶数サンプルから前記B信号の下位7ビットを抽出すると共に、Yチャンネルと同一サンプル番号(偶数サンプル)であるG信号の上位2ビットからG14,G15を抽出し、前記第3のHD−SDIにおけるYチャンネルの奇数サンプルから前記R信号の下位7ビットを抽出すると共に、Yチャンネルと同一サンプル番号(奇数サンプル)であるG信号の上位2ビットからG14,G15を抽出し、CBチャンネルから前記B信号の上位9ビットを抽出し、CRチャンネルから前記R信号の上位9ビットを抽出する第2の抽出制御部と、を備える

請求項6記載の信号受信装置。

【請求項8】

r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインであり、a−bが23.98P−30P又は47.95I−60Iである

請求項7記載の信号受信装置。

【請求項9】

r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインであり、a−bが47.95P−60Pである場合に、

二組の前記書込み制御部と、

二組の前記抽出制御部と、

二組の前記ワード多重制御部と、

前記ワード多重制御部によってワード多重されたr:g:bが4:4:4である2chの16ビット信号であるインターレース信号を、一ラインずつ交互に多重して、r:g:bが4:4:4である1chの16ビット信号とするライン多重制御部を備え、

二組の前記書込み制御部は、入力する二組の前記第1〜第3のHD−SDIを前記記憶部に書込む

請求項7記載の信号受信装置。

【請求項10】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:2:2である3chの10ビット信号からなる第1〜第3のHD−SDIを記憶部に書込むことと、

前記記憶部から読み出した、2chの10ビット信号からなる前記第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号を抽出すると共に、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号を抽出することと、

r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重することによって、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号を生成することと、を含む

信号受信方法。

【請求項11】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号、及びr:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングするワード間引き制御部と、

ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造に従って、r:g:bが4:2:2である2chの10ビット信号からなる第1及び第2のHD−SDIにマッピングすると共に、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造に従って、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIにマッピングするマッピング制御部と、

前記第1〜第3のHD−SDIを出力する読出し制御部と、を有する信号送信装置と、

3chの10ビット信号からなる前記第1〜第3のHD−SDIを記憶部に書込む書込み制御部と、

前記記憶部から読み出した前記第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2である1chの16ビット信号を抽出すると共に、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、r:g:bが0:2:2である1chの16ビット信号を抽出する抽出制御部と、

r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重することによって、r:g:bが4:4:4である1chの16ビット信号を生成するワード多重制御部と、を有する信号受信装置と、を備える

信号伝送システム。

【請求項1】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号、及びr:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングするワード間引き制御部と、

ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造に従って、r:g:bが4:2:2である2chの10ビット信号からなる第1及び第2のHD−SDIにマッピングすると共に、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造に従って、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIにマッピングするマッピング制御部と、

前記第1〜第3のHD−SDIを出力する読出し制御部と、を備える

信号送信装置。

【請求項2】

前記マッピング制御部は、

前記第1のHD−SDIのYチャンネルに前記G信号でYチャンネルと同一サンプル番号の奇数ビットをマッピングし、CBチャンネルに前記B信号でCBチャンネルと同一サンプル番号の奇数ビットをマッピングし、CRチャンネルに前記R信号でCRチャンネルと同一サンプル番号の奇数ビットをマッピングすると共に、Yチャンネルと同一サンプル番号であるG信号のG14,G15をYチャンネルの上位2ビットに多重し、CBチャンネルと同一サンプル番号であるB信号のB14,B15を前記CBチャンネルの上位2ビットに多重し、CRチャンネルと同一サンプル番号であるR信号のR14,R15を前記CRチャンネルの上位2ビットに多重し、前記第2のHD−SDIのYチャンネルに前記G信号でYチャンネルと同一サンプル番号の偶数ビットをマッピングし、CBチャンネルに前記B信号でCBチャンネルと同一サンプル番号の偶数ビットをマッピングし、CRチャンネルに前記R信号でCRチャンネルと同一サンプル番号の偶数ビットをマッピングすると共に、Yチャンネルと同一サンプル番号であるG信号のG14,G15をYチャンネルの上位2ビットに多重し、CBチャンネルと同一サンプル番号であるB信号のB14,B15を前記CBチャンネルの上位2ビットに多重し、CRチャンネルと同一サンプル番号であるR信号のR14,R15を前記CRチャンネルの上位2ビットに多重した上で、前記第1及び第2のHD−SDIのYチャンネル、CBチャンネル及びCRチャンネルの各チャンネルに対して、所定位置のビットを反転した反転ビットを多重する第1のマッピング制御部と、

前記第3のHD−SDIにおけるYチャンネルの偶数サンプルに前記B信号の下位7ビットをマッピングすると共に、Yチャンネルと同一サンプル番号(偶数サンプル)であるG信号のG14,G15をYチャンネルの偶数サンプルの上位2ビットに多重し、前記第3のHD−SDIにおけるYチャンネルの奇数サンプルに前記R信号の下位7ビットをマッピングすると共に、Yチャンネルと同一サンプル番号(奇数サンプル)であるG信号のG14,G15をYチャンネルの奇数サンプルの上位2ビットに多重し、CBチャンネルに同じサンプル番号である前記B信号の上位9ビットをマッピングし、CRチャンネルに同じサンプル番号である前記R信号の上位9ビットをマッピングした上で、Yチャンネルの偶数サンプル及び奇数サンプル、CBチャンネル及びCRチャンネルの各チャンネルに対して、前記所定位置のビットを反転した反転ビットを多重する第2のマッピング制御部と、を備える

請求項1記載の信号送信装置。

【請求項3】

r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインであり、a−bが23.98P−30P又は47.95I−60Iである。

請求項2記載の信号送信装置。

【請求項4】

r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインであり、a−bが47.95P−60Pである場合に、

二組の前記ワード間引き制御部と、

二組の前記マッピング制御部と、

二組の前記読出し制御部と、

r:g:bが4:4:4である1chの16ビット信号を一ラインずつ交互に間引いて2チャンネルのインターレース信号とした映像信号を、二組の前記ワード間引き制御部にそれぞれ出力するライン間引き制御部と、を備え、

二組の前記読出し制御部は、二組の前記第1〜第3のHD−SDIを出力する

請求項2記載の信号送信装置。

【請求項5】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号、及びr:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングすることと、

ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造に従って、r:g:bが4:2:2である2chの10ビット信号からなる第1及び第2のHD−SDIにマッピングすると共に、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造に従って、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIにマッピングすることと、

前記第1〜第3のHD−SDIを出力することと、を含む

信号送信方法。

【請求項6】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:2:2である3chの10ビット信号からなる第1〜第3のHD−SDIを記憶部に書込む書込み制御部と、

前記記憶部から読み出した、2chの10ビット信号からなる前記第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号を抽出すると共に、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号を抽出する抽出制御部と、

r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重することによって、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号を生成するワード多重制御部と、を備える

信号受信装置。

【請求項7】

前記抽出制御部は、

前記第1のHD−SDIのYチャンネルから前記G信号でこのYチャンネルと同一サンプル番号の奇数ビットを抽出し、CBチャンネルから前記B信号でCBチャンネルと同一サンプル番号の奇数ビットを抽出し、CRチャンネルから前記R信号でCRチャンネルと同一サンプル番号の奇数ビットを抽出すると共に、Yチャンネルの上位2ビットからYチャンネルと同一サンプル番号であるG信号のG14,G15を抽出し、前記CBチャンネルの上位2ビットからCBチャンネルと同一サンプル番号であるB信号のB14,B15を抽出し、前記CRチャンネルの上位2ビットからCRチャンネルと同一サンプル番号であるR信号のR14,R15を抽出し、前記第2のHD−SDIのYチャンネルから前記G信号でYチャンネルと同一サンプル番号の偶数ビットを抽出し、CBチャンネルから前記B信号でCBチャンネルと同一サンプル番号の偶数ビットを抽出し、CRチャンネルから前記R信号でCRチャンネルと同一サンプル番号の偶数ビットを抽出すると共に、Yチャンネルの上位2ビットからYチャンネルと同一サンプル番号であるG信号のG14,G15を抽出し、前記CBチャンネルの上位2ビットからCBチャンネルと同一サンプル番号であるB信号のB14,B15を抽出し、前記CRチャンネルの上位2ビットからCRチャンネルと同一サンプル番号であるR信号のR14,R15を抽出する第1の抽出制御部と、前記第3のHD−SDIにおけるYチャンネルの偶数サンプルから前記B信号の下位7ビットを抽出すると共に、Yチャンネルと同一サンプル番号(偶数サンプル)であるG信号の上位2ビットからG14,G15を抽出し、前記第3のHD−SDIにおけるYチャンネルの奇数サンプルから前記R信号の下位7ビットを抽出すると共に、Yチャンネルと同一サンプル番号(奇数サンプル)であるG信号の上位2ビットからG14,G15を抽出し、CBチャンネルから前記B信号の上位9ビットを抽出し、CRチャンネルから前記R信号の上位9ビットを抽出する第2の抽出制御部と、を備える

請求項6記載の信号受信装置。

【請求項8】

r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインであり、a−bが23.98P−30P又は47.95I−60Iである

請求項7記載の信号受信装置。

【請求項9】

r:g:bが4:4:4である1chの16ビット信号は、m×nが1920サンプル×1080ライン又は2048サンプル×1080ラインであり、a−bが47.95P−60Pである場合に、

二組の前記書込み制御部と、

二組の前記抽出制御部と、

二組の前記ワード多重制御部と、

前記ワード多重制御部によってワード多重されたr:g:bが4:4:4である2chの16ビット信号であるインターレース信号を、一ラインずつ交互に多重して、r:g:bが4:4:4である1chの16ビット信号とするライン多重制御部を備え、

二組の前記書込み制御部は、入力する二組の前記第1〜第3のHD−SDIを前記記憶部に書込む

請求項7記載の信号受信装置。

【請求項10】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:2:2である3chの10ビット信号からなる第1〜第3のHD−SDIを記憶部に書込むことと、

前記記憶部から読み出した、2chの10ビット信号からなる前記第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号を抽出すると共に、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、r:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号を抽出することと、

r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重することによって、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号を生成することと、を含む

信号受信方法。

【請求項11】

撮像素子が出力する映像信号がm×n(m,nは、mサンプル×nライン)/a−b(a,bは、フレームレート)/r:g:b(r,g,bは、所定の信号伝送方式である場合における信号比率)/16ビット信号で規定され、1chの16ビット信号に含まれる全サンプルのG信号の各ビットをG0,G1,…,G15とし、B信号の各ビットをB0,B1,…,B15とし、R信号の各ビットをR0,R1,…,R15とする場合に、r:g:bが4:4:4であって、全サンプルのG,B,R信号によって構成される1chの16ビット信号をワード毎に間引いて、r:g:bが4:2:2であって、全サンプルのG信号と、偶数サンプルのB,R信号によって構成される1chの16ビット信号、及びr:g:bが0:2:2であって、G信号がなく、奇数サンプルのB,R信号によって構成される1chの16ビット信号にマッピングするワード間引き制御部と、

ワード毎に間引かれたr:g:bが4:2:2である1chの16ビット信号を、第1のマッピング構造に従って、r:g:bが4:2:2である2chの10ビット信号からなる第1及び第2のHD−SDIにマッピングすると共に、ワード毎に間引かれたr:g:bが0:2:2である1chの16ビット信号を、第2のマッピング構造に従って、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIにマッピングするマッピング制御部と、

前記第1〜第3のHD−SDIを出力する読出し制御部と、を有する信号送信装置と、

3chの10ビット信号からなる前記第1〜第3のHD−SDIを記憶部に書込む書込み制御部と、

前記記憶部から読み出した前記第1及び第2のHD−SDIから、第1のマッピング構造に従って、r:g:bが4:2:2である1chの16ビット信号を抽出すると共に、r:g:bが4:2:2である1chの10ビット信号からなる第3のHD−SDIから、第2のマッピング構造に従って、r:g:bが0:2:2である1chの16ビット信号を抽出する抽出制御部と、

r:g:bが4:2:2である1chの16ビット信号、及びr:g:bが0:2:2である1chの16ビット信号をワード毎に多重することによって、r:g:bが4:4:4である1chの16ビット信号を生成するワード多重制御部と、を有する信号受信装置と、を備える

信号伝送システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−55395(P2013−55395A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−190549(P2011−190549)

【出願日】平成23年9月1日(2011.9.1)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月1日(2011.9.1)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]