信号配線システム及びジッタ抑制回路

【課題】従来は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することが難しかった。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、信号配線システム及びジッタ抑制回路に関するものである。

【背景技術】

【0002】

ジッタ抑制回路の従来技術として、特許文献1、2のような技術が開示されている。

【0003】

特許文献1には、図26に示すように、帯域通過フィルタ12と、整形回路13とを有するジッタ除去整形回路10が記載されている。帯域通過フィルタ12は、入力端子11から入力したジッタを有する基本クロック信号から基本クロック周波数成分のみを通過させる。整形回路13は、帯域通過フィルタ12の出力信号をコンパレータで電圧比較して基本クロックを再生し出力する。

【0004】

特許文献2には、図27に示すように、ジッタ成分検出回路22と、可変増幅器23と、差動増幅器24と、クロック再生回路25とを有するジッタ抑制回路20が記載されている。ジッタ成分検出回路22は、入力端子21からのジッタ成分を含んだクロック信号からジッタ成分のみを取り出す。可変増幅器23は、取り出されたジッタ成分をクロック信号の振幅より小さい振幅に設定する。差動増幅器24は、クロック信号と可変増幅器出力との差をとり、ジッタ位相を補正した差信号を生成し、出力する。クロック再生回路25は差信号のゼロクロス点を時間基準として再生クロック信号を出力端子に出力する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2001−344040号公報

【特許文献2】特開平6−53947号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1の技術では、帯域通過フィルタ12を構成するアナログ回路部品が必要である。帯域通過フィルタを構成する素子として、キャパシタや抵抗等があるが、半導体チップ上にキャパシタを形成する場合、素子面積の抑制が難しく、チップサイズが大きくなってしまう。逆に、キャパシタ等の素子サイズを小さくした場合、帯域通過フィルタの周波数帯域が狭くなり、当然ジッタ除去可能な周波数範囲も狭くなる。特に、低周波領域のジッタ抑制効果が小さくなる問題がある。

【0007】

特許文献2の技術では、ジッタ成分検出回路22が、ジッタ成分を含んだクロック信号からジッタ成分のみを取り出すが、この場合もフィルタ等のアナログ回路が必要となる。このため、上記した特許文献1と同様、素子面積の抑制が難しく、チップサイズが大きくなってしまう問題が発生する。また、可変増幅器23も回路規模の増加の原因となる。

【課題を解決するための手段】

【0008】

本発明の第1の態様は、差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部から前記受信部へ前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システムである。

【0009】

本発明の第2の態様は、差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記出力部から前記受信部へ前記差動信号を伝達する信号配線部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、を有し、前記出力部は、前記ジッタ抑制回路の前記抑制係数に応じた駆動能力で、前記差動信号を出力する信号配線システムである。

【0010】

本発明の第3の態様は、差動入力信号を反転入力端子、非反転入力端子に入力し、前記差動入力信号に応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、前記差動増幅回路の前記反転入力端子と非反転出力端子との間に接続される第1の帰還抵抗部と、前記差動増幅回路の前記非反転入力端子と反転出力端子との間に接続される第2の帰還抵抗部と、を有し、前記第1、第2の帰還抵抗部が、前記差動増幅回路の前記差動入力信号に対する前記出力信号のDCゲインが5〜15dB以下となる抵抗値を有するジッタ抑制回路である。

【0011】

本発明は、アナログ回路で構成されるフィルタを使用せず、受信部が受信する差動信号のジッタ量を削減することができる。

【発明の効果】

【0012】

本発明は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することができる。

【図面の簡単な説明】

【0013】

【図1】実施の形態1にかかるSerDes回路の構成である。

【図2】実施の形態1にかかるクロックドライバの構成である。

【図3】実施の形態1にかかるSerDes回路の構成である。

【図4】実施の形態1にかかる分周回路の構成である。

【図5】実施の形態1にかかる分周回路のタイミングチャート(理想動作)である。

【図6】実施の形態1にかかるジッタ抑制回路の構成である。

【図7】実施の形態1にかかるジッタ抑制回路の詳細な構成である。

【図8】実施の形態1にかかるジッタ抑制回路の効果を説明するための参考回路構成である。

【図9】実施の形態1にかかるジッタ抑制回路の効果を説明するための回路構成である。

【図10】実施の形態1にかかるジッタ抑制回路の効果を説明するための回路構成である。

【図11】図8の回路構成における各信号のアイパターンである。

【図12】実施の形態1にかかる図9の回路構成における各信号のアイパターンである。

【図13】図8の回路構成における各信号の波形図である。

【図14】実施の形態1にかかる図9の回路構成における各信号の波形図である。

【図15】実施の形態1にかかる図10の回路構成における各信号のアイパターンである。

【図16】実施の形態1にかかるジッタ抑制回路のゲインの周波数特性である。

【図17】実施の形態1にかかるジッタ抑制回路のDCゲインに対するジッタ特性である。

【図18】実施の形態1にかかるSerDes回路の信号分配配線の配線長に対するジッタ特性である。

【図19】実施の形態1にかかるSerDes回路におけるジッタ抑制回路の抑制効果に応じたジッタ量の変化を説明するグラフである。

【図20】実施の形態1にかかるSerDes回路におけるジッタ抑制回路の抑制効果に応じたジッタ量の変化を説明するグラフである。

【図21】実施の形態1にかかるSerDes回路におけるジッタ抑制回路の抑制効果に応じたジッタ量の変化を説明するグラフである。

【図22】実施の形態2にかかるジッタ抑制回路の構成である。

【図23】実施の形態2にかかるジッタ抑制回路の構成である。

【図24】実施の形態3にかかるクロックドライバの構成である。

【図25】その他の実施の形態にかかる半導体集積回路のブロック構成である。

【図26】従来技術の回路構成である。

【図27】従来技術の回路構成である。

【発明を実施するための形態】

【0014】

発明の実施の形態1

【0015】

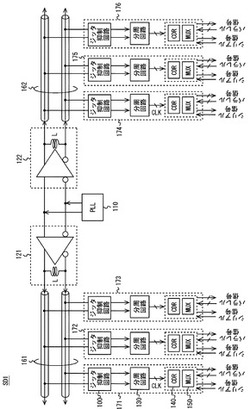

以下、本発明を適用した具体的な実施の形態1について、図面を参照しながら詳細に説明する。この実施の形態1は、本発明をSerDes回路が備えるジッタ抑制回路に適用したものである。まず、図1に本実施の形態1にかかるSerDes(Serializer/Deserializer)回路SD1の構成を示す。

【0016】

図1に示すように、SerDes回路SD1は、PLL回路110と、クロックドライバ121、122と、送受信回路171〜176と、信号分配配線161、162とを有する。

【0017】

SerDes回路SD1は、複数の高速データ信号を送受信する。SerDes回路SD1は、パラレル信号をシリアル信号に、シリアル信号をパラレル信号に変換する。例えば、USB3.0等のような5Gbpsの高速データ信号を送受信する。このSerDes回路SD1のように高速データ信号を送受信する場合、パラレル−シリアル変換、シリアル−パラレル変換を行う送受信回路171〜176の動作クロックも高速なものが必要となる。

【0018】

PLL回路110は、SerDes回路SD1内で使用されるクロック信号を生成する。この生成されるクロック信号のクロック周波数は、例えば、5GHzと高速である。なお、本例では、このPLL回路110が生成するクロック信号は差動信号であり、以下、差動クロック信号と称す。

【0019】

クロックドライバ121、122は、PLL回路110が生成した差動クロック信号を、それぞれバッファリングし、信号分配配線161、162に出力する。図2に、クロックドライバ121の回路構成を示す。なお、クロックドライバ122も同様の回路構成である。図2に示すように、クロックドライバ121は、PMOSトランジスタMP11、MP12と、NMOSトランジスタMN11〜MN14と、インダクタLとを有する。

【0020】

PMOSトランジスタMP11は、ソースが電源端子VDD、ドレインが反転出力端子OB、ゲートがノードN12に接続される。PMOSトランジスタMP12は、ソースが電源端子VDD、ドレインが非反転出力端子OT、ゲートがノードN11に接続される。

【0021】

NMOSトランジスタMN13は、ドレインが反転出力端子OB、ソースがノードN11、ゲートが電源端子VDDに接続される。NMOSトランジスタMN14は、ドレインが非反転出力端子OT、ソースがノードN12、ゲートが電源端子VDDに接続される。

【0022】

NMOSトランジスタMN11は、ドレインがノードN11、ソースが接地端子GND、ゲートが非反転入力端子ITに接続される。NMOSトランジスタMN12は、ドレインがノードN12、ソースが接地端子GND、ゲートが反転入力端子IBに接続される。

【0023】

インダクタLが非反転出力端子OTと反転出力端子OBとの間に接続される。

【0024】

上記反転入力端子、非反転入力端子にPLL回路110が生成した差動クロック信号を入力し、反転出力端子、非反転出力端子から差動クロック信号が出力される。

【0025】

ここで、クロックドライバ121、122の電源を供給する端子(電源端子VDD)に供給される電圧(以降、必要に応じて電源電圧VDDと称す)にノイズが重畳されると、非反転出力端子OTと反転出力端子OBから出力される差動クロック信号にも、同様にその電源ノイズが重畳される(後述する図13、図14参照)。そして、そのノイズが重畳された差動クロック信号が、信号分配配線161、162に出力される。

【0026】

クロックドライバ121が出力した差動クロック信号は、信号分配配線161を経由して送受信回路171〜173に分配される。クロックドライバ122が出力した差動クロック信号は、信号分配配線162を経由して送受信回路174〜176に分配される。

【0027】

信号分配配線161、162は、例えば3mm程度の配線長を有し、数mm角の半導体チップにおいて大きな負荷容量となる。ここで、本例のように例えば3mmのような信号分配配線161、162で伝達されると、この高周波の差動クロック信号は減衰し、クロック振幅が小さくなってしまう。しかし、差動クロック信号に重畳されるジッタ量は減衰しないため、このジッタを抑制する機構が必要とされる。なお、上記「3mm」は単なる一例であり、配線長はこの数値に特に限定されない。

【0028】

また、図1のSerDes回路SD1では、クロックドライバ121、122のそれぞれがドライブする差動クロック信号が3分配であったが、それよりも分配数が多くなる場合、信号分配配線161、162の配線長を長くし、接続する送受信回路を増やさなければならない。しかし、上述したように、差動クロック信号の振幅が減衰してしまうため、減衰した差動クロック信号を増幅する必要がある。このため、図3に示すように、クロックドライバを複数段直列に接続して、差動クロック信号を分配するSerDes回路SD2のような構成を採用してもよい。図3の例では、クロックドライバ121にクロックドライバ122を直列接続する例を示しており、その他の構成は、図1と同様である。図3に示すように、クロックドライバを複数段直列に接続しているが、この場合、クロックドライバを複数段通ることで、クロックドライバ121、122の電源ノイズ等により、増幅される差動クロック信号に更にジッタが重畳される問題がある。そして、接続されるクロックドライバの段数が多ければ多いほどジッタ品質が劣化することになる。このため、やはり図3のような構成であっても、ジッタを抑制する機構が必要とされる。

【0029】

送受信回路171〜176はそれぞれ、ジッタ抑制回路100と、分周回路(DIV)130と、クロックデータリカバリ回路(CDR)140と、多重化回路(MUX)150とを有する。

【0030】

分周回路130は、ジッタ抑制回路100を経て入力した差動クロック信号を2分周し、4相のクロック信号CLK1〜CLK4を生成する。図4に分周回路130の構成の一例を示す。図4に示すように、分周回路130は、ラッチ回路LTC1、LTC2を有し、トグルフリップフロップを構成する。また、図5に、分周回路130の理想的な動作タイミングチャートを示す。なお、このタイミングチャートに示す信号波形は、ジッタ等の影響を受けていない理想的な動作を行っている場合を示す。なお、トグルフリップフロップを用いた分周回路は、一般的に用いられており、動作等の詳しい説明は省略する。分周回路130が生成したクロック信号CLK1〜CLK4は、クロックデータリカバリ回路140、多重化回路150の動作クロックとなる。本来は、例えば5GHzの高周波動作となるため、分周回路130に入力される差動クロック信号のジッタ品質が悪い(ジッタ量が多い)場合、分周回路130が出力するクロック信号のジッタ品質も当然悪化する。

【0031】

クロックデータリカバリ回路140は、分周回路130が生成したクロック信号を動作クロックとして動作する。クロックデータリカバリ回路140は、入力したシリアルデータをパラレルデータに変換し、出力する。

【0032】

多重化回路150は、分周回路130が生成したクロック信号を動作クロックとして動作する。多重化回路150は、入力したパラレルデータをシリアルデータに変換し、出力する。

【0033】

クロックデータリカバリ回路140及び多重化回路150は、分周回路130が生成したクロック信号を動作クロックとしているため、このクロック信号のジッタ品質が悪い場合、高速データの受信特性、送信特性を劣化させる原因となる。このため、分周回路130に入力される差動クロック信号のジッタを抑制する機構が必要とされる。

【0034】

ジッタ抑制回路100は、送受信回路171〜176のそれぞれに入力される差動クロック信号のジッタを抑制する機能を有する。分周回路130に入力される差動クロック信号のジッタを抑制することで、分周回路130が出力する4相のクロック信号CLK1〜CLK4のジッタを抑制する。結果として、このジッタが抑制された4相のクロック信号CLK1〜CLK4を動作クロックとするクロックデータリカバリ回路140及び多重化回路150の高速データの受信特性、送信特性の劣化も回避することが可能となる。

【0035】

図6に、ジッタ抑制回路100の構成を示す。図6に示すように、ジッタ抑制回路100は、差動増幅回路AMP1と、帰還抵抗R1、R2とを有する。

【0036】

差動増幅回路AMP1は、差動クロック信号の一方を非反転入力端子ITに入力し、他方を反転入力端子IBに入力する。差動増幅回路AMP1は、非反転入力端子、反転入力端子に入力した差動クロック信号に応じた、出力差動信号を非反転出力端子OT、反転出力端子OBから出力する。

【0037】

帰還抵抗R1は、差動増幅回路AMP1の非反転入力端子ITと反転出力端子OBとの間に接続される。帰還抵抗R2は、差動増幅回路AMP1の反転入力端子IBと非反転出力端子OTとの間に接続される。

【0038】

図7に、差動増幅回路AMP1の構成を示す。図7に示すように、差動増幅回路AMP1は、PMOSトランジスタMP1、MP2と、NMOSトランジスタMN1〜MN4とを有する。

【0039】

PMOSトランジスタMP1は、ソースが電源端子VDD、ドレインが反転出力端子OB、ゲートがノードN2に接続される。PMOSトランジスタMP2は、ソースが電源端子VDD、ドレインが非反転出力端子OT、ゲートがノードN1に接続される。

【0040】

NMOSトランジスタMN3は、ドレインが反転出力端子OB、ソースがノードN1、ゲートが電源端子VDDに接続される。NMOSトランジスタMN4は、ドレインが非反転出力端子OT、ソースがノードN2、ゲートが電源端子VDDに接続される。

【0041】

NMOSトランジスタMN1は、ドレインがノードN1、ソースが接地端子GND、ゲートが非反転入力端子ITに接続される。NMOSトランジスタMN2は、ドレインがノードN2、ソースが接地端子GND、ゲートが反転入力端子IBに接続される。

【0042】

ここで、本実施の形態1の効果を説明するため、図8にジッタ抑制回路100が接続されない場合の例のSerDes回路を示す。また、図9に、本実施の形態1のジッタ抑制回路100が、信号分配配線161と分周回路130との接続ノードに、ジッタ抑制回路100の入力端子が接続される場合のSerDes回路構成を示す。更に、図10に、本実施の形態1のジッタ抑制回路100が、信号分配配線161と分周回路130との間で直列に接続された場合のSerDes回路構成を示す。なお、上記いずれの場合も図面の簡略化のため、PLL回路110、クロックドライバ121、信号分配配線161と、送受信回路171のジッタ抑制回路100、分周回路130の部分だけを示し、その他の部分は省略する。また、信号分配配線161から分周回路130までの配線距離は、信号分配配線161の配線長(例えば、3mm)と比較して十分に小さく、無視できるものとする。

【0043】

まず、図11に、図8のジッタ抑制回路100が接続されない回路構成における各ポイントでの信号S1〜S3、クロック信号CLK1〜CLK4のアイパターン波形を示す。このグラフの縦軸はクロック信号の電圧レベル[V]、横軸は時間[ns(ナノセカンド)]である。信号S1は、クロックドライバ121の入力差動クロック信号である。信号S2は、クロックドライバ121の出力差動クロック信号である。ここで、この信号S2に、クロックドライバ121の電源電圧ノイズによるジッタが重畳される場合を示す。本例では、A1[ns]のジッタが重畳される。

【0044】

信号S3は、上記電源ノイズによるジッタが重畳された信号S2が、信号分配配線161を通過し、分周回路130に入力されるノードでの波形を示している。この信号S3も信号S2のジッタがそのまま伝わっており、A2[ns]のジッタが重畳されている。そして、クロック信号CLK1〜CLK4は、信号S3を入力した分周回路130が出力するクロック信号である。このクロック信号CLK1〜CLK4にも、A2と同程度のジッタA3[ns]が重畳されている。

【0045】

次に、図12に、本実施の形態1の図9の回路構成の各ポイントにおける信号S1〜S3、クロック信号CLK1〜CLK4のアイパターン波形を示す。信号S1は、クロックドライバ121の入力差動クロック信号である。信号S2は、クロックドライバ121が出力する差動クロック信号であり、図11の場合と同等のジッタA1が重畳される。

【0046】

信号S3は、分周回路130に入力されるノードでの波形であるが、このノードにはジッタ抑制回路100の非反転入力端子IT、反転入力端子IBが接続されている。

【0047】

ここで、ジッタ抑制回路100の差動増幅回路AMP1は、非反転入力端子IT、反転入力端子IBに入力される差動信号の入力レベルが上昇すると、反転出力端子OT、反転出力端子OBに出力する差動信号の出力レベルを下降させる。逆に、入力される差動信号の入力レベルが下降すると、出力差動信号の出力レベルを上昇させる。

【0048】

本実施の形態1のジッタ抑制回路100では、この差動増幅回路AMP1の非反転入力端子ITと反転出力端子OBとの間に帰還抵抗R1、反転入力端子IBと非反転出力端子OTとの間に帰還抵抗R2が接続されており、出力側(OT、OB)から入力側(IT、IB)に帰還抵抗R1、R2を介して帰還がかかっている。このため、入力レベルが上昇した場合、それを下降させる力が働き、逆に入力レベルが下降した場合、それを上昇させる力が働き、入力側の変動が抑制される。更に、入力側の変動が抑制され、その抑制された信号が差動増幅回路AMP1に入力されるので、出力側の変動も更に抑制されることになる。図13、図14を用いて、この変動抑制の具体的な効果を示す。

【0049】

図13に、図8のジッタ抑制回路100が接続されない回路構成における信号S2、S3の信号波形及びクロックドライバ121に印加される電源電圧変動波形を示し、図14に、本実施の形態1の図9の回路構成における信号S2、S3、S4の信号波形及びクロックドライバ121に印加される電源電圧変動波形を示す。これらのグラフの縦軸はクロック信号の電圧レベル[V]、横軸は時間[ns]である。

【0050】

図13からもわかるように、クロックドライバ121に印加される電源電圧がノイズにより変動される。この電源ノイズによる変動に応じて、クロックドライバ121が出力する信号S2も変動し、ジッタが重畳される。信号S3では、信号分配配線161により電圧レベルは減衰しているが、上記電源ノイズによる変動がそのまま伝わっていることがわかる。

【0051】

しかし、本実施の形態1にかかるジッタ抑制回路100が接続された図9の回路構成でも図14に示すように、図13と同様、信号S2にクロックドライバ121に印加される電源電圧の揺れに応じたノイズが重畳されているが、信号S3にはその揺れによるノイズがそのまま伝わらず減衰しているのがわかる。これは、上述したジッタ抑制回路100の抑制効果により、ジッタ抑制回路100の入力側の変動が抑制されているためである。なお、信号S4(ジッタ抑制回路100の出力)では、更にノイズが小さくなっていることがわかる。

【0052】

このように、ジッタが重畳された信号S2が、信号分配配線161を通過し、ジッタ抑制回路100に入力されると、その信号レベルの変動を抑える働きをジッタ抑制回路100が行う。この結果、分周回路130に入力されるノードの信号波形の変動が抑制されることになる。よって、本実施の形態1では信号S3の信号レベルの変動(ノイズ)が抑制され、ジッタ抑制回路100が接続されない図11のジッタA2と比較して、信号S3のジッタB2[ns]が減少する。

【0053】

そして、この信号S3が分周回路130に入力され、分周回路130が信号S3に応じたクロック信号CLK1〜CLK4を出力する。結果として、図12からもわかるように、クロック信号CLK1〜CLK4のジッタB3[ns]は、図11のジッタA3と比較して大きく減少する。

【0054】

なお、上記説明は、ジッタ抑制回路100の非反転入力端子IT、反転入力端子IBにノイズが重畳された差動信号(信号S2)が入力された場合の説明であるが、ジッタ抑制回路100自身の電源電圧にノイズが重畳された場合にも、同様のジッタ抑制の効果がある。以下に説明する。

【0055】

通常、差動増幅回路は、電源電圧にノイズが重畳された場合、ノイズにより電源電圧が上昇すると差動増幅回路の出力レベルも上昇し、ノイズにより電源電圧が下降すれば出力レベルも下降する。このことにより、差動増幅回路の出力にはジッタが発生する。

【0056】

しかし、本実施の形態1のジッタ抑制回路100では、差動増幅回路AMP1の出力側が帰還抵抗R1、R2を介して入力側に帰還がかかっている。このため、電源ノイズにより差動増幅回路AMP1の出力レベルが上昇した場合、入力側を上昇させる方向に働き、結果として差動増幅回路AMP1の出力レベルを下降させる方向に働く。逆に、電源ノイズにより差動増幅回路AMP1の出力レベルが下降した場合、入力側を下降させる方向に働き、結果として差動増幅回路AMP1の出力レベルを上昇させる方向に働く。以上のことから、ジッタ抑制回路100は、自身の電源にノイズが発生した場合であっても、ジッタを抑制させる効果を有している。

【0057】

次に、図15に、本実施の形態1の図10の回路構成の各ポイントにおける信号S1〜S3、クロック信号CLK1〜CLK4のアイパターン波形を示す。信号S1は、クロックドライバ121の入力差動信号である。信号S2は、クロックドライバ121が出力する差動クロック信号であり、図11、図12の場合と同等のジッタA1が重畳される。

【0058】

信号S3は、信号S2が信号分配配線161を通過し、ジッタ抑制回路100に入力されるノードでの波形を示している。図15に示すように、信号S2にクロックドライバ121に印加される電源電圧の揺れに応じたノイズが重畳されているが、信号S3にはその揺れによるノイズがそのまま伝わらず減衰しているのがわかる。これは、上述したようにジッタ抑制回路100は、入力レベルが上昇した場合、それを下降させ、逆に入力レベルが下降した場合、それを上昇させ、入力側の変動が抑制されるためである。更に、入力側の変動が抑制され、その抑制された信号が差動増幅回路AMP1に入力されるので、出力側の変動も更に抑制される。よって、ジッタが重畳された信号S3が、ジッタ抑制回路100に入力されると、その信号のレベルの変動を抑える働きをジッタ抑制回路100が行い、その変動が抑制された差動信号がジッタ抑制回路100の非反転出力端子OT、反転出力端子OBから分周回路130の接続ノードへ信号S4として出力される。

【0059】

この信号S4のジッタC2[ns]は、信号S3のジッタA2と比較して、非常に小さな値となっている。この信号S4が分周回路130に入力され、信号S4に応じたクロック信号CLK1〜CLK4が分周回路130から出力される。結果として、図15からもわかるように、クロック信号CLK1〜CLK4のジッタC3[ns]は、図11のジッタA3、さらには図12のジッタB3と比較しても大きく減少する。

【0060】

更に、図16に、本実施の形態1の図10の回路構成におけるジッタ抑制回路100の周波数特性の一例を示す。このグラフの横軸はクロック周波数[Hz]、縦軸はゲイン[dB]である。この例では、例えばDCゲインが約4dBであり、また、クロック周波数が5GHzのとき、ゲインが約1dBとなる。上記DCゲインは、ジッタ抑制回路100の帰還抵抗R1、R2の大小により増減させることができる。例えば、抵抗値を大きくするとDCゲインも大きくなり、抵抗値を小さくするとDCゲインも小さくなる。

【0061】

また更に、図17に、本実施の形態1の図10の回路構成においてジッタ抑制回路100のDCゲインを変化させた、その変化に対するジッタ抑制回路100の入出力信号のジッタ量を示す。なお、ジッタ抑制回路100のDCゲインの変化は、帰還抵抗R1、R2の抵抗値を変えることにより行われる。横軸がDCゲイン[dB]、縦軸がジッタ量[ps(ピコセカンド)]である。

【0062】

また、ジッタ抑制回路100に入力される差動クロック信号(信号S3)の振幅レベルを所定の値の場合(図中の「中」)、所定の値より大きい場合(図中の「大」)、所定の値より小さい場合(図中の「小」)の3種類に分けて示す。この差動クロック信号(信号S3)の振幅レベルの大きさは、クロックドライバ121の出力や信号分配配線161の長さ等に応じて決定される。

【0063】

この図17のグラフからわかるように、DCゲインが小さい場合、つまり帰還抵抗の抵抗値が小さい場合、ジッタ抑制回路100の入出力共にジッタ量も小さくなり、逆にジッタ抑制回路100のDCゲインが大きい場合、つまり帰還抵抗の抵抗値が大きい場合、ジッタ抑制回路100の入出力共にジッタ量も大きくなる。特に、DCゲインが約15dBより大きくなると急激にジッタも増加する。但し、ジッタ抑制回路100の出力に関しては、帰還抵抗の抵抗値を小さくしていく(DCゲインを大きくしていく)と、約5dB付近からジッタ量が大きくなっていく。この理由は後述する。

【0064】

この様に、ジッタ抑制回路100の帰還抵抗の値の大きさによりジッタ量の抑制効果が異なり、入力する信号の振幅には依らず、DCゲインが5dBから15dB付近で最もジッタ量の抑制効果が大きくなる。

【0065】

なお、DCゲインが30dBで、入出力信号のジッタ量の値がほぼ同一となるのは、帰還抵抗の抵抗値が無限大、つまりジッタ抑制回路100の入力側と出力側との間がオープンとなっている状態であり、入力側のジッタがほぼそのまま出力側に現れているからである。

【0066】

上述したように、ジッタ抑制回路100は、電源ノイズの影響を受けて入力する差動信号の信号レベルが上下に変動した場合、帰還抵抗R1、R2を介して出力側から入力側に帰還がかかることにより、入力側の信号レベルの変動が抑制される。このことにより、ジッタ抑制回路100の差動増幅回路AMP1の入力には信号レベルの変動が抑制された信号が入力する。よって、差動増幅回路AMP1の出力も信号レベルの変動が抑制されたものになる。

【0067】

ここで、帰還抵抗の値が小さいほど、ジッタ抑制回路100の出力側から入力側への帰還量が大きくなる。このため、入力側の信号レベルの変動の抑制量も大きくなり、ジッタ抑制効果が大きくなる。但し、帰還抵抗の値を更に小さくする場合は、帰還量が大きくなりすぎ、信号レベルが逆方向に補正がかかるため、ジッタ抑制効果が悪化していくことになる。これは、図17のグラフでジッタ抑制回路100の出力が、帰還抵抗の値を小さくしていく(DCゲインを大きくしていく)と、ジッタ量が大きくなっていく理由となる。

【0068】

このため、ジッタ抑制回路100では、出力側から入力側への帰還量を大きくするため、使用する帰還抵抗の値を出来るだけ小さい値としたいが、その値が小さすぎてもジッタ量が増加してしまう。また、上述のように帰還抵抗の値が大きくなるほどジッタ量が増加する。このため、帰還抵抗の値が所定の値よりも小さすぎても、大きすぎてもやはりジッタ量が増加することから、ジッタ抑制回路100のDCゲインが約5〜15dBであることに対応する帰還抵抗の値とすることが、最もジッタ量を低下させる(ジッタ抑制効果が大きい)条件として好適となる。

【0069】

このように、本実施の形態1のジッタ抑制回路100では、特許文献1、2の従来技術のように、キャパシタを用いたアナログ回路のフィルタを使用せずに伝達する信号のジッタ量を低減させることが可能となり、回路素子の面積増大化を防止することができる。結果として、このジッタ抑制回路100が形成される半導体チップのチップ面積の増大化を防止することができ、製品コストの削減も可能となる。また、抵抗素子により帰還をかけているだけなので、クロック信号の低周波領域で、ジッタ抑制効果が小さくなることがない。

【0070】

また、特許文献1、2の技術では、入力から出力までに、信号がフィルタや複数の増幅回路等を直列に通過する。このため、通過する増幅回路等による信号の遅延が発生したり、増幅回路自身により発生するジッタが付加されて出力される問題があったが、本実施の形態1のジッタ抑制回路100では、ジッタ抑制回路100自身で発生するジッタを抑制する効果を有しており、上記問題の発生を抑制することができる。

【0071】

また、図18に、図10の回路構成でジッタ抑制回路100のDCゲインを一定にした状態で、信号分配配線161の配線長を変化させた、その変化に対するジッタ抑制回路100の出力信号のジッタ量を示す。横軸が配線長[μm]、縦軸がジッタ量[ps(ピコセカンド)]である。また、これと同時に図8の回路構成、つまり、ジッタ抑制回路100が無い構成でのジッタ量も示す。なお、図18において、図10の回路構成を「ジッタ抑制回路有」、図8の回路構成「ジッタ抑制回路無」と記載する。

【0072】

ここで、本図では、クロックドライバ121の駆動能力が大、中、小(それぞれ、図18中の「駆動能力大」、「駆動能力中」、「駆動能力小」として示す)の場合についてそれぞれプロットしている。なお、クロックドライバ121の駆動能力が小の場合を「1」として、駆動能力が中の場合ではその1.5倍、駆動能力が大の場合では3倍としている。

【0073】

図18において、ジッタ抑制回路100が無い図8の回路構成のグラフからもわかるように、クロックドライバ121の駆動能力が大きいほど、ジッタ量も小さくなっている。また、信号分配配線161の配線長が短いほどジッタ量も小さくなっている。

【0074】

ここで、一般的にクロックドライバ121のようなドライブアンプは、駆動能力が大きいほど消費電力も大きくなり、回路面積も大きくなる。但し、駆動能力が大きいほど、出力のクロック信号振幅が大きくなるので、電源ノイズの影響を受ける割合が小さくなり、図18に示すように、ジッタ量も小さくなる。逆に、駆動能力が小さいほどジッタ量は大きくなる。

【0075】

また、信号分配配線161の配線長が長くなるほど、クロックドライバ121の出力のクロック信号は減衰して振幅が小さくなる。このため、電源ノイズの影響を受ける割合が大きくなり、ジッタ量は大きくなる。逆に配線長が短いほど、ジッタ量は小さくなる。

【0076】

しかし、本実施の形態1のジッタ抑制回路100が接続された図10の回路構成では、図18からもわかるように、クロックドライバ121の駆動能力を大きくしても、ジッタ抑制回路100が無い場合と比較してジッタ量がほぼ変化しない。また、信号分配配線161の配線長が長くなっても、同様にジッタ量がほぼ変化しない。

【0077】

以上の結果から、図1や図3のような、クロックドライバ121と、それに接続される信号分配配線161を有するクロック分配系の回路構成では、ジッタ抑制回路100が無い場合と比較してクロックドライバ121の駆動能力を小さくしてもジッタ量を減らすことができる。このため、SerDes回路SD1の消費電力、回路面積を小さくすることができる。更に、信号分配配線161の配線長を長くしても、同様にジッタ量を減らすことができる。このため、クロックドライバを従属に接続する個数を減らすことができ、SerDes回路SD1の消費電力の削減、回路面積の削減に効果が大きい。

【0078】

図19〜図21に、クロックドライバ121の駆動能力を大、中、小の場合の各々について、ジッタ抑制回路100のジッタ抑制効果が大、中、小の場合、及び、ジッタ抑制回路100を使用しない場合(図8の回路構成)での信号分配配線161の配線長に対するジッタ量をプロットしたグラフを示す。なお、クロックドライバ121の駆動能力の大、中、小は、図18で説明したものと同様、クロックドライバ121の駆動能力が小の場合を「1」として、駆動能力が中の場合では1.5倍、駆動能力が大の場合では3倍としている。また、ジッタ抑制回路100のジッタ抑制効果は、上述したように帰還抵抗R1、R2の値を調整し、DCゲインを変化させることで実現する。なお、ジッタ抑制効果が大の場合、DCゲインの値を7dB、ジッタ抑制効果が中の場合、DCゲインの値を17dB、ジッタ抑制効果が小の場合、DCゲインの値を21dBとする。なお、このジッタ抑制回路100のジッタ抑制効果の大きさを、ジッタ抑制係数としてとらえることもできる。

【0079】

図19〜図21のそれぞれにおいて、ジッタ抑制回路100を使用しない回路構成では、信号分配配線161の配線長がM1〜M3[μm]と長くなるにつれ、ジッタ量も大きく増加している。しかし、本実施の形態1のジッタ抑制回路100が使用される場合では、配線長がM1〜M3[μm]が長くなるのに応じて、ジッタ抑制回路100のジッタ抑制効果を大きくすると、ほぼ一定の値以下のジッタ量を保つことができる。

【0080】

例えば、クロックドライバ121の駆動能力が小さく、最もジッタ量が大きい図21の場合を例に説明する。図21において、ジッタ抑制回路100を使用しない回路構成では、配線長がM1〜M3[μm]と長くなるにつれ、ジッタ量も大きく増加している。しかし、本実施の形態1のジッタ抑制回路100が使用される場合では、配線長がM1(配線長小)でジッタ抑制回路100のジッタ抑制効果が小のジッタ量J1、配線長がM2(配線長中)でジッタ抑制回路100のジッタ抑制効果が中のジッタ量J2、配線長がM3(配線長大)でジッタ抑制回路100のジッタ抑制効果が大のジッタ量J3で、ほぼ同一の値となっている。

【0081】

このように、クロックドライバ121の駆動能力が一定の場合、信号分配配線161の配線長が長くなるにつれ、ジッタ抑制回路100のジッタ抑制効果(抑制係数)を大きくすることで、ジッタ量を所定の値以下に抑制することができる。

【0082】

また、図19〜図21からわかるように、信号分配配線161の配線長が一定、例えば、配線長がM3[μm]の場合、クロックドライバ121の駆動能力が小さくなるほど、ジッタ量も大きくなっている。しかし、本実施の形態1のジッタ抑制回路100が使用される場合では、クロックドライバ121の駆動能力が大、中、小に応じて、ジッタ抑制回路100のジッタ抑制効果をそれぞれ小、中、大とすると、ジッタ量がJ4、J5、J3とほぼ一定の値以下のジッタ量を保つことができる。

【0083】

このように、信号分配配線161の配線長が一定の場合、クロックドライバ121の駆動能力が小さくなるにつれ、ジッタ抑制回路100のジッタ抑制効果(抑制係数)を大きくすることで、ジッタ量を所定の値以下に抑制することができる。

【0084】

以上のように、ジッタ抑制回路100のジッタ抑制効果(抑制係数)が大きいほど、信号分配配線161の配線長を長くすることができる。また、ジッタ抑制回路100のジッタ抑制効果(抑制係数)が大きいほど、クロックドライバ121の駆動能力を小さくすることができ、SerDes回路SD1の消費電力、回路面積を小さくすることができることがわかる。

【0085】

なお、特開2007−202147号公報に、高利得、広帯域のトランスインピーダンス増幅器の技術が開示されている。この高利得、広帯域のトランスインピーダンス増幅器では、差動増幅回路の入力側と出力側との間に帰還抵抗を接続しているが、本技術では高利得の増幅を前提として帰還抵抗を選択しなければならない。このため、大きな値の帰還抵抗を選択せねばならず、本実施の形態1のジッタ抑制回路100のように、上述したような所定の値に限定された帰還抵抗の値を用いることがなく、また、その示唆もされていない。

【0086】

更に、特開2007−202147号公報に開示されている高利得、広帯域のトランスインピーダンス増幅器は、増幅回路を多段に接続して利得を稼いでいるが、この場合、伝送される信号のジッタは接続段数が増加すると更に増加していくことになり、本構成をジッタ抑制回路として適用することは不可能となる。

【0087】

以上のことから、本発明が目的としている回路素子の面積増大化を防止しつつ、ジッタを削減することが、特開2007−202147号公報に開示されている高利得、広帯域のトランスインピーダンス増幅器では不可能であり、本実施の形態1のジッタ抑制回路100と特開2007−202147号公報に開示されている高利得、広帯域のトランスインピーダンス増幅器とは異なる構成となると言える。

【0088】

発明の実施の形態2

【0089】

以下、本発明を適用した具体的な実施の形態2について、図面を参照しながら詳細に説明する。この実施の形態2は、実施の形態1と同様、本発明をSerDes回路が備えるジッタ抑制回路に適用したものである。

【0090】

図22に本実施の形態2にかかるジッタ抑制回路200の構成を示す。図22に示すように、ジッタ抑制回路200は、差動増幅回路AMP1と、トランスファーゲートTG1、TG2とを有する。

【0091】

差動増幅回路AMP1は、差動クロック信号の一方を非反転入力端子ITに入力し、他方を反転入力端子IBに入力する。差動増幅回路AMP1は、非反転入力端子IT、反転入力端子IBに入力した差動クロック信号に応じた、出力差動信号を非反転出力端子OT、反転出力端子OBから出力する。

【0092】

トランスファーゲートTG1は、差動増幅回路AMP1の非反転入力端子ITと反転出力端子OBとの間に接続される。トランスファーゲートTG2は、差動増幅回路AMP1の反転入力端子IBと非反転出力端子OTとの間に接続される。

【0093】

なお、差動増幅回路AMP1の構成は、図7に示したものと同様であるためここでの説明は省略する。

【0094】

以上のように、本実施の形態2では、実施の形態1の帰還抵抗R1、R2を、それぞれトランスファーゲートTG1、TG2に置き換えている。トランスファーゲートTG1、TG2は、MOSトランジスタで形成されるので、抵抗素子よりも半導体チップに形成される素子面積が小さくすることが可能である。このため、帰還抵抗R1、R2を使用する場合と比較して、本実施の形態2では回路規模を小さくすることが可能となり、ジッタ抑制回路200が形成される半導体チップのチップ面積の増大化を更に強力に防止することができ、更なる製品コストの削減が可能となる。

【0095】

なお、差動増幅回路AMP1を図23に示すような構成の差動増幅回路AMP2としてもよい。差動増幅回路AMP2は、差動増幅回路AMP1からNMOSトランジスタMN3、MN4を削除した構成となっている。差動増幅回路AMP1と比較して、応答速度が低下するが、NMOSトランジスタMN3、MN4分の回路規模を削減することができる。なお、差動増幅回路AMP2を実施の形態1においても差動増幅回路AMP1の変わりに適用してもよい。

【0096】

発明の実施の形態3

【0097】

以下、本発明を適用した具体的な実施の形態3について、図面を参照しながら詳細に説明する。この実施の形態3は、実施の形態1と同様、本発明をSerDes回路が備えるジッタ抑制回路に適用したものである。

【0098】

本実施の形態3では、実施の形態1のクロックドライバ121を、図24に示すような構成とする。クロックドライバ122は、クロックドライバ121と同様の構成となるため、ここでの説明は省略する。

【0099】

図24に示すように、本実施の形態3のクロックドライバ121は、PMOSトランジスタMP11、MP12と、NMOSトランジスタMN11〜MN14と、帰還抵抗R11、R12と、インダクタLとを有する。帰還抵抗R11は、非反転入力端子ITと反転出力端子OBの間に接続される。帰還抵抗R12は、反転入力端子IBと非反転出力端子OTの間に接続される。その他の接続構成は、図2と同様であるため説明は省略する。

【0100】

このクロックドライバ121の構成は、図24に示すように、インダクタLを除き図7のジッタ抑制回路100と同様の構成となる。このため、ジッタ抑制回路100と同様、クロックドライバ121は、出力信号を帰還抵抗R11、R12を介して帰還をかける構成を有する。このため、何らかの原因でジッタが重畳された差動信号をPLL回路110から入力した場合や、クロックドライバ121の電源にノイズが乗っている場合等であっても、ジッタ抑制回路100と同様、出力する信号のジッタを抑制する効果を発揮することができる。このため、クロックドライバ121が信号分配配線161に出力する差動クロック信号のジッタを削減することができる。なお、破線で囲ったUNIT1の構成部分が図2のクロックドライバ121に相当する。

【0101】

以上のように、実施の形態3では、クロックドライバ121、122をジッタ抑制回路100と同様の構成とすることで、信号分配配線161、162に対する送信側のジッタを削減でき、実施の形態1、2の受信側のジッタ抑制回路と併用することで、SerDes回路のクロック伝達系システム内のジッタ抑制を効果的に行うことが可能となる。

【0102】

なお、本発明は上記実施の形態に限られたものでなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、上述した実施の形態1〜3では、本発明をSerDes回路のクロック伝達系システムに適用しているが、SerDes回路に限らず、図25に示すような一般的なクロック信号を分配するクロック伝達系システムに適用してもよい。

【0103】

図25に示すように、半導体集積回路(LSI)400内の回路ユニット41〜4n(n:自然数)のそれぞれがジッタ抑制回路100を有する。クロック生成回路40は、回路ユニット41〜4nに対して、クロック分配線を経由してクロック信号を分配する。このクロック分配線を経由して伝達されるクロック信号にジッタが重畳される場合、ジッタ抑制回路100が実施の形態1で説明したように、そのジッタを削減することできる。このため、回路ユニット41〜4nが使用する動作クロックのジッタ品質の劣化を防ぐことができる。なお、クロック分配線は、実施の形態1で説明したような差動クロック信号が伝達される。

【0104】

更に、ジッタを抑制する信号はクロック信号に限る必要はなく、データ信号であってもよい。例えば、SerDes回路の高速データ送信回路は、大きな配線寄生容量負荷を駆動する必要があるため、大きな消費電流を必要とする。このように、消費電流が大きいと電源に大きな電流供給負荷がかかり、電源ノイズも大きくなる。このため、電源ノイズの影響により、高速データ送信回路からのデータ出力信号のジッタが増大する。ここで、本発明のジッタ抑制回路100をデータ信号伝送系に使用することで、データ出力信号のジッタを抑制することができ、非常に効果的である。また、同様に、データ送信部分だけでなくSerDes回路の高速データ受信回路に応用することで、受信回路の電源ノイズに起因するジッタ等を抑制できる効果がある。

【符号の説明】

【0105】

SD1、SD2 SerDes回路

110 PLL回路

121、122 クロックドライバ

161、162 信号分配配線

171〜176 送受信回路

100 ジッタ抑制回路

130 分周回路

140 クロックデータリカバリ回路

150 多重化回路

AMP1、AMP2 差動増幅回路

R1、R2、R11、R12 帰還抵抗

MP1、MP2、MP11、MP12 PMOSトランジスタ

MN1〜MN4、MN11〜MN14 NMOSトランジスタ

L インダクタ

TG1、TG2 トランスファーゲート

LTC1、LTC2 ラッチ回路

【技術分野】

【0001】

本発明は、信号配線システム及びジッタ抑制回路に関するものである。

【背景技術】

【0002】

ジッタ抑制回路の従来技術として、特許文献1、2のような技術が開示されている。

【0003】

特許文献1には、図26に示すように、帯域通過フィルタ12と、整形回路13とを有するジッタ除去整形回路10が記載されている。帯域通過フィルタ12は、入力端子11から入力したジッタを有する基本クロック信号から基本クロック周波数成分のみを通過させる。整形回路13は、帯域通過フィルタ12の出力信号をコンパレータで電圧比較して基本クロックを再生し出力する。

【0004】

特許文献2には、図27に示すように、ジッタ成分検出回路22と、可変増幅器23と、差動増幅器24と、クロック再生回路25とを有するジッタ抑制回路20が記載されている。ジッタ成分検出回路22は、入力端子21からのジッタ成分を含んだクロック信号からジッタ成分のみを取り出す。可変増幅器23は、取り出されたジッタ成分をクロック信号の振幅より小さい振幅に設定する。差動増幅器24は、クロック信号と可変増幅器出力との差をとり、ジッタ位相を補正した差信号を生成し、出力する。クロック再生回路25は差信号のゼロクロス点を時間基準として再生クロック信号を出力端子に出力する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2001−344040号公報

【特許文献2】特開平6−53947号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1の技術では、帯域通過フィルタ12を構成するアナログ回路部品が必要である。帯域通過フィルタを構成する素子として、キャパシタや抵抗等があるが、半導体チップ上にキャパシタを形成する場合、素子面積の抑制が難しく、チップサイズが大きくなってしまう。逆に、キャパシタ等の素子サイズを小さくした場合、帯域通過フィルタの周波数帯域が狭くなり、当然ジッタ除去可能な周波数範囲も狭くなる。特に、低周波領域のジッタ抑制効果が小さくなる問題がある。

【0007】

特許文献2の技術では、ジッタ成分検出回路22が、ジッタ成分を含んだクロック信号からジッタ成分のみを取り出すが、この場合もフィルタ等のアナログ回路が必要となる。このため、上記した特許文献1と同様、素子面積の抑制が難しく、チップサイズが大きくなってしまう問題が発生する。また、可変増幅器23も回路規模の増加の原因となる。

【課題を解決するための手段】

【0008】

本発明の第1の態様は、差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部から前記受信部へ前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システムである。

【0009】

本発明の第2の態様は、差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記出力部から前記受信部へ前記差動信号を伝達する信号配線部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、を有し、前記出力部は、前記ジッタ抑制回路の前記抑制係数に応じた駆動能力で、前記差動信号を出力する信号配線システムである。

【0010】

本発明の第3の態様は、差動入力信号を反転入力端子、非反転入力端子に入力し、前記差動入力信号に応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、前記差動増幅回路の前記反転入力端子と非反転出力端子との間に接続される第1の帰還抵抗部と、前記差動増幅回路の前記非反転入力端子と反転出力端子との間に接続される第2の帰還抵抗部と、を有し、前記第1、第2の帰還抵抗部が、前記差動増幅回路の前記差動入力信号に対する前記出力信号のDCゲインが5〜15dB以下となる抵抗値を有するジッタ抑制回路である。

【0011】

本発明は、アナログ回路で構成されるフィルタを使用せず、受信部が受信する差動信号のジッタ量を削減することができる。

【発明の効果】

【0012】

本発明は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することができる。

【図面の簡単な説明】

【0013】

【図1】実施の形態1にかかるSerDes回路の構成である。

【図2】実施の形態1にかかるクロックドライバの構成である。

【図3】実施の形態1にかかるSerDes回路の構成である。

【図4】実施の形態1にかかる分周回路の構成である。

【図5】実施の形態1にかかる分周回路のタイミングチャート(理想動作)である。

【図6】実施の形態1にかかるジッタ抑制回路の構成である。

【図7】実施の形態1にかかるジッタ抑制回路の詳細な構成である。

【図8】実施の形態1にかかるジッタ抑制回路の効果を説明するための参考回路構成である。

【図9】実施の形態1にかかるジッタ抑制回路の効果を説明するための回路構成である。

【図10】実施の形態1にかかるジッタ抑制回路の効果を説明するための回路構成である。

【図11】図8の回路構成における各信号のアイパターンである。

【図12】実施の形態1にかかる図9の回路構成における各信号のアイパターンである。

【図13】図8の回路構成における各信号の波形図である。

【図14】実施の形態1にかかる図9の回路構成における各信号の波形図である。

【図15】実施の形態1にかかる図10の回路構成における各信号のアイパターンである。

【図16】実施の形態1にかかるジッタ抑制回路のゲインの周波数特性である。

【図17】実施の形態1にかかるジッタ抑制回路のDCゲインに対するジッタ特性である。

【図18】実施の形態1にかかるSerDes回路の信号分配配線の配線長に対するジッタ特性である。

【図19】実施の形態1にかかるSerDes回路におけるジッタ抑制回路の抑制効果に応じたジッタ量の変化を説明するグラフである。

【図20】実施の形態1にかかるSerDes回路におけるジッタ抑制回路の抑制効果に応じたジッタ量の変化を説明するグラフである。

【図21】実施の形態1にかかるSerDes回路におけるジッタ抑制回路の抑制効果に応じたジッタ量の変化を説明するグラフである。

【図22】実施の形態2にかかるジッタ抑制回路の構成である。

【図23】実施の形態2にかかるジッタ抑制回路の構成である。

【図24】実施の形態3にかかるクロックドライバの構成である。

【図25】その他の実施の形態にかかる半導体集積回路のブロック構成である。

【図26】従来技術の回路構成である。

【図27】従来技術の回路構成である。

【発明を実施するための形態】

【0014】

発明の実施の形態1

【0015】

以下、本発明を適用した具体的な実施の形態1について、図面を参照しながら詳細に説明する。この実施の形態1は、本発明をSerDes回路が備えるジッタ抑制回路に適用したものである。まず、図1に本実施の形態1にかかるSerDes(Serializer/Deserializer)回路SD1の構成を示す。

【0016】

図1に示すように、SerDes回路SD1は、PLL回路110と、クロックドライバ121、122と、送受信回路171〜176と、信号分配配線161、162とを有する。

【0017】

SerDes回路SD1は、複数の高速データ信号を送受信する。SerDes回路SD1は、パラレル信号をシリアル信号に、シリアル信号をパラレル信号に変換する。例えば、USB3.0等のような5Gbpsの高速データ信号を送受信する。このSerDes回路SD1のように高速データ信号を送受信する場合、パラレル−シリアル変換、シリアル−パラレル変換を行う送受信回路171〜176の動作クロックも高速なものが必要となる。

【0018】

PLL回路110は、SerDes回路SD1内で使用されるクロック信号を生成する。この生成されるクロック信号のクロック周波数は、例えば、5GHzと高速である。なお、本例では、このPLL回路110が生成するクロック信号は差動信号であり、以下、差動クロック信号と称す。

【0019】

クロックドライバ121、122は、PLL回路110が生成した差動クロック信号を、それぞれバッファリングし、信号分配配線161、162に出力する。図2に、クロックドライバ121の回路構成を示す。なお、クロックドライバ122も同様の回路構成である。図2に示すように、クロックドライバ121は、PMOSトランジスタMP11、MP12と、NMOSトランジスタMN11〜MN14と、インダクタLとを有する。

【0020】

PMOSトランジスタMP11は、ソースが電源端子VDD、ドレインが反転出力端子OB、ゲートがノードN12に接続される。PMOSトランジスタMP12は、ソースが電源端子VDD、ドレインが非反転出力端子OT、ゲートがノードN11に接続される。

【0021】

NMOSトランジスタMN13は、ドレインが反転出力端子OB、ソースがノードN11、ゲートが電源端子VDDに接続される。NMOSトランジスタMN14は、ドレインが非反転出力端子OT、ソースがノードN12、ゲートが電源端子VDDに接続される。

【0022】

NMOSトランジスタMN11は、ドレインがノードN11、ソースが接地端子GND、ゲートが非反転入力端子ITに接続される。NMOSトランジスタMN12は、ドレインがノードN12、ソースが接地端子GND、ゲートが反転入力端子IBに接続される。

【0023】

インダクタLが非反転出力端子OTと反転出力端子OBとの間に接続される。

【0024】

上記反転入力端子、非反転入力端子にPLL回路110が生成した差動クロック信号を入力し、反転出力端子、非反転出力端子から差動クロック信号が出力される。

【0025】

ここで、クロックドライバ121、122の電源を供給する端子(電源端子VDD)に供給される電圧(以降、必要に応じて電源電圧VDDと称す)にノイズが重畳されると、非反転出力端子OTと反転出力端子OBから出力される差動クロック信号にも、同様にその電源ノイズが重畳される(後述する図13、図14参照)。そして、そのノイズが重畳された差動クロック信号が、信号分配配線161、162に出力される。

【0026】

クロックドライバ121が出力した差動クロック信号は、信号分配配線161を経由して送受信回路171〜173に分配される。クロックドライバ122が出力した差動クロック信号は、信号分配配線162を経由して送受信回路174〜176に分配される。

【0027】

信号分配配線161、162は、例えば3mm程度の配線長を有し、数mm角の半導体チップにおいて大きな負荷容量となる。ここで、本例のように例えば3mmのような信号分配配線161、162で伝達されると、この高周波の差動クロック信号は減衰し、クロック振幅が小さくなってしまう。しかし、差動クロック信号に重畳されるジッタ量は減衰しないため、このジッタを抑制する機構が必要とされる。なお、上記「3mm」は単なる一例であり、配線長はこの数値に特に限定されない。

【0028】

また、図1のSerDes回路SD1では、クロックドライバ121、122のそれぞれがドライブする差動クロック信号が3分配であったが、それよりも分配数が多くなる場合、信号分配配線161、162の配線長を長くし、接続する送受信回路を増やさなければならない。しかし、上述したように、差動クロック信号の振幅が減衰してしまうため、減衰した差動クロック信号を増幅する必要がある。このため、図3に示すように、クロックドライバを複数段直列に接続して、差動クロック信号を分配するSerDes回路SD2のような構成を採用してもよい。図3の例では、クロックドライバ121にクロックドライバ122を直列接続する例を示しており、その他の構成は、図1と同様である。図3に示すように、クロックドライバを複数段直列に接続しているが、この場合、クロックドライバを複数段通ることで、クロックドライバ121、122の電源ノイズ等により、増幅される差動クロック信号に更にジッタが重畳される問題がある。そして、接続されるクロックドライバの段数が多ければ多いほどジッタ品質が劣化することになる。このため、やはり図3のような構成であっても、ジッタを抑制する機構が必要とされる。

【0029】

送受信回路171〜176はそれぞれ、ジッタ抑制回路100と、分周回路(DIV)130と、クロックデータリカバリ回路(CDR)140と、多重化回路(MUX)150とを有する。

【0030】

分周回路130は、ジッタ抑制回路100を経て入力した差動クロック信号を2分周し、4相のクロック信号CLK1〜CLK4を生成する。図4に分周回路130の構成の一例を示す。図4に示すように、分周回路130は、ラッチ回路LTC1、LTC2を有し、トグルフリップフロップを構成する。また、図5に、分周回路130の理想的な動作タイミングチャートを示す。なお、このタイミングチャートに示す信号波形は、ジッタ等の影響を受けていない理想的な動作を行っている場合を示す。なお、トグルフリップフロップを用いた分周回路は、一般的に用いられており、動作等の詳しい説明は省略する。分周回路130が生成したクロック信号CLK1〜CLK4は、クロックデータリカバリ回路140、多重化回路150の動作クロックとなる。本来は、例えば5GHzの高周波動作となるため、分周回路130に入力される差動クロック信号のジッタ品質が悪い(ジッタ量が多い)場合、分周回路130が出力するクロック信号のジッタ品質も当然悪化する。

【0031】

クロックデータリカバリ回路140は、分周回路130が生成したクロック信号を動作クロックとして動作する。クロックデータリカバリ回路140は、入力したシリアルデータをパラレルデータに変換し、出力する。

【0032】

多重化回路150は、分周回路130が生成したクロック信号を動作クロックとして動作する。多重化回路150は、入力したパラレルデータをシリアルデータに変換し、出力する。

【0033】

クロックデータリカバリ回路140及び多重化回路150は、分周回路130が生成したクロック信号を動作クロックとしているため、このクロック信号のジッタ品質が悪い場合、高速データの受信特性、送信特性を劣化させる原因となる。このため、分周回路130に入力される差動クロック信号のジッタを抑制する機構が必要とされる。

【0034】

ジッタ抑制回路100は、送受信回路171〜176のそれぞれに入力される差動クロック信号のジッタを抑制する機能を有する。分周回路130に入力される差動クロック信号のジッタを抑制することで、分周回路130が出力する4相のクロック信号CLK1〜CLK4のジッタを抑制する。結果として、このジッタが抑制された4相のクロック信号CLK1〜CLK4を動作クロックとするクロックデータリカバリ回路140及び多重化回路150の高速データの受信特性、送信特性の劣化も回避することが可能となる。

【0035】

図6に、ジッタ抑制回路100の構成を示す。図6に示すように、ジッタ抑制回路100は、差動増幅回路AMP1と、帰還抵抗R1、R2とを有する。

【0036】

差動増幅回路AMP1は、差動クロック信号の一方を非反転入力端子ITに入力し、他方を反転入力端子IBに入力する。差動増幅回路AMP1は、非反転入力端子、反転入力端子に入力した差動クロック信号に応じた、出力差動信号を非反転出力端子OT、反転出力端子OBから出力する。

【0037】

帰還抵抗R1は、差動増幅回路AMP1の非反転入力端子ITと反転出力端子OBとの間に接続される。帰還抵抗R2は、差動増幅回路AMP1の反転入力端子IBと非反転出力端子OTとの間に接続される。

【0038】

図7に、差動増幅回路AMP1の構成を示す。図7に示すように、差動増幅回路AMP1は、PMOSトランジスタMP1、MP2と、NMOSトランジスタMN1〜MN4とを有する。

【0039】

PMOSトランジスタMP1は、ソースが電源端子VDD、ドレインが反転出力端子OB、ゲートがノードN2に接続される。PMOSトランジスタMP2は、ソースが電源端子VDD、ドレインが非反転出力端子OT、ゲートがノードN1に接続される。

【0040】

NMOSトランジスタMN3は、ドレインが反転出力端子OB、ソースがノードN1、ゲートが電源端子VDDに接続される。NMOSトランジスタMN4は、ドレインが非反転出力端子OT、ソースがノードN2、ゲートが電源端子VDDに接続される。

【0041】

NMOSトランジスタMN1は、ドレインがノードN1、ソースが接地端子GND、ゲートが非反転入力端子ITに接続される。NMOSトランジスタMN2は、ドレインがノードN2、ソースが接地端子GND、ゲートが反転入力端子IBに接続される。

【0042】

ここで、本実施の形態1の効果を説明するため、図8にジッタ抑制回路100が接続されない場合の例のSerDes回路を示す。また、図9に、本実施の形態1のジッタ抑制回路100が、信号分配配線161と分周回路130との接続ノードに、ジッタ抑制回路100の入力端子が接続される場合のSerDes回路構成を示す。更に、図10に、本実施の形態1のジッタ抑制回路100が、信号分配配線161と分周回路130との間で直列に接続された場合のSerDes回路構成を示す。なお、上記いずれの場合も図面の簡略化のため、PLL回路110、クロックドライバ121、信号分配配線161と、送受信回路171のジッタ抑制回路100、分周回路130の部分だけを示し、その他の部分は省略する。また、信号分配配線161から分周回路130までの配線距離は、信号分配配線161の配線長(例えば、3mm)と比較して十分に小さく、無視できるものとする。

【0043】

まず、図11に、図8のジッタ抑制回路100が接続されない回路構成における各ポイントでの信号S1〜S3、クロック信号CLK1〜CLK4のアイパターン波形を示す。このグラフの縦軸はクロック信号の電圧レベル[V]、横軸は時間[ns(ナノセカンド)]である。信号S1は、クロックドライバ121の入力差動クロック信号である。信号S2は、クロックドライバ121の出力差動クロック信号である。ここで、この信号S2に、クロックドライバ121の電源電圧ノイズによるジッタが重畳される場合を示す。本例では、A1[ns]のジッタが重畳される。

【0044】

信号S3は、上記電源ノイズによるジッタが重畳された信号S2が、信号分配配線161を通過し、分周回路130に入力されるノードでの波形を示している。この信号S3も信号S2のジッタがそのまま伝わっており、A2[ns]のジッタが重畳されている。そして、クロック信号CLK1〜CLK4は、信号S3を入力した分周回路130が出力するクロック信号である。このクロック信号CLK1〜CLK4にも、A2と同程度のジッタA3[ns]が重畳されている。

【0045】

次に、図12に、本実施の形態1の図9の回路構成の各ポイントにおける信号S1〜S3、クロック信号CLK1〜CLK4のアイパターン波形を示す。信号S1は、クロックドライバ121の入力差動クロック信号である。信号S2は、クロックドライバ121が出力する差動クロック信号であり、図11の場合と同等のジッタA1が重畳される。

【0046】

信号S3は、分周回路130に入力されるノードでの波形であるが、このノードにはジッタ抑制回路100の非反転入力端子IT、反転入力端子IBが接続されている。

【0047】

ここで、ジッタ抑制回路100の差動増幅回路AMP1は、非反転入力端子IT、反転入力端子IBに入力される差動信号の入力レベルが上昇すると、反転出力端子OT、反転出力端子OBに出力する差動信号の出力レベルを下降させる。逆に、入力される差動信号の入力レベルが下降すると、出力差動信号の出力レベルを上昇させる。

【0048】

本実施の形態1のジッタ抑制回路100では、この差動増幅回路AMP1の非反転入力端子ITと反転出力端子OBとの間に帰還抵抗R1、反転入力端子IBと非反転出力端子OTとの間に帰還抵抗R2が接続されており、出力側(OT、OB)から入力側(IT、IB)に帰還抵抗R1、R2を介して帰還がかかっている。このため、入力レベルが上昇した場合、それを下降させる力が働き、逆に入力レベルが下降した場合、それを上昇させる力が働き、入力側の変動が抑制される。更に、入力側の変動が抑制され、その抑制された信号が差動増幅回路AMP1に入力されるので、出力側の変動も更に抑制されることになる。図13、図14を用いて、この変動抑制の具体的な効果を示す。

【0049】

図13に、図8のジッタ抑制回路100が接続されない回路構成における信号S2、S3の信号波形及びクロックドライバ121に印加される電源電圧変動波形を示し、図14に、本実施の形態1の図9の回路構成における信号S2、S3、S4の信号波形及びクロックドライバ121に印加される電源電圧変動波形を示す。これらのグラフの縦軸はクロック信号の電圧レベル[V]、横軸は時間[ns]である。

【0050】

図13からもわかるように、クロックドライバ121に印加される電源電圧がノイズにより変動される。この電源ノイズによる変動に応じて、クロックドライバ121が出力する信号S2も変動し、ジッタが重畳される。信号S3では、信号分配配線161により電圧レベルは減衰しているが、上記電源ノイズによる変動がそのまま伝わっていることがわかる。

【0051】

しかし、本実施の形態1にかかるジッタ抑制回路100が接続された図9の回路構成でも図14に示すように、図13と同様、信号S2にクロックドライバ121に印加される電源電圧の揺れに応じたノイズが重畳されているが、信号S3にはその揺れによるノイズがそのまま伝わらず減衰しているのがわかる。これは、上述したジッタ抑制回路100の抑制効果により、ジッタ抑制回路100の入力側の変動が抑制されているためである。なお、信号S4(ジッタ抑制回路100の出力)では、更にノイズが小さくなっていることがわかる。

【0052】

このように、ジッタが重畳された信号S2が、信号分配配線161を通過し、ジッタ抑制回路100に入力されると、その信号レベルの変動を抑える働きをジッタ抑制回路100が行う。この結果、分周回路130に入力されるノードの信号波形の変動が抑制されることになる。よって、本実施の形態1では信号S3の信号レベルの変動(ノイズ)が抑制され、ジッタ抑制回路100が接続されない図11のジッタA2と比較して、信号S3のジッタB2[ns]が減少する。

【0053】

そして、この信号S3が分周回路130に入力され、分周回路130が信号S3に応じたクロック信号CLK1〜CLK4を出力する。結果として、図12からもわかるように、クロック信号CLK1〜CLK4のジッタB3[ns]は、図11のジッタA3と比較して大きく減少する。

【0054】

なお、上記説明は、ジッタ抑制回路100の非反転入力端子IT、反転入力端子IBにノイズが重畳された差動信号(信号S2)が入力された場合の説明であるが、ジッタ抑制回路100自身の電源電圧にノイズが重畳された場合にも、同様のジッタ抑制の効果がある。以下に説明する。

【0055】

通常、差動増幅回路は、電源電圧にノイズが重畳された場合、ノイズにより電源電圧が上昇すると差動増幅回路の出力レベルも上昇し、ノイズにより電源電圧が下降すれば出力レベルも下降する。このことにより、差動増幅回路の出力にはジッタが発生する。

【0056】

しかし、本実施の形態1のジッタ抑制回路100では、差動増幅回路AMP1の出力側が帰還抵抗R1、R2を介して入力側に帰還がかかっている。このため、電源ノイズにより差動増幅回路AMP1の出力レベルが上昇した場合、入力側を上昇させる方向に働き、結果として差動増幅回路AMP1の出力レベルを下降させる方向に働く。逆に、電源ノイズにより差動増幅回路AMP1の出力レベルが下降した場合、入力側を下降させる方向に働き、結果として差動増幅回路AMP1の出力レベルを上昇させる方向に働く。以上のことから、ジッタ抑制回路100は、自身の電源にノイズが発生した場合であっても、ジッタを抑制させる効果を有している。

【0057】

次に、図15に、本実施の形態1の図10の回路構成の各ポイントにおける信号S1〜S3、クロック信号CLK1〜CLK4のアイパターン波形を示す。信号S1は、クロックドライバ121の入力差動信号である。信号S2は、クロックドライバ121が出力する差動クロック信号であり、図11、図12の場合と同等のジッタA1が重畳される。

【0058】

信号S3は、信号S2が信号分配配線161を通過し、ジッタ抑制回路100に入力されるノードでの波形を示している。図15に示すように、信号S2にクロックドライバ121に印加される電源電圧の揺れに応じたノイズが重畳されているが、信号S3にはその揺れによるノイズがそのまま伝わらず減衰しているのがわかる。これは、上述したようにジッタ抑制回路100は、入力レベルが上昇した場合、それを下降させ、逆に入力レベルが下降した場合、それを上昇させ、入力側の変動が抑制されるためである。更に、入力側の変動が抑制され、その抑制された信号が差動増幅回路AMP1に入力されるので、出力側の変動も更に抑制される。よって、ジッタが重畳された信号S3が、ジッタ抑制回路100に入力されると、その信号のレベルの変動を抑える働きをジッタ抑制回路100が行い、その変動が抑制された差動信号がジッタ抑制回路100の非反転出力端子OT、反転出力端子OBから分周回路130の接続ノードへ信号S4として出力される。

【0059】

この信号S4のジッタC2[ns]は、信号S3のジッタA2と比較して、非常に小さな値となっている。この信号S4が分周回路130に入力され、信号S4に応じたクロック信号CLK1〜CLK4が分周回路130から出力される。結果として、図15からもわかるように、クロック信号CLK1〜CLK4のジッタC3[ns]は、図11のジッタA3、さらには図12のジッタB3と比較しても大きく減少する。

【0060】

更に、図16に、本実施の形態1の図10の回路構成におけるジッタ抑制回路100の周波数特性の一例を示す。このグラフの横軸はクロック周波数[Hz]、縦軸はゲイン[dB]である。この例では、例えばDCゲインが約4dBであり、また、クロック周波数が5GHzのとき、ゲインが約1dBとなる。上記DCゲインは、ジッタ抑制回路100の帰還抵抗R1、R2の大小により増減させることができる。例えば、抵抗値を大きくするとDCゲインも大きくなり、抵抗値を小さくするとDCゲインも小さくなる。

【0061】

また更に、図17に、本実施の形態1の図10の回路構成においてジッタ抑制回路100のDCゲインを変化させた、その変化に対するジッタ抑制回路100の入出力信号のジッタ量を示す。なお、ジッタ抑制回路100のDCゲインの変化は、帰還抵抗R1、R2の抵抗値を変えることにより行われる。横軸がDCゲイン[dB]、縦軸がジッタ量[ps(ピコセカンド)]である。

【0062】

また、ジッタ抑制回路100に入力される差動クロック信号(信号S3)の振幅レベルを所定の値の場合(図中の「中」)、所定の値より大きい場合(図中の「大」)、所定の値より小さい場合(図中の「小」)の3種類に分けて示す。この差動クロック信号(信号S3)の振幅レベルの大きさは、クロックドライバ121の出力や信号分配配線161の長さ等に応じて決定される。

【0063】

この図17のグラフからわかるように、DCゲインが小さい場合、つまり帰還抵抗の抵抗値が小さい場合、ジッタ抑制回路100の入出力共にジッタ量も小さくなり、逆にジッタ抑制回路100のDCゲインが大きい場合、つまり帰還抵抗の抵抗値が大きい場合、ジッタ抑制回路100の入出力共にジッタ量も大きくなる。特に、DCゲインが約15dBより大きくなると急激にジッタも増加する。但し、ジッタ抑制回路100の出力に関しては、帰還抵抗の抵抗値を小さくしていく(DCゲインを大きくしていく)と、約5dB付近からジッタ量が大きくなっていく。この理由は後述する。

【0064】

この様に、ジッタ抑制回路100の帰還抵抗の値の大きさによりジッタ量の抑制効果が異なり、入力する信号の振幅には依らず、DCゲインが5dBから15dB付近で最もジッタ量の抑制効果が大きくなる。

【0065】

なお、DCゲインが30dBで、入出力信号のジッタ量の値がほぼ同一となるのは、帰還抵抗の抵抗値が無限大、つまりジッタ抑制回路100の入力側と出力側との間がオープンとなっている状態であり、入力側のジッタがほぼそのまま出力側に現れているからである。

【0066】

上述したように、ジッタ抑制回路100は、電源ノイズの影響を受けて入力する差動信号の信号レベルが上下に変動した場合、帰還抵抗R1、R2を介して出力側から入力側に帰還がかかることにより、入力側の信号レベルの変動が抑制される。このことにより、ジッタ抑制回路100の差動増幅回路AMP1の入力には信号レベルの変動が抑制された信号が入力する。よって、差動増幅回路AMP1の出力も信号レベルの変動が抑制されたものになる。

【0067】

ここで、帰還抵抗の値が小さいほど、ジッタ抑制回路100の出力側から入力側への帰還量が大きくなる。このため、入力側の信号レベルの変動の抑制量も大きくなり、ジッタ抑制効果が大きくなる。但し、帰還抵抗の値を更に小さくする場合は、帰還量が大きくなりすぎ、信号レベルが逆方向に補正がかかるため、ジッタ抑制効果が悪化していくことになる。これは、図17のグラフでジッタ抑制回路100の出力が、帰還抵抗の値を小さくしていく(DCゲインを大きくしていく)と、ジッタ量が大きくなっていく理由となる。

【0068】

このため、ジッタ抑制回路100では、出力側から入力側への帰還量を大きくするため、使用する帰還抵抗の値を出来るだけ小さい値としたいが、その値が小さすぎてもジッタ量が増加してしまう。また、上述のように帰還抵抗の値が大きくなるほどジッタ量が増加する。このため、帰還抵抗の値が所定の値よりも小さすぎても、大きすぎてもやはりジッタ量が増加することから、ジッタ抑制回路100のDCゲインが約5〜15dBであることに対応する帰還抵抗の値とすることが、最もジッタ量を低下させる(ジッタ抑制効果が大きい)条件として好適となる。

【0069】

このように、本実施の形態1のジッタ抑制回路100では、特許文献1、2の従来技術のように、キャパシタを用いたアナログ回路のフィルタを使用せずに伝達する信号のジッタ量を低減させることが可能となり、回路素子の面積増大化を防止することができる。結果として、このジッタ抑制回路100が形成される半導体チップのチップ面積の増大化を防止することができ、製品コストの削減も可能となる。また、抵抗素子により帰還をかけているだけなので、クロック信号の低周波領域で、ジッタ抑制効果が小さくなることがない。

【0070】

また、特許文献1、2の技術では、入力から出力までに、信号がフィルタや複数の増幅回路等を直列に通過する。このため、通過する増幅回路等による信号の遅延が発生したり、増幅回路自身により発生するジッタが付加されて出力される問題があったが、本実施の形態1のジッタ抑制回路100では、ジッタ抑制回路100自身で発生するジッタを抑制する効果を有しており、上記問題の発生を抑制することができる。

【0071】

また、図18に、図10の回路構成でジッタ抑制回路100のDCゲインを一定にした状態で、信号分配配線161の配線長を変化させた、その変化に対するジッタ抑制回路100の出力信号のジッタ量を示す。横軸が配線長[μm]、縦軸がジッタ量[ps(ピコセカンド)]である。また、これと同時に図8の回路構成、つまり、ジッタ抑制回路100が無い構成でのジッタ量も示す。なお、図18において、図10の回路構成を「ジッタ抑制回路有」、図8の回路構成「ジッタ抑制回路無」と記載する。

【0072】

ここで、本図では、クロックドライバ121の駆動能力が大、中、小(それぞれ、図18中の「駆動能力大」、「駆動能力中」、「駆動能力小」として示す)の場合についてそれぞれプロットしている。なお、クロックドライバ121の駆動能力が小の場合を「1」として、駆動能力が中の場合ではその1.5倍、駆動能力が大の場合では3倍としている。

【0073】

図18において、ジッタ抑制回路100が無い図8の回路構成のグラフからもわかるように、クロックドライバ121の駆動能力が大きいほど、ジッタ量も小さくなっている。また、信号分配配線161の配線長が短いほどジッタ量も小さくなっている。

【0074】

ここで、一般的にクロックドライバ121のようなドライブアンプは、駆動能力が大きいほど消費電力も大きくなり、回路面積も大きくなる。但し、駆動能力が大きいほど、出力のクロック信号振幅が大きくなるので、電源ノイズの影響を受ける割合が小さくなり、図18に示すように、ジッタ量も小さくなる。逆に、駆動能力が小さいほどジッタ量は大きくなる。

【0075】

また、信号分配配線161の配線長が長くなるほど、クロックドライバ121の出力のクロック信号は減衰して振幅が小さくなる。このため、電源ノイズの影響を受ける割合が大きくなり、ジッタ量は大きくなる。逆に配線長が短いほど、ジッタ量は小さくなる。

【0076】

しかし、本実施の形態1のジッタ抑制回路100が接続された図10の回路構成では、図18からもわかるように、クロックドライバ121の駆動能力を大きくしても、ジッタ抑制回路100が無い場合と比較してジッタ量がほぼ変化しない。また、信号分配配線161の配線長が長くなっても、同様にジッタ量がほぼ変化しない。

【0077】

以上の結果から、図1や図3のような、クロックドライバ121と、それに接続される信号分配配線161を有するクロック分配系の回路構成では、ジッタ抑制回路100が無い場合と比較してクロックドライバ121の駆動能力を小さくしてもジッタ量を減らすことができる。このため、SerDes回路SD1の消費電力、回路面積を小さくすることができる。更に、信号分配配線161の配線長を長くしても、同様にジッタ量を減らすことができる。このため、クロックドライバを従属に接続する個数を減らすことができ、SerDes回路SD1の消費電力の削減、回路面積の削減に効果が大きい。

【0078】

図19〜図21に、クロックドライバ121の駆動能力を大、中、小の場合の各々について、ジッタ抑制回路100のジッタ抑制効果が大、中、小の場合、及び、ジッタ抑制回路100を使用しない場合(図8の回路構成)での信号分配配線161の配線長に対するジッタ量をプロットしたグラフを示す。なお、クロックドライバ121の駆動能力の大、中、小は、図18で説明したものと同様、クロックドライバ121の駆動能力が小の場合を「1」として、駆動能力が中の場合では1.5倍、駆動能力が大の場合では3倍としている。また、ジッタ抑制回路100のジッタ抑制効果は、上述したように帰還抵抗R1、R2の値を調整し、DCゲインを変化させることで実現する。なお、ジッタ抑制効果が大の場合、DCゲインの値を7dB、ジッタ抑制効果が中の場合、DCゲインの値を17dB、ジッタ抑制効果が小の場合、DCゲインの値を21dBとする。なお、このジッタ抑制回路100のジッタ抑制効果の大きさを、ジッタ抑制係数としてとらえることもできる。

【0079】

図19〜図21のそれぞれにおいて、ジッタ抑制回路100を使用しない回路構成では、信号分配配線161の配線長がM1〜M3[μm]と長くなるにつれ、ジッタ量も大きく増加している。しかし、本実施の形態1のジッタ抑制回路100が使用される場合では、配線長がM1〜M3[μm]が長くなるのに応じて、ジッタ抑制回路100のジッタ抑制効果を大きくすると、ほぼ一定の値以下のジッタ量を保つことができる。

【0080】

例えば、クロックドライバ121の駆動能力が小さく、最もジッタ量が大きい図21の場合を例に説明する。図21において、ジッタ抑制回路100を使用しない回路構成では、配線長がM1〜M3[μm]と長くなるにつれ、ジッタ量も大きく増加している。しかし、本実施の形態1のジッタ抑制回路100が使用される場合では、配線長がM1(配線長小)でジッタ抑制回路100のジッタ抑制効果が小のジッタ量J1、配線長がM2(配線長中)でジッタ抑制回路100のジッタ抑制効果が中のジッタ量J2、配線長がM3(配線長大)でジッタ抑制回路100のジッタ抑制効果が大のジッタ量J3で、ほぼ同一の値となっている。

【0081】

このように、クロックドライバ121の駆動能力が一定の場合、信号分配配線161の配線長が長くなるにつれ、ジッタ抑制回路100のジッタ抑制効果(抑制係数)を大きくすることで、ジッタ量を所定の値以下に抑制することができる。

【0082】

また、図19〜図21からわかるように、信号分配配線161の配線長が一定、例えば、配線長がM3[μm]の場合、クロックドライバ121の駆動能力が小さくなるほど、ジッタ量も大きくなっている。しかし、本実施の形態1のジッタ抑制回路100が使用される場合では、クロックドライバ121の駆動能力が大、中、小に応じて、ジッタ抑制回路100のジッタ抑制効果をそれぞれ小、中、大とすると、ジッタ量がJ4、J5、J3とほぼ一定の値以下のジッタ量を保つことができる。

【0083】

このように、信号分配配線161の配線長が一定の場合、クロックドライバ121の駆動能力が小さくなるにつれ、ジッタ抑制回路100のジッタ抑制効果(抑制係数)を大きくすることで、ジッタ量を所定の値以下に抑制することができる。

【0084】

以上のように、ジッタ抑制回路100のジッタ抑制効果(抑制係数)が大きいほど、信号分配配線161の配線長を長くすることができる。また、ジッタ抑制回路100のジッタ抑制効果(抑制係数)が大きいほど、クロックドライバ121の駆動能力を小さくすることができ、SerDes回路SD1の消費電力、回路面積を小さくすることができることがわかる。

【0085】

なお、特開2007−202147号公報に、高利得、広帯域のトランスインピーダンス増幅器の技術が開示されている。この高利得、広帯域のトランスインピーダンス増幅器では、差動増幅回路の入力側と出力側との間に帰還抵抗を接続しているが、本技術では高利得の増幅を前提として帰還抵抗を選択しなければならない。このため、大きな値の帰還抵抗を選択せねばならず、本実施の形態1のジッタ抑制回路100のように、上述したような所定の値に限定された帰還抵抗の値を用いることがなく、また、その示唆もされていない。

【0086】

更に、特開2007−202147号公報に開示されている高利得、広帯域のトランスインピーダンス増幅器は、増幅回路を多段に接続して利得を稼いでいるが、この場合、伝送される信号のジッタは接続段数が増加すると更に増加していくことになり、本構成をジッタ抑制回路として適用することは不可能となる。

【0087】

以上のことから、本発明が目的としている回路素子の面積増大化を防止しつつ、ジッタを削減することが、特開2007−202147号公報に開示されている高利得、広帯域のトランスインピーダンス増幅器では不可能であり、本実施の形態1のジッタ抑制回路100と特開2007−202147号公報に開示されている高利得、広帯域のトランスインピーダンス増幅器とは異なる構成となると言える。

【0088】

発明の実施の形態2

【0089】

以下、本発明を適用した具体的な実施の形態2について、図面を参照しながら詳細に説明する。この実施の形態2は、実施の形態1と同様、本発明をSerDes回路が備えるジッタ抑制回路に適用したものである。

【0090】

図22に本実施の形態2にかかるジッタ抑制回路200の構成を示す。図22に示すように、ジッタ抑制回路200は、差動増幅回路AMP1と、トランスファーゲートTG1、TG2とを有する。

【0091】

差動増幅回路AMP1は、差動クロック信号の一方を非反転入力端子ITに入力し、他方を反転入力端子IBに入力する。差動増幅回路AMP1は、非反転入力端子IT、反転入力端子IBに入力した差動クロック信号に応じた、出力差動信号を非反転出力端子OT、反転出力端子OBから出力する。

【0092】

トランスファーゲートTG1は、差動増幅回路AMP1の非反転入力端子ITと反転出力端子OBとの間に接続される。トランスファーゲートTG2は、差動増幅回路AMP1の反転入力端子IBと非反転出力端子OTとの間に接続される。

【0093】

なお、差動増幅回路AMP1の構成は、図7に示したものと同様であるためここでの説明は省略する。

【0094】

以上のように、本実施の形態2では、実施の形態1の帰還抵抗R1、R2を、それぞれトランスファーゲートTG1、TG2に置き換えている。トランスファーゲートTG1、TG2は、MOSトランジスタで形成されるので、抵抗素子よりも半導体チップに形成される素子面積が小さくすることが可能である。このため、帰還抵抗R1、R2を使用する場合と比較して、本実施の形態2では回路規模を小さくすることが可能となり、ジッタ抑制回路200が形成される半導体チップのチップ面積の増大化を更に強力に防止することができ、更なる製品コストの削減が可能となる。

【0095】

なお、差動増幅回路AMP1を図23に示すような構成の差動増幅回路AMP2としてもよい。差動増幅回路AMP2は、差動増幅回路AMP1からNMOSトランジスタMN3、MN4を削除した構成となっている。差動増幅回路AMP1と比較して、応答速度が低下するが、NMOSトランジスタMN3、MN4分の回路規模を削減することができる。なお、差動増幅回路AMP2を実施の形態1においても差動増幅回路AMP1の変わりに適用してもよい。

【0096】

発明の実施の形態3

【0097】

以下、本発明を適用した具体的な実施の形態3について、図面を参照しながら詳細に説明する。この実施の形態3は、実施の形態1と同様、本発明をSerDes回路が備えるジッタ抑制回路に適用したものである。

【0098】

本実施の形態3では、実施の形態1のクロックドライバ121を、図24に示すような構成とする。クロックドライバ122は、クロックドライバ121と同様の構成となるため、ここでの説明は省略する。

【0099】

図24に示すように、本実施の形態3のクロックドライバ121は、PMOSトランジスタMP11、MP12と、NMOSトランジスタMN11〜MN14と、帰還抵抗R11、R12と、インダクタLとを有する。帰還抵抗R11は、非反転入力端子ITと反転出力端子OBの間に接続される。帰還抵抗R12は、反転入力端子IBと非反転出力端子OTの間に接続される。その他の接続構成は、図2と同様であるため説明は省略する。

【0100】

このクロックドライバ121の構成は、図24に示すように、インダクタLを除き図7のジッタ抑制回路100と同様の構成となる。このため、ジッタ抑制回路100と同様、クロックドライバ121は、出力信号を帰還抵抗R11、R12を介して帰還をかける構成を有する。このため、何らかの原因でジッタが重畳された差動信号をPLL回路110から入力した場合や、クロックドライバ121の電源にノイズが乗っている場合等であっても、ジッタ抑制回路100と同様、出力する信号のジッタを抑制する効果を発揮することができる。このため、クロックドライバ121が信号分配配線161に出力する差動クロック信号のジッタを削減することができる。なお、破線で囲ったUNIT1の構成部分が図2のクロックドライバ121に相当する。

【0101】

以上のように、実施の形態3では、クロックドライバ121、122をジッタ抑制回路100と同様の構成とすることで、信号分配配線161、162に対する送信側のジッタを削減でき、実施の形態1、2の受信側のジッタ抑制回路と併用することで、SerDes回路のクロック伝達系システム内のジッタ抑制を効果的に行うことが可能となる。

【0102】

なお、本発明は上記実施の形態に限られたものでなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、上述した実施の形態1〜3では、本発明をSerDes回路のクロック伝達系システムに適用しているが、SerDes回路に限らず、図25に示すような一般的なクロック信号を分配するクロック伝達系システムに適用してもよい。

【0103】

図25に示すように、半導体集積回路(LSI)400内の回路ユニット41〜4n(n:自然数)のそれぞれがジッタ抑制回路100を有する。クロック生成回路40は、回路ユニット41〜4nに対して、クロック分配線を経由してクロック信号を分配する。このクロック分配線を経由して伝達されるクロック信号にジッタが重畳される場合、ジッタ抑制回路100が実施の形態1で説明したように、そのジッタを削減することできる。このため、回路ユニット41〜4nが使用する動作クロックのジッタ品質の劣化を防ぐことができる。なお、クロック分配線は、実施の形態1で説明したような差動クロック信号が伝達される。

【0104】

更に、ジッタを抑制する信号はクロック信号に限る必要はなく、データ信号であってもよい。例えば、SerDes回路の高速データ送信回路は、大きな配線寄生容量負荷を駆動する必要があるため、大きな消費電流を必要とする。このように、消費電流が大きいと電源に大きな電流供給負荷がかかり、電源ノイズも大きくなる。このため、電源ノイズの影響により、高速データ送信回路からのデータ出力信号のジッタが増大する。ここで、本発明のジッタ抑制回路100をデータ信号伝送系に使用することで、データ出力信号のジッタを抑制することができ、非常に効果的である。また、同様に、データ送信部分だけでなくSerDes回路の高速データ受信回路に応用することで、受信回路の電源ノイズに起因するジッタ等を抑制できる効果がある。

【符号の説明】

【0105】

SD1、SD2 SerDes回路

110 PLL回路

121、122 クロックドライバ

161、162 信号分配配線

171〜176 送受信回路

100 ジッタ抑制回路

130 分周回路

140 クロックデータリカバリ回路

150 多重化回路

AMP1、AMP2 差動増幅回路

R1、R2、R11、R12 帰還抵抗

MP1、MP2、MP11、MP12 PMOSトランジスタ

MN1〜MN4、MN11〜MN14 NMOSトランジスタ

L インダクタ

TG1、TG2 トランスファーゲート

LTC1、LTC2 ラッチ回路

【特許請求の範囲】

【請求項1】

差動信号を出力する出力部と、

前記出力部からの前記差動信号を受信する受信部と、

前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、

前記出力部から前記受信部へ前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する

信号配線システム。

【請求項2】

前記出力部が出力する前記差動信号は、クロック信号であり、

前記信号配線部は、前記クロック信号を複数の前記受信部に分配するクロック分配配線である

請求項1に記載の信号配線システム。

【請求項3】

前記ジッタ抑制回路は、

前記信号配線部が伝達する前記差動信号を反転入力端子、非反転入力端子に入力し、それに応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記反転入力端子と非反転出力端子との間に接続される第1の帰還抵抗部と、

前記非反転入力端子と反転出力端子との間に接続される第2の帰還抵抗部と、を備え、

前記抑制係数は、前記第1、第2の帰還抵抗部の抵抗値に応じて決定される

請求項1または請求項2に記載の信号配線システム。

【請求項4】

前記差動増幅回路の反転入力端子、非反転入力端子が前記信号配線部と接続され、

前記差動増幅回路の反転出力端子、非反転出力端子が前記受信部と接続される

請求項3に記載の信号配線システム。

【請求項5】

前記差動増幅回路の反転入力端子、非反転入力端子が、前記信号配線部と第1、第2のノードで接続され、

前記第1、第2のノードが前記受信部と接続される

請求項3に記載の信号配線システム。

【請求項6】

前記第1、第2の帰還抵抗部が、抵抗素子もしくはトランスファーゲートである

請求項3〜請求項5のいずれか1項に記載の信号配線システム。

【請求項7】

前記出力部が、前記差動信号を生成する出力ドライバを有し、

前記出力ドライバは、

前段からの差動信号を反転入力端子、非反転入力端子に入力し、それに応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記差動増幅回路の前記反転入力端子と非反転出力端子との間に接続される第3の帰還抵抗部と、

前記差動増幅回路の前記非反転入力端子と反転出力端子との間に接続される第4の帰還抵抗部と、を備える

請求項1〜請求項6のいずれか1項に記載の信号配線システム。

【請求項8】

差動信号を出力する出力部と、

前記出力部からの前記差動信号を受信する受信部と、

前記出力部から前記受信部へ前記差動信号を伝達する信号配線部と、

前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、を有し、

前記出力部は、前記ジッタ抑制回路の前記抑制係数に応じた駆動能力で、前記差動信号を出力する

信号配線システム。

【請求項9】

前記出力部が出力する前記差動信号は、クロック信号であり、

前記信号配線部は、前記クロック信号を複数の前記受信部に分配するクロック分配配線である

請求項8に記載の信号配線システム。

【請求項10】

前記ジッタ抑制回路は、

前記信号配線部が伝達する前記差動信号を反転入力端子、非反転入力端子に入力し、それに応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記反転入力端子と非反転出力端子との間に接続される第1の帰還抵抗部と、

前記非反転入力端子と反転出力端子との間に接続される第2の帰還抵抗部と、を備え、

前記抑制係数は、前記第1、第2の帰還抵抗部の抵抗値に応じて決定される

請求項8または請求項9に記載の信号配線システム。

【請求項11】

前記差動増幅回路の反転入力端子、非反転入力端子が前記信号配線部と接続され、

前記差動増幅回路の反転出力端子、非反転出力端子が前記受信部と接続される

請求項10に記載の信号配線システム。

【請求項12】

前記差動増幅回路の反転入力端子、非反転入力端子が、前記信号配線部と第1、第2のノードで接続され、

前記第1、第2のノードが前記受信部と接続される

請求項10に記載の信号配線システム。

【請求項13】

前記第1、第2の帰還抵抗部が、抵抗素子もしくはトランスファーゲートである

請求項10〜請求項12のいずれか1項に記載の信号配線システム。

【請求項14】

前記出力部が、前記差動信号を生成する出力ドライバを有し、

前記出力ドライバは、

前段からの差動信号を反転入力端子、非反転入力端子に入力し、それに応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記差動増幅回路の前記反転入力端子と非反転出力端子との間に接続される第3の帰還抵抗部と、

前記差動増幅回路の前記非反転入力端子と反転出力端子との間に接続される第4の帰還抵抗部と、を備える

請求項8〜請求項13のいずれか1項に記載の信号配線システム。

【請求項15】

差動入力信号を反転入力端子、非反転入力端子に入力し、前記差動入力信号に応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記差動増幅回路の前記反転入力端子と非反転出力端子との間に接続される第1の帰還抵抗部と、

前記差動増幅回路の前記非反転入力端子と反転出力端子との間に接続される第2の帰還抵抗部と、を有し、

前記第1、第2の帰還抵抗部が、前記差動増幅回路の前記差動入力信号に対する前記出力信号のDCゲインが5〜15dB以下となる抵抗値を有する

ジッタ抑制回路。

【請求項16】

前記第1、第2の帰還抵抗部が、抵抗素子もしくはトランスファーゲートである

請求項15に記載のジッタ抑制回路。

【請求項1】

差動信号を出力する出力部と、

前記出力部からの前記差動信号を受信する受信部と、

前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、

前記出力部から前記受信部へ前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する

信号配線システム。

【請求項2】

前記出力部が出力する前記差動信号は、クロック信号であり、

前記信号配線部は、前記クロック信号を複数の前記受信部に分配するクロック分配配線である

請求項1に記載の信号配線システム。

【請求項3】

前記ジッタ抑制回路は、

前記信号配線部が伝達する前記差動信号を反転入力端子、非反転入力端子に入力し、それに応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記反転入力端子と非反転出力端子との間に接続される第1の帰還抵抗部と、

前記非反転入力端子と反転出力端子との間に接続される第2の帰還抵抗部と、を備え、

前記抑制係数は、前記第1、第2の帰還抵抗部の抵抗値に応じて決定される

請求項1または請求項2に記載の信号配線システム。

【請求項4】

前記差動増幅回路の反転入力端子、非反転入力端子が前記信号配線部と接続され、

前記差動増幅回路の反転出力端子、非反転出力端子が前記受信部と接続される

請求項3に記載の信号配線システム。

【請求項5】

前記差動増幅回路の反転入力端子、非反転入力端子が、前記信号配線部と第1、第2のノードで接続され、

前記第1、第2のノードが前記受信部と接続される

請求項3に記載の信号配線システム。

【請求項6】

前記第1、第2の帰還抵抗部が、抵抗素子もしくはトランスファーゲートである

請求項3〜請求項5のいずれか1項に記載の信号配線システム。

【請求項7】

前記出力部が、前記差動信号を生成する出力ドライバを有し、

前記出力ドライバは、

前段からの差動信号を反転入力端子、非反転入力端子に入力し、それに応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記差動増幅回路の前記反転入力端子と非反転出力端子との間に接続される第3の帰還抵抗部と、

前記差動増幅回路の前記非反転入力端子と反転出力端子との間に接続される第4の帰還抵抗部と、を備える

請求項1〜請求項6のいずれか1項に記載の信号配線システム。

【請求項8】

差動信号を出力する出力部と、

前記出力部からの前記差動信号を受信する受信部と、

前記出力部から前記受信部へ前記差動信号を伝達する信号配線部と、

前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、を有し、

前記出力部は、前記ジッタ抑制回路の前記抑制係数に応じた駆動能力で、前記差動信号を出力する

信号配線システム。

【請求項9】

前記出力部が出力する前記差動信号は、クロック信号であり、

前記信号配線部は、前記クロック信号を複数の前記受信部に分配するクロック分配配線である

請求項8に記載の信号配線システム。

【請求項10】

前記ジッタ抑制回路は、

前記信号配線部が伝達する前記差動信号を反転入力端子、非反転入力端子に入力し、それに応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記反転入力端子と非反転出力端子との間に接続される第1の帰還抵抗部と、

前記非反転入力端子と反転出力端子との間に接続される第2の帰還抵抗部と、を備え、

前記抑制係数は、前記第1、第2の帰還抵抗部の抵抗値に応じて決定される

請求項8または請求項9に記載の信号配線システム。

【請求項11】

前記差動増幅回路の反転入力端子、非反転入力端子が前記信号配線部と接続され、

前記差動増幅回路の反転出力端子、非反転出力端子が前記受信部と接続される

請求項10に記載の信号配線システム。

【請求項12】

前記差動増幅回路の反転入力端子、非反転入力端子が、前記信号配線部と第1、第2のノードで接続され、

前記第1、第2のノードが前記受信部と接続される

請求項10に記載の信号配線システム。

【請求項13】

前記第1、第2の帰還抵抗部が、抵抗素子もしくはトランスファーゲートである

請求項10〜請求項12のいずれか1項に記載の信号配線システム。

【請求項14】

前記出力部が、前記差動信号を生成する出力ドライバを有し、

前記出力ドライバは、

前段からの差動信号を反転入力端子、非反転入力端子に入力し、それに応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記差動増幅回路の前記反転入力端子と非反転出力端子との間に接続される第3の帰還抵抗部と、

前記差動増幅回路の前記非反転入力端子と反転出力端子との間に接続される第4の帰還抵抗部と、を備える

請求項8〜請求項13のいずれか1項に記載の信号配線システム。

【請求項15】

差動入力信号を反転入力端子、非反転入力端子に入力し、前記差動入力信号に応じた出力信号を反転出力端子、非反転出力端子に出力する差動増幅回路と、

前記差動増幅回路の前記反転入力端子と非反転出力端子との間に接続される第1の帰還抵抗部と、

前記差動増幅回路の前記非反転入力端子と反転出力端子との間に接続される第2の帰還抵抗部と、を有し、

前記第1、第2の帰還抵抗部が、前記差動増幅回路の前記差動入力信号に対する前記出力信号のDCゲインが5〜15dB以下となる抵抗値を有する

ジッタ抑制回路。

【請求項16】

前記第1、第2の帰還抵抗部が、抵抗素子もしくはトランスファーゲートである

請求項15に記載のジッタ抑制回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2012−182709(P2012−182709A)

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願番号】特願2011−44895(P2011−44895)

【出願日】平成23年3月2日(2011.3.2)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願日】平成23年3月2日(2011.3.2)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]