信頼性向上のためのケイ化銅パッシベーション

【課題】その表面をケイ化銅に転化することにより、銅相互接続構造の露出銅表面を直接不動態化するための方法を提供すること。

【解決手段】その後の誘電体フィルムの形成とともに原位置に実行されるシラン・パッシベーション・プロセスは、Cu相互接続構造の露出したCu表面をケイ化銅に転化する。ケイ化銅は、Cu拡散およびエレクトロマイグレーションを抑制し、後続導体材料との接触が行われる領域内でバリア材として機能する。銅相互接続構造の銅表面全体をケイ化する場合もあれば、銅表面の一部分を露出するように上に重なる誘電体に開口部を形成した後で表面の局部部分をケイ化する場合もある。

【解決手段】その後の誘電体フィルムの形成とともに原位置に実行されるシラン・パッシベーション・プロセスは、Cu相互接続構造の露出したCu表面をケイ化銅に転化する。ケイ化銅は、Cu拡散およびエレクトロマイグレーションを抑制し、後続導体材料との接触が行われる領域内でバリア材として機能する。銅相互接続構造の銅表面全体をケイ化する場合もあれば、銅表面の一部分を露出するように上に重なる誘電体に開口部を形成した後で表面の局部部分をケイ化する場合もある。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に半導体集積回路およびこれを形成するための方法に関する。より具体的には、本発明は、半導体回路などの内部における銅拡散の抑制に関する。

【背景技術】

【0002】

銅相互接続フィーチャの使用は、半導体集積回路デバイスなどではますます一般的になっている。バイアおよび相互接続リード線(ワイヤとしても知られる)などの銅相互接続フィーチャは、一般に、食刻装飾処理方法を使用して形成される。相互接続材料として銅を使用することはデバイス速度の増加に備えるもので、銅相互接続フィーチャは、アルミニウムおよびその合金などの従来使用していた材料に比べ、低いライン抵抗を含む。しかし、銅は、低温でも金属および誘電体内での拡散速度が非常に高い。銅拡散の結果、漏れおよび信頼性障害に至る可能性がある。このような銅拡散および障害を防止するための手法の1つは、食刻装飾銅相互接続構造が従来通り形成されるバイア、トレンチ、その他の開口部内にタンタルおよび窒化タンタルなどのバリア材を導入することを含む。このバリア材は、開口部内の銅をカプセル化する。しかし、研磨操作を行って構造を平坦化し、誘電体内に食刻装飾銅相互接続フィーチャを形成した後、上部研磨銅表面が露出する。この露出銅表面がカプセル化またはその他の方法で覆われていない場合、露出銅表面からの銅は銅相互接続構造上に形成した導体および/または誘電体材料内またはこれを通って拡散する可能性がある。

【0003】

銅表面を覆い、銅拡散を防止するための従来の技法の1つは、銅構造の上に後続誘電体フィルムをその後付着する前に、構造全体(銅表面上を含む)の上に窒化ケイ素または炭化ケイ素層を形成することである。その場合、窒化ケイ素または炭化ケイ素層は必然的に、上にある誘電体スタックの一部を形成する。この多層誘電体スタックは表面上、窒化ケイ素または炭化ケイ素層を形成するために追加の処理操作を必要とする。その上、銅拡散または銅のエレクトロマイグレーションは、炭化ケイ素/銅または窒化ケイ素/銅の境界面に沿って発生し、デバイスの信頼性の低下に至る可能性がある。

【発明の概要】

【発明が解決しようとする課題】

【0004】

したがって、当技術分野では、銅/誘電体の境界面に沿った銅のエレクトロマイグレーションおよび上に重なる誘電体および導体材料内およびこれを通る銅拡散を防止するための方法および構造が必要になっている。

【課題を解決するための手段】

【0005】

本発明は、その表面をケイ化銅に転化することにより、銅相互接続構造の露出銅表面を直接不動態化するための方法を提供する。銅相互接続構造上に直接形成された薄いケイ化銅層は、銅拡散およびエレクトロマイグレーションを防止し、銅相互接続構造を他の導体フィーチャに結合するために形成された接点内のバリア層としても機能する。一実施形態では、銅相互接続構造の上に窒化ケイ素または炭化ケイ素など、上に重なる誘電体層も形成される原位置シーケンス中に、シランによって銅表面を不動態化することができる。この実施形態によれば、銅相互接続構造の上部表面全体上にケイ化銅が形成されるように、パッシベーションまたは銅のケイ化を実行することができる。

【0006】

他の例示的な実施形態では、本発明は、上部銅表面を供給し、その表面の上に誘電体層を形成し、誘電体層を貫通する開口部を形成し、それにより上部銅表面の一部分を露出し、次にそれをケイ化銅材料に転化することにより上部銅表面の露出部分を局部的に不動態化することに備えるものである。

【0007】

他の例示的な実施形態では、本発明は、基板の上に形成された銅相互接続構造を含み、上面の少なくとも一部分が銅相互接続構造の銅とシリコンとの錯化の結果として形成されたケイ化銅である上面を含む、半導体製品を提供する。

【0008】

本発明は、添付図面と関連して読んだときに以下の詳細な説明から最も良く理解される。一般的な慣行により、図面の様々な特徴は一定の縮尺ではないことを強調しておく。これに反して、明瞭にするため、様々な特徴の寸法は任意に拡大または縮小されている。図面および明細書全体を通じて、同様の番号は同様の要素を示す。図面には、以下の図が示されている。

【図面の簡単な説明】

【0009】

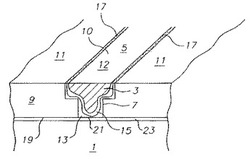

【図1】例示的な食刻装飾銅相互接続リード線の断面斜視図である。

【図2】露出銅表面をケイ化銅に転化した後の図1の構造を示す図である。

【図2A】図2の一部分の拡大断面図である。

【図3】不動態化したケイ化銅表面の上に形成された誘電体材料を示す断面図である。

【図4】図3に示した不動態化したケイ化銅表面の上に形成された導体構造を示す断面図である。

【図5】銅相互接続リード線の上に形成された例示的な導体構造を示す平面図である。

【図6】誘電体を貫通して形成され、銅表面の一部分を露出する開口部を示す断面図である。

【図7】パッシベーション・プロセスを使用して露出銅表面をケイ化した後の図6に示す構造を示す図である。

【図8】銅相互接続ワイヤの局部的にケイ化した領域を示す平面図である。

【図9】図7に示す開口部内に形成された導体食刻装飾構造を示す断面図である。

【図10】ある表面の上に形成された銅線の断面斜視図である。

【図11】露出銅表面上にケイ化銅をケイ化した後の図10の構造を示す図である。

【発明を実施するための形態】

【0010】

本発明は、シランなどのシリコン環境において銅相互接続構造の露出銅(Cu)表面を不動態化して、銅表面の露出部分をケイ化銅に転化することに備えるものである。このパッシベーション・プロセスは代わりにケイ化プロセスと呼ぶこともできる。ケイ化銅は、シリコンが元の銅表面に浸透し、その中の銅と錯化するにつれて形成される。ケイ化銅は、上に重なる導体材料および上に重なる誘電体材料など、上に重なる任意の材料に表面から銅が拡散するのを防止する働きをする。また、ケイ化銅は、ケイ化銅領域内の後続導体材料が銅相互接続構造に接触する領域内で金属間バリア層としても機能する。最初は露出していた銅表面から形成されるケイ化銅は、その銅表面と、炭化ケイ素、窒化ケイ素、様々な低k誘電体材料など上に重なる誘電体材料との間に形成される境界面に沿った銅のエレクトロマイグレーションも防止する。このような炭化ケイ素または窒化ケイ素材料は、一般に、食刻装飾処理技術を使用して形成される銅相互接続構造の上に形成される。その上、ケイ化銅は、ヒロック形成を抑制し、銅相互接続構造のケイ化銅表面に接触するように形成されたフィルムへの付着力を改善する。シランなどのシリコン含有化学物質に対して銅表面を露出することにより実行される銅表面のパッシベーションは、銅相互接続構造の上に窒化ケイ素、炭化ケイ素、その他の誘電体を形成するために使用するプロセス操作によって、原位置に有利に実行することができる。

【0011】

本発明は、銅表面の露出部分の局部的パッシベーションにも備えるものである。この実施形態によれば、銅表面の上に誘電体が形成され、誘電体を通って延び、銅表面の一部分を露出するように開口部が形成される。次に、シリコン化学物質を使用するパッシベーション・プロセスを実行して、銅表面の露出部分をケイ化銅に転化する。バリア層として機能するケイ化銅領域に接触する後続導体材料を開口部内に形成してもよい。また、任意選択で、個別に形成した追加のバリア層を後続導体材料の一部として使用してもよい。この実施形態では、ケイ化銅領域は、金属間拡散バリアとして作用し、高いアスペクト比を有する開口部内にバリア層を形成することに関連する問題も克服する。

【0012】

銅相互接続技術では通常、食刻装飾処理技術を使用して、バイア、相互接続線などの銅相互接続構造を形成するが、フォトリソグラフィ技法とともにエッチング・プロセスを使用して表面の上に形成された銅フィルムにパターン形成するための技法が現在開発されている。その場合、パターン形成した銅は、当技術分野で使用する他のパターン形成した相互接続材料と同様の露出上部表面および露出側壁を含む。本発明は、パターン形成した銅構造のすべての露出表面を不動態化して、側壁を含むすべての表面上にケイ化銅を形成し、それにより、パターン形成した銅構造の上にその後形成される誘電体層の境界面に沿った銅のマイグレーションおよび銅拡散を防止するように銅相互接続構造を不動態化することに備えるものである。第1の非局部的パッシベーション実施形態のように、このパッシベーション/ケイ化は、上に重なる誘電体フィルムをその後付着することにより原位置に有利に実行することができる。

【0013】

図1は、食刻装飾技法を使用して形成される銅相互接続構造の断面斜視図である。図1の図示の実施形態では、例示的な銅相互接続構造は銅相互接続リード線10であり、これは基板1の上で縦方向に移動し、横方向に分離されたフィーチャ間の接触を可能にすることができる。銅相互接続リード線10は例示のみを目的とするものであり、他の例示的な実施形態では、本発明により不動態化/ケイ化される銅構造は、食刻装飾処理技術を使用して形成されるバイアその他の導体構造にすることができる。さらに他の例示的な実施形態では、図10および図11に示すように、フォトリソグラフィでパターン形成しエッチングを施した銅リード線を使用することもできる。

【0014】

さらに図1を参照すると、銅相互接続リード線10は、基板1の上に形成され、より具体的には、誘電体材料9内に形成された開口部7内に形成される。基板1は、シリコン、ガリウムヒ素、その他の適当な材料から形成されるような半導体ウェハにすることができる。図示の実施形態に示す基板1は、このようなウェハの上に形成された誘電体またはその他の層も表すことができる。誘電体材料9は、SiOC−Hなどのシリコンベースの誘電体である場合もあれば、スピンオン芳香族炭素である場合もあれば、有機ケイ酸塩ガラス(OSG)である場合もあれば、ポリイミドまたはPSGあるいは銅相互接続フィーチャとともに使用する他の様々な適当な誘電体のいずれかである場合もある。

【0015】

好ましい実施形態では、誘電体材料9は、低k誘電体材料、すなわち、4.0未満の誘電率を有する材料になる。例示的な図示の実施形態では、開口部7は、誘電体材料9内に形成された二重食刻装飾開口部である。この二重食刻装飾開口部は、従来の技法を使用して形成することができ、例示のみを目的とするものである。他の例示的な実施形態では、単一食刻装飾構造を使用することができ、様々な形状を含むことができる。誘電体材料9は単体層として示されているが、誘電体材料9は複数の誘電体層から構成することもできる。たとえば、1つの個別誘電体層は、二重食刻装飾開口部7の各段に対応する場合もある。他の実施形態では、誘電体材料9は、例示的な二重食刻装飾(2段階)開口部7の形成を支援可能な少なくとも1つのハード・マスク層を含む誘電体の多層スタックにすることができる。開口部7は、誘電体材料9の底部19まで延びて、基板1の上に形成された下にある層23の一部分21に接触する。これは、バイアと同様に銅相互接続リード線10が下にある構成要素に電気的に接触する実施形態の例証となるものである。これは例示のみを目的とするものであり、他の例示的な実施形態では、開口部7は、他の形状を取る場合もあれば、底部19まで下に延びていない場合もあり、むしろ誘電体材料9内に完全に掘削される場合もある。図示の実施形態によれば、下にある層23は、銅相互接続リード線10の機能および構造に応じて、ハード・マスク、バリア層、導体材料、誘電体材料、または様々な材料のいずれかにすることができる。他の例示的な実施形態によれば、下にある層23が存在しない場合もある。

【0016】

図示の実施形態では、銅相互接続リード線10は、塊の銅部分3と、2つのバリア層13および15から形成される。バリア層と、バリア層の上の塊の銅材を形成するために、従来の方法を使用することができる。このバリア層は、銅相互接続リード線10の塊の銅部分3を横方向と下方に効果的にカプセル化する。例示的な実施形態では、下部バリア層13はタンタルTaから形成することができ、上部バリア層15は窒化タンタルTaNから形成することができる。これらのフィルムは例示のみを目的とするものであり、他の例示的な実施形態では、チタン、窒化チタン、タングステン、チタンタングステンから形成される他のバリア層を使用することができる。他の例示的な実施形態によれば、様々なケイ化物をバリア層として使用することができる。様々な例示的な実施形態では、単一のバリア層のみを使用する。さらに他の例示的な実施形態によれば、バリア層は含まれない。図1の例示では、研磨または他の適当な食刻装飾技法を使用してこの構造を実質的に平坦化し、開口部7内に銅相互接続リード線10を形成した後の構造を示している。銅相互接続リード線10は、本質的に平面であり、誘電体材料9の上面11と共面にある上部表面12を含む。上部表面12は、上部銅表面5と、バリア層から形成されるエッジ17とを含む。任意選択の単数または複数のバリア層の後に図1に示す構造を形成し、次いで塊の銅材3を開口部7内に形成するために、当技術分野で使用可能な様々な研磨その他の技法を使用することができる。

【0017】

次に、図1に示す構造を不動態化して、図2に示す構造を形成する。この例示的な実施形態によれば、本発明のパッシベーション/ケイ化プロセスを使用して、上部銅表面5の全体を露出し、実質的に上部銅表面5のすべてをケイ化銅に転化する。このパッシベーション/ケイ化プロセスでは、300〜400℃の範囲内の温度でシランを有利に使用し、300〜1000sccmの範囲にすることができる流量と、1〜10トルの範囲内にすることができる圧力と、13.56MHzで50〜1000ワットの範囲内のRFプラズマ出力とを含む。例示的な一実施形態によれば、シラン流量は約300sccmにすることができ、プロセスは、5トルの圧力と、350℃の温度と、500〜1000ワットの範囲のRF出力を含むことができる。他の例示的な実施形態では、他のSiソースを使用する気体化学物質を使用することができる。また、上記の値は例示のみであり、他の例示的な実施形態によれば、プラズマ化学物質からのシリコンを露出したCu表面に浸透させ、その中のCuと反応させることにより上部銅表面5の露出部分をケイ化銅に転化するために、プロセス・パラメータの各種組合せを使用することができる。様々な相のケイ化銅を形成することができる。当業者であれば分かるように、ケイ化度は時間とともに増加する可能性がある。一実施形態では、このプロセスは5〜20分の範囲の時間の間、実行することができるが、必要なケイ化度に応じて他の処理時間も使用することができる。

【0018】

図2は、実質的に露出した上部銅表面5の全体(図1に示す)をケイ化銅表面25に転化した後の図1に示す構造を示している。他の実施形態では、上部銅表面5の露出領域の少なくとも一部分をケイ化銅表面25に転化する。元のCu表面5と比較すると、ケイ化銅表面25は表面積が増加したより粗い表面であり、本質的に望ましくない酸化銅を一切含まない。表面積の増加により、ケイ化銅表面25の上に形成され、それに接触するフィルムへの付着力が改善される。また、ケイ化銅表面25は、銅相互接続リード線10内のヒロック形成を抑制するという利点も含む。

【0019】

図2Aは、ケイ化銅に転化された最初は銅の表面の拡大断面図である。図2Aは、図1に示す元の上部銅表面5がケイ化銅表面25に転化され、それが塊の銅材3を浸食するケイ化銅29を含むことを示している。ケイ化銅29は、シリコンが元の上部表面に浸透し、その中の銅と錯化してケイ化銅を形成する、銅相互接続リード線10の転化部分を表している。シランまたはその他のシリコン気体化学物質からのシリコンが元の上部銅表面5に浸透してCuと錯化し、それにより、その表面の上部部分をケイ化銅29に転化することにより、ケイ化銅が形成されるように、処理パラメータが選択される。ケイ化銅29は、20〜200オングストロームの範囲の深さ31を含むことができるが、別法としてその他の厚さも使用することができる。当業者であれば、プロセス温度とプロセス持続時間を変化させて、ケイ化銅29の厚さ31を制御できることが分かるだろう。厚さ31は、銅相互接続構造からの銅拡散を防止するのに十分な厚さで、相互接続リード線10内の銅のシート抵抗の増加を最小限にするのに十分な薄さになるよう、所望のケイ化度とともに選択することができる。図示の実施形態では、ケイ化銅表面25は、粗く不規則な表面として示されている。このような粗く不規則な表面は、その上に形成されたフィルムへの付着力を改善するような追加の表面積をもたらす。

【0020】

350℃〜400℃の温度範囲内で持続時間が短い任意選択のアニールを実行して、銅相互接続リード線のシート抵抗を低減し、ケイ化銅表面25と、ケイ化銅表面25に接触するように形成可能な後続導体材料との接触抵抗を低減することができる。この任意選択のアニールは、数秒台または数分台のアニール時間を含むことができる。持続時間が短いアニールによって最初に形成されたケイ化銅の相が変化するため、またはシリコンの超過により追加のケイ化銅形成が発生するため、あるいはその両方のために、シート/接触抵抗の低減が達成されると考えられている。このアニール・プロセスは、窒素その他の不活性種を含むことができる。他の例示的な実施形態によれば、このアニーリング・プロセスを使用しない場合もある。

【0021】

図2は、ケイ化銅表面25を形成した後の構造を示している。例示的な一実施形態によれば、本発明の利点の1つはこの構造の上に後続フィルムをその後形成することとともに、本発明のケイ化/パッシベーション・プロセスが原位置に実行可能であることなので、この構造は中間構造になる可能性がある。この後続フィルムは、上にある誘電体スタックを形成するために使用する様々な誘電体フィルムのいずれかにすることができ、例示的な一実施形態によれば、その表面の上に直接形成された第1の層は、ケイ化/パッシベーション・プロセスによって原位置に形成される窒化ケイ素または炭化ケイ素のフィルムにすることができる。

【0022】

図3は、図2に一般的に示す下部構造の上に形成された上部誘電体35を示す断面図であるが、明瞭にするため、下にある層23とバリア層13および15は除去されている。したがって、図示されていないが、これらのフィーチャは図示の実施形態などの様々な実施形態に含めることができることを理解されたい。上部誘電体35は、上記のようにケイ化銅29を含むケイ化銅表面25および上面11の上に形成される。上部誘電体35は、単一の誘電体フィルムである場合もあれば、複数誘電体のスタックを表す場合もあり、その誘電体の一部または全部はケイ化/パッシベーション・プロセスによって原位置に形成することができる。低k誘電体材料およびSiベースの材料を使用することができ、この誘電体材料は図1の誘電体材料9に関連して前述した通りのものにすることができる。例示的な一実施形態では、上部誘電体35は、複数の個別層からなる複合物またはスタックにすることができる。上部誘電体35は、点線で分離した2つの層35Aおよび35Bから形成することができる。この例示的な実施形態によれば、誘電体層35Aは窒化ケイ素または炭化ケイ素にすることができ、誘電体層35Bは低k誘電体材料にすることができる。これは例示のみを目的とするものであり、他の例示的な実施形態では、他の数の様々な誘電体フィルムを使用して、上部誘電体35を形成することができる。上部誘電体35には、1つまたは複数のハードマスク・フィルムを含めることができる。本発明の1つの態様は、特にケイ化したケイ化銅表面25と接触している誘電体層が窒化ケイ素または炭化ケイ素であるときに、ケイ化したケイ化銅表面25と上部誘電体35との付着力が改善されることである。

【0023】

図4は、上部誘電体35に形成された開口部41の底部から銅相互接続リード線10のケイ化銅表面25と接触するように例示的な導体構造39を形成した後の図3の構造を示している。開口部41は上部誘電体層35の底部まで延び、ケイ化銅表面25のセクション51を露出する。例示的な実施形態では、開口部41は二重食刻装飾開口部であるが、他の実施形態では他の開口部を使用して銅相互接続リード線10のケイ化銅表面25との接触に備えることができる。開口部41は、ケイ化銅表面25の一部のみを露出する。ケイ化銅表面25の他の部分は、上部誘電体35によって覆われたままになる。(これについては図5により明瞭に示されている。)導体構造39は、任意選択のバリア層43および45と、塊の導体材料47とを含む。任意選択のバリア層43および45は、銅相互接続リード線10に関連して述べたバリア層13および15と同様のものであり、塊の導体材料47は銅またはその他の適当な導体材料にすることができる。本発明の1つの利点は、例示的な一実施例によれば、ケイ化銅表面25が銅相互接続リード線10と導体構造39との間の拡散バリアとして機能するので任意選択のバリア層43および45が不要になることである。図示の例示的な実施形態によれば、導体構造39は、上部誘電体35の上面37と実質的に共面の平面化した上面49を含む食刻装飾構造である。他の例示的な実施形態では、他の様々な食刻装飾導体構造および非食刻装飾導体構造を使用して、ケイ化銅表面25に接触してもよい。

【0024】

図5は、図4に示すように銅相互接続リード線10の上に形成され、それと接触する上部導体構造39を示す平面図である。この例示的な実施形態では、導体構造39は、開口部(図4に示す開口部41)内に形成され、銅相互接続リード線10のケイ化銅表面25のセクション51に接触するバイアである。ケイ化銅表面25の他の部分は上部誘電体35によって覆われている。任意選択のバリア層43および45は図5に示されていない。

【0025】

図示の例示的な実施形態によれば、銅相互接続リード線10は、デバイスを通って横方向に延びる長いトレンチ内に延びる相互接続ワイヤであり、導体構造39はバイアであるが、他の例示的な実施形態により他の配置を使用することもできる。たとえば、上部食刻装飾相互接続構造がそれが形成されている誘電体層の底部まで延びている例示的な実施形態によれば、ほぼ直交関係で互いに横切る2つの相互接続リード線間で接触を行うことができる。その上、他の例示的な実施形態によれば、上部相互接続構造は非食刻装飾構造でもよい。

【0026】

本発明のもう1つの実施形態は、露出銅表面の局部ケイ化である。図6は、誘電体材料9内に形成された例示的な銅相互接続リード線10の断面図である。第2の誘電体層61は、上部銅表面5と、誘電体材料9の上面11の上に形成される。第2の誘電体61は、前述の通り、様々な材料のいずれかまたは複数材料の層からなる様々なスタックのいずれかにすることができる。たとえば、第2の誘電体61は、Siベースの低k誘電体層を含むかまたはこのような誘電体層から排他的に形成することができ、少なくとも1つのハード・マスク層を含むことができる。開口部65は、第2の誘電体61を通って延び、上部銅表面5のセクション67を露出する。例示的な開口部65は二重食刻装飾開口部として示されているが、他の例示的な実施形態では他の様々な開口部を形成することができる。その場合、上記のパッシベーション/ケイ化プロセスにより、銅相互接続リード線10の上部銅表面5の露出セクション67を不動態化することができる。図6に示す構造に対してパッシベーション/ケイ化プロセスを実行して、図7に示す構造を形成する。

【0027】

図7は、銅相互接続リード線10の最初は銅の上部表面の露出セクション67に形成された局部ケイ化銅表面25を示している。上部銅表面5の他の非露出部分については、このような不動態化が行われない。シリコンが元の銅上部表面に浸透し、銅相互接続リード線10の銅と錯化するにつれて、Cu相互接続リード線10を浸食し、上部銅表面5の露出セクション67内の銅をケイ化銅29に転化するように、ケイ化銅29を形成する。この実施形態では、局部的ケイ化銅29は、銅相互接続リード線10と、その後形成され、銅相互接続リード線10と接触する導体構造との間のバリア層として機能することができる。これにより、開口部65内に連続バリア層フィルムを形成して銅相互接続リード線10と接触しようと試みるという欠点が克服される。開口部65が高いアスペクト比を有する例示的な実施形態によれば、従来の方法を使用して形成されるバリア層フィルムは、不連続になり、開口部内に空の領域を発生する傾向がある。

【0028】

図8は、図7に示す構造の平面図である。図8は、銅相互接続リード線10の上に位置合せされたバイアを形成するために使用する、例示的な二重食刻装飾開口部65を示している。局部ケイ化銅表面25は、ケイ化銅に転化された銅相互接続リード線10の元の上部銅表面5の露出部分であるセクション67内のみに実質的に形成される。上部銅表面5のうち、露出されず、局部的にケイ化されない他の部分は、覆いのない銅として存続する。このようにして、図7に断面で示す第2の誘電体層61は、上部銅表面5を覆い、それを通って元の上部銅表面5のセクション67を露出する開口部65を含み、その上部銅表面5はセクション67内のみでケイ化銅表面25に転化されている。したがって、開口部65は、上部銅表面のうち、ケイ化銅に転化される局部的部分を規定する。

【0029】

図9は、セクション67で局部的ケイ化銅表面25に接触するように開口部65内に形成される上部導体構造71を示している。上部導体構造71は塊の導体材料77を含み、従来の方法を使用して形成することができる。塊の導体材料77は、銅、アルミニウム、またはその他の適当な導体材料にすることができる。図示の実施形態では、上部導体構造71はバイアであり、上面81が第2の誘電体61の上部表面69と本質的に共面になるように食刻装飾処理を使用して形成することができる。他の例示的な実施形態によれば、上部導体構造71は、ケイ化銅表面25と接触する、相互接続リード線などの他の食刻装飾構造のいずれかにすることができる。さらに他の例示的な実施形態によれば、非食刻装飾構造は、ケイ化銅表面25に転化される元の上部銅表面5の局部部分(セクション67)を規定する開口部65を充填するように形成することができる。したがって、本発明の1つの利点は、開口部内に連続バリア層フィルムを形成することを困難にするような高いアスペクト比を含む可能性のある開口部65などの開口部内にフィルムを付着する必要なしに、銅相互接続リード線10と上部導体構造71との間にバリア層、すなわち、ケイ化銅29を形成することである。他の例示的な実施形態では、ケイ化銅29とともに追加のバリア層を使用してもよい。

【0030】

図10は、層101の表面103の上に形成された銅相互接続ワイヤ105の斜視断面図である。層101は、基板またはその他の半導体構造の上に形成された誘電体またはその他の層にすることができる。銅相互接続ワイヤ105は、フォトリソグラフィならびに当技術分野で現在開発中のパターン形成およびエッチング手順などの様々な技法を使用して形成することができる。銅にパターン形成およびエッチングを施すための改良された方法は引き続き当技術分野で開発されることが検討されている。パターン形成した銅相互接続ワイヤ105は、それぞれが銅で構成される上面107と側壁109とを含む。

【0031】

上記のように、本発明のケイ化/パッシベーション・プロセスを使用して、銅相互接続ワイヤ105の露出表面(上面107および側壁109)を不動態化することができる。パッシベーション・プロセスの結果として、銅相互接続ワイヤ105の側壁および上面がケイ化銅に転化される。

【0032】

図11は、上記の実施形態に示し記載したように、その時点でケイ化銅を含むケイ化銅表面である転化側壁119と転化上面117を示している。図11に示すケイ化構造は、ケイ化銅表面119および117がこのような外方拡散を抑制するので、銅相互接続ワイヤ105からの銅拡散が低減されるという利点を享受するものである。ケイ化銅表面117および119は、銅相互接続ワイヤ105と誘電体またはその上に形成された他の材料との間に形成された境界に沿った銅のエレクトロマイグレーションも抑制する。その後形成される材料、特に窒化ケイ素および炭化ケイ素の銅相互接続ワイヤ105に対する付着力は、このケイ化銅のために改善される。ヒロック形成は抑制される。任意選択でバリア層を含むことができる様々な導体材料は、ケイ化表面117および119に形成されたケイ化銅領域と接触するように形成することができる。銅相互接続ワイヤ105のケイ化銅表面がバリア材として作用するので、他の実施形態では追加のバリア層を使用しない。

【0033】

上記の説明は単に本発明の原理を例示するものである。したがって、当業者であれば、本明細書に明示的に記載または図示していないが、本発明の原理を実施し、その範囲および精神の範囲内に含まれる様々な配置を考案できることが分かるだろう。また、本明細書に列挙するすべての例および条件言語は主に、教育学的目的専用とし、本発明の原理および当技術分野の促進に対して本発明者らが寄与する概念を理解するのを助けることを特に意図したものであり、このように具体的に列挙した例および条件に制限を加えないものであると解釈すべきである。さらに、本発明の原理、態様、実施形態、ならびにその特定の例を本明細書で列挙するすべての記載は、構造および機能の両面でそれと同等のものを包含するためのものである。その上、このような同等物は、現在既知の同等物と、将来開発される同等物、すなわち、開発される要素のうち、構造にかかわらず同じ機能を実行するものすべてを含むものとする。したがって、本発明の範囲は、図示し、本明細書に記載した例示的な実施形態に限定されないものとする。むしろ、本発明の範囲および精神は特許請求の範囲によって実施されるものである。

【技術分野】

【0001】

本発明は、一般に半導体集積回路およびこれを形成するための方法に関する。より具体的には、本発明は、半導体回路などの内部における銅拡散の抑制に関する。

【背景技術】

【0002】

銅相互接続フィーチャの使用は、半導体集積回路デバイスなどではますます一般的になっている。バイアおよび相互接続リード線(ワイヤとしても知られる)などの銅相互接続フィーチャは、一般に、食刻装飾処理方法を使用して形成される。相互接続材料として銅を使用することはデバイス速度の増加に備えるもので、銅相互接続フィーチャは、アルミニウムおよびその合金などの従来使用していた材料に比べ、低いライン抵抗を含む。しかし、銅は、低温でも金属および誘電体内での拡散速度が非常に高い。銅拡散の結果、漏れおよび信頼性障害に至る可能性がある。このような銅拡散および障害を防止するための手法の1つは、食刻装飾銅相互接続構造が従来通り形成されるバイア、トレンチ、その他の開口部内にタンタルおよび窒化タンタルなどのバリア材を導入することを含む。このバリア材は、開口部内の銅をカプセル化する。しかし、研磨操作を行って構造を平坦化し、誘電体内に食刻装飾銅相互接続フィーチャを形成した後、上部研磨銅表面が露出する。この露出銅表面がカプセル化またはその他の方法で覆われていない場合、露出銅表面からの銅は銅相互接続構造上に形成した導体および/または誘電体材料内またはこれを通って拡散する可能性がある。

【0003】

銅表面を覆い、銅拡散を防止するための従来の技法の1つは、銅構造の上に後続誘電体フィルムをその後付着する前に、構造全体(銅表面上を含む)の上に窒化ケイ素または炭化ケイ素層を形成することである。その場合、窒化ケイ素または炭化ケイ素層は必然的に、上にある誘電体スタックの一部を形成する。この多層誘電体スタックは表面上、窒化ケイ素または炭化ケイ素層を形成するために追加の処理操作を必要とする。その上、銅拡散または銅のエレクトロマイグレーションは、炭化ケイ素/銅または窒化ケイ素/銅の境界面に沿って発生し、デバイスの信頼性の低下に至る可能性がある。

【発明の概要】

【発明が解決しようとする課題】

【0004】

したがって、当技術分野では、銅/誘電体の境界面に沿った銅のエレクトロマイグレーションおよび上に重なる誘電体および導体材料内およびこれを通る銅拡散を防止するための方法および構造が必要になっている。

【課題を解決するための手段】

【0005】

本発明は、その表面をケイ化銅に転化することにより、銅相互接続構造の露出銅表面を直接不動態化するための方法を提供する。銅相互接続構造上に直接形成された薄いケイ化銅層は、銅拡散およびエレクトロマイグレーションを防止し、銅相互接続構造を他の導体フィーチャに結合するために形成された接点内のバリア層としても機能する。一実施形態では、銅相互接続構造の上に窒化ケイ素または炭化ケイ素など、上に重なる誘電体層も形成される原位置シーケンス中に、シランによって銅表面を不動態化することができる。この実施形態によれば、銅相互接続構造の上部表面全体上にケイ化銅が形成されるように、パッシベーションまたは銅のケイ化を実行することができる。

【0006】

他の例示的な実施形態では、本発明は、上部銅表面を供給し、その表面の上に誘電体層を形成し、誘電体層を貫通する開口部を形成し、それにより上部銅表面の一部分を露出し、次にそれをケイ化銅材料に転化することにより上部銅表面の露出部分を局部的に不動態化することに備えるものである。

【0007】

他の例示的な実施形態では、本発明は、基板の上に形成された銅相互接続構造を含み、上面の少なくとも一部分が銅相互接続構造の銅とシリコンとの錯化の結果として形成されたケイ化銅である上面を含む、半導体製品を提供する。

【0008】

本発明は、添付図面と関連して読んだときに以下の詳細な説明から最も良く理解される。一般的な慣行により、図面の様々な特徴は一定の縮尺ではないことを強調しておく。これに反して、明瞭にするため、様々な特徴の寸法は任意に拡大または縮小されている。図面および明細書全体を通じて、同様の番号は同様の要素を示す。図面には、以下の図が示されている。

【図面の簡単な説明】

【0009】

【図1】例示的な食刻装飾銅相互接続リード線の断面斜視図である。

【図2】露出銅表面をケイ化銅に転化した後の図1の構造を示す図である。

【図2A】図2の一部分の拡大断面図である。

【図3】不動態化したケイ化銅表面の上に形成された誘電体材料を示す断面図である。

【図4】図3に示した不動態化したケイ化銅表面の上に形成された導体構造を示す断面図である。

【図5】銅相互接続リード線の上に形成された例示的な導体構造を示す平面図である。

【図6】誘電体を貫通して形成され、銅表面の一部分を露出する開口部を示す断面図である。

【図7】パッシベーション・プロセスを使用して露出銅表面をケイ化した後の図6に示す構造を示す図である。

【図8】銅相互接続ワイヤの局部的にケイ化した領域を示す平面図である。

【図9】図7に示す開口部内に形成された導体食刻装飾構造を示す断面図である。

【図10】ある表面の上に形成された銅線の断面斜視図である。

【図11】露出銅表面上にケイ化銅をケイ化した後の図10の構造を示す図である。

【発明を実施するための形態】

【0010】

本発明は、シランなどのシリコン環境において銅相互接続構造の露出銅(Cu)表面を不動態化して、銅表面の露出部分をケイ化銅に転化することに備えるものである。このパッシベーション・プロセスは代わりにケイ化プロセスと呼ぶこともできる。ケイ化銅は、シリコンが元の銅表面に浸透し、その中の銅と錯化するにつれて形成される。ケイ化銅は、上に重なる導体材料および上に重なる誘電体材料など、上に重なる任意の材料に表面から銅が拡散するのを防止する働きをする。また、ケイ化銅は、ケイ化銅領域内の後続導体材料が銅相互接続構造に接触する領域内で金属間バリア層としても機能する。最初は露出していた銅表面から形成されるケイ化銅は、その銅表面と、炭化ケイ素、窒化ケイ素、様々な低k誘電体材料など上に重なる誘電体材料との間に形成される境界面に沿った銅のエレクトロマイグレーションも防止する。このような炭化ケイ素または窒化ケイ素材料は、一般に、食刻装飾処理技術を使用して形成される銅相互接続構造の上に形成される。その上、ケイ化銅は、ヒロック形成を抑制し、銅相互接続構造のケイ化銅表面に接触するように形成されたフィルムへの付着力を改善する。シランなどのシリコン含有化学物質に対して銅表面を露出することにより実行される銅表面のパッシベーションは、銅相互接続構造の上に窒化ケイ素、炭化ケイ素、その他の誘電体を形成するために使用するプロセス操作によって、原位置に有利に実行することができる。

【0011】

本発明は、銅表面の露出部分の局部的パッシベーションにも備えるものである。この実施形態によれば、銅表面の上に誘電体が形成され、誘電体を通って延び、銅表面の一部分を露出するように開口部が形成される。次に、シリコン化学物質を使用するパッシベーション・プロセスを実行して、銅表面の露出部分をケイ化銅に転化する。バリア層として機能するケイ化銅領域に接触する後続導体材料を開口部内に形成してもよい。また、任意選択で、個別に形成した追加のバリア層を後続導体材料の一部として使用してもよい。この実施形態では、ケイ化銅領域は、金属間拡散バリアとして作用し、高いアスペクト比を有する開口部内にバリア層を形成することに関連する問題も克服する。

【0012】

銅相互接続技術では通常、食刻装飾処理技術を使用して、バイア、相互接続線などの銅相互接続構造を形成するが、フォトリソグラフィ技法とともにエッチング・プロセスを使用して表面の上に形成された銅フィルムにパターン形成するための技法が現在開発されている。その場合、パターン形成した銅は、当技術分野で使用する他のパターン形成した相互接続材料と同様の露出上部表面および露出側壁を含む。本発明は、パターン形成した銅構造のすべての露出表面を不動態化して、側壁を含むすべての表面上にケイ化銅を形成し、それにより、パターン形成した銅構造の上にその後形成される誘電体層の境界面に沿った銅のマイグレーションおよび銅拡散を防止するように銅相互接続構造を不動態化することに備えるものである。第1の非局部的パッシベーション実施形態のように、このパッシベーション/ケイ化は、上に重なる誘電体フィルムをその後付着することにより原位置に有利に実行することができる。

【0013】

図1は、食刻装飾技法を使用して形成される銅相互接続構造の断面斜視図である。図1の図示の実施形態では、例示的な銅相互接続構造は銅相互接続リード線10であり、これは基板1の上で縦方向に移動し、横方向に分離されたフィーチャ間の接触を可能にすることができる。銅相互接続リード線10は例示のみを目的とするものであり、他の例示的な実施形態では、本発明により不動態化/ケイ化される銅構造は、食刻装飾処理技術を使用して形成されるバイアその他の導体構造にすることができる。さらに他の例示的な実施形態では、図10および図11に示すように、フォトリソグラフィでパターン形成しエッチングを施した銅リード線を使用することもできる。

【0014】

さらに図1を参照すると、銅相互接続リード線10は、基板1の上に形成され、より具体的には、誘電体材料9内に形成された開口部7内に形成される。基板1は、シリコン、ガリウムヒ素、その他の適当な材料から形成されるような半導体ウェハにすることができる。図示の実施形態に示す基板1は、このようなウェハの上に形成された誘電体またはその他の層も表すことができる。誘電体材料9は、SiOC−Hなどのシリコンベースの誘電体である場合もあれば、スピンオン芳香族炭素である場合もあれば、有機ケイ酸塩ガラス(OSG)である場合もあれば、ポリイミドまたはPSGあるいは銅相互接続フィーチャとともに使用する他の様々な適当な誘電体のいずれかである場合もある。

【0015】

好ましい実施形態では、誘電体材料9は、低k誘電体材料、すなわち、4.0未満の誘電率を有する材料になる。例示的な図示の実施形態では、開口部7は、誘電体材料9内に形成された二重食刻装飾開口部である。この二重食刻装飾開口部は、従来の技法を使用して形成することができ、例示のみを目的とするものである。他の例示的な実施形態では、単一食刻装飾構造を使用することができ、様々な形状を含むことができる。誘電体材料9は単体層として示されているが、誘電体材料9は複数の誘電体層から構成することもできる。たとえば、1つの個別誘電体層は、二重食刻装飾開口部7の各段に対応する場合もある。他の実施形態では、誘電体材料9は、例示的な二重食刻装飾(2段階)開口部7の形成を支援可能な少なくとも1つのハード・マスク層を含む誘電体の多層スタックにすることができる。開口部7は、誘電体材料9の底部19まで延びて、基板1の上に形成された下にある層23の一部分21に接触する。これは、バイアと同様に銅相互接続リード線10が下にある構成要素に電気的に接触する実施形態の例証となるものである。これは例示のみを目的とするものであり、他の例示的な実施形態では、開口部7は、他の形状を取る場合もあれば、底部19まで下に延びていない場合もあり、むしろ誘電体材料9内に完全に掘削される場合もある。図示の実施形態によれば、下にある層23は、銅相互接続リード線10の機能および構造に応じて、ハード・マスク、バリア層、導体材料、誘電体材料、または様々な材料のいずれかにすることができる。他の例示的な実施形態によれば、下にある層23が存在しない場合もある。

【0016】

図示の実施形態では、銅相互接続リード線10は、塊の銅部分3と、2つのバリア層13および15から形成される。バリア層と、バリア層の上の塊の銅材を形成するために、従来の方法を使用することができる。このバリア層は、銅相互接続リード線10の塊の銅部分3を横方向と下方に効果的にカプセル化する。例示的な実施形態では、下部バリア層13はタンタルTaから形成することができ、上部バリア層15は窒化タンタルTaNから形成することができる。これらのフィルムは例示のみを目的とするものであり、他の例示的な実施形態では、チタン、窒化チタン、タングステン、チタンタングステンから形成される他のバリア層を使用することができる。他の例示的な実施形態によれば、様々なケイ化物をバリア層として使用することができる。様々な例示的な実施形態では、単一のバリア層のみを使用する。さらに他の例示的な実施形態によれば、バリア層は含まれない。図1の例示では、研磨または他の適当な食刻装飾技法を使用してこの構造を実質的に平坦化し、開口部7内に銅相互接続リード線10を形成した後の構造を示している。銅相互接続リード線10は、本質的に平面であり、誘電体材料9の上面11と共面にある上部表面12を含む。上部表面12は、上部銅表面5と、バリア層から形成されるエッジ17とを含む。任意選択の単数または複数のバリア層の後に図1に示す構造を形成し、次いで塊の銅材3を開口部7内に形成するために、当技術分野で使用可能な様々な研磨その他の技法を使用することができる。

【0017】

次に、図1に示す構造を不動態化して、図2に示す構造を形成する。この例示的な実施形態によれば、本発明のパッシベーション/ケイ化プロセスを使用して、上部銅表面5の全体を露出し、実質的に上部銅表面5のすべてをケイ化銅に転化する。このパッシベーション/ケイ化プロセスでは、300〜400℃の範囲内の温度でシランを有利に使用し、300〜1000sccmの範囲にすることができる流量と、1〜10トルの範囲内にすることができる圧力と、13.56MHzで50〜1000ワットの範囲内のRFプラズマ出力とを含む。例示的な一実施形態によれば、シラン流量は約300sccmにすることができ、プロセスは、5トルの圧力と、350℃の温度と、500〜1000ワットの範囲のRF出力を含むことができる。他の例示的な実施形態では、他のSiソースを使用する気体化学物質を使用することができる。また、上記の値は例示のみであり、他の例示的な実施形態によれば、プラズマ化学物質からのシリコンを露出したCu表面に浸透させ、その中のCuと反応させることにより上部銅表面5の露出部分をケイ化銅に転化するために、プロセス・パラメータの各種組合せを使用することができる。様々な相のケイ化銅を形成することができる。当業者であれば分かるように、ケイ化度は時間とともに増加する可能性がある。一実施形態では、このプロセスは5〜20分の範囲の時間の間、実行することができるが、必要なケイ化度に応じて他の処理時間も使用することができる。

【0018】

図2は、実質的に露出した上部銅表面5の全体(図1に示す)をケイ化銅表面25に転化した後の図1に示す構造を示している。他の実施形態では、上部銅表面5の露出領域の少なくとも一部分をケイ化銅表面25に転化する。元のCu表面5と比較すると、ケイ化銅表面25は表面積が増加したより粗い表面であり、本質的に望ましくない酸化銅を一切含まない。表面積の増加により、ケイ化銅表面25の上に形成され、それに接触するフィルムへの付着力が改善される。また、ケイ化銅表面25は、銅相互接続リード線10内のヒロック形成を抑制するという利点も含む。

【0019】

図2Aは、ケイ化銅に転化された最初は銅の表面の拡大断面図である。図2Aは、図1に示す元の上部銅表面5がケイ化銅表面25に転化され、それが塊の銅材3を浸食するケイ化銅29を含むことを示している。ケイ化銅29は、シリコンが元の上部表面に浸透し、その中の銅と錯化してケイ化銅を形成する、銅相互接続リード線10の転化部分を表している。シランまたはその他のシリコン気体化学物質からのシリコンが元の上部銅表面5に浸透してCuと錯化し、それにより、その表面の上部部分をケイ化銅29に転化することにより、ケイ化銅が形成されるように、処理パラメータが選択される。ケイ化銅29は、20〜200オングストロームの範囲の深さ31を含むことができるが、別法としてその他の厚さも使用することができる。当業者であれば、プロセス温度とプロセス持続時間を変化させて、ケイ化銅29の厚さ31を制御できることが分かるだろう。厚さ31は、銅相互接続構造からの銅拡散を防止するのに十分な厚さで、相互接続リード線10内の銅のシート抵抗の増加を最小限にするのに十分な薄さになるよう、所望のケイ化度とともに選択することができる。図示の実施形態では、ケイ化銅表面25は、粗く不規則な表面として示されている。このような粗く不規則な表面は、その上に形成されたフィルムへの付着力を改善するような追加の表面積をもたらす。

【0020】

350℃〜400℃の温度範囲内で持続時間が短い任意選択のアニールを実行して、銅相互接続リード線のシート抵抗を低減し、ケイ化銅表面25と、ケイ化銅表面25に接触するように形成可能な後続導体材料との接触抵抗を低減することができる。この任意選択のアニールは、数秒台または数分台のアニール時間を含むことができる。持続時間が短いアニールによって最初に形成されたケイ化銅の相が変化するため、またはシリコンの超過により追加のケイ化銅形成が発生するため、あるいはその両方のために、シート/接触抵抗の低減が達成されると考えられている。このアニール・プロセスは、窒素その他の不活性種を含むことができる。他の例示的な実施形態によれば、このアニーリング・プロセスを使用しない場合もある。

【0021】

図2は、ケイ化銅表面25を形成した後の構造を示している。例示的な一実施形態によれば、本発明の利点の1つはこの構造の上に後続フィルムをその後形成することとともに、本発明のケイ化/パッシベーション・プロセスが原位置に実行可能であることなので、この構造は中間構造になる可能性がある。この後続フィルムは、上にある誘電体スタックを形成するために使用する様々な誘電体フィルムのいずれかにすることができ、例示的な一実施形態によれば、その表面の上に直接形成された第1の層は、ケイ化/パッシベーション・プロセスによって原位置に形成される窒化ケイ素または炭化ケイ素のフィルムにすることができる。

【0022】

図3は、図2に一般的に示す下部構造の上に形成された上部誘電体35を示す断面図であるが、明瞭にするため、下にある層23とバリア層13および15は除去されている。したがって、図示されていないが、これらのフィーチャは図示の実施形態などの様々な実施形態に含めることができることを理解されたい。上部誘電体35は、上記のようにケイ化銅29を含むケイ化銅表面25および上面11の上に形成される。上部誘電体35は、単一の誘電体フィルムである場合もあれば、複数誘電体のスタックを表す場合もあり、その誘電体の一部または全部はケイ化/パッシベーション・プロセスによって原位置に形成することができる。低k誘電体材料およびSiベースの材料を使用することができ、この誘電体材料は図1の誘電体材料9に関連して前述した通りのものにすることができる。例示的な一実施形態では、上部誘電体35は、複数の個別層からなる複合物またはスタックにすることができる。上部誘電体35は、点線で分離した2つの層35Aおよび35Bから形成することができる。この例示的な実施形態によれば、誘電体層35Aは窒化ケイ素または炭化ケイ素にすることができ、誘電体層35Bは低k誘電体材料にすることができる。これは例示のみを目的とするものであり、他の例示的な実施形態では、他の数の様々な誘電体フィルムを使用して、上部誘電体35を形成することができる。上部誘電体35には、1つまたは複数のハードマスク・フィルムを含めることができる。本発明の1つの態様は、特にケイ化したケイ化銅表面25と接触している誘電体層が窒化ケイ素または炭化ケイ素であるときに、ケイ化したケイ化銅表面25と上部誘電体35との付着力が改善されることである。

【0023】

図4は、上部誘電体35に形成された開口部41の底部から銅相互接続リード線10のケイ化銅表面25と接触するように例示的な導体構造39を形成した後の図3の構造を示している。開口部41は上部誘電体層35の底部まで延び、ケイ化銅表面25のセクション51を露出する。例示的な実施形態では、開口部41は二重食刻装飾開口部であるが、他の実施形態では他の開口部を使用して銅相互接続リード線10のケイ化銅表面25との接触に備えることができる。開口部41は、ケイ化銅表面25の一部のみを露出する。ケイ化銅表面25の他の部分は、上部誘電体35によって覆われたままになる。(これについては図5により明瞭に示されている。)導体構造39は、任意選択のバリア層43および45と、塊の導体材料47とを含む。任意選択のバリア層43および45は、銅相互接続リード線10に関連して述べたバリア層13および15と同様のものであり、塊の導体材料47は銅またはその他の適当な導体材料にすることができる。本発明の1つの利点は、例示的な一実施例によれば、ケイ化銅表面25が銅相互接続リード線10と導体構造39との間の拡散バリアとして機能するので任意選択のバリア層43および45が不要になることである。図示の例示的な実施形態によれば、導体構造39は、上部誘電体35の上面37と実質的に共面の平面化した上面49を含む食刻装飾構造である。他の例示的な実施形態では、他の様々な食刻装飾導体構造および非食刻装飾導体構造を使用して、ケイ化銅表面25に接触してもよい。

【0024】

図5は、図4に示すように銅相互接続リード線10の上に形成され、それと接触する上部導体構造39を示す平面図である。この例示的な実施形態では、導体構造39は、開口部(図4に示す開口部41)内に形成され、銅相互接続リード線10のケイ化銅表面25のセクション51に接触するバイアである。ケイ化銅表面25の他の部分は上部誘電体35によって覆われている。任意選択のバリア層43および45は図5に示されていない。

【0025】

図示の例示的な実施形態によれば、銅相互接続リード線10は、デバイスを通って横方向に延びる長いトレンチ内に延びる相互接続ワイヤであり、導体構造39はバイアであるが、他の例示的な実施形態により他の配置を使用することもできる。たとえば、上部食刻装飾相互接続構造がそれが形成されている誘電体層の底部まで延びている例示的な実施形態によれば、ほぼ直交関係で互いに横切る2つの相互接続リード線間で接触を行うことができる。その上、他の例示的な実施形態によれば、上部相互接続構造は非食刻装飾構造でもよい。

【0026】

本発明のもう1つの実施形態は、露出銅表面の局部ケイ化である。図6は、誘電体材料9内に形成された例示的な銅相互接続リード線10の断面図である。第2の誘電体層61は、上部銅表面5と、誘電体材料9の上面11の上に形成される。第2の誘電体61は、前述の通り、様々な材料のいずれかまたは複数材料の層からなる様々なスタックのいずれかにすることができる。たとえば、第2の誘電体61は、Siベースの低k誘電体層を含むかまたはこのような誘電体層から排他的に形成することができ、少なくとも1つのハード・マスク層を含むことができる。開口部65は、第2の誘電体61を通って延び、上部銅表面5のセクション67を露出する。例示的な開口部65は二重食刻装飾開口部として示されているが、他の例示的な実施形態では他の様々な開口部を形成することができる。その場合、上記のパッシベーション/ケイ化プロセスにより、銅相互接続リード線10の上部銅表面5の露出セクション67を不動態化することができる。図6に示す構造に対してパッシベーション/ケイ化プロセスを実行して、図7に示す構造を形成する。

【0027】

図7は、銅相互接続リード線10の最初は銅の上部表面の露出セクション67に形成された局部ケイ化銅表面25を示している。上部銅表面5の他の非露出部分については、このような不動態化が行われない。シリコンが元の銅上部表面に浸透し、銅相互接続リード線10の銅と錯化するにつれて、Cu相互接続リード線10を浸食し、上部銅表面5の露出セクション67内の銅をケイ化銅29に転化するように、ケイ化銅29を形成する。この実施形態では、局部的ケイ化銅29は、銅相互接続リード線10と、その後形成され、銅相互接続リード線10と接触する導体構造との間のバリア層として機能することができる。これにより、開口部65内に連続バリア層フィルムを形成して銅相互接続リード線10と接触しようと試みるという欠点が克服される。開口部65が高いアスペクト比を有する例示的な実施形態によれば、従来の方法を使用して形成されるバリア層フィルムは、不連続になり、開口部内に空の領域を発生する傾向がある。

【0028】

図8は、図7に示す構造の平面図である。図8は、銅相互接続リード線10の上に位置合せされたバイアを形成するために使用する、例示的な二重食刻装飾開口部65を示している。局部ケイ化銅表面25は、ケイ化銅に転化された銅相互接続リード線10の元の上部銅表面5の露出部分であるセクション67内のみに実質的に形成される。上部銅表面5のうち、露出されず、局部的にケイ化されない他の部分は、覆いのない銅として存続する。このようにして、図7に断面で示す第2の誘電体層61は、上部銅表面5を覆い、それを通って元の上部銅表面5のセクション67を露出する開口部65を含み、その上部銅表面5はセクション67内のみでケイ化銅表面25に転化されている。したがって、開口部65は、上部銅表面のうち、ケイ化銅に転化される局部的部分を規定する。

【0029】

図9は、セクション67で局部的ケイ化銅表面25に接触するように開口部65内に形成される上部導体構造71を示している。上部導体構造71は塊の導体材料77を含み、従来の方法を使用して形成することができる。塊の導体材料77は、銅、アルミニウム、またはその他の適当な導体材料にすることができる。図示の実施形態では、上部導体構造71はバイアであり、上面81が第2の誘電体61の上部表面69と本質的に共面になるように食刻装飾処理を使用して形成することができる。他の例示的な実施形態によれば、上部導体構造71は、ケイ化銅表面25と接触する、相互接続リード線などの他の食刻装飾構造のいずれかにすることができる。さらに他の例示的な実施形態によれば、非食刻装飾構造は、ケイ化銅表面25に転化される元の上部銅表面5の局部部分(セクション67)を規定する開口部65を充填するように形成することができる。したがって、本発明の1つの利点は、開口部内に連続バリア層フィルムを形成することを困難にするような高いアスペクト比を含む可能性のある開口部65などの開口部内にフィルムを付着する必要なしに、銅相互接続リード線10と上部導体構造71との間にバリア層、すなわち、ケイ化銅29を形成することである。他の例示的な実施形態では、ケイ化銅29とともに追加のバリア層を使用してもよい。

【0030】

図10は、層101の表面103の上に形成された銅相互接続ワイヤ105の斜視断面図である。層101は、基板またはその他の半導体構造の上に形成された誘電体またはその他の層にすることができる。銅相互接続ワイヤ105は、フォトリソグラフィならびに当技術分野で現在開発中のパターン形成およびエッチング手順などの様々な技法を使用して形成することができる。銅にパターン形成およびエッチングを施すための改良された方法は引き続き当技術分野で開発されることが検討されている。パターン形成した銅相互接続ワイヤ105は、それぞれが銅で構成される上面107と側壁109とを含む。

【0031】

上記のように、本発明のケイ化/パッシベーション・プロセスを使用して、銅相互接続ワイヤ105の露出表面(上面107および側壁109)を不動態化することができる。パッシベーション・プロセスの結果として、銅相互接続ワイヤ105の側壁および上面がケイ化銅に転化される。

【0032】

図11は、上記の実施形態に示し記載したように、その時点でケイ化銅を含むケイ化銅表面である転化側壁119と転化上面117を示している。図11に示すケイ化構造は、ケイ化銅表面119および117がこのような外方拡散を抑制するので、銅相互接続ワイヤ105からの銅拡散が低減されるという利点を享受するものである。ケイ化銅表面117および119は、銅相互接続ワイヤ105と誘電体またはその上に形成された他の材料との間に形成された境界に沿った銅のエレクトロマイグレーションも抑制する。その後形成される材料、特に窒化ケイ素および炭化ケイ素の銅相互接続ワイヤ105に対する付着力は、このケイ化銅のために改善される。ヒロック形成は抑制される。任意選択でバリア層を含むことができる様々な導体材料は、ケイ化表面117および119に形成されたケイ化銅領域と接触するように形成することができる。銅相互接続ワイヤ105のケイ化銅表面がバリア材として作用するので、他の実施形態では追加のバリア層を使用しない。

【0033】

上記の説明は単に本発明の原理を例示するものである。したがって、当業者であれば、本明細書に明示的に記載または図示していないが、本発明の原理を実施し、その範囲および精神の範囲内に含まれる様々な配置を考案できることが分かるだろう。また、本明細書に列挙するすべての例および条件言語は主に、教育学的目的専用とし、本発明の原理および当技術分野の促進に対して本発明者らが寄与する概念を理解するのを助けることを特に意図したものであり、このように具体的に列挙した例および条件に制限を加えないものであると解釈すべきである。さらに、本発明の原理、態様、実施形態、ならびにその特定の例を本明細書で列挙するすべての記載は、構造および機能の両面でそれと同等のものを包含するためのものである。その上、このような同等物は、現在既知の同等物と、将来開発される同等物、すなわち、開発される要素のうち、構造にかかわらず同じ機能を実行するものすべてを含むものとする。したがって、本発明の範囲は、図示し、本明細書に記載した例示的な実施形態に限定されないものとする。むしろ、本発明の範囲および精神は特許請求の範囲によって実施されるものである。

【特許請求の範囲】

【請求項1】

半導体製品を形成するための方法において、

基板の上にCu相互接続構造を形成し、前記Cu相互接続構造が露出したCu表面を含むことと、

前記露出したCu表面の少なくとも一部分を、Siを含む気体材料を有するプラズマ反応条件下でケイ化銅に転化する工程を含み、

前記Cu相互接続構造を形成する工程が、上部Cu表面を有するCu相互接続構造を形成し、前記上部Cu表面上に誘電体層を形成し、及び、前記誘電体層に開口を形成して前記露出したCu表面である前記上部Cu表面の少なくとも一部を露出し、

前記転化する工程が、前記露出したCu表面を前記ケイ化銅へ転化する工程を含む方法。

【請求項1】

半導体製品を形成するための方法において、

基板の上にCu相互接続構造を形成し、前記Cu相互接続構造が露出したCu表面を含むことと、

前記露出したCu表面の少なくとも一部分を、Siを含む気体材料を有するプラズマ反応条件下でケイ化銅に転化する工程を含み、

前記Cu相互接続構造を形成する工程が、上部Cu表面を有するCu相互接続構造を形成し、前記上部Cu表面上に誘電体層を形成し、及び、前記誘電体層に開口を形成して前記露出したCu表面である前記上部Cu表面の少なくとも一部を露出し、

前記転化する工程が、前記露出したCu表面を前記ケイ化銅へ転化する工程を含む方法。

【図1】

【図2】

【図2A】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図2A】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−232676(P2010−232676A)

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願番号】特願2010−137862(P2010−137862)

【出願日】平成22年6月17日(2010.6.17)

【分割の表示】特願2003−120807(P2003−120807)の分割

【原出願日】平成15年4月25日(2003.4.25)

【出願人】(500587067)アギア システムズ インコーポレーテッド (302)

【Fターム(参考)】

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願日】平成22年6月17日(2010.6.17)

【分割の表示】特願2003−120807(P2003−120807)の分割

【原出願日】平成15年4月25日(2003.4.25)

【出願人】(500587067)アギア システムズ インコーポレーテッド (302)

【Fターム(参考)】

[ Back to top ]