側面パッドを備えるチップ、その製造方法及びそのチップを利用したパッケージ

【課題】側面パッドを備えるチップ、その製造方法及びそのチップを利用したパッケージを提供する。

【解決手段】上部表面、下部表面及び上部表面と下部表面とに連結された側部表面を持つ第1チップ100を備える半導体装置であり、第1チップは、チップ基板、チップ基板上の下部導電性パターン、下部導電性パターン上の層間誘電層及び層間誘電層上の上部導電性パターンを備え、下部導電性パターン120bの少なくとも一部及び上部導電性パターンの少なくとも一部は、集合的に側面パッド120を形成するように第1チップの側部表面上に露出される。

【解決手段】上部表面、下部表面及び上部表面と下部表面とに連結された側部表面を持つ第1チップ100を備える半導体装置であり、第1チップは、チップ基板、チップ基板上の下部導電性パターン、下部導電性パターン上の層間誘電層及び層間誘電層上の上部導電性パターンを備え、下部導電性パターン120bの少なくとも一部及び上部導電性パターンの少なくとも一部は、集合的に側面パッド120を形成するように第1チップの側部表面上に露出される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体チップ、その製造方法及びパッケージに係り、さらに詳細には側面パッドを備えるチップ、その製造方法及びそのチップを利用したパッケージに関する。

【背景技術】

【0002】

電子製品の大きさが益々小型化されその容量が増大するにつれて、前記電子製品内の半導体パッケージも小型でありつつも高容量を持つように製造されることが必要になった。図1は、従来の製造方法によって製造された複数のチップ10を持つ従来のウェーハの断面図である。

【0003】

図1を参照すれば、従来のチップ10のうち一つは、その上部表面20上に複数のチップパッド40を持ち、上部表面20は、多様な電気的構成要素が形成される活性面である。チップパッド40を通じて、チップ10内に形成された電気的構成要素と外部装置(図示せず)との間に信号が伝送される。

【0004】

しかし、性能上の要求、メモリキャパシタ、半導体パッケージの集積化及び小型化が進むほど、チップパッド40の密度は必然的に増大する。その結果、上部表面20上にチップパッド40を適切に形成することはさらに難しくなっている。たとえば、再配線パターンが占有できる上部表面20の可用面積に対する制限によって、上部表面20上に前記再配線パターンを適切に形成することはさらに難しくなっている。

【0005】

最近、チップ10は、ボンディングワイヤーまたはソルダーボールのような外部接続端子を使用して下地回路基板(図示せず)に電気的に結合される。前記ボンディングワイヤーを使用する場合に、チップパッド40が上部表面20上に配され、前記ボンディングワイヤーがチップパッド40と前記回路基板上のボンドフィンガーのような基板パッドとの間に結合されるように、前記チップ10が配される。前記ソルダーボールを使用する場合に、チップ10は、フリップ接触されてチップパッド40が上部表面20の下部に配され、ソルダーボールは、チップパッド40と前記回路基板上の基板パッドとの間に結合される。

【0006】

下地の回路基板にチップ10をワイヤーボンディングする時に、前記ボンディングワイヤーはチップ表面20上へ延びる。一方、チップ10がソルダーボールを使用して下地の回路基板に結合される時には、前記ソルダーボールは、チップ10と前記回路基板との間の距離を大きくさせる。いずれの場合にも、製造された半導体パッケージの厚さは、実質的にチップ10と前記回路基板との結合された厚さよりかなり厚くなる。本発明は、このような従来技術が持つ多様な問題点を解決するためのものである。

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、ボンディングパッドの全体数がかなり増加してもチップのサイズを大きくせずにボンディングパッドを容易に収容でき、かつチップのサイズが同じ場合にボンディングパッドの数を低減させうる半導体チップ、その製造方法及びパッケージ、さらに詳細には側面パッドを備えるチップ、その製造方法及び前記チップを利用したパッケージを提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一実施形態による半導体装置は、上部表面、下部表面及び前記上部表面と前記下部表面とに連結された側部表面を持つ第1チップを備える。前記第1チップは、チップ基板、前記チップ基板上の下部導電性パターン、前記下部導電性パターン上の層間誘電層及び前記層間誘電層上の上部導電性パターンを備える。前記下部導電性パターンの少なくとも一部及び前記上部導電性パターンの少なくとも一部は、集合的に側面パッドを形成するように、前記第1チップの前記側部表面上に露出されうる。

【0009】

本発明の他の実施形態による半導体装置の製造方法は、上部表面、下部表面及び前記上部表面と前記下部表面とに連結された側部表面を持つ第1チップを備える。前記第1チップは、チップ基板を提供する工程、前記チップ基板上に下部導電性パターンを形成する工程、前記下部導電性パターン上に層間誘電層を形成する工程、及び前記層間誘電層上に上部導電性パターンを形成する工程により提供される。前記下部導電性パターンの少なくとも一部及び前記上部導電性パターンの少なくとも一部は、集合的に側面パッドを形成するように、前記第1チップの前記側部表面上に露出されうる。

【発明の効果】

【0010】

本発明による側面パッドを使用すれば、ボンディングパッドの全体数がかなり増加しても、チップのサイズを増大させずにボンディングパッドを容易に収容できる。すなわち、本発明の実施形態によれば、同じチップサイズでもチップパッドの全体数がかなり増加できる。

【発明を実施するための最良の形態】

【0011】

以下に、図面を参照して、本発明の多様な実施形態について詳細に説明する。しかし、これら実施形態は多くの他の形態に変形して実施することができ、本明細書で説明した実施形態に制限されるものと解釈されてはならない。これらの実施形態は本発明の開示をさらに完全にして当業者に本発明の思想を十分に理解できるようにするために提供されたものである。図面で、層及び領域の厚さは説明の明確性のために誇張されている。また、本明細書全体で、同じ構成要素は同じ参照番号により参照される。

【0012】

図2A及び図2Bは、実施形態による側面パッドを持つチップの斜視図である。

【0013】

図2Aを参照すれば、図示されたチップ100は、ロジックチップ、メモリチップなど、またはシステムオンチップ(SOC)のようなものの複合機能を持つチップである。たとえば、実施形態によれば、チップ100は、上部表面140、上部表面140に対向する下部表面(図示せず)及び上部表面140と前記下部表面とに連結された複数の側部表面150を備える。図2Aで、チップ100は、4つの側部表面150を持つことが図示されている。しかし、チップ100は、本発明の思想及び範囲内であれば任意の数の側部パッドを持っていてもよい。たとえば、チップ100は、少なくとも3つの側部表面150のみを持つ必要もある。後述するように、チップ100内に一般的に形成される配線部材及び/またはビアパターンを形成するための一つ以上の導電層(本明細書で導電性パターンと称することもある)を使用して、複数の側部表面150のうち少なくとも一つ以上の側部表面150上に複数の側面パッド120が形成される。

【0014】

チップ100は、チップ基板または半導体基板(図2Aには図示していないが、図3Bには図示する)を備える。Al、Cu、W、Mo、TiN、TaNまたはWNのような導電性金属窒化物のような材料を含む導電性パターンが複数の側面パッド120を形成するように側部表面150を通じて露出される。一実施形態で、チップ100はまた、前記チップ基板上に下部導電性パターン120b、下部導電性パターン120b上に層間絶縁層(たとえば、図4Cの110)及び前記層間絶縁層上に上部導電性パターン120aを備える。

【0015】

一実施形態で、下部導電性パターン120bの少なくとも一部及び/または上部導電性パターン120aの少なくとも一部は、チップ100の側部表面150のうち少なくとも一つの側部表面150上に露出されて、側面パッド120を形成する。たとえば、上部導電性パターン120aの少なくとも一部が、チップ100の上部表面140と下部導電性パターン120bとの間に垂直方向に配される。具体的には、チップ100の側部表面150上に露出された上部導電性パターン120aの一部は、チップ100の側部表面150上に露出された下部導電性パターン120bの一部とチップ100の上部表面140との間に配される。

【0016】

側面パッド120は、2個の導電性パターンを備えているものが図示されているが、側面パッド120は、任意の数の導電性パターン、すなわち、一つ以上の導電性パターンを持つことができることは明らかである。しかし、側面パッド120のために2つ以上の導電性パターンが、側面パッド120と、たとえば、図13Bに図示された導電性配線312のようなコンタクトターミナルとの間のコンタクト抵抗を低減させ、側面パッド120とコンタクトターミナルとの整列マージンを増大させるためには効果的である。また、2以上の導電性パターンの場合、側面パッド120と前記コンタクトターミナルとの間の溶融度を改善させることができる。

【0017】

上部導電性パターン120aと下部導電性パターン120bとの幅及び厚さは、チップの形状、パッケージの種類及びチップ100内の電気的構成要素を形成するための製造工程のような要因により決定される。

【0018】

また、側面パッド120は、チップ100の複数の側部表面150と実質的に同一平面上にあるか、これらから突出してもよい。選択的には、側面パッド120は適用製品によってチップ100の側部表面150からリセスされることもある。

【0019】

一実施形態によれば、上部導電性パターン120aと下部導電性パターン120bとの間に誘電材料が配される。後述するように、上部導電性パターン120aと下部導電性パターン120bとの間に付加的な導電性パターンが配されることもある。

【0020】

図2Aに説明された一実施形態で、チップパッド130は、チップ100の上部表面140上に配される。チップパッド130は、電気的導電性配線構造(図示せず)により導電性構造104(図3B)及び/または導電性パターン108(図3B)に電気的に連結される。しかし、チップ100は、チップパッド130を備えなくてもよいことは明らかである。このような実施形態は、図2Bに図示されている。

【0021】

図3Aは、チップ100内に提供されたパッドの配置を示す平面図である。図3Bは、図3Aに図示された線“A−A”に沿って切り取った断面図である。

【0022】

図3A及び図3Bを参照すれば、複数のチップ100は、一般的に従来の製造方法により同じ基板“a”(たとえば、半導体基板)上に共に形成される。チップ領域内に複数のチップ100が形成される。基板上でチップ領域は当該技術分野で公知のように実質的に均一な幅を持つダイシング領域(すなわち、スクライブラインSLで指示された領域)だけ互いに離隔される。各チップ100は、複数の導電性パターン108を備えることができる。各導電性パターン108の第1部分は、チップ100により占有された基板の領域上に配され、各導電性パターン108の第2部分は前記ダイシング領域、すなわち、スクライブラインSLにより占有された基板の領域上に配される。導電性パターン108の端部の断面図は、四角形を限定する点線により指示されている。

【0023】

図3Bを参照すれば、各チップ100は、たとえば、半導体基板(本明細書で102で例示される)上に形成された導電性構造体104、第1層間誘電層106及び前述した導電性パターン108を備える。一実施形態で、導電性構造体104は、たとえば、セルトランジスタ、コアトランジスタ、ペリフェラルトランジスタ、ストレージキャパシタまたはこれらの組み合わせのような電気的構成要素を含む。他の実施形態で、導電性構造体104は、配線、コンタクトまたはこれらが組み合わせられたもののような他の構造体を備えることができ、これらは電気的構成要素に結合されうる。一実施形態で、第1層間誘電層106は、たとえば、酸化物(たとえば、SiO2)、低誘電率(low−k)物質(たとえば、SiCOH)またはこれらの組み合わせを含む。

【0024】

図3Bにさらに詳細に図示されているように、チップ100は、たとえば、複数の導電性パターン108として、上部導電性パターン108a及び下部導電性パターン108bを備えることができる。

【0025】

実施形態によれば、前記導電性パターンは、ビットラインまたはメモリ素子のセル領域、メモリ素子のペリフェラル領域または当該技術分野で公知の他の電気的構成要素またはこれらの組み合わせに連結された配線でありうる。一実施形態で、側面パッドを形成するための導電性パターンは、ビットラインが形成された後に形成されることもある。実施形態によれば、導電性パターン108は、ビアパターン、ダミーライン、ダミートランジスタのようなトランジスタまたはこれらの組み合わせでありうる。したがって、ダミートランジスタの一部だけでも、たとえば、図2Aに示したように、側面パッド120を形成するために使われる。上部導電性パターン108a及び下部導電性パターン108bの一部は、スクライブラインSLにより表示された半導体基板102の領域上へ延びる。上部導電性パターン108aの厚さまたは下部導電性パターン108bの厚さは、少なくとも約1μm以上である。望ましくは、上部導電性パターン108a及び下部導電性パターン108bの厚さは、約1μmないし約2μmである。しかし、本発明は、このような特定厚さ範囲に制限されず、図13Bに示したように導電性配線部材312と接触するのに十分なコンタクト面積を持つ側面パッド120を提供するかぎり、上部導電性パターン108a及び下部導電性パターン108bを結合した任意の厚さが許容されうる。

【0026】

また、上部導電性パターン108a及び下部導電性パターン108bは、配線のような他の素子構造物を形成する間に形成される。たとえば、従来の配線及び側面パッド120用導電性パターン108は、前記配線を形成するためのマスクに付加的なパターンを追加するだけでも同一工程で形成されうる。したがって、上部導電性パターン108a及び下部導電性パターン108bを形成するための付加的なマスクは省略できる。したがって、本発明は付加的なコストなしでも実施できる。

【0027】

第2層間誘電層110は、上部導電性パターン108aと下部導電性パターン108bとの間に配され、第3層間誘電層112は下部導電性パターン108b上に配される。

【0028】

一般的に、電力と接地配線と(たとえば、図1に示したような)チップパッドとの間に多層配線レベルが要求され、前記チップパッドは、チップ100の上部上に形成されうる。また、前記多層配線レベルは、チップパッド130と、セルトランジスタ、コアトランジスタ、ペリフェラルトランジスタ、ストレージキャパシタのような下地の導電性構造体との間で要求されることもある。また、従来技術のように、前記電源または接地配線が、抵抗及び干渉を考慮して単一パッドよりは複数のチップパッド130に連結された場合、電力または接地のための配線経路は一般的に非常に複雑であるか長い。各配線レベルは前記配線レベルの長さに比例して信号遅延を生じさせる電気抵抗を伴う。

【0029】

しかし、前述したように、側面パッド120を提供することによって、前記電源または接地配線または信号ラインがチップ100の上部上に配されるチップパッド130を通じる必要がなく、従来技術よりさらに短い経路で側面パッド(ボンディングパッド)120に連結されるので、配線レベルの数及び配線の長さはかなり減少する。その結果、電気抵抗及び信号遅延はだいぶ減少する。また、側面パッド120の提供により、導電性構造体と外部信号ソース(たとえば、電源ソース、接地、通常の信号ソースなど)との間の信号経路の複雑性が低下する。本発明の一部の実施形態によるこのような特徴は、図12Aないし図12Cを参照してさらに詳細に説明する。

【0030】

図4Aないし4Cは、図2に図示されたチップを形成する方法を説明するための断面図である。

【0031】

図2Aに図示されたチップの形成方法は、一般的に上部表面140、下部表面(図示せず)及び上部表面140及び前記下部表面に連結された側部表面150を持つチップ100を形成する工程を有するという特徴を持つ。

【0032】

図4Aを参照すれば、チップ100は、当該技術分野で公知のように、半導体基板またはチップ基板102を提供する工程、半導体基板102上に導電性構造体104を形成する工程により形成される。前述したように、一実施形態で、導電性構造体104は、たとえば、セルトランジスタ、コアトランジスタ、ペリフェラルトランジスタ、ストレージキャパシタなどまたはこれらの組み合わせのような電気的構成部材を備えることができる。他の実施形態で、導電性構造体104は、前記電気的構成部材に結合されうる配線、コンタクトまたはこれらの組み合わせのような導電性構造体を備えることができる。

【0033】

次いで、第1層間誘電層106は、半導体基板102及び導電性構造体104を備える結果物上に形成される。一実施形態で、第1層間誘電層106は、電気絶縁物質をコーティングする工程、及びたとえば、機械化学的研磨工程(Chemical Mechanical Polishing:CMP)により前記電気絶縁物質の上部表面を平坦化する工程により形成される。一実施形態で、前記電気絶縁物質は、たとえば、酸化物(たとえば、SiO2)、低誘電率物質(たとえば、SiCOH)など、またはこれらの組み合わせを含むことができる。

【0034】

図4Bを参照すれば、導電性パターン108は、第1層間誘電層106上に形成される。一実施形態で、導電性パターン108は、連続的に第1層間誘電層106上に下部導電性パターン108bを形成する工程、下部導電層パターン108b上に第2層間誘電層110を形成する工程、及び上部導電層パターン108a上に第3層間誘電層112を形成する工程により形成される。

【0035】

一実施形態で、第2層間誘電層110及び第3層間誘電層112は、第1層間誘電層106が形成された方法と実質的に同一または類似した方法で形成されうる。上部導電性パターン108a及び下部導電性パターン108bは、下地の層間誘電層上に導電性物質を蒸着する工程、及び各導電性パターン108の少なくとも一部が半導体基板102のスクライブラインSLにより占有された領域上に配されるように、前記導電性物質をパターニングする工程により形成されうる。各導電性パターン108は、チップ100内の一つ以上の導電性パターン108に電気的に連結されうる。

【0036】

簡単に言えば、チップ100は半導体基板またはチップ基板102を提供する工程、前記チップ基板102上に下部導電性パターン102bを形成する工程、下部導電性パターン120b上に層間誘電層を形成する工程、及び前記層間誘電層上に上部導電性パターン120aを形成する工程により形成されうる。下部導電性パターン120bの少なくとも一部と上部導電性パターン120aの少なくとも一部とがチップ100の側部表面上に露出されて、集合的に側面パッド120を形成できる。下部導電性パターン108a及び上部導電性パターン108bは、他の素子または配線部材構造体が前述した方法と後述する方法のように形成される間に形成される。

【0037】

導電性パターン108を形成する工程の後に、チップパッド130は、従来の技術を使用して第3層間誘電層112上に形成されうる。前述したように、チップパッド130は、導電性構造104及び/または導電性パターン108のうちいずれか一つに電気的に連結されうる。したがって、チップパッド130は、側部パッド120に電気的に連結されうる。

【0038】

実施形態によれば、導電性パターン108は、ビットライン、メモリ素子のセルまたは周辺領域に結合される配線、ビアパターン、ダミーライン、トランジスタまたはこれらの組み合わせの形成に利用される工程と同じ方法により形成されうる。したがって、図3Bを参照して説明したように、追加的なフォトレジストパターンを形成するために利用される別途の工程が要求されない。

【0039】

図4Cを参照すれば、隣接するように配されたチップ100は、たとえば、レーザーまたは従来のダイアモンドカッターまたはダイアモンドソウ(saw)を使用して、スクライブラインSLに沿って、たとえば、ダイシング工程を行うことにより互いに個別化される。チップ100を個別化する時に、スクライブラインSLにより占有された半導体基板102の領域上に各導電性パターン108の一部が除去される。前記ダイシング工程の後に、チップ100内に残留する各導電性パターン108の一部が側面パッド120の一部を限定する。したがって、前記ダイシング工程の後に、チップ100内に残る下部導電性パターン108bの一部は、たとえば、図2A及び図2Bに示したような側面パッド120の一部を限定する下部導電性パターン120bを形成する。同様に、前記ダイシング工程後に、チップ100内に残る上部導電性パターン108aの一部は、側面パッド120の上部導電性パターン120aを形成する。以後、選択的には、導電性配線312とさらによく連結されるように、側面パッド120が露出されるチップの側部表面を研磨または滑らかにすることができる。

【0040】

簡単に言えば、チップ100は、ダイシング領域により離隔された複数のチップ領域を持つ半導体基板102を提供する工程、半導体基板102上にそして少なくとも一つのチップ領域内に下部導電性パターン108bを形成する工程、下部導電性パターン108b及び前記ダイシング領域上に層間誘電層110を形成する工程、及び下部108b及び上部導電性パターン108aのうち少なくとも一つが前記ダイシング領域に延長されるように、層間誘電層110及び前記少なくとも一つのチップ領域上に上部導電性パターン108aを形成する工程、及び前記ダイシング領域から前記チップ領域を分離する工程を行うことによって形成される。したがって、チップ100がスクライブラインSLで半導体基板をダイシングすることによって個別化される場合に、それによって、側部表面上に層間誘電層110を通じて露出された下部導電性パターン108の端部は側面パッド120を限定する。

【0041】

チップ100を個別化する工程の前に、半導体基板102上にパッシベーション層(図示せず)が形成されうる。このような実施形態で、前記パッシベーション層は第3層間誘電層112及びチップパッド130上に形成され、開口(たとえば、従来のフォトリソグラフィ工程により)が前記パッシベーション層内に形成されて、チップパッド130を露出させることができる。

【0042】

図5A及び図5Bは、他の実施形態による側面パッドを持つチップを示す斜視図である。

【0043】

図5Aを参照すれば、他の実施形態によるチップ100は、図2Aを参照して説明したチップ100と類似している。図5Aに図示されたチップ100の側面パッド160は、図2Aに図示された側面パッド120と類似しているが、上部導電性パターン120aと下部導電性パターン120bとの間に中間導電性パターン160aをさらに備えている点が異なっている。

【0044】

一実施形態で、中間導電性パターン160aは、上部導電性パターン120a及び下部導電性パターン120bに電気的に連結されうる。中間導電性パターン160aの少なくとも一部がチップ100の側部表面150上に露出されうる。一実施形態で、中間導電性パターン160aは“バー型導電性パターン”であり、上部導電性パターン120a及び/または下部導電性パターン120bの幅と実質的に同じ幅を持つことができる。一態様によれば、断面を見る時、前記バー型導電性パターンの場合には、長さに対する幅の比が約1:2でありうる。バー型中間導電性パターン160aを提供することによって、側面パッド160のコンタクト面積は改善された溶融度及び低下したコンタクト抵抗を確保するために大きくなりうる。しかし、他の実施形態で、中間導電性パターン160aは“コンタクト型導電性パターン”であり、上部導電性パターン120a及び/または下部導電性パターン120bの幅よりさらに狭い幅を持つことができる。前記コンタクト型パターンは、他のレベルの金属配線を連結する一般的なビアパターンの形状を持つことができる。

【0045】

さらに他の実施形態で、中間導電性パターン160aは、チップ100の側部表面150から隠蔽されることもある。したがって、上部導電性パターン120a及び下部導電性パターン120bの露出された部分は、必ずしも側部表面150だけではなくチップ100の他の内部に電気的に結合されることもある。しかし、チップ100がチップパッド130を備えないこともあるということは明らかである。図5Bにこの実施形態を例示した。

【0046】

図6Aないし図6Cは、図5Aに示したようなチップを形成するための方法を示す断面図である。

【0047】

図6Aを参照すれば、たとえば、半導体基板102上に導電性構造体104を形成する工程を含む方法によって、チップ100が形成されることもある。一実施形態で、導電性構造体104は、図4Aを参照して既述した導電性構造体104と実質的に同一または類似している。次いで、第1層間誘電層106は、半導体基板102及び導電性構造体104を備える結果物上に形成されうる。次いで、第1層間誘電層106上には、たとえば、下部導電性パターン108bのような導電性パターンが形成され、図4Bを参照して説明したものと実質的に同一または類似した方法で、下部導電性パターン108b上に第2層間誘電層110が形成されうる。以後、第2層間誘電層110内に下部導電性パターン108bの少なくとも一部を露出するように、開口が限定されうる。一実施形態で、前記開口は、下部導電性パターン108bの幅よりさらに小さく、これによって、コンタクト型導電性パターンを形成する工程を連続的に行うことを容易にする。他の実施形態で、前記開口は下部導電性パターン108bの幅と実質的に同一であり、これによって、バー型導電性パターンを形成する工程を連続的に行うことを容易にする。一実施形態で、前記開口を限定するために、従来の写真エッチング技術を使用して第2層間誘電層110の一部が除去される。前記開口内に中間導電性パターン152aが形成されうる。

【0048】

図6Bを参照すれば、以後、他の導電性パターン、たとえば上部導電性パターン108aが第2層間誘電層110と中間導電性パターン152aの上に形成され、次いで、上部導電性パターン108a上に第3層間誘電層112を形成する工程を行う。中間導電性パターン152aの幅及び上部導電性パターン108aの幅は、実質的に同一でありえる。しかし、必ずしも同一である必要はない。

【0049】

他の素子構造体が形成されながら、層間導電性パターン152aが形成される。たとえば、従来の半導体製造工程の間に、ビアパターンが形成されながら中間導電性パターン152aが形成される。したがって、前記ビアパターンを形成するためのフォトマスクに中間導電性パターン152aが追加されるので、中間導電性パターン152aを形成するための追加的なマスクは必要ない。したがって、中間導電性パターン152aを形成するための追加的なフォトリソグラフィ工程は必要ない。

【0050】

一実施形態で、第2層間誘電層110及び第3層間誘電層112は、第1層間誘電層106が形成されるのと同一または類似した方法で形成されうる。一実施形態で、上部導電性パターン108a及び下部導電性パターン108bは、図4Bを参照して説明した方法と実質的に同一または類似した方法で形成されうる。

【0051】

一実施形態で、第2層間絶縁層110内に限定された開口内に導電性物質を蒸着する工程及び前記開口外部の前記導電性物質の一部を選択的に除去する工程を行うことによって、中間導電性パターン152aが形成されうる。したがって、第2層間絶縁層110内に限定された開口の幅によって、前述したような導電性ビアパターンまたは導電性コンタクトとして、中間導電性パターン152aが提供されうる。

【0052】

導電性パターン108a上に第3層間誘電層112を形成する工程の後に、第3層間誘電層112上にチップパッド130が形成されうる。一実施形態で、チップパッド130は、図4Bを参照して説明したチップパッド130と実質的に同一または類似している。

【0053】

図6Cを参照すれば、以後、チップ100は、図4Cを参照して説明した方法と実質的に同一または類似した方法で互いに個別化されうる。したがって、チップ100の個別化工程時に、スクライブラインSLが占める半導体基板102の領域上に配される中間導電性パターン152aの一部が除去される。ダイシング工程後に、チップ100内に残っている各中間導電性パターン152aの一部は、側面パッド160を形成する中間導電性パターン160aを形成する。したがって、前述した方法によれば、下部導電性パターン120b及び上部導電性パターン120aが中間導電性パターン160aと電気的に連結されて側面パッド160を形成する。一実施形態で、中間導電性パターン160の少なくとも一部がチップ100の側部表面150上に露出されうる。

【0054】

図4Cを参照して説明した方法と実質的に同一または類似した方法により、パッシベーション層(図示せず)が半導体基板102上に形成されうる。

【0055】

図7は、本発明のさらに他の実施形態による側面パッドを持つチップの斜視図である。

【0056】

図7を参照すれば、さらに他の実施形態によるチップ100は、図2Aを参照して説明したチップ100と類似しており、ただし、下部導電性パターン120bの下にチップ100の側部表面150の上に露出された導電性部材170をさらに備えることができる。しかし、チップ100がチップパッド130を備えないこともあるということは明らかである。一実施形態で、導電性部材170は、Al、Cu、W、Mo等、またはこれらの組み合わせのような金属、及び/またはTiN、TaN、WNなど、またはこれらの組み合わせのような導電性金属窒化物を含むことができる。

【0057】

図示したように導電性部材170は、たとえば、チップ100の側部表面150で下部導電性パターン120bに連結されうる。しかし、他の実施形態で、導電性部材170は、チップ100の側部表面150で下部導電性パターン120bに連結されず、たとえば、チップ100の内部のような他の場所で下部導電性パターン120bに電気的に連結されることもある。また、導電性部材170は、半導体基板102から離隔するか、連結されないこともある。

【0058】

一実施形態で、導電性部材170は“バー型導電性部材”であり、下部導電性パターン120bの幅と実質的に同等な幅を持つこともある。バー型導電性部材170を提供することによって、側面パッド120のコンタクト面積は、改善された溶融度及び減少したコンタクト抵抗を確保するために大きくなることもある。他の実施形態で、導電性部材170は“コンタクト型導電性部材”であり、下部導電性パターン120bの幅よりさらに狭い幅を持つことができる。

【0059】

図8Aないし8Cは、図7に図示されたチップを形成するための実施形態を示す断面図である。

【0060】

図8Aを参照すれば、チップ100を形成するために半導体基板102上に導電性構造体104が形成される。一実施形態で、導電性構造体104は、図4Aを参照して説明した導電性構造体104と実質的に同一または類似している。次いで、半導体基板102と導電性構造体104とを備える結果物上に第1層間誘電層106が形成されうる。一実施形態で、導電性構造物104は、図4Aを参照して説明した導電性構造物104と実質的に同一または類似している。導電性部材170aは、薄膜蒸着法のような従来の技術及びCMPのような平坦化工程を利用して形成されうる。前述したように、導電性部材170aは、半導体基板102と接触をしても、しなくてもよい。

【0061】

図8B及び8Cに示したようにチップ100を形成するための残りの工程は、図4B及び図4Cを参照して説明した方法と実質的に同一または類似している。たとえば、図8Cに図示したように、隣接して配されたチップ100はたとえば、レーザーまたは従来のダイアモンドチップカッターまたはダイアモンドソウを使用して、スクライブラインSLに沿ってダイシング工程を行うことにより互いに個別化されうる。チップ100を個別化させるとき、半導体基板102でスクライブラインSLが占める領域上に配される各導電性パターン108の一部が除去される。ダイシング工程後に、チップ100内に残る各導電性パターン108の一部は側面パッド120を形成する。したがって、前記ダイシング工程後に、チップ100内に残る下部導電性パターン108bの一部は、側面パッド120の下部導電性パターン120bを形成する。同様に、前記ダイシング工程の後に、チップ100内に残る上部導電性パターン120aの一部は側面パッド120の上部導電性パターン120aを形成する。この工程中に導電性部材170は、第1層間誘電層106を通じて露出されうる。

【0062】

したがって、要するに、チップ100は、下部導電性パターン120bの下部に配された導電性部材170を形成する工程により形成されうる。導電性部材170の少なくとも一部がチップ100の側部表面150上に露出され、下部導電性パターン120bに電気的に連結される。すなわち、下部導電性パターン108bが導電性部材170上に形成され、導電性部材170は下部導電性パターン108bと接触できる。

【0063】

図9はさらに他の実施形態による側面パッドを持つチップの斜視図である。図9を参照すれば、さらに他の実施形態によるチップ100は、図7を参照して既述したように下部導電性パターン120bの下にチップ100の側部表面150上に導電性部材170が露出されうるという点を除いては、図5Aを参照して説明したチップ100と類似している。しかし、チップ100がチップパッド130を備えていないこともあるということは明らかである。

【0064】

図示したように、導電性部材170は、チップ100の側部表面150で、下部導電性パターン120bに電気的に連結されうる。しかし、他の実施形態で、導電性部材170は、チップ100の側部表面150で下部導電性パターン120bに電気的に連結されず、チップ100の内部のような他の所に連結されることもある。一実施形態で、導電性部材170は“バー型導電性部材”であり、下部導電性パターン120bの幅と実質的に同等な幅を持つことができる。バー型導電性部材170を提供することによって、側面パッド160のコンタクト領域は、溶融度を高めてコンタクト抵抗を低下させるために大きくなりうる。他の実施形態で、導電性部材170は“コンタクト型導電性部材”であり、下部導電性パターン120bの幅よりさらに狭い幅を持つことができる。

【0065】

図10Aないし図10Cは、図9に図示されたチップを形成する方法を示す断面図である。

【0066】

図10Aを参照すれば、チップ100は、図8Aを参照して説明した方法と実質的に同一または類似した方法によって、導電性部材170がさらに形成される点を除いては、図6Aを参照して説明した工程と実質的に同一または類似した工程により形成される。図10B及び図10Cに示したように、チップ100を形成するための工程の残りは、図6B及び図6Cを参照して説明したような実質的に同一または類似した方法である。

【0067】

図11は、さらに他の実施形態による側面パッドを持つチップを形成する方法を示す斜視図である。

【0068】

図11を参照すれば、さらに他の実施形態によるチップ100は、上部導電性パターン120a上でチップ100の側部表面150上に導電性部材180が露出された点を除いては、図9を参照して説明したチップ100と類似している。

【0069】

図示したように、導電性部材180は、チップ100の側部表面150で上部導電性パターン120aに連結されうる。したがって、チップ100は、上部導電性パターン120a上に配された導電性部材180を形成する工程により形成されうる。導電性部材180の少なくとも一部がチップ100の側部表面150上に露出され、上部導電性パターン120aに電気的に連結される。他の実施形態で、図示していないが、導電性部材180は、チップ100の側部表面150で上部導電性パターン120aに連結されずに、チップ100の内部のような他の所に連結されうる。

【0070】

一実施形態で、導電性部材180は“バー型導電性部材”であり、上部導電性パターン120aの幅と実質的に同等な幅を持つことができる。バー型導電性部材180を提供することによって、側面パッド160のコンタクト領域は、溶融度を改善してコンタクト抵抗を低下させるために大きくなりうる。他の実施形態で、導電性部材180は“コンタクト型導電性部材”であり、上部導電性パターン120aの幅より狭い幅を持つことができる。しかし、チップ100が図5Aに示したようにチップパッド130を備えることもできるということは明らかである。

【0071】

図12Aないし図12Cは、ビアパターン及び配線部材のような素子構造体と、側面パッドとの関係及び連結方式を説明するために、一部の実施形態による電気的連結及び側面パッドを示す平面図である。

【0072】

図12Aを参照すれば、たとえば図3Bに示した半導体基板102の表面と実質的に平行した平面に沿って実質的に水平方向に延びた追加的な導電性ワイヤリングパターンまたは配線部材210は、前述した側面パッド160と共に形成されうる。すなわち、導電性ワイヤリングパターン210は、側面パッド160を形成する導電性パターンを形成するために利用される工程と同じ工程で形成されうる。すなわち、たとえば、図3Bに図示された導電性ワイヤリングパターン210及び上部導電性パターン120aは、同じ工程中に層間誘電層200a内に形成されうる。その結果、各側面パッド160は、必要ならば導電性ワイヤーパターン210に電気的に連結されうる。これによって、配線レベルの数(及びこれら構成の複雑性)が、一般的に信号経路がチップ100の上部(たとえば、図1に示したチップパッド40)からトランジスタのような導電性構造体に延びる従来の半導体素子に比べて減少できる。チップ構造が多層配線部材によって非常に複雑ならば、信号遅延及び製造工程の複雑性は重大な関心事でありうる。前述したように、チップ100内の配線レベルの数を減少させることによって、チップ100内の信号経路の長さが短くなり、これによって長い信号経路による信号遅延及び配線抵抗と関連した問題が減少しうる。

【0073】

図12Bを参照すれば、導電性ビアパターン212及び側面パッド160の中間導電性パターン160a(たとえば、図5Aを参照)は、層間誘電層200bで同じ工程で形成されうる。すなわち、導電性ビアパターン212は、側面パッド160の中間導電性パターン160aを形成するために利用される同じ工程で形成されうる。一実施形態で、導電性ビアパターン212は、互いに対して垂直方向に配された少なくとも2個の導電性パターンで電気的に連結されるように形成されうる。他の実施形態で、導電性ビアパターン212は、バー型ビアパターン(すなわち、上及び/または下の導電性パターンの幅と実質的に同じ幅を持つビアパターン)またはコンタクト型ビアパターン(すなわち、上の及び/または下の導電性パターンの幅よりさらに狭い幅を持つビアパターン)として提供されうる。

【0074】

図12Cを参照すれば、たとえば図3に示した追加的な導電性ワイヤリングパターン214及び下部導電性パターン120bが他の誘電層200c内に形成されうる。これら層は同じ工程中に形成されうる。一実施形態で、一つ以上の電気的構成要素220が側面パッド160に電気的に連結されうる。その結果、配線レベルの数を減少させることができ、これによって、前述したように配線工程の複雑性を低下させることができる。

【0075】

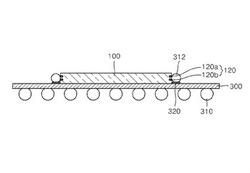

図13Aは、一実施形態によるチップを備えるパッケージの平面図である。図13B及び図13Cは、図13Aに示した線“B−B”に沿って切り取った断面図を持つ他の実施形態に関する。

【0076】

図13Aないし図13Cを参照すれば、パッケージは、たとえば、第1チップ100、回路基板300(たとえば、PCB)、複数の外部コンタクトターミナル310(たとえば、ソルダーボール)、複数の導電性配線312及び複数の第1回路基板パッド320を備えることができる。一実施形態で、回路基板300は、多層PCBまたは有機材料基板上に回路パターンを備えるフィルムパッケージ基板でありうる。回路基板300は、メモリ回路、ディスプレイまたはLDI装置のような多様な応用装置に適用されうる。回路基板300は、複数の第1回路基板パッド320を備えることができる。したがって、導電性配線312は、回路基板300上の第1回路基板パッド320のうち対応する一つに側面パッド120を電気的に連結できる。したがって、パッケージは、たとえば、複数の第1回路基板パッド320を持つ回路基板300を提供する工程、及び側面パッド120、すなわち、第1チップ100の側面パッド120上に露出された下部及び上部導電性パターン120b及び120aに導電性配線312で第1回路基板パッド320を連結する工程により形成されうる。

【0077】

一実施形態で、導電性配線312は、導電性ボール、導電性バンプ、ソルダーボール、ソルダーバンプ、ソルダーペースト、異方性導電フィルム、金属層またはこれらの組み合わせを備えることができる。図2A及び図2B、図5A、図7、図9または図11を参照して説明したように、第1チップ100が提供される。たとえば、図13Bに示したように、第1チップ100は、チップパッド130なしに、図7を参照して説明したように提供されうる。

【0078】

図13B及び図13Cに示したように、導電性配線312は、回路基板300上に形成された第1基板パッド320に第1チップ100の側面パッド120を電気的及び機械的に連結する。一実施形態で、導電性配線312は、導電性部材170の少なくとも一部と接触できる。側面パッド120を通じて第1チップ100と回路基板300とを電気的に連結することによって、チップ100の上部表面上に延びるワイヤーのような電気的配線部材、またはチップ100と回路基板300との間に配されるソルダーボールが要求されない。したがって、パッケージの厚さは、たとえば、チップ100及び回路基板300の結合された厚さと実質的に同等な程度に実質的に薄く維持されうる。したがって、パッケージの大きさが減少する。

【0079】

一側面によれば、図13Aないし図13Cに示した第1チップ100は、応用装置によって、たとえば、PCBである回路基板300に直接付着されうる。第1チップ100が回路基板300に直接付着されるならば、たとえば、接着層のような層が回路基板300と第1チップ100との間に存在する必要がない。すなわち、第1チップ100は、それらの間に何の物理的または機械的な連結なしに回路基板300上に配される。その結果、第1チップ100を備えるパッケージの厚さは、接着層のような付加層が形成される必要がないので、さらに薄くなる。しかし、チップ100と回路基板300との間に追加的な付着力を提供するために、接着層のような付加層が配されることもある。

【0080】

他の側面で、図13B及び図13Cに示したソルダーボール310は不要であり、パッケージとPCBとの間に他の公知の電気的連結形態が利用されることもある。

【0081】

図14A及び図14B、図15A及び図15B及び図16A及び図16Bは、図13に示した線“B−B”に沿って切り取ったパッケージの他の実施形態を示す断面図である。

【0082】

図13Aないし図13Cを参照して説明した導電性配線312は、実質的に球形の導電性配線として提供されうる。しかし、前記導電性配線は、チップ100と回路基板300との間に適した電気的連結を提供できるならば、実質的にいかなる形態にも提供されうる。たとえば、第1チップ100は、図14A及び図14Bに示したように、実質的に長方形導電性配線316、図15A及び図15Bに示したように実質的に三角形導電性配線318、または図16A及び図16Bに示したような凹状三角形導電性配線319などを通じて回路基板300に電気的に連結されうる。

【0083】

前記導電性配線が四角形または三角形の導電性配線を持つ場合に、導電性配線312とチップ100との接触面積は球形配線に比べてさらに大きくなり、これによって、チップ100と導電性配線312との接着力をさらに増大させることができる。三角形導電性配線318は、四角形のように他の形状を持つ導電性配線312をリップロー(replow)工程を行うことによって形成できる。図14B、15B及び16Bに示したように、導電性配線316、318及び319は、導電性部材180の少なくとも一部と接触する。

【0084】

図17Aないし図17Dは、複数のチップを備えるパッケージの実施形態を示す断面図である。

【0085】

図17Aを参照すれば、パッケージは、たとえば、図13Bを参照して説明したものと類似したパッケージである。しかし、図示された実施形態のように、第1チップ100はチップパッド130を備えることができる。したがって、第1チップ100は、図2Aを参照して説明したように提供され、チップパッド322を持つ第2チップ400は、チップパッド130とチップパッド322との対応するものの間に配される電気的配線部材または外部コンタクトターミナル314(たとえば、ソルダーボール、ソルダーペースト、異方性導電性フィルム、金属層またはこれらの組み合わせ)を通じて第1チップ100に結合されうる。したがって、パッケージは、第1チップ100の上部表面上にチップパッド130を提供する工程、第1チップ100の上に第2チップ400を提供する工程、及び外部コンタクトターミナル314で第1チップ100のチップパッド130に第2チップ400を連結する工程を行うことによって形成されうる。

【0086】

第2チップ400は、第1チップ100と同一であるかまたは異なる。たとえば、第1チップ100及び第2チップ400は、ロジック及び/またはメモリチップのように多様に提供されうる。図17Bは、第1チップ100が、図7を参照して説明したように導電性部材170を備える点を除いては、図17Aに示した実施形態と類似した他の実施形態に関するパッケージを図示する。明示的に図示してはいないが、図5Aまたは図9を参照して説明したように、第1チップ100もまた、あるいは選択的に提供されうるということは明らかである。

【0087】

図17Cを参照すれば、パッケージ、たとえば、複数の第1チップ100(たとえば、下部第1チップ100a及び上部第1チップ100b)が、図2Bを参照して前述したように提供されうる。下部第1チップ100a上には、上部第1チップ100bが配される。したがって、複数の第1チップ100が回路基板300上に互いに隣接して垂直方向に整列されうる。下部第1チップ100aの側面パッドは、図14Aを参照して説明した実質的に四角形の導電性配線316のような導電性配線部材を通じて、上部第1チップ100bの側面パッド120に電気的及び機械的に連結されうる。図17Cは、互いに積層された2個の第1チップ100を図示しているが、任意の数の第1チップ100が互いに積層され、導電性配線を通じて電気的/機械的に連結されうるということは明らかである。また、任意形状の導電性配線が積層された第1チップ100を電気的/機械的に連結するために使われうる。導電性配線(たとえば、実質的に四角形の導電性配線316)は、下部第1チップ100a及び上部第1チップ100bを電気的及び機械的に連結しているために、これらの間に接着層が挿入される必要がない。しかし、必要な場合、下部第1チップ100aと上部第1チップ100bとの間に接着層が配されうるということは明らかである。また、図17Cが、図2Bを参照して説明したように、第1チップ100を図示しているが、図2A及び図2B、図5A及び図5B、図7、図9または図11を参照して説明したように、一つ以上の第1チップ100が提供されうるということは明らかである。

【0088】

図17Dを参照すれば、パッケージは、たとえば、図11を参照して前述したように、下部第1チップ100aが提供され、図7を参照して説明したように上部第1チップ100bが提供されるという点を除いては、図17Cを参照して説明したものと類似したパッケージを提供できる。したがって、下部第1チップ100の導電性部材180は、上部第1チップ100の導電性部材170と直接接触して第1チップ100間の接触面積をさらに大きくすることができる。

【0089】

図18Aは、一実施形態による複数のチップを備えるパッケージの平面図である。図18B及び図18Cは、図18Aに図示された線“B−B”に沿って切り取ったパッケージの実施形態を示す断面図である。図19は、他の実施形態によって複数のチップを備えるパッケージを示す平面図である。

【0090】

図18A及び図18Bを参照すれば、パッケージは、たとえば、図13Bを参照して説明したものと類似したパッケージを提供できる。図18Cを参照すれば、パッケージは、図13Cを参照して説明したものと類似している。しかし、図示された実施形態で、複数の第1チップ100は、回路基板300上で互いに隣接して水平方向に整列されうる。また、複数の第1チップ100は、複数の導電性配線312を通じて回路基板300に電気的及び機械的に連結されるだけでなく、互いに電気的及び機械的に連結されることもある。すなわち、前記パッケージは、回路基板300上に複数の第1チップ100を提供する工程、及び第1チップ100のうちいずれか一つのチップの側部表面150上に露出された下部及び上部導電性パターン120b及び120a(すなわち、側面パッド120)の一部と、第1チップ100のうち他の一つの側部表面150上に露出された下部及び上部導電性パターン120b及び120a(すなわち、側部パッド120)の一部とを導電性配線312に連結させる工程により形成される。したがって、一実施形態で各導電性配線312は、第1チップ100のうちいずれか一つの側部表面150上に露出された下部及び上部導電性パターン120b及び120aの一部を、第1チップ100のうち他の一つの側部表面150上に露出された下部及び上部導電性パターン120b及び120aの一部に連結する。一実施形態で、第1チップ100のうち隣接するものの側部表面150は互いに離隔し、導電性配線312により電気的に連結されることもある。その結果、前記パッケージの大きさ(幅)は、導電性配線312が第1チップ100それぞれにより共通使用されるために縮小する。また、それぞれの第1チップ100内の回路は、パッケージの全体サイズを縮小させるように共有されうる。

【0091】

第1チップ100は、任意の数そして任意の配列に提供されうるということは明らかである。たとえば、図19を参照すれば、パッケージには、複数の導電性配線312により互いに電気的及び機械的に連結された4個の第1チップ100が提供されうる。したがって、チップ及びパッケージのサイズは、これらが導電性配線312とこれらの間の内部回路とを共有することによってさらに縮小する。一実施形態で、導電性配線312は、導電性バンプ、ソルダーボール及び固形化されたソルダーペーストのうち少なくとも一つを備えることができる。

【0092】

図20Aは、さらに他の実施形態によるチップを備えるパッケージの平面図である。図20B及び図20Cは、図20Aに図示された線“D-D”に沿って切り取った断面図をそれぞれ示す。図21Aは、さらに他の実施形態によるチップを備えるパッケージの平面図である。図21Bは、一実施形態による図21Aに図示された線“E−E”に沿って切り取った断面図である。図22Aないし図23Cは、他の実施形態によるチップを備えるパッケージの平面図である。

【0093】

図20A及び図20Bを参照すれば、たとえば、パッケージは、図13Bを参照して説明したものと類似したパッケージである。図20Cを参照すれば、たとえば、パッケージは、図13Cを参照して説明したものと類似したパッケージである。しかし、図示された実施形態で、第1チップ100は、その上部表面上に形成されたチップパッド130をさらに備えることができ、回路基板300は、第2回路基板パッド332をさらに備えることもできる。したがって、電気的配線部材330(たとえば、ボンディングワイヤー)は、チップパッド130のうち対応する一つに第2回路基板パッド332を電気的に連結させることができる。すなわち、パッケージは、第1チップ100の上部表面上にチップパッド130を提供する工程、及び少なくとも一つの電気的配線部材330で第2チップ基板パッド332をチップパッド130に連結する工程によって形成される。

【0094】

図20Aないし図20Cに図示された実施形態は、それぞれ多数の入/出力パッドを備え、それにより、高速ICまたは高集積メモリチップのような応用装置に使われうる。図20Aないし図20Cは、複数のチップパッド130が第1チップ100のあらゆる側壁に沿って配されたパッケージを図示している。ワイヤー330は、各チップパッド130を対応する第2回路基板パッド332に電気的に連結させる。チップパッド130(及びワイヤー330)は任意の数ほど、そして任意の配列で提供されうるということは明らかである。たとえば、図21A及び図21Bを参照すれば、側面パッド120が第1チップ100の各側部表面150に提供されるが、パッケージのチップパッド130は、第1チップ100の側部の一部分に沿って配される。図21Bに図示された第1チップ100が図7を参照して説明されたが、第1チップ100は、たとえば、図2B、図5Bまたは9を参照して説明したように提供されることもある。

【0095】

図22Aないし図22Cを参照すれば、チップパッド130は、第1チップ100の一つ以上の側部に沿って配されうる。図20Aないし図20C、図21A、図22A及び図22Bは、複数の導電性配線312と側面パッド120とが第1チップ100のあらゆる側部に沿って配されるパッケージを図示しているが、導電性配線312及び側面パッド120は任意の数及び配列で提供されうるということは明らかである。たとえば、図22Cを参照すれば、パッケージは、第1チップ100の対向する一対の側部に沿って配される複数の導電性配線312及び側面パッド120を備えるように提供されうるということは明らかである。また、図22Cに図示されたパッケージは、第1チップ100の一つの側部上にのみ配されるようにチップパッド130を備えることもできる。

【0096】

図23Aは、さらに他の実施形態によるチップを備えるパッケージの平面図である。図23B及び図23Cは、図23Aに図示された線“F−F”に沿って図示された断面図である。

【0097】

図23A及び23Bを参照すれば、パッケージは、たとえば、図13Bを参照して説明したものと類似したパッケージでありうる。図23Cを参照すれば、パッケージは、たとえば、図23Bに図示されたものと類似したパッケージであるが、図11を参照して説明したような第1チップ100を備えるか、本明細書に開示された他の適切なチップを備えることもできる。一実施形態で、図23Cに図示された導電性配線316は、導電性部材180の少なくとも一部と接触できる。しかし、図示された実施形態で、第1チップ100は、下部表面に配されたチップパッド130を備えることもある。したがって、第1チップ100の側面パッド120は、図14A及び図14Bに示したように、複数の実質的に四角形の導電性配線316を通じて第1回路基板パッド320に電気的に連結され、チップパッド130は、電気的配線部材314、たとえば、導電性ボール、導電性バンプ、ソルダーボール、ソルダーバンプ、ソルダーペースト、異方性導電性フィルム、金属層またはこれらの組み合わせを通じて回路基板300上に配された第2回路基板パッド340に電気的に連結されることもある。すなわち、パッケージは、第1チップ100の下部表面上にチップパッド130を提供する工程、及びチップパッド130に少なくとも一つの電気的配線部材314を使用して第2回路基板パッド340を連結する工程により形成されうる。

【0098】

前記実施形態によれば、側面パッドは、チップの側部表面上に露出される。前記チップの側部表面上に前記側面パッドを提供することによって、導電性構造体と外部装置との間の信号経路の長さが短くなる。前記信号経路の長さが短くなることで、信号遅延と関連した問題点が減少できる。また、電源または接地金属配線が多少遠距離に配されるチップ100の上部に配されるチップパッド130の代りに、近くに位置する側面パッド120に連結されうるために、ボンディングパッドと、電源または接地金属配線との間の配線部材が減少できる。

【0099】

また、チップ上に側面パッドを提供することによって、チップを備えるパッケージの全体厚さが薄くなる。また、チップの側部表面上に側面パッドを備えることによって、トランジスタまたは抵抗のような多様な電気的構成要素を連結するための配線部材の設計が、従来技術に比べればかなり容易になりうる。また、図12Aないし図12Cに示したような側面パッドを使用することによって、電源または接地ラインのための金属配線ルーティングのデザインがさらに融通性を持つことができる。

【0100】

一部の実施形態によれば、当業者は、本明細書でこのようなあらゆる組み合わせが開示されていないにもかかわらず、本明細書に開示されたパッケージが側面パッドを持つ多様な半導体チップを備えるということが容易に理解できるであろう。

【0101】

本発明の実施形態は、特定実施形態に係り、これについて開示したが、当業者ならば特許請求範囲の請求項により限定されたように、本発明の思想及び範ちゅうを外れずに形態及び細部事項において多様な変形が可能であるということが理解できるであろう。

【産業上の利用可能性】

【0102】

本発明は、半導体関連の技術分野に好適に用いられる。

【図面の簡単な説明】

【0103】

【図1】従来のパッドを持つ複数の従来のチップを備える従来のウェーハを示す斜視図である。

【図2A】本発明の一実施形態による側面パッドを持つチップの斜視図である。

【図2B】本発明の一実施形態による側面パッドを持つチップの斜視図である。

【図3A】ウェーハ上に配されたチップ内に提供されたパッドの配列を示す平面図である。

【図3B】図3Aに図示された線“A−A”に沿って切り取った断面図である。

【図4A】図2Aに図示されたチップを形成するための一実施形態を示す断面図である。

【図4B】図2Aに図示されたチップを形成するための一実施形態を示す断面図である。

【図4C】図2Aに図示されたチップを形成するための一実施形態を示す断面図である。

【図5A】本発明の他の実施形態による側面パッドを持つチップを示す斜視図である。

【図5B】本発明の他の実施形態による側面パッドを持つチップを示す斜視図である。

【図6A】図5Aに図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図6B】図5Aに図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図6C】図5Aに図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図7】本発明のさらに他の実施形態による側面パッドを持つチップを示す斜視図である。

【図8A】図7に図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図8B】図7に図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図8C】図7に図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図9】本発明のさらに他の実施形態による側面パッドを備えるチップを示す斜視図である。

【図10A】図9に図示されたチップを形成するための本発明の一実施形態による製造方法を説明する断面図である。

【図10B】図9に図示されたチップを形成するための本発明の一実施形態による製造方法を説明する断面図である。

【図10C】図9に図示されたチップを形成するための本発明の一実施形態による製造方法を説明する断面図である。

【図11】本発明の他の実施形態による側面パッドを持つチップを形成するための製造方法を説明する斜視図である。

【図12A】本発明の実施形態による電気的接続及び側面パッドを示す平面図である。

【図12B】本発明の実施形態による電気的接続及び側面パッドを示す平面図である。

【図12C】本発明の実施形態による電気的接続及び側面パッドを示す平面図である。

【図13A】本発明の一実施形態によるチップを備えるパッケージを示す平面図である。

【図13B】図13Aに図示された線“B−B”に沿って切り取った他の実施形態による断面図である。

【図13C】図13Aに図示された線“B−B”に沿って切り取った他の実施形態による断面図である。

【図14A】図13Aに図示された線“B−B”に沿って切り取った他の実施形態によるパッケージを示す断面図である。

【図14B】図13Aに図示された線“B−B”に沿って切り取った他の実施形態によるパッケージを示す断面図である。

【図15A】図13Aに図示された線“B−B”に沿って切り取ったさらに他の実施形態によるパッケージを示す断面図である。

【図15B】図13Aに図示された線“B−B”に沿って切り取ったさらに他の実施形態によるパッケージを示す断面図である。

【図16A】図13Aに図示された線“B−B”に沿って切り取ったさらに他の実施形態によるパッケージを示す断面図である。

【図16B】図13Aに図示された線“B−B”に沿って切り取ったさらに他の実施形態によるパッケージを示す断面図である。

【図17A】本発明の実施形態による複数のチップを備えるパッケージを示す断面図である。

【図17B】本発明の実施形態による複数のチップを備えるパッケージを示す断面図である。

【図17C】本発明の実施形態による複数のチップを備えるパッケージを示す断面図である。

【図17D】本発明の実施形態による複数のチップを備えるパッケージを示す断面図である。

【図18A】本発明の一実施形態による複数のチップを備えるパッケージを示す平面図である。

【図18B】図18Aに図示された線“B−B”に沿って切り取った本発明の実施形態によるパッケージを示す断面図である。

【図18C】図18Aに図示された線“B−B”に沿って切り取った本発明の実施形態によるパッケージを示す断面図である。

【図19】本発明の他の実施形態による複数のチップを備えるパッケージを示す平面図である。

【図20A】本発明の他の実施形態によるチップを備えるパッケージを示す平面図である。

【図20B】本発明の一部の実施形態によって、図20Aに図示された線“D−D”に沿って切り取った断面図である。

【図20C】本発明の一部の実施形態によって、図20Aに図示された線“D−D”に沿って切り取った断面図である。

【図21A】本発明のさらに他の実施形態によるチップを備えるパッケージを示す平面図である。

【図21B】本発明の一実施形態による図21Aに図示された線“E−E”に沿って切り取った断面図である。

【図22A】本発明の他の実施形態によるチップを備えるパッケージの平面図である。

【図22B】本発明の他の実施形態によるチップを備えるパッケージの平面図である。

【図22C】本発明の他の実施形態によるチップを備えるパッケージの平面図である。

【図23A】本発明のさらに他の実施形態によるチップを備えるパッケージの平面図である。

【図23B】本発明の一部の実施形態による図23Aに図示された線“F−F”に沿って切り取った断面図である。

【図23C】本発明の一部の実施形態による図23Aに図示された線“F−F”に沿って切り取った断面図である。

【符号の説明】

【0104】

100 チップ、

120 側面パッド、

120a 上部導電性パターン、

120b 下部導電性パターン、

300 回路基板、

310 外部コンタクトターミナル、

312 導電性配線、

320 第1回路基板パッド。

【技術分野】

【0001】

本発明は半導体チップ、その製造方法及びパッケージに係り、さらに詳細には側面パッドを備えるチップ、その製造方法及びそのチップを利用したパッケージに関する。

【背景技術】

【0002】

電子製品の大きさが益々小型化されその容量が増大するにつれて、前記電子製品内の半導体パッケージも小型でありつつも高容量を持つように製造されることが必要になった。図1は、従来の製造方法によって製造された複数のチップ10を持つ従来のウェーハの断面図である。

【0003】

図1を参照すれば、従来のチップ10のうち一つは、その上部表面20上に複数のチップパッド40を持ち、上部表面20は、多様な電気的構成要素が形成される活性面である。チップパッド40を通じて、チップ10内に形成された電気的構成要素と外部装置(図示せず)との間に信号が伝送される。

【0004】

しかし、性能上の要求、メモリキャパシタ、半導体パッケージの集積化及び小型化が進むほど、チップパッド40の密度は必然的に増大する。その結果、上部表面20上にチップパッド40を適切に形成することはさらに難しくなっている。たとえば、再配線パターンが占有できる上部表面20の可用面積に対する制限によって、上部表面20上に前記再配線パターンを適切に形成することはさらに難しくなっている。

【0005】

最近、チップ10は、ボンディングワイヤーまたはソルダーボールのような外部接続端子を使用して下地回路基板(図示せず)に電気的に結合される。前記ボンディングワイヤーを使用する場合に、チップパッド40が上部表面20上に配され、前記ボンディングワイヤーがチップパッド40と前記回路基板上のボンドフィンガーのような基板パッドとの間に結合されるように、前記チップ10が配される。前記ソルダーボールを使用する場合に、チップ10は、フリップ接触されてチップパッド40が上部表面20の下部に配され、ソルダーボールは、チップパッド40と前記回路基板上の基板パッドとの間に結合される。

【0006】

下地の回路基板にチップ10をワイヤーボンディングする時に、前記ボンディングワイヤーはチップ表面20上へ延びる。一方、チップ10がソルダーボールを使用して下地の回路基板に結合される時には、前記ソルダーボールは、チップ10と前記回路基板との間の距離を大きくさせる。いずれの場合にも、製造された半導体パッケージの厚さは、実質的にチップ10と前記回路基板との結合された厚さよりかなり厚くなる。本発明は、このような従来技術が持つ多様な問題点を解決するためのものである。

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、ボンディングパッドの全体数がかなり増加してもチップのサイズを大きくせずにボンディングパッドを容易に収容でき、かつチップのサイズが同じ場合にボンディングパッドの数を低減させうる半導体チップ、その製造方法及びパッケージ、さらに詳細には側面パッドを備えるチップ、その製造方法及び前記チップを利用したパッケージを提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一実施形態による半導体装置は、上部表面、下部表面及び前記上部表面と前記下部表面とに連結された側部表面を持つ第1チップを備える。前記第1チップは、チップ基板、前記チップ基板上の下部導電性パターン、前記下部導電性パターン上の層間誘電層及び前記層間誘電層上の上部導電性パターンを備える。前記下部導電性パターンの少なくとも一部及び前記上部導電性パターンの少なくとも一部は、集合的に側面パッドを形成するように、前記第1チップの前記側部表面上に露出されうる。

【0009】

本発明の他の実施形態による半導体装置の製造方法は、上部表面、下部表面及び前記上部表面と前記下部表面とに連結された側部表面を持つ第1チップを備える。前記第1チップは、チップ基板を提供する工程、前記チップ基板上に下部導電性パターンを形成する工程、前記下部導電性パターン上に層間誘電層を形成する工程、及び前記層間誘電層上に上部導電性パターンを形成する工程により提供される。前記下部導電性パターンの少なくとも一部及び前記上部導電性パターンの少なくとも一部は、集合的に側面パッドを形成するように、前記第1チップの前記側部表面上に露出されうる。

【発明の効果】

【0010】

本発明による側面パッドを使用すれば、ボンディングパッドの全体数がかなり増加しても、チップのサイズを増大させずにボンディングパッドを容易に収容できる。すなわち、本発明の実施形態によれば、同じチップサイズでもチップパッドの全体数がかなり増加できる。

【発明を実施するための最良の形態】

【0011】

以下に、図面を参照して、本発明の多様な実施形態について詳細に説明する。しかし、これら実施形態は多くの他の形態に変形して実施することができ、本明細書で説明した実施形態に制限されるものと解釈されてはならない。これらの実施形態は本発明の開示をさらに完全にして当業者に本発明の思想を十分に理解できるようにするために提供されたものである。図面で、層及び領域の厚さは説明の明確性のために誇張されている。また、本明細書全体で、同じ構成要素は同じ参照番号により参照される。

【0012】

図2A及び図2Bは、実施形態による側面パッドを持つチップの斜視図である。

【0013】

図2Aを参照すれば、図示されたチップ100は、ロジックチップ、メモリチップなど、またはシステムオンチップ(SOC)のようなものの複合機能を持つチップである。たとえば、実施形態によれば、チップ100は、上部表面140、上部表面140に対向する下部表面(図示せず)及び上部表面140と前記下部表面とに連結された複数の側部表面150を備える。図2Aで、チップ100は、4つの側部表面150を持つことが図示されている。しかし、チップ100は、本発明の思想及び範囲内であれば任意の数の側部パッドを持っていてもよい。たとえば、チップ100は、少なくとも3つの側部表面150のみを持つ必要もある。後述するように、チップ100内に一般的に形成される配線部材及び/またはビアパターンを形成するための一つ以上の導電層(本明細書で導電性パターンと称することもある)を使用して、複数の側部表面150のうち少なくとも一つ以上の側部表面150上に複数の側面パッド120が形成される。

【0014】

チップ100は、チップ基板または半導体基板(図2Aには図示していないが、図3Bには図示する)を備える。Al、Cu、W、Mo、TiN、TaNまたはWNのような導電性金属窒化物のような材料を含む導電性パターンが複数の側面パッド120を形成するように側部表面150を通じて露出される。一実施形態で、チップ100はまた、前記チップ基板上に下部導電性パターン120b、下部導電性パターン120b上に層間絶縁層(たとえば、図4Cの110)及び前記層間絶縁層上に上部導電性パターン120aを備える。

【0015】

一実施形態で、下部導電性パターン120bの少なくとも一部及び/または上部導電性パターン120aの少なくとも一部は、チップ100の側部表面150のうち少なくとも一つの側部表面150上に露出されて、側面パッド120を形成する。たとえば、上部導電性パターン120aの少なくとも一部が、チップ100の上部表面140と下部導電性パターン120bとの間に垂直方向に配される。具体的には、チップ100の側部表面150上に露出された上部導電性パターン120aの一部は、チップ100の側部表面150上に露出された下部導電性パターン120bの一部とチップ100の上部表面140との間に配される。

【0016】

側面パッド120は、2個の導電性パターンを備えているものが図示されているが、側面パッド120は、任意の数の導電性パターン、すなわち、一つ以上の導電性パターンを持つことができることは明らかである。しかし、側面パッド120のために2つ以上の導電性パターンが、側面パッド120と、たとえば、図13Bに図示された導電性配線312のようなコンタクトターミナルとの間のコンタクト抵抗を低減させ、側面パッド120とコンタクトターミナルとの整列マージンを増大させるためには効果的である。また、2以上の導電性パターンの場合、側面パッド120と前記コンタクトターミナルとの間の溶融度を改善させることができる。

【0017】

上部導電性パターン120aと下部導電性パターン120bとの幅及び厚さは、チップの形状、パッケージの種類及びチップ100内の電気的構成要素を形成するための製造工程のような要因により決定される。

【0018】

また、側面パッド120は、チップ100の複数の側部表面150と実質的に同一平面上にあるか、これらから突出してもよい。選択的には、側面パッド120は適用製品によってチップ100の側部表面150からリセスされることもある。

【0019】

一実施形態によれば、上部導電性パターン120aと下部導電性パターン120bとの間に誘電材料が配される。後述するように、上部導電性パターン120aと下部導電性パターン120bとの間に付加的な導電性パターンが配されることもある。

【0020】

図2Aに説明された一実施形態で、チップパッド130は、チップ100の上部表面140上に配される。チップパッド130は、電気的導電性配線構造(図示せず)により導電性構造104(図3B)及び/または導電性パターン108(図3B)に電気的に連結される。しかし、チップ100は、チップパッド130を備えなくてもよいことは明らかである。このような実施形態は、図2Bに図示されている。

【0021】

図3Aは、チップ100内に提供されたパッドの配置を示す平面図である。図3Bは、図3Aに図示された線“A−A”に沿って切り取った断面図である。

【0022】

図3A及び図3Bを参照すれば、複数のチップ100は、一般的に従来の製造方法により同じ基板“a”(たとえば、半導体基板)上に共に形成される。チップ領域内に複数のチップ100が形成される。基板上でチップ領域は当該技術分野で公知のように実質的に均一な幅を持つダイシング領域(すなわち、スクライブラインSLで指示された領域)だけ互いに離隔される。各チップ100は、複数の導電性パターン108を備えることができる。各導電性パターン108の第1部分は、チップ100により占有された基板の領域上に配され、各導電性パターン108の第2部分は前記ダイシング領域、すなわち、スクライブラインSLにより占有された基板の領域上に配される。導電性パターン108の端部の断面図は、四角形を限定する点線により指示されている。

【0023】

図3Bを参照すれば、各チップ100は、たとえば、半導体基板(本明細書で102で例示される)上に形成された導電性構造体104、第1層間誘電層106及び前述した導電性パターン108を備える。一実施形態で、導電性構造体104は、たとえば、セルトランジスタ、コアトランジスタ、ペリフェラルトランジスタ、ストレージキャパシタまたはこれらの組み合わせのような電気的構成要素を含む。他の実施形態で、導電性構造体104は、配線、コンタクトまたはこれらが組み合わせられたもののような他の構造体を備えることができ、これらは電気的構成要素に結合されうる。一実施形態で、第1層間誘電層106は、たとえば、酸化物(たとえば、SiO2)、低誘電率(low−k)物質(たとえば、SiCOH)またはこれらの組み合わせを含む。

【0024】

図3Bにさらに詳細に図示されているように、チップ100は、たとえば、複数の導電性パターン108として、上部導電性パターン108a及び下部導電性パターン108bを備えることができる。

【0025】

実施形態によれば、前記導電性パターンは、ビットラインまたはメモリ素子のセル領域、メモリ素子のペリフェラル領域または当該技術分野で公知の他の電気的構成要素またはこれらの組み合わせに連結された配線でありうる。一実施形態で、側面パッドを形成するための導電性パターンは、ビットラインが形成された後に形成されることもある。実施形態によれば、導電性パターン108は、ビアパターン、ダミーライン、ダミートランジスタのようなトランジスタまたはこれらの組み合わせでありうる。したがって、ダミートランジスタの一部だけでも、たとえば、図2Aに示したように、側面パッド120を形成するために使われる。上部導電性パターン108a及び下部導電性パターン108bの一部は、スクライブラインSLにより表示された半導体基板102の領域上へ延びる。上部導電性パターン108aの厚さまたは下部導電性パターン108bの厚さは、少なくとも約1μm以上である。望ましくは、上部導電性パターン108a及び下部導電性パターン108bの厚さは、約1μmないし約2μmである。しかし、本発明は、このような特定厚さ範囲に制限されず、図13Bに示したように導電性配線部材312と接触するのに十分なコンタクト面積を持つ側面パッド120を提供するかぎり、上部導電性パターン108a及び下部導電性パターン108bを結合した任意の厚さが許容されうる。

【0026】

また、上部導電性パターン108a及び下部導電性パターン108bは、配線のような他の素子構造物を形成する間に形成される。たとえば、従来の配線及び側面パッド120用導電性パターン108は、前記配線を形成するためのマスクに付加的なパターンを追加するだけでも同一工程で形成されうる。したがって、上部導電性パターン108a及び下部導電性パターン108bを形成するための付加的なマスクは省略できる。したがって、本発明は付加的なコストなしでも実施できる。

【0027】

第2層間誘電層110は、上部導電性パターン108aと下部導電性パターン108bとの間に配され、第3層間誘電層112は下部導電性パターン108b上に配される。

【0028】

一般的に、電力と接地配線と(たとえば、図1に示したような)チップパッドとの間に多層配線レベルが要求され、前記チップパッドは、チップ100の上部上に形成されうる。また、前記多層配線レベルは、チップパッド130と、セルトランジスタ、コアトランジスタ、ペリフェラルトランジスタ、ストレージキャパシタのような下地の導電性構造体との間で要求されることもある。また、従来技術のように、前記電源または接地配線が、抵抗及び干渉を考慮して単一パッドよりは複数のチップパッド130に連結された場合、電力または接地のための配線経路は一般的に非常に複雑であるか長い。各配線レベルは前記配線レベルの長さに比例して信号遅延を生じさせる電気抵抗を伴う。

【0029】

しかし、前述したように、側面パッド120を提供することによって、前記電源または接地配線または信号ラインがチップ100の上部上に配されるチップパッド130を通じる必要がなく、従来技術よりさらに短い経路で側面パッド(ボンディングパッド)120に連結されるので、配線レベルの数及び配線の長さはかなり減少する。その結果、電気抵抗及び信号遅延はだいぶ減少する。また、側面パッド120の提供により、導電性構造体と外部信号ソース(たとえば、電源ソース、接地、通常の信号ソースなど)との間の信号経路の複雑性が低下する。本発明の一部の実施形態によるこのような特徴は、図12Aないし図12Cを参照してさらに詳細に説明する。

【0030】

図4Aないし4Cは、図2に図示されたチップを形成する方法を説明するための断面図である。

【0031】

図2Aに図示されたチップの形成方法は、一般的に上部表面140、下部表面(図示せず)及び上部表面140及び前記下部表面に連結された側部表面150を持つチップ100を形成する工程を有するという特徴を持つ。

【0032】

図4Aを参照すれば、チップ100は、当該技術分野で公知のように、半導体基板またはチップ基板102を提供する工程、半導体基板102上に導電性構造体104を形成する工程により形成される。前述したように、一実施形態で、導電性構造体104は、たとえば、セルトランジスタ、コアトランジスタ、ペリフェラルトランジスタ、ストレージキャパシタなどまたはこれらの組み合わせのような電気的構成部材を備えることができる。他の実施形態で、導電性構造体104は、前記電気的構成部材に結合されうる配線、コンタクトまたはこれらの組み合わせのような導電性構造体を備えることができる。

【0033】

次いで、第1層間誘電層106は、半導体基板102及び導電性構造体104を備える結果物上に形成される。一実施形態で、第1層間誘電層106は、電気絶縁物質をコーティングする工程、及びたとえば、機械化学的研磨工程(Chemical Mechanical Polishing:CMP)により前記電気絶縁物質の上部表面を平坦化する工程により形成される。一実施形態で、前記電気絶縁物質は、たとえば、酸化物(たとえば、SiO2)、低誘電率物質(たとえば、SiCOH)など、またはこれらの組み合わせを含むことができる。

【0034】

図4Bを参照すれば、導電性パターン108は、第1層間誘電層106上に形成される。一実施形態で、導電性パターン108は、連続的に第1層間誘電層106上に下部導電性パターン108bを形成する工程、下部導電層パターン108b上に第2層間誘電層110を形成する工程、及び上部導電層パターン108a上に第3層間誘電層112を形成する工程により形成される。

【0035】

一実施形態で、第2層間誘電層110及び第3層間誘電層112は、第1層間誘電層106が形成された方法と実質的に同一または類似した方法で形成されうる。上部導電性パターン108a及び下部導電性パターン108bは、下地の層間誘電層上に導電性物質を蒸着する工程、及び各導電性パターン108の少なくとも一部が半導体基板102のスクライブラインSLにより占有された領域上に配されるように、前記導電性物質をパターニングする工程により形成されうる。各導電性パターン108は、チップ100内の一つ以上の導電性パターン108に電気的に連結されうる。

【0036】

簡単に言えば、チップ100は半導体基板またはチップ基板102を提供する工程、前記チップ基板102上に下部導電性パターン102bを形成する工程、下部導電性パターン120b上に層間誘電層を形成する工程、及び前記層間誘電層上に上部導電性パターン120aを形成する工程により形成されうる。下部導電性パターン120bの少なくとも一部と上部導電性パターン120aの少なくとも一部とがチップ100の側部表面上に露出されて、集合的に側面パッド120を形成できる。下部導電性パターン108a及び上部導電性パターン108bは、他の素子または配線部材構造体が前述した方法と後述する方法のように形成される間に形成される。

【0037】

導電性パターン108を形成する工程の後に、チップパッド130は、従来の技術を使用して第3層間誘電層112上に形成されうる。前述したように、チップパッド130は、導電性構造104及び/または導電性パターン108のうちいずれか一つに電気的に連結されうる。したがって、チップパッド130は、側部パッド120に電気的に連結されうる。

【0038】

実施形態によれば、導電性パターン108は、ビットライン、メモリ素子のセルまたは周辺領域に結合される配線、ビアパターン、ダミーライン、トランジスタまたはこれらの組み合わせの形成に利用される工程と同じ方法により形成されうる。したがって、図3Bを参照して説明したように、追加的なフォトレジストパターンを形成するために利用される別途の工程が要求されない。

【0039】

図4Cを参照すれば、隣接するように配されたチップ100は、たとえば、レーザーまたは従来のダイアモンドカッターまたはダイアモンドソウ(saw)を使用して、スクライブラインSLに沿って、たとえば、ダイシング工程を行うことにより互いに個別化される。チップ100を個別化する時に、スクライブラインSLにより占有された半導体基板102の領域上に各導電性パターン108の一部が除去される。前記ダイシング工程の後に、チップ100内に残留する各導電性パターン108の一部が側面パッド120の一部を限定する。したがって、前記ダイシング工程の後に、チップ100内に残る下部導電性パターン108bの一部は、たとえば、図2A及び図2Bに示したような側面パッド120の一部を限定する下部導電性パターン120bを形成する。同様に、前記ダイシング工程後に、チップ100内に残る上部導電性パターン108aの一部は、側面パッド120の上部導電性パターン120aを形成する。以後、選択的には、導電性配線312とさらによく連結されるように、側面パッド120が露出されるチップの側部表面を研磨または滑らかにすることができる。

【0040】

簡単に言えば、チップ100は、ダイシング領域により離隔された複数のチップ領域を持つ半導体基板102を提供する工程、半導体基板102上にそして少なくとも一つのチップ領域内に下部導電性パターン108bを形成する工程、下部導電性パターン108b及び前記ダイシング領域上に層間誘電層110を形成する工程、及び下部108b及び上部導電性パターン108aのうち少なくとも一つが前記ダイシング領域に延長されるように、層間誘電層110及び前記少なくとも一つのチップ領域上に上部導電性パターン108aを形成する工程、及び前記ダイシング領域から前記チップ領域を分離する工程を行うことによって形成される。したがって、チップ100がスクライブラインSLで半導体基板をダイシングすることによって個別化される場合に、それによって、側部表面上に層間誘電層110を通じて露出された下部導電性パターン108の端部は側面パッド120を限定する。

【0041】

チップ100を個別化する工程の前に、半導体基板102上にパッシベーション層(図示せず)が形成されうる。このような実施形態で、前記パッシベーション層は第3層間誘電層112及びチップパッド130上に形成され、開口(たとえば、従来のフォトリソグラフィ工程により)が前記パッシベーション層内に形成されて、チップパッド130を露出させることができる。

【0042】

図5A及び図5Bは、他の実施形態による側面パッドを持つチップを示す斜視図である。

【0043】

図5Aを参照すれば、他の実施形態によるチップ100は、図2Aを参照して説明したチップ100と類似している。図5Aに図示されたチップ100の側面パッド160は、図2Aに図示された側面パッド120と類似しているが、上部導電性パターン120aと下部導電性パターン120bとの間に中間導電性パターン160aをさらに備えている点が異なっている。

【0044】

一実施形態で、中間導電性パターン160aは、上部導電性パターン120a及び下部導電性パターン120bに電気的に連結されうる。中間導電性パターン160aの少なくとも一部がチップ100の側部表面150上に露出されうる。一実施形態で、中間導電性パターン160aは“バー型導電性パターン”であり、上部導電性パターン120a及び/または下部導電性パターン120bの幅と実質的に同じ幅を持つことができる。一態様によれば、断面を見る時、前記バー型導電性パターンの場合には、長さに対する幅の比が約1:2でありうる。バー型中間導電性パターン160aを提供することによって、側面パッド160のコンタクト面積は改善された溶融度及び低下したコンタクト抵抗を確保するために大きくなりうる。しかし、他の実施形態で、中間導電性パターン160aは“コンタクト型導電性パターン”であり、上部導電性パターン120a及び/または下部導電性パターン120bの幅よりさらに狭い幅を持つことができる。前記コンタクト型パターンは、他のレベルの金属配線を連結する一般的なビアパターンの形状を持つことができる。

【0045】

さらに他の実施形態で、中間導電性パターン160aは、チップ100の側部表面150から隠蔽されることもある。したがって、上部導電性パターン120a及び下部導電性パターン120bの露出された部分は、必ずしも側部表面150だけではなくチップ100の他の内部に電気的に結合されることもある。しかし、チップ100がチップパッド130を備えないこともあるということは明らかである。図5Bにこの実施形態を例示した。

【0046】

図6Aないし図6Cは、図5Aに示したようなチップを形成するための方法を示す断面図である。

【0047】

図6Aを参照すれば、たとえば、半導体基板102上に導電性構造体104を形成する工程を含む方法によって、チップ100が形成されることもある。一実施形態で、導電性構造体104は、図4Aを参照して既述した導電性構造体104と実質的に同一または類似している。次いで、第1層間誘電層106は、半導体基板102及び導電性構造体104を備える結果物上に形成されうる。次いで、第1層間誘電層106上には、たとえば、下部導電性パターン108bのような導電性パターンが形成され、図4Bを参照して説明したものと実質的に同一または類似した方法で、下部導電性パターン108b上に第2層間誘電層110が形成されうる。以後、第2層間誘電層110内に下部導電性パターン108bの少なくとも一部を露出するように、開口が限定されうる。一実施形態で、前記開口は、下部導電性パターン108bの幅よりさらに小さく、これによって、コンタクト型導電性パターンを形成する工程を連続的に行うことを容易にする。他の実施形態で、前記開口は下部導電性パターン108bの幅と実質的に同一であり、これによって、バー型導電性パターンを形成する工程を連続的に行うことを容易にする。一実施形態で、前記開口を限定するために、従来の写真エッチング技術を使用して第2層間誘電層110の一部が除去される。前記開口内に中間導電性パターン152aが形成されうる。

【0048】

図6Bを参照すれば、以後、他の導電性パターン、たとえば上部導電性パターン108aが第2層間誘電層110と中間導電性パターン152aの上に形成され、次いで、上部導電性パターン108a上に第3層間誘電層112を形成する工程を行う。中間導電性パターン152aの幅及び上部導電性パターン108aの幅は、実質的に同一でありえる。しかし、必ずしも同一である必要はない。

【0049】

他の素子構造体が形成されながら、層間導電性パターン152aが形成される。たとえば、従来の半導体製造工程の間に、ビアパターンが形成されながら中間導電性パターン152aが形成される。したがって、前記ビアパターンを形成するためのフォトマスクに中間導電性パターン152aが追加されるので、中間導電性パターン152aを形成するための追加的なマスクは必要ない。したがって、中間導電性パターン152aを形成するための追加的なフォトリソグラフィ工程は必要ない。

【0050】

一実施形態で、第2層間誘電層110及び第3層間誘電層112は、第1層間誘電層106が形成されるのと同一または類似した方法で形成されうる。一実施形態で、上部導電性パターン108a及び下部導電性パターン108bは、図4Bを参照して説明した方法と実質的に同一または類似した方法で形成されうる。

【0051】

一実施形態で、第2層間絶縁層110内に限定された開口内に導電性物質を蒸着する工程及び前記開口外部の前記導電性物質の一部を選択的に除去する工程を行うことによって、中間導電性パターン152aが形成されうる。したがって、第2層間絶縁層110内に限定された開口の幅によって、前述したような導電性ビアパターンまたは導電性コンタクトとして、中間導電性パターン152aが提供されうる。

【0052】

導電性パターン108a上に第3層間誘電層112を形成する工程の後に、第3層間誘電層112上にチップパッド130が形成されうる。一実施形態で、チップパッド130は、図4Bを参照して説明したチップパッド130と実質的に同一または類似している。

【0053】

図6Cを参照すれば、以後、チップ100は、図4Cを参照して説明した方法と実質的に同一または類似した方法で互いに個別化されうる。したがって、チップ100の個別化工程時に、スクライブラインSLが占める半導体基板102の領域上に配される中間導電性パターン152aの一部が除去される。ダイシング工程後に、チップ100内に残っている各中間導電性パターン152aの一部は、側面パッド160を形成する中間導電性パターン160aを形成する。したがって、前述した方法によれば、下部導電性パターン120b及び上部導電性パターン120aが中間導電性パターン160aと電気的に連結されて側面パッド160を形成する。一実施形態で、中間導電性パターン160の少なくとも一部がチップ100の側部表面150上に露出されうる。

【0054】

図4Cを参照して説明した方法と実質的に同一または類似した方法により、パッシベーション層(図示せず)が半導体基板102上に形成されうる。

【0055】

図7は、本発明のさらに他の実施形態による側面パッドを持つチップの斜視図である。

【0056】

図7を参照すれば、さらに他の実施形態によるチップ100は、図2Aを参照して説明したチップ100と類似しており、ただし、下部導電性パターン120bの下にチップ100の側部表面150の上に露出された導電性部材170をさらに備えることができる。しかし、チップ100がチップパッド130を備えないこともあるということは明らかである。一実施形態で、導電性部材170は、Al、Cu、W、Mo等、またはこれらの組み合わせのような金属、及び/またはTiN、TaN、WNなど、またはこれらの組み合わせのような導電性金属窒化物を含むことができる。

【0057】

図示したように導電性部材170は、たとえば、チップ100の側部表面150で下部導電性パターン120bに連結されうる。しかし、他の実施形態で、導電性部材170は、チップ100の側部表面150で下部導電性パターン120bに連結されず、たとえば、チップ100の内部のような他の場所で下部導電性パターン120bに電気的に連結されることもある。また、導電性部材170は、半導体基板102から離隔するか、連結されないこともある。

【0058】

一実施形態で、導電性部材170は“バー型導電性部材”であり、下部導電性パターン120bの幅と実質的に同等な幅を持つこともある。バー型導電性部材170を提供することによって、側面パッド120のコンタクト面積は、改善された溶融度及び減少したコンタクト抵抗を確保するために大きくなることもある。他の実施形態で、導電性部材170は“コンタクト型導電性部材”であり、下部導電性パターン120bの幅よりさらに狭い幅を持つことができる。

【0059】

図8Aないし8Cは、図7に図示されたチップを形成するための実施形態を示す断面図である。

【0060】

図8Aを参照すれば、チップ100を形成するために半導体基板102上に導電性構造体104が形成される。一実施形態で、導電性構造体104は、図4Aを参照して説明した導電性構造体104と実質的に同一または類似している。次いで、半導体基板102と導電性構造体104とを備える結果物上に第1層間誘電層106が形成されうる。一実施形態で、導電性構造物104は、図4Aを参照して説明した導電性構造物104と実質的に同一または類似している。導電性部材170aは、薄膜蒸着法のような従来の技術及びCMPのような平坦化工程を利用して形成されうる。前述したように、導電性部材170aは、半導体基板102と接触をしても、しなくてもよい。

【0061】

図8B及び8Cに示したようにチップ100を形成するための残りの工程は、図4B及び図4Cを参照して説明した方法と実質的に同一または類似している。たとえば、図8Cに図示したように、隣接して配されたチップ100はたとえば、レーザーまたは従来のダイアモンドチップカッターまたはダイアモンドソウを使用して、スクライブラインSLに沿ってダイシング工程を行うことにより互いに個別化されうる。チップ100を個別化させるとき、半導体基板102でスクライブラインSLが占める領域上に配される各導電性パターン108の一部が除去される。ダイシング工程後に、チップ100内に残る各導電性パターン108の一部は側面パッド120を形成する。したがって、前記ダイシング工程後に、チップ100内に残る下部導電性パターン108bの一部は、側面パッド120の下部導電性パターン120bを形成する。同様に、前記ダイシング工程の後に、チップ100内に残る上部導電性パターン120aの一部は側面パッド120の上部導電性パターン120aを形成する。この工程中に導電性部材170は、第1層間誘電層106を通じて露出されうる。

【0062】

したがって、要するに、チップ100は、下部導電性パターン120bの下部に配された導電性部材170を形成する工程により形成されうる。導電性部材170の少なくとも一部がチップ100の側部表面150上に露出され、下部導電性パターン120bに電気的に連結される。すなわち、下部導電性パターン108bが導電性部材170上に形成され、導電性部材170は下部導電性パターン108bと接触できる。

【0063】

図9はさらに他の実施形態による側面パッドを持つチップの斜視図である。図9を参照すれば、さらに他の実施形態によるチップ100は、図7を参照して既述したように下部導電性パターン120bの下にチップ100の側部表面150上に導電性部材170が露出されうるという点を除いては、図5Aを参照して説明したチップ100と類似している。しかし、チップ100がチップパッド130を備えていないこともあるということは明らかである。

【0064】

図示したように、導電性部材170は、チップ100の側部表面150で、下部導電性パターン120bに電気的に連結されうる。しかし、他の実施形態で、導電性部材170は、チップ100の側部表面150で下部導電性パターン120bに電気的に連結されず、チップ100の内部のような他の所に連結されることもある。一実施形態で、導電性部材170は“バー型導電性部材”であり、下部導電性パターン120bの幅と実質的に同等な幅を持つことができる。バー型導電性部材170を提供することによって、側面パッド160のコンタクト領域は、溶融度を高めてコンタクト抵抗を低下させるために大きくなりうる。他の実施形態で、導電性部材170は“コンタクト型導電性部材”であり、下部導電性パターン120bの幅よりさらに狭い幅を持つことができる。

【0065】

図10Aないし図10Cは、図9に図示されたチップを形成する方法を示す断面図である。

【0066】

図10Aを参照すれば、チップ100は、図8Aを参照して説明した方法と実質的に同一または類似した方法によって、導電性部材170がさらに形成される点を除いては、図6Aを参照して説明した工程と実質的に同一または類似した工程により形成される。図10B及び図10Cに示したように、チップ100を形成するための工程の残りは、図6B及び図6Cを参照して説明したような実質的に同一または類似した方法である。

【0067】

図11は、さらに他の実施形態による側面パッドを持つチップを形成する方法を示す斜視図である。

【0068】

図11を参照すれば、さらに他の実施形態によるチップ100は、上部導電性パターン120a上でチップ100の側部表面150上に導電性部材180が露出された点を除いては、図9を参照して説明したチップ100と類似している。

【0069】

図示したように、導電性部材180は、チップ100の側部表面150で上部導電性パターン120aに連結されうる。したがって、チップ100は、上部導電性パターン120a上に配された導電性部材180を形成する工程により形成されうる。導電性部材180の少なくとも一部がチップ100の側部表面150上に露出され、上部導電性パターン120aに電気的に連結される。他の実施形態で、図示していないが、導電性部材180は、チップ100の側部表面150で上部導電性パターン120aに連結されずに、チップ100の内部のような他の所に連結されうる。

【0070】

一実施形態で、導電性部材180は“バー型導電性部材”であり、上部導電性パターン120aの幅と実質的に同等な幅を持つことができる。バー型導電性部材180を提供することによって、側面パッド160のコンタクト領域は、溶融度を改善してコンタクト抵抗を低下させるために大きくなりうる。他の実施形態で、導電性部材180は“コンタクト型導電性部材”であり、上部導電性パターン120aの幅より狭い幅を持つことができる。しかし、チップ100が図5Aに示したようにチップパッド130を備えることもできるということは明らかである。

【0071】

図12Aないし図12Cは、ビアパターン及び配線部材のような素子構造体と、側面パッドとの関係及び連結方式を説明するために、一部の実施形態による電気的連結及び側面パッドを示す平面図である。

【0072】

図12Aを参照すれば、たとえば図3Bに示した半導体基板102の表面と実質的に平行した平面に沿って実質的に水平方向に延びた追加的な導電性ワイヤリングパターンまたは配線部材210は、前述した側面パッド160と共に形成されうる。すなわち、導電性ワイヤリングパターン210は、側面パッド160を形成する導電性パターンを形成するために利用される工程と同じ工程で形成されうる。すなわち、たとえば、図3Bに図示された導電性ワイヤリングパターン210及び上部導電性パターン120aは、同じ工程中に層間誘電層200a内に形成されうる。その結果、各側面パッド160は、必要ならば導電性ワイヤーパターン210に電気的に連結されうる。これによって、配線レベルの数(及びこれら構成の複雑性)が、一般的に信号経路がチップ100の上部(たとえば、図1に示したチップパッド40)からトランジスタのような導電性構造体に延びる従来の半導体素子に比べて減少できる。チップ構造が多層配線部材によって非常に複雑ならば、信号遅延及び製造工程の複雑性は重大な関心事でありうる。前述したように、チップ100内の配線レベルの数を減少させることによって、チップ100内の信号経路の長さが短くなり、これによって長い信号経路による信号遅延及び配線抵抗と関連した問題が減少しうる。

【0073】

図12Bを参照すれば、導電性ビアパターン212及び側面パッド160の中間導電性パターン160a(たとえば、図5Aを参照)は、層間誘電層200bで同じ工程で形成されうる。すなわち、導電性ビアパターン212は、側面パッド160の中間導電性パターン160aを形成するために利用される同じ工程で形成されうる。一実施形態で、導電性ビアパターン212は、互いに対して垂直方向に配された少なくとも2個の導電性パターンで電気的に連結されるように形成されうる。他の実施形態で、導電性ビアパターン212は、バー型ビアパターン(すなわち、上及び/または下の導電性パターンの幅と実質的に同じ幅を持つビアパターン)またはコンタクト型ビアパターン(すなわち、上の及び/または下の導電性パターンの幅よりさらに狭い幅を持つビアパターン)として提供されうる。

【0074】

図12Cを参照すれば、たとえば図3に示した追加的な導電性ワイヤリングパターン214及び下部導電性パターン120bが他の誘電層200c内に形成されうる。これら層は同じ工程中に形成されうる。一実施形態で、一つ以上の電気的構成要素220が側面パッド160に電気的に連結されうる。その結果、配線レベルの数を減少させることができ、これによって、前述したように配線工程の複雑性を低下させることができる。

【0075】

図13Aは、一実施形態によるチップを備えるパッケージの平面図である。図13B及び図13Cは、図13Aに示した線“B−B”に沿って切り取った断面図を持つ他の実施形態に関する。

【0076】

図13Aないし図13Cを参照すれば、パッケージは、たとえば、第1チップ100、回路基板300(たとえば、PCB)、複数の外部コンタクトターミナル310(たとえば、ソルダーボール)、複数の導電性配線312及び複数の第1回路基板パッド320を備えることができる。一実施形態で、回路基板300は、多層PCBまたは有機材料基板上に回路パターンを備えるフィルムパッケージ基板でありうる。回路基板300は、メモリ回路、ディスプレイまたはLDI装置のような多様な応用装置に適用されうる。回路基板300は、複数の第1回路基板パッド320を備えることができる。したがって、導電性配線312は、回路基板300上の第1回路基板パッド320のうち対応する一つに側面パッド120を電気的に連結できる。したがって、パッケージは、たとえば、複数の第1回路基板パッド320を持つ回路基板300を提供する工程、及び側面パッド120、すなわち、第1チップ100の側面パッド120上に露出された下部及び上部導電性パターン120b及び120aに導電性配線312で第1回路基板パッド320を連結する工程により形成されうる。

【0077】

一実施形態で、導電性配線312は、導電性ボール、導電性バンプ、ソルダーボール、ソルダーバンプ、ソルダーペースト、異方性導電フィルム、金属層またはこれらの組み合わせを備えることができる。図2A及び図2B、図5A、図7、図9または図11を参照して説明したように、第1チップ100が提供される。たとえば、図13Bに示したように、第1チップ100は、チップパッド130なしに、図7を参照して説明したように提供されうる。

【0078】

図13B及び図13Cに示したように、導電性配線312は、回路基板300上に形成された第1基板パッド320に第1チップ100の側面パッド120を電気的及び機械的に連結する。一実施形態で、導電性配線312は、導電性部材170の少なくとも一部と接触できる。側面パッド120を通じて第1チップ100と回路基板300とを電気的に連結することによって、チップ100の上部表面上に延びるワイヤーのような電気的配線部材、またはチップ100と回路基板300との間に配されるソルダーボールが要求されない。したがって、パッケージの厚さは、たとえば、チップ100及び回路基板300の結合された厚さと実質的に同等な程度に実質的に薄く維持されうる。したがって、パッケージの大きさが減少する。

【0079】

一側面によれば、図13Aないし図13Cに示した第1チップ100は、応用装置によって、たとえば、PCBである回路基板300に直接付着されうる。第1チップ100が回路基板300に直接付着されるならば、たとえば、接着層のような層が回路基板300と第1チップ100との間に存在する必要がない。すなわち、第1チップ100は、それらの間に何の物理的または機械的な連結なしに回路基板300上に配される。その結果、第1チップ100を備えるパッケージの厚さは、接着層のような付加層が形成される必要がないので、さらに薄くなる。しかし、チップ100と回路基板300との間に追加的な付着力を提供するために、接着層のような付加層が配されることもある。

【0080】

他の側面で、図13B及び図13Cに示したソルダーボール310は不要であり、パッケージとPCBとの間に他の公知の電気的連結形態が利用されることもある。

【0081】

図14A及び図14B、図15A及び図15B及び図16A及び図16Bは、図13に示した線“B−B”に沿って切り取ったパッケージの他の実施形態を示す断面図である。

【0082】

図13Aないし図13Cを参照して説明した導電性配線312は、実質的に球形の導電性配線として提供されうる。しかし、前記導電性配線は、チップ100と回路基板300との間に適した電気的連結を提供できるならば、実質的にいかなる形態にも提供されうる。たとえば、第1チップ100は、図14A及び図14Bに示したように、実質的に長方形導電性配線316、図15A及び図15Bに示したように実質的に三角形導電性配線318、または図16A及び図16Bに示したような凹状三角形導電性配線319などを通じて回路基板300に電気的に連結されうる。

【0083】

前記導電性配線が四角形または三角形の導電性配線を持つ場合に、導電性配線312とチップ100との接触面積は球形配線に比べてさらに大きくなり、これによって、チップ100と導電性配線312との接着力をさらに増大させることができる。三角形導電性配線318は、四角形のように他の形状を持つ導電性配線312をリップロー(replow)工程を行うことによって形成できる。図14B、15B及び16Bに示したように、導電性配線316、318及び319は、導電性部材180の少なくとも一部と接触する。

【0084】

図17Aないし図17Dは、複数のチップを備えるパッケージの実施形態を示す断面図である。

【0085】

図17Aを参照すれば、パッケージは、たとえば、図13Bを参照して説明したものと類似したパッケージである。しかし、図示された実施形態のように、第1チップ100はチップパッド130を備えることができる。したがって、第1チップ100は、図2Aを参照して説明したように提供され、チップパッド322を持つ第2チップ400は、チップパッド130とチップパッド322との対応するものの間に配される電気的配線部材または外部コンタクトターミナル314(たとえば、ソルダーボール、ソルダーペースト、異方性導電性フィルム、金属層またはこれらの組み合わせ)を通じて第1チップ100に結合されうる。したがって、パッケージは、第1チップ100の上部表面上にチップパッド130を提供する工程、第1チップ100の上に第2チップ400を提供する工程、及び外部コンタクトターミナル314で第1チップ100のチップパッド130に第2チップ400を連結する工程を行うことによって形成されうる。

【0086】

第2チップ400は、第1チップ100と同一であるかまたは異なる。たとえば、第1チップ100及び第2チップ400は、ロジック及び/またはメモリチップのように多様に提供されうる。図17Bは、第1チップ100が、図7を参照して説明したように導電性部材170を備える点を除いては、図17Aに示した実施形態と類似した他の実施形態に関するパッケージを図示する。明示的に図示してはいないが、図5Aまたは図9を参照して説明したように、第1チップ100もまた、あるいは選択的に提供されうるということは明らかである。

【0087】

図17Cを参照すれば、パッケージ、たとえば、複数の第1チップ100(たとえば、下部第1チップ100a及び上部第1チップ100b)が、図2Bを参照して前述したように提供されうる。下部第1チップ100a上には、上部第1チップ100bが配される。したがって、複数の第1チップ100が回路基板300上に互いに隣接して垂直方向に整列されうる。下部第1チップ100aの側面パッドは、図14Aを参照して説明した実質的に四角形の導電性配線316のような導電性配線部材を通じて、上部第1チップ100bの側面パッド120に電気的及び機械的に連結されうる。図17Cは、互いに積層された2個の第1チップ100を図示しているが、任意の数の第1チップ100が互いに積層され、導電性配線を通じて電気的/機械的に連結されうるということは明らかである。また、任意形状の導電性配線が積層された第1チップ100を電気的/機械的に連結するために使われうる。導電性配線(たとえば、実質的に四角形の導電性配線316)は、下部第1チップ100a及び上部第1チップ100bを電気的及び機械的に連結しているために、これらの間に接着層が挿入される必要がない。しかし、必要な場合、下部第1チップ100aと上部第1チップ100bとの間に接着層が配されうるということは明らかである。また、図17Cが、図2Bを参照して説明したように、第1チップ100を図示しているが、図2A及び図2B、図5A及び図5B、図7、図9または図11を参照して説明したように、一つ以上の第1チップ100が提供されうるということは明らかである。

【0088】

図17Dを参照すれば、パッケージは、たとえば、図11を参照して前述したように、下部第1チップ100aが提供され、図7を参照して説明したように上部第1チップ100bが提供されるという点を除いては、図17Cを参照して説明したものと類似したパッケージを提供できる。したがって、下部第1チップ100の導電性部材180は、上部第1チップ100の導電性部材170と直接接触して第1チップ100間の接触面積をさらに大きくすることができる。

【0089】

図18Aは、一実施形態による複数のチップを備えるパッケージの平面図である。図18B及び図18Cは、図18Aに図示された線“B−B”に沿って切り取ったパッケージの実施形態を示す断面図である。図19は、他の実施形態によって複数のチップを備えるパッケージを示す平面図である。

【0090】

図18A及び図18Bを参照すれば、パッケージは、たとえば、図13Bを参照して説明したものと類似したパッケージを提供できる。図18Cを参照すれば、パッケージは、図13Cを参照して説明したものと類似している。しかし、図示された実施形態で、複数の第1チップ100は、回路基板300上で互いに隣接して水平方向に整列されうる。また、複数の第1チップ100は、複数の導電性配線312を通じて回路基板300に電気的及び機械的に連結されるだけでなく、互いに電気的及び機械的に連結されることもある。すなわち、前記パッケージは、回路基板300上に複数の第1チップ100を提供する工程、及び第1チップ100のうちいずれか一つのチップの側部表面150上に露出された下部及び上部導電性パターン120b及び120a(すなわち、側面パッド120)の一部と、第1チップ100のうち他の一つの側部表面150上に露出された下部及び上部導電性パターン120b及び120a(すなわち、側部パッド120)の一部とを導電性配線312に連結させる工程により形成される。したがって、一実施形態で各導電性配線312は、第1チップ100のうちいずれか一つの側部表面150上に露出された下部及び上部導電性パターン120b及び120aの一部を、第1チップ100のうち他の一つの側部表面150上に露出された下部及び上部導電性パターン120b及び120aの一部に連結する。一実施形態で、第1チップ100のうち隣接するものの側部表面150は互いに離隔し、導電性配線312により電気的に連結されることもある。その結果、前記パッケージの大きさ(幅)は、導電性配線312が第1チップ100それぞれにより共通使用されるために縮小する。また、それぞれの第1チップ100内の回路は、パッケージの全体サイズを縮小させるように共有されうる。

【0091】

第1チップ100は、任意の数そして任意の配列に提供されうるということは明らかである。たとえば、図19を参照すれば、パッケージには、複数の導電性配線312により互いに電気的及び機械的に連結された4個の第1チップ100が提供されうる。したがって、チップ及びパッケージのサイズは、これらが導電性配線312とこれらの間の内部回路とを共有することによってさらに縮小する。一実施形態で、導電性配線312は、導電性バンプ、ソルダーボール及び固形化されたソルダーペーストのうち少なくとも一つを備えることができる。

【0092】

図20Aは、さらに他の実施形態によるチップを備えるパッケージの平面図である。図20B及び図20Cは、図20Aに図示された線“D-D”に沿って切り取った断面図をそれぞれ示す。図21Aは、さらに他の実施形態によるチップを備えるパッケージの平面図である。図21Bは、一実施形態による図21Aに図示された線“E−E”に沿って切り取った断面図である。図22Aないし図23Cは、他の実施形態によるチップを備えるパッケージの平面図である。

【0093】

図20A及び図20Bを参照すれば、たとえば、パッケージは、図13Bを参照して説明したものと類似したパッケージである。図20Cを参照すれば、たとえば、パッケージは、図13Cを参照して説明したものと類似したパッケージである。しかし、図示された実施形態で、第1チップ100は、その上部表面上に形成されたチップパッド130をさらに備えることができ、回路基板300は、第2回路基板パッド332をさらに備えることもできる。したがって、電気的配線部材330(たとえば、ボンディングワイヤー)は、チップパッド130のうち対応する一つに第2回路基板パッド332を電気的に連結させることができる。すなわち、パッケージは、第1チップ100の上部表面上にチップパッド130を提供する工程、及び少なくとも一つの電気的配線部材330で第2チップ基板パッド332をチップパッド130に連結する工程によって形成される。

【0094】

図20Aないし図20Cに図示された実施形態は、それぞれ多数の入/出力パッドを備え、それにより、高速ICまたは高集積メモリチップのような応用装置に使われうる。図20Aないし図20Cは、複数のチップパッド130が第1チップ100のあらゆる側壁に沿って配されたパッケージを図示している。ワイヤー330は、各チップパッド130を対応する第2回路基板パッド332に電気的に連結させる。チップパッド130(及びワイヤー330)は任意の数ほど、そして任意の配列で提供されうるということは明らかである。たとえば、図21A及び図21Bを参照すれば、側面パッド120が第1チップ100の各側部表面150に提供されるが、パッケージのチップパッド130は、第1チップ100の側部の一部分に沿って配される。図21Bに図示された第1チップ100が図7を参照して説明されたが、第1チップ100は、たとえば、図2B、図5Bまたは9を参照して説明したように提供されることもある。

【0095】

図22Aないし図22Cを参照すれば、チップパッド130は、第1チップ100の一つ以上の側部に沿って配されうる。図20Aないし図20C、図21A、図22A及び図22Bは、複数の導電性配線312と側面パッド120とが第1チップ100のあらゆる側部に沿って配されるパッケージを図示しているが、導電性配線312及び側面パッド120は任意の数及び配列で提供されうるということは明らかである。たとえば、図22Cを参照すれば、パッケージは、第1チップ100の対向する一対の側部に沿って配される複数の導電性配線312及び側面パッド120を備えるように提供されうるということは明らかである。また、図22Cに図示されたパッケージは、第1チップ100の一つの側部上にのみ配されるようにチップパッド130を備えることもできる。

【0096】

図23Aは、さらに他の実施形態によるチップを備えるパッケージの平面図である。図23B及び図23Cは、図23Aに図示された線“F−F”に沿って図示された断面図である。

【0097】

図23A及び23Bを参照すれば、パッケージは、たとえば、図13Bを参照して説明したものと類似したパッケージでありうる。図23Cを参照すれば、パッケージは、たとえば、図23Bに図示されたものと類似したパッケージであるが、図11を参照して説明したような第1チップ100を備えるか、本明細書に開示された他の適切なチップを備えることもできる。一実施形態で、図23Cに図示された導電性配線316は、導電性部材180の少なくとも一部と接触できる。しかし、図示された実施形態で、第1チップ100は、下部表面に配されたチップパッド130を備えることもある。したがって、第1チップ100の側面パッド120は、図14A及び図14Bに示したように、複数の実質的に四角形の導電性配線316を通じて第1回路基板パッド320に電気的に連結され、チップパッド130は、電気的配線部材314、たとえば、導電性ボール、導電性バンプ、ソルダーボール、ソルダーバンプ、ソルダーペースト、異方性導電性フィルム、金属層またはこれらの組み合わせを通じて回路基板300上に配された第2回路基板パッド340に電気的に連結されることもある。すなわち、パッケージは、第1チップ100の下部表面上にチップパッド130を提供する工程、及びチップパッド130に少なくとも一つの電気的配線部材314を使用して第2回路基板パッド340を連結する工程により形成されうる。

【0098】

前記実施形態によれば、側面パッドは、チップの側部表面上に露出される。前記チップの側部表面上に前記側面パッドを提供することによって、導電性構造体と外部装置との間の信号経路の長さが短くなる。前記信号経路の長さが短くなることで、信号遅延と関連した問題点が減少できる。また、電源または接地金属配線が多少遠距離に配されるチップ100の上部に配されるチップパッド130の代りに、近くに位置する側面パッド120に連結されうるために、ボンディングパッドと、電源または接地金属配線との間の配線部材が減少できる。

【0099】

また、チップ上に側面パッドを提供することによって、チップを備えるパッケージの全体厚さが薄くなる。また、チップの側部表面上に側面パッドを備えることによって、トランジスタまたは抵抗のような多様な電気的構成要素を連結するための配線部材の設計が、従来技術に比べればかなり容易になりうる。また、図12Aないし図12Cに示したような側面パッドを使用することによって、電源または接地ラインのための金属配線ルーティングのデザインがさらに融通性を持つことができる。

【0100】

一部の実施形態によれば、当業者は、本明細書でこのようなあらゆる組み合わせが開示されていないにもかかわらず、本明細書に開示されたパッケージが側面パッドを持つ多様な半導体チップを備えるということが容易に理解できるであろう。

【0101】

本発明の実施形態は、特定実施形態に係り、これについて開示したが、当業者ならば特許請求範囲の請求項により限定されたように、本発明の思想及び範ちゅうを外れずに形態及び細部事項において多様な変形が可能であるということが理解できるであろう。

【産業上の利用可能性】

【0102】

本発明は、半導体関連の技術分野に好適に用いられる。

【図面の簡単な説明】

【0103】

【図1】従来のパッドを持つ複数の従来のチップを備える従来のウェーハを示す斜視図である。

【図2A】本発明の一実施形態による側面パッドを持つチップの斜視図である。

【図2B】本発明の一実施形態による側面パッドを持つチップの斜視図である。

【図3A】ウェーハ上に配されたチップ内に提供されたパッドの配列を示す平面図である。

【図3B】図3Aに図示された線“A−A”に沿って切り取った断面図である。

【図4A】図2Aに図示されたチップを形成するための一実施形態を示す断面図である。

【図4B】図2Aに図示されたチップを形成するための一実施形態を示す断面図である。

【図4C】図2Aに図示されたチップを形成するための一実施形態を示す断面図である。

【図5A】本発明の他の実施形態による側面パッドを持つチップを示す斜視図である。

【図5B】本発明の他の実施形態による側面パッドを持つチップを示す斜視図である。

【図6A】図5Aに図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図6B】図5Aに図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図6C】図5Aに図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図7】本発明のさらに他の実施形態による側面パッドを持つチップを示す斜視図である。

【図8A】図7に図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図8B】図7に図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図8C】図7に図示されたチップを形成するための本発明の一実施形態による製造方法を説明するための断面図である。

【図9】本発明のさらに他の実施形態による側面パッドを備えるチップを示す斜視図である。

【図10A】図9に図示されたチップを形成するための本発明の一実施形態による製造方法を説明する断面図である。

【図10B】図9に図示されたチップを形成するための本発明の一実施形態による製造方法を説明する断面図である。

【図10C】図9に図示されたチップを形成するための本発明の一実施形態による製造方法を説明する断面図である。

【図11】本発明の他の実施形態による側面パッドを持つチップを形成するための製造方法を説明する斜視図である。

【図12A】本発明の実施形態による電気的接続及び側面パッドを示す平面図である。

【図12B】本発明の実施形態による電気的接続及び側面パッドを示す平面図である。

【図12C】本発明の実施形態による電気的接続及び側面パッドを示す平面図である。

【図13A】本発明の一実施形態によるチップを備えるパッケージを示す平面図である。

【図13B】図13Aに図示された線“B−B”に沿って切り取った他の実施形態による断面図である。

【図13C】図13Aに図示された線“B−B”に沿って切り取った他の実施形態による断面図である。

【図14A】図13Aに図示された線“B−B”に沿って切り取った他の実施形態によるパッケージを示す断面図である。

【図14B】図13Aに図示された線“B−B”に沿って切り取った他の実施形態によるパッケージを示す断面図である。

【図15A】図13Aに図示された線“B−B”に沿って切り取ったさらに他の実施形態によるパッケージを示す断面図である。

【図15B】図13Aに図示された線“B−B”に沿って切り取ったさらに他の実施形態によるパッケージを示す断面図である。

【図16A】図13Aに図示された線“B−B”に沿って切り取ったさらに他の実施形態によるパッケージを示す断面図である。

【図16B】図13Aに図示された線“B−B”に沿って切り取ったさらに他の実施形態によるパッケージを示す断面図である。

【図17A】本発明の実施形態による複数のチップを備えるパッケージを示す断面図である。

【図17B】本発明の実施形態による複数のチップを備えるパッケージを示す断面図である。

【図17C】本発明の実施形態による複数のチップを備えるパッケージを示す断面図である。

【図17D】本発明の実施形態による複数のチップを備えるパッケージを示す断面図である。

【図18A】本発明の一実施形態による複数のチップを備えるパッケージを示す平面図である。

【図18B】図18Aに図示された線“B−B”に沿って切り取った本発明の実施形態によるパッケージを示す断面図である。

【図18C】図18Aに図示された線“B−B”に沿って切り取った本発明の実施形態によるパッケージを示す断面図である。

【図19】本発明の他の実施形態による複数のチップを備えるパッケージを示す平面図である。

【図20A】本発明の他の実施形態によるチップを備えるパッケージを示す平面図である。

【図20B】本発明の一部の実施形態によって、図20Aに図示された線“D−D”に沿って切り取った断面図である。

【図20C】本発明の一部の実施形態によって、図20Aに図示された線“D−D”に沿って切り取った断面図である。

【図21A】本発明のさらに他の実施形態によるチップを備えるパッケージを示す平面図である。

【図21B】本発明の一実施形態による図21Aに図示された線“E−E”に沿って切り取った断面図である。

【図22A】本発明の他の実施形態によるチップを備えるパッケージの平面図である。

【図22B】本発明の他の実施形態によるチップを備えるパッケージの平面図である。

【図22C】本発明の他の実施形態によるチップを備えるパッケージの平面図である。

【図23A】本発明のさらに他の実施形態によるチップを備えるパッケージの平面図である。

【図23B】本発明の一部の実施形態による図23Aに図示された線“F−F”に沿って切り取った断面図である。

【図23C】本発明の一部の実施形態による図23Aに図示された線“F−F”に沿って切り取った断面図である。

【符号の説明】

【0104】

100 チップ、

120 側面パッド、

120a 上部導電性パターン、

120b 下部導電性パターン、

300 回路基板、

310 外部コンタクトターミナル、

312 導電性配線、

320 第1回路基板パッド。

【特許請求の範囲】

【請求項1】

上部表面、下部表面及び前記上部及び下部表面に連結された側部表面を持つ第1チップを備え、

前記第1チップは、チップ基板、前記チップ基板上の下部導電性パターン、前記下部導電性パターン上の層間誘電層及び前記層間誘電層上の上部導電性パターンを備え、

前記第1チップの前記側部表面上に前記下部導電性パターンの少なくとも一部及び前記上部導電性パターンの少なくとも一部が露出されて集合的に側面パッドを形成することを特徴とする半導体素子。

【請求項2】

前記第1チップの前記側部表面上に露出された前記上部導電性パターンの前記一部は、前記第1チップの前記側部表面上に露出された前記下部導電性パターンの前記一部と、前記第1チップの前記上部表面との間に配されることを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記第1チップは、前記下部導電性パターンと前記上部導電性パターンとの間に配される中間導電性パターンをさらに備えることを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記中間導電性パターンの少なくとも一部は、前記第1チップの前記側部表面上に露出されることを特徴とする請求項3に記載の半導体素子。

【請求項5】

前記中間導電性パターンは、バー型導電性パターンまたはコンタクト型導電性パターンであることを特徴とする請求項3に記載の半導体素子。

【請求項6】

第1回路基板パッドを持つ回路基板と、

前記第1チップの前記側部表面上に露出された前記下部及び上部導電性パターンに、前記第1回路基板パッドを連結させる導電性配線部材をさらに備えることを特徴とする請求項1に記載の半導体素子。

【請求項7】

前記第1チップは、前記第1チップの前記側部表面上に露出されて、前記第1チップの前記側面パッドに電気的に連結される導電性部材を備え、

前記導電性部材の少なくとも一部と前記導電性配線部材とが接触することを特徴とする請求項6に記載の半導体素子。

【請求項8】

前記導電性配線部材は、球形、四角形、三角形または凹状三角形の形状を持つことを特徴とする請求項6または7に記載の半導体素子。

【請求項9】

前記回路基板は、第2回路基板パッドを備え、

前記半導体素子は、

前記第1チップの前記上部及び下部表面のうち少なくともいずれか一つの上に配されたチップパッドと、

前記チップパッドに前記第2回路基板パッドを連結する少なくとも一つの電気的配線部材と、

をさらに備えることを特徴とする請求項6に記載の半導体素子。

【請求項10】

前記第1チップは、

複数の側面パッド及び複数の側部表面を備え、前記側部表面のうち少なくとも2以上の側部表面上に少なくとも一つの前記側面パッドが露出され、

前記半導体素子は、前記複数の側部表面のうち少なくとも2以上の側部表面に隣接する複数のチップをさらに備えることを特徴とする請求項9に記載の半導体素子。

【請求項11】

前記チップパッドは、前記側面パッドに電気的に連結されることを特徴とする請求項9に記載の半導体素子。

【請求項12】

前記第1チップの前記上部表面上のチップパッドと、

前記第1チップ上の第2チップと、

前記第1チップの前記チップパッドに前記第2チップを連結する電気的配線部材と、

をさらに備えることを特徴とする請求項6に記載の半導体素子。

【請求項13】

前記回路基板上の複数の第1チップと、

前記複数の第1チップのうち、第1チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部と、前記複数の第1チップの第2チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部とを連結させる導電性配線部材と、

をさらに備えることを特徴とする請求項6に記載の半導体素子。

【請求項14】

前記複数の第1チップのうち、少なくとも2個のチップは、前記回路基板上で互いに隣接して水平方向に整列されることを特徴とする請求項13に記載の半導体素子。

【請求項15】

前記複数の第1チップのうち、少なくとも2個のチップは、前記回路基板上で互いに垂直方向に整列されることを特徴とする請求項13に記載の半導体素子。

【請求項16】

互いに隣接して垂直方向に整列される前記複数の第1チップのうち、少なくとも2個のチップ間に接着層をさらに備えることを特徴とする請求項15に記載の半導体素子。

【請求項17】

前記複数の第1チップのうち、少なくとも2個のうち少なくとも一つは導電性部材を備え、

前記導電性部材の少なくとも一部は前記複数の第1チップのうち、少なくとも2つのうちの少なくとも一つの前記側部表面上に露出され、前記複数の第1チップのうち、少なくとも2つのうちの少なくとも一つの前記側面パッドに電気的に連結されることを特徴とする請求項15に記載の半導体素子。

【請求項18】

前記複数の第1チップのうち、少なくとも2個のチップは導電性部材を備え、

前記第1チップに垂直方向に隣接する少なくとも2個の前記導電性部材は、互いに直接接触することを特徴とする請求項17に記載の半導体素子。

【請求項19】

前記導電性配線部材は、導電性バンプ、ソルダーボール及び固形化されたソルダーペーストのうち少なくとも一つを備え、前記複数の第1チップのうち、前記第1チップ及び前記第2チップの側部表面は、前記導電性配線部材により互いに離隔されることを特徴とする請求項13に記載の半導体素子。

【請求項20】

前記第1チップは、前記下部導電性パターンの下に配される導電性部材をさらに備え、前記導電性部材の少なくとも一部が前記第1チップの前記側部表面上に露出されて前記下部導電性パターンに電気的に連結され、前記第1チップは、前記下部導電性パターンと前記上部導電性パターンとの間に配された中間導電性パターンをさらに備えることを特徴とする請求項1に記載の半導体素子。

【請求項21】

前記第1チップは、前記上部導電性パターンの上に配される導電性部材をさらに備え、前記導電性部材の少なくとも一部が前記第1チップの前記側部表面上に露出されて前記上部導電性パターンに電気的に連結され、前記第1チップは、前記下部導電性パターンと前記下部導電性パターンとの間に配される中間導電性パターンをさらに備えることを特徴とする請求項1に記載の半導体素子。

【請求項22】

前記第1チップは、

複数の側面パッドと、

前記チップ基板の表面に実質的に平行した平面に沿って実質的に水平方向に延長される少なくとも一つの導電性ワイヤリングパターンとをさらに備え、

前記少なくとも一つの導電性ワイヤリングパターンは、前記複数の側面パッドと共に電気的に連結されることを特徴とする請求項1に記載の半導体素子。

【請求項23】

前記少なくとも一つの導電性ワイヤリングパターンは、前記中間誘電層上に配されることを特徴とする請求項22に記載の半導体素子。

【請求項24】

前記第1チップは、

前記チップ基板上に形成された電気的構成部材と、

前記チップ基板上の導電性ワイヤリングパターンと、をさらに備え、

前記導電性ワイヤリングパターンは、前記下部導電性パターンと前記電気的構成部材とを共に電気的に連結することを特徴とする請求項1に記載の半導体素子。

【請求項25】

前記第1チップは、

複数の側面パッドと、

複数の側部表面と、を備え、

前記少なくとも一つの側面パッドは、前記複数のあらゆる側部表面上に露出されることを特徴とする請求項1に記載の半導体素子。

【請求項26】

上部表面、下部表面及び前記上部及び下部表面に連結された側部表面を持つ第1チップを形成する工程を含み、

前記第1チップを形成する工程は、

チップ基板を提供する工程と、

前記チップ基板上に下部導電性パターンを形成する工程と、

前記下部導電性パターン上に層間誘電層を形成する工程と、

前記層間誘電層上に上部導電性パターンを形成する工程と、を含み、

前記下部及び上部導電性パターンはダイシング領域内へ延び、前記下部導電性パターンの少なくとも一部と前記上部導電性パターンの少なくとも一部とは、前記第1チップの前記側部表面上に露出されて集合的に側面パッドを形成することを特徴とする半導体素子の製造方法。

【請求項27】

前記第1チップを形成する工程は、

ダイシング領域により離隔された複数のチップ領域を持つ基板を提供する工程と、

前記基板上に、そして少なくとも一つのチップ領域内に前記下部導電性パターンを形成する工程と、

前記下部導電性パターン上に、そして少なくとも一つの前記チップ領域及び前記ダイシング領域内に前記層間誘電層を形成する工程と、

前記層間誘電層上に、そして少なくとも一つの前記チップ領域内に前記上部導電性パターンを形成する工程と、

前記ダイシング領域で前記複数のチップ領域を個別化する工程と、を含み、

前記下部及び上部導電性パターンのうち、少なくとも一つは前記ダイシング領域内へ延びることを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項28】

前記第1チップの前記側部表面上に露出された前記下部導電性パターンと、前記第1チップの前記上部表面との間に配されるように、前記第1チップの前記側部表面上に露出された上部導電性パターンを形成する工程をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項29】

前記第1チップを形成する工程は、

前記下部導電性パターンと前記上部導電性パターンとの間に中間導電性パターンを形成する工程をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項30】

前記中間導電性パターンの少なくとも一部が前記第1チップの前記側部表面上に露出されることを特徴とする請求項29に記載の半導体素子の製造方法。

【請求項31】

第1回路基板パッドを持つ回路基板を提供する工程と、

前記第1チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部に、前記第1回路基板パッドを導電性配線部材で連結する工程と、

をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項32】

前記第1チップを形成する工程は、

前記第1チップの前記側部表面上に露出され、前記第1チップの前記側面パッドに電気的に連結される導電性部材を形成する工程をさらに含み、

前記半導体素子の製造方法は、前記導電性部材の少なくとも一部に前記導電性配線部材を接触させる工程をさらに含むことを特徴とする請求項31に記載の半導体素子の製造方法。

【請求項33】

前記導電性配線部材は、球形、四角形、三角形または凹状三角形の形状を持つことを特徴とする請求項31または32に記載の半導体素子の製造方法。

【請求項34】

前記半導体基板は第2回路基板パッドをさらに備え、

前記半導体素子の製造方法は、

前記第1チップの前記上部及び下部表面のうち少なくとも一つの上にチップパッドを提供する工程と、

前記チップパッドに前記第2回路基板パッドを少なくとも一つの電気的配線部材で連結する工程と、

をさらに含むことを特徴とする請求項31に記載の半導体素子の製造方法。

【請求項35】

前記第1チップは、複数の側面パッド及び複数の側部表面を備え、前記少なくとも一つの側面パッドが前記複数の側部表面のうち少なくとも2個の側部表面上に露出され、

前記複数の側部表面のうち少なくとも2個の側部表面上に隣接する複数のチップパッドを提供する工程をさらに含むことを特徴とする請求項34に記載の半導体素子の製造方法。

【請求項36】

前記側面パッドに前記チップパッドを電気的に連結させる工程をさらに含むことを特徴とする請求項35に記載の半導体素子の製造方法。

【請求項37】

前記第1チップの前記上部表面上にチップパッドを提供する工程と、

前記第1チップ上に第2チップを提供する工程と、

前記第1チップの前記チップパッドに前記第2チップを電気的配線部材で連結する工程と、

をさらに含むことを特徴とする請求項31に記載の半導体素子の製造方法。

【請求項38】

前記回路基板上に複数の第1チップを提供する工程と、

前記複数の第1チップのうち、第1チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部と、前記複数の第1チップの第2チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部とを導電性配線部材で連結する工程と、

をさらに含むことを特徴とする請求項31に記載の半導体素子の製造方法。

【請求項39】

前記複数の第1チップのうち少なくとも2個のチップを、前記回路基板上で互いに水平方向に隣接するように配する工程をさらに含むことを特徴とする請求項38に記載の半導体素子の製造方法。

【請求項40】

前記複数の第1チップのうち少なくとも2個のチップを、前記回路基板上で互いに垂直方向に隣接するように配する工程をさらに含むことを特徴とする請求項38に記載の半導体素子の製造方法。

【請求項41】

前記複数の第1チップのうちの少なくとも2個のチップのうち、少なくとも一つのチップ内に導電性部材を形成する工程をさらに含み、

前記導電性部材の少なくとも一部が前記複数の第1チップのうち、少なくとも2つのうちの少なくとも一つのチップの前記側部表面上に露出され、前記複数の第1チップのうちの少なくとも2つのうち、少なくとも一つのチップの前記側面パッドに電気的に連結されることを特徴とする請求項40に記載の半導体素子の製造方法。

【請求項42】

前記複数の第1チップのうち少なくとも2つ以上のチップ内に導電性部材を形成する工程と、

少なくとも2個の垂直方向に隣接する第1チップの導電性部材を接触させる工程と、

をさらに含むことを特徴とする請求項41に記載の半導体素子の製造方法。

【請求項43】

前記導電性配線部材は、導電性バンプ、ソルダーボール及び固形化されたソルダーペーストのうち少なくとも一つを含み、前記複数の第1チップのうち前記第1及び第2チップの前記側部表面は、前記導電性配線部材により離隔されることを特徴とする請求項38に記載の半導体素子の製造方法。

【請求項44】

前記第1チップを形成する工程は、

前記下部導電性パターンの下に配される導電性部材を形成する工程をさらに含み、

前記導電性部材の少なくとも一部は、前記第1チップの前記側部表面上に露出されて前記下部導電性パターンに電気的に連結され、

前記第1チップを形成するする工程は、前記下部導電性パターンと前記上部導電性パターンとの間に配される中間導電性パターンを形成する工程をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項45】

前記第1チップを形成する工程は、前記上部導電性パターンの上に配される導電性部材を形成する工程をさらに含み、

前記導電性部材の少なくとも一部は、前記第1チップの前記側部表面上に露出されて前記上部導電性パターンに電気的に連結され、

前記第1チップを形成する工程は、前記下部導電性パターンと前記上部導電性パターンとの間に配される中間導電性パターンを形成する工程をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項46】

前記第1チップを形成する工程は、

前記複数の側面パッドを形成する工程と、

前記チップ基板の表面に実質的に平行した平面に沿って実質的に水平方向に延長される少なくとも一つの導電性ワイヤリングパターンを形成する工程と、をさらに含み、

前記少なくとも一つの導電性ワイヤリングパターンは、前記少なくとも2つの複数の側面パッドを共に連結することを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項47】

前記層間誘電層上に少なくとも一つの導電性ワイヤリングパターンを配する工程をさらに含むことを特徴とする請求項46に記載の半導体素子の製造方法。

【請求項48】

前記第1チップを形成する工程は、

前記チップ基板上に導電性構造体を形成する工程と、

前記チップ基板上に導電性ワイヤリングパターンを形成する工程と、をさらに含み、

前記導電性ワイヤリングパターンは、前記導電性パターンと前記導電性構造体とを互いに電気的に連結することを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項49】

前記第1チップは複数の側部表面を備え、

前記第1チップを形成する工程は、前記複数の側面パッドを形成する工程を含み、前記複数の側部表面のうち少なくとも2個の側部表面上に、前記側面パッドのうち少なくとも一つが露出されることを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項1】

上部表面、下部表面及び前記上部及び下部表面に連結された側部表面を持つ第1チップを備え、

前記第1チップは、チップ基板、前記チップ基板上の下部導電性パターン、前記下部導電性パターン上の層間誘電層及び前記層間誘電層上の上部導電性パターンを備え、

前記第1チップの前記側部表面上に前記下部導電性パターンの少なくとも一部及び前記上部導電性パターンの少なくとも一部が露出されて集合的に側面パッドを形成することを特徴とする半導体素子。

【請求項2】

前記第1チップの前記側部表面上に露出された前記上部導電性パターンの前記一部は、前記第1チップの前記側部表面上に露出された前記下部導電性パターンの前記一部と、前記第1チップの前記上部表面との間に配されることを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記第1チップは、前記下部導電性パターンと前記上部導電性パターンとの間に配される中間導電性パターンをさらに備えることを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記中間導電性パターンの少なくとも一部は、前記第1チップの前記側部表面上に露出されることを特徴とする請求項3に記載の半導体素子。

【請求項5】

前記中間導電性パターンは、バー型導電性パターンまたはコンタクト型導電性パターンであることを特徴とする請求項3に記載の半導体素子。

【請求項6】

第1回路基板パッドを持つ回路基板と、

前記第1チップの前記側部表面上に露出された前記下部及び上部導電性パターンに、前記第1回路基板パッドを連結させる導電性配線部材をさらに備えることを特徴とする請求項1に記載の半導体素子。

【請求項7】

前記第1チップは、前記第1チップの前記側部表面上に露出されて、前記第1チップの前記側面パッドに電気的に連結される導電性部材を備え、

前記導電性部材の少なくとも一部と前記導電性配線部材とが接触することを特徴とする請求項6に記載の半導体素子。

【請求項8】

前記導電性配線部材は、球形、四角形、三角形または凹状三角形の形状を持つことを特徴とする請求項6または7に記載の半導体素子。

【請求項9】

前記回路基板は、第2回路基板パッドを備え、

前記半導体素子は、

前記第1チップの前記上部及び下部表面のうち少なくともいずれか一つの上に配されたチップパッドと、

前記チップパッドに前記第2回路基板パッドを連結する少なくとも一つの電気的配線部材と、

をさらに備えることを特徴とする請求項6に記載の半導体素子。

【請求項10】

前記第1チップは、

複数の側面パッド及び複数の側部表面を備え、前記側部表面のうち少なくとも2以上の側部表面上に少なくとも一つの前記側面パッドが露出され、

前記半導体素子は、前記複数の側部表面のうち少なくとも2以上の側部表面に隣接する複数のチップをさらに備えることを特徴とする請求項9に記載の半導体素子。

【請求項11】

前記チップパッドは、前記側面パッドに電気的に連結されることを特徴とする請求項9に記載の半導体素子。

【請求項12】

前記第1チップの前記上部表面上のチップパッドと、

前記第1チップ上の第2チップと、

前記第1チップの前記チップパッドに前記第2チップを連結する電気的配線部材と、

をさらに備えることを特徴とする請求項6に記載の半導体素子。

【請求項13】

前記回路基板上の複数の第1チップと、

前記複数の第1チップのうち、第1チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部と、前記複数の第1チップの第2チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部とを連結させる導電性配線部材と、

をさらに備えることを特徴とする請求項6に記載の半導体素子。

【請求項14】

前記複数の第1チップのうち、少なくとも2個のチップは、前記回路基板上で互いに隣接して水平方向に整列されることを特徴とする請求項13に記載の半導体素子。

【請求項15】

前記複数の第1チップのうち、少なくとも2個のチップは、前記回路基板上で互いに垂直方向に整列されることを特徴とする請求項13に記載の半導体素子。

【請求項16】

互いに隣接して垂直方向に整列される前記複数の第1チップのうち、少なくとも2個のチップ間に接着層をさらに備えることを特徴とする請求項15に記載の半導体素子。

【請求項17】

前記複数の第1チップのうち、少なくとも2個のうち少なくとも一つは導電性部材を備え、

前記導電性部材の少なくとも一部は前記複数の第1チップのうち、少なくとも2つのうちの少なくとも一つの前記側部表面上に露出され、前記複数の第1チップのうち、少なくとも2つのうちの少なくとも一つの前記側面パッドに電気的に連結されることを特徴とする請求項15に記載の半導体素子。

【請求項18】

前記複数の第1チップのうち、少なくとも2個のチップは導電性部材を備え、

前記第1チップに垂直方向に隣接する少なくとも2個の前記導電性部材は、互いに直接接触することを特徴とする請求項17に記載の半導体素子。

【請求項19】

前記導電性配線部材は、導電性バンプ、ソルダーボール及び固形化されたソルダーペーストのうち少なくとも一つを備え、前記複数の第1チップのうち、前記第1チップ及び前記第2チップの側部表面は、前記導電性配線部材により互いに離隔されることを特徴とする請求項13に記載の半導体素子。

【請求項20】

前記第1チップは、前記下部導電性パターンの下に配される導電性部材をさらに備え、前記導電性部材の少なくとも一部が前記第1チップの前記側部表面上に露出されて前記下部導電性パターンに電気的に連結され、前記第1チップは、前記下部導電性パターンと前記上部導電性パターンとの間に配された中間導電性パターンをさらに備えることを特徴とする請求項1に記載の半導体素子。

【請求項21】

前記第1チップは、前記上部導電性パターンの上に配される導電性部材をさらに備え、前記導電性部材の少なくとも一部が前記第1チップの前記側部表面上に露出されて前記上部導電性パターンに電気的に連結され、前記第1チップは、前記下部導電性パターンと前記下部導電性パターンとの間に配される中間導電性パターンをさらに備えることを特徴とする請求項1に記載の半導体素子。

【請求項22】

前記第1チップは、

複数の側面パッドと、

前記チップ基板の表面に実質的に平行した平面に沿って実質的に水平方向に延長される少なくとも一つの導電性ワイヤリングパターンとをさらに備え、

前記少なくとも一つの導電性ワイヤリングパターンは、前記複数の側面パッドと共に電気的に連結されることを特徴とする請求項1に記載の半導体素子。

【請求項23】

前記少なくとも一つの導電性ワイヤリングパターンは、前記中間誘電層上に配されることを特徴とする請求項22に記載の半導体素子。

【請求項24】

前記第1チップは、

前記チップ基板上に形成された電気的構成部材と、

前記チップ基板上の導電性ワイヤリングパターンと、をさらに備え、

前記導電性ワイヤリングパターンは、前記下部導電性パターンと前記電気的構成部材とを共に電気的に連結することを特徴とする請求項1に記載の半導体素子。

【請求項25】

前記第1チップは、

複数の側面パッドと、

複数の側部表面と、を備え、

前記少なくとも一つの側面パッドは、前記複数のあらゆる側部表面上に露出されることを特徴とする請求項1に記載の半導体素子。

【請求項26】

上部表面、下部表面及び前記上部及び下部表面に連結された側部表面を持つ第1チップを形成する工程を含み、

前記第1チップを形成する工程は、

チップ基板を提供する工程と、

前記チップ基板上に下部導電性パターンを形成する工程と、

前記下部導電性パターン上に層間誘電層を形成する工程と、

前記層間誘電層上に上部導電性パターンを形成する工程と、を含み、

前記下部及び上部導電性パターンはダイシング領域内へ延び、前記下部導電性パターンの少なくとも一部と前記上部導電性パターンの少なくとも一部とは、前記第1チップの前記側部表面上に露出されて集合的に側面パッドを形成することを特徴とする半導体素子の製造方法。

【請求項27】

前記第1チップを形成する工程は、

ダイシング領域により離隔された複数のチップ領域を持つ基板を提供する工程と、

前記基板上に、そして少なくとも一つのチップ領域内に前記下部導電性パターンを形成する工程と、

前記下部導電性パターン上に、そして少なくとも一つの前記チップ領域及び前記ダイシング領域内に前記層間誘電層を形成する工程と、

前記層間誘電層上に、そして少なくとも一つの前記チップ領域内に前記上部導電性パターンを形成する工程と、

前記ダイシング領域で前記複数のチップ領域を個別化する工程と、を含み、

前記下部及び上部導電性パターンのうち、少なくとも一つは前記ダイシング領域内へ延びることを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項28】

前記第1チップの前記側部表面上に露出された前記下部導電性パターンと、前記第1チップの前記上部表面との間に配されるように、前記第1チップの前記側部表面上に露出された上部導電性パターンを形成する工程をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項29】

前記第1チップを形成する工程は、

前記下部導電性パターンと前記上部導電性パターンとの間に中間導電性パターンを形成する工程をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項30】

前記中間導電性パターンの少なくとも一部が前記第1チップの前記側部表面上に露出されることを特徴とする請求項29に記載の半導体素子の製造方法。

【請求項31】

第1回路基板パッドを持つ回路基板を提供する工程と、

前記第1チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部に、前記第1回路基板パッドを導電性配線部材で連結する工程と、

をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項32】

前記第1チップを形成する工程は、

前記第1チップの前記側部表面上に露出され、前記第1チップの前記側面パッドに電気的に連結される導電性部材を形成する工程をさらに含み、

前記半導体素子の製造方法は、前記導電性部材の少なくとも一部に前記導電性配線部材を接触させる工程をさらに含むことを特徴とする請求項31に記載の半導体素子の製造方法。

【請求項33】

前記導電性配線部材は、球形、四角形、三角形または凹状三角形の形状を持つことを特徴とする請求項31または32に記載の半導体素子の製造方法。

【請求項34】

前記半導体基板は第2回路基板パッドをさらに備え、

前記半導体素子の製造方法は、

前記第1チップの前記上部及び下部表面のうち少なくとも一つの上にチップパッドを提供する工程と、

前記チップパッドに前記第2回路基板パッドを少なくとも一つの電気的配線部材で連結する工程と、

をさらに含むことを特徴とする請求項31に記載の半導体素子の製造方法。

【請求項35】

前記第1チップは、複数の側面パッド及び複数の側部表面を備え、前記少なくとも一つの側面パッドが前記複数の側部表面のうち少なくとも2個の側部表面上に露出され、

前記複数の側部表面のうち少なくとも2個の側部表面上に隣接する複数のチップパッドを提供する工程をさらに含むことを特徴とする請求項34に記載の半導体素子の製造方法。

【請求項36】

前記側面パッドに前記チップパッドを電気的に連結させる工程をさらに含むことを特徴とする請求項35に記載の半導体素子の製造方法。

【請求項37】

前記第1チップの前記上部表面上にチップパッドを提供する工程と、

前記第1チップ上に第2チップを提供する工程と、

前記第1チップの前記チップパッドに前記第2チップを電気的配線部材で連結する工程と、

をさらに含むことを特徴とする請求項31に記載の半導体素子の製造方法。

【請求項38】

前記回路基板上に複数の第1チップを提供する工程と、

前記複数の第1チップのうち、第1チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部と、前記複数の第1チップの第2チップの前記側部表面上に露出された前記下部及び上部導電性パターンの一部とを導電性配線部材で連結する工程と、

をさらに含むことを特徴とする請求項31に記載の半導体素子の製造方法。

【請求項39】

前記複数の第1チップのうち少なくとも2個のチップを、前記回路基板上で互いに水平方向に隣接するように配する工程をさらに含むことを特徴とする請求項38に記載の半導体素子の製造方法。

【請求項40】

前記複数の第1チップのうち少なくとも2個のチップを、前記回路基板上で互いに垂直方向に隣接するように配する工程をさらに含むことを特徴とする請求項38に記載の半導体素子の製造方法。

【請求項41】

前記複数の第1チップのうちの少なくとも2個のチップのうち、少なくとも一つのチップ内に導電性部材を形成する工程をさらに含み、

前記導電性部材の少なくとも一部が前記複数の第1チップのうち、少なくとも2つのうちの少なくとも一つのチップの前記側部表面上に露出され、前記複数の第1チップのうちの少なくとも2つのうち、少なくとも一つのチップの前記側面パッドに電気的に連結されることを特徴とする請求項40に記載の半導体素子の製造方法。

【請求項42】

前記複数の第1チップのうち少なくとも2つ以上のチップ内に導電性部材を形成する工程と、

少なくとも2個の垂直方向に隣接する第1チップの導電性部材を接触させる工程と、

をさらに含むことを特徴とする請求項41に記載の半導体素子の製造方法。

【請求項43】

前記導電性配線部材は、導電性バンプ、ソルダーボール及び固形化されたソルダーペーストのうち少なくとも一つを含み、前記複数の第1チップのうち前記第1及び第2チップの前記側部表面は、前記導電性配線部材により離隔されることを特徴とする請求項38に記載の半導体素子の製造方法。

【請求項44】

前記第1チップを形成する工程は、

前記下部導電性パターンの下に配される導電性部材を形成する工程をさらに含み、

前記導電性部材の少なくとも一部は、前記第1チップの前記側部表面上に露出されて前記下部導電性パターンに電気的に連結され、

前記第1チップを形成するする工程は、前記下部導電性パターンと前記上部導電性パターンとの間に配される中間導電性パターンを形成する工程をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項45】

前記第1チップを形成する工程は、前記上部導電性パターンの上に配される導電性部材を形成する工程をさらに含み、

前記導電性部材の少なくとも一部は、前記第1チップの前記側部表面上に露出されて前記上部導電性パターンに電気的に連結され、

前記第1チップを形成する工程は、前記下部導電性パターンと前記上部導電性パターンとの間に配される中間導電性パターンを形成する工程をさらに含むことを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項46】

前記第1チップを形成する工程は、

前記複数の側面パッドを形成する工程と、

前記チップ基板の表面に実質的に平行した平面に沿って実質的に水平方向に延長される少なくとも一つの導電性ワイヤリングパターンを形成する工程と、をさらに含み、

前記少なくとも一つの導電性ワイヤリングパターンは、前記少なくとも2つの複数の側面パッドを共に連結することを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項47】

前記層間誘電層上に少なくとも一つの導電性ワイヤリングパターンを配する工程をさらに含むことを特徴とする請求項46に記載の半導体素子の製造方法。

【請求項48】

前記第1チップを形成する工程は、

前記チップ基板上に導電性構造体を形成する工程と、

前記チップ基板上に導電性ワイヤリングパターンを形成する工程と、をさらに含み、

前記導電性ワイヤリングパターンは、前記導電性パターンと前記導電性構造体とを互いに電気的に連結することを特徴とする請求項26に記載の半導体素子の製造方法。

【請求項49】

前記第1チップは複数の側部表面を備え、

前記第1チップを形成する工程は、前記複数の側面パッドを形成する工程を含み、前記複数の側部表面のうち少なくとも2個の側部表面上に、前記側面パッドのうち少なくとも一つが露出されることを特徴とする請求項26に記載の半導体素子の製造方法。

【図1】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図4C】

【図5A】

【図5B】

【図6A】

【図6B】

【図6C】

【図7】

【図8A】

【図8B】

【図8C】

【図9】

【図10A】

【図10B】

【図10C】

【図11】

【図12A】

【図12B】

【図12C】

【図13A】

【図13B】

【図13C】

【図14A】

【図14B】

【図15A】

【図15B】

【図16A】

【図16B】

【図17A】

【図17B】

【図17C】

【図17D】

【図18A】

【図18B】

【図18C】

【図19】

【図20A】

【図20B】

【図20C】

【図21A】

【図21B】

【図22A】

【図22B】

【図22C】

【図23A】

【図23B】

【図23C】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図4C】

【図5A】

【図5B】

【図6A】

【図6B】

【図6C】

【図7】

【図8A】

【図8B】

【図8C】

【図9】

【図10A】

【図10B】

【図10C】

【図11】

【図12A】

【図12B】

【図12C】

【図13A】

【図13B】

【図13C】

【図14A】

【図14B】

【図15A】

【図15B】

【図16A】

【図16B】

【図17A】

【図17B】

【図17C】

【図17D】

【図18A】

【図18B】

【図18C】

【図19】

【図20A】

【図20B】

【図20C】

【図21A】

【図21B】

【図22A】

【図22B】

【図22C】

【図23A】

【図23B】

【図23C】

【公開番号】特開2008−182235(P2008−182235A)

【公開日】平成20年8月7日(2008.8.7)

【国際特許分類】

【出願番号】特願2008−11936(P2008−11936)

【出願日】平成20年1月22日(2008.1.22)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】SAMSUNG ELECTRONICS CO.,LTD.

【住所又は居所原語表記】416,Maetan−dong,Yeongtong−gu,Suwon−si,Gyeonggi−do 442−742(KR)

【Fターム(参考)】

【公開日】平成20年8月7日(2008.8.7)

【国際特許分類】

【出願日】平成20年1月22日(2008.1.22)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】SAMSUNG ELECTRONICS CO.,LTD.

【住所又は居所原語表記】416,Maetan−dong,Yeongtong−gu,Suwon−si,Gyeonggi−do 442−742(KR)

【Fターム(参考)】

[ Back to top ]