充電回路およびそれを利用した電子機器

【課題】異なる電源からの複数の直流電圧にもとづき、高効率で電池を充電する。

【解決手段】第1電圧検出回路16は、第1入力端子DCの電圧が所定の第1しきい値電圧より高いときにアサートされる第1入力検出信号DET_DCを生成する。第2電圧検出回路18は、第2入力端子USBの電圧が所定の第2しきい値電圧より高いときにアサートされる第2入力検出信号DET_USBを生成する。入力セレクタ20は、第1入力検出信号DET_DCと第2入力検出信号DET_USBにもとづいて、第1入力端子DCと第2入力端子USBの一方の電圧を選択する。DC/DCコンバータ30は、入力セレクタ30の出力電圧VINを降圧し、システム電圧VSYSを生成する。リニアチャージャ50は、システム電圧VSYSを受け、電池2を定電流モードまたは定電圧モードで充電する。

【解決手段】第1電圧検出回路16は、第1入力端子DCの電圧が所定の第1しきい値電圧より高いときにアサートされる第1入力検出信号DET_DCを生成する。第2電圧検出回路18は、第2入力端子USBの電圧が所定の第2しきい値電圧より高いときにアサートされる第2入力検出信号DET_USBを生成する。入力セレクタ20は、第1入力検出信号DET_DCと第2入力検出信号DET_USBにもとづいて、第1入力端子DCと第2入力端子USBの一方の電圧を選択する。DC/DCコンバータ30は、入力セレクタ30の出力電圧VINを降圧し、システム電圧VSYSを生成する。リニアチャージャ50は、システム電圧VSYSを受け、電池2を定電流モードまたは定電圧モードで充電する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、2次電池を充電する充電回路に関する。

【背景技術】

【0002】

携帯電話、PDA(Personal Digital Assistant)、ノート型パーソナルコンピュータ、ポータブルオーディオプレイヤをはじめとする電池駆動デバイスは、充電可能な2次電池とともに、それを充電するための充電回路を内蔵する。充電回路は、外部からの直流電圧を受け、それにもとづいて2次電池を充電する。

【0003】

充電回路に対して、異なる複数の電源から外部からの直流電圧が供給される場合がある。たとえばある電子機器は、ACアダプタ(AC/DCコンバータ)からの直流電圧と、USBバスから直流電圧を受けて動作可能となっている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−60977号公報

【特許文献2】特開2006−304500号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は係る状況においてなされたものであり、そのある態様の例示的な目的のひとつは、異なる電源からの複数の直流電圧にもとづき、高効率で電池を充電可能な充電回路の提供にある。

【課題を解決するための手段】

【0006】

本発明のある態様は、異なる電源からの直流電圧を受け、電池を充電する充電回路に関する。この充電回路は、交流アダプタからの第1直流電圧を受ける第1入力端子と、USB(Universal Serial Bus)からの第2直流電圧を受ける第2入力端子と、第1入力端子の電圧を所定の第1しきい値電圧と比較し、第1入力端子の電圧の方が高いときにアサートされる第1入力検出信号を生成する第1電圧検出回路と、第2入力端子の電圧を所定の第2しきい値電圧と比較し、第2入力端子の電圧の方が高いときにアサートされる第2入力検出信号を生成する第2電圧検出回路と、(i)第1入力検出信号がアサートされ、第2入力検出信号がネゲートされるとき、第1入力端子の電圧を出力し、(ii)第1入力検出信号がネゲートされ、第2入力検出信号がアサートされるとき、第2入力端子の電圧を出力し、(iii)第1入力検出信号、第2入力検出信号の両方がアサートされるとき、第1入力端子の電圧を出力する入力セレクタと、入力セレクタの出力電圧を降圧し、システム電圧を生成する降圧DC/DCコンバータと、システム電圧を受け、電池を定電流モードまたは定電圧モードで充電するリニアチャージャと、を備える。

【0007】

第1、第2電圧検出回路によって、複数の電源のいずれからの電力供給を受けているかが判定され、判定された電源からの直流電圧が、降圧DC/DCコンバータに供給される。そして降圧DC/DCコンバータによって、外部からの直流電圧を、電池電圧付近まで降圧することにより、リニアチャージャにおける電力損失を低減することができる。この態様によれば、いずれの直流電圧が供給される場合であっても、高効率な充電が可能となる。

【0008】

入力セレクタは、当該入力セレクタの出力端子と第1入力端子の間に設けられたPチャンネルMOSFETの第1スイッチと、入力セレクタの出力端子と第2入力端子の間に設けられたPチャンネルMOSFETの第2スイッチと、(i)第1入力検出信号がアサートされ、第2入力検出信号がネゲートされるとき、第1スイッチのゲートにローレベル電圧を印加し、(ii)第1入力検出信号がネゲートされ、第2入力検出信号がアサートされるとき、第2スイッチのゲートにローレベル電圧を印加し、(iii)第1入力検出信号、第2入力検出信号の両方がアサートされるとき、第1スイッチのゲートにローレベル電圧を印加する入力検出部と、を含んでもよい。第1スイッチのバックゲートおよび第2スイッチのバックゲートは、第1スイッチのボディダイオードと第2スイッチのボディダイオードのカソードが向かい合うように結線されてもよい。

【0009】

降圧DC/DCコンバータは、システム電圧の目標電圧を、電池の電圧に応じて変化させてもよい。

降圧DC/DCコンバータは、電池の電圧が所定のしきい値より低いとき、システム電圧の目標値を、しきい値電圧より所定の電圧幅高い値に設定し、電池の電圧が所定のしきい値より高いとき、システム電圧の目標値を、電池の電圧より所定の電圧幅高い値に設定してもよい。

【0010】

本発明のさらに別の態様は、電子機器に関する。電子機器は、電池と、電池を充電する上述のいずれかの態様の充電回路と、を備えてもよい。

【0011】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0012】

本発明によれば、異なる電源からの複数の直流電圧にもとづき、高効率で電池を充電できる。

【図面の簡単な説明】

【0013】

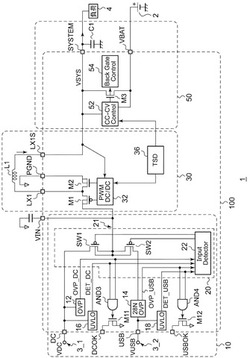

【図1】実施の形態に係る充電回路を備える電子機器の構成を示す回路図である。

【図2】パワーパス部の具体的な構成例を示す回路図である。

【図3】電池電圧VBATとDC/DCコンバータが生成するシステム電圧VSYSの関係を示す図である。

【図4】PWMコントローラの具体的な構成例を示す回路図である。

【発明を実施するための形態】

【0014】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0015】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合や、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0016】

図1は、実施の形態に係る充電回路100を備える電子機器1の構成を示す回路図である。電子機器1は、たとえば携帯電話端末や、PDA、ノート型PCなどの電池駆動型の情報端末機器である。電子機器1は、充電回路100および電池2、負荷4を備える。

【0017】

電池2は、リチウムイオン電池やニッケル水素電池などの2次電池であり電池電圧VBATを出力する。電池電圧VBATは、満充電状態で4.2V程度となる。電子機器1には、ACアダプタやUSB(Universal Serial Bus)などの外部電源が着脱可能な複数のアダプタ端子3_1、3_2が設けられる。本実施の形態では、第1のアダプタ端子3_1には、ACアダプタからの第1直流電圧VDCが、第2のアダプタ端子3_2には、USBバスからの第2直流電圧VUSBが入力される。直流電圧VDC、VUSBの典型的な値は5Vである。

【0018】

充電回路100の第1入力端子DCには、第1直流電圧VDCが入力され、第2入力端子USBには、第2直流電圧VUSBが入力される。

充電回路100は、主として、パワーパス部10、DC/DCコンバータ30、リニアチャージャ50を備える。

【0019】

パワーパス部10は、直流電圧VDC、VUSBの入力の有無を判定し、適切な直流電圧を選択して、後段のDC/DCコンバータ30に供給するとともに、過電圧保護を行う。

【0020】

パワーパス部10は、第1OVP(過電圧保護)回路12、第2OVP回路14、第1電圧検出回路16、第2電圧検出回路18、入力セレクタ20を備える。

第1電圧検出回路16は、第1入力端子DCの電圧を所定の第1しきい値電圧VTH1と比較し、第1入力端子DCの電圧の方が高いときにアサート(ハイレベル)される第1入力検出信号DET_DCを生成する。つまり第1入力検出信号DET_DCは、アダプタ端子3_1に外部からの直流電圧VDCが供給された状態でアサートされる。

第2電圧検出回路18は、第2入力端子USBの電圧を所定の第2しきい値電圧VTH2と比較し、第2入力端子USBの電圧の方が高いときにアサート(ハイレベル)される第2入力検出信号DET_USBを生成する。つまり第2入力検出信号DET_USBは、アダプタ端子3_2に外部からの直流電圧VUSBが供給された状態でアサートされる。

【0021】

第1OVP回路12は、第1直流電圧VDCの過電圧状態を検出するために設けられる。第1OVP回路12は、第1入力端子DCの電圧を、所定の第3しきい値電圧VTH3と比較し、第1入力端子DCの電圧の方が低いときにアサートされる第1過電圧保護信号OVP_DCを生成する。第1過電圧保護信号OVP_DCは、過電圧状態においてネゲートされ、通常状態でアサートされる。

【0022】

第2OVP回路14は、第2直流電圧VUSBの過電圧状態を検出するために設けられる。第2OVP回路14は、第2入力端子USBの電圧を、所定の第4しきい値電圧VTH4(たとえば28V)と比較し、第2入力端子USBの電圧の方が低いときにアサートされる第2過電圧保護信号OVP_USBを生成する。第2過電圧保護信号OVP_USBは、過電圧状態においてネゲートされ、通常状態でアサートされる。また第2OVP回路14は、過電圧を検出すると、第2スイッチSW2をオフすることにより、第2直流電圧VUSBの経路を遮断する。

【0023】

充電回路100は、ステータス端子DCOK、USBOKを有する。トランジスタM11のドレインは、ステータス端子DCOKと接続される。第3ANDゲートAND3は、第1過電圧保護信号OVP_DCと第1入力検出信号DET_DCの論理積を生成し、トランジスタM11のゲートに出力する。DCOK端子は、直流電圧VDCが正常であるときローレベル、過電圧状態または低電圧状態においてハイインピーダンスとなる。

トランジスタM12のドレインは、ステータス端子USBOKと接続される。第4ANDゲートAND4は、第2過電圧保護信号OVP_USBと第2入力検出信号DET_USBの論理積を生成し、トランジスタM12のゲートに出力する。USBOK端子は、直流電圧VUSBが正常であるときローレベル、過電圧状態または低電圧状態においてハイインピーダンスとなる。

充電回路100の外部に設けられるマイコン(不図示)は、ステータス端子DCOK、USBOKの状態を参照することにより、直流電圧VDC、VUSBが電子機器1に供給されているか否かを判定できる。

【0024】

入力セレクタ20は、その基本動作として、(i)第1入力検出信号DET_DCがアサートされ、第2入力検出信号DET_USBがネゲートされるとき、第1入力端子DCの電圧を出力する。また、(ii)第1入力検出信号DET_DCがネゲートされ、第2入力検出信号DET_USBがアサートされるとき、第2入力端子USBの電圧を出力しする。また(iii)第1入力検出信号DET_DC、第2入力検出信号DET_USBの両方がアサートされるとき、第1入力端子DCの電圧を出力する。

【0025】

入力セレクタ20は、第1スイッチSW1、第2スイッチSW2、入力検出部22を備える。

第1スイッチSW1は、PチャンネルMOSFETであり、入力セレクタ20の出力端子21と第1入力端子DCの間に設けられる。第2スイッチSW2は、PチャンネルMOSFETであり、入力セレクタ20の出力端子21と第2入力端子USBの間に設けられる。

【0026】

入力検出部22は、(i)第1入力検出信号DET_DCがアサートされ、第2入力検出信号DET_USBがネゲートされるとき、第1スイッチSW1のゲートにローレベル電圧を印加し、第1スイッチSW1をオンする。また(ii)第1入力検出信号DET_DCがネゲートされ、第2入力検出信号DET_USBがアサートされるとき、第2スイッチSW2のゲートにローレベル電圧を印加し、第2スイッチSW2をオンする。(iii)第1入力検出信号DET_DC、第2入力検出信号DET_USBの両方がアサートされるとき、第1スイッチSW1のゲートにローレベル電圧を印加し、第1スイッチSW1をオンする。

【0027】

第1スイッチSW1のバックゲートおよび第2スイッチSW2のバックゲートは、第1スイッチSW1のボディダイオードD1と第2スイッチSW2のボディダイオードD2のカソードが向かい合うように結線される。これにより、電流の逆流を防止できる。

【0028】

なお後述するように、入力セレクタ20は、第1入力検出信号DET_DC、第2入力検出信号DET_USBに加えて、第1過電圧保護信号OVP_DCおよび第2過電圧保護信号OVP_USBにもとづいて第1スイッチSW1、第2スイッチSW2を制御してもよい。

【0029】

図2は、パワーパス部10の具体的な構成例を示す回路図である。

第1OVP回路12、第2OVP回路14、第1電圧検出回路16、第2電圧検出回路18は同様に構成される。具体的には、抵抗によって監視対象の電圧を分圧し、コンパレータによって、分圧された電圧を所定のしきい値電圧と比較する。

【0030】

入力検出部22は、第1インバータINV1〜第3インバータINV3、第1ANDゲートAND1、第2ANDゲートAND2を含む。第1ANDゲートAND1は、第1入力検出信号DET_DCと第1過電圧保護信号OVP_DCの論理積を生成する。第1インバータINV1は、第1ANDゲートの出力を反転し、第1スイッチSW1のゲートに出力する。第2インバータINV2は、第1ANDゲートAND1の出力を反転する。第2ANDゲートAND2は、第2インバータINV2の出力と、第2過電圧保護信号OVP_USBと、第2入力検出信号DET_USBの論理積を生成する。第3インバータINV3は、第2ANDゲートAND2の出力を反転し、第2スイッチSW2のゲートに出力する。これにより、第2スイッチSW2は、第1スイッチSW1がオフ状態つまり第1直流電圧VDCが異常であり、かつ第2直流電圧VUSBが正常であるときにオンとなる。

【0031】

なお、図2の入力検出部22の構成は例示であり、当業者であれば、デジタル回路を用いた様々な回路によって、同様の機能が実現できることが理解される。

【0032】

第3スイッチSW3は、NチャンネルMOSFETであり、第2入力端子USBと入力検出部22の間に設けられる。チャージポンプ回路24は、第1インバータINV1の出力がハイレベルのとき、つまり第1ANDゲートAND1の出力がネゲート(ローレベル)されるとき動作状態となり、第3スイッチSW3のゲートにハイレベル電圧を出力して第3スイッチSW3をオンする。反対に第1インバータINV1の出力がローレベルのとき、つまり第1ANDゲートAND1の出力がアサート(ハイレベル)されるとき、チャージポンプ回路24は停止し、第3スイッチSW3のゲートにローレベル電圧が入力され、第3スイッチSW3はオフする。これにより第1直流電圧VDCが正常であるときに第3スイッチSW3がオフされ、第1直流電圧VDCが異常であるときに第3スイッチSW3がオンして、第2直流電圧VUSBの経路が有効となる。

【0033】

なお、第3スイッチSW3としてPチャンネルMOSFETを用いる場合には、チャージポンプ回路24は不要となる。この場合、第1ANDゲートAND1の出力がネゲート(ローレベル)されるとき、第3スイッチSW3のゲートにローレベル電圧を出力して第3スイッチSW3をオンすればよい。反対に第1ANDゲートAND1の出力がアサート(ハイレベル)されるとき、第3スイッチSW3のゲートにハイレベル電圧を出力して第3スイッチSW3はオフすればよい。

【0034】

また、第3スイッチSW3の制御に、第2入力検出信号DET_USB、第2過電圧保護信号OVP_USBのいずれかあるいは両方を反映させてもよい。すなわち、第2直流電圧VUSBの低電圧状態、および/または過電圧状態において第3スイッチSW3をオフとしてもよい。

【0035】

図1に戻る。入力セレクタ20の出力端子は、VIN端子と接続される。VIN端子に外付けされる平滑用キャパシタは、入力セレクタ20の出力電圧(入力電圧VIN)を安定化する。降圧DC/DCコンバータ30は、入力電圧VINを降圧し、システム電圧VSYSを生成する。

【0036】

DC/DCコンバータ30は、スイッチングトランジスタM1、同期整流トランジスタM2、インダクタL1、出力キャパシタC1、PWM(Pulse Width Modulation)コントローラ32、サーマルシャットダウン回路36を備える。

【0037】

スイッチングトランジスタM1、同期整流トランジスタM2、インダクタL1、出力キャパシタC1の構成は、一般的であるため説明を省略する。

PWMコントローラ32は、システム電圧VSYSが目標電圧と一致するようにデューティ比が調節されるパルス信号を生成し、当該パルス信号にもとづいて、スイッチングトランジスタM1、同期整流トランジスタM2を相補的にスイッチングする。PWMコントローラ32は、電圧モード、平均電流モード、ピーク電流モード、ヒステリシス制御など、公知の回路を利用すればよく、その構成は限定されない。DC/DCコンバータ30が生成したシステム電圧VSYSは、後段のリニアチャージャ50に供給されるともに、図示しないその他の負荷4へと供給される。

【0038】

DC/DCコンバータ30は、システム電圧VSYSの目標電圧を、電池2の電圧VBATに応じて変化させる。図3は、電池電圧VBATとDC/DCコンバータ30が生成するシステム電圧VSYSの関係を示す図である。具体的には、電池電圧VBATが所定のしきい値Vx(たとえば3V)より低いとき、システム電圧VSYSの目標値を、しきい値電圧Vxより所定の電圧幅ΔV(100mV)高い値(Vx+ΔV)に設定する。また、電池電圧VBATが所定のしきい値(3V)より高いとき、システム電圧VSYSの目標値を、電池電圧VBATより所定の電圧幅ΔV(100mV)高い値(VBAT+ΔV)に設定する。

【0039】

図4は、PWMコントローラ32の具体的な構成例を示す回路図である。

図4のPWMコントローラ32は、電圧モードの変調器を有する。充電回路100のREGINV端子には、システム電圧VSYSがフィードバックされる。ERRINV端子には、システム電圧VSYSを分圧した電圧VSYS’がフィードバックされる。

【0040】

PWMコントローラ32は、出力が共通にカップリングされた誤差増幅器EA1、EA2を備える。誤差増幅器EA1は、システム電圧VSYS’と、所定の基準電圧VREFの誤差を増幅する。電圧源40は、システム電圧VSYSを電圧幅ΔV低い電圧にシフトする。誤差増幅器EA2は、シフトされた電圧VSYS−ΔVと、電池電圧VBATの誤差を増幅する。電池電圧VBATがしきい値Vxより低い領域では、誤差増幅器EA1が支配的となり、電池電圧VBATがしきい値Vxより高い領域では、誤差増幅器EA2が支配的となる。したがって、誤差増幅器EA1、EA2により生成されるフィードバック電圧VFBは、VBAT>Vxの領域では、電圧VSYS−ΔVが電池電圧VBATと近づくように調節され、VBAT<Vxの領域では、電圧VSYS’が基準電圧VREFと近づくように調節される。オシレータ42は、所定の周波数の三角波またはのこぎり波の周期電圧VOSCを生成する。PWMコンパレータ44は、周期電圧VOSCとフィードバック電圧VFBを比較し、パルス幅変調(PWM)信号を生成する。ドライバ46は、PWM信号にもとづいて、スイッチングトランジスタM1および同期整流トランジスタM2をスイッチングする。

【0041】

このPWMコントローラ32によれば、電池電圧VBATとシステム電圧VSYSを、図3に示す関係に保つことができる。なお上述したように、PWMコントローラ32の構成は図4の電圧モードの変調器には限定されず、平均電流モード、ピーク電流モードなどを採用してもよい。

【0042】

図1に戻る。リニアチャージャ50は、DC/DCコンバータ30により生成されたシステム電圧VSYSを受け、電池2を充電する。リニアチャージャ50は、出力トランジスタM3、リニアチャージャ52、バックゲートコントローラ54を備える。出力トランジスタM3は、SYSTEM端子と、VBAT端子の間に設けられる。リニアチャージャ52は、出力トランジスタM3のゲート電圧を制御することにより、出力トランジスタM3のインピーダンスを調節する。具体的にはリニアチャージャ52は、電池電圧VBATが低い状態では、定電流モードで動作し、充電電流が一定となるように出力トランジスタM3のインピーダンスを調節する。電池電圧VBATが満充電レベルに近づくと定電圧モードで動作し、電池電圧VBATが一定となるように出力トランジスタM3のインピーダンスを調節する。

【0043】

バックゲートコントローラ54は、出力トランジスタM3のバックゲートを介して、電池2から電流が逆流しないように、出力トランジスタM3のバックゲートの接続先を制御する。バックゲートコントローラ54は公知の技術を用いればよく、その構成は特に限定されない。

【0044】

以上が充電回路100の構成である。続いてその動作を説明する。

【0045】

充電回路100は、パワーパス部10によって第1直流電圧VDC、第2直流電圧VUSBのいずれが供給されているかを自動判定し、供給されている一方を、入力電圧VINとして後段のDC/DCコンバータ30に出力する。そして電力効率が高いDC/DCコンバータ30によって、入力電圧VINを電池電圧VBATよりわずかに高い電圧レベルのシステム電圧VSYSに降圧する。そして、リニアチャージャ50によって、システム電圧VSYSにもとづいて電池2を充電する。

【0046】

もしDC/DCコンバータ30を省略して、入力電圧VINがリニアチャージャ50に供給されるとする。この場合、VIN=5V、VBAT=4.2Vとすれば、出力トランジスタM3において0.8Vもの電圧降下が発生し、電力損失が大きくなる。これに対して、充電回路100によれば、第1直流電圧VDC、第2直流電圧VUSBのいずれが供給される場合であっても、それをシステム電圧VSYSに降圧して、リニアチャージャ50に供給するため、高効率で電池2を充電することができる。具体的には、VIN=5V、VSYS=4.3Vとすれば、出力トランジスタM3の電圧降下は0.1Vとなり、電力損失を低減することができる。

【0047】

一般的には、USBバスよりもACアダプタの方が信頼性が高く、あるいは電流能力が大きい。そこでパワーパス部10は、第1直流電圧VDCと第2直流電圧VUSBの両方が供給されている場合には、第1直流電圧VDCを優先して出力する。これにより、電池2を信頼性の高い電源にもとづいて確実に充電でき、あるいは大電流で急速に充電できる。

【0048】

さらに、図3に示すように、電池電圧VBATがしきい値電圧Vxより高い領域では、システム電圧VSYSを電池電圧VBATに追従させることにより、出力トランジスタM3の電圧降下を、電圧幅ΔVに保つことができる。その結果、電池2を高効率で充電することができる。

【0049】

充電回路100の別の利点は、比較技術との対比によって明確となる。比較技術においては、リニアチャージャ50を省略し、DC/DCコンバータ30によって直接電池2を充電する。比較技術では、出力トランジスタM3における電力損失が存在しないため、効率の観点で優れている。ところが、DC/DCコンバータ30の出力であるシステム電圧VSYSが電池電圧VBATと等しくなるため、電池電圧VBATが非常に低い状況(たとえば1.5V)において、DC/DCコンバータ30が生成するシステム電圧VSYSも低くなる。つまり、高効率充電と引き換えに、負荷4に十分な電源電圧を供給できなくなる。

【0050】

これに対して、実施の形態に係る充電回路100では、電池電圧VBATがしきい値Vxより低い領域においては、システム電圧VSYSを(Vx+ΔV)に安定化する。これにより、電池2を充電しつつも、負荷4に十分な電源電圧を供給することができる。

【0051】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0052】

1…電子機器、2…電池、4…負荷、100…充電回路、10…パワーパス部、12…第1OVP回路、14…第2OVP回路、16…第1電圧検出回路、18…第2電圧検出回路、20…入力セレクタ、SW1…第1スイッチ、SW2…第2スイッチ、SW3…第3スイッチ、22…入力検出部、24…チャージポンプ回路、AND1…第1ANDゲート、AND2…第2ANDゲート、INV1…第1インバータ、INV2…第2インバータ、INV3…第3インバータ、30…DC/DCコンバータ、M1…スイッチングトランジスタ、M2…同期整流トランジスタ、L1…インダクタ、C1…出力キャパシタ、32…PWMコントローラ、36…サーマルシャットダウン回路、50…リニアチャージャ、52…リニアチャージャ、54…バックゲートコントローラ、M3…出力トランジスタ、DC…第1入力端子、USB…第2入力端子、VDC…第1直流電圧、VUSB…第2直流電圧、DET_DC…第1入力検出信号、DET_USB…第2入力検出信号、OVP_DC…第1過電圧保護信号、OVP_USB…第2過電圧保護信号。

【技術分野】

【0001】

本発明は、2次電池を充電する充電回路に関する。

【背景技術】

【0002】

携帯電話、PDA(Personal Digital Assistant)、ノート型パーソナルコンピュータ、ポータブルオーディオプレイヤをはじめとする電池駆動デバイスは、充電可能な2次電池とともに、それを充電するための充電回路を内蔵する。充電回路は、外部からの直流電圧を受け、それにもとづいて2次電池を充電する。

【0003】

充電回路に対して、異なる複数の電源から外部からの直流電圧が供給される場合がある。たとえばある電子機器は、ACアダプタ(AC/DCコンバータ)からの直流電圧と、USBバスから直流電圧を受けて動作可能となっている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−60977号公報

【特許文献2】特開2006−304500号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は係る状況においてなされたものであり、そのある態様の例示的な目的のひとつは、異なる電源からの複数の直流電圧にもとづき、高効率で電池を充電可能な充電回路の提供にある。

【課題を解決するための手段】

【0006】

本発明のある態様は、異なる電源からの直流電圧を受け、電池を充電する充電回路に関する。この充電回路は、交流アダプタからの第1直流電圧を受ける第1入力端子と、USB(Universal Serial Bus)からの第2直流電圧を受ける第2入力端子と、第1入力端子の電圧を所定の第1しきい値電圧と比較し、第1入力端子の電圧の方が高いときにアサートされる第1入力検出信号を生成する第1電圧検出回路と、第2入力端子の電圧を所定の第2しきい値電圧と比較し、第2入力端子の電圧の方が高いときにアサートされる第2入力検出信号を生成する第2電圧検出回路と、(i)第1入力検出信号がアサートされ、第2入力検出信号がネゲートされるとき、第1入力端子の電圧を出力し、(ii)第1入力検出信号がネゲートされ、第2入力検出信号がアサートされるとき、第2入力端子の電圧を出力し、(iii)第1入力検出信号、第2入力検出信号の両方がアサートされるとき、第1入力端子の電圧を出力する入力セレクタと、入力セレクタの出力電圧を降圧し、システム電圧を生成する降圧DC/DCコンバータと、システム電圧を受け、電池を定電流モードまたは定電圧モードで充電するリニアチャージャと、を備える。

【0007】

第1、第2電圧検出回路によって、複数の電源のいずれからの電力供給を受けているかが判定され、判定された電源からの直流電圧が、降圧DC/DCコンバータに供給される。そして降圧DC/DCコンバータによって、外部からの直流電圧を、電池電圧付近まで降圧することにより、リニアチャージャにおける電力損失を低減することができる。この態様によれば、いずれの直流電圧が供給される場合であっても、高効率な充電が可能となる。

【0008】

入力セレクタは、当該入力セレクタの出力端子と第1入力端子の間に設けられたPチャンネルMOSFETの第1スイッチと、入力セレクタの出力端子と第2入力端子の間に設けられたPチャンネルMOSFETの第2スイッチと、(i)第1入力検出信号がアサートされ、第2入力検出信号がネゲートされるとき、第1スイッチのゲートにローレベル電圧を印加し、(ii)第1入力検出信号がネゲートされ、第2入力検出信号がアサートされるとき、第2スイッチのゲートにローレベル電圧を印加し、(iii)第1入力検出信号、第2入力検出信号の両方がアサートされるとき、第1スイッチのゲートにローレベル電圧を印加する入力検出部と、を含んでもよい。第1スイッチのバックゲートおよび第2スイッチのバックゲートは、第1スイッチのボディダイオードと第2スイッチのボディダイオードのカソードが向かい合うように結線されてもよい。

【0009】

降圧DC/DCコンバータは、システム電圧の目標電圧を、電池の電圧に応じて変化させてもよい。

降圧DC/DCコンバータは、電池の電圧が所定のしきい値より低いとき、システム電圧の目標値を、しきい値電圧より所定の電圧幅高い値に設定し、電池の電圧が所定のしきい値より高いとき、システム電圧の目標値を、電池の電圧より所定の電圧幅高い値に設定してもよい。

【0010】

本発明のさらに別の態様は、電子機器に関する。電子機器は、電池と、電池を充電する上述のいずれかの態様の充電回路と、を備えてもよい。

【0011】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0012】

本発明によれば、異なる電源からの複数の直流電圧にもとづき、高効率で電池を充電できる。

【図面の簡単な説明】

【0013】

【図1】実施の形態に係る充電回路を備える電子機器の構成を示す回路図である。

【図2】パワーパス部の具体的な構成例を示す回路図である。

【図3】電池電圧VBATとDC/DCコンバータが生成するシステム電圧VSYSの関係を示す図である。

【図4】PWMコントローラの具体的な構成例を示す回路図である。

【発明を実施するための形態】

【0014】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0015】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合や、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0016】

図1は、実施の形態に係る充電回路100を備える電子機器1の構成を示す回路図である。電子機器1は、たとえば携帯電話端末や、PDA、ノート型PCなどの電池駆動型の情報端末機器である。電子機器1は、充電回路100および電池2、負荷4を備える。

【0017】

電池2は、リチウムイオン電池やニッケル水素電池などの2次電池であり電池電圧VBATを出力する。電池電圧VBATは、満充電状態で4.2V程度となる。電子機器1には、ACアダプタやUSB(Universal Serial Bus)などの外部電源が着脱可能な複数のアダプタ端子3_1、3_2が設けられる。本実施の形態では、第1のアダプタ端子3_1には、ACアダプタからの第1直流電圧VDCが、第2のアダプタ端子3_2には、USBバスからの第2直流電圧VUSBが入力される。直流電圧VDC、VUSBの典型的な値は5Vである。

【0018】

充電回路100の第1入力端子DCには、第1直流電圧VDCが入力され、第2入力端子USBには、第2直流電圧VUSBが入力される。

充電回路100は、主として、パワーパス部10、DC/DCコンバータ30、リニアチャージャ50を備える。

【0019】

パワーパス部10は、直流電圧VDC、VUSBの入力の有無を判定し、適切な直流電圧を選択して、後段のDC/DCコンバータ30に供給するとともに、過電圧保護を行う。

【0020】

パワーパス部10は、第1OVP(過電圧保護)回路12、第2OVP回路14、第1電圧検出回路16、第2電圧検出回路18、入力セレクタ20を備える。

第1電圧検出回路16は、第1入力端子DCの電圧を所定の第1しきい値電圧VTH1と比較し、第1入力端子DCの電圧の方が高いときにアサート(ハイレベル)される第1入力検出信号DET_DCを生成する。つまり第1入力検出信号DET_DCは、アダプタ端子3_1に外部からの直流電圧VDCが供給された状態でアサートされる。

第2電圧検出回路18は、第2入力端子USBの電圧を所定の第2しきい値電圧VTH2と比較し、第2入力端子USBの電圧の方が高いときにアサート(ハイレベル)される第2入力検出信号DET_USBを生成する。つまり第2入力検出信号DET_USBは、アダプタ端子3_2に外部からの直流電圧VUSBが供給された状態でアサートされる。

【0021】

第1OVP回路12は、第1直流電圧VDCの過電圧状態を検出するために設けられる。第1OVP回路12は、第1入力端子DCの電圧を、所定の第3しきい値電圧VTH3と比較し、第1入力端子DCの電圧の方が低いときにアサートされる第1過電圧保護信号OVP_DCを生成する。第1過電圧保護信号OVP_DCは、過電圧状態においてネゲートされ、通常状態でアサートされる。

【0022】

第2OVP回路14は、第2直流電圧VUSBの過電圧状態を検出するために設けられる。第2OVP回路14は、第2入力端子USBの電圧を、所定の第4しきい値電圧VTH4(たとえば28V)と比較し、第2入力端子USBの電圧の方が低いときにアサートされる第2過電圧保護信号OVP_USBを生成する。第2過電圧保護信号OVP_USBは、過電圧状態においてネゲートされ、通常状態でアサートされる。また第2OVP回路14は、過電圧を検出すると、第2スイッチSW2をオフすることにより、第2直流電圧VUSBの経路を遮断する。

【0023】

充電回路100は、ステータス端子DCOK、USBOKを有する。トランジスタM11のドレインは、ステータス端子DCOKと接続される。第3ANDゲートAND3は、第1過電圧保護信号OVP_DCと第1入力検出信号DET_DCの論理積を生成し、トランジスタM11のゲートに出力する。DCOK端子は、直流電圧VDCが正常であるときローレベル、過電圧状態または低電圧状態においてハイインピーダンスとなる。

トランジスタM12のドレインは、ステータス端子USBOKと接続される。第4ANDゲートAND4は、第2過電圧保護信号OVP_USBと第2入力検出信号DET_USBの論理積を生成し、トランジスタM12のゲートに出力する。USBOK端子は、直流電圧VUSBが正常であるときローレベル、過電圧状態または低電圧状態においてハイインピーダンスとなる。

充電回路100の外部に設けられるマイコン(不図示)は、ステータス端子DCOK、USBOKの状態を参照することにより、直流電圧VDC、VUSBが電子機器1に供給されているか否かを判定できる。

【0024】

入力セレクタ20は、その基本動作として、(i)第1入力検出信号DET_DCがアサートされ、第2入力検出信号DET_USBがネゲートされるとき、第1入力端子DCの電圧を出力する。また、(ii)第1入力検出信号DET_DCがネゲートされ、第2入力検出信号DET_USBがアサートされるとき、第2入力端子USBの電圧を出力しする。また(iii)第1入力検出信号DET_DC、第2入力検出信号DET_USBの両方がアサートされるとき、第1入力端子DCの電圧を出力する。

【0025】

入力セレクタ20は、第1スイッチSW1、第2スイッチSW2、入力検出部22を備える。

第1スイッチSW1は、PチャンネルMOSFETであり、入力セレクタ20の出力端子21と第1入力端子DCの間に設けられる。第2スイッチSW2は、PチャンネルMOSFETであり、入力セレクタ20の出力端子21と第2入力端子USBの間に設けられる。

【0026】

入力検出部22は、(i)第1入力検出信号DET_DCがアサートされ、第2入力検出信号DET_USBがネゲートされるとき、第1スイッチSW1のゲートにローレベル電圧を印加し、第1スイッチSW1をオンする。また(ii)第1入力検出信号DET_DCがネゲートされ、第2入力検出信号DET_USBがアサートされるとき、第2スイッチSW2のゲートにローレベル電圧を印加し、第2スイッチSW2をオンする。(iii)第1入力検出信号DET_DC、第2入力検出信号DET_USBの両方がアサートされるとき、第1スイッチSW1のゲートにローレベル電圧を印加し、第1スイッチSW1をオンする。

【0027】

第1スイッチSW1のバックゲートおよび第2スイッチSW2のバックゲートは、第1スイッチSW1のボディダイオードD1と第2スイッチSW2のボディダイオードD2のカソードが向かい合うように結線される。これにより、電流の逆流を防止できる。

【0028】

なお後述するように、入力セレクタ20は、第1入力検出信号DET_DC、第2入力検出信号DET_USBに加えて、第1過電圧保護信号OVP_DCおよび第2過電圧保護信号OVP_USBにもとづいて第1スイッチSW1、第2スイッチSW2を制御してもよい。

【0029】

図2は、パワーパス部10の具体的な構成例を示す回路図である。

第1OVP回路12、第2OVP回路14、第1電圧検出回路16、第2電圧検出回路18は同様に構成される。具体的には、抵抗によって監視対象の電圧を分圧し、コンパレータによって、分圧された電圧を所定のしきい値電圧と比較する。

【0030】

入力検出部22は、第1インバータINV1〜第3インバータINV3、第1ANDゲートAND1、第2ANDゲートAND2を含む。第1ANDゲートAND1は、第1入力検出信号DET_DCと第1過電圧保護信号OVP_DCの論理積を生成する。第1インバータINV1は、第1ANDゲートの出力を反転し、第1スイッチSW1のゲートに出力する。第2インバータINV2は、第1ANDゲートAND1の出力を反転する。第2ANDゲートAND2は、第2インバータINV2の出力と、第2過電圧保護信号OVP_USBと、第2入力検出信号DET_USBの論理積を生成する。第3インバータINV3は、第2ANDゲートAND2の出力を反転し、第2スイッチSW2のゲートに出力する。これにより、第2スイッチSW2は、第1スイッチSW1がオフ状態つまり第1直流電圧VDCが異常であり、かつ第2直流電圧VUSBが正常であるときにオンとなる。

【0031】

なお、図2の入力検出部22の構成は例示であり、当業者であれば、デジタル回路を用いた様々な回路によって、同様の機能が実現できることが理解される。

【0032】

第3スイッチSW3は、NチャンネルMOSFETであり、第2入力端子USBと入力検出部22の間に設けられる。チャージポンプ回路24は、第1インバータINV1の出力がハイレベルのとき、つまり第1ANDゲートAND1の出力がネゲート(ローレベル)されるとき動作状態となり、第3スイッチSW3のゲートにハイレベル電圧を出力して第3スイッチSW3をオンする。反対に第1インバータINV1の出力がローレベルのとき、つまり第1ANDゲートAND1の出力がアサート(ハイレベル)されるとき、チャージポンプ回路24は停止し、第3スイッチSW3のゲートにローレベル電圧が入力され、第3スイッチSW3はオフする。これにより第1直流電圧VDCが正常であるときに第3スイッチSW3がオフされ、第1直流電圧VDCが異常であるときに第3スイッチSW3がオンして、第2直流電圧VUSBの経路が有効となる。

【0033】

なお、第3スイッチSW3としてPチャンネルMOSFETを用いる場合には、チャージポンプ回路24は不要となる。この場合、第1ANDゲートAND1の出力がネゲート(ローレベル)されるとき、第3スイッチSW3のゲートにローレベル電圧を出力して第3スイッチSW3をオンすればよい。反対に第1ANDゲートAND1の出力がアサート(ハイレベル)されるとき、第3スイッチSW3のゲートにハイレベル電圧を出力して第3スイッチSW3はオフすればよい。

【0034】

また、第3スイッチSW3の制御に、第2入力検出信号DET_USB、第2過電圧保護信号OVP_USBのいずれかあるいは両方を反映させてもよい。すなわち、第2直流電圧VUSBの低電圧状態、および/または過電圧状態において第3スイッチSW3をオフとしてもよい。

【0035】

図1に戻る。入力セレクタ20の出力端子は、VIN端子と接続される。VIN端子に外付けされる平滑用キャパシタは、入力セレクタ20の出力電圧(入力電圧VIN)を安定化する。降圧DC/DCコンバータ30は、入力電圧VINを降圧し、システム電圧VSYSを生成する。

【0036】

DC/DCコンバータ30は、スイッチングトランジスタM1、同期整流トランジスタM2、インダクタL1、出力キャパシタC1、PWM(Pulse Width Modulation)コントローラ32、サーマルシャットダウン回路36を備える。

【0037】

スイッチングトランジスタM1、同期整流トランジスタM2、インダクタL1、出力キャパシタC1の構成は、一般的であるため説明を省略する。

PWMコントローラ32は、システム電圧VSYSが目標電圧と一致するようにデューティ比が調節されるパルス信号を生成し、当該パルス信号にもとづいて、スイッチングトランジスタM1、同期整流トランジスタM2を相補的にスイッチングする。PWMコントローラ32は、電圧モード、平均電流モード、ピーク電流モード、ヒステリシス制御など、公知の回路を利用すればよく、その構成は限定されない。DC/DCコンバータ30が生成したシステム電圧VSYSは、後段のリニアチャージャ50に供給されるともに、図示しないその他の負荷4へと供給される。

【0038】

DC/DCコンバータ30は、システム電圧VSYSの目標電圧を、電池2の電圧VBATに応じて変化させる。図3は、電池電圧VBATとDC/DCコンバータ30が生成するシステム電圧VSYSの関係を示す図である。具体的には、電池電圧VBATが所定のしきい値Vx(たとえば3V)より低いとき、システム電圧VSYSの目標値を、しきい値電圧Vxより所定の電圧幅ΔV(100mV)高い値(Vx+ΔV)に設定する。また、電池電圧VBATが所定のしきい値(3V)より高いとき、システム電圧VSYSの目標値を、電池電圧VBATより所定の電圧幅ΔV(100mV)高い値(VBAT+ΔV)に設定する。

【0039】

図4は、PWMコントローラ32の具体的な構成例を示す回路図である。

図4のPWMコントローラ32は、電圧モードの変調器を有する。充電回路100のREGINV端子には、システム電圧VSYSがフィードバックされる。ERRINV端子には、システム電圧VSYSを分圧した電圧VSYS’がフィードバックされる。

【0040】

PWMコントローラ32は、出力が共通にカップリングされた誤差増幅器EA1、EA2を備える。誤差増幅器EA1は、システム電圧VSYS’と、所定の基準電圧VREFの誤差を増幅する。電圧源40は、システム電圧VSYSを電圧幅ΔV低い電圧にシフトする。誤差増幅器EA2は、シフトされた電圧VSYS−ΔVと、電池電圧VBATの誤差を増幅する。電池電圧VBATがしきい値Vxより低い領域では、誤差増幅器EA1が支配的となり、電池電圧VBATがしきい値Vxより高い領域では、誤差増幅器EA2が支配的となる。したがって、誤差増幅器EA1、EA2により生成されるフィードバック電圧VFBは、VBAT>Vxの領域では、電圧VSYS−ΔVが電池電圧VBATと近づくように調節され、VBAT<Vxの領域では、電圧VSYS’が基準電圧VREFと近づくように調節される。オシレータ42は、所定の周波数の三角波またはのこぎり波の周期電圧VOSCを生成する。PWMコンパレータ44は、周期電圧VOSCとフィードバック電圧VFBを比較し、パルス幅変調(PWM)信号を生成する。ドライバ46は、PWM信号にもとづいて、スイッチングトランジスタM1および同期整流トランジスタM2をスイッチングする。

【0041】

このPWMコントローラ32によれば、電池電圧VBATとシステム電圧VSYSを、図3に示す関係に保つことができる。なお上述したように、PWMコントローラ32の構成は図4の電圧モードの変調器には限定されず、平均電流モード、ピーク電流モードなどを採用してもよい。

【0042】

図1に戻る。リニアチャージャ50は、DC/DCコンバータ30により生成されたシステム電圧VSYSを受け、電池2を充電する。リニアチャージャ50は、出力トランジスタM3、リニアチャージャ52、バックゲートコントローラ54を備える。出力トランジスタM3は、SYSTEM端子と、VBAT端子の間に設けられる。リニアチャージャ52は、出力トランジスタM3のゲート電圧を制御することにより、出力トランジスタM3のインピーダンスを調節する。具体的にはリニアチャージャ52は、電池電圧VBATが低い状態では、定電流モードで動作し、充電電流が一定となるように出力トランジスタM3のインピーダンスを調節する。電池電圧VBATが満充電レベルに近づくと定電圧モードで動作し、電池電圧VBATが一定となるように出力トランジスタM3のインピーダンスを調節する。

【0043】

バックゲートコントローラ54は、出力トランジスタM3のバックゲートを介して、電池2から電流が逆流しないように、出力トランジスタM3のバックゲートの接続先を制御する。バックゲートコントローラ54は公知の技術を用いればよく、その構成は特に限定されない。

【0044】

以上が充電回路100の構成である。続いてその動作を説明する。

【0045】

充電回路100は、パワーパス部10によって第1直流電圧VDC、第2直流電圧VUSBのいずれが供給されているかを自動判定し、供給されている一方を、入力電圧VINとして後段のDC/DCコンバータ30に出力する。そして電力効率が高いDC/DCコンバータ30によって、入力電圧VINを電池電圧VBATよりわずかに高い電圧レベルのシステム電圧VSYSに降圧する。そして、リニアチャージャ50によって、システム電圧VSYSにもとづいて電池2を充電する。

【0046】

もしDC/DCコンバータ30を省略して、入力電圧VINがリニアチャージャ50に供給されるとする。この場合、VIN=5V、VBAT=4.2Vとすれば、出力トランジスタM3において0.8Vもの電圧降下が発生し、電力損失が大きくなる。これに対して、充電回路100によれば、第1直流電圧VDC、第2直流電圧VUSBのいずれが供給される場合であっても、それをシステム電圧VSYSに降圧して、リニアチャージャ50に供給するため、高効率で電池2を充電することができる。具体的には、VIN=5V、VSYS=4.3Vとすれば、出力トランジスタM3の電圧降下は0.1Vとなり、電力損失を低減することができる。

【0047】

一般的には、USBバスよりもACアダプタの方が信頼性が高く、あるいは電流能力が大きい。そこでパワーパス部10は、第1直流電圧VDCと第2直流電圧VUSBの両方が供給されている場合には、第1直流電圧VDCを優先して出力する。これにより、電池2を信頼性の高い電源にもとづいて確実に充電でき、あるいは大電流で急速に充電できる。

【0048】

さらに、図3に示すように、電池電圧VBATがしきい値電圧Vxより高い領域では、システム電圧VSYSを電池電圧VBATに追従させることにより、出力トランジスタM3の電圧降下を、電圧幅ΔVに保つことができる。その結果、電池2を高効率で充電することができる。

【0049】

充電回路100の別の利点は、比較技術との対比によって明確となる。比較技術においては、リニアチャージャ50を省略し、DC/DCコンバータ30によって直接電池2を充電する。比較技術では、出力トランジスタM3における電力損失が存在しないため、効率の観点で優れている。ところが、DC/DCコンバータ30の出力であるシステム電圧VSYSが電池電圧VBATと等しくなるため、電池電圧VBATが非常に低い状況(たとえば1.5V)において、DC/DCコンバータ30が生成するシステム電圧VSYSも低くなる。つまり、高効率充電と引き換えに、負荷4に十分な電源電圧を供給できなくなる。

【0050】

これに対して、実施の形態に係る充電回路100では、電池電圧VBATがしきい値Vxより低い領域においては、システム電圧VSYSを(Vx+ΔV)に安定化する。これにより、電池2を充電しつつも、負荷4に十分な電源電圧を供給することができる。

【0051】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0052】

1…電子機器、2…電池、4…負荷、100…充電回路、10…パワーパス部、12…第1OVP回路、14…第2OVP回路、16…第1電圧検出回路、18…第2電圧検出回路、20…入力セレクタ、SW1…第1スイッチ、SW2…第2スイッチ、SW3…第3スイッチ、22…入力検出部、24…チャージポンプ回路、AND1…第1ANDゲート、AND2…第2ANDゲート、INV1…第1インバータ、INV2…第2インバータ、INV3…第3インバータ、30…DC/DCコンバータ、M1…スイッチングトランジスタ、M2…同期整流トランジスタ、L1…インダクタ、C1…出力キャパシタ、32…PWMコントローラ、36…サーマルシャットダウン回路、50…リニアチャージャ、52…リニアチャージャ、54…バックゲートコントローラ、M3…出力トランジスタ、DC…第1入力端子、USB…第2入力端子、VDC…第1直流電圧、VUSB…第2直流電圧、DET_DC…第1入力検出信号、DET_USB…第2入力検出信号、OVP_DC…第1過電圧保護信号、OVP_USB…第2過電圧保護信号。

【特許請求の範囲】

【請求項1】

異なる電源からの直流電圧を受け、電池を充電する充電回路であって、

交流アダプタからの第1直流電圧を受ける第1入力端子と、

USB(Universal Serial Bus)からの第2直流電圧を受ける第2入力端子と、

前記第1入力端子の電圧を所定の第1しきい値電圧と比較し、前記第1入力端子の電圧の方が高いときにアサートされる第1入力検出信号を生成する第1電圧検出回路と、

前記第2入力端子の電圧を所定の第2しきい値電圧と比較し、前記第2入力端子の電圧の方が高いときにアサートされる第2入力検出信号を生成する第2電圧検出回路と、

(i)前記第1入力検出信号がアサートされ、前記第2入力検出信号がネゲートされるとき、前記第1入力端子の電圧を出力し、(ii)前記第1入力検出信号がネゲートされ、前記第2入力検出信号がアサートされるとき、前記第2入力端子の電圧を出力し、(iii)前記第1入力検出信号、前記第2入力検出信号の両方がアサートされるとき、前記第1入力端子の電圧を出力する入力セレクタと、

前記入力セレクタの出力電圧を降圧し、システム電圧を生成する降圧DC/DCコンバータと、

前記システム電圧を受け、前記電池を定電流モードまたは定電圧モードで充電するリニアチャージャと、

を備えることを特徴とする充電回路。

【請求項2】

前記入力セレクタは、

前記入力セレクタの出力端子と前記第1入力端子の間に設けられたPチャンネルMOSFETの第1スイッチと、

前記入力セレクタの出力端子と前記第2入力端子の間に設けられたPチャンネルMOSFETの第2スイッチと、

(i)前記第1入力検出信号がアサートされ、前記第2入力検出信号がネゲートされるとき、前記第1スイッチのゲートにローレベル電圧を印加し、(ii)前記第1入力検出信号がネゲートされ、前記第2入力検出信号がアサートされるとき、前記第2スイッチのゲートにローレベル電圧を印加し、(iii)前記第1入力検出信号、前記第2入力検出信号の両方がアサートされるとき、前記第1スイッチのゲートにローレベル電圧を印加する入力検出部と、

を含み、

前記第1スイッチのバックゲートおよび前記第2スイッチのバックゲートは、前記第1スイッチのボディダイオードと前記第2スイッチのボディダイオードのカソードが向かい合うように結線されることを特徴とする請求項1に記載の充電回路。

【請求項3】

前記第1入力端子の電圧を所定の第3しきい値電圧と比較し、前記第1入力端子の電圧の方が低いときにアサートされる第1過電圧保護信号を生成する第1過電圧保護回路と、

前記第2入力端子の電圧を所定の第4しきい値電圧と比較し、前記第2入力端子の電圧の方が低いときにアサートされる第2過電圧保護信号を生成する第2過電圧保護回路と、

をさらに備え、

前記入力検出部は、

前記第1入力検出信号と前記第1過電圧保護信号の論理積を生成する第1ANDゲートと、

前記第1ANDゲートの出力を反転し、前記第1スイッチのゲートに出力する第1インバータと、

前記第1ANDゲートの出力を反転する第2インバータと、

前記第2インバータの出力と、前記第2過電圧保護信号と、前記第2入力検出信号の論理積を生成する第2ANDゲートと、

前記第2ANDゲートの出力を反転し、前記第2スイッチのゲートに出力する第3インバータと、

を含むことを特徴とする請求項2に記載の充電回路。

【請求項4】

前記入力セレクタの出力端子と前記第2入力端子の間に、前記第2スイッチと直列に設けられた第3スイッチをさらに備えることを特徴とする請求項2または3に記載の充電回路。

【請求項5】

前記第3スイッチは、前記第1スイッチがオフの状態において、オンすることを特徴とする請求項4に記載の充電回路。

【請求項6】

前記降圧DC/DCコンバータは、前記システム電圧の目標電圧を、前記電池の電圧に応じて変化させることを特徴とする請求項1から5のいずれかに記載の充電回路。

【請求項7】

前記降圧DC/DCコンバータは、前記電池の電圧が所定のしきい値より低いとき、前記システム電圧の目標値を、前記しきい値電圧より所定の電圧幅高い値に設定し、

前記電池の電圧が所定のしきい値より高いとき、前記システム電圧の目標値を、前記電池の電圧より所定の電圧幅高い値に設定することを特徴とする請求項6に記載の充電回路。

【請求項8】

電池と、

前記電池を充電する請求項1から7のいずれかに記載の充電回路と、

を備えることを特徴とする電子機器。

【請求項1】

異なる電源からの直流電圧を受け、電池を充電する充電回路であって、

交流アダプタからの第1直流電圧を受ける第1入力端子と、

USB(Universal Serial Bus)からの第2直流電圧を受ける第2入力端子と、

前記第1入力端子の電圧を所定の第1しきい値電圧と比較し、前記第1入力端子の電圧の方が高いときにアサートされる第1入力検出信号を生成する第1電圧検出回路と、

前記第2入力端子の電圧を所定の第2しきい値電圧と比較し、前記第2入力端子の電圧の方が高いときにアサートされる第2入力検出信号を生成する第2電圧検出回路と、

(i)前記第1入力検出信号がアサートされ、前記第2入力検出信号がネゲートされるとき、前記第1入力端子の電圧を出力し、(ii)前記第1入力検出信号がネゲートされ、前記第2入力検出信号がアサートされるとき、前記第2入力端子の電圧を出力し、(iii)前記第1入力検出信号、前記第2入力検出信号の両方がアサートされるとき、前記第1入力端子の電圧を出力する入力セレクタと、

前記入力セレクタの出力電圧を降圧し、システム電圧を生成する降圧DC/DCコンバータと、

前記システム電圧を受け、前記電池を定電流モードまたは定電圧モードで充電するリニアチャージャと、

を備えることを特徴とする充電回路。

【請求項2】

前記入力セレクタは、

前記入力セレクタの出力端子と前記第1入力端子の間に設けられたPチャンネルMOSFETの第1スイッチと、

前記入力セレクタの出力端子と前記第2入力端子の間に設けられたPチャンネルMOSFETの第2スイッチと、

(i)前記第1入力検出信号がアサートされ、前記第2入力検出信号がネゲートされるとき、前記第1スイッチのゲートにローレベル電圧を印加し、(ii)前記第1入力検出信号がネゲートされ、前記第2入力検出信号がアサートされるとき、前記第2スイッチのゲートにローレベル電圧を印加し、(iii)前記第1入力検出信号、前記第2入力検出信号の両方がアサートされるとき、前記第1スイッチのゲートにローレベル電圧を印加する入力検出部と、

を含み、

前記第1スイッチのバックゲートおよび前記第2スイッチのバックゲートは、前記第1スイッチのボディダイオードと前記第2スイッチのボディダイオードのカソードが向かい合うように結線されることを特徴とする請求項1に記載の充電回路。

【請求項3】

前記第1入力端子の電圧を所定の第3しきい値電圧と比較し、前記第1入力端子の電圧の方が低いときにアサートされる第1過電圧保護信号を生成する第1過電圧保護回路と、

前記第2入力端子の電圧を所定の第4しきい値電圧と比較し、前記第2入力端子の電圧の方が低いときにアサートされる第2過電圧保護信号を生成する第2過電圧保護回路と、

をさらに備え、

前記入力検出部は、

前記第1入力検出信号と前記第1過電圧保護信号の論理積を生成する第1ANDゲートと、

前記第1ANDゲートの出力を反転し、前記第1スイッチのゲートに出力する第1インバータと、

前記第1ANDゲートの出力を反転する第2インバータと、

前記第2インバータの出力と、前記第2過電圧保護信号と、前記第2入力検出信号の論理積を生成する第2ANDゲートと、

前記第2ANDゲートの出力を反転し、前記第2スイッチのゲートに出力する第3インバータと、

を含むことを特徴とする請求項2に記載の充電回路。

【請求項4】

前記入力セレクタの出力端子と前記第2入力端子の間に、前記第2スイッチと直列に設けられた第3スイッチをさらに備えることを特徴とする請求項2または3に記載の充電回路。

【請求項5】

前記第3スイッチは、前記第1スイッチがオフの状態において、オンすることを特徴とする請求項4に記載の充電回路。

【請求項6】

前記降圧DC/DCコンバータは、前記システム電圧の目標電圧を、前記電池の電圧に応じて変化させることを特徴とする請求項1から5のいずれかに記載の充電回路。

【請求項7】

前記降圧DC/DCコンバータは、前記電池の電圧が所定のしきい値より低いとき、前記システム電圧の目標値を、前記しきい値電圧より所定の電圧幅高い値に設定し、

前記電池の電圧が所定のしきい値より高いとき、前記システム電圧の目標値を、前記電池の電圧より所定の電圧幅高い値に設定することを特徴とする請求項6に記載の充電回路。

【請求項8】

電池と、

前記電池を充電する請求項1から7のいずれかに記載の充電回路と、

を備えることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−99040(P2013−99040A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−237867(P2011−237867)

【出願日】平成23年10月28日(2011.10.28)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月28日(2011.10.28)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]