光または放射線検出器の製造方法

【課題】大面積の検出器を安価に製造することができる光または放射線検出器の製造方法を提供する。

【解決手段】本発明の検出器の製造方法によれば、絶縁基板に直接ではなく、第1凸版11の表面に成膜してからこれを絶縁基板に転写することで検出器が生成される。これにより、絶縁基板1に対する工程は全て大気中で行うことが可能である。そうすれば、大型の成膜装置が必要でなくなり、絶縁基板を自由に大型化することができるうえ、検出器の製造コストを抑制することができるのである。

【解決手段】本発明の検出器の製造方法によれば、絶縁基板に直接ではなく、第1凸版11の表面に成膜してからこれを絶縁基板に転写することで検出器が生成される。これにより、絶縁基板1に対する工程は全て大気中で行うことが可能である。そうすれば、大型の成膜装置が必要でなくなり、絶縁基板を自由に大型化することができるうえ、検出器の製造コストを抑制することができるのである。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、光または放射線を検出する検出素子が二次元状に配列されて構成される検出器の製造方法に関し、特に、絶縁層、配線、半導体層が基板上に積層されて構成される光または放射線検出器の製造方法に関する。

【背景技術】

【0002】

医療機関には、被検体の放射線画像を取得する放射線撮影装置が備えられている。この様な放射線撮影装置は、光または放射線(以下、放射線等と呼ぶ)を検出する検出素子が2次元状に配列されて構成される検出器が備えられている。

【0003】

この検出器の構成について説明する。検出器50は、図35に示すように、読み出し基板54に積層された変換層51を有している。変換層51は、検出器50に入射する放射線等を電荷に変換する層である。変換層で発生した電流は、変換層51に接するように設けられた読み出し基板54に向けて流れる。

【0004】

読み出し基板54には、電荷を蓄積するコンデンサ54cと、蓄積された電荷の取り出しを制御するためのトランジスタ54tが形成されている。このコンデンサ54cとトランジスタ54tは、読み出し基板54に絶縁層、配線、半導体層を積層することで構成されているものである。この様なコンデンサ54cとトランジスタ54tのセットが単一の検出素子を構成し、読み出し基板54には、これらが2次元的に配列されている。

【0005】

従来の読み出し基板54における各層の積層法について説明する。まず、各層の形状を模したマスクを用意して、フォトレジストを塗布した読み出し基板54を覆う。そして、露光処理、現像処理、エッチングを経て所望の形状の層を形成する。これを幾度か繰返して読み出し基板54上のコンデンサ54c,トランジスタ54tは製造されるのである(特許文献1参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−278428号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、従来の検出器の製造方法には次の様な問題点がある。すなわち、従来の検出器の製造方法によれば、高価な製造装置を必要としてしまい、製造コストが増加するという問題点がある。

【0008】

つまり、従来の製造方法によれば、成膜処理を真空中で行わなければならない。読み出し基板54全体を露光処理装置の内部に導入しなければならないのであるから、大型の検出器を製造するには、それだけ大きな露光処理装置が必要となる。この様な制約は、検出器の製造コストを増加させるだけでなく、製造可能な検出器の大きさの限界を決定してしまう。

【0009】

また、従来の製造方法には、各層をインクジェット方式による印刷処理で積層する方法が知られている。この方法によれば、真空中の処理が必要がないので、製造コストを抑制することができる。しかし、この方法では、読み出し基板54上に所望のパターンを正確に形成することが難しいという問題点がある。すなわち、インクジェット方式によれば、球体のインクの粒を読み出し基板54の表面に吹き付けて各層を形成する。したがって、読み出し基板54上では、球体のインクが繋がって直線や長方形を形作ることになる。つまり、インクジェット方式によって形成される各層のパターンの輪郭は蛇行したり、一部で滲んでしまったりして、正確なパターンを生成することが困難なのである。各コンデンサ54cや配線に形状のムラがあると、検出素子の検出特性にムラが現れることにもなりかねない。

【0010】

本発明は、この様な事情に鑑みてなされたものであって、その目的は、大面積の検出器を安価に製造することができる光または放射線検出器の製造方法を提供することにある。

【課題を解決するための手段】

【0011】

本発明は、上述の課題を解決するために次の様な構成をとる。

すなわち、本発明に係る光または放射線検出器の製造方法は、光または放射線を検出する検出素子が基板上に2次元マトリックス状に配列された光または放射線検出器の製造方法であって、検出器を構成する各層のうちの少なくとも1つは、版の表面に膜を生成する成膜工程と、版の表面に生成された膜を転写部材の表面に写し取る巻き取り工程と、転写部材に巻き取られた膜を基板の表面に写し取る転写工程とにより製造されることを特徴とするものである。

【0012】

[作用・効果]本発明の構成によれば、基板に直接ではなく、版の表面に成膜してからこれを基板に転写することで検出器が生成される。この様に構成すれば、版に成膜処理を施せばよいということになる。つまり、成膜処理を真空中で行わなければならなかったとしても、版を真空条件下に置くだけでよく、基板に対する工程は全て大気中で行うことが可能である。そうすれば、基板を成膜装置に導入させずして、真空中で成長した膜を基板上に配置することができる。つまり、基板を自由に大型化することができるうえ、検出器の製造コストを抑制することができるのである。

【0013】

また、上述の転写部材は、円筒形のローラであり、巻き取り工程、および転写工程は、ローラが版または基板の表面に押し当てられながら回転されることで行われればより望ましい。

【0014】

[作用・効果]上述の構成は、本発明の具体的な構成を示している。つまり、転写部材は円筒形のローラであり、これが版、または基板の表面に押し当てながら回転されることにより各工程が行われる。この様にすれば、膜は確実に基板の表面に転写される。

【0015】

また、上述の膜を表面に吸着させる吸着性は、版、転写部材、基板の順に強いものとなっていればより望ましい。

【0016】

[作用・効果]上述の構成は、本発明の具体的な構成を示している。すなわち、膜を表面に吸着させる吸着性は、版、転写部材、基板の順に強いものとなっている。吸着性は、版よりも転写部材の方が強力なので、巻き取り工程において、版の表面に存している膜は、版から剥離して転写部材の表面に吸着されることになる。また、吸着性は、転写部材よりも基板のほうが強力なので、転写工程において、転写部材の表面に存している膜は、転写部材から剥離して基板の表面に吸着されることになる。この様に、上述の構成によれば、版の表面の膜を確実に基板上に転写させることができるのである。

【0017】

また、上述の版は、基板に形成される膜の形状が凸部となった凸版であり、成膜工程は、真空中において凸版に膜を蒸着させることで行われればより望ましい。

【0018】

また、上述の版は、基板に形成される膜の形状が凹部となった凹版であり、成膜工程は、凹版の凹部にインクを流し込むことにより行われればより望ましい。

【0019】

[作用・効果]上述の構成によれば、インクジェットによる印刷で膜を成膜するよりも正確なパターンを生成することができる。インクジェットの印刷によって基板上に膜を生成すると、膜の輪郭が蛇行したり、滲んだりしてしまう。インクジェット方式においては、液状のインクの粒を基板に飛ばして成膜するからである。しかし、上述の構成によれば、凸版、または凹版を用いて成膜するので、膜のパターンは、正確なものとなる。

【0020】

また、上述の転写工程を基板の位置を変えながら繰り返し行うことにより、版で形成された膜のパターンが基板の表面に縦横に繰返されればより望ましい。

【0021】

[作用・効果]上述の構成によれば、転写工程を基板の位置を変えながら繰り返し行うことにより、版で形成された膜のパターンが基板の表面に縦横に繰返される。つまり、版は、基板よりも遥かに小さなものとすることができる。これにより、小型の成膜装置さえあれば大型の検出器を製造することができるようになるので、検出器の製造コストは大幅に抑制される。

【0022】

また、上述の検出素子は、電荷を蓄積するコンデンサを有し、コンデンサを構成する2つの電極は、成膜工程、巻き取り工程、転写工程により形成されたものであればより望ましい。

【0023】

[作用・効果]上述の構成によれば、コンデンサを構成する2つの電極は、成膜工程、巻き取り工程、転写工程により形成されたものである。コンデンサの物理的特性は、各検出素子の間で一定であることが望ましい。コンデンサの電気容量等が検出素子の各々でまちまちであれば、正確な画像を取得することができなくなる。本発明におけるコンデンサを構成する2つの電極は、信頼性の高い転写方式を用いているので、コンデンサの形状のバラツキは極力抑えられている。したがって、上述の製造方法によれば、正確な画像を取得することができる検出器が提供できる。

【図面の簡単な説明】

【0024】

【図1】実施例1に係る検出器の構成を説明する断面図である。

【図2】実施例1に係る検出器の構成を説明する模式図である。

【図3】実施例1に係る検出器の構成を説明する図である。

【図4】実施例1に係る検出器の構成を説明する模式図である。

【図5】実施例1に係る検出器の動作を説明する断面図である。

【図6】実施例1に係る検出器の動作を説明する断面図である。

【図7】実施例1に係る検出器の動作を説明する断面図である。

【図8】実施例1に係る検出器の製造方法を説明するフローチャートである。

【図9】実施例1に係る検出器の製造方法を説明するフローチャートである。

【図10】実施例1に係る検出器の製造方法を説明する断面図である。

【図11】実施例1に係る検出器の製造方法を説明する断面図である。

【図12】実施例1に係る検出器の製造方法を説明する断面図である。

【図13】実施例1に係る検出器の製造方法を説明する断面図である。

【図14】実施例1に係る検出器の製造方法を説明する平面図である。

【図15】実施例1に係る検出器の製造方法を説明する断面図である。

【図16】実施例1に係る検出器の製造方法を説明する断面図である。

【図17】実施例1に係る検出器の製造方法を説明する断面図である。

【図18】実施例1に係る検出器の製造方法を説明する断面図である。

【図19】実施例1に係る検出器の製造方法を説明する断面図である。

【図20】実施例1に係る検出器の製造方法を説明する断面図である。

【図21】実施例1に係る検出器の製造方法を説明する断面図である。

【図22】実施例1に係る検出器の製造方法を説明する平面図である。

【図23】実施例1に係る検出器の製造方法を説明する断面図である。

【図24】実施例1に係る検出器の製造方法を説明する平面図である。

【図25】実施例1に係る検出器の製造方法を説明する断面図である。

【図26】実施例1に係る検出器の製造方法を説明する平面図である。

【図27】実施例1に係る検出器の製造方法を説明する断面図である。

【図28】実施例1に係る検出器の製造方法を説明する断面図である。

【図29】実施例1に係る検出器の製造方法を説明する平面図である。

【図30】実施例2に係る検出器の製造方法を説明する断面図である。

【図31】実施例2に係る検出器の製造方法を説明する断面図である。

【図32】実施例2に係る検出器の製造方法を説明する断面図である。

【図33】実施例2に係る検出器の製造方法を説明する断面図である。

【図34】実施例2に係る検出器の製造方法を説明する断面図である。

【図35】従来構成に係る検出器の構成を説明する断面図である。

【実施例1】

【0025】

次に、実施例1に係る検出器の各実施例を図面を参照しながら説明する。なお、各実施例におけるX線は、実施例1の構成の放射線に相当する。FPDは、フラットパネル・ディテクタの略であり、本発明の検出器に相当する。

【0026】

<FPDの構成>

FPD4の構成について説明する。FPD4は、図1に示すように、アモルファスセレンで構成される変換層40と、この変換層40に積層されたアクティブマトリックス基板41と、変換層40を所定の電場に置くための平面電極42とを備えている。アクティブマトリックス基板41には、キャリア収集用の収集電極6が変換層40に接するように設けられている。この収集電極6は、アクティブマトリックス基板41の広がる平面に沿ってマトリックス状に配列されている。収集電極6の各々には、電荷を蓄積するコンデンサ41cが設けられている。コンデンサ41cの各々には電荷の取り出しを制御するトランジスタ41tが設けられている。したがって、コンデンサ41c,トランジスタ41tは、図2に示すように2次元的に配列されていることになる。なお、平面電極42は、絶縁層39に被覆されている。

【0027】

2次元的に配列されたトランジスタ41tは、縦横に格子状に伸びる配線に接続されている。すなわち、図2における一番左側において縦方向に配列したトランジスタ41tの読み出し電極αは、縦方向に伸びる配線に接続されており、全て共通のアンプ電極Q1に接続されており、同様に、各列のトランジスタ41tは縦方向に伸びる配線に接続されて共通のアンプ電極Q1〜Q4に接続されている。

【0028】

また、図2における一番上側の横方向に配列したトランジスタ41tのゲートGは、横方向に伸びる配線に接続されており、全て共通のゲート制御電極H1に接続され、同様に、各行のトランジスタ41tは横方向に伸びる配線に接続されて共通のゲート制御電極H1〜H4に接続されている。

【0029】

ゲート制御電極H1〜H4は、ゲートドライバ43に接続され、アンプ電極Q1〜Q4は、アンプアレイ44に接続される。

【0030】

各コンデンサ41cに電荷を読み出す動作について説明する。図2におけるコンデンサ41cの各々に電荷が蓄積されているものとする。ゲートドライバ43は、ゲート制御電極H1を通じて一番上側の横方向に配列した各トランジスタ41tを一斉にオンする。オンされた4つのトランジスタ41tは、アンプ電極Q1〜Q4を通じて、電荷(原信号)をアンプアレイ44に伝達する。

【0031】

次に、ゲートドライバ43は、ゲート制御電極H2を通じて二番目に上側の横方向にトランジスタ41tを一斉にオンする。この様に、ゲートドライバ43は、ゲート制御電極H1〜H4を順番にオンしていく。その度ごとに行の異なるトランジスタ41tがオンされる。こうして、FPD4は、コンデンサ41cの各々に蓄積された電荷を1行毎に読み出す構成となっている。

【0032】

アンプアレイ44には、アンプ電極Q1〜Q4の各々に、信号を増幅するアンプが設けられている。アンプ電極Q1〜Q4からアンプアレイ44に入力された原信号は、ここで所定の増幅率で増幅される。なお、図2においては、検出素子が4行4列で配列されているが、実際のFPD4においては、検出素子が1,024×1,024の縦横に配列されている。

【0033】

次に、アクティブマトリックス基板41の構成について説明する。アクティブマトリックス基板41は、図3(a)の断面図に示すように、絶縁基板1の一面に各層が積み重なって生成されている。すなわち、絶縁基板1の上表面(変換層40から見たときの絶縁基板1のオモテ面)には、導電性のゲート配線2a,およびグランド配線2bが生成されている。この配線2a,2bが設けられている層を第1層と呼ぶことにする。なお、配線2a,2bの上表面は、全て絶縁層7aによって覆われている。この様に、配線2a,2bは、絶縁基板1と絶縁層7aとに挟まれる位置に存する。ゲート配線2aは、ゲートドライバ43に電気的に接続される。絶縁基板1は、本発明の基板に相当する。第1層における配線2a,2bは、本発明の膜に相当する。

【0034】

絶縁層7aの上表面には、非導電性のゲート対向絶縁層3aとグランド対向絶縁層3bとが備えられている。ゲート対向絶縁層3aは、変換層40から見て、ゲート配線2aの一部に重なるように設けられており、ゲート対向絶縁層3a,ゲート配線2aの間には、絶縁層7aが存している。また、グランド対向絶縁層3bは、変換層40から見て、グランド配線2bの一部に重なるように設けられており、グランド対向絶縁層3b,グランド配線2bの間には、絶縁層7aが存している。

【0035】

半導体で構成されるチャンネル層4aは、変換層40から見て、ゲート対向絶縁層3aの全域を覆うように設けられており、両層3a,4aは、会合している。同様に、グランド対向導電層4bは、変換層40から見て、グランド対向絶縁層3bの全域を覆うように設けられており、両層3b,4bは、会合している。ゲート対向絶縁層3a,グランド対向絶縁層3b,チャンネル層4a,グランド対向導電層4bをまとめて第2層と呼ぶことにする。第2層における各層3a,3b,4a,4bは、本発明の膜に相当する。

【0036】

ソース配線5aは、図3(a)の紙面左右方向に飛び石のように並んで設けられたチャンネル層4aの各々を電気的に接続する配線である。電荷誘導層5bは、チャンネル層4aとグランド対向導電層4bとに跨るように各層4a,4bの上面上に設けられている。ソース配線5a,電荷誘導層5bは、アクティブマトリックス基板41の同一の深さに設けられている。そして、ソース配線5aと電荷誘導層5bとの間には間隙が設けられており、会合していない。したがって、電荷誘導層5bからソース配線5aに向けて電荷が流れる時には、必ずチャンネル層4aを通過しなければならないことになる。なお、ソース配線5aは、アンプアレイ44に接続されている。

【0037】

絶縁層7bは、ソース配線5aの全域とソース配線5aから露出したチャンネル層4aの一部を覆うように、これらの上面上に設けられている。電荷誘導層5bの輪郭もこの絶縁層7bに覆われることになる。

【0038】

電荷誘導層5bの上面上には、電荷を収集するための収集電極6が設けられている。収集電極6は、変換層40から見てマトリックス状に配列されている。絶縁層7cは、各収集電極6の隙間を埋めるように設けられている。

【0039】

変換層40は、収集電極6の各々を覆うように設けられており、変換層40は、収集電極6と電気的に接続されている。図3(a)は、単一の検出素子を表している。この様な構造が、変換層40から見たときに絶縁基板1にマトリックス状に配列されてアクティブマトリックス基板41が構成される。

【0040】

図3(b)は、図3(a)の等価回路に相当する。すなわち、ソース配線5a,電荷誘導層5b,チャンネル層4aがトランジスタ41tを構成し、グランド対向導電層4b,グランド配線2b(正確には、グランド配線2bのうちの矩形に膨張している部分:図3(c)参照)がコンデンサ41cを構成する。

【0041】

図3(c)は、各配線2a,2b,5aを変換層40から見たときの平面図である。同一平面上にある配線2a,2bは、縦方向に伸びており、ソース配線5aは、より変換層40に近い平面にあり、横方向に伸びている。図3(c)における矢印は、図3(a)における裁断位置を表している。

【0042】

図4の上側に示すのは、アクティブマトリックス基板41の表面に形成されたパターンを示している。一つのパターンには複数の図3(c)に示す構造が縦横に配列されている。そして、図4の上側のパターンが更に縦横に繰返されて、図4の下側に示すように、アクティブマトリックス基板41の全面を覆っている。図4の上側の構造を単位パターンと呼ぶことにする。説明の便宜上、単位パターンには、4×4の縦横に検出素子が並んでいるものとするが、本発明は、この構成に限られるものではない。

【0043】

<FPDの動作>

次に、FPD4の動作について説明する。図5は、変換層40に光または放射線が入射した状態を示している。変換層40に放射線等が入射すると、放射線等は、図5の黒い点で表した電荷に変換される。電荷は、平面電極42に反発して最寄の収集電極6に向かい、収集電極6,電荷誘導層5bを通じてグランド対向導電層4bに蓄積される(図6参照)。図6の状態においては、トランジスタ41tがOFF状態となっている。

【0044】

ゲート配線2aに電流が流され、トランジスタ41tがON状態となると、図7に示すように、グランド対向導電層4bに蓄えられた電荷が、電荷誘導層5b,チャンネル層4aを通じて、ソース配線5aに流れる。こうして、トランジスタ41tを制御することで、アクティブマトリックス基板41から電荷を取り出すことができるのである。

【0045】

<FPDの製造方法>

次に、FPD4の製造方法について説明する。本発明に係るFPD4は、その製造方法に特徴がある。具体的には、FPD4の製造方法は、図8に示すようにゲート配線2a等の第1層を生成する第1層生成工程S1と、各パターンを電気的に接続する接続工程S2と、チャンネル層4a等の第2層を生成する第2層生成工程S3と、ソース配線を配線するソース配線工程S4と、収集電極6を生成する収集電極生成工程S5とを備えている。

【0046】

第1層生成工程S1,および第2層生成工程S3は、ほぼ同様な工程であり、図9に示すように、各層を生成する成膜工程Saと、各層をローラで巻き取る巻き取り工程Sbと、絶縁基板1の上面上に各層を転写させる転写工程Scとを備えている。以降、各工程の詳細を順を追って説明する。

【0047】

<第1層生成工程S1>

<成膜工程S1a>

まず、配線2a,2bを生成する。図10は、配線2a,2bを生成するための第1凸版11である。第1凸版11の表面には、配線2a,2bの形状をした凸部が設けられている。そして、第1凸版11の表面には、4×4に縦横に並んだ検出素子を構成するパターンが現れている。したがって、ゲート配線2aの形状をした図10の紙面貫通方向に伸びる凸部と、グランド配線2bの形状をした図10の紙面貫通方向に伸びる凸部とが第1凸版11の表面に交互に配列されている。第1凸版11は、本発明の版に相当する。

【0048】

各配線は蒸着法やスパッタ法等により生成される。すなわち、第1凸版11を成膜装置の容器内に導入し、容器を真空とする。そして、原料を第1凸版11に吹き付けて堆積させる。成膜工程S1aが終了すると、図11のように導電性のゲート配線2a,グランド配線2bが第1凸版11の表面に現れる。第1凸版11には、凹凸が設けられているので、導電性物質が堆積する際に、凸部と凹部の間で段切れが起こる。これにより、配線2a,2bの形状および配列が凸部の表面に形成されるのである。

【0049】

<巻き取り工程S1b>

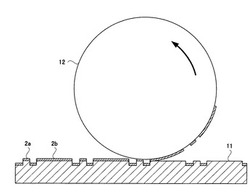

第1凸版11を大気中に戻して、図12に示すように、円筒形状のローラ12を第1凸版11の表面に押し当てながら回転させる。ローラ12は、第1凸版11よりも強く配線2a,2bに吸着するので、第1凸版11の表面に存していた配線2a,2bは、第1凸版11の表面から剥離して、ローラ12の表面側に巻き取られることになる。ローラ12は、本発明の転写部材に相当する。

【0050】

<転写工程S1c>

次に、図13に示すように、ローラ12を絶縁性の絶縁基板1の上面上に押し当てながら回転させる。絶縁基板1は、ローラ12よりも強く配線2a,2bに吸着するので、ローラ12の表面に存していた配線2a,2bは、ローラ12の表面から剥離して、絶縁基板1の上面上に転写されることになる。

【0051】

ローラ12の表面には、半導体用転写フィルムが巻きつけられている。このフィルムを交換すれば、配線2a,2bとローラ12の吸着性を自由に変更することができる。具体的には、ローラ12が配線2a,2bを吸着する吸着性は、第1凸版11の表面のそれよりも強く、絶縁基板1のそれよりも弱い。

【0052】

こうしてローラ12は、将来的には4×4の検出素子を構成することになる第1層の単位パターンを絶縁基板1に転写する。成膜工程S1a,巻き取り工程S1b,転写工程S1cを幾度も繰返すことで、絶縁基板1は、マトリックス状に配列された単位パターンで埋め尽くされることになる。

【0053】

<接続工程S2>

図14は、絶縁基板1を変換層40側から見たときの平面図である。縦方向に伸びた配線2a,2bが交互に配列している。図14は、単位パターンのつなぎ目を現している。すなわち、図14の上半分は単位パターンRaであり、下半分は単位パターンRbとなっている。接続工程S2では、単位パターン同士の導電性を確保する目的で、単位パターンのつなぎ目に導電性のインクを印刷する。実際の印刷方法としてはインクジェット方式の印刷機を使用することができる。こうして、単位パターンを跨いで縦方向(ゲート配線2aの伸びる方向)に連接するゲート配線2aの各々が、本工程で単一の配線となるのである。同様に、単位パターンを跨いで縦方向(グランド配線2bの伸びる方向)に連接するグランド配線2bの伸びる方向の各々が、本工程で単一の配線となるのである。

【0054】

<前処理>

第2層生成工程S3を行う前に、図15に示すように、ポリイミド等の液体の非導電性インクを絶縁基板1に塗布しておく。この非導電性インクは、将来的に絶縁層7aとなる。非導電性インクは、配線2a,2bが設けられている部分において、盛り上がる特性がある。

【0055】

<第2層生成工程S3>

<成膜工程S3a>

次に、各層3a,3b,4a,4bを生成する。図16は、各層3a,3b,4a,4bを生成するための第2凸版13である。第2凸版13には、各層3a,3b,4a,4bの形状をした凸部が設けられている。第2凸版13には、4×4に縦横に並んだ検出素子を構成する単位パターンが現れている。したがって、第2凸版13には、各層3b,4bとなる大きな矩形が2次元的に配列されており、各層3a,4aとなる小さな矩形が各層3b,4bの隙間に1つずつ配置されて、第2凸版13を全体として眺めれば、各凸部が2次元的に配列されている構成となっている。

【0056】

各層3a,3b,4a,4bは蒸着法やスパッタ法等により生成される。すなわち、第2凸版13を成膜装置の容器内に導入し、容器を真空とする。そして、原料を第2凸版13に吹き付けて堆積させる。成膜工程S3aが終了すると、図17のように非導電性のゲート対向絶縁層3aとグランド対向絶縁層3bが第2凸版13の表面に現れる。第2凸版13には、凹凸が設けられているので、導電性物質が堆積する際に、凸部と凹部の間で段切れが起こる。これにより、ゲート対向絶縁層3aとグランド対向絶縁層3bの形状および配列が凸部の表面に形成されるのである。

【0057】

各絶縁層3a,3bが生成された後、図18に示すように、第1遮蔽材14aを第2凸版13の上面上に配置することでゲート対向絶縁層3aをマスクして、蒸着法やスパッタ法等により、導電性のグランド対向導電層4bをグランド対向絶縁層3bの上面上に成長させる。その後、図19に示すように、第2遮蔽材14bを第2凸版13の上面上に配置することでグランド対向導電層4bをマスクして、蒸着法やスパッタ法等により、半導電性のチャンネル層4aをゲート対向絶縁層3aの上面上に成長させる。チャンネル層4aは、半導体層となっている。

【0058】

<巻き取り工程S3b>

第2凸版13を大気中に戻して、図20に示すように、円筒形状のローラ12を第2凸版13の表面に押し当てながら回転させる。ローラ12は第2凸版13よりも強く各層3a,3b,4a,4bに吸着するので、第2凸版13の表面に存していた各層3a,3b,4a,4bは、第2凸版13の表面から剥離して、ローラ12の表面側に巻き取られることになる。

【0059】

<転写工程S3c>

次に、図21に示すように、ローラ12を絶縁基板1の上面上に押し当てながら回転させる。絶縁基板1は、ローラ12よりも強く各層3a,3b,4a,4bに吸着するので、ローラ12の表面に存していた各層3a,3b,4a,4bは、ローラ12の表面から剥離して、絶縁基板1の上面上に転写されることになる。

【0060】

ローラ12の表面には、半導体用転写フィルムが巻きつけられている。このフィルムを交換すれば、各層3a,3b,4a,4bとローラ12の吸着性を自由に変更することができる。

【0061】

こうしてローラ12は、将来的には4×4の前記検出素子を構成することになる第2層の単位パターンを絶縁基板1に転写する。成膜工程S3a,巻き取り工程S3b,転写工程S3cを幾度も繰返すことで、絶縁基板1は、マトリックス状に配列された単位パターンで埋め尽くされることになる。図22は、本工程まで終了した状態において、絶縁基板1を変換層40側から見たときの平面図である。図22が示すように、大きな矩形のグランド対向絶縁層3bの隣に小さな矩形のチャンネル層4aが存するパターンがマトリックス状に配列している構成となっている。

【0062】

<ソース配線工程S4>

転写が終了すると、図23に示すように、絶縁基板1の上面上に、ソース配線5a,電荷誘導層5bがインクジェット方式により印刷される。ソース配線5aは、チャンネル層4aの一端を覆う様に構成され、電荷誘導層5bは、チャンネル層4aの他端からグランド対向導電層4bの全域にかけて各層4a,4bに跨るように構成される。図24は、本工程まで終了した状態において、絶縁基板1を変換層40側から見たときの平面図である。図24が示すように、矩形状の電荷誘導層5bがマトリックス状に配置し、各電荷誘導層5bの間には、横方向に伸びるソース配線5aが配線されている。グランド対向導電層4bは電荷誘導層5bにより全て隠され、チャンネル層4aの一部は、ソース配線5aと電荷誘導層5bとによって隠されている。

【0063】

<前処理>

収集電極生成工程S5を行う前に、図25に示すように、液体の非導電性インクをインクジェット方式により絶縁基板1に塗布しておく。この非導電性インクは、将来的に絶縁層7bとなる。絶縁基板1の上面上に露出していたソース配線5aとチャンネル層4aは絶縁層7bによって完全に覆われ、電荷誘導層5bの輪郭も絶縁層7bによって覆われる。図26は、本工程まで終了した状態において、絶縁基板1を変換層40側から見たときの平面図である。図26が示すように、矩形の電荷誘導層5bがマトリックス状に配列している構成となっている。

【0064】

<収集電極生成工程S5>

次に、図27に示すように、絶縁基板1の上面上に露出した電荷誘導層5bを覆い隠すように、導電性の収集電極6を配置する。収集電極6は、絶縁基板1の上面上において、マトリックス状に配列することになる。この時点で、収集電極6は、絶縁基板1上から盛り上がっている。

【0065】

その後、図28に示すように、隣り合う収集電極6同士における隙間を埋めるように非導電性インクをインクジェット方式により絶縁基板1に印刷する。この非導電性インクは、将来的に絶縁層7cとなる。図29は、本工程まで終了した状態において、絶縁基板1を変換層40側から見たときの平面図である。図29が示すように、矩形の収集電極6がマトリックス状に配列している構成となっている。これをもって、アクティブマトリックス基板41は完成となる。アクティブマトリックス基板41の上面上に変換層40等の各層を形成し、本発明のFPD4は、完成となる。

【0066】

以上のように、実施例1の構成によれば、絶縁基板1に直接ではなく、凸版11,13の表面に成膜してからこれを絶縁基板1に転写することで検出器が生成される。この様に構成すれば、凸版11,13に成膜処理を施せばよいということになる。つまり、成膜処理を真空中で行わなければならなかったとしても、凸版11,13を真空条件下に置くだけでよく、絶縁基板1に対する工程は全て大気中で行うことが可能である。そうすれば、絶縁基板1を成膜装置に導入させずして、真空中で成長した膜を基板上に配置することができる。つまり、絶縁基板1を自由に大型化することができるうえ、検出器の製造コストを抑制することができるのである。

【0067】

また、本発明の転写部材は円筒形のローラ12であり、これが凸版11,13,または絶縁基板1の表面に押し当てながら回転されることにより各工程が行われる。この様にすれば、膜は確実に絶縁基板1の表面に転写される。

【0068】

上述の構成における膜を表面に吸着させる吸着性は、凸版11,13,ローラ12,絶縁基板1の順に強いものとなっている。吸着性は、凸版11,13よりもローラ12の方が強力なので、巻き取り工程Sbにおいて、凸版11,13の表面に存している膜は、凸版11,13から剥離してローラ12の表面に吸着されることになる。また、吸着性は、ローラ12よりも絶縁基板1のほうが強力なので、転写工程Scにおいて、ローラ12の表面に存している膜は、ローラ12から剥離して絶縁基板1の表面に吸着されることになる。この様に、上述の構成によれば、凸版11,13の表面の膜を確実に基板上に転写させることができるのである。

【0069】

すなわち、上述の構成によれば、インクジェットによる印刷で膜を成膜するよりも正確なパターンを生成することができる。インクジェットの印刷によって基板上に膜を生成すると、膜の輪郭が蛇行したり、滲んだりしてしまう。インクジェット方式においては、液状のインクの粒を絶縁基板1に飛ばして成膜するからである。実施例1の構成によれば、より正確な成膜が可能な転写方式を利用することができる。

【0070】

そして、上述の構成によれば、転写工程Scを絶縁基板1の位置を変えながら繰り返し行うことにより、凸版11,13で形成された膜のパターンが絶縁基板1の表面に縦横に繰返される。つまり、凸版11,13は、絶縁基板1よりも遥かに小さなものとすることができる。これにより、小型の成膜装置さえあれば大型の検出器を製造することができるようになるので、検出器の製造コストは大幅に抑制される。

【0071】

上述の構成によれば、コンデンサ41cを構成する2つの電極は、成膜工程Sa,巻き取り工程Sb,転写工程Scにより形成されたものである。コンデンサ41cの物理的特性は、各検出素子の間で一定であることが望ましい。コンデンサ41cの電気容量等が検出素子の各々でまちまちであれば、正確な画像を取得することができなくなる。本発明におけるコンデンサ41cを構成する2つの電極は、信頼性の高い転写方式を用いているので、コンデンサ41cの形状のバラツキは極力抑えられている。したがって、上述の製造方法によれば、正確な画像を取得することができる検出器が提供できる。

【実施例2】

【0072】

上述の実施例1の第1層生成工程S1では、第1凸版11を用いていたが、これに代えて凹版を用いることもできる。以降、凹版を用いた場合の製造方法について説明する。

【0073】

<成膜工程S1a>

図30は、配線2a,2bを生成するための第1凹版11aである。第1凹版11aには、配線2a,2bの形状をした凹部が設けられている。第1凹版11aには、4×4に縦横に並んだ検出素子を構成する単位パターンが刻まれている。したがって、第1凹版11aには、ゲート配線2aの形状をした図10の紙面貫通方向に伸びる凹部と、グランド配線2bの形状をした図10の紙面貫通方向に伸びる凹部とが交互に配列されている。第1凹版11aは、本発明の版に相当する。

【0074】

この第1凹版11aには、導電性のインク15が塗布される。すると、図31に示すように、凹部の全てにインク15が流し込まれることになる。この状態で図32に示すように、短冊状のブレード16の先端を第1凹版11aの表面に接触させながら移動させると、ブレード16によって第1凹版11aの表面上の余分なインク15が追いやられて、図33に示すように、凹部にのみインク15が溜まった状態となる。

【0075】

<巻き取り工程S1b>

次に、図34に示すように、円筒形状のローラ12を第1凹版11aの表面に押し当てながら回転させる。ローラ12は第1凹版11aよりも強く配線2a,2bに吸着するので、第1凹版11aの表面に存していた配線2a,2bは、第1凹版11aの表面から脱離して、ローラ12の表面側に巻き取られることになる。このとき、インク15の乾燥を待つ必要は必ずしもない。

【0076】

<転写工程S1c>

次に、図13に示すように、ローラ12を絶縁基板1の上面上に押し当てながら回転させる。絶縁基板1は、ローラ12よりも強く配線2a,2bに吸着するので、ローラ12の表面に存していた配線2a,2bは、ローラ12の表面から剥離して、絶縁基板1の上面上に転写されることになる。

【0077】

ローラ12の表面には、インク用転写フィルムが巻きつけられてる。このフィルムを交換すれば、配線2a,2bとローラ12の吸着性を自由に変更することができる。具体的には、ローラ12が配線2a,2bを吸着する吸着性は、第1凹版11aの表面のそれよりも強く、絶縁基板1のそれよりも弱い。

【0078】

こうしてローラ12は、将来的には4×4の検出素子を構成することになる第1層の単位パターンを絶縁基板1に転写する。成膜工程S1a,巻き取り工程S1b,転写工程S1cを幾度も繰返すことで、絶縁基板1は、マトリックス状に配列された単位パターンで埋め尽くされることになる。

【0079】

その後の製造方法は、実施例1における図14以降の説明と同様である。

【0080】

以上のように、実施例2の構成によれば、全て大気中で各工程を行うことができる。実施例2によれば、大掛かりな装置を必要としないので、検出器を安価に製造することができる。

【0081】

本発明は、上述の構成に限られず、下記の様に変形実施することができる。

【0082】

(1)上述した実施例では、アクティブマトリックス基板を製造していたが、これに代えてパッシブマトリックス基板を製造してもよい。

【0083】

(2)上述した実施例では、ボトムゲート型アクティブマトリックス基板を製造していたが、これに代えてトップゲート型アクティブマトリックス基板を製造してもよい。

【0084】

(3)上述した実施例では、第1層、第2層を生成する際には、検出素子16個分のパターンを一度に転写していたが、本発明はこの構成に限られない。すなわち、一度に転写される検出素子の個数を増減することができる。更に、第1層と第2層で一度に転写される検出素子の個数を違えることもできる。

【符号の説明】

【0085】

Sa 成膜工程

Sb 巻き取り工程

Sc 転写工程

1 絶縁基板(基板)

11 凸版(版)

12 ローラ(転写部材)

13 凹版(版)

41c コンデンサ

【技術分野】

【0001】

この発明は、光または放射線を検出する検出素子が二次元状に配列されて構成される検出器の製造方法に関し、特に、絶縁層、配線、半導体層が基板上に積層されて構成される光または放射線検出器の製造方法に関する。

【背景技術】

【0002】

医療機関には、被検体の放射線画像を取得する放射線撮影装置が備えられている。この様な放射線撮影装置は、光または放射線(以下、放射線等と呼ぶ)を検出する検出素子が2次元状に配列されて構成される検出器が備えられている。

【0003】

この検出器の構成について説明する。検出器50は、図35に示すように、読み出し基板54に積層された変換層51を有している。変換層51は、検出器50に入射する放射線等を電荷に変換する層である。変換層で発生した電流は、変換層51に接するように設けられた読み出し基板54に向けて流れる。

【0004】

読み出し基板54には、電荷を蓄積するコンデンサ54cと、蓄積された電荷の取り出しを制御するためのトランジスタ54tが形成されている。このコンデンサ54cとトランジスタ54tは、読み出し基板54に絶縁層、配線、半導体層を積層することで構成されているものである。この様なコンデンサ54cとトランジスタ54tのセットが単一の検出素子を構成し、読み出し基板54には、これらが2次元的に配列されている。

【0005】

従来の読み出し基板54における各層の積層法について説明する。まず、各層の形状を模したマスクを用意して、フォトレジストを塗布した読み出し基板54を覆う。そして、露光処理、現像処理、エッチングを経て所望の形状の層を形成する。これを幾度か繰返して読み出し基板54上のコンデンサ54c,トランジスタ54tは製造されるのである(特許文献1参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−278428号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、従来の検出器の製造方法には次の様な問題点がある。すなわち、従来の検出器の製造方法によれば、高価な製造装置を必要としてしまい、製造コストが増加するという問題点がある。

【0008】

つまり、従来の製造方法によれば、成膜処理を真空中で行わなければならない。読み出し基板54全体を露光処理装置の内部に導入しなければならないのであるから、大型の検出器を製造するには、それだけ大きな露光処理装置が必要となる。この様な制約は、検出器の製造コストを増加させるだけでなく、製造可能な検出器の大きさの限界を決定してしまう。

【0009】

また、従来の製造方法には、各層をインクジェット方式による印刷処理で積層する方法が知られている。この方法によれば、真空中の処理が必要がないので、製造コストを抑制することができる。しかし、この方法では、読み出し基板54上に所望のパターンを正確に形成することが難しいという問題点がある。すなわち、インクジェット方式によれば、球体のインクの粒を読み出し基板54の表面に吹き付けて各層を形成する。したがって、読み出し基板54上では、球体のインクが繋がって直線や長方形を形作ることになる。つまり、インクジェット方式によって形成される各層のパターンの輪郭は蛇行したり、一部で滲んでしまったりして、正確なパターンを生成することが困難なのである。各コンデンサ54cや配線に形状のムラがあると、検出素子の検出特性にムラが現れることにもなりかねない。

【0010】

本発明は、この様な事情に鑑みてなされたものであって、その目的は、大面積の検出器を安価に製造することができる光または放射線検出器の製造方法を提供することにある。

【課題を解決するための手段】

【0011】

本発明は、上述の課題を解決するために次の様な構成をとる。

すなわち、本発明に係る光または放射線検出器の製造方法は、光または放射線を検出する検出素子が基板上に2次元マトリックス状に配列された光または放射線検出器の製造方法であって、検出器を構成する各層のうちの少なくとも1つは、版の表面に膜を生成する成膜工程と、版の表面に生成された膜を転写部材の表面に写し取る巻き取り工程と、転写部材に巻き取られた膜を基板の表面に写し取る転写工程とにより製造されることを特徴とするものである。

【0012】

[作用・効果]本発明の構成によれば、基板に直接ではなく、版の表面に成膜してからこれを基板に転写することで検出器が生成される。この様に構成すれば、版に成膜処理を施せばよいということになる。つまり、成膜処理を真空中で行わなければならなかったとしても、版を真空条件下に置くだけでよく、基板に対する工程は全て大気中で行うことが可能である。そうすれば、基板を成膜装置に導入させずして、真空中で成長した膜を基板上に配置することができる。つまり、基板を自由に大型化することができるうえ、検出器の製造コストを抑制することができるのである。

【0013】

また、上述の転写部材は、円筒形のローラであり、巻き取り工程、および転写工程は、ローラが版または基板の表面に押し当てられながら回転されることで行われればより望ましい。

【0014】

[作用・効果]上述の構成は、本発明の具体的な構成を示している。つまり、転写部材は円筒形のローラであり、これが版、または基板の表面に押し当てながら回転されることにより各工程が行われる。この様にすれば、膜は確実に基板の表面に転写される。

【0015】

また、上述の膜を表面に吸着させる吸着性は、版、転写部材、基板の順に強いものとなっていればより望ましい。

【0016】

[作用・効果]上述の構成は、本発明の具体的な構成を示している。すなわち、膜を表面に吸着させる吸着性は、版、転写部材、基板の順に強いものとなっている。吸着性は、版よりも転写部材の方が強力なので、巻き取り工程において、版の表面に存している膜は、版から剥離して転写部材の表面に吸着されることになる。また、吸着性は、転写部材よりも基板のほうが強力なので、転写工程において、転写部材の表面に存している膜は、転写部材から剥離して基板の表面に吸着されることになる。この様に、上述の構成によれば、版の表面の膜を確実に基板上に転写させることができるのである。

【0017】

また、上述の版は、基板に形成される膜の形状が凸部となった凸版であり、成膜工程は、真空中において凸版に膜を蒸着させることで行われればより望ましい。

【0018】

また、上述の版は、基板に形成される膜の形状が凹部となった凹版であり、成膜工程は、凹版の凹部にインクを流し込むことにより行われればより望ましい。

【0019】

[作用・効果]上述の構成によれば、インクジェットによる印刷で膜を成膜するよりも正確なパターンを生成することができる。インクジェットの印刷によって基板上に膜を生成すると、膜の輪郭が蛇行したり、滲んだりしてしまう。インクジェット方式においては、液状のインクの粒を基板に飛ばして成膜するからである。しかし、上述の構成によれば、凸版、または凹版を用いて成膜するので、膜のパターンは、正確なものとなる。

【0020】

また、上述の転写工程を基板の位置を変えながら繰り返し行うことにより、版で形成された膜のパターンが基板の表面に縦横に繰返されればより望ましい。

【0021】

[作用・効果]上述の構成によれば、転写工程を基板の位置を変えながら繰り返し行うことにより、版で形成された膜のパターンが基板の表面に縦横に繰返される。つまり、版は、基板よりも遥かに小さなものとすることができる。これにより、小型の成膜装置さえあれば大型の検出器を製造することができるようになるので、検出器の製造コストは大幅に抑制される。

【0022】

また、上述の検出素子は、電荷を蓄積するコンデンサを有し、コンデンサを構成する2つの電極は、成膜工程、巻き取り工程、転写工程により形成されたものであればより望ましい。

【0023】

[作用・効果]上述の構成によれば、コンデンサを構成する2つの電極は、成膜工程、巻き取り工程、転写工程により形成されたものである。コンデンサの物理的特性は、各検出素子の間で一定であることが望ましい。コンデンサの電気容量等が検出素子の各々でまちまちであれば、正確な画像を取得することができなくなる。本発明におけるコンデンサを構成する2つの電極は、信頼性の高い転写方式を用いているので、コンデンサの形状のバラツキは極力抑えられている。したがって、上述の製造方法によれば、正確な画像を取得することができる検出器が提供できる。

【図面の簡単な説明】

【0024】

【図1】実施例1に係る検出器の構成を説明する断面図である。

【図2】実施例1に係る検出器の構成を説明する模式図である。

【図3】実施例1に係る検出器の構成を説明する図である。

【図4】実施例1に係る検出器の構成を説明する模式図である。

【図5】実施例1に係る検出器の動作を説明する断面図である。

【図6】実施例1に係る検出器の動作を説明する断面図である。

【図7】実施例1に係る検出器の動作を説明する断面図である。

【図8】実施例1に係る検出器の製造方法を説明するフローチャートである。

【図9】実施例1に係る検出器の製造方法を説明するフローチャートである。

【図10】実施例1に係る検出器の製造方法を説明する断面図である。

【図11】実施例1に係る検出器の製造方法を説明する断面図である。

【図12】実施例1に係る検出器の製造方法を説明する断面図である。

【図13】実施例1に係る検出器の製造方法を説明する断面図である。

【図14】実施例1に係る検出器の製造方法を説明する平面図である。

【図15】実施例1に係る検出器の製造方法を説明する断面図である。

【図16】実施例1に係る検出器の製造方法を説明する断面図である。

【図17】実施例1に係る検出器の製造方法を説明する断面図である。

【図18】実施例1に係る検出器の製造方法を説明する断面図である。

【図19】実施例1に係る検出器の製造方法を説明する断面図である。

【図20】実施例1に係る検出器の製造方法を説明する断面図である。

【図21】実施例1に係る検出器の製造方法を説明する断面図である。

【図22】実施例1に係る検出器の製造方法を説明する平面図である。

【図23】実施例1に係る検出器の製造方法を説明する断面図である。

【図24】実施例1に係る検出器の製造方法を説明する平面図である。

【図25】実施例1に係る検出器の製造方法を説明する断面図である。

【図26】実施例1に係る検出器の製造方法を説明する平面図である。

【図27】実施例1に係る検出器の製造方法を説明する断面図である。

【図28】実施例1に係る検出器の製造方法を説明する断面図である。

【図29】実施例1に係る検出器の製造方法を説明する平面図である。

【図30】実施例2に係る検出器の製造方法を説明する断面図である。

【図31】実施例2に係る検出器の製造方法を説明する断面図である。

【図32】実施例2に係る検出器の製造方法を説明する断面図である。

【図33】実施例2に係る検出器の製造方法を説明する断面図である。

【図34】実施例2に係る検出器の製造方法を説明する断面図である。

【図35】従来構成に係る検出器の構成を説明する断面図である。

【実施例1】

【0025】

次に、実施例1に係る検出器の各実施例を図面を参照しながら説明する。なお、各実施例におけるX線は、実施例1の構成の放射線に相当する。FPDは、フラットパネル・ディテクタの略であり、本発明の検出器に相当する。

【0026】

<FPDの構成>

FPD4の構成について説明する。FPD4は、図1に示すように、アモルファスセレンで構成される変換層40と、この変換層40に積層されたアクティブマトリックス基板41と、変換層40を所定の電場に置くための平面電極42とを備えている。アクティブマトリックス基板41には、キャリア収集用の収集電極6が変換層40に接するように設けられている。この収集電極6は、アクティブマトリックス基板41の広がる平面に沿ってマトリックス状に配列されている。収集電極6の各々には、電荷を蓄積するコンデンサ41cが設けられている。コンデンサ41cの各々には電荷の取り出しを制御するトランジスタ41tが設けられている。したがって、コンデンサ41c,トランジスタ41tは、図2に示すように2次元的に配列されていることになる。なお、平面電極42は、絶縁層39に被覆されている。

【0027】

2次元的に配列されたトランジスタ41tは、縦横に格子状に伸びる配線に接続されている。すなわち、図2における一番左側において縦方向に配列したトランジスタ41tの読み出し電極αは、縦方向に伸びる配線に接続されており、全て共通のアンプ電極Q1に接続されており、同様に、各列のトランジスタ41tは縦方向に伸びる配線に接続されて共通のアンプ電極Q1〜Q4に接続されている。

【0028】

また、図2における一番上側の横方向に配列したトランジスタ41tのゲートGは、横方向に伸びる配線に接続されており、全て共通のゲート制御電極H1に接続され、同様に、各行のトランジスタ41tは横方向に伸びる配線に接続されて共通のゲート制御電極H1〜H4に接続されている。

【0029】

ゲート制御電極H1〜H4は、ゲートドライバ43に接続され、アンプ電極Q1〜Q4は、アンプアレイ44に接続される。

【0030】

各コンデンサ41cに電荷を読み出す動作について説明する。図2におけるコンデンサ41cの各々に電荷が蓄積されているものとする。ゲートドライバ43は、ゲート制御電極H1を通じて一番上側の横方向に配列した各トランジスタ41tを一斉にオンする。オンされた4つのトランジスタ41tは、アンプ電極Q1〜Q4を通じて、電荷(原信号)をアンプアレイ44に伝達する。

【0031】

次に、ゲートドライバ43は、ゲート制御電極H2を通じて二番目に上側の横方向にトランジスタ41tを一斉にオンする。この様に、ゲートドライバ43は、ゲート制御電極H1〜H4を順番にオンしていく。その度ごとに行の異なるトランジスタ41tがオンされる。こうして、FPD4は、コンデンサ41cの各々に蓄積された電荷を1行毎に読み出す構成となっている。

【0032】

アンプアレイ44には、アンプ電極Q1〜Q4の各々に、信号を増幅するアンプが設けられている。アンプ電極Q1〜Q4からアンプアレイ44に入力された原信号は、ここで所定の増幅率で増幅される。なお、図2においては、検出素子が4行4列で配列されているが、実際のFPD4においては、検出素子が1,024×1,024の縦横に配列されている。

【0033】

次に、アクティブマトリックス基板41の構成について説明する。アクティブマトリックス基板41は、図3(a)の断面図に示すように、絶縁基板1の一面に各層が積み重なって生成されている。すなわち、絶縁基板1の上表面(変換層40から見たときの絶縁基板1のオモテ面)には、導電性のゲート配線2a,およびグランド配線2bが生成されている。この配線2a,2bが設けられている層を第1層と呼ぶことにする。なお、配線2a,2bの上表面は、全て絶縁層7aによって覆われている。この様に、配線2a,2bは、絶縁基板1と絶縁層7aとに挟まれる位置に存する。ゲート配線2aは、ゲートドライバ43に電気的に接続される。絶縁基板1は、本発明の基板に相当する。第1層における配線2a,2bは、本発明の膜に相当する。

【0034】

絶縁層7aの上表面には、非導電性のゲート対向絶縁層3aとグランド対向絶縁層3bとが備えられている。ゲート対向絶縁層3aは、変換層40から見て、ゲート配線2aの一部に重なるように設けられており、ゲート対向絶縁層3a,ゲート配線2aの間には、絶縁層7aが存している。また、グランド対向絶縁層3bは、変換層40から見て、グランド配線2bの一部に重なるように設けられており、グランド対向絶縁層3b,グランド配線2bの間には、絶縁層7aが存している。

【0035】

半導体で構成されるチャンネル層4aは、変換層40から見て、ゲート対向絶縁層3aの全域を覆うように設けられており、両層3a,4aは、会合している。同様に、グランド対向導電層4bは、変換層40から見て、グランド対向絶縁層3bの全域を覆うように設けられており、両層3b,4bは、会合している。ゲート対向絶縁層3a,グランド対向絶縁層3b,チャンネル層4a,グランド対向導電層4bをまとめて第2層と呼ぶことにする。第2層における各層3a,3b,4a,4bは、本発明の膜に相当する。

【0036】

ソース配線5aは、図3(a)の紙面左右方向に飛び石のように並んで設けられたチャンネル層4aの各々を電気的に接続する配線である。電荷誘導層5bは、チャンネル層4aとグランド対向導電層4bとに跨るように各層4a,4bの上面上に設けられている。ソース配線5a,電荷誘導層5bは、アクティブマトリックス基板41の同一の深さに設けられている。そして、ソース配線5aと電荷誘導層5bとの間には間隙が設けられており、会合していない。したがって、電荷誘導層5bからソース配線5aに向けて電荷が流れる時には、必ずチャンネル層4aを通過しなければならないことになる。なお、ソース配線5aは、アンプアレイ44に接続されている。

【0037】

絶縁層7bは、ソース配線5aの全域とソース配線5aから露出したチャンネル層4aの一部を覆うように、これらの上面上に設けられている。電荷誘導層5bの輪郭もこの絶縁層7bに覆われることになる。

【0038】

電荷誘導層5bの上面上には、電荷を収集するための収集電極6が設けられている。収集電極6は、変換層40から見てマトリックス状に配列されている。絶縁層7cは、各収集電極6の隙間を埋めるように設けられている。

【0039】

変換層40は、収集電極6の各々を覆うように設けられており、変換層40は、収集電極6と電気的に接続されている。図3(a)は、単一の検出素子を表している。この様な構造が、変換層40から見たときに絶縁基板1にマトリックス状に配列されてアクティブマトリックス基板41が構成される。

【0040】

図3(b)は、図3(a)の等価回路に相当する。すなわち、ソース配線5a,電荷誘導層5b,チャンネル層4aがトランジスタ41tを構成し、グランド対向導電層4b,グランド配線2b(正確には、グランド配線2bのうちの矩形に膨張している部分:図3(c)参照)がコンデンサ41cを構成する。

【0041】

図3(c)は、各配線2a,2b,5aを変換層40から見たときの平面図である。同一平面上にある配線2a,2bは、縦方向に伸びており、ソース配線5aは、より変換層40に近い平面にあり、横方向に伸びている。図3(c)における矢印は、図3(a)における裁断位置を表している。

【0042】

図4の上側に示すのは、アクティブマトリックス基板41の表面に形成されたパターンを示している。一つのパターンには複数の図3(c)に示す構造が縦横に配列されている。そして、図4の上側のパターンが更に縦横に繰返されて、図4の下側に示すように、アクティブマトリックス基板41の全面を覆っている。図4の上側の構造を単位パターンと呼ぶことにする。説明の便宜上、単位パターンには、4×4の縦横に検出素子が並んでいるものとするが、本発明は、この構成に限られるものではない。

【0043】

<FPDの動作>

次に、FPD4の動作について説明する。図5は、変換層40に光または放射線が入射した状態を示している。変換層40に放射線等が入射すると、放射線等は、図5の黒い点で表した電荷に変換される。電荷は、平面電極42に反発して最寄の収集電極6に向かい、収集電極6,電荷誘導層5bを通じてグランド対向導電層4bに蓄積される(図6参照)。図6の状態においては、トランジスタ41tがOFF状態となっている。

【0044】

ゲート配線2aに電流が流され、トランジスタ41tがON状態となると、図7に示すように、グランド対向導電層4bに蓄えられた電荷が、電荷誘導層5b,チャンネル層4aを通じて、ソース配線5aに流れる。こうして、トランジスタ41tを制御することで、アクティブマトリックス基板41から電荷を取り出すことができるのである。

【0045】

<FPDの製造方法>

次に、FPD4の製造方法について説明する。本発明に係るFPD4は、その製造方法に特徴がある。具体的には、FPD4の製造方法は、図8に示すようにゲート配線2a等の第1層を生成する第1層生成工程S1と、各パターンを電気的に接続する接続工程S2と、チャンネル層4a等の第2層を生成する第2層生成工程S3と、ソース配線を配線するソース配線工程S4と、収集電極6を生成する収集電極生成工程S5とを備えている。

【0046】

第1層生成工程S1,および第2層生成工程S3は、ほぼ同様な工程であり、図9に示すように、各層を生成する成膜工程Saと、各層をローラで巻き取る巻き取り工程Sbと、絶縁基板1の上面上に各層を転写させる転写工程Scとを備えている。以降、各工程の詳細を順を追って説明する。

【0047】

<第1層生成工程S1>

<成膜工程S1a>

まず、配線2a,2bを生成する。図10は、配線2a,2bを生成するための第1凸版11である。第1凸版11の表面には、配線2a,2bの形状をした凸部が設けられている。そして、第1凸版11の表面には、4×4に縦横に並んだ検出素子を構成するパターンが現れている。したがって、ゲート配線2aの形状をした図10の紙面貫通方向に伸びる凸部と、グランド配線2bの形状をした図10の紙面貫通方向に伸びる凸部とが第1凸版11の表面に交互に配列されている。第1凸版11は、本発明の版に相当する。

【0048】

各配線は蒸着法やスパッタ法等により生成される。すなわち、第1凸版11を成膜装置の容器内に導入し、容器を真空とする。そして、原料を第1凸版11に吹き付けて堆積させる。成膜工程S1aが終了すると、図11のように導電性のゲート配線2a,グランド配線2bが第1凸版11の表面に現れる。第1凸版11には、凹凸が設けられているので、導電性物質が堆積する際に、凸部と凹部の間で段切れが起こる。これにより、配線2a,2bの形状および配列が凸部の表面に形成されるのである。

【0049】

<巻き取り工程S1b>

第1凸版11を大気中に戻して、図12に示すように、円筒形状のローラ12を第1凸版11の表面に押し当てながら回転させる。ローラ12は、第1凸版11よりも強く配線2a,2bに吸着するので、第1凸版11の表面に存していた配線2a,2bは、第1凸版11の表面から剥離して、ローラ12の表面側に巻き取られることになる。ローラ12は、本発明の転写部材に相当する。

【0050】

<転写工程S1c>

次に、図13に示すように、ローラ12を絶縁性の絶縁基板1の上面上に押し当てながら回転させる。絶縁基板1は、ローラ12よりも強く配線2a,2bに吸着するので、ローラ12の表面に存していた配線2a,2bは、ローラ12の表面から剥離して、絶縁基板1の上面上に転写されることになる。

【0051】

ローラ12の表面には、半導体用転写フィルムが巻きつけられている。このフィルムを交換すれば、配線2a,2bとローラ12の吸着性を自由に変更することができる。具体的には、ローラ12が配線2a,2bを吸着する吸着性は、第1凸版11の表面のそれよりも強く、絶縁基板1のそれよりも弱い。

【0052】

こうしてローラ12は、将来的には4×4の検出素子を構成することになる第1層の単位パターンを絶縁基板1に転写する。成膜工程S1a,巻き取り工程S1b,転写工程S1cを幾度も繰返すことで、絶縁基板1は、マトリックス状に配列された単位パターンで埋め尽くされることになる。

【0053】

<接続工程S2>

図14は、絶縁基板1を変換層40側から見たときの平面図である。縦方向に伸びた配線2a,2bが交互に配列している。図14は、単位パターンのつなぎ目を現している。すなわち、図14の上半分は単位パターンRaであり、下半分は単位パターンRbとなっている。接続工程S2では、単位パターン同士の導電性を確保する目的で、単位パターンのつなぎ目に導電性のインクを印刷する。実際の印刷方法としてはインクジェット方式の印刷機を使用することができる。こうして、単位パターンを跨いで縦方向(ゲート配線2aの伸びる方向)に連接するゲート配線2aの各々が、本工程で単一の配線となるのである。同様に、単位パターンを跨いで縦方向(グランド配線2bの伸びる方向)に連接するグランド配線2bの伸びる方向の各々が、本工程で単一の配線となるのである。

【0054】

<前処理>

第2層生成工程S3を行う前に、図15に示すように、ポリイミド等の液体の非導電性インクを絶縁基板1に塗布しておく。この非導電性インクは、将来的に絶縁層7aとなる。非導電性インクは、配線2a,2bが設けられている部分において、盛り上がる特性がある。

【0055】

<第2層生成工程S3>

<成膜工程S3a>

次に、各層3a,3b,4a,4bを生成する。図16は、各層3a,3b,4a,4bを生成するための第2凸版13である。第2凸版13には、各層3a,3b,4a,4bの形状をした凸部が設けられている。第2凸版13には、4×4に縦横に並んだ検出素子を構成する単位パターンが現れている。したがって、第2凸版13には、各層3b,4bとなる大きな矩形が2次元的に配列されており、各層3a,4aとなる小さな矩形が各層3b,4bの隙間に1つずつ配置されて、第2凸版13を全体として眺めれば、各凸部が2次元的に配列されている構成となっている。

【0056】

各層3a,3b,4a,4bは蒸着法やスパッタ法等により生成される。すなわち、第2凸版13を成膜装置の容器内に導入し、容器を真空とする。そして、原料を第2凸版13に吹き付けて堆積させる。成膜工程S3aが終了すると、図17のように非導電性のゲート対向絶縁層3aとグランド対向絶縁層3bが第2凸版13の表面に現れる。第2凸版13には、凹凸が設けられているので、導電性物質が堆積する際に、凸部と凹部の間で段切れが起こる。これにより、ゲート対向絶縁層3aとグランド対向絶縁層3bの形状および配列が凸部の表面に形成されるのである。

【0057】

各絶縁層3a,3bが生成された後、図18に示すように、第1遮蔽材14aを第2凸版13の上面上に配置することでゲート対向絶縁層3aをマスクして、蒸着法やスパッタ法等により、導電性のグランド対向導電層4bをグランド対向絶縁層3bの上面上に成長させる。その後、図19に示すように、第2遮蔽材14bを第2凸版13の上面上に配置することでグランド対向導電層4bをマスクして、蒸着法やスパッタ法等により、半導電性のチャンネル層4aをゲート対向絶縁層3aの上面上に成長させる。チャンネル層4aは、半導体層となっている。

【0058】

<巻き取り工程S3b>

第2凸版13を大気中に戻して、図20に示すように、円筒形状のローラ12を第2凸版13の表面に押し当てながら回転させる。ローラ12は第2凸版13よりも強く各層3a,3b,4a,4bに吸着するので、第2凸版13の表面に存していた各層3a,3b,4a,4bは、第2凸版13の表面から剥離して、ローラ12の表面側に巻き取られることになる。

【0059】

<転写工程S3c>

次に、図21に示すように、ローラ12を絶縁基板1の上面上に押し当てながら回転させる。絶縁基板1は、ローラ12よりも強く各層3a,3b,4a,4bに吸着するので、ローラ12の表面に存していた各層3a,3b,4a,4bは、ローラ12の表面から剥離して、絶縁基板1の上面上に転写されることになる。

【0060】

ローラ12の表面には、半導体用転写フィルムが巻きつけられている。このフィルムを交換すれば、各層3a,3b,4a,4bとローラ12の吸着性を自由に変更することができる。

【0061】

こうしてローラ12は、将来的には4×4の前記検出素子を構成することになる第2層の単位パターンを絶縁基板1に転写する。成膜工程S3a,巻き取り工程S3b,転写工程S3cを幾度も繰返すことで、絶縁基板1は、マトリックス状に配列された単位パターンで埋め尽くされることになる。図22は、本工程まで終了した状態において、絶縁基板1を変換層40側から見たときの平面図である。図22が示すように、大きな矩形のグランド対向絶縁層3bの隣に小さな矩形のチャンネル層4aが存するパターンがマトリックス状に配列している構成となっている。

【0062】

<ソース配線工程S4>

転写が終了すると、図23に示すように、絶縁基板1の上面上に、ソース配線5a,電荷誘導層5bがインクジェット方式により印刷される。ソース配線5aは、チャンネル層4aの一端を覆う様に構成され、電荷誘導層5bは、チャンネル層4aの他端からグランド対向導電層4bの全域にかけて各層4a,4bに跨るように構成される。図24は、本工程まで終了した状態において、絶縁基板1を変換層40側から見たときの平面図である。図24が示すように、矩形状の電荷誘導層5bがマトリックス状に配置し、各電荷誘導層5bの間には、横方向に伸びるソース配線5aが配線されている。グランド対向導電層4bは電荷誘導層5bにより全て隠され、チャンネル層4aの一部は、ソース配線5aと電荷誘導層5bとによって隠されている。

【0063】

<前処理>

収集電極生成工程S5を行う前に、図25に示すように、液体の非導電性インクをインクジェット方式により絶縁基板1に塗布しておく。この非導電性インクは、将来的に絶縁層7bとなる。絶縁基板1の上面上に露出していたソース配線5aとチャンネル層4aは絶縁層7bによって完全に覆われ、電荷誘導層5bの輪郭も絶縁層7bによって覆われる。図26は、本工程まで終了した状態において、絶縁基板1を変換層40側から見たときの平面図である。図26が示すように、矩形の電荷誘導層5bがマトリックス状に配列している構成となっている。

【0064】

<収集電極生成工程S5>

次に、図27に示すように、絶縁基板1の上面上に露出した電荷誘導層5bを覆い隠すように、導電性の収集電極6を配置する。収集電極6は、絶縁基板1の上面上において、マトリックス状に配列することになる。この時点で、収集電極6は、絶縁基板1上から盛り上がっている。

【0065】

その後、図28に示すように、隣り合う収集電極6同士における隙間を埋めるように非導電性インクをインクジェット方式により絶縁基板1に印刷する。この非導電性インクは、将来的に絶縁層7cとなる。図29は、本工程まで終了した状態において、絶縁基板1を変換層40側から見たときの平面図である。図29が示すように、矩形の収集電極6がマトリックス状に配列している構成となっている。これをもって、アクティブマトリックス基板41は完成となる。アクティブマトリックス基板41の上面上に変換層40等の各層を形成し、本発明のFPD4は、完成となる。

【0066】

以上のように、実施例1の構成によれば、絶縁基板1に直接ではなく、凸版11,13の表面に成膜してからこれを絶縁基板1に転写することで検出器が生成される。この様に構成すれば、凸版11,13に成膜処理を施せばよいということになる。つまり、成膜処理を真空中で行わなければならなかったとしても、凸版11,13を真空条件下に置くだけでよく、絶縁基板1に対する工程は全て大気中で行うことが可能である。そうすれば、絶縁基板1を成膜装置に導入させずして、真空中で成長した膜を基板上に配置することができる。つまり、絶縁基板1を自由に大型化することができるうえ、検出器の製造コストを抑制することができるのである。

【0067】

また、本発明の転写部材は円筒形のローラ12であり、これが凸版11,13,または絶縁基板1の表面に押し当てながら回転されることにより各工程が行われる。この様にすれば、膜は確実に絶縁基板1の表面に転写される。

【0068】

上述の構成における膜を表面に吸着させる吸着性は、凸版11,13,ローラ12,絶縁基板1の順に強いものとなっている。吸着性は、凸版11,13よりもローラ12の方が強力なので、巻き取り工程Sbにおいて、凸版11,13の表面に存している膜は、凸版11,13から剥離してローラ12の表面に吸着されることになる。また、吸着性は、ローラ12よりも絶縁基板1のほうが強力なので、転写工程Scにおいて、ローラ12の表面に存している膜は、ローラ12から剥離して絶縁基板1の表面に吸着されることになる。この様に、上述の構成によれば、凸版11,13の表面の膜を確実に基板上に転写させることができるのである。

【0069】

すなわち、上述の構成によれば、インクジェットによる印刷で膜を成膜するよりも正確なパターンを生成することができる。インクジェットの印刷によって基板上に膜を生成すると、膜の輪郭が蛇行したり、滲んだりしてしまう。インクジェット方式においては、液状のインクの粒を絶縁基板1に飛ばして成膜するからである。実施例1の構成によれば、より正確な成膜が可能な転写方式を利用することができる。

【0070】

そして、上述の構成によれば、転写工程Scを絶縁基板1の位置を変えながら繰り返し行うことにより、凸版11,13で形成された膜のパターンが絶縁基板1の表面に縦横に繰返される。つまり、凸版11,13は、絶縁基板1よりも遥かに小さなものとすることができる。これにより、小型の成膜装置さえあれば大型の検出器を製造することができるようになるので、検出器の製造コストは大幅に抑制される。

【0071】

上述の構成によれば、コンデンサ41cを構成する2つの電極は、成膜工程Sa,巻き取り工程Sb,転写工程Scにより形成されたものである。コンデンサ41cの物理的特性は、各検出素子の間で一定であることが望ましい。コンデンサ41cの電気容量等が検出素子の各々でまちまちであれば、正確な画像を取得することができなくなる。本発明におけるコンデンサ41cを構成する2つの電極は、信頼性の高い転写方式を用いているので、コンデンサ41cの形状のバラツキは極力抑えられている。したがって、上述の製造方法によれば、正確な画像を取得することができる検出器が提供できる。

【実施例2】

【0072】

上述の実施例1の第1層生成工程S1では、第1凸版11を用いていたが、これに代えて凹版を用いることもできる。以降、凹版を用いた場合の製造方法について説明する。

【0073】

<成膜工程S1a>

図30は、配線2a,2bを生成するための第1凹版11aである。第1凹版11aには、配線2a,2bの形状をした凹部が設けられている。第1凹版11aには、4×4に縦横に並んだ検出素子を構成する単位パターンが刻まれている。したがって、第1凹版11aには、ゲート配線2aの形状をした図10の紙面貫通方向に伸びる凹部と、グランド配線2bの形状をした図10の紙面貫通方向に伸びる凹部とが交互に配列されている。第1凹版11aは、本発明の版に相当する。

【0074】

この第1凹版11aには、導電性のインク15が塗布される。すると、図31に示すように、凹部の全てにインク15が流し込まれることになる。この状態で図32に示すように、短冊状のブレード16の先端を第1凹版11aの表面に接触させながら移動させると、ブレード16によって第1凹版11aの表面上の余分なインク15が追いやられて、図33に示すように、凹部にのみインク15が溜まった状態となる。

【0075】

<巻き取り工程S1b>

次に、図34に示すように、円筒形状のローラ12を第1凹版11aの表面に押し当てながら回転させる。ローラ12は第1凹版11aよりも強く配線2a,2bに吸着するので、第1凹版11aの表面に存していた配線2a,2bは、第1凹版11aの表面から脱離して、ローラ12の表面側に巻き取られることになる。このとき、インク15の乾燥を待つ必要は必ずしもない。

【0076】

<転写工程S1c>

次に、図13に示すように、ローラ12を絶縁基板1の上面上に押し当てながら回転させる。絶縁基板1は、ローラ12よりも強く配線2a,2bに吸着するので、ローラ12の表面に存していた配線2a,2bは、ローラ12の表面から剥離して、絶縁基板1の上面上に転写されることになる。

【0077】

ローラ12の表面には、インク用転写フィルムが巻きつけられてる。このフィルムを交換すれば、配線2a,2bとローラ12の吸着性を自由に変更することができる。具体的には、ローラ12が配線2a,2bを吸着する吸着性は、第1凹版11aの表面のそれよりも強く、絶縁基板1のそれよりも弱い。

【0078】

こうしてローラ12は、将来的には4×4の検出素子を構成することになる第1層の単位パターンを絶縁基板1に転写する。成膜工程S1a,巻き取り工程S1b,転写工程S1cを幾度も繰返すことで、絶縁基板1は、マトリックス状に配列された単位パターンで埋め尽くされることになる。

【0079】

その後の製造方法は、実施例1における図14以降の説明と同様である。

【0080】

以上のように、実施例2の構成によれば、全て大気中で各工程を行うことができる。実施例2によれば、大掛かりな装置を必要としないので、検出器を安価に製造することができる。

【0081】

本発明は、上述の構成に限られず、下記の様に変形実施することができる。

【0082】

(1)上述した実施例では、アクティブマトリックス基板を製造していたが、これに代えてパッシブマトリックス基板を製造してもよい。

【0083】

(2)上述した実施例では、ボトムゲート型アクティブマトリックス基板を製造していたが、これに代えてトップゲート型アクティブマトリックス基板を製造してもよい。

【0084】

(3)上述した実施例では、第1層、第2層を生成する際には、検出素子16個分のパターンを一度に転写していたが、本発明はこの構成に限られない。すなわち、一度に転写される検出素子の個数を増減することができる。更に、第1層と第2層で一度に転写される検出素子の個数を違えることもできる。

【符号の説明】

【0085】

Sa 成膜工程

Sb 巻き取り工程

Sc 転写工程

1 絶縁基板(基板)

11 凸版(版)

12 ローラ(転写部材)

13 凹版(版)

41c コンデンサ

【特許請求の範囲】

【請求項1】

光または放射線を検出する検出素子が基板上に2次元マトリックス状に配列された光または放射線検出器の製造方法であって、

前記検出器を構成する各層のうちの少なくとも1つは、

版の表面に膜を生成する成膜工程と、

前記版の表面に生成された前記膜を転写部材の表面に写し取る巻き取り工程と、

前記転写部材に巻き取られた前記膜を基板の表面に写し取る転写工程とにより製造されることを特徴とする光または放射線検出器の製造方法。

【請求項2】

請求項1に記載の光または放射線検出器の製造方法において、

前記転写部材は、円筒形のローラであり、

前記巻き取り工程、および前記転写工程は、前記ローラが前記版または前記基板の表面に押し当てられながら回転されることで行われることを特徴とする光または放射線検出器の製造方法。

【請求項3】

請求項1または請求項2に記載の光または放射線検出器の製造方法において、

前記膜を表面に吸着させる吸着性は、前記版、前記転写部材、前記基板の順に強いものとなっていることを特徴とする光または放射線検出器の製造方法。

【請求項4】

請求項1ないし請求項3のいずれかに記載の光または放射線検出器の製造方法において、

前記版は、前記基板に形成される前記膜の形状が凸部となった凸版であり、

前記成膜工程は、真空中において前記凸版に前記膜を蒸着させることで行われることを特徴とする光または放射線検出器の製造方法。

【請求項5】

請求項1ないし請求項3のいずれかに記載の光または放射線検出器の製造方法において、

前記版は、前記基板に形成される前記膜の形状が凹部となった凹版であり、

前記成膜工程は、前記凹版の前記凹部にインクを流し込むことにより行われることを特徴とする放射線検出器の製造方法。

【請求項6】

請求項1ないし請求項5のいずれかに記載の光または放射線検出器の製造方法において、

前記転写工程を前記基板の位置を変えながら繰り返し行うことにより、前記版で形成された前記膜のパターンが前記基板の表面に縦横に繰返されることを特徴とする光または放射線検出器の製造方法。

【請求項7】

請求項1ないし請求項6のいずれかに記載の光または放射線検出器の製造方法において、

前記検出素子は、電荷を蓄積するコンデンサを有し、

前記コンデンサを構成する2つの電極は、前記成膜工程、巻き前記取り工程、前記転写工程により形成されたものであることを特徴とする光または放射線検出器の製造方法。

【請求項1】

光または放射線を検出する検出素子が基板上に2次元マトリックス状に配列された光または放射線検出器の製造方法であって、

前記検出器を構成する各層のうちの少なくとも1つは、

版の表面に膜を生成する成膜工程と、

前記版の表面に生成された前記膜を転写部材の表面に写し取る巻き取り工程と、

前記転写部材に巻き取られた前記膜を基板の表面に写し取る転写工程とにより製造されることを特徴とする光または放射線検出器の製造方法。

【請求項2】

請求項1に記載の光または放射線検出器の製造方法において、

前記転写部材は、円筒形のローラであり、

前記巻き取り工程、および前記転写工程は、前記ローラが前記版または前記基板の表面に押し当てられながら回転されることで行われることを特徴とする光または放射線検出器の製造方法。

【請求項3】

請求項1または請求項2に記載の光または放射線検出器の製造方法において、

前記膜を表面に吸着させる吸着性は、前記版、前記転写部材、前記基板の順に強いものとなっていることを特徴とする光または放射線検出器の製造方法。

【請求項4】

請求項1ないし請求項3のいずれかに記載の光または放射線検出器の製造方法において、

前記版は、前記基板に形成される前記膜の形状が凸部となった凸版であり、

前記成膜工程は、真空中において前記凸版に前記膜を蒸着させることで行われることを特徴とする光または放射線検出器の製造方法。

【請求項5】

請求項1ないし請求項3のいずれかに記載の光または放射線検出器の製造方法において、

前記版は、前記基板に形成される前記膜の形状が凹部となった凹版であり、

前記成膜工程は、前記凹版の前記凹部にインクを流し込むことにより行われることを特徴とする放射線検出器の製造方法。

【請求項6】

請求項1ないし請求項5のいずれかに記載の光または放射線検出器の製造方法において、

前記転写工程を前記基板の位置を変えながら繰り返し行うことにより、前記版で形成された前記膜のパターンが前記基板の表面に縦横に繰返されることを特徴とする光または放射線検出器の製造方法。

【請求項7】

請求項1ないし請求項6のいずれかに記載の光または放射線検出器の製造方法において、

前記検出素子は、電荷を蓄積するコンデンサを有し、

前記コンデンサを構成する2つの電極は、前記成膜工程、巻き前記取り工程、前記転写工程により形成されたものであることを特徴とする光または放射線検出器の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【公開番号】特開2011−54779(P2011−54779A)

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願番号】特願2009−202623(P2009−202623)

【出願日】平成21年9月2日(2009.9.2)

【出願人】(000001993)株式会社島津製作所 (3,708)

【Fターム(参考)】

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願日】平成21年9月2日(2009.9.2)

【出願人】(000001993)株式会社島津製作所 (3,708)

【Fターム(参考)】

[ Back to top ]