光ディスク装置のダビングシステム、光ディスク装置のダビング方法、スピンドルモーター制御装置および出力レート制御装置

【課題】 CDプレイヤーからMDプレイヤーへのダビングの際、ディスクの回転ムラの影響でダビングデータの転送速度をジッタマージン分低く設定する必要があった。

【解決手段】 スピンドルモーター制御装置は、メモリ16とメモリコントローラ13、出力信号生成部17、アドレス差スピンドルモーター制御部32を備えることで光ディスク再生信号を、ディスクの回転ムラによるジッターに関係無く一定の転送速度でデータを出力することができる。また、出力レート制御装置は、メモリへの書き込みアドレスと読み出しアドレスの差分データを参照することにより出力レートを制御し、メモリの容量が小さい場合でも、オーバーフローやアンダーフローを起こすことが無く、安定したデータ転送が行える。

【解決手段】 スピンドルモーター制御装置は、メモリ16とメモリコントローラ13、出力信号生成部17、アドレス差スピンドルモーター制御部32を備えることで光ディスク再生信号を、ディスクの回転ムラによるジッターに関係無く一定の転送速度でデータを出力することができる。また、出力レート制御装置は、メモリへの書き込みアドレスと読み出しアドレスの差分データを参照することにより出力レートを制御し、メモリの容量が小さい場合でも、オーバーフローやアンダーフローを起こすことが無く、安定したデータ転送が行える。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、光ディスク装置のダビングシステム、光ディスク装置のダビング方法、スピンドルモーター制御装置および出力レート制御装置に関するものである。

【0002】

特に、CDプレーヤー、CD−ROMドライブ、DVDプレーヤー、DVD−ROMドライブ、MDプレーヤー等の光ディスク装置におけるスピンドルモーター制御装置、および出力信号がデジタルダビングの対象となる出力レート制御装置の改良を図ることで、光ディスク装置のダビングの高速化を達成できるようにしたものに関する。

【背景技術】

【0003】

従来、音楽データ等が記録された光ディスク、例えばCDが広く使用されている。

音楽CDのディスクは非圧縮の音楽データを記録しているが、多数の曲を収録したディスクは直径が12cmである。これに対しMDディスクはATRAC(Adaptive Transform Acoustic Coding)方式により原音の約1/5の容量に圧縮記録を行うため、12cmのCDの内容をより小型なMDディスクに収容できる。このため、CDディスクの内容をMDディスクにデジタルダビングして持ち歩くことが多くなっている。

【0004】

図19はこうしたデジタルダビングが可能なオーディオ機器の一例であるシステムコンポーネントステレオを示すものである。

図において、システムコンポーネントステレオCMPはCDプレーヤーと、録音機能を有するMDデッキ(以下、MDプレーヤーと称す)とを搭載している。キーKY中のイジェクトボタンを押すことで、CDトレイCDTが開き、CDディスクをケースから取り出しセットする。またMDディスクをスロットMDSを介してMDプレーヤーにセットする。

【0005】

キーKY操作によりCDディスクからMDディスクへのダビングを標準速、即ち1倍速で行うように選択してもよいが、74分もの時間を要するので、この種のダビング機能を有するオーディオ機器は4倍速等の高速ダビング機能を搭載する場合が多くなっている。スピーカSP1,SP2はCDやMDの再生時に再生音を流す。

【0006】

図20はこの種のシステムコンポーネントステレオの概略ブロック構成を示す。図において、CDドライブ401およびMDドライブ402はCDプレーヤーおよびMDプレーヤーの中核部分をなす。システムコントローラ1100は図19のキーKY操作に応じてCD制御部55を制御する。CD制御部55はCDドライブ401を制御しその再生データをMDドライブ402に出力することでダビングを行う。

【0007】

図21はこのシステムコントローラ1100およびCD制御部55の構成を示す。図において、システムコントローラ1100内のキー入力検出部1101はキーKY入力を検出する。高速ダビングキー操作検出部1102はキー操作が高速ダビングキーであるか否かを検出する。スピンドルモーター制御信号設定部1103は高速ダビングキーが操作された場合にスピンドルモーターが所定の倍速回転で回転を行うように制御信号を設定する。CD制御部55内のスピンドルモーター回転制御部551はスピンドルモーター制御信号に応じてスピンドルモーターの回転を制御する。

【0008】

図22はこの従来の高速ダビングモードにおけるCDプレーヤーのスピンドルモーターの回転速度を示す。

ここではCDディスクは標準的な74分記録が行われたものとする。スピンドルモーターは、CDの再生開始時である0分から再生終了時の74分まで、常に標準再生速度の5倍で回転する。これにより、標準速、すなわち1倍速でダビングが行われた場合に較べ、1枚のCDのMDへのダビングが完了するまでの時間の短縮を実現することができる。

【0009】

図23はCDディスクをデジタルダビングする際の、従来のCDシステムのより詳細な概念図を示す。このCDシステムは図20のCD制御部に相当するものである。

この図23に示す従来のCDシステム160は、CD等の光ディスクDに記録された情報を読み取る光学ピックアップ41により再生されたデータからクロックを再生するPLL161、光学ピックアップ41からの再生データの復調・訂正を行う信号処理部162、誤り訂正されたデータのショックプルーフ用メモリ164への書き込み・読み出し制御を行うメモリコントローラ163、メモリコントローラ163により読み出されたデータをアナログデータに変換するD/Aコンバータ165、信号処理部162により誤り訂正されたデータからシリアルデータを生成するシリアル出力信号生成部166を有する。

【0010】

また、信号処理部162は、CIRCRAM(CIRC;Cross Interleaved Reed-solomon Code)1622へのデータの書き込みを行う書き込み系1621、CIRCRAM1622への書き込みデータと読み出しデータとの位相差に応じたクロックを発生するPLL1623、CIRCRAM1622からのデータの読み出しを行う読み出し系1625、読み出し系1625へのクロックを外部からの水晶クロックとPLL1623の出力クロックとをシステムコントローラ1100からのジッターフリー設定により切り替えるセレクタ1624とを有する。なお、水晶クロックとは水晶発振器により発振されたクロック信号のことである。

【0011】

次に動作について説明する。光学ピックアップ41は光ディスクDの信号面に記録されているデータを読み取り再生する。光ディスクDの回転むらにより光ディスクDから得られる信号の入力レートが一定ではない場合でも、光ディスクからは、DSL(Data Slice)PLL部1623により2値化された音楽データと、回転と同期したクロックとがその再生信号として得られる。2値化された音楽データは、信号処理部162により復調・訂正される。訂正で使用するCIRCRAM1622へのデータ書き込みは書き込み系1621により行う。この書き込みはPLL1623により入力レートと同期しており、このため、ジッターの影響を受けない、いわゆるジッターフリーの状態でエラー訂正を行うことができる。CIRCRAM1622からの読み出しにはアナログPLL1623の発振信号を読み出し系1625のクロックとして用いている。なお、CDディスクからMDディスクへのダビングを行わず、単に再生を行う場合には、図示しない制御部がセレクタ1624をOFFに設定することで、ジッターフリー設定をオフにすることも可能である。この場合、読み出し系1625は外部からの水晶クロック入力により動作する。

【0012】

復調・訂正された音楽データは、メモリコントローラ163によりショックプルーフ用メモリ164に一時的に蓄えられる。このため、光学ピックアップが装置外部から加わる物理的な振動等によりトラック外れを起こしたとしても、ショックプルーフ用メモリ164の記憶容量により決まる時間以内に光学ピックアップが本来のトラックに復帰するようにトラッキング制御を行い、再度本来のトラックを再生することで、支障なく再生を行うことができ、強い耐振動性を実現できる。このショックプルーフ用メモリ164から読み出されたデータはD/Aコンバータ165によりアナログのオーディオ出力に変換され、スピーカ,イヤホン等により再生される。また、シリアル出力信号生成部166は信号処理部162の出力を、光ディスクの回転と同期したレートで所定のフォーマットに変更しMDデッキに向けて出力する。

【0013】

このように、CDなどの光ディスクを再生する際、線速度が一定になるようにスピンドルモーターをCLV(Constant Linear Velocity)制御し、得られる再生信号を信号処理部により復調・訂正し、一旦、メモリ、例えばダイナミック・ランダムアクセスメモリ(DRAM)に書き込み、一定期間データを蓄えた後、メモリから格納されたデータを読み出すことにより、振動などにより光ディスクからの再生信号に異常があった場合でも出力信号に対する影響を回避することが可能となっている。

【0014】

また、図24はサーボ外れが生じた場合に回復を行う従来のCDシステムの構成を示す。

この図24において、復調(訂正)部11は図23の信号処理部162に相当する。サーボ外れ検出部14は光学ピックアップ41による再生信号中にフレーム同期信号が含まれるか否かでサーボ外れが生じているか否かを検出する。サーボ外れを検出した場合、サーボ外れ信号38により、セレクタ53は固定値出力部21からの固定値を選択し、スピンドルモーター37にその制御信号として出力する。これにより、CLV制御部20からの制御信号を選択するよりも加速が抑えられ、サーボを引き込みやすくする。

【0015】

ところで、前記の従来の光ディスク再生装置は、メモリの残量が規定値以上の場合はメモリへの書き込みを停止するといった処理を行っていた(例えば、特許文献1参照)。

さらに、この従来例では、高倍速でデータ転送を行う場合であっても、線速度が一定であるCLV再生で光ディスクを再生し、データを転送していた。

【0016】

また、スピンドルモーターの回転数が一定であり、入力データのレートが一定でない場合、ショックプルーフメモリから読み出した再生信号はマイクロコンピュータなど外部から出力レートを切替える操作を行っていた(例えば、特許文献2参照)。

【特許文献1】特開平5−128531号公報(第4頁−第8頁、図1−図3)

【特許文献2】特開平6−314170号公報(第3頁−第4頁、図1−図3)

【発明の開示】

【発明が解決しようとする課題】

【0017】

ところで、前記のように線速度が一定で光ディスクより得られた再生信号には、回転制御の誤差によるジッターが存在し、例えば、CDプレーヤーからMDプレーヤーに高倍速でダビングを行う際には、ダビングされる側の最高動作速度を超えないように、ジッターマージン分だけ再生する側の回転速度を低く抑える必要があり、ダビング時間の高速化を充分達成できないものとなっていた。

【0018】

例えば、コンポーネントオーディオ機器のCDプレーヤーのスピンドルモーターは、CLV制御の場合、光ディスクの内周側では例えば5倍速、外周側では7−8倍速で回転できるにもかかわらず、受け側のダビング速度の限界値のために、外周側においても例えば5倍速に回転速度を抑えざるを得ない。従って、高速ダビングを本来期待できる最高速よりも抑えた速度で実行せざるを得ず、その分時間を要するものとなっていた。

【0019】

また、メモリの残量により書き込みを停止する処理を行った場合、光ディスクの読み取り位置へ光学ピックアップをトラックジャンプさせる必要があり、再生信号の質の低下を招く原因となっていた。

【0020】

本発明は、前記のような従来のものの問題点を解決するためになされたもので、ダビング時間を短縮し、メモリの書き込みを停止させないことを目的とするスピンドルモーター制御装置を提供することを目的としている。

【0021】

また、上述のように、高倍速でデータ転送を行う場合、線速度が一定であるCLVで再生した場合、スピンドルモーターの限界回転数で再生しようとすると、ジッタの影響で、出力レートがMD側のエンコーダの処理能力を越えてしまい、エンコーダの処理に破綻が生じてしまう。このため、スピンドルモーターの限界回転数で再生することが出来ず、ダビングなどを行う際にダビング時間が多くかかってしまう。

【0022】

また、スピンドルモーターの回転数の限界で光ディスクを再生する際に、メモリ容量が小さく高倍速で再生する場合、出力信号のレートを外部から制御していたのではメモリがオーバーフローやアンダーフローを起こしてしまうことが多い。

【0023】

本発明は、前記のような従来のものの問題点を解決するためになされたもので、アナログPLL部が不要であり、高倍速でも安定した再生信号のデータ転送が可能となる出力レート制御装置を提供することを目的としている。

【0024】

さらに、光ディスク装置からダビング速度に限界を有する受け側装置にデータをダビングする際、光ディスクの内周側,外周側のいずれを再生する場合であってもそのダビングを高速化できる光ディスク装置のダビングシステムおよびダビング方法を提供することを目的としている。

【課題を解決するための手段】

【0025】

前記課題を解決するために、

この発明の請求項1に係る光ディスク装置のダビングシステムは、光ディスクを再生する光ディスク装置と、ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビングシステムにおいて、前記光ディスク装置が前記光ディスクの外周側を再生する際、該光ディスクが前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定する回転数設定部と、当該光ディスクの外周側においてスピンドルモーターの回転により生じるジッタを吸収するジッタ吸収部と、前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御する出力レート制御部とを備えたことを特徴とするものである。

【0026】

この発明の請求項2に係る光ディスク装置のダビングシステムは、請求項1に記載の光ディスク装置のダビングシステムにおいて、前記光ディスク装置はCDドライブであり、前記受け側装置はMDドライブであることを特徴とするものである。

【0027】

この発明の請求項3に係る光ディスク装置のダビングシステムは、請求項1に記載の光ディスク装置のダビングシステムにおいて、前記スピンドルモーターは、線速度一定(以下、CLVと称す)となるように回転制御されることを特徴とするものである。

【0028】

この発明の請求項4に係る光ディスク装置のダビング方法は、光ディスクを再生する光ディスク装置と、ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビング方法において、前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御し、前記光ディスク装置が前記光ディスクの外周側を再生する際、前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定し、当該外周側におけるスピンドルモーターの回転により生じるジッタを吸収することを特徴とするものである。

【0029】

この発明の請求項5に係るスピンドルモーター制御装置は、光ディスク装置のスピンドルモーターの制御装置において、光学ピックアップにより復調された光ディスク再生信号を書き込むメモリと、該メモリへの書込み・読出しを制御するメモリコントローラと、該メモリコントローラの前記メモリへの書込みアドレスと読出しアドレスのアドレス差を参照してスピンドルモーター制御信号を生成するアドレス差スピンドルモーター制御部と、前記メモリから読み出した読出しデータを出力データへ変換する出力信号生成部とを備えたことを特徴とするものである。

【0030】

この発明の請求項6に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記アドレス差と、アドレス差の目標値である目標アドレス差との差に応じた位相差信号を生成する位相制御部と、前記アドレス差を保持するメモリに保持されたアドレス差と、前記アドレス差との差に応じた速度信号を生成する速度制御部とを備え、前記位相差信号と速度信号とを演算した結果を前記スピンドルモーターの制御信号として出力することを特徴とするものである。

【0031】

この発明の請求項7に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、前記メモリへの書込みデータと読出しデータを、可逆圧縮伸張する可逆圧縮伸張部を備えたことを特徴とするものである。

【0032】

この発明の請求項8に係るスピンドルモーター制御装置は、請求項5ないし請求項7のいずれかに記載のスピンドルモーター制御装置において、前記メモリは、前記光ディスク装置に加わる物理的衝撃により当該光ディスク装置に生じる再生むらを緩和するショックプルーフ用のメモリであることを特徴とするものである。

【0033】

この発明の請求項9に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部と、該サーボ外れ検出部で検出したサーボ外れ信号を参照して前記アドレス差スピンドルモーター制御部の出力と、固定値出力とを切替える切換え部とをさらに備えたことを特徴とするものである。

【0034】

この発明の請求項10に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部をさらに備え、前記アドレス差スピンドルモーター制御部は、該サーボ外れ検出部で検出したサーボ外れ信号を参照してサーボ外れ時にゲインを下げることを特徴とするものである。

【0035】

この発明の請求項11に係るスピンドルモーター制御装置は、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから一定期間前記アドレス差スピンドルモーター制御部のゲインを上げることを特徴とするものである。

【0036】

この発明の請求項12に係るスピンドルモーター制御装置は、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、アドレス差が規定範囲に入るまで、前記アドレス差スピンドルモーター制御部のゲインを上げることを特徴とするものである。

【0037】

この発明の請求項13に係るスピンドルモーター制御装置は、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、位相制御部の出力の極性が反転するまで、前記アドレス差スピンドルモーター制御部のゲインを上げることを特徴とするものである。

【0038】

この発明の請求項14に係るスピンドルモーター制御装置は、請求項10に記載のスピンドルモーター制御装置において、サーボ外れを検出するサーボ外れ検出部をさらに備え、該サーボ外れ検出部で検出したサーボ外れ信号を参照して、前記アドレス差スピンドルモーター制御部の出力値をホールドすることを特徴とするものである。

【0039】

この発明の請求項15に係るスピンドルモーター制御装置は、請求項14に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、アドレス差が規定範囲を外れるとゲインを上げることを特徴とするものである。

【0040】

この発明の請求項16に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、線速度一定となるようにスピンドルモーターの回転を制御するCLV制御部をさらに備え、アドレス差が規定量以下になった場合に、該CLV制御部の出力信号を前記スピンドルモーター制御信号として使用するとともに、前記出力信号生成部の入力を前記光ディスク再生信号に切替えることを特徴とするものである。

【0041】

この発明の請求項17に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、アドレス差が規定の範囲に入った場合、スピンドルモーター制御信号を、CLV制御部の出力からアドレス差スピンドルモーター制御部の出力に切替えると共に、前記出力信号生成部の入力を復調部からの出力からメモリからの出力に切替えることを特徴とするものである。

【0042】

この発明の請求項18に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、アドレス差スピンドルモーター制御部のアドレス差が規定の範囲に入った場合、スピンドルモーターの制御周波数を下げることを特徴とするものである。

【0043】

この発明の請求項19に係る出力レート制御装置は、光ディスクから読み出した再生信号を復調・訂正する信号処理部と、該信号処理部にて復調・訂正された再生信号を書きこむメモリと、該メモリへの書き込み・読み出しを制御するメモリコントローラと、前記メモリから読み出したデータをあらかじめ決められた形式に変換し出力するための信号を生成する出力信号生成部とを備え、前記メモリコントローラは、前記メモリへの書き込みアドレスと読み出しアドレスの差であるアドレス差分データを生成し、前記出力信号生成部は、前記アドレス差分データを入力し、出力信号のレートを制御することを特徴とするものである。

【0044】

この発明の請求項20に係る出力レート制御装置は、前記出力信号生成部から出力される信号は、複数ビットからなるデータを単位とする区切りタイミングを発生する制御信号と、ビットを単位とする区切りタイミングを発生するビットクロックと、前記データを単位とする区切りタイミング間の一部に有効なデータを収容したシリアルデータとからなることを特徴とするものである。

【0045】

この発明の請求項21に係る出力レート制御装置は、請求項19に記載の出力レート制御装置において、前記アドレス差分データから、前記シリアルデータの出力レートを演算する演算部をさらに備えたことを特徴とするものである。

【0046】

この発明の請求項22に係る出力レート制御装置は、請求項19に記載の出力レート制御装置において、前記アドレス差分データが、ある一定値以上または以下になった場合に、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算し、前記差分データが規定範囲内の時は前記シリアルデータの出力レートを保持する演算部をさらに備えたことを特徴とするものである。

【0047】

この発明の請求項23に係る出力レート制御装置は、請求項19に記載の出力レート制御装置において、前記アドレス差分データをある一定期間積分し、その差分の積分データの極性と、前記アドレス差分データの極性から、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算する演算部をさらに備えたことを特徴とするものである。

【0048】

この発明の請求項24に係る出力レート制御装置は、請求項19に記載の出力レート制御装置において、前記アドレス差分データが示すアドレス残量に応じて、前記シリアルデータの出力レートを切替えることを特徴とするものである。

【発明の効果】

【0049】

この発明によるスピンドルモーター制御装置では、ジッターを含む光ディスクからの読み取り信号を一旦メモリに蓄えて、ジッターの少ないクロック同期で読み取ってから出力するため、ジッターマージン分だけ光ディスク(CD)の回転数を低くする必要が無くなり、最高転送レートを維持した出力が可能となる。

【0050】

さらに、サーボエラー時やメモリエンプティー時のセルフリカバリが行えるため再生信号を間欠なく出力することが可能である。

【0051】

また、メモリの書き込みデータと読み出しデータのアドレス差に基づいてスピンドルモーター制御を行うため、モーター制御周波数が低くなり、モーターの低消費電力、長寿命化が可能となる。

【0052】

この発明による出力レート制御装置では、おもにダビング装置へのデータ転送に用いられ、トラックバッファメモリの書き込みアドレスと読み出しアドレスの差分データを参照し、随時自動で出力のピッチシフト量を演算しデータ転送するため、メモリの容量が小さいときや再生データが高倍速であっても、メモリがオーバーフロー、アンダーフローすることが無く、スピンドルモーターの限界まで回転させることが出来、より短い時間でのダビングが可能である。

【0053】

即ち、この発明の請求項1に係る光ディスク装置のダビングシステムによれば、光ディスクを再生する光ディスク装置と、ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビングシステムにおいて、前記光ディスク装置が前記光ディスクの外周側を再生する際、該光ディスクが前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定する回転数設定部と、当該光ディスクの外周側においてスピンドルモーターの回転により生じるジッタを吸収するジッタ吸収部と、前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御する出力レート制御部とを備えるようにしたので、光ディスク装置から受け側装置へのダビングを行う際に、光ディスクの外周側を再生する際、極力高回転に設定でき、内周側では受け側装置のダビング速度の限界を越えない上限の出力レートでデータを転送でき、データのダビングのさらなる高速化が実現可能となる効果がある。

【0054】

また、この発明の請求項2に係る光ディスク装置のダビングシステムによれば、請求項1に記載の光ディスク装置のダビングシステムにおいて、前記光ディスク装置はCDドライブであり、前記受け側装置はMDドライブであるものとしたので、CDディスクからMDディスクへのダビングのさらなる高速化が実現可能となる効果がある。

【0055】

また、この発明の請求項3に係る光ディスク装置のダビングシステムによれば、請求項1に記載の光ディスク装置のダビングシステムにおいて、前記スピンドルモーターは、線速度一定(以下、CLVと称す)となるように回転制御されるようにしたので、内周側よりも外周側が高速に回転する第1の光ディスクの回転の高速化を内周側,外周側のそれぞれの領域でより進めることが可能となり、データのダビングのさらなる高速化が実現可能となる効果がある。

【0056】

また、この発明の請求項4に係る光ディスク装置のダビング方法によれば、光ディスクを再生する光ディスク装置と、ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビング方法において、前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御し、前記光ディスク装置が前記光ディスクの外周側を再生する際、前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定し、当該外周側におけるスピンドルモーターの回転により生じるジッタを吸収するようにしたので、光ディスク装置から受け側装置へのダビングを行う際に、光ディスクの外周側を再生する際、極力高回転に設定でき、内周側では受け側装置のダビング速度の限界を越えない上限の出力レートでデータを転送でき、データのダビングのさらなる高速化が実現可能となる効果がある。

【0057】

また、この発明の請求項5に係るスピンドルモーター制御装置によれば、光ディスク装置のスピンドルモーターの制御装置において、光学ピックアップにより復調された光ディスク再生信号を書き込むメモリと、該メモリへの書込み・読出しを制御するメモリコントローラと、該メモリコントローラの前記メモリへの書込みアドレスと読出しアドレスのアドレス差を参照してスピンドルモーター制御信号を生成するアドレス差スピンドルモーター制御部と、前記メモリから読み出した読出しデータを出力データへ変換する出力信号生成部とを備えるようにしたので、光ディスクの外周側でスピンドルモーターを可能な限り高速に回転させるとともに、このスピンドルモーター制御装置を稼動させることにより、スピンドルモーターの回転むらにより生じるジッターをメモリにより吸収でき、ダビング用の再生データを高速にかつ安定して得ることが可能となる効果がある。

【0058】

また、この発明の請求項6に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記アドレス差と、アドレス差の目標値である目標アドレス差との差に応じた位相差信号を生成する位相制御部と、前記アドレス差を保持するメモリに保持されたアドレス差と、前記アドレス差との差に応じた速度信号を生成する速度制御部とを備え、前記位相差信号と速度信号とを演算した結果を前記スピンドルモーターの制御信号として出力するようにしたので、メモリに記憶しているデータが空にならないように光ディスクの回転数を制御でき、ダビング用の再生データを高速にかつ安定して得ることが可能となる効果がある。

【0059】

また、この発明の請求項7に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、前記メモリへの書込みデータと読出しデータを、可逆圧縮伸張する可逆圧縮伸張部を備えるようにしたので、メモリへの書き込み,読み出しを行った前後でデータの品質に劣化を生じることなく、メモリの容量を削減でき、ダビング用の再生データを高速にかつ安定して得ることが可能となる効果がある。

【0060】

また、この発明の請求項8に係るスピンドルモーター制御装置によれば、請求項5ないし請求項7のいずれかに記載のスピンドルモーター制御装置において、前記メモリは、前記光ディスク装置に加わる物理的衝撃により当該光ディスク装置に生じる再生むらを緩和するショックプルーフ用のメモリであるものとしたので、物理的衝撃により生じる再生むらと回転むらによる再生品質の劣化とを同時にかつ低コストに除去でき、ダビング用の再生データを間断なく、高速にかつ安定して得ることが可能となる効果がある。

【0061】

また、この発明の請求項9に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部と、該サーボ外れ検出部で検出したサーボ外れ信号を参照して前記アドレス差スピンドルモーター制御部の出力と、固定値出力とを切替える切換え部とをさらに備えるようにしたので、サーボ外れが生じたとしてもダビング用の再生データを間断なく、高速にかつ安定して得ることが可能となる効果がある。

【0062】

また、この発明の請求項10に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部をさらに備え、前記アドレス差スピンドルモーター制御部は、該サーボ外れ検出部で検出したサーボ外れ信号を参照してサーボ外れ時にゲインを下げるようにしたので、サーボ外れが生じたとしてもすみやかに回復することが可能となり、ダビング用の再生データを間断なく、高速にかつ安定して得ることが可能となる効果がある。

【0063】

また、この発明の請求項11に係るスピンドルモーター制御装置によれば、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから一定期間前記アドレス差スピンドルモーター制御部のゲインを上げるようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0064】

また、この発明の請求項12に係るスピンドルモーター制御装置によれば、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、アドレス差が規定範囲に入るまで、前記アドレス差スピンドルモーター制御部のゲインを上げるようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0065】

また、この発明の請求項13に係るスピンドルモーター制御装置によれば、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、位相制御部の出力の極性が反転するまで、前記アドレス差スピンドルモーター制御部のゲインを上げるようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0066】

また、この発明の請求項14に係るスピンドルモーター制御装置によれば、請求項10に記載のスピンドルモーター制御装置において、サーボ外れを検出するサーボ外れ検出部をさらに備え、該サーボ外れ検出部で検出したサーボ外れ信号を参照して、前記アドレス差スピンドルモーター制御部の出力値をホールドするようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0067】

また、この発明の請求項15に係るスピンドルモーター制御装置によれば、請求項14に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、アドレス差が規定範囲を外れるとゲインを上げるようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0068】

また、この発明の請求項16に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、線速度一定となるようにスピンドルモーターの回転を制御するCLV制御部をさらに備え、アドレス差が規定量以下になった場合に、該CLV制御部の出力信号を前記スピンドルモーター制御信号として使用するとともに、前記出力信号生成部の入力を前記光ディスク再生信号に切替えるようにしたので、メモリに記憶しているデータが空きにならないように光ディスクの回転数を制御でき、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0069】

また、この発明の請求項17に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、アドレス差が規定の範囲に入った場合、スピンドルモーター制御信号を、CLV制御部の出力からアドレス差スピンドルモーター制御部の出力に切替えると共に、前記出力信号生成部の入力を復調部からの出力からメモリからの出力に切替えるようにしたので、メモリが空きになりダビングすべきデータに欠落が生じ得る状態を脱した後、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0070】

また、この発明の請求項18に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、アドレス差スピンドルモーター制御部のアドレス差が規定の範囲に入った場合、スピンドルモーターの制御周波数を下げるようにしたので、スピンドルモーターの低消費電力化および長寿命化を実現することが可能となる効果がある。

【0071】

また、この発明の請求項19に係る出力レート制御装置によれば、光ディスクから読み出した再生信号を復調・訂正する信号処理部と、該信号処理部にて復調・訂正された再生信号を書きこむメモリと、該メモリへの書き込み・読み出しを制御するメモリコントローラと、前記メモリから読み出したデータをあらかじめ決められた形式に変換し出力するための信号を生成する出力信号生成部とを備え、前記メモリコントローラは、前記メモリへの書き込みアドレスと読み出しアドレスの差であるアドレス差分データを生成し、前記出力信号生成部は、前記アドレス差分データを入力し、出力信号のレートを制御するようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0072】

また、この発明の請求項20に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記出力信号生成部から出力される信号は、複数ビットからなるデータを単位とする区切りタイミングを発生する制御信号と、ビットを単位とする区切りタイミングを発生するビットクロックと、前記データを単位とする区切りタイミング間の一部に有効なデータを収容したシリアルデータとからなるものとしたので、有効なデータを収容した部分以外を伸縮することで、出力レートを適宜変化することができ、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0073】

また、この発明の請求項21に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記アドレス差分データから、前記シリアルデータの出力レートを演算する演算部をさらに備えるようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0074】

この発明の請求項22に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記アドレス差分データが、ある一定値以上または以下になった場合に、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算し、前記差分データが規定範囲内の時は前記シリアルデータの出力レートを保持する演算部をさらに備えるようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0075】

また、この発明の請求項23に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記アドレス差分データをある一定期間積分し、その差分の積分データの極性と、前記アドレス差分データの極性から、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算する演算部をさらに備えるようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0076】

さらに、この発明の請求項24に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記アドレス差分データが示すアドレス残量に応じて、前記シリアルデータの出力レートを切替えるようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【発明を実施するための最良の形態】

【0077】

(実施の形態1)

本発明は、CLV制御により光ディスクを回転制御しその再生を行うCDプレーヤー(光ディスク装置)から、記録時にデータの圧縮処理を行うためダビング速度に限界を有するMDプレーヤー(受け側装置)にデータのダビングを行う状況において、CDプレーヤーが光ディスクを再生する際、外周側の高速化をスピンドルモーター制御装置により、内周側の高速化を出力レート制御装置により、それぞれ実現できるようにしたものである。

【0078】

この場合の、光ディスク装置のダビングシステムに相当するシステムコンポーネントステレオのシステムコントローラ1000およびCD制御部50の構成は図2に示すようになる。

【0079】

システムコントローラ1000内のキー入力検出部1001はキーKY入力があることを検出する。高速ダビングキー操作検出部1102は操作されたキーが高速ダビングキーであるか否かを検出する(図7のステップ110参照)。ダビング範囲判定部1003はダビング範囲がCDの全体か一部かをキー入力により判定する(ステップ111参照)。制御切換部1004は高速ダビング中のCDの再生箇所がディスクの内周側および外周側のいずれに該当するかを判定し(図4のステップ101,図7のステップ112参照)、内周側に相当する場合は内周側制御部501を(図4のステップ102参照)、外周側に相当する場合は外周側制御部502をそれぞれ動作させる(ステップ103参照)。この内周側制御部501は出力レート制御装置に、外周側制御部502はスピンドルモーター制御装置にそれぞれ対応する。この内周側と外周側との判定は図5に示すサブコードSCを用いる。このサブコードはCDより再生され、最初の曲の頭から現在の再生箇所に至るまでの経過時間を分m,秒s,フレームf(=1/30秒)で表す。

【0080】

即ち、図6に示すように、スピンドルモーター制御装置は、CDプレーヤーが再生する光ディスクの外周側における回転速度の上限付近まで回転数を上げるようにスピンドルモーターの制御を行い、かつその際のジッタの影響をショックプルーフ用のメモリで吸収し、また、出力レート制御装置は、CDプレーヤーの内周側を再生する際の高回転にジッタが加わることでMDプレーヤーのデータ圧縮処理に破綻が生じないように、出力レートの制御を行うことにより、CDプレーヤーの回転速度を光ディスクの内周側および外周側において可能な限り高回転の限界近くに維持でき、ダビングの高速化を実現できるようにしたものである。

【0081】

この点をより詳細に述べると、図7のステップ112,116において内周側と判定し、最内周から再生を開始する場合、MD側の入力許容範囲以上の出力レートとなった場合(図7のステップ118参照)、出力レートを下げ(図7のステップ119参照)、MD側の入力許容範囲内の出力レートとなるまで(図7のステップ120参照)、出力レートを下げる。また、ステップ116において外周側に入ったと判定した場合、CD上の当該再生位置における所定の回転数に設定する(図7のステップ113参照)。つぎにこの所定の回転数を保って所定時間が経過した場合(図7のステップ114参照)、スピンドルモーターの回転数を所定だけ増加する(ステップ115参照)。この操作を最外周まで繰り返す。

【0082】

これにより、例えば図6に示すように、内周側では内周側で回転可能な最大回転数でスピンドルモーターを回転でき、MDプレーヤーの圧縮処理が破綻をきたさない上限の出力レートでデータを出力することができ、外周側では出力レートを一定とし、スピンドルモーターの回転数を制御することで、高速ダビング性能を限界まで高めることが可能となる。

【0083】

なお、図5のタイムコードを利用することにより、CDの全体ではなくその一部をダビングする場合であっても、図7のフローチャートのステップ117によりその一部が内周側,外周側のいずれに該当するかを判断することで、ダビングの高速化を達成できる。

【0084】

このように、本実施の形態1によれば、非圧縮のデータを記録したCDディスクからデータを圧縮して記録するMDディスクにダビングを行う際、CDディスクの内周側では当該内周側で回転可能な上限にまでディスクの回転数を高めてその際に発生するジッターはメモリで吸収し、外周側では当該外周側でMD側での圧縮処理が正常に動作可能な上限の出力レートでデータを転送するので、ダビングの高速化を一層達成することが可能となる。

【0085】

(実施の形態2)

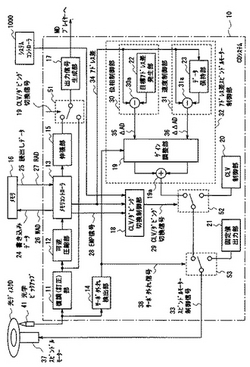

図1は本発明の実施の形態2による、CDプレーヤーからMDプレーヤーへ音楽データをダビングするCDシステムに搭載されるスピンドルモーター制御装置のブロック図である。

このスピンドルモーター制御装置は実施の形態1における外周側制御部に相当するものである。

【0086】

図1において、この実施の形態2によるスピンドルモーター制御装置は、CDシステム10と、メモリ16と、システムコントローラ1000とを有する。

【0087】

CDシステム10は復調(訂正)部11と、可逆圧縮部12と、メモリコントローラ13と、伸張部15と、セレクタ51と、出力信号生成部17と、サーボ外れ検出部14と、CLV/ダビング切換制御部18と、CLV制御部20と、アドレス差スピンドルモーター制御回路32と、セレクタ52と、固定値出力部21と、セレクタ53とを有する。

【0088】

また、アドレス差スピンドルモーター制御部32は、位相制御部30と、速度制御部31と、ゲイン調整部19と、加算部19aとを有する。

位相制御部30は目標アドレス差発生部22と、減算部30aとを有する。

速度制御部31はデータ保持部23と、減算部31aとを有する。

【0089】

次に動作について説明する。

(通常再生モード)

まず、使用者がキー操作により標準速でCDを再生する通常再生モードを選択したとする。

【0090】

システムコントローラ1000はキー入力により通常再生モードが選択されたと判断する。これにより、CLV/ダビング切換制御部18はCLVモードである旨のCLV/ダビング切換制御信号29を発生する。このCLV/ダビング切換信号29によりセレクタ52はCLV制御部20の出力信号を選択する。

【0091】

サーボ外れが生じていないとすると、セレクタ53はスピンドルモーター制御信号33としてセレクタ52の出力信号を選択するので、スピンドルモーター37はCLV制御部20の出力信号により標準速で線速度一定となるように、即ち内周側から外周側に向けて徐々に低回転数から高回転数に移行するように、回転制御が行われる。

【0092】

また、この時、セレクタ51は復調(訂正)部11の出力信号を選択するので、出力信号生成部17は標準速にて再生され復調(訂正)部11で復調,誤り訂正された信号を処理し、アナログ信号に変換した後、スピーカは音を発生する。

【0093】

一方、サーボ外れ検出部14がサーボ外れを検出した場合は、サーボ外れ信号38によりセレクタ53が固定値出力部21の固定値を選択し、これをスピンドルモーター制御信号33として出力する。従って、スピンドルモーター37はこの固定値によって安定した回転を回復し、サーボ外れ状態から定常状態に復帰できる。

【0094】

(ダビングモード)

次に、使用者がキー操作によりダビングモードを選択したとする。

この場合、CLV/ダビング切換制御部18の制御によりセレクタ52はアドレス差スピンドルモーター制御回路32の出力信号を選択し、セレクタ51は伸張部15の出力信号を選択する。

【0095】

まず、図示しない電圧発生部により外周側では受け側の許容倍数を超えないようにスピンドルモーター37を回転させて、光ディスクDより再生信号を読み出す。

光ディスクDより読み出された再生信号は復調(訂正)部11により信号処理が行われ、メモリコントローラ13によりメモリ16に書き込まれる。このメモリ16への書き込み,読み出しを行う際、可逆圧縮部12および伸張部15を用いることにより、メモリ16容量を削減でき、かつ圧縮伸張処理によるデータの損失をなくすようにしている。

【0096】

復調(訂正)部11は、光学ピックアップ41により光ディスクDより読み出した再生信号を復調し、復調されたデータを内部の誤り訂正部によりデータを復元し補間する。

可逆圧縮部12は、データを圧縮し圧縮したデータを伸張部15で伸張する際に、元のデータに損失を生じさせることなく伸張できる圧縮・伸張方法を実行する。

メモリ16は、書き込み、読み出し可能なRAM等で構成される。このメモリ16は本来、CDプレーヤーとMDプレーヤーとを有するCDシステムに外部から物理的な衝撃力が加わった場合に、衝撃による再生への影響を緩和するために再生データを一定期間蓄積するショックプルーフに用いられるものである。

【0097】

メモリコントローラ13は、メモリ16への書き込み、読み出しを制御するもので、メモリ16により蓄えられたデータは、メモリコントローラ13により読み出される。

メモリ16から読出されたデータ25は、出力信号生成部17により一定の転送速度に保たれ、MDプレーヤーにデータ転送される。

出力信号生成部17は、MDなどのダビングする側がダビング可能なデータ形式を生成する。

【0098】

メモリコントローラ13はメモリ16がオーバーフローやアンダーフローを起こさないように書き込みアドレス26と読み出しアドレス27を制御している。これにより、メモリコントローラ13による読み出し速度と出力信号生成部17からのデータ出力速度は同じとなり、光ディスクの回転速度を変化させた場合でもMDプレーヤーへの転送速度は一定に保たれる。これは、スピンドルモーターを外周側では受け側の許容倍数を超えないように回転させた場合に生じるジッターを、ショックプルーフ用のメモリ16で吸収することを意味する。

【0099】

このため、ジッターの影響を抑えるためにマージンを持つことなく、スピンドルモーターの回転数を限界まで高く設定することが可能となる。

【0100】

アドレス差スピンドルモーター制御部32は、位相制御部30と速度制御部31とゲイン調整部19と加算部19aとで構成される。

【0101】

位相制御部30は、メモリコントローラ13から、書き込みデータ24と、読出しデータ25とのアドレス差を任意の周波数毎に受け取り、目標アドレス差発生部22からの目標アドレス差とアドレス差34との差であるアドレス差差分ΔAD 35を生成する。

【0102】

目標アドレス差とは、書き込みデータ24と読み出しデータ25のアドレス差の目標値であり、この値は設定が可能である。目標アドレス差はメモリ16がオーバーフロー及びアンダーフローを起こさない程度に設定する必要があり、メモリ16の容量の1/2から3/4程度に設定するのが良い。本実施の形態2ではアドレス差34が目標アドレス差に近づくようにスピンドルモーター制御信号を生成する。

【0103】

速度制御部31では、減算部31aによりアドレス差34と、データ保持部23により保持されたアドレス差との差であるアドレス差差分ΔΔAD 36を生成する。

データ保持部23では、1サンプル前のアドレス差34を保持する。

ゲイン調整部19によりゲイン調整した後、加算部19aはアドレス差差分ΔAD 35とΔΔAD 36とを加算し、アドレス差34を目標アドレス差に収束するようにスピンドルの出力値を制御する。

【0104】

例えば、

スピンドルモーター制御信号=(ΔAD・Kθ)+(ΔΔAD・Kv)

と書くことができる。

但し、Kθは位相項,Kvは速度項である。

【0105】

このスピンドルモーター制御により、外周部において許容される最高回転数に設定することが可能である。

つまり、単に線速度が一定でダビングした場合はジッターの影響を見込んで高倍速を抑え気味に設定せざるを得ないが、この実施の形態2のダビングモードでは、ジッターマージン分だけ高い回転数に設定でき、この分速くダビングを行うことができる。

【0106】

また、光ディスク再生中にエラーが発生してもショックプルーフ制御が可能なメモリ16、メモリコントローラ13を備えることにより、音飛びなどを防ぐことも可能である。

さらに、アドレス差34が目標アドレス差付近の規定範囲内で収束したときは、メモリコントローラ13から受け取るアドレス差信号34のサンプリング周波数を下げることにより更にスピンドルモーター37の負担を減らすことができる。

【0107】

ところで、このようなダビングモードから脱調した場合に、自動的に元のダビングモードに復帰する、いわゆるセルフリカバリモードとして、以下の切り替えモードおよびサーボエラー回復モードがある。

【0108】

(切替えモード)

この切替えモードは、スピンドルモーター制御装置での制御方法をダビングモードとCLV(Constant Linear Velocity)モード、即ち通常再生モードとの間で切り替えを行うことにより、ショックプルーフ用メモリがエンプティとなってもデータを間断なく転送できるものである。

【0109】

以下、この切り替えについて図1及び図8ないし図11を用いて説明する。

図8はメモリの概念図である。縦軸は書き込みアドレスと読み出しアドレスとの差、すなわち、メモリに蓄積したデータの残量を示す。目標アドレス差付近を規定範囲と呼び、規定範囲内でアドレス差が収まっているならダビングモードは安定状態であると言える。また、アドレス差が小さくなりある一定の値を下回ることを規定範囲以下と呼ぶ。

【0110】

図9はCLV/ダビング切り替え制御部18の状態遷移図である。

図9に示すように、この切り替えモードは2つの状態S1,S2を有する。状態S1はダビングモード、状態S2はCLVモードであり、これらの状態における動作はそれぞれ上述したとおりである。アドレス差が規定範囲以上であればダビングモードS1を維持し、アドレス差が規定範囲以下となればCLVモードS2に移行する。アドレス差が規定範囲外であればCLVモードを維持し、規定範囲内に戻ればダビングモードS1に戻る。

【0111】

図10はこの状態遷移図に対応するフローチャートを示す。

図11はCLV/ダビング切り替え制御部18の内部構成を示す。

【0112】

図1及び図10,図11において、CLV/ダビング切換制御部18内のアドレス差信号受信部181はメモリコントローラ3よりアドレス差34を受け取り、アドレス差判定部182はダビングモード時に(図10のステップ201参照)アドレス差34が規定量以下になった場合(ステップ202参照)、CLV/ダビング切換信号発生部183はCLV/ダビング切換信号の値を変更し、ダビングモードからCLVモードに移行する(ステップ203参照)。その時、スピンドルモーター制御信号33となる信号は、アドレス差スピンドルモーター制御部32の出力から、CLV制御部20の出力に切替える。また同時に、出力信号生成部17に入力する信号はメモリコントローラ13(もしくは伸張部15)の出力から、復調(訂正)部11の出力に切替える。

【0113】

この動作により、ダビングモードより転送速度は遅くなるが、メモリ16がエンプティー状態でも、データを間欠なく転送することが可能となる。

【0114】

CLVモード再生中にアドレス差34が規定範囲に入った場合(ステップ204)、アドレス差スピンドルモーター制御部32はCLVモードからダビングモードに移行する。このとき、スピンドルモーター制御信号33をCLV制御部20の出力から、アドレス差スピンドルモーター制御部32の出力に切替える。また同時に、出力信号生成部17の入力を復調(訂正)部11の出力からメモリコントローラ13(もしくは伸張部15)の出力に切替える。

【0115】

以上の動作は、メモリ16のアドレス差34が小さければCLVモードに、大きければダビングモードとすることであり、これにより、メモリ16がエンプティー状態でも、データを間欠無く転送することが可能であり、CLVモードで再生するより高倍速でのデータ転送が可能となる。

【0116】

(サーボエラー回復モード)

このサーボエラー回復モードでは、サーボにエラーが生じた場合にゲインを上げるように調整を行うことでダビングモードへの復帰を行う。この回復動作について図1及び図12ないし図14を用いて説明する。

【0117】

図1において、サーボ外れ検出部14は光ディスクDより読み出されたフレーム同期信号を検出出来なかった場合にサーボ外れ信号38を出力する。

サーボエラー回復モードにおけるスピンドルモーター制御装置の制御方法として、スピンドルモーター制御信号33を任意の一定値にする強制出力モードと、ダビングモードがある。

【0118】

また、ダビングモード時アドレス差34が規定範囲内にある場合は、安定状態と呼ぶことにする。図12の状態遷移図を用いて本実施の形態2のサーボエラー時の動作について説明する。

【0119】

このサーボエラー回復モードは3つの状態S3,S4,S5を有する。ダビングモードS3は、図9における状態S1と同様のものである。状態D4はゲインを下げるとともに固定値を出力し、状態S5ではゲインを上げる。サーボ外れ信号が未検出であればダビングモードS3を維持し、サーボ外れ信号が検出されれば状態S4に遷移する。状態S4においてサーボ外れ信号が検出され続ければ状態S4を維持し、サーボ外れ信号が未検出となれば状態S5に移行する。状態S5においてアドレス差が規定範囲外であれば状態S5を維持し、アドレス差が規定範囲内に収まれば状態S3に戻る。

【0120】

図13はこの状態遷移図に対応するフローチャートである。

ダビングモード(ステップ301)で光ディスクDを再生中にサーボ外れ検出部により、フレーム同期信号が未検出となり、サーボ外れ信号38が出力される。サーボ外れ信号38が検出されると(ステップ302)、メモリ16に書き込まれる入力信号がなくなり、アドレス差34が小さくなるため、アドレス差スピンドルモーター制御部32の出力はスピンドルモーター37を加速させる方向になり、逆にサーボを引き込みにくくしてしまう。これを防ぐために、サーボ外れ信号38を検出したときの動作として、ダビングモードを強制出力モードに切り替えスピンドルモーター37の加速を抑える制御を行う。また別の方法として、サーボ外れ信号38を検出したとき、ダビングモードを維持したままゲインを下げる(ステップ303)ことによりスピンドルモーター37の加速を抑える。以上の制御を行うことでサーボを引き込みやすくする。

【0121】

以上の動作の結果、サーボを引き込みサーボ外れ信号38が未検出となった場合、ダビングモードに復帰させアドレス差34を大きくする目的で、ゲイン調整部19のゲインを一定期間もしくはアドレス差34が規定範囲内になるまで上げる。これによりダビングモードの安定状態へ短時間で復帰させることが可能となる。また、別の方法として、サーボを引き込みサーボ外れ信号38が未検出となった場合(ステップ304)、ΔADの極性が負から正になるまでゲイン調整部19のゲインを上げる(ステップ305)。アドレス差が規定範囲内に戻れば(ステップ306)、ダビングモードに戻る。いずれの制御においてもダビングモードの安定状態への短時間での復帰が可能となる。

【0122】

このように、本実施の形態2によるスピンドルモーター制御装置によれば、CLVにより回転制御を行っているCDプレーヤーからMDプレーヤーにダビングを行う際、CDの外周側において、スピンドルモーターをその限界回転数で回転し再生を行うようにその制御信号を固定値に設定し、CLV制御により生じるジッタはショックプルーフ用メモリにより吸収することで、CDの外周側におけるMDへのダビングを高速化することが可能となる。

【0123】

(実施の形態3)

この実施の形態3は、出力レート制御装置に関するものである。この出力レート制御装置は、実施の形態1における内周側制御部に相当するものである。

【0124】

出力レート制御装置は、光ディスクの内周側において、スピンドルモーターの限界回転数で再生しようとすると、ジッタの影響で、出力レートがMD側のエンコーダの処理能力を越えてしまい、エンコーダの処理に破綻が生じてしまうことがあり、スピンドルモーターの限界回転数で再生することが出来ず、ダビングなどを行う際にダビング時間が多くかかってしまうという問題を解決できるものである。

【0125】

即ち、メモリ容量が小さく高倍速で再生している場合、出力信号のレートを外部から制御していたのではメモリがオーバーフローやアンダーフローを起こしてしまうことが多い。

本実施の形態3の出力レート制御装置では、こうしたメモリオーバーフローやメモリアンダーフローを防ぐために、メモリのアドレス差分データを随時監視し、アドレス差分データを演算しピッチシフト量を得て、出力信号のレートを自動で変更することでメモリのオーバーフローやアンダーフローを防ぎ、より高倍速でのデータ転送が可能になるようにしたものである。

【0126】

図15は本発明の実施の形態3におけるCDプレーヤーからMDプレーヤーへ音楽データをダビングする際のCDプレーヤーの主要なブロック図である。

この例では、記録する装置、つまりMDプレーヤーへ音楽データをダビング用途等のために高倍速で転送するためのものである。

【0127】

図15において、音楽CDディスク等の光ディスクDが、スピンドルモーターにより一定の回転数に保たれ回転するものとする。つまり、線速度は内周から外周にかけて徐々に速くなるわけである。今仮に、スピンドルモーターの限界回転数を2000rpmとすれば最内周ではその4倍で再生することになる。CDプレーヤーの再生可能倍速とMDのダビング可能倍速がともに4倍以上であるなら、最内周ではスピンドルモーターの性能により約4倍速でのダビングしか出来ないことになる。

【0128】

光学ピックアップ41は、光ディスクDから得られる音楽データを読み取る。光学ピックアップ41により読み取られた音楽データは、まずデータスライス部63により、2値にスライスされた音楽データが生成されるとともに、そのPLL機能により音楽データの再生速度と同期したクロックが生成される。

【0129】

2値化された音楽データは信号処理部64によりEFM(Eight to Fourteen Modulation)復調される。復調後のデータは、書き込み系641により信号処理部64内のCIRC(Cross Interleaved Reed−solomon Code)と呼ばれる誤り訂正部に入り、読み出されたデータが正しいか誤っているかを判断し、誤ったデータを訂正する。このときにメモリであるCIRCRAM642が使用され、読み出し系643により読み出しが行われる。通常モードの場合はCIRCRAM642への書き込みは光ディスクの回転と同期して行われ、CIRCRAM642の読み出しは水晶発振子と同期して出力することにより、スピンドルモーターの回転ジッターをメモリで吸収する。

【0130】

しかしながら、スピンドルモーターの回転数が一定であり、線速度が一定でないときを考える。CIRCRAM642の読み出しは書き込みと同期して行われ、信号処理部内では光ディスクの回転と同期して信号が処理される。スピンドルモーターの回転数が一定であることによる線速度の変化をCIRCRAM642で吸収しようとしても、これには、メモリ容量が不十分で、オーバーフローを起こしやすい。そのため線速度の変化をショックプルーフメモリ16で吸収し、書き込み、読み出しを制御して高倍速での安定したデータ転送を行う。

【0131】

復調・訂正された音楽データはメモリコントローラ63で制御され、ショックプルーフメモリ16への書き込み,読み出しが行われる。このときショックプルーフメモリ16への書き込みは光ディスクDの回転と同期して書き込まれる。MDプレーヤーへの転送速度とショックプルーフメモリ16からの読み出しは同期しており、MDプレーヤーへの転送速度を切替えることによりショックプルーフメモリ16の読み出し速度を変化させる。これにより、ショックプルーフメモリ16のオーバーフロー、アンダーフローを防ぐ。

【0132】

シリアル出力信号生成部69では、ショックプルーフメモリ16より読み出された音楽データをダビング装置であるMDプレーヤー側がダビング可能なフォーマットに変換し、出力レートを設定し出力する。また、メモリコントローラ63から書き込みアドレスと読み出しアドレスのアドレス差の差分データを受け取り、差分データを演算することにより出力のピッチシフト量を演算する。また、出力レートよりメモリコントローラ63においてショックプルーフメモリ16の読み出しの動作速度を制御する。

【0133】

転送データのフォーマットとしてのシリアル出力の信号波形を図16に示す。図16に示すように、データSRDATA 221、Lch、Rch識別信号 LRCK222、ビットクロック BCLK 223の3線によりシリアル出力を伝送する。このシリアル出力の特徴として、データSRD/ATA221は1LRCKのうち0ビットから15ビットまでが音声データであり、16ビットから31ビットまではInvalidとして扱う。また、Lch、Rch識別信号 LRCK222の1つのLRCK中には通常32クロックのビットクロックBCLKがある。そのためシリアル出力の転送レートはデータSRDATA221のビット数が32のままで、BCLK223とLRCK222の周期を変化させて、それに伴いSRDATA221を伸縮させることにより転送レートを変化する場合と、1LRCK中のSRDATA221をLSBから16ビットはそのままでMSBからnビット増減させ、それに伴い1LRCK中のBCLK223のクロック数をnクロック増減することにより転送レートを変化させる場合、の2種類がある。例えば、BCLKの周波数を1倍速再生時の4倍にし、SRDATAの16ビット目から31ビット目までを削ることにより、4×32/(32−16)=8倍速でのデータ転送が可能となる。

【0134】

図17はシリアル出力信号生成部69の詳細ブロック図である。図17を用いて前記で説明したシリアル出力の生成方法を説明する。ビットクロックBCLKは図示しない水晶発振器で発生した水晶クロックを分周部694で分周することにより生成する。

【0135】

このシリアル出力信号生成部69はアドレス差分データを演算しピッチシフト量を決定するアドレス差分データ演算部691と、1LRCK中にBCLKが何個存在するかを設定するピッチシフトアップダウンカウンタ692と、ピッチシフトアップダウンカウンタの値をロードしカウントダウンするダウンカウンタ693とを有し、カウント値が0になると信号を反転することでLRCKを生成する。パラレルデータを入力しダウンカウンタのカウント値を用いてパラレル−シリアル変換を行い、SRDATAを作成する。

【0136】

シリアル出力信号生成部69の出力レート制御方法について以下に述べる。前記のようにショックプルーフメモリ16への書き込みアドレスと読み出しアドレスとの差分データ73をメモリコントローラ63から受け取る。ここでメモリのアドレス差分データ73をメモリの残量と言い換えるとともに、図18を用いてショックプルーフメモリ16の制御方法について説明する。

【0137】

まず、目標メモリ残量を任意の値に設定する(図18(a)参照)。ショックプルーフメモリ16のオーバーフロー、アンダーフローを防ぐために、メモリ容量の1/2から3/4あたりに設定するのが良い。目標メモリ残量と現在のメモリ残量とを比較し、現在のメモリ残量が目標メモリ残量より少なければ、シリアル出力信号生成部69の出力レートを下げるようにピッチシフト量を演算する。現在のメモリ残量が目標メモリ残量より多ければ、シリアル出力信号生成部の出力レートを上げるようにピッチシフト量を演算する。このようにショックプルーフメモリに継続的に書き込まれる音楽データをメモリ残量が目標メモリ残量に近づくようにシリアル出力信号生成部69の出力レートを変化させることにより、ショックプルーフメモリのオーバーフロー、アンダーフローを防ぐ。

【0138】

シリアル出力信号生成部におけるピッチシフト量の演算方法として以下に例をあげる。1LRCK中のBCLKのクロック数を16から127まで設定できるとすれば、ピッチシフト量は16から127まで設定できる。SRDATAのデータ部分は16ビットあるため16以下には設定できない。通常1LRCKは32クロックのビットクロックBCLKがあるため、32を基準値とし前記のピッチシフト量の演算により基準値32からカウントアップ、又はカウントダウンする。1LRCK中のBCLKのクロック数を変化させることによりピッチシフト量を随時決定し出力レートに反映させる。この方法で出力レートを変化させた場合は、BCLKの周期は変わらない。

【0139】

図18(b)に示すように、シリアル出力信号生成部69は、目標メモリ残量(上限)および目標メモリ残量(下限)を設定し、現在のメモリ残量が目標メモリ残量(上限)以上の時は、ピッチシフト量のカウンタ値を下げることで出力レートを上げメモリの残量を減らす方向に移行する。現在のメモリ残量が目標メモリ残量(下限)以下の時は、ピッチシフト量のカウンタ値を上げることで出力レートを下げメモリの残量を増やす方向に移行する。現在のメモリ残量が目標メモリ残量(上限)と目標メモリ残量(下限)の間にある時はピッチシフトを行わずピッチシフト量の値を保持する。ピッチシフト量のカウンタ値により出力レートを決定し、メモリ残量が目標メモリ残量付近で収束するように制御する。

【0140】

また、アドレス差分データ演算部691は、ある一定期間のメモリ残量を積分し、その極性を判定する。現在のメモリ残量と目標メモリ残量との差の極性が正であり、且つ積分値の極性が正であるならピッチシフト量のカウンタ値を上げ、積分値の極性が負であるならピッチシフト量のカウンタ値を保持する。また、現在のメモリ残量と目標メモリ残量との差の極性が負であり、且つ積分値の極性が正であるならピッチシフト量のカウンタ値を保持し、積分値の極性が負であるならピッチシフト量のカウンタ値を下げる。ピッチシフト量のカウンタ値により出力レートを決定し、メモリ残量が目標メモリ残量付近で収束するように制御する。

【0141】

図18(c)のようにメモリをn分割し、それぞれの領域毎に出力レートを設定しておき、現在のメモリ残量とメモリの領域を参照し、出力レートを切替える。

【0142】

以上はそれぞれ出力レートを制御する方法であり、これらを実行することでショックプルーフメモリ16のオーバーフローやアンダーフローを抑制し、高倍速でのデータ転送を安定して行うことができる。

【0143】

このように、実施の形態3による出力レート制御装置によれば、トラックバッファメモリを備え、メモリのアドレス差分データを随時監視し、アドレス差分データを演算しピッチシフト量を得て、出力信号のレートを自動で変更することにより、メモリのオーバーフローやアンダーフローを防ぎ、高倍速でも安定した再生信号のデータ転送を行うことが可能となる。

【0144】

このため、光ディスクの内周側において、スピンドルモーターの限界回転数で再生しようとすると、ジッタの影響で、出力レートがMD側のエンコーダの処理能力を越えてしまい、エンコーダの処理に破綻が生じてしまい、このため、スピンドルモーターの限界回転数で再生することが出来ず、ダビングなどを行う際にダビング時間が多くかかってしまう、という問題、および、スピンドルモーターの回転数の限界で光ディスクを再生した場合、メモリ容量が小さく高倍速で再生している場合、出力信号のレートを外部から制御していたのではメモリがオーバーフローやアンダーフローを起こしてしまうことが多い、という問題を解決でき、アナログPLL部が不要となり、高倍速でも安定した再生信号のデータ転送が可能となり、CDディスクからMDディスクへのダビングを高速に行うことが可能となる効果がある。

【0145】

なお、上記各実施の形態では、ハードウエアとして実現した場合を説明したが、ハードウエアでしか実現できない箇所を除き、ソフトウエアにより実現してもよい。

【0146】

また、音楽CDディスクからMDディスクへのダビングを例にとって説明したが、第1のメディアが非圧縮のデータを記録したものであり、第2のメディアが圧縮したデータを記録するものであれば、他の光ディスクであってもよく、さらには半導体メモリや磁気ディスク等の他のメディアであってもよい。

【産業上の利用可能性】

【0147】

以上のように、本発明のスピンドルモータ制御装置は、メモリ、メモリコントローラ、出力信号生成部及びアドレス差スピンドルモーター制御部を備えることにより、光ディスク再生装置、例えばCDやDVDなどを再生する装置の高倍速再生に適しており、ショックプルーフ用のメモリを使用するため再生データを間欠なく再生することが可能である。このため、ディスクの回転ムラによるジッタに関係なく一定の転送速度でデータを出力することができ、データのダビングを一層高速化するのに適する。

【0148】

また、スピンドルモーター制御周波数が低くモーターの低消費電力、長寿命化が可能となり、その産業上の利用可能性は非常に広く且つ大きい。

【0149】

また、本発明の出力レート制御装置は、復調・訂正を行う信号処理部と、トラックバッファメモリ、メモリコントローラ、出力信号生成部を備えており、スピンドルモーターを最大回転数で光ディスクを再生する場合や、トラックバッファメモリの容量が小さい場合でも、メモリのオーバーフローやアンダーフローを起こさずに、高倍速でデータ出力が可能であり、デジタルダビング装置へのデータ転送が可能な再生装置として有用であり、その産業上の利用可能性は非常に広く且つ大きい。

【図面の簡単な説明】

【0150】

【図1】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行うダビングシステムを示す図

【図2】本発明の実施の形態1におけるシステムコントローラおよびCD制御部のブロック構成を示す図

【図3】本発明の実施の形態1における動作モードの相違を表わす表を示す図

【図4】本発明の実施の形態1における動作モードの切換えを行うフローチャートを示す図

【図5】CDディスクにおける経過時間を示すタイムコードを示す図

【図6】本発明の実施の形態1におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の回転倍速の変化を示す図

【図7】本発明の実施の形態1におけるCDプレーヤーからMDプレーヤーへのダビングを行う際のフローチャートを示す図

【図8】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際のメモリの残量の制御指標を示す図

【図9】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の動作状態の遷移を示す状態遷移図

【図10】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の動作状態の遷移を示すフローチャート図

【図11】本発明の実施の形態3におけるCDプレーヤーからMDプレーヤーへのダビングを行う際のCLV/ダビング切換制御部のブロック構成を示す図

【図12】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の動作状態の遷移を示す状態遷移図

【図13】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の動作状態の遷移を示すフローチャート図

【図14】本発明の実施の形態2におけるサーボ外れ検出部のブロック構成を示す図

【図15】本発明の実施の形態3におけるCDプレーヤーからMDプレーヤーへのダビングを行うダビングシステムを示す図

【図16】本発明の実施の形態3におけるCDプレーヤーからMDプレーヤーへのダビングを行う際のシリアル出力のデータフォーマットを示す図

【図17】本発明の実施の形態3におけるシリアル出力信号生成部のブロック構成を示す図

【図18】本発明の実施の形態3によるメモリ残量制御の様子を示す図

【図19】本発明が適用される対象であるシステムコンポーネントを示す図

【図20】本発明が適用される対象であるシステムコンポーネントのブロック構成を示す図

【図21】従来のシステムコンポーネントのシステムコントローラ及びCD制御部のブロック構成を示す図

【図22】従来のシステムコンポーネントの高速ダビング時のCDプレーヤーの回転数を示す図

【図23】従来のシステムコンポーネントのCDシステムの構成を示す図

【図24】従来のシステムコンポーネントのCDシステムの構成を示す図

【符号の説明】

【0151】

D 光ディスク

10 CDシステム

11 復調(訂正)部

12 可逆圧縮部

13 メモリコントローラ

14 サーボ外れ検出部

15 伸張部

16 メモリ

17 出力信号生成部

18 CLV/ダビング切換制御部

19 ゲイン調整部

20 CLV制御部

21 固定値出力発生部

22 目標アドレス差発生部

23 データ保持部

24 書き込みデータ

25 読み出しデータ

26 メモリへのデータ書きこみの際のアドレス(WAD)

27 メモリからのデータ読み出しの際のアドレス(RAD)

28 EMP信号

29 CLV/ダビング切換信号

30 位相制御部

31 速度制御部

32 アドレス差スピンドルモーター制御部

33 スピンドルモーター制御信号

34 アドレス差信号

35 ΔAD信号

36 ΔΔAD信号

37 スピンドルモーター

38 サーボ外れ信号

41 光学ピックアップ

63 データスライス部

64 信号処理部(復調・訂正)

69 シリアル出力信号生成部

1000 システムコントローラ

【技術分野】

【0001】

この発明は、光ディスク装置のダビングシステム、光ディスク装置のダビング方法、スピンドルモーター制御装置および出力レート制御装置に関するものである。

【0002】

特に、CDプレーヤー、CD−ROMドライブ、DVDプレーヤー、DVD−ROMドライブ、MDプレーヤー等の光ディスク装置におけるスピンドルモーター制御装置、および出力信号がデジタルダビングの対象となる出力レート制御装置の改良を図ることで、光ディスク装置のダビングの高速化を達成できるようにしたものに関する。

【背景技術】

【0003】

従来、音楽データ等が記録された光ディスク、例えばCDが広く使用されている。

音楽CDのディスクは非圧縮の音楽データを記録しているが、多数の曲を収録したディスクは直径が12cmである。これに対しMDディスクはATRAC(Adaptive Transform Acoustic Coding)方式により原音の約1/5の容量に圧縮記録を行うため、12cmのCDの内容をより小型なMDディスクに収容できる。このため、CDディスクの内容をMDディスクにデジタルダビングして持ち歩くことが多くなっている。

【0004】

図19はこうしたデジタルダビングが可能なオーディオ機器の一例であるシステムコンポーネントステレオを示すものである。

図において、システムコンポーネントステレオCMPはCDプレーヤーと、録音機能を有するMDデッキ(以下、MDプレーヤーと称す)とを搭載している。キーKY中のイジェクトボタンを押すことで、CDトレイCDTが開き、CDディスクをケースから取り出しセットする。またMDディスクをスロットMDSを介してMDプレーヤーにセットする。

【0005】

キーKY操作によりCDディスクからMDディスクへのダビングを標準速、即ち1倍速で行うように選択してもよいが、74分もの時間を要するので、この種のダビング機能を有するオーディオ機器は4倍速等の高速ダビング機能を搭載する場合が多くなっている。スピーカSP1,SP2はCDやMDの再生時に再生音を流す。

【0006】

図20はこの種のシステムコンポーネントステレオの概略ブロック構成を示す。図において、CDドライブ401およびMDドライブ402はCDプレーヤーおよびMDプレーヤーの中核部分をなす。システムコントローラ1100は図19のキーKY操作に応じてCD制御部55を制御する。CD制御部55はCDドライブ401を制御しその再生データをMDドライブ402に出力することでダビングを行う。

【0007】

図21はこのシステムコントローラ1100およびCD制御部55の構成を示す。図において、システムコントローラ1100内のキー入力検出部1101はキーKY入力を検出する。高速ダビングキー操作検出部1102はキー操作が高速ダビングキーであるか否かを検出する。スピンドルモーター制御信号設定部1103は高速ダビングキーが操作された場合にスピンドルモーターが所定の倍速回転で回転を行うように制御信号を設定する。CD制御部55内のスピンドルモーター回転制御部551はスピンドルモーター制御信号に応じてスピンドルモーターの回転を制御する。

【0008】

図22はこの従来の高速ダビングモードにおけるCDプレーヤーのスピンドルモーターの回転速度を示す。

ここではCDディスクは標準的な74分記録が行われたものとする。スピンドルモーターは、CDの再生開始時である0分から再生終了時の74分まで、常に標準再生速度の5倍で回転する。これにより、標準速、すなわち1倍速でダビングが行われた場合に較べ、1枚のCDのMDへのダビングが完了するまでの時間の短縮を実現することができる。

【0009】

図23はCDディスクをデジタルダビングする際の、従来のCDシステムのより詳細な概念図を示す。このCDシステムは図20のCD制御部に相当するものである。

この図23に示す従来のCDシステム160は、CD等の光ディスクDに記録された情報を読み取る光学ピックアップ41により再生されたデータからクロックを再生するPLL161、光学ピックアップ41からの再生データの復調・訂正を行う信号処理部162、誤り訂正されたデータのショックプルーフ用メモリ164への書き込み・読み出し制御を行うメモリコントローラ163、メモリコントローラ163により読み出されたデータをアナログデータに変換するD/Aコンバータ165、信号処理部162により誤り訂正されたデータからシリアルデータを生成するシリアル出力信号生成部166を有する。

【0010】

また、信号処理部162は、CIRCRAM(CIRC;Cross Interleaved Reed-solomon Code)1622へのデータの書き込みを行う書き込み系1621、CIRCRAM1622への書き込みデータと読み出しデータとの位相差に応じたクロックを発生するPLL1623、CIRCRAM1622からのデータの読み出しを行う読み出し系1625、読み出し系1625へのクロックを外部からの水晶クロックとPLL1623の出力クロックとをシステムコントローラ1100からのジッターフリー設定により切り替えるセレクタ1624とを有する。なお、水晶クロックとは水晶発振器により発振されたクロック信号のことである。

【0011】

次に動作について説明する。光学ピックアップ41は光ディスクDの信号面に記録されているデータを読み取り再生する。光ディスクDの回転むらにより光ディスクDから得られる信号の入力レートが一定ではない場合でも、光ディスクからは、DSL(Data Slice)PLL部1623により2値化された音楽データと、回転と同期したクロックとがその再生信号として得られる。2値化された音楽データは、信号処理部162により復調・訂正される。訂正で使用するCIRCRAM1622へのデータ書き込みは書き込み系1621により行う。この書き込みはPLL1623により入力レートと同期しており、このため、ジッターの影響を受けない、いわゆるジッターフリーの状態でエラー訂正を行うことができる。CIRCRAM1622からの読み出しにはアナログPLL1623の発振信号を読み出し系1625のクロックとして用いている。なお、CDディスクからMDディスクへのダビングを行わず、単に再生を行う場合には、図示しない制御部がセレクタ1624をOFFに設定することで、ジッターフリー設定をオフにすることも可能である。この場合、読み出し系1625は外部からの水晶クロック入力により動作する。

【0012】

復調・訂正された音楽データは、メモリコントローラ163によりショックプルーフ用メモリ164に一時的に蓄えられる。このため、光学ピックアップが装置外部から加わる物理的な振動等によりトラック外れを起こしたとしても、ショックプルーフ用メモリ164の記憶容量により決まる時間以内に光学ピックアップが本来のトラックに復帰するようにトラッキング制御を行い、再度本来のトラックを再生することで、支障なく再生を行うことができ、強い耐振動性を実現できる。このショックプルーフ用メモリ164から読み出されたデータはD/Aコンバータ165によりアナログのオーディオ出力に変換され、スピーカ,イヤホン等により再生される。また、シリアル出力信号生成部166は信号処理部162の出力を、光ディスクの回転と同期したレートで所定のフォーマットに変更しMDデッキに向けて出力する。

【0013】

このように、CDなどの光ディスクを再生する際、線速度が一定になるようにスピンドルモーターをCLV(Constant Linear Velocity)制御し、得られる再生信号を信号処理部により復調・訂正し、一旦、メモリ、例えばダイナミック・ランダムアクセスメモリ(DRAM)に書き込み、一定期間データを蓄えた後、メモリから格納されたデータを読み出すことにより、振動などにより光ディスクからの再生信号に異常があった場合でも出力信号に対する影響を回避することが可能となっている。

【0014】

また、図24はサーボ外れが生じた場合に回復を行う従来のCDシステムの構成を示す。

この図24において、復調(訂正)部11は図23の信号処理部162に相当する。サーボ外れ検出部14は光学ピックアップ41による再生信号中にフレーム同期信号が含まれるか否かでサーボ外れが生じているか否かを検出する。サーボ外れを検出した場合、サーボ外れ信号38により、セレクタ53は固定値出力部21からの固定値を選択し、スピンドルモーター37にその制御信号として出力する。これにより、CLV制御部20からの制御信号を選択するよりも加速が抑えられ、サーボを引き込みやすくする。

【0015】

ところで、前記の従来の光ディスク再生装置は、メモリの残量が規定値以上の場合はメモリへの書き込みを停止するといった処理を行っていた(例えば、特許文献1参照)。

さらに、この従来例では、高倍速でデータ転送を行う場合であっても、線速度が一定であるCLV再生で光ディスクを再生し、データを転送していた。

【0016】

また、スピンドルモーターの回転数が一定であり、入力データのレートが一定でない場合、ショックプルーフメモリから読み出した再生信号はマイクロコンピュータなど外部から出力レートを切替える操作を行っていた(例えば、特許文献2参照)。

【特許文献1】特開平5−128531号公報(第4頁−第8頁、図1−図3)

【特許文献2】特開平6−314170号公報(第3頁−第4頁、図1−図3)

【発明の開示】

【発明が解決しようとする課題】

【0017】

ところで、前記のように線速度が一定で光ディスクより得られた再生信号には、回転制御の誤差によるジッターが存在し、例えば、CDプレーヤーからMDプレーヤーに高倍速でダビングを行う際には、ダビングされる側の最高動作速度を超えないように、ジッターマージン分だけ再生する側の回転速度を低く抑える必要があり、ダビング時間の高速化を充分達成できないものとなっていた。

【0018】

例えば、コンポーネントオーディオ機器のCDプレーヤーのスピンドルモーターは、CLV制御の場合、光ディスクの内周側では例えば5倍速、外周側では7−8倍速で回転できるにもかかわらず、受け側のダビング速度の限界値のために、外周側においても例えば5倍速に回転速度を抑えざるを得ない。従って、高速ダビングを本来期待できる最高速よりも抑えた速度で実行せざるを得ず、その分時間を要するものとなっていた。

【0019】

また、メモリの残量により書き込みを停止する処理を行った場合、光ディスクの読み取り位置へ光学ピックアップをトラックジャンプさせる必要があり、再生信号の質の低下を招く原因となっていた。

【0020】

本発明は、前記のような従来のものの問題点を解決するためになされたもので、ダビング時間を短縮し、メモリの書き込みを停止させないことを目的とするスピンドルモーター制御装置を提供することを目的としている。

【0021】

また、上述のように、高倍速でデータ転送を行う場合、線速度が一定であるCLVで再生した場合、スピンドルモーターの限界回転数で再生しようとすると、ジッタの影響で、出力レートがMD側のエンコーダの処理能力を越えてしまい、エンコーダの処理に破綻が生じてしまう。このため、スピンドルモーターの限界回転数で再生することが出来ず、ダビングなどを行う際にダビング時間が多くかかってしまう。

【0022】

また、スピンドルモーターの回転数の限界で光ディスクを再生する際に、メモリ容量が小さく高倍速で再生する場合、出力信号のレートを外部から制御していたのではメモリがオーバーフローやアンダーフローを起こしてしまうことが多い。

【0023】

本発明は、前記のような従来のものの問題点を解決するためになされたもので、アナログPLL部が不要であり、高倍速でも安定した再生信号のデータ転送が可能となる出力レート制御装置を提供することを目的としている。

【0024】

さらに、光ディスク装置からダビング速度に限界を有する受け側装置にデータをダビングする際、光ディスクの内周側,外周側のいずれを再生する場合であってもそのダビングを高速化できる光ディスク装置のダビングシステムおよびダビング方法を提供することを目的としている。

【課題を解決するための手段】

【0025】

前記課題を解決するために、

この発明の請求項1に係る光ディスク装置のダビングシステムは、光ディスクを再生する光ディスク装置と、ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビングシステムにおいて、前記光ディスク装置が前記光ディスクの外周側を再生する際、該光ディスクが前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定する回転数設定部と、当該光ディスクの外周側においてスピンドルモーターの回転により生じるジッタを吸収するジッタ吸収部と、前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御する出力レート制御部とを備えたことを特徴とするものである。

【0026】

この発明の請求項2に係る光ディスク装置のダビングシステムは、請求項1に記載の光ディスク装置のダビングシステムにおいて、前記光ディスク装置はCDドライブであり、前記受け側装置はMDドライブであることを特徴とするものである。

【0027】

この発明の請求項3に係る光ディスク装置のダビングシステムは、請求項1に記載の光ディスク装置のダビングシステムにおいて、前記スピンドルモーターは、線速度一定(以下、CLVと称す)となるように回転制御されることを特徴とするものである。

【0028】

この発明の請求項4に係る光ディスク装置のダビング方法は、光ディスクを再生する光ディスク装置と、ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビング方法において、前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御し、前記光ディスク装置が前記光ディスクの外周側を再生する際、前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定し、当該外周側におけるスピンドルモーターの回転により生じるジッタを吸収することを特徴とするものである。

【0029】

この発明の請求項5に係るスピンドルモーター制御装置は、光ディスク装置のスピンドルモーターの制御装置において、光学ピックアップにより復調された光ディスク再生信号を書き込むメモリと、該メモリへの書込み・読出しを制御するメモリコントローラと、該メモリコントローラの前記メモリへの書込みアドレスと読出しアドレスのアドレス差を参照してスピンドルモーター制御信号を生成するアドレス差スピンドルモーター制御部と、前記メモリから読み出した読出しデータを出力データへ変換する出力信号生成部とを備えたことを特徴とするものである。

【0030】

この発明の請求項6に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記アドレス差と、アドレス差の目標値である目標アドレス差との差に応じた位相差信号を生成する位相制御部と、前記アドレス差を保持するメモリに保持されたアドレス差と、前記アドレス差との差に応じた速度信号を生成する速度制御部とを備え、前記位相差信号と速度信号とを演算した結果を前記スピンドルモーターの制御信号として出力することを特徴とするものである。

【0031】

この発明の請求項7に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、前記メモリへの書込みデータと読出しデータを、可逆圧縮伸張する可逆圧縮伸張部を備えたことを特徴とするものである。

【0032】

この発明の請求項8に係るスピンドルモーター制御装置は、請求項5ないし請求項7のいずれかに記載のスピンドルモーター制御装置において、前記メモリは、前記光ディスク装置に加わる物理的衝撃により当該光ディスク装置に生じる再生むらを緩和するショックプルーフ用のメモリであることを特徴とするものである。

【0033】

この発明の請求項9に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部と、該サーボ外れ検出部で検出したサーボ外れ信号を参照して前記アドレス差スピンドルモーター制御部の出力と、固定値出力とを切替える切換え部とをさらに備えたことを特徴とするものである。

【0034】

この発明の請求項10に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部をさらに備え、前記アドレス差スピンドルモーター制御部は、該サーボ外れ検出部で検出したサーボ外れ信号を参照してサーボ外れ時にゲインを下げることを特徴とするものである。

【0035】

この発明の請求項11に係るスピンドルモーター制御装置は、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから一定期間前記アドレス差スピンドルモーター制御部のゲインを上げることを特徴とするものである。

【0036】

この発明の請求項12に係るスピンドルモーター制御装置は、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、アドレス差が規定範囲に入るまで、前記アドレス差スピンドルモーター制御部のゲインを上げることを特徴とするものである。

【0037】

この発明の請求項13に係るスピンドルモーター制御装置は、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、位相制御部の出力の極性が反転するまで、前記アドレス差スピンドルモーター制御部のゲインを上げることを特徴とするものである。

【0038】

この発明の請求項14に係るスピンドルモーター制御装置は、請求項10に記載のスピンドルモーター制御装置において、サーボ外れを検出するサーボ外れ検出部をさらに備え、該サーボ外れ検出部で検出したサーボ外れ信号を参照して、前記アドレス差スピンドルモーター制御部の出力値をホールドすることを特徴とするものである。

【0039】

この発明の請求項15に係るスピンドルモーター制御装置は、請求項14に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、アドレス差が規定範囲を外れるとゲインを上げることを特徴とするものである。

【0040】

この発明の請求項16に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、線速度一定となるようにスピンドルモーターの回転を制御するCLV制御部をさらに備え、アドレス差が規定量以下になった場合に、該CLV制御部の出力信号を前記スピンドルモーター制御信号として使用するとともに、前記出力信号生成部の入力を前記光ディスク再生信号に切替えることを特徴とするものである。

【0041】

この発明の請求項17に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、アドレス差が規定の範囲に入った場合、スピンドルモーター制御信号を、CLV制御部の出力からアドレス差スピンドルモーター制御部の出力に切替えると共に、前記出力信号生成部の入力を復調部からの出力からメモリからの出力に切替えることを特徴とするものである。

【0042】

この発明の請求項18に係るスピンドルモーター制御装置は、請求項5に記載のスピンドルモーター制御装置において、アドレス差スピンドルモーター制御部のアドレス差が規定の範囲に入った場合、スピンドルモーターの制御周波数を下げることを特徴とするものである。

【0043】

この発明の請求項19に係る出力レート制御装置は、光ディスクから読み出した再生信号を復調・訂正する信号処理部と、該信号処理部にて復調・訂正された再生信号を書きこむメモリと、該メモリへの書き込み・読み出しを制御するメモリコントローラと、前記メモリから読み出したデータをあらかじめ決められた形式に変換し出力するための信号を生成する出力信号生成部とを備え、前記メモリコントローラは、前記メモリへの書き込みアドレスと読み出しアドレスの差であるアドレス差分データを生成し、前記出力信号生成部は、前記アドレス差分データを入力し、出力信号のレートを制御することを特徴とするものである。

【0044】

この発明の請求項20に係る出力レート制御装置は、前記出力信号生成部から出力される信号は、複数ビットからなるデータを単位とする区切りタイミングを発生する制御信号と、ビットを単位とする区切りタイミングを発生するビットクロックと、前記データを単位とする区切りタイミング間の一部に有効なデータを収容したシリアルデータとからなることを特徴とするものである。

【0045】

この発明の請求項21に係る出力レート制御装置は、請求項19に記載の出力レート制御装置において、前記アドレス差分データから、前記シリアルデータの出力レートを演算する演算部をさらに備えたことを特徴とするものである。

【0046】

この発明の請求項22に係る出力レート制御装置は、請求項19に記載の出力レート制御装置において、前記アドレス差分データが、ある一定値以上または以下になった場合に、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算し、前記差分データが規定範囲内の時は前記シリアルデータの出力レートを保持する演算部をさらに備えたことを特徴とするものである。

【0047】

この発明の請求項23に係る出力レート制御装置は、請求項19に記載の出力レート制御装置において、前記アドレス差分データをある一定期間積分し、その差分の積分データの極性と、前記アドレス差分データの極性から、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算する演算部をさらに備えたことを特徴とするものである。

【0048】

この発明の請求項24に係る出力レート制御装置は、請求項19に記載の出力レート制御装置において、前記アドレス差分データが示すアドレス残量に応じて、前記シリアルデータの出力レートを切替えることを特徴とするものである。

【発明の効果】

【0049】

この発明によるスピンドルモーター制御装置では、ジッターを含む光ディスクからの読み取り信号を一旦メモリに蓄えて、ジッターの少ないクロック同期で読み取ってから出力するため、ジッターマージン分だけ光ディスク(CD)の回転数を低くする必要が無くなり、最高転送レートを維持した出力が可能となる。

【0050】

さらに、サーボエラー時やメモリエンプティー時のセルフリカバリが行えるため再生信号を間欠なく出力することが可能である。

【0051】

また、メモリの書き込みデータと読み出しデータのアドレス差に基づいてスピンドルモーター制御を行うため、モーター制御周波数が低くなり、モーターの低消費電力、長寿命化が可能となる。

【0052】

この発明による出力レート制御装置では、おもにダビング装置へのデータ転送に用いられ、トラックバッファメモリの書き込みアドレスと読み出しアドレスの差分データを参照し、随時自動で出力のピッチシフト量を演算しデータ転送するため、メモリの容量が小さいときや再生データが高倍速であっても、メモリがオーバーフロー、アンダーフローすることが無く、スピンドルモーターの限界まで回転させることが出来、より短い時間でのダビングが可能である。

【0053】

即ち、この発明の請求項1に係る光ディスク装置のダビングシステムによれば、光ディスクを再生する光ディスク装置と、ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビングシステムにおいて、前記光ディスク装置が前記光ディスクの外周側を再生する際、該光ディスクが前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定する回転数設定部と、当該光ディスクの外周側においてスピンドルモーターの回転により生じるジッタを吸収するジッタ吸収部と、前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御する出力レート制御部とを備えるようにしたので、光ディスク装置から受け側装置へのダビングを行う際に、光ディスクの外周側を再生する際、極力高回転に設定でき、内周側では受け側装置のダビング速度の限界を越えない上限の出力レートでデータを転送でき、データのダビングのさらなる高速化が実現可能となる効果がある。

【0054】

また、この発明の請求項2に係る光ディスク装置のダビングシステムによれば、請求項1に記載の光ディスク装置のダビングシステムにおいて、前記光ディスク装置はCDドライブであり、前記受け側装置はMDドライブであるものとしたので、CDディスクからMDディスクへのダビングのさらなる高速化が実現可能となる効果がある。

【0055】

また、この発明の請求項3に係る光ディスク装置のダビングシステムによれば、請求項1に記載の光ディスク装置のダビングシステムにおいて、前記スピンドルモーターは、線速度一定(以下、CLVと称す)となるように回転制御されるようにしたので、内周側よりも外周側が高速に回転する第1の光ディスクの回転の高速化を内周側,外周側のそれぞれの領域でより進めることが可能となり、データのダビングのさらなる高速化が実現可能となる効果がある。

【0056】

また、この発明の請求項4に係る光ディスク装置のダビング方法によれば、光ディスクを再生する光ディスク装置と、ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビング方法において、前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御し、前記光ディスク装置が前記光ディスクの外周側を再生する際、前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定し、当該外周側におけるスピンドルモーターの回転により生じるジッタを吸収するようにしたので、光ディスク装置から受け側装置へのダビングを行う際に、光ディスクの外周側を再生する際、極力高回転に設定でき、内周側では受け側装置のダビング速度の限界を越えない上限の出力レートでデータを転送でき、データのダビングのさらなる高速化が実現可能となる効果がある。

【0057】

また、この発明の請求項5に係るスピンドルモーター制御装置によれば、光ディスク装置のスピンドルモーターの制御装置において、光学ピックアップにより復調された光ディスク再生信号を書き込むメモリと、該メモリへの書込み・読出しを制御するメモリコントローラと、該メモリコントローラの前記メモリへの書込みアドレスと読出しアドレスのアドレス差を参照してスピンドルモーター制御信号を生成するアドレス差スピンドルモーター制御部と、前記メモリから読み出した読出しデータを出力データへ変換する出力信号生成部とを備えるようにしたので、光ディスクの外周側でスピンドルモーターを可能な限り高速に回転させるとともに、このスピンドルモーター制御装置を稼動させることにより、スピンドルモーターの回転むらにより生じるジッターをメモリにより吸収でき、ダビング用の再生データを高速にかつ安定して得ることが可能となる効果がある。

【0058】

また、この発明の請求項6に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記アドレス差と、アドレス差の目標値である目標アドレス差との差に応じた位相差信号を生成する位相制御部と、前記アドレス差を保持するメモリに保持されたアドレス差と、前記アドレス差との差に応じた速度信号を生成する速度制御部とを備え、前記位相差信号と速度信号とを演算した結果を前記スピンドルモーターの制御信号として出力するようにしたので、メモリに記憶しているデータが空にならないように光ディスクの回転数を制御でき、ダビング用の再生データを高速にかつ安定して得ることが可能となる効果がある。

【0059】

また、この発明の請求項7に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、前記メモリへの書込みデータと読出しデータを、可逆圧縮伸張する可逆圧縮伸張部を備えるようにしたので、メモリへの書き込み,読み出しを行った前後でデータの品質に劣化を生じることなく、メモリの容量を削減でき、ダビング用の再生データを高速にかつ安定して得ることが可能となる効果がある。

【0060】

また、この発明の請求項8に係るスピンドルモーター制御装置によれば、請求項5ないし請求項7のいずれかに記載のスピンドルモーター制御装置において、前記メモリは、前記光ディスク装置に加わる物理的衝撃により当該光ディスク装置に生じる再生むらを緩和するショックプルーフ用のメモリであるものとしたので、物理的衝撃により生じる再生むらと回転むらによる再生品質の劣化とを同時にかつ低コストに除去でき、ダビング用の再生データを間断なく、高速にかつ安定して得ることが可能となる効果がある。

【0061】

また、この発明の請求項9に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部と、該サーボ外れ検出部で検出したサーボ外れ信号を参照して前記アドレス差スピンドルモーター制御部の出力と、固定値出力とを切替える切換え部とをさらに備えるようにしたので、サーボ外れが生じたとしてもダビング用の再生データを間断なく、高速にかつ安定して得ることが可能となる効果がある。

【0062】

また、この発明の請求項10に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部をさらに備え、前記アドレス差スピンドルモーター制御部は、該サーボ外れ検出部で検出したサーボ外れ信号を参照してサーボ外れ時にゲインを下げるようにしたので、サーボ外れが生じたとしてもすみやかに回復することが可能となり、ダビング用の再生データを間断なく、高速にかつ安定して得ることが可能となる効果がある。

【0063】

また、この発明の請求項11に係るスピンドルモーター制御装置によれば、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから一定期間前記アドレス差スピンドルモーター制御部のゲインを上げるようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0064】

また、この発明の請求項12に係るスピンドルモーター制御装置によれば、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、アドレス差が規定範囲に入るまで、前記アドレス差スピンドルモーター制御部のゲインを上げるようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0065】

また、この発明の請求項13に係るスピンドルモーター制御装置によれば、請求項10に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、位相制御部の出力の極性が反転するまで、前記アドレス差スピンドルモーター制御部のゲインを上げるようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0066】

また、この発明の請求項14に係るスピンドルモーター制御装置によれば、請求項10に記載のスピンドルモーター制御装置において、サーボ外れを検出するサーボ外れ検出部をさらに備え、該サーボ外れ検出部で検出したサーボ外れ信号を参照して、前記アドレス差スピンドルモーター制御部の出力値をホールドするようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0067】

また、この発明の請求項15に係るスピンドルモーター制御装置によれば、請求項14に記載のスピンドルモーター制御装置において、前記アドレス差スピンドルモーター制御部は、アドレス差が規定範囲を外れるとゲインを上げるようにしたので、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0068】

また、この発明の請求項16に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、線速度一定となるようにスピンドルモーターの回転を制御するCLV制御部をさらに備え、アドレス差が規定量以下になった場合に、該CLV制御部の出力信号を前記スピンドルモーター制御信号として使用するとともに、前記出力信号生成部の入力を前記光ディスク再生信号に切替えるようにしたので、メモリに記憶しているデータが空きにならないように光ディスクの回転数を制御でき、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0069】

また、この発明の請求項17に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、アドレス差が規定の範囲に入った場合、スピンドルモーター制御信号を、CLV制御部の出力からアドレス差スピンドルモーター制御部の出力に切替えると共に、前記出力信号生成部の入力を復調部からの出力からメモリからの出力に切替えるようにしたので、メモリが空きになりダビングすべきデータに欠落が生じ得る状態を脱した後、ダビング用の再生データを間断なく、高速にかつ安定して得られる状態に復帰することが可能となる効果がある。

【0070】

また、この発明の請求項18に係るスピンドルモーター制御装置によれば、請求項5に記載のスピンドルモーター制御装置において、アドレス差スピンドルモーター制御部のアドレス差が規定の範囲に入った場合、スピンドルモーターの制御周波数を下げるようにしたので、スピンドルモーターの低消費電力化および長寿命化を実現することが可能となる効果がある。

【0071】

また、この発明の請求項19に係る出力レート制御装置によれば、光ディスクから読み出した再生信号を復調・訂正する信号処理部と、該信号処理部にて復調・訂正された再生信号を書きこむメモリと、該メモリへの書き込み・読み出しを制御するメモリコントローラと、前記メモリから読み出したデータをあらかじめ決められた形式に変換し出力するための信号を生成する出力信号生成部とを備え、前記メモリコントローラは、前記メモリへの書き込みアドレスと読み出しアドレスの差であるアドレス差分データを生成し、前記出力信号生成部は、前記アドレス差分データを入力し、出力信号のレートを制御するようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0072】

また、この発明の請求項20に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記出力信号生成部から出力される信号は、複数ビットからなるデータを単位とする区切りタイミングを発生する制御信号と、ビットを単位とする区切りタイミングを発生するビットクロックと、前記データを単位とする区切りタイミング間の一部に有効なデータを収容したシリアルデータとからなるものとしたので、有効なデータを収容した部分以外を伸縮することで、出力レートを適宜変化することができ、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0073】

また、この発明の請求項21に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記アドレス差分データから、前記シリアルデータの出力レートを演算する演算部をさらに備えるようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0074】

この発明の請求項22に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記アドレス差分データが、ある一定値以上または以下になった場合に、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算し、前記差分データが規定範囲内の時は前記シリアルデータの出力レートを保持する演算部をさらに備えるようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0075】

また、この発明の請求項23に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記アドレス差分データをある一定期間積分し、その差分の積分データの極性と、前記アドレス差分データの極性から、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算する演算部をさらに備えるようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【0076】

さらに、この発明の請求項24に係る出力レート制御装置によれば、請求項19に記載の出力レート制御装置において、前記アドレス差分データが示すアドレス残量に応じて、前記シリアルデータの出力レートを切替えるようにしたので、光ディスクの内周側において光ディスクを高速回転させており、出力信号の受け側がダビング速度に限界を有する場合に、そのダビング速度の限界を越えない出力レートとなるように出力レートを抑えることが可能となり、光ディスクの読み出し速度を確保しながら、受け側のダビング速度の限界を越えない上限の出力レートを得ることが可能となる効果がある。

【発明を実施するための最良の形態】

【0077】

(実施の形態1)

本発明は、CLV制御により光ディスクを回転制御しその再生を行うCDプレーヤー(光ディスク装置)から、記録時にデータの圧縮処理を行うためダビング速度に限界を有するMDプレーヤー(受け側装置)にデータのダビングを行う状況において、CDプレーヤーが光ディスクを再生する際、外周側の高速化をスピンドルモーター制御装置により、内周側の高速化を出力レート制御装置により、それぞれ実現できるようにしたものである。

【0078】

この場合の、光ディスク装置のダビングシステムに相当するシステムコンポーネントステレオのシステムコントローラ1000およびCD制御部50の構成は図2に示すようになる。

【0079】

システムコントローラ1000内のキー入力検出部1001はキーKY入力があることを検出する。高速ダビングキー操作検出部1102は操作されたキーが高速ダビングキーであるか否かを検出する(図7のステップ110参照)。ダビング範囲判定部1003はダビング範囲がCDの全体か一部かをキー入力により判定する(ステップ111参照)。制御切換部1004は高速ダビング中のCDの再生箇所がディスクの内周側および外周側のいずれに該当するかを判定し(図4のステップ101,図7のステップ112参照)、内周側に相当する場合は内周側制御部501を(図4のステップ102参照)、外周側に相当する場合は外周側制御部502をそれぞれ動作させる(ステップ103参照)。この内周側制御部501は出力レート制御装置に、外周側制御部502はスピンドルモーター制御装置にそれぞれ対応する。この内周側と外周側との判定は図5に示すサブコードSCを用いる。このサブコードはCDより再生され、最初の曲の頭から現在の再生箇所に至るまでの経過時間を分m,秒s,フレームf(=1/30秒)で表す。

【0080】

即ち、図6に示すように、スピンドルモーター制御装置は、CDプレーヤーが再生する光ディスクの外周側における回転速度の上限付近まで回転数を上げるようにスピンドルモーターの制御を行い、かつその際のジッタの影響をショックプルーフ用のメモリで吸収し、また、出力レート制御装置は、CDプレーヤーの内周側を再生する際の高回転にジッタが加わることでMDプレーヤーのデータ圧縮処理に破綻が生じないように、出力レートの制御を行うことにより、CDプレーヤーの回転速度を光ディスクの内周側および外周側において可能な限り高回転の限界近くに維持でき、ダビングの高速化を実現できるようにしたものである。

【0081】

この点をより詳細に述べると、図7のステップ112,116において内周側と判定し、最内周から再生を開始する場合、MD側の入力許容範囲以上の出力レートとなった場合(図7のステップ118参照)、出力レートを下げ(図7のステップ119参照)、MD側の入力許容範囲内の出力レートとなるまで(図7のステップ120参照)、出力レートを下げる。また、ステップ116において外周側に入ったと判定した場合、CD上の当該再生位置における所定の回転数に設定する(図7のステップ113参照)。つぎにこの所定の回転数を保って所定時間が経過した場合(図7のステップ114参照)、スピンドルモーターの回転数を所定だけ増加する(ステップ115参照)。この操作を最外周まで繰り返す。

【0082】

これにより、例えば図6に示すように、内周側では内周側で回転可能な最大回転数でスピンドルモーターを回転でき、MDプレーヤーの圧縮処理が破綻をきたさない上限の出力レートでデータを出力することができ、外周側では出力レートを一定とし、スピンドルモーターの回転数を制御することで、高速ダビング性能を限界まで高めることが可能となる。

【0083】

なお、図5のタイムコードを利用することにより、CDの全体ではなくその一部をダビングする場合であっても、図7のフローチャートのステップ117によりその一部が内周側,外周側のいずれに該当するかを判断することで、ダビングの高速化を達成できる。

【0084】

このように、本実施の形態1によれば、非圧縮のデータを記録したCDディスクからデータを圧縮して記録するMDディスクにダビングを行う際、CDディスクの内周側では当該内周側で回転可能な上限にまでディスクの回転数を高めてその際に発生するジッターはメモリで吸収し、外周側では当該外周側でMD側での圧縮処理が正常に動作可能な上限の出力レートでデータを転送するので、ダビングの高速化を一層達成することが可能となる。

【0085】

(実施の形態2)

図1は本発明の実施の形態2による、CDプレーヤーからMDプレーヤーへ音楽データをダビングするCDシステムに搭載されるスピンドルモーター制御装置のブロック図である。

このスピンドルモーター制御装置は実施の形態1における外周側制御部に相当するものである。

【0086】

図1において、この実施の形態2によるスピンドルモーター制御装置は、CDシステム10と、メモリ16と、システムコントローラ1000とを有する。

【0087】

CDシステム10は復調(訂正)部11と、可逆圧縮部12と、メモリコントローラ13と、伸張部15と、セレクタ51と、出力信号生成部17と、サーボ外れ検出部14と、CLV/ダビング切換制御部18と、CLV制御部20と、アドレス差スピンドルモーター制御回路32と、セレクタ52と、固定値出力部21と、セレクタ53とを有する。

【0088】

また、アドレス差スピンドルモーター制御部32は、位相制御部30と、速度制御部31と、ゲイン調整部19と、加算部19aとを有する。

位相制御部30は目標アドレス差発生部22と、減算部30aとを有する。

速度制御部31はデータ保持部23と、減算部31aとを有する。

【0089】

次に動作について説明する。

(通常再生モード)

まず、使用者がキー操作により標準速でCDを再生する通常再生モードを選択したとする。

【0090】

システムコントローラ1000はキー入力により通常再生モードが選択されたと判断する。これにより、CLV/ダビング切換制御部18はCLVモードである旨のCLV/ダビング切換制御信号29を発生する。このCLV/ダビング切換信号29によりセレクタ52はCLV制御部20の出力信号を選択する。

【0091】

サーボ外れが生じていないとすると、セレクタ53はスピンドルモーター制御信号33としてセレクタ52の出力信号を選択するので、スピンドルモーター37はCLV制御部20の出力信号により標準速で線速度一定となるように、即ち内周側から外周側に向けて徐々に低回転数から高回転数に移行するように、回転制御が行われる。

【0092】

また、この時、セレクタ51は復調(訂正)部11の出力信号を選択するので、出力信号生成部17は標準速にて再生され復調(訂正)部11で復調,誤り訂正された信号を処理し、アナログ信号に変換した後、スピーカは音を発生する。

【0093】

一方、サーボ外れ検出部14がサーボ外れを検出した場合は、サーボ外れ信号38によりセレクタ53が固定値出力部21の固定値を選択し、これをスピンドルモーター制御信号33として出力する。従って、スピンドルモーター37はこの固定値によって安定した回転を回復し、サーボ外れ状態から定常状態に復帰できる。

【0094】

(ダビングモード)

次に、使用者がキー操作によりダビングモードを選択したとする。

この場合、CLV/ダビング切換制御部18の制御によりセレクタ52はアドレス差スピンドルモーター制御回路32の出力信号を選択し、セレクタ51は伸張部15の出力信号を選択する。

【0095】

まず、図示しない電圧発生部により外周側では受け側の許容倍数を超えないようにスピンドルモーター37を回転させて、光ディスクDより再生信号を読み出す。

光ディスクDより読み出された再生信号は復調(訂正)部11により信号処理が行われ、メモリコントローラ13によりメモリ16に書き込まれる。このメモリ16への書き込み,読み出しを行う際、可逆圧縮部12および伸張部15を用いることにより、メモリ16容量を削減でき、かつ圧縮伸張処理によるデータの損失をなくすようにしている。

【0096】

復調(訂正)部11は、光学ピックアップ41により光ディスクDより読み出した再生信号を復調し、復調されたデータを内部の誤り訂正部によりデータを復元し補間する。

可逆圧縮部12は、データを圧縮し圧縮したデータを伸張部15で伸張する際に、元のデータに損失を生じさせることなく伸張できる圧縮・伸張方法を実行する。

メモリ16は、書き込み、読み出し可能なRAM等で構成される。このメモリ16は本来、CDプレーヤーとMDプレーヤーとを有するCDシステムに外部から物理的な衝撃力が加わった場合に、衝撃による再生への影響を緩和するために再生データを一定期間蓄積するショックプルーフに用いられるものである。

【0097】

メモリコントローラ13は、メモリ16への書き込み、読み出しを制御するもので、メモリ16により蓄えられたデータは、メモリコントローラ13により読み出される。

メモリ16から読出されたデータ25は、出力信号生成部17により一定の転送速度に保たれ、MDプレーヤーにデータ転送される。

出力信号生成部17は、MDなどのダビングする側がダビング可能なデータ形式を生成する。

【0098】

メモリコントローラ13はメモリ16がオーバーフローやアンダーフローを起こさないように書き込みアドレス26と読み出しアドレス27を制御している。これにより、メモリコントローラ13による読み出し速度と出力信号生成部17からのデータ出力速度は同じとなり、光ディスクの回転速度を変化させた場合でもMDプレーヤーへの転送速度は一定に保たれる。これは、スピンドルモーターを外周側では受け側の許容倍数を超えないように回転させた場合に生じるジッターを、ショックプルーフ用のメモリ16で吸収することを意味する。

【0099】

このため、ジッターの影響を抑えるためにマージンを持つことなく、スピンドルモーターの回転数を限界まで高く設定することが可能となる。

【0100】

アドレス差スピンドルモーター制御部32は、位相制御部30と速度制御部31とゲイン調整部19と加算部19aとで構成される。

【0101】

位相制御部30は、メモリコントローラ13から、書き込みデータ24と、読出しデータ25とのアドレス差を任意の周波数毎に受け取り、目標アドレス差発生部22からの目標アドレス差とアドレス差34との差であるアドレス差差分ΔAD 35を生成する。

【0102】

目標アドレス差とは、書き込みデータ24と読み出しデータ25のアドレス差の目標値であり、この値は設定が可能である。目標アドレス差はメモリ16がオーバーフロー及びアンダーフローを起こさない程度に設定する必要があり、メモリ16の容量の1/2から3/4程度に設定するのが良い。本実施の形態2ではアドレス差34が目標アドレス差に近づくようにスピンドルモーター制御信号を生成する。

【0103】

速度制御部31では、減算部31aによりアドレス差34と、データ保持部23により保持されたアドレス差との差であるアドレス差差分ΔΔAD 36を生成する。

データ保持部23では、1サンプル前のアドレス差34を保持する。

ゲイン調整部19によりゲイン調整した後、加算部19aはアドレス差差分ΔAD 35とΔΔAD 36とを加算し、アドレス差34を目標アドレス差に収束するようにスピンドルの出力値を制御する。

【0104】

例えば、

スピンドルモーター制御信号=(ΔAD・Kθ)+(ΔΔAD・Kv)

と書くことができる。

但し、Kθは位相項,Kvは速度項である。

【0105】

このスピンドルモーター制御により、外周部において許容される最高回転数に設定することが可能である。

つまり、単に線速度が一定でダビングした場合はジッターの影響を見込んで高倍速を抑え気味に設定せざるを得ないが、この実施の形態2のダビングモードでは、ジッターマージン分だけ高い回転数に設定でき、この分速くダビングを行うことができる。

【0106】

また、光ディスク再生中にエラーが発生してもショックプルーフ制御が可能なメモリ16、メモリコントローラ13を備えることにより、音飛びなどを防ぐことも可能である。

さらに、アドレス差34が目標アドレス差付近の規定範囲内で収束したときは、メモリコントローラ13から受け取るアドレス差信号34のサンプリング周波数を下げることにより更にスピンドルモーター37の負担を減らすことができる。

【0107】

ところで、このようなダビングモードから脱調した場合に、自動的に元のダビングモードに復帰する、いわゆるセルフリカバリモードとして、以下の切り替えモードおよびサーボエラー回復モードがある。

【0108】

(切替えモード)

この切替えモードは、スピンドルモーター制御装置での制御方法をダビングモードとCLV(Constant Linear Velocity)モード、即ち通常再生モードとの間で切り替えを行うことにより、ショックプルーフ用メモリがエンプティとなってもデータを間断なく転送できるものである。

【0109】

以下、この切り替えについて図1及び図8ないし図11を用いて説明する。

図8はメモリの概念図である。縦軸は書き込みアドレスと読み出しアドレスとの差、すなわち、メモリに蓄積したデータの残量を示す。目標アドレス差付近を規定範囲と呼び、規定範囲内でアドレス差が収まっているならダビングモードは安定状態であると言える。また、アドレス差が小さくなりある一定の値を下回ることを規定範囲以下と呼ぶ。

【0110】

図9はCLV/ダビング切り替え制御部18の状態遷移図である。

図9に示すように、この切り替えモードは2つの状態S1,S2を有する。状態S1はダビングモード、状態S2はCLVモードであり、これらの状態における動作はそれぞれ上述したとおりである。アドレス差が規定範囲以上であればダビングモードS1を維持し、アドレス差が規定範囲以下となればCLVモードS2に移行する。アドレス差が規定範囲外であればCLVモードを維持し、規定範囲内に戻ればダビングモードS1に戻る。

【0111】

図10はこの状態遷移図に対応するフローチャートを示す。

図11はCLV/ダビング切り替え制御部18の内部構成を示す。

【0112】

図1及び図10,図11において、CLV/ダビング切換制御部18内のアドレス差信号受信部181はメモリコントローラ3よりアドレス差34を受け取り、アドレス差判定部182はダビングモード時に(図10のステップ201参照)アドレス差34が規定量以下になった場合(ステップ202参照)、CLV/ダビング切換信号発生部183はCLV/ダビング切換信号の値を変更し、ダビングモードからCLVモードに移行する(ステップ203参照)。その時、スピンドルモーター制御信号33となる信号は、アドレス差スピンドルモーター制御部32の出力から、CLV制御部20の出力に切替える。また同時に、出力信号生成部17に入力する信号はメモリコントローラ13(もしくは伸張部15)の出力から、復調(訂正)部11の出力に切替える。

【0113】

この動作により、ダビングモードより転送速度は遅くなるが、メモリ16がエンプティー状態でも、データを間欠なく転送することが可能となる。

【0114】

CLVモード再生中にアドレス差34が規定範囲に入った場合(ステップ204)、アドレス差スピンドルモーター制御部32はCLVモードからダビングモードに移行する。このとき、スピンドルモーター制御信号33をCLV制御部20の出力から、アドレス差スピンドルモーター制御部32の出力に切替える。また同時に、出力信号生成部17の入力を復調(訂正)部11の出力からメモリコントローラ13(もしくは伸張部15)の出力に切替える。

【0115】

以上の動作は、メモリ16のアドレス差34が小さければCLVモードに、大きければダビングモードとすることであり、これにより、メモリ16がエンプティー状態でも、データを間欠無く転送することが可能であり、CLVモードで再生するより高倍速でのデータ転送が可能となる。

【0116】

(サーボエラー回復モード)

このサーボエラー回復モードでは、サーボにエラーが生じた場合にゲインを上げるように調整を行うことでダビングモードへの復帰を行う。この回復動作について図1及び図12ないし図14を用いて説明する。

【0117】

図1において、サーボ外れ検出部14は光ディスクDより読み出されたフレーム同期信号を検出出来なかった場合にサーボ外れ信号38を出力する。

サーボエラー回復モードにおけるスピンドルモーター制御装置の制御方法として、スピンドルモーター制御信号33を任意の一定値にする強制出力モードと、ダビングモードがある。

【0118】

また、ダビングモード時アドレス差34が規定範囲内にある場合は、安定状態と呼ぶことにする。図12の状態遷移図を用いて本実施の形態2のサーボエラー時の動作について説明する。

【0119】

このサーボエラー回復モードは3つの状態S3,S4,S5を有する。ダビングモードS3は、図9における状態S1と同様のものである。状態D4はゲインを下げるとともに固定値を出力し、状態S5ではゲインを上げる。サーボ外れ信号が未検出であればダビングモードS3を維持し、サーボ外れ信号が検出されれば状態S4に遷移する。状態S4においてサーボ外れ信号が検出され続ければ状態S4を維持し、サーボ外れ信号が未検出となれば状態S5に移行する。状態S5においてアドレス差が規定範囲外であれば状態S5を維持し、アドレス差が規定範囲内に収まれば状態S3に戻る。

【0120】

図13はこの状態遷移図に対応するフローチャートである。

ダビングモード(ステップ301)で光ディスクDを再生中にサーボ外れ検出部により、フレーム同期信号が未検出となり、サーボ外れ信号38が出力される。サーボ外れ信号38が検出されると(ステップ302)、メモリ16に書き込まれる入力信号がなくなり、アドレス差34が小さくなるため、アドレス差スピンドルモーター制御部32の出力はスピンドルモーター37を加速させる方向になり、逆にサーボを引き込みにくくしてしまう。これを防ぐために、サーボ外れ信号38を検出したときの動作として、ダビングモードを強制出力モードに切り替えスピンドルモーター37の加速を抑える制御を行う。また別の方法として、サーボ外れ信号38を検出したとき、ダビングモードを維持したままゲインを下げる(ステップ303)ことによりスピンドルモーター37の加速を抑える。以上の制御を行うことでサーボを引き込みやすくする。

【0121】

以上の動作の結果、サーボを引き込みサーボ外れ信号38が未検出となった場合、ダビングモードに復帰させアドレス差34を大きくする目的で、ゲイン調整部19のゲインを一定期間もしくはアドレス差34が規定範囲内になるまで上げる。これによりダビングモードの安定状態へ短時間で復帰させることが可能となる。また、別の方法として、サーボを引き込みサーボ外れ信号38が未検出となった場合(ステップ304)、ΔADの極性が負から正になるまでゲイン調整部19のゲインを上げる(ステップ305)。アドレス差が規定範囲内に戻れば(ステップ306)、ダビングモードに戻る。いずれの制御においてもダビングモードの安定状態への短時間での復帰が可能となる。

【0122】

このように、本実施の形態2によるスピンドルモーター制御装置によれば、CLVにより回転制御を行っているCDプレーヤーからMDプレーヤーにダビングを行う際、CDの外周側において、スピンドルモーターをその限界回転数で回転し再生を行うようにその制御信号を固定値に設定し、CLV制御により生じるジッタはショックプルーフ用メモリにより吸収することで、CDの外周側におけるMDへのダビングを高速化することが可能となる。

【0123】

(実施の形態3)

この実施の形態3は、出力レート制御装置に関するものである。この出力レート制御装置は、実施の形態1における内周側制御部に相当するものである。

【0124】

出力レート制御装置は、光ディスクの内周側において、スピンドルモーターの限界回転数で再生しようとすると、ジッタの影響で、出力レートがMD側のエンコーダの処理能力を越えてしまい、エンコーダの処理に破綻が生じてしまうことがあり、スピンドルモーターの限界回転数で再生することが出来ず、ダビングなどを行う際にダビング時間が多くかかってしまうという問題を解決できるものである。

【0125】

即ち、メモリ容量が小さく高倍速で再生している場合、出力信号のレートを外部から制御していたのではメモリがオーバーフローやアンダーフローを起こしてしまうことが多い。

本実施の形態3の出力レート制御装置では、こうしたメモリオーバーフローやメモリアンダーフローを防ぐために、メモリのアドレス差分データを随時監視し、アドレス差分データを演算しピッチシフト量を得て、出力信号のレートを自動で変更することでメモリのオーバーフローやアンダーフローを防ぎ、より高倍速でのデータ転送が可能になるようにしたものである。

【0126】

図15は本発明の実施の形態3におけるCDプレーヤーからMDプレーヤーへ音楽データをダビングする際のCDプレーヤーの主要なブロック図である。

この例では、記録する装置、つまりMDプレーヤーへ音楽データをダビング用途等のために高倍速で転送するためのものである。

【0127】

図15において、音楽CDディスク等の光ディスクDが、スピンドルモーターにより一定の回転数に保たれ回転するものとする。つまり、線速度は内周から外周にかけて徐々に速くなるわけである。今仮に、スピンドルモーターの限界回転数を2000rpmとすれば最内周ではその4倍で再生することになる。CDプレーヤーの再生可能倍速とMDのダビング可能倍速がともに4倍以上であるなら、最内周ではスピンドルモーターの性能により約4倍速でのダビングしか出来ないことになる。

【0128】

光学ピックアップ41は、光ディスクDから得られる音楽データを読み取る。光学ピックアップ41により読み取られた音楽データは、まずデータスライス部63により、2値にスライスされた音楽データが生成されるとともに、そのPLL機能により音楽データの再生速度と同期したクロックが生成される。

【0129】

2値化された音楽データは信号処理部64によりEFM(Eight to Fourteen Modulation)復調される。復調後のデータは、書き込み系641により信号処理部64内のCIRC(Cross Interleaved Reed−solomon Code)と呼ばれる誤り訂正部に入り、読み出されたデータが正しいか誤っているかを判断し、誤ったデータを訂正する。このときにメモリであるCIRCRAM642が使用され、読み出し系643により読み出しが行われる。通常モードの場合はCIRCRAM642への書き込みは光ディスクの回転と同期して行われ、CIRCRAM642の読み出しは水晶発振子と同期して出力することにより、スピンドルモーターの回転ジッターをメモリで吸収する。

【0130】

しかしながら、スピンドルモーターの回転数が一定であり、線速度が一定でないときを考える。CIRCRAM642の読み出しは書き込みと同期して行われ、信号処理部内では光ディスクの回転と同期して信号が処理される。スピンドルモーターの回転数が一定であることによる線速度の変化をCIRCRAM642で吸収しようとしても、これには、メモリ容量が不十分で、オーバーフローを起こしやすい。そのため線速度の変化をショックプルーフメモリ16で吸収し、書き込み、読み出しを制御して高倍速での安定したデータ転送を行う。

【0131】

復調・訂正された音楽データはメモリコントローラ63で制御され、ショックプルーフメモリ16への書き込み,読み出しが行われる。このときショックプルーフメモリ16への書き込みは光ディスクDの回転と同期して書き込まれる。MDプレーヤーへの転送速度とショックプルーフメモリ16からの読み出しは同期しており、MDプレーヤーへの転送速度を切替えることによりショックプルーフメモリ16の読み出し速度を変化させる。これにより、ショックプルーフメモリ16のオーバーフロー、アンダーフローを防ぐ。

【0132】

シリアル出力信号生成部69では、ショックプルーフメモリ16より読み出された音楽データをダビング装置であるMDプレーヤー側がダビング可能なフォーマットに変換し、出力レートを設定し出力する。また、メモリコントローラ63から書き込みアドレスと読み出しアドレスのアドレス差の差分データを受け取り、差分データを演算することにより出力のピッチシフト量を演算する。また、出力レートよりメモリコントローラ63においてショックプルーフメモリ16の読み出しの動作速度を制御する。

【0133】

転送データのフォーマットとしてのシリアル出力の信号波形を図16に示す。図16に示すように、データSRDATA 221、Lch、Rch識別信号 LRCK222、ビットクロック BCLK 223の3線によりシリアル出力を伝送する。このシリアル出力の特徴として、データSRD/ATA221は1LRCKのうち0ビットから15ビットまでが音声データであり、16ビットから31ビットまではInvalidとして扱う。また、Lch、Rch識別信号 LRCK222の1つのLRCK中には通常32クロックのビットクロックBCLKがある。そのためシリアル出力の転送レートはデータSRDATA221のビット数が32のままで、BCLK223とLRCK222の周期を変化させて、それに伴いSRDATA221を伸縮させることにより転送レートを変化する場合と、1LRCK中のSRDATA221をLSBから16ビットはそのままでMSBからnビット増減させ、それに伴い1LRCK中のBCLK223のクロック数をnクロック増減することにより転送レートを変化させる場合、の2種類がある。例えば、BCLKの周波数を1倍速再生時の4倍にし、SRDATAの16ビット目から31ビット目までを削ることにより、4×32/(32−16)=8倍速でのデータ転送が可能となる。

【0134】

図17はシリアル出力信号生成部69の詳細ブロック図である。図17を用いて前記で説明したシリアル出力の生成方法を説明する。ビットクロックBCLKは図示しない水晶発振器で発生した水晶クロックを分周部694で分周することにより生成する。

【0135】

このシリアル出力信号生成部69はアドレス差分データを演算しピッチシフト量を決定するアドレス差分データ演算部691と、1LRCK中にBCLKが何個存在するかを設定するピッチシフトアップダウンカウンタ692と、ピッチシフトアップダウンカウンタの値をロードしカウントダウンするダウンカウンタ693とを有し、カウント値が0になると信号を反転することでLRCKを生成する。パラレルデータを入力しダウンカウンタのカウント値を用いてパラレル−シリアル変換を行い、SRDATAを作成する。

【0136】

シリアル出力信号生成部69の出力レート制御方法について以下に述べる。前記のようにショックプルーフメモリ16への書き込みアドレスと読み出しアドレスとの差分データ73をメモリコントローラ63から受け取る。ここでメモリのアドレス差分データ73をメモリの残量と言い換えるとともに、図18を用いてショックプルーフメモリ16の制御方法について説明する。

【0137】

まず、目標メモリ残量を任意の値に設定する(図18(a)参照)。ショックプルーフメモリ16のオーバーフロー、アンダーフローを防ぐために、メモリ容量の1/2から3/4あたりに設定するのが良い。目標メモリ残量と現在のメモリ残量とを比較し、現在のメモリ残量が目標メモリ残量より少なければ、シリアル出力信号生成部69の出力レートを下げるようにピッチシフト量を演算する。現在のメモリ残量が目標メモリ残量より多ければ、シリアル出力信号生成部の出力レートを上げるようにピッチシフト量を演算する。このようにショックプルーフメモリに継続的に書き込まれる音楽データをメモリ残量が目標メモリ残量に近づくようにシリアル出力信号生成部69の出力レートを変化させることにより、ショックプルーフメモリのオーバーフロー、アンダーフローを防ぐ。

【0138】

シリアル出力信号生成部におけるピッチシフト量の演算方法として以下に例をあげる。1LRCK中のBCLKのクロック数を16から127まで設定できるとすれば、ピッチシフト量は16から127まで設定できる。SRDATAのデータ部分は16ビットあるため16以下には設定できない。通常1LRCKは32クロックのビットクロックBCLKがあるため、32を基準値とし前記のピッチシフト量の演算により基準値32からカウントアップ、又はカウントダウンする。1LRCK中のBCLKのクロック数を変化させることによりピッチシフト量を随時決定し出力レートに反映させる。この方法で出力レートを変化させた場合は、BCLKの周期は変わらない。

【0139】

図18(b)に示すように、シリアル出力信号生成部69は、目標メモリ残量(上限)および目標メモリ残量(下限)を設定し、現在のメモリ残量が目標メモリ残量(上限)以上の時は、ピッチシフト量のカウンタ値を下げることで出力レートを上げメモリの残量を減らす方向に移行する。現在のメモリ残量が目標メモリ残量(下限)以下の時は、ピッチシフト量のカウンタ値を上げることで出力レートを下げメモリの残量を増やす方向に移行する。現在のメモリ残量が目標メモリ残量(上限)と目標メモリ残量(下限)の間にある時はピッチシフトを行わずピッチシフト量の値を保持する。ピッチシフト量のカウンタ値により出力レートを決定し、メモリ残量が目標メモリ残量付近で収束するように制御する。

【0140】

また、アドレス差分データ演算部691は、ある一定期間のメモリ残量を積分し、その極性を判定する。現在のメモリ残量と目標メモリ残量との差の極性が正であり、且つ積分値の極性が正であるならピッチシフト量のカウンタ値を上げ、積分値の極性が負であるならピッチシフト量のカウンタ値を保持する。また、現在のメモリ残量と目標メモリ残量との差の極性が負であり、且つ積分値の極性が正であるならピッチシフト量のカウンタ値を保持し、積分値の極性が負であるならピッチシフト量のカウンタ値を下げる。ピッチシフト量のカウンタ値により出力レートを決定し、メモリ残量が目標メモリ残量付近で収束するように制御する。

【0141】

図18(c)のようにメモリをn分割し、それぞれの領域毎に出力レートを設定しておき、現在のメモリ残量とメモリの領域を参照し、出力レートを切替える。

【0142】

以上はそれぞれ出力レートを制御する方法であり、これらを実行することでショックプルーフメモリ16のオーバーフローやアンダーフローを抑制し、高倍速でのデータ転送を安定して行うことができる。

【0143】

このように、実施の形態3による出力レート制御装置によれば、トラックバッファメモリを備え、メモリのアドレス差分データを随時監視し、アドレス差分データを演算しピッチシフト量を得て、出力信号のレートを自動で変更することにより、メモリのオーバーフローやアンダーフローを防ぎ、高倍速でも安定した再生信号のデータ転送を行うことが可能となる。

【0144】

このため、光ディスクの内周側において、スピンドルモーターの限界回転数で再生しようとすると、ジッタの影響で、出力レートがMD側のエンコーダの処理能力を越えてしまい、エンコーダの処理に破綻が生じてしまい、このため、スピンドルモーターの限界回転数で再生することが出来ず、ダビングなどを行う際にダビング時間が多くかかってしまう、という問題、および、スピンドルモーターの回転数の限界で光ディスクを再生した場合、メモリ容量が小さく高倍速で再生している場合、出力信号のレートを外部から制御していたのではメモリがオーバーフローやアンダーフローを起こしてしまうことが多い、という問題を解決でき、アナログPLL部が不要となり、高倍速でも安定した再生信号のデータ転送が可能となり、CDディスクからMDディスクへのダビングを高速に行うことが可能となる効果がある。

【0145】

なお、上記各実施の形態では、ハードウエアとして実現した場合を説明したが、ハードウエアでしか実現できない箇所を除き、ソフトウエアにより実現してもよい。

【0146】

また、音楽CDディスクからMDディスクへのダビングを例にとって説明したが、第1のメディアが非圧縮のデータを記録したものであり、第2のメディアが圧縮したデータを記録するものであれば、他の光ディスクであってもよく、さらには半導体メモリや磁気ディスク等の他のメディアであってもよい。

【産業上の利用可能性】

【0147】

以上のように、本発明のスピンドルモータ制御装置は、メモリ、メモリコントローラ、出力信号生成部及びアドレス差スピンドルモーター制御部を備えることにより、光ディスク再生装置、例えばCDやDVDなどを再生する装置の高倍速再生に適しており、ショックプルーフ用のメモリを使用するため再生データを間欠なく再生することが可能である。このため、ディスクの回転ムラによるジッタに関係なく一定の転送速度でデータを出力することができ、データのダビングを一層高速化するのに適する。

【0148】

また、スピンドルモーター制御周波数が低くモーターの低消費電力、長寿命化が可能となり、その産業上の利用可能性は非常に広く且つ大きい。

【0149】

また、本発明の出力レート制御装置は、復調・訂正を行う信号処理部と、トラックバッファメモリ、メモリコントローラ、出力信号生成部を備えており、スピンドルモーターを最大回転数で光ディスクを再生する場合や、トラックバッファメモリの容量が小さい場合でも、メモリのオーバーフローやアンダーフローを起こさずに、高倍速でデータ出力が可能であり、デジタルダビング装置へのデータ転送が可能な再生装置として有用であり、その産業上の利用可能性は非常に広く且つ大きい。

【図面の簡単な説明】

【0150】

【図1】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行うダビングシステムを示す図

【図2】本発明の実施の形態1におけるシステムコントローラおよびCD制御部のブロック構成を示す図

【図3】本発明の実施の形態1における動作モードの相違を表わす表を示す図

【図4】本発明の実施の形態1における動作モードの切換えを行うフローチャートを示す図

【図5】CDディスクにおける経過時間を示すタイムコードを示す図

【図6】本発明の実施の形態1におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の回転倍速の変化を示す図

【図7】本発明の実施の形態1におけるCDプレーヤーからMDプレーヤーへのダビングを行う際のフローチャートを示す図

【図8】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際のメモリの残量の制御指標を示す図

【図9】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の動作状態の遷移を示す状態遷移図

【図10】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の動作状態の遷移を示すフローチャート図

【図11】本発明の実施の形態3におけるCDプレーヤーからMDプレーヤーへのダビングを行う際のCLV/ダビング切換制御部のブロック構成を示す図

【図12】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の動作状態の遷移を示す状態遷移図

【図13】本発明の実施の形態2におけるCDプレーヤーからMDプレーヤーへのダビングを行う際の動作状態の遷移を示すフローチャート図

【図14】本発明の実施の形態2におけるサーボ外れ検出部のブロック構成を示す図

【図15】本発明の実施の形態3におけるCDプレーヤーからMDプレーヤーへのダビングを行うダビングシステムを示す図

【図16】本発明の実施の形態3におけるCDプレーヤーからMDプレーヤーへのダビングを行う際のシリアル出力のデータフォーマットを示す図

【図17】本発明の実施の形態3におけるシリアル出力信号生成部のブロック構成を示す図

【図18】本発明の実施の形態3によるメモリ残量制御の様子を示す図

【図19】本発明が適用される対象であるシステムコンポーネントを示す図

【図20】本発明が適用される対象であるシステムコンポーネントのブロック構成を示す図

【図21】従来のシステムコンポーネントのシステムコントローラ及びCD制御部のブロック構成を示す図

【図22】従来のシステムコンポーネントの高速ダビング時のCDプレーヤーの回転数を示す図

【図23】従来のシステムコンポーネントのCDシステムの構成を示す図

【図24】従来のシステムコンポーネントのCDシステムの構成を示す図

【符号の説明】

【0151】

D 光ディスク

10 CDシステム

11 復調(訂正)部

12 可逆圧縮部

13 メモリコントローラ

14 サーボ外れ検出部

15 伸張部

16 メモリ

17 出力信号生成部

18 CLV/ダビング切換制御部

19 ゲイン調整部

20 CLV制御部

21 固定値出力発生部

22 目標アドレス差発生部

23 データ保持部

24 書き込みデータ

25 読み出しデータ

26 メモリへのデータ書きこみの際のアドレス(WAD)

27 メモリからのデータ読み出しの際のアドレス(RAD)

28 EMP信号

29 CLV/ダビング切換信号

30 位相制御部

31 速度制御部

32 アドレス差スピンドルモーター制御部

33 スピンドルモーター制御信号

34 アドレス差信号

35 ΔAD信号

36 ΔΔAD信号

37 スピンドルモーター

38 サーボ外れ信号

41 光学ピックアップ

63 データスライス部

64 信号処理部(復調・訂正)

69 シリアル出力信号生成部

1000 システムコントローラ

【特許請求の範囲】

【請求項1】

光ディスクを再生する光ディスク装置と、

ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、

前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビングシステムにおいて、

前記光ディスク装置が前記光ディスクの外周側を再生する際、該光ディスクが前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定する回転数設定部と、

当該光ディスクの外周側においてスピンドルモーターの回転により生じるジッタを吸収するジッタ吸収部と、

前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御する出力レート制御部とを備えた、

ことを特徴とする光ディスク装置のダビングシステム。

【請求項2】

請求項1に記載の光ディスク装置のダビングシステムにおいて、

前記光ディスク装置はCDドライブであり、

前記受け側装置はMDドライブである、

ことを特徴とする光ディスク装置のダビングシステム。

【請求項3】

請求項1に記載の光ディスク装置のダビングシステムにおいて、

前記スピンドルモーターは、線速度一定(以下、CLVと称す)となるように回転制御される、

ことを特徴とする光ディスク装置のダビングシステム。

【請求項4】

光ディスクを再生する光ディスク装置と、

ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、

前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビング方法において、

前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御し、

前記光ディスク装置が前記光ディスクの外周側を再生する際、前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定し、

当該外周側におけるスピンドルモーターの回転により生じるジッタを吸収する、

ことを特徴とする光ディスク装置のダビング方法。

【請求項5】

光ディスク装置のスピンドルモーターの制御装置において、

光学ピックアップにより復調された光ディスク再生信号を書き込むメモリと、

該メモリへの書込み・読出しを制御するメモリコントローラと、

該メモリコントローラの前記メモリへの書込みアドレスと読出しアドレスのアドレス差を参照してスピンドルモーター制御信号を生成するアドレス差スピンドルモーター制御部と、

前記メモリから読み出した読出しデータを出力データへ変換する出力信号生成部とを備えた、

ことを特徴とするスピンドルモーター制御装置。

【請求項6】

請求項5に記載のスピンドルモーター制御装置において、

前記アドレス差スピンドルモーター制御部は、

前記アドレス差と、アドレス差の目標値である目標アドレス差との差に応じた位相差信号を生成する位相制御部と、

前記アドレス差を保持するメモリに保持されたアドレス差と、前記アドレス差との差に応じた速度信号を生成する速度制御部とを備え、

前記位相差信号と速度信号とを演算した結果を前記スピンドルモーターの制御信号として出力する、

ことを特徴とするスピンドルモーター制御装置。

【請求項7】

請求項5に記載のスピンドルモーター制御装置において、

前記メモリへの書込みデータと読出しデータを、可逆圧縮伸張する可逆圧縮伸張部を備えた、

ことを特徴とするスピンドルモーター制御装置。

【請求項8】

請求項5ないし請求項7のいずれかに記載のスピンドルモーター制御装置において、

前記メモリは、前記光ディスク装置に加わる物理的衝撃により当該光ディスク装置に生じる再生むらを緩和するショックプルーフ用のメモリである、

ことを特徴とするスピンドルモーター制御装置。

【請求項9】

請求項5に記載のスピンドルモーター制御装置において、

前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部と、

該サーボ外れ検出部で検出したサーボ外れ信号を参照して前記アドレス差スピンドルモーター制御部の出力と、固定値出力とを切替える切換え部とをさらに備えた、

ことを特徴とするスピンドルモーター制御装置。

【請求項10】

請求項5に記載のスピンドルモーター制御装置において、

前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部をさらに備え、

前記アドレス差スピンドルモーター制御部は、該サーボ外れ検出部で検出したサーボ外れ信号を参照してサーボ外れ時にゲインを下げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項11】

請求項10に記載のスピンドルモーター制御装置において、

前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから一定期間前記アドレス差スピンドルモーター制御部のゲインを上げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項12】

請求項10に記載のスピンドルモーター制御装置において、

前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、アドレス差が規定範囲に入るまで、前記アドレス差スピンドルモーター制御部のゲインを上げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項13】

請求項10に記載のスピンドルモーター制御装置において、

前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、位相制御部の出力の極性が反転するまで、前記アドレス差スピンドルモーター制御部のゲインを上げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項14】

請求項10に記載のスピンドルモーター制御装置において、

サーボ外れを検出するサーボ外れ検出部をさらに備え、

該サーボ外れ検出部で検出したサーボ外れ信号を参照して、前記アドレス差スピンドルモーター制御部の出力値をホールドする、

ことを特徴とするスピンドルモーター制御装置。

【請求項15】

請求項14に記載のスピンドルモーター制御装置において、

前記アドレス差スピンドルモーター制御部は、アドレス差が規定範囲を外れるとゲインを上げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項16】

請求項5に記載のスピンドルモーター制御装置において、

線速度一定となるようにスピンドルモーターの回転を制御するCLV制御部をさらに備え、

アドレス差が規定量以下になった場合に、該CLV制御部の出力信号を前記スピンドルモーター制御信号として使用するとともに、前記出力信号生成部の入力を前記光ディスク再生信号に切替える、

ことを特徴とするスピンドルモーター制御装置。

【請求項17】

請求項5に記載のスピンドルモーター制御装置において、

アドレス差が規定の範囲に入った場合、スピンドルモーター制御信号をCLV制御部の出力からアドレス差スピンドルモーター制御部の出力に切替えると共に前記出力信号生成部の入力を復調部からの出力からメモリからの出力に切替える、

ことを特徴とするスピンドルモーター制御装置。

【請求項18】

請求項5に記載のスピンドルモーター制御装置において、

アドレス差スピンドルモーター制御部のアドレス差が規定の範囲に入った場合、スピンドルモーターの制御周波数を下げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項19】

光ディスクから読み出した再生信号を復調・訂正する信号処理部と、

該信号処理部にて復調・訂正された再生信号を書きこむメモリと、

該メモリへの書き込み・読み出しを制御するメモリコントローラと、

前記メモリから読み出したデータをあらかじめ決められた形式に変換し出力するための信号を生成する出力信号生成部とを備え、

前記メモリコントローラは、前記メモリへの書き込みアドレスと読み出しアドレスの差であるアドレス差分データを生成し、

前記出力信号生成部は、前記アドレス差分データを入力し、出力信号のレートを制御する、

ことを特徴とする出力レート制御装置。

【請求項20】

請求項19に記載の出力レート制御装置において、

前記出力信号生成部から出力される信号は、複数ビットからなるデータを単位とする区切りタイミングを発生する制御信号と、ビットを単位とする区切りタイミングを発生するビットクロックと、前記データを単位とする区切りタイミング間の一部に有効なデータを収容したシリアルデータとからなる、

ことを特徴とする出力レート制御装置。

【請求項21】

請求項19に記載の出力レート制御装置において、

前記アドレス差分データから、前記シリアルデータの出力レートを演算する演算部をさらに備えた、

ことを特徴とする出力レート制御装置。

【請求項22】

請求項19に記載の出力レート制御装置において、

前記アドレス差分データが、ある一定値以上または以下になった場合に、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算し、前記差分データが規定範囲内の時は前記シリアルデータの出力レートを保持する演算部をさらに備えた、

ことを特徴とする出力レート制御装置。

【請求項23】

請求項19に記載の出力レート制御装置において、

前記アドレス差分データをある一定期間積分し、その差分の積分データの極性と、前記アドレス差分データの極性から、前記書き込みアドレスに前記読み出しアドレスが追従するように前記シリアルデータの出力レートを演算する演算部をさらに備えた、

ことを特徴とする出力レート制御装置。

【請求項24】

請求項19に記載の出力レート制御装置において、

前記アドレス差分データが示すアドレス残量に応じて、前記シリアルデータの出力レートを切替える、

ことを特徴とする出力レート制御装置。

【請求項1】

光ディスクを再生する光ディスク装置と、

ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、

前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビングシステムにおいて、

前記光ディスク装置が前記光ディスクの外周側を再生する際、該光ディスクが前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定する回転数設定部と、

当該光ディスクの外周側においてスピンドルモーターの回転により生じるジッタを吸収するジッタ吸収部と、

前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御する出力レート制御部とを備えた、

ことを特徴とする光ディスク装置のダビングシステム。

【請求項2】

請求項1に記載の光ディスク装置のダビングシステムにおいて、

前記光ディスク装置はCDドライブであり、

前記受け側装置はMDドライブである、

ことを特徴とする光ディスク装置のダビングシステム。

【請求項3】

請求項1に記載の光ディスク装置のダビングシステムにおいて、

前記スピンドルモーターは、線速度一定(以下、CLVと称す)となるように回転制御される、

ことを特徴とする光ディスク装置のダビングシステム。

【請求項4】

光ディスクを再生する光ディスク装置と、

ダビング速度に限界を有し、該光ディスク装置が再生したデータがダビングされる受け側装置と、を備え、

前記光ディスク装置と前記受け側装置間でデータのダビングを行う光ディスク装置のダビング方法において、

前記光ディスク装置が前記光ディスクの内周側を再生する際、前記受け側装置のダビング速度の限界を越えないよう、前記光ディスク装置の出力レートを制御し、

前記光ディスク装置が前記光ディスクの外周側を再生する際、前記受け側装置の許容倍速を超えないよう、該光ディスクを回転させるスピンドルモーターの回転数を設定し、

当該外周側におけるスピンドルモーターの回転により生じるジッタを吸収する、

ことを特徴とする光ディスク装置のダビング方法。

【請求項5】

光ディスク装置のスピンドルモーターの制御装置において、

光学ピックアップにより復調された光ディスク再生信号を書き込むメモリと、

該メモリへの書込み・読出しを制御するメモリコントローラと、

該メモリコントローラの前記メモリへの書込みアドレスと読出しアドレスのアドレス差を参照してスピンドルモーター制御信号を生成するアドレス差スピンドルモーター制御部と、

前記メモリから読み出した読出しデータを出力データへ変換する出力信号生成部とを備えた、

ことを特徴とするスピンドルモーター制御装置。

【請求項6】

請求項5に記載のスピンドルモーター制御装置において、

前記アドレス差スピンドルモーター制御部は、

前記アドレス差と、アドレス差の目標値である目標アドレス差との差に応じた位相差信号を生成する位相制御部と、

前記アドレス差を保持するメモリに保持されたアドレス差と、前記アドレス差との差に応じた速度信号を生成する速度制御部とを備え、

前記位相差信号と速度信号とを演算した結果を前記スピンドルモーターの制御信号として出力する、

ことを特徴とするスピンドルモーター制御装置。

【請求項7】

請求項5に記載のスピンドルモーター制御装置において、

前記メモリへの書込みデータと読出しデータを、可逆圧縮伸張する可逆圧縮伸張部を備えた、

ことを特徴とするスピンドルモーター制御装置。

【請求項8】

請求項5ないし請求項7のいずれかに記載のスピンドルモーター制御装置において、

前記メモリは、前記光ディスク装置に加わる物理的衝撃により当該光ディスク装置に生じる再生むらを緩和するショックプルーフ用のメモリである、

ことを特徴とするスピンドルモーター制御装置。

【請求項9】

請求項5に記載のスピンドルモーター制御装置において、

前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部と、

該サーボ外れ検出部で検出したサーボ外れ信号を参照して前記アドレス差スピンドルモーター制御部の出力と、固定値出力とを切替える切換え部とをさらに備えた、

ことを特徴とするスピンドルモーター制御装置。

【請求項10】

請求項5に記載のスピンドルモーター制御装置において、

前記スピンドルモーターがサーボ外れを起こしたことを検出するサーボ外れ検出部をさらに備え、

前記アドレス差スピンドルモーター制御部は、該サーボ外れ検出部で検出したサーボ外れ信号を参照してサーボ外れ時にゲインを下げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項11】

請求項10に記載のスピンドルモーター制御装置において、

前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから一定期間前記アドレス差スピンドルモーター制御部のゲインを上げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項12】

請求項10に記載のスピンドルモーター制御装置において、

前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、アドレス差が規定範囲に入るまで、前記アドレス差スピンドルモーター制御部のゲインを上げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項13】

請求項10に記載のスピンドルモーター制御装置において、

前記アドレス差スピンドルモーター制御部は、前記サーボ外れ検出部でサーボ外れが未検出となってから、位相制御部の出力の極性が反転するまで、前記アドレス差スピンドルモーター制御部のゲインを上げる、

ことを特徴とするスピンドルモーター制御装置。

【請求項14】

請求項10に記載のスピンドルモーター制御装置において、

サーボ外れを検出するサーボ外れ検出部をさらに備え、

該サーボ外れ検出部で検出したサーボ外れ信号を参照して、前記アドレス差スピンドルモーター制御部の出力値をホールドする、