光ファイバジャイロスコープにおいて限られた電源品質でジャイロスコープ誤差を低減するシステム

【課題】光ファイバジャイロスコープにおいて限られた電源品質でジャイロスコープ誤差を低減する。

【解決手段】1つの実施の形態は、少なくとも1つの主電源と、前記主電源を前記光ファイバジャイロスコープに含まれる復調器に動作可能に結合する少なくとも1つの復調器ローカル電源と、前記主電源を前記光ファイバジャイロスコープに含まれるバイアス変調器に動作可能に結合する少なくとも1つの変調器ローカル電源とを備える光ファイバジャイロスコープのための電源を対象とする。前記復調器ローカル電源は、前記復調器に電流を供給する第1の電流源と、前記復調器に関連付けられる負荷の両端に結合される第1のシャントレギュレータとを備える。前記変調器ローカル電源は、前記バイアス変調器に電流を供給する第2の電流源と、前記バイアス変調器に関連付けられる負荷の両端に結合される第2のシャントレギュレータとを備える。

【解決手段】1つの実施の形態は、少なくとも1つの主電源と、前記主電源を前記光ファイバジャイロスコープに含まれる復調器に動作可能に結合する少なくとも1つの復調器ローカル電源と、前記主電源を前記光ファイバジャイロスコープに含まれるバイアス変調器に動作可能に結合する少なくとも1つの変調器ローカル電源とを備える光ファイバジャイロスコープのための電源を対象とする。前記復調器ローカル電源は、前記復調器に電流を供給する第1の電流源と、前記復調器に関連付けられる負荷の両端に結合される第1のシャントレギュレータとを備える。前記変調器ローカル電源は、前記バイアス変調器に電流を供給する第2の電流源と、前記バイアス変調器に関連付けられる負荷の両端に結合される第2のシャントレギュレータとを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光ファイバジャイロスコープにおいて限られた電源品質でジャイロスコープ誤差を低減するシステムに関する。

[連邦政府による資金提供を受けた研究開発に関する記載]

本発明は、空軍研究所によって与えられた契約番号第FA9453−08−C−0263号に基づく政府支援でなされたものである。政府は、本発明に一定の権利を有する。

【背景技術】

【0002】

干渉光ファイバジャイロスコープ(IFOG)は、光ファイバコイル内を対向伝播する電磁波を利用してコイルのまわりの回転を検知するものであるが、電子雑音の影響を受けやすい可能性がある。このような光ファイバジャイロスコープは、バイアス変調を用いて、インターフェログラムの速度検知部に対してジャイロスコープをバイアスする。バイアス変調周波数は、復調回路部内へ結合して、バイアスオフセット及び不感帯の増加を引き起こす可能性がある。例えば、復調アナログ/デジタル変換器に存在するどのコヒーレント(同相)雑音もエラー源であり、バイアス安定性、バイアスオフセット、及びジャイロスコープ不感帯のサイズに影響を与える。

【発明の概要】

【発明が解決しようとする課題】

【0003】

従来のIFOG電子機器は、電源雑音及び内部雑音を十分にフィルタリング除去するが、このようなIFOG電子機器は、電源の基準として雑音の少ない低インピーダンスのシャーシ接地接続を有する接地方式を必要とする。この手法は、ジャイロスコープが、電力伝送及びデータ伝送用にスリップリングを用いて回転されるジンバル化球(gimbaled sphere)で機能するが、次世代慣性基準システムは、スリップリングを用いず、その代わり、データ伝送及び電力伝送の双方に無線技術を用いる。この無線手法は、シャーシ(アース)接地接続を除去し、電子機器が、フローティング電源基準に起因した雑音の影響を受けやすくなる可能性がある。

【0004】

バイアス変調回路部用及び対応する復調回路部用に別々の電源を用いて、IFOG軸ことに別々の電源を用いることが可能であるが、これは、サイズ及び電力消耗が増加することから大部分実用的ではない。外部電源及び複数の分離された電源からの内部回路部の双方のサイズは法外なものになる。その上、複数の電源からの余分な電力消耗も、通常は小さなシステム電力バジェットに負担となる。加えて、慣性基準システムが非常に低いリップル電圧でジャイロスコープに電力を提供することを必要とすることは、常に実用的であるとは限らない。

【課題を解決するための手段】

【0005】

1つの実施の形態は、少なくとも1つの主電源と、前記主電源を前記光ファイバジャイロスコープに含まれる復調器に動作可能に結合する少なくとも1つの復調器ローカル電源と、前記主電源を前記光ファイバジャイロスコープに含まれるバイアス変調器に動作可能に結合する少なくとも1つの変調器ローカル電源とを備える光ファイバジャイロスコープのための電源を対象とする。前記復調器ローカル電源は、前記復調器に電流を供給する第1の電流源と、前記復調器に関連付けられる負荷の両端に結合される第1のシャントレギュレータとを備える。前記変調器ローカル電源は、前記バイアス変調器に電流を供給する第2の電流源と、前記バイアス変調器に関連付けられる負荷の両端に結合される第2のシャントレギュレータとを備える。

【図面の簡単な説明】

【0006】

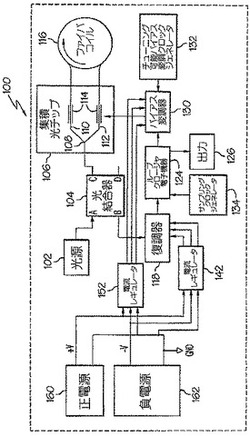

【図1】単一の光ファイバジャイロスコープ(FOG)軸の1つの例示的な実施形態を示す図である。

【図2】図1に示される電流レギュレータの一例を示すブロック図である。

【図3】図2に示される電流レギュレータの1つの例示的な実施態様のブロック図である。

【発明を実施するための形態】

【0007】

図1は、干渉FOG等の光ファイバジャイロスコープ(FOG)100の1つの例示的な実施形態を示す。FOG100は、一般に、光源102、光結合器104、光変調器106、光ファイバコイル116、復調器118、ループクロージャ電子機器モジュール124、バイアス変調器130、正電源160、及び負電源162を含む。加えて、1つ又は複数の電源レギュレータ142が復調器118に結合され、1つ又は複数の電源レギュレータ152がバイアス変調器130に結合される。これらのコンポーネントのそれぞれは、次の通りにさらに詳細に論述される。

【0008】

光源102は、光波を、FOG100を通って伝播させるための任意の適した光源とすることができる。例えば、光源102は、ポンプレーザを用いて実装することができる。光源102は、光ファイバ等の適した光路を用いることによって光結合器104と光通信する。

【0009】

光結合器104は、4つのポートA、B、C、及びDの間に延びる光伝送媒体を有する。ポートAは光源102に接続され、ポートBは復調器118に接続され、ポートCは光変調器106に接続される。一般に、光結合器104が、自身のポートのいずかにおいて光波を受信したとき、光結合器104は、送信された光のおよそ半分が入来ポートの反対端部における2つのポートのそれぞれに現れるように波を送信する。同時に、光波は、入来ポートと同じ端部にあるポートへは実質的に伝播されない。例えば、ポートAにおいて受信された光は、ポートC及びDへは送信されるが、ポートBへは実質的に伝播されない。同様に、ポートCにおいて受信された光は、ポートA及びBへは伝播されるが、ポートDへは伝播されない。

【0010】

動作中、光源102は、光結合器104のポートAへ光を送信する。光結合器104は、送信された光を分割し、ポートC及びDに光を提供する。ポートCへ送信された光は、光ファイバ又は他の適したメカニズムを介して光変調器106へさらに伝播される。

【0011】

光変調器106は、集積光チップとすることができ、Y接合部108及び一対の導波路110、112を含む。加えて、光変調器106は、導波路110、112と統合された複数の光位相変調器電極114を含む。光が光変調器106へ送信されたとき、光は、Y接合部108においてさらに分割され、導波路110、112に供給される。導波路110の光は、光ファイバコイル116へ送信され、光ファイバコイル116において、光は、光ファイバコイル116の長さに沿って時計回りに伝播し、導波路112に戻る。同様に、導波路112の光は、光ファイバコイル116へ送信され、光ファイバコイル116において、光は、光ファイバコイル116の長さに沿って時計回り及び反時計回りの双方に伝播し、光結合器106内の導波路110に戻る。

【0012】

光ファイバコイル116は、通常、検知される回転の軸を中心にしてコアのまわりに巻きつけられる。光ファイバコイル116は、光が対向する方向で伝播し、最終的には、復調器118における検出器に衝突する閉光路を提供する。検知軸を中心にした一方向の回転によって、一方の方向に対する光路長の有効な増加が引き起こされ、他方の方向において光路長の減少が引き起こされる。この光路長の差によって、サニャック効果として知られている結果である光波間の位相シフトが引き起こされる。

【0013】

光波は、光ファイバコイル116から伝播され、それらの各導波路を通過した後、Y接合部108において結合され、光結合部104へ伝播する。結合された光波は、復調器118へ出力される。復調器118における検出器は、光波の光信号を電気信号に変換する適切なフォトダイオード及び適した増幅器等の光検出器、又は他の適した検出器とすることができる。この検出器は、電気信号を出力し、この電気信号は、検出器に衝突する2つの光波の強度に比例する。

【0014】

復調器118から出力された電気信号は、ループクロージャ電子機器モジュール124に渡される。一般に、ループクロージャ電子機器モジュール124は、検出器から電流を受信し、インターフェロメータの2つの測定値の強度の差を0に保つのに必要とされるフィードバック位相シフトに光変調器106を駆動する。したがって、回転速度測定値は、フィードバック位相から計算することができ、出力126として配信することができる。

【0015】

2つの対向伝播する波が検出器に衝突したとき、検出器からの出力は、2つの波の間の位相差の余弦に従う。2つの波の間の位相差は、バイアス変調器130で変調される。バイアス変調器130は、光変調器106の入来波及び出行波に位相シフトを印加することによって位相バイアス変調を引き起こす。バイアス変調器130は、光変調器106における電極114間の変調電圧として用いられる方法電気信号を出力する。この電圧の印加によって、有効光路長は伸長又は短縮され、それによって、印加電圧に比例した光位相シフトが引き起こされる。図1に示す実施形態の一実施態様では、バイアス変調器130は、光信号の位相変調のために20キロヘルツの方形波を出力する。

【0016】

バイアス変調によって、検出器がインターフェロメータの最も高い点で強度をもはや測定するのではなく、2つのオフセット点で強度を測定するように、インターフェロメータにおける検出点がシフトされる。検出器において測定された回転速度は、したがって、2つのオフセット点における放出強度の差に比例する。対向伝播する波が、光変調器106に戻るときに出行波と逆の変調に遭遇するように、バイアス変調信号の周期は、コイルを通る光のループ通過時間の2分の1にチューニング可能である。このような変調方式は、実施されると、2つの波がY接合部108で結合されたときに干渉するように、入来波の位相を進め、出行波の位相を遅らせる。

【0017】

バイアス変調信号の周波数は、チューニング可能なバイアス変調クロックジェネレータ132によって制御される。

上述したように、復調器118における検出器は、光結合器104から波を受信し、2つの波の強度に比例した出力電流を提供する。復調器118の出力は、ループクロージャ電子機器124に渡される。ループクロージャ電子機器124は、復調器118の出力をサンプリングして、2つの波の強度を求める。復調器118の出力のサンプリングは、サンプリングクロックによって制御される。サンプリングクロックは、サンプリングクロックジェネレータ134によって作成される。サンプリングクロックは、バイアス変調クロックの半周期当たりのサンプル数が結果として所望の個数となる周波数を有するように選択される。

【0018】

バイアス変調回路部から復調回路部に結合し、電源から復調回路部に、かつバイアス変調回路部に結合するコモンモード雑音及び差動モード雑音を低減又は除去するために、FOG100において、「アクティブインダクタ」(ここでは、「電流源電源」とも呼ばれる)方式が実施される。ジャイロデータ及びジャイロ接地システムの双方に電源リップルが結合される可能性は小さいので、結果として、FOG100に与えられる電源電圧において、相対的に雑音が大きくなる可能性がある。

【0019】

1つ又は複数の「ローカル」電源142を用いて「主」電源160及び162を復調器118に結合し、1つ又は複数の「ローカル」電源152を用いて「主」電源160及び162をバイアス変調器130に結合することによって、アクティブインダクタ方式が実施される。ここで、ローカル電源142及び152は電流レギュレータ142及び152として実現されるように示される。電流レギュレータ142を用いて、正電源162によって出力される正電圧(+V)を復調器118に結合する。ここで、電流レギュレータ142は「復調器電流レギュレータ」142とも呼ばれる。同様に、電流レギュレータ152を用いて、正電源160によって出力される正電圧(+V)をバイアス変調器130に結合する。ここで、電流レギュレータ152は「バイアス変調器電流レギュレータ」152とも呼ばれる。また、電流レギュレータ142及び152は共通接地(GND)基準を復調器118及びバイアス変調器130にそれぞれ結合する。

【0020】

ここで、電流レギュレータ142及び152は、正電源160を復調器118及びバイアス変調器130から分離することに関連して説明されるが、電流レギュレータ142及び152は概ね同じようにして、負電源162を復調器118及びバイアス変調器130から分離するためにも用いることができることを理解されたい。

【0021】

正電源160によって出力される正電圧(+V)を復調器118に結合するために用いられる電流レギュレータ142は、正電圧(+V)に関連付けられる電流を供給する電流源202を含む。図2に示される電流レギュレータ142はシャントレギュレータ204も含み、シャントレギュレータ204は、その中を流れる電流が十分に高いときに、シャントレギュレータ自体及び負荷(すなわち、復調器118)にかかる定電圧を保持する。同様に、正電源160によって出力される正電圧(+V)をバイアス変調器130に結合するために用いられる電流レギュレータ152は、正電源160の正電圧(+V)に関連付けられる電流を供給する電流源206を含む。電流源152はシャントレギュレータ208も含み、シャントレギュレータ208は、その中を流れる電流が十分に高いときに、シャントレギュレータ自体及び負荷(すなわち、バイアス変調器130)にかかる定電圧を保持する。

【0022】

シャントレギュレータ204及び208はいずれも、負荷電流リップルによってそれぞれの電流源202及び206にかかる電圧を制限し、それぞれ復調器118及び変調器130のための低インピーダンスのローカル供給電圧を与える。また、電流源202及び206は、それぞれのシャントレギュレータ204及び208からそれぞれの主電源160への高インピーダンス結合を提供するので、それぞれのシャントレギュレータ204及び208にかかる小さなリップル電圧が、主電源160においてさらに小さな電流リップルになる。さらに、電流源202及び206は、主電源160上の電圧リップルによって引き起こされる電流リップルも減衰させるので、シャントレギュレータ204及び208のインピーダンスは、主電源160上の雑音を大きく減衰させることができる。

【0023】

電流レギュレータ142及び152のそれぞれは、同じ大きさ及び重量の通常の受動フィルタ回路を用いて与えることができる実効インダクタンスよりも大きな実効インダクタンスを、それぞれの負荷に対して与える。さらに、電流レギュレータ−シャントレギュレータ対142及び152のそれぞれは、それぞれのリターン電流のための接地への経路を与え、その経路は、他の電流レギュレータ−シャントレギュレータ対によって与えられるリターン−電流経路から離れている。すなわち、レギュレータ対152はバイアス変調器リターン電流(IMODULATOR)のための接地経路を与え、その接地経路は、復調器リターン電流(IDEMODULATOR)のためにレギュレータ対142によって与えられる接地経路から離れている。結果として、バイアス変調器130に関連付けられる「雑音のある」電流が、それほど復調器118に影響を及ぼさなくなるように、より実効的に減衰させて、分離することができる。

【0024】

図3は、図2に示される電流レギュレータ−シャントレギュレータ対142及び152の1つの例示的な実施態様のブロック図である。すなわち、図3は、正電源160によって出力される正電圧(+V)を復調器118及びバイアス変調器130にそれぞれ結合するために用いられる電流レギュレータ142及び152の1つの例示的な実施態様を示す。

【0025】

図3に示されるように、正電源160は、直流(DC)電圧源302及び抵抗器304を含む。

図3に示される例では、電流レギュレータ152の電流源206は一対のPNPバイポーラトランジスタ306及び308を用いて実装され、第1のトランジスタ306のベース及びコレクタ並びに第2のトランジスタ308のベースは、一対の抵抗器310及び312によって与えられる共通バイアス電圧に結合される。

【0026】

バイパスキャパシタ314が、正電圧(+V)レールと、2つのバイアス抵抗器310と312との間の接合部との間に結合され、+Vリップル除去率を高める。さらに雑音を低減するために、正電圧(+V)レールと共通バイアス電圧との間に別のバイパスキャパシタ316が結合される。正電圧(+V)レールと第1のトランジスタ306のエミッタとの間に電圧基準318(たとえば、逆方向バイアスをかけられたツェナーダイオードを用いて実装される)が結合される。

【0027】

正電圧(+V)レールと第2のトランジスタ308のエミッタとの間に抵抗器320が結合され、電流源のDC出力電流レベルを設定し、かつその電流源の出力インピーダンスを高める。ここで説明される技法は、バイアス変調器130によって生成される雑音電流が復調器118に達するのを防ぐために用いられる。図3に示される例では、そのような雑音電流は、第2のトランジスタ308のコレクタと接地(GND)との間に結合される交流(AC)電流源322として表される。

【0028】

電流レギュレータ152の電流源206は、電流源206の出力における電圧(V1)がDCにおいて共通バイアス電圧(V2)以上であり、かつ電流源206が広い周波数範囲(少なくとも、対象とする周波数範囲を含む)にわたってACにおいて高いインピーダンスを有するように構成される。また、上述したように、電流レギュレータ142は、同じ大きさ及び重量の典型的な受動フィルタ回路を用いて与えることができる実効インダクタンスよりも大きな実効インダクタンスを負荷に対して与える。

【0029】

図3に示される例では、シャントレギュレータ208は、逆方向バイアスをかけられた一対のツェナーダイオード324及び326を用いて実装される。また、図3に示される例では、バイアス変調器130を電流レギュレータ152から分離するために、電流レギュレータ152の出力と接地(GND)との間にバイパスキャパシタ328が結合される。

【0030】

図3に示される例では、電流レギュレータ142の電流源202は、電流レギュレータ152の電流源206と同じようにして実装される。電流源202は一対のPNPバイポーラトランジスタ336及び338を用いて実装され、トランジスタ336のベース及びコレクタ並びにトランジスタ338のベースは、一対のバイアス抵抗器340及び342によって与えられる共通バイアス電圧(V3)に結合される。

【0031】

キャパシタ344が、正電圧(+V)レールと、2つのバイアス抵抗器340及び342間の接合部との間に結合され、+Vリップル除去率を高める。さらに雑音を低減するために、正電圧(+V)レールと共通バイアス電圧(V3)との間に別のキャパシタ346が結合される。正電圧(+V)レールと第1のトランジスタ336のエミッタとの間に電圧基準348(たとえば、逆方向バイアスをかけられたツェナーダイオードを用いて実装される)が結合される。

【0032】

正電圧(+V)レールとトランジスタ338のエミッタとの間に抵抗器350が結合される。抵抗器350及び電圧基準348は、電流源202の出力レベルを設定する。

電流レギュレータ142の電流源202は、電流源202の出力における電圧(V4)がDCにおいて共通バイアス電圧(V3)以下であり、電流源202が広い周波数範囲(少なくとも、対象とする周波数範囲を含む)にわたってACにおいて高いインピーダンスを有するように構成される。また、上述したように、電流レギュレータ142は、同じ大きさ及び重量の通常の受動フィルタ回路を用いて与えることができる実効インダクタンスよりも大きな実効インダクタンスを負荷に対して与える。

【0033】

図3に示される例では、シャントレギュレータ204は、逆方向バイアスをかけられた一対のツェナーダイオード354及び356を用いて実装される。また、図3に示される例では、復調器118を電流レギュレータ142から分離するために、電流レギュレータ142の出力と接地(GND)との間にキャパシタ358が結合される。

【0034】

本発明は、その本質的な特徴から逸脱することなく、他の具体的な形態で実施することができる。説明した実施形態は、すべての点において、単に例示とみなされるべきであり、制限的とみなされるべきではない。したがって、本発明の範囲は、上記説明ではなく、添付の特許請求の範囲によって示される。特許請求の範囲の意味及び特許請求の範囲の均等なものの範囲内に入るすべての変更は、特許請求の範囲の範囲内に包含されるべきである。

【技術分野】

【0001】

本発明は、光ファイバジャイロスコープにおいて限られた電源品質でジャイロスコープ誤差を低減するシステムに関する。

[連邦政府による資金提供を受けた研究開発に関する記載]

本発明は、空軍研究所によって与えられた契約番号第FA9453−08−C−0263号に基づく政府支援でなされたものである。政府は、本発明に一定の権利を有する。

【背景技術】

【0002】

干渉光ファイバジャイロスコープ(IFOG)は、光ファイバコイル内を対向伝播する電磁波を利用してコイルのまわりの回転を検知するものであるが、電子雑音の影響を受けやすい可能性がある。このような光ファイバジャイロスコープは、バイアス変調を用いて、インターフェログラムの速度検知部に対してジャイロスコープをバイアスする。バイアス変調周波数は、復調回路部内へ結合して、バイアスオフセット及び不感帯の増加を引き起こす可能性がある。例えば、復調アナログ/デジタル変換器に存在するどのコヒーレント(同相)雑音もエラー源であり、バイアス安定性、バイアスオフセット、及びジャイロスコープ不感帯のサイズに影響を与える。

【発明の概要】

【発明が解決しようとする課題】

【0003】

従来のIFOG電子機器は、電源雑音及び内部雑音を十分にフィルタリング除去するが、このようなIFOG電子機器は、電源の基準として雑音の少ない低インピーダンスのシャーシ接地接続を有する接地方式を必要とする。この手法は、ジャイロスコープが、電力伝送及びデータ伝送用にスリップリングを用いて回転されるジンバル化球(gimbaled sphere)で機能するが、次世代慣性基準システムは、スリップリングを用いず、その代わり、データ伝送及び電力伝送の双方に無線技術を用いる。この無線手法は、シャーシ(アース)接地接続を除去し、電子機器が、フローティング電源基準に起因した雑音の影響を受けやすくなる可能性がある。

【0004】

バイアス変調回路部用及び対応する復調回路部用に別々の電源を用いて、IFOG軸ことに別々の電源を用いることが可能であるが、これは、サイズ及び電力消耗が増加することから大部分実用的ではない。外部電源及び複数の分離された電源からの内部回路部の双方のサイズは法外なものになる。その上、複数の電源からの余分な電力消耗も、通常は小さなシステム電力バジェットに負担となる。加えて、慣性基準システムが非常に低いリップル電圧でジャイロスコープに電力を提供することを必要とすることは、常に実用的であるとは限らない。

【課題を解決するための手段】

【0005】

1つの実施の形態は、少なくとも1つの主電源と、前記主電源を前記光ファイバジャイロスコープに含まれる復調器に動作可能に結合する少なくとも1つの復調器ローカル電源と、前記主電源を前記光ファイバジャイロスコープに含まれるバイアス変調器に動作可能に結合する少なくとも1つの変調器ローカル電源とを備える光ファイバジャイロスコープのための電源を対象とする。前記復調器ローカル電源は、前記復調器に電流を供給する第1の電流源と、前記復調器に関連付けられる負荷の両端に結合される第1のシャントレギュレータとを備える。前記変調器ローカル電源は、前記バイアス変調器に電流を供給する第2の電流源と、前記バイアス変調器に関連付けられる負荷の両端に結合される第2のシャントレギュレータとを備える。

【図面の簡単な説明】

【0006】

【図1】単一の光ファイバジャイロスコープ(FOG)軸の1つの例示的な実施形態を示す図である。

【図2】図1に示される電流レギュレータの一例を示すブロック図である。

【図3】図2に示される電流レギュレータの1つの例示的な実施態様のブロック図である。

【発明を実施するための形態】

【0007】

図1は、干渉FOG等の光ファイバジャイロスコープ(FOG)100の1つの例示的な実施形態を示す。FOG100は、一般に、光源102、光結合器104、光変調器106、光ファイバコイル116、復調器118、ループクロージャ電子機器モジュール124、バイアス変調器130、正電源160、及び負電源162を含む。加えて、1つ又は複数の電源レギュレータ142が復調器118に結合され、1つ又は複数の電源レギュレータ152がバイアス変調器130に結合される。これらのコンポーネントのそれぞれは、次の通りにさらに詳細に論述される。

【0008】

光源102は、光波を、FOG100を通って伝播させるための任意の適した光源とすることができる。例えば、光源102は、ポンプレーザを用いて実装することができる。光源102は、光ファイバ等の適した光路を用いることによって光結合器104と光通信する。

【0009】

光結合器104は、4つのポートA、B、C、及びDの間に延びる光伝送媒体を有する。ポートAは光源102に接続され、ポートBは復調器118に接続され、ポートCは光変調器106に接続される。一般に、光結合器104が、自身のポートのいずかにおいて光波を受信したとき、光結合器104は、送信された光のおよそ半分が入来ポートの反対端部における2つのポートのそれぞれに現れるように波を送信する。同時に、光波は、入来ポートと同じ端部にあるポートへは実質的に伝播されない。例えば、ポートAにおいて受信された光は、ポートC及びDへは送信されるが、ポートBへは実質的に伝播されない。同様に、ポートCにおいて受信された光は、ポートA及びBへは伝播されるが、ポートDへは伝播されない。

【0010】

動作中、光源102は、光結合器104のポートAへ光を送信する。光結合器104は、送信された光を分割し、ポートC及びDに光を提供する。ポートCへ送信された光は、光ファイバ又は他の適したメカニズムを介して光変調器106へさらに伝播される。

【0011】

光変調器106は、集積光チップとすることができ、Y接合部108及び一対の導波路110、112を含む。加えて、光変調器106は、導波路110、112と統合された複数の光位相変調器電極114を含む。光が光変調器106へ送信されたとき、光は、Y接合部108においてさらに分割され、導波路110、112に供給される。導波路110の光は、光ファイバコイル116へ送信され、光ファイバコイル116において、光は、光ファイバコイル116の長さに沿って時計回りに伝播し、導波路112に戻る。同様に、導波路112の光は、光ファイバコイル116へ送信され、光ファイバコイル116において、光は、光ファイバコイル116の長さに沿って時計回り及び反時計回りの双方に伝播し、光結合器106内の導波路110に戻る。

【0012】

光ファイバコイル116は、通常、検知される回転の軸を中心にしてコアのまわりに巻きつけられる。光ファイバコイル116は、光が対向する方向で伝播し、最終的には、復調器118における検出器に衝突する閉光路を提供する。検知軸を中心にした一方向の回転によって、一方の方向に対する光路長の有効な増加が引き起こされ、他方の方向において光路長の減少が引き起こされる。この光路長の差によって、サニャック効果として知られている結果である光波間の位相シフトが引き起こされる。

【0013】

光波は、光ファイバコイル116から伝播され、それらの各導波路を通過した後、Y接合部108において結合され、光結合部104へ伝播する。結合された光波は、復調器118へ出力される。復調器118における検出器は、光波の光信号を電気信号に変換する適切なフォトダイオード及び適した増幅器等の光検出器、又は他の適した検出器とすることができる。この検出器は、電気信号を出力し、この電気信号は、検出器に衝突する2つの光波の強度に比例する。

【0014】

復調器118から出力された電気信号は、ループクロージャ電子機器モジュール124に渡される。一般に、ループクロージャ電子機器モジュール124は、検出器から電流を受信し、インターフェロメータの2つの測定値の強度の差を0に保つのに必要とされるフィードバック位相シフトに光変調器106を駆動する。したがって、回転速度測定値は、フィードバック位相から計算することができ、出力126として配信することができる。

【0015】

2つの対向伝播する波が検出器に衝突したとき、検出器からの出力は、2つの波の間の位相差の余弦に従う。2つの波の間の位相差は、バイアス変調器130で変調される。バイアス変調器130は、光変調器106の入来波及び出行波に位相シフトを印加することによって位相バイアス変調を引き起こす。バイアス変調器130は、光変調器106における電極114間の変調電圧として用いられる方法電気信号を出力する。この電圧の印加によって、有効光路長は伸長又は短縮され、それによって、印加電圧に比例した光位相シフトが引き起こされる。図1に示す実施形態の一実施態様では、バイアス変調器130は、光信号の位相変調のために20キロヘルツの方形波を出力する。

【0016】

バイアス変調によって、検出器がインターフェロメータの最も高い点で強度をもはや測定するのではなく、2つのオフセット点で強度を測定するように、インターフェロメータにおける検出点がシフトされる。検出器において測定された回転速度は、したがって、2つのオフセット点における放出強度の差に比例する。対向伝播する波が、光変調器106に戻るときに出行波と逆の変調に遭遇するように、バイアス変調信号の周期は、コイルを通る光のループ通過時間の2分の1にチューニング可能である。このような変調方式は、実施されると、2つの波がY接合部108で結合されたときに干渉するように、入来波の位相を進め、出行波の位相を遅らせる。

【0017】

バイアス変調信号の周波数は、チューニング可能なバイアス変調クロックジェネレータ132によって制御される。

上述したように、復調器118における検出器は、光結合器104から波を受信し、2つの波の強度に比例した出力電流を提供する。復調器118の出力は、ループクロージャ電子機器124に渡される。ループクロージャ電子機器124は、復調器118の出力をサンプリングして、2つの波の強度を求める。復調器118の出力のサンプリングは、サンプリングクロックによって制御される。サンプリングクロックは、サンプリングクロックジェネレータ134によって作成される。サンプリングクロックは、バイアス変調クロックの半周期当たりのサンプル数が結果として所望の個数となる周波数を有するように選択される。

【0018】

バイアス変調回路部から復調回路部に結合し、電源から復調回路部に、かつバイアス変調回路部に結合するコモンモード雑音及び差動モード雑音を低減又は除去するために、FOG100において、「アクティブインダクタ」(ここでは、「電流源電源」とも呼ばれる)方式が実施される。ジャイロデータ及びジャイロ接地システムの双方に電源リップルが結合される可能性は小さいので、結果として、FOG100に与えられる電源電圧において、相対的に雑音が大きくなる可能性がある。

【0019】

1つ又は複数の「ローカル」電源142を用いて「主」電源160及び162を復調器118に結合し、1つ又は複数の「ローカル」電源152を用いて「主」電源160及び162をバイアス変調器130に結合することによって、アクティブインダクタ方式が実施される。ここで、ローカル電源142及び152は電流レギュレータ142及び152として実現されるように示される。電流レギュレータ142を用いて、正電源162によって出力される正電圧(+V)を復調器118に結合する。ここで、電流レギュレータ142は「復調器電流レギュレータ」142とも呼ばれる。同様に、電流レギュレータ152を用いて、正電源160によって出力される正電圧(+V)をバイアス変調器130に結合する。ここで、電流レギュレータ152は「バイアス変調器電流レギュレータ」152とも呼ばれる。また、電流レギュレータ142及び152は共通接地(GND)基準を復調器118及びバイアス変調器130にそれぞれ結合する。

【0020】

ここで、電流レギュレータ142及び152は、正電源160を復調器118及びバイアス変調器130から分離することに関連して説明されるが、電流レギュレータ142及び152は概ね同じようにして、負電源162を復調器118及びバイアス変調器130から分離するためにも用いることができることを理解されたい。

【0021】

正電源160によって出力される正電圧(+V)を復調器118に結合するために用いられる電流レギュレータ142は、正電圧(+V)に関連付けられる電流を供給する電流源202を含む。図2に示される電流レギュレータ142はシャントレギュレータ204も含み、シャントレギュレータ204は、その中を流れる電流が十分に高いときに、シャントレギュレータ自体及び負荷(すなわち、復調器118)にかかる定電圧を保持する。同様に、正電源160によって出力される正電圧(+V)をバイアス変調器130に結合するために用いられる電流レギュレータ152は、正電源160の正電圧(+V)に関連付けられる電流を供給する電流源206を含む。電流源152はシャントレギュレータ208も含み、シャントレギュレータ208は、その中を流れる電流が十分に高いときに、シャントレギュレータ自体及び負荷(すなわち、バイアス変調器130)にかかる定電圧を保持する。

【0022】

シャントレギュレータ204及び208はいずれも、負荷電流リップルによってそれぞれの電流源202及び206にかかる電圧を制限し、それぞれ復調器118及び変調器130のための低インピーダンスのローカル供給電圧を与える。また、電流源202及び206は、それぞれのシャントレギュレータ204及び208からそれぞれの主電源160への高インピーダンス結合を提供するので、それぞれのシャントレギュレータ204及び208にかかる小さなリップル電圧が、主電源160においてさらに小さな電流リップルになる。さらに、電流源202及び206は、主電源160上の電圧リップルによって引き起こされる電流リップルも減衰させるので、シャントレギュレータ204及び208のインピーダンスは、主電源160上の雑音を大きく減衰させることができる。

【0023】

電流レギュレータ142及び152のそれぞれは、同じ大きさ及び重量の通常の受動フィルタ回路を用いて与えることができる実効インダクタンスよりも大きな実効インダクタンスを、それぞれの負荷に対して与える。さらに、電流レギュレータ−シャントレギュレータ対142及び152のそれぞれは、それぞれのリターン電流のための接地への経路を与え、その経路は、他の電流レギュレータ−シャントレギュレータ対によって与えられるリターン−電流経路から離れている。すなわち、レギュレータ対152はバイアス変調器リターン電流(IMODULATOR)のための接地経路を与え、その接地経路は、復調器リターン電流(IDEMODULATOR)のためにレギュレータ対142によって与えられる接地経路から離れている。結果として、バイアス変調器130に関連付けられる「雑音のある」電流が、それほど復調器118に影響を及ぼさなくなるように、より実効的に減衰させて、分離することができる。

【0024】

図3は、図2に示される電流レギュレータ−シャントレギュレータ対142及び152の1つの例示的な実施態様のブロック図である。すなわち、図3は、正電源160によって出力される正電圧(+V)を復調器118及びバイアス変調器130にそれぞれ結合するために用いられる電流レギュレータ142及び152の1つの例示的な実施態様を示す。

【0025】

図3に示されるように、正電源160は、直流(DC)電圧源302及び抵抗器304を含む。

図3に示される例では、電流レギュレータ152の電流源206は一対のPNPバイポーラトランジスタ306及び308を用いて実装され、第1のトランジスタ306のベース及びコレクタ並びに第2のトランジスタ308のベースは、一対の抵抗器310及び312によって与えられる共通バイアス電圧に結合される。

【0026】

バイパスキャパシタ314が、正電圧(+V)レールと、2つのバイアス抵抗器310と312との間の接合部との間に結合され、+Vリップル除去率を高める。さらに雑音を低減するために、正電圧(+V)レールと共通バイアス電圧との間に別のバイパスキャパシタ316が結合される。正電圧(+V)レールと第1のトランジスタ306のエミッタとの間に電圧基準318(たとえば、逆方向バイアスをかけられたツェナーダイオードを用いて実装される)が結合される。

【0027】

正電圧(+V)レールと第2のトランジスタ308のエミッタとの間に抵抗器320が結合され、電流源のDC出力電流レベルを設定し、かつその電流源の出力インピーダンスを高める。ここで説明される技法は、バイアス変調器130によって生成される雑音電流が復調器118に達するのを防ぐために用いられる。図3に示される例では、そのような雑音電流は、第2のトランジスタ308のコレクタと接地(GND)との間に結合される交流(AC)電流源322として表される。

【0028】

電流レギュレータ152の電流源206は、電流源206の出力における電圧(V1)がDCにおいて共通バイアス電圧(V2)以上であり、かつ電流源206が広い周波数範囲(少なくとも、対象とする周波数範囲を含む)にわたってACにおいて高いインピーダンスを有するように構成される。また、上述したように、電流レギュレータ142は、同じ大きさ及び重量の典型的な受動フィルタ回路を用いて与えることができる実効インダクタンスよりも大きな実効インダクタンスを負荷に対して与える。

【0029】

図3に示される例では、シャントレギュレータ208は、逆方向バイアスをかけられた一対のツェナーダイオード324及び326を用いて実装される。また、図3に示される例では、バイアス変調器130を電流レギュレータ152から分離するために、電流レギュレータ152の出力と接地(GND)との間にバイパスキャパシタ328が結合される。

【0030】

図3に示される例では、電流レギュレータ142の電流源202は、電流レギュレータ152の電流源206と同じようにして実装される。電流源202は一対のPNPバイポーラトランジスタ336及び338を用いて実装され、トランジスタ336のベース及びコレクタ並びにトランジスタ338のベースは、一対のバイアス抵抗器340及び342によって与えられる共通バイアス電圧(V3)に結合される。

【0031】

キャパシタ344が、正電圧(+V)レールと、2つのバイアス抵抗器340及び342間の接合部との間に結合され、+Vリップル除去率を高める。さらに雑音を低減するために、正電圧(+V)レールと共通バイアス電圧(V3)との間に別のキャパシタ346が結合される。正電圧(+V)レールと第1のトランジスタ336のエミッタとの間に電圧基準348(たとえば、逆方向バイアスをかけられたツェナーダイオードを用いて実装される)が結合される。

【0032】

正電圧(+V)レールとトランジスタ338のエミッタとの間に抵抗器350が結合される。抵抗器350及び電圧基準348は、電流源202の出力レベルを設定する。

電流レギュレータ142の電流源202は、電流源202の出力における電圧(V4)がDCにおいて共通バイアス電圧(V3)以下であり、電流源202が広い周波数範囲(少なくとも、対象とする周波数範囲を含む)にわたってACにおいて高いインピーダンスを有するように構成される。また、上述したように、電流レギュレータ142は、同じ大きさ及び重量の通常の受動フィルタ回路を用いて与えることができる実効インダクタンスよりも大きな実効インダクタンスを負荷に対して与える。

【0033】

図3に示される例では、シャントレギュレータ204は、逆方向バイアスをかけられた一対のツェナーダイオード354及び356を用いて実装される。また、図3に示される例では、復調器118を電流レギュレータ142から分離するために、電流レギュレータ142の出力と接地(GND)との間にキャパシタ358が結合される。

【0034】

本発明は、その本質的な特徴から逸脱することなく、他の具体的な形態で実施することができる。説明した実施形態は、すべての点において、単に例示とみなされるべきであり、制限的とみなされるべきではない。したがって、本発明の範囲は、上記説明ではなく、添付の特許請求の範囲によって示される。特許請求の範囲の意味及び特許請求の範囲の均等なものの範囲内に入るすべての変更は、特許請求の範囲の範囲内に包含されるべきである。

【特許請求の範囲】

【請求項1】

少なくとも1つの主電源と、

前記主電源を前記光ファイバジャイロスコープに含まれる復調器に動作可能に結合する少なくとも1つの復調器ローカル電源と、

前記主電源を前記光ファイバジャイロスコープに含まれるバイアス変調器に動作可能に結合する少なくとも1つの変調器ローカル電源と、

を備える光ファイバジャイロスコープのための電源であって、

前記復調器ローカル電源は、前記復調器に電流を供給する第1の電流源と、前記復調器に関連付けられる負荷の両端に結合される第1のシャントレギュレータとを備え、

前記変調器ローカル電源は、前記バイアス変調器に電流を供給する第2の電流源と、前記バイアス変調器に関連付けられる負荷の両端に結合される第2のシャントレギュレータとを備える、光ファイバジャイロスコープのための電源。

【請求項2】

前記少なくとも1つの主電源は、正電圧を出力する主正電源と、負電圧を出力する主負電源とを備え、

オプションで、前記復調器ローカル電源は、前記主正電源を前記復調器に結合する第1の電流レギュレータ−シャントレギュレータ対と、前記主負電源を前記復調器に結合する第2の電流レギュレータ−シャントレギュレータ対とを備え、

オプションで、前記変調器ローカル電源は、前記主正電源を前記バイアス変調器に結合する第3の電流レギュレータ−シャントレギュレータ対と、前記主負電源を前記バイアス変調器に結合する第4の電流レギュレータ−シャントレギュレータ対とを備える、請求項1に記載の電源。

【請求項3】

請求項1に記載の電源を備え、

光源と光通信し、該光源から光信号を受信するように構成される光結合器と、

前記光結合器と光通信する光変調器と、

前記光変調器と光通信する光ファイバコイルと、

前記光結合器から光信号を受信し、該光信号を電気信号に変換するように構成される復調器と、

前記光変調器に変調信号を出力するように構成されるバイアス変調器と、

をさらに備える、光ファイバジャイロスコープ。

【請求項1】

少なくとも1つの主電源と、

前記主電源を前記光ファイバジャイロスコープに含まれる復調器に動作可能に結合する少なくとも1つの復調器ローカル電源と、

前記主電源を前記光ファイバジャイロスコープに含まれるバイアス変調器に動作可能に結合する少なくとも1つの変調器ローカル電源と、

を備える光ファイバジャイロスコープのための電源であって、

前記復調器ローカル電源は、前記復調器に電流を供給する第1の電流源と、前記復調器に関連付けられる負荷の両端に結合される第1のシャントレギュレータとを備え、

前記変調器ローカル電源は、前記バイアス変調器に電流を供給する第2の電流源と、前記バイアス変調器に関連付けられる負荷の両端に結合される第2のシャントレギュレータとを備える、光ファイバジャイロスコープのための電源。

【請求項2】

前記少なくとも1つの主電源は、正電圧を出力する主正電源と、負電圧を出力する主負電源とを備え、

オプションで、前記復調器ローカル電源は、前記主正電源を前記復調器に結合する第1の電流レギュレータ−シャントレギュレータ対と、前記主負電源を前記復調器に結合する第2の電流レギュレータ−シャントレギュレータ対とを備え、

オプションで、前記変調器ローカル電源は、前記主正電源を前記バイアス変調器に結合する第3の電流レギュレータ−シャントレギュレータ対と、前記主負電源を前記バイアス変調器に結合する第4の電流レギュレータ−シャントレギュレータ対とを備える、請求項1に記載の電源。

【請求項3】

請求項1に記載の電源を備え、

光源と光通信し、該光源から光信号を受信するように構成される光結合器と、

前記光結合器と光通信する光変調器と、

前記光変調器と光通信する光ファイバコイルと、

前記光結合器から光信号を受信し、該光信号を電気信号に変換するように構成される復調器と、

前記光変調器に変調信号を出力するように構成されるバイアス変調器と、

をさらに備える、光ファイバジャイロスコープ。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−2800(P2012−2800A)

【公開日】平成24年1月5日(2012.1.5)

【国際特許分類】

【外国語出願】

【出願番号】特願2011−69983(P2011−69983)

【出願日】平成23年3月28日(2011.3.28)

【出願人】(500575824)ハネウェル・インターナショナル・インコーポレーテッド (1,504)

【Fターム(参考)】

【公開日】平成24年1月5日(2012.1.5)

【国際特許分類】

【出願番号】特願2011−69983(P2011−69983)

【出願日】平成23年3月28日(2011.3.28)

【出願人】(500575824)ハネウェル・インターナショナル・インコーポレーテッド (1,504)

【Fターム(参考)】

[ Back to top ]