光学的ディエンファシス信号を生成するための光変調器とその方法

【課題】光学的ディエンファシス駆動方式を使うことができる光変調器とその信号生成方法とを提供する。

【解決手段】光変調器50は、第1位相変調器52によって位相変調された第1光信号を伝送するための第1光導波路58−1と、第1位相変調器の長さより短い長さを有する第2位相変調器54によって位相変調された第2光信号を伝送するための第2光導波路58−2と、を含み、第2光導波路の長さは、第1光導波路の長さより長い。

【解決手段】光変調器50は、第1位相変調器52によって位相変調された第1光信号を伝送するための第1光導波路58−1と、第1位相変調器の長さより短い長さを有する第2位相変調器54によって位相変調された第2光信号を伝送するための第2光導波路58−2と、を含み、第2光導波路の長さは、第1光導波路の長さより長い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光変調器に係り、特に、光学的ディエンファシス信号を生成することができる光変調器及びその方法に関する。

【背景技術】

【0002】

光変調器(optical modulator)は、光のビーム(beam)を変調するために使われる装置である。ビームは、自由空間、光繊維、または光導波路を通じて伝送される。操作される光のビームのパラメータ(parameter)によって、変調器は、振幅変調器、位相変調器、または極性変調器などに分類される。

【発明の概要】

【発明が解決しようとする課題】

【0003】

本発明が解決しようとする技術的な課題は、光学的ディエンファシス駆動方式を使うことができる光変調器と該光変調器の信号生成方法とを提供するところにある。

【課題を解決するための手段】

【0004】

本発明の実施形態による光変調器は、第1位相変調器によって位相変調された第1光信号を伝送するための第1光導波路と、第1位相変調器の長さより短い長さを有する第2位相変調器によって位相変調された第2光信号を伝送するための第2光導波路と、を含む。

第2光導波路の長さは、第1光導波路の長さより長い。

【0005】

第2光導波路の長さは、位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させるための長さだけ第1光導波路の長さより長い。

実施形態によって、第1位相変調器と第2位相変調器のそれぞれは、同じ入力データストリームによって、位相変調された第1光信号と位相変調された第2光信号のそれぞれを生成する。

【0006】

他の実施形態によって、第1位相変調器は、第1入力データストリームによって、位相変調された第1光信号を生成し、第2位相変調器は、第2入力データストリームによって、位相変調された第2光信号を生成する。

第2入力データストリームは、第1入力データストリームよりN(ここで、Nは、実数)ビットだけ遅延される。

【0007】

光変調器は、第1入力データストリームをN(ここで、Nは、実数)ビットだけ遅延させ、第2データストリームを生成するためのビット遅延ユニットをさらに含む。

光変調器は、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成するための光結合器をさらに含む。

【0008】

光変調器は、位相変調された第2光信号をN(ここで、Nは、実数)ビットだけ遅延させるためのビット遅延ユニットをさらに含む。

光変調器は、持続波形を有する光信号を出力するための光源と、光信号を同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器と第2位相変調器のそれぞれに出力するための光分離器と、をさらに含む。

【0009】

本発明の他の実施形態による光変調器は、第1データストリームによって位相変調された第1光信号を生成するための第1位相変調器と、第1データストリームの位相と振幅とを調節するための調節器と、調節器から出力された第2データストリームによって位相変調された第2光信号を生成するための第2位相変調器と、を含む。

【0010】

調節器は、第1データストリームをN(ここで、Nは、実数)ビット遅延させ、第2データストリームを生成する。

光変調器は、持続波形を有する光信号を出力するための光源と、光信号を同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器と第2位相変調器のそれぞれに出力するための光分離器と、をさらに含む。

光変調器は、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成するための光結合器をさらに含む。

【0011】

本発明のまた他の実施形態による光変調器は、第1データストリームによって位相変調された第1光信号を生成するための第1位相変調器と、第1データストリームの振幅を減衰させるための減衰器と、減衰器から出力された第2データストリームによって位相変調された第2光信号を生成するための第2位相変調器と、第2位相変調器から出力され、位相変調された第2光信号を遅延させるための遅延ユニットと、を含む。

【0012】

光変調器は、位相変調された第1光信号を伝送するための第1光導波路と、位相変調された第2光信号を伝送するための第2光導波路と、をさらに含み、遅延ユニットは、第2光導波路の一部として具現される。

遅延ユニットが形成された第2光導波路の長さは、第1光導波路の長さより長い。

遅延ユニットは、位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させる。

【0013】

光変調器は、持続波形を有する光信号を出力するための光源と、光信号を同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器と第2位相変調器のそれぞれに出力するための光分離器と、をさらに含む。

光変調器は、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成するための光結合器をさらに含む。

【0014】

第1データストリームは、第1入力信号と第2入力信号との差によって生成される。

本発明の実施形態による光変調器の光変調信号生成方法は、第1位相変調器によって位相変調された第1光信号を、第1光導波路を通じて伝送する段階と、第1位相変調器の長さより短い長さを有する第2位相変調器によって位相変調された第2光信号を、第2光導波路を通じて伝送する段階と、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、を含む。

【0015】

第2光導波路の長さは、第1光導波路の長さより長い。

本発明の他の実施形態による光変調器の光変調信号生成方法は、第1位相変調器を用いて第1データストリームによって位相変調された第1光信号を生成する段階と、第1データストリームの位相と振幅とを調節して第2データストリームを生成する段階と、第2位相変調器を用いて第2データストリームによって位相変調された第2光信号を生成する段階と、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、を含む。

【0016】

第2データストリームを生成する段階は、第1データストリームをN(ここで、Nは、実数)ビット遅延させ、第2データストリームを生成する。

【0017】

本発明のまた他の実施形態による光変調器の光変調信号生成方法は、第1位相変調器を用いてデータストリームによって位相変調された第1光信号を生成する段階と、データストリームの振幅を減衰させる段階と、第2位相変調器を用いて振幅減衰されたデータストリームによって位相変調された第2光信号を生成する段階と、位相変調された第2光信号を遅延させる段階と、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、を含む。

【0018】

位相変調された第2光信号を遅延させる段階は、位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させる。

【発明の効果】

【0019】

本発明の実施形態による光変調器は、光学的ディエンファシス波形を有する出力光信号を生成することができるので、変調速度を改善することができる。

【図面の簡単な説明】

【0020】

本発明の詳細な説明で引用される図面をより十分に理解するために、各図面の詳細な説明が提供される。

【図1】本発明の一実施形態による光変調器の概略的な回路図を示す。

【図2】本発明の他の実施形態による光変調器の概略的な回路図を示す。

【図3】本発明のまた他の実施形態による光変調器の概略的な回路図を示す。

【図4】本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。

【図5】本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。

【図6】図1から図5に示された光変調器のうちの何れか一つを含む本発明の一実施形態によるデータ処理システムのブロック図を示す。

【図7】図1から図5に示された光変調器のうちの何れか一つを含む本発明の他の実施形態によるデータ処理システムのブロック図を示す。

【図8】図1から図5に示された光変調器のうちの何れか一つを含む本発明のまた他の実施形態によるデータ処理システムのブロック図を示す。

【図9】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図10】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図11】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図12】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図13】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図14】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図15】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【発明を実施するための形態】

【0021】

以下、添付した図面を参照して、本発明を詳しく説明する。

【0022】

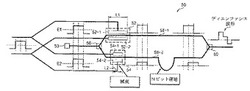

図1は、本発明の一実施形態による光変調器の概略的な回路図を示す。図1を参照すると、マッハツェンダ干渉計(Mach−Zehnder interferometer)またはマッハツェンダ変調器(Mach−Zehnder modulator)として具現可能な光変調器50は、第1位相変調器52、第2位相変調器54、光分離器56、及び光結合器60を含む。

【0023】

位相シフタ(phase shifter)の機能を行える第1位相変調器52は、入力データストリーム(data stream)によって第1光信号の位相を変調し、該位相変調された第1光信号を第1光導波路58−1に伝送する。位相シフタの機能を行える第2位相変調器54は、入力データストリームによって第2光信号の位相を変調し、該位相変調された第2光信号を第2光導波路58−2に伝送する。

【0024】

入力データストリームは、各位相変調器52、54の第1電極52−1、54−1に供給される第1電気信号E1と各位相変調器52、54の第2電極52−2、54−2に供給される第2電気信号E2との差によって発生したデータストリームを意味する。第1電気信号E1は、同じ振幅を有する2つの信号に分離され、第2電気信号E2は、同じ振幅を有する2つの信号に分離される。

【0025】

光分離器56は、光源53から出力された持続波形(continuous waveform)を有する光信号を受信し、これを同様に2つにパワー分離(power−splitting)し、該パワー分離された光信号のそれぞれを第1位相変調器52内に形成された光導波路(optical waveguide)と第2位相変調器54内に形成された光導波路のそれぞれに伝送する。

【0026】

第2光信号の位相を変調することができる第2位相変調器54の長さL2は、第1光信号の位相を変調することができる第1位相変調器52の長さL1より短く形成される。位相変調器の長さが短ければ短いほど同じ光信号に対して位相変調(または、位相シフト)の量も少なくなる。したがって、光信号に対する減衰が発生する。

【0027】

第1位相変調器52によって位相変調された第1光信号は、第1光導波路58−1を通じて光結合器60に伝送され、第2位相変調器54によって位相変調された第2光信号は、第2光導波路58−2を通じて光結合器60に伝送される。

【0028】

図1に示したように、第1光導波路58−1の長さ(より具体的に、第1位相変調器52内に形成された光導波路を除いた長さ)は、第2光導波路58−2の長さ(より具体的に、第2位相変調器54内に形成された光導波路を除いた長さ)より短い。例えば、第1位相変調器52の相対的な長さが2であり、第1光導波路58−1の相対的な長さが8である時、第2位相変調器54の相対的な長さが1であり、第2光導波路58−2の相対的な長さは9である。

【0029】

第2光導波路58−2の長さを調節することによって、第2光導波路58−2を通じて伝送される位相変調された第2光信号は、第1光導波路58−1を通じて伝送される位相変調された第1光信号より一定時間またはNビット遅延されうる。この際、Nは、実数である。他の実施形態によって、第1光導波路58−1の長さと第2光導波路58−2の長さとが互いに同様に具現される時、光変調器50は、第2光導波路58−2を通じて伝送される位相変調された第2光信号をNビット(bit)遅延させるためのビット遅延ユニット(unit)を含みうる。

【0030】

光結合器60は、第1光導波路58−1を通じて伝送された位相変調された第1光信号と、第2光導波路58−2を通じて伝送されながらNビット遅延された位相変調された第2光信号とを結合して、ディエンファシス(de−emphasis)波形を有する出力光信号を生成する。前述したように、光変調器50は、別途の電気的ディエンファシス駆動回路なしでも、第2位相変調器54と第2光導波路58−2とを用いて、ディエンファシス波形を有する出力光信号を生成することができる効果がある。

【0031】

図2は、本発明の他の実施形態による光変調器の概略的な回路図を示す。図2を参照すると、マッハツェンダ干渉計またはマッハツェンダ変調器として具現可能な光変調器70は、第1位相変調器72、第2位相変調器74、光分離器76、及び光結合器80を含む。

【0032】

位相シフタの機能を行える第1位相変調器72は、第1データストリームによって第1光信号の位相を変調し、該位相変調された第1光信号を第1光導波路78−1に伝送する。第1データストリームは、第1位相変調器72の第1電極72−1に供給される第1電気信号E1と第1位相変調器72の第2電極72−2に供給される第2電気信号E2との差によって発生したデータストリームを意味する。

【0033】

位相シフタの機能を行える第2位相変調器74は、第2入力データストリームによって第2光信号の位相を変調し、該位相変調された第2光信号を第2光導波路78−2に伝送する。第2データストリームは、第2位相変調器74の第1電極74−1に供給される第3電気信号と第2位相変調器74の第2電極74−2に供給される第4電気信号との差によって発生したデータストリームを意味する。

【0034】

光変調器70は、第1データストリームの位相と振幅とを調節するための調節器82をさらに含む。調節器82は、第1データストリームを所定時間またはN(ここで、Nは、実数)ビット遅延させ、第1データストリームの振幅(または、パワー(power))を減衰させることができる。調節器82は、遅延と減衰とを同時に、または順次に行うことができる。調節器82は、遅延を減衰より先に行うか、または後で行うことができる。

【0035】

調節器82は、第1電気信号E1と第2電気信号E2のそれぞれの位相と振幅とを調節し、第3電気信号と第4電気信号のそれぞれを生成することができる。第1電気信号E1は、同じ振幅(または、パワー)を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つは調節器82に入力される。また、第2電気信号E2は、同じ振幅(または、パワー)を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つは調節器82に入力される。

【0036】

光分離器76は、光源73から出力された持続波形を有する光信号を受信し、これを同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器72内に形成された光導波路と第2位相変調器74内に形成された光導波路のそれぞれに伝送する。この際、第1位相変調器72の長さL1は、第2位相変調器74の長さL1と同一である。

【0037】

光結合器80は、第1光導波路78−1を通じて伝送された位相変調された第1光信号と第2光導波路78−2を通じて伝送された位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する。したがって、光変調器70は、電気的ディエンファシス駆動回路より簡単な調節器82を使って、ディエンファシス波形を有する出力光信号を生成することができる効果がある。

【0038】

図3は、本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。図3を参照すると、マッハツェンダ干渉計またはマッハツェンダ変調器として具現可能な光変調器90は、第1位相変調器92、第2位相変調器94、光分離器96、及び光結合器100を含む。

【0039】

位相シフタの機能を行える第1位相変調器92は、第1データストリームによって第1光信号の位相を変調し、該位相変調された第1光信号を第1光導波路98−1に伝送する。第1データストリームは、第1位相変調器92の第1電極92−1に供給される第1電気信号E1と第1位相変調器92の第2電極92−2に供給される第2電気信号E2との差によって発生したデータストリームを意味する。

【0040】

位相シフタの機能を行える第2位相変調器94は、第2入力データストリームによって第2光信号の位相を変調し、該位相変調された第2光信号を第2光導波路98−2に伝送する。第2データストリームは、第2位相変調器94の第1電極94−1に供給される第3電気信号と第2位相変調器94の第2電極94−2に供給される第4電気信号との差によって発生したデータストリームを意味する。

【0041】

光変調器90は、第1データストリームの振幅(または、パワー)を減衰させるための減衰器(attenuator)102をさらに含む。減衰器102は、第1データストリーム振幅を減衰させ、第2データストリームを生成する。例えば、減衰器102は、第1電気信号E1と第2電気信号E2のそれぞれの振幅を減衰させ、第3電気信号と第4電気信号のそれぞれを生成することができる。

【0042】

第1電気信号E1は、同じ振幅を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つは減衰器102に入力される。また、第2電気信号E2は、同じ振幅を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つは減衰器(または、調節器)102に入力される。

【0043】

光分離器96は、光源93から出力された持続波形を有する光信号を受信し、これを同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器92内に形成された光導波路と第2位相変調器94内に形成された光導波路のそれぞれに伝送する。この際、第1位相変調器92の長さL1は、第2位相変調器94の長さL1と同一である。第1位相変調器92によって位相変調された第1光信号は、第1光導波路98−1に沿って光結合器100に伝送され、第2位相変調器92によって位相変調された第2光信号は、第2光導波路98−2に沿って光結合器100に伝送される。

【0044】

図3に示したように、第1光導波路98−1の長さは、第2光導波路98−2の長さより短い。第2光導波路98−2の長さを調節することによって、第2光導波路98−2を通じて伝送される位相変調された第2光信号は、第1光導波路98−1を通じて伝送される位相変調された第1光信号よりNビット遅延されうる。

【0045】

他の実施形態によって、第1光導波路98−1の長さと第2光導波路98−2の長さとが互いに同様に具現される時、光変調器90は、第2光導波路98−2を通じて伝送される位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させるためのビット遅延ユニットをさらに含みうる。

【0046】

光結合器100は、第1光導波路98−1を通じて伝送され、位相変調された第1光信号と、第2光導波路98−2を通じて伝送されながらN(Nは、実数)ビット遅延され、位相変調された第2光信号とを結合して、ディエンファシス波形を変調された出力光信号を生成することができる効果がある。すなわち、光変調器90は、第1データストリームの振幅(または、パワー)を減衰させるための減衰器102と第1光導波路98−1の長さより長い長さを有する第2光導波路98−2とを用いて、ディエンファシス波形を有する変調された出力光信号を生成することができる効果がある。

【0047】

図4は、本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。図4を参照すると、マッハツェンダ干渉計またはマッハツェンダ変調器として具現可能な光変調器110は、第1位相変調器112、第2位相変調器114、光分離器116、及び光結合器120を含む。

【0048】

位相シフタの機能を行える第1位相変調器112は、第1入力データストリームによって第1光信号の位相を変調し、該位相変調された第1光信号を第1光導波路118−1に伝送する。前記第1入力データストリームは、第1位相変調器112の第1電極112−1に供給される第1電気信号E1と第1位相変調器112の第2電極112−1に供給される第2電気信号E2との差によって発生したデータストリームを意味する。

【0049】

位相シフタの機能を行える第2位相変調器114は、第2入力データストリームによって第2光信号の位相を変調し、該位相変調された第2光信号を第2光導波路118−2に伝送する。第2データストリームは、第2位相変調器114の第1電極114−1に供給される第3電気信号と第2位相変調器114の第2電極114−2に供給される第4電気信号との差によって発生したデータストリームを意味する。

【0050】

光変調器110は、第1データストリームの位相をN(Nは、実数)ビット遅延させるためのビット遅延ユニット122をさらに含む。ビット遅延ユニット122は、第1データストリームの位相をN(Nは、実数)ビット遅延させ、第2データストリームを生成する。例えば、ビット遅延ユニット122は、第1電気信号E1と第2電気信号E2のそれぞれの位相をNビット遅延させ、第3電気信号と第4電気信号のそれぞれを生成することができる。

【0051】

第1電気信号E1は、同じ振幅を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つはビット遅延ユニット122に入力される。第2電気信号E2は、同じ振幅を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つはビット遅延ユニット122に入力される。

【0052】

光分離器116は、光源113から出力された持続波形を有する光信号を受信し、これを同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器112内に形成された光導波路と第2位相変調器114内に形成された光導波路のそれぞれに伝送する。

【0053】

第2光信号を変調するための第2位相変調器114の長さL2は、第1光信号を変調するための第1位相変調器112の長さL1より短い。位相変調器の長さが短ければ短いほど同じ光信号に対して位相変調(または、位相シフト)の量も少なくなる。したがって、前記光信号に対する減衰が発生する。

【0054】

第1位相変調器112によって位相変調された第1光信号は、第1光導波路118−1を通じて光結合器120に伝送され、第2位相変調器114によって位相変調された第2光信号は、第2光導波路118−2を通じて光結合器120に伝送される。この際、第1光導波路118−1の長さ(より具体的に、第1位相変調器112に形成された光導波路を除いた長さ)と第2光導波路118−2の長さ(より具体的に、第1位相変調器112に形成された光導波路を除いた長さ)は、互いに同一である。

【0055】

光結合器120は、第1光導波路118−1を通じて伝送され、位相変調された第1光信号と第2光導波路118−2を通じて伝送され、位相変調された第2光信号とを結合して、ディエンファシス波形を有する変調された出力光信号を生成する。すなわち、光結合器120は、第1データストリームを遅延させるためのビット遅延ユニット122と第1位相変調器112の長さL1より短い長さL2を有する第2位相変調器114とを用いて、ディエンファシス波形を有する変調された出力光信号を生成することができる効果がある。

【0056】

図5は、本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。図5に示された光変調器30は、ディエンファシス方法を用いて光−電変換を行う。ディエンファシス方法は、ローレベルからハイレベルに遷移するか、またはハイレベルからローレベルに遷移する遷移ビット(transition bit)は、そのまま置き、残りのビットのそれぞれの変調振幅を減らして、変調特性を改善する方法を意味する。

【0057】

図5を参照すると、光変調器30は、第1位相変調器32、第2位相変調器34、光分離器36、及び光結合器38を含む。光分離器36から出力された第1光信号は、第1位相変調器32に供給され、光分離器36から出力された第2光信号は、第2位相変調器34に供給される。

【0058】

第1ディエンファシス信号は、第1位相変調器32の2つの電極32−1、32−2に供給され、第2ディエンファシス信号は、第2位相変調器34の2つの電極34−1、34−2に供給される。第1ディエンファシス信号と第2ディエンファシス信号は、経時的に同期され、第1ディエンファシス信号の位相は、第2ディエンファシス信号の位相と逆である。

【0059】

光結合器38は、第1位相変調器32によって位相変調された第1光信号と第2位相変調器34によって位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を出力する。ディエンファシス方式を使う光変調器30は、変調速度を改善することができる。

【0060】

図6は、図1から図5に示された光変調器のうちの何れか一つを含む本発明の一実施形態によるデータ処理システムのブロック図を示す。図6を参照すると、データ処理システム200は、第1装置210と第2装置220とを含む。第1装置210と第2装置220とは、シリアル通信を通じてディエンファシス波形を光信号で通信することができる。

【0061】

第1装置210は、第1光源212、電−光変換(electrical to optical conversion)動作を行える第1光変調器214、及び光−電変換(optical to electrical conversion)動作を行える第1光復調器(optical de−modulator)216を含む。

【0062】

第1光源212は、持続波形を有する光信号を出力する。第1光源212は、図1から図4に示された光源53、73、93、及び113のうちの何れか一つで具現可能である。第1光変調器214は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。第1光復調器216は、第2装置220の第2光変調器224から出力されたディエンファシス波形を有する出力光信号を受信して復調し、該復調された電気信号を出力する。

【0063】

第2装置220は、第2光源222、第2光変調器224、及び第2光復調器226を含む。第2光源222は、持続波形を有する光信号を出力する。第2光源222は、図1から図4に示された光源53、73、93、及び113のうちの何れか一つで具現可能である。第2光変調器224は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。第2光復調器226は、第1装置210の第1光変調器214から出力されたディエンファシス波形を有する出力光信号を受信して復調し、該復調された電気信号を出力する。

【0064】

図7は、図1から図5に示された光変調器のうちの何れか一つを含む本発明の他の実施形態によるデータ処理システムのブロック図を示す。図7に示されたMOD(E/O)は、電−光変換器として使われる光変調器を意味するものであって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0065】

図7を参照すると、データ処理システム300は、CPU310、複数のデータバス301−1〜301−3、及び複数のメモリモジュール340を含む。複数のメモリモジュール340のそれぞれは、複数のデータバス301−1〜301−3のそれぞれに接続された複数のカプラ311−1、311−2、及び311−3のそれぞれを通じてディエンファシス波形を有する光信号を送受信することができる。実施形態によって、複数のカプラ311−1、311−2、及び311−3のそれぞれは、電気的なカプラ(electrical coupler)または光学的なカプラ(optical coupler)で具現可能である。

【0066】

CPU310は、少なくとも一つの光変調器MOD(E/O)と少なくとも一つの光復調器DEM(O/E)とを含む第1光送受信器316、及びメモリコントローラ312を含む。少なくとも一つの光復調器DEM(O/E)は、光−電変換器として使われる。

【0067】

メモリコントローラ312は、CPU310の制御下で第1光送受信器316の動作、例えば、送信動作または受信動作を制御することができる。例えば、ライト動作時に、第1光送受信器316の第1光変調器MOD(E/O)は、メモリコントローラ312の制御下でアドレスと制御信号とを図2から図6を参照して説明したように、ディエンファシス波形を有する変調された光信号を生成し、該生成された光信号ADD/CTRLを光通信バス301−3に伝送しうる。

【0068】

第1光送受信器316が、光信号ADD/CTRLを光通信バス301−3に伝送した後、第1光送受信器316の第2光変調器MOD(E/O)は、ディエンファシス波形を有する変調された光ライトデータWDATAを生成し、該生成された光ライトデータWDATAを光通信バス301−2に伝送しうる。

【0069】

各メモリモジュール340は、第2光送受信器330及び複数のメモリ装置335を含む。各メモリモジュール340は、光学的DIMM(optical dual in−line memory module)、光学的Fully Buffered DIMM、光学的SO−DIMM(small outline dual in−line memory module)、Optical RDIMM(Registered DIMM)、Optical LRDIMM(Load Reduced DIMM)、UDIMM(Unbuffered DIMM)、光学的MicroDIMM、または光学的SIMM(single in−line memory module)として具現可能である。

【0070】

図7を参照すると、第2光送受信器330に具現された光復調器DEM(O/E)は、光通信バス301−2を通じて入力された光ライトデータWDATAを復調し、該復調された電気信号を複数のメモリ装置335のうちの少なくとも一つのメモリ装置に伝送しうる。

【0071】

実施形態によって、各メモリモジュール340は、光復調器DEM(O/E)から出力された電気信号をバッファリング(buffering)するための電気的なバッファ(buffer)333をさらに含みうる。例えば、電気的なバッファ333は、復調された電気信号をバッファリングし、該バッファリングされた電気信号を複数のメモリ装置335のうちの少なくとも一つのメモリ装置に伝送しうる。

【0072】

複数のメモリ装置335のそれぞれは、複数のメモリセル(memory cells)を含むメモリアレイ(memory array)337、メモリアレイ337にアクセス(access)できるアクセス回路339、及びアクセス回路339の動作を制御することができるコントロールロジック(control ligic;図示せず)を含みうる。

【0073】

リード(read)動作時に、メモリ装置335から出力された電気信号は、第2光送受信器330に具現された光変調器MOD(E/O)によってディエンファシス波形を有する光リードデータ(read data)RDATAに変調される。光リードデータRDATAは、光通信バス301−1を通じてCPU310に具現された第1光復調器DEM(O/E)に伝送される。第1光復調器DEMは、光リードデータRDATAを復調し、該復調された電気信号をメモリコントローラ312に伝送する。

【0074】

図8は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システム(system)のブロック図を示す。

図8に示されたMOD(E/O)は、電−光変換機能を行う光変調器であって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0075】

図8を参照すると、データ伝送システム400は、CPU410、複数のデータバス(data buses)401−1、401−2、及び401−3、及び複数のメモリモジュール(memory module)440を含む。複数のデータバス401−1、401−2、及び401−3のそれぞれは、電気的または光学的に信号を伝送しうる。

複数のメモリモジュール440のそれぞれは、複数のメモリ装置441を含み、複数のメモリ装置441のそれぞれは、第2光送受信器445を含む。

【0076】

また、複数のメモリ装置441のそれぞれは、複数のメモリセルを含むメモリアレイ443、メモリアレイ443にアクセスできるアクセス回路(図示せず)、及びアクセス回路の動作を制御することができるコントロールロジック(図示せず)を含みうる。

データ処理システム400のライト(write)動作が説明される。まず、ライト動作を行うためのアドレス(addresses)と制御信号ADD/CTRLは、対応するデータバス401−3を通じて既に複数のメモリ装置441のうちの少なくとも一つに伝送されたと仮定する。

【0077】

CPU410の第1光送受信器416内の光変調器MOD(E/O)は、メモリコントローラ412の制御下でディエンファシス波形を有する光ライトデータWDATAをデータバス401−2に接続された光学的カプラ411−2を通じて第1メモリモジュール440の第2光送受信器445の光復調器DEM(O/E)に伝送する。

【0078】

第2光送受信器445の光復調器DEM(O/E)は、光ライトデータWDATAを復調し、該復調された電気信号を発生させる。アクセス回路は、コントロールロジックの制御下で、電気信号をメモリアレイ443にライトする。

データ処理システム400のリード動作が説明される。

【0079】

まず、リード動作を行うためのアドレスと制御信号ADD/CTRLとは、対応するデータバス401−3を通じて既に複数のメモリ装置441のうちの何れか一つのメモリ装置に伝送されたと仮定する。メモリ装置441の第2光送受信器445内の光変調器MOD(E/O)は、メモリアレイ443から出力された電気信号を、ディエンファシス波形を有する光リードデータRDATAに変調し、これをデータバス401−1に接続された光学的カプラ411−1を通じてCPU410の第1光送受信器416の復調器DEM(O/E)に伝送する。第1光送受信器416の第1光復調器DEM(O/E)は、光リードデータRDATAを電気信号に復調し、該復調された電気信号をメモリコントローラ412に出力する。

【0080】

図9は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図9を参照すると、データ処理システム500は、第1装置510と第2装置530とを含む。図9に示されたMOD(E/O)は、光変調器を意味するものであって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0081】

第1装置510と第2装置530のそれぞれは、シリアル(serial)通信プロトコル(protocol)を用いてデータを送受信することができる装置を意味する。シリアル通信プロトコルは、その実施形態として、UART(Universal Asynchronous Receiver Transmitter)、SPI(Serial Peripheral Interface)、I2C(Inter−integrated Circuit)、SMBus(System Management Bus)、CAN(Controller Area Network)、USB(Universal Serial Bus)、IC(Inter−chip)−USB、MIPI(登録商標)(mibile industry processor interface)で規定するCSI(camera serial interface)、MIPI(登録商標)で規定するDSI(display serial interface)、MDDI(MobileDisplay Digital Interface)、またはLIN(Local Interconnect Network)を支援するデータ通信プロトコルであり得る。

【0082】

図9を参照すると、第1装置510に具現された第1光送受信512の第1光変調器518は、第1マイクロプロセッサ514の制御下でディエンファシス波形を有する変調された光信号を、データバスを通じて第2装置530の第2光送受信器532の第2光復調器540に伝送する。第2光復調器540は、受信された光信号を電気信号に復調する。第2マイクロプロセッサ(microprocessor)534は、第2光復調器540から出力され、復調された電気信号を処理する。例えば、ライト動作時に、第2マイクロプロセッサ534は、電気信号をメモリアレイにライトすることができる。

【0083】

第2装置530の第2光送受信器532の第2光変調器538は、第2マイクロプロセッサ534の制御下でディエンファシス波形を有する変調された光信号を、データバスを通じて第1装置510の第1光送受信器512の第1光復調器520に伝送する。第1光復調器520は、受信された光信号を電気信号に復調する。

【0084】

第1マイクロプロセッサ514は、第1光復調器520から出力され、復調された電気信号を処理する。例えば、リード動作時に、第1マイクロプロセッサ514は、電気信号をリードデータとして処理することができる。各マイクロプロセッサ514、534は、その名称にもかかわらず、各装置510、530の動作、例えば、ライト動作またはリード動作を制御することができるプロセッサを意味する。

【0085】

図10は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図10を参照すると、SPI(serial peripheral interface)通信プロトコルを使って、シリアルデータを送受信することができるデータ処理システム700は、SPIマスタ(master)710と少なくとも一つのSPIスレーブ(slave)720、730、740、及び750を含む。

【0086】

図10に示されたMOD(E/O)は、光変調器を意味するものであって、光変調器MOD(E/O)は、図2から図6に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0087】

複数のSPIスレーブ720、730、740、及び750のうちの何れか一つは、シフトレジスタ(shift register)、メモリチップ(memory chip)、ポート拡張器(port expander)、ディスプレイドライバ(displaydriver)、データ変換器(data converter)、プリンタ(printer)、データ保存装置(data storage)、センサ(sensor)、またはマイクロプロセッサであり得る。

【0088】

第1光送受信器712と各第2光送受信器722、732、742、または752は、対応する光学的データバスを通じてディエンファシス波形を有する光信号(MOSI(Master Out Slave In)またはMISO(Master In Slave Out)を送受信することができる。SPIマスタ710は、第1光送受信器712の動作を制御することができるマイクロプロセッサ(図示せず)を含み、複数のSPIスレーブ720、730、740、及び750のそれぞれは、第2光送受信器722、732、742、または750の動作を制御することができるマイクロプロセッサ(図示せず)を含む。

【0089】

また、第1光送受信器712は、シリアルクロック信号CLKを電気的なデータバスまたは光学的データバスを通じて各第2光送受信器722、732、742、または752に伝送しうる。各SPIスレーブ720、730、740、及び750は、各チップ選択信号SS0、SS1、SS2、及びSS3によって選択されうる。この場合、各チップ選択信号SS0、SS1、SS2、及びSS3は、電気的なデータバスまたは光学的データバスを通じて各第2光送受信器722、732、742、または752に伝送することができる。

【0090】

図11は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。SATA(Serial Advanced Technology Attachment)通信プロトコルを使って、シリアルデータを送受信することができるデータ処理システム800は、SATAホスト810とSATA装置830とを含む。図11に示されたMOD(E/O)は、光変調器を意味するものであって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0091】

SATAホスト810は、ホストCPU811、データバス813、メモリ815、DMAコントローラ817、及び第1SATAインタフェース819を含む。ホストCPU811は、DMAコントローラ(direct memory access controller)817または第1SATAインタフェース819の動作を制御する。第1SATAインタフェース819は、第1光変調器MOD(E/O)と第1光復調器DEM(O/E)とを含む。

【0092】

SATAホスト810は、第1SATAインタフェース819の動作を制御することができるコントローラを含みうる。実施形態によって、コントローラは、第1SATAインタフェース819の内部に具現されることもあり、ホストCPU811が、コントローラの機能を行える。SATA装置830は、ハードディスクコントローラ840とメモリ装置850、及び磁気的記録媒体860を含む。ハードディスクコントローラ840は、MCU(main control unit)841、データバス843、第2SATAインタフェース845、バッファ847、及びディスクコントローラ849を含む。

【0093】

MCU841は、第2SATAインタフェース845、バッファ847、及びディスクコントローラ849のうちの少なくとも一つの動作を制御する。

第2SATAインタフェース845は、第2光変調器MOD(O/E)と第2光復調器DEM(E/O)とを含む。SATA装置830は、第2SATAインタフェース845の動作を制御することができるコントローラを含みうる。実施形態によって、コントローラは、第2SATAインタフェース845の内部に具現されることもあり、MCU841が、コントローラの機能を行える。

【0094】

ライト動作時に、メモリ815に保存されたライトデータは、DMAコントローラ817の制御下で第1SATAインタフェース819の第1光変調器MOD(E/O)に伝送される。

【0095】

第1光変調器MOD(E/O)は、ライトデータによってディエンファシス波形を有する光ライトデータを生成し、該生成された光ライトデータを、データバスを通じて第2SATAインタフェース845の第2光復調器DEM(O/E)に伝送する。第2光復調器DEM(E/O)は、光ライトデータを電気信号に復調することができる。バッファ847は、電気信号をバッファリングし、該バッファされた電気信号をメモリ装置850に一時的に保存する。

【0096】

ディスクコントローラ(disk controller)849は、メモリ装置850に保存された電気信号をリードして、ライトアドレスによって指定された磁気的記録媒体860、例えば、ディスク(disk)にライトする。

リード動作時に、ディスクコントローラ849は、リードアドレスによって指定された磁気的記録媒体860からデータをリードし、該リードされたデータを、バッファ847を通じてメモリ装置850に保存する。

【0097】

第2SATAインタフェース845の第2変調器MOD(E/O)は、バッファ847を通じてメモリ装置850からデータによってディエンファシス波形を有する光リードデータを生成し、該生成された光リードデータを、データバスを通じて第1SATAインタフェース819の第1光復調器DEM(O/E)に伝送する。第2光復調器DEM(O/E)は、受信された光リードデータを電気信号に復調する。DMAコントローラ817は、第2光復調器DEM(O/E)によって復調された電気信号をメモリ815に保存する。

【0098】

図12は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。USB(Universal Serial Bus)通信プロトコルまたはIC−USB通信プロトコルを使って、シリアルデータを送受信することができるデータ処理システム900は、USBホスト910とUSB装置920とを含む。図12に示されたMOD(E/O)は、光変調器を意味するものであって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0099】

USBホスト910の第1光送受信器912の第1光変調器MOD(E/O)によって生成されたディエンファシス波形を有する光信号は、データバス900−1を通じてUSB装置920の第2光送受信器914の第2光復調器DEM(O/E)に伝送され、USB装置920の第2光復調器DEM(O/E)は、受信された光信号を復調して電気信号を生成する。

【0100】

USBホスト910は、第1光送受信器912の動作を制御することができるマイクロコントローラ(図示せず)をさらに含みうる。

USB装置920の第2光送受信器914の第2変調器MOD(E/O)によって生成されたディエンファシス波形を有する光信号は、データバス900−2を通じてUSBホスト910の第1光送受信器912の第1復調器DEM(O/E)に伝送され、USBホスト910の第1光復調器DEM(O/E)は、受信された光信号を復調して電気信号を生成する。

【0101】

USB装置920は、第1光送受信器912の動作を制御することができるマイクロコントローラ(図示せず)をさらに含みうる。

【0102】

図13は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図13に示されたSoC(system on chip)1000は、複数のマスタ1010、1020、複数のスレーブ1030、1040、及び複数のバス1001を含む。複数のマスタ1010、1020のそれぞれと複数のスレーブ1030、1040のそれぞれは、光変調器MOD(E/O)と光復調器DEM(O/E)とを含む。複数のバス1001のそれぞれは、光導波路として具現可能である。

【0103】

各光変調器MOD(E/O)によって変調された光信号は、それぞれが光導波路として具現された複数のバス1001のうち対応するバスを通じて各光復調器DEM(O/E)に伝送され、各光復調器DEM(O/E)は、受信された光信号を復調して電気信号を発生させる。

【0104】

図14は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図14に示されたデータ処理システム1100は、複数のレイヤ(layers)1110、1120を含む積層構造で形成される。

【0105】

第1レイヤ1110は、第1光送受信器1111と第1光送受信器1111の動作を制御することができる第1データプロセッシング(data processing)回路1113とを含む。

【0106】

第1光送受信器1111の第1光変調器MOD(E/O)は、ディエンファシス波形を有する光信号を光伝送手段、例えば、光導波路、TSV(through siliconvia)、または光纎維を通じて第2レイヤ1120の第2光復調器DEM(O/E)に伝送する。第2光復調器DEM(O/E)によって復調された電気信号は、第2データプロセッシング回路1123によって処理される。

【0107】

第2光送受信器1121の第2光変調器MOD(E/O)は、ディエンファシス波形を有する光信号を光伝送手段、例えば、光導波路、TSV、または光纎維を通じて第1レイヤ1110の第1光復調器DEM(O/E)に伝送する。第1光復調器DEM(O/E)によって復調された電気信号は、第1データプロセッシング回路1113によって処理される。

【0108】

図15は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図15に示されたデータ処理システム1200は、MIPI(登録商標)(Mobile Industry Processor Interface)を使用または支援することができるデータ処理装置、例えば、携帯電話機(mobile phone)、スマートフォン(smart phone)、PDA(personal digital assistant)、PMP(portable media player)、または移動通信装置として具現可能である。

【0109】

データ処理システム1200は、アプリケーションプロセッサ1210、イメージセンサ1240、及びディスプレイ1250を含む。アプリケーションプロセッサ1210に具現されたCSIホスト1220は、カメラシリアルインタフェース(cameraserial interface、CSI)を通じてイメージセンサ1240のCSI装置1241とシリアル通信することができる。例えば、CSIホスト1220には、光復調器DEMが具現され、CSI装置1241の光変調器MODは、図2から図6に示された光変調器50、70、90、110、及び30のうちの何れか一つが具現可能である。

【0110】

アプリケーションプロセッサ1210に具現されたDSIホスト1230は、ディスプレイシリアルインタフェース(display serial interface、DSI)を通じてディスプレイ1250のDSI装置1251とシリアル通信することができる。例えば、DSIホスト1230の光変調器MODは、図2から図6に示された光変調器50、70、90、110、及び30のうちの何れか一つが具現可能である。

【0111】

データ処理システム1200は、アプリケーションプロセッサ1210と通信することができるRFチップ1260をさらに含みうる。データ処理システム1200のPHYとRFチップ1260のPHYは、MIPI DigRFによってデータを送受信することができる。データ処理システム1200は、ストレージ1270、マイク1280、及びスピーカ1290のうちの少なくとも一つをさらに含みうる。

【0112】

本明細書に使われた電気信号は、直列電気信号または並列電気信号を意味し、また電気信号は、直列データまたは並列データを意味する。

本発明は、図面に示された一実施形態を参考にして説明されたが、これは例示的なものに過ぎず、当業者ならば、これより多様な変形及び均等な他実施形態が可能であるという点を理解できるであろう。したがって、本発明の真の技術的保護範囲は、特許請求の範囲の技術的思想によって決定されるべきである。

【産業上の利用可能性】

【0113】

本発明は、光変調器に使われる。

【符号の説明】

【0114】

50:光変調器

52:第1位相変調器

54:第2位相変調器

58−1:第1光導波路

58−2:第2光導波路

82:調節器

102:減衰器

122:ビット遅延ユニット

【技術分野】

【0001】

本発明は、光変調器に係り、特に、光学的ディエンファシス信号を生成することができる光変調器及びその方法に関する。

【背景技術】

【0002】

光変調器(optical modulator)は、光のビーム(beam)を変調するために使われる装置である。ビームは、自由空間、光繊維、または光導波路を通じて伝送される。操作される光のビームのパラメータ(parameter)によって、変調器は、振幅変調器、位相変調器、または極性変調器などに分類される。

【発明の概要】

【発明が解決しようとする課題】

【0003】

本発明が解決しようとする技術的な課題は、光学的ディエンファシス駆動方式を使うことができる光変調器と該光変調器の信号生成方法とを提供するところにある。

【課題を解決するための手段】

【0004】

本発明の実施形態による光変調器は、第1位相変調器によって位相変調された第1光信号を伝送するための第1光導波路と、第1位相変調器の長さより短い長さを有する第2位相変調器によって位相変調された第2光信号を伝送するための第2光導波路と、を含む。

第2光導波路の長さは、第1光導波路の長さより長い。

【0005】

第2光導波路の長さは、位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させるための長さだけ第1光導波路の長さより長い。

実施形態によって、第1位相変調器と第2位相変調器のそれぞれは、同じ入力データストリームによって、位相変調された第1光信号と位相変調された第2光信号のそれぞれを生成する。

【0006】

他の実施形態によって、第1位相変調器は、第1入力データストリームによって、位相変調された第1光信号を生成し、第2位相変調器は、第2入力データストリームによって、位相変調された第2光信号を生成する。

第2入力データストリームは、第1入力データストリームよりN(ここで、Nは、実数)ビットだけ遅延される。

【0007】

光変調器は、第1入力データストリームをN(ここで、Nは、実数)ビットだけ遅延させ、第2データストリームを生成するためのビット遅延ユニットをさらに含む。

光変調器は、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成するための光結合器をさらに含む。

【0008】

光変調器は、位相変調された第2光信号をN(ここで、Nは、実数)ビットだけ遅延させるためのビット遅延ユニットをさらに含む。

光変調器は、持続波形を有する光信号を出力するための光源と、光信号を同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器と第2位相変調器のそれぞれに出力するための光分離器と、をさらに含む。

【0009】

本発明の他の実施形態による光変調器は、第1データストリームによって位相変調された第1光信号を生成するための第1位相変調器と、第1データストリームの位相と振幅とを調節するための調節器と、調節器から出力された第2データストリームによって位相変調された第2光信号を生成するための第2位相変調器と、を含む。

【0010】

調節器は、第1データストリームをN(ここで、Nは、実数)ビット遅延させ、第2データストリームを生成する。

光変調器は、持続波形を有する光信号を出力するための光源と、光信号を同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器と第2位相変調器のそれぞれに出力するための光分離器と、をさらに含む。

光変調器は、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成するための光結合器をさらに含む。

【0011】

本発明のまた他の実施形態による光変調器は、第1データストリームによって位相変調された第1光信号を生成するための第1位相変調器と、第1データストリームの振幅を減衰させるための減衰器と、減衰器から出力された第2データストリームによって位相変調された第2光信号を生成するための第2位相変調器と、第2位相変調器から出力され、位相変調された第2光信号を遅延させるための遅延ユニットと、を含む。

【0012】

光変調器は、位相変調された第1光信号を伝送するための第1光導波路と、位相変調された第2光信号を伝送するための第2光導波路と、をさらに含み、遅延ユニットは、第2光導波路の一部として具現される。

遅延ユニットが形成された第2光導波路の長さは、第1光導波路の長さより長い。

遅延ユニットは、位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させる。

【0013】

光変調器は、持続波形を有する光信号を出力するための光源と、光信号を同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器と第2位相変調器のそれぞれに出力するための光分離器と、をさらに含む。

光変調器は、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成するための光結合器をさらに含む。

【0014】

第1データストリームは、第1入力信号と第2入力信号との差によって生成される。

本発明の実施形態による光変調器の光変調信号生成方法は、第1位相変調器によって位相変調された第1光信号を、第1光導波路を通じて伝送する段階と、第1位相変調器の長さより短い長さを有する第2位相変調器によって位相変調された第2光信号を、第2光導波路を通じて伝送する段階と、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、を含む。

【0015】

第2光導波路の長さは、第1光導波路の長さより長い。

本発明の他の実施形態による光変調器の光変調信号生成方法は、第1位相変調器を用いて第1データストリームによって位相変調された第1光信号を生成する段階と、第1データストリームの位相と振幅とを調節して第2データストリームを生成する段階と、第2位相変調器を用いて第2データストリームによって位相変調された第2光信号を生成する段階と、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、を含む。

【0016】

第2データストリームを生成する段階は、第1データストリームをN(ここで、Nは、実数)ビット遅延させ、第2データストリームを生成する。

【0017】

本発明のまた他の実施形態による光変調器の光変調信号生成方法は、第1位相変調器を用いてデータストリームによって位相変調された第1光信号を生成する段階と、データストリームの振幅を減衰させる段階と、第2位相変調器を用いて振幅減衰されたデータストリームによって位相変調された第2光信号を生成する段階と、位相変調された第2光信号を遅延させる段階と、位相変調された第1光信号と位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、を含む。

【0018】

位相変調された第2光信号を遅延させる段階は、位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させる。

【発明の効果】

【0019】

本発明の実施形態による光変調器は、光学的ディエンファシス波形を有する出力光信号を生成することができるので、変調速度を改善することができる。

【図面の簡単な説明】

【0020】

本発明の詳細な説明で引用される図面をより十分に理解するために、各図面の詳細な説明が提供される。

【図1】本発明の一実施形態による光変調器の概略的な回路図を示す。

【図2】本発明の他の実施形態による光変調器の概略的な回路図を示す。

【図3】本発明のまた他の実施形態による光変調器の概略的な回路図を示す。

【図4】本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。

【図5】本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。

【図6】図1から図5に示された光変調器のうちの何れか一つを含む本発明の一実施形態によるデータ処理システムのブロック図を示す。

【図7】図1から図5に示された光変調器のうちの何れか一つを含む本発明の他の実施形態によるデータ処理システムのブロック図を示す。

【図8】図1から図5に示された光変調器のうちの何れか一つを含む本発明のまた他の実施形態によるデータ処理システムのブロック図を示す。

【図9】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図10】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図11】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図12】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図13】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図14】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【図15】図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。

【発明を実施するための形態】

【0021】

以下、添付した図面を参照して、本発明を詳しく説明する。

【0022】

図1は、本発明の一実施形態による光変調器の概略的な回路図を示す。図1を参照すると、マッハツェンダ干渉計(Mach−Zehnder interferometer)またはマッハツェンダ変調器(Mach−Zehnder modulator)として具現可能な光変調器50は、第1位相変調器52、第2位相変調器54、光分離器56、及び光結合器60を含む。

【0023】

位相シフタ(phase shifter)の機能を行える第1位相変調器52は、入力データストリーム(data stream)によって第1光信号の位相を変調し、該位相変調された第1光信号を第1光導波路58−1に伝送する。位相シフタの機能を行える第2位相変調器54は、入力データストリームによって第2光信号の位相を変調し、該位相変調された第2光信号を第2光導波路58−2に伝送する。

【0024】

入力データストリームは、各位相変調器52、54の第1電極52−1、54−1に供給される第1電気信号E1と各位相変調器52、54の第2電極52−2、54−2に供給される第2電気信号E2との差によって発生したデータストリームを意味する。第1電気信号E1は、同じ振幅を有する2つの信号に分離され、第2電気信号E2は、同じ振幅を有する2つの信号に分離される。

【0025】

光分離器56は、光源53から出力された持続波形(continuous waveform)を有する光信号を受信し、これを同様に2つにパワー分離(power−splitting)し、該パワー分離された光信号のそれぞれを第1位相変調器52内に形成された光導波路(optical waveguide)と第2位相変調器54内に形成された光導波路のそれぞれに伝送する。

【0026】

第2光信号の位相を変調することができる第2位相変調器54の長さL2は、第1光信号の位相を変調することができる第1位相変調器52の長さL1より短く形成される。位相変調器の長さが短ければ短いほど同じ光信号に対して位相変調(または、位相シフト)の量も少なくなる。したがって、光信号に対する減衰が発生する。

【0027】

第1位相変調器52によって位相変調された第1光信号は、第1光導波路58−1を通じて光結合器60に伝送され、第2位相変調器54によって位相変調された第2光信号は、第2光導波路58−2を通じて光結合器60に伝送される。

【0028】

図1に示したように、第1光導波路58−1の長さ(より具体的に、第1位相変調器52内に形成された光導波路を除いた長さ)は、第2光導波路58−2の長さ(より具体的に、第2位相変調器54内に形成された光導波路を除いた長さ)より短い。例えば、第1位相変調器52の相対的な長さが2であり、第1光導波路58−1の相対的な長さが8である時、第2位相変調器54の相対的な長さが1であり、第2光導波路58−2の相対的な長さは9である。

【0029】

第2光導波路58−2の長さを調節することによって、第2光導波路58−2を通じて伝送される位相変調された第2光信号は、第1光導波路58−1を通じて伝送される位相変調された第1光信号より一定時間またはNビット遅延されうる。この際、Nは、実数である。他の実施形態によって、第1光導波路58−1の長さと第2光導波路58−2の長さとが互いに同様に具現される時、光変調器50は、第2光導波路58−2を通じて伝送される位相変調された第2光信号をNビット(bit)遅延させるためのビット遅延ユニット(unit)を含みうる。

【0030】

光結合器60は、第1光導波路58−1を通じて伝送された位相変調された第1光信号と、第2光導波路58−2を通じて伝送されながらNビット遅延された位相変調された第2光信号とを結合して、ディエンファシス(de−emphasis)波形を有する出力光信号を生成する。前述したように、光変調器50は、別途の電気的ディエンファシス駆動回路なしでも、第2位相変調器54と第2光導波路58−2とを用いて、ディエンファシス波形を有する出力光信号を生成することができる効果がある。

【0031】

図2は、本発明の他の実施形態による光変調器の概略的な回路図を示す。図2を参照すると、マッハツェンダ干渉計またはマッハツェンダ変調器として具現可能な光変調器70は、第1位相変調器72、第2位相変調器74、光分離器76、及び光結合器80を含む。

【0032】

位相シフタの機能を行える第1位相変調器72は、第1データストリームによって第1光信号の位相を変調し、該位相変調された第1光信号を第1光導波路78−1に伝送する。第1データストリームは、第1位相変調器72の第1電極72−1に供給される第1電気信号E1と第1位相変調器72の第2電極72−2に供給される第2電気信号E2との差によって発生したデータストリームを意味する。

【0033】

位相シフタの機能を行える第2位相変調器74は、第2入力データストリームによって第2光信号の位相を変調し、該位相変調された第2光信号を第2光導波路78−2に伝送する。第2データストリームは、第2位相変調器74の第1電極74−1に供給される第3電気信号と第2位相変調器74の第2電極74−2に供給される第4電気信号との差によって発生したデータストリームを意味する。

【0034】

光変調器70は、第1データストリームの位相と振幅とを調節するための調節器82をさらに含む。調節器82は、第1データストリームを所定時間またはN(ここで、Nは、実数)ビット遅延させ、第1データストリームの振幅(または、パワー(power))を減衰させることができる。調節器82は、遅延と減衰とを同時に、または順次に行うことができる。調節器82は、遅延を減衰より先に行うか、または後で行うことができる。

【0035】

調節器82は、第1電気信号E1と第2電気信号E2のそれぞれの位相と振幅とを調節し、第3電気信号と第4電気信号のそれぞれを生成することができる。第1電気信号E1は、同じ振幅(または、パワー)を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つは調節器82に入力される。また、第2電気信号E2は、同じ振幅(または、パワー)を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つは調節器82に入力される。

【0036】

光分離器76は、光源73から出力された持続波形を有する光信号を受信し、これを同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器72内に形成された光導波路と第2位相変調器74内に形成された光導波路のそれぞれに伝送する。この際、第1位相変調器72の長さL1は、第2位相変調器74の長さL1と同一である。

【0037】

光結合器80は、第1光導波路78−1を通じて伝送された位相変調された第1光信号と第2光導波路78−2を通じて伝送された位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する。したがって、光変調器70は、電気的ディエンファシス駆動回路より簡単な調節器82を使って、ディエンファシス波形を有する出力光信号を生成することができる効果がある。

【0038】

図3は、本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。図3を参照すると、マッハツェンダ干渉計またはマッハツェンダ変調器として具現可能な光変調器90は、第1位相変調器92、第2位相変調器94、光分離器96、及び光結合器100を含む。

【0039】

位相シフタの機能を行える第1位相変調器92は、第1データストリームによって第1光信号の位相を変調し、該位相変調された第1光信号を第1光導波路98−1に伝送する。第1データストリームは、第1位相変調器92の第1電極92−1に供給される第1電気信号E1と第1位相変調器92の第2電極92−2に供給される第2電気信号E2との差によって発生したデータストリームを意味する。

【0040】

位相シフタの機能を行える第2位相変調器94は、第2入力データストリームによって第2光信号の位相を変調し、該位相変調された第2光信号を第2光導波路98−2に伝送する。第2データストリームは、第2位相変調器94の第1電極94−1に供給される第3電気信号と第2位相変調器94の第2電極94−2に供給される第4電気信号との差によって発生したデータストリームを意味する。

【0041】

光変調器90は、第1データストリームの振幅(または、パワー)を減衰させるための減衰器(attenuator)102をさらに含む。減衰器102は、第1データストリーム振幅を減衰させ、第2データストリームを生成する。例えば、減衰器102は、第1電気信号E1と第2電気信号E2のそれぞれの振幅を減衰させ、第3電気信号と第4電気信号のそれぞれを生成することができる。

【0042】

第1電気信号E1は、同じ振幅を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つは減衰器102に入力される。また、第2電気信号E2は、同じ振幅を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つは減衰器(または、調節器)102に入力される。

【0043】

光分離器96は、光源93から出力された持続波形を有する光信号を受信し、これを同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器92内に形成された光導波路と第2位相変調器94内に形成された光導波路のそれぞれに伝送する。この際、第1位相変調器92の長さL1は、第2位相変調器94の長さL1と同一である。第1位相変調器92によって位相変調された第1光信号は、第1光導波路98−1に沿って光結合器100に伝送され、第2位相変調器92によって位相変調された第2光信号は、第2光導波路98−2に沿って光結合器100に伝送される。

【0044】

図3に示したように、第1光導波路98−1の長さは、第2光導波路98−2の長さより短い。第2光導波路98−2の長さを調節することによって、第2光導波路98−2を通じて伝送される位相変調された第2光信号は、第1光導波路98−1を通じて伝送される位相変調された第1光信号よりNビット遅延されうる。

【0045】

他の実施形態によって、第1光導波路98−1の長さと第2光導波路98−2の長さとが互いに同様に具現される時、光変調器90は、第2光導波路98−2を通じて伝送される位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させるためのビット遅延ユニットをさらに含みうる。

【0046】

光結合器100は、第1光導波路98−1を通じて伝送され、位相変調された第1光信号と、第2光導波路98−2を通じて伝送されながらN(Nは、実数)ビット遅延され、位相変調された第2光信号とを結合して、ディエンファシス波形を変調された出力光信号を生成することができる効果がある。すなわち、光変調器90は、第1データストリームの振幅(または、パワー)を減衰させるための減衰器102と第1光導波路98−1の長さより長い長さを有する第2光導波路98−2とを用いて、ディエンファシス波形を有する変調された出力光信号を生成することができる効果がある。

【0047】

図4は、本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。図4を参照すると、マッハツェンダ干渉計またはマッハツェンダ変調器として具現可能な光変調器110は、第1位相変調器112、第2位相変調器114、光分離器116、及び光結合器120を含む。

【0048】

位相シフタの機能を行える第1位相変調器112は、第1入力データストリームによって第1光信号の位相を変調し、該位相変調された第1光信号を第1光導波路118−1に伝送する。前記第1入力データストリームは、第1位相変調器112の第1電極112−1に供給される第1電気信号E1と第1位相変調器112の第2電極112−1に供給される第2電気信号E2との差によって発生したデータストリームを意味する。

【0049】

位相シフタの機能を行える第2位相変調器114は、第2入力データストリームによって第2光信号の位相を変調し、該位相変調された第2光信号を第2光導波路118−2に伝送する。第2データストリームは、第2位相変調器114の第1電極114−1に供給される第3電気信号と第2位相変調器114の第2電極114−2に供給される第4電気信号との差によって発生したデータストリームを意味する。

【0050】

光変調器110は、第1データストリームの位相をN(Nは、実数)ビット遅延させるためのビット遅延ユニット122をさらに含む。ビット遅延ユニット122は、第1データストリームの位相をN(Nは、実数)ビット遅延させ、第2データストリームを生成する。例えば、ビット遅延ユニット122は、第1電気信号E1と第2電気信号E2のそれぞれの位相をNビット遅延させ、第3電気信号と第4電気信号のそれぞれを生成することができる。

【0051】

第1電気信号E1は、同じ振幅を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つはビット遅延ユニット122に入力される。第2電気信号E2は、同じ振幅を有する2つの信号に分離され、該分離された2つの信号のうちの何れか一つはビット遅延ユニット122に入力される。

【0052】

光分離器116は、光源113から出力された持続波形を有する光信号を受信し、これを同様に2つにパワー分離し、該パワー分離された光信号のそれぞれを第1位相変調器112内に形成された光導波路と第2位相変調器114内に形成された光導波路のそれぞれに伝送する。

【0053】

第2光信号を変調するための第2位相変調器114の長さL2は、第1光信号を変調するための第1位相変調器112の長さL1より短い。位相変調器の長さが短ければ短いほど同じ光信号に対して位相変調(または、位相シフト)の量も少なくなる。したがって、前記光信号に対する減衰が発生する。

【0054】

第1位相変調器112によって位相変調された第1光信号は、第1光導波路118−1を通じて光結合器120に伝送され、第2位相変調器114によって位相変調された第2光信号は、第2光導波路118−2を通じて光結合器120に伝送される。この際、第1光導波路118−1の長さ(より具体的に、第1位相変調器112に形成された光導波路を除いた長さ)と第2光導波路118−2の長さ(より具体的に、第1位相変調器112に形成された光導波路を除いた長さ)は、互いに同一である。

【0055】

光結合器120は、第1光導波路118−1を通じて伝送され、位相変調された第1光信号と第2光導波路118−2を通じて伝送され、位相変調された第2光信号とを結合して、ディエンファシス波形を有する変調された出力光信号を生成する。すなわち、光結合器120は、第1データストリームを遅延させるためのビット遅延ユニット122と第1位相変調器112の長さL1より短い長さL2を有する第2位相変調器114とを用いて、ディエンファシス波形を有する変調された出力光信号を生成することができる効果がある。

【0056】

図5は、本発明のさらに他の実施形態による光変調器の概略的な回路図を示す。図5に示された光変調器30は、ディエンファシス方法を用いて光−電変換を行う。ディエンファシス方法は、ローレベルからハイレベルに遷移するか、またはハイレベルからローレベルに遷移する遷移ビット(transition bit)は、そのまま置き、残りのビットのそれぞれの変調振幅を減らして、変調特性を改善する方法を意味する。

【0057】

図5を参照すると、光変調器30は、第1位相変調器32、第2位相変調器34、光分離器36、及び光結合器38を含む。光分離器36から出力された第1光信号は、第1位相変調器32に供給され、光分離器36から出力された第2光信号は、第2位相変調器34に供給される。

【0058】

第1ディエンファシス信号は、第1位相変調器32の2つの電極32−1、32−2に供給され、第2ディエンファシス信号は、第2位相変調器34の2つの電極34−1、34−2に供給される。第1ディエンファシス信号と第2ディエンファシス信号は、経時的に同期され、第1ディエンファシス信号の位相は、第2ディエンファシス信号の位相と逆である。

【0059】

光結合器38は、第1位相変調器32によって位相変調された第1光信号と第2位相変調器34によって位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を出力する。ディエンファシス方式を使う光変調器30は、変調速度を改善することができる。

【0060】

図6は、図1から図5に示された光変調器のうちの何れか一つを含む本発明の一実施形態によるデータ処理システムのブロック図を示す。図6を参照すると、データ処理システム200は、第1装置210と第2装置220とを含む。第1装置210と第2装置220とは、シリアル通信を通じてディエンファシス波形を光信号で通信することができる。

【0061】

第1装置210は、第1光源212、電−光変換(electrical to optical conversion)動作を行える第1光変調器214、及び光−電変換(optical to electrical conversion)動作を行える第1光復調器(optical de−modulator)216を含む。

【0062】

第1光源212は、持続波形を有する光信号を出力する。第1光源212は、図1から図4に示された光源53、73、93、及び113のうちの何れか一つで具現可能である。第1光変調器214は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。第1光復調器216は、第2装置220の第2光変調器224から出力されたディエンファシス波形を有する出力光信号を受信して復調し、該復調された電気信号を出力する。

【0063】

第2装置220は、第2光源222、第2光変調器224、及び第2光復調器226を含む。第2光源222は、持続波形を有する光信号を出力する。第2光源222は、図1から図4に示された光源53、73、93、及び113のうちの何れか一つで具現可能である。第2光変調器224は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。第2光復調器226は、第1装置210の第1光変調器214から出力されたディエンファシス波形を有する出力光信号を受信して復調し、該復調された電気信号を出力する。

【0064】

図7は、図1から図5に示された光変調器のうちの何れか一つを含む本発明の他の実施形態によるデータ処理システムのブロック図を示す。図7に示されたMOD(E/O)は、電−光変換器として使われる光変調器を意味するものであって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0065】

図7を参照すると、データ処理システム300は、CPU310、複数のデータバス301−1〜301−3、及び複数のメモリモジュール340を含む。複数のメモリモジュール340のそれぞれは、複数のデータバス301−1〜301−3のそれぞれに接続された複数のカプラ311−1、311−2、及び311−3のそれぞれを通じてディエンファシス波形を有する光信号を送受信することができる。実施形態によって、複数のカプラ311−1、311−2、及び311−3のそれぞれは、電気的なカプラ(electrical coupler)または光学的なカプラ(optical coupler)で具現可能である。

【0066】

CPU310は、少なくとも一つの光変調器MOD(E/O)と少なくとも一つの光復調器DEM(O/E)とを含む第1光送受信器316、及びメモリコントローラ312を含む。少なくとも一つの光復調器DEM(O/E)は、光−電変換器として使われる。

【0067】

メモリコントローラ312は、CPU310の制御下で第1光送受信器316の動作、例えば、送信動作または受信動作を制御することができる。例えば、ライト動作時に、第1光送受信器316の第1光変調器MOD(E/O)は、メモリコントローラ312の制御下でアドレスと制御信号とを図2から図6を参照して説明したように、ディエンファシス波形を有する変調された光信号を生成し、該生成された光信号ADD/CTRLを光通信バス301−3に伝送しうる。

【0068】

第1光送受信器316が、光信号ADD/CTRLを光通信バス301−3に伝送した後、第1光送受信器316の第2光変調器MOD(E/O)は、ディエンファシス波形を有する変調された光ライトデータWDATAを生成し、該生成された光ライトデータWDATAを光通信バス301−2に伝送しうる。

【0069】

各メモリモジュール340は、第2光送受信器330及び複数のメモリ装置335を含む。各メモリモジュール340は、光学的DIMM(optical dual in−line memory module)、光学的Fully Buffered DIMM、光学的SO−DIMM(small outline dual in−line memory module)、Optical RDIMM(Registered DIMM)、Optical LRDIMM(Load Reduced DIMM)、UDIMM(Unbuffered DIMM)、光学的MicroDIMM、または光学的SIMM(single in−line memory module)として具現可能である。

【0070】

図7を参照すると、第2光送受信器330に具現された光復調器DEM(O/E)は、光通信バス301−2を通じて入力された光ライトデータWDATAを復調し、該復調された電気信号を複数のメモリ装置335のうちの少なくとも一つのメモリ装置に伝送しうる。

【0071】

実施形態によって、各メモリモジュール340は、光復調器DEM(O/E)から出力された電気信号をバッファリング(buffering)するための電気的なバッファ(buffer)333をさらに含みうる。例えば、電気的なバッファ333は、復調された電気信号をバッファリングし、該バッファリングされた電気信号を複数のメモリ装置335のうちの少なくとも一つのメモリ装置に伝送しうる。

【0072】

複数のメモリ装置335のそれぞれは、複数のメモリセル(memory cells)を含むメモリアレイ(memory array)337、メモリアレイ337にアクセス(access)できるアクセス回路339、及びアクセス回路339の動作を制御することができるコントロールロジック(control ligic;図示せず)を含みうる。

【0073】

リード(read)動作時に、メモリ装置335から出力された電気信号は、第2光送受信器330に具現された光変調器MOD(E/O)によってディエンファシス波形を有する光リードデータ(read data)RDATAに変調される。光リードデータRDATAは、光通信バス301−1を通じてCPU310に具現された第1光復調器DEM(O/E)に伝送される。第1光復調器DEMは、光リードデータRDATAを復調し、該復調された電気信号をメモリコントローラ312に伝送する。

【0074】

図8は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システム(system)のブロック図を示す。

図8に示されたMOD(E/O)は、電−光変換機能を行う光変調器であって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0075】

図8を参照すると、データ伝送システム400は、CPU410、複数のデータバス(data buses)401−1、401−2、及び401−3、及び複数のメモリモジュール(memory module)440を含む。複数のデータバス401−1、401−2、及び401−3のそれぞれは、電気的または光学的に信号を伝送しうる。

複数のメモリモジュール440のそれぞれは、複数のメモリ装置441を含み、複数のメモリ装置441のそれぞれは、第2光送受信器445を含む。

【0076】

また、複数のメモリ装置441のそれぞれは、複数のメモリセルを含むメモリアレイ443、メモリアレイ443にアクセスできるアクセス回路(図示せず)、及びアクセス回路の動作を制御することができるコントロールロジック(図示せず)を含みうる。

データ処理システム400のライト(write)動作が説明される。まず、ライト動作を行うためのアドレス(addresses)と制御信号ADD/CTRLは、対応するデータバス401−3を通じて既に複数のメモリ装置441のうちの少なくとも一つに伝送されたと仮定する。

【0077】

CPU410の第1光送受信器416内の光変調器MOD(E/O)は、メモリコントローラ412の制御下でディエンファシス波形を有する光ライトデータWDATAをデータバス401−2に接続された光学的カプラ411−2を通じて第1メモリモジュール440の第2光送受信器445の光復調器DEM(O/E)に伝送する。

【0078】

第2光送受信器445の光復調器DEM(O/E)は、光ライトデータWDATAを復調し、該復調された電気信号を発生させる。アクセス回路は、コントロールロジックの制御下で、電気信号をメモリアレイ443にライトする。

データ処理システム400のリード動作が説明される。

【0079】

まず、リード動作を行うためのアドレスと制御信号ADD/CTRLとは、対応するデータバス401−3を通じて既に複数のメモリ装置441のうちの何れか一つのメモリ装置に伝送されたと仮定する。メモリ装置441の第2光送受信器445内の光変調器MOD(E/O)は、メモリアレイ443から出力された電気信号を、ディエンファシス波形を有する光リードデータRDATAに変調し、これをデータバス401−1に接続された光学的カプラ411−1を通じてCPU410の第1光送受信器416の復調器DEM(O/E)に伝送する。第1光送受信器416の第1光復調器DEM(O/E)は、光リードデータRDATAを電気信号に復調し、該復調された電気信号をメモリコントローラ412に出力する。

【0080】

図9は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図9を参照すると、データ処理システム500は、第1装置510と第2装置530とを含む。図9に示されたMOD(E/O)は、光変調器を意味するものであって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0081】

第1装置510と第2装置530のそれぞれは、シリアル(serial)通信プロトコル(protocol)を用いてデータを送受信することができる装置を意味する。シリアル通信プロトコルは、その実施形態として、UART(Universal Asynchronous Receiver Transmitter)、SPI(Serial Peripheral Interface)、I2C(Inter−integrated Circuit)、SMBus(System Management Bus)、CAN(Controller Area Network)、USB(Universal Serial Bus)、IC(Inter−chip)−USB、MIPI(登録商標)(mibile industry processor interface)で規定するCSI(camera serial interface)、MIPI(登録商標)で規定するDSI(display serial interface)、MDDI(MobileDisplay Digital Interface)、またはLIN(Local Interconnect Network)を支援するデータ通信プロトコルであり得る。

【0082】

図9を参照すると、第1装置510に具現された第1光送受信512の第1光変調器518は、第1マイクロプロセッサ514の制御下でディエンファシス波形を有する変調された光信号を、データバスを通じて第2装置530の第2光送受信器532の第2光復調器540に伝送する。第2光復調器540は、受信された光信号を電気信号に復調する。第2マイクロプロセッサ(microprocessor)534は、第2光復調器540から出力され、復調された電気信号を処理する。例えば、ライト動作時に、第2マイクロプロセッサ534は、電気信号をメモリアレイにライトすることができる。

【0083】

第2装置530の第2光送受信器532の第2光変調器538は、第2マイクロプロセッサ534の制御下でディエンファシス波形を有する変調された光信号を、データバスを通じて第1装置510の第1光送受信器512の第1光復調器520に伝送する。第1光復調器520は、受信された光信号を電気信号に復調する。

【0084】

第1マイクロプロセッサ514は、第1光復調器520から出力され、復調された電気信号を処理する。例えば、リード動作時に、第1マイクロプロセッサ514は、電気信号をリードデータとして処理することができる。各マイクロプロセッサ514、534は、その名称にもかかわらず、各装置510、530の動作、例えば、ライト動作またはリード動作を制御することができるプロセッサを意味する。

【0085】

図10は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図10を参照すると、SPI(serial peripheral interface)通信プロトコルを使って、シリアルデータを送受信することができるデータ処理システム700は、SPIマスタ(master)710と少なくとも一つのSPIスレーブ(slave)720、730、740、及び750を含む。

【0086】

図10に示されたMOD(E/O)は、光変調器を意味するものであって、光変調器MOD(E/O)は、図2から図6に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0087】

複数のSPIスレーブ720、730、740、及び750のうちの何れか一つは、シフトレジスタ(shift register)、メモリチップ(memory chip)、ポート拡張器(port expander)、ディスプレイドライバ(displaydriver)、データ変換器(data converter)、プリンタ(printer)、データ保存装置(data storage)、センサ(sensor)、またはマイクロプロセッサであり得る。

【0088】

第1光送受信器712と各第2光送受信器722、732、742、または752は、対応する光学的データバスを通じてディエンファシス波形を有する光信号(MOSI(Master Out Slave In)またはMISO(Master In Slave Out)を送受信することができる。SPIマスタ710は、第1光送受信器712の動作を制御することができるマイクロプロセッサ(図示せず)を含み、複数のSPIスレーブ720、730、740、及び750のそれぞれは、第2光送受信器722、732、742、または750の動作を制御することができるマイクロプロセッサ(図示せず)を含む。

【0089】

また、第1光送受信器712は、シリアルクロック信号CLKを電気的なデータバスまたは光学的データバスを通じて各第2光送受信器722、732、742、または752に伝送しうる。各SPIスレーブ720、730、740、及び750は、各チップ選択信号SS0、SS1、SS2、及びSS3によって選択されうる。この場合、各チップ選択信号SS0、SS1、SS2、及びSS3は、電気的なデータバスまたは光学的データバスを通じて各第2光送受信器722、732、742、または752に伝送することができる。

【0090】

図11は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。SATA(Serial Advanced Technology Attachment)通信プロトコルを使って、シリアルデータを送受信することができるデータ処理システム800は、SATAホスト810とSATA装置830とを含む。図11に示されたMOD(E/O)は、光変調器を意味するものであって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0091】

SATAホスト810は、ホストCPU811、データバス813、メモリ815、DMAコントローラ817、及び第1SATAインタフェース819を含む。ホストCPU811は、DMAコントローラ(direct memory access controller)817または第1SATAインタフェース819の動作を制御する。第1SATAインタフェース819は、第1光変調器MOD(E/O)と第1光復調器DEM(O/E)とを含む。

【0092】

SATAホスト810は、第1SATAインタフェース819の動作を制御することができるコントローラを含みうる。実施形態によって、コントローラは、第1SATAインタフェース819の内部に具現されることもあり、ホストCPU811が、コントローラの機能を行える。SATA装置830は、ハードディスクコントローラ840とメモリ装置850、及び磁気的記録媒体860を含む。ハードディスクコントローラ840は、MCU(main control unit)841、データバス843、第2SATAインタフェース845、バッファ847、及びディスクコントローラ849を含む。

【0093】

MCU841は、第2SATAインタフェース845、バッファ847、及びディスクコントローラ849のうちの少なくとも一つの動作を制御する。

第2SATAインタフェース845は、第2光変調器MOD(O/E)と第2光復調器DEM(E/O)とを含む。SATA装置830は、第2SATAインタフェース845の動作を制御することができるコントローラを含みうる。実施形態によって、コントローラは、第2SATAインタフェース845の内部に具現されることもあり、MCU841が、コントローラの機能を行える。

【0094】

ライト動作時に、メモリ815に保存されたライトデータは、DMAコントローラ817の制御下で第1SATAインタフェース819の第1光変調器MOD(E/O)に伝送される。

【0095】

第1光変調器MOD(E/O)は、ライトデータによってディエンファシス波形を有する光ライトデータを生成し、該生成された光ライトデータを、データバスを通じて第2SATAインタフェース845の第2光復調器DEM(O/E)に伝送する。第2光復調器DEM(E/O)は、光ライトデータを電気信号に復調することができる。バッファ847は、電気信号をバッファリングし、該バッファされた電気信号をメモリ装置850に一時的に保存する。

【0096】

ディスクコントローラ(disk controller)849は、メモリ装置850に保存された電気信号をリードして、ライトアドレスによって指定された磁気的記録媒体860、例えば、ディスク(disk)にライトする。

リード動作時に、ディスクコントローラ849は、リードアドレスによって指定された磁気的記録媒体860からデータをリードし、該リードされたデータを、バッファ847を通じてメモリ装置850に保存する。

【0097】

第2SATAインタフェース845の第2変調器MOD(E/O)は、バッファ847を通じてメモリ装置850からデータによってディエンファシス波形を有する光リードデータを生成し、該生成された光リードデータを、データバスを通じて第1SATAインタフェース819の第1光復調器DEM(O/E)に伝送する。第2光復調器DEM(O/E)は、受信された光リードデータを電気信号に復調する。DMAコントローラ817は、第2光復調器DEM(O/E)によって復調された電気信号をメモリ815に保存する。

【0098】

図12は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。USB(Universal Serial Bus)通信プロトコルまたはIC−USB通信プロトコルを使って、シリアルデータを送受信することができるデータ処理システム900は、USBホスト910とUSB装置920とを含む。図12に示されたMOD(E/O)は、光変調器を意味するものであって、光変調器MOD(E/O)は、図1から図5に示された光変調器50、70、90、110、及び30のうちの何れか一つで具現可能である。

【0099】

USBホスト910の第1光送受信器912の第1光変調器MOD(E/O)によって生成されたディエンファシス波形を有する光信号は、データバス900−1を通じてUSB装置920の第2光送受信器914の第2光復調器DEM(O/E)に伝送され、USB装置920の第2光復調器DEM(O/E)は、受信された光信号を復調して電気信号を生成する。

【0100】

USBホスト910は、第1光送受信器912の動作を制御することができるマイクロコントローラ(図示せず)をさらに含みうる。

USB装置920の第2光送受信器914の第2変調器MOD(E/O)によって生成されたディエンファシス波形を有する光信号は、データバス900−2を通じてUSBホスト910の第1光送受信器912の第1復調器DEM(O/E)に伝送され、USBホスト910の第1光復調器DEM(O/E)は、受信された光信号を復調して電気信号を生成する。

【0101】

USB装置920は、第1光送受信器912の動作を制御することができるマイクロコントローラ(図示せず)をさらに含みうる。

【0102】

図13は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図13に示されたSoC(system on chip)1000は、複数のマスタ1010、1020、複数のスレーブ1030、1040、及び複数のバス1001を含む。複数のマスタ1010、1020のそれぞれと複数のスレーブ1030、1040のそれぞれは、光変調器MOD(E/O)と光復調器DEM(O/E)とを含む。複数のバス1001のそれぞれは、光導波路として具現可能である。

【0103】

各光変調器MOD(E/O)によって変調された光信号は、それぞれが光導波路として具現された複数のバス1001のうち対応するバスを通じて各光復調器DEM(O/E)に伝送され、各光復調器DEM(O/E)は、受信された光信号を復調して電気信号を発生させる。

【0104】

図14は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図14に示されたデータ処理システム1100は、複数のレイヤ(layers)1110、1120を含む積層構造で形成される。

【0105】

第1レイヤ1110は、第1光送受信器1111と第1光送受信器1111の動作を制御することができる第1データプロセッシング(data processing)回路1113とを含む。

【0106】

第1光送受信器1111の第1光変調器MOD(E/O)は、ディエンファシス波形を有する光信号を光伝送手段、例えば、光導波路、TSV(through siliconvia)、または光纎維を通じて第2レイヤ1120の第2光復調器DEM(O/E)に伝送する。第2光復調器DEM(O/E)によって復調された電気信号は、第2データプロセッシング回路1123によって処理される。

【0107】

第2光送受信器1121の第2光変調器MOD(E/O)は、ディエンファシス波形を有する光信号を光伝送手段、例えば、光導波路、TSV、または光纎維を通じて第1レイヤ1110の第1光復調器DEM(O/E)に伝送する。第1光復調器DEM(O/E)によって復調された電気信号は、第1データプロセッシング回路1113によって処理される。

【0108】

図15は、図1から図5に示された光変調器のうちの何れか一つを含む本発明のさらに他の実施形態によるデータ処理システムのブロック図を示す。図15に示されたデータ処理システム1200は、MIPI(登録商標)(Mobile Industry Processor Interface)を使用または支援することができるデータ処理装置、例えば、携帯電話機(mobile phone)、スマートフォン(smart phone)、PDA(personal digital assistant)、PMP(portable media player)、または移動通信装置として具現可能である。

【0109】

データ処理システム1200は、アプリケーションプロセッサ1210、イメージセンサ1240、及びディスプレイ1250を含む。アプリケーションプロセッサ1210に具現されたCSIホスト1220は、カメラシリアルインタフェース(cameraserial interface、CSI)を通じてイメージセンサ1240のCSI装置1241とシリアル通信することができる。例えば、CSIホスト1220には、光復調器DEMが具現され、CSI装置1241の光変調器MODは、図2から図6に示された光変調器50、70、90、110、及び30のうちの何れか一つが具現可能である。

【0110】

アプリケーションプロセッサ1210に具現されたDSIホスト1230は、ディスプレイシリアルインタフェース(display serial interface、DSI)を通じてディスプレイ1250のDSI装置1251とシリアル通信することができる。例えば、DSIホスト1230の光変調器MODは、図2から図6に示された光変調器50、70、90、110、及び30のうちの何れか一つが具現可能である。

【0111】

データ処理システム1200は、アプリケーションプロセッサ1210と通信することができるRFチップ1260をさらに含みうる。データ処理システム1200のPHYとRFチップ1260のPHYは、MIPI DigRFによってデータを送受信することができる。データ処理システム1200は、ストレージ1270、マイク1280、及びスピーカ1290のうちの少なくとも一つをさらに含みうる。

【0112】

本明細書に使われた電気信号は、直列電気信号または並列電気信号を意味し、また電気信号は、直列データまたは並列データを意味する。

本発明は、図面に示された一実施形態を参考にして説明されたが、これは例示的なものに過ぎず、当業者ならば、これより多様な変形及び均等な他実施形態が可能であるという点を理解できるであろう。したがって、本発明の真の技術的保護範囲は、特許請求の範囲の技術的思想によって決定されるべきである。

【産業上の利用可能性】

【0113】

本発明は、光変調器に使われる。

【符号の説明】

【0114】

50:光変調器

52:第1位相変調器

54:第2位相変調器

58−1:第1光導波路

58−2:第2光導波路

82:調節器

102:減衰器

122:ビット遅延ユニット

【特許請求の範囲】

【請求項1】

第1位相変調器によって位相変調された第1光信号を伝送するための第1光導波路と、

前記第1位相変調器の長さより短い長さを有する第2位相変調器によって位相変調された第2光信号を伝送するための第2光導波路と、を含み、

前記第2光導波路の長さは、前記第1光導波路の長さより長いことを特徴とする光変調器。

【請求項2】

前記第2光導波路の長さは、前記位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させるための長さだけ前記第1光導波路の長さより長いことを特徴とする請求項1に記載の光変調器。

【請求項3】

前記第1位相変調器と前記第2位相変調器のそれぞれは、同じ入力データストリームによって、前記位相変調された第1光信号と前記位相変調された第2光信号のそれぞれを生成することを特徴とする請求項1に記載の光変調器。

【請求項4】

前記光変調器は、前記位相変調された第1光信号と前記位相変調された第2光信号とを結合して、ディエンファシス(de−emphasis)波形を有する出力光信号を生成するための光結合器(optical coupler)をさらに含むことを特徴とする請求項1に記載の光変調器。

【請求項5】

前記光変調器は、

持続波形(continuous waveform)を有する光信号を出力するための光源と、

前記光信号を同様に2つにパワー分離(power−splitting)し、パワー分離された前記光信号のそれぞれを前記第1位相変調器と前記第2位相変調器のそれぞれに出力するための光分離器と、

をさらに含むことを特徴とする請求項1に記載の光変調器。

【請求項6】

第1データストリームによって位相変調された第1光信号を生成するための第1位相変調器と、

前記第1データストリームの位相と振幅とを調節するための調節器と、

前記調節器から出力された第2データストリームによって位相変調された第2光信号を生成するための第2位相変調器と、

を含むことを特徴とする光変調器。

【請求項7】

前記調節器は、前記第1データストリームをN(ここで、Nは、実数)ビット遅延させ、前記第2データストリームを生成することを特徴とする請求項6に記載の光変調器。

【請求項8】

前記光変調器は、前記位相変調された第1光信号と前記位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成するための光結合器をさらに含むことを特徴とする請求項6に記載の光変調器。

【請求項9】

第1位相変調器によって位相変調された第1光信号を、第1光導波路を通じて伝送する段階と、

前記第1位相変調器の長さより短い長さを有する第2位相変調器によって位相変調された第2光信号を、第2光導波路を通じて伝送する段階と、

前記位相変調された第1光信号と前記位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、

を含むことを特徴とする光変調器の光変調信号生成方法。

【請求項10】

前記第2光導波路の長さは、前記第1光導波路の長さより長いことを特徴とする請求項9に記載の光変調器の光変調信号生成方法。

【請求項11】

第1位相変調器を用いて第1データストリームによって位相変調された第1光信号を生成する段階と、

前記第1データストリームの位相と振幅とを調節して第2データストリームを生成する段階と、

第2位相変調器を用いて前記第2データストリームによって位相変調された第2光信号を生成する段階と、

前記位相変調された第1光信号と前記位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、

を含むことを特徴とする光変調器の光変調信号生成方法。

【請求項12】

前記第2データストリームを生成する段階は、前記第1データストリームをN(ここで、Nは、実数)ビット遅延させ、前記第2データストリームを生成することを特徴とする請求項11に記載の光変調器の光変調信号生成方法。

【請求項1】

第1位相変調器によって位相変調された第1光信号を伝送するための第1光導波路と、

前記第1位相変調器の長さより短い長さを有する第2位相変調器によって位相変調された第2光信号を伝送するための第2光導波路と、を含み、

前記第2光導波路の長さは、前記第1光導波路の長さより長いことを特徴とする光変調器。

【請求項2】

前記第2光導波路の長さは、前記位相変調された第2光信号をN(ここで、Nは、実数)ビット遅延させるための長さだけ前記第1光導波路の長さより長いことを特徴とする請求項1に記載の光変調器。

【請求項3】

前記第1位相変調器と前記第2位相変調器のそれぞれは、同じ入力データストリームによって、前記位相変調された第1光信号と前記位相変調された第2光信号のそれぞれを生成することを特徴とする請求項1に記載の光変調器。

【請求項4】

前記光変調器は、前記位相変調された第1光信号と前記位相変調された第2光信号とを結合して、ディエンファシス(de−emphasis)波形を有する出力光信号を生成するための光結合器(optical coupler)をさらに含むことを特徴とする請求項1に記載の光変調器。

【請求項5】

前記光変調器は、

持続波形(continuous waveform)を有する光信号を出力するための光源と、

前記光信号を同様に2つにパワー分離(power−splitting)し、パワー分離された前記光信号のそれぞれを前記第1位相変調器と前記第2位相変調器のそれぞれに出力するための光分離器と、

をさらに含むことを特徴とする請求項1に記載の光変調器。

【請求項6】

第1データストリームによって位相変調された第1光信号を生成するための第1位相変調器と、

前記第1データストリームの位相と振幅とを調節するための調節器と、

前記調節器から出力された第2データストリームによって位相変調された第2光信号を生成するための第2位相変調器と、

を含むことを特徴とする光変調器。

【請求項7】

前記調節器は、前記第1データストリームをN(ここで、Nは、実数)ビット遅延させ、前記第2データストリームを生成することを特徴とする請求項6に記載の光変調器。

【請求項8】

前記光変調器は、前記位相変調された第1光信号と前記位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成するための光結合器をさらに含むことを特徴とする請求項6に記載の光変調器。

【請求項9】

第1位相変調器によって位相変調された第1光信号を、第1光導波路を通じて伝送する段階と、

前記第1位相変調器の長さより短い長さを有する第2位相変調器によって位相変調された第2光信号を、第2光導波路を通じて伝送する段階と、

前記位相変調された第1光信号と前記位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、

を含むことを特徴とする光変調器の光変調信号生成方法。

【請求項10】

前記第2光導波路の長さは、前記第1光導波路の長さより長いことを特徴とする請求項9に記載の光変調器の光変調信号生成方法。

【請求項11】

第1位相変調器を用いて第1データストリームによって位相変調された第1光信号を生成する段階と、

前記第1データストリームの位相と振幅とを調節して第2データストリームを生成する段階と、

第2位相変調器を用いて前記第2データストリームによって位相変調された第2光信号を生成する段階と、

前記位相変調された第1光信号と前記位相変調された第2光信号とを結合して、ディエンファシス波形を有する出力光信号を生成する段階と、

を含むことを特徴とする光変調器の光変調信号生成方法。

【請求項12】

前記第2データストリームを生成する段階は、前記第1データストリームをN(ここで、Nは、実数)ビット遅延させ、前記第2データストリームを生成することを特徴とする請求項11に記載の光変調器の光変調信号生成方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2012−63768(P2012−63768A)

【公開日】平成24年3月29日(2012.3.29)

【国際特許分類】

【出願番号】特願2011−200785(P2011−200785)

【出願日】平成23年9月14日(2011.9.14)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】416,Maetan−dong,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成24年3月29日(2012.3.29)

【国際特許分類】

【出願日】平成23年9月14日(2011.9.14)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】416,Maetan−dong,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]