光書込み装置、画像形成装置及び光書込み装置の制御方法

【課題】アドレス変換テーブルを設けることにより異なる種類のLEDAに対応可能な光書込み装置の装置構成を効率化する。

【解決手段】形成すべき画像を構成する画素の情報である画素情報を取得する速度変換部121と、画素情報の配列を変換する配列変換SRAM122と、感光体を露光する光源に応じた画素情報の配列の変換態様を示すアドレス変換テーブルを取得して記憶するリードアドレス発生メモリ124と、画素情報の配列の変換を制御するためのライトアドレス信号を生成して出力するデコータ125とを含み、前記リードアドレス発生メモリ124は、同時にアクセス可能な複数の記憶領域に分割されており、アドレス変換テーブルを複数の記憶領域に分割して記憶する。

【解決手段】形成すべき画像を構成する画素の情報である画素情報を取得する速度変換部121と、画素情報の配列を変換する配列変換SRAM122と、感光体を露光する光源に応じた画素情報の配列の変換態様を示すアドレス変換テーブルを取得して記憶するリードアドレス発生メモリ124と、画素情報の配列の変換を制御するためのライトアドレス信号を生成して出力するデコータ125とを含み、前記リードアドレス発生メモリ124は、同時にアクセス可能な複数の記憶領域に分割されており、アドレス変換テーブルを複数の記憶領域に分割して記憶する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光書込み装置、画像形成装置及び光書込み装置の制御方法に関し、特に、画像形成出力する対象の画像を構成する画素の配列変換に関する。

【背景技術】

【0002】

近年、情報の電子化が推進される傾向にあり、電子化された情報の出力に用いられるプリンタやファクシミリ及び書類の電子化に用いるスキャナ等の画像処理装置は欠かせない機器となっている。このような画像処理装置は、撮像機能、画像形成機能及び通信機能等を備えることにより、プリンタ、ファクシミリ、スキャナ、複写機として利用可能な複合機として構成されることが多い。

【0003】

このような画像処理装置のうち、電子化された書類の出力に用いられる画像形成装置においては、電子写真方式の画像形成装置が広く用いられている。電子写真方式の画像形成装置においては、感光体を露光することにより静電潜像を形成し、トナー等の顕色剤を用いてその静電潜像を現像してトナー画像を形成し、そのトナー画像を用紙に転写することによって紙出力を行う。

【0004】

電子写真方式の画像形成装置において、感光体を露光する光書込み装置にはLD(Laser Diode)ラスター光学系方式とLED(Light Emitting Diode)書込み方式とがある。LED書込み方式の場合、LEDA(LED Array)ヘッドを含む。

【0005】

LED書込み方式の光書込み装置においては、上述したようにLEDAによって感光体ドラムを露光することにより静電潜像を形成する。そして、LEDAに含まれるLED素子の点灯/消灯は、画像形成出力する対象の画像に応じて制御される。そのため、LEDAを制御する制御部は、画像形成出力する対象の画像の情報に基づいて各LED素子の点灯/消灯を示す画素情報が生成されると、生成された画素情報における画素の並び順をLEDAのドライバの構成に応じて変換し、変換後の並び順に従ってLEDAを発光制御する(例えば、特許文献1参照)。

【発明の概要】

【発明が解決しようとする課題】

【0006】

このような技術の例として、画素情報を一時的に格納するためのSRAM(Static Random Access Memory)と、SRAMに格納された画素情報を配列変換して読み出すためのリードアドレスカウンタ生成のための複数のカウンタから成る画像書込み制御部を用いることが考えられる。

【0007】

しかしながら、この場合、複数のカウンタをドライバ回路に含むため、回路規模が大きくなり、コスト高となってしまう。また、このようなLED書込み方式の光書込み装置は、画像形成装置のコントローラによって生成された画素情報に対して上述したような配列変換等の処理を行う制御装置と、LEDAとが組み合わせられて構成される。そして、画素情報の配列変換ルールは接続されるLEDAによって異なるため、異なるLEDAが用いられる装置を設計する度に、制御装置も設計し直す必要があり、設計負荷がかかるという問題もある。

【0008】

このような課題に対して、接続されるLEDAの配列変換ルールを示す情報(以降、アドレス変換テーブルとする)を記憶媒体に格納し、その情報に基づいて画素情報の配列変換を行うことにより、異なる種類のLEDAに対応可能とすることが考えられる。このような構成により、アドレス変換テーブルを書き換えることで、同一のLEDAの制御回路で様々な種類のLEDAに対応することが可能となる。

【0009】

ここで、フルカラー等の複数色の出力に対応した電子写真方式の画像形成装置は、夫々の色に対応した複数のLEDAを含む。上述したような複数のLEDAを含む画像形成装置の場合、夫々のLEDAにおける画素情報の配列変換ルールが同一であれば、アドレス変換テーブルも共通化することにより、記憶媒体の記憶容量の削減や回路規模の削減を図ることが好ましい。

【0010】

ここで、夫々のLEDAが露光する各色の感光体ドラムの副走査方向の位置が異なるため、感光体ドラム上に現像された各色のトナー像を重ね合わせるため、夫々のLEDAの点灯タイミングは異なることが一般的である。そして、夫々のLEDAの点灯タイミングが異なるため、夫々のLEDAに供給する配列変換の信号も異なることとなる。その結果、同一の配列変換ルールを適用するLEDAであっても、夫々別個にアドレス変換テーブルを設けることとなり、非効率な構成となってしまう。

【0011】

本発明は、上記実情を考慮してなされたものであり、アドレス変換テーブルを設けることにより異なる種類のLEDAに対応可能な光書込み装置の装置構成を効率化することを目的とする。

【課題を解決するための手段】

【0012】

上記課題を解決するために、本発明の一態様は、感光体上に静電潜像を形成する光書込み装置であって、前記静電潜像として形成すべき画像を構成する画素の情報である画素情報を取得する画素情報取得部と、前記取得された画素情報の配列を変換する配列変換部と、前記感光体を露光する光源に応じた前記画素情報の配列の変換態様を示す配列変換情報を取得して記憶する配列変換情報記憶部と、前記記憶された配列変換情報に基づき、前記配列変換部による画素情報の配列の変換を制御するための配列変換制御信号を生成して出力する制御信号出力部とを含み、前記配列変換情報記憶部の記憶領域は、同時にアクセス可能な複数の記憶領域に分割されており、前記配列変換情報を前記複数の記憶領域に分割して記憶することを特徴とする。

【0013】

また、本発明の他の態様は、画像形成装置であって、上記光書込み装置を含むことを特徴とする。

【0014】

また、本発明の更に他の態様は、感光体上に静電潜像を形成する光書込み装置の制御方法であって、前記静電潜像として形成すべき画像を構成する画素の情報である画素情報を取得し、前記感光体を露光する光源に応じた前記画素情報の配列の変換態様を示す配列変換情報を取得して、同時にアクセス可能な複数の記憶領域に分割された記憶媒体における複数の記憶領域に分割して記憶し、前記分割して記憶された夫々の配列変換情報に基づき、前記画素情報の配列の変換を制御するための配列変換制御信号を生成して出力し、前記配列変換制御信号に応じて、前記取得された画素情報の配列を変換し、前記変換された画素情報に従って前記感光体を露光する光源を発光させることを特徴とする。

【発明の効果】

【0015】

本発明によれば、アドレス変換テーブルを設けることにより異なる種類のLEDAに対応可能な光書込み装置の装置構成を効率化することができる。

【図面の簡単な説明】

【0016】

【図1】本発明の実施形態に係る画像形成装置のハードウェア構成を示すブロック図である。

【図2】本発明の実施形態に係る画像形成装置の機能構成を示す図である。

【図3】本発明の実施形態に係るプリントエンジンの構成を示す図である。

【図4】本発明の実施形態に係る光書込み装置の構成を模式的に示す図である。

【図5】本発明の実施形態に係る光書込み装置の制御部を示すブロック図である。

【図6】本発明の実施形態に係るリードアドレス発生メモリにロードされるアドレス変換テーブルの例を示す図である。

【図7】本発明の実施形態に係るリードアドレス発生メモリに格納されたアドレス変換テーブルのデコータによる読み出し態様を示す図である。

【図8】本発明の他の実施形態に係るLEDAの構成を模式的に示す図である。

【図9】本発明の実施形態に係る一のLEDAの発光タイミングを示すタイミングチャートである。

【図10】本発明の実施形態に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【図11】本発明の実施形態に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【図12】比較例に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【図13】本発明の実施形態に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【図14】本発明の実施形態に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【発明を実施するための形態】

【0017】

以下、図面を参照して、本発明の実施形態を詳細に説明する。本実施形態においては、画像形成装置としての複合機(MFP:Multi Function Peripheral)を例として説明する。尚、画像形成装置は複合機でなくとも良く、例えば、複写機、プリンタ、ファクシミリ装置等であっても良い。

【0018】

図1は、本実施形態に係る画像形成装置1のハードウェア構成を示すブロック図である。図1に示すように、本実施形態に係る画像形成装置1は、一般的なサーバやPC(Personal Computer)等の情報処理端末と同様の構成に加えて、画像形成を実行するエンジンを有する。即ち、本実施形態に係る画像形成装置1は、CPU(Central Processing Unit)10、RAM(Random Access Memory)11、ROM(Read Only Memory)12、エンジン13、HDD(Hard Disk Drive)14及びI/F15がバス18を介して接続されている。また、I/F15にはLCD(Liquid Crystal Display)16及び操作部17が接続されている。

【0019】

CPU10は演算手段であり、画像形成装置1全体の動作を制御する。RAM11は、情報の高速な読み書きが可能な揮発性の記憶媒体であり、CPU10が情報を処理する際の作業領域として用いられる。ROM12は、読み出し専用の不揮発性記憶媒体であり、ファームウェア等のプログラムが格納されている。エンジン13は、画像形成装置1において実際に画像形成を実行する機構である。

【0020】

HDD14は、情報の読み書きが可能な不揮発性の記憶媒体であり、OS(Operating System)や各種の制御プログラム、アプリケーション・プログラム等が格納されている。I/F15は、バス18と各種のハードウェアやネットワーク等を接続し制御する。LCD16は、ユーザが画像形成装置1の状態を確認するための視覚的ユーザインタフェースである。操作部17は、キーボードやマウス等、ユーザが画像形成装置1に情報を入力するためのユーザインタフェースである。

【0021】

このようなハードウェア構成において、ROM12やHDD14若しくは図示しない光学ディスク等の記録媒体に格納されたプログラムがRAM11に読み出され、CPU10がそれらのプログラムに従って演算を行うことにより、ソフトウェア制御部が構成される。このようにして構成されたソフトウェア制御部と、ハードウェアとの組み合わせによって、本実施形態に係る画像形成装置1の機能を実現する機能ブロックが構成される。

【0022】

次に、図2を参照して、本実施形態に係る画像形成装置1の機能構成について説明する。図2は、本実施形態に係る画像形成装置1の機能構成を示すブロック図である。図2に示すように、本実施形態に係る画像形成装置1は、コントローラ20、ADF(Auto Documennt Feeder:原稿自動搬送装置)21、スキャナユニット22、排紙トレイ23、ディスプレイパネル24、給紙テーブル25、プリントエンジン26、排紙トレイ27及びネットワークI/F28を有する。

【0023】

また、コントローラ20は、主制御部30、エンジン制御部31、入出力制御部32、画像処理部33及び操作表示制御部34を有する。図2に示すように、本実施形態に係る画像形成装置1は、スキャナユニット22、プリントエンジン26を有する複合機として構成されている。尚、図2においては、電気的接続を実線の矢印で示しており、用紙の流れを破線の矢印で示している。

【0024】

ディスプレイパネル24は、画像形成装置1の状態を視覚的に表示する出力インタフェースであると共に、タッチパネルとしてユーザが画像形成装置1を直接操作し若しくは画像形成装置1に対して情報を入力する際の入力インタフェース(操作部)でもある。ネットワークI/F28は、画像形成装置1がネットワークを介して他の機器と通信するためのインタフェースであり、Ethernet(登録商標)やUSB(Universal Serial Bus)インタフェースが用いられる。

【0025】

コントローラ20は、ソフトウェアとハードウェアとの組み合わせによって構成される。具体的には、ROM12や不揮発性メモリ並びにHDD14や光学ディスク等の不揮発性記録媒体に格納されたファームウェア等の制御プログラムが、RAM11等の揮発性メモリ(以下、メモリ)にロードされ、CPU10の制御に従って構成されるソフトウェア制御部と集積回路などのハードウェアとによってコントローラ20が構成される。コントローラ20は、画像形成装置1全体を制御する制御部として機能する。

【0026】

主制御部30は、コントローラ20に含まれる各部を制御する役割を担い、コントローラ20の各部に命令を与える。エンジン制御部31は、プリントエンジン26やスキャナユニット22等を制御若しくは駆動する駆動手段としての役割を担う。入出力制御部32は、ネットワークI/F28を介して入力される信号や命令を主制御部30に入力する。また、主制御部30は、入出力制御部32を制御し、ネットワークI/F28を介して他の機器にアクセスする。

【0027】

画像処理部33は、主制御部30の制御に従い、入力された印刷ジョブに含まれる印刷情報に基づいて描画情報を生成する。この描画情報とは、画像形成部であるプリントエンジン26が画像形成動作において形成すべき画像を描画するための情報であり、出力するべき画像を構成する画素の情報、即ち画素情報である。また、印刷ジョブに含まれる印刷情報とは、PC等の情報処理装置にインストールされたプリンタドライバによって画像形成装置1が認識可能な形式に変換された画像情報である。操作表示制御部34は、ディスプレイパネル24に情報表示を行い若しくはディスプレイパネル24を介して入力された情報を主制御部30に通知する。

【0028】

画像形成装置1がプリンタとして動作する場合は、まず、入出力制御部32がネットワークI/F28を介して印刷ジョブを受信する。入出力制御部32は、受信した印刷ジョブを主制御部30に転送する。主制御部30は、印刷ジョブを受信すると、画像処理部33を制御して、印刷ジョブに含まれる印刷情報に基づいて描画情報を生成させる。

【0029】

画像処理部33によって描画情報が生成されると、エンジン制御部31は、生成された描画情報に基づき、給紙テーブル25から搬送される用紙に対して画像形成を実行する。即ち、プリントエンジン26が画像形成部として機能する。プリントエンジン26によって画像形成が施された用紙は排紙トレイ27に排紙される。

【0030】

次に、本実施形態に係るプリントエンジン26の構成について、図3を参照して説明する。図3に示すように、本実施形態に係るプリントエンジン26は、無端状移動手段である搬送ベルト105に沿って各色の画像形成部106が並べられた構成を備えるものであり、所謂タンデムタイプといわれるものである。すなわち、給紙トレイ101から給紙ローラ102と分離ローラ103とにより分離給紙される用紙(記録媒体の一例)104に転写するための中間転写画像が形成される中間転写ベルトである搬送ベルト105に沿って、この搬送ベルト105の搬送方向の上流側から順に、複数の画像形成部(電子写真プロセス部)106BK、106M、106C、106Yが配列されている。

【0031】

これら複数の画像形成部106BK、106M、106C、106Yは、形成するトナー画像の色が異なるだけで内部構成は共通である。画像形成部106BKはブラックの画像を、画像形成部106Mはマゼンタの画像を、画像形成部106Cはシアンの画像を、画像形成部106Yはイエローの画像をそれぞれ形成する。尚、以下の説明においては、画像形成部106BKについて具体的に説明するが、他の画像形成部106M、106C、106Yは画像形成部106BKと同様であるので、その画像形成部106M、106C、106Yの各構成要素については、画像形成部106BKの各構成要素に付したBKに替えて、M、C、Yによって区別した符号を図に表示するにとどめ、説明を省略する。

【0032】

搬送ベルト105は、回転駆動される駆動ローラ107と従動ローラ108とに架け渡されたエンドレスのベルト、即ち無端状ベルトである。この駆動ローラ107は、不図示の駆動モータにより回転駆動させられ、この駆動モータと、駆動ローラ107と、従動ローラ108とが、無端状移動手段である搬送ベルト105を移動させる駆動手段として機能する。

【0033】

画像形成に際しては、回転駆動される搬送ベルト105に対して、最初の画像形成部106BKが、ブラックのトナー画像を転写する。画像形成部106BKは、感光体としての感光体ドラム109BK、この感光体ドラム109BKの周囲に配置された帯電器110BK、光書込み装置200、現像器112BK、感光体クリーナ(図示せず)、除電器113BK等から構成されている。光書込み装置200は、夫々の感光体ドラム109BK、109M、109C、109Y(以降、総じて「感光体ドラム109」という)に対して光を照射するように構成されている。

【0034】

画像形成に際し、感光体ドラム109BKの外周面は、暗中にて帯電器110BKにより一様に帯電された後、光書込み装置200からのブラック画像に対応した光源からの光により書込みが行われ、静電潜像が形成される。現像器112BKは、この静電潜像をブラックトナーにより可視像化し、このことにより感光体ドラム109BK上にブラックのトナー画像が形成される。

【0035】

このトナー画像は、感光体ドラム109BKと搬送ベルト105とが当接若しくは最も接近する位置(転写位置)で、転写器115BKの働きにより搬送ベルト105上に転写される。この転写により、搬送ベルト105上にブラックのトナーによる画像が形成される。トナー画像の転写が終了した感光体ドラム109BKは、外周面に残留した不要なトナーを感光体クリーナにより払拭された後、除電器113BKにより除電され、次の画像形成のために待機する。

【0036】

以上のようにして、画像形成部106BKにより搬送ベルト105上に転写されたブラックのトナー画像は、搬送ベルト105のローラ駆動により次の画像形成部106Mに搬送される。画像形成部106Mでは、画像形成部106BKでの画像形成プロセスと同様のプロセスにより感光体ドラム109M上にマゼンタのトナー画像が形成され、そのトナー画像が既に形成されたブラックの画像に重畳されて転写される。

【0037】

搬送ベルト105上に転写されたブラック、マゼンタのトナー画像は、さらに次の画像形成部106C、106Yに搬送され、同様の動作により、感光体ドラム109C上に形成されたシアンのトナー画像と、感光体ドラム109Y上に形成されたイエローのトナー画像とが、既に転写されている画像上に重畳されて転写される。こうして、搬送ベルト105上にフルカラーの中間転写画像が形成される。

【0038】

給紙トレイ101に収納された用紙104は最も上のものから順に送り出され、その搬送経路が搬送ベルト105と接触する位置若しくは最も接近する位置において、搬送ベルト105上に形成された中間転写画像がその紙面上に転写される。これにより、用紙104の紙面上に画像が形成される。紙面上に画像が形成された用紙104は更に搬送され、定着器116にて画像を定着された後、画像形成装置の外部に排紙される。

【0039】

次に、本実施形態に係る光書込み装置111について説明する。図4は、本実施形態に係る光書込み装置111と感光体ドラム109との配置関係を示す図である。図4に示すように、各色の感光体ドラム109BK、109M、109C、109Y夫々に照射される照射光は、光源であるLEDA(LED Array)130BK、130M、130C、130Y(以降、総じてLEDA112とする)から照射される。

【0040】

LEDA130は、発光素子であるLEDが、感光体ドラム109の主走査方向に並べられて構成されている。光書込み装置111に含まれる制御部は、主走査方向に並べられている夫々のLEDの点灯/消灯状態を、コントローラ20から入力された描画情報に基づいて主走査ライン毎に制御することにより、感光体ドラム109の表面を選択的に露光し、静電潜像を形成する。

【0041】

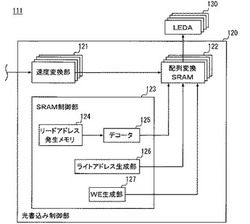

次に、本実施形態に係る光書込み装置111の制御ブロックについて、図5を参照して説明する。図5は、本実施形態に係る光書込み装置111を制御する光書込み制御部120の機能構成及びLEDA130との接続関係を示す図である。

【0042】

図5に示すように、本実施形態に係る光書込み制御部120は、速度変換部121、配列変換SRAM(Static Random Access Memory)122、SRAM制御部123を含む。また、SRAM制御部123は、リードアドレス発生メモリ124、デコータ125、ライトアドレス発生部126、WE(Write Enable)生成部127を含む。

【0043】

尚、プリントエンジン26は、図1において説明した画像形成装置1本体と同様に、CPU10や、RAM11並びにROM12等の記憶媒体といった情報処理機構を含み、画像形成装置1のコントローラ20と同様に、ROM12等の記憶媒体に記憶されている制御プログラムがRAM11にロードされ、CPU10がそのプログラムに従って演算を行うことにより構成されるソフトウェア制御部と、ハードウェアとの組み合わせによって構成される。

【0044】

そして、図5に示す光書込み装置111は、上述したように構成されるプリントエンジン26の制御部によって制御される。図4において説明したように、LEDA130は、感光体ドラム109の各色に対応して設けられる。従って、光書込み制御部120においては、速度変換部121及び配列変換SRAM122も各色に対応して設けられる。

【0045】

速度変換部121は、コントローラ20から所定の周波数で画素毎に入力される画素情報の周波数を変換して配列変換SRAM122に格納する。本実施形態においては、配列変換SRAM122への画素情報の格納をライト動作として説明する。即ち、速度変換部121が、コントローラ20から入力される画素情報を取得して配列変換SRAM122に格納する画素情報取得部として機能する。

【0046】

配列変換SRAM122は、速度変換部121によって格納された画素情報を、SRAM制御部123の制御に従って配列を変換してLEDA130に入力する。即ち、配列変換SRAM122が、配列変換部として機能する。本実施形態においては、配列変換SRAM122からLEDA130への画素情報の入力をリード動作として説明する。

【0047】

SRAM制御部123は、配列変換SRAM122の動作を制御する制御回路であり、上記ライド動作におけるライトタイミング及び画素情報を格納するライトアドレスを制御すると共に、上記リード動作において読み出す画素情報の配列の変換を制御する機能を有する。

【0048】

リードアドレス発生メモリ124は、上記リード動作における画素情報の配列の変換ルールが記述されたアドレス変換テーブルを記憶する不揮発性の記憶媒体である。リードアドレス発生メモリ124には、プリントエンジン26のCPU10によってアドレス変換テーブルがロードされる。即ち、リードアドレス発生メモリ124が、画素情報の配列変換態様を示す配列変換情報を取得して記憶する配列変換情報記憶部である。

【0049】

図6は、本実施形態に係るアドレス変換テーブルの例を示す図である。図6に示すように、本実施形態に係るアドレス変換テーブルにおいては、LEDA130に入力する画素の順番を示す“画素番号”と、それぞれの順番において読み出す画素が格納されているアドレスを示す“読出しアドレス”とが関連付けて格納されている。

【0050】

図6に示すようなアドレス変換テーブルは、図1に示す構成と同様の情報処理機構によって構成されるプリントエンジン26の制御部において、ROM12やHDD14等の不揮発性の記憶媒体に格納されており、プリントエンジン26の起動に応じて、CPU10の制御に従ってリードアドレス発生メモリ124にロードされる。

【0051】

ここで、LEDA130は、複数のLED素子が一方向に並べられて集積されたチップが、更に複数組み合わせられて1ラインの全範囲をカバー可能な主走査方向のサイズが構成される。これに応じて、図6に示すように、アドレス変換テーブルにおいては、夫々のチップ毎に“画素番号”と“読出しアドレス”とが関連付けられて格納されている。

【0052】

デコータ125は、リードアドレス発生メモリ124に格納されたアドレス変換テーブルの情報を、配列変換SRAM122の配列変換制御のためのリードアドレス信号に変換して配列変換SRAM122に入力する。即ち、デコータ125は、リードアドレス発生メモリ124に格納されたアドレス変換テーブルに従い、配列変換SRAM122による配列変換を制御するための配列変換制御信号を出力する制御信号出力部として機能する。

【0053】

本実施形態に係る配列変換SRAM122は、LEDA130に画素情報を入力する際に画素情報を読み出すアドレスを、図6に示すようなアドレス変換テーブルの情報に従って決定することにより、画素情報の配列変換を実行する。換言すると、配列変換SRAM122は、記憶した画素情報を読み出す順番を、デコータ125が出力する制御信号であるリードアドレス信号に従って変えることにより、配列変換を実行する。

【0054】

ライトアドレス生成部126は、速度変換部121から配列変換SRAM122に入力される画素情報を格納するアドレスを指定するためのライトアドレス信号を出力する。本実施形態に係るライト動作においては、特に配列変換に関する処理は実行されず、速度変換部121から入力される画素情報は配列変換SRAM122におけるアドレスの順番に従って格納される。

【0055】

WE生成部127は、速度変換部121から入力される画素情報を配列変換SRAM122に格納するタイミングを制御するためのライトイネーブル信号を出力する。配列変換SRAM122は、WE生成部127から入力されるライトイネーブル信号に応じて、ライドアドレス生成部126から入力されるライトアドレス信号に従ったアドレスに画素情報を格納する。

【0056】

このような画像書込み制御部120の構成によれば、リードアドレス発生メモリ124に格納するアドレス変換テーブを変更することにより、同一の光書込み制御部120によって異なる種類のLEDA130に対応することが可能となる。

【0057】

ここで、異なる種類のLEDA130とは、例えばA4用、A3用等のサイズの異なるLEDAである。サイズが異なれば、主走査方向の画素数が異なり、その結果画素の配列変換ルールも当然異なることとなる。また、本実施形態に係る画像形成装置1のようにタンデムタイプのプリントエンジン26を含む場合、各色毎に配列変換ルールが異なる場合もあり得る。

【0058】

本実施形態に係る光書込み装置111によれば、リードアドレス発生メモリ124に格納されるアドレス変換テーブルをソフトウェアによって書き換えることが可能であるため、上述したような異なる種類のLEDA130に対して、光書込み制御部120を再設計することなく容易に対応可能であり、簡易な構成により、異なる種類のLEDAに対応可能な光書込み装置を実現することができる。

【0059】

ここで、本実施形態に係る要旨は、デコータ125によるリードアドレス発生メモリ124からのアドレス変換テーブルの読み出しと、夫々の配列変換SRAM122へのリードアドレス信号の入力の具体的な態様にある。以下、本実施形態の要旨に係る処理について説明する。

【0060】

図7は、本実施形態に係る要旨、即ち、デコータ125によるリードアドレス発生メモリ124からのアドレス変換テーブルの読み出しと、夫々の配列変換SRAM122へのリードアドレス信号の入力の具体的な態様を示すブロック図である。図7においては、各色のLEDA130に対応する夫々の配列変換SRAM122を、配列変換SRAM122BK、122M、122C、122Yとして夫々示している。

【0061】

図7に示すように、リードアドレス発生メモリ124においては、記憶領域が分割されており、夫々の記憶領域には、“テーブル1”〜“テーブル4”の4つに分割されたアドレス変換テーブルが夫々格納されている。この分割されたアドレス変換テーブルは、例えば、図6に示すチップ毎のテーブルである。

【0062】

デコータ125は、リードアドレス発生メモリ124において分割された夫々の領域(以降、分割領域とする)に対して、同時にアクセスすることが可能である。換言すると、本実施形態に係るリードアドレス発生メモリ124は、同時にアクセス可能な複数の記憶領域に分割されており、分割された夫々の記憶領域にアドレス変換テーブルを分割して記憶する。

【0063】

即ち、配列変換SRAM122BKに対しては、テーブル1をデコードして生成したリードアドレス信号を出力しつつ、配列変換SRAM122Mに対しては、テーブル2をデコードして生成したリードアドレス信号を出力することが可能である。これにより、1つのアドレス変換テーブルによって複数のLEDA130の制御に対応可能とすることが本実施形態に係る要旨である。

【0064】

次に、本実施形態に係る光書込み制御部120によるLEDA130の制御態様について説明する。図8は、本実施形態に係るLEDA130の構成を模式的に示す図である。図8に示すように、本実施形態に係るLEDA130は、複数のLEDチップ130a〜130dが主走査方向に連結されて組み合わされることにより構成されている。

【0065】

また、本実施形態に係るLEDA130においては、夫々のLEDチップ130a〜130dは、図8に示すように副走査方向にずらされて配置されている。そのため、夫々のチップの発光タイミングが異なる。図9に、1つのLEDA130についての発光タイミング及びリードアドレス発生メモリ124からの各テーブルの読み出しタイミングを示す。

【0066】

図9において“hsync”は水平同期信号であり、主走査ライン毎のタイミングの基準を示す信号である。図8に示すLEDチップ130a〜130dをチップ1〜チップ4とすると、図9に示すように、hsyncの立ち上がりに応じて、チップ1〜チップ4が順番に発光する。

【0067】

そして、デコータ125は、LEDA130の発光タイミングに合わせて配列変換SRAM122にリードアドレス信号を入力する。そのため、夫々のチップに対応するテーブル1〜テーブル4の読み出しタイミングも、図9において“メモリリード”として示すように、夫々のチップの発光タイミングに応じたタイミングとなる。即ち、デコータ125は、それぞれのLEDA130を1ライン分発光させるために、図7に示すテーブル1〜テーブル4を順番に読出し、1つの配列変換SRAM122に対して順番にリードアドレス信号を出力する。

【0068】

次に、本実施形態に係る要旨となる制御の制御タイミングについて図10を参照して説明する。図10は、4つのLEDA130BK〜130Yの発光タイミングに応じたアドレス変換テーブルのメモリリードのタイミングを示すタイミングチャートである。

【0069】

図10に示すように、4つのLEDA130BK〜130Y夫々の発光タイミングは、“hsync_BK”、“hsync_M”、“hsync_C”、“hsync_Y”の4つのタイミングの異なる水平同期信号によって制御される。4つのLEDA130夫々の発光タイミングは、図4に示すように副走査方向に順番に配置されている感光体ドラム109において現像されたトナー像が重ね合わせられるように、搬送ベルト105の搬送速度に応じてずらされている。また、4つのLEDA130夫々の発光タイミングは、光書込み装置111の組み付け誤差や感光体ドラム109の組み付け誤差等によって生じる微小なタイミングのずれも吸収するように調整されている。

【0070】

そして、図7において説明したように、本実施形態に係るリードアドレス発生メモリ124は、夫々の領域に対して並列してアクセスが可能なように記憶領域が分割されているため、デコーダ125は、夫々の分割領域に格納されているテーブルに対して並列してアクセスし、夫々のテーブルに基づいて生成したリードアドレス信号を夫々異なる配列変換SRAM122に入力する。

【0071】

例えば、LEDA130BKの発光制御タイミングは、図10に示す“hsync_BK”によって制御される。LEDA130BKのチップ4の発光タイミングにおいて、デコータ125は、テーブル4に基づいて生成したリードアドレス信号を配列変換SRAM122BKに入力している。それと並行して、デコータ125は、テーブル3に基づいて生成したリードアドレス信号を配列変換SRAM122Mに、テーブル2に基づいて生成したリードアドレス信号を配列変換SRAM122Cに、テーブル1に基づいて生成したリードアドレス信号を配列変換SRAM122Yに、夫々入力している。

【0072】

図11は、LEDA130が、LEDA130BKとLEDA130Yとの2つの場合の例を示す図である。図11の例の場合、リードアドレス発生メモリ124の記憶領域は2つの分割領域に分割されており、夫々の分割領域に“テーブル1”、“テーブル2”として分割されたアドレス変換テーブルが格納されている。この場合、図11に示すように、配列変換SRAM122BKに対してテーブル2に基づいて生成されたリードアドレス信号が出力されている間に、配列変換SRAM122Yに対してテーブル1に基づいて生成されたリードアドレス信号が出力されるような制御が可能となる。

【0073】

図12は、本実施形態に係る比較例として、リードアドレス発生用メモリ124が、夫々並行してアクセス可能な分割領域に分割されていない場合の例を示す図である。この例の場合、“hsync_BK”に応じて、配列変換SRAM122BKにリードアドレス信号を入力するためにリードアドレス発生メモリ124にアクセスしている場合、そのリードアドレス発生メモリに対する他のアクセスが不可能である。

【0074】

そのため、図12にメモリ1〜4として示すように、配列変換SRAM122BKにリードアドレス信号を入力するためのアドレス変換テーブルが格納されたメモリとは別のメモリを用意し、“hsync_M”、“hsync_C”、“hsync_Y”に対応したリードアドレス信号を生成するためのアドレス変換テーブルを格納しておく必要がある。その結果、アドレス変換テーブルの容量が4倍となり、装置構成の非効率化や回路規模の大型化を招く。本実施形態によれば、このような課題を解決することが可能となる。

【0075】

以上説明したように、本実施形態に係る光書込み制御部120を含む画像形成装置1においては、1つのアドレス変換テーブルのみで、複数のLEDA130の発光を制御するためのリードアドレス信号を生成して出力することが可能となり、アドレス変換テーブルを設けることにより異なる種類のLEDAに対応可能な光書込み装置の装置構成を効率化することが可能となる。

【0076】

尚、上記実施形態においては、図10に示すように、4つのLEDA130の発光タイミングがすべて異なる場合を例として説明した。ここで、上述したように、“hsync_BK”、“hsync_M”、“hsync_C”、“hsync_Y”の4つの水平同期信号は、4つの感光体ドラム109の副走査方向の位置及び搬送ベルト105の搬送スピードに加えて、製造公差をも考慮してタイミングが調整されている。

【0077】

従って、製造公差によるタイミングの調整量によっては、異なるLEDA130に対応する水平同期信号のタイミングが一致する可能性がある。その場合、デコータ125は、図13に示すように、異なるLEDA130であっても同一のタイミングで同一のテーブルに基づいて生成したリードアドレス信号を入力する。図13の例の場合、デコータ125は、リードアドレス発生メモリ124から読み出したテーブルに基づいて生成したリードアドレス信号を配列変換SRAM122BK及び配列変換SRAM122Cに入力する。

【0078】

また、水平同期信号のタイミングが完全に一致しない場合であっても、夫々のチップ毎の発光期間との比較において一致しているとみなせる程度の微小な期間のずれであれば、一致しているとみなしてメモリリードのタイミングを制御しても良い。図14は、そのような場合の例を示す図である。図14に示すように、水平同期信号のずれが、同一であるとみなすことができる期間の閾値T以下であれば、図13の例と同様に、デコータ125は同一のタイミングで同一のテーブルに基づいて生成したリードアドレス信号を入力する。

【0079】

図14に示すように、水平同期信号のタイミングが一致しているとみなして、2つの配列変換SRAM122に対して同一のタイミングでリードアドレス信号を入力した場合、一方のLEDA130(図14の例の場合、LEDA130C)の発光タイミングが、水平同期信号のズレ量の分ずれることとなる。従って、図14に示す閾値Tは、一方のLEDA130の発光タイミングのずれの許容値という意味合いを持つ。

【0080】

この閾値Tの値の例としては、例えば、副走査方向の一画素分のずれ量に相当する期間である。このずれ量は、画像の大きさに応じて、十画素分のずれ量に相当する期間等に定めることもできる。このように閾値Tを定めることにより、LEDA130の制御構成の効率化を保ちつつ、形成される画像の画質をも保つことができる。

【符号の説明】

【0081】

1 画像形成装置

10 CPU

11 RAM

12 ROM

13 エンジン

14 HDD

15 I/F

16 LCD

17 操作部

18 バス

20 コントローラ

21 ADF

22 スキャナユニット

23 排紙トレイ

24 ディスプレイパネル

25 給紙テーブル

26 プリントエンジン

27 排紙トレイ

28 ネットワークI/F

30 主制御部

31 エンジン制御部

32 入出力制御部

33 画像処理部

34 操作表示制御部

101 給紙トレイ

102 給紙ローラ

103 分離ローラ

104 用紙

105 搬送ベルト

106BK、106C、106M、106Y 画像形成部

107 駆動ローラ

108 従動ローラ

109BK、109C、109M、109Y 感光体ドラム

110BK 帯電器

111光書込み装置

112BK、112C、112M、112Y 現像器

113BK、113C、113M、113Y 除電器

115BK、115C、115M、115Y 転写器

116 定着器

120 光書込み制御部

121 速度変換部

122 配列変換SRAM

123 SRAM制御部

124 リードアドレス発生メモリ

125 デコータ

126 ライトアドレス生成部

127 WE生成部

130、130BK、130M、130C、130Y LEDA

130a、130b、130c、130d LEDチップ

【先行技術文献】

【特許文献】

【0082】

【特許文献1】特開2008−070469号公報

【技術分野】

【0001】

本発明は、光書込み装置、画像形成装置及び光書込み装置の制御方法に関し、特に、画像形成出力する対象の画像を構成する画素の配列変換に関する。

【背景技術】

【0002】

近年、情報の電子化が推進される傾向にあり、電子化された情報の出力に用いられるプリンタやファクシミリ及び書類の電子化に用いるスキャナ等の画像処理装置は欠かせない機器となっている。このような画像処理装置は、撮像機能、画像形成機能及び通信機能等を備えることにより、プリンタ、ファクシミリ、スキャナ、複写機として利用可能な複合機として構成されることが多い。

【0003】

このような画像処理装置のうち、電子化された書類の出力に用いられる画像形成装置においては、電子写真方式の画像形成装置が広く用いられている。電子写真方式の画像形成装置においては、感光体を露光することにより静電潜像を形成し、トナー等の顕色剤を用いてその静電潜像を現像してトナー画像を形成し、そのトナー画像を用紙に転写することによって紙出力を行う。

【0004】

電子写真方式の画像形成装置において、感光体を露光する光書込み装置にはLD(Laser Diode)ラスター光学系方式とLED(Light Emitting Diode)書込み方式とがある。LED書込み方式の場合、LEDA(LED Array)ヘッドを含む。

【0005】

LED書込み方式の光書込み装置においては、上述したようにLEDAによって感光体ドラムを露光することにより静電潜像を形成する。そして、LEDAに含まれるLED素子の点灯/消灯は、画像形成出力する対象の画像に応じて制御される。そのため、LEDAを制御する制御部は、画像形成出力する対象の画像の情報に基づいて各LED素子の点灯/消灯を示す画素情報が生成されると、生成された画素情報における画素の並び順をLEDAのドライバの構成に応じて変換し、変換後の並び順に従ってLEDAを発光制御する(例えば、特許文献1参照)。

【発明の概要】

【発明が解決しようとする課題】

【0006】

このような技術の例として、画素情報を一時的に格納するためのSRAM(Static Random Access Memory)と、SRAMに格納された画素情報を配列変換して読み出すためのリードアドレスカウンタ生成のための複数のカウンタから成る画像書込み制御部を用いることが考えられる。

【0007】

しかしながら、この場合、複数のカウンタをドライバ回路に含むため、回路規模が大きくなり、コスト高となってしまう。また、このようなLED書込み方式の光書込み装置は、画像形成装置のコントローラによって生成された画素情報に対して上述したような配列変換等の処理を行う制御装置と、LEDAとが組み合わせられて構成される。そして、画素情報の配列変換ルールは接続されるLEDAによって異なるため、異なるLEDAが用いられる装置を設計する度に、制御装置も設計し直す必要があり、設計負荷がかかるという問題もある。

【0008】

このような課題に対して、接続されるLEDAの配列変換ルールを示す情報(以降、アドレス変換テーブルとする)を記憶媒体に格納し、その情報に基づいて画素情報の配列変換を行うことにより、異なる種類のLEDAに対応可能とすることが考えられる。このような構成により、アドレス変換テーブルを書き換えることで、同一のLEDAの制御回路で様々な種類のLEDAに対応することが可能となる。

【0009】

ここで、フルカラー等の複数色の出力に対応した電子写真方式の画像形成装置は、夫々の色に対応した複数のLEDAを含む。上述したような複数のLEDAを含む画像形成装置の場合、夫々のLEDAにおける画素情報の配列変換ルールが同一であれば、アドレス変換テーブルも共通化することにより、記憶媒体の記憶容量の削減や回路規模の削減を図ることが好ましい。

【0010】

ここで、夫々のLEDAが露光する各色の感光体ドラムの副走査方向の位置が異なるため、感光体ドラム上に現像された各色のトナー像を重ね合わせるため、夫々のLEDAの点灯タイミングは異なることが一般的である。そして、夫々のLEDAの点灯タイミングが異なるため、夫々のLEDAに供給する配列変換の信号も異なることとなる。その結果、同一の配列変換ルールを適用するLEDAであっても、夫々別個にアドレス変換テーブルを設けることとなり、非効率な構成となってしまう。

【0011】

本発明は、上記実情を考慮してなされたものであり、アドレス変換テーブルを設けることにより異なる種類のLEDAに対応可能な光書込み装置の装置構成を効率化することを目的とする。

【課題を解決するための手段】

【0012】

上記課題を解決するために、本発明の一態様は、感光体上に静電潜像を形成する光書込み装置であって、前記静電潜像として形成すべき画像を構成する画素の情報である画素情報を取得する画素情報取得部と、前記取得された画素情報の配列を変換する配列変換部と、前記感光体を露光する光源に応じた前記画素情報の配列の変換態様を示す配列変換情報を取得して記憶する配列変換情報記憶部と、前記記憶された配列変換情報に基づき、前記配列変換部による画素情報の配列の変換を制御するための配列変換制御信号を生成して出力する制御信号出力部とを含み、前記配列変換情報記憶部の記憶領域は、同時にアクセス可能な複数の記憶領域に分割されており、前記配列変換情報を前記複数の記憶領域に分割して記憶することを特徴とする。

【0013】

また、本発明の他の態様は、画像形成装置であって、上記光書込み装置を含むことを特徴とする。

【0014】

また、本発明の更に他の態様は、感光体上に静電潜像を形成する光書込み装置の制御方法であって、前記静電潜像として形成すべき画像を構成する画素の情報である画素情報を取得し、前記感光体を露光する光源に応じた前記画素情報の配列の変換態様を示す配列変換情報を取得して、同時にアクセス可能な複数の記憶領域に分割された記憶媒体における複数の記憶領域に分割して記憶し、前記分割して記憶された夫々の配列変換情報に基づき、前記画素情報の配列の変換を制御するための配列変換制御信号を生成して出力し、前記配列変換制御信号に応じて、前記取得された画素情報の配列を変換し、前記変換された画素情報に従って前記感光体を露光する光源を発光させることを特徴とする。

【発明の効果】

【0015】

本発明によれば、アドレス変換テーブルを設けることにより異なる種類のLEDAに対応可能な光書込み装置の装置構成を効率化することができる。

【図面の簡単な説明】

【0016】

【図1】本発明の実施形態に係る画像形成装置のハードウェア構成を示すブロック図である。

【図2】本発明の実施形態に係る画像形成装置の機能構成を示す図である。

【図3】本発明の実施形態に係るプリントエンジンの構成を示す図である。

【図4】本発明の実施形態に係る光書込み装置の構成を模式的に示す図である。

【図5】本発明の実施形態に係る光書込み装置の制御部を示すブロック図である。

【図6】本発明の実施形態に係るリードアドレス発生メモリにロードされるアドレス変換テーブルの例を示す図である。

【図7】本発明の実施形態に係るリードアドレス発生メモリに格納されたアドレス変換テーブルのデコータによる読み出し態様を示す図である。

【図8】本発明の他の実施形態に係るLEDAの構成を模式的に示す図である。

【図9】本発明の実施形態に係る一のLEDAの発光タイミングを示すタイミングチャートである。

【図10】本発明の実施形態に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【図11】本発明の実施形態に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【図12】比較例に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【図13】本発明の実施形態に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【図14】本発明の実施形態に係る複数のLEDAのアドレス変換テーブルのリードタイミングを示すタイミングチャートである。

【発明を実施するための形態】

【0017】

以下、図面を参照して、本発明の実施形態を詳細に説明する。本実施形態においては、画像形成装置としての複合機(MFP:Multi Function Peripheral)を例として説明する。尚、画像形成装置は複合機でなくとも良く、例えば、複写機、プリンタ、ファクシミリ装置等であっても良い。

【0018】

図1は、本実施形態に係る画像形成装置1のハードウェア構成を示すブロック図である。図1に示すように、本実施形態に係る画像形成装置1は、一般的なサーバやPC(Personal Computer)等の情報処理端末と同様の構成に加えて、画像形成を実行するエンジンを有する。即ち、本実施形態に係る画像形成装置1は、CPU(Central Processing Unit)10、RAM(Random Access Memory)11、ROM(Read Only Memory)12、エンジン13、HDD(Hard Disk Drive)14及びI/F15がバス18を介して接続されている。また、I/F15にはLCD(Liquid Crystal Display)16及び操作部17が接続されている。

【0019】

CPU10は演算手段であり、画像形成装置1全体の動作を制御する。RAM11は、情報の高速な読み書きが可能な揮発性の記憶媒体であり、CPU10が情報を処理する際の作業領域として用いられる。ROM12は、読み出し専用の不揮発性記憶媒体であり、ファームウェア等のプログラムが格納されている。エンジン13は、画像形成装置1において実際に画像形成を実行する機構である。

【0020】

HDD14は、情報の読み書きが可能な不揮発性の記憶媒体であり、OS(Operating System)や各種の制御プログラム、アプリケーション・プログラム等が格納されている。I/F15は、バス18と各種のハードウェアやネットワーク等を接続し制御する。LCD16は、ユーザが画像形成装置1の状態を確認するための視覚的ユーザインタフェースである。操作部17は、キーボードやマウス等、ユーザが画像形成装置1に情報を入力するためのユーザインタフェースである。

【0021】

このようなハードウェア構成において、ROM12やHDD14若しくは図示しない光学ディスク等の記録媒体に格納されたプログラムがRAM11に読み出され、CPU10がそれらのプログラムに従って演算を行うことにより、ソフトウェア制御部が構成される。このようにして構成されたソフトウェア制御部と、ハードウェアとの組み合わせによって、本実施形態に係る画像形成装置1の機能を実現する機能ブロックが構成される。

【0022】

次に、図2を参照して、本実施形態に係る画像形成装置1の機能構成について説明する。図2は、本実施形態に係る画像形成装置1の機能構成を示すブロック図である。図2に示すように、本実施形態に係る画像形成装置1は、コントローラ20、ADF(Auto Documennt Feeder:原稿自動搬送装置)21、スキャナユニット22、排紙トレイ23、ディスプレイパネル24、給紙テーブル25、プリントエンジン26、排紙トレイ27及びネットワークI/F28を有する。

【0023】

また、コントローラ20は、主制御部30、エンジン制御部31、入出力制御部32、画像処理部33及び操作表示制御部34を有する。図2に示すように、本実施形態に係る画像形成装置1は、スキャナユニット22、プリントエンジン26を有する複合機として構成されている。尚、図2においては、電気的接続を実線の矢印で示しており、用紙の流れを破線の矢印で示している。

【0024】

ディスプレイパネル24は、画像形成装置1の状態を視覚的に表示する出力インタフェースであると共に、タッチパネルとしてユーザが画像形成装置1を直接操作し若しくは画像形成装置1に対して情報を入力する際の入力インタフェース(操作部)でもある。ネットワークI/F28は、画像形成装置1がネットワークを介して他の機器と通信するためのインタフェースであり、Ethernet(登録商標)やUSB(Universal Serial Bus)インタフェースが用いられる。

【0025】

コントローラ20は、ソフトウェアとハードウェアとの組み合わせによって構成される。具体的には、ROM12や不揮発性メモリ並びにHDD14や光学ディスク等の不揮発性記録媒体に格納されたファームウェア等の制御プログラムが、RAM11等の揮発性メモリ(以下、メモリ)にロードされ、CPU10の制御に従って構成されるソフトウェア制御部と集積回路などのハードウェアとによってコントローラ20が構成される。コントローラ20は、画像形成装置1全体を制御する制御部として機能する。

【0026】

主制御部30は、コントローラ20に含まれる各部を制御する役割を担い、コントローラ20の各部に命令を与える。エンジン制御部31は、プリントエンジン26やスキャナユニット22等を制御若しくは駆動する駆動手段としての役割を担う。入出力制御部32は、ネットワークI/F28を介して入力される信号や命令を主制御部30に入力する。また、主制御部30は、入出力制御部32を制御し、ネットワークI/F28を介して他の機器にアクセスする。

【0027】

画像処理部33は、主制御部30の制御に従い、入力された印刷ジョブに含まれる印刷情報に基づいて描画情報を生成する。この描画情報とは、画像形成部であるプリントエンジン26が画像形成動作において形成すべき画像を描画するための情報であり、出力するべき画像を構成する画素の情報、即ち画素情報である。また、印刷ジョブに含まれる印刷情報とは、PC等の情報処理装置にインストールされたプリンタドライバによって画像形成装置1が認識可能な形式に変換された画像情報である。操作表示制御部34は、ディスプレイパネル24に情報表示を行い若しくはディスプレイパネル24を介して入力された情報を主制御部30に通知する。

【0028】

画像形成装置1がプリンタとして動作する場合は、まず、入出力制御部32がネットワークI/F28を介して印刷ジョブを受信する。入出力制御部32は、受信した印刷ジョブを主制御部30に転送する。主制御部30は、印刷ジョブを受信すると、画像処理部33を制御して、印刷ジョブに含まれる印刷情報に基づいて描画情報を生成させる。

【0029】

画像処理部33によって描画情報が生成されると、エンジン制御部31は、生成された描画情報に基づき、給紙テーブル25から搬送される用紙に対して画像形成を実行する。即ち、プリントエンジン26が画像形成部として機能する。プリントエンジン26によって画像形成が施された用紙は排紙トレイ27に排紙される。

【0030】

次に、本実施形態に係るプリントエンジン26の構成について、図3を参照して説明する。図3に示すように、本実施形態に係るプリントエンジン26は、無端状移動手段である搬送ベルト105に沿って各色の画像形成部106が並べられた構成を備えるものであり、所謂タンデムタイプといわれるものである。すなわち、給紙トレイ101から給紙ローラ102と分離ローラ103とにより分離給紙される用紙(記録媒体の一例)104に転写するための中間転写画像が形成される中間転写ベルトである搬送ベルト105に沿って、この搬送ベルト105の搬送方向の上流側から順に、複数の画像形成部(電子写真プロセス部)106BK、106M、106C、106Yが配列されている。

【0031】

これら複数の画像形成部106BK、106M、106C、106Yは、形成するトナー画像の色が異なるだけで内部構成は共通である。画像形成部106BKはブラックの画像を、画像形成部106Mはマゼンタの画像を、画像形成部106Cはシアンの画像を、画像形成部106Yはイエローの画像をそれぞれ形成する。尚、以下の説明においては、画像形成部106BKについて具体的に説明するが、他の画像形成部106M、106C、106Yは画像形成部106BKと同様であるので、その画像形成部106M、106C、106Yの各構成要素については、画像形成部106BKの各構成要素に付したBKに替えて、M、C、Yによって区別した符号を図に表示するにとどめ、説明を省略する。

【0032】

搬送ベルト105は、回転駆動される駆動ローラ107と従動ローラ108とに架け渡されたエンドレスのベルト、即ち無端状ベルトである。この駆動ローラ107は、不図示の駆動モータにより回転駆動させられ、この駆動モータと、駆動ローラ107と、従動ローラ108とが、無端状移動手段である搬送ベルト105を移動させる駆動手段として機能する。

【0033】

画像形成に際しては、回転駆動される搬送ベルト105に対して、最初の画像形成部106BKが、ブラックのトナー画像を転写する。画像形成部106BKは、感光体としての感光体ドラム109BK、この感光体ドラム109BKの周囲に配置された帯電器110BK、光書込み装置200、現像器112BK、感光体クリーナ(図示せず)、除電器113BK等から構成されている。光書込み装置200は、夫々の感光体ドラム109BK、109M、109C、109Y(以降、総じて「感光体ドラム109」という)に対して光を照射するように構成されている。

【0034】

画像形成に際し、感光体ドラム109BKの外周面は、暗中にて帯電器110BKにより一様に帯電された後、光書込み装置200からのブラック画像に対応した光源からの光により書込みが行われ、静電潜像が形成される。現像器112BKは、この静電潜像をブラックトナーにより可視像化し、このことにより感光体ドラム109BK上にブラックのトナー画像が形成される。

【0035】

このトナー画像は、感光体ドラム109BKと搬送ベルト105とが当接若しくは最も接近する位置(転写位置)で、転写器115BKの働きにより搬送ベルト105上に転写される。この転写により、搬送ベルト105上にブラックのトナーによる画像が形成される。トナー画像の転写が終了した感光体ドラム109BKは、外周面に残留した不要なトナーを感光体クリーナにより払拭された後、除電器113BKにより除電され、次の画像形成のために待機する。

【0036】

以上のようにして、画像形成部106BKにより搬送ベルト105上に転写されたブラックのトナー画像は、搬送ベルト105のローラ駆動により次の画像形成部106Mに搬送される。画像形成部106Mでは、画像形成部106BKでの画像形成プロセスと同様のプロセスにより感光体ドラム109M上にマゼンタのトナー画像が形成され、そのトナー画像が既に形成されたブラックの画像に重畳されて転写される。

【0037】

搬送ベルト105上に転写されたブラック、マゼンタのトナー画像は、さらに次の画像形成部106C、106Yに搬送され、同様の動作により、感光体ドラム109C上に形成されたシアンのトナー画像と、感光体ドラム109Y上に形成されたイエローのトナー画像とが、既に転写されている画像上に重畳されて転写される。こうして、搬送ベルト105上にフルカラーの中間転写画像が形成される。

【0038】

給紙トレイ101に収納された用紙104は最も上のものから順に送り出され、その搬送経路が搬送ベルト105と接触する位置若しくは最も接近する位置において、搬送ベルト105上に形成された中間転写画像がその紙面上に転写される。これにより、用紙104の紙面上に画像が形成される。紙面上に画像が形成された用紙104は更に搬送され、定着器116にて画像を定着された後、画像形成装置の外部に排紙される。

【0039】

次に、本実施形態に係る光書込み装置111について説明する。図4は、本実施形態に係る光書込み装置111と感光体ドラム109との配置関係を示す図である。図4に示すように、各色の感光体ドラム109BK、109M、109C、109Y夫々に照射される照射光は、光源であるLEDA(LED Array)130BK、130M、130C、130Y(以降、総じてLEDA112とする)から照射される。

【0040】

LEDA130は、発光素子であるLEDが、感光体ドラム109の主走査方向に並べられて構成されている。光書込み装置111に含まれる制御部は、主走査方向に並べられている夫々のLEDの点灯/消灯状態を、コントローラ20から入力された描画情報に基づいて主走査ライン毎に制御することにより、感光体ドラム109の表面を選択的に露光し、静電潜像を形成する。

【0041】

次に、本実施形態に係る光書込み装置111の制御ブロックについて、図5を参照して説明する。図5は、本実施形態に係る光書込み装置111を制御する光書込み制御部120の機能構成及びLEDA130との接続関係を示す図である。

【0042】

図5に示すように、本実施形態に係る光書込み制御部120は、速度変換部121、配列変換SRAM(Static Random Access Memory)122、SRAM制御部123を含む。また、SRAM制御部123は、リードアドレス発生メモリ124、デコータ125、ライトアドレス発生部126、WE(Write Enable)生成部127を含む。

【0043】

尚、プリントエンジン26は、図1において説明した画像形成装置1本体と同様に、CPU10や、RAM11並びにROM12等の記憶媒体といった情報処理機構を含み、画像形成装置1のコントローラ20と同様に、ROM12等の記憶媒体に記憶されている制御プログラムがRAM11にロードされ、CPU10がそのプログラムに従って演算を行うことにより構成されるソフトウェア制御部と、ハードウェアとの組み合わせによって構成される。

【0044】

そして、図5に示す光書込み装置111は、上述したように構成されるプリントエンジン26の制御部によって制御される。図4において説明したように、LEDA130は、感光体ドラム109の各色に対応して設けられる。従って、光書込み制御部120においては、速度変換部121及び配列変換SRAM122も各色に対応して設けられる。

【0045】

速度変換部121は、コントローラ20から所定の周波数で画素毎に入力される画素情報の周波数を変換して配列変換SRAM122に格納する。本実施形態においては、配列変換SRAM122への画素情報の格納をライト動作として説明する。即ち、速度変換部121が、コントローラ20から入力される画素情報を取得して配列変換SRAM122に格納する画素情報取得部として機能する。

【0046】

配列変換SRAM122は、速度変換部121によって格納された画素情報を、SRAM制御部123の制御に従って配列を変換してLEDA130に入力する。即ち、配列変換SRAM122が、配列変換部として機能する。本実施形態においては、配列変換SRAM122からLEDA130への画素情報の入力をリード動作として説明する。

【0047】

SRAM制御部123は、配列変換SRAM122の動作を制御する制御回路であり、上記ライド動作におけるライトタイミング及び画素情報を格納するライトアドレスを制御すると共に、上記リード動作において読み出す画素情報の配列の変換を制御する機能を有する。

【0048】

リードアドレス発生メモリ124は、上記リード動作における画素情報の配列の変換ルールが記述されたアドレス変換テーブルを記憶する不揮発性の記憶媒体である。リードアドレス発生メモリ124には、プリントエンジン26のCPU10によってアドレス変換テーブルがロードされる。即ち、リードアドレス発生メモリ124が、画素情報の配列変換態様を示す配列変換情報を取得して記憶する配列変換情報記憶部である。

【0049】

図6は、本実施形態に係るアドレス変換テーブルの例を示す図である。図6に示すように、本実施形態に係るアドレス変換テーブルにおいては、LEDA130に入力する画素の順番を示す“画素番号”と、それぞれの順番において読み出す画素が格納されているアドレスを示す“読出しアドレス”とが関連付けて格納されている。

【0050】

図6に示すようなアドレス変換テーブルは、図1に示す構成と同様の情報処理機構によって構成されるプリントエンジン26の制御部において、ROM12やHDD14等の不揮発性の記憶媒体に格納されており、プリントエンジン26の起動に応じて、CPU10の制御に従ってリードアドレス発生メモリ124にロードされる。

【0051】

ここで、LEDA130は、複数のLED素子が一方向に並べられて集積されたチップが、更に複数組み合わせられて1ラインの全範囲をカバー可能な主走査方向のサイズが構成される。これに応じて、図6に示すように、アドレス変換テーブルにおいては、夫々のチップ毎に“画素番号”と“読出しアドレス”とが関連付けられて格納されている。

【0052】

デコータ125は、リードアドレス発生メモリ124に格納されたアドレス変換テーブルの情報を、配列変換SRAM122の配列変換制御のためのリードアドレス信号に変換して配列変換SRAM122に入力する。即ち、デコータ125は、リードアドレス発生メモリ124に格納されたアドレス変換テーブルに従い、配列変換SRAM122による配列変換を制御するための配列変換制御信号を出力する制御信号出力部として機能する。

【0053】

本実施形態に係る配列変換SRAM122は、LEDA130に画素情報を入力する際に画素情報を読み出すアドレスを、図6に示すようなアドレス変換テーブルの情報に従って決定することにより、画素情報の配列変換を実行する。換言すると、配列変換SRAM122は、記憶した画素情報を読み出す順番を、デコータ125が出力する制御信号であるリードアドレス信号に従って変えることにより、配列変換を実行する。

【0054】

ライトアドレス生成部126は、速度変換部121から配列変換SRAM122に入力される画素情報を格納するアドレスを指定するためのライトアドレス信号を出力する。本実施形態に係るライト動作においては、特に配列変換に関する処理は実行されず、速度変換部121から入力される画素情報は配列変換SRAM122におけるアドレスの順番に従って格納される。

【0055】

WE生成部127は、速度変換部121から入力される画素情報を配列変換SRAM122に格納するタイミングを制御するためのライトイネーブル信号を出力する。配列変換SRAM122は、WE生成部127から入力されるライトイネーブル信号に応じて、ライドアドレス生成部126から入力されるライトアドレス信号に従ったアドレスに画素情報を格納する。

【0056】

このような画像書込み制御部120の構成によれば、リードアドレス発生メモリ124に格納するアドレス変換テーブを変更することにより、同一の光書込み制御部120によって異なる種類のLEDA130に対応することが可能となる。

【0057】

ここで、異なる種類のLEDA130とは、例えばA4用、A3用等のサイズの異なるLEDAである。サイズが異なれば、主走査方向の画素数が異なり、その結果画素の配列変換ルールも当然異なることとなる。また、本実施形態に係る画像形成装置1のようにタンデムタイプのプリントエンジン26を含む場合、各色毎に配列変換ルールが異なる場合もあり得る。

【0058】

本実施形態に係る光書込み装置111によれば、リードアドレス発生メモリ124に格納されるアドレス変換テーブルをソフトウェアによって書き換えることが可能であるため、上述したような異なる種類のLEDA130に対して、光書込み制御部120を再設計することなく容易に対応可能であり、簡易な構成により、異なる種類のLEDAに対応可能な光書込み装置を実現することができる。

【0059】

ここで、本実施形態に係る要旨は、デコータ125によるリードアドレス発生メモリ124からのアドレス変換テーブルの読み出しと、夫々の配列変換SRAM122へのリードアドレス信号の入力の具体的な態様にある。以下、本実施形態の要旨に係る処理について説明する。

【0060】

図7は、本実施形態に係る要旨、即ち、デコータ125によるリードアドレス発生メモリ124からのアドレス変換テーブルの読み出しと、夫々の配列変換SRAM122へのリードアドレス信号の入力の具体的な態様を示すブロック図である。図7においては、各色のLEDA130に対応する夫々の配列変換SRAM122を、配列変換SRAM122BK、122M、122C、122Yとして夫々示している。

【0061】

図7に示すように、リードアドレス発生メモリ124においては、記憶領域が分割されており、夫々の記憶領域には、“テーブル1”〜“テーブル4”の4つに分割されたアドレス変換テーブルが夫々格納されている。この分割されたアドレス変換テーブルは、例えば、図6に示すチップ毎のテーブルである。

【0062】

デコータ125は、リードアドレス発生メモリ124において分割された夫々の領域(以降、分割領域とする)に対して、同時にアクセスすることが可能である。換言すると、本実施形態に係るリードアドレス発生メモリ124は、同時にアクセス可能な複数の記憶領域に分割されており、分割された夫々の記憶領域にアドレス変換テーブルを分割して記憶する。

【0063】

即ち、配列変換SRAM122BKに対しては、テーブル1をデコードして生成したリードアドレス信号を出力しつつ、配列変換SRAM122Mに対しては、テーブル2をデコードして生成したリードアドレス信号を出力することが可能である。これにより、1つのアドレス変換テーブルによって複数のLEDA130の制御に対応可能とすることが本実施形態に係る要旨である。

【0064】

次に、本実施形態に係る光書込み制御部120によるLEDA130の制御態様について説明する。図8は、本実施形態に係るLEDA130の構成を模式的に示す図である。図8に示すように、本実施形態に係るLEDA130は、複数のLEDチップ130a〜130dが主走査方向に連結されて組み合わされることにより構成されている。

【0065】

また、本実施形態に係るLEDA130においては、夫々のLEDチップ130a〜130dは、図8に示すように副走査方向にずらされて配置されている。そのため、夫々のチップの発光タイミングが異なる。図9に、1つのLEDA130についての発光タイミング及びリードアドレス発生メモリ124からの各テーブルの読み出しタイミングを示す。

【0066】

図9において“hsync”は水平同期信号であり、主走査ライン毎のタイミングの基準を示す信号である。図8に示すLEDチップ130a〜130dをチップ1〜チップ4とすると、図9に示すように、hsyncの立ち上がりに応じて、チップ1〜チップ4が順番に発光する。

【0067】

そして、デコータ125は、LEDA130の発光タイミングに合わせて配列変換SRAM122にリードアドレス信号を入力する。そのため、夫々のチップに対応するテーブル1〜テーブル4の読み出しタイミングも、図9において“メモリリード”として示すように、夫々のチップの発光タイミングに応じたタイミングとなる。即ち、デコータ125は、それぞれのLEDA130を1ライン分発光させるために、図7に示すテーブル1〜テーブル4を順番に読出し、1つの配列変換SRAM122に対して順番にリードアドレス信号を出力する。

【0068】

次に、本実施形態に係る要旨となる制御の制御タイミングについて図10を参照して説明する。図10は、4つのLEDA130BK〜130Yの発光タイミングに応じたアドレス変換テーブルのメモリリードのタイミングを示すタイミングチャートである。

【0069】

図10に示すように、4つのLEDA130BK〜130Y夫々の発光タイミングは、“hsync_BK”、“hsync_M”、“hsync_C”、“hsync_Y”の4つのタイミングの異なる水平同期信号によって制御される。4つのLEDA130夫々の発光タイミングは、図4に示すように副走査方向に順番に配置されている感光体ドラム109において現像されたトナー像が重ね合わせられるように、搬送ベルト105の搬送速度に応じてずらされている。また、4つのLEDA130夫々の発光タイミングは、光書込み装置111の組み付け誤差や感光体ドラム109の組み付け誤差等によって生じる微小なタイミングのずれも吸収するように調整されている。

【0070】

そして、図7において説明したように、本実施形態に係るリードアドレス発生メモリ124は、夫々の領域に対して並列してアクセスが可能なように記憶領域が分割されているため、デコーダ125は、夫々の分割領域に格納されているテーブルに対して並列してアクセスし、夫々のテーブルに基づいて生成したリードアドレス信号を夫々異なる配列変換SRAM122に入力する。

【0071】

例えば、LEDA130BKの発光制御タイミングは、図10に示す“hsync_BK”によって制御される。LEDA130BKのチップ4の発光タイミングにおいて、デコータ125は、テーブル4に基づいて生成したリードアドレス信号を配列変換SRAM122BKに入力している。それと並行して、デコータ125は、テーブル3に基づいて生成したリードアドレス信号を配列変換SRAM122Mに、テーブル2に基づいて生成したリードアドレス信号を配列変換SRAM122Cに、テーブル1に基づいて生成したリードアドレス信号を配列変換SRAM122Yに、夫々入力している。

【0072】

図11は、LEDA130が、LEDA130BKとLEDA130Yとの2つの場合の例を示す図である。図11の例の場合、リードアドレス発生メモリ124の記憶領域は2つの分割領域に分割されており、夫々の分割領域に“テーブル1”、“テーブル2”として分割されたアドレス変換テーブルが格納されている。この場合、図11に示すように、配列変換SRAM122BKに対してテーブル2に基づいて生成されたリードアドレス信号が出力されている間に、配列変換SRAM122Yに対してテーブル1に基づいて生成されたリードアドレス信号が出力されるような制御が可能となる。

【0073】

図12は、本実施形態に係る比較例として、リードアドレス発生用メモリ124が、夫々並行してアクセス可能な分割領域に分割されていない場合の例を示す図である。この例の場合、“hsync_BK”に応じて、配列変換SRAM122BKにリードアドレス信号を入力するためにリードアドレス発生メモリ124にアクセスしている場合、そのリードアドレス発生メモリに対する他のアクセスが不可能である。

【0074】

そのため、図12にメモリ1〜4として示すように、配列変換SRAM122BKにリードアドレス信号を入力するためのアドレス変換テーブルが格納されたメモリとは別のメモリを用意し、“hsync_M”、“hsync_C”、“hsync_Y”に対応したリードアドレス信号を生成するためのアドレス変換テーブルを格納しておく必要がある。その結果、アドレス変換テーブルの容量が4倍となり、装置構成の非効率化や回路規模の大型化を招く。本実施形態によれば、このような課題を解決することが可能となる。

【0075】

以上説明したように、本実施形態に係る光書込み制御部120を含む画像形成装置1においては、1つのアドレス変換テーブルのみで、複数のLEDA130の発光を制御するためのリードアドレス信号を生成して出力することが可能となり、アドレス変換テーブルを設けることにより異なる種類のLEDAに対応可能な光書込み装置の装置構成を効率化することが可能となる。

【0076】

尚、上記実施形態においては、図10に示すように、4つのLEDA130の発光タイミングがすべて異なる場合を例として説明した。ここで、上述したように、“hsync_BK”、“hsync_M”、“hsync_C”、“hsync_Y”の4つの水平同期信号は、4つの感光体ドラム109の副走査方向の位置及び搬送ベルト105の搬送スピードに加えて、製造公差をも考慮してタイミングが調整されている。

【0077】

従って、製造公差によるタイミングの調整量によっては、異なるLEDA130に対応する水平同期信号のタイミングが一致する可能性がある。その場合、デコータ125は、図13に示すように、異なるLEDA130であっても同一のタイミングで同一のテーブルに基づいて生成したリードアドレス信号を入力する。図13の例の場合、デコータ125は、リードアドレス発生メモリ124から読み出したテーブルに基づいて生成したリードアドレス信号を配列変換SRAM122BK及び配列変換SRAM122Cに入力する。

【0078】

また、水平同期信号のタイミングが完全に一致しない場合であっても、夫々のチップ毎の発光期間との比較において一致しているとみなせる程度の微小な期間のずれであれば、一致しているとみなしてメモリリードのタイミングを制御しても良い。図14は、そのような場合の例を示す図である。図14に示すように、水平同期信号のずれが、同一であるとみなすことができる期間の閾値T以下であれば、図13の例と同様に、デコータ125は同一のタイミングで同一のテーブルに基づいて生成したリードアドレス信号を入力する。

【0079】

図14に示すように、水平同期信号のタイミングが一致しているとみなして、2つの配列変換SRAM122に対して同一のタイミングでリードアドレス信号を入力した場合、一方のLEDA130(図14の例の場合、LEDA130C)の発光タイミングが、水平同期信号のズレ量の分ずれることとなる。従って、図14に示す閾値Tは、一方のLEDA130の発光タイミングのずれの許容値という意味合いを持つ。

【0080】

この閾値Tの値の例としては、例えば、副走査方向の一画素分のずれ量に相当する期間である。このずれ量は、画像の大きさに応じて、十画素分のずれ量に相当する期間等に定めることもできる。このように閾値Tを定めることにより、LEDA130の制御構成の効率化を保ちつつ、形成される画像の画質をも保つことができる。

【符号の説明】

【0081】

1 画像形成装置

10 CPU

11 RAM

12 ROM

13 エンジン

14 HDD

15 I/F

16 LCD

17 操作部

18 バス

20 コントローラ

21 ADF

22 スキャナユニット

23 排紙トレイ

24 ディスプレイパネル

25 給紙テーブル

26 プリントエンジン

27 排紙トレイ

28 ネットワークI/F

30 主制御部

31 エンジン制御部

32 入出力制御部

33 画像処理部

34 操作表示制御部

101 給紙トレイ

102 給紙ローラ

103 分離ローラ

104 用紙

105 搬送ベルト

106BK、106C、106M、106Y 画像形成部

107 駆動ローラ

108 従動ローラ

109BK、109C、109M、109Y 感光体ドラム

110BK 帯電器

111光書込み装置

112BK、112C、112M、112Y 現像器

113BK、113C、113M、113Y 除電器

115BK、115C、115M、115Y 転写器

116 定着器

120 光書込み制御部

121 速度変換部

122 配列変換SRAM

123 SRAM制御部

124 リードアドレス発生メモリ

125 デコータ

126 ライトアドレス生成部

127 WE生成部

130、130BK、130M、130C、130Y LEDA

130a、130b、130c、130d LEDチップ

【先行技術文献】

【特許文献】

【0082】

【特許文献1】特開2008−070469号公報

【特許請求の範囲】

【請求項1】

感光体上に静電潜像を形成する光書込み装置であって、

前記静電潜像として形成すべき画像を構成する画素の情報である画素情報を取得する画素情報取得部と、

前記取得された画素情報の配列を変換する配列変換部と、

前記感光体を露光する光源に応じた前記画素情報の配列の変換態様を示す配列変換情報を取得して記憶する配列変換情報記憶部と、

前記記憶された配列変換情報に基づき、前記配列変換部による画素情報の配列の変換を制御するための配列変換制御信号を生成して出力する制御信号出力部とを含み、

前記配列変換情報記憶部の記憶領域は、同時にアクセス可能な複数の記憶領域に分割されており、前記配列変換情報を前記複数の記憶領域に分割して記憶することを特徴とする光書込み装置。

【請求項2】

前記感光体は色毎に複数設けられて配置されており、

前記配列変換情報記憶部は、前記複数の感光体を夫々露光する複数の光源に対して共通する一の前記配列変換情報を取得して記憶し、

前記配列変換部は、前記複数の光源夫々に対応して設けられており、

前記制御信号出力部は、前記複数の光源夫々の発光タイミングに応じて、前記複数の光源夫々に異なる前記記憶領域に記憶されている配列変換情報に基づいて生成した配列変換制御信号を出力することを特徴とする請求項1に記載の光書込み装置。

【請求項3】

前記制御信号出力部は、発光タイミングが同一である複数の光源に対応する配列変換部に対して、同一の配列変換情報に基づいて生成した配列変換制御信号を出力することを特徴とする請求項2に記載の光書込み装置。

【請求項4】

前記制御信号出力部は、発光タイミングの差異が所定の閾値以下である複数の光源の発光タイミングを同一であるとみなして前記配列変換制御信号を出力することを特徴とする請求項3に記載の光書き込み装置。

【請求項5】

前記配列変換情報記憶部の記憶領域は、前記複数の光源の数以上に分割されていることを特徴とする請求項1乃至4いずれか1項に記載の光書込み装置。

【請求項6】

前記光源は夫々の画素に対応する発光素子が集積されたチップが複数連結されて構成され、

前記配列変換情報記憶部の記憶領域は、前記チップの数に分割されており、

前記分割された複数の記憶領域は、夫々の前記チップに対応した配列変換情報を記憶していることを特徴とする請求項1乃至5いずれか1項に記載の光書込み装置。

【請求項7】

前記配列変換部は、前記取得された画像情報を記憶媒体に記憶し、記憶した画素情報を読み出す順番を前記配列変換制御信号に従って変えることにより前記取得された画素情報の配列を変換することを特徴とする請求項1乃至6いずれか1項に記載の光書込み装置。

【請求項8】

請求項1乃至7いずれか1項に記載の光書込み装置を含むことを特徴とする画像形成装置。

【請求項9】

感光体上に静電潜像を形成する光書込み装置の制御方法であって、

前記静電潜像として形成すべき画像を構成する画素の情報である画素情報を取得し、

前記感光体を露光する光源に応じた前記画素情報の配列の変換態様を示す配列変換情報を取得して、同時にアクセス可能な複数の記憶領域に分割された記憶媒体における複数の記憶領域に分割して記憶し、

前記分割して記憶された夫々の配列変換情報に基づき、前記画素情報の配列の変換を制御するための配列変換制御信号を生成して出力し、

前記配列変換制御信号に応じて、前記取得された画素情報の配列を変換し、

前記変換された画素情報に従って前記感光体を露光する光源を発光させることを特徴とする光書込み装置の制御方法。

【請求項1】

感光体上に静電潜像を形成する光書込み装置であって、

前記静電潜像として形成すべき画像を構成する画素の情報である画素情報を取得する画素情報取得部と、

前記取得された画素情報の配列を変換する配列変換部と、

前記感光体を露光する光源に応じた前記画素情報の配列の変換態様を示す配列変換情報を取得して記憶する配列変換情報記憶部と、

前記記憶された配列変換情報に基づき、前記配列変換部による画素情報の配列の変換を制御するための配列変換制御信号を生成して出力する制御信号出力部とを含み、

前記配列変換情報記憶部の記憶領域は、同時にアクセス可能な複数の記憶領域に分割されており、前記配列変換情報を前記複数の記憶領域に分割して記憶することを特徴とする光書込み装置。

【請求項2】

前記感光体は色毎に複数設けられて配置されており、

前記配列変換情報記憶部は、前記複数の感光体を夫々露光する複数の光源に対して共通する一の前記配列変換情報を取得して記憶し、

前記配列変換部は、前記複数の光源夫々に対応して設けられており、

前記制御信号出力部は、前記複数の光源夫々の発光タイミングに応じて、前記複数の光源夫々に異なる前記記憶領域に記憶されている配列変換情報に基づいて生成した配列変換制御信号を出力することを特徴とする請求項1に記載の光書込み装置。

【請求項3】

前記制御信号出力部は、発光タイミングが同一である複数の光源に対応する配列変換部に対して、同一の配列変換情報に基づいて生成した配列変換制御信号を出力することを特徴とする請求項2に記載の光書込み装置。

【請求項4】

前記制御信号出力部は、発光タイミングの差異が所定の閾値以下である複数の光源の発光タイミングを同一であるとみなして前記配列変換制御信号を出力することを特徴とする請求項3に記載の光書き込み装置。

【請求項5】

前記配列変換情報記憶部の記憶領域は、前記複数の光源の数以上に分割されていることを特徴とする請求項1乃至4いずれか1項に記載の光書込み装置。

【請求項6】

前記光源は夫々の画素に対応する発光素子が集積されたチップが複数連結されて構成され、

前記配列変換情報記憶部の記憶領域は、前記チップの数に分割されており、

前記分割された複数の記憶領域は、夫々の前記チップに対応した配列変換情報を記憶していることを特徴とする請求項1乃至5いずれか1項に記載の光書込み装置。

【請求項7】

前記配列変換部は、前記取得された画像情報を記憶媒体に記憶し、記憶した画素情報を読み出す順番を前記配列変換制御信号に従って変えることにより前記取得された画素情報の配列を変換することを特徴とする請求項1乃至6いずれか1項に記載の光書込み装置。

【請求項8】

請求項1乃至7いずれか1項に記載の光書込み装置を含むことを特徴とする画像形成装置。

【請求項9】

感光体上に静電潜像を形成する光書込み装置の制御方法であって、

前記静電潜像として形成すべき画像を構成する画素の情報である画素情報を取得し、

前記感光体を露光する光源に応じた前記画素情報の配列の変換態様を示す配列変換情報を取得して、同時にアクセス可能な複数の記憶領域に分割された記憶媒体における複数の記憶領域に分割して記憶し、

前記分割して記憶された夫々の配列変換情報に基づき、前記画素情報の配列の変換を制御するための配列変換制御信号を生成して出力し、

前記配列変換制御信号に応じて、前記取得された画素情報の配列を変換し、

前記変換された画素情報に従って前記感光体を露光する光源を発光させることを特徴とする光書込み装置の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−39680(P2013−39680A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2011−176103(P2011−176103)

【出願日】平成23年8月11日(2011.8.11)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成23年8月11日(2011.8.11)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]