光素子集積モジュール

【課題】構成の簡素化及び低価格化を実現できる光素子集積モジュールを提供する。

【解決手段】光素子集積モジュールは、光サーキュレータ111,112,113,1114と、光クロック信号分岐部130と、光データ信号A1〜A4に応じて光短パルス列B1〜B4を変調することによって変調光データ信号C1〜C4を出力する光/光変換器121,122,123,124と、変調光データ信号C1〜C4から光時分割多重信号D1〜D4を生成する光時分割多重部160を備え、光データ信号A1〜A4は、外部から光サーキュレータ111,112,113,114の第1ポートP1に入力され、第2ポートP2を経由して光/光変換器121,122,123,124に入力され、変調光データ信号C1〜C4は、光サーキュレータ111,112,113,114の第2ポートP2に入力され、第3ポートP3を経由して光時分割多重部160に入力される。

【解決手段】光素子集積モジュールは、光サーキュレータ111,112,113,1114と、光クロック信号分岐部130と、光データ信号A1〜A4に応じて光短パルス列B1〜B4を変調することによって変調光データ信号C1〜C4を出力する光/光変換器121,122,123,124と、変調光データ信号C1〜C4から光時分割多重信号D1〜D4を生成する光時分割多重部160を備え、光データ信号A1〜A4は、外部から光サーキュレータ111,112,113,114の第1ポートP1に入力され、第2ポートP2を経由して光/光変換器121,122,123,124に入力され、変調光データ信号C1〜C4は、光サーキュレータ111,112,113,114の第2ポートP2に入力され、第3ポートP3を経由して光時分割多重部160に入力される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光受動素子及び光能動素子を集積することによって形成された光素子集積モジュールに関し、特に、光短パルス列を光データ信号に応じて変調する光素子集積モジュールに関するものである。

【背景技術】

【0002】

EA(エレクトロアブソープション)変調器の電解吸収効果を利用して光短パルス列を変調する技術を用いた光素子集積モジュールが、例えば、特許文献1又は非特許文献1に開示されている。

【0003】

【特許文献1】特開2005−26725号公報

【非特許文献1】村井仁著、「EA変調器を用いた160Gbit/s超高速光時分割多重/分離技術」、 O plus E、 2005年5月号、 Vol.27、 No.5、 pp.535−540

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上記従来技術においては、EA変調器に高周波電気信号を入力することによって光短パルス列を変調している。この高周波電気信号を得るためには、光データ信号を電気信号に変換するための光/電気変換装置が必要になる。また、EA変調器に高周波電気信号を入力するための電気回路も必要になる。このため、上記従来技術においては、装置の構成が複雑になり、装置の価格が高額になる問題があった。

【0005】

そこで、本発明は、上記従来技術の課題を解決するためになされたものであり、その目的は、構成の簡素化及び低価格化を実現できる、光短パルス列を変調する光素子集積モジュールを提供することにある。

【課題を解決するための手段】

【0006】

本発明の光素子集積モジュールの一形態においては、第1ポート、第2ポート、及び第3ポートを具備し、前記第1ポートに入力した光信号を前記第2ポートから出力し、前記第2ポートに入力した光信号を前記第3ポートから出力し、前記第3ポートに入力した光信号を前記第1ポートから出力する第1乃至第n(nは2以上の整数)の光サーキュレータと、外部から入力される光短パルス列を分岐して第1乃至第nの光短パルス列を生成する光クロック信号分岐部と、第1乃至第nの光データ信号のそれぞれに応じて前記第1乃至第nの光短パルス列のそれぞれを変調することによって第1乃至第nの変調光データ信号を出力する第1乃至第nの光/光変換器と、前記第1乃至第nの変調光データ信号を時分割多重して光時分割多重信号を生成する光時分割多重部とを備え、前記第1乃至第nの光データ信号のそれぞれは、外部から前記第1乃至第nの光サーキュレータの前記第1ポートのそれぞれに入力され、前記第2ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、前記第1乃至第nの変調光データ信号のそれぞれは、前記第1乃至第nの光サーキュレータの前記第2ポートのそれぞれに入力され、前記第3ポートのそれぞれを経由して前記光時分割多重部に入力されることを特徴としている。

【0007】

また、本発明の光素子集積モジュールの他の形態においては、第1ポート、第2ポート、及び第3ポートを具備し、前記第1ポートに入力した光信号を前記第2ポートから出力し、前記第2ポートに入力した光信号を前記第3ポートから出力し、前記第3ポートに入力した光信号を前記第1ポートから出力する第1乃至第n(nは2以上の整数)の入力用光サーキュレータと、第4ポート、第5ポート、及び第6ポートを具備し、前記第4ポートに入力した光信号を前記第5ポートから出力し、前記第5ポートに入力した光信号を前記第6ポートから出力し、前記第6ポートに入力した光信号を前記第4ポートから出力する第1乃至第nの出力用光サーキュレータと、第1乃至第nの光/光変換器と、外部から入力される光時分割多重信号を分岐して第1乃至第nの光時分割多重信号を生成する光時分割多重信号分岐部とを備え、前記第1乃至第nの光短パルス列のそれぞれは、外部から前記第1乃至第nの入力用光サーキュレータの前記第1ポートのそれぞれに入力され、前記第2ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、前記第1乃至第nの光時分割多重信号は、前記第1乃至第nの出力用光サーキュレータの前記第5ポートのそれぞれに入力され、前記第6ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、前記第1乃至第nの光/光変換器のそれぞれは、第1乃至第nの光時分割多重信号のそれぞれに応じて前記第1乃至第nの光短パルス列のそれぞれを変調することによって第1乃至第nの変調光データ信号を出力し、前記第1乃至第nの変調光データ信号のそれぞれは、前記第1乃至第nの出力用光サーキュレータの前記第6ポートのそれぞれに入力され、前記第4ポートのそれぞれを経由して外部に出力されることを特徴としている。

【発明の効果】

【0008】

本発明の光素子集積モジュールによれば、光短パルス列を光データ信号に応じて変調しているので、構成の簡素化及び低価格化を実現することができる。

【0009】

また、本発明の光素子集積モジュールによれば、光/光変調器から出力された変調光データ信号を、光サーキュレータを介して、光時分割多重部又は光分割分離信号出力部に導いているので、出力される光信号のパワーの損失を抑制することができる。

【発明を実施するための最良の形態】

【0010】

第1の実施形態

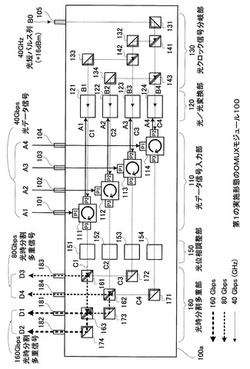

図1は、本発明の第1の実施形態に係る光素子集積モジュールとしての光マルチプレクサ(OMUX)モジュール100の構成を概略的に示す図である。

【0011】

図1に示されるように、第1の実施形態に係るOMUXモジュール100は、筐体100aと、筐体100a内に備えられた、光データ信号入力部110、光/光変換部120、光クロック信号分岐部130、光位相調整部150、及び光時分割多重部160を備えている。また、第1の実施形態に係るOMUXモジュール100は、筐体100aに、光データ信号入力ポート101,102,103,104と、光短パルス列(光クロック信号)入力ポート105と、光時分割多重信号出力ポート181,182,183,184を備えている。図1に示されるように、第1の実施形態においては、光データ信号入力部110は、光/光変換部120と光時分割多重部160との間に配置されている。また、第1の実施形態においては、光位相調整部150は、光データ信号入力部110と光時分割多重部160との間に配置されている。また、光/光変換部120は、光データ信号入力部110と光クロック信号分岐部130との間に配置されている。

【0012】

図1に示されるように、光データ信号入力部110は、第1乃至第4の光サーキュレータ111,112,113,114を有している。第1乃至第4の光サーキュレータ111,112,113,114のそれぞれは、第1ポートP1と、第2ポートP2と、第3ポートP3を具備している。第1乃至第4の光サーキュレータ111,112,113,114のそれぞれは、第1ポートP1に入力した光信号を第2ポートP2から出力し、第2ポートP2に入力した光信号を第3ポートP3から出力し、第3ポートP3に入力した光信号を第1ポートP1から出力する。第1乃至第4の光サーキュレータ111,112,113,114としては、例えば、対向する2つの偏光プリズム、これらの間に配置された2分の1波長板及びファラデー回転子(ガーネット膜)を配置したものを用いることができる。このような光サーキュレータは公知のものを使用でき、例えば、オプトロニクス社発行の「図解光デバイス辞典」に説明がある。

【0013】

図1に示されるように、光/光変換部120は、クロスアブソープション(相互吸収型)変調を利用した第1乃至第4の光/光変調器121,122,123,124を有している。光/光変調器121,122,123,124の具体例としては、EA変調器のクロスアブソープション効果を利用する形態が考えられる。EA変調器の通常の使用法は、高周波電気信号を入力することによって光短パルス列を変調するものである。しかし、本発明においては、高周波電気信号をデータ入力信号として使用せず、光データ信号A1,A2,A3,A4をデータ入力信号として使用する。クロスアブソープション効果は、可飽和吸収体にバイアス電圧を印加しておくと、このバイアス電圧が印加された領域に入力された第1の光が弱い間は可飽和吸収体は光の吸収体となり、第1の光が強くなると可飽和吸収体は他の光を吸収できなくなって透明体になる効果である。このクロスアブソープション効果を利用することによって、光データ信号A1,A2,A3,A4がハイレベルの期間だけ、光/光変調器光短パルス列B1,B2,B3,B4を通過させることができる。なお、EA変調器のクロスアブソープション効果は公知の技術であり、例えば、以下の文献に説明がある。

Murai, Kagawa, Tsuji, and Fujii, “80−Gb/s Error−Free Transmission Over 5600 km Using a Cross Absorption Modulation Based Optical 3R Regenerator”, IEEE PHOTONICS TECHNOLOGY LETTERS, Vol.17, No.9, September 2005, pp.1965−1967

また、光/光変調器121,122,123,124として、SOA(半導体光増幅器)のような他の変調器を用いることもできる。

【0014】

図1に示されるように、光クロック信号分岐部130は、外部から入力される光短パルス列(光クロック信号)B0を分岐して第1乃至第4の光短パルス列B1,B2,B3,B4を生成する。光クロック信号分岐部130は、光短パルス列B0を直角に反射するミラー131と、反射された光短パルス列B0を互いに直交する方向に2分岐するハーフミラー141と、ハーフミラー141を透過する光短パルス列を互いに直交する方向に2分岐するハーフミラー143と、ハーフミラー141で反射された光短パルス列を直下に反射するミラー132と、ミラー132で反射された光短パルス列を互いに直交する方向に2分岐するハーフミラー142と、ハーフミラー142で反射された光短パルス列を直角に反射するミラー133と、ハーフミラー143で反射された光短パルス列を反射するミラー134とを有している。このような構成により、外部から入力される光短パルス列(光クロック信号)B0は、第1乃至第4の光短パルス列B1,B2,B3,B4として光/光変換部120の第1乃至第4の光/光変換器121,122,123,124に入力される。なお、第1の実施形態においては、光短パルス列B0の周波数は、40GHzであり、第1乃至第4の光短パルス列B1,B2,B3,B4の周波数は、40GHzである。ただし、光クロック信号分岐部130の構成は、図示の構成に限定されない。

【0015】

図1に示されるように、光位相調整部150は、第1乃至第4の光位相調整器151,152,153,154を有している。第1乃至第4の光位相調整器151,152,153,154は、例えば、液晶部によって構成される。ただし、光位相調整部150の構成は、図示の構成に限定されない。なお、光位相調整部150は、変調された光信号の位相調整が必要でない場合には、不要な構成である。

【0016】

図1に示されるように、光時分割多重部160は、第1乃至第4の変調光データ信号C1、C2,C3,C4を時分割多重して光時分割多重信号D1,D2,D3,D4を生成する。第1の実施形態においては、第1乃至第4の変調光データ信号C1,C2,C3.C4のデータレートは、40Gbpsであり、光時分割多重信号D1,D2のデータレートは160Gbpsであり、光時分割多重信号D3,D4のデータレートは80Gbpsである。光時分割多重部160は、第3の変調光データ信号C4を直角に反射するミラー171と、第3の変調光データ信号C3を直角に反射するミラー172と、第1の変調光データ信号C1と第3の変調光データ信号C3とを光時分割多重して互いに直交する2方向に分岐するハーフミラー161と、第2の変調光データ信号C2と第4の変調光データ信号C4とを光時分割多重して互いに直交する2方向に分岐するハーフミラー162と、ハーフミラー162から出力される変調光データ信号を直角に反射するミラー173と、ハーフミラー161から出力される変調光データ信号とミラー173で反射された変調光データ信号とを時分割多重して互いに直交する2方向に分岐するハーフミラー163と、ハーフミラー163で反射された変調光データ信号を直角に反射するミラー174とを有している。ただし、光時分割多重部160の構成は、図示の構成に限定されない。

【0017】

次に、第1の実施形態に係るOMUXモジュール100の動作を説明する。第1乃至第4の光データ信号A1,A2,A3,A4のそれぞれは、外部から光データ信号入力ポート101,102,103,104を通して第1乃至第4の光サーキュレータ111,112,113,114の第1ポートP1のそれぞれに入力され、第2ポートP2を経由して第1乃至第4の光/光変換器121,122,123,124のそれぞれに入力される。

【0018】

一方、光クロック信号分岐部130は、入力ポート105を通して入力される光短パルス列B0を第1乃至第4の光短パルス列B1,B2,B3,B4に分岐し、第1乃至第4の光短パルス列B1,B2,B3,B4のそれぞれを第1乃至第4の光/光変換器121,122,123,124に入力する。光/光変換器121,122,123,124は、クロスアブソープション効果を利用して、入力される第1乃至第4の光データ信号A1,A2,A3,A4のそれぞれに応じて第1乃至第4の光短パルス列B1,B2,B3,B4のそれぞれを変調することによって第1乃至第4の変調光データ信号C1,C2,C3.C4を出力する。第1の実施形態においては、光短パルス列B0の周波数は、40GHzであり、第1乃至第4の光短パルス列B1,B2,B3,B4の周波数は、40GHzである。また、第1乃至第4の光データ信号A1,A2,A3,A4のデータレートは、40Gbpsであり、第1乃至第4の変調光データ信号C1,C2,C3.C4のデータレートは、40Gbpsである。また、光/光変換器121,122,123,124の反対の端面(図1において右側の端面)から出力された光データ信号は出力先で、全て終端される。具体的には、ハーフミラーを通り、光が集光されていないものは放射減衰して終端し、光ポートヘ達したものは、光アイソレータ(図示せず)で終端される。

【0019】

第1乃至第4の変調光データ信号C1,C2,C3,C4のそれぞれは、第1乃至第4の光サーキュレータ111,112,113,114の第2ポートP2のそれぞれに入力され、第3ポートP3のそれぞれを経由して光位相調整部150に入力され、位相調整を受けた後、光時分割多重部160に入力される。

【0020】

光時分割多重部160に入力された第1乃至第4の変調光データ信号C1,C2,C3,C4は、光時分割多重され、出力ポート181及び182から160Gbpsの光時分割多重信号D1及びD2として出力され、出力ポート183及び184から80Gbpsの光時分割多重信号D3及びD4として出力される。

【0021】

以上に説明したように、第1の実施形態に係るOMUXモジュール100によれば、光短パルス列を光データ信号に応じて変調しているので、光データ信号を高周波電気信号に変換する電気回路や高周波電気信号を印加する電気回路が不要になり、装置の構成の簡素化及び低価格化を実現することができる。

【0022】

また、第1の実施形態に係るOMUXモジュール100によれば、第1乃至第4の光サーキュレータ111,112,113,114を用いることによって、第1乃至第4の変調光データ信号C1,C2,C3,C4を、光時分割多重部160に導いているので、第1乃至第4の光サーキュレータ111,112,113,114に代えてハーフミラーを用いる形態(常に3dB(パワーの半分)を損失する形態)に比べて、第1乃至第4の変調光データ信号C1,C2,C3,C4のパワーを損失せずに合波できるため、出力される光時分割多重信号のS/Nを向上させることができる。

【0023】

なお、第1の実施形態においては、入力データ信号が4入力であり、光サーキュレータ、光/光変調器、及び光位相調整器のそれぞれの数が4の場合を例示したが、これらの数は2以上であれば幾つでもよい。

【0024】

また、第1の実施形態においては、入力データ信号が40Gbps、光時分割多重信号が160Gbps,80Gbpsの場合を例示したが、他のデータレートを適用することも可能である。

【0025】

第2の実施形態

図2は、本発明の第2の実施形態に係る光素子集積モジュールとしての光マルチプレクサ(OMUX)Xモジュール200の構成を概略的に示す図である。図2において、図1に示される構成と、同一又は対応する構成には、同じ符号を付して、その説明を省略する。

【0026】

図2に示されるように、第2の実施形態に係るOMUXモジュール200は、筐体200a内の構成のうち、光位相調整部250と光時分割多重部260の構成が、第1の実施形態に係るOMUXモジュール100の構成と相違する。

【0027】

第1の実施形態においては、光位相調整部150は、光データ信号入力部110と光時分割多重部160との間に配置されているが、第2の実施形態においては、光位相調整部250は、光サーキュレータ111の第3ポートP3からの変調光データ信号の位相を調整する光位相調整器251と、光サーキュレータ114の第3ポートP3からの変調光データ信号の位相を調整する光位相調整器254と、光サーキュレータ111の第3ポートP3からの変調光データ信号と光位相調整器254からの変調光データ信号とが入力されるハーフミラー262からの出力を受ける光位相調整器252とを有している。

【0028】

第1の実施形態においては、光位相制御は各パスで各々行う構成を採用していたので、多重後の信号が更に多重される場合に、2つの位相調整器を同時に制御する必要があったが、第2の実施形態においては、位相調整器252をハーフミラー262の下流側に配置したので位相調整器252を制御する1つの制御部を制御すればよい。

【0029】

以上に説明したように、第2の実施形態に係るOMUXモジュール200によれば、上記第1の実施形態の効果に加え、光位相調整部250の構成の簡素化及び位相調整制御の簡素化を実現できる。

【0030】

なお、第2の実施形態において、上記以外の点は、第1の実施形態の場合と同じである。

【0031】

第3の実施形態

図3は、本発明の第3の実施形態に係る光素子集積モジュールとしての光デマルチプレクサ(ODeMUX)モジュール300の構成を概略的に示す図である。

【0032】

図3に示されるように、第3の実施形態に係るODeMUXモジュール300は、筐体300aと、筐体300a内に備えられた、光クロック信号入力部310、光/光変換部320、光時分割多重信号分岐部330、及び光時分割分離信号出力部350を備えている。また、第3の実施形態に係るODeMUXモジュール300は、筐体300aに、光短パルス列(光クロック信号)入力ポート301,302,303,304と、光時分割多重信号入力ポート305と、光データ信号出力ポート361,362,363,364を備えている。図3に示されるように、第3の実施形態においては、光/光変換器320は、光クロック信号入力部310と光時分割分離信号出力部350との間に配置され、光時分割分離信号出力部350は、光/光変換器320と光時分割多重信号分岐部330との間に配置されている。

【0033】

図3に示されるように、光クロック信号入力部310は、第1乃至第4の入力用光サーキュレータ311,312,313,314を有している。第1乃至第4の入力用光サーキュレータ311,312,313,314のそれぞれは、第1ポートP1と、第2ポートP2と、第3ポートP3を具備している。第1乃至第4の入力用光サーキュレータ311,312,313,314のそれぞれは、第1ポートP1に入力した光信号を第2ポートP2から出力し、第2ポートP2に入力した光信号を第3ポートP3から出力し、第3ポートP3に入力した光信号を第1ポートP1から出力する。第1乃至第4の入力用光サーキュレータ311,312,313,314の構成は、第1の実施形態の光サーキュレータと同じである。

【0034】

図3に示されるように、光/光変換部320は、クロスアブソープション(相互吸収型)変調を利用した第1乃至第4の光/光変調器321,322,323,324を有している。第1乃至第4の光/光変調器321,322,323,324は、第1の実施形態の光/光変調器と同じである。また、第1乃至第4の光/光変調器321,322,323,324として、SOA(半導体光増幅器)のような他の変調器を用いることもできる。

【0035】

図3に示されるように、光時分割多重信号分岐部330は、外部から入力される光時分割多重信号E0(160Gbps,+16dBm)を分岐して第1乃至第4の光時分割多重信号E1,E2,E3,E4(160Gbps)を生成する。光時分割多重信号分岐部330は、光時分割多重信号E0を直角に反射するミラー331と、反射された光時分割多重信号E0を互いに直交する方向に2分岐するハーフミラー341と、ハーフミラー341を透過する光時分割多重信号を互いに直交する方向に2分岐するハーフミラー343と、ハーフミラー341で反射された光時分割多重信号を直角に反射するミラー332と、ミラー332で反射された光時分割多重信号を互いに直交する方向に2分岐するハーフミラー342と、ハーフミラー342で反射された光時分割多重信号を直角に反射するミラー333と、ハーフミラー343で反射された光時分割多重信号を反射するミラー334とを有している。ただし、光時分割多重信号分岐部330の構成は、図示の構成に限定されない。

【0036】

図3に示されるように、光時分割分離信号出力部350は、第1乃至第4の出力用光サーキュレータ351,352,353,354を有している。第1乃至第4の出力用光サーキュレータ351,352,353,354のそれぞれは、第4ポートP4と、第5ポートP5と、第6ポートP6を具備している。第1乃至第4の出力用光サーキュレータ351,352,353,354のそれぞれは、第4ポートP4に入力した光信号を第5ポートP5から出力し、第5ポートP5に入力した光信号を第6ポートP6から出力し、第6ポートP6に入力した光信号を第4ポートP4から出力する。第1乃至第4の出力用光サーキュレータ351,352,353,354の構成は、第1の実施形態の光サーキュレータと同じである。ただし、光時分割分離信号出力部350の構成は、図示の構成に限定されない。例えば、第1乃至第4の出力用光サーキュレータ351,352,353,354を上下反転させ、光の進行方向を反時計回り方向にすることによって、出力ポート361,362,363,364を図3における下側に備えることもできる。

【0037】

次に、第3の実施形態に係るODeMUXモジュール300の動作を説明する。

第1乃至第4の光短パルス列(光クロック信号)F1,F2,F3,F4のそれぞれは、外部から入力ポート301,302,303,304を介して第1乃至第4の入力用光サーキュレータ311,312,313,314の第1ポートP1のそれぞれに入力され、第2ポートP2のそれぞれを経由して第1乃至第4の光/光変換器321,322,323,324のそれぞれに入力される。

【0038】

一方、光時分割多重信号分岐部330の入力ポート305に入力された光時分割多重信号E0から生成された第1乃至第4の光時分割多重信号E1,E2,E3,E4は、第1乃至第4の出力用光サーキュレータ351,352,353,354の第5ポートP5のそれぞれに入力され、第6ポートP6のそれぞれを経由して第1乃至第4の光/光変換器321,322,323,324のそれぞれに入力される。

【0039】

第1乃至第4の光/光変換器321,322,323,324のそれぞれは、第1乃至第4の光時分割多重信号E1,E2,E3,E4のそれぞれに応じて第1乃至第4の光短パルス列F1,F2,F3,F4のそれぞれを変調することによって第1乃至第4の変調光データ信号G1,G2,G3,G4を出力する。

【0040】

第1乃至第4の光/光変換器321,322,323,324から出力された第1乃至第4の変調光データ信号G1,G2,G3,G4のそれぞれは、第1乃至第4の出力用光サーキュレータ351,352,353,354の第6ポートP6のそれぞれに入力され、第4ポートP4のそれぞれを経由して、出力ポート361,362,363,364を介して外部に出力される。

【0041】

以上に説明したように、第3の実施形態に係るODeMUXモジュール300によれば、光短パルス列を光データ信号に応じて変調しているので、光データ信号を高周波電気信号に変換する電気回路や高周波電気信号を印加する電気回路が不要になり、装置の構成の簡素化及び低価格化を実現することができる。

【0042】

また、第3の実施形態に係るODeMUXモジュール300によれば、第1乃至第4の入力用光サーキュレータ311,312,313,314を用いることによって、第1乃至第4の光短パルス列F1,F2,F3,F4を、光/光変換部320に導いているので、第1乃至第4の入力用光サーキュレータ311,312,313,314に代えてハーフミラーを用いる形態(常に3dB(パワーの半分)を損失する形態)に比べて、第1乃至第4の光短パルス列F1,F2,F3,F4のパワーを損失せずに合波できるため、出力される光データ信号361,362,363,364のS/Nを向上させることができる。

【0043】

なお、第3の実施形態においては、入力データ信号が4入力であり、光サーキュレータ、及び光/光変調器のそれぞれの数が4の場合を例示したが、これらの数は2以上であれば幾つでもよい。

【0044】

また、第3の実施形態においては、光時分割多重信号E0が160Gbps、光短パルス列が40GHzの場合を例示したが、他の周波数又はデータレートを適用することも可能である。

【図面の簡単な説明】

【0045】

【図1】本発明の第1の実施形態に係る光素子集積モジュールとしてのOMUXモジュールの構成を概略的に示す図である。

【図2】本発明の第2の実施形態に係る光素子集積モジュールとしてのOMUXモジュールの構成を概略的に示す図である。

【図3】本発明の第3の実施形態に係る光素子集積モジュールとしてのODeMUXモジュールの構成を概略的に示す図である。

【符号の説明】

【0046】

100,200 OMUXモジュール(光素子集積モジュール)、

100a,200a,300a 筐体、

101,102,103,104 光データ信号入力ポート、

105 光短パルス列(光クロック信号)入力ポート、

110 光データ信号入力部、

111,112,113,114 第1乃至第4の光サーキュレータ、

120 光/光変換部、

121,122,123,124 第1乃至第4の光/光変換器、

130 光クロック信号分岐部、

131,132,133 ミラー、

141,142,143 ハーフミラー、

150 光位相調整部、

151,152,153,154 第1乃至第4の光位相調整器、

160 光時分割多重部、

161,162,163 ハーフミラー、

171,172,173,174 ミラー、

181,182,183,184 光時分割多重信号出力ポート、

250 光位相調整部、

251,252,254 第1乃至第3の光位相調整器、

260 光時分割多重部、

261,262,263 ハーフミラー、

271,272,273,174 ミラー、

300 ODeMUXモジュール(光素子集積モジュール)、

301,302,303,304 光短パルス列入力ポート、

305 光時分割多重信号入力ポート、

310 光クロック信号入力部、

311,312,313,314 第1乃至第4の入力用光サーキュレータ、

320 光/光変換部、

321,322,323,324 第1乃至第4の光/光変換器、

330 光時分割多重信号分岐部、

331,332,333,334 ミラー、

341,342,343 ハーフミラー、

350 光時分割分離信号出力部、

351,352,353,354 第1乃至第4の出力用光サーキュレータ、

361,362,363,364 光データ信号出力ポート、

A1,A2,A3,A4 第1乃至第4の光データ信号、

B0 光短パルス列、

B1,B2,B3,B4 第1乃至第4の光短パルス列、

C1,C2,C3,C4 第1乃至第4の変調光データ信号、

D1,D2,D3,D4 第1乃至第4の光時分割多重信号、

E0 光時分割多重信号、

E1,E2,E3,E4 第1乃至第4の光時分割多重信号、

F1,F2,F3,F4 第1乃至第4の光短パルス列、

G1,G2,G3,G4 第1乃至第4の変調光データ信号(第1乃至第4の光データ信号)、

P1 第1ポート、

P2 第2ポート、

P3 第3ポート、

P4 第4ポート、

P5 第5ポート、

P6 第6ポート。

【技術分野】

【0001】

本発明は、光受動素子及び光能動素子を集積することによって形成された光素子集積モジュールに関し、特に、光短パルス列を光データ信号に応じて変調する光素子集積モジュールに関するものである。

【背景技術】

【0002】

EA(エレクトロアブソープション)変調器の電解吸収効果を利用して光短パルス列を変調する技術を用いた光素子集積モジュールが、例えば、特許文献1又は非特許文献1に開示されている。

【0003】

【特許文献1】特開2005−26725号公報

【非特許文献1】村井仁著、「EA変調器を用いた160Gbit/s超高速光時分割多重/分離技術」、 O plus E、 2005年5月号、 Vol.27、 No.5、 pp.535−540

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上記従来技術においては、EA変調器に高周波電気信号を入力することによって光短パルス列を変調している。この高周波電気信号を得るためには、光データ信号を電気信号に変換するための光/電気変換装置が必要になる。また、EA変調器に高周波電気信号を入力するための電気回路も必要になる。このため、上記従来技術においては、装置の構成が複雑になり、装置の価格が高額になる問題があった。

【0005】

そこで、本発明は、上記従来技術の課題を解決するためになされたものであり、その目的は、構成の簡素化及び低価格化を実現できる、光短パルス列を変調する光素子集積モジュールを提供することにある。

【課題を解決するための手段】

【0006】

本発明の光素子集積モジュールの一形態においては、第1ポート、第2ポート、及び第3ポートを具備し、前記第1ポートに入力した光信号を前記第2ポートから出力し、前記第2ポートに入力した光信号を前記第3ポートから出力し、前記第3ポートに入力した光信号を前記第1ポートから出力する第1乃至第n(nは2以上の整数)の光サーキュレータと、外部から入力される光短パルス列を分岐して第1乃至第nの光短パルス列を生成する光クロック信号分岐部と、第1乃至第nの光データ信号のそれぞれに応じて前記第1乃至第nの光短パルス列のそれぞれを変調することによって第1乃至第nの変調光データ信号を出力する第1乃至第nの光/光変換器と、前記第1乃至第nの変調光データ信号を時分割多重して光時分割多重信号を生成する光時分割多重部とを備え、前記第1乃至第nの光データ信号のそれぞれは、外部から前記第1乃至第nの光サーキュレータの前記第1ポートのそれぞれに入力され、前記第2ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、前記第1乃至第nの変調光データ信号のそれぞれは、前記第1乃至第nの光サーキュレータの前記第2ポートのそれぞれに入力され、前記第3ポートのそれぞれを経由して前記光時分割多重部に入力されることを特徴としている。

【0007】

また、本発明の光素子集積モジュールの他の形態においては、第1ポート、第2ポート、及び第3ポートを具備し、前記第1ポートに入力した光信号を前記第2ポートから出力し、前記第2ポートに入力した光信号を前記第3ポートから出力し、前記第3ポートに入力した光信号を前記第1ポートから出力する第1乃至第n(nは2以上の整数)の入力用光サーキュレータと、第4ポート、第5ポート、及び第6ポートを具備し、前記第4ポートに入力した光信号を前記第5ポートから出力し、前記第5ポートに入力した光信号を前記第6ポートから出力し、前記第6ポートに入力した光信号を前記第4ポートから出力する第1乃至第nの出力用光サーキュレータと、第1乃至第nの光/光変換器と、外部から入力される光時分割多重信号を分岐して第1乃至第nの光時分割多重信号を生成する光時分割多重信号分岐部とを備え、前記第1乃至第nの光短パルス列のそれぞれは、外部から前記第1乃至第nの入力用光サーキュレータの前記第1ポートのそれぞれに入力され、前記第2ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、前記第1乃至第nの光時分割多重信号は、前記第1乃至第nの出力用光サーキュレータの前記第5ポートのそれぞれに入力され、前記第6ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、前記第1乃至第nの光/光変換器のそれぞれは、第1乃至第nの光時分割多重信号のそれぞれに応じて前記第1乃至第nの光短パルス列のそれぞれを変調することによって第1乃至第nの変調光データ信号を出力し、前記第1乃至第nの変調光データ信号のそれぞれは、前記第1乃至第nの出力用光サーキュレータの前記第6ポートのそれぞれに入力され、前記第4ポートのそれぞれを経由して外部に出力されることを特徴としている。

【発明の効果】

【0008】

本発明の光素子集積モジュールによれば、光短パルス列を光データ信号に応じて変調しているので、構成の簡素化及び低価格化を実現することができる。

【0009】

また、本発明の光素子集積モジュールによれば、光/光変調器から出力された変調光データ信号を、光サーキュレータを介して、光時分割多重部又は光分割分離信号出力部に導いているので、出力される光信号のパワーの損失を抑制することができる。

【発明を実施するための最良の形態】

【0010】

第1の実施形態

図1は、本発明の第1の実施形態に係る光素子集積モジュールとしての光マルチプレクサ(OMUX)モジュール100の構成を概略的に示す図である。

【0011】

図1に示されるように、第1の実施形態に係るOMUXモジュール100は、筐体100aと、筐体100a内に備えられた、光データ信号入力部110、光/光変換部120、光クロック信号分岐部130、光位相調整部150、及び光時分割多重部160を備えている。また、第1の実施形態に係るOMUXモジュール100は、筐体100aに、光データ信号入力ポート101,102,103,104と、光短パルス列(光クロック信号)入力ポート105と、光時分割多重信号出力ポート181,182,183,184を備えている。図1に示されるように、第1の実施形態においては、光データ信号入力部110は、光/光変換部120と光時分割多重部160との間に配置されている。また、第1の実施形態においては、光位相調整部150は、光データ信号入力部110と光時分割多重部160との間に配置されている。また、光/光変換部120は、光データ信号入力部110と光クロック信号分岐部130との間に配置されている。

【0012】

図1に示されるように、光データ信号入力部110は、第1乃至第4の光サーキュレータ111,112,113,114を有している。第1乃至第4の光サーキュレータ111,112,113,114のそれぞれは、第1ポートP1と、第2ポートP2と、第3ポートP3を具備している。第1乃至第4の光サーキュレータ111,112,113,114のそれぞれは、第1ポートP1に入力した光信号を第2ポートP2から出力し、第2ポートP2に入力した光信号を第3ポートP3から出力し、第3ポートP3に入力した光信号を第1ポートP1から出力する。第1乃至第4の光サーキュレータ111,112,113,114としては、例えば、対向する2つの偏光プリズム、これらの間に配置された2分の1波長板及びファラデー回転子(ガーネット膜)を配置したものを用いることができる。このような光サーキュレータは公知のものを使用でき、例えば、オプトロニクス社発行の「図解光デバイス辞典」に説明がある。

【0013】

図1に示されるように、光/光変換部120は、クロスアブソープション(相互吸収型)変調を利用した第1乃至第4の光/光変調器121,122,123,124を有している。光/光変調器121,122,123,124の具体例としては、EA変調器のクロスアブソープション効果を利用する形態が考えられる。EA変調器の通常の使用法は、高周波電気信号を入力することによって光短パルス列を変調するものである。しかし、本発明においては、高周波電気信号をデータ入力信号として使用せず、光データ信号A1,A2,A3,A4をデータ入力信号として使用する。クロスアブソープション効果は、可飽和吸収体にバイアス電圧を印加しておくと、このバイアス電圧が印加された領域に入力された第1の光が弱い間は可飽和吸収体は光の吸収体となり、第1の光が強くなると可飽和吸収体は他の光を吸収できなくなって透明体になる効果である。このクロスアブソープション効果を利用することによって、光データ信号A1,A2,A3,A4がハイレベルの期間だけ、光/光変調器光短パルス列B1,B2,B3,B4を通過させることができる。なお、EA変調器のクロスアブソープション効果は公知の技術であり、例えば、以下の文献に説明がある。

Murai, Kagawa, Tsuji, and Fujii, “80−Gb/s Error−Free Transmission Over 5600 km Using a Cross Absorption Modulation Based Optical 3R Regenerator”, IEEE PHOTONICS TECHNOLOGY LETTERS, Vol.17, No.9, September 2005, pp.1965−1967

また、光/光変調器121,122,123,124として、SOA(半導体光増幅器)のような他の変調器を用いることもできる。

【0014】

図1に示されるように、光クロック信号分岐部130は、外部から入力される光短パルス列(光クロック信号)B0を分岐して第1乃至第4の光短パルス列B1,B2,B3,B4を生成する。光クロック信号分岐部130は、光短パルス列B0を直角に反射するミラー131と、反射された光短パルス列B0を互いに直交する方向に2分岐するハーフミラー141と、ハーフミラー141を透過する光短パルス列を互いに直交する方向に2分岐するハーフミラー143と、ハーフミラー141で反射された光短パルス列を直下に反射するミラー132と、ミラー132で反射された光短パルス列を互いに直交する方向に2分岐するハーフミラー142と、ハーフミラー142で反射された光短パルス列を直角に反射するミラー133と、ハーフミラー143で反射された光短パルス列を反射するミラー134とを有している。このような構成により、外部から入力される光短パルス列(光クロック信号)B0は、第1乃至第4の光短パルス列B1,B2,B3,B4として光/光変換部120の第1乃至第4の光/光変換器121,122,123,124に入力される。なお、第1の実施形態においては、光短パルス列B0の周波数は、40GHzであり、第1乃至第4の光短パルス列B1,B2,B3,B4の周波数は、40GHzである。ただし、光クロック信号分岐部130の構成は、図示の構成に限定されない。

【0015】

図1に示されるように、光位相調整部150は、第1乃至第4の光位相調整器151,152,153,154を有している。第1乃至第4の光位相調整器151,152,153,154は、例えば、液晶部によって構成される。ただし、光位相調整部150の構成は、図示の構成に限定されない。なお、光位相調整部150は、変調された光信号の位相調整が必要でない場合には、不要な構成である。

【0016】

図1に示されるように、光時分割多重部160は、第1乃至第4の変調光データ信号C1、C2,C3,C4を時分割多重して光時分割多重信号D1,D2,D3,D4を生成する。第1の実施形態においては、第1乃至第4の変調光データ信号C1,C2,C3.C4のデータレートは、40Gbpsであり、光時分割多重信号D1,D2のデータレートは160Gbpsであり、光時分割多重信号D3,D4のデータレートは80Gbpsである。光時分割多重部160は、第3の変調光データ信号C4を直角に反射するミラー171と、第3の変調光データ信号C3を直角に反射するミラー172と、第1の変調光データ信号C1と第3の変調光データ信号C3とを光時分割多重して互いに直交する2方向に分岐するハーフミラー161と、第2の変調光データ信号C2と第4の変調光データ信号C4とを光時分割多重して互いに直交する2方向に分岐するハーフミラー162と、ハーフミラー162から出力される変調光データ信号を直角に反射するミラー173と、ハーフミラー161から出力される変調光データ信号とミラー173で反射された変調光データ信号とを時分割多重して互いに直交する2方向に分岐するハーフミラー163と、ハーフミラー163で反射された変調光データ信号を直角に反射するミラー174とを有している。ただし、光時分割多重部160の構成は、図示の構成に限定されない。

【0017】

次に、第1の実施形態に係るOMUXモジュール100の動作を説明する。第1乃至第4の光データ信号A1,A2,A3,A4のそれぞれは、外部から光データ信号入力ポート101,102,103,104を通して第1乃至第4の光サーキュレータ111,112,113,114の第1ポートP1のそれぞれに入力され、第2ポートP2を経由して第1乃至第4の光/光変換器121,122,123,124のそれぞれに入力される。

【0018】

一方、光クロック信号分岐部130は、入力ポート105を通して入力される光短パルス列B0を第1乃至第4の光短パルス列B1,B2,B3,B4に分岐し、第1乃至第4の光短パルス列B1,B2,B3,B4のそれぞれを第1乃至第4の光/光変換器121,122,123,124に入力する。光/光変換器121,122,123,124は、クロスアブソープション効果を利用して、入力される第1乃至第4の光データ信号A1,A2,A3,A4のそれぞれに応じて第1乃至第4の光短パルス列B1,B2,B3,B4のそれぞれを変調することによって第1乃至第4の変調光データ信号C1,C2,C3.C4を出力する。第1の実施形態においては、光短パルス列B0の周波数は、40GHzであり、第1乃至第4の光短パルス列B1,B2,B3,B4の周波数は、40GHzである。また、第1乃至第4の光データ信号A1,A2,A3,A4のデータレートは、40Gbpsであり、第1乃至第4の変調光データ信号C1,C2,C3.C4のデータレートは、40Gbpsである。また、光/光変換器121,122,123,124の反対の端面(図1において右側の端面)から出力された光データ信号は出力先で、全て終端される。具体的には、ハーフミラーを通り、光が集光されていないものは放射減衰して終端し、光ポートヘ達したものは、光アイソレータ(図示せず)で終端される。

【0019】

第1乃至第4の変調光データ信号C1,C2,C3,C4のそれぞれは、第1乃至第4の光サーキュレータ111,112,113,114の第2ポートP2のそれぞれに入力され、第3ポートP3のそれぞれを経由して光位相調整部150に入力され、位相調整を受けた後、光時分割多重部160に入力される。

【0020】

光時分割多重部160に入力された第1乃至第4の変調光データ信号C1,C2,C3,C4は、光時分割多重され、出力ポート181及び182から160Gbpsの光時分割多重信号D1及びD2として出力され、出力ポート183及び184から80Gbpsの光時分割多重信号D3及びD4として出力される。

【0021】

以上に説明したように、第1の実施形態に係るOMUXモジュール100によれば、光短パルス列を光データ信号に応じて変調しているので、光データ信号を高周波電気信号に変換する電気回路や高周波電気信号を印加する電気回路が不要になり、装置の構成の簡素化及び低価格化を実現することができる。

【0022】

また、第1の実施形態に係るOMUXモジュール100によれば、第1乃至第4の光サーキュレータ111,112,113,114を用いることによって、第1乃至第4の変調光データ信号C1,C2,C3,C4を、光時分割多重部160に導いているので、第1乃至第4の光サーキュレータ111,112,113,114に代えてハーフミラーを用いる形態(常に3dB(パワーの半分)を損失する形態)に比べて、第1乃至第4の変調光データ信号C1,C2,C3,C4のパワーを損失せずに合波できるため、出力される光時分割多重信号のS/Nを向上させることができる。

【0023】

なお、第1の実施形態においては、入力データ信号が4入力であり、光サーキュレータ、光/光変調器、及び光位相調整器のそれぞれの数が4の場合を例示したが、これらの数は2以上であれば幾つでもよい。

【0024】

また、第1の実施形態においては、入力データ信号が40Gbps、光時分割多重信号が160Gbps,80Gbpsの場合を例示したが、他のデータレートを適用することも可能である。

【0025】

第2の実施形態

図2は、本発明の第2の実施形態に係る光素子集積モジュールとしての光マルチプレクサ(OMUX)Xモジュール200の構成を概略的に示す図である。図2において、図1に示される構成と、同一又は対応する構成には、同じ符号を付して、その説明を省略する。

【0026】

図2に示されるように、第2の実施形態に係るOMUXモジュール200は、筐体200a内の構成のうち、光位相調整部250と光時分割多重部260の構成が、第1の実施形態に係るOMUXモジュール100の構成と相違する。

【0027】

第1の実施形態においては、光位相調整部150は、光データ信号入力部110と光時分割多重部160との間に配置されているが、第2の実施形態においては、光位相調整部250は、光サーキュレータ111の第3ポートP3からの変調光データ信号の位相を調整する光位相調整器251と、光サーキュレータ114の第3ポートP3からの変調光データ信号の位相を調整する光位相調整器254と、光サーキュレータ111の第3ポートP3からの変調光データ信号と光位相調整器254からの変調光データ信号とが入力されるハーフミラー262からの出力を受ける光位相調整器252とを有している。

【0028】

第1の実施形態においては、光位相制御は各パスで各々行う構成を採用していたので、多重後の信号が更に多重される場合に、2つの位相調整器を同時に制御する必要があったが、第2の実施形態においては、位相調整器252をハーフミラー262の下流側に配置したので位相調整器252を制御する1つの制御部を制御すればよい。

【0029】

以上に説明したように、第2の実施形態に係るOMUXモジュール200によれば、上記第1の実施形態の効果に加え、光位相調整部250の構成の簡素化及び位相調整制御の簡素化を実現できる。

【0030】

なお、第2の実施形態において、上記以外の点は、第1の実施形態の場合と同じである。

【0031】

第3の実施形態

図3は、本発明の第3の実施形態に係る光素子集積モジュールとしての光デマルチプレクサ(ODeMUX)モジュール300の構成を概略的に示す図である。

【0032】

図3に示されるように、第3の実施形態に係るODeMUXモジュール300は、筐体300aと、筐体300a内に備えられた、光クロック信号入力部310、光/光変換部320、光時分割多重信号分岐部330、及び光時分割分離信号出力部350を備えている。また、第3の実施形態に係るODeMUXモジュール300は、筐体300aに、光短パルス列(光クロック信号)入力ポート301,302,303,304と、光時分割多重信号入力ポート305と、光データ信号出力ポート361,362,363,364を備えている。図3に示されるように、第3の実施形態においては、光/光変換器320は、光クロック信号入力部310と光時分割分離信号出力部350との間に配置され、光時分割分離信号出力部350は、光/光変換器320と光時分割多重信号分岐部330との間に配置されている。

【0033】

図3に示されるように、光クロック信号入力部310は、第1乃至第4の入力用光サーキュレータ311,312,313,314を有している。第1乃至第4の入力用光サーキュレータ311,312,313,314のそれぞれは、第1ポートP1と、第2ポートP2と、第3ポートP3を具備している。第1乃至第4の入力用光サーキュレータ311,312,313,314のそれぞれは、第1ポートP1に入力した光信号を第2ポートP2から出力し、第2ポートP2に入力した光信号を第3ポートP3から出力し、第3ポートP3に入力した光信号を第1ポートP1から出力する。第1乃至第4の入力用光サーキュレータ311,312,313,314の構成は、第1の実施形態の光サーキュレータと同じである。

【0034】

図3に示されるように、光/光変換部320は、クロスアブソープション(相互吸収型)変調を利用した第1乃至第4の光/光変調器321,322,323,324を有している。第1乃至第4の光/光変調器321,322,323,324は、第1の実施形態の光/光変調器と同じである。また、第1乃至第4の光/光変調器321,322,323,324として、SOA(半導体光増幅器)のような他の変調器を用いることもできる。

【0035】

図3に示されるように、光時分割多重信号分岐部330は、外部から入力される光時分割多重信号E0(160Gbps,+16dBm)を分岐して第1乃至第4の光時分割多重信号E1,E2,E3,E4(160Gbps)を生成する。光時分割多重信号分岐部330は、光時分割多重信号E0を直角に反射するミラー331と、反射された光時分割多重信号E0を互いに直交する方向に2分岐するハーフミラー341と、ハーフミラー341を透過する光時分割多重信号を互いに直交する方向に2分岐するハーフミラー343と、ハーフミラー341で反射された光時分割多重信号を直角に反射するミラー332と、ミラー332で反射された光時分割多重信号を互いに直交する方向に2分岐するハーフミラー342と、ハーフミラー342で反射された光時分割多重信号を直角に反射するミラー333と、ハーフミラー343で反射された光時分割多重信号を反射するミラー334とを有している。ただし、光時分割多重信号分岐部330の構成は、図示の構成に限定されない。

【0036】

図3に示されるように、光時分割分離信号出力部350は、第1乃至第4の出力用光サーキュレータ351,352,353,354を有している。第1乃至第4の出力用光サーキュレータ351,352,353,354のそれぞれは、第4ポートP4と、第5ポートP5と、第6ポートP6を具備している。第1乃至第4の出力用光サーキュレータ351,352,353,354のそれぞれは、第4ポートP4に入力した光信号を第5ポートP5から出力し、第5ポートP5に入力した光信号を第6ポートP6から出力し、第6ポートP6に入力した光信号を第4ポートP4から出力する。第1乃至第4の出力用光サーキュレータ351,352,353,354の構成は、第1の実施形態の光サーキュレータと同じである。ただし、光時分割分離信号出力部350の構成は、図示の構成に限定されない。例えば、第1乃至第4の出力用光サーキュレータ351,352,353,354を上下反転させ、光の進行方向を反時計回り方向にすることによって、出力ポート361,362,363,364を図3における下側に備えることもできる。

【0037】

次に、第3の実施形態に係るODeMUXモジュール300の動作を説明する。

第1乃至第4の光短パルス列(光クロック信号)F1,F2,F3,F4のそれぞれは、外部から入力ポート301,302,303,304を介して第1乃至第4の入力用光サーキュレータ311,312,313,314の第1ポートP1のそれぞれに入力され、第2ポートP2のそれぞれを経由して第1乃至第4の光/光変換器321,322,323,324のそれぞれに入力される。

【0038】

一方、光時分割多重信号分岐部330の入力ポート305に入力された光時分割多重信号E0から生成された第1乃至第4の光時分割多重信号E1,E2,E3,E4は、第1乃至第4の出力用光サーキュレータ351,352,353,354の第5ポートP5のそれぞれに入力され、第6ポートP6のそれぞれを経由して第1乃至第4の光/光変換器321,322,323,324のそれぞれに入力される。

【0039】

第1乃至第4の光/光変換器321,322,323,324のそれぞれは、第1乃至第4の光時分割多重信号E1,E2,E3,E4のそれぞれに応じて第1乃至第4の光短パルス列F1,F2,F3,F4のそれぞれを変調することによって第1乃至第4の変調光データ信号G1,G2,G3,G4を出力する。

【0040】

第1乃至第4の光/光変換器321,322,323,324から出力された第1乃至第4の変調光データ信号G1,G2,G3,G4のそれぞれは、第1乃至第4の出力用光サーキュレータ351,352,353,354の第6ポートP6のそれぞれに入力され、第4ポートP4のそれぞれを経由して、出力ポート361,362,363,364を介して外部に出力される。

【0041】

以上に説明したように、第3の実施形態に係るODeMUXモジュール300によれば、光短パルス列を光データ信号に応じて変調しているので、光データ信号を高周波電気信号に変換する電気回路や高周波電気信号を印加する電気回路が不要になり、装置の構成の簡素化及び低価格化を実現することができる。

【0042】

また、第3の実施形態に係るODeMUXモジュール300によれば、第1乃至第4の入力用光サーキュレータ311,312,313,314を用いることによって、第1乃至第4の光短パルス列F1,F2,F3,F4を、光/光変換部320に導いているので、第1乃至第4の入力用光サーキュレータ311,312,313,314に代えてハーフミラーを用いる形態(常に3dB(パワーの半分)を損失する形態)に比べて、第1乃至第4の光短パルス列F1,F2,F3,F4のパワーを損失せずに合波できるため、出力される光データ信号361,362,363,364のS/Nを向上させることができる。

【0043】

なお、第3の実施形態においては、入力データ信号が4入力であり、光サーキュレータ、及び光/光変調器のそれぞれの数が4の場合を例示したが、これらの数は2以上であれば幾つでもよい。

【0044】

また、第3の実施形態においては、光時分割多重信号E0が160Gbps、光短パルス列が40GHzの場合を例示したが、他の周波数又はデータレートを適用することも可能である。

【図面の簡単な説明】

【0045】

【図1】本発明の第1の実施形態に係る光素子集積モジュールとしてのOMUXモジュールの構成を概略的に示す図である。

【図2】本発明の第2の実施形態に係る光素子集積モジュールとしてのOMUXモジュールの構成を概略的に示す図である。

【図3】本発明の第3の実施形態に係る光素子集積モジュールとしてのODeMUXモジュールの構成を概略的に示す図である。

【符号の説明】

【0046】

100,200 OMUXモジュール(光素子集積モジュール)、

100a,200a,300a 筐体、

101,102,103,104 光データ信号入力ポート、

105 光短パルス列(光クロック信号)入力ポート、

110 光データ信号入力部、

111,112,113,114 第1乃至第4の光サーキュレータ、

120 光/光変換部、

121,122,123,124 第1乃至第4の光/光変換器、

130 光クロック信号分岐部、

131,132,133 ミラー、

141,142,143 ハーフミラー、

150 光位相調整部、

151,152,153,154 第1乃至第4の光位相調整器、

160 光時分割多重部、

161,162,163 ハーフミラー、

171,172,173,174 ミラー、

181,182,183,184 光時分割多重信号出力ポート、

250 光位相調整部、

251,252,254 第1乃至第3の光位相調整器、

260 光時分割多重部、

261,262,263 ハーフミラー、

271,272,273,174 ミラー、

300 ODeMUXモジュール(光素子集積モジュール)、

301,302,303,304 光短パルス列入力ポート、

305 光時分割多重信号入力ポート、

310 光クロック信号入力部、

311,312,313,314 第1乃至第4の入力用光サーキュレータ、

320 光/光変換部、

321,322,323,324 第1乃至第4の光/光変換器、

330 光時分割多重信号分岐部、

331,332,333,334 ミラー、

341,342,343 ハーフミラー、

350 光時分割分離信号出力部、

351,352,353,354 第1乃至第4の出力用光サーキュレータ、

361,362,363,364 光データ信号出力ポート、

A1,A2,A3,A4 第1乃至第4の光データ信号、

B0 光短パルス列、

B1,B2,B3,B4 第1乃至第4の光短パルス列、

C1,C2,C3,C4 第1乃至第4の変調光データ信号、

D1,D2,D3,D4 第1乃至第4の光時分割多重信号、

E0 光時分割多重信号、

E1,E2,E3,E4 第1乃至第4の光時分割多重信号、

F1,F2,F3,F4 第1乃至第4の光短パルス列、

G1,G2,G3,G4 第1乃至第4の変調光データ信号(第1乃至第4の光データ信号)、

P1 第1ポート、

P2 第2ポート、

P3 第3ポート、

P4 第4ポート、

P5 第5ポート、

P6 第6ポート。

【特許請求の範囲】

【請求項1】

第1ポート、第2ポート、及び第3ポートを具備し、前記第1ポートに入力した光信号を前記第2ポートから出力し、前記第2ポートに入力した光信号を前記第3ポートから出力し、前記第3ポートに入力した光信号を前記第1ポートから出力する第1乃至第n(nは2以上の整数)の光サーキュレータと、

外部から入力される光短パルス列を分岐して第1乃至第nの光短パルス列を生成する光クロック信号分岐部と、

第1乃至第nの光データ信号のそれぞれに応じて前記第1乃至第nの光短パルス列のそれぞれを変調することによって第1乃至第nの変調光データ信号を出力する第1乃至第nの光/光変換器と、

前記第1乃至第nの変調光データ信号を時分割多重して光時分割多重信号を生成する光時分割多重部と

を備え、

前記第1乃至第nの光データ信号のそれぞれは、外部から前記第1乃至第nの光サーキュレータの前記第1ポートのそれぞれに入力され、前記第2ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、

前記第1乃至第nの変調光データ信号のそれぞれは、前記第1乃至第nの光サーキュレータの前記第2ポートのそれぞれに入力され、前記第3ポートのそれぞれを経由して前記光時分割多重部に入力される

ことを特徴とする光素子集積モジュール。

【請求項2】

前記第1乃至第nの光/光変換器のそれぞれは、クロスアブソープション変調を利用した変調器であることを特徴とする請求項1に記載の光素子集積モジュール。

【請求項3】

前記第1乃至第nの光サーキュレータは、前記第1乃至第nの光/光変換器と前記光時分割多重部との間に配置されたことを特徴とする請求項1又は2に記載の光素子集積モジュール。

【請求項4】

前記第1乃至第nの変調光データ信号のそれぞれ又は幾つかの位相を変調する光位相調整部を備えたことを特徴とする請求項1乃至3のいずれか1項に記載の光素子集積モジュール。

【請求項5】

nは4であり、

前記光短パルス列の周波数は、40GHzであり、

第1乃至第nの光短パルス列の周波数は、40GHzであり、

前記第1乃至第nの光データ信号のデータレートは、40Gbpsであり、

前記光時分割多重信号は、データレートが160Gbpsの光信号を含む

ことを特徴とする請求項1乃至4のいずれか1項に記載の光素子集積モジュール。

【請求項6】

第1ポート、第2ポート、及び第3ポートを具備し、前記第1ポートに入力した光信号を前記第2ポートから出力し、前記第2ポートに入力した光信号を前記第3ポートから出力し、前記第3ポートに入力した光信号を前記第1ポートから出力する第1乃至第n(nは2以上の整数)の入力用光サーキュレータと、

第4ポート、第5ポート、及び第6ポートを具備し、前記第4ポートに入力した光信号を前記第5ポートから出力し、前記第5ポートに入力した光信号を前記第6ポートから出力し、前記第6ポートに入力した光信号を前記第4ポートから出力する第1乃至第nの出力用光サーキュレータと、

第1乃至第nの光/光変換器と、

外部から入力される光時分割多重信号を分岐して第1乃至第nの光時分割多重信号を生成する光時分割多重信号分岐部と

を備え、

前記第1乃至第nの光短パルス列のそれぞれは、外部から前記第1乃至第nの入力用光サーキュレータの前記第1ポートのそれぞれに入力され、前記第2ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、

前記第1乃至第nの光時分割多重信号は、前記第1乃至第nの出力用光サーキュレータの前記第5ポートのそれぞれに入力され、前記第6ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、

前記第1乃至第nの光/光変換器のそれぞれは、第1乃至第nの光時分割多重信号のそれぞれに応じて前記第1乃至第nの光短パルス列のそれぞれを変調することによって第1乃至第nの変調光データ信号を出力し、

前記第1乃至第nの変調光データ信号のそれぞれは、前記第1乃至第nの出力用光サーキュレータの前記第6ポートのそれぞれに入力され、前記第4ポートのそれぞれを経由して外部に出力される

ことを特徴とする光素子集積モジュール。

【請求項7】

前記第1乃至第nの光/光変換器のそれぞれは、クロスアブソープション変調を利用した変調器であることを特徴とする請求項6に記載の光素子集積モジュール。

【請求項8】

前記第1乃至第nの光/光変換器は、前記第1乃至第nの入力用光サーキュレータと前記第1乃至第nの出力用光サーキュレータとの間に配置され、

前記第1乃至第nの出力用光サーキュレータは、前記第1乃至第nの光/光変換器と前記光時分割多重信号分岐部との間に配置された

ことを特徴とする請求項6又は7に記載の光素子集積モジュール。

【請求項9】

nは4であり、

前記第1乃至第nの光短パルス列の周波数は、40GHzであり、

前記光時分割多重信号のデータレートは、160Gbpsであり、

前記第1乃至第nの光時分割多重信号のデータレートは、160Gbpsであり、

前記第1乃至第nの変調光データ信号のデータレートは、40Gbpsである

ことを特徴とする請求項6乃至8のいずれか1項に記載の光素子集積モジュール。

【請求項1】

第1ポート、第2ポート、及び第3ポートを具備し、前記第1ポートに入力した光信号を前記第2ポートから出力し、前記第2ポートに入力した光信号を前記第3ポートから出力し、前記第3ポートに入力した光信号を前記第1ポートから出力する第1乃至第n(nは2以上の整数)の光サーキュレータと、

外部から入力される光短パルス列を分岐して第1乃至第nの光短パルス列を生成する光クロック信号分岐部と、

第1乃至第nの光データ信号のそれぞれに応じて前記第1乃至第nの光短パルス列のそれぞれを変調することによって第1乃至第nの変調光データ信号を出力する第1乃至第nの光/光変換器と、

前記第1乃至第nの変調光データ信号を時分割多重して光時分割多重信号を生成する光時分割多重部と

を備え、

前記第1乃至第nの光データ信号のそれぞれは、外部から前記第1乃至第nの光サーキュレータの前記第1ポートのそれぞれに入力され、前記第2ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、

前記第1乃至第nの変調光データ信号のそれぞれは、前記第1乃至第nの光サーキュレータの前記第2ポートのそれぞれに入力され、前記第3ポートのそれぞれを経由して前記光時分割多重部に入力される

ことを特徴とする光素子集積モジュール。

【請求項2】

前記第1乃至第nの光/光変換器のそれぞれは、クロスアブソープション変調を利用した変調器であることを特徴とする請求項1に記載の光素子集積モジュール。

【請求項3】

前記第1乃至第nの光サーキュレータは、前記第1乃至第nの光/光変換器と前記光時分割多重部との間に配置されたことを特徴とする請求項1又は2に記載の光素子集積モジュール。

【請求項4】

前記第1乃至第nの変調光データ信号のそれぞれ又は幾つかの位相を変調する光位相調整部を備えたことを特徴とする請求項1乃至3のいずれか1項に記載の光素子集積モジュール。

【請求項5】

nは4であり、

前記光短パルス列の周波数は、40GHzであり、

第1乃至第nの光短パルス列の周波数は、40GHzであり、

前記第1乃至第nの光データ信号のデータレートは、40Gbpsであり、

前記光時分割多重信号は、データレートが160Gbpsの光信号を含む

ことを特徴とする請求項1乃至4のいずれか1項に記載の光素子集積モジュール。

【請求項6】

第1ポート、第2ポート、及び第3ポートを具備し、前記第1ポートに入力した光信号を前記第2ポートから出力し、前記第2ポートに入力した光信号を前記第3ポートから出力し、前記第3ポートに入力した光信号を前記第1ポートから出力する第1乃至第n(nは2以上の整数)の入力用光サーキュレータと、

第4ポート、第5ポート、及び第6ポートを具備し、前記第4ポートに入力した光信号を前記第5ポートから出力し、前記第5ポートに入力した光信号を前記第6ポートから出力し、前記第6ポートに入力した光信号を前記第4ポートから出力する第1乃至第nの出力用光サーキュレータと、

第1乃至第nの光/光変換器と、

外部から入力される光時分割多重信号を分岐して第1乃至第nの光時分割多重信号を生成する光時分割多重信号分岐部と

を備え、

前記第1乃至第nの光短パルス列のそれぞれは、外部から前記第1乃至第nの入力用光サーキュレータの前記第1ポートのそれぞれに入力され、前記第2ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、

前記第1乃至第nの光時分割多重信号は、前記第1乃至第nの出力用光サーキュレータの前記第5ポートのそれぞれに入力され、前記第6ポートのそれぞれを経由して前記第1乃至第nの光/光変換器のそれぞれに入力され、

前記第1乃至第nの光/光変換器のそれぞれは、第1乃至第nの光時分割多重信号のそれぞれに応じて前記第1乃至第nの光短パルス列のそれぞれを変調することによって第1乃至第nの変調光データ信号を出力し、

前記第1乃至第nの変調光データ信号のそれぞれは、前記第1乃至第nの出力用光サーキュレータの前記第6ポートのそれぞれに入力され、前記第4ポートのそれぞれを経由して外部に出力される

ことを特徴とする光素子集積モジュール。

【請求項7】

前記第1乃至第nの光/光変換器のそれぞれは、クロスアブソープション変調を利用した変調器であることを特徴とする請求項6に記載の光素子集積モジュール。

【請求項8】

前記第1乃至第nの光/光変換器は、前記第1乃至第nの入力用光サーキュレータと前記第1乃至第nの出力用光サーキュレータとの間に配置され、

前記第1乃至第nの出力用光サーキュレータは、前記第1乃至第nの光/光変換器と前記光時分割多重信号分岐部との間に配置された

ことを特徴とする請求項6又は7に記載の光素子集積モジュール。

【請求項9】

nは4であり、

前記第1乃至第nの光短パルス列の周波数は、40GHzであり、

前記光時分割多重信号のデータレートは、160Gbpsであり、

前記第1乃至第nの光時分割多重信号のデータレートは、160Gbpsであり、

前記第1乃至第nの変調光データ信号のデータレートは、40Gbpsである

ことを特徴とする請求項6乃至8のいずれか1項に記載の光素子集積モジュール。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2008−271184(P2008−271184A)

【公開日】平成20年11月6日(2008.11.6)

【国際特許分類】

【出願番号】特願2007−111373(P2007−111373)

【出願日】平成19年4月20日(2007.4.20)

【国等の委託研究の成果に係る記載事項】(出願人による申告)国等の委託研究の成果に係る特許出願(平成18年度独立行政法人情報通信研究機構「超高速光マルチメディア配信システムの研究開発」委託研究、産業活力再生特別措置法第30条の適用を受ける特許出願)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【Fターム(参考)】

【公開日】平成20年11月6日(2008.11.6)

【国際特許分類】

【出願日】平成19年4月20日(2007.4.20)

【国等の委託研究の成果に係る記載事項】(出願人による申告)国等の委託研究の成果に係る特許出願(平成18年度独立行政法人情報通信研究機構「超高速光マルチメディア配信システムの研究開発」委託研究、産業活力再生特別措置法第30条の適用を受ける特許出願)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【Fターム(参考)】

[ Back to top ]