光電変換システム

【課題】被写体の撮像と並行して、A/D変換器に供給されるカウント信号の検査を行うことができる光電変換システムを提供することを課題とする。

【解決手段】マトリクス状に配置された複数の画素と、ランプ信号を生成する参照信号生成部と、列毎に配置され、画素からの信号をA/D変換するA/D変換器と、ランプ信号の出力に合わせてカウント動作を行い、カウント信号をカウント信号線を介してA/D変換器に供給するカウンタと、A/D変換器とは独立して設けられ、カウント信号の期待値とカウント信号線を介して供給されるカウンタからのカウント信号とを照合することによりカウンタの検査を行うカウンタ検査回路を備え、被写体の撮像と並行に、カウント信号の検査を行えるようにする。

【解決手段】マトリクス状に配置された複数の画素と、ランプ信号を生成する参照信号生成部と、列毎に配置され、画素からの信号をA/D変換するA/D変換器と、ランプ信号の出力に合わせてカウント動作を行い、カウント信号をカウント信号線を介してA/D変換器に供給するカウンタと、A/D変換器とは独立して設けられ、カウント信号の期待値とカウント信号線を介して供給されるカウンタからのカウント信号とを照合することによりカウンタの検査を行うカウンタ検査回路を備え、被写体の撮像と並行に、カウント信号の検査を行えるようにする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光電変換システムに関する。

【背景技術】

【0002】

アナログデジタル変換器(A/D変換器)を内蔵したイメージセンサ等の光電変換装置において、A/D変換器の故障診断回路を内蔵するものが提案されている。特許文献1では、画素信号の代わりに検査用信号を入力するなどして、列毎に設けてあるラッチ(列メモリ)に任意の時刻でカウント信号を書き込み、これを読み出すことで、故障診断を行っている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−331883号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1に記載のイメージセンサの故障診断回路には、以下のような問題がある。A/D変換器に供給されるカウント信号のリニアリティを確認しようとする場合には、画像信号を読み出すためのラッチ(列メモリ)にカウント信号を書き込むことにより検査を行うので、検査を行っている期間は撮像ができないという問題がある。このため、例えばイメージセンサの出荷テストを行う場合に、被写体の撮影による画素部欠陥の有無を検出する検査と、A/D変換器に供給されるカウント信号のリニアリティの検査とは、別々に行う必要があり、検査時間の増加につながっていた。

【0005】

本発明の目的は、被写体の撮像と並行して、A/D変換器に供給されるカウント信号の検査を行うことができる光電変換システムを提供することである。

【課題を解決するための手段】

【0006】

本発明の光電変換システムは、各々が光電変換素子を含み、マトリクス状に配列された複数の画素と、時間の経過にともなって信号レベルが単調に変化する参照信号を生成する参照信号生成部と、前記画素の列毎に配置され、前記画素からの信号をアナログデジタル変換するA/D変換器と、前記参照信号生成部からの参照信号の出力に合わせてカウント動作を行い、カウント信号をカウント信号線を介して前記A/D変換器に供給するカウンタとを備え、前記A/D変換器は、前記画素からの信号と前記参照信号生成部により生成された前記参照信号とを比較する比較器と、前記カウンタからのカウント信号を、前記比較器の出力が反転したときに記憶する記憶部とを有し、前記カウント信号線に接続され、かつ前記A/D変換器とは独立して設けられ、カウント信号の期待値と、前記カウント信号線を介して供給される前記カウンタからのカウント信号とを照合することにより前記カウンタの検査を行う検査回路を備えることを特徴とする。

【発明の効果】

【0007】

本発明によれば、被写体の撮像と並行して、カウント信号の検査を行うことができ、検査時間を短縮することができる。

【図面の簡単な説明】

【0008】

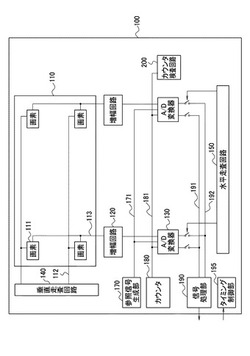

【図1】本発明の第1の実施形態に係る光電変換システムの構成例を示す図である。

【図2】本発明の実施形態に係る画素の構成例を示す図である。

【図3】本発明の実施形態に係る増幅回路の構成例を示す図である。

【図4】本発明の実施形態に係るA/D変換器の構成例を示す図である。

【図5】本発明の実施形態に係る信号波形を示すタイミングチャートである。

【図6】本発明の実施形態に係るカウンタ検査回路の構成例を示す図である。

【図7】本発明の実施形態に係るカウンタ検査回路の動作例を示すフローチャートである。

【図8】本発明の実施形態に係るカウンタ検査の期待値の一例を示す図である。

【図9】本発明の第2の実施形態に係る光電変換システムの構成例を示す図である。

【図10】本発明の第3の実施形態に係る光電変換システムの構成例を示す図である。

【図11】本発明の第3の実施形態に係る調整回路の構成例を示す図である。

【図12】本発明の実施形態に係るラッチパルス生成を示すタイミングチャートである。

【発明を実施するための形態】

【0009】

以下、本発明の実施形態を図面に基づいて説明する。なお、以下の説明において、図面を通じて同一の構成要素には同一の符号を付し、重複する説明は省略する。

【0010】

(第1の実施形態)

本発明の第1の実施形態について説明する。

図1は、第1の実施形態に係る光電変換システムの構成例を示すブロック図である。光電変換装置100は、例えばCMOSイメージセンサであり、本実施形態に係る光電変換システムを有する。光電変換装置100は、被写体像を示す入射光を光電変換し、光電変換により得られた電気信号をデジタルデータとして外部に出力する。光電変換装置100は、画素アレイ110、増幅回路120、A/D変換器130、垂直走査回路140、水平走査回路150、参照信号生成部170、カウンタ180、信号処理回路190、タイミング制御部195、及びカウンタ検査回路200を有する。

【0011】

画素アレイ110は、光電変換素子を含む複数の画素111を有し、それらがマトリクス状に(行方向及び列方向に)配置されている。図1においては、簡単のために4つの画素111を示しているが、画素111の個数はこれに限られず、より多くの画素を有する。各画素111において、光電変換装置100への入射光がアナログ信号へ光電変換される。

【0012】

垂直走査回路140は、画素行毎に配置された行制御線112に駆動パルス信号を順番に供給する。行制御線112に駆動パルス信号が供給されると、対応する画素行に含まれる各画素111からアナログ信号が列信号線113に読み出される。本実施形態では、画素アレイ110からのアナログ信号として、画素111のリセットレベルの信号であるノイズ信号と、光電変換により発生した電荷に応じた信号にノイズ信号が重畳した画素信号とが読み出される。画素信号からノイズ信号を引いた値が有効な画素値を表す。

【0013】

増幅回路120及びA/D変換器(アナログデジタル変換器)130は、画素アレイ110の各列に対応して、列信号線113毎に設けられる。増幅回路120は、列信号線113を介して画素111から入力されたアナログ信号を増幅してA/D変換器130へ供給する。A/D変換器130は、入力されたアナログ信号をデジタルデータにアナログデジタル変換(A/D変換)して出力する。

【0014】

参照信号生成部170は、参照信号であるランプ信号を生成し、生成したランプ信号をランプ信号線171を通じて各A/D変換器130に供給する。ここで、ランプ信号は、時間の経過にともなって信号レベル(信号の大きさ)が単調に変化する信号であり、例えば出力電圧が時間の経過とともに単調増加若しくは単調減少する信号である。カウンタ180は、参照信号生成部170からのランプ信号の出力に合わせてカウント動作を行い、カウント値を表現する信号であるカウント信号をカウント信号線181を通じて各A/D変換器130に供給する。カウンタ180の種類は任意であり、例えばグレイカウンタやバイナリカウンタを用いてもよく、カウンタ180はアップダウン機能を有してもよい。本実施形態では、複数のA/D変換器130が、参照信号生成部170及びカウンタ180を共有する例を示すが、A/D変換器130毎に、これらの構成要素を有してもよい。

【0015】

水平走査回路150は、A/D変換器130が出力するデジタルデータを列毎にデジタル信号線191、192に転送する。デジタル信号線191、192に転送されたデジタルデータは、信号処理部190に供給される。本実施形態では、デジタル信号線191、192に、それぞれノイズ信号を表すデジタルデータと画素信号を表すデジタルデータとが順次読み出される。信号処理部190は、画素信号を表すデジタルデータからノイズ信号を表すデジタルデータを減算して、有効な画素値を外部に出力する。

【0016】

タイミング制御部195は、前述した各構成要素に制御信号を供給して光電変換装置100の動作を制御する。なお、図1においては、タイミング制御部195から各構成要素へ制御信号を送信するための信号線は図示していない。カウンタ検査回路200は、A/D変換器130とは独立して設けられており、カウント信号線181を介してカウンタ180からカウント信号が供給され、供給されるカウント信号に基づいてカウンタ180の出力の検査を行う。

【0017】

本実施形態においては、光電変換装置100が増幅回路120を含むことによって、A/D変換器130で発生するノイズの影響を軽減できる。しかし、光電変換装置100は増幅回路120を含まずに、画素111からのアナログ信号が列信号線113を介して直接にA/D変換器130へ供給されるようにしてもよい。また、図1に示した例では、画素アレイ110の一方の側に増幅回路120、A/D変換器130及び水平走査回路150が配置されるが、これらの構成要素が画素アレイ110の両側に配置され、画素列毎に何れか一方の側の構成要素に振り分けられてもよい。

【0018】

図2は、画素111の構成例を示す図である。画素111は、その画素値を算出するためのアナログ信号をA/D変換器130に供給できれば如何なる構成であってもよい。画素111は、光電変換を行う光電変換素子(フォトダイオード)114及び複数のトランジスタ115、116、117、118を有する。光電変換素子114は、転送スイッチ115を介してフローティングディフュージョン部FDに接続される。フローティングディフュージョン部FDはまた、リセットスイッチ116を介して電圧源VDDに接続されるとともに、増幅トランジスタ117のゲート電極に接続される。増幅トランジスタ117は、第1主電極が電圧源VDDに接続され、第2主電極が行選択スイッチ118を介して列信号線113に接続される。行選択スイッチ118のゲート電極は、行制御線112の1つである行選択線PSELに接続される。リセットスイッチ116のゲート電極は、行制御線112の1つであるリセット線PRESに接続される。また、転送スイッチ115のゲート電極は、行制御線の1つである転送線PTXに接続される。

【0019】

図3は、増幅回路120の構成例を示す図である。増幅回路120は、画素111の画素値を算出するためのアナログ信号をA/D変換器130に供給できれば如何なる構成であってもよい。増幅回路120は、例えば図3に示す反転アンプである。増幅器121の反転入力端子は、クランプ容量COを介して列信号線113に接続され、増幅器121の非反転入力端子には電圧VCORが供給される。増幅器121の出力端子は、A/D変換器130に接続される。また、増幅器121の反転入力端子と出力端子との間に、帰還容量CF及びアンプリセットスイッチ122が並列に接続される。図3に示したように構成することにより、増幅回路120は、列信号線113を介して入力された信号をクランプ容量COと帰還容量CFとの容量値の比で増幅し出力する。

【0020】

図4は、A/D変換器130の構成例を示す図である。

入力端子INには、列信号線113を介してアナログ信号が入力される。比較器131は、入力端子INより入力されたアナログ信号の電圧とランプ信号線171を介して供給される比較対象のランプ信号の電圧とを比較し、その比較結果に応じたレベルの出力信号CMPOを出力する。比較器131の出力信号CMPOは、RSフリップフロップ138のS入力に入力される。RSフリップフロップ138のQ出力、及びディレイ生成用バッファにより遅延されたRSフリップフロップ138のQB(Qバー)出力が、ANDゲート(論理積演算回路)139に入力される。このようにして、ANDゲート139に入力されるRSフリップフロップ138のQB出力が反転するのが遅れ、ANDゲート139の出力は、図12に示すように比較器131の出力信号CMPOの変化に応じて細幅パルスQ*QB’を出力する。ラッチ回路(LNW、LSW、LNR、LSR)132、133、134、135は、記憶部であり、比較器131の出力信号CMPOに応じてデジタルデータを記憶する。ラッチ回路(LNW)132のD入力及びラッチ回路(LSW)133のD入力は、ともにカウント信号線181に接続される。ラッチ回路(LNW)132のG入力は、ANDゲート139の出力及び制御信号PMSELNを入力とするANDゲート136の出力線に接続される。ラッチ回路(LSW)133のG入力は、ANDゲート139の出力及び制御信号PMSELSを入力とするANDゲート137の出力線に接続される。ラッチ回路(LNW)132のQ出力は、ラッチ回路(LNR)134のD入力に接続され、ラッチ回路(LSW)133のQ出力は、ラッチ回路(LSR)135のD入力に接続される。ラッチ回路(LNR)134のG入力及びラッチ回路(LSR)135のG入力は、ともに制御線PMTXに接続される。ラッチ回路(LNR)134のQ出力は、出力端子OUTNに接続され、ラッチ回路(LSR)135のQ出力は、出力端子OUTSに接続される。

【0021】

次に、図1に示した光電変換システムの動作について説明する。図5は、第1の実施形態に係る信号波形を示すタイミングチャートであり、画素行1行分の画素111のアナログ信号(光電変換信号)がA/D変換器130でデジタルデータに変換されるまでの動作を説明するためのタイミングチャートを示している。なお、以下の説明では、信号のハイレベルを“H”と記し、信号のローレベルを“L”と記す。

【0022】

まず、時刻t0において、行選択パルスPSELが“H”となることで行選択スイッチ118がオン(導通状態)になり、任意の行に配列された画素111が列信号線113に接続される。時刻t0〜t1の期間に、画素リセットパルスPRESが“H”となり、リセットスイッチ116によって、画素111のフローティングディフュージョン部FDがリセットされる。そして、画素111のリセット状態に対応した出力(以下、画素リセットレベルと呼ぶ)が、列信号線113に出力される。時刻t0〜t2の期間に、リセットパルスPC0Rが“H”となることで増幅回路120のアンプリセットスイッチ122がオン(導通状態)になり、画素リセットレベルをクランプする。このときの増幅器121の出力AMPOを、以下Nレベルと呼ぶ。

【0023】

続いて、時刻t2〜t5の期間において、A/D変換器130が、Nレベルをアナログ入力として、対応するデジタルデータに変換する第1のA/D変換処理を行う。時刻t2〜t3において、コンパレータリセットパルスPCMPRが“H”となり、増幅器121から出力されるNレベルおよび参照信号生成部170で生成される基準電圧がそれぞれ入力容量でクランプされる。その後、コンパレータリセットパルスPCMPRが“L”となり、それぞれの入力容量にクランプされた電圧の差電圧が比較器131の初期値となる。その後、参照信号生成部170からのランプ信号VRMPは、いったん基準電圧より所定電圧だけ低いレベルに下がり、時刻t3〜t5の間、一定の傾きで電圧(信号レベル)が上昇する。例えば、時刻t4において、Nレベルとランプ信号VRMPのレベルとが一致すると、比較器131の出力信号CMPOは“L”から“H”に変化する。

【0024】

一方、カウンタ180から供給されるカウント信号CNT[3:0]は、時刻t3〜t5において、時刻t3からの時間、すなわち一定の傾きで変化するランプ信号の出力を開始してからの時間を計測している。本実施形態では4ビットのグレイカウンタを用いている場合を示しているが、これに限らない。時刻t4において、比較器131の出力信号CMPOが“L”から“H”に反転すると、ANDゲート136の出力が“L”から“H”になり、Nレベルに対応するカウント信号CNTが、デジタルデータとしてラッチ回路(LNW)132にラッチされる。時刻t5において、第1のA/D変換処理が終了する。

【0025】

続いて、時刻t6〜t7の期間に、画素転送パルスPTXが“H”となり、光電変換素子114から入射光量に応じた光電荷が転送スイッチ115を介して読み出される。そして、画素リセットレベルに光電変換出力が重畳したレベルが、列信号線113に読み出される。すると、増幅回路120において反転増幅された出力が、A/D変換器130に入力される。このときの増幅器121の出力AMPOを、以下Sレベルと呼ぶ。

【0026】

時刻t8〜t10の期間において、時刻t3〜t5と同様にして、A/D変換器130が、Sレベルをアナログ入力として、対応するデジタルデータに変換する第2のA/D変換処理を行う。第2のA/D変換処理中の例えば時刻t9において、Sレベルとランプ信号VRMPのレベルとが一致すると、比較器131の出力信号CMPOは“L”から“H”に変化する。時刻t9において、比較器131の出力信号CMPOが“L”から“H”に反転すると、ANDゲート137の出力が“L”から“H”になり、Sレベルに対応するカウント信号CNTが、デジタルデータとしてラッチ回路(LSW)133にラッチされる。時刻t10において、第2のA/D変換処理が終了する。

【0027】

時刻t11〜t12の期間に、メモリ転送パルスPMTXが“H”となり、ラッチ回路(LNW)132及びラッチ回路(LSW)133のデジタルデータQLNW、QLSWが、ラッチ回路(LNR)134、ラッチ回路(LSR)135に転送される。ラッチ回路(LNR)134及びラッチ回路(LSR)135に格納された一行分のデジタルデータQLNR、QLSRは、水平走査回路150によりデジタル信号線191、192を介して信号処理部190に順次入力される。そして、信号処理部190が、Nレベルに対応するデジタルデータとSレベルに対応するデジタルデータとの差分演算を行い、演算結果を光電変換出力として光電変換装置100外に出力する。

【0028】

同様にして、画素アレイ110の次の行が垂直走査回路140によって選択され、同じ読み出し動作が行われ、画素アレイを一通り走査し終わることで、一枚の画像出力が出力される。

【0029】

次に、カウンタ検査回路200について説明する。

図6は、カウンタ検査回路200の構成例を示すブロック図である。カウンタ検査回路200は、制御回路201、セレクタ202、203、検査信号ラッチ204、及び期待値照合回路205を有する。

【0030】

制御回路201は、図7に示す検査フローに基づいて、データ入力選択信号DATSEL、クロック入力選択信号CLKSEL、及び期待値EVAL[D,CK]を出力する。制御回路201は、期待値照合回路205より出力される照合結果を用いてカウント信号CNTの検査を実行し、最終的に検査結果RSLTを出力する。検査結果RSLTは、例えば撮像データの最終行の直後に光電変換装置100から出力される。

【0031】

カウンタ検査回路200には、カウント信号線181を介してカウント信号CNT[3:0]が供給される。セレクタ202は、データ入力選択信号DATSELに応じて、検査信号ラッチ204のデータ入力に入力されるデータCNT[D]をカウント信号から選択する。また、セレクタ203は、クロック入力選択信号CLKSELに応じて、検査信号ラッチ204のクロック入力に入力されるデータCNT[CK]をカウント信号から選択する。検査信号ラッチ204は、データCNT[CK]をクロックとして動作し、所定のタイミングでデータCNT[D]をラッチする。検査信号ラッチ204の出力は、期待値照合回路205に入力され、制御回路201から供給される期待値EVAL[D,CK]と照合される。

【0032】

期待値照合回路205は、XOR回路(排他的論理和演算回路)206及びインバータ207を有する。XOR回路206は、検査信号ラッチ204の出力が入力されるとともに、制御回路201からの期待値EVAL[D,CK]がインバータ207を介して入力される。XOR回路206の出力が照合結果として出力される。すなわち、期待値照合回路205は、検査信号と期待値とが一致した場合には照合結果として“H”を出力し、不一致の場合には照合結果として“L”を出力し、制御回路201に値を返す。

【0033】

次に、カウンタ検査回路200の動作について説明する。

図7は、カウンタ検査回路200の動作例を示すフローチャートである。本実施形態の例ではカウンタ180は4ビットのグレイカウンタであるため、図7においては、グレイカウンタの各ビットの立上りエッジにおける下位ビットの期待値と、実際の値を照合するアルゴリズムとなっている。また、変数Dは、データ入力選択信号DATSELに応じてセレクタ202によりデータCNT[D]として選択されるカウント信号CNTのビットを示している。変数CKは、クロック入力選択信号CLKSELに応じて、セレクタ203によりデータCNT[CK]として選択されるカウント信号CNTのビットを示している。

【0034】

制御回路201は、変数CKの値を0にする(ステップS101)。次に、制御回路201は、変数CKの値を1インクリメントし(ステップS102)、変数Dの値を0にする(ステップS103)。

【0035】

そして、カウント信号CNT[CK]の立ち上がりにおいてカウント信号CNT[D]が検査信号ラッチ204によりラッチされるとともに、カウント信号CNT[D]が期待値照合回路205に入力される。また、制御回路201より期待値EVAL[D,CK]が出力されて、期待値照合回路205に入力される。期待値照合回路205は、カウント信号CNT[D]と期待値EVAL[D,CK]とが一致した場合には照合結果として“H”を出力し、不一致の場合には照合結果として“L”を出力する。

【0036】

制御回路201は、期待値照合回路205より出力される照合結果に基づいて、カウント信号CNT[D]と期待値EVAL[D,CK]とが一致しているか否かを判定する(ステップS104)。判定の結果、カウント信号CNT[D]と期待値EVAL[D,CK]とが一致していないと判定した場合には、FAIL(故障)として終了する。一方、判定の結果、カウント信号CNT[D]と期待値EVAL[D,CK]とが一致していると判定した場合には、制御回路201は、変数Dの値を1インクリメントする(ステップS105)。そして、変数Dの値が変数CKの値に達するまで、前述したステップS104及びS105の処理を繰り返し行う(ステップS106のNO)。

【0037】

変数Dの値が変数CKの値に達すると(ステップS106のYES)、制御回路201は、変数CKの値がカウント信号CNTのビット数に達したか否かを判断する(ステップS107)。判断の結果、変数CKの値がカウント信号CNTのビット数に達した場合には、PASS(正常)として終了し、そうでない場合にはステップS102に戻り、前述したステップS102〜S107の処理を行う。

【0038】

以上説明した動作により、カウンタ検査回路200は、図8に示した期待値テーブルに基づき、カウンタ180からのカウント信号CNT[3:0]を検査する。例えば、カウンタ検査回路200は、カウント信号CNT[1]の立上りエッジにおけるカウント信号CNT[0]のデータを、期待値EVAL[0,1]と照合することで、下位2bitが正常であることを確認する。次に、カウンタ検査回路200は、カウント信号CNT[2]の立上りエッジにおけるカウント信号CNT[1]及びCNT[0]のデータを、期待値EVAL[1,2]、EVAL[0,2]とそれぞれ照合することで、下位3bitが正常であることを確認する。さらに、カウンタ検査回路200は、カウント信号CNT[3]の立上りエッジにおけるカウント信号CNT[2]、CNT[1]、CNT[0]のデータを、期待値EVAL[2,3]、EVAL[1,3]、EVAL[0,3]と照合する。これにより、最終的に4ビットのカウント信号が正常であることを確認する。

【0039】

カウンタ検査回路200は、カウント信号CNTと期待値EVALとの照合を第2のA/D変換処理と並行して行う。前述した図7に示した例では全部で6回の照合を行うため、画素アレイ110の6行分のA/D変換期間において、A/D変換処理と並行にカウンタ検査を行うことができる。

【0040】

第1の実施形態によれば、A/D変換器130とは独立してカウンタ検査回路200を設けることで、画素111からの信号のA/D変換と並行してカウンタ180の検査を行うことができる。したがって、検査時間を増加させることなく、テストコストの低い光電変換システムが実現できる。

【0041】

なお、カウンタ検査回路200は、カウント信号線上の任意の位置に置くことができる。例えば、カウンタ180からみて、カウント信号線181の末端(カウンタ180からみてA/D変換器130よりも遠い位置)に配置した場合には、カウント信号線181の導通チェックも合わせて行うことができる。また、例えばカウント信号線が複数に分岐する場合には、各分岐の末端に配置するようにしてもよい。また、前述したカウンタの形式やA/D変換の分解能や検査フローは一例に過ぎず、他の方式をとり得ることは明らかである。例えば、カウンタ形式はバイナリカウンタであっても良い。また、カウンタの検査フローとして、カウント信号の各ビットの最初の立上りエッジの時間差を計測し、期待値と照合する等の方法を用いてもよい。

【0042】

(第2の実施形態)

次に、本発明の第2の実施形態について説明する。

図9は、第2の実施形態に係る光電変換システムの構成例を示すブロック図である。

前述した第1の実施形態では、光電変換装置100の内部にカウンタ検査回路200を設けていたが、第2の実施形態に係る光電変換システムは、光電変換装置100の外部にカウンタ検査回路200を設けている。また、カウント信号線181に接続され、カウント信号を外部のカウンタ検査回路200に対して出力するバッファ回路182を設けている。その他の構成及び動作は、第1の実施形態と同様である。図9に示すように、カウンタ検査回路200を光電変換装置100の外部に設けることで、光電変換装置100の回路面積を低減することができ、製造コストの低い光電変換システムが実現できる。

【0043】

(第3の実施形態)

次に、本発明の第3の実施形態について説明する。

図10は、第3の実施形態に係る光電変換システムの構成例を示すブロック図である。

第3の実施形態に係る光電変換システムは、カウンタ180とカウント信号線181との間に調整回路183を設けている。調整回路183は、カウンタ検査回路200からの制御信号に基づいて、カウント信号CNTの遅延量をビット毎に制御する。

【0044】

図11は、調整回路183の構成例を示す図である。調整回路183は、カウント信号CNTの各ビットに対応して遅延制御部184を有する。遅延制御部184は、カウンタ180から出力されたカウント信号CNT[3:0]_Oが入力され、そのカウント信号CNT[3:0]_Oを遅延回路185−1、185−2、185−3により遅延させる。また、遅延制御部184は、入力されたカウント信号CNT[3:0]_O及び遅延回路185により遅延されたカウント信号CNT[3:0]_Oの内から1つの信号を選択し、カウント信号CNT[3:0]としてカウント信号線181に対して出力する。

【0045】

第3の実施形態によれば、調整回路183を設けることにより、カウント信号CNTの各ビットの遅延量を制御することができる。例えば、カウンタ180から出力されたカウント信号CNTにおいて、任意のビット間の位相関係がずれていた場合には、カウンタ検査回路200の判定に応じて、位相のずれを補正することができる。また、例えばカウンタ検査回路200によりカウント信号の検査や補正を、温度等の撮影環境の変化に応じて適宜実行することで、耐環境性に優れた光電変換システムを実現することができる。

【0046】

なお、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

【産業上の利用可能性】

【0047】

本発明に係る光電変換システムは、例えばスキャナ、ビデオカメラ、デジタルスチルカメラ等に適用可能である。

【符号の説明】

【0048】

100…光電変換装置、110…画素アレイ、111…画素、113…列信号線、120…増幅回路、121…増幅器、130…A/D変換器、131…比較器、132…ラッチ(LNW)、133…ラッチ(LSW)、134…ラッチ(LNR)、135…ラッチ(LSR)、170…参照信号生成部、180…カウンタ、181…カウント信号線、183…カウント信号調整回路、200…カウンタ検査回路

【技術分野】

【0001】

本発明は、光電変換システムに関する。

【背景技術】

【0002】

アナログデジタル変換器(A/D変換器)を内蔵したイメージセンサ等の光電変換装置において、A/D変換器の故障診断回路を内蔵するものが提案されている。特許文献1では、画素信号の代わりに検査用信号を入力するなどして、列毎に設けてあるラッチ(列メモリ)に任意の時刻でカウント信号を書き込み、これを読み出すことで、故障診断を行っている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−331883号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1に記載のイメージセンサの故障診断回路には、以下のような問題がある。A/D変換器に供給されるカウント信号のリニアリティを確認しようとする場合には、画像信号を読み出すためのラッチ(列メモリ)にカウント信号を書き込むことにより検査を行うので、検査を行っている期間は撮像ができないという問題がある。このため、例えばイメージセンサの出荷テストを行う場合に、被写体の撮影による画素部欠陥の有無を検出する検査と、A/D変換器に供給されるカウント信号のリニアリティの検査とは、別々に行う必要があり、検査時間の増加につながっていた。

【0005】

本発明の目的は、被写体の撮像と並行して、A/D変換器に供給されるカウント信号の検査を行うことができる光電変換システムを提供することである。

【課題を解決するための手段】

【0006】

本発明の光電変換システムは、各々が光電変換素子を含み、マトリクス状に配列された複数の画素と、時間の経過にともなって信号レベルが単調に変化する参照信号を生成する参照信号生成部と、前記画素の列毎に配置され、前記画素からの信号をアナログデジタル変換するA/D変換器と、前記参照信号生成部からの参照信号の出力に合わせてカウント動作を行い、カウント信号をカウント信号線を介して前記A/D変換器に供給するカウンタとを備え、前記A/D変換器は、前記画素からの信号と前記参照信号生成部により生成された前記参照信号とを比較する比較器と、前記カウンタからのカウント信号を、前記比較器の出力が反転したときに記憶する記憶部とを有し、前記カウント信号線に接続され、かつ前記A/D変換器とは独立して設けられ、カウント信号の期待値と、前記カウント信号線を介して供給される前記カウンタからのカウント信号とを照合することにより前記カウンタの検査を行う検査回路を備えることを特徴とする。

【発明の効果】

【0007】

本発明によれば、被写体の撮像と並行して、カウント信号の検査を行うことができ、検査時間を短縮することができる。

【図面の簡単な説明】

【0008】

【図1】本発明の第1の実施形態に係る光電変換システムの構成例を示す図である。

【図2】本発明の実施形態に係る画素の構成例を示す図である。

【図3】本発明の実施形態に係る増幅回路の構成例を示す図である。

【図4】本発明の実施形態に係るA/D変換器の構成例を示す図である。

【図5】本発明の実施形態に係る信号波形を示すタイミングチャートである。

【図6】本発明の実施形態に係るカウンタ検査回路の構成例を示す図である。

【図7】本発明の実施形態に係るカウンタ検査回路の動作例を示すフローチャートである。

【図8】本発明の実施形態に係るカウンタ検査の期待値の一例を示す図である。

【図9】本発明の第2の実施形態に係る光電変換システムの構成例を示す図である。

【図10】本発明の第3の実施形態に係る光電変換システムの構成例を示す図である。

【図11】本発明の第3の実施形態に係る調整回路の構成例を示す図である。

【図12】本発明の実施形態に係るラッチパルス生成を示すタイミングチャートである。

【発明を実施するための形態】

【0009】

以下、本発明の実施形態を図面に基づいて説明する。なお、以下の説明において、図面を通じて同一の構成要素には同一の符号を付し、重複する説明は省略する。

【0010】

(第1の実施形態)

本発明の第1の実施形態について説明する。

図1は、第1の実施形態に係る光電変換システムの構成例を示すブロック図である。光電変換装置100は、例えばCMOSイメージセンサであり、本実施形態に係る光電変換システムを有する。光電変換装置100は、被写体像を示す入射光を光電変換し、光電変換により得られた電気信号をデジタルデータとして外部に出力する。光電変換装置100は、画素アレイ110、増幅回路120、A/D変換器130、垂直走査回路140、水平走査回路150、参照信号生成部170、カウンタ180、信号処理回路190、タイミング制御部195、及びカウンタ検査回路200を有する。

【0011】

画素アレイ110は、光電変換素子を含む複数の画素111を有し、それらがマトリクス状に(行方向及び列方向に)配置されている。図1においては、簡単のために4つの画素111を示しているが、画素111の個数はこれに限られず、より多くの画素を有する。各画素111において、光電変換装置100への入射光がアナログ信号へ光電変換される。

【0012】

垂直走査回路140は、画素行毎に配置された行制御線112に駆動パルス信号を順番に供給する。行制御線112に駆動パルス信号が供給されると、対応する画素行に含まれる各画素111からアナログ信号が列信号線113に読み出される。本実施形態では、画素アレイ110からのアナログ信号として、画素111のリセットレベルの信号であるノイズ信号と、光電変換により発生した電荷に応じた信号にノイズ信号が重畳した画素信号とが読み出される。画素信号からノイズ信号を引いた値が有効な画素値を表す。

【0013】

増幅回路120及びA/D変換器(アナログデジタル変換器)130は、画素アレイ110の各列に対応して、列信号線113毎に設けられる。増幅回路120は、列信号線113を介して画素111から入力されたアナログ信号を増幅してA/D変換器130へ供給する。A/D変換器130は、入力されたアナログ信号をデジタルデータにアナログデジタル変換(A/D変換)して出力する。

【0014】

参照信号生成部170は、参照信号であるランプ信号を生成し、生成したランプ信号をランプ信号線171を通じて各A/D変換器130に供給する。ここで、ランプ信号は、時間の経過にともなって信号レベル(信号の大きさ)が単調に変化する信号であり、例えば出力電圧が時間の経過とともに単調増加若しくは単調減少する信号である。カウンタ180は、参照信号生成部170からのランプ信号の出力に合わせてカウント動作を行い、カウント値を表現する信号であるカウント信号をカウント信号線181を通じて各A/D変換器130に供給する。カウンタ180の種類は任意であり、例えばグレイカウンタやバイナリカウンタを用いてもよく、カウンタ180はアップダウン機能を有してもよい。本実施形態では、複数のA/D変換器130が、参照信号生成部170及びカウンタ180を共有する例を示すが、A/D変換器130毎に、これらの構成要素を有してもよい。

【0015】

水平走査回路150は、A/D変換器130が出力するデジタルデータを列毎にデジタル信号線191、192に転送する。デジタル信号線191、192に転送されたデジタルデータは、信号処理部190に供給される。本実施形態では、デジタル信号線191、192に、それぞれノイズ信号を表すデジタルデータと画素信号を表すデジタルデータとが順次読み出される。信号処理部190は、画素信号を表すデジタルデータからノイズ信号を表すデジタルデータを減算して、有効な画素値を外部に出力する。

【0016】

タイミング制御部195は、前述した各構成要素に制御信号を供給して光電変換装置100の動作を制御する。なお、図1においては、タイミング制御部195から各構成要素へ制御信号を送信するための信号線は図示していない。カウンタ検査回路200は、A/D変換器130とは独立して設けられており、カウント信号線181を介してカウンタ180からカウント信号が供給され、供給されるカウント信号に基づいてカウンタ180の出力の検査を行う。

【0017】

本実施形態においては、光電変換装置100が増幅回路120を含むことによって、A/D変換器130で発生するノイズの影響を軽減できる。しかし、光電変換装置100は増幅回路120を含まずに、画素111からのアナログ信号が列信号線113を介して直接にA/D変換器130へ供給されるようにしてもよい。また、図1に示した例では、画素アレイ110の一方の側に増幅回路120、A/D変換器130及び水平走査回路150が配置されるが、これらの構成要素が画素アレイ110の両側に配置され、画素列毎に何れか一方の側の構成要素に振り分けられてもよい。

【0018】

図2は、画素111の構成例を示す図である。画素111は、その画素値を算出するためのアナログ信号をA/D変換器130に供給できれば如何なる構成であってもよい。画素111は、光電変換を行う光電変換素子(フォトダイオード)114及び複数のトランジスタ115、116、117、118を有する。光電変換素子114は、転送スイッチ115を介してフローティングディフュージョン部FDに接続される。フローティングディフュージョン部FDはまた、リセットスイッチ116を介して電圧源VDDに接続されるとともに、増幅トランジスタ117のゲート電極に接続される。増幅トランジスタ117は、第1主電極が電圧源VDDに接続され、第2主電極が行選択スイッチ118を介して列信号線113に接続される。行選択スイッチ118のゲート電極は、行制御線112の1つである行選択線PSELに接続される。リセットスイッチ116のゲート電極は、行制御線112の1つであるリセット線PRESに接続される。また、転送スイッチ115のゲート電極は、行制御線の1つである転送線PTXに接続される。

【0019】

図3は、増幅回路120の構成例を示す図である。増幅回路120は、画素111の画素値を算出するためのアナログ信号をA/D変換器130に供給できれば如何なる構成であってもよい。増幅回路120は、例えば図3に示す反転アンプである。増幅器121の反転入力端子は、クランプ容量COを介して列信号線113に接続され、増幅器121の非反転入力端子には電圧VCORが供給される。増幅器121の出力端子は、A/D変換器130に接続される。また、増幅器121の反転入力端子と出力端子との間に、帰還容量CF及びアンプリセットスイッチ122が並列に接続される。図3に示したように構成することにより、増幅回路120は、列信号線113を介して入力された信号をクランプ容量COと帰還容量CFとの容量値の比で増幅し出力する。

【0020】

図4は、A/D変換器130の構成例を示す図である。

入力端子INには、列信号線113を介してアナログ信号が入力される。比較器131は、入力端子INより入力されたアナログ信号の電圧とランプ信号線171を介して供給される比較対象のランプ信号の電圧とを比較し、その比較結果に応じたレベルの出力信号CMPOを出力する。比較器131の出力信号CMPOは、RSフリップフロップ138のS入力に入力される。RSフリップフロップ138のQ出力、及びディレイ生成用バッファにより遅延されたRSフリップフロップ138のQB(Qバー)出力が、ANDゲート(論理積演算回路)139に入力される。このようにして、ANDゲート139に入力されるRSフリップフロップ138のQB出力が反転するのが遅れ、ANDゲート139の出力は、図12に示すように比較器131の出力信号CMPOの変化に応じて細幅パルスQ*QB’を出力する。ラッチ回路(LNW、LSW、LNR、LSR)132、133、134、135は、記憶部であり、比較器131の出力信号CMPOに応じてデジタルデータを記憶する。ラッチ回路(LNW)132のD入力及びラッチ回路(LSW)133のD入力は、ともにカウント信号線181に接続される。ラッチ回路(LNW)132のG入力は、ANDゲート139の出力及び制御信号PMSELNを入力とするANDゲート136の出力線に接続される。ラッチ回路(LSW)133のG入力は、ANDゲート139の出力及び制御信号PMSELSを入力とするANDゲート137の出力線に接続される。ラッチ回路(LNW)132のQ出力は、ラッチ回路(LNR)134のD入力に接続され、ラッチ回路(LSW)133のQ出力は、ラッチ回路(LSR)135のD入力に接続される。ラッチ回路(LNR)134のG入力及びラッチ回路(LSR)135のG入力は、ともに制御線PMTXに接続される。ラッチ回路(LNR)134のQ出力は、出力端子OUTNに接続され、ラッチ回路(LSR)135のQ出力は、出力端子OUTSに接続される。

【0021】

次に、図1に示した光電変換システムの動作について説明する。図5は、第1の実施形態に係る信号波形を示すタイミングチャートであり、画素行1行分の画素111のアナログ信号(光電変換信号)がA/D変換器130でデジタルデータに変換されるまでの動作を説明するためのタイミングチャートを示している。なお、以下の説明では、信号のハイレベルを“H”と記し、信号のローレベルを“L”と記す。

【0022】

まず、時刻t0において、行選択パルスPSELが“H”となることで行選択スイッチ118がオン(導通状態)になり、任意の行に配列された画素111が列信号線113に接続される。時刻t0〜t1の期間に、画素リセットパルスPRESが“H”となり、リセットスイッチ116によって、画素111のフローティングディフュージョン部FDがリセットされる。そして、画素111のリセット状態に対応した出力(以下、画素リセットレベルと呼ぶ)が、列信号線113に出力される。時刻t0〜t2の期間に、リセットパルスPC0Rが“H”となることで増幅回路120のアンプリセットスイッチ122がオン(導通状態)になり、画素リセットレベルをクランプする。このときの増幅器121の出力AMPOを、以下Nレベルと呼ぶ。

【0023】

続いて、時刻t2〜t5の期間において、A/D変換器130が、Nレベルをアナログ入力として、対応するデジタルデータに変換する第1のA/D変換処理を行う。時刻t2〜t3において、コンパレータリセットパルスPCMPRが“H”となり、増幅器121から出力されるNレベルおよび参照信号生成部170で生成される基準電圧がそれぞれ入力容量でクランプされる。その後、コンパレータリセットパルスPCMPRが“L”となり、それぞれの入力容量にクランプされた電圧の差電圧が比較器131の初期値となる。その後、参照信号生成部170からのランプ信号VRMPは、いったん基準電圧より所定電圧だけ低いレベルに下がり、時刻t3〜t5の間、一定の傾きで電圧(信号レベル)が上昇する。例えば、時刻t4において、Nレベルとランプ信号VRMPのレベルとが一致すると、比較器131の出力信号CMPOは“L”から“H”に変化する。

【0024】

一方、カウンタ180から供給されるカウント信号CNT[3:0]は、時刻t3〜t5において、時刻t3からの時間、すなわち一定の傾きで変化するランプ信号の出力を開始してからの時間を計測している。本実施形態では4ビットのグレイカウンタを用いている場合を示しているが、これに限らない。時刻t4において、比較器131の出力信号CMPOが“L”から“H”に反転すると、ANDゲート136の出力が“L”から“H”になり、Nレベルに対応するカウント信号CNTが、デジタルデータとしてラッチ回路(LNW)132にラッチされる。時刻t5において、第1のA/D変換処理が終了する。

【0025】

続いて、時刻t6〜t7の期間に、画素転送パルスPTXが“H”となり、光電変換素子114から入射光量に応じた光電荷が転送スイッチ115を介して読み出される。そして、画素リセットレベルに光電変換出力が重畳したレベルが、列信号線113に読み出される。すると、増幅回路120において反転増幅された出力が、A/D変換器130に入力される。このときの増幅器121の出力AMPOを、以下Sレベルと呼ぶ。

【0026】

時刻t8〜t10の期間において、時刻t3〜t5と同様にして、A/D変換器130が、Sレベルをアナログ入力として、対応するデジタルデータに変換する第2のA/D変換処理を行う。第2のA/D変換処理中の例えば時刻t9において、Sレベルとランプ信号VRMPのレベルとが一致すると、比較器131の出力信号CMPOは“L”から“H”に変化する。時刻t9において、比較器131の出力信号CMPOが“L”から“H”に反転すると、ANDゲート137の出力が“L”から“H”になり、Sレベルに対応するカウント信号CNTが、デジタルデータとしてラッチ回路(LSW)133にラッチされる。時刻t10において、第2のA/D変換処理が終了する。

【0027】

時刻t11〜t12の期間に、メモリ転送パルスPMTXが“H”となり、ラッチ回路(LNW)132及びラッチ回路(LSW)133のデジタルデータQLNW、QLSWが、ラッチ回路(LNR)134、ラッチ回路(LSR)135に転送される。ラッチ回路(LNR)134及びラッチ回路(LSR)135に格納された一行分のデジタルデータQLNR、QLSRは、水平走査回路150によりデジタル信号線191、192を介して信号処理部190に順次入力される。そして、信号処理部190が、Nレベルに対応するデジタルデータとSレベルに対応するデジタルデータとの差分演算を行い、演算結果を光電変換出力として光電変換装置100外に出力する。

【0028】

同様にして、画素アレイ110の次の行が垂直走査回路140によって選択され、同じ読み出し動作が行われ、画素アレイを一通り走査し終わることで、一枚の画像出力が出力される。

【0029】

次に、カウンタ検査回路200について説明する。

図6は、カウンタ検査回路200の構成例を示すブロック図である。カウンタ検査回路200は、制御回路201、セレクタ202、203、検査信号ラッチ204、及び期待値照合回路205を有する。

【0030】

制御回路201は、図7に示す検査フローに基づいて、データ入力選択信号DATSEL、クロック入力選択信号CLKSEL、及び期待値EVAL[D,CK]を出力する。制御回路201は、期待値照合回路205より出力される照合結果を用いてカウント信号CNTの検査を実行し、最終的に検査結果RSLTを出力する。検査結果RSLTは、例えば撮像データの最終行の直後に光電変換装置100から出力される。

【0031】

カウンタ検査回路200には、カウント信号線181を介してカウント信号CNT[3:0]が供給される。セレクタ202は、データ入力選択信号DATSELに応じて、検査信号ラッチ204のデータ入力に入力されるデータCNT[D]をカウント信号から選択する。また、セレクタ203は、クロック入力選択信号CLKSELに応じて、検査信号ラッチ204のクロック入力に入力されるデータCNT[CK]をカウント信号から選択する。検査信号ラッチ204は、データCNT[CK]をクロックとして動作し、所定のタイミングでデータCNT[D]をラッチする。検査信号ラッチ204の出力は、期待値照合回路205に入力され、制御回路201から供給される期待値EVAL[D,CK]と照合される。

【0032】

期待値照合回路205は、XOR回路(排他的論理和演算回路)206及びインバータ207を有する。XOR回路206は、検査信号ラッチ204の出力が入力されるとともに、制御回路201からの期待値EVAL[D,CK]がインバータ207を介して入力される。XOR回路206の出力が照合結果として出力される。すなわち、期待値照合回路205は、検査信号と期待値とが一致した場合には照合結果として“H”を出力し、不一致の場合には照合結果として“L”を出力し、制御回路201に値を返す。

【0033】

次に、カウンタ検査回路200の動作について説明する。

図7は、カウンタ検査回路200の動作例を示すフローチャートである。本実施形態の例ではカウンタ180は4ビットのグレイカウンタであるため、図7においては、グレイカウンタの各ビットの立上りエッジにおける下位ビットの期待値と、実際の値を照合するアルゴリズムとなっている。また、変数Dは、データ入力選択信号DATSELに応じてセレクタ202によりデータCNT[D]として選択されるカウント信号CNTのビットを示している。変数CKは、クロック入力選択信号CLKSELに応じて、セレクタ203によりデータCNT[CK]として選択されるカウント信号CNTのビットを示している。

【0034】

制御回路201は、変数CKの値を0にする(ステップS101)。次に、制御回路201は、変数CKの値を1インクリメントし(ステップS102)、変数Dの値を0にする(ステップS103)。

【0035】

そして、カウント信号CNT[CK]の立ち上がりにおいてカウント信号CNT[D]が検査信号ラッチ204によりラッチされるとともに、カウント信号CNT[D]が期待値照合回路205に入力される。また、制御回路201より期待値EVAL[D,CK]が出力されて、期待値照合回路205に入力される。期待値照合回路205は、カウント信号CNT[D]と期待値EVAL[D,CK]とが一致した場合には照合結果として“H”を出力し、不一致の場合には照合結果として“L”を出力する。

【0036】

制御回路201は、期待値照合回路205より出力される照合結果に基づいて、カウント信号CNT[D]と期待値EVAL[D,CK]とが一致しているか否かを判定する(ステップS104)。判定の結果、カウント信号CNT[D]と期待値EVAL[D,CK]とが一致していないと判定した場合には、FAIL(故障)として終了する。一方、判定の結果、カウント信号CNT[D]と期待値EVAL[D,CK]とが一致していると判定した場合には、制御回路201は、変数Dの値を1インクリメントする(ステップS105)。そして、変数Dの値が変数CKの値に達するまで、前述したステップS104及びS105の処理を繰り返し行う(ステップS106のNO)。

【0037】

変数Dの値が変数CKの値に達すると(ステップS106のYES)、制御回路201は、変数CKの値がカウント信号CNTのビット数に達したか否かを判断する(ステップS107)。判断の結果、変数CKの値がカウント信号CNTのビット数に達した場合には、PASS(正常)として終了し、そうでない場合にはステップS102に戻り、前述したステップS102〜S107の処理を行う。

【0038】

以上説明した動作により、カウンタ検査回路200は、図8に示した期待値テーブルに基づき、カウンタ180からのカウント信号CNT[3:0]を検査する。例えば、カウンタ検査回路200は、カウント信号CNT[1]の立上りエッジにおけるカウント信号CNT[0]のデータを、期待値EVAL[0,1]と照合することで、下位2bitが正常であることを確認する。次に、カウンタ検査回路200は、カウント信号CNT[2]の立上りエッジにおけるカウント信号CNT[1]及びCNT[0]のデータを、期待値EVAL[1,2]、EVAL[0,2]とそれぞれ照合することで、下位3bitが正常であることを確認する。さらに、カウンタ検査回路200は、カウント信号CNT[3]の立上りエッジにおけるカウント信号CNT[2]、CNT[1]、CNT[0]のデータを、期待値EVAL[2,3]、EVAL[1,3]、EVAL[0,3]と照合する。これにより、最終的に4ビットのカウント信号が正常であることを確認する。

【0039】

カウンタ検査回路200は、カウント信号CNTと期待値EVALとの照合を第2のA/D変換処理と並行して行う。前述した図7に示した例では全部で6回の照合を行うため、画素アレイ110の6行分のA/D変換期間において、A/D変換処理と並行にカウンタ検査を行うことができる。

【0040】

第1の実施形態によれば、A/D変換器130とは独立してカウンタ検査回路200を設けることで、画素111からの信号のA/D変換と並行してカウンタ180の検査を行うことができる。したがって、検査時間を増加させることなく、テストコストの低い光電変換システムが実現できる。

【0041】

なお、カウンタ検査回路200は、カウント信号線上の任意の位置に置くことができる。例えば、カウンタ180からみて、カウント信号線181の末端(カウンタ180からみてA/D変換器130よりも遠い位置)に配置した場合には、カウント信号線181の導通チェックも合わせて行うことができる。また、例えばカウント信号線が複数に分岐する場合には、各分岐の末端に配置するようにしてもよい。また、前述したカウンタの形式やA/D変換の分解能や検査フローは一例に過ぎず、他の方式をとり得ることは明らかである。例えば、カウンタ形式はバイナリカウンタであっても良い。また、カウンタの検査フローとして、カウント信号の各ビットの最初の立上りエッジの時間差を計測し、期待値と照合する等の方法を用いてもよい。

【0042】

(第2の実施形態)

次に、本発明の第2の実施形態について説明する。

図9は、第2の実施形態に係る光電変換システムの構成例を示すブロック図である。

前述した第1の実施形態では、光電変換装置100の内部にカウンタ検査回路200を設けていたが、第2の実施形態に係る光電変換システムは、光電変換装置100の外部にカウンタ検査回路200を設けている。また、カウント信号線181に接続され、カウント信号を外部のカウンタ検査回路200に対して出力するバッファ回路182を設けている。その他の構成及び動作は、第1の実施形態と同様である。図9に示すように、カウンタ検査回路200を光電変換装置100の外部に設けることで、光電変換装置100の回路面積を低減することができ、製造コストの低い光電変換システムが実現できる。

【0043】

(第3の実施形態)

次に、本発明の第3の実施形態について説明する。

図10は、第3の実施形態に係る光電変換システムの構成例を示すブロック図である。

第3の実施形態に係る光電変換システムは、カウンタ180とカウント信号線181との間に調整回路183を設けている。調整回路183は、カウンタ検査回路200からの制御信号に基づいて、カウント信号CNTの遅延量をビット毎に制御する。

【0044】

図11は、調整回路183の構成例を示す図である。調整回路183は、カウント信号CNTの各ビットに対応して遅延制御部184を有する。遅延制御部184は、カウンタ180から出力されたカウント信号CNT[3:0]_Oが入力され、そのカウント信号CNT[3:0]_Oを遅延回路185−1、185−2、185−3により遅延させる。また、遅延制御部184は、入力されたカウント信号CNT[3:0]_O及び遅延回路185により遅延されたカウント信号CNT[3:0]_Oの内から1つの信号を選択し、カウント信号CNT[3:0]としてカウント信号線181に対して出力する。

【0045】

第3の実施形態によれば、調整回路183を設けることにより、カウント信号CNTの各ビットの遅延量を制御することができる。例えば、カウンタ180から出力されたカウント信号CNTにおいて、任意のビット間の位相関係がずれていた場合には、カウンタ検査回路200の判定に応じて、位相のずれを補正することができる。また、例えばカウンタ検査回路200によりカウント信号の検査や補正を、温度等の撮影環境の変化に応じて適宜実行することで、耐環境性に優れた光電変換システムを実現することができる。

【0046】

なお、前記実施形態は、何れも本発明を実施するにあたっての具体化のほんの一例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

【産業上の利用可能性】

【0047】

本発明に係る光電変換システムは、例えばスキャナ、ビデオカメラ、デジタルスチルカメラ等に適用可能である。

【符号の説明】

【0048】

100…光電変換装置、110…画素アレイ、111…画素、113…列信号線、120…増幅回路、121…増幅器、130…A/D変換器、131…比較器、132…ラッチ(LNW)、133…ラッチ(LSW)、134…ラッチ(LNR)、135…ラッチ(LSR)、170…参照信号生成部、180…カウンタ、181…カウント信号線、183…カウント信号調整回路、200…カウンタ検査回路

【特許請求の範囲】

【請求項1】

各々が光電変換素子を含み、マトリクス状に配列された複数の画素と、

時間の経過にともなって信号レベルが単調に変化する参照信号を生成する参照信号生成部と、

前記画素の列毎に配置され、前記画素からの信号をアナログデジタル変換するA/D変換器と、

前記参照信号生成部からの参照信号の出力に合わせてカウント動作を行い、カウント信号をカウント信号線を介して前記A/D変換器に供給するカウンタとを備え、

前記A/D変換器は、

前記画素からの信号と前記参照信号生成部により生成された前記参照信号とを比較する比較器と、

前記カウンタからのカウント信号を、前記比較器の出力が反転したときに記憶する記憶部とを有し、

前記カウント信号線に接続され、かつ前記A/D変換器とは独立して設けられ、カウント信号の期待値と、前記カウント信号線を介して供給される前記カウンタからのカウント信号とを照合することにより前記カウンタの検査を行う検査回路を備えることを特徴とする光電変換システム。

【請求項2】

前記検査回路は、前記カウンタから供給される前記カウント信号を所定のタイミングで取り込み、取り込んだカウント信号と前記期待値とを照合することを特徴とする請求項1記載の光電変換システム。

【請求項3】

前記検査回路は、前記カウンタから供給される前記カウント信号のうちの所定のビットが変化するタイミングで前記カウント信号を取り込むことを特徴とする請求項2記載の光電変換システム。

【請求項4】

前記検査回路が、前記カウンタからみて前記カウント信号線上の前記A/D変換器よりも遠い位置に設けられていることを特徴とする請求項1〜3の何れか1項に記載の光電変換システム。

【請求項5】

前記カウント信号線が複数に分岐しており、分岐した前記カウント信号線の各々に対して前記検査回路が設けられていることを特徴とする請求項1〜4の何れか1項に記載の光電変換システム。

【請求項6】

前記カウンタと前記カウント信号線との間に、前記カウント信号の遅延量をビット毎に制御する調整回路を備えることを特徴とする請求項1〜5の何れか1項に記載の光電変換システム。

【請求項7】

前記複数の画素、前記参照信号生成部、前記A/D変換器、及び前記カウンタを含む光電変換装置の外部に、前記検査回路を設けたことを特徴とする請求項1〜6の何れか1項に記載の光電変換システム。

【請求項8】

前記複数の画素、前記参照信号生成部、前記A/D変換器、及び前記カウンタを含む光電変換装置の内部に、前記検査回路を設けたことを特徴とする請求項1〜6の何れか1項に記載の光電変換システム。

【請求項9】

前記画素の列毎に配置され、前記画素からの信号を増幅して前記A/D変換器に供給する増幅回路を備えることを特徴とする請求項1〜8の何れか1項に記載の光電変換システム。

【請求項1】

各々が光電変換素子を含み、マトリクス状に配列された複数の画素と、

時間の経過にともなって信号レベルが単調に変化する参照信号を生成する参照信号生成部と、

前記画素の列毎に配置され、前記画素からの信号をアナログデジタル変換するA/D変換器と、

前記参照信号生成部からの参照信号の出力に合わせてカウント動作を行い、カウント信号をカウント信号線を介して前記A/D変換器に供給するカウンタとを備え、

前記A/D変換器は、

前記画素からの信号と前記参照信号生成部により生成された前記参照信号とを比較する比較器と、

前記カウンタからのカウント信号を、前記比較器の出力が反転したときに記憶する記憶部とを有し、

前記カウント信号線に接続され、かつ前記A/D変換器とは独立して設けられ、カウント信号の期待値と、前記カウント信号線を介して供給される前記カウンタからのカウント信号とを照合することにより前記カウンタの検査を行う検査回路を備えることを特徴とする光電変換システム。

【請求項2】

前記検査回路は、前記カウンタから供給される前記カウント信号を所定のタイミングで取り込み、取り込んだカウント信号と前記期待値とを照合することを特徴とする請求項1記載の光電変換システム。

【請求項3】

前記検査回路は、前記カウンタから供給される前記カウント信号のうちの所定のビットが変化するタイミングで前記カウント信号を取り込むことを特徴とする請求項2記載の光電変換システム。

【請求項4】

前記検査回路が、前記カウンタからみて前記カウント信号線上の前記A/D変換器よりも遠い位置に設けられていることを特徴とする請求項1〜3の何れか1項に記載の光電変換システム。

【請求項5】

前記カウント信号線が複数に分岐しており、分岐した前記カウント信号線の各々に対して前記検査回路が設けられていることを特徴とする請求項1〜4の何れか1項に記載の光電変換システム。

【請求項6】

前記カウンタと前記カウント信号線との間に、前記カウント信号の遅延量をビット毎に制御する調整回路を備えることを特徴とする請求項1〜5の何れか1項に記載の光電変換システム。

【請求項7】

前記複数の画素、前記参照信号生成部、前記A/D変換器、及び前記カウンタを含む光電変換装置の外部に、前記検査回路を設けたことを特徴とする請求項1〜6の何れか1項に記載の光電変換システム。

【請求項8】

前記複数の画素、前記参照信号生成部、前記A/D変換器、及び前記カウンタを含む光電変換装置の内部に、前記検査回路を設けたことを特徴とする請求項1〜6の何れか1項に記載の光電変換システム。

【請求項9】

前記画素の列毎に配置され、前記画素からの信号を増幅して前記A/D変換器に供給する増幅回路を備えることを特徴とする請求項1〜8の何れか1項に記載の光電変換システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−85109(P2013−85109A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−223330(P2011−223330)

【出願日】平成23年10月7日(2011.10.7)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月7日(2011.10.7)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]