光電変換素子及びその製造方法

【課題】3次元的に規則的に配置された量子ドット列を有する光電変換素子及びその製造方法を提供する。

【解決手段】積層された複数のトンネル接合型半導体層を有する積層体を作製する積層体作製工程と、該積層体作製工程後に、積層体の上面側に量子ドット用の複数の凸部を有する凹凸パターンを形成するパターン形成工程と、該パターン形成工程で形成した凹部を削って複数の半導体層を貫通する溝を形成する溝形成工程と、を経て形成された3次元量子ドット列を有する、光電変換素子の製造方法とし、該製造方法で製造された光電変換素子とする。

【解決手段】積層された複数のトンネル接合型半導体層を有する積層体を作製する積層体作製工程と、該積層体作製工程後に、積層体の上面側に量子ドット用の複数の凸部を有する凹凸パターンを形成するパターン形成工程と、該パターン形成工程で形成した凹部を削って複数の半導体層を貫通する溝を形成する溝形成工程と、を経て形成された3次元量子ドット列を有する、光電変換素子の製造方法とし、該製造方法で製造された光電変換素子とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は光電変換素子及びその製造方法に関し、特に、量子ドット列を有する光電変換素子及びその製造方法に関する。

【背景技術】

【0002】

太陽電池は、発電量当たりの二酸化炭素排出量が少なく、発電用の燃料が不要という利点を有している。そのため、様々な種類の太陽電池に関する研究が、盛んに進められている。現在、実用化されている太陽電池の中では、単結晶シリコン又は多結晶シリコンを用いた、一組のpn接合を有する単接合太陽電池が主流となっている。ところが、単接合太陽電池の光電変換効率の理論限界(以下において、「理論限界効率」という。)は約30%に留まっているため、理論限界効率をさらに向上させる新たな方法が検討されている。

【0003】

これまでに検討されている新たな方法の1つに、バンドギャップ中に狭いバンドあるいは準位を有する中間準位型太陽電池がある。中間準位を生成させる方法としては、量子ドット等の量子構造を用いる方法等が知られている。量子構造を用いることにより、これまで用いられていた半導体のバンドギャップ中に中間準位を形成することが可能になり、従来の太陽電池では吸収することができなかった帯域の太陽光スペクトルをも吸収させることが可能になる。そのため、量子構造を利用した太陽電池によれば、理論限界効率を60%以上にまで向上させることも可能になると考えられている。

【0004】

このような太陽電池に関する技術として、例えば特許文献1には、固体材料の表面にレーザー照射を施して、該表面に量子ドット構造を1バッチの照射で複数個同時に形成し、かつ、量子ドット構造を周期配列させる工程を含む量子ドット形成表面の製造方法が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−269435号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に開示されている技術は、量子ドットの2次元周期パターン配列形成表面を製造する方法である。この技術を用いて、3次元的に配置された量子ドット構造(面内方向のみならず厚さ方向にも量子ドットが周期的に配置された構造)を有する太陽電池を作製するためには、特許文献1に開示されている技術で作製した量子ドットの2次元周期パターン配列形成表面の上側に、量子ドットの2次元周期パターン配列形成表面を繰り返し作製する必要がある。このようにして量子ドットを3次元的に配置すると、量子ドットの厚さ方向の位置が揃い難く、量子ドットによる性能向上効果が不十分になりやすいという問題があった。また、Stranski-Krastanov(SK)モードを用いて量子ドットを作製すると、厚さ方向に隣接する量子ドットの間に配置される障壁層の厚さを薄くすることが困難であり、その厚さを10nm以上30nm以下程度としなければ、障壁層の上に量子ドットを成長させることが困難である。しかしながら、障壁層の厚さが5nmを超えると、光を吸収することにより生成された電子及び正孔(以下において、これらをまとめて「キャリア」ということがある。)が障壁層を通過することが困難になるため、量子ドットによる性能向上効果が不十分になりやすいという問題もあった。

【0007】

そこで本発明は、3次元的に規則的に配置された量子ドット列を有する光電変換素子及びその製造方法を提供することを課題とする。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明は以下の手段をとる。すなわち、

本発明の第1の態様は、積層された複数のトンネル接合型半導体層を有する積層体を作製する積層体作製工程と、該積層体作製工程後に、積層体の上面側に量子ドット用の複数の凸部を有する凹凸パターンを形成するパターン形成工程と、該パターン形成工程で形成した凹部を削って、複数の半導体層を貫通する溝を形成する溝形成工程と、を経て形成された3次元量子ドット列を有することを特徴とする、光電変換素子の製造方法である。

【0009】

本発明の第1の態様及び以下に示す本発明の第2の態様において、「光電変換素子」とは、太陽電池のほか、光検出素子等も含む概念である。また、「トンネル接合型半導体層」とは、絶縁膜と半導体からなる層で構成されており、絶縁膜が、トンネル電流(印加する電圧が仕事関数より低い電圧(例えば、5V以下。素子では0.1V前後。)でも流れる電流。)が流れる程度に薄く(絶縁膜がSi酸化膜である場合、厚さは1nm前後。)構成されている構造をいう。

【0010】

本発明の第1の態様では、積層体を作製した後に、量子ドット用の複数の凸部を有する凹凸パターンを形成し、凹部を削って溝を形成する。そのため、厚さ方向に連なった複数の量子ドットを有する複数の凸部を残すことができ、量子ドットの面内方向位置のみならず厚さ方向の位置をも揃えることができる。したがって、本発明の第1の態様によれば、3次元的に規則的に配置された量子ドット列を有する光電変換素子を製造することが可能な、光電変換素子の製造方法を提供することができる。

【0011】

また、上記本発明の第1の態様において、パターン形成工程で形成される複数の凸部の形状が、円柱状であることが好ましい。かかる形態とすることにより、量子ドットによる量子閉じ込め効果が得られやすくなるので、上記効果に加えて、効率を高めやすい光電変換素子を製造することが可能になる。

【0012】

また、上記本発明の第1の態様において、積層体作製工程とパターン形成工程との間に、積層体の上面側にマスク層を形成するマスク層形成工程を有し、凹凸パターンが、マスク層の上面に形成される多層レジスト法を用いる形態であっても良い。かかる形態とすることにより、量子ドット用の複数の凸部の形状を制御しやすくなるので、光電変換素子の効率を高めやすくなる。

【0013】

また、積層体の上面にマスク層が備えられる上記本発明の第1の態様において、凹凸パターンを自己組織化法で形成しても良い。かかる形態であっても、3次元的に規則的に配置された量子ドット列を有する光電変換素子を製造することが可能な、光電変換素子の製造方法を提供することができる。

【0014】

また、積層体の上面にマスク層が備えられる上記本発明の第1の態様において、マスク層に金属層が含まれることが好ましい。かかる形態とすることにより、量子ドットの形状制御が容易になるので、光電変換素子の効率を高めやすくなる。

【0015】

また、上記本発明の第1の態様において、積層体作製工程が、透明基板又は高分子基板上に積層体を形成する工程であっても良い。かかる形態であっても、3次元的に規則的に配置された量子ドット列を有する光電変換素子を製造することが可能な、光電変換素子の製造方法を提供することができる。

【0016】

本発明の第2の態様は、上記本発明の第1の態様にかかる光電変換素子の製造方法を用いて製造したことを特徴とする、光電変換素子である。

【0017】

本発明の第2の態様にかかる光電変換素子は、上記本発明の第1の態様にかかる光電変換素子の製造方法を用いて製造される。本発明の第1の態様によれば、3次元的に規則的に配置された量子ドット列を有する光電変換素子を製造することが可能なので、本発明の第2の態様によれば、3次元的に規則的に配置された量子ドット列を有する光電変換素子を提供することができる。

【発明の効果】

【0018】

本発明によれば、3次元的に規則的に配置された量子ドット列を有する光電変換素子及びその製造方法を提供することができる。

【図面の簡単な説明】

【0019】

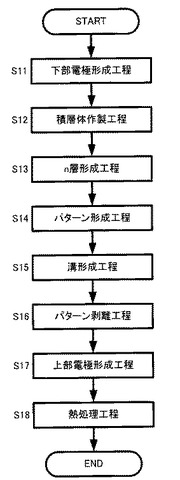

【図1】太陽電池の製造方法を説明するフロー図である。

【図2】各工程を簡略化して説明する図である。

【図3】凹凸パターンの例を示す図である。

【図4】太陽電池の製造方法を説明するフロー図である。

【図5】各工程にオーミック接触や2層レジスト法を加えたものを簡略化して説明する図である。

【図6】エッチング速度の調査結果を示す図である。

【図7】エッチング速度の調査結果を示す図である。

【図8】太陽電池の製造方法を説明するフロー図である。

【図9】各工程を簡略化して説明する図である。

【図10】太陽電池の製造方法を説明するフロー図である。

【図11】各工程を簡略化して説明する図である。

【図12】アニール後のPS−PDMSを説明する図である。

【図13】自己組織化法で形成したドット列を示す図である。

【発明を実施するための形態】

【0020】

以下、図面を参照しつつ、本発明の一形態である太陽電池及びその製造方法について説明する。なお、以下に示す形態は本発明の例示であり、本発明は以下に示す形態に限定されない。

【0021】

図1は、本発明の一形態である太陽電池の製造方法(第1の態様)を説明するフロー図であり、図2は、図1に示した各工程を簡略化して説明する図である。図2では、繰り返される一部符号の記載を省略している。図1に示した本発明の太陽電池の製造方法は、下部電極形成工程(S11)と、積層体作製工程(S12)と、n層形成工程(S13)と、パターン形成工程(S14)と、溝形成工程(S15)と、パターン剥離工程(S16)と、上部電極形成工程(S17)と、熱処理工程(S18)と、を有している。

【0022】

下部電極形成工程(以下において、「S11」という。)は、基板2の一方の面に下部電極1を形成する工程である。S11は、太陽電池の電極である下部電極1を基板2に形成可能であれば、その形態は特に限定されない。S11は、例えば蒸着法等の公知の方法によって、基板2の一方の面に下部電極1を形成する工程、とすることができる。S11において、下部電極1には、例えばAl、Ag、Au等、太陽電池の電極として使用可能な公知の材料を適宜用いることができ、基板2には、例えば公知のp型半導体の基板(例えば、p型のSi基板等)を適宜用いることができる。

【0023】

積層体作製工程(以下において、「S12」という。)は、下部電極1が形成されていない側の基板2の面(下部電極1を形成した面の裏面側)に、絶縁層3aとi型の半導体層3bとを交互に形成することにより、交互に積層された複数の絶縁層3a、3a、…、及び、半導体層3b、3b、…を有する積層体3を作製する工程である。S12において、絶縁層3a、3a、…や半導体層3b、3b、…を形成する方法は、特に限定されず、例えば、分子線エピタキシ法(MBE)、化学気相成長法(CVD)等の公知の方法を適宜用いることができる。S12において、絶縁層3aには、例えばSiO2等、太陽電池に用いることが可能な公知の絶縁性材料を適宜用いることができ、半導体層3bには、例えばSi、GaAs、InP、InAs等、太陽電池に用いることが可能な公知のi型の半導体を適宜用いることができる。

【0024】

n層形成工程(以下において、「S13」という。)は、S12で形成した積層体3の上面に、n型の半導体層4(以下において、「n層4」ということがある。)を形成する工程である。n層4を形成する方法は特に限定されず、例えば、化学気相成長法(CVD)、分子線エピタキシ法(MBE)等の公知の方法を適宜用いることができる。S13において、n層4には、例えばSi等、太陽電池に用いることが可能な公知のn型の半導体を適宜用いることができる。

【0025】

パターン形成工程(以下において、「S14」という。)は、S13で形成したn型の半導体層4の上面に、量子ドット用の複数の凸部5a、5a、…を有する凹凸パターン5を形成する工程である。より具体的には、S14は、公知のレジストをn型の半導体層4の上面に塗布した後、電子ビーム描画装置を用いて、量子ドット用の複数の凸部5a、5a、…を有する凹凸パターン5(レジストパターン5)を形成する工程である。S14において、凹凸パターン5を形成する際に使用可能なレジスト材料としては、カリクサレン、水素化シルセスキオキサン(HSQ)等を例示ことができる。S14で形成した凹凸パターン5の例を図3(a)〜(c)に示す。図3(a)〜(c)の明るい部位が凸部であり、図3(a)〜(c)に示した凸部の直径は、約15nmである。図3(a)は、図の左右方向の間隔が30nmで図の上下方向の間隔が30nmとなるように形成した複数の凸部を示している。また、図3(b)は、図の左右方向の間隔が30nmで図の上下方向の間隔が25nmとなるように形成した複数の凸部を示している。また、図3(c)は、図の左右方向の間隔が25nmで図の上下方向の間隔が25nmとなるように形成した複数の凸部を示している。

【0026】

溝形成工程(以下において、「S15」という。)は、S14で形成した凹凸パターン5の凹部を削って、複数の半導体層3b、3b、…を貫通する溝6を形成する工程である。S15は、凹凸パターン5の凹部を削って半導体層3b、3b、…を貫通する溝6を形成可能であれば、その形態は特に限定されない。S15は、例えば、イオンミリングや反応性イオンエッチング法(RIE法)により、溝6を形成する工程、とすることができる。イオンミリングを用いた場合、凹凸パターン5に照射されるイオンとしては、Arイオン等を例示することができる。

【0027】

パターン剥離工程(以下において、「S16」という。)は、S15の後に、量子ドット用の凸部5a、5a、…を除去する工程である。S16は、n層4、積層体3、基板2、及び、下部電極1を残したまま、凸部5a、5a、…を除去可能であれば、その形態は特に限定されない。S16は、レジストを除去する際に使用することが可能な公知の方法を適宜用いることができる。

【0028】

上部電極形成工程(以下において、「S17」という。)は、S16の後に、凸部5a、5a、…が除去された複数の凸部7、7、…の上面に、上部電極8を形成する工程である。S17は、凸部7、7、…の上面に上部電極8を形成可能であれば、その形態は特に限定されない。S17は、例えば、斜めスパッタ法により、凸部7、7、…の上面に上部電極8を形成する工程、とすることができる。また、S17は、例えば、スパッタ法等を用いて上部電極8を別途作製した後、当該上部電極8の表面に接着剤(例えばペースト状の銀等)を塗布し、この接着剤を介して凸部7、7、…と上部電極8とを接着することにより、凸部7、7、…の上面に上部電極8を形成する工程、とすることも可能である。接着剤を介して凸部7、7、…と上部電極8とを接着する場合、後述する熱処理工程の時間を調整することにより、凸部7、7、…と上部電極8との接合具合を調整することが可能になる。このほか、S17は、例えば、凸部7、7、…の斜め上方からTi電極膜を薄く蒸着してから、斜めスパッタ法により、Ti電極膜の上面に上部電極8を形成する工程、とすることも可能である。S17において、上部電極8には、太陽電池の電極に使用可能な透明導電性材料を適宜用いることができる。そのような透明導電性材料としては、酸化インジウムスズ(ITO)等を例示することができる。

【0029】

熱処理工程(以下において、「S18」という。)は、S17の後に、凸部7、7、…等に残存している損傷(上記S15で凸部7、7、…等に形成された損傷)を緩和し、且つ、凸部7、7、…に含まれる半導体層3b、3b、…やn層4等を結晶化するために、熱処理(アニール)を行う工程である。S18は、凸部7、7、…に残存している損傷を緩和すること及び半導体を結晶化させることが可能であれば、その形態は特に限定されない。S18は、例えば、レーザー光を断続的に照射することによって、S17を経た試料を局所的に加熱する工程、とすることも可能である。S18で加熱される試料の温度は、例えば850℃以上1200℃以下とすることができ、S18の時間(熱処理時間)は、例えば1秒以上60分以下とすることができる。エッチング後のアニールとしては、上記の条件が必要であるが、電極に銀等を用いた場合、上記のように温度を上げることができず、500℃以下でアニールする必要がある。

【0030】

上記S11〜S18を経ることにより、面内方向(図2の紙面左右方向や図2の紙面奥/手前方向。第1の態様に関する以下の説明において同じ。)は溝で隔てられ、且つ、厚さ方向(図2の紙面上下方向。第1の態様に関する以下の説明において同じ。)は絶縁層3a、3a、…で隔てられた、3次元的に規則的に配置された量子ドット3d、3d、…を有する太陽電池10を作製することができる。太陽電池10を作製する際には、積層体3を作製した後に、溝6を形成するので、面内方向のみならず厚さ方向にも、量子ドット3d、3d、…を規則的に配置することができる。したがって、本発明によれば、3次元的に規則的に配置された量子ドット3d、3d、…を有する光電変換素子(太陽電池10)を製造することが可能な、光電変換素子の製造方法を提供することができる。量子ドット3d、3d、…を面内方向及び厚さ方向に規則的に配置することにより、量子ドットによる性能向上効果が得られやすくなるので、太陽電池10によれば、従来の量子ドット型太陽電池よりも、性能を高めることが可能になる。

【0031】

上記太陽電池の製造方法において、太陽電池の効率を高めやすい形態にする観点から、キャリアが電極方向(図2の紙面上下方向)へ移動しやすい形態にすることが好ましい。かかる観点から、絶縁層3a、3a、…は、キャリアがトンネル伝導により通過可能な厚さにする。絶縁層3a、3a、…の厚さは、例えば、1nm以上3nm以下程度とすることが好ましい。

【0032】

また、上記太陽電池の製造方法において、太陽電池の効率を高めやすい形態にする観点から、キャリアが面内方向へ移動し難い形態にすることが好ましい。かかる観点から、面内方向に隣接する量子ドット3d、3dの間隔は、3nmよりも広くすることが好ましく、例えば10nm程度とすることが好ましい。

【0033】

また、上記太陽電池の製造方法において、太陽電池の効率を高めやすい形態にする観点から、キャリアを電極へと導きやすい形態とすることが好ましく、そのために、量子ドット3d、3d、…内でキャリアが再結合し難い形態とすることが好ましい。量子ドット3d、3d、…の大きさが大きくなると量子ドット3d、3d、…内でキャリアが再結合しやすくなるので、量子ドット3d、3d、…の大きさ(図2の紙面上下方向の大きさ(厚さ)及び図2の紙面左右方向や図2の紙面奥/手前方向の大きさ(直径)。以下において同じ。)は、デバイ長未満とすることが好ましい。量子ドット3d、3d、…の大きさは、例えば40nm未満とする。一方、量子ドット3d、3d、…の大きさは、キャリアが入った時にポテンシャルが上昇しない程度の大きさにすることが好ましい。かかる観点から、量子ドット3d、3d、…の大きさは、例えば10nmよりも大きくすることが好ましい。それゆえ、量子ドット3d、3d、…の大きさは、例えば10nm以上40nm未満とすることが好ましい。量子ドット3d、3d、…をこのような大きさとした場合に、キャリアが面内方向へ移動し難い形態にする観点から、面内方向に隣接する量子ドット3d、3dの中心の間隔は、ドット径+10nmよりも広くすることが好ましい。ここで、量子ドット3d、3d、…の厚さは半導体層3a、3a、…の厚さに相当する。それゆえ、半導体層3a、3a、…の厚さは、例えば10nm以上40nm未満とすることが好ましい。

【0034】

また、上記太陽電池の製造方法において、量子ドット3d、3d、…による量子閉じ込め効果が得られやすい形態にする等の観点から、厚さ方向を法線方向とする切断面における量子ドット3d、3d、…の形状は、円形とすることが好ましい。このような形状の量子ドット3d、3d、…を形成可能にするため、凸部5a、5a、…は円柱状とすることが好ましい。

【0035】

図4は、本発明の一形態である太陽電池の製造方法(第2の態様)を説明するフロー図であり、図5は、図4に示した各工程にオーミック接触や2層レジスト法を加えたものを簡略化して説明する図である。図5において、太陽電池10と同様の構成には、図2で使用した符号と同一の符号を付し、その説明を適宜省略する。また、図5では、繰り返される一部符号の記載を省略している。図4に示した本発明の太陽電池の製造方法は、下部電極形成工程(S21)と、積層体作製工程(S22)と、n層形成工程(S23)と、マスク層形成工程(S24)と、パターン形成工程(S25)と、溝形成工程(S26)と、パターン剥離工程(S27)と、上部電極形成工程(S28)と、熱処理工程(S29)と、を有している。

【0036】

下部電極形成工程(以下において、「S21」という。)は、基板2の一方の面に下部電極1を形成する工程である。S21はS11と同様の工程であるため、ここでは説明を省略する。

【0037】

積層体作製工程(以下において、「S22」という。)は、下部電極1が形成されていない側の基板2の面(下部電極1を形成した面の裏面側)に、積層体3を作製する工程である。S22はS12と同様の工程であるため、ここでは説明を省略する。

【0038】

n型半導体層形成工程(以下において、「S23」という。)は、S22で形成した積層体3の上面に、n型半導体層4を形成する工程である。S23はS13と同様の工程であるため、ここでは説明を省略する。

【0039】

マスク層形成工程(以下において、「S24」という。)は、S23で形成したn層4の上面に、マスク層21を形成する工程である。マスク層21はn層4と電極とをオーミック接触できる金属を用いることが好ましく、例えばTi等が用いられる。これと同時に、マスク層21は2層レジストの下部層として用いる。マスク層21を形成する方法は特に限定されず、例えば、スパッタ法、蒸着法等の公知の方法を適宜用いることができる。S24において、マスク層21には、例えば上記のようにTi等の金属層を適宜用いることができる。

【0040】

パターン形成工程(以下において、「S25」という。)は、S24で形成したマスク層21の上面に、量子ドット用の複数の凸部5a、5a、…を有する凹凸パターン5を形成する工程である。S25では、最初にレジスト層をマスク層21上に塗布する。これは2層レジスト法の上部層になる。これに電子線描画を行い、凸部5a、5a、…を形成する。マスク層21上に凹凸パターン5を形成する点でS25はS14と異なるが、このほかはS14と同様の工程であるため、ここでは説明を省略する。

【0041】

溝形成工程(以下において、「S26」という。)は、S25で形成した凹凸パターン5の凹部を削って、マスク層21を貫通する溝22を形成することにより、凹凸パターン5をマスク層21へ転写し、その後、マスク層21に転写された凹部を反応性イオンエッチング(RIE)で削ることにより、複数の半導体層3b、3b、…を貫通する溝6を形成する工程である。S26のうち、溝22を形成するステップはS15と同様の工程であるため、ここでは説明を省略する。

【0042】

パターン剥離工程(以下において、「S27」という。)は、S26の後に、量子ドット用の凸部5a、5a、…を除去する工程である。マスク層21は、オーミック接触金属として残す。これまではマスク層21はオーミック接触と2層レジストとしての役目を有したが、これからはオーミック接触用金属となる。S27はS16と同様の工程であるため、ここでは説明を省略する。

【0043】

上部電極形成工程(以下において、「S28」という。)は、S27の後に、凸部5a、5a、…が除去されたマスク層21上の複数の凸部7、7、…の上面に、上部電極8を形成する工程である。S28はS17と同様の工程であるため、ここでは説明を省略する。

【0044】

熱処理工程(以下において、「S29」という。)は、S28の後に、凸部7、7、…に残存している損傷(上記S26で凸部7、7、…に形成された損傷)を緩和し、且つ、凸部7、7、…に含まれる半導体層3b、3b、…やn層4等を結晶化する、あるいは損傷軽減のために、熱処理(アニール)を行う工程である。S29はS18と同様の工程であるため、ここでは説明を省略する。

【0045】

上記S21〜S29を経る第2の態様によれば、面内方向(図5の紙面左右方向や図5の紙面奥/手前方向。第2の態様に関する以下の説明において同じ。)は溝で隔てられ、且つ、厚さ方向(図5の紙面上下方向。第2の態様に関する以下の説明において同じ。)は絶縁層3a、3a、…で隔てられた、3次元的に規則的に配置された量子ドット3d、3d、…を有する太陽電池20を作製することができる。太陽電池20を作製する際にも、積層体3を作製した後に、溝6を形成するので、面内方向のみならず厚さ方向にも、量子ドット3d、3d、…を規則的に配置することができる。さらに、第2の態様では、マスク層21の上面に凹凸パターン5を形成して、凹凸パターン5をマスク層21に転写してから溝6をRIEで形成する。かかる形態とすることにより、凸部7、7、…を狙った形状にしやすくなる。狙った形状の凸部7、7、…を形成することにより、太陽電池の性能を高めやすくなるので、第2の態様によれば、太陽電池10よりも高性能の太陽電池20を製造することが可能になる。

【0046】

上記第2の態様の説明では、マスク層21にTi層等の金属層が用いられる形態を例示したが、第2の態様は当該形態に限定されない。ただし、狙った形状やオーミック接触を可能にする凸部7、7、…を形成しやすい形態にする等の観点から、マスク層21はTi層等の金属層とすることが好ましい。

【0047】

また、本発明の製造方法に関する説明では、パターン剥離工程を有する形態について言及しているが、本発明の製造方法は当該形態に限定されない。複数の半導体層を貫通する溝を形成する際に、積層体のみならず凹凸パターン5の凸部5a、5a、…やマスク層21も削ることが可能なので、凸部5a、5a、…やマスク層21の厚さを調整することによって、溝6の形成が完了すると同時に、凸部5a、5a、…やマスク層21が完全に除去される形態(溝形成工程とは別工程のパターン剥離工程を有しない形態)とすることも可能である。

【0048】

上記第2の態様において、基板2を凹ませることなく積層体3のみを貫通する溝6をS26で形成するために必要な、凹凸パターン5形成用のレジスト材料、当該レジスト材料の厚さ、Ti層(マスク層21)の厚さ、及び、積層体3の厚さについて検討した。結果を以下に示す。なお、上述したように、積層体3を構成する絶縁層3b、3b、…は、キャリアがトンネル伝導により通過可能な形態にするため、その厚さは、半導体層3a、3a、…の厚さの数%以下になる。それゆえ、今回の検討では、積層体3がSi層であると仮定した。

【0049】

厚さ100nmのSi層(積層体3)のエッチング(RIE)を行うためのマスクとして、第1のマスクであるレジストの下部に金属膜を形成し、金属膜をエッチングすることにより第2のマスクを形成した。エッチングレートをレジスト≒金属膜<Si層とするために必要なレジスト及び金属膜の材料を選定し、それぞれの必要膜厚を求めた。この方法を2層レジスト法あるいは多層レジスト法という。

【0050】

<検討1:レジスト及び金属の組み合わせの検討>

2種類のレジスト材料(HSQ(水素化シルセスキオキサン)、カリクサレン)、並びに、Ti、Au、及び、Siのエッチングレートを調査した。結果を図6に示す。この結果は、200eVで加速したAr+を用いたイオンミリングの結果である。図6の縦軸はエッチング深さ[nm]であり、横軸はエッチング時間[min]である。マスク層21としてTiを選択したので、これと同等か小さいエッチング速度が良く、図6ではカリクサレンレジストが適していることが分かる。図6に示したように、カリクサレン及びTiのエッチングレート[nm/min]は、カリクサレン:Ti≒1.3:1であり、カリクサレン及びTiのエッチングレートは、Au及びHSQよりもエッチングレートが低く、レジストとしてカリクサレンが一番良い結果を示している。

【0051】

<検討2:金属及びSiのエッチングレートの確認>

CF4を用いた反応性イオンエッチング法(RIE法)によってSiをエッチングして溝6を作製するため、金属(Ti、Au)及びSiのエッチングレートを調査した。結果を図7に示す。図7の縦軸はエッチング深さ[nm]であり、横軸はエッチング時間[min]である。図7に示したように、Ti及びSiのエッチングレート[nm/min]は、Ti:Si≒1:2であり、TiのエッチングレートはSiのエッチングレートよりも小さかった。この結果から、SiエッチングにはマスクとしてTiが適していることが分かった。そのため、レジスト材料としてカリクサレンを用い、マスク層21としてTiを用いるのが適当と判断した。これにより、2層レジスト法の材料を決定できた。

【0052】

<検討3:各層の厚みの決定>

上記検討1及び検討2から、全体の厚さ100nmの多層Si膜と多層SiO2膜のエッチングを行うためには、エッチングレートの大きい膜は厚く、エッチングレートの小さい膜は薄くすることにより、レジスト材料及びマスク層のエッチング終了時とSi層のエッチング終了時とをそろえることが可能になる。なお、SiO2のエッチング速度はSiのエッチング速度と同じとした。上記検討1及び検討2より、エッチングレート[nm/min]は、カリクサレン:Ti:Si≒1.3:1:2である。そのため、厚さ100nmのSi膜を貫通する溝6の深さが100nmになった時にレジスト材料及びマスク層21をちょうど除去するために必要なレジスト材料及びマスク層21の厚さは、それぞれ、65nm及び50nmであることが分かった。これより、安全をみて、多目の層厚が望ましい。また、マスク層21はオーミック接触層として残す必要があるため、Tiのマスク層21の厚さは50nmより大きく、また、カリクサレン膜は70nm以上が必要である。

【0053】

太陽電池の製造方法に関する上記説明では、p層(基板2)とn層4との間にi型の半導体層3a、3a、…が備えられている形態の太陽電池10、20を製造する形態について言及したが、本発明の一形態である太陽電池の製造方法(以下において、「本発明の製造方法」ということがある。)は、当該形態に限定されない。また、本発明の製造方法に関する上記説明では、p型の基板2の上に積層体3等を形成していく形態について言及したが、本発明の製造方法は当該形態に限定されない。本発明の製造方法は、i層を有しない太陽電池を製造する形態とすることも可能であり、n型の基板の上に積層体を形成する形態とすることも可能である。そこで、当該形態の製造方法について、以下に説明する。

【0054】

図8は、本発明の製造方法(第3の態様)を説明するフロー図であり、図9は、図8に示した各工程を簡略化して説明する図である。図9において、太陽電池10と同様の構成には、図2で使用した符号と同一の符号を付し、その説明を適宜省略する。また、図9では、繰り返される一部符号の記載を省略している。図8に示した本発明の製造方法は、下部電極形成工程(S31)と、積層体作製工程(S32)と、パターン形成工程(S33)と、溝形成工程(S34)と、電極分離用絶縁層形成工程(S35)と、パターン剥離工程(S36)と、正孔輸送層形成工程(S37)と、上部電極形成工程(S38)と、熱処理工程(S39)と、を有している。

【0055】

下部電極形成工程(以下において、「S31」という。)は、基板31の一方の面に下部電極1を形成する工程である。S31は、太陽電池の電極である下部電極1を基板31に形成可能であれば、その形態は特に限定されない。S31は、例えば蒸着法等の公知の方法によって、基板31の一方の面に下部電極1を形成する工程、とすることができる。S31において、下部電極1には、例えばAl、Ag、Au等、太陽電池の電極として使用可能な公知の材料を適宜用いることができ、基板31には、例えば公知のn型半導体の基板(例えば、n型のSi基板等)を適宜用いることができる。

【0056】

積層体作製工程(以下において、「S32」という。)は、下部電極1が形成されていない側の基板31の面(下部電極1を形成した面の裏面側)に、絶縁層32とn型の半導体層33a、33a、…又はp型の半導体層33b、33b、…とを交互に形成することにより、交互に積層された複数の絶縁層32、32、…、及び、半導体層33a、33a、…、33a、33b、…を有する積層体34を作製する工程である。n型の半導体層33a、33a、…は、図9の紙面上側に位置する層よりも紙面下側に位置する層の方が、多くの電子を含有するように、n型の半導体層33a、33a、…の形成時に添加される、電子を生じさせるn型不純物濃度が調整されている。また、p型の半導体層33b、33b、…は、図9の紙面下側に位置する層よりも紙面上側に位置する層の方が、多くの正孔を含有するように、p型の半導体層33b、33b、…の形成時に添加される、正孔を生じさせるp型不純物濃度が調整されている。すなわち、積層体34を構成する複数の半導体層33a、33a、…、33b、33b、…は、図9の紙面下側から上側に向かって、徐々にn型からp型に変化している。S32において、絶縁層32、32、…や半導体層33a、33a、…、33b、33b、…を形成する方法は、特に限定されず、例えば、化学気相成長法(CVD)、分子線エピタキシ法(MBE)等の公知の方法を適宜用いることができる。S32において、絶縁層32には、例えばSiO2等、太陽電池に用いることが可能な公知の絶縁性材料を適宜用いることができ、半導体層33a、33a、…、33b、33b、…には、例えばSi、GaAs、InP、InAs等、太陽電池に用いることが可能な公知の半導体を適宜用いることができる。また、S32において、n型不純物及びp型不純物は、公知のn型不純物及びp型不純物を適宜用いることができる。

【0057】

パターン形成工程(以下において、「S33」という。)は、S32で形成した積層体34の上面に、量子ドット用の複数の凸部5a、5a、…を有する凹凸パターン5を形成する工程である。S33はS14と同様の工程であるため、ここでは説明を省略する。

【0058】

溝形成工程(以下において、「S34」という。)は、S33で形成した凹凸パターン5の凹部を削って、複数の半導体層33a、33a、…、33b、33b、…を貫通する溝35を形成する工程である。S34は、凹凸パターン5の凹部を削って溝35を形成可能であれば、その形態は特に限定されない。S34は、例えば、イオンミリングにより、溝35を形成する工程、とすることができる。凹凸パターン5に照射されるイオンとしては、Arイオン等を例示することができる。

【0059】

電極分離用絶縁層形成工程(以下において、「S35」という。)は、S34で形成した溝35に絶縁性材料36を充填することにより、面内方向に隣接する量子ドット34ad、34ad、…又は量子ドット34bd、34bd、…の間に絶縁性材料36を配置する工程である。S35は、例えば、スパッタ法等の公知の方法によって、溝35に絶縁性材料36(例えば、SiO2等)を充填する工程、とすることができる。

【0060】

パターン剥離工程(以下において、「S36」という。)は、S35の後に、凸部5a、5a、…、及び、一番上に配置された絶縁層32よりも上に存在する絶縁性材料36を除去する工程である。S36は、積層体34、基板31、及び、下部電極1を残したまま、凸部5a、5a、…及び一番上に配置された絶縁層32よりも上に存在する絶縁性材料36を除去可能であれば、その形態は特に限定されない。S36は、例えば、イオンミリングやエッチング等の公知の方法によって、凸部5a、5a、…及び一番上に配置された絶縁層32よりも上に存在する絶縁性材料36を除去する工程、とすることができる。S35及びS36を経ることにより、溝35に絶縁性材料36が充填された積層体34の上面を平滑面にすることが可能になる。

【0061】

正孔輸送層形成工程(以下において、「S37」という。)は、S36の後に、積層体34の上面に正孔輸送層37を形成する工程である。S36で形成される正孔輸送層37は、多数の正孔を含有する層であり、例えば、積層体34に含まれるp型の半導体層33b、33b、…のうち、最も多くの正孔を含有する半導体層33bよりも、多くの正孔を含有する層を正孔輸送層37とすることができる。S37は、例えば、公知のp型不純物をドープしながら、化学気相成長法(CVD)、分子線エピタキシ法(MBE)、その他、イオン打込み法、拡散法等を使用して積層体34の上面に正孔輸送層37を形成する工程、とすることができる。正孔輸送層37は、例えば、Si、GaAs、InP、InAs等、太陽電池に用いることが可能な公知の半導体を適宜用いることができる。

【0062】

上部電極形成工程(以下において、「S38」という。)は、S37で形成された正孔輸送層37の上面に上部電極8を形成する工程である。S38は、例えば、スパッタ法等の公知の方法によって、正孔輸送層37の上面に上部電極8を形成する工程、とすることができる。

【0063】

熱処理工程(以下において、「S39」という。)は、S38の後に、量子ドット34ad、34ad、…、及び、量子ドット34bd、34bd、…(以下において、単に「量子ドット」という。)等に残存している損傷を緩和し、且つ、量子ドットや正孔輸送層37等を結晶化するために、熱処理(アニール)を行う工程である。S39は、量子ドット等に残存している損傷を緩和すること及び半導体を結晶化させることが可能であれば、その形態は特に限定されない。S39は、例えば、レーザー光を断続的に照射することによって、S38を経た試料を局所的に加熱する工程、とすることも可能である。S39で加熱される試料の温度は、例えば850℃以上1200℃以下とすることができ、S39の時間(熱処理時間)は、例えば1秒以上60分以下とすることができる。

【0064】

上記S31〜S39を経ることにより、面内方向(図9の紙面左右方向や図9の紙面奥/手前方向。第3の態様に関する以下の説明において同じ。)は絶縁性材料36で隔てられ、且つ、厚さ方向(図9の紙面上下方向。第3の態様に関する以下の説明において同じ。)は絶縁層32、32、…で隔てられた、3次元的に規則的に配置された量子ドットを有する太陽電池30を作製することができる。太陽電池30を作製する際にも、積層体34を作製した後に、溝35を形成するので、面内方向のみならず厚さ方向にも、量子ドットを規則的に配置することができる。さらに、第3の態様では、溝35に絶縁性材料36を充填するので、面内方向に隣接する量子ドットや厚さ方向に隣接する量子ドットが導電性材料を介して接続される事態を回避することが可能になる。隣接する量子ドットが導電性材料を介して接続される事態を回避することにより、太陽電池30に備えられているすべての量子ドットに量子閉じ込め効果を発揮させること、及び、下部電極1と上部電極8との短絡を防止することが可能になるので、太陽電池30の性能を高めやすくなる。したがって、第3の態様によれば、性能を高めやすい太陽電池30を製造することが可能になる。

【0065】

本発明の製造方法に関する上記説明では、電子ビーム描画装置を用いて凹凸パターン5を形成する形態を例示したが、本発明の製造方法は当該形態に限定されない。そこで、他の方法によって量子ドット用の凸部を有する凹凸パターンを形成する工程を有する、本発明の製造方法について、以下に説明する。

【0066】

図10は、本発明の製造方法(第4の態様)を説明するフロー図であり、図11は、図10に示した各工程を簡略化して説明する図である。図11において、太陽電池10や太陽電池20と同様の構成には、図2や図4で使用した符号と同一の符号を付し、その説明を適宜省略する。また、図11では、繰り返される一部符号の記載を省略している。図10に示した本発明の製造方法は、下部電極形成工程(S41)と、積層体作製工程(S42)と、n層形成工程(S43)と、マスク層形成工程(S44)と、パターン形成工程(S45)と、溝形成工程(S46)と、パターン剥離工程(S47)と、上部電極形成工程(S48)と、熱処理工程(S49)と、を有している。

【0067】

下部電極形成工程(以下において、「S41」という。)は、基板2の一方の面に下部電極1を形成する工程である。S41はS11と同様の工程であるため、ここでは説明を省略する。

【0068】

積層体作製工程(以下において、「S42」という。)は、下部電極1が形成されていない側の基板2の面(下部電極1を形成した面の裏面側)に、積層体3を作製する工程である。S42はS12と同様の工程であるため、ここでは説明を省略する。

【0069】

n層形成工程(以下において、「S43」という。)は、S42で形成した積層体3の上面に、n層4を形成する工程である。S43はS13と同様の工程であるため、ここでは説明を省略する。

【0070】

マスク層形成工程(以下において、「S44」という。)は、S43で形成したn層4の上面に、マスク層21を形成する工程である。S44はS24と同様の工程であるため、ここでは説明を省略する。

【0071】

パターン形成工程(以下において、「S45」という。)は、S44で形成したマスク層21の上面に、量子ドット用の複数の凸部41a、41a、…を有する凹凸パターン41を形成する工程である。より具体的には、例えば、プロピレングリコールモノメチルエーテルアセテート(PGMEA)溶剤へ、ポリスチレン(PS)とポリジメチルシロキサン(PDMS)とが共有結合している高分子(PS−PDMS。分子量は30000及び7500の2種類。)を合計で2質量%添加することにより、PS−PDMS溶液を作製する。その後、PS−PDMS溶液をマスク層21(例えばTi層)の上面へスピンコート法(回転数:毎分3000回転、時間:90秒)により塗布する。次いで、窒素ガス雰囲気下、170℃の環境に11時間に亘って保持してアニールした後、プラズマエッチングを行う。ここで、プラズマエッチングは、四フッ化炭素ガスを用いた10秒間に亘るプラズマエッチングによりPDMSをエッチングし、酸素ガスを用いた180秒間に亘るプラズマエッチングによりPSをエッチングする。S45では、アニールすることにより、中央にPDMSが、その周囲にPSがそれぞれ配置された複数の粒を、自己組織化過程により形成することができ、プラズマエッチングすることにより、量子ドット用の複数の凸部41a、41a、…を有する凹凸パターン41を形成することができる。アニール後のPS−PDMSの様子(マスク層21の上方から見た様子を示す概念図)を図12に、プラズマエッチング後の凹凸パターン41の様子(写真)を図13に、それぞれ示す。図13の暗部が、凸部41a、41a、…である。

【0072】

溝形成工程(以下において、「S46」という。)は、S45で形成した凹凸パターン41の凹部を削って、複数の半導体層3b、3b、…を貫通する溝6を形成する工程である。S46はS26と同様の工程であるため、ここでは説明を省略する。

【0073】

パターン剥離工程(以下において、「S47」という。)は、S46の後に、マスク層21及び量子ドット用の凸部41a、41a、…を除去する工程である。マスク層21も除去する点を除いてS47はS27と同様の工程であるため、ここでは説明を省略する。

【0074】

上部電極形成工程(以下において、「S48」という。)は、S47の後に、マスク層21及び凸部41a、41a、…が除去された複数の凸部7、7、…の上面に、上部電極8を形成する工程である。S48はS17と同様の工程であるため、ここでは説明を省略する。

【0075】

熱処理工程(以下において、「S49」という。)は、S48の後に、凸部7、7、…に残存している損傷(上記S46で凸部7、7、…に形成された損傷)を緩和し、且つ、凸部7、7、…に含まれる半導体層3b、3b、…やn層4等を結晶化するために、熱処理(アニール)を行う工程である。S49はS18と同様の工程であるため、ここでは説明を省略する。

【0076】

上記S41〜S49を経ることにより、面内方向(図11の紙面左右方向や図11の紙面奥/手前方向。第4の態様に関する以下の説明において同じ。)は溝で隔てられ、且つ、厚さ方向(図11の紙面上下方向。第4の態様に関する以下の説明において同じ。)は絶縁層3a、3a、…で隔てられた、3次元的に規則的に配置された量子ドット3d、3d、…を有する太陽電池40を作製することができる。図13に示したように、電子ビーム描画装置を用いなくても、量子ドット用の凸部41a、41a、…を有する凹凸パターン41を形成することができ、この凹凸パターン41の凹部を削る過程を経て、3次元的に規則的に配置された量子ドット3d、3d、…を有する太陽電池40を作製することができる。第4の態様は、凹凸パターンの形成方法を除いて、第2の態様と同様である。したがって、第4の態様によれば、太陽電池20と同様の性能を有する太陽電池40を製造することが可能になる。

【0077】

第4の態様に関する上記説明では、マスク層21がTi層であり、PS及びPDMSが用いられる形態を例示したが、第4の態様は当該形態に限定されない。マスク層21にはTi以外の物質を用いることも可能であり、凹凸パターンの材料として、PS及びPDMS以外の物質を用いることも可能である。

【0078】

自己組織化のドット径は約20nm以下であるため、厚さも20nm前後と薄い。このため、マスク層21であるTiと自己組織化ドットの間にSi/カーボン層を用いる多層レジスト法が理想的であり、このような多層レジスト法も本発明の技術的範囲に含まれる。

【0079】

また、電極材については、透明膜が必要であり、凸部7、7、…の上にITO膜の形成も必要である。さらに、基板側にもガラス基板や高分子膜等を用いて本発明を適用してもよく、これも本発明の技術的範囲に含まれる。

【符号の説明】

【0080】

1…下部電極

2、31…基板

3、34…積層体

3a、32…絶縁層

3b、33a、33b…半導体層

3d、34ad、34bd…量子ドット

4…n層

5、41…凹凸パターン

5a、41a…凸部

6、22、35…溝

7…凸部

8…上部電極

10、20、30、40…太陽電池

21…マスク層

36…絶縁性材料

37…正孔輸送層

【技術分野】

【0001】

本発明は光電変換素子及びその製造方法に関し、特に、量子ドット列を有する光電変換素子及びその製造方法に関する。

【背景技術】

【0002】

太陽電池は、発電量当たりの二酸化炭素排出量が少なく、発電用の燃料が不要という利点を有している。そのため、様々な種類の太陽電池に関する研究が、盛んに進められている。現在、実用化されている太陽電池の中では、単結晶シリコン又は多結晶シリコンを用いた、一組のpn接合を有する単接合太陽電池が主流となっている。ところが、単接合太陽電池の光電変換効率の理論限界(以下において、「理論限界効率」という。)は約30%に留まっているため、理論限界効率をさらに向上させる新たな方法が検討されている。

【0003】

これまでに検討されている新たな方法の1つに、バンドギャップ中に狭いバンドあるいは準位を有する中間準位型太陽電池がある。中間準位を生成させる方法としては、量子ドット等の量子構造を用いる方法等が知られている。量子構造を用いることにより、これまで用いられていた半導体のバンドギャップ中に中間準位を形成することが可能になり、従来の太陽電池では吸収することができなかった帯域の太陽光スペクトルをも吸収させることが可能になる。そのため、量子構造を利用した太陽電池によれば、理論限界効率を60%以上にまで向上させることも可能になると考えられている。

【0004】

このような太陽電池に関する技術として、例えば特許文献1には、固体材料の表面にレーザー照射を施して、該表面に量子ドット構造を1バッチの照射で複数個同時に形成し、かつ、量子ドット構造を周期配列させる工程を含む量子ドット形成表面の製造方法が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−269435号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に開示されている技術は、量子ドットの2次元周期パターン配列形成表面を製造する方法である。この技術を用いて、3次元的に配置された量子ドット構造(面内方向のみならず厚さ方向にも量子ドットが周期的に配置された構造)を有する太陽電池を作製するためには、特許文献1に開示されている技術で作製した量子ドットの2次元周期パターン配列形成表面の上側に、量子ドットの2次元周期パターン配列形成表面を繰り返し作製する必要がある。このようにして量子ドットを3次元的に配置すると、量子ドットの厚さ方向の位置が揃い難く、量子ドットによる性能向上効果が不十分になりやすいという問題があった。また、Stranski-Krastanov(SK)モードを用いて量子ドットを作製すると、厚さ方向に隣接する量子ドットの間に配置される障壁層の厚さを薄くすることが困難であり、その厚さを10nm以上30nm以下程度としなければ、障壁層の上に量子ドットを成長させることが困難である。しかしながら、障壁層の厚さが5nmを超えると、光を吸収することにより生成された電子及び正孔(以下において、これらをまとめて「キャリア」ということがある。)が障壁層を通過することが困難になるため、量子ドットによる性能向上効果が不十分になりやすいという問題もあった。

【0007】

そこで本発明は、3次元的に規則的に配置された量子ドット列を有する光電変換素子及びその製造方法を提供することを課題とする。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明は以下の手段をとる。すなわち、

本発明の第1の態様は、積層された複数のトンネル接合型半導体層を有する積層体を作製する積層体作製工程と、該積層体作製工程後に、積層体の上面側に量子ドット用の複数の凸部を有する凹凸パターンを形成するパターン形成工程と、該パターン形成工程で形成した凹部を削って、複数の半導体層を貫通する溝を形成する溝形成工程と、を経て形成された3次元量子ドット列を有することを特徴とする、光電変換素子の製造方法である。

【0009】

本発明の第1の態様及び以下に示す本発明の第2の態様において、「光電変換素子」とは、太陽電池のほか、光検出素子等も含む概念である。また、「トンネル接合型半導体層」とは、絶縁膜と半導体からなる層で構成されており、絶縁膜が、トンネル電流(印加する電圧が仕事関数より低い電圧(例えば、5V以下。素子では0.1V前後。)でも流れる電流。)が流れる程度に薄く(絶縁膜がSi酸化膜である場合、厚さは1nm前後。)構成されている構造をいう。

【0010】

本発明の第1の態様では、積層体を作製した後に、量子ドット用の複数の凸部を有する凹凸パターンを形成し、凹部を削って溝を形成する。そのため、厚さ方向に連なった複数の量子ドットを有する複数の凸部を残すことができ、量子ドットの面内方向位置のみならず厚さ方向の位置をも揃えることができる。したがって、本発明の第1の態様によれば、3次元的に規則的に配置された量子ドット列を有する光電変換素子を製造することが可能な、光電変換素子の製造方法を提供することができる。

【0011】

また、上記本発明の第1の態様において、パターン形成工程で形成される複数の凸部の形状が、円柱状であることが好ましい。かかる形態とすることにより、量子ドットによる量子閉じ込め効果が得られやすくなるので、上記効果に加えて、効率を高めやすい光電変換素子を製造することが可能になる。

【0012】

また、上記本発明の第1の態様において、積層体作製工程とパターン形成工程との間に、積層体の上面側にマスク層を形成するマスク層形成工程を有し、凹凸パターンが、マスク層の上面に形成される多層レジスト法を用いる形態であっても良い。かかる形態とすることにより、量子ドット用の複数の凸部の形状を制御しやすくなるので、光電変換素子の効率を高めやすくなる。

【0013】

また、積層体の上面にマスク層が備えられる上記本発明の第1の態様において、凹凸パターンを自己組織化法で形成しても良い。かかる形態であっても、3次元的に規則的に配置された量子ドット列を有する光電変換素子を製造することが可能な、光電変換素子の製造方法を提供することができる。

【0014】

また、積層体の上面にマスク層が備えられる上記本発明の第1の態様において、マスク層に金属層が含まれることが好ましい。かかる形態とすることにより、量子ドットの形状制御が容易になるので、光電変換素子の効率を高めやすくなる。

【0015】

また、上記本発明の第1の態様において、積層体作製工程が、透明基板又は高分子基板上に積層体を形成する工程であっても良い。かかる形態であっても、3次元的に規則的に配置された量子ドット列を有する光電変換素子を製造することが可能な、光電変換素子の製造方法を提供することができる。

【0016】

本発明の第2の態様は、上記本発明の第1の態様にかかる光電変換素子の製造方法を用いて製造したことを特徴とする、光電変換素子である。

【0017】

本発明の第2の態様にかかる光電変換素子は、上記本発明の第1の態様にかかる光電変換素子の製造方法を用いて製造される。本発明の第1の態様によれば、3次元的に規則的に配置された量子ドット列を有する光電変換素子を製造することが可能なので、本発明の第2の態様によれば、3次元的に規則的に配置された量子ドット列を有する光電変換素子を提供することができる。

【発明の効果】

【0018】

本発明によれば、3次元的に規則的に配置された量子ドット列を有する光電変換素子及びその製造方法を提供することができる。

【図面の簡単な説明】

【0019】

【図1】太陽電池の製造方法を説明するフロー図である。

【図2】各工程を簡略化して説明する図である。

【図3】凹凸パターンの例を示す図である。

【図4】太陽電池の製造方法を説明するフロー図である。

【図5】各工程にオーミック接触や2層レジスト法を加えたものを簡略化して説明する図である。

【図6】エッチング速度の調査結果を示す図である。

【図7】エッチング速度の調査結果を示す図である。

【図8】太陽電池の製造方法を説明するフロー図である。

【図9】各工程を簡略化して説明する図である。

【図10】太陽電池の製造方法を説明するフロー図である。

【図11】各工程を簡略化して説明する図である。

【図12】アニール後のPS−PDMSを説明する図である。

【図13】自己組織化法で形成したドット列を示す図である。

【発明を実施するための形態】

【0020】

以下、図面を参照しつつ、本発明の一形態である太陽電池及びその製造方法について説明する。なお、以下に示す形態は本発明の例示であり、本発明は以下に示す形態に限定されない。

【0021】

図1は、本発明の一形態である太陽電池の製造方法(第1の態様)を説明するフロー図であり、図2は、図1に示した各工程を簡略化して説明する図である。図2では、繰り返される一部符号の記載を省略している。図1に示した本発明の太陽電池の製造方法は、下部電極形成工程(S11)と、積層体作製工程(S12)と、n層形成工程(S13)と、パターン形成工程(S14)と、溝形成工程(S15)と、パターン剥離工程(S16)と、上部電極形成工程(S17)と、熱処理工程(S18)と、を有している。

【0022】

下部電極形成工程(以下において、「S11」という。)は、基板2の一方の面に下部電極1を形成する工程である。S11は、太陽電池の電極である下部電極1を基板2に形成可能であれば、その形態は特に限定されない。S11は、例えば蒸着法等の公知の方法によって、基板2の一方の面に下部電極1を形成する工程、とすることができる。S11において、下部電極1には、例えばAl、Ag、Au等、太陽電池の電極として使用可能な公知の材料を適宜用いることができ、基板2には、例えば公知のp型半導体の基板(例えば、p型のSi基板等)を適宜用いることができる。

【0023】

積層体作製工程(以下において、「S12」という。)は、下部電極1が形成されていない側の基板2の面(下部電極1を形成した面の裏面側)に、絶縁層3aとi型の半導体層3bとを交互に形成することにより、交互に積層された複数の絶縁層3a、3a、…、及び、半導体層3b、3b、…を有する積層体3を作製する工程である。S12において、絶縁層3a、3a、…や半導体層3b、3b、…を形成する方法は、特に限定されず、例えば、分子線エピタキシ法(MBE)、化学気相成長法(CVD)等の公知の方法を適宜用いることができる。S12において、絶縁層3aには、例えばSiO2等、太陽電池に用いることが可能な公知の絶縁性材料を適宜用いることができ、半導体層3bには、例えばSi、GaAs、InP、InAs等、太陽電池に用いることが可能な公知のi型の半導体を適宜用いることができる。

【0024】

n層形成工程(以下において、「S13」という。)は、S12で形成した積層体3の上面に、n型の半導体層4(以下において、「n層4」ということがある。)を形成する工程である。n層4を形成する方法は特に限定されず、例えば、化学気相成長法(CVD)、分子線エピタキシ法(MBE)等の公知の方法を適宜用いることができる。S13において、n層4には、例えばSi等、太陽電池に用いることが可能な公知のn型の半導体を適宜用いることができる。

【0025】

パターン形成工程(以下において、「S14」という。)は、S13で形成したn型の半導体層4の上面に、量子ドット用の複数の凸部5a、5a、…を有する凹凸パターン5を形成する工程である。より具体的には、S14は、公知のレジストをn型の半導体層4の上面に塗布した後、電子ビーム描画装置を用いて、量子ドット用の複数の凸部5a、5a、…を有する凹凸パターン5(レジストパターン5)を形成する工程である。S14において、凹凸パターン5を形成する際に使用可能なレジスト材料としては、カリクサレン、水素化シルセスキオキサン(HSQ)等を例示ことができる。S14で形成した凹凸パターン5の例を図3(a)〜(c)に示す。図3(a)〜(c)の明るい部位が凸部であり、図3(a)〜(c)に示した凸部の直径は、約15nmである。図3(a)は、図の左右方向の間隔が30nmで図の上下方向の間隔が30nmとなるように形成した複数の凸部を示している。また、図3(b)は、図の左右方向の間隔が30nmで図の上下方向の間隔が25nmとなるように形成した複数の凸部を示している。また、図3(c)は、図の左右方向の間隔が25nmで図の上下方向の間隔が25nmとなるように形成した複数の凸部を示している。

【0026】

溝形成工程(以下において、「S15」という。)は、S14で形成した凹凸パターン5の凹部を削って、複数の半導体層3b、3b、…を貫通する溝6を形成する工程である。S15は、凹凸パターン5の凹部を削って半導体層3b、3b、…を貫通する溝6を形成可能であれば、その形態は特に限定されない。S15は、例えば、イオンミリングや反応性イオンエッチング法(RIE法)により、溝6を形成する工程、とすることができる。イオンミリングを用いた場合、凹凸パターン5に照射されるイオンとしては、Arイオン等を例示することができる。

【0027】

パターン剥離工程(以下において、「S16」という。)は、S15の後に、量子ドット用の凸部5a、5a、…を除去する工程である。S16は、n層4、積層体3、基板2、及び、下部電極1を残したまま、凸部5a、5a、…を除去可能であれば、その形態は特に限定されない。S16は、レジストを除去する際に使用することが可能な公知の方法を適宜用いることができる。

【0028】

上部電極形成工程(以下において、「S17」という。)は、S16の後に、凸部5a、5a、…が除去された複数の凸部7、7、…の上面に、上部電極8を形成する工程である。S17は、凸部7、7、…の上面に上部電極8を形成可能であれば、その形態は特に限定されない。S17は、例えば、斜めスパッタ法により、凸部7、7、…の上面に上部電極8を形成する工程、とすることができる。また、S17は、例えば、スパッタ法等を用いて上部電極8を別途作製した後、当該上部電極8の表面に接着剤(例えばペースト状の銀等)を塗布し、この接着剤を介して凸部7、7、…と上部電極8とを接着することにより、凸部7、7、…の上面に上部電極8を形成する工程、とすることも可能である。接着剤を介して凸部7、7、…と上部電極8とを接着する場合、後述する熱処理工程の時間を調整することにより、凸部7、7、…と上部電極8との接合具合を調整することが可能になる。このほか、S17は、例えば、凸部7、7、…の斜め上方からTi電極膜を薄く蒸着してから、斜めスパッタ法により、Ti電極膜の上面に上部電極8を形成する工程、とすることも可能である。S17において、上部電極8には、太陽電池の電極に使用可能な透明導電性材料を適宜用いることができる。そのような透明導電性材料としては、酸化インジウムスズ(ITO)等を例示することができる。

【0029】

熱処理工程(以下において、「S18」という。)は、S17の後に、凸部7、7、…等に残存している損傷(上記S15で凸部7、7、…等に形成された損傷)を緩和し、且つ、凸部7、7、…に含まれる半導体層3b、3b、…やn層4等を結晶化するために、熱処理(アニール)を行う工程である。S18は、凸部7、7、…に残存している損傷を緩和すること及び半導体を結晶化させることが可能であれば、その形態は特に限定されない。S18は、例えば、レーザー光を断続的に照射することによって、S17を経た試料を局所的に加熱する工程、とすることも可能である。S18で加熱される試料の温度は、例えば850℃以上1200℃以下とすることができ、S18の時間(熱処理時間)は、例えば1秒以上60分以下とすることができる。エッチング後のアニールとしては、上記の条件が必要であるが、電極に銀等を用いた場合、上記のように温度を上げることができず、500℃以下でアニールする必要がある。

【0030】

上記S11〜S18を経ることにより、面内方向(図2の紙面左右方向や図2の紙面奥/手前方向。第1の態様に関する以下の説明において同じ。)は溝で隔てられ、且つ、厚さ方向(図2の紙面上下方向。第1の態様に関する以下の説明において同じ。)は絶縁層3a、3a、…で隔てられた、3次元的に規則的に配置された量子ドット3d、3d、…を有する太陽電池10を作製することができる。太陽電池10を作製する際には、積層体3を作製した後に、溝6を形成するので、面内方向のみならず厚さ方向にも、量子ドット3d、3d、…を規則的に配置することができる。したがって、本発明によれば、3次元的に規則的に配置された量子ドット3d、3d、…を有する光電変換素子(太陽電池10)を製造することが可能な、光電変換素子の製造方法を提供することができる。量子ドット3d、3d、…を面内方向及び厚さ方向に規則的に配置することにより、量子ドットによる性能向上効果が得られやすくなるので、太陽電池10によれば、従来の量子ドット型太陽電池よりも、性能を高めることが可能になる。

【0031】

上記太陽電池の製造方法において、太陽電池の効率を高めやすい形態にする観点から、キャリアが電極方向(図2の紙面上下方向)へ移動しやすい形態にすることが好ましい。かかる観点から、絶縁層3a、3a、…は、キャリアがトンネル伝導により通過可能な厚さにする。絶縁層3a、3a、…の厚さは、例えば、1nm以上3nm以下程度とすることが好ましい。

【0032】

また、上記太陽電池の製造方法において、太陽電池の効率を高めやすい形態にする観点から、キャリアが面内方向へ移動し難い形態にすることが好ましい。かかる観点から、面内方向に隣接する量子ドット3d、3dの間隔は、3nmよりも広くすることが好ましく、例えば10nm程度とすることが好ましい。

【0033】

また、上記太陽電池の製造方法において、太陽電池の効率を高めやすい形態にする観点から、キャリアを電極へと導きやすい形態とすることが好ましく、そのために、量子ドット3d、3d、…内でキャリアが再結合し難い形態とすることが好ましい。量子ドット3d、3d、…の大きさが大きくなると量子ドット3d、3d、…内でキャリアが再結合しやすくなるので、量子ドット3d、3d、…の大きさ(図2の紙面上下方向の大きさ(厚さ)及び図2の紙面左右方向や図2の紙面奥/手前方向の大きさ(直径)。以下において同じ。)は、デバイ長未満とすることが好ましい。量子ドット3d、3d、…の大きさは、例えば40nm未満とする。一方、量子ドット3d、3d、…の大きさは、キャリアが入った時にポテンシャルが上昇しない程度の大きさにすることが好ましい。かかる観点から、量子ドット3d、3d、…の大きさは、例えば10nmよりも大きくすることが好ましい。それゆえ、量子ドット3d、3d、…の大きさは、例えば10nm以上40nm未満とすることが好ましい。量子ドット3d、3d、…をこのような大きさとした場合に、キャリアが面内方向へ移動し難い形態にする観点から、面内方向に隣接する量子ドット3d、3dの中心の間隔は、ドット径+10nmよりも広くすることが好ましい。ここで、量子ドット3d、3d、…の厚さは半導体層3a、3a、…の厚さに相当する。それゆえ、半導体層3a、3a、…の厚さは、例えば10nm以上40nm未満とすることが好ましい。

【0034】

また、上記太陽電池の製造方法において、量子ドット3d、3d、…による量子閉じ込め効果が得られやすい形態にする等の観点から、厚さ方向を法線方向とする切断面における量子ドット3d、3d、…の形状は、円形とすることが好ましい。このような形状の量子ドット3d、3d、…を形成可能にするため、凸部5a、5a、…は円柱状とすることが好ましい。

【0035】

図4は、本発明の一形態である太陽電池の製造方法(第2の態様)を説明するフロー図であり、図5は、図4に示した各工程にオーミック接触や2層レジスト法を加えたものを簡略化して説明する図である。図5において、太陽電池10と同様の構成には、図2で使用した符号と同一の符号を付し、その説明を適宜省略する。また、図5では、繰り返される一部符号の記載を省略している。図4に示した本発明の太陽電池の製造方法は、下部電極形成工程(S21)と、積層体作製工程(S22)と、n層形成工程(S23)と、マスク層形成工程(S24)と、パターン形成工程(S25)と、溝形成工程(S26)と、パターン剥離工程(S27)と、上部電極形成工程(S28)と、熱処理工程(S29)と、を有している。

【0036】

下部電極形成工程(以下において、「S21」という。)は、基板2の一方の面に下部電極1を形成する工程である。S21はS11と同様の工程であるため、ここでは説明を省略する。

【0037】

積層体作製工程(以下において、「S22」という。)は、下部電極1が形成されていない側の基板2の面(下部電極1を形成した面の裏面側)に、積層体3を作製する工程である。S22はS12と同様の工程であるため、ここでは説明を省略する。

【0038】

n型半導体層形成工程(以下において、「S23」という。)は、S22で形成した積層体3の上面に、n型半導体層4を形成する工程である。S23はS13と同様の工程であるため、ここでは説明を省略する。

【0039】

マスク層形成工程(以下において、「S24」という。)は、S23で形成したn層4の上面に、マスク層21を形成する工程である。マスク層21はn層4と電極とをオーミック接触できる金属を用いることが好ましく、例えばTi等が用いられる。これと同時に、マスク層21は2層レジストの下部層として用いる。マスク層21を形成する方法は特に限定されず、例えば、スパッタ法、蒸着法等の公知の方法を適宜用いることができる。S24において、マスク層21には、例えば上記のようにTi等の金属層を適宜用いることができる。

【0040】

パターン形成工程(以下において、「S25」という。)は、S24で形成したマスク層21の上面に、量子ドット用の複数の凸部5a、5a、…を有する凹凸パターン5を形成する工程である。S25では、最初にレジスト層をマスク層21上に塗布する。これは2層レジスト法の上部層になる。これに電子線描画を行い、凸部5a、5a、…を形成する。マスク層21上に凹凸パターン5を形成する点でS25はS14と異なるが、このほかはS14と同様の工程であるため、ここでは説明を省略する。

【0041】

溝形成工程(以下において、「S26」という。)は、S25で形成した凹凸パターン5の凹部を削って、マスク層21を貫通する溝22を形成することにより、凹凸パターン5をマスク層21へ転写し、その後、マスク層21に転写された凹部を反応性イオンエッチング(RIE)で削ることにより、複数の半導体層3b、3b、…を貫通する溝6を形成する工程である。S26のうち、溝22を形成するステップはS15と同様の工程であるため、ここでは説明を省略する。

【0042】

パターン剥離工程(以下において、「S27」という。)は、S26の後に、量子ドット用の凸部5a、5a、…を除去する工程である。マスク層21は、オーミック接触金属として残す。これまではマスク層21はオーミック接触と2層レジストとしての役目を有したが、これからはオーミック接触用金属となる。S27はS16と同様の工程であるため、ここでは説明を省略する。

【0043】

上部電極形成工程(以下において、「S28」という。)は、S27の後に、凸部5a、5a、…が除去されたマスク層21上の複数の凸部7、7、…の上面に、上部電極8を形成する工程である。S28はS17と同様の工程であるため、ここでは説明を省略する。

【0044】

熱処理工程(以下において、「S29」という。)は、S28の後に、凸部7、7、…に残存している損傷(上記S26で凸部7、7、…に形成された損傷)を緩和し、且つ、凸部7、7、…に含まれる半導体層3b、3b、…やn層4等を結晶化する、あるいは損傷軽減のために、熱処理(アニール)を行う工程である。S29はS18と同様の工程であるため、ここでは説明を省略する。

【0045】

上記S21〜S29を経る第2の態様によれば、面内方向(図5の紙面左右方向や図5の紙面奥/手前方向。第2の態様に関する以下の説明において同じ。)は溝で隔てられ、且つ、厚さ方向(図5の紙面上下方向。第2の態様に関する以下の説明において同じ。)は絶縁層3a、3a、…で隔てられた、3次元的に規則的に配置された量子ドット3d、3d、…を有する太陽電池20を作製することができる。太陽電池20を作製する際にも、積層体3を作製した後に、溝6を形成するので、面内方向のみならず厚さ方向にも、量子ドット3d、3d、…を規則的に配置することができる。さらに、第2の態様では、マスク層21の上面に凹凸パターン5を形成して、凹凸パターン5をマスク層21に転写してから溝6をRIEで形成する。かかる形態とすることにより、凸部7、7、…を狙った形状にしやすくなる。狙った形状の凸部7、7、…を形成することにより、太陽電池の性能を高めやすくなるので、第2の態様によれば、太陽電池10よりも高性能の太陽電池20を製造することが可能になる。

【0046】

上記第2の態様の説明では、マスク層21にTi層等の金属層が用いられる形態を例示したが、第2の態様は当該形態に限定されない。ただし、狙った形状やオーミック接触を可能にする凸部7、7、…を形成しやすい形態にする等の観点から、マスク層21はTi層等の金属層とすることが好ましい。

【0047】

また、本発明の製造方法に関する説明では、パターン剥離工程を有する形態について言及しているが、本発明の製造方法は当該形態に限定されない。複数の半導体層を貫通する溝を形成する際に、積層体のみならず凹凸パターン5の凸部5a、5a、…やマスク層21も削ることが可能なので、凸部5a、5a、…やマスク層21の厚さを調整することによって、溝6の形成が完了すると同時に、凸部5a、5a、…やマスク層21が完全に除去される形態(溝形成工程とは別工程のパターン剥離工程を有しない形態)とすることも可能である。

【0048】

上記第2の態様において、基板2を凹ませることなく積層体3のみを貫通する溝6をS26で形成するために必要な、凹凸パターン5形成用のレジスト材料、当該レジスト材料の厚さ、Ti層(マスク層21)の厚さ、及び、積層体3の厚さについて検討した。結果を以下に示す。なお、上述したように、積層体3を構成する絶縁層3b、3b、…は、キャリアがトンネル伝導により通過可能な形態にするため、その厚さは、半導体層3a、3a、…の厚さの数%以下になる。それゆえ、今回の検討では、積層体3がSi層であると仮定した。

【0049】

厚さ100nmのSi層(積層体3)のエッチング(RIE)を行うためのマスクとして、第1のマスクであるレジストの下部に金属膜を形成し、金属膜をエッチングすることにより第2のマスクを形成した。エッチングレートをレジスト≒金属膜<Si層とするために必要なレジスト及び金属膜の材料を選定し、それぞれの必要膜厚を求めた。この方法を2層レジスト法あるいは多層レジスト法という。

【0050】

<検討1:レジスト及び金属の組み合わせの検討>

2種類のレジスト材料(HSQ(水素化シルセスキオキサン)、カリクサレン)、並びに、Ti、Au、及び、Siのエッチングレートを調査した。結果を図6に示す。この結果は、200eVで加速したAr+を用いたイオンミリングの結果である。図6の縦軸はエッチング深さ[nm]であり、横軸はエッチング時間[min]である。マスク層21としてTiを選択したので、これと同等か小さいエッチング速度が良く、図6ではカリクサレンレジストが適していることが分かる。図6に示したように、カリクサレン及びTiのエッチングレート[nm/min]は、カリクサレン:Ti≒1.3:1であり、カリクサレン及びTiのエッチングレートは、Au及びHSQよりもエッチングレートが低く、レジストとしてカリクサレンが一番良い結果を示している。

【0051】

<検討2:金属及びSiのエッチングレートの確認>

CF4を用いた反応性イオンエッチング法(RIE法)によってSiをエッチングして溝6を作製するため、金属(Ti、Au)及びSiのエッチングレートを調査した。結果を図7に示す。図7の縦軸はエッチング深さ[nm]であり、横軸はエッチング時間[min]である。図7に示したように、Ti及びSiのエッチングレート[nm/min]は、Ti:Si≒1:2であり、TiのエッチングレートはSiのエッチングレートよりも小さかった。この結果から、SiエッチングにはマスクとしてTiが適していることが分かった。そのため、レジスト材料としてカリクサレンを用い、マスク層21としてTiを用いるのが適当と判断した。これにより、2層レジスト法の材料を決定できた。

【0052】

<検討3:各層の厚みの決定>

上記検討1及び検討2から、全体の厚さ100nmの多層Si膜と多層SiO2膜のエッチングを行うためには、エッチングレートの大きい膜は厚く、エッチングレートの小さい膜は薄くすることにより、レジスト材料及びマスク層のエッチング終了時とSi層のエッチング終了時とをそろえることが可能になる。なお、SiO2のエッチング速度はSiのエッチング速度と同じとした。上記検討1及び検討2より、エッチングレート[nm/min]は、カリクサレン:Ti:Si≒1.3:1:2である。そのため、厚さ100nmのSi膜を貫通する溝6の深さが100nmになった時にレジスト材料及びマスク層21をちょうど除去するために必要なレジスト材料及びマスク層21の厚さは、それぞれ、65nm及び50nmであることが分かった。これより、安全をみて、多目の層厚が望ましい。また、マスク層21はオーミック接触層として残す必要があるため、Tiのマスク層21の厚さは50nmより大きく、また、カリクサレン膜は70nm以上が必要である。

【0053】

太陽電池の製造方法に関する上記説明では、p層(基板2)とn層4との間にi型の半導体層3a、3a、…が備えられている形態の太陽電池10、20を製造する形態について言及したが、本発明の一形態である太陽電池の製造方法(以下において、「本発明の製造方法」ということがある。)は、当該形態に限定されない。また、本発明の製造方法に関する上記説明では、p型の基板2の上に積層体3等を形成していく形態について言及したが、本発明の製造方法は当該形態に限定されない。本発明の製造方法は、i層を有しない太陽電池を製造する形態とすることも可能であり、n型の基板の上に積層体を形成する形態とすることも可能である。そこで、当該形態の製造方法について、以下に説明する。

【0054】

図8は、本発明の製造方法(第3の態様)を説明するフロー図であり、図9は、図8に示した各工程を簡略化して説明する図である。図9において、太陽電池10と同様の構成には、図2で使用した符号と同一の符号を付し、その説明を適宜省略する。また、図9では、繰り返される一部符号の記載を省略している。図8に示した本発明の製造方法は、下部電極形成工程(S31)と、積層体作製工程(S32)と、パターン形成工程(S33)と、溝形成工程(S34)と、電極分離用絶縁層形成工程(S35)と、パターン剥離工程(S36)と、正孔輸送層形成工程(S37)と、上部電極形成工程(S38)と、熱処理工程(S39)と、を有している。

【0055】

下部電極形成工程(以下において、「S31」という。)は、基板31の一方の面に下部電極1を形成する工程である。S31は、太陽電池の電極である下部電極1を基板31に形成可能であれば、その形態は特に限定されない。S31は、例えば蒸着法等の公知の方法によって、基板31の一方の面に下部電極1を形成する工程、とすることができる。S31において、下部電極1には、例えばAl、Ag、Au等、太陽電池の電極として使用可能な公知の材料を適宜用いることができ、基板31には、例えば公知のn型半導体の基板(例えば、n型のSi基板等)を適宜用いることができる。

【0056】

積層体作製工程(以下において、「S32」という。)は、下部電極1が形成されていない側の基板31の面(下部電極1を形成した面の裏面側)に、絶縁層32とn型の半導体層33a、33a、…又はp型の半導体層33b、33b、…とを交互に形成することにより、交互に積層された複数の絶縁層32、32、…、及び、半導体層33a、33a、…、33a、33b、…を有する積層体34を作製する工程である。n型の半導体層33a、33a、…は、図9の紙面上側に位置する層よりも紙面下側に位置する層の方が、多くの電子を含有するように、n型の半導体層33a、33a、…の形成時に添加される、電子を生じさせるn型不純物濃度が調整されている。また、p型の半導体層33b、33b、…は、図9の紙面下側に位置する層よりも紙面上側に位置する層の方が、多くの正孔を含有するように、p型の半導体層33b、33b、…の形成時に添加される、正孔を生じさせるp型不純物濃度が調整されている。すなわち、積層体34を構成する複数の半導体層33a、33a、…、33b、33b、…は、図9の紙面下側から上側に向かって、徐々にn型からp型に変化している。S32において、絶縁層32、32、…や半導体層33a、33a、…、33b、33b、…を形成する方法は、特に限定されず、例えば、化学気相成長法(CVD)、分子線エピタキシ法(MBE)等の公知の方法を適宜用いることができる。S32において、絶縁層32には、例えばSiO2等、太陽電池に用いることが可能な公知の絶縁性材料を適宜用いることができ、半導体層33a、33a、…、33b、33b、…には、例えばSi、GaAs、InP、InAs等、太陽電池に用いることが可能な公知の半導体を適宜用いることができる。また、S32において、n型不純物及びp型不純物は、公知のn型不純物及びp型不純物を適宜用いることができる。

【0057】

パターン形成工程(以下において、「S33」という。)は、S32で形成した積層体34の上面に、量子ドット用の複数の凸部5a、5a、…を有する凹凸パターン5を形成する工程である。S33はS14と同様の工程であるため、ここでは説明を省略する。

【0058】

溝形成工程(以下において、「S34」という。)は、S33で形成した凹凸パターン5の凹部を削って、複数の半導体層33a、33a、…、33b、33b、…を貫通する溝35を形成する工程である。S34は、凹凸パターン5の凹部を削って溝35を形成可能であれば、その形態は特に限定されない。S34は、例えば、イオンミリングにより、溝35を形成する工程、とすることができる。凹凸パターン5に照射されるイオンとしては、Arイオン等を例示することができる。

【0059】

電極分離用絶縁層形成工程(以下において、「S35」という。)は、S34で形成した溝35に絶縁性材料36を充填することにより、面内方向に隣接する量子ドット34ad、34ad、…又は量子ドット34bd、34bd、…の間に絶縁性材料36を配置する工程である。S35は、例えば、スパッタ法等の公知の方法によって、溝35に絶縁性材料36(例えば、SiO2等)を充填する工程、とすることができる。

【0060】

パターン剥離工程(以下において、「S36」という。)は、S35の後に、凸部5a、5a、…、及び、一番上に配置された絶縁層32よりも上に存在する絶縁性材料36を除去する工程である。S36は、積層体34、基板31、及び、下部電極1を残したまま、凸部5a、5a、…及び一番上に配置された絶縁層32よりも上に存在する絶縁性材料36を除去可能であれば、その形態は特に限定されない。S36は、例えば、イオンミリングやエッチング等の公知の方法によって、凸部5a、5a、…及び一番上に配置された絶縁層32よりも上に存在する絶縁性材料36を除去する工程、とすることができる。S35及びS36を経ることにより、溝35に絶縁性材料36が充填された積層体34の上面を平滑面にすることが可能になる。

【0061】

正孔輸送層形成工程(以下において、「S37」という。)は、S36の後に、積層体34の上面に正孔輸送層37を形成する工程である。S36で形成される正孔輸送層37は、多数の正孔を含有する層であり、例えば、積層体34に含まれるp型の半導体層33b、33b、…のうち、最も多くの正孔を含有する半導体層33bよりも、多くの正孔を含有する層を正孔輸送層37とすることができる。S37は、例えば、公知のp型不純物をドープしながら、化学気相成長法(CVD)、分子線エピタキシ法(MBE)、その他、イオン打込み法、拡散法等を使用して積層体34の上面に正孔輸送層37を形成する工程、とすることができる。正孔輸送層37は、例えば、Si、GaAs、InP、InAs等、太陽電池に用いることが可能な公知の半導体を適宜用いることができる。

【0062】

上部電極形成工程(以下において、「S38」という。)は、S37で形成された正孔輸送層37の上面に上部電極8を形成する工程である。S38は、例えば、スパッタ法等の公知の方法によって、正孔輸送層37の上面に上部電極8を形成する工程、とすることができる。

【0063】

熱処理工程(以下において、「S39」という。)は、S38の後に、量子ドット34ad、34ad、…、及び、量子ドット34bd、34bd、…(以下において、単に「量子ドット」という。)等に残存している損傷を緩和し、且つ、量子ドットや正孔輸送層37等を結晶化するために、熱処理(アニール)を行う工程である。S39は、量子ドット等に残存している損傷を緩和すること及び半導体を結晶化させることが可能であれば、その形態は特に限定されない。S39は、例えば、レーザー光を断続的に照射することによって、S38を経た試料を局所的に加熱する工程、とすることも可能である。S39で加熱される試料の温度は、例えば850℃以上1200℃以下とすることができ、S39の時間(熱処理時間)は、例えば1秒以上60分以下とすることができる。

【0064】

上記S31〜S39を経ることにより、面内方向(図9の紙面左右方向や図9の紙面奥/手前方向。第3の態様に関する以下の説明において同じ。)は絶縁性材料36で隔てられ、且つ、厚さ方向(図9の紙面上下方向。第3の態様に関する以下の説明において同じ。)は絶縁層32、32、…で隔てられた、3次元的に規則的に配置された量子ドットを有する太陽電池30を作製することができる。太陽電池30を作製する際にも、積層体34を作製した後に、溝35を形成するので、面内方向のみならず厚さ方向にも、量子ドットを規則的に配置することができる。さらに、第3の態様では、溝35に絶縁性材料36を充填するので、面内方向に隣接する量子ドットや厚さ方向に隣接する量子ドットが導電性材料を介して接続される事態を回避することが可能になる。隣接する量子ドットが導電性材料を介して接続される事態を回避することにより、太陽電池30に備えられているすべての量子ドットに量子閉じ込め効果を発揮させること、及び、下部電極1と上部電極8との短絡を防止することが可能になるので、太陽電池30の性能を高めやすくなる。したがって、第3の態様によれば、性能を高めやすい太陽電池30を製造することが可能になる。

【0065】

本発明の製造方法に関する上記説明では、電子ビーム描画装置を用いて凹凸パターン5を形成する形態を例示したが、本発明の製造方法は当該形態に限定されない。そこで、他の方法によって量子ドット用の凸部を有する凹凸パターンを形成する工程を有する、本発明の製造方法について、以下に説明する。

【0066】

図10は、本発明の製造方法(第4の態様)を説明するフロー図であり、図11は、図10に示した各工程を簡略化して説明する図である。図11において、太陽電池10や太陽電池20と同様の構成には、図2や図4で使用した符号と同一の符号を付し、その説明を適宜省略する。また、図11では、繰り返される一部符号の記載を省略している。図10に示した本発明の製造方法は、下部電極形成工程(S41)と、積層体作製工程(S42)と、n層形成工程(S43)と、マスク層形成工程(S44)と、パターン形成工程(S45)と、溝形成工程(S46)と、パターン剥離工程(S47)と、上部電極形成工程(S48)と、熱処理工程(S49)と、を有している。

【0067】

下部電極形成工程(以下において、「S41」という。)は、基板2の一方の面に下部電極1を形成する工程である。S41はS11と同様の工程であるため、ここでは説明を省略する。

【0068】

積層体作製工程(以下において、「S42」という。)は、下部電極1が形成されていない側の基板2の面(下部電極1を形成した面の裏面側)に、積層体3を作製する工程である。S42はS12と同様の工程であるため、ここでは説明を省略する。

【0069】

n層形成工程(以下において、「S43」という。)は、S42で形成した積層体3の上面に、n層4を形成する工程である。S43はS13と同様の工程であるため、ここでは説明を省略する。

【0070】

マスク層形成工程(以下において、「S44」という。)は、S43で形成したn層4の上面に、マスク層21を形成する工程である。S44はS24と同様の工程であるため、ここでは説明を省略する。

【0071】

パターン形成工程(以下において、「S45」という。)は、S44で形成したマスク層21の上面に、量子ドット用の複数の凸部41a、41a、…を有する凹凸パターン41を形成する工程である。より具体的には、例えば、プロピレングリコールモノメチルエーテルアセテート(PGMEA)溶剤へ、ポリスチレン(PS)とポリジメチルシロキサン(PDMS)とが共有結合している高分子(PS−PDMS。分子量は30000及び7500の2種類。)を合計で2質量%添加することにより、PS−PDMS溶液を作製する。その後、PS−PDMS溶液をマスク層21(例えばTi層)の上面へスピンコート法(回転数:毎分3000回転、時間:90秒)により塗布する。次いで、窒素ガス雰囲気下、170℃の環境に11時間に亘って保持してアニールした後、プラズマエッチングを行う。ここで、プラズマエッチングは、四フッ化炭素ガスを用いた10秒間に亘るプラズマエッチングによりPDMSをエッチングし、酸素ガスを用いた180秒間に亘るプラズマエッチングによりPSをエッチングする。S45では、アニールすることにより、中央にPDMSが、その周囲にPSがそれぞれ配置された複数の粒を、自己組織化過程により形成することができ、プラズマエッチングすることにより、量子ドット用の複数の凸部41a、41a、…を有する凹凸パターン41を形成することができる。アニール後のPS−PDMSの様子(マスク層21の上方から見た様子を示す概念図)を図12に、プラズマエッチング後の凹凸パターン41の様子(写真)を図13に、それぞれ示す。図13の暗部が、凸部41a、41a、…である。

【0072】

溝形成工程(以下において、「S46」という。)は、S45で形成した凹凸パターン41の凹部を削って、複数の半導体層3b、3b、…を貫通する溝6を形成する工程である。S46はS26と同様の工程であるため、ここでは説明を省略する。

【0073】

パターン剥離工程(以下において、「S47」という。)は、S46の後に、マスク層21及び量子ドット用の凸部41a、41a、…を除去する工程である。マスク層21も除去する点を除いてS47はS27と同様の工程であるため、ここでは説明を省略する。

【0074】

上部電極形成工程(以下において、「S48」という。)は、S47の後に、マスク層21及び凸部41a、41a、…が除去された複数の凸部7、7、…の上面に、上部電極8を形成する工程である。S48はS17と同様の工程であるため、ここでは説明を省略する。

【0075】

熱処理工程(以下において、「S49」という。)は、S48の後に、凸部7、7、…に残存している損傷(上記S46で凸部7、7、…に形成された損傷)を緩和し、且つ、凸部7、7、…に含まれる半導体層3b、3b、…やn層4等を結晶化するために、熱処理(アニール)を行う工程である。S49はS18と同様の工程であるため、ここでは説明を省略する。

【0076】

上記S41〜S49を経ることにより、面内方向(図11の紙面左右方向や図11の紙面奥/手前方向。第4の態様に関する以下の説明において同じ。)は溝で隔てられ、且つ、厚さ方向(図11の紙面上下方向。第4の態様に関する以下の説明において同じ。)は絶縁層3a、3a、…で隔てられた、3次元的に規則的に配置された量子ドット3d、3d、…を有する太陽電池40を作製することができる。図13に示したように、電子ビーム描画装置を用いなくても、量子ドット用の凸部41a、41a、…を有する凹凸パターン41を形成することができ、この凹凸パターン41の凹部を削る過程を経て、3次元的に規則的に配置された量子ドット3d、3d、…を有する太陽電池40を作製することができる。第4の態様は、凹凸パターンの形成方法を除いて、第2の態様と同様である。したがって、第4の態様によれば、太陽電池20と同様の性能を有する太陽電池40を製造することが可能になる。

【0077】

第4の態様に関する上記説明では、マスク層21がTi層であり、PS及びPDMSが用いられる形態を例示したが、第4の態様は当該形態に限定されない。マスク層21にはTi以外の物質を用いることも可能であり、凹凸パターンの材料として、PS及びPDMS以外の物質を用いることも可能である。

【0078】

自己組織化のドット径は約20nm以下であるため、厚さも20nm前後と薄い。このため、マスク層21であるTiと自己組織化ドットの間にSi/カーボン層を用いる多層レジスト法が理想的であり、このような多層レジスト法も本発明の技術的範囲に含まれる。

【0079】

また、電極材については、透明膜が必要であり、凸部7、7、…の上にITO膜の形成も必要である。さらに、基板側にもガラス基板や高分子膜等を用いて本発明を適用してもよく、これも本発明の技術的範囲に含まれる。

【符号の説明】

【0080】

1…下部電極

2、31…基板

3、34…積層体

3a、32…絶縁層

3b、33a、33b…半導体層

3d、34ad、34bd…量子ドット

4…n層

5、41…凹凸パターン

5a、41a…凸部

6、22、35…溝

7…凸部

8…上部電極

10、20、30、40…太陽電池

21…マスク層

36…絶縁性材料

37…正孔輸送層

【特許請求の範囲】

【請求項1】

積層された複数のトンネル接合型半導体層を有する積層体を作製する積層体作製工程と、

前記積層体作製工程後に、前記積層体の上面側に量子ドット用の複数の凸部を有する凹凸パターンを形成するパターン形成工程と、

前記パターン形成工程で形成した凹部を削って前記複数の半導体層を貫通する溝を形成する溝形成工程と、を経て形成された3次元量子ドット列を有することを特徴とする、光電変換素子の製造方法。

【請求項2】

前記パターン形成工程で形成される前記複数の凸部の形状が、円柱状であることを特徴とする、請求項1に記載の光電変換素子の製造方法。

【請求項3】

前記積層体作製工程と前記パターン形成工程との間に、前記積層体の上面側にマスク層を形成するマスク層形成工程を有し、

前記凹凸パターンが、前記マスク層の上面に形成される多層レジスト法を用いることを特徴とする、請求項1又は2に記載の光電変換素子の製造方法。

【請求項4】

前記凹凸パターンを自己組織化法で形成したことを特徴とする、請求項3に記載の光電変換素子の製造方法。

【請求項5】

前記マスク層が、金属層であることを特徴とする、請求項3又は4に記載の光電変換素子の製造方法。

【請求項6】

前記積層体作製工程が、透明基板又は高分子基板上に前記積層体を形成する工程であることを特徴とする、請求項1〜5のいずれか1項に記載の光電変換素子の製造方法。

【請求項7】

請求項1〜6のいずれか1項に記載の光電変換素子の製造方法を用いて製造したことを特徴とする、光電変換素子。

【請求項1】

積層された複数のトンネル接合型半導体層を有する積層体を作製する積層体作製工程と、

前記積層体作製工程後に、前記積層体の上面側に量子ドット用の複数の凸部を有する凹凸パターンを形成するパターン形成工程と、

前記パターン形成工程で形成した凹部を削って前記複数の半導体層を貫通する溝を形成する溝形成工程と、を経て形成された3次元量子ドット列を有することを特徴とする、光電変換素子の製造方法。

【請求項2】

前記パターン形成工程で形成される前記複数の凸部の形状が、円柱状であることを特徴とする、請求項1に記載の光電変換素子の製造方法。

【請求項3】

前記積層体作製工程と前記パターン形成工程との間に、前記積層体の上面側にマスク層を形成するマスク層形成工程を有し、

前記凹凸パターンが、前記マスク層の上面に形成される多層レジスト法を用いることを特徴とする、請求項1又は2に記載の光電変換素子の製造方法。

【請求項4】

前記凹凸パターンを自己組織化法で形成したことを特徴とする、請求項3に記載の光電変換素子の製造方法。

【請求項5】

前記マスク層が、金属層であることを特徴とする、請求項3又は4に記載の光電変換素子の製造方法。

【請求項6】

前記積層体作製工程が、透明基板又は高分子基板上に前記積層体を形成する工程であることを特徴とする、請求項1〜5のいずれか1項に記載の光電変換素子の製造方法。

【請求項7】

請求項1〜6のいずれか1項に記載の光電変換素子の製造方法を用いて製造したことを特徴とする、光電変換素子。

【図1】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図3】

【図13】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図3】

【図13】

【公開番号】特開2013−46007(P2013−46007A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2011−184581(P2011−184581)

【出願日】平成23年8月26日(2011.8.26)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【出願人】(504145364)国立大学法人群馬大学 (352)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成23年8月26日(2011.8.26)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【出願人】(504145364)国立大学法人群馬大学 (352)

【Fターム(参考)】

[ Back to top ]