光電変換装置

【課題】電気特性を向上させた光電変換装置を提供する。

【解決手段】結晶性シリコン基板100の一方の面において、第1のシリコン半導体層110および第2のシリコン半導体層120の積層で窓層が形成された光電変換装置であり、第2のシリコン半導体層120は第1のシリコン半導体層110よりもキャリア濃度が高く、かつ開口部を有する構成とする。該開口部においては、第2のシリコン半導体層120を介さずに第1のシリコン半導体層110に光が照射されるため、窓層における光吸収損失を低減することができる。

【解決手段】結晶性シリコン基板100の一方の面において、第1のシリコン半導体層110および第2のシリコン半導体層120の積層で窓層が形成された光電変換装置であり、第2のシリコン半導体層120は第1のシリコン半導体層110よりもキャリア濃度が高く、かつ開口部を有する構成とする。該開口部においては、第2のシリコン半導体層120を介さずに第1のシリコン半導体層110に光が照射されるため、窓層における光吸収損失を低減することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光電変換装置に関する。

【背景技術】

【0002】

近年、地球温暖化対策として、発電時に二酸化炭素の排出の無い光電変換装置が注目されている。その代表例としては、単結晶シリコンや多結晶シリコンなどの結晶性シリコン基板を用いた太陽電池が知られている。

【0003】

結晶性シリコン基板を用いた太陽電池では、結晶性シリコン基板の導電型とは逆の導電型となる層を不純物の拡散で該結晶性シリコン基板の一方の面側に形成する、所謂ホモ接合を有する構成が広く用いられている。

【0004】

また、結晶性シリコン基板の一方の面に、該結晶性シリコン基板とは光学バンドギャップおよび導電型の異なる非晶質シリコンを成膜し、ヘテロ接合を形成した構成も知られている(特許文献1、2参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平4−130671号公報

【特許文献2】特開平10−135497号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述したヘテロ接合を有する太陽電池では、一導電型の単結晶半導体基板と該単結晶シリコン基板とは逆の導電型を有する非晶質半導体層との間にi型の非晶質半導体層を介在したp−n接合を形成している。

【0007】

上記p−n接合領域におけるi型の非晶質半導体層の介在は、単結晶半導体基板の表面欠陥を終端するとともに急峻な接合を形成する効果を奏し、ヘテロ界面でのキャリアの再結合低減に寄与する。

【0008】

一方、窓層として設けられる該単結晶シリコン基板とは逆の導電型を有する非晶質半導体層、および上記i型の非晶質半導体層は、光吸収損失の一要因となっている。

【0009】

窓層においても光キャリアは発生するが、窓層内では少数キャリアが再結合しやすく、電流として取り出せる光キャリアのほとんどはp−n接合より裏面電極側の結晶性シリコン基板内で発生する。つまり、窓層で吸収された光は実質的に利用されない。

【0010】

また、上記i型の非晶質半導体層は、非晶質であるが故に電気伝導度が小さいこともあり、抵抗損失の要因ともなっている。

【0011】

したがって、本発明の一態様は、光吸収損失の少ない光電変換装置を提供することを目的の一つとする。また、抵抗損失の少ない光電変換装置を提供することを目的の一つとする。

【課題を解決するための手段】

【0012】

本明細書で開示する本発明の一態様は、第1のシリコン半導体層および第2のシリコン半導体層の積層で窓層が形成された光電変換装置であり、第2のシリコン半導体層は第1のシリコン半導体層よりもキャリア濃度が高く、かつ開口部を有することを特徴とする。

【0013】

本明細書で開示する本発明の一態様は、結晶性シリコン基板と、結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層と、第1のシリコン半導体層および第2のシリコン半導体層上に形成された透光性導電膜と、透光性導電膜上に形成された、第2のシリコン半導体層と重なる第1の電極と、結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、第3のシリコン半導体層上に形成された第4のシリコン半導体層と、第4のシリコン半導体層上に形成された第2の電極と、を有することを特徴とする光電変換装置である。

【0014】

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、順序や数を限定するものではないことを付記する。

【0015】

上記第4のシリコン半導体層には開口部が形成され、第3のシリコン半導体層および第4のシリコン半導体層上に透光性導電膜が形成されていてもよい。

【0016】

また、第1の電極は、第2のシリコン半導体層の一部と重ねて形成することができる。

【0017】

また、本明細書に開示する本発明の他の一態様は、結晶性シリコン基板と、結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、第1のシリコン半導体層上に形成された開口部を有する第1の透光性導電膜と、開口部に形成された、第1のシリコン半導体層と接する第2のシリコン半導体層と、第2のシリコン半導体層上に形成された第1の電極と、第1の透光性導電膜、第2のシリコン半導体層および第1の電極を覆う第2の透光性導電膜と、結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、第3のシリコン半導体層上に形成された第4のシリコン半導体層と、第4のシリコン半導体層上に形成された第2の電極と、を有することを特徴とする光電変換装置である。

【0018】

また、本明細書に開示する本発明の他の一態様は、結晶性シリコン基板と、結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層と、第2のシリコン半導体層上と重なる第1の電極と、第1のシリコン半導体層、第2のシリコン半導体層および第1の電極を覆う透光性薄膜と、結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、第3のシリコン半導体層上に形成された第4のシリコン半導体層と、第4のシリコン半導体層上に形成された第2の電極と、を有することを特徴とする光電変換装置である。

【0019】

上記結晶性シリコン基板の導電型はn型であり、第1のシリコン半導体層および第2のシリコン半導体層の導電型はp型であり、第3のシリコン半導体層の導電型はi型またはn型であり、第4のシリコン半導体層の導電型はn型であることが好ましい。

【0020】

また、第2のシリコン半導体層のキャリア濃度は、第1のシリコン半導体層のキャリア濃度よりも高く、第4のシリコン半導体層のキャリア濃度は、第3のシリコン半導体層のキャリア濃度よりも高くすることが好ましい。

【発明の効果】

【0021】

本発明の一態様を用いることにより、光電変換装置の窓層における光吸収損失を少なくすることができる。また、光電変換装置の抵抗損失を少なくすることができる。したがって、変換効率の高い光電変換装置を提供することができる。

【図面の簡単な説明】

【0022】

【図1】本発明の一態様である光電変換装置を説明する平面図および断面図。

【図2】本発明の一態様である光電変換装置を説明する平面図および断面図。

【図3】本発明の一態様である光電変換装置を説明する断面図。

【図4】本発明の一態様である光電変換装置を説明する断面図。

【図5】本発明の一態様である光電変換装置を説明する平面図。

【図6】本発明の一態様である光電変換装置を説明する平面図。

【図7】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図8】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図9】本発明の一態様である光電変換装置を説明する断面図。

【図10】本発明の一態様である光電変換装置を説明する断面図。

【図11】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図12】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図13】本発明の一態様である光電変換装置を説明する断面図。

【図14】本発明の一態様である光電変換装置を説明する断面図。

【図15】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図16】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【発明を実施するための形態】

【0023】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略することがある。

【0024】

(実施の形態1)

本実施の形態では、本発明の一態様における光電変換装置、およびその作製方法について説明する。

【0025】

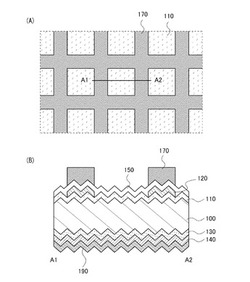

図1(A)は、本発明の一態様における光電変換装置の平面図であり、図1(B)は、該平面図の線分A1−A2における断面図である。該光電変換装置は、結晶性シリコン基板100、該結晶性シリコン基板の一方の面上に形成された第1のシリコン半導体層110、第2のシリコン半導体層120、透光性導電膜150、および第1の電極170、並びに、該結晶性シリコン基板の他方の面上に形成された第3のシリコン半導体層130、第4のシリコン半導体層140、および第2の電極190を含んで構成される。なお、第1の電極170はグリッド電極であり、第1の電極170側が受光面となる。

【0026】

なお、図1(A)の平面図に示す第1の電極170の形状は一例であり、それに限らない。例えば、縦、横の各電極の一方をバスバー電極、他方をフィンガー電極として作用させるために、縦、横の各電極の幅、本数、間隔を実施者が任意に設定することができる。また、図5に示すように、第1の電極170と第2のシリコン半導体層120が重なる領域を少なくして、受光領域を拡大する構成としてもよい。

【0027】

また、図1(B)では、結晶性シリコン基板100の表裏に凹凸加工を施した例を示している。凹凸加工された面では入射光が多重反射し、光電変換領域内には光が斜めに進行することから光路長を増大させることができる。また、裏面反射光が表面で全反射する、所謂光閉じ込め効果を起こさせることもできる。なお、第1の電極170の広幅化や断線を防ぐために、第1のシリコン半導体層110が接する結晶性シリコン基板100の一領域は、凹凸加工をせずに平坦な領域としてもよい。

【0028】

結晶性シリコン基板100には一導電型を有する単結晶シリコン基板、または多結晶シリコン基板を用いることができる。本実施の形態においては、結晶性シリコン基板100にはn型の導電型を有する単結晶シリコン基板が用いられる。

【0029】

上記構造において、結晶性シリコン基板100の一方の面上に形成される第1のシリコン半導体層110および開口部を有する第2のシリコン半導体層120には、p型のシリコン半導体層を用いることができる。該p型シリコン半導体層には、例えば、ホウ素、アルミニウム、またはガリウムなどのp型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0030】

なお、第1のシリコン半導体層110には、第2のシリコン半導体層120よりもキャリア濃度が低いシリコン半導体層を用いることができる。このような構成を明瞭化するため、本明細書においては、第1のシリコン半導体層110などの相対的にキャリア濃度の低いp型半導体層の導電型をp−型と呼称するのに対し、第2のシリコン半導体層120などの相対的にキャリア濃度の高いp型半導体層の導電型をp+型と呼称する。

【0031】

なお、半導体層のキャリア濃度を調整するには、プラズマCVD法等による成膜時にドーパントガスの流量比率を変化させれば良い。原料ガス(例えば、モノシランなど)に対して、ドーパントガス(例えば、ジボラン、ホスフィンなど)の流量比率を高くするほどキャリア濃度を高くすることができる。または、成膜圧力、温度、電力密度などを変化させることにより、形成された半導体層中の不純物の活性化率を変化させてキャリア濃度を調整することもできる。

【0032】

なお、本発明の一態様におけるp−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−10S/cm〜1×10−5S/cm、好ましくは1×10−9S/cm〜1×10−6S/cm、さらに好ましくは1×10−9S/cm〜1×10−7S/cmである。

【0033】

なお、上記電気伝導度(暗伝導度)を有する非晶質シリコン半導体層は、p型の導電型を付与する不純物を故意に添加することによってp−型に制御された非晶質シリコン半導体層である。

【0034】

また、本発明の一態様におけるp+型シリコン半導体層の電気伝導度は、暗状態で1×10−5S/cmより大きいことが好ましい。

【0035】

p−n接合を用いた光電変換装置では、p−n接合内の電界を高め、拡散電位を高めることが電気特性を向上させる一つの手段となる。一般的にはキャリア濃度の高いp+型半導体またはn+型半導体を用いて接合を形成することで拡散電位を高めることができるが、p+型半導体およびn+型半導体は導電型を付与する不純物を多く含み、該不純物は局在準位を増加させてしまう。また、該局在準位によって界面準位の生成が進み、接合部近傍でキャリアの再結合が誘発されてしまう。したがって、接合層のキャリア濃度を高めるだけでは、光電変換装置の電気特性の向上は見込めない。

【0036】

一方、本発明の一態様における光電変換装置では、結晶性シリコン基板100の一方の面において、p−型シリコン半導体層と、p+型シリコン半導体層を積層した構成となっている。該p−型シリコン半導体層は、水素を含む欠陥の少ない半導体層であり、結晶性シリコン基板表面の欠陥を終端するパッシベーション層として作用すると同時に、拡散電位を形成する接合層として寄与する。また、該p+型シリコン半導体層は、さらに拡散電位を高めるように作用する。このような緩やかな接合(n−p−−p+)が形成される構造により、拡散電位を高めながらも界面準位の影響によるキャリアの再結合を極力抑えることができる。

【0037】

また、本発明の一態様である光電変換装置では、第2のシリコン半導体層120に開口部が設けられている。したがって、該開口部においては、第2のシリコン半導体層120を介さずに光電変換領域である結晶性シリコン基板へ光の照射をさせることができる。従来のヘテロ接合型光電変換装置では、界面欠陥を低減させるためのパッシベーション層と拡散電位を高めるための接合層の双方が光電変換領域の全面に積層されていたため、光吸収損失が顕著であった。一方で、本発明の一態様である光電変換装置では、該開口部において、接合層に相当する第2のシリコン半導体層120による光吸収がないため、光吸収損失を極めて少なくすることができる。この効果により、特に光電変換装置の短絡電流を向上させることができる。

【0038】

また、本発明の一態様である光電変換装置は、図2(A)に示す平面図、および図2(B)に示す該平面図の線分B1−B2における断面図の構成を有していてもよい。該光電変換装置は、図1(A)、(B)に示す光電変換装置とは第2のシリコン半導体層120の開口部を少なくした点で異なり、その他の構成は同じである。なお、第2のシリコン半導体層120の開口形状や開口面積は図示した例に限らず、自由に設定することができる。

【0039】

なお、図2(A)の平面図に示す第1の電極170の形状は一例であり、それに限らない。例えば、縦、横の各電極の一方をバスバー電極、他方をフィンガー電極として作用させるために、縦、横の各電極の幅、本数、間隔を実施者が任意に設定することができる。また、図6に示すように、第1の電極170と第2のシリコン半導体層120が重なる領域を少なくして、受光領域を拡大する構成としてもよい。

【0040】

このような構成とすることで、拡散電位をさらに高めることができ、開放電圧および曲線因子を向上させることができる。なお、図2(A)、(B)に示す光電変換装置では、一部の第2のシリコン半導体層120で光吸収が起こるため、図1(A)、(B)に示す光電変換装置よりも短絡電流は小さくなる。したがって、両者の構成の選択は、実施者が用途に応じて適宜選択すればよい。

【0041】

結晶性シリコン基板100の他方の面上に形成される第3のシリコン半導体層130および第4のシリコン半導体層140には、n型のシリコン半導体層を用いることができる。該n型半導体層には、例えば、リン、ヒ素、またはアンチモンなどのn型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0042】

なお、第3のシリコン半導体層130には、第4のシリコン半導体層140よりもキャリア濃度が低いシリコン半導体層を用いることができる。このような構成を明瞭化するため、本明細書においては、第3のシリコン半導体層130などの相対的にキャリア濃度の低いn型半導体層の導電型をn−型と呼称するのに対し、第4のシリコン半導体層140などの相対的にキャリア濃度の高いn型半導体層の導電型をn+型と呼称する。

【0043】

なお、本発明の一態様におけるn−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層は、水素を含む欠陥の少ない半導体層であり、結晶性シリコン基板100の表面欠陥を終端するパッシベーション層として作用させることができる。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−9S/cm〜1×10−4S/cm、好ましくは1×10−8S/cm〜1×10−5S/cm、さらに好ましくは1×10−8S/cm〜1×10−6S/cmである。

【0044】

なお、上記電気伝導度(暗伝導度)を有する非晶質シリコン半導体層は、n型の導電型を付与する不純物を故意に添加することによってn−型に制御された非晶質シリコン半導体層である。

【0045】

また、本発明の一態様におけるn+型シリコン半導体層の電気伝導度は、暗状態で1×10−4S/cmより大きいことが好ましい。

【0046】

また、n+型シリコン半導体層である第4のシリコン半導体層140と結晶性シリコン基板100との間には、第3のシリコン半導体層130を介してn−n+接合が形成される。つまり、第4のシリコン半導体層140は、BSF(Back Surface Field)層として作用する。該接合により形成される電界により少数キャリアがp−n接合側にはね返されることから、第2の電極190近傍でのキャリアの再結合を防止することができる。

【0047】

なお、本発明の一態様における光電変換装置においては、第3のシリコン半導体層130がi型であってもよい。本実施の形態においてi型の半導体層とは、p型もしくはn型を付与する不純物を故意に添加しない高抵抗半導体層、または、p型もしくはn型を付与する不純物を故意に添加することによって導電型が調整された高抵抗半導体層であって、上述したp−型シリコン半導体層およびn−型シリコン半導体層よりも小さい値の電気伝導度(暗伝導度)を有する実質i型の半導体層を意味する。

【0048】

透光性導電膜150には、例えば、インジウム錫酸化物、珪素を含むインジウム錫酸化物、亜鉛を含む酸化インジウム、酸化亜鉛、ガリウムを含む酸化亜鉛、アルミニウムを含む酸化亜鉛、酸化錫、フッ素を含む酸化錫、アンチモンを含む酸化錫、またはグラフェン等を用いることができる。また、透光性導電膜は単層に限らず、異なる膜の積層でも良い。

【0049】

また、第1の電極170および第2の電極190には、銀、アルミニウム、銅などの低抵抗金属を用いることができ、スパッタ法や真空蒸着法などで形成することができる。または、スクリーン印刷法やインクジェット法を用いて、銀ペーストや、銅ペーストなどの導電性樹脂で形成しても良い。

【0050】

なお、本発明の一態様における光電変換装置は、図3(A)、(B)に例示するように、表裏のどちらか一方のみに凹凸加工を施した構成であっても良い。両面が凹凸加工された光電変換装置では、光路長増大などの光学的効果が得られる一方で、結晶性シリコン基板の表面積が増大するため、表面欠陥の絶対量も増大してしまう。したがって、光学的効果と表面欠陥量のバランスを考慮し、より良好な電気特性が得られるように実施者が構造を決定すればよい。

【0051】

また、本発明の一態様における光電変換装置は、図4(A)、(B)に例示するように、第3のシリコン半導体層上に開口部を有する第4のシリコン半導体層140を形成し、該第4のシリコン半導体層上に透光性導電膜180を形成し、該透光性導電膜上にグリッド形状の第2の電極190を形成して、両面を受光面とする構造としてもよい。

【0052】

次に、図1(A)、(B)に示した光電変換装置の作製方法について、図7および図8を用いて説明する。

【0053】

本発明の一態様に用いることのできる結晶性シリコン基板100には、n型の導電型を有する単結晶シリコン基板や多結晶シリコン基板を用いることができる。これらの結晶性シリコン基板の製造方法は、特に限定されない。本実施の形態においては、結晶性シリコン基板100にMCZ(Magnetic Czochralski)法で製造された(100)面を表面に有する単結晶シリコン基板を用いる。

【0054】

次に、結晶性シリコン基板100の表裏に凹凸加工を行う(図7(A)参照)。なお、ここでは上述したように(100)面を表面に有する単結晶シリコン基板を用いる場合を例として凹凸加工の方法の一例を説明する。結晶性シリコン基板100として多結晶シリコン基板を用いる場合は、ドライエッチング法などを用いて凹凸加工を行えばよい。

【0055】

初期の単結晶シリコン基板がスライス加工のみである基板の場合は、単結晶シリコン基板の表面から10〜20μmに残留するダメージ層をウエットエッチング工程にて取り除く。エッチング液には、比較的高濃度のアルカリ溶液、例えば、10〜50%の水酸化ナトリウム水溶液、または同濃度の水酸化カリウム水溶液を用いることができる。または、フッ酸と硝酸を混合した混酸や、それらに酢酸を混合した混酸を用いても良い。

【0056】

次に、ダメージ層除去後の単結晶シリコン基板表面に付着している不純物を酸洗浄で取り除く。酸としては、例えば、0.5%フッ酸と1%過酸化水素水の混合液(FPM)などを用いることができる。またはRCA洗浄などを行っても良い。なお、この酸洗浄工程は省いても良い。

【0057】

凹凸は、結晶シリコンのアルカリ溶液によるエッチングにおいて、面方位に対するエッチングレートの違いを利用して形成する。エッチング液には比較的低濃度のアルカリ溶液、例えば、1〜5%の水酸化ナトリウム水溶液、または同濃度の水酸化カリウム水溶液を用いることができ、好ましくは、数%のイソプロピルアルコールを添加する。エッチング液の温度は70〜90℃とし、30〜60分間、単結晶シリコン基板をエッチング液に浸漬する。この処理により、単結晶シリコン基板表面に、微細な略四角錐状の複数の凸部、および隣接する凸部間で構成される凹部からなる凹凸を形成することができる。

【0058】

次に、上述の凹凸を形成するためのエッチング工程では、シリコンの表層に不均一な酸化層が形成されるため、該酸化層を取り除く。また、該酸化層にはアルカリ溶液の成分が残存しやすいため、それを取り除く目的もある。アルカリ金属、例えばNaイオンやKイオンがシリコン中に侵入するとライフタイムが劣化するため、光電変換装置の電気特性が著しく低下してしまう。なお、この酸化層を除去するには、1〜5%の希フッ酸を用いれば良い。

【0059】

次に、フッ酸と硝酸を混合した混酸、または、それらに酢酸を混合した混酸を用いて単結晶シリコン基板の表面をエッチングし、金属成分などの不純物を除去することが好ましい。酢酸を混合することで、硝酸の酸化力を維持し、エッチング工程を安定にする効果、およびエッチングレートを調整する効果が得られる。例えば、各酸の体積比率は、フッ酸:硝酸:酢酸=1:(1.5〜3):(2〜4)とすることができる。なお、本明細書では、フッ酸、硝酸および酢酸の混酸液をフッ硝酢酸と呼ぶ。また、このフッ硝酢酸を用いたエッチング工程では、凸部の頂点の断面における角度を大きくする方向に変化させることから、表面積が低減し、表面欠陥の絶対量を低減することができる。なお、このフッ硝酢酸を用いたエッチングを行う場合は、上述の希フッ酸を用いた酸化層の除去工程を省くこともできる。ここまでの工程により、結晶性シリコン基板100である単結晶シリコン基板の表面に凹凸を形成することができる。

【0060】

なお、図3(A)、(B)に示すような、結晶性シリコン基板100の片面のみに凹凸加工を行うには、上記凹凸加工工程を行う前に、結晶性シリコン基板100の一方の面にアルカリ耐性および酸耐性の強い樹脂膜などを設け、上記凹凸加工工程後に該樹脂膜を取り除けばよい。

【0061】

次いで、水洗などの適切な洗浄の後、受光面とは逆側となる結晶性シリコン基板100の面上にプラズマCVD法を用いて第3のシリコン半導体層130を形成する。第3のシリコン半導体層130の厚さは、3nm以上50nm以下とすることが好ましい。本実施の形態において、第3のシリコン半導体層130はn−型の非晶質シリコンであり、膜厚は5nmとする。

【0062】

第3のシリコン半導体層130の成膜条件としては、例えば、反応室にモノシラン:水素ベースのホスフィン(0.5%)=1:(0.3〜1未満)となる流量比率で原料ガスを導入し、反応室内の圧力を100Pa以上200Pa以下、電極間隔を10mm以上40mm以下、カソード電極の面積を基準とする電力密度を8mW/cm2以上120mW/cm2以下、基板温度を150℃以上300℃以下とすればよい。

【0063】

次に、第3のシリコン半導体層130上に第4のシリコン半導体層140を形成する(図3(B)参照)。第4のシリコン半導体層140の厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、第4のシリコン半導体層140はn+型の非晶質シリコンであり、膜厚は10nmとする。

【0064】

第4のシリコン半導体層140の成膜条件は、例えば、反応室にモノシラン:水素ベースのホスフィン(0.5%)=1:(1〜15)となる流量比率で原料ガスを導入し、反応室内の圧力を100Pa以上200Pa以下とし、電極間隔を10mm以上40mm以下とし、カソード電極の面積を基準とする電力密度を8mW/cm2以上120mW/cm2以下、基板温度を150℃以上300℃以下とすればよい。

【0065】

次に、受光面側となる結晶性シリコン基板100の面上にプラズマCVD法を用いて第1のシリコン半導体層110を形成する(図7(B)参照)。第1のシリコン半導体層110の厚さは、3nm以上50nm以下とすることが好ましく、本実施の形態において、第1のシリコン半導体層110はp−型の非晶質シリコンであり、膜厚は5nmとする。

【0066】

第1のシリコン半導体層110の成膜条件としては、例えば、反応室にモノシラン:水素ベースのジボラン(0.1%)=1:(0.01〜1未満)となる流量比率で原料ガスを導入し、反応室内の圧力を100Pa以上200Pa以下、電極間隔を10mm以上40mm以下、カソード電極の面積を基準とする電力密度を8mW/cm2以上120mW/cm2以下、基板温度を150℃以上300℃以下とすればよい。

【0067】

次に、第1のシリコン半導体層110上に開口部を有するマスク200を形成する。第2のシリコン半導体層120は該マスクを利用して、リフトオフ法により形成する。該マスクには、フォトレジストや酸化シリコンなどの無機材料で形成することが好ましい。本実施の形態では、スパッタ法などの成膜方法を用いて酸化シリコン層を形成し、フォトリソグラフィ法、エッチング法などの公知の方法を用いて、マスク200を形成する(図7(C)参照)。

【0068】

次に、マスク200および第1のシリコン半導体層110上にp型の導電型を有するシリコン半導体膜120aを形成する(図8(A)参照)。シリコン半導体膜120aの厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、シリコン半導体膜120aはp+型の非晶質シリコンであり、膜厚は10nmとする。

【0069】

シリコン半導体膜120aの成膜条件は、例えば、反応室にモノシラン:水素ベースのジボラン(0.1%)=1:(1〜20)となる流量比率で原料ガスを導入し、反応室内の圧力を100Pa以上200Pa以下とし、電極間隔を8mm以上40mm以下とし、カソード電極の面積を基準とする電力密度を8mW/cm2以上50mW/cm2以下、基板温度を150℃以上300℃以下とすればよい。

【0070】

次に、希フッ酸、またはフッ酸とフッ化アンモニウムの混合液であるバッファードフッ酸を用いて、マスク200および余分なシリコン半導体膜120aを同時に除去して、第2のシリコン半導体層120を形成する(図8(B)参照)。

【0071】

なお、本実施の形態において、第1のシリコン半導体層110、第2のシリコン半導体層120、第3のシリコン半導体層130、および第4のシリコン半導体層140の成膜に用いる電源には周波数13.56MHzのRF電源を用いるが、27.12MHz、60MHz、または100MHzのRF電源を用いても良い。また、連続放電だけでなく、パルス放電にて成膜を行っても良い。パルス放電を行うことで、膜質の向上や気相中で発生するパーティクルを低減することができる。

【0072】

また、結晶性シリコン基板100の表裏に設ける膜の形成順序は、上記の方法に限らず、図8(B)に示した構造が形成できればよい。例えば、第3のシリコン半導体層130を形成し、その次に第1のシリコン半導体層110を形成してもよい。

【0073】

次に、第2のシリコン半導体層120上に透光性導電膜150を形成する。該透光性導電膜は、前述の材料を例えばスパッタ法などを用いて成膜することができる。膜厚は10nm以上1000nm以下とすることが好ましい。

【0074】

次に、第4のシリコン半導体層140上に第2の電極190を形成する。第2の電極190には、銀、アルミニウム、銅などの低抵抗金属を用いることができ、スパッタ法や真空蒸着法などで形成することができる。または、スクリーン印刷法やインクジェット法を用いて、銀ペーストや、銅ペーストなどの導電性樹脂で形成しても良い。

【0075】

次に、透光性導電膜150上に、第2のシリコン半導体層120と重なるように第1の電極170を形成する(図8(C)参照)。第1の電極170はグリッド電極であり、銀ペースト、銅ペースト、ニッケルペースト、モリブデンペーストなどの導電性樹脂を用いて、スクリーン印刷法やインクジェット法で形成することが好ましい。また、第1の電極170は、銀ペーストと銅ペーストを積層するなど、異なる材料の積層であっても良い。

【0076】

なお、図2(A)、(B)に示した光電変換装置を作製するには、第1の電極170と第2のシリコン半導体層120の一部とが重なるように、それぞれの形状を異ならせて形成すればよい。

【0077】

また、図4(A)、(B)の構成の光電変換装置を形成するには、第3のシリコン半導体層130を形成した後に、図7(C)〜図8(C)に示す第2のシリコン半導体層120、透光性導電膜150、第1の電極170の形成方法に従って、第4のシリコン半導体層140、透光性導電膜180、第2の電極190を形成すればよい。

【0078】

以上により、本発明の一態様である光吸収損失および抵抗損失の少ない光電変換装置を作製することができる。

【0079】

本実施の形態は、他の実施の形態と自由に組み合わすことができる。

【0080】

(実施の形態2)

本実施の形態では、実施の形態1で示した光電変換装置とは異なる構成の光電変換装置について説明する。なお、実施の形態1と共通する点については、本実施の形態ではその詳細な説明は省略する。

【0081】

図9は、本発明の一態様における光電変換装置の断面図である。該光電変換装置は、表面が凹凸加工された結晶性シリコン基板300、該結晶性シリコン基板の一方の面上に形成された第1のシリコン半導体層310、該第1のシリコン半導体層上に形成された開口部を有する第1の透光性導電膜410、該開口部に形成された第2のシリコン半導体層320、該第2のシリコン半導体層上に形成された第1の電極370、および該結晶性シリコン基板の一方の面上に形成された上記積層膜を覆う第2の透光性導電膜420を含む。また、該光電変換装置は、該結晶性シリコン基板の他方の面上に形成された第3のシリコン半導体層330、該第3のシリコン半導体層に形成された第4のシリコン半導体層340、該第4のシリコン半導体層上に形成された第2の電極390を含む。なお、第1の電極370はグリッド電極であり、第1の電極370側が受光面となる。

【0082】

また、図10(A)に示すように、表裏のどちらか一方のみに凹凸加工を施した構成であっても良い。なお、第1の電極370の広幅化や断線を防ぐために、第1のシリコン半導体層310が接する結晶性シリコン基板300の一領域は、凹凸加工をせずに平坦な領域としてもよい。

【0083】

また、図10(B)に示すように、第3のシリコン半導体層330上に開口部を有する第3の透光性導電膜430を形成し、該開口部に第4のシリコン半導体層340を形成し、該第4のシリコン半導体層上に第2の電極390を形成し、該結晶性シリコン基板の他方の面上に形成された上記積層膜を覆う第4の透光性導電膜440を形成して、両面を受光面とする構造としてもよい。

【0084】

上記構造において、結晶性シリコン基板300の一方の面上に形成される第1のシリコン半導体層310および第2のシリコン半導体層320には、p型のシリコン半導体層を用いることができる。該p型半導体層には、例えば、ホウ素、アルミニウム、またはガリウムなどのp型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0085】

なお、第1のシリコン半導体層310には、第2のシリコン半導体層320よりもキャリア濃度が低いシリコン半導体層を用いることができる。すなわち、第1のシリコン半導体層310にはp−型、第2のシリコン半導体層320にはp+型の導電型を有するシリコン半導体層を用いることができる。

【0086】

なお、本発明の一態様におけるp−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−10S/cm〜1×10−5S/cm、好ましくは1×10−9S/cm〜1×10−6S/cm、さらに好ましくは1×10−9S/cm〜1×10−7S/cmである。

【0087】

また、本発明の一態様におけるp+型シリコン半導体層の電気伝導度は、暗状態で1×10−5S/cmより大きいことが好ましい。

【0088】

また、結晶性シリコン基板100の他方の面上に形成される第3のシリコン半導体層330および第4のシリコン半導体層340には、n型のシリコン半導体層を用いることができる。該n型シリコン半導体層には、例えば、リン、ヒ素、またはアンチモンなどのn型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0089】

なお、第3のシリコン半導体層330には、第4のシリコン半導体層340よりもキャリア濃度が低いシリコン半導体層を用いることができる。すなわち、第3のシリコン半導体層330にはn−型、第4のシリコン半導体層340にはn+型の導電型を有するシリコン半導体層を用いることができる。

【0090】

なお、本発明の一態様におけるn−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−9S/cm〜1×10−4S/cm、好ましくは1×10−9S/cm〜1×10−5S/cm、さらに好ましくは1×10−9S/cm〜1×10−6S/cmである。

【0091】

また、本発明の一態様におけるn+型シリコン半導体層の電気伝導度は、暗状態で1×10−4S/cmより大きいことが好ましい。

【0092】

第1乃至第4の透光性導電膜410、420、430、440には、例えば、インジウム錫酸化物、珪素を含むインジウム錫酸化物、亜鉛を含む酸化インジウム、酸化亜鉛、ガリウムを含む酸化亜鉛、アルミニウムを含む酸化亜鉛、酸化錫、フッ素を含む酸化錫、アンチモンを含む酸化錫、またはグラフェン等を用いることができる。また、透光性導電膜は単層に限らず、異なる膜の積層でも良い。

【0093】

また、第1の電極370および第2の電極390には、銀、アルミニウム、銅などの低抵抗金属を用いることができ、スパッタ法や真空蒸着法などで形成することができる。または、スクリーン印刷法やインクジェット法を用いて、銀ペーストや、銅ペーストなどの導電性樹脂で形成しても良い。

【0094】

以上の構成を有する本実施の形態における光電変換装置は、実施の形態1で説明した光電変換装置と同様に緩やかな接合(n−p−−p+)が形成される構造であり、拡散電位を高めながらも界面準位の影響によるキャリアの再結合を極力抑えることができる。したがって、特に開放電圧、および曲線因子を向上させることができる。

【0095】

また、本実施の形態における光電変換装置では、第2のシリコン半導体層320に開口部が形成されており、該開口部においては、第2のシリコン半導体層320による光吸収がないため、光吸収損失を極めて少なくすることができる。

【0096】

次に、図9に示した光電変換装置の作製方法について、図11および図12を用いて説明する。

【0097】

本発明の一態様に用いることのできる結晶性シリコン基板300には、n型の導電型を有する単結晶シリコン基板や多結晶シリコン基板を用いることができる。

【0098】

次に、実施の形態1の図7(A)を説明する方法に従って、結晶性シリコン基板300の表裏に凹凸加工を行う(図11(A)参照)。

【0099】

次に、受光面とは逆側となる結晶性シリコン基板300の面上にプラズマCVD法を用いて第3のシリコン半導体層330を形成する。第3のシリコン半導体層330の厚さは、3nm以上50nm以下とすることが好ましい。本実施の形態において、第3のシリコン半導体層330はn−型の非晶質シリコンであり、膜厚は5nmとする。

【0100】

第3のシリコン半導体層330の成膜条件としては、実施の形態1で説明した第3のシリコン半導体層130の成膜条件を参照することができる。

【0101】

次に、第3のシリコン半導体層330上に第4のシリコン半導体層340を形成する。第4のシリコン半導体層340の厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、第4のシリコン半導体層340はn+型の非晶質シリコンであり、膜厚は10nmとする。

【0102】

第4のシリコン半導体層340の成膜条件としては、実施の形態1で説明した第4のシリコン半導体層140の成膜条件を参照することができる。

【0103】

次に、受光面側となる結晶性シリコン基板100の面上にプラズマCVD法を用いて第1のシリコン半導体層310を形成する(図11(B)参照)。第1のシリコン半導体層310の厚さは、3nm以上50nm以下とすることが好ましく、本実施の形態において、第1のシリコン半導体層310はp−型の非晶質シリコンであり、膜厚は5nmとする。

【0104】

第1のシリコン半導体層310の成膜条件としては、実施の形態1で説明した第1のシリコン半導体層110の成膜条件を参照することができる。

【0105】

次に、第1のシリコン半導体層310上に開口部を有する第1の透光性導電膜410を形成する(図11(C)参照)。該透光性導電膜の開口部は、成膜後にフォトリソグラフィ法、エッチング法などの公知の方法を用いて形成するほか、メタルマスクを用いた成膜、またはリフトオフ法などを用いてもよい。なお、該透光性導電膜の成膜はスパッタ法を用いることが好ましい。

【0106】

次に、第1のシリコン半導体層310および第1の透光性導電膜410上にp型の導電型を有するシリコン半導体膜320aを形成する(図12(A)参照)。シリコン半導体膜320aの厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、シリコン半導体膜320aはp+型の非晶質シリコンであり、膜厚は10nmとする。

【0107】

シリコン半導体膜320aの成膜条件は、実施の形態1で説明したシリコン半導体膜120aの成膜条件を参照することができる。

【0108】

なお、結晶性シリコン基板300の表裏に設ける膜の形成順序は、上記の方法に限らず、図12(A)に示した構造が形成できればよい。例えば、第3のシリコン半導体層330を形成し、その次に第1のシリコン半導体層310を形成してもよい。

【0109】

次に、シリコン半導体膜320a上に第1の電極370を形成する。このとき、第1の電極370は、第1の透光性導電膜410に形成された開口部の形状に合わせて形成することが好ましい。第1の電極370の形成方法は、実施の形態1の第1の電極170の形成方法を参照することができる。

【0110】

そして、第1の電極370をマスクにして、余分なシリコン半導体膜320aを公知の方法で取り除き、第2のシリコン半導体層320を形成する(図12(B)参照)。

【0111】

次に、第4のシリコン半導体層340上に第2の電極390を形成する。第2の電極390の形成方法は、実施の形態1で説明した第2の電極190の形成方法を参照することができる。

【0112】

次に、第1の透光性導電膜410上に形成された上記積層を覆うように第2の透光性導電膜420を形成する(図12(C)参照)。第2の透光性導電膜420は、スパッタ法等で形成すればよい。

【0113】

以上により、本発明の一態様である光吸収損失および抵抗損失の少ない光電変換装置を作製することができる。

【0114】

本実施の形態は、他の実施の形態と自由に組み合わすことができる。

【0115】

(実施の形態3)

本実施の形態では、実施の形態1および2で示した光電変換装置とは異なる構成の光電変換装置について説明する。なお、実施の形態1と共通する点については、本実施の形態ではその詳細な説明は省略する。

【0116】

図13は、本発明の一態様における光電変換装置の断面図である。該光電変換装置は、表面が凹凸加工された結晶性シリコン基板500、該結晶性シリコン基板の一方の面上に形成された第1のシリコン半導体層510、該第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層520、該第2のシリコン半導体層上に形成された第1の電極570、および該結晶性シリコン基板の一方の面上に形成された上記積層膜を覆う透光性薄膜610を含む。また、該光電変換装置は、該結晶性シリコン基板の他方の面上に形成された第3のシリコン半導体層530、該第3のシリコン半導体層に形成された第4のシリコン半導体層540、該第4のシリコン半導体層上に形成された第2の電極590を含む。なお、第1の電極570はグリッド電極であり、第1の電極570側が受光面となる。

【0117】

また、図14(A)に示すように、表裏のどちらか一方のみに凹凸加工を施した構成であっても良い。なお、第1の電極570の広幅化や断線を防ぐために、第1のシリコン半導体層510が接する結晶性シリコン基板500の一領域は、凹凸加工をせずに平坦な領域としてもよい。

【0118】

また、図14(B)に示すように、第3のシリコン半導体層530上に開口部を有する第4のシリコン半導体層540を形成し、該第4のシリコン半導体層上に第2の電極590を形成し、該結晶性シリコン基板の他方の面上に形成された上記積層膜を覆う透光性薄膜630を形成して、両面を受光面とする構造としてもよい。

【0119】

上記構造において、結晶性シリコン基板500の一方の面上に形成される第1のシリコン半導体層510および第2のシリコン半導体層520には、p型のシリコン半導体層を用いることができる。該p型半導体層には、例えば、ホウ素、アルミニウム、またはガリウムなどのp型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0120】

なお、第1のシリコン半導体層510には、第2のシリコン半導体層520よりもキャリア濃度が低いシリコン半導体層を用いることができる。すなわち、第1のシリコン半導体層510にはp−型、第2のシリコン半導体層520にはp+型の導電型を有するシリコン半導体層を用いることができる。

【0121】

なお、本発明の一態様におけるp−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−10S/cm〜1×10−5S/cm、好ましくは1×10−9S/cm〜1×10−6S/cm、さらに好ましくは1×10−9S/cm〜1×10−7S/cmである。

【0122】

また、本発明の一態様におけるp+型シリコン半導体層の電気伝導度は、暗状態で1×10−5S/cmより大きいことが好ましい。

【0123】

また、結晶性シリコン基板500の他方の面上に形成される第3のシリコン半導体層530および第4のシリコン半導体層540には、n型のシリコン半導体層を用いることができる。該n型シリコン半導体層には、例えば、リン、ヒ素、またはアンチモンなどのn型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0124】

なお、第3のシリコン半導体層530には、第4のシリコン半導体層540よりもキャリア濃度が低いシリコン半導体層を用いることができる。すなわち、第3のシリコン半導体層530にはn−型、第4のシリコン半導体層540にはn+型の導電型を有するシリコン半導体層を用いることができる。

【0125】

なお、本発明の一態様におけるn−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−9S/cm〜1×10−4S/cm、好ましくは1×10−9S/cm〜1×10−5S/cm、さらに好ましくは1×10−9S/cm〜1×10−6S/cmである。

【0126】

また、本発明の一態様におけるn+型シリコン半導体層の電気伝導度は、暗状態で1×10−4S/cmより大きいことが好ましい。

【0127】

透光性薄膜610には、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン(SiNxOy(x>y>0))膜、酸化窒化シリコン(SiOxNy(x>y>0))膜、酸化アルミニウム膜などの絶縁膜を用いることができる。透光性薄膜610を設けることで、第1のシリコン半導体層510の表面近傍における少数キャリアの再結合を低減させることができる。また、透光性薄膜610は反射防止膜としても作用する。なお、第1の電極570が配線などに接続される部位においては、透光性薄膜610は取り除かれている構成とする。

【0128】

第1の電極570および第2の電極590には、銀ペーストや、銅ペーストなどの導電性樹脂を用いることができ、スクリーン印刷法やインクジェット法などで形成することができる。また、銀、アルミニウム、銅などの低抵抗金属をスパッタ法や真空蒸着法などで形成してもよい。

【0129】

ここで、第1の電極570の幅は、好ましくは100μm以下、さらに好ましくは50μm以下とする。また、第1の電極570が形成される間隔は、500μm以下、好ましくは100μm以下、さらに好ましくは50μm以下とする。このように第1の電極570の線幅を細く、間隔を短くすることで光キャリアの損失を抑えることができる。つまり、実施の形態1または2で説明した光電変換装置と異なり、透光性導電膜を不要にすることができる。なお、図14における第2の電極590も同様である。

【0130】

以上の構成を有する本実施の形態における光電変換装置は、実施の形態1または2で説明した光電変換装置と同様に緩やかな接合(n−p−−p+)が形成される構造であり、拡散電位を高めながらも界面準位の影響によるキャリアの再結合を極力抑えることができる。したがって、特に開放電圧、および曲線因子を向上させることができる。

【0131】

また、本実施の形態における光電変換装置では、第2のシリコン半導体層520に開口部が形成されており、該開口部においては、第2のシリコン半導体層520による光吸収がないため、光吸収損失を極めて少なくすることができる。また、透光性導電膜が形成されていないため、該透光性導電膜による光吸収損失の影響も排除することができる。

【0132】

次に、図13に示した光電変換装置の作製方法について、図15および図16を用いて説明する。

【0133】

本発明の一態様に用いることのできる結晶性シリコン基板500には、n型の導電型を有する単結晶シリコン基板や多結晶シリコン基板を用いることができる。

【0134】

次に、実施の形態1の図7(A)を説明する方法に従って、結晶性シリコン基板300の表裏に凹凸加工を行う(図15(A)参照)。

【0135】

次に、受光面とは逆側となる結晶性シリコン基板500の面上にプラズマCVD法を用いて第3のシリコン半導体層530を形成する。第3のシリコン半導体層530の厚さは、3nm以上50nm以下とすることが好ましい。本実施の形態において、第3のシリコン半導体層530はn−型の非晶質シリコンであり、膜厚は5nmとする。

【0136】

第3のシリコン半導体層530の成膜条件としては、実施の形態1で説明した第3のシリコン半導体層130の成膜条件を参照することができる。

【0137】

次に、第3のシリコン半導体層530上に第4のシリコン半導体層540を形成する。第4のシリコン半導体層540の厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、第4のシリコン半導体層540はn+型の非晶質シリコンであり、膜厚は10nmとする。

【0138】

第4のシリコン半導体層540の成膜条件としては、実施の形態1で説明した第4のシリコン半導体層140の成膜条件を参照することができる。

【0139】

次に、受光面側となる結晶性シリコン基板100の面上にプラズマCVD法を用いて第1のシリコン半導体層510を形成する(図15(B)参照)。第1のシリコン半導体層510の厚さは、3nm以上50nm以下とすることが好ましく、本実施の形態において、第1のシリコン半導体層510はp−型の非晶質シリコンであり、膜厚は5nmとする。

【0140】

第1のシリコン半導体層510の成膜条件としては、実施の形態1で説明した第1のシリコン半導体層110の成膜条件を参照することができる。

【0141】

次に、第1のシリコン半導体層510上に開口部を有するマスク600を形成する。第2のシリコン半導体層520は該マスクを利用して、リフトオフ法により形成する。該マスクには、フォトレジストや酸化シリコンなどの無機材料で形成することが好ましい。本実施の形態では、スパッタ法などの成膜方法を用いて酸化シリコン層を形成し、フォトリソグラフィ法、エッチング法などの方法を用いて、マスク600を形成する(図15(C)参照)。

【0142】

次に、マスク600および第1のシリコン半導体層510上にp型の導電型を有するシリコン半導体膜520aを形成する。シリコン半導体膜520aの厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、シリコン半導体膜520aはp+型の非晶質シリコンであり、膜厚は10nmとする。

【0143】

次に、マスク600の開口部にシリコン半導体膜520a上に導電層570aを形成する(図16(A)参照)。該導電層には、銀ペーストや、銅ペーストなどの導電性樹脂を用いることができ、スクリーン印刷法やインクジェット法などで形成することができる。また、銀、アルミニウム、銅などの低抵抗金属をスパッタ法や真空蒸着法などで形成してもよい。

【0144】

次に、希フッ酸、またはフッ酸とフッ化アンモニウムの混合液であるバッファードフッ酸を用いて、マスク600および余分なシリコン半導体膜520aを同時に除去して、第2のシリコン半導体層520を形成する(図16(B)参照)。

【0145】

次に、第1のシリコン半導体層510、第2のシリコン半導体層520、および第1の電極570を覆うように透光性薄膜610を形成する。該透光性薄膜としては、プラズマCVD法やスパッタ法で成膜される50nm以上100nm以下の膜厚の酸化シリコン膜や窒化シリコン膜を用いることができる。本実施の形態では、50nmの窒化シリコン膜を透光性薄膜610として用いる。

【0146】

次に、第4のシリコン半導体層540上に第2の電極590を形成する。第2の電極590の形成方法は、実施の形態1で説明した第2の電極190の形成方法を参照することができる。

【0147】

以上により、本発明の一態様である光吸収損失および抵抗損失の少ない光電変換装置を作製することができる。

【0148】

本実施の形態は、他の実施の形態と自由に組み合わすことができる。

【符号の説明】

【0149】

100 結晶性シリコン基板

110 第1のシリコン半導体層

120 第2のシリコン半導体層

120a シリコン半導体膜

130 第3のシリコン半導体層

140 第4のシリコン半導体層

150 透光性導電膜

170 第1の電極

180 透光性導電膜

190 第2の電極

200 マスク

300 結晶性シリコン基板

310 第1のシリコン半導体層

320 第2のシリコン半導体層

320a シリコン半導体膜

330 第3のシリコン半導体層

340 第4のシリコン半導体層

370 第1の電極

390 第2の電極

410 第1の透光性導電膜

420 第2の透光性導電膜

430 第3の透光性導電膜

440 第4の透光性導電膜

500 結晶性シリコン基板

510 第1のシリコン半導体層

520 第2のシリコン半導体層

520a シリコン半導体膜

530 第3のシリコン半導体層

540 第4のシリコン半導体層

570 第1の電極

570a 導電層

590 第2の電極

600 マスク

610 透光性薄膜

630 透光性薄膜

【技術分野】

【0001】

本発明は、光電変換装置に関する。

【背景技術】

【0002】

近年、地球温暖化対策として、発電時に二酸化炭素の排出の無い光電変換装置が注目されている。その代表例としては、単結晶シリコンや多結晶シリコンなどの結晶性シリコン基板を用いた太陽電池が知られている。

【0003】

結晶性シリコン基板を用いた太陽電池では、結晶性シリコン基板の導電型とは逆の導電型となる層を不純物の拡散で該結晶性シリコン基板の一方の面側に形成する、所謂ホモ接合を有する構成が広く用いられている。

【0004】

また、結晶性シリコン基板の一方の面に、該結晶性シリコン基板とは光学バンドギャップおよび導電型の異なる非晶質シリコンを成膜し、ヘテロ接合を形成した構成も知られている(特許文献1、2参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平4−130671号公報

【特許文献2】特開平10−135497号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述したヘテロ接合を有する太陽電池では、一導電型の単結晶半導体基板と該単結晶シリコン基板とは逆の導電型を有する非晶質半導体層との間にi型の非晶質半導体層を介在したp−n接合を形成している。

【0007】

上記p−n接合領域におけるi型の非晶質半導体層の介在は、単結晶半導体基板の表面欠陥を終端するとともに急峻な接合を形成する効果を奏し、ヘテロ界面でのキャリアの再結合低減に寄与する。

【0008】

一方、窓層として設けられる該単結晶シリコン基板とは逆の導電型を有する非晶質半導体層、および上記i型の非晶質半導体層は、光吸収損失の一要因となっている。

【0009】

窓層においても光キャリアは発生するが、窓層内では少数キャリアが再結合しやすく、電流として取り出せる光キャリアのほとんどはp−n接合より裏面電極側の結晶性シリコン基板内で発生する。つまり、窓層で吸収された光は実質的に利用されない。

【0010】

また、上記i型の非晶質半導体層は、非晶質であるが故に電気伝導度が小さいこともあり、抵抗損失の要因ともなっている。

【0011】

したがって、本発明の一態様は、光吸収損失の少ない光電変換装置を提供することを目的の一つとする。また、抵抗損失の少ない光電変換装置を提供することを目的の一つとする。

【課題を解決するための手段】

【0012】

本明細書で開示する本発明の一態様は、第1のシリコン半導体層および第2のシリコン半導体層の積層で窓層が形成された光電変換装置であり、第2のシリコン半導体層は第1のシリコン半導体層よりもキャリア濃度が高く、かつ開口部を有することを特徴とする。

【0013】

本明細書で開示する本発明の一態様は、結晶性シリコン基板と、結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層と、第1のシリコン半導体層および第2のシリコン半導体層上に形成された透光性導電膜と、透光性導電膜上に形成された、第2のシリコン半導体層と重なる第1の電極と、結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、第3のシリコン半導体層上に形成された第4のシリコン半導体層と、第4のシリコン半導体層上に形成された第2の電極と、を有することを特徴とする光電変換装置である。

【0014】

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、順序や数を限定するものではないことを付記する。

【0015】

上記第4のシリコン半導体層には開口部が形成され、第3のシリコン半導体層および第4のシリコン半導体層上に透光性導電膜が形成されていてもよい。

【0016】

また、第1の電極は、第2のシリコン半導体層の一部と重ねて形成することができる。

【0017】

また、本明細書に開示する本発明の他の一態様は、結晶性シリコン基板と、結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、第1のシリコン半導体層上に形成された開口部を有する第1の透光性導電膜と、開口部に形成された、第1のシリコン半導体層と接する第2のシリコン半導体層と、第2のシリコン半導体層上に形成された第1の電極と、第1の透光性導電膜、第2のシリコン半導体層および第1の電極を覆う第2の透光性導電膜と、結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、第3のシリコン半導体層上に形成された第4のシリコン半導体層と、第4のシリコン半導体層上に形成された第2の電極と、を有することを特徴とする光電変換装置である。

【0018】

また、本明細書に開示する本発明の他の一態様は、結晶性シリコン基板と、結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層と、第2のシリコン半導体層上と重なる第1の電極と、第1のシリコン半導体層、第2のシリコン半導体層および第1の電極を覆う透光性薄膜と、結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、第3のシリコン半導体層上に形成された第4のシリコン半導体層と、第4のシリコン半導体層上に形成された第2の電極と、を有することを特徴とする光電変換装置である。

【0019】

上記結晶性シリコン基板の導電型はn型であり、第1のシリコン半導体層および第2のシリコン半導体層の導電型はp型であり、第3のシリコン半導体層の導電型はi型またはn型であり、第4のシリコン半導体層の導電型はn型であることが好ましい。

【0020】

また、第2のシリコン半導体層のキャリア濃度は、第1のシリコン半導体層のキャリア濃度よりも高く、第4のシリコン半導体層のキャリア濃度は、第3のシリコン半導体層のキャリア濃度よりも高くすることが好ましい。

【発明の効果】

【0021】

本発明の一態様を用いることにより、光電変換装置の窓層における光吸収損失を少なくすることができる。また、光電変換装置の抵抗損失を少なくすることができる。したがって、変換効率の高い光電変換装置を提供することができる。

【図面の簡単な説明】

【0022】

【図1】本発明の一態様である光電変換装置を説明する平面図および断面図。

【図2】本発明の一態様である光電変換装置を説明する平面図および断面図。

【図3】本発明の一態様である光電変換装置を説明する断面図。

【図4】本発明の一態様である光電変換装置を説明する断面図。

【図5】本発明の一態様である光電変換装置を説明する平面図。

【図6】本発明の一態様である光電変換装置を説明する平面図。

【図7】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図8】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図9】本発明の一態様である光電変換装置を説明する断面図。

【図10】本発明の一態様である光電変換装置を説明する断面図。

【図11】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図12】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図13】本発明の一態様である光電変換装置を説明する断面図。

【図14】本発明の一態様である光電変換装置を説明する断面図。

【図15】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【図16】本発明の一態様である光電変換装置の作製方法を説明する工程断面図。

【発明を実施するための形態】

【0023】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略することがある。

【0024】

(実施の形態1)

本実施の形態では、本発明の一態様における光電変換装置、およびその作製方法について説明する。

【0025】

図1(A)は、本発明の一態様における光電変換装置の平面図であり、図1(B)は、該平面図の線分A1−A2における断面図である。該光電変換装置は、結晶性シリコン基板100、該結晶性シリコン基板の一方の面上に形成された第1のシリコン半導体層110、第2のシリコン半導体層120、透光性導電膜150、および第1の電極170、並びに、該結晶性シリコン基板の他方の面上に形成された第3のシリコン半導体層130、第4のシリコン半導体層140、および第2の電極190を含んで構成される。なお、第1の電極170はグリッド電極であり、第1の電極170側が受光面となる。

【0026】

なお、図1(A)の平面図に示す第1の電極170の形状は一例であり、それに限らない。例えば、縦、横の各電極の一方をバスバー電極、他方をフィンガー電極として作用させるために、縦、横の各電極の幅、本数、間隔を実施者が任意に設定することができる。また、図5に示すように、第1の電極170と第2のシリコン半導体層120が重なる領域を少なくして、受光領域を拡大する構成としてもよい。

【0027】

また、図1(B)では、結晶性シリコン基板100の表裏に凹凸加工を施した例を示している。凹凸加工された面では入射光が多重反射し、光電変換領域内には光が斜めに進行することから光路長を増大させることができる。また、裏面反射光が表面で全反射する、所謂光閉じ込め効果を起こさせることもできる。なお、第1の電極170の広幅化や断線を防ぐために、第1のシリコン半導体層110が接する結晶性シリコン基板100の一領域は、凹凸加工をせずに平坦な領域としてもよい。

【0028】

結晶性シリコン基板100には一導電型を有する単結晶シリコン基板、または多結晶シリコン基板を用いることができる。本実施の形態においては、結晶性シリコン基板100にはn型の導電型を有する単結晶シリコン基板が用いられる。

【0029】

上記構造において、結晶性シリコン基板100の一方の面上に形成される第1のシリコン半導体層110および開口部を有する第2のシリコン半導体層120には、p型のシリコン半導体層を用いることができる。該p型シリコン半導体層には、例えば、ホウ素、アルミニウム、またはガリウムなどのp型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0030】

なお、第1のシリコン半導体層110には、第2のシリコン半導体層120よりもキャリア濃度が低いシリコン半導体層を用いることができる。このような構成を明瞭化するため、本明細書においては、第1のシリコン半導体層110などの相対的にキャリア濃度の低いp型半導体層の導電型をp−型と呼称するのに対し、第2のシリコン半導体層120などの相対的にキャリア濃度の高いp型半導体層の導電型をp+型と呼称する。

【0031】

なお、半導体層のキャリア濃度を調整するには、プラズマCVD法等による成膜時にドーパントガスの流量比率を変化させれば良い。原料ガス(例えば、モノシランなど)に対して、ドーパントガス(例えば、ジボラン、ホスフィンなど)の流量比率を高くするほどキャリア濃度を高くすることができる。または、成膜圧力、温度、電力密度などを変化させることにより、形成された半導体層中の不純物の活性化率を変化させてキャリア濃度を調整することもできる。

【0032】

なお、本発明の一態様におけるp−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−10S/cm〜1×10−5S/cm、好ましくは1×10−9S/cm〜1×10−6S/cm、さらに好ましくは1×10−9S/cm〜1×10−7S/cmである。

【0033】

なお、上記電気伝導度(暗伝導度)を有する非晶質シリコン半導体層は、p型の導電型を付与する不純物を故意に添加することによってp−型に制御された非晶質シリコン半導体層である。

【0034】

また、本発明の一態様におけるp+型シリコン半導体層の電気伝導度は、暗状態で1×10−5S/cmより大きいことが好ましい。

【0035】

p−n接合を用いた光電変換装置では、p−n接合内の電界を高め、拡散電位を高めることが電気特性を向上させる一つの手段となる。一般的にはキャリア濃度の高いp+型半導体またはn+型半導体を用いて接合を形成することで拡散電位を高めることができるが、p+型半導体およびn+型半導体は導電型を付与する不純物を多く含み、該不純物は局在準位を増加させてしまう。また、該局在準位によって界面準位の生成が進み、接合部近傍でキャリアの再結合が誘発されてしまう。したがって、接合層のキャリア濃度を高めるだけでは、光電変換装置の電気特性の向上は見込めない。

【0036】

一方、本発明の一態様における光電変換装置では、結晶性シリコン基板100の一方の面において、p−型シリコン半導体層と、p+型シリコン半導体層を積層した構成となっている。該p−型シリコン半導体層は、水素を含む欠陥の少ない半導体層であり、結晶性シリコン基板表面の欠陥を終端するパッシベーション層として作用すると同時に、拡散電位を形成する接合層として寄与する。また、該p+型シリコン半導体層は、さらに拡散電位を高めるように作用する。このような緩やかな接合(n−p−−p+)が形成される構造により、拡散電位を高めながらも界面準位の影響によるキャリアの再結合を極力抑えることができる。

【0037】

また、本発明の一態様である光電変換装置では、第2のシリコン半導体層120に開口部が設けられている。したがって、該開口部においては、第2のシリコン半導体層120を介さずに光電変換領域である結晶性シリコン基板へ光の照射をさせることができる。従来のヘテロ接合型光電変換装置では、界面欠陥を低減させるためのパッシベーション層と拡散電位を高めるための接合層の双方が光電変換領域の全面に積層されていたため、光吸収損失が顕著であった。一方で、本発明の一態様である光電変換装置では、該開口部において、接合層に相当する第2のシリコン半導体層120による光吸収がないため、光吸収損失を極めて少なくすることができる。この効果により、特に光電変換装置の短絡電流を向上させることができる。

【0038】

また、本発明の一態様である光電変換装置は、図2(A)に示す平面図、および図2(B)に示す該平面図の線分B1−B2における断面図の構成を有していてもよい。該光電変換装置は、図1(A)、(B)に示す光電変換装置とは第2のシリコン半導体層120の開口部を少なくした点で異なり、その他の構成は同じである。なお、第2のシリコン半導体層120の開口形状や開口面積は図示した例に限らず、自由に設定することができる。

【0039】

なお、図2(A)の平面図に示す第1の電極170の形状は一例であり、それに限らない。例えば、縦、横の各電極の一方をバスバー電極、他方をフィンガー電極として作用させるために、縦、横の各電極の幅、本数、間隔を実施者が任意に設定することができる。また、図6に示すように、第1の電極170と第2のシリコン半導体層120が重なる領域を少なくして、受光領域を拡大する構成としてもよい。

【0040】

このような構成とすることで、拡散電位をさらに高めることができ、開放電圧および曲線因子を向上させることができる。なお、図2(A)、(B)に示す光電変換装置では、一部の第2のシリコン半導体層120で光吸収が起こるため、図1(A)、(B)に示す光電変換装置よりも短絡電流は小さくなる。したがって、両者の構成の選択は、実施者が用途に応じて適宜選択すればよい。

【0041】

結晶性シリコン基板100の他方の面上に形成される第3のシリコン半導体層130および第4のシリコン半導体層140には、n型のシリコン半導体層を用いることができる。該n型半導体層には、例えば、リン、ヒ素、またはアンチモンなどのn型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0042】

なお、第3のシリコン半導体層130には、第4のシリコン半導体層140よりもキャリア濃度が低いシリコン半導体層を用いることができる。このような構成を明瞭化するため、本明細書においては、第3のシリコン半導体層130などの相対的にキャリア濃度の低いn型半導体層の導電型をn−型と呼称するのに対し、第4のシリコン半導体層140などの相対的にキャリア濃度の高いn型半導体層の導電型をn+型と呼称する。

【0043】

なお、本発明の一態様におけるn−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層は、水素を含む欠陥の少ない半導体層であり、結晶性シリコン基板100の表面欠陥を終端するパッシベーション層として作用させることができる。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−9S/cm〜1×10−4S/cm、好ましくは1×10−8S/cm〜1×10−5S/cm、さらに好ましくは1×10−8S/cm〜1×10−6S/cmである。

【0044】

なお、上記電気伝導度(暗伝導度)を有する非晶質シリコン半導体層は、n型の導電型を付与する不純物を故意に添加することによってn−型に制御された非晶質シリコン半導体層である。

【0045】

また、本発明の一態様におけるn+型シリコン半導体層の電気伝導度は、暗状態で1×10−4S/cmより大きいことが好ましい。

【0046】

また、n+型シリコン半導体層である第4のシリコン半導体層140と結晶性シリコン基板100との間には、第3のシリコン半導体層130を介してn−n+接合が形成される。つまり、第4のシリコン半導体層140は、BSF(Back Surface Field)層として作用する。該接合により形成される電界により少数キャリアがp−n接合側にはね返されることから、第2の電極190近傍でのキャリアの再結合を防止することができる。

【0047】

なお、本発明の一態様における光電変換装置においては、第3のシリコン半導体層130がi型であってもよい。本実施の形態においてi型の半導体層とは、p型もしくはn型を付与する不純物を故意に添加しない高抵抗半導体層、または、p型もしくはn型を付与する不純物を故意に添加することによって導電型が調整された高抵抗半導体層であって、上述したp−型シリコン半導体層およびn−型シリコン半導体層よりも小さい値の電気伝導度(暗伝導度)を有する実質i型の半導体層を意味する。

【0048】

透光性導電膜150には、例えば、インジウム錫酸化物、珪素を含むインジウム錫酸化物、亜鉛を含む酸化インジウム、酸化亜鉛、ガリウムを含む酸化亜鉛、アルミニウムを含む酸化亜鉛、酸化錫、フッ素を含む酸化錫、アンチモンを含む酸化錫、またはグラフェン等を用いることができる。また、透光性導電膜は単層に限らず、異なる膜の積層でも良い。

【0049】

また、第1の電極170および第2の電極190には、銀、アルミニウム、銅などの低抵抗金属を用いることができ、スパッタ法や真空蒸着法などで形成することができる。または、スクリーン印刷法やインクジェット法を用いて、銀ペーストや、銅ペーストなどの導電性樹脂で形成しても良い。

【0050】

なお、本発明の一態様における光電変換装置は、図3(A)、(B)に例示するように、表裏のどちらか一方のみに凹凸加工を施した構成であっても良い。両面が凹凸加工された光電変換装置では、光路長増大などの光学的効果が得られる一方で、結晶性シリコン基板の表面積が増大するため、表面欠陥の絶対量も増大してしまう。したがって、光学的効果と表面欠陥量のバランスを考慮し、より良好な電気特性が得られるように実施者が構造を決定すればよい。

【0051】

また、本発明の一態様における光電変換装置は、図4(A)、(B)に例示するように、第3のシリコン半導体層上に開口部を有する第4のシリコン半導体層140を形成し、該第4のシリコン半導体層上に透光性導電膜180を形成し、該透光性導電膜上にグリッド形状の第2の電極190を形成して、両面を受光面とする構造としてもよい。

【0052】

次に、図1(A)、(B)に示した光電変換装置の作製方法について、図7および図8を用いて説明する。

【0053】

本発明の一態様に用いることのできる結晶性シリコン基板100には、n型の導電型を有する単結晶シリコン基板や多結晶シリコン基板を用いることができる。これらの結晶性シリコン基板の製造方法は、特に限定されない。本実施の形態においては、結晶性シリコン基板100にMCZ(Magnetic Czochralski)法で製造された(100)面を表面に有する単結晶シリコン基板を用いる。

【0054】

次に、結晶性シリコン基板100の表裏に凹凸加工を行う(図7(A)参照)。なお、ここでは上述したように(100)面を表面に有する単結晶シリコン基板を用いる場合を例として凹凸加工の方法の一例を説明する。結晶性シリコン基板100として多結晶シリコン基板を用いる場合は、ドライエッチング法などを用いて凹凸加工を行えばよい。

【0055】

初期の単結晶シリコン基板がスライス加工のみである基板の場合は、単結晶シリコン基板の表面から10〜20μmに残留するダメージ層をウエットエッチング工程にて取り除く。エッチング液には、比較的高濃度のアルカリ溶液、例えば、10〜50%の水酸化ナトリウム水溶液、または同濃度の水酸化カリウム水溶液を用いることができる。または、フッ酸と硝酸を混合した混酸や、それらに酢酸を混合した混酸を用いても良い。

【0056】

次に、ダメージ層除去後の単結晶シリコン基板表面に付着している不純物を酸洗浄で取り除く。酸としては、例えば、0.5%フッ酸と1%過酸化水素水の混合液(FPM)などを用いることができる。またはRCA洗浄などを行っても良い。なお、この酸洗浄工程は省いても良い。

【0057】

凹凸は、結晶シリコンのアルカリ溶液によるエッチングにおいて、面方位に対するエッチングレートの違いを利用して形成する。エッチング液には比較的低濃度のアルカリ溶液、例えば、1〜5%の水酸化ナトリウム水溶液、または同濃度の水酸化カリウム水溶液を用いることができ、好ましくは、数%のイソプロピルアルコールを添加する。エッチング液の温度は70〜90℃とし、30〜60分間、単結晶シリコン基板をエッチング液に浸漬する。この処理により、単結晶シリコン基板表面に、微細な略四角錐状の複数の凸部、および隣接する凸部間で構成される凹部からなる凹凸を形成することができる。

【0058】

次に、上述の凹凸を形成するためのエッチング工程では、シリコンの表層に不均一な酸化層が形成されるため、該酸化層を取り除く。また、該酸化層にはアルカリ溶液の成分が残存しやすいため、それを取り除く目的もある。アルカリ金属、例えばNaイオンやKイオンがシリコン中に侵入するとライフタイムが劣化するため、光電変換装置の電気特性が著しく低下してしまう。なお、この酸化層を除去するには、1〜5%の希フッ酸を用いれば良い。

【0059】

次に、フッ酸と硝酸を混合した混酸、または、それらに酢酸を混合した混酸を用いて単結晶シリコン基板の表面をエッチングし、金属成分などの不純物を除去することが好ましい。酢酸を混合することで、硝酸の酸化力を維持し、エッチング工程を安定にする効果、およびエッチングレートを調整する効果が得られる。例えば、各酸の体積比率は、フッ酸:硝酸:酢酸=1:(1.5〜3):(2〜4)とすることができる。なお、本明細書では、フッ酸、硝酸および酢酸の混酸液をフッ硝酢酸と呼ぶ。また、このフッ硝酢酸を用いたエッチング工程では、凸部の頂点の断面における角度を大きくする方向に変化させることから、表面積が低減し、表面欠陥の絶対量を低減することができる。なお、このフッ硝酢酸を用いたエッチングを行う場合は、上述の希フッ酸を用いた酸化層の除去工程を省くこともできる。ここまでの工程により、結晶性シリコン基板100である単結晶シリコン基板の表面に凹凸を形成することができる。

【0060】

なお、図3(A)、(B)に示すような、結晶性シリコン基板100の片面のみに凹凸加工を行うには、上記凹凸加工工程を行う前に、結晶性シリコン基板100の一方の面にアルカリ耐性および酸耐性の強い樹脂膜などを設け、上記凹凸加工工程後に該樹脂膜を取り除けばよい。

【0061】

次いで、水洗などの適切な洗浄の後、受光面とは逆側となる結晶性シリコン基板100の面上にプラズマCVD法を用いて第3のシリコン半導体層130を形成する。第3のシリコン半導体層130の厚さは、3nm以上50nm以下とすることが好ましい。本実施の形態において、第3のシリコン半導体層130はn−型の非晶質シリコンであり、膜厚は5nmとする。

【0062】

第3のシリコン半導体層130の成膜条件としては、例えば、反応室にモノシラン:水素ベースのホスフィン(0.5%)=1:(0.3〜1未満)となる流量比率で原料ガスを導入し、反応室内の圧力を100Pa以上200Pa以下、電極間隔を10mm以上40mm以下、カソード電極の面積を基準とする電力密度を8mW/cm2以上120mW/cm2以下、基板温度を150℃以上300℃以下とすればよい。

【0063】

次に、第3のシリコン半導体層130上に第4のシリコン半導体層140を形成する(図3(B)参照)。第4のシリコン半導体層140の厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、第4のシリコン半導体層140はn+型の非晶質シリコンであり、膜厚は10nmとする。

【0064】

第4のシリコン半導体層140の成膜条件は、例えば、反応室にモノシラン:水素ベースのホスフィン(0.5%)=1:(1〜15)となる流量比率で原料ガスを導入し、反応室内の圧力を100Pa以上200Pa以下とし、電極間隔を10mm以上40mm以下とし、カソード電極の面積を基準とする電力密度を8mW/cm2以上120mW/cm2以下、基板温度を150℃以上300℃以下とすればよい。

【0065】

次に、受光面側となる結晶性シリコン基板100の面上にプラズマCVD法を用いて第1のシリコン半導体層110を形成する(図7(B)参照)。第1のシリコン半導体層110の厚さは、3nm以上50nm以下とすることが好ましく、本実施の形態において、第1のシリコン半導体層110はp−型の非晶質シリコンであり、膜厚は5nmとする。

【0066】

第1のシリコン半導体層110の成膜条件としては、例えば、反応室にモノシラン:水素ベースのジボラン(0.1%)=1:(0.01〜1未満)となる流量比率で原料ガスを導入し、反応室内の圧力を100Pa以上200Pa以下、電極間隔を10mm以上40mm以下、カソード電極の面積を基準とする電力密度を8mW/cm2以上120mW/cm2以下、基板温度を150℃以上300℃以下とすればよい。

【0067】

次に、第1のシリコン半導体層110上に開口部を有するマスク200を形成する。第2のシリコン半導体層120は該マスクを利用して、リフトオフ法により形成する。該マスクには、フォトレジストや酸化シリコンなどの無機材料で形成することが好ましい。本実施の形態では、スパッタ法などの成膜方法を用いて酸化シリコン層を形成し、フォトリソグラフィ法、エッチング法などの公知の方法を用いて、マスク200を形成する(図7(C)参照)。

【0068】

次に、マスク200および第1のシリコン半導体層110上にp型の導電型を有するシリコン半導体膜120aを形成する(図8(A)参照)。シリコン半導体膜120aの厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、シリコン半導体膜120aはp+型の非晶質シリコンであり、膜厚は10nmとする。

【0069】

シリコン半導体膜120aの成膜条件は、例えば、反応室にモノシラン:水素ベースのジボラン(0.1%)=1:(1〜20)となる流量比率で原料ガスを導入し、反応室内の圧力を100Pa以上200Pa以下とし、電極間隔を8mm以上40mm以下とし、カソード電極の面積を基準とする電力密度を8mW/cm2以上50mW/cm2以下、基板温度を150℃以上300℃以下とすればよい。

【0070】

次に、希フッ酸、またはフッ酸とフッ化アンモニウムの混合液であるバッファードフッ酸を用いて、マスク200および余分なシリコン半導体膜120aを同時に除去して、第2のシリコン半導体層120を形成する(図8(B)参照)。

【0071】

なお、本実施の形態において、第1のシリコン半導体層110、第2のシリコン半導体層120、第3のシリコン半導体層130、および第4のシリコン半導体層140の成膜に用いる電源には周波数13.56MHzのRF電源を用いるが、27.12MHz、60MHz、または100MHzのRF電源を用いても良い。また、連続放電だけでなく、パルス放電にて成膜を行っても良い。パルス放電を行うことで、膜質の向上や気相中で発生するパーティクルを低減することができる。

【0072】

また、結晶性シリコン基板100の表裏に設ける膜の形成順序は、上記の方法に限らず、図8(B)に示した構造が形成できればよい。例えば、第3のシリコン半導体層130を形成し、その次に第1のシリコン半導体層110を形成してもよい。

【0073】

次に、第2のシリコン半導体層120上に透光性導電膜150を形成する。該透光性導電膜は、前述の材料を例えばスパッタ法などを用いて成膜することができる。膜厚は10nm以上1000nm以下とすることが好ましい。

【0074】

次に、第4のシリコン半導体層140上に第2の電極190を形成する。第2の電極190には、銀、アルミニウム、銅などの低抵抗金属を用いることができ、スパッタ法や真空蒸着法などで形成することができる。または、スクリーン印刷法やインクジェット法を用いて、銀ペーストや、銅ペーストなどの導電性樹脂で形成しても良い。

【0075】

次に、透光性導電膜150上に、第2のシリコン半導体層120と重なるように第1の電極170を形成する(図8(C)参照)。第1の電極170はグリッド電極であり、銀ペースト、銅ペースト、ニッケルペースト、モリブデンペーストなどの導電性樹脂を用いて、スクリーン印刷法やインクジェット法で形成することが好ましい。また、第1の電極170は、銀ペーストと銅ペーストを積層するなど、異なる材料の積層であっても良い。

【0076】

なお、図2(A)、(B)に示した光電変換装置を作製するには、第1の電極170と第2のシリコン半導体層120の一部とが重なるように、それぞれの形状を異ならせて形成すればよい。

【0077】

また、図4(A)、(B)の構成の光電変換装置を形成するには、第3のシリコン半導体層130を形成した後に、図7(C)〜図8(C)に示す第2のシリコン半導体層120、透光性導電膜150、第1の電極170の形成方法に従って、第4のシリコン半導体層140、透光性導電膜180、第2の電極190を形成すればよい。

【0078】

以上により、本発明の一態様である光吸収損失および抵抗損失の少ない光電変換装置を作製することができる。

【0079】

本実施の形態は、他の実施の形態と自由に組み合わすことができる。

【0080】

(実施の形態2)

本実施の形態では、実施の形態1で示した光電変換装置とは異なる構成の光電変換装置について説明する。なお、実施の形態1と共通する点については、本実施の形態ではその詳細な説明は省略する。

【0081】

図9は、本発明の一態様における光電変換装置の断面図である。該光電変換装置は、表面が凹凸加工された結晶性シリコン基板300、該結晶性シリコン基板の一方の面上に形成された第1のシリコン半導体層310、該第1のシリコン半導体層上に形成された開口部を有する第1の透光性導電膜410、該開口部に形成された第2のシリコン半導体層320、該第2のシリコン半導体層上に形成された第1の電極370、および該結晶性シリコン基板の一方の面上に形成された上記積層膜を覆う第2の透光性導電膜420を含む。また、該光電変換装置は、該結晶性シリコン基板の他方の面上に形成された第3のシリコン半導体層330、該第3のシリコン半導体層に形成された第4のシリコン半導体層340、該第4のシリコン半導体層上に形成された第2の電極390を含む。なお、第1の電極370はグリッド電極であり、第1の電極370側が受光面となる。

【0082】

また、図10(A)に示すように、表裏のどちらか一方のみに凹凸加工を施した構成であっても良い。なお、第1の電極370の広幅化や断線を防ぐために、第1のシリコン半導体層310が接する結晶性シリコン基板300の一領域は、凹凸加工をせずに平坦な領域としてもよい。

【0083】

また、図10(B)に示すように、第3のシリコン半導体層330上に開口部を有する第3の透光性導電膜430を形成し、該開口部に第4のシリコン半導体層340を形成し、該第4のシリコン半導体層上に第2の電極390を形成し、該結晶性シリコン基板の他方の面上に形成された上記積層膜を覆う第4の透光性導電膜440を形成して、両面を受光面とする構造としてもよい。

【0084】

上記構造において、結晶性シリコン基板300の一方の面上に形成される第1のシリコン半導体層310および第2のシリコン半導体層320には、p型のシリコン半導体層を用いることができる。該p型半導体層には、例えば、ホウ素、アルミニウム、またはガリウムなどのp型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0085】

なお、第1のシリコン半導体層310には、第2のシリコン半導体層320よりもキャリア濃度が低いシリコン半導体層を用いることができる。すなわち、第1のシリコン半導体層310にはp−型、第2のシリコン半導体層320にはp+型の導電型を有するシリコン半導体層を用いることができる。

【0086】

なお、本発明の一態様におけるp−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−10S/cm〜1×10−5S/cm、好ましくは1×10−9S/cm〜1×10−6S/cm、さらに好ましくは1×10−9S/cm〜1×10−7S/cmである。

【0087】

また、本発明の一態様におけるp+型シリコン半導体層の電気伝導度は、暗状態で1×10−5S/cmより大きいことが好ましい。

【0088】

また、結晶性シリコン基板100の他方の面上に形成される第3のシリコン半導体層330および第4のシリコン半導体層340には、n型のシリコン半導体層を用いることができる。該n型シリコン半導体層には、例えば、リン、ヒ素、またはアンチモンなどのn型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0089】

なお、第3のシリコン半導体層330には、第4のシリコン半導体層340よりもキャリア濃度が低いシリコン半導体層を用いることができる。すなわち、第3のシリコン半導体層330にはn−型、第4のシリコン半導体層340にはn+型の導電型を有するシリコン半導体層を用いることができる。

【0090】

なお、本発明の一態様におけるn−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−9S/cm〜1×10−4S/cm、好ましくは1×10−9S/cm〜1×10−5S/cm、さらに好ましくは1×10−9S/cm〜1×10−6S/cmである。

【0091】

また、本発明の一態様におけるn+型シリコン半導体層の電気伝導度は、暗状態で1×10−4S/cmより大きいことが好ましい。

【0092】

第1乃至第4の透光性導電膜410、420、430、440には、例えば、インジウム錫酸化物、珪素を含むインジウム錫酸化物、亜鉛を含む酸化インジウム、酸化亜鉛、ガリウムを含む酸化亜鉛、アルミニウムを含む酸化亜鉛、酸化錫、フッ素を含む酸化錫、アンチモンを含む酸化錫、またはグラフェン等を用いることができる。また、透光性導電膜は単層に限らず、異なる膜の積層でも良い。

【0093】

また、第1の電極370および第2の電極390には、銀、アルミニウム、銅などの低抵抗金属を用いることができ、スパッタ法や真空蒸着法などで形成することができる。または、スクリーン印刷法やインクジェット法を用いて、銀ペーストや、銅ペーストなどの導電性樹脂で形成しても良い。

【0094】

以上の構成を有する本実施の形態における光電変換装置は、実施の形態1で説明した光電変換装置と同様に緩やかな接合(n−p−−p+)が形成される構造であり、拡散電位を高めながらも界面準位の影響によるキャリアの再結合を極力抑えることができる。したがって、特に開放電圧、および曲線因子を向上させることができる。

【0095】

また、本実施の形態における光電変換装置では、第2のシリコン半導体層320に開口部が形成されており、該開口部においては、第2のシリコン半導体層320による光吸収がないため、光吸収損失を極めて少なくすることができる。

【0096】

次に、図9に示した光電変換装置の作製方法について、図11および図12を用いて説明する。

【0097】

本発明の一態様に用いることのできる結晶性シリコン基板300には、n型の導電型を有する単結晶シリコン基板や多結晶シリコン基板を用いることができる。

【0098】

次に、実施の形態1の図7(A)を説明する方法に従って、結晶性シリコン基板300の表裏に凹凸加工を行う(図11(A)参照)。

【0099】

次に、受光面とは逆側となる結晶性シリコン基板300の面上にプラズマCVD法を用いて第3のシリコン半導体層330を形成する。第3のシリコン半導体層330の厚さは、3nm以上50nm以下とすることが好ましい。本実施の形態において、第3のシリコン半導体層330はn−型の非晶質シリコンであり、膜厚は5nmとする。

【0100】

第3のシリコン半導体層330の成膜条件としては、実施の形態1で説明した第3のシリコン半導体層130の成膜条件を参照することができる。

【0101】

次に、第3のシリコン半導体層330上に第4のシリコン半導体層340を形成する。第4のシリコン半導体層340の厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、第4のシリコン半導体層340はn+型の非晶質シリコンであり、膜厚は10nmとする。

【0102】

第4のシリコン半導体層340の成膜条件としては、実施の形態1で説明した第4のシリコン半導体層140の成膜条件を参照することができる。

【0103】

次に、受光面側となる結晶性シリコン基板100の面上にプラズマCVD法を用いて第1のシリコン半導体層310を形成する(図11(B)参照)。第1のシリコン半導体層310の厚さは、3nm以上50nm以下とすることが好ましく、本実施の形態において、第1のシリコン半導体層310はp−型の非晶質シリコンであり、膜厚は5nmとする。

【0104】

第1のシリコン半導体層310の成膜条件としては、実施の形態1で説明した第1のシリコン半導体層110の成膜条件を参照することができる。

【0105】

次に、第1のシリコン半導体層310上に開口部を有する第1の透光性導電膜410を形成する(図11(C)参照)。該透光性導電膜の開口部は、成膜後にフォトリソグラフィ法、エッチング法などの公知の方法を用いて形成するほか、メタルマスクを用いた成膜、またはリフトオフ法などを用いてもよい。なお、該透光性導電膜の成膜はスパッタ法を用いることが好ましい。

【0106】

次に、第1のシリコン半導体層310および第1の透光性導電膜410上にp型の導電型を有するシリコン半導体膜320aを形成する(図12(A)参照)。シリコン半導体膜320aの厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、シリコン半導体膜320aはp+型の非晶質シリコンであり、膜厚は10nmとする。

【0107】

シリコン半導体膜320aの成膜条件は、実施の形態1で説明したシリコン半導体膜120aの成膜条件を参照することができる。

【0108】

なお、結晶性シリコン基板300の表裏に設ける膜の形成順序は、上記の方法に限らず、図12(A)に示した構造が形成できればよい。例えば、第3のシリコン半導体層330を形成し、その次に第1のシリコン半導体層310を形成してもよい。

【0109】

次に、シリコン半導体膜320a上に第1の電極370を形成する。このとき、第1の電極370は、第1の透光性導電膜410に形成された開口部の形状に合わせて形成することが好ましい。第1の電極370の形成方法は、実施の形態1の第1の電極170の形成方法を参照することができる。

【0110】

そして、第1の電極370をマスクにして、余分なシリコン半導体膜320aを公知の方法で取り除き、第2のシリコン半導体層320を形成する(図12(B)参照)。

【0111】

次に、第4のシリコン半導体層340上に第2の電極390を形成する。第2の電極390の形成方法は、実施の形態1で説明した第2の電極190の形成方法を参照することができる。

【0112】

次に、第1の透光性導電膜410上に形成された上記積層を覆うように第2の透光性導電膜420を形成する(図12(C)参照)。第2の透光性導電膜420は、スパッタ法等で形成すればよい。

【0113】

以上により、本発明の一態様である光吸収損失および抵抗損失の少ない光電変換装置を作製することができる。

【0114】

本実施の形態は、他の実施の形態と自由に組み合わすことができる。

【0115】

(実施の形態3)

本実施の形態では、実施の形態1および2で示した光電変換装置とは異なる構成の光電変換装置について説明する。なお、実施の形態1と共通する点については、本実施の形態ではその詳細な説明は省略する。

【0116】

図13は、本発明の一態様における光電変換装置の断面図である。該光電変換装置は、表面が凹凸加工された結晶性シリコン基板500、該結晶性シリコン基板の一方の面上に形成された第1のシリコン半導体層510、該第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層520、該第2のシリコン半導体層上に形成された第1の電極570、および該結晶性シリコン基板の一方の面上に形成された上記積層膜を覆う透光性薄膜610を含む。また、該光電変換装置は、該結晶性シリコン基板の他方の面上に形成された第3のシリコン半導体層530、該第3のシリコン半導体層に形成された第4のシリコン半導体層540、該第4のシリコン半導体層上に形成された第2の電極590を含む。なお、第1の電極570はグリッド電極であり、第1の電極570側が受光面となる。

【0117】

また、図14(A)に示すように、表裏のどちらか一方のみに凹凸加工を施した構成であっても良い。なお、第1の電極570の広幅化や断線を防ぐために、第1のシリコン半導体層510が接する結晶性シリコン基板500の一領域は、凹凸加工をせずに平坦な領域としてもよい。

【0118】

また、図14(B)に示すように、第3のシリコン半導体層530上に開口部を有する第4のシリコン半導体層540を形成し、該第4のシリコン半導体層上に第2の電極590を形成し、該結晶性シリコン基板の他方の面上に形成された上記積層膜を覆う透光性薄膜630を形成して、両面を受光面とする構造としてもよい。

【0119】

上記構造において、結晶性シリコン基板500の一方の面上に形成される第1のシリコン半導体層510および第2のシリコン半導体層520には、p型のシリコン半導体層を用いることができる。該p型半導体層には、例えば、ホウ素、アルミニウム、またはガリウムなどのp型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0120】

なお、第1のシリコン半導体層510には、第2のシリコン半導体層520よりもキャリア濃度が低いシリコン半導体層を用いることができる。すなわち、第1のシリコン半導体層510にはp−型、第2のシリコン半導体層520にはp+型の導電型を有するシリコン半導体層を用いることができる。

【0121】

なお、本発明の一態様におけるp−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−10S/cm〜1×10−5S/cm、好ましくは1×10−9S/cm〜1×10−6S/cm、さらに好ましくは1×10−9S/cm〜1×10−7S/cmである。

【0122】

また、本発明の一態様におけるp+型シリコン半導体層の電気伝導度は、暗状態で1×10−5S/cmより大きいことが好ましい。

【0123】

また、結晶性シリコン基板500の他方の面上に形成される第3のシリコン半導体層530および第4のシリコン半導体層540には、n型のシリコン半導体層を用いることができる。該n型シリコン半導体層には、例えば、リン、ヒ素、またはアンチモンなどのn型の導電型を付与する不純物、および水素を含むシリコン半導体層を用いることができる。

【0124】

なお、第3のシリコン半導体層530には、第4のシリコン半導体層540よりもキャリア濃度が低いシリコン半導体層を用いることができる。すなわち、第3のシリコン半導体層530にはn−型、第4のシリコン半導体層540にはn+型の導電型を有するシリコン半導体層を用いることができる。

【0125】

なお、本発明の一態様におけるn−型シリコン半導体層には、不純物による局在準位の少ない非晶質シリコン半導体層を用いることが好ましい。該非晶質シリコン半導体層の電気伝導度は、暗状態で1×10−9S/cm〜1×10−4S/cm、好ましくは1×10−9S/cm〜1×10−5S/cm、さらに好ましくは1×10−9S/cm〜1×10−6S/cmである。

【0126】

また、本発明の一態様におけるn+型シリコン半導体層の電気伝導度は、暗状態で1×10−4S/cmより大きいことが好ましい。

【0127】

透光性薄膜610には、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン(SiNxOy(x>y>0))膜、酸化窒化シリコン(SiOxNy(x>y>0))膜、酸化アルミニウム膜などの絶縁膜を用いることができる。透光性薄膜610を設けることで、第1のシリコン半導体層510の表面近傍における少数キャリアの再結合を低減させることができる。また、透光性薄膜610は反射防止膜としても作用する。なお、第1の電極570が配線などに接続される部位においては、透光性薄膜610は取り除かれている構成とする。

【0128】

第1の電極570および第2の電極590には、銀ペーストや、銅ペーストなどの導電性樹脂を用いることができ、スクリーン印刷法やインクジェット法などで形成することができる。また、銀、アルミニウム、銅などの低抵抗金属をスパッタ法や真空蒸着法などで形成してもよい。

【0129】

ここで、第1の電極570の幅は、好ましくは100μm以下、さらに好ましくは50μm以下とする。また、第1の電極570が形成される間隔は、500μm以下、好ましくは100μm以下、さらに好ましくは50μm以下とする。このように第1の電極570の線幅を細く、間隔を短くすることで光キャリアの損失を抑えることができる。つまり、実施の形態1または2で説明した光電変換装置と異なり、透光性導電膜を不要にすることができる。なお、図14における第2の電極590も同様である。

【0130】

以上の構成を有する本実施の形態における光電変換装置は、実施の形態1または2で説明した光電変換装置と同様に緩やかな接合(n−p−−p+)が形成される構造であり、拡散電位を高めながらも界面準位の影響によるキャリアの再結合を極力抑えることができる。したがって、特に開放電圧、および曲線因子を向上させることができる。

【0131】

また、本実施の形態における光電変換装置では、第2のシリコン半導体層520に開口部が形成されており、該開口部においては、第2のシリコン半導体層520による光吸収がないため、光吸収損失を極めて少なくすることができる。また、透光性導電膜が形成されていないため、該透光性導電膜による光吸収損失の影響も排除することができる。

【0132】

次に、図13に示した光電変換装置の作製方法について、図15および図16を用いて説明する。

【0133】

本発明の一態様に用いることのできる結晶性シリコン基板500には、n型の導電型を有する単結晶シリコン基板や多結晶シリコン基板を用いることができる。

【0134】

次に、実施の形態1の図7(A)を説明する方法に従って、結晶性シリコン基板300の表裏に凹凸加工を行う(図15(A)参照)。

【0135】

次に、受光面とは逆側となる結晶性シリコン基板500の面上にプラズマCVD法を用いて第3のシリコン半導体層530を形成する。第3のシリコン半導体層530の厚さは、3nm以上50nm以下とすることが好ましい。本実施の形態において、第3のシリコン半導体層530はn−型の非晶質シリコンであり、膜厚は5nmとする。

【0136】

第3のシリコン半導体層530の成膜条件としては、実施の形態1で説明した第3のシリコン半導体層130の成膜条件を参照することができる。

【0137】

次に、第3のシリコン半導体層530上に第4のシリコン半導体層540を形成する。第4のシリコン半導体層540の厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、第4のシリコン半導体層540はn+型の非晶質シリコンであり、膜厚は10nmとする。

【0138】

第4のシリコン半導体層540の成膜条件としては、実施の形態1で説明した第4のシリコン半導体層140の成膜条件を参照することができる。

【0139】

次に、受光面側となる結晶性シリコン基板100の面上にプラズマCVD法を用いて第1のシリコン半導体層510を形成する(図15(B)参照)。第1のシリコン半導体層510の厚さは、3nm以上50nm以下とすることが好ましく、本実施の形態において、第1のシリコン半導体層510はp−型の非晶質シリコンであり、膜厚は5nmとする。

【0140】

第1のシリコン半導体層510の成膜条件としては、実施の形態1で説明した第1のシリコン半導体層110の成膜条件を参照することができる。

【0141】

次に、第1のシリコン半導体層510上に開口部を有するマスク600を形成する。第2のシリコン半導体層520は該マスクを利用して、リフトオフ法により形成する。該マスクには、フォトレジストや酸化シリコンなどの無機材料で形成することが好ましい。本実施の形態では、スパッタ法などの成膜方法を用いて酸化シリコン層を形成し、フォトリソグラフィ法、エッチング法などの方法を用いて、マスク600を形成する(図15(C)参照)。

【0142】

次に、マスク600および第1のシリコン半導体層510上にp型の導電型を有するシリコン半導体膜520aを形成する。シリコン半導体膜520aの厚さは3nm以上50nm以下とすることが好ましい。本実施の形態において、シリコン半導体膜520aはp+型の非晶質シリコンであり、膜厚は10nmとする。

【0143】

次に、マスク600の開口部にシリコン半導体膜520a上に導電層570aを形成する(図16(A)参照)。該導電層には、銀ペーストや、銅ペーストなどの導電性樹脂を用いることができ、スクリーン印刷法やインクジェット法などで形成することができる。また、銀、アルミニウム、銅などの低抵抗金属をスパッタ法や真空蒸着法などで形成してもよい。

【0144】

次に、希フッ酸、またはフッ酸とフッ化アンモニウムの混合液であるバッファードフッ酸を用いて、マスク600および余分なシリコン半導体膜520aを同時に除去して、第2のシリコン半導体層520を形成する(図16(B)参照)。

【0145】

次に、第1のシリコン半導体層510、第2のシリコン半導体層520、および第1の電極570を覆うように透光性薄膜610を形成する。該透光性薄膜としては、プラズマCVD法やスパッタ法で成膜される50nm以上100nm以下の膜厚の酸化シリコン膜や窒化シリコン膜を用いることができる。本実施の形態では、50nmの窒化シリコン膜を透光性薄膜610として用いる。

【0146】

次に、第4のシリコン半導体層540上に第2の電極590を形成する。第2の電極590の形成方法は、実施の形態1で説明した第2の電極190の形成方法を参照することができる。

【0147】

以上により、本発明の一態様である光吸収損失および抵抗損失の少ない光電変換装置を作製することができる。

【0148】

本実施の形態は、他の実施の形態と自由に組み合わすことができる。

【符号の説明】

【0149】

100 結晶性シリコン基板

110 第1のシリコン半導体層

120 第2のシリコン半導体層

120a シリコン半導体膜

130 第3のシリコン半導体層

140 第4のシリコン半導体層

150 透光性導電膜

170 第1の電極

180 透光性導電膜

190 第2の電極

200 マスク

300 結晶性シリコン基板

310 第1のシリコン半導体層

320 第2のシリコン半導体層

320a シリコン半導体膜

330 第3のシリコン半導体層

340 第4のシリコン半導体層

370 第1の電極

390 第2の電極

410 第1の透光性導電膜

420 第2の透光性導電膜

430 第3の透光性導電膜

440 第4の透光性導電膜

500 結晶性シリコン基板

510 第1のシリコン半導体層

520 第2のシリコン半導体層

520a シリコン半導体膜

530 第3のシリコン半導体層

540 第4のシリコン半導体層

570 第1の電極

570a 導電層

590 第2の電極

600 マスク

610 透光性薄膜

630 透光性薄膜

【特許請求の範囲】

【請求項1】

結晶性シリコン基板と、

前記結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、

前記第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層と、

前記第1のシリコン半導体層および前記第2のシリコン半導体層上に形成された透光性導電膜と、

前記透光性導電膜上に形成された、前記第2のシリコン半導体層と重なる第1の電極と、

前記結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、

前記第3のシリコン半導体層上に形成された第4のシリコン半導体層と、

前記第4のシリコン半導体層上に形成された第2の電極と、

を有することを特徴とする光電変換装置。

【請求項2】

請求項1において、前記第4のシリコン半導体層に開口部が形成され、前記第3のシリコン半導体層および前記第4のシリコン半導体層上に透光性導電膜が形成されていることを特徴とする光電変換装置。

【請求項3】

請求項1または2において、前記第1の電極は、前記第2のシリコン半導体層の一部と重なって形成されていることを特徴とする光電変換装置。

【請求項4】

結晶性シリコン基板と、

前記結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、

前記第1のシリコン半導体層上に形成された開口部を有する第1の透光性導電膜と、

前記開口部に形成された、前記第1のシリコン半導体層と接する第2のシリコン半導体層と、

前記第2のシリコン半導体層上に形成された第1の電極と、

前記第1の透光性導電膜、前記第2のシリコン半導体層および前記第1の電極をを覆う第2の透光性導電膜と、

前記結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、

前記第3のシリコン半導体層上に形成された第4のシリコン半導体層と、

前記第4のシリコン半導体層上に形成された第2の電極と、

を有することを特徴とする光電変換装置。

【請求項5】

結晶性シリコン基板と、

前記結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、

前記第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層と、

前記第2のシリコン半導体層上と重なる第1の電極と、

前記第1のシリコン半導体層、前記第2のシリコン半導体層および前記第1の電極を覆う透光性薄膜と、

前記結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、

前記第3のシリコン半導体層上に形成された第4のシリコン半導体層と、

前記第4のシリコン半導体層上に形成された第2の電極と、

を有することを特徴とする光電変換装置。

【請求項6】

請求項1乃至5のいずれか一項において、前記結晶性シリコン基板の導電型はn型であり、前記第1のシリコン半導体層および前記第2のシリコン半導体層の導電型はp型であり、前記第3のシリコン半導体層の導電型はi型またはn型であり、前記第4のシリコン半導体層の導電型はn型であることを特徴とする光電変換装置。

【請求項7】

請求項1乃至6のいずれか一項において、前記第2のシリコン半導体層のキャリア濃度は、前記第1のシリコン半導体層のキャリア濃度よりも高く、前記第4のシリコン半導体層のキャリア濃度は、前記第3のシリコン半導体層のキャリア濃度よりも高いことを特徴とする光電変換装置。

【請求項1】

結晶性シリコン基板と、

前記結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、

前記第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層と、

前記第1のシリコン半導体層および前記第2のシリコン半導体層上に形成された透光性導電膜と、

前記透光性導電膜上に形成された、前記第2のシリコン半導体層と重なる第1の電極と、

前記結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、

前記第3のシリコン半導体層上に形成された第4のシリコン半導体層と、

前記第4のシリコン半導体層上に形成された第2の電極と、

を有することを特徴とする光電変換装置。

【請求項2】

請求項1において、前記第4のシリコン半導体層に開口部が形成され、前記第3のシリコン半導体層および前記第4のシリコン半導体層上に透光性導電膜が形成されていることを特徴とする光電変換装置。

【請求項3】

請求項1または2において、前記第1の電極は、前記第2のシリコン半導体層の一部と重なって形成されていることを特徴とする光電変換装置。

【請求項4】

結晶性シリコン基板と、

前記結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、

前記第1のシリコン半導体層上に形成された開口部を有する第1の透光性導電膜と、

前記開口部に形成された、前記第1のシリコン半導体層と接する第2のシリコン半導体層と、

前記第2のシリコン半導体層上に形成された第1の電極と、

前記第1の透光性導電膜、前記第2のシリコン半導体層および前記第1の電極をを覆う第2の透光性導電膜と、

前記結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、

前記第3のシリコン半導体層上に形成された第4のシリコン半導体層と、

前記第4のシリコン半導体層上に形成された第2の電極と、

を有することを特徴とする光電変換装置。

【請求項5】

結晶性シリコン基板と、

前記結晶性シリコン基板の一方の面に形成された第1のシリコン半導体層と、

前記第1のシリコン半導体層上に形成された開口部を有する第2のシリコン半導体層と、

前記第2のシリコン半導体層上と重なる第1の電極と、

前記第1のシリコン半導体層、前記第2のシリコン半導体層および前記第1の電極を覆う透光性薄膜と、

前記結晶性シリコン基板の他方の面に形成された第3のシリコン半導体層と、

前記第3のシリコン半導体層上に形成された第4のシリコン半導体層と、

前記第4のシリコン半導体層上に形成された第2の電極と、

を有することを特徴とする光電変換装置。

【請求項6】

請求項1乃至5のいずれか一項において、前記結晶性シリコン基板の導電型はn型であり、前記第1のシリコン半導体層および前記第2のシリコン半導体層の導電型はp型であり、前記第3のシリコン半導体層の導電型はi型またはn型であり、前記第4のシリコン半導体層の導電型はn型であることを特徴とする光電変換装置。

【請求項7】

請求項1乃至6のいずれか一項において、前記第2のシリコン半導体層のキャリア濃度は、前記第1のシリコン半導体層のキャリア濃度よりも高く、前記第4のシリコン半導体層のキャリア濃度は、前記第3のシリコン半導体層のキャリア濃度よりも高いことを特徴とする光電変換装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2013−93543(P2013−93543A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2012−107481(P2012−107481)

【出願日】平成24年5月9日(2012.5.9)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成24年5月9日(2012.5.9)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]