全デジタル位相ロックループ

【課題】周波数差の変化を正しくDCOに伝達し、且つグリッチノイズを低減する。

【解決手段】一つの実施形態の全デジタル位相ロックループ90には、デジタル周波数比較器1、グリッチ発生期間検出回路2、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6が設けられる。デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。グリッチ発生期間検出回路2は、小数部周波数差生成回路12から出力されるTDC出力信号Stdcoが入力され、グリッチ発生期間信号Sgctimを生成する。グリッチ補正回路3は、加算器13から出力される周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、グリッチ発生期間信号Sgctimがイネーブル状態のときに周波数差信号Sfdifに含まれるグリッチノイズを低減処理する。

【解決手段】一つの実施形態の全デジタル位相ロックループ90には、デジタル周波数比較器1、グリッチ発生期間検出回路2、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6が設けられる。デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。グリッチ発生期間検出回路2は、小数部周波数差生成回路12から出力されるTDC出力信号Stdcoが入力され、グリッチ発生期間信号Sgctimを生成する。グリッチ補正回路3は、加算器13から出力される周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、グリッチ発生期間信号Sgctimがイネーブル状態のときに周波数差信号Sfdifに含まれるグリッチノイズを低減処理する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、全デジタル位相ロックループに関する。

【背景技術】

【0002】

無線通信に使用される周波数シンセサイザ、マイクロプロセッサに使用される高速クロック生成回路、FM復調器、CDR(Clock Data Recovery)などには位相ロックループ(Phase Locked Loop PLL)が多用される。位相ロックループは、アナログ回路やアナログ・デジタル回路で実現されている。近年、CMOS技術の微細化、高集積度化、低消費電流化の進展に伴い、すべてデジタル回路で構成される全デジタル位相ロックループ(All Digital Phase Locked Loop ADPLL)が種々の機関で開発されている。全デジタル位相ロックループは、アナログフィルタやチャージ・ポンプ回路が不要なので、低電圧動作、低位相雑音、高速整定が可能となる(例えば、特許文献1参照。)。

【0003】

全デジタル位相ロックループは、トレース間の容量性結合、電源リップル、複数のデバイスによる瞬時高電流などが起因となるグリッチノイズが発生する可能性がある。また、論理回路でクロック信号とデータ信号の立ち上がり或いは立ち下がりが重なった場合に発生するメタスタビリティなどによってもグリッチノイズが発生する可能性がある。所定の周波数にロックされている定常状態で、所定量以上の周波数誤差であるグリッチノイズが発生した場合、グリッチ補正回路を用いてグリッチノイズを低減している(例えば、特許文献2参照。)。

【0004】

ところが、グリッチ補正回路を設けた全デジタル位相ロックループでは、グリッチノイズに起因しない周波数誤差が発生した場合、誤ってグリッチノイズ補正処理を実行する可能性がある。誤ってグリッチノイズ補正処理を実行すると、周波数差の変化が正しくDCO(Digitally Controlled Oscillator デジタル制御発振器)に伝達されず、全デジタル位相ロックループから出力される発振周波数信号の精度が低下するという問題点が発生する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−76886号公報

【特許文献2】特開2002−164782号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、周波数差の変化が正しくDCOに伝達され、且つグリッチノイズを低減できる全デジタル位相ロックループを提供することにある。

【課題を解決するための手段】

【0007】

一つの実施形態の全デジタル位相ロックループは、基準周波数クロック信号及びDCO出力信号が入力され、整数部周波数信号を生成する整数部周波数差生成回路と、前記基準周波数クロック信号及び前記DCO出力信号が入力され、前記基準周波数クロック信号に基づいて、前記DCO出力信号を計測するTDCが設けられ、小数部周波数信号を生成する小数部周波数差生成回路と、FCW信号、前記整数部周波数信号、及び前記小数部周波数信号が入力され、前記FCW信号から前記整数部周波数信号及び前記小数部周波数信号を減算処理して周波数差信号を生成する加算器とを有するデジタル周波数比較器と、前記TDCから出力されるTDC出力信号が入力され、グリッチ発生期間信号を生成するグリッチ発生期間検出回路と、前記周波数差信号及び前記グリッチ発生期間信号が入力され、前記グリッチ発生期間信号がイネーブル状態のときに、前記周波数差信号に含まれるグリッチノイズを低減処理してグリッチ補正済み周波数差信号を生成するグリッチ補正回路と、前記グリッチ補正済み周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号を生成するループフィルタと、前記周波数制御信号に応じた前記DCO出力信号を生成し、前記DCO出力信号を発振周波数信号として出力し、前記DCO出力信号を前記デジタル周波数比較器に帰還入力するDCOとを具備し、前記デジタル周波数比較器、前記グリッチ補正回路、前記ループフィルタ、及び前記DCOは閉ループ状に接続されることを特徴とする。

【図面の簡単な説明】

【0008】

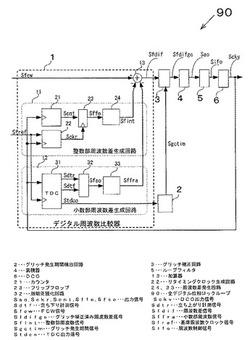

【図1】本発明の第1の実施形態に係る全デジタル位相ロックループを示すブロック図である。

【図2】本発明の第1の実施形態に係るグリッチ補正回路を示すブロック図である。

【図3】本発明の第1の実施形態に係る比較例の全デジタル位相ロックループを示すブロック図である。

【図4】本発明の第1の実施形態に係る比較例の全デジタル位相ロックループで発生するグリッチノイズを説明する模式図である。

【図5】本発明の第1の実施形態に係るメタスタビリティが発生したときの周波数検出を示す図。

【図6】図5の拡大図である。

【図7】本発明の第1の実施形態に係る別のメタスタビリティが発生したときの周波数検出を示す図。

【図8】図7の拡大図である。

【図9】本発明の第2の実施形態に係る全デジタル位相ロックループを示すブロック図である。

【図10】本発明の第2の実施形態に係るグリッチ補正回路を示すブロック図である。

【図11】本発明の第2の実施形態に係るメタスタビリティが発生したときの周波数検出を示す図。

【図12】図11の拡大図である。

【図13】本発明の第2の実施形態に係る別のメタスタビリティが発生したときの周波数検出を示す図。

【図14】図13の拡大図である。

【発明を実施するための形態】

【0009】

以下本発明の実施形態について図面を参照しながら説明する。

【0010】

(第1の実施形態)

まず、本発明の第1の実施形態に係る全デジタル位相ロックループについて、図面を参照して説明する。図1は全デジタル位相ロックループを示すブロック図である。図2はグリッチ補正回路を示すブロック図である。本実施形態では、デジタル周波数比較器の出力側にグリッチノイズを低減するグリッチ補正回路を設け、周波数差の変化を正しくDCOに伝達するためにグリッチ発生期間検出回路を設けている。

【0011】

図1に示すように、全デジタル位相ロックループ(All Digital Phase Locked Loop ADPLL)90には、デジタル周波数比較器1、グリッチ発生期間検出回路2、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO(Digitally Controlled Oscillator)6が設けられる。全デジタル位相ロックループ90は、デジタル周波数比較器1、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6が、閉ループ状に接続されて構成され、DCO出力信号Sckvがデジタル周波数比較器1が帰還入力される。全デジタル位相ロックループ90は、周波数差の変化が正しくDCO6に伝達され、且つグリッチノイズが低減され、精度のよい発振周波数信号を生成する。

【0012】

デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。デジタル周波数比較器1は、FCW(Frequency Command Word 周波数制御語)信号Sfcw、基準周波数クロック信号Sfref、及び帰還入力されるDCO出力信号Sckvが入力され、周波数差信号Sfdifをグリッチ補正回路3に出力し、TDC出力信号Stdcoをグリッチ発生期間検出回路2に出力する。

【0013】

整数部周波数差生成回路11には、カウンタ21、リタイミングクロック生成回路22、フリップフロップ23、及び周波数差発生回路24が設けられる。整数部周波数差生成回路11は、基準周波数クロック信号Sfref及びDCO出力信号Sckvが入力され、DCO出力信号Sckvの周波数が基準周波数クロック信号Sfrefの周波数の何倍の整数値に相当するかを計測し、計測した整数部周波数信号Sfintを加算器13に出力する。

【0014】

カウンタ21は、DCO出力信号Sckvが入力され、DCO出力信号Sckvをカウントした出力信号Scntをフリップフロップ23に出力する。リタイミングクロック生成回路22は、基準周波数クロック信号Sfref及びDCO出力信号Sckvが入力され、DCO出力信号Sckvに基づいて、リタイミングされたクロック信号である出力信号Sckrをフリップフロップ23に出力する。

【0015】

フリップフロップ23は、出力信号Scnt及び出力信号Sckrが入力され、出力信号Sckrに基づいて、出力信号Scntをデータラッチして、ラッチされた信号である出力信号Sffoを周波数差発生回路24に出力する。周波数差発生回路24は、出力信号Sffoが入力され、DCO出力信号Sckvの周波数が基準周波数クロック信号Sfrefの周波数の何倍の整数値に相当するかの計測がなされた整数部周波数信号Sfintを加算器13に出力する。

【0016】

小数部周波数差生成回路12には、TDC(Time to Digital Converter)31、周期正規化回路32、及び周波数差発生回路33が設けられる。小数部周波数差生成回路12は、基準周波数クロック信号Sfref及びDCO出力信号Sckvが入力され、DCO出力信号Sckvの周波数が基準周波数クロック信号Sfrefの周波数の差異の小数部を計測し、計測した小数部周波数信号Sffraを加算器13に出力する。

【0017】

TDC31は、基準周波数クロック信号Sfref及びDCO出力信号Sckvが入力され、基準周波数クロック信号Sfrefに基づいて、DCO出力信号Sckvを計測し、立ち上がり計測信号Sdtr及び立ち下がり計測信号Sdtfを周期正規化回路32に出力し、TDC出力信号Stdcoをグリッチ発生期間検出回路2に出力する。

【0018】

周期正規化回路32は、立ち上がり計測信号Sdtr及び立ち下がり計測信号Sdtfが入力され、周期を正規化した信号である出力信号Sfsoを周波数差発生回路33に出力する。周波数差発生回路33は、出力信号Sfsoが入力され、DCO出力信号Sckvの周波数が基準周波数クロック信号Sfrefの周波数の差異の小数部が計測された小数部周波数信号Sffraを加算器13に出力する。

【0019】

加算器13は、FCW信号Sfcw、整数部周波数信号Sfint、及び小数部周波数信号Sffraが入力され、周波数制御語であるFCWから整数部の周波数差(Sfint)と小数部の周波数差(Sffra)とを減算し、周波数差信号Sfdifをグリッチ補正回路3に出力する。

【0020】

グリッチ発生期間検出回路2は、TDC出力信号Stdcoが入力され、図示しない外部制御装置により予め設定してあるグリッチ発生期間開始とするTDC出力値及びグリッチ発生期間終了とするTDC出力値を基に、グリッチ発生期間信号Sgctimをグリッチ補正回路3に出力する。

【0021】

グリッチ補正回路3は、デジタル周波数比較器1及びグリッチ発生期間検出回路2と累積器4の間に設けられ、周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、グリッチ補正処理を行い、グリッチ補正済み周波数差信号Sfdifgcを累積器4に出力する。

【0022】

グリッチ補正回路3は、グリッチ発生期間信号Sgctimがイネーブル状態で、周波数差信号Sfdifにグリッチノイズが付加されていると判定された場合、グリッチ補正処理を実行してグリッチノイズを低減する。具体的には、回路要因等で発生したと推定されるグリッチノイズによって、許容されるジッタ以上の周波数誤差が生じた場合、この周波数誤差を補正する。

【0023】

グリッチ補正回路3は、グリッチ発生期間信号Sgctimがディセーブル状態で、周波数差信号Sfdifにグリッチノイズが付加されていないと判定された場合、グリッチ補正処理を実行しない。

【0024】

ここで、全デジタル位相ロックループで発生するグリッチノイズについて図3及び図4を参照して説明する。図3は比較例の全デジタル位相ロックループを示すブロック図である。図4は比較例の全デジタル位相ロックループで発生するグリッチノイズを説明する模式図である。グリッチノイズは、トレース間の容量性結合、電源リップル、複数のデバイスによる瞬時高電流、或いはメタスタビリティなどが原因で発生するが、ここではデジタル周波数比較器1aのリタイミングクロック生成回路22で発生するメタスタビリティ起因のグリッチノイズを例にして説明する。

【0025】

図3に示すように、比較例の全デジタル位相ロックループ100では、本実施形態の全デジタル位相ロックループ90のグリッチ発生期間検出回路2及びグリッチ補正回路3が設けられていない。

【0026】

図4に示すように、例えば基準周波数クロック信号Sfref及びDCO出力信号Sckvの立ち上がり或いは立ち下がりが重なった場合、デジタル周波数比較器1aのリタイミングクロック生成回路22の出力がメタステーブル状態となる。メタステーブル状態とは、“H”(例えば「1」)と“L”(例えば「0(ゼロ)」の間の中間の値を保っている状態である。

【0027】

リタイミングクロック生成回路22からメタスタビリティの出力信号Sckrがフリップフロップ23に入力されると、フリップフロップ23の出力信号が「1」或いは「0(ゼロ)」のどちらにもならない中間値となる可能性がある。この中間値が発生すると加算器13から出力される周波数差信号Sfdifにグリッチノイズが付加されることになる。本実施形態の全デジタル位相ロックループ90では、このグリッチノイズを低減するためにグリッチ補正回路3が設けられている。

【0028】

図2に示すように、グリッチ補正回路3には、フリップフロップ41、加算器42、変化量検出回路43、所定値選択回路44、加算器45、及び基準値発生回路46が設けられる。グリッチ補正回路3は、フリップフロップ41、加算器42、変化量検出回路43、所定値選択回路44、及び加算器45が閉ループ状に接続され、グリッチ補正済み周波数差信号Sfdifgcがフリップフロップ41に帰還入力される。

【0029】

フリップフロップ41は、加算器45と加算器42の間に設けられ、帰還入力されるグリッチ補正済み周波数差信号Sfdifgcと基準周波数クロック信号Sfrefとが入力され、基準周波数クロック信号Sfrefに基づいて、グリッチ補正済み周波数差信号Sfdifgcをデータラッチし、ラッチされた信号を出力信号S11として加算器42に出力する。

【0030】

加算器42は、フリップフロップ41と変化量検出回路43の間に設けられ、出力信号S11及び周波数差信号Sfdifが入力され、周波数差(Sfdif)から出力信号S11の値を減算処理し、出力信号S12を変化量検出回路43に出力する。

【0031】

基準値発生回路46は、グリッチ補正処理の判断基準となる基準値En1乃至3を生成して、変化量検出回路43に出力する。

【0032】

変化量検出回路43は、加算器42及び基準値発生回路46と所定値選択回路44の間に設けられ、出力信号S12、基準値En1乃至3が入力される。変化量検出回路43は、例えば、基準値En1を用いて変化量検出信号である出力信号S13aを生成し、基準値En2を用いて変化量検出信号である出力信号S13bを生成し、基準値En3を用いて変化量検出信号である出力信号S13cを生成し、これらの信号を所定値選択回路44に出力する。即ち、変化量検出回路43は、周波数差信号Sfdifから現在の周波数差との差である周波数差の変化量のレベルが、所定の条件を満たしたときにグリッチノイズ起因と判定する。例えば、基準値En1のときに所定の条件を満たしたと判断してグリッチ補正回路3でグリッチ補正処理が実行される。

【0033】

所定値選択回路44は、変化量検出回路43と加算器45の間に設けられ、グリッチ発生期間信号Sgctim、出力信号S13a乃至cが入力され、所定値である「0(ゼロ)」、「+1」、或いは「−1」を周波数差の整数部に加算することにより周波数差を補正した出力信号S14を加算器45に出力する。この所定値は、グリッチ期間検出回路2が生成するグリッチ発生期間に、周波数差の変化量のレベルが満たした条件により周波数差の変化量を相殺するように設定される。

【0034】

加算器45は、所定値選択回路44とフリップフロップ41の間に設けられ、出力信号S14及び周波数差信号Sfdifが入力され、出力信号S14と周波数差信号Sfdifを加算処理してグリッチ補正済み周波数差信号Sfdifgcを生成する。

【0035】

累積器4は、グリッチ補正回路3とループフィルタ5の間に設けられ、グリッチ補正済み周波数差信号Sfdifgcが入力され、累積処理された出力信号Saoをループフィルタ5に出力する。

【0036】

ループフィルタ5は、累積器4とDCO6の間に設けられ、出力信号Saoが入力され、累積器4から順次出力される周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号SlfoをDCO6に出力する。

【0037】

DCO6は、ループフィルタ5とデジタル周波数比較器1の間に設けられ、周波数制御信号Slfoが入力され、周波数制御信号Slfoに応じた発振周波数信号であるDCO出力信号Sckvを生成する。DCO出力信号Sckvは、全デジタル位相ロックループ90の発振周波数信号として使用されるとともに、フィードバック制御用としてデジタル周波数比較器1に帰還入力される。DCO6は、例えば、たすき掛けされたMOSトランジスタからなる負性抵抗、インダクタ、及びコンデンサから構成されるLC発振回路として実現できる。

【0038】

次に、全デジタル位相ロックループ90の周波数検出動作について図5乃至8を参照して説明する。図5は全デジタル位相ロックループ90のメタスタビリティが発生したときの周波数検出を示す図である。図6は図5の拡大図である。

【0039】

図5及び図6に示すように、基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)とDCO出力信号Sckvの立ち上がりが略同時刻の場合について説明する。本来、DCO出力信号Sckvの期間C2での周波数差tm3におけるDCO出力信号Sckvの立ち上がり(Sckv計測クロック)で出力信号Sckrが生成される。ところが、メタスタビリティの影響により周波数差trにおける基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)により、DCO出力信号Sckvの期間C1での周波数差tm1におけるDCO出力信号Sckvの立ち上がり(Sckv計測クロック)で出力信号Sckrが生成される。

【0040】

定常的な状態では、第5図に示すようにメタスタビリティの発生により、DCO出力信号Sckvの計測値がN−1となるので整数部の周期ΔTm1は、

ΔTm1=M−(N−1)=M−N+1・・・・・・・・・・・式(1)

と表される。このため、1つ前の値であるΔT=M−Nに対して「+1」の値になるので、整数部の周波数差の変化量は「+1」となる。

【0041】

グリッチ発生期間検出回路2では、予め設定してあるグリッチ発生期間の開始値と終了値を基に、TDC出力信号Stdcoの値からグリッチ発生期間信号Sgctimを生成する。

【0042】

グリッチ補正回路3は、判定条件を満たしていればグリッチ補正処理を行う(周波数差の変化量=誤差を打ち消す方向となる値を加算する)。全デジタル位相ロックループ90のグリッチ補正回路3では、例えば、定常状態であることから周波数差の変化量レベルが、

条件1:−0.75>周波数差の変化量

条件2:周波数差の変化量>+0.75

のいずれかを満たし、且つ、グリッチ発生期間検出回路2が生成するグリッチ発生期間信号Sgctimが、

条件3:グリッチ発生期間信号Sgctim=“H”(グリッチ発生期間内、イネーブル状態)

を満たしたときに、メタスタビリティ起因のグリッチ発生による誤差と判定し、グリッチ補正処理を実行する。この場合、周波数差の変化量が「+1」であり、且つ、グリッチ発生期間信号Sgctim=“H”なので(条件2且つ条件3を満たしているので)、整数部の周波数差に「−1」を加算する。

【0043】

次に、グリッチ発生期間を拡大した第6図を用いて更に動作を説明する。まず、例えば、図示しない外部制御装置よりグリッチ発生期間の開始とするTDC出力TDCp0とグリッチ発生期間の終了とするTDC出力TDCp2の値をそれぞれ設定する。

【0044】

TDC出力信号StdcoがTDCp0となる周波数差をtm0とし、TDC出力信号StdcoがTDCp1となる周波数差をtm1とし、TDC出力信号StdcoがTDCp2となる周波数差をtm2とする。この設定により、グリッチ発生期間検出回路2は、周波数差がtm0→tm1→tm2の遷移を満たす期間をグリッチ発生期間とし、グリッチ発生期間信号Sgctimを生成する。ここでは、グリッチ発生期間信号Sgctimが正極性であるが、負極性であってもよい。

【0045】

グリッチ補正回路3は、グリッチ発生期間信号Sgctimが“H”(イネーブル状態)期間で、且つ、周波数差の変化量が「1」の場合、グリッチノイズが発生したと判断してグリッチ補正処理を実行する。また、グリッチ補正回路3は、グリッチ発生期間信号Sgctimが“L”期間(ディセーブル状態)の場合、周波数差の変化量が「1」となってもグリッチノイズが発生したと判断せずにグリッチ補正処理を実行しない。

【0046】

なお、周波数差tm0〜tm1と周波数差tm1〜tm2とは等しい値でもよいし、異なる値でもよい。図6では、TDCp1は任意の値となっているが、ゼロでもよい。また、グリッチ補正処理の実行の判定基準としている周波数差の変化量を「1」としているが任意の値でもよい。

【0047】

次に、別のメタスタビリティが発生した場合について図7及び図8を参照して説明する。図7は別のメタスタビリティが発生したときの周波数検出を示す図である。図8は図7の拡大図である。

【0048】

図7及び図8は、周波数誤差が発生した場合について示している。具体的には、外乱などにより目標周波数(FCW)と実周波数(ΔT)とに大きな周波数差が発生し、周波数差trで基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)が発生し、出力信号Sckrが周波数差tm1で生成される場合である。

【0049】

定常的な状態において、基準周波数クロック信号SfrefとDCO出力信号Sckvが同時刻ではない。即ち、メタスタビリティが発生しない場合、出力信号Sckrは周波数trの基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)により、DCO出力信号Sckvの期間C2における周波数差tm1でのDCO出力信号Sckvの立ち上がりで生成される。

【0050】

定常的な状態において、メタスタビリティが発生しないような場合、DCO出力信号Sckvの計測値がN−2となったとき、整数部の周期ΔTeは、

ΔTe=M−(N−2)=M−N+2・・・・・・・・・・・式(2)

と表される。このため、1つ前の値であるΔT=M−Nに対して「−2」の値になるので整数部の周波数差の変化量は「−2」となる。

【0051】

グリッチ発生期間検出回路2では、予め設定してあるグリッチ発生期間の開始値と終了値を基に、TDC出力信号Stdcoの値からグリッチ発生期間信号Sgctimを生成する。

【0052】

グリッチ補正回路3では、判定条件を満たしていればグリッチ補正処理を実行する(周波数差の変化量=誤差を打ち消す方向となる値を加算する)。全デジタル位相ロックループ90のグリッチ補正回路3では、例えば、定常状態であることから周波数差の変化量レベルが、

条件1:−0.75>周波数差の変化量

条件2:周波数差の変化量>+0.75

のどちらかを満たし、且つ、グリッチ発生期間検出回路2が生成するグリッチ発生期間信号Sgctimが、

条件3:グリッチ発生期間信号Sgctim=“L”(グリッチ発生期間外、ディセーブル状態)

を満たしたときに、メタスタビリティ起因のグリッチ発生による誤差と判定せず、グリッチ補正処理を実行しない。この場合、周波数差の変化量が「−2」であり、且つ、グリッチ発生期間信号Sgctim=“L”(ディセーブル状態)なので(条件2且つ条件3を満たしていないので)、整数部の周波数差には何も加算しない。

【0053】

なお、周波数差tm0〜tm1と周波数差tm1〜tm2とは等しい値でもよいし、異なる値でもよい。図8ではTDCp1は任意の値となっているが、ゼロでもよい。

【0054】

上述したように、本実施形態の全デジタル位相ロックループでは、デジタル周波数比較器1、グリッチ発生期間検出回路2、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6が設けられ、DCO出力信号Sckvがデジタル周波数比較器1に帰還入力される。デジタル周波数比較器1、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6は閉ループ状に接続される。デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。整数部周波数差生成回路11には、カウンタ21、リタイミングクロック生成回路22、フリップフロップ23、及び周波数差発生回路24が設けられる。小数部周波数差生成回路12には、TDC31、周期正規化回路32、及び周波数差発生回路33が設けられる。グリッチ発生期間検出回路2は、TDC出力信号Stdcoが入力され、グリッチ発生期間信号Sgctimを生成する。グリッチ補正回路3は、加算器13から出力される周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、グリッチ発生期間信号Sgctimがイネーブル状態のとき、周波数差信号Sfdifに含まれるグリッチノイズを低減処理する。グリッチ補正回路3は、グリッチ発生期間信号Sgctimがディセーブル状態のとき、グリッチノイズ補正処理を実行しない。

【0055】

このため、グリッチノイズが発生した場合、グリッチノイズを大幅に低減化することができる。メタスタビリティ等に起因しない外乱などの周波数差の変化(誤差)が発生した場合、この周波数差の変化(誤差)をDCO6に正しく伝達し、その誤差を元に戻すことができるため、全デジタル位相ロックループ90では、精度の高い発振周波数信号を生成することができる。

【0056】

なお、本実施形態例では、累積器4をグリッチ補正回路3とループフィルタ5の間に設け、累積器4を独立した回路としているが機能上1つのデジタルフィルタとしてループフィルタ5に含めてもよい。

【0057】

(第2の実施形態)

次に、本発明の第2の実施形態に係る全デジタル位相ロックループについて、図面を参照して説明する。図9は全デジタル位相ロックループを示すブロック図である。図10はグリッチ補正回路を示すブロック図である。本実施形態では、デジタル周波数比較器の出力側にグリッチノイズを低減するグリッチ補正回路を設け、周波数差の変化を正しくDCOに伝達するためにグリッチ発生期間検出回路を設けている。

【0058】

以下、第1の実施形態と同一構成部分には、同一符号を付してその部分の説明を省略し、異なる部分のみ説明する。

【0059】

図9に示すように、全デジタル位相ロックループ91には、デジタル周波数比較器1、グリッチ発生期間検出回路2a、グリッチ補正回路3a、累積器4、ループフィルタ5、及びDCO6が設けられる。デジタル周波数比較器1、グリッチ補正回路3a、累積器4、ループフィルタ5、及びDCO6は、閉ループ状に接続され、DCO出力信号Sckvがデジタル周波数比較器1に帰還入力される。全デジタル位相ロックループ91は、周波数差の変化が正しくDCO6に伝達され、且つグリッチノイズが低減され、精度のよい発振周波数信号を生成する。

【0060】

グリッチ発生期間検出回路2aは、グリッチ補正回路3aから出力される検出信号Sfq1detとTDC出力信号Stdcoが入力される。グリッチ発生期間検出回路2aは、周波数差「1」の検出信号Sfq1detに基づいて、TDC出力信号Stdcoの値に応じて発生頻度を計測して所定の発生頻度を満たしたTDC出力信号Stdcoを、グリッチ発生期間信号Sgctimを生成するTDC遷移値として採用する。グリッチ発生期間検出回路2aは、グリッチ補正回路3aから出力される周波数差「1」の検出信号Sfq1detに基づいて、そのときのTDC出力信号Stdcoの値を保持し、同じ値のTDC出力信号Stdcoの発生頻度を計測する。グリッチ発生期間検出回路2aは、同じ値のTDC出力信号Stdcoの発生頻度に基づいて、グリッチ発生期間信号Sgctimを生成してグリッチ補正回路3aに出力する。

【0061】

グリッチ補正回路3aは、デジタル周波数比較器1及びグリッチ発生期間検出回路2aと累積器4の間に設けられ、周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力される。グリッチ補正回路3aは、全デジタル位相ロックループ91が所定の周波数にロックされている定常状態、即ち許容されるジッタ分しか周波数誤差が発生していない状態では、周波数差「1」を検出し、周波数差「1」の検出信号Sfq1detをグリッチ発生期間検出回路2aに出力する。グリッチ補正回路3aは、グリッチ発生期間検出回路2aで生成されたグリッチ発生期間信号Sgctimに基づいて、グリッチ発生期間において発生した周波数差をグリッチノイズ起因の誤差と判定し、周波数差を補正する。

【0062】

図10に示すように、グリッチ補正回路3aには、フリップフロップ41、加算器42、変化量検出回路43a、所定値選択回路44、加算器45、及び基準値発生回路46が設けられる。フリップフロップ41、加算器42、変化量検出回路43a、所定値選択回路44、加算器45、及び基準値発生回路46は、閉ループ状に接続され、グリッチ補正済み周波数差信号Sfdifgcがフリップフロップ41に帰還入力される。

【0063】

変化量検出回路43aは、加算器42及び基準値発生回路46と所定値選択回路44の間に設けられ、出力信号S12、基準値En1乃至3が入力される。変化量検出回路43aは、周波数差「1」を検出し、周波数差「1」の検出信号Sfq1detをグリッチ発生期間検出回路2aに出力する。変化量検出回路43aは、周波数差信号Sfdifから現在の周波数差との差である周波数差の変化量のレベルが、所定の条件を満たしたときにグリッチノイズ起因と判定する。

【0064】

所定値選択回路44は、変化量検出回路43aと加算器45の間に設けられ、グリッチ発生期間信号Sgctim、出力信号S13a乃至cが入力される。所定値選択回路44は、グリッチ期間検出回路2が生成するグリッチ発生期間に、周波数差の変化量のレベルを満たした条件により、周波数差の変化量を相殺するように所定の値を周波数差の整数部に加算する(周波数差の補正処理)。

【0065】

次に、全デジタル位相ロックループ91の周波数検出動作について図11乃至14を参照して説明する。図11は全デジタル位相ロックループ91のメタスタビリティが発生したときの周波数検出を示す図である。図12は図11の拡大図である。

【0066】

図11及び図12に示すように、基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)とDCO出力信号Sckvの立ち上がりが略同時刻の場合について説明する。本来、DCO出力信号Sckvの期間C2での周波数差tn5におけるDCO出力信号Sckvの立ち上がり(Sckv計測クロック)で出力信号Sckrが生成される。ところが、メタスタビリティの影響により周波数差trにおける基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)により、DCO出力信号Sckvの期間C1での周波数差tn1におけるDCO出力信号Sckvの立ち上がり(Sckv計測クロック)で出力信号Sckrが生成される。

【0067】

定常的な状態では、第11図に示すようにメタスタビリティの発生により、DCO出力信号Sckvの計測値がN−1となるので整数部の周期ΔTm1は

ΔTm1=M−(N−1)=M−N+1・・・・・・・・・(式3)

と表される。このため、1つ前の値であるΔT=M−Nに対して「+1」の値になるので、整数部の周波数差の変化量は「+1」となる。

【0068】

グリッチ発生期間検出回路2aは、グリッチ補正回路3aの変化量検出回路43aが生成する周波数差「1」の検出信号Sfq1detに基づいて、所定の周波数差が発生したTDC出力信号Stdcoの値の発生頻度を計測する。計測したTDC出力信号Stdcoの値が所定の予め設定された条件を満たす場合、このTDC出力信号Stdcoの値をグリッチ発生期間の開始値または終了値とし、グリッチ発生期間信号Sgctimを生成する。

【0069】

グリッチ補正回路3aは、判定条件を満たしていれば補正を行う(周波数差の変化量=誤差を打ち消す方向となる値を加算する)。全デジタル位相ロックループ91のグリッチ補正回路3aでは、例えば、定常状態であることから周波数差の変化量レベルが、

条件1:−0.75>周波数差の変化量

条件2:周波数差の変化量>+0.75

のどちらかを満たし、且つ、グリッチ発生期間検出回路2aが生成するグリッチ発生期間信号Sgctimが、

条件3:グリッチ発生期間信号Sgctim=“H”(グリッチ発生期間内、イネーブル状態)

を満たしたときに、メタスタビリティ起因のグリッチ発生による誤差と判定し、グリッチ補正処理を実行する。この場合、周波数差の変化量が「+1」であり、且つ、グリッチ発生期間信号Sgctim=“H”(イネーブル状態)なので(条件2且つ条件3を満たしているので)、整数部の周波数差に「−1」を加算する。

【0070】

次に、グリッチ発生期間を拡大した図12を用いて更に動作を説明する。まず、外部制御装置によりグリッチ発生期間の開始とするTDC出力TDCq0とグリッチ発生期間終了とするTDC出力TDCq2の値をそれぞれ設定する。TDC31の出力がTDCq0となる周波数差をtn0とし、TDCの出力がTDCq2となる周波数差をtn2とする。

【0071】

グリッチ補正回路3aの変化量検出回路43aは周波数差「1」を検出し、グリッチ発生期間検出回路2aに周波数差「1」の検出信号Sfq1detを出力する。

【0072】

グリッチ発生期間検出回路2aは、周波数差「1」の検出信号Sfq1detに基づき、そのときのTDCの出力値(TDCq3)を保持すると共に、TDCq3の発生回数を計測する。周波数差が最大となるTDC値をTDCq1aとすると、TDC出力TDCq3が、

TDCq3<TDCq1a・・・・・・・・・・・・・・式(4)

を満たし、且つ、TDCq3がM回(Mは1以上の整数)発生した場合、TDCq3からTDCq2をグリッチ発生期間(TDCq3をグリッチ期間の開始)とする。なお、検出回数Mは別途外部より制御する。

【0073】

ここでは、グリッチ期間の開始点(TDCq3)について1つだけの値を保持し計測しているが、複数の値を保持し、計測してもよい。また、グリッチ期間の開始点について計測・学習のみ説明しているが、グリッチ期間の終了点についても同様に計測・学習してもよい。図12ではTDCq1は任意の値となっているが、ゼロでもよい。また、tn3=trとしているが、tn3=tr−αでもよい。但しαは、tn3がDCO出力信号Sckvの1周期を超えない任意の値とする。

【0074】

グリッチ補正回路3aは、グリッチ発生期間信号Sgctimが“H”(イネーブル状態)期間で、且つ、周波数差の変化量が「1」の場合、グリッチノイズが発生したと判定してグリッチ補正処理を実行する。グリッチ補正回路3aは、グリッチ発生期間信号Sgctimが“L”(ディセーブル状態)期間の場合、周波数差の変化量が「1」となってもグリッチノイズが発生したとは判定せずにグリッチ補正処理を実行しない。

【0075】

次に、別のメタスタビリティが発生した場合について図13及び図14を参照して説明する。図13は別のメタスタビリティが発生したときの周波数検出を示す図である。図14は図13の拡大図である。

【0076】

図13及び図14は、周波数誤差が発生した場合について示している。具体的には、基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)とDCO出力信号Sckvの立ち上がりエッジが略同時刻の場合である。本来、DCO出力信号Sckvの期間C2での周波数差tn1におけるDCO出力信号Sckvの立ち上がりで出力信号Sckrは生成される。ところが、出力信号Sckrはメタスタビリティの影響で周波数差trの基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)により、DCO出力信号Sckvの期間C3での周波数差tn5におけるDCO出力信号Sckvの立ち上がりで生成される。

【0077】

定常的な状態では、図13に示すようにメタスタビリティの発生により、DCO出力信号Sckvの計測値がN+1となるので整数部の周期ΔTm2は、

ΔTm2=M−(N+1)=M−N−1・・・・・・・・・式(5)

と表される。このため、1つ前の値であるΔT=M−Nに対して「−1」の値になるので、整数部の周波数差の変化量は「−1」となる。

【0078】

グリッチ発生期間検出回路2aは、グリッチ補正回路3aの変化量検出回路43aが生成する周波数差「1」の検出信号Sfq1detに基づいて、所定の周波数差が発生したTDC出力信号Stdcoの発生頻度を計測する。計測したTDC出力信号Stdcoの値が所定の予め設定された条件を満たす場合、このTDC出力信号Stdcoの値をグリッチ発生期間の開始値または終了値とし、グリッチ発生期間信号Sgctimを生成する。

【0079】

グリッチ補正回路3aは、判定条件を満たしていれば補正を行う(周波数差の変化量=誤差を打ち消す方向となる値を加算する)。全デジタル位相ロックループ91のグリッチ補正回路3aでは、例えば、定常状態であることから周波数差の変化量レベルが、

条件1:−0.75>周波数差の変化量

条件2:周波数差の変化量>+0.75

のどちらかを満たし、且つ、グリッチ発生期間検出回路2aが生成するグリッチ発生期間信号Sgctimが、

条件3:グリッチ発生期間信号Sgctim=“H”(グリッチ発生期間内、イネーブル状態)

を満たしたときに、メタスタビリティ起因によるグリッチノイズの発生による誤差と判定し、グリッチ補正処理を実行する。この場合、周波数差の変化量が「−1」であり、かつ、グリッチ発生期間信号Sgctim=“H”(イネーブル状態)なので(条件1且つ条件3を満たしているので)、整数部の周波数差に「+1」を加算する。

【0080】

グリッチ発生期間を拡大した図14を用いて更に動作を説明する。まず、外部制御装置によりグリッチ発生期間の開始とするTDC出力TDCq0とグリッチ発生期間終了とするTDC出力TDCq2の値をそれぞれ設定する。TDCの出力がTDCq0となる周波数差をtn0とし、TDCの出力がTDCq2となる周波数差をtn2とする。

【0081】

グリッチ補正回路3aの変化量検出回路43aは周波数差「1」を検出し、グリッチ発生期間検出回路2aに周波数差「1」の検出信号Sfq1detを出力する。グリッチ発生期間検出回路2aは、周波数差「1」の検出信号Sfq1detに基づいて、そのときのTDCの出力値(TDCq4)を保持すると共に、TDCq4の発生回数を計測する。TDCq4が、

TDCq1<TDCq4・・・・・・・・・・・・・・・式(6)

を満たし、且つ、TDCq4がN回(Nは1以上の整数)発生した場合、TDCq0からTDCq4をグリッチ発生期間(TDCq4をグリッチ期間の終了)とする。なお、検出回数Nは別途外部より制御する。

【0082】

ここでは、グリッチ期間の終了点(TDCq4)について1つだけの値を保持し計測しているが、複数の値を保持し、計測してもよい。また、グリッチ期間の終了点について計測・学習のみ説明しているが、グリッチ期間の開始点についても同様に計測・学習してもよい。図14ではTDCq1は任意の値となっているが、ゼロでもよい。また、tn4=trとしているが、tn4=tr−βでもよい。但しβは、tn4がDCO出力信号Sckvの1周期を超えない任意の値である。

【0083】

グリッチ補正回路3aは、グリッチ発生期間信号Sgctimが“H”(イネーブル状態)期間で、且つ、周波数差の変化量が「1」の場合、グリッチノイズが発生したと判定してグリッチ補正処理を実行する。また、グリッチ補正回路3aは、グリッチ発生期間信号Sgctimが“L”(ディセーブル状態)期間の場合、周波数差の変化量が「1」となってもグリッチノイズが発生した判定せずにグリッチ補正処理を実行しない。

【0084】

上述したように、本実施形態の全デジタル位相ロックループでは、デジタル周波数比較器1、グリッチ発生期間検出回路2a、グリッチ補正回路3a、累積器4、ループフィルタ5、及びDCO6が設けられ、DCO出力信号Sckvがデジタル周波数比較器1に帰還入力される。デジタル周波数比較器1、グリッチ補正回路3a、累積器4、ループフィルタ5、及びDCO6は閉ループ状に接続される。デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。整数部周波数差生成回路11には、カウンタ21、リタイミングクロック生成回路22、フリップフロップ23、及び周波数差発生回路24が設けられる。小数部周波数差生成回路12には、TDC31、周期正規化回路32、及び周波数差発生回路33が設けられる。グリッチ発生期間検出回路2aは、TDC出力信号Stdco及びグリッチ補正回路3aから出力される周波数差「1」の検出信号Sfq1detが入力され、周波数差「1」の検出信号Sfq1detに基づいて、そのときのTDC出力信号Stdcoの値を保持し、同じ値のTDC出力信号Stdcoの発生頻度を計測し、同じ値のTDC出力信号Stdcoの発生頻度に基づいて、グリッチ発生期間信号Sgctimを生成する。グリッチ補正回路3aは、加算器13から出力される周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、所定の周波数にロックされている定常状態では、周波数差「1」を検出して周波数差「1」の検出信号Sfq1detを生成し、グリッチ発生期間信号Sgctimがイネーブル状態のとき、周波数差信号Sfdifに含まれるグリッチノイズを低減処理する。グリッチ補正回路3aは、グリッチ発生期間信号Sgctimがディセーブル状態のとき、グリッチノイズ補正処理を実行しない。

【0085】

このため、グリッチ発生期間を計測・学習することで経時変化などによるグリッチ発生期間の変化に対応できる。この結果、グリッチノイズが発生した場合、グリッチ補正回路3aはグリッチノイズを大幅に低減化することができる。グリッチ補正回路3aは、メタスタビリティに起因しない周波数差の変化(誤差)が発生した場合、この周波数差の変化をDCO6に正しく伝達し、その誤差を元に戻すことができるため、全デジタル位相ロックループ91では、安定して精度の高い発振周波数信号を生成できる。

【0086】

本発明は、上記実施形態に限定されるものではなく、発明の趣旨を逸脱しない範囲で、種々、変更してもよい。

【0087】

実施形態では、FCW信号Sfcwを直接加算器13に入力しているが、加算器13の前段にカウンタを設け、このカウンタがリタイミングクロック生成回路22の出力信号Sckrに基づいてFCW信号をカウントし、カウントされたFCW信号を参照信号入力として加算器13に入力させてもよい。また、TDC31を構成する所定時間遅延させるインバータの遅延量は周囲温度や電圧変動の影響を受けるので、例えばTDC31に自己校正機能を付加して周囲温度や電圧変動の影響をキャンセルするのが好ましい。

【0088】

本発明は、以下の付記に記載されているような構成が考えられる。

(付記1) 基準周波数クロック信号及びDCO出力信号が入力され、整数部周波数信号を生成する整数部周波数差生成回路と、前記基準周波数クロック信号及び前記DCO出力信号が入力され、前記基準周波数クロック信号に基づいて、前記DCO出力信号を計測するTDCが設けられ、小数部周波数信号を生成する小数部周波数差生成回路と、FCW信号、前記整数部周波数信号、及び前記小数部周波数信号が入力され、前記FCW信号から前記整数部周波数信号及び前記小数部周波数信号を減算処理して周波数差信号を生成する加算器とを有するデジタル周波数比較器と、前記TDCから出力されるTDC出力信号が入力され、グリッチ発生期間信号を生成するグリッチ発生期間検出回路と、前記周波数差信号及び前記グリッチ発生期間信号が入力され、前記グリッチ発生期間信号がイネーブル状態のときに、前記周波数差信号に含まれるグリッチノイズを低減処理してグリッチ補正済み周波数差信号を生成するグリッチ補正回路と、前記グリッチ補正済み周波数差信号が入力され、前記グリッチ補正済み周波数差信号を累積処理する累積器と、累積処理された前記グリッチ補正済み周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号を生成するループフィルタと、

前記周波数制御信号に応じた前記DCO出力信号を生成し、前記DCO出力信号を発振周波数信号として出力し、前記DCO出力信号を前記デジタル周波数比較器に帰還入力するDCOとを具備し、前記デジタル周波数比較器、前記グリッチ補正回路、前記累積器、前記ループフィルタ、及び前記DCOは閉ループ状に接続される全デジタル位相ロックループ。

【0089】

(付記2) 前記グリッチ補正回路は、許容されるジッタ以上の周波数差の変化が発生した場合、前記グリッチ発生期間信号がグリッチ発生期間内のとき、前記周波数差の変化をメタスタビリティに起因するグリッチノイズと判定して前記周波数差の変化を補正する付記1に記載の全デジタル位相ロックループ。

【0090】

(付記3) 前記整数部周波数差生成回路は、前記DCO出力信号をカウントするカウンタと、前記FCW信号及び前記DCO出力信号が入力され、前記DCO出力信号に基づいて、リタイミングされたクロック信号を生成するリタイミングクロック生成回路と、前記カウンタの出力信号が入力され、前記リタイミングクロック生成回路の出力信号に基づいて、前記カウンタの出力信号をデータラッチするフリップフロップと、前記フリップフロップの出力信号が入力され、前記DCO出力信号の周波数が前記基準周波数クロック信号の周波数の何倍の整数値に相当するかの計測を行う周波数差発生回路とを有する付記1或いは2に記載の全デジタル位相ロックループ。

【符号の説明】

【0091】

1 デジタル周波数比較器

2、2a デジタル発生期間検出回路

3、3a グリッチ補正回路

4 累積器

5 ループフィルタ

6 DCO

11 整数部周波数差生成回路

12、12a 少数部周波数差生成回路

13、42、45 加算器

21 カウンタ

22 リタイミングクロック生成回路

23、41 フリップフロップ

24、33 周波数差発生回路

31、31a TDC出力信号

32 周期正規化回路

43、43a 変化量検出回路

44 所定値選択回路

46 基準値発生回路

90、91、100 全デジタル位相ロックループ

Sao、Sckr、Scnt、Sffo、Sfso、S11、S12、S13a〜c、S14 出力信号

Sckv DCO出力信号

Sdtf 立ち下がり計測信号

Sdtr 立ち上がり計測信号

Sfcw FCW信号

Sfdif 周波数差信号

Sfdifgc グリッチ補正済み周波数差信号

Sffra 少数部周波数信号

Sfint 整数部周波数信号

Sfq1det 検出信号

Sfref 基準周波数クロック信号

Sgctim グリッチ発生期間信号

Slfo 周波数制御信号

Stdco TDC出力信号

TDCp0 tm0におけるTDC出力

TDCp1 tm1におけるTDC出力

TDCp2 tm2におけるTDC出力

TDCq0 tn0におけるTDC出力

TDCq1 tn1におけるTDC出力

TDCq1a 周波数差が最大となるTDC出力

TDCq2 tn2におけるTDC出力

TDCq3 tn3におけるTDC出力

TDCq4 tn4におけるTDC出力

Tglc グリッチ発生期間(tn0〜tn2)

Tglc0 グリッチ発生期間(学習前初期値)

Tglc1 グリッチ発生期間(tn3〜tn2)

Tglc2 グリッチ発生期間(tn0〜tn4)

tm0 グリッチ発生期間(開始)

tm1、tm3 Sckv立ち上がりエッジ(Sckv計測クロック)

tm2 グリッチ発生期間(終了)

tn0 グリッチ発生期間(開始初期値)

tn1、tn5 Sckv立ち上がりエッジ(Sckv計測クロック)

tn2 グリッチ発生期間(終了初期値)

tn3 グリッチ発生期間(開始学習値)

tn4 グリッチ発生期間(終了学習値)

tr Sfref立ち上がりエッジ

【技術分野】

【0001】

本発明の実施形態は、全デジタル位相ロックループに関する。

【背景技術】

【0002】

無線通信に使用される周波数シンセサイザ、マイクロプロセッサに使用される高速クロック生成回路、FM復調器、CDR(Clock Data Recovery)などには位相ロックループ(Phase Locked Loop PLL)が多用される。位相ロックループは、アナログ回路やアナログ・デジタル回路で実現されている。近年、CMOS技術の微細化、高集積度化、低消費電流化の進展に伴い、すべてデジタル回路で構成される全デジタル位相ロックループ(All Digital Phase Locked Loop ADPLL)が種々の機関で開発されている。全デジタル位相ロックループは、アナログフィルタやチャージ・ポンプ回路が不要なので、低電圧動作、低位相雑音、高速整定が可能となる(例えば、特許文献1参照。)。

【0003】

全デジタル位相ロックループは、トレース間の容量性結合、電源リップル、複数のデバイスによる瞬時高電流などが起因となるグリッチノイズが発生する可能性がある。また、論理回路でクロック信号とデータ信号の立ち上がり或いは立ち下がりが重なった場合に発生するメタスタビリティなどによってもグリッチノイズが発生する可能性がある。所定の周波数にロックされている定常状態で、所定量以上の周波数誤差であるグリッチノイズが発生した場合、グリッチ補正回路を用いてグリッチノイズを低減している(例えば、特許文献2参照。)。

【0004】

ところが、グリッチ補正回路を設けた全デジタル位相ロックループでは、グリッチノイズに起因しない周波数誤差が発生した場合、誤ってグリッチノイズ補正処理を実行する可能性がある。誤ってグリッチノイズ補正処理を実行すると、周波数差の変化が正しくDCO(Digitally Controlled Oscillator デジタル制御発振器)に伝達されず、全デジタル位相ロックループから出力される発振周波数信号の精度が低下するという問題点が発生する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−76886号公報

【特許文献2】特開2002−164782号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、周波数差の変化が正しくDCOに伝達され、且つグリッチノイズを低減できる全デジタル位相ロックループを提供することにある。

【課題を解決するための手段】

【0007】

一つの実施形態の全デジタル位相ロックループは、基準周波数クロック信号及びDCO出力信号が入力され、整数部周波数信号を生成する整数部周波数差生成回路と、前記基準周波数クロック信号及び前記DCO出力信号が入力され、前記基準周波数クロック信号に基づいて、前記DCO出力信号を計測するTDCが設けられ、小数部周波数信号を生成する小数部周波数差生成回路と、FCW信号、前記整数部周波数信号、及び前記小数部周波数信号が入力され、前記FCW信号から前記整数部周波数信号及び前記小数部周波数信号を減算処理して周波数差信号を生成する加算器とを有するデジタル周波数比較器と、前記TDCから出力されるTDC出力信号が入力され、グリッチ発生期間信号を生成するグリッチ発生期間検出回路と、前記周波数差信号及び前記グリッチ発生期間信号が入力され、前記グリッチ発生期間信号がイネーブル状態のときに、前記周波数差信号に含まれるグリッチノイズを低減処理してグリッチ補正済み周波数差信号を生成するグリッチ補正回路と、前記グリッチ補正済み周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号を生成するループフィルタと、前記周波数制御信号に応じた前記DCO出力信号を生成し、前記DCO出力信号を発振周波数信号として出力し、前記DCO出力信号を前記デジタル周波数比較器に帰還入力するDCOとを具備し、前記デジタル周波数比較器、前記グリッチ補正回路、前記ループフィルタ、及び前記DCOは閉ループ状に接続されることを特徴とする。

【図面の簡単な説明】

【0008】

【図1】本発明の第1の実施形態に係る全デジタル位相ロックループを示すブロック図である。

【図2】本発明の第1の実施形態に係るグリッチ補正回路を示すブロック図である。

【図3】本発明の第1の実施形態に係る比較例の全デジタル位相ロックループを示すブロック図である。

【図4】本発明の第1の実施形態に係る比較例の全デジタル位相ロックループで発生するグリッチノイズを説明する模式図である。

【図5】本発明の第1の実施形態に係るメタスタビリティが発生したときの周波数検出を示す図。

【図6】図5の拡大図である。

【図7】本発明の第1の実施形態に係る別のメタスタビリティが発生したときの周波数検出を示す図。

【図8】図7の拡大図である。

【図9】本発明の第2の実施形態に係る全デジタル位相ロックループを示すブロック図である。

【図10】本発明の第2の実施形態に係るグリッチ補正回路を示すブロック図である。

【図11】本発明の第2の実施形態に係るメタスタビリティが発生したときの周波数検出を示す図。

【図12】図11の拡大図である。

【図13】本発明の第2の実施形態に係る別のメタスタビリティが発生したときの周波数検出を示す図。

【図14】図13の拡大図である。

【発明を実施するための形態】

【0009】

以下本発明の実施形態について図面を参照しながら説明する。

【0010】

(第1の実施形態)

まず、本発明の第1の実施形態に係る全デジタル位相ロックループについて、図面を参照して説明する。図1は全デジタル位相ロックループを示すブロック図である。図2はグリッチ補正回路を示すブロック図である。本実施形態では、デジタル周波数比較器の出力側にグリッチノイズを低減するグリッチ補正回路を設け、周波数差の変化を正しくDCOに伝達するためにグリッチ発生期間検出回路を設けている。

【0011】

図1に示すように、全デジタル位相ロックループ(All Digital Phase Locked Loop ADPLL)90には、デジタル周波数比較器1、グリッチ発生期間検出回路2、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO(Digitally Controlled Oscillator)6が設けられる。全デジタル位相ロックループ90は、デジタル周波数比較器1、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6が、閉ループ状に接続されて構成され、DCO出力信号Sckvがデジタル周波数比較器1が帰還入力される。全デジタル位相ロックループ90は、周波数差の変化が正しくDCO6に伝達され、且つグリッチノイズが低減され、精度のよい発振周波数信号を生成する。

【0012】

デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。デジタル周波数比較器1は、FCW(Frequency Command Word 周波数制御語)信号Sfcw、基準周波数クロック信号Sfref、及び帰還入力されるDCO出力信号Sckvが入力され、周波数差信号Sfdifをグリッチ補正回路3に出力し、TDC出力信号Stdcoをグリッチ発生期間検出回路2に出力する。

【0013】

整数部周波数差生成回路11には、カウンタ21、リタイミングクロック生成回路22、フリップフロップ23、及び周波数差発生回路24が設けられる。整数部周波数差生成回路11は、基準周波数クロック信号Sfref及びDCO出力信号Sckvが入力され、DCO出力信号Sckvの周波数が基準周波数クロック信号Sfrefの周波数の何倍の整数値に相当するかを計測し、計測した整数部周波数信号Sfintを加算器13に出力する。

【0014】

カウンタ21は、DCO出力信号Sckvが入力され、DCO出力信号Sckvをカウントした出力信号Scntをフリップフロップ23に出力する。リタイミングクロック生成回路22は、基準周波数クロック信号Sfref及びDCO出力信号Sckvが入力され、DCO出力信号Sckvに基づいて、リタイミングされたクロック信号である出力信号Sckrをフリップフロップ23に出力する。

【0015】

フリップフロップ23は、出力信号Scnt及び出力信号Sckrが入力され、出力信号Sckrに基づいて、出力信号Scntをデータラッチして、ラッチされた信号である出力信号Sffoを周波数差発生回路24に出力する。周波数差発生回路24は、出力信号Sffoが入力され、DCO出力信号Sckvの周波数が基準周波数クロック信号Sfrefの周波数の何倍の整数値に相当するかの計測がなされた整数部周波数信号Sfintを加算器13に出力する。

【0016】

小数部周波数差生成回路12には、TDC(Time to Digital Converter)31、周期正規化回路32、及び周波数差発生回路33が設けられる。小数部周波数差生成回路12は、基準周波数クロック信号Sfref及びDCO出力信号Sckvが入力され、DCO出力信号Sckvの周波数が基準周波数クロック信号Sfrefの周波数の差異の小数部を計測し、計測した小数部周波数信号Sffraを加算器13に出力する。

【0017】

TDC31は、基準周波数クロック信号Sfref及びDCO出力信号Sckvが入力され、基準周波数クロック信号Sfrefに基づいて、DCO出力信号Sckvを計測し、立ち上がり計測信号Sdtr及び立ち下がり計測信号Sdtfを周期正規化回路32に出力し、TDC出力信号Stdcoをグリッチ発生期間検出回路2に出力する。

【0018】

周期正規化回路32は、立ち上がり計測信号Sdtr及び立ち下がり計測信号Sdtfが入力され、周期を正規化した信号である出力信号Sfsoを周波数差発生回路33に出力する。周波数差発生回路33は、出力信号Sfsoが入力され、DCO出力信号Sckvの周波数が基準周波数クロック信号Sfrefの周波数の差異の小数部が計測された小数部周波数信号Sffraを加算器13に出力する。

【0019】

加算器13は、FCW信号Sfcw、整数部周波数信号Sfint、及び小数部周波数信号Sffraが入力され、周波数制御語であるFCWから整数部の周波数差(Sfint)と小数部の周波数差(Sffra)とを減算し、周波数差信号Sfdifをグリッチ補正回路3に出力する。

【0020】

グリッチ発生期間検出回路2は、TDC出力信号Stdcoが入力され、図示しない外部制御装置により予め設定してあるグリッチ発生期間開始とするTDC出力値及びグリッチ発生期間終了とするTDC出力値を基に、グリッチ発生期間信号Sgctimをグリッチ補正回路3に出力する。

【0021】

グリッチ補正回路3は、デジタル周波数比較器1及びグリッチ発生期間検出回路2と累積器4の間に設けられ、周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、グリッチ補正処理を行い、グリッチ補正済み周波数差信号Sfdifgcを累積器4に出力する。

【0022】

グリッチ補正回路3は、グリッチ発生期間信号Sgctimがイネーブル状態で、周波数差信号Sfdifにグリッチノイズが付加されていると判定された場合、グリッチ補正処理を実行してグリッチノイズを低減する。具体的には、回路要因等で発生したと推定されるグリッチノイズによって、許容されるジッタ以上の周波数誤差が生じた場合、この周波数誤差を補正する。

【0023】

グリッチ補正回路3は、グリッチ発生期間信号Sgctimがディセーブル状態で、周波数差信号Sfdifにグリッチノイズが付加されていないと判定された場合、グリッチ補正処理を実行しない。

【0024】

ここで、全デジタル位相ロックループで発生するグリッチノイズについて図3及び図4を参照して説明する。図3は比較例の全デジタル位相ロックループを示すブロック図である。図4は比較例の全デジタル位相ロックループで発生するグリッチノイズを説明する模式図である。グリッチノイズは、トレース間の容量性結合、電源リップル、複数のデバイスによる瞬時高電流、或いはメタスタビリティなどが原因で発生するが、ここではデジタル周波数比較器1aのリタイミングクロック生成回路22で発生するメタスタビリティ起因のグリッチノイズを例にして説明する。

【0025】

図3に示すように、比較例の全デジタル位相ロックループ100では、本実施形態の全デジタル位相ロックループ90のグリッチ発生期間検出回路2及びグリッチ補正回路3が設けられていない。

【0026】

図4に示すように、例えば基準周波数クロック信号Sfref及びDCO出力信号Sckvの立ち上がり或いは立ち下がりが重なった場合、デジタル周波数比較器1aのリタイミングクロック生成回路22の出力がメタステーブル状態となる。メタステーブル状態とは、“H”(例えば「1」)と“L”(例えば「0(ゼロ)」の間の中間の値を保っている状態である。

【0027】

リタイミングクロック生成回路22からメタスタビリティの出力信号Sckrがフリップフロップ23に入力されると、フリップフロップ23の出力信号が「1」或いは「0(ゼロ)」のどちらにもならない中間値となる可能性がある。この中間値が発生すると加算器13から出力される周波数差信号Sfdifにグリッチノイズが付加されることになる。本実施形態の全デジタル位相ロックループ90では、このグリッチノイズを低減するためにグリッチ補正回路3が設けられている。

【0028】

図2に示すように、グリッチ補正回路3には、フリップフロップ41、加算器42、変化量検出回路43、所定値選択回路44、加算器45、及び基準値発生回路46が設けられる。グリッチ補正回路3は、フリップフロップ41、加算器42、変化量検出回路43、所定値選択回路44、及び加算器45が閉ループ状に接続され、グリッチ補正済み周波数差信号Sfdifgcがフリップフロップ41に帰還入力される。

【0029】

フリップフロップ41は、加算器45と加算器42の間に設けられ、帰還入力されるグリッチ補正済み周波数差信号Sfdifgcと基準周波数クロック信号Sfrefとが入力され、基準周波数クロック信号Sfrefに基づいて、グリッチ補正済み周波数差信号Sfdifgcをデータラッチし、ラッチされた信号を出力信号S11として加算器42に出力する。

【0030】

加算器42は、フリップフロップ41と変化量検出回路43の間に設けられ、出力信号S11及び周波数差信号Sfdifが入力され、周波数差(Sfdif)から出力信号S11の値を減算処理し、出力信号S12を変化量検出回路43に出力する。

【0031】

基準値発生回路46は、グリッチ補正処理の判断基準となる基準値En1乃至3を生成して、変化量検出回路43に出力する。

【0032】

変化量検出回路43は、加算器42及び基準値発生回路46と所定値選択回路44の間に設けられ、出力信号S12、基準値En1乃至3が入力される。変化量検出回路43は、例えば、基準値En1を用いて変化量検出信号である出力信号S13aを生成し、基準値En2を用いて変化量検出信号である出力信号S13bを生成し、基準値En3を用いて変化量検出信号である出力信号S13cを生成し、これらの信号を所定値選択回路44に出力する。即ち、変化量検出回路43は、周波数差信号Sfdifから現在の周波数差との差である周波数差の変化量のレベルが、所定の条件を満たしたときにグリッチノイズ起因と判定する。例えば、基準値En1のときに所定の条件を満たしたと判断してグリッチ補正回路3でグリッチ補正処理が実行される。

【0033】

所定値選択回路44は、変化量検出回路43と加算器45の間に設けられ、グリッチ発生期間信号Sgctim、出力信号S13a乃至cが入力され、所定値である「0(ゼロ)」、「+1」、或いは「−1」を周波数差の整数部に加算することにより周波数差を補正した出力信号S14を加算器45に出力する。この所定値は、グリッチ期間検出回路2が生成するグリッチ発生期間に、周波数差の変化量のレベルが満たした条件により周波数差の変化量を相殺するように設定される。

【0034】

加算器45は、所定値選択回路44とフリップフロップ41の間に設けられ、出力信号S14及び周波数差信号Sfdifが入力され、出力信号S14と周波数差信号Sfdifを加算処理してグリッチ補正済み周波数差信号Sfdifgcを生成する。

【0035】

累積器4は、グリッチ補正回路3とループフィルタ5の間に設けられ、グリッチ補正済み周波数差信号Sfdifgcが入力され、累積処理された出力信号Saoをループフィルタ5に出力する。

【0036】

ループフィルタ5は、累積器4とDCO6の間に設けられ、出力信号Saoが入力され、累積器4から順次出力される周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号SlfoをDCO6に出力する。

【0037】

DCO6は、ループフィルタ5とデジタル周波数比較器1の間に設けられ、周波数制御信号Slfoが入力され、周波数制御信号Slfoに応じた発振周波数信号であるDCO出力信号Sckvを生成する。DCO出力信号Sckvは、全デジタル位相ロックループ90の発振周波数信号として使用されるとともに、フィードバック制御用としてデジタル周波数比較器1に帰還入力される。DCO6は、例えば、たすき掛けされたMOSトランジスタからなる負性抵抗、インダクタ、及びコンデンサから構成されるLC発振回路として実現できる。

【0038】

次に、全デジタル位相ロックループ90の周波数検出動作について図5乃至8を参照して説明する。図5は全デジタル位相ロックループ90のメタスタビリティが発生したときの周波数検出を示す図である。図6は図5の拡大図である。

【0039】

図5及び図6に示すように、基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)とDCO出力信号Sckvの立ち上がりが略同時刻の場合について説明する。本来、DCO出力信号Sckvの期間C2での周波数差tm3におけるDCO出力信号Sckvの立ち上がり(Sckv計測クロック)で出力信号Sckrが生成される。ところが、メタスタビリティの影響により周波数差trにおける基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)により、DCO出力信号Sckvの期間C1での周波数差tm1におけるDCO出力信号Sckvの立ち上がり(Sckv計測クロック)で出力信号Sckrが生成される。

【0040】

定常的な状態では、第5図に示すようにメタスタビリティの発生により、DCO出力信号Sckvの計測値がN−1となるので整数部の周期ΔTm1は、

ΔTm1=M−(N−1)=M−N+1・・・・・・・・・・・式(1)

と表される。このため、1つ前の値であるΔT=M−Nに対して「+1」の値になるので、整数部の周波数差の変化量は「+1」となる。

【0041】

グリッチ発生期間検出回路2では、予め設定してあるグリッチ発生期間の開始値と終了値を基に、TDC出力信号Stdcoの値からグリッチ発生期間信号Sgctimを生成する。

【0042】

グリッチ補正回路3は、判定条件を満たしていればグリッチ補正処理を行う(周波数差の変化量=誤差を打ち消す方向となる値を加算する)。全デジタル位相ロックループ90のグリッチ補正回路3では、例えば、定常状態であることから周波数差の変化量レベルが、

条件1:−0.75>周波数差の変化量

条件2:周波数差の変化量>+0.75

のいずれかを満たし、且つ、グリッチ発生期間検出回路2が生成するグリッチ発生期間信号Sgctimが、

条件3:グリッチ発生期間信号Sgctim=“H”(グリッチ発生期間内、イネーブル状態)

を満たしたときに、メタスタビリティ起因のグリッチ発生による誤差と判定し、グリッチ補正処理を実行する。この場合、周波数差の変化量が「+1」であり、且つ、グリッチ発生期間信号Sgctim=“H”なので(条件2且つ条件3を満たしているので)、整数部の周波数差に「−1」を加算する。

【0043】

次に、グリッチ発生期間を拡大した第6図を用いて更に動作を説明する。まず、例えば、図示しない外部制御装置よりグリッチ発生期間の開始とするTDC出力TDCp0とグリッチ発生期間の終了とするTDC出力TDCp2の値をそれぞれ設定する。

【0044】

TDC出力信号StdcoがTDCp0となる周波数差をtm0とし、TDC出力信号StdcoがTDCp1となる周波数差をtm1とし、TDC出力信号StdcoがTDCp2となる周波数差をtm2とする。この設定により、グリッチ発生期間検出回路2は、周波数差がtm0→tm1→tm2の遷移を満たす期間をグリッチ発生期間とし、グリッチ発生期間信号Sgctimを生成する。ここでは、グリッチ発生期間信号Sgctimが正極性であるが、負極性であってもよい。

【0045】

グリッチ補正回路3は、グリッチ発生期間信号Sgctimが“H”(イネーブル状態)期間で、且つ、周波数差の変化量が「1」の場合、グリッチノイズが発生したと判断してグリッチ補正処理を実行する。また、グリッチ補正回路3は、グリッチ発生期間信号Sgctimが“L”期間(ディセーブル状態)の場合、周波数差の変化量が「1」となってもグリッチノイズが発生したと判断せずにグリッチ補正処理を実行しない。

【0046】

なお、周波数差tm0〜tm1と周波数差tm1〜tm2とは等しい値でもよいし、異なる値でもよい。図6では、TDCp1は任意の値となっているが、ゼロでもよい。また、グリッチ補正処理の実行の判定基準としている周波数差の変化量を「1」としているが任意の値でもよい。

【0047】

次に、別のメタスタビリティが発生した場合について図7及び図8を参照して説明する。図7は別のメタスタビリティが発生したときの周波数検出を示す図である。図8は図7の拡大図である。

【0048】

図7及び図8は、周波数誤差が発生した場合について示している。具体的には、外乱などにより目標周波数(FCW)と実周波数(ΔT)とに大きな周波数差が発生し、周波数差trで基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)が発生し、出力信号Sckrが周波数差tm1で生成される場合である。

【0049】

定常的な状態において、基準周波数クロック信号SfrefとDCO出力信号Sckvが同時刻ではない。即ち、メタスタビリティが発生しない場合、出力信号Sckrは周波数trの基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)により、DCO出力信号Sckvの期間C2における周波数差tm1でのDCO出力信号Sckvの立ち上がりで生成される。

【0050】

定常的な状態において、メタスタビリティが発生しないような場合、DCO出力信号Sckvの計測値がN−2となったとき、整数部の周期ΔTeは、

ΔTe=M−(N−2)=M−N+2・・・・・・・・・・・式(2)

と表される。このため、1つ前の値であるΔT=M−Nに対して「−2」の値になるので整数部の周波数差の変化量は「−2」となる。

【0051】

グリッチ発生期間検出回路2では、予め設定してあるグリッチ発生期間の開始値と終了値を基に、TDC出力信号Stdcoの値からグリッチ発生期間信号Sgctimを生成する。

【0052】

グリッチ補正回路3では、判定条件を満たしていればグリッチ補正処理を実行する(周波数差の変化量=誤差を打ち消す方向となる値を加算する)。全デジタル位相ロックループ90のグリッチ補正回路3では、例えば、定常状態であることから周波数差の変化量レベルが、

条件1:−0.75>周波数差の変化量

条件2:周波数差の変化量>+0.75

のどちらかを満たし、且つ、グリッチ発生期間検出回路2が生成するグリッチ発生期間信号Sgctimが、

条件3:グリッチ発生期間信号Sgctim=“L”(グリッチ発生期間外、ディセーブル状態)

を満たしたときに、メタスタビリティ起因のグリッチ発生による誤差と判定せず、グリッチ補正処理を実行しない。この場合、周波数差の変化量が「−2」であり、且つ、グリッチ発生期間信号Sgctim=“L”(ディセーブル状態)なので(条件2且つ条件3を満たしていないので)、整数部の周波数差には何も加算しない。

【0053】

なお、周波数差tm0〜tm1と周波数差tm1〜tm2とは等しい値でもよいし、異なる値でもよい。図8ではTDCp1は任意の値となっているが、ゼロでもよい。

【0054】

上述したように、本実施形態の全デジタル位相ロックループでは、デジタル周波数比較器1、グリッチ発生期間検出回路2、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6が設けられ、DCO出力信号Sckvがデジタル周波数比較器1に帰還入力される。デジタル周波数比較器1、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6は閉ループ状に接続される。デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。整数部周波数差生成回路11には、カウンタ21、リタイミングクロック生成回路22、フリップフロップ23、及び周波数差発生回路24が設けられる。小数部周波数差生成回路12には、TDC31、周期正規化回路32、及び周波数差発生回路33が設けられる。グリッチ発生期間検出回路2は、TDC出力信号Stdcoが入力され、グリッチ発生期間信号Sgctimを生成する。グリッチ補正回路3は、加算器13から出力される周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、グリッチ発生期間信号Sgctimがイネーブル状態のとき、周波数差信号Sfdifに含まれるグリッチノイズを低減処理する。グリッチ補正回路3は、グリッチ発生期間信号Sgctimがディセーブル状態のとき、グリッチノイズ補正処理を実行しない。

【0055】

このため、グリッチノイズが発生した場合、グリッチノイズを大幅に低減化することができる。メタスタビリティ等に起因しない外乱などの周波数差の変化(誤差)が発生した場合、この周波数差の変化(誤差)をDCO6に正しく伝達し、その誤差を元に戻すことができるため、全デジタル位相ロックループ90では、精度の高い発振周波数信号を生成することができる。

【0056】

なお、本実施形態例では、累積器4をグリッチ補正回路3とループフィルタ5の間に設け、累積器4を独立した回路としているが機能上1つのデジタルフィルタとしてループフィルタ5に含めてもよい。

【0057】

(第2の実施形態)

次に、本発明の第2の実施形態に係る全デジタル位相ロックループについて、図面を参照して説明する。図9は全デジタル位相ロックループを示すブロック図である。図10はグリッチ補正回路を示すブロック図である。本実施形態では、デジタル周波数比較器の出力側にグリッチノイズを低減するグリッチ補正回路を設け、周波数差の変化を正しくDCOに伝達するためにグリッチ発生期間検出回路を設けている。

【0058】

以下、第1の実施形態と同一構成部分には、同一符号を付してその部分の説明を省略し、異なる部分のみ説明する。

【0059】

図9に示すように、全デジタル位相ロックループ91には、デジタル周波数比較器1、グリッチ発生期間検出回路2a、グリッチ補正回路3a、累積器4、ループフィルタ5、及びDCO6が設けられる。デジタル周波数比較器1、グリッチ補正回路3a、累積器4、ループフィルタ5、及びDCO6は、閉ループ状に接続され、DCO出力信号Sckvがデジタル周波数比較器1に帰還入力される。全デジタル位相ロックループ91は、周波数差の変化が正しくDCO6に伝達され、且つグリッチノイズが低減され、精度のよい発振周波数信号を生成する。

【0060】

グリッチ発生期間検出回路2aは、グリッチ補正回路3aから出力される検出信号Sfq1detとTDC出力信号Stdcoが入力される。グリッチ発生期間検出回路2aは、周波数差「1」の検出信号Sfq1detに基づいて、TDC出力信号Stdcoの値に応じて発生頻度を計測して所定の発生頻度を満たしたTDC出力信号Stdcoを、グリッチ発生期間信号Sgctimを生成するTDC遷移値として採用する。グリッチ発生期間検出回路2aは、グリッチ補正回路3aから出力される周波数差「1」の検出信号Sfq1detに基づいて、そのときのTDC出力信号Stdcoの値を保持し、同じ値のTDC出力信号Stdcoの発生頻度を計測する。グリッチ発生期間検出回路2aは、同じ値のTDC出力信号Stdcoの発生頻度に基づいて、グリッチ発生期間信号Sgctimを生成してグリッチ補正回路3aに出力する。

【0061】

グリッチ補正回路3aは、デジタル周波数比較器1及びグリッチ発生期間検出回路2aと累積器4の間に設けられ、周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力される。グリッチ補正回路3aは、全デジタル位相ロックループ91が所定の周波数にロックされている定常状態、即ち許容されるジッタ分しか周波数誤差が発生していない状態では、周波数差「1」を検出し、周波数差「1」の検出信号Sfq1detをグリッチ発生期間検出回路2aに出力する。グリッチ補正回路3aは、グリッチ発生期間検出回路2aで生成されたグリッチ発生期間信号Sgctimに基づいて、グリッチ発生期間において発生した周波数差をグリッチノイズ起因の誤差と判定し、周波数差を補正する。

【0062】

図10に示すように、グリッチ補正回路3aには、フリップフロップ41、加算器42、変化量検出回路43a、所定値選択回路44、加算器45、及び基準値発生回路46が設けられる。フリップフロップ41、加算器42、変化量検出回路43a、所定値選択回路44、加算器45、及び基準値発生回路46は、閉ループ状に接続され、グリッチ補正済み周波数差信号Sfdifgcがフリップフロップ41に帰還入力される。

【0063】

変化量検出回路43aは、加算器42及び基準値発生回路46と所定値選択回路44の間に設けられ、出力信号S12、基準値En1乃至3が入力される。変化量検出回路43aは、周波数差「1」を検出し、周波数差「1」の検出信号Sfq1detをグリッチ発生期間検出回路2aに出力する。変化量検出回路43aは、周波数差信号Sfdifから現在の周波数差との差である周波数差の変化量のレベルが、所定の条件を満たしたときにグリッチノイズ起因と判定する。

【0064】

所定値選択回路44は、変化量検出回路43aと加算器45の間に設けられ、グリッチ発生期間信号Sgctim、出力信号S13a乃至cが入力される。所定値選択回路44は、グリッチ期間検出回路2が生成するグリッチ発生期間に、周波数差の変化量のレベルを満たした条件により、周波数差の変化量を相殺するように所定の値を周波数差の整数部に加算する(周波数差の補正処理)。

【0065】

次に、全デジタル位相ロックループ91の周波数検出動作について図11乃至14を参照して説明する。図11は全デジタル位相ロックループ91のメタスタビリティが発生したときの周波数検出を示す図である。図12は図11の拡大図である。

【0066】

図11及び図12に示すように、基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)とDCO出力信号Sckvの立ち上がりが略同時刻の場合について説明する。本来、DCO出力信号Sckvの期間C2での周波数差tn5におけるDCO出力信号Sckvの立ち上がり(Sckv計測クロック)で出力信号Sckrが生成される。ところが、メタスタビリティの影響により周波数差trにおける基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)により、DCO出力信号Sckvの期間C1での周波数差tn1におけるDCO出力信号Sckvの立ち上がり(Sckv計測クロック)で出力信号Sckrが生成される。

【0067】

定常的な状態では、第11図に示すようにメタスタビリティの発生により、DCO出力信号Sckvの計測値がN−1となるので整数部の周期ΔTm1は

ΔTm1=M−(N−1)=M−N+1・・・・・・・・・(式3)

と表される。このため、1つ前の値であるΔT=M−Nに対して「+1」の値になるので、整数部の周波数差の変化量は「+1」となる。

【0068】

グリッチ発生期間検出回路2aは、グリッチ補正回路3aの変化量検出回路43aが生成する周波数差「1」の検出信号Sfq1detに基づいて、所定の周波数差が発生したTDC出力信号Stdcoの値の発生頻度を計測する。計測したTDC出力信号Stdcoの値が所定の予め設定された条件を満たす場合、このTDC出力信号Stdcoの値をグリッチ発生期間の開始値または終了値とし、グリッチ発生期間信号Sgctimを生成する。

【0069】

グリッチ補正回路3aは、判定条件を満たしていれば補正を行う(周波数差の変化量=誤差を打ち消す方向となる値を加算する)。全デジタル位相ロックループ91のグリッチ補正回路3aでは、例えば、定常状態であることから周波数差の変化量レベルが、

条件1:−0.75>周波数差の変化量

条件2:周波数差の変化量>+0.75

のどちらかを満たし、且つ、グリッチ発生期間検出回路2aが生成するグリッチ発生期間信号Sgctimが、

条件3:グリッチ発生期間信号Sgctim=“H”(グリッチ発生期間内、イネーブル状態)

を満たしたときに、メタスタビリティ起因のグリッチ発生による誤差と判定し、グリッチ補正処理を実行する。この場合、周波数差の変化量が「+1」であり、且つ、グリッチ発生期間信号Sgctim=“H”(イネーブル状態)なので(条件2且つ条件3を満たしているので)、整数部の周波数差に「−1」を加算する。

【0070】

次に、グリッチ発生期間を拡大した図12を用いて更に動作を説明する。まず、外部制御装置によりグリッチ発生期間の開始とするTDC出力TDCq0とグリッチ発生期間終了とするTDC出力TDCq2の値をそれぞれ設定する。TDC31の出力がTDCq0となる周波数差をtn0とし、TDCの出力がTDCq2となる周波数差をtn2とする。

【0071】

グリッチ補正回路3aの変化量検出回路43aは周波数差「1」を検出し、グリッチ発生期間検出回路2aに周波数差「1」の検出信号Sfq1detを出力する。

【0072】

グリッチ発生期間検出回路2aは、周波数差「1」の検出信号Sfq1detに基づき、そのときのTDCの出力値(TDCq3)を保持すると共に、TDCq3の発生回数を計測する。周波数差が最大となるTDC値をTDCq1aとすると、TDC出力TDCq3が、

TDCq3<TDCq1a・・・・・・・・・・・・・・式(4)

を満たし、且つ、TDCq3がM回(Mは1以上の整数)発生した場合、TDCq3からTDCq2をグリッチ発生期間(TDCq3をグリッチ期間の開始)とする。なお、検出回数Mは別途外部より制御する。

【0073】

ここでは、グリッチ期間の開始点(TDCq3)について1つだけの値を保持し計測しているが、複数の値を保持し、計測してもよい。また、グリッチ期間の開始点について計測・学習のみ説明しているが、グリッチ期間の終了点についても同様に計測・学習してもよい。図12ではTDCq1は任意の値となっているが、ゼロでもよい。また、tn3=trとしているが、tn3=tr−αでもよい。但しαは、tn3がDCO出力信号Sckvの1周期を超えない任意の値とする。

【0074】

グリッチ補正回路3aは、グリッチ発生期間信号Sgctimが“H”(イネーブル状態)期間で、且つ、周波数差の変化量が「1」の場合、グリッチノイズが発生したと判定してグリッチ補正処理を実行する。グリッチ補正回路3aは、グリッチ発生期間信号Sgctimが“L”(ディセーブル状態)期間の場合、周波数差の変化量が「1」となってもグリッチノイズが発生したとは判定せずにグリッチ補正処理を実行しない。

【0075】

次に、別のメタスタビリティが発生した場合について図13及び図14を参照して説明する。図13は別のメタスタビリティが発生したときの周波数検出を示す図である。図14は図13の拡大図である。

【0076】

図13及び図14は、周波数誤差が発生した場合について示している。具体的には、基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)とDCO出力信号Sckvの立ち上がりエッジが略同時刻の場合である。本来、DCO出力信号Sckvの期間C2での周波数差tn1におけるDCO出力信号Sckvの立ち上がりで出力信号Sckrは生成される。ところが、出力信号Sckrはメタスタビリティの影響で周波数差trの基準周波数クロック信号Sfrefの遷移(“L”から“H”への立ち上がり)により、DCO出力信号Sckvの期間C3での周波数差tn5におけるDCO出力信号Sckvの立ち上がりで生成される。

【0077】

定常的な状態では、図13に示すようにメタスタビリティの発生により、DCO出力信号Sckvの計測値がN+1となるので整数部の周期ΔTm2は、

ΔTm2=M−(N+1)=M−N−1・・・・・・・・・式(5)

と表される。このため、1つ前の値であるΔT=M−Nに対して「−1」の値になるので、整数部の周波数差の変化量は「−1」となる。

【0078】

グリッチ発生期間検出回路2aは、グリッチ補正回路3aの変化量検出回路43aが生成する周波数差「1」の検出信号Sfq1detに基づいて、所定の周波数差が発生したTDC出力信号Stdcoの発生頻度を計測する。計測したTDC出力信号Stdcoの値が所定の予め設定された条件を満たす場合、このTDC出力信号Stdcoの値をグリッチ発生期間の開始値または終了値とし、グリッチ発生期間信号Sgctimを生成する。

【0079】

グリッチ補正回路3aは、判定条件を満たしていれば補正を行う(周波数差の変化量=誤差を打ち消す方向となる値を加算する)。全デジタル位相ロックループ91のグリッチ補正回路3aでは、例えば、定常状態であることから周波数差の変化量レベルが、

条件1:−0.75>周波数差の変化量

条件2:周波数差の変化量>+0.75

のどちらかを満たし、且つ、グリッチ発生期間検出回路2aが生成するグリッチ発生期間信号Sgctimが、

条件3:グリッチ発生期間信号Sgctim=“H”(グリッチ発生期間内、イネーブル状態)

を満たしたときに、メタスタビリティ起因によるグリッチノイズの発生による誤差と判定し、グリッチ補正処理を実行する。この場合、周波数差の変化量が「−1」であり、かつ、グリッチ発生期間信号Sgctim=“H”(イネーブル状態)なので(条件1且つ条件3を満たしているので)、整数部の周波数差に「+1」を加算する。

【0080】

グリッチ発生期間を拡大した図14を用いて更に動作を説明する。まず、外部制御装置によりグリッチ発生期間の開始とするTDC出力TDCq0とグリッチ発生期間終了とするTDC出力TDCq2の値をそれぞれ設定する。TDCの出力がTDCq0となる周波数差をtn0とし、TDCの出力がTDCq2となる周波数差をtn2とする。

【0081】

グリッチ補正回路3aの変化量検出回路43aは周波数差「1」を検出し、グリッチ発生期間検出回路2aに周波数差「1」の検出信号Sfq1detを出力する。グリッチ発生期間検出回路2aは、周波数差「1」の検出信号Sfq1detに基づいて、そのときのTDCの出力値(TDCq4)を保持すると共に、TDCq4の発生回数を計測する。TDCq4が、

TDCq1<TDCq4・・・・・・・・・・・・・・・式(6)

を満たし、且つ、TDCq4がN回(Nは1以上の整数)発生した場合、TDCq0からTDCq4をグリッチ発生期間(TDCq4をグリッチ期間の終了)とする。なお、検出回数Nは別途外部より制御する。

【0082】

ここでは、グリッチ期間の終了点(TDCq4)について1つだけの値を保持し計測しているが、複数の値を保持し、計測してもよい。また、グリッチ期間の終了点について計測・学習のみ説明しているが、グリッチ期間の開始点についても同様に計測・学習してもよい。図14ではTDCq1は任意の値となっているが、ゼロでもよい。また、tn4=trとしているが、tn4=tr−βでもよい。但しβは、tn4がDCO出力信号Sckvの1周期を超えない任意の値である。

【0083】

グリッチ補正回路3aは、グリッチ発生期間信号Sgctimが“H”(イネーブル状態)期間で、且つ、周波数差の変化量が「1」の場合、グリッチノイズが発生したと判定してグリッチ補正処理を実行する。また、グリッチ補正回路3aは、グリッチ発生期間信号Sgctimが“L”(ディセーブル状態)期間の場合、周波数差の変化量が「1」となってもグリッチノイズが発生した判定せずにグリッチ補正処理を実行しない。

【0084】

上述したように、本実施形態の全デジタル位相ロックループでは、デジタル周波数比較器1、グリッチ発生期間検出回路2a、グリッチ補正回路3a、累積器4、ループフィルタ5、及びDCO6が設けられ、DCO出力信号Sckvがデジタル周波数比較器1に帰還入力される。デジタル周波数比較器1、グリッチ補正回路3a、累積器4、ループフィルタ5、及びDCO6は閉ループ状に接続される。デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。整数部周波数差生成回路11には、カウンタ21、リタイミングクロック生成回路22、フリップフロップ23、及び周波数差発生回路24が設けられる。小数部周波数差生成回路12には、TDC31、周期正規化回路32、及び周波数差発生回路33が設けられる。グリッチ発生期間検出回路2aは、TDC出力信号Stdco及びグリッチ補正回路3aから出力される周波数差「1」の検出信号Sfq1detが入力され、周波数差「1」の検出信号Sfq1detに基づいて、そのときのTDC出力信号Stdcoの値を保持し、同じ値のTDC出力信号Stdcoの発生頻度を計測し、同じ値のTDC出力信号Stdcoの発生頻度に基づいて、グリッチ発生期間信号Sgctimを生成する。グリッチ補正回路3aは、加算器13から出力される周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、所定の周波数にロックされている定常状態では、周波数差「1」を検出して周波数差「1」の検出信号Sfq1detを生成し、グリッチ発生期間信号Sgctimがイネーブル状態のとき、周波数差信号Sfdifに含まれるグリッチノイズを低減処理する。グリッチ補正回路3aは、グリッチ発生期間信号Sgctimがディセーブル状態のとき、グリッチノイズ補正処理を実行しない。

【0085】

このため、グリッチ発生期間を計測・学習することで経時変化などによるグリッチ発生期間の変化に対応できる。この結果、グリッチノイズが発生した場合、グリッチ補正回路3aはグリッチノイズを大幅に低減化することができる。グリッチ補正回路3aは、メタスタビリティに起因しない周波数差の変化(誤差)が発生した場合、この周波数差の変化をDCO6に正しく伝達し、その誤差を元に戻すことができるため、全デジタル位相ロックループ91では、安定して精度の高い発振周波数信号を生成できる。

【0086】

本発明は、上記実施形態に限定されるものではなく、発明の趣旨を逸脱しない範囲で、種々、変更してもよい。

【0087】

実施形態では、FCW信号Sfcwを直接加算器13に入力しているが、加算器13の前段にカウンタを設け、このカウンタがリタイミングクロック生成回路22の出力信号Sckrに基づいてFCW信号をカウントし、カウントされたFCW信号を参照信号入力として加算器13に入力させてもよい。また、TDC31を構成する所定時間遅延させるインバータの遅延量は周囲温度や電圧変動の影響を受けるので、例えばTDC31に自己校正機能を付加して周囲温度や電圧変動の影響をキャンセルするのが好ましい。

【0088】

本発明は、以下の付記に記載されているような構成が考えられる。

(付記1) 基準周波数クロック信号及びDCO出力信号が入力され、整数部周波数信号を生成する整数部周波数差生成回路と、前記基準周波数クロック信号及び前記DCO出力信号が入力され、前記基準周波数クロック信号に基づいて、前記DCO出力信号を計測するTDCが設けられ、小数部周波数信号を生成する小数部周波数差生成回路と、FCW信号、前記整数部周波数信号、及び前記小数部周波数信号が入力され、前記FCW信号から前記整数部周波数信号及び前記小数部周波数信号を減算処理して周波数差信号を生成する加算器とを有するデジタル周波数比較器と、前記TDCから出力されるTDC出力信号が入力され、グリッチ発生期間信号を生成するグリッチ発生期間検出回路と、前記周波数差信号及び前記グリッチ発生期間信号が入力され、前記グリッチ発生期間信号がイネーブル状態のときに、前記周波数差信号に含まれるグリッチノイズを低減処理してグリッチ補正済み周波数差信号を生成するグリッチ補正回路と、前記グリッチ補正済み周波数差信号が入力され、前記グリッチ補正済み周波数差信号を累積処理する累積器と、累積処理された前記グリッチ補正済み周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号を生成するループフィルタと、

前記周波数制御信号に応じた前記DCO出力信号を生成し、前記DCO出力信号を発振周波数信号として出力し、前記DCO出力信号を前記デジタル周波数比較器に帰還入力するDCOとを具備し、前記デジタル周波数比較器、前記グリッチ補正回路、前記累積器、前記ループフィルタ、及び前記DCOは閉ループ状に接続される全デジタル位相ロックループ。

【0089】

(付記2) 前記グリッチ補正回路は、許容されるジッタ以上の周波数差の変化が発生した場合、前記グリッチ発生期間信号がグリッチ発生期間内のとき、前記周波数差の変化をメタスタビリティに起因するグリッチノイズと判定して前記周波数差の変化を補正する付記1に記載の全デジタル位相ロックループ。

【0090】

(付記3) 前記整数部周波数差生成回路は、前記DCO出力信号をカウントするカウンタと、前記FCW信号及び前記DCO出力信号が入力され、前記DCO出力信号に基づいて、リタイミングされたクロック信号を生成するリタイミングクロック生成回路と、前記カウンタの出力信号が入力され、前記リタイミングクロック生成回路の出力信号に基づいて、前記カウンタの出力信号をデータラッチするフリップフロップと、前記フリップフロップの出力信号が入力され、前記DCO出力信号の周波数が前記基準周波数クロック信号の周波数の何倍の整数値に相当するかの計測を行う周波数差発生回路とを有する付記1或いは2に記載の全デジタル位相ロックループ。

【符号の説明】

【0091】

1 デジタル周波数比較器

2、2a デジタル発生期間検出回路

3、3a グリッチ補正回路

4 累積器

5 ループフィルタ

6 DCO

11 整数部周波数差生成回路

12、12a 少数部周波数差生成回路

13、42、45 加算器

21 カウンタ

22 リタイミングクロック生成回路

23、41 フリップフロップ

24、33 周波数差発生回路

31、31a TDC出力信号

32 周期正規化回路

43、43a 変化量検出回路

44 所定値選択回路

46 基準値発生回路

90、91、100 全デジタル位相ロックループ

Sao、Sckr、Scnt、Sffo、Sfso、S11、S12、S13a〜c、S14 出力信号

Sckv DCO出力信号

Sdtf 立ち下がり計測信号

Sdtr 立ち上がり計測信号

Sfcw FCW信号

Sfdif 周波数差信号

Sfdifgc グリッチ補正済み周波数差信号

Sffra 少数部周波数信号

Sfint 整数部周波数信号

Sfq1det 検出信号

Sfref 基準周波数クロック信号

Sgctim グリッチ発生期間信号

Slfo 周波数制御信号

Stdco TDC出力信号

TDCp0 tm0におけるTDC出力

TDCp1 tm1におけるTDC出力

TDCp2 tm2におけるTDC出力

TDCq0 tn0におけるTDC出力

TDCq1 tn1におけるTDC出力

TDCq1a 周波数差が最大となるTDC出力

TDCq2 tn2におけるTDC出力

TDCq3 tn3におけるTDC出力

TDCq4 tn4におけるTDC出力

Tglc グリッチ発生期間(tn0〜tn2)

Tglc0 グリッチ発生期間(学習前初期値)

Tglc1 グリッチ発生期間(tn3〜tn2)

Tglc2 グリッチ発生期間(tn0〜tn4)

tm0 グリッチ発生期間(開始)

tm1、tm3 Sckv立ち上がりエッジ(Sckv計測クロック)

tm2 グリッチ発生期間(終了)

tn0 グリッチ発生期間(開始初期値)

tn1、tn5 Sckv立ち上がりエッジ(Sckv計測クロック)

tn2 グリッチ発生期間(終了初期値)

tn3 グリッチ発生期間(開始学習値)

tn4 グリッチ発生期間(終了学習値)

tr Sfref立ち上がりエッジ

【特許請求の範囲】

【請求項1】

基準周波数クロック信号及びDCO出力信号が入力され、整数部周波数信号を生成する整数部周波数差生成回路と、前記基準周波数クロック信号及び前記DCO出力信号が入力され、前記基準周波数クロック信号に基づいて、前記DCO出力信号を計測するTDCが設けられ、小数部周波数信号を生成する小数部周波数差生成回路と、FCW信号、前記整数部周波数信号、及び前記小数部周波数信号が入力され、前記FCW信号から前記整数部周波数信号及び前記小数部周波数信号を減算処理して周波数差信号を生成する加算器とを有するデジタル周波数比較器と、

前記TDCから出力されるTDC出力信号が入力され、グリッチ発生期間信号を生成するグリッチ発生期間検出回路と、

前記周波数差信号及び前記グリッチ発生期間信号が入力され、前記グリッチ発生期間信号がイネーブル状態のときに、前記周波数差信号に含まれるグリッチノイズを低減処理してグリッチ補正済み周波数差信号を生成するグリッチ補正回路と、

前記グリッチ補正済み周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号を生成するループフィルタと、

前記周波数制御信号に応じた前記DCO出力信号を生成し、前記DCO出力信号を発振周波数信号として出力し、前記DCO出力信号を前記デジタル周波数比較器に帰還入力するDCOと、

を具備し、前記デジタル周波数比較器、前記グリッチ補正回路、前記ループフィルタ、及び前記DCOは閉ループ状に接続されることを特徴とする全デジタル位相ロックループ。

【請求項2】

前記グリッチ補正回路は、

前記グリッチ補正済み周波数差信号が入力され、前記基準周波数クロック信号に基づいて、前記グリッチ補正済み周波数差信号をデータラッチするフリップフロップと、

前記周波数差信号及び前記フリップフロップの出力信号が入力され、前記周波数差信号から前記フリップフロップの出力信号を減算処理する第1の加算器と、

前記第1の加算器の出力信号が入力され、基準値を用いて変化量を検出する変化量検出回路と、

変化量検出回路の出力信号及び前記グリッチ発生期間信号が入力され、所定値を用いて周波数差を補正処理する所定値選択回路と、

前記周波数差信号及び前記所定値選択回路の出力信号が入力され、前記周波数差信号と前記所定値選択回路の出力信号を加算処理して前記グリッチ補正済み周波数差信号を生成し、前記グリッチ補正済み周波数差信号を前記フリップフロップに帰還入力する第2の加算器と、

を具備し、前記フリップフロップ、前記第1の加算器、前記変化量検出回路、前記所定値選択回路、及び第2の加算器が閉ループ状に接続されることを特徴とする請求項1に記載の全デジタル位相ロックループ。

【請求項3】

基準周波数クロック信号及びDCO出力信号が入力され、整数部周波数信号を生成する整数部周波数差生成回路と、前記基準周波数クロック信号及び前記DCO出力信号が入力され、前記基準周波数クロック信号に基づいて、前記DCO出力信号を計測するTDCが設けられ、小数部周波数信号を生成する小数部周波数差生成回路と、FCW信号、前記整数部周波数信号、及び前記小数部周波数信号が入力され、前記FCW信号から前記整数部周波数信号及び前記小数部周波数信号を減算処理して周波数差信号を生成する加算器とを有するデジタル周波数比較器と、

前記TDCから出力されるTDC出力信号及び周波数差「1」の検出信号が入力され、前記周波数差「1」の検出信号に基づいて、そのときの前記TDC出力信号の値を保持し、同じ値のTDC出力信号の発生頻度を計測し、同じ値のTDC出力信号の発生頻度に基づいて、グリッチ発生期間信号を生成するグリッチ発生期間検出回路と、

前記周波数差信号及び前記グリッチ発生期間信号が入力され、所定の周波数にロックされている定常状態では、周波数差「1」を検出し、前記周波数差「1」の検出信号を前記グリッチ発生期間検出回路に出力し、グリッチ発生期間信号がイネーブル状態のときに、前記周波数差信号に含まれるグリッチノイズを低減処理してグリッチ補正済み周波数差信号を生成するグリッチ補正回路と、

前記グリッチ補正済み周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号を生成するループフィルタと、

前記周波数制御信号に応じた前記DCO出力信号を生成し、前記DCO出力信号を発振周波数信号として出力し、前記DCO出力信号を前記デジタル周波数比較器に帰還入力するDCOと、

を具備し、前記デジタル周波数比較器、前記グリッチ補正回路、前記ループフィルタ、及び前記DCOは閉ループ状に接続されることを特徴とする全デジタル位相ロックループ。

【請求項4】

前記グリッチ補正回路は、

前記グリッチ補正済み周波数差信号が入力され、前記基準周波数クロック信号に基づいて、前記グリッチ補正済み周波数差信号をデータラッチするフリップフロップと、

前記周波数差信号及び前記フリップフロップの出力信号が入力され、前記周波数差信号から前記フリップフロップの出力信号を減算処理する第1の加算器と、

前記第1の加算器の出力信号が入力され、基準値を用いて変化量を検出し、前記周波数差「1」の検出信号を生成する変化量検出回路と、

変化量検出回路の出力信号及び前記グリッチ発生期間信号が入力され、所定値を用いて周波数差を補正処理する所定値選択回路と、

前記周波数差信号及び前記所定値選択回路の出力信号が入力され、前記周波数差信号と前記所定値選択回路の出力信号を加算処理して前記グリッチ補正済み周波数差信号を生成し、前記グリッチ補正済み周波数差信号を前記フリップフロップに帰還入力する第2の加算器と、

を具備し、前記フリップフロップ、前記第1の加算器、前記変化量検出回路、前記所定値選択回路、及び第2の加算器が閉ループ状に接続されることを特徴とする請求項3に記載の全デジタル位相ロックループ。

【請求項5】

前記グリッチ補正回路と前記ループフィルタの間に累積器が設けられ、前記累積器はグリッチ補正済み周波数差信号を累積処理することを特徴とする請求項1乃至4のいずれか1項に記載の全デジタル位相ロックループ。

【請求項1】

基準周波数クロック信号及びDCO出力信号が入力され、整数部周波数信号を生成する整数部周波数差生成回路と、前記基準周波数クロック信号及び前記DCO出力信号が入力され、前記基準周波数クロック信号に基づいて、前記DCO出力信号を計測するTDCが設けられ、小数部周波数信号を生成する小数部周波数差生成回路と、FCW信号、前記整数部周波数信号、及び前記小数部周波数信号が入力され、前記FCW信号から前記整数部周波数信号及び前記小数部周波数信号を減算処理して周波数差信号を生成する加算器とを有するデジタル周波数比較器と、

前記TDCから出力されるTDC出力信号が入力され、グリッチ発生期間信号を生成するグリッチ発生期間検出回路と、

前記周波数差信号及び前記グリッチ発生期間信号が入力され、前記グリッチ発生期間信号がイネーブル状態のときに、前記周波数差信号に含まれるグリッチノイズを低減処理してグリッチ補正済み周波数差信号を生成するグリッチ補正回路と、

前記グリッチ補正済み周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号を生成するループフィルタと、

前記周波数制御信号に応じた前記DCO出力信号を生成し、前記DCO出力信号を発振周波数信号として出力し、前記DCO出力信号を前記デジタル周波数比較器に帰還入力するDCOと、

を具備し、前記デジタル周波数比較器、前記グリッチ補正回路、前記ループフィルタ、及び前記DCOは閉ループ状に接続されることを特徴とする全デジタル位相ロックループ。

【請求項2】

前記グリッチ補正回路は、

前記グリッチ補正済み周波数差信号が入力され、前記基準周波数クロック信号に基づいて、前記グリッチ補正済み周波数差信号をデータラッチするフリップフロップと、

前記周波数差信号及び前記フリップフロップの出力信号が入力され、前記周波数差信号から前記フリップフロップの出力信号を減算処理する第1の加算器と、

前記第1の加算器の出力信号が入力され、基準値を用いて変化量を検出する変化量検出回路と、

変化量検出回路の出力信号及び前記グリッチ発生期間信号が入力され、所定値を用いて周波数差を補正処理する所定値選択回路と、

前記周波数差信号及び前記所定値選択回路の出力信号が入力され、前記周波数差信号と前記所定値選択回路の出力信号を加算処理して前記グリッチ補正済み周波数差信号を生成し、前記グリッチ補正済み周波数差信号を前記フリップフロップに帰還入力する第2の加算器と、

を具備し、前記フリップフロップ、前記第1の加算器、前記変化量検出回路、前記所定値選択回路、及び第2の加算器が閉ループ状に接続されることを特徴とする請求項1に記載の全デジタル位相ロックループ。

【請求項3】

基準周波数クロック信号及びDCO出力信号が入力され、整数部周波数信号を生成する整数部周波数差生成回路と、前記基準周波数クロック信号及び前記DCO出力信号が入力され、前記基準周波数クロック信号に基づいて、前記DCO出力信号を計測するTDCが設けられ、小数部周波数信号を生成する小数部周波数差生成回路と、FCW信号、前記整数部周波数信号、及び前記小数部周波数信号が入力され、前記FCW信号から前記整数部周波数信号及び前記小数部周波数信号を減算処理して周波数差信号を生成する加算器とを有するデジタル周波数比較器と、

前記TDCから出力されるTDC出力信号及び周波数差「1」の検出信号が入力され、前記周波数差「1」の検出信号に基づいて、そのときの前記TDC出力信号の値を保持し、同じ値のTDC出力信号の発生頻度を計測し、同じ値のTDC出力信号の発生頻度に基づいて、グリッチ発生期間信号を生成するグリッチ発生期間検出回路と、

前記周波数差信号及び前記グリッチ発生期間信号が入力され、所定の周波数にロックされている定常状態では、周波数差「1」を検出し、前記周波数差「1」の検出信号を前記グリッチ発生期間検出回路に出力し、グリッチ発生期間信号がイネーブル状態のときに、前記周波数差信号に含まれるグリッチノイズを低減処理してグリッチ補正済み周波数差信号を生成するグリッチ補正回路と、

前記グリッチ補正済み周波数差信号の不要な周波数帯域成分を除去し、デジタル値である周波数制御信号を生成するループフィルタと、

前記周波数制御信号に応じた前記DCO出力信号を生成し、前記DCO出力信号を発振周波数信号として出力し、前記DCO出力信号を前記デジタル周波数比較器に帰還入力するDCOと、

を具備し、前記デジタル周波数比較器、前記グリッチ補正回路、前記ループフィルタ、及び前記DCOは閉ループ状に接続されることを特徴とする全デジタル位相ロックループ。

【請求項4】

前記グリッチ補正回路は、

前記グリッチ補正済み周波数差信号が入力され、前記基準周波数クロック信号に基づいて、前記グリッチ補正済み周波数差信号をデータラッチするフリップフロップと、

前記周波数差信号及び前記フリップフロップの出力信号が入力され、前記周波数差信号から前記フリップフロップの出力信号を減算処理する第1の加算器と、

前記第1の加算器の出力信号が入力され、基準値を用いて変化量を検出し、前記周波数差「1」の検出信号を生成する変化量検出回路と、

変化量検出回路の出力信号及び前記グリッチ発生期間信号が入力され、所定値を用いて周波数差を補正処理する所定値選択回路と、

前記周波数差信号及び前記所定値選択回路の出力信号が入力され、前記周波数差信号と前記所定値選択回路の出力信号を加算処理して前記グリッチ補正済み周波数差信号を生成し、前記グリッチ補正済み周波数差信号を前記フリップフロップに帰還入力する第2の加算器と、

を具備し、前記フリップフロップ、前記第1の加算器、前記変化量検出回路、前記所定値選択回路、及び第2の加算器が閉ループ状に接続されることを特徴とする請求項3に記載の全デジタル位相ロックループ。

【請求項5】

前記グリッチ補正回路と前記ループフィルタの間に累積器が設けられ、前記累積器はグリッチ補正済み周波数差信号を累積処理することを特徴とする請求項1乃至4のいずれか1項に記載の全デジタル位相ロックループ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−23646(P2012−23646A)

【公開日】平成24年2月2日(2012.2.2)

【国際特許分類】

【出願番号】特願2010−161157(P2010−161157)

【出願日】平成22年7月16日(2010.7.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年2月2日(2012.2.2)

【国際特許分類】

【出願日】平成22年7月16日(2010.7.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]