全波整流回路

【課題】コンデンサインプット型全波整流回路をnチャンネルMOSFETのみで実現する。

【解決手段】抵抗101は、MOSFET22,24のソース側に接続され、MOSFET22,24を流れる電流を検知する電流検知回路を構成し、電流値に対応した電圧をコンパレータ104の反転入力端子に出力する。コンパレータ104は、抵抗102,103の所定の分圧比により設定される所定の閾値となる電圧と、抵抗101の電圧とを比較し、抵抗101の電圧が所定の閾値よりも小さくなり、抵抗101を流れる電流が所定の閾値よりも小さくなったとみなされた場合、トランジスタ105,106をオンさせて、MOSFET22,24をオフに制御することにより、平滑コンデンサ81による電流の逆流を防止する。本技術は、コンデンサインプット型全波整流回路に適用することができる。

【解決手段】抵抗101は、MOSFET22,24のソース側に接続され、MOSFET22,24を流れる電流を検知する電流検知回路を構成し、電流値に対応した電圧をコンパレータ104の反転入力端子に出力する。コンパレータ104は、抵抗102,103の所定の分圧比により設定される所定の閾値となる電圧と、抵抗101の電圧とを比較し、抵抗101の電圧が所定の閾値よりも小さくなり、抵抗101を流れる電流が所定の閾値よりも小さくなったとみなされた場合、トランジスタ105,106をオンさせて、MOSFET22,24をオフに制御することにより、平滑コンデンサ81による電流の逆流を防止する。本技術は、コンデンサインプット型全波整流回路に適用することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は、全波整流回路に関し、特に、電力損失を低減すると共に、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)を保護することにより動作の安定性を向上させるようにした全波整流回路に関する。

【背景技術】

【0002】

従来より、スイッチング電源装置を小型化、軽量化、および高効率化するために、スイッチング電源装置の電力損失を低減することが重要な課題となっていた。特に、スイッチング電源装置に設けられ、交流電圧を全波整流する全波整流回路は電力損失が大きく、全波整流回路の損失の低減は重要な課題となっている。

【0003】

この課題に対応すべく、入力電源より、出力側へ流れる電流をPch-MOSFET(pチャンネルMOSFET)で整流し、負荷側から入力電源に帰還する電流はNch-MOSFET(nチャンネルMOSFET)よりで整流し、全波同期整流を実現している(特許文献1参照)。

【0004】

また、使用するMOSFET全てをPch型のものよりもオン抵抗の小さなNch型のものとすることにより、電力損失を低減させるようにするものが提案されている(特許文献2参照)。

【0005】

しかしながら、特許文献1の技術においては、Pch-MOSFETはNch-MOSFETよりもオン抵抗が大きく、Nch-MOSFETを用いる時よりもロスが大きくなってしまうおそれがある。また、コンパレータを4つ用いたとしても、コンパレータの同相入力の問題や、ゲート−ソース間の耐電圧を超えた電圧がMOSFETに印加される可能性があった。

【0006】

また、特許文献2の技術においては、Nch-MOSFETで構成されており、Pch-MOSFETを用いる時よりもロスは少なくなるが、回路構成では交流電源から出力側へ流れる電流を整流するMOSFETは入力位相が逆になってからオフする制御方法をとっているため貫通電流が流れる可能性があった。

【0007】

そこで、交流電源の位相が切り替わる前に、MOSFETをオフに制御することにより、4個のMOSFETをNch-MOSFETで構成できるようにする全波整流回路の技術が提案されている(特許文献3参照)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平9−131064号公報

【特許文献2】特開2005−295627号公報

【特許文献3】特開2010−178519号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献3の技術においては、負荷と並列にコンデンサを接続する、いわゆるコンデンサインプット型の全波整流回路を構成すると、貫通電流が流れる可能性があった。

【0010】

本技術はこのような状況に鑑みてなされたものであり、特に、コンデンサインプット型の全波整流回路であっても、主要構成部をNch-MOSFETのみで構成し、全波同期整流において、安価な回路構成で、かつ、確実に全波整流を実現できるようにするものである。

【課題を解決するための手段】

【0011】

本技術の一側面の全波整流回路は、交流電源から入力された交流電圧を全波整流する全波整流回路であって、内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第1の端子に接続された第1のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)と、内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第1の端子に接続された第2のMOSFETと、内部の寄生ダイオードにおけるカソードに対応する端子が前記第1のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第2の端子に接続された第3のMOSFETと、内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第2の端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記第2のMOSFETの内部の寄生ダイオードにおけるアノードに対応する端子に接続された第4のMOSFETと、前記交流電源の第1の端子に接続された交流電圧の位相を検知する第1の位相検知回路と、前記交流電源の第2の端子に接続された交流電圧の位相を検知する第2の位相検知回路と、前記第1の位相検知回路の検知結果に基づき、前記第1のMOSFETをオンする第1の制御回路と、前記第2の位相検知回路の検知結果に基づき、前記第3のMOSFETをオンする第2の制御回路と、前記第2および第4のMOSFETに流れる電流値を検知する電流検知回路と、前記電流検知回路の検知結果である電流値が所定値よりも小さくなった場合、前記第1乃至第4のMOSFETのうち、少なくとも1つをオフするように接続された強制遮断回路とを含む。

【0012】

前記第1および前記第3のMOSFETの内部寄生ダイオードのカソードに対応する端子と、前記第2および前記第4のMOSFETの内部寄生ダイオードのアノードに対応する端子との間の電圧によって得られる脈流電圧を平滑するように接続された平滑コンデンサをさらに含ませるようにすることができ、前記電流検知回路には、前記平滑コンデンサと、前記第2および前記第4のMOSFETとの間に電流を検出するための電流検出抵抗と、前記電流検出抵抗に流れる電流値が所定値よりも小さいか否かにより信号を出力するコンパレータとを含ませるようにすることができる。

【0013】

前記コンパレータの最低入力端子は、前記電流検出抵抗を介して前記第2および第4のMOSFETのソース、またはドレインと接続されるようにすることができる。

【0014】

前記強制遮断制御回路には、前記第2および第4のMOSFETの少なくとも1つをオフにする遮断制御回路を含ませるようにすることができる。

【0015】

前記遮断回路には、抵抗、およびトランジスタを含ませるようにすることができ、前記抵抗の一方の端部が前記コンパレータの出力端子に接続され、前記抵抗の他方の端部が前記トランジスタのベースに接続され、前記トランジスタのコレクタが、前記第2および第4のMOSFETのゲートの少なくともそのいずれかに接続されるようにすることができる。

【0016】

前記第1乃至第4のMOSFETは、nチャンネルMOSFETとすることができる。

【0017】

前記第1の制御回路には、前記交流電源の第1の端子の電圧よりも高い電圧を生成する第1のチャージポンプ回路を含ませるようにすることができ、前記第1の位相検知回路の検知結果に基づいて、フォトカプラによって前記第1のチャージポンプ回路より前記第1のMOSFETのゲートに電圧を印加するように接続され、前記第1の端子の電位が前記第2の端子の電位よりも低くならないうちに前記第1のMOSFETのゲートおよびソース間の電圧を所定値より小さくするように接続されるようにすることができる。

【0018】

前記第1のチャージポンプ回路には、第1のダイオードおよび第1のコンデンサを含ませるようにすることができ、前記第1のダイオードのアノードが前記第1のMOSFETの内部寄生ダイオードにおけるカソードに対応する端子、または前記交流電源の第2の端子に接続され、前記第1のダイオードのカソードと前記交流電源の第1の端子との間に第1のコンデンサが接続されるようにすることができる。

【0019】

前記第1のMOSFETのゲートおよびソース間に抵抗を含ませるようにすることができ、前記抵抗の抵抗値は、前記第1の位相検知回路の検知結果で得られるタイミングより、前記交流電源の第1の端子と第2の端子との間の電圧が正から負若しくは負から正に切り替わるタイミングに至るまでの期間内にゲートおよびソース間の電位を第1のMOSFETが確実にオフできる値とすることができる。

【0020】

前記第2の制御回路には、前記交流電源の第2の端子の電圧よりも高い電圧を生成する第2のチャージポンプ回路を含ませるようにすることができ、前記第2の位相検知回路の検知結果に基づいて、フォトカプラによって前記第2のチャージポンプ回路より前記第3のMOSFETのゲートに電圧を印加するように接続され、前記第2の端子の電位が前記第1の端子の電位よりも低くならないうちに前記第3のMOSFETのゲートおよびソース間の電圧を所定値より小さくするように接続されるようにすることができる。

【0021】

前記第2のチャージポンプ回路には、第2のダイオードおよび第2のコンデンサを含ませるようにすることができ、前記第2のダイオードのアノードが前記第3のMOSFETの内部寄生ダイオードにおけるカソードに対応する端子、または前記交流電源の第1の端子に接続され、前記第2のダイオードのカソードと前記交流電源の第2の端子との間に第2のコンデンサが接続されるようにすることができる。

【0022】

前記第3のMOSFETのゲートおよびソース間に抵抗を含ませるようにすることができ、前記抵抗の抵抗値は、前記第2の位相検知回路の検知結果で得られるタイミングより、前記交流電源の第1の端子と第2の端子との間の電圧が正から負若しくは負から正に切り替わるタイミングに至るまでの期間内にゲートおよびソース間の電位を第3のMOSFETが確実にオフできる値とすることができる。

【0023】

本技術の請求項1に記載の全波整流回路を含む電源システムは、力率改善回路と、全波整流された出力に直列接続されたインダクタと、前記インダクタの出力とグランドの間にドレインおよびソースが接続された第5のMOSFETと、前記インダクタの出力と直列に接続されたMOSFETの寄生ダイオードのアノードに対応する端子がインダクタの出力となるように接続された第6のMOSFETとを、請求項1に記載の全波整流回路にさらに含ませるようにすることができ、前記電流検知回路には、前記力率改善回路のグランドと第2および第4のMOSFETの寄生ダイオードにおけるアノードに対応する端子との間の電流値を検知させ、前記強制遮断回路には、前記交流電源の前記電流検知回路の検知結果に基づいて、前記力率改善回路の出力信号を制御して、前記電流値が所定値よりも小さい場合、少なくとも第1乃至第4および第6のMOSFETのうち、少なくとも1つをオフさせるようにすることができる。

【0024】

本技術の一側面の全波整流回路においては、交流電源から入力された交流電圧を全波整流する全波整流回路であって、第1のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)の内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第1の端子に接続され、第2のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第1の端子に接続され、第3のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子が前記第1のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第2の端子に接続され、第4のMOSFETが、内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第2の端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記第2のMOSFETの内部の寄生ダイオードにおけるアノードに対応する端子に接続され、第1の位相検知回路により、前記交流電源の第1の端子に接続された交流電圧の位相が検知され、第2の位相検知回路により、前記交流電源の第2の端子に接続された交流電圧の位相が検知され、第1の制御回路により、前記第1の位相検知回路の検知結果に基づき、前記第1のnチャンネルMOSFETがオンされ、第2の制御回路により、前記第2の位相検知回路の検知結果に基づき、前記第3のnチャンネルMOSFETがオンされ、電流検知回路により、前記第2および第4のMOSFETに流れる電流値が検知され、前記電流検知回路の検知結果である電流値が所定値よりも小さくなった場合、強制遮断回路により、前記第1乃至第4のMOSFETのうち、少なくとも1つがオフされる。

【0025】

すなわち、本技術の全波整流回路は、前記第1の位相検知回路の検知結果に基づき、前記第1のMOSFETがオンされ、前記第2の位相検知回路の検知結果に基づき、前記第3のMOSFETがオンされるので、交流電源の位相が正から負に、または、負から正に切り替わる前後の位相を検出して、位相が切り替わる前に第1のMOSFETおよび第3のMOSFETをオフの状態とすることで、ゲート−ソース間電圧を放電させ、ゲート−ソース間の電圧が放電したタイミングでオンの状態とすることができる。また、電流検知回路により、第2および第4のMOSFETを流れる電流が検知されて、この電流が所定値よりも小さい、位相が切り替わる前後の、電流値が所定値より小さくなるタイミングで、強制遮断回路が第1乃至第4のMOSFETのうち、いずれかをオフにすることができる。この結果、負荷と並列にコンデンサが接続された、いわゆるコンデンサインプット型の全波整流回路においてコンデンサから生じる逆方向の電流を強制的に遮断することができ、貫通電流の発生を抑制することができる。

【発明の効果】

【0026】

本技術によれば、nチャンネルMOSFETのみでもコンデンサインプット型の全波整流を実現することができ、MOSFETを保護することが可能となるので、電力損失を低減すると共に、動作の安定性を向上させることが可能となる。

【図面の簡単な説明】

【0027】

【図1】一般的な全波整流回路の構成例を説明する図である。

【図2】図1の全波整流回路のダイオードをMOSFETに置き換えた全波整流回路の動作を説明する図である。

【図3】図2のMOSFETの内部構成を加えた全波整流回路の動作を説明する図である。

【図4】チャージポンプ回路を説明する図である。

【図5】全波整流回路にチャージポンプ回路を付加する構成例を説明する図である。

【図6】全波整流回路に位相検知回路を付加する構成例を説明する図である。

【図7】全波整流回路における貫通電流の経路を説明する図である。

【図8】nチャンネルMOSFETのみで全波同期整流を実現するための動作を説明する図である。

【図9】全波整流回路における逆流電流の発生経路を説明する図である。

【図10】全波整流回路に力率改善回路を設ける場合の構成例を説明する図である。

【図11】コンデンサインプット型全波整流において発生する波形を説明する波形図である。

【図12】コンデンサインプット型全波整流において発生する波形を説明する波形図である。

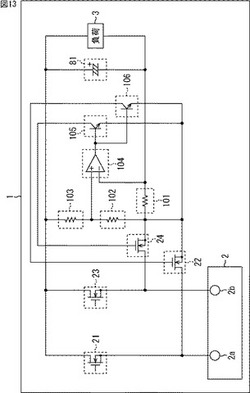

【図13】本技術を適用した全波整流回路の第1の実施の形態の構成例を説明する図である。

【図14】図13の全波整流回路における動作を説明する波形図である。

【図15】図13の全波整流回路における動作を説明する波形図である。

【図16】図13の全波整流回路を実現するための詳細な構成例を説明する図である。

【図17】全波整流回路に力率改善回路を付加することにより生じる逆方向の電流の発生経路を説明する図である。

【図18】本技術を適用した全波整流回路の第2の実施の形態の構成例を示す図である。

【発明を実施するための形態】

【0028】

以下、技術を実施するための形態(以下実施の形態とする)について説明する。なお、説明は以下の順序で行なう。

1.第1の実施の形態(コンデンサインプット型全波整流回路)

2.第2の実施の形態(力率改善回路を含む全波整流回路)

【0029】

<1.第1の実施の形態>

[一般的な全波整流回路]

図1は、一般的な全波整流回路の構成例を示す図である。全波整流回路1は、ダイオード11乃至14、および交流電源2、並びに負荷3より構成されている。ダイオード11は、アノードが交流電源2の第1の端子2aに接続されており、カソードが負荷3の一方の端子に接続されている。また、ダイオード12は、アノードが負荷3の他方の端子に接続されており、カソードが交流電源2の第1の端子2aに接続されている。ダイオード13は、アノードが交流電源2の第2の端子2bに接続されており、カソードが負荷3の一方の端子に接続されている。また、ダイオード14は、アノードが負荷3の他方の端子に接続されており、カソードが交流電源2の第2の端子2bに接続されている。

【0030】

このような構成により、交流電源2の第1の端子2aが第2の端子2bよりも電圧が高い場合(この場合の位相を0°乃至180°であるものとする場合)、図1中の点線で示される経路で電流が流れ、負荷3に直流の電力が供給される。また、交流電圧2の第2の端子2bが第1の端子2aよりも電圧が高い場合(位相が180°乃至360°の場合)、図1中の実線で示される経路で電流が流れ負荷3に直流の電力が供給される。

【0031】

[MOSFETを用いた全波整流回路]

ところで、図1の全波整流回路1は、4個のダイオード11乃至14から構成されているが、ダイオードは、発生する熱等により生じるロスが問題となることが知られている。そこで、ダイオードの構成をMOSFETに置換することで、ダイオードロスの問題を解決させることができる。

【0032】

図2は、ダイオード11乃至14に代えて、MOSFET21乃至24を用いるようにした、全波整流回路1の構成例を示している。

【0033】

すなわち、上述した位相が0°乃至180°の場合、MOSFET21,24がオン、かつ、MOSFET22,23がオフの状態とされ、位相が180°乃至360°の場合、MOSFET21,24がオフ、かつ、MOSFET22,23がオンされるように、MOSFET21乃至24が制御されると、図1における全波整流回路と等価な回路を実現させることができ、この場合、ダイオードが全てMOSFETとされたことにより、ダイオードロスの問題が解消されることになる。この様に、MOSFET21乃至24のオン、またはオフを同期して制御し、全波整流を実現する回路を、一般に、全波同期整流回路という。以降においては、全波同期整流回路を単に全波整流回路とも称するものとし、同期整流するものとして説明を進めるものとする。

【0034】

[寄生ダイオード]

MOSFETは、内部に寄生ダイオード(ボディダイオード)と呼ばれるダイオードが存在する。図3は、MOSFET21乃至24のそれぞれの寄生ダイオードをダイオード31乃至34として回路図上に付記した全波整流回路1の構成例を示している。すなわち、ダイオード31は、MOSFET21の内部に寄生するダイオードであり、アノードが交流電源2の第1の端子2aに接続され、カソードが負荷3の一方の端子に接続される。ダイオード32は、MOSFET22の内部に寄生するダイオードであり、アノードが負荷3の他方の端子に接続され、カソードが交流電源2の第1の端子2aに接続される。ダイオード33は、MOSFET23の内部に寄生するダイオードであり、アノードが交流電源2の第2の端子2bに接続され、カソードが負荷3の一方の端子に接続される。ダイオード34は、MOSFET24の内部に寄生するダイオードであり、アノードが負荷3の他方の端子に接続され、カソードが交流電源2の第2の端子2bに接続される。

【0035】

これらのダイオード31乃至34は、それぞれに対応するMOSFET21乃至24がオフにされたとしても、電流が流れることになり、結果として、上述した図1の4個のダイオードからなる全波整流回路における場合のダイオード11乃至14と同様に機能する。尚、寄生ダイオードであるダイオード31乃至34は、MOSFET21乃至24の動作特性上、そのようなダイオードが仮想的に存在すると考えれば回路上で表記できるというものであって、ダイオードとしての回路が実在するものではない。

【0036】

MOSFETは、nチャンネルMOSFETとpチャンネルMOSFETの2種類が存在し、MOSFETがオンした際の抵抗値は、nチャンネルMOSFETの方が、pチャンネルMOSFETよりも小さい事が一般に知られている。nチャンネルMOSFETは、ゲートの電圧がソースの電圧よりも一定以上高くなるときオンになる。また、nチャンネルMOSFETにおいて、内部の寄生ダイオードのアノードに対応する端子はソースである。また、pチャンネルMOSFETは、ゲートの電圧がソースの電圧よりも一定以上低くなるときオンする。また、pチャンネルMOSFETにおいて、内部の寄生ダイオードのアノードに対応する端子はドレインである。従って、例えば、MOSFET21にnチャンネルMOSFETを用いる際には、ソースを第1の端子2aに接続し、pチャンネルMOSFETを用いる際にはドレインを第1の端子2aに接続する。すなわち、nチャンネルMOSFETとpチャンネルMOSFETとでは接続方法が異なる。尚、寄生ダイオード31乃至34は、以降の図中において記載しない場合においても、図3に示されるように構成されるものとして説明を進めるものとする。

【0037】

上述の理由から、MOSFET22,24にpチャンネルMOSFETが用いられた場合、交流電源2の第1の端子2a、および第2の端子2bよりも低い電圧が必要であるため、駆動する上で制御に困難が生じる。また、MOSFET22,24にnチャンネルMOSFETが用いられた場合、ソースに対応する端子の電圧は、交流電源2の第1の端子2aまたは第2の端子2bの電圧よりも低い電圧であるため、nチャンネルMOSFETを駆動するにあたり、制御が容易であると考えられる。

【0038】

また、MOSFET21,23にpチャンネルMOSFETが用いられた場合、交流電源2の第1の端子2aまたは第2の端子2bは、ソースよりも低いため駆動にあたり、制御が容易であると考えられる。一方、MOSFET21,23にnチャンネルMOSFETが用いられた場合、上述の通りソースが交流電源2の第1の端子2aまたは第2の端子2bに接続されるため、第1の端子2aまたは第2の端子2bよりも高い電圧が必要となる。

【0039】

しかしながら、前述の通り、nチャンネルMOSFETの方がpチャンネルMOSFETよりもオン抵抗が小さいので、MOSFET21,23にnチャンネルMOSFETが用いられるようにした方がロスは低減されることになる。そこで、MOSFET21,23にnチャンネルMOSFETを用いるための技術としてチャージポンプ回路が考えられる。

【0040】

[チャージポンプ回路]

ここで、図4を参照して、チャージポンプ回路について説明する。図4の回路は、電源VDD1の正端子にスイッチS1の一方の端部が接続されており、負端子に切替スイッチS2の一方の切替端子、電源VDD2の負端子、およびコンデンサC2の他方の端子が接続されている。スイッチS1は、一方の端子が電源VDD1の正端子に接続され、他方の端子がコンデンサC1の一方の端子、およびスイッチS3の一方の端子に接続されている。コンデンサC1の一方の端子は、スイッチS1の他方の端子、および、スイッチS3の一方の端子に接続される。コンデンサC1の他方の端子は、切替スイッチS2の一方の端子に接続される。スイッチS2の一方の端子は、コンデンサC1の他方の端子に接続され、一方の切替端子は、電源VDD1,VDD2の負端子、およびコンデンサC2の他方の端子に接続されている。スイッチS2の他方の切替端子は、電源VDD2の正端子に接続されている。電源VDD2の正端子は、切替スイッチS2の他方の切替端子に接続され、負端子は、電源VDD1の負端子、切替スイッチS2の一方の切替端子、およびコンデンサC2の他方の端子に接続されている。スイッチS3の一方の端子は、スイッチS1の他方の端子、およびコンデンサC1の一方の端子に接続されており、他方の端子は、コンデンサC2の一方の端子に接続されている。コンデンサC2の一方の端子は、スイッチS3の他方の端子に接続されており、他方の端子は、電源VDD1,VDD2の負端子、および切替スイッチS2の一方の切替端子に接続されている。尚、図4においては、左部、および右部のいずれにおいても同一の回路が示されているが、異なる動作状態を示している。また、電源VDD1,VDD2は、いずれも電圧VDDの直流電源である。

【0041】

例えば、図4の左部に示されるように、スイッチS1がオンとされ、切替スイッチS2が一方の切替端子に接続され、スイッチS3がオフとされる場合、コンデンサC1は電源VDD1の電圧VDDによってVDDに充電される。この状態から、図4の右部で示されるように、スイッチS1がオフとされ、切替スイッチS2が他方の切替端子に接続され、スイッチS3がオンとされる場合、コンデンサC1および電源VDD2とは、直列接続されることになるので、図4の右部における点aの電圧は、VDDの2倍となる。同時にスイッチS3がオンとされることにより、実質的に電圧VDD×2に昇圧された電圧が得られるので、コンデンサC2は、電圧VDD×2の電圧で充電される。この様に蓄えた電荷を利用して入力電圧よりも高い電圧を生成する回路が、チャージポンプ回路である。この回路を応用すれば、交流電源2の第1の端子2aまたは第2の端子2bよりも高い電圧を生成する事が可能となる。

【0042】

図5は、チャージポンプ回路を追加した全波整流回路1の構成例を示している。尚、図5において、図3における全波整流回路1と同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。図5の全波整流回路1において、図3の全波整流回路1と異なる点は、ダイオード51およびコンデンサ52を直列に接続し、MOSFET21に並列に接続した点である。ダイオード51のアノードは、MOSFET21の寄生ダイオード31のカソードに対応する端子に接続されており、カソードは、コンデンサ52の一方の端子に接続されている。また、コンデンサ52は、一方の端子がダイオード51のカソードに接続されており、他方の端子がMOSFET21の寄生ダイオード31のアノード側の端子に接続されている。

【0043】

すなわち、図5で示されるように、MOSFET21に並列に接続された、直列接続されているダイオード51およびコンデンサ52が、チャージポンプ回路として構成される。図5の全波整流回路1により、位相が180°乃至360°となる時、図5の実線で示される経路でコンデンサ52を第2の端子2bおよび第1の端子2aの電位差分だけ充電することが可能となる。また、次に位相が0°乃至180°となる時、コンデンサ52には電荷が蓄積されているので先ほどと同じ原理で入力電圧よりも高い電圧が得られる。得られる電圧は最高で入力電圧の最高値分となり、例えば、交流電源2の電源電圧がAC24Vの場合、AC24V×1.41≒33Vが得られる。次に、位相が0°乃至180°となる時、上記コンデンサ52に蓄えられた電圧を利用してMOSFET21をオンすれば良い。尚、ダイオード51のアノードについては、交流電源2の第2の端子2bに直接接続するようにしてもよい。

【0044】

そこで、上述したような位相のタイミングにおいて、MOSFET21をオンできるように制御する構成として、例えば、図6で示されるような全波整流回路1が考えられる。

【0045】

図6の全波整流回路1において、図5の全波整流回路1と同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。図6の全波整流回路1において、図5の全波整流回路1と異なる点は、抵抗61、フォトダイオード62、フォトカプラ63、および抵抗64を新たに設けた点である。抵抗61、およびフォトダイオード62は、抵抗61の一方の端子が交流電源2の第1の端子2aに接続され、他方の端子がフォトダイオード62のアノードに接続される。フォトダイオード62は、アノードが抵抗61の他方の端子に接続され、カソードが交流電源2の第2の端子2bに接続される。そして、フォトカプラ63は、フォトダイオード62が発光する光を受光できるように物理的に構成されている。すなわち、抵抗61、フォトダイオード62は、直列に接続されて、交流電源2の第1の端子2aおよび第2の端子2bを跨ぐように接続されている。また、フォトカプラ63は、フォトダイオード62が発光するとき、その光を受光でき、フォトカプラ63のエミッタがMOSFET21のゲートに接続され、コレクタが抵抗64の一方の端子に接続され、抵抗64の他方の端子がダイオード51のカソードおよびコンデンサ52の一方の端子と接続される。

【0046】

このように構成されることにより、交流電源2の第1の端子2a、および第2の端子2bのそれぞれの出力電圧の位相に伴って以下のように動作する。すなわち、位相が180°乃至360°となる時、フォトダイオード62は発光しない。従って、この間、図5で示されるように、コンデンサ52が第2の端子2bと第1の端子2aとの電位差分だけ充電される。そして、位相が0°乃至180°となる時、フォトダイオード62は発光する。従って、この間、フォトカプラ63はオンの状態となり、MOSFET21のゲートには、ダイオード51およびコンデンサ52より構成されるチャージポンプ回路で得られた、ソース(第1の端子2a)よりも高い電圧が印加されることになるので、MOSFET21がオンされる。すなわち、抵抗61、フォトダイオード62、フォトカプラ63、および抵抗64が、位相が0°乃至180°であるか、または、180°乃至360°であるかを検知する、位相検知回路を構成している。そして、この位相検知回路の検知結果に基づいて、チャージポンプ回路がコンデンサ52に電圧を充電させると共に、MOSFET21のオン、またはオフが制御されている。

【0047】

尚、MOSFET23においても、MOSFET21におけるチャージポンプ回路、並びに、抵抗61、フォトダイオード62、フォトカプラ63、および抵抗64を設ける。ただし、この場合、MOSFET23がオンされるタイミングが、MOSFET21がオンされるタイミングと180°異なるように構成される必要がある。

【0048】

ところで、MOSFETには入力容量が必ず存在し、一般的にオン抵抗が低いものの方が入力容量は大きい。仮に、第1の端子2aの電圧が、第2の端子2bの電圧よりも低くなっても、MOSFET21がオンしたままであった場合、MOSFET23がオンしていない状態であっても、図7の点線で示されるように、MOSFET23の寄生ダイオード33を通るループで貫通電流が流れてしまう恐れがある。

【0049】

このような貫通電流は、多大なため素子を破壊する恐れが高い。そこで図8で示されるように半周期の一部分だけMOSFET21のゲートを印加し、位相が反転するまで時間の猶予を作り、このΔtの間に完全にコンデンサ52に充電された電荷を放電する事によって、上述した貫通電流を防ぐ事ができる。尚、図8は、第1の端子2aの出力電圧の波形であり、時刻t0乃至t3が、位相が0°乃至180°を示しており、時刻t3以降が位相が180°乃至360°である。すなわち、位相が0°乃至180°のうち、時刻t1乃至t2において、MOSFET21のゲートが印加され、位相が切り替わる近傍の時刻t2乃至t3のΔtにおいては、MOSFET21のゲートが印加されない。すなわち、第1の端子2aの電圧が、第2の端子2bの電圧よりも低くなっても、MOSFET21はオフの状態となるため、図7の点線で示されるような経路による貫通電流は発生しない。尚、この技術については、特開2010−178519号公報により本出願人により出願されている。詳細については、特開2010−178519号公報を参照されたい。

【0050】

しかしながら、例えば、図9で示されるように、出力にコンデンサが追加されると動作上、障害が発生する。すなわち、出力に大きな容量のコンデンサがある場合においては、MOSFETは双方向に電流を流す素子であるため、電源の構成がコンデンサインプット型のとき、例えば、MOSFET21がオンしている間、交流電源2の第1の端子2aは、交流電源2の出力電圧Voにクランプされる。一方、MOSFET21がオンの状態となる、位相が0°乃至180°のタイミングにおいては、MOSFET24もオンの状態とされるので、交流電源2の第2の端子2bはグランド電位にクランプされる。しかしながら、入力電圧は、位相が90°乃至180°の間、交流電源2の出力電圧は減少方向になるため、図9の点線で示されるように、交流電源2を通じて出力電圧を放電する方向に電流が逆流する。従って、結果的に出力電圧は直流の状態を保持できないため、逆流した過大な電流によって、各種の回路を保護するためにヒューズ等が設けられていると、溶断されてしまう可能性がある。

【0051】

尚、上述した特開2010−178519号公報に開示された技術においては、図10で示されるように、インダクタ92からなる力率改善回路を後段に備えた回路が想定されているため、ダイオード93が設けられている。図10の全波整流回路1においては、図2の全波整流回路1と同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。すなわち、図10の全波整流回路1において、図2の全波整流回路1と異なるのは、平滑コンデンサ81、MOSFET91、インダクタ92、およびダイオード93を備えた点である。

【0052】

平滑コンデンサ81は、負荷3に対して並列に接続されている。インダクタ92は、一方の端子がMOSFET21,23の寄生ダイオードのカソードに対応する端子に接続され、他方の端子がMOSFET91の寄生ダイオードのカソードに対応する端子に接続される。ダイオード93は、アノードがインダクタ92の他方の端子、およびMOSFET91の寄生ダイオードがカソードに対応する端子に接続され、カソードが平滑コンデンサ81の一方の端子、および負荷3の一方の端子に接続される。MOSFET91は、寄生ダイオードのカソードに対応する端子が、インダクタ92の他方の端子、およびダイオード93のアノードに接続され、寄生ダイオードのアノードに対応する端子が、MOSFET22,24の寄生ダイオードのアノードに対応する端子、平滑コンデンサ81の他方の端子、および負荷3の他方の端子に接続されている。このような構成により、MOSFET91がオンオフに制御されることで、力率改善回路が実現される。

【0053】

このダイオード93の効果により平滑コンデンサ81の出力に蓄えられた電荷が逆流する事は無い。しかしながら、力率改善回路は必ずしも必要な構成ではないため仕様によっては力率改善回路が要らない場合も多々あり、その場合において同期整流が不可能となってしまう。

【0054】

ところで、図9で示されるような、コンデンサインプット型の全波整流回路1の場合、図11,図12で示される通り、交流電源2より出力される出力電圧の1周期に対して電力が伝達される期間は短くなる。尚、図11,図12においては、時刻t0乃至t14が出力電圧の1周期である。また、電力が伝達される期間は、時刻t11乃至t12であり、時刻t12乃至t13は、電力が伝達されない期間となる。

【0055】

これはMOSFET21,23とMOSFT22,24との間に接続された平滑コンデンサ81で整流された脈流電圧を直流に置き換えるためであり、交流電源2の第1の端子2aの出力電圧よりも高い状態の時のみ交流電源2より電流が流れる(電力が伝達される)。ここで、図11,図12において、点線は、交流電源2の第1の端子2aの出力電圧を、太実線は第1の端子2aの電流値を、細実線は、平滑コンデンサ81の充電電圧を、一点鎖線は、MOSFET21のゲートの印加電圧をそれぞれ示している。

【0056】

また、図6を参照して説明した位相検知回路により、例えば、図12の一点差線で示されるように、交流電源2の第1の端子2aの1周期の間の時刻t31乃至t32で示される一定期間のみMOSFET21はオン状態にある。MOSFET21は、特性上ドレインからソース方向にも、ソースからドレイン方向にも双方向に電流を流す素子であるため、MOSFET21がオンしている間、図9で示されるように、交流電源2の第1の端子2aと平滑コンデンサ81の低電位側(以後グランドと称する)の間の電圧は出力電圧とほぼ同じ電圧が印加される。そのため、MOSFET21をnチャンネルMOSFETで構成するものとし、この状態においてMOSFET24もオンの状態にあると、図9で示されるように、平滑コンデンサ81に蓄えられた電荷を放電する経路で電流が流れる事になる。

【0057】

[本技術を適用した全波整流回路]

上述した平滑コンデンサ81により発生する逆流電流の発生を防止することで、nチャンネルMOSFETのみによりコンデンサインプット型の全波整流回路を実現することができる。

【0058】

図13は、上述した平滑コンデンサ81により発生する逆流電流の発生を防止することで、nチャンネルMOSFETのみにより実現されるコンデンサインプット型の全波整流回路の構成例を示している。尚、図13の全波整流回路1において、図9における全波整流回路1と同様の機能を備えた構成については、同一の符号を付しており、その説明は、適宜省略するものとする。

【0059】

すなわち、図13の全波整流回路1において、図9の全波整流回路1と異なる点は、新たに、抵抗101乃至103、コンパレータ104、およびトランジスタ105,106を新たに設けた点にある。

【0060】

抵抗101は、一方の端子が、MOSFET22,24の寄生ダイオードのアノード側の端子に接続され、他方の端子が、負荷3、および平滑コンデンサ81のそれぞれの他方の端子、およびコンパレータ104の反転入力端子に接続されている。抵抗101は、MOSFET22,24と平滑コンデンサ81との間を流れる電流検出回路として機能し、検出した両端間で発生する電圧値に対応する電圧がコンパレータ104の反転入力端子に入力される。

【0061】

抵抗102は、一方の端子が、抵抗103の他方の端子、およびコンパレータ104の非反転入力端子に接続され、他方の端子が、MOSFET22,24の寄生ダイオードのアノード側の端子、抵抗101の一方の端子、およびトランジスタ105,106のエミッタに接続されている。抵抗103は、一方の端子が、MOSFET21,23の寄生ダイオードのカソード側の端子、並びに、平滑コンデンサ81、および負荷3の一方の端子に接続され、他方の端子が、抵抗102の一方の端子、およびコンパレータ104の非反転入力端子に接続されている。すなわち、抵抗102,103は、コンパレータ104の非反転入力端子に入力する電圧の分圧抵抗を構成している。従って、抵抗102,103のそれぞれ抵抗値は、コンパレータ104の非反転入力端子に入力する電圧が所定の閾値となるように設定される。

【0062】

コンパレータ104は、非反転入力端子が抵抗102の一方の端子、および抵抗103の他方の端子に接続され、反転入力端子が抵抗101の他方の端子、および平滑コンデンサ81、および負荷3の他方の端子に接続され、出力端子がトランジスタ105,106のベースに接続されている。すなわち、コンパレータ104は、電流検出回路を構成する抵抗101の両端電圧の検出結果と、抵抗102,103の分圧比により設定される所定の閾値とを比較し、電流検出回路を構成する抵抗101の両端電圧の検出結果が所定の閾値として設定される電圧より低下するとトランジスタ105,106をオンにする。

【0063】

トランジスタ105,106は、それぞれのベースがコンパレータ104の出力端子に接続され、それぞれのエミッタがMOSFET22,24の寄生ダイオードのアノード側の端子に接続され、それぞれのコレクタがMOSFET22,24のゲートに接続されている。すなわち、トランジスタ105,106は、コンパレータ104によりオンされると、MOSFET22,24を強制的にオフにする。尚、図13においては、寄生ダイオード31乃至34が表記されていないが、上述したように、図3で示されるように内部に寄生して存在している。

【0064】

[図13の全波整流回路の動作説明]

次に、図14,図15のタイミングチャートを参照して、交流電源2の第1の端子2aより出力される交流電圧の1周期分の波形に基づいて、図13の全波整流回路1の動作について説明する。尚、図14において、実線で示される波形は、MOSFET22,24を制御するためにトランジスタ105,106により制御されMOSFET22,24のゲートに印加される電圧値を、点線で示される波形は、交流電源2の第1の端子2aの出力電圧の波形を、一点鎖線で示される波形は、MOSFET21または23のゲートに供給される位相検知回路からの入力電圧を、2点鎖線で示される波形は、第1の端子2aの電流値を、それぞれ示している。また、図15は、図14における時刻T5,T6近傍を拡大した波形図である。

【0065】

時刻T0乃至T1において、MOSFET21乃至24は、いずれもオンしておらず、交流電源2からMOSFET21乃至24のそれぞれの内部に存在する寄生ダイオード31乃至34が逆流を防止しており、負荷3への電力供給が行われない。

【0066】

時刻T1乃至T2において、MOSFET21は、上述した位相検知回路より、ゲートに信号が送り込まれて、オフからオンに変化する。このとき、MOSFET22乃至24はいずれもオフの状態が維持されている。MOSFET21乃至24、またはMOSFET22乃至24の内部に存在する寄生ダイオード31乃至34、または寄生ダイオード32乃至34が逆流を防止しており、負荷3に対して電力は供給されていない。すなわち、このタイミングにおいては、位相検知回路からMOSFET21のゲートに対して信号が送られていない状態であっても実質的に同様の状態となる。そして、時刻T2乃至T3においては、この状態が継続される。

【0067】

時刻T3乃至T4において、MOSFET21は、上述した位相検知回路より、ゲートに信号が送り込まれることにより、オンの状態となっている。また、MOSFET22乃至24はいずれもオフしている。このとき、交流電源2の第1の端子2aおよび第2の端子2b間の電圧は、平滑コンデンサ81の電圧よりも高くなるため、交流電源2の第1の端子2aからMOSFET21を介して、負荷3に電流が流れ、MOSFET24の寄生ダイオード34を介して、交流電源2の第2の端子2bへ帰還電流が流れる。このため、第1の端子2aを流れる電流量が急激に増大するので、対応して抵抗101の両端電圧が急激に上昇する。尚、この時、MOSFET21もオフするように制御し、交流電源2の第1の端子2aからMOSFET21の寄生ダイオード31を介して、負荷3側に電力を供給するようにし、MOSFET24の寄生ダイオード34を介して交流電源2の第2の端子2bへと帰還電流が流れるように制御してもよい。さらに、MOSFET21をオフするようにし、MOSFET24がオンするように制御することも可能であり、その場合、MOSFET21の寄生ダイオード31を介して、負荷3側に電力が供給され、MOSFET24を介して交流電源2の第2の端子2bへ帰還電流が流れる。

【0068】

時刻T4乃至T5において、MOSFET21は、位相検知回路からゲートに信号が供給されるのでオンにされ、同時に、電流検知回路を構成する抵抗101の両端電圧が、コンパレータ104の非反転入力端子の電圧を超えることにより、コンパレータ104からの出力がオフにされ、これに伴ってトランジスタ105,106もオフにされるので、MOSFET22,24は、いずれもオンとされる。交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の電圧よりも高いため、交流電源2の第1の端子2aからMOSFET21を介して負荷3側に電力が供給され、MOSFET24を介して交流電源2の第2の端子2bへ帰還電流が流れる。

【0069】

時刻T5乃至T6において、MOSFET21は、上述した位相検知回路より、ゲートに信号が送り込まれることにより、オンされている。しかしながら、電流検出回路を構成する抵抗101を流れる電流の変化に伴って、減少し、図15で示されるように、時刻T5の直前の時刻T5’において、コンパレータ104は、反転入力端子に供給される電圧が、非反転入力端子に入力される閾値となる電圧よりも低くなるので、出力端子より信号を出力する。これに応じてトランジスタ105,106がオンとされるため、MOSFET22,24は、オフとされる。したがって、時刻T5の時点においては、MOSFET22乃至24はいずれもオフの状態であり、交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の充電電圧よりも高いため、交流電源2の第1の端子2aからMOSFET21を通り負荷3側に電力が供給されて、MOSFET24の寄生ダイオード34を通って交流電源2の第2の端子2bへ帰還電流が流れる。尚、この時、MOSFET21をオフに制御して、MOSFET24のみをオンに制御するようにしてもよいし、または、MOSFET21乃至24を全てオフに制御してもよい。

【0070】

時刻T6乃至T7において、MOSFET21がオンにされ、MOSFET22乃至24がいずれもオフとされているが、MOSFET22乃至24の内部寄生ダイオード32乃至34が逆流を防止しており、負荷3に対して電力の供給が行われない。尚、この時、MOSFET21をオフに制御して、MOSFET24のみをオンに制御してもよいし、または、MOSFET21乃至24の全てをオフに制御してもよい。

【0071】

時刻T7乃至T8において、MOSFET21が、位相検知回路からの信号がなくなり、オンからオフへ推移する。MOSFET22乃至24はいずれもオフのままであり、MOSFET21乃至24、またはMOSFET22乃至24の内部寄生ダイオード31乃至34、または32乃至34が逆流を防止しており、負荷3への電力供給は行われない。

【0072】

時刻T8乃至T10において、MOSFET21乃至24はいずれもオンしておらず、交流電源2からMOSFET21乃至24の内部寄生ダイオード31乃至34が逆流を防止しており、負荷3への電力供給がなされていない。尚、時刻T9において、第1の端子2aの出力電圧が、正から負に反転する。

【0073】

時刻T10乃至T11において、MOSFET23は、位相検知回路からゲートに供給される信号により、オフからオンに推移し、MOSFET21,22,24はいずれもオフのままであり、MOSFET21乃至24、または21,22,24の内部寄生ダイオード31乃至34、または31,32,34が逆流を防止しており、負荷3への電力供給は行われない。尚、この時、MOSFET23のゲートへの位相検知回路から供給される信号が送られないような制御とするようにしてもよい。

【0074】

時刻T11乃至T12において、MOSFET23は、位相検知回路からゲートに供給される信号により、オンしており、MOSFET21,22,24はいずれもオフのままであり、MOSFET21,22,24の内部寄生ダイオード31,32,34が逆流を防止しており、負荷3への電力供給は行われない。尚、この時、MOSFET23もオフしていても同様の効果が得られる。)

【0075】

時刻T12乃至T13において、MOSFET23は、位相検知回路からゲートに供給される信号により、オンしており、MOSFET21,22,24はいずれもオフとされている。また、交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の電圧よりも高くなるため、交流電源2の第2の端子2bからMOSFET23を介して負荷3側に電力が供給され、MOSFET22の寄生ダイオード32を介して交流電源2の第1の端子2aへ帰還電流が流れる。尚、この時、MOSFET23もオフするようにし、MOSFET23の寄生ダイオード33を介して負荷3側に電力を供給させ、MOSFET22の寄生ダイオード32を介して交流電源2の第2の端子2bへ帰還電流が流れるようにしてもよい。さらに、MOSFET23をオフするようにし、MOSFET22がオンするように制御するようにしてもよい。その場合、MOSFET23の寄生ダイオード33を介して負荷3側に電力が供給され、MOSFET22を介して交流電源2の第2の端子2bへ帰還電流が流れる。

【0076】

時刻T13乃至T14において、MOSFET22,23がオンしており、交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の電圧よりも高いため、交流電源2の第2の端子2bからMOSFET23を介して負荷3側に電流が流れMOSFET22を介して交流電源2の第1の端子2aへ帰還電流が流れる。

【0077】

時刻T14乃至T15において、MOSFET23がオンしており、MOSFET21,22,24はいずれもオフしており、交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の充電電圧よりも高いため、交流電源2の第2の端子2bからMOSFET23を介して負荷3側に電流が流れ、MOSFET22の寄生ダイオード32を介して交流電源2の第1の端子2aへ帰還電流が流れる。すなわち、時刻T5乃至T6と同様に、電流検出回路を構成する抵抗101を流れる電流の変化に伴って、減少し、時刻T15の直前のタイミング(時刻T5’に対応するタイミング)において、コンパレータ104は、反転入力端子に供給される電圧が、非反転入力端子に入力される閾値となる電圧よりも低くなるので、出力端子より信号を出力する。これに応じてトランジスタ105,106がオンとされるため、MOSFET22,24は、オフとされる。尚、この時、MOSFET23をオフしてMOSFET22のみオン制御するようにしても良いし、MOSFET21乃至24の全てをオフとするように制御するようにしてもよい。

【0078】

時刻T15乃至T16において、MOSFET23がオンにされており、MOSFET21,22,24はいずれもオフされており、MOSFET21,22,24の内部寄生ダイオード31,32,34が逆流を防止しており、負荷3への電力供給は行われない。尚、この時、MOSFET23をオフしてMOSFET22のみオンにするように制御してもよいし、MOSFET21乃至24を全てオフとするように制御してもよい。

【0079】

時刻T16乃至T17において、MOSFET23は、オンからオフへと推移し、MOSFET21,22,24はいずれもオフにされており、MOSFET21乃至24、または21,22,24の内部寄生ダイオード31乃至34、または31,32,34が逆流を防止しており、負荷3への電力供給は行われない。

【0080】

時刻T17乃至T18において、MOSFET21乃至24は全てオンにされておらず、交流電源2からMOSFET21乃至24は全て内部寄生ダイオード31乃至34が逆流を防止しており、負荷3への電力供給は行われない。

【0081】

すなわち、時刻T4乃至T5で示されるように、平滑コンデンサ81に蓄えられた電荷を放電する担い手であったnチャンネルMOSFET21,24若しくはnチャンネルMOSFET22,23の片方、または両方をオフする事によって逆流経路を完全に遮断することができる。

【0082】

また、nチャンネルMOSFET21乃至24の内部には必ずソースからドレイン方向に寄生ダイオードが存在する。その為、平滑コンデンサ81の電荷が0状態で電源投入されたとしても、定常状態に推移するまでの間はMOSFET21乃至24の寄生ダイオード31乃至34が電流伝達の担い手となる。つまりは、電流の担い手であったMOSFET21乃至24を急遽オフしたとしても、MOSFET21乃至24の寄生ダイオード31乃至34を介して電流を流すため、逆起電力が発生して阻止が破壊されたりする事はない。

【0083】

このような構成により、電流が反転する前にMOSFET22,24をオフする事ができるので、コンデンサインプット型の同期整流が可能となる。

【0084】

[図13の全波整流回路を応用した全波整流回路]

次に、図16を参照して、図13の全波整流回路1を実現するための詳細な全波整流回路1の構成例について説明する。尚、図16の全波整流回路1において、図6,図13の全波整流回路1において同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。

【0085】

すなわち、図16の全波整流回路1におけるnチャンネルMOSFET21は、ソースが交流電源2の第1の端子2aに接続される。nチャンネルMOSFET22は、ドレインが交流電源2の第1の端子2aに接続される。nチャンネルMOSFET23は、ドレインがnチャンネルMOSFET21のドレインに接続され、ソースが交流電源2の第2の端子2bに接続される。nチャンネルMOSFET24は、ドレインが交流電源2の第2の端子2bに接続され、ソースがnチャンネルMOSFET22のソースに接続される。

【0086】

ダイオード51−1は、アノードがnチャンネルMOSFET21のドレインと接続される。コンデンサ52−1は、ダイオード51−1のカソードと交流電源2の第1の端子2aの間の電圧によりチャージされ、ダイオード51−1と共にMOSFET21を駆動させるためのチャージポンプ回路を構成する。ダイオード51−2は、アノードがnチャンネルMOSFET23のドレインと接続される。コンデンサ52−2は、ダイオード51−2のカソードと交流電源2の第2の端子2bの間の電圧によりチャージされ、ダイオード51−2と共に、MOSFET23を駆動させるためのチャージポンプ回路を構成する。

【0087】

フォトダイオード62−1は、ダイオード62a−1、ツェナーダイオード255−1、および抵抗61−1と共に、交流電源2の第1の端子2aに接続された、交流電圧の位相を検知するMOSFET21を駆動させるための位相検知回路を構成する。

【0088】

NPNトランジスタ253−1は、コレクタにコンデンサ52−1が接続され、エミッタにnチャンネルMOSFET21のゲートが接続され、ベースにツェナーダイオード252−1を介して交流電源2の第1の端子2aと接続される。抵抗64−1は、一方の端子が、コンデンサ52−1と接続され、他方の端子がフォトカプラ63−1の受光側のコレクタに接続される。フォトカプラ63−1の受光側のエミッタは、NPNトランジスタ253−1のベースに接続される。抵抗251−1、ツェナーダイオード252−1、NPNトランジスタ253−1、コンデンサ52−1、フォトカプラ63−1、および抵抗64−1は、MOSFET21を駆動させるための位相検知回路の検知結果、すなわち、フォトダイオード62−1の発光の有無に基づいて、nチャンネルMOSFET21をオンする信号を送る制御回路を構成する。

【0089】

このnチャンネルMOSFET21をオンする信号を送る制御回路は、MOSFET21を駆動させるための位相検知回路の検知結果であるフォトダイオード62−1の発光状態に基づいて、フォトカプラ63−1によってMOSFET21を駆動させるチャージポンプ回路よりMOSFET21のゲートに電圧を印加するように接続され、第1の端子2aの電位が第2の端子2bの電位よりも低くならないうちにMOSFET21のゲートおよびソース間の電圧を所定値より小さくするように制御する。

【0090】

抵抗254−1は、nチャンネルMOSFET21のソース−ゲート間に接続され、MOSFET21の放電回路を構成する。放電回路を構成する抵抗254−1の抵抗値は、MOSFET21を駆動させる位相検知回路の検知結果で得られるタイミングより、交流電源2の第1の端子2aと第2の端子2bとの間の電圧が、正から負または負から正に切り替わるタイミングに至るまでの期間内にゲート−ソース間の電位をMOSFET21が確実にオフできる値とされる。

【0091】

フォトダイオード62−2は、ダイオード62a−2、ツェナーダイオード255−2、および抵抗61−2と共に、交流電源2の第2の端子2bに接続された、交流電圧の位相を検知するMOSFET23を駆動させるための位相検知回路を構成する。

【0092】

NPNトランジスタ253−2は、コレクタがコンデンサ52−2に接続され、エミッタがnチャンネルMOSFET23のゲートに接続され、ベースがツェナーダイオード252−2を介して、交流電源2の第2の端子2bと接続される。抵抗64−2は、一方の端子が第2のコンデンサ52−2と接続され、他方の端子がフォトカプラ63−2の受光側のコレクタに接続される。フォトカプラ63−2の受光側のエミッタは、NPNトランジスタ253−2のベースと接続される。抵抗251−2、ツェナーダイオード252−2、NPNトランジスタ253−2、コンデンサ52−2、フォトカプラ63−2、および抵抗64−2は、MOSFET23を駆動させるための位相検知回路の検知結果、すなわち、フォトダイオード62−2の発光の有無に基づいて、nチャンネルMOSFET23をオンする信号を送る制御回路を構成する。

【0093】

このnチャンネルMOSFET23をオンする信号を送る制御回路は、MOSFET23を駆動させるための位相検知回路の検知結果であるフォトダイオード62−2の発光状態に基づいて、フォトカプラ63−2によってMOSFET23を駆動させるチャージポンプ回路よりMOSFET23のゲートに電圧を印加するように接続され、第2の端子2bの電位が第1の端子2aの電位よりも低くならないうちにMOSFET23のゲートおよびソース間の電圧を所定値より小さくするように制御する。

【0094】

抵抗254−2は、nチャンネルMOSFET23のソース−ゲート間に接続され、MOSFET23の放電回路を構成する。放電回路を構成する抵抗254−2の抵抗値は、MOSFET23を駆動させる位相検知回路の検知結果で得られるタイミングより、交流電源2の第1の端子2aと第2の端子2bとの間の電圧が、正から負または負から正に切り替わるタイミングに至るまでの期間内にゲート−ソース間の電位をMOSFET23が確実にオフできる値とされる。

【0095】

抵抗262−1,264−1は、交流電源2の第2の端子2bとnチャンネルMOSFET22,24のソースの間の電圧を分圧した第1の駆動電圧をnチャンネルMOSFET22のソース−ゲート間に印加する第1の分圧回路を構成する。

【0096】

抵抗261−1,262−2は、交流電源2の第1の端子2aとnチャンネルMOSFET22,24のソースの間の電圧を分圧した第2の駆動電圧をnチャンネルMOSFET24のソース−ゲート間に印加する第2の分圧回路を構成する。

【0097】

平滑コンデンサ81は、nチャンネルMOSFET21,23のドレインおよびnチャンネルMOSFET22,24のソースとの間の電圧により充電される。

【0098】

抵抗101は、平滑コンデンサ81とnチャンネルMOSFET22,24のソースに接続された電流値を検出する電流検出回路を構成する。

【0099】

抵抗102,103は、MOSFET21,23のドレインとMOSFET22,24のソースの間の電圧を分圧した第3の分圧回路を構成する。

【0100】

コンパレータ104は、非反転入力端子に前記第3の分圧回路で分圧された電圧が印加され、反転入力端子に電流検出回路を構成する抵抗101により検出される平滑コンデンサ81とnチャンネルMOSFET22,24のソース間に流れる電流値に対応する電圧が入力され、比較結果をトランジスタ105,106のベースに出力する。

【0101】

トランジスタ105,106は、それぞれベースにコンパレータ104の出力に応じてMOSFET22,24をオフする様に構成され、抵抗211乃至214と共に、MOSFET22,24をオフするための制御回路100を構成する。

【0102】

尚、図16の全波整流回路1は、図13の全波整流回路1の動作を実現させるための詳細な構成であり、動作そのものは、図13における全波整流回路1と同様であるので、その説明は省略する。

【0103】

<第2の実施の形態>

[力率改善回路を含めた場合の問題]

以上においては、コンデンサインプット型の全波整流回路を実現させる構成について説明してきたが、力率改善回路を含めた構成とした場合、同期整流を実現すると、以下のように逆流する電流が発生し、障害が発生する恐れがある。

【0104】

すなわち、例えば、図17で示されるような構成の場合、図中の一点鎖線で示される経路を介して逆流する電流が発生する恐れがある。

【0105】

図17の回路は、AC100VをAC24Vに変換する電源トランス310と、電源トランス310に接続された複数の電源ユニット320−1乃至320−nから構成されている。電源ユニット320−1は、AC24Vを同期整流型ブリッジにより整流する整流回路330と、整流された電圧の力率を改善する力率改善回路340と、直流電圧を出力する出力回路350より構成されている。力率改善回路340は、インダクタLと、MOSFETからなるFET1と、FET2と、FET1およびFET2のスイッチングを制御する制御回路352を備えており、制御回路352は、FET1とFET2のデューテイ比を調整する。

【0106】

[力率改善回路を含む全波整流回路]

以上において、問題となるのは、図17におけるFET1で示されるハイサイド側のオンオフを制御するMOSFETが、逆流電流が発生しているタイミングにおいてオンの状態となり得ることである。したがって、上述した電流検知回路を構成し、逆流電流が発生する直前のタイミングにおいて、ハイサイド側のMOSFETをオフに制御することで力率改善回路を付した全波整流回路により安定した同期整流を実現することができる。

【0107】

図18は、力率改善回路を付した全波整流回路1である。図18の全波整流回路1において、図3,図6,図13,図16の全波整流回路1における構成と同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。また、図18の全波整流回路1においては、同期全波整流を実現させるための構成、すなわち、MOSFET21乃至24等については、図16の全波整流回路1と同一の機能であり、同一の動作をするものであるので、ここでは、力率改善回路についてのみ説明するものとする。

【0108】

図18の全波整流回路1における力率改善回路は、力率改善制御回路401、オン時ディレイ回路402、反転回路403、オン時ディレイ回路404、ローサイド用オンオフ回路405、ハイサイド用オンオフ回路406、MOSFET407,408、およびインダクタ409より構成される。また、コンパレータ104に代えてコンパレータ104’が設けられている。コンパレータ104’における機能は、コンパレータ104とほぼ同様の機能であるが、非反転入力端子側に電流検知回路を構成する抵抗101の電流値に対応する電圧が入力され、反転入力端子側に固定電圧値を出力する電源410より供給される固定電圧値が閾値電圧値として入力され、出力端子が、ハイサイド用オンオフ回路406に接続されている点が異なる。

【0109】

力率改善制御回路401は、入力端子Vinに同期整流された電圧が入力され、電源端子Vccより図示せぬ電源より電力が供給され、電流検知端子ISが、MOSFET22,24のソースに接続され、帰還電圧入力端子FBがMOSFET408のドレインに接続され、グランド端子GNDが接地され、出力端子outが、オン時ディレイ回路402、および反転回路403に接続されている。オン時ディレイ回路402は、力率改善制御回路401より出力されるローサイド用のMOSFET407をオンに制御する信号を所定時間だけ遅延させてローサイド用オンオフ回路405に供給する。ローサイド用オンオフ回路405は、オン時ディレイ回路402より供給されてくるローサイド用のMOSFET407をオンに制御する信号に基づいてMOSFET407のオンに制御し、それ以外のときオフに制御する。反転回路403は、力率改善制御回路401より供給されてくるローサイド用のMOSFET407をオフに制御する信号を、オンに制御する信号に反転させて、ハイサイド用のMOSFET408をオン時ディレイ回路404に供給する。オン時ディレイ回路404は、反転回路403より出力されるハイサイド用のMOSFET408をオンに制御する信号を所定時間だけ遅延させてハイサイド用オンオフ回路406に供給する。ハイサイド用オンオフ回路406は、オン時ディレイ回路404より供給されてくるハイサイド用のMOSFET408をオンに制御する信号に基づいてMOSFET408のオンに制御し、それ以外のときオフに制御する。

【0110】

このような構成により、MOSFET407,408のオンオフの制御と、インダクタ409により、力率が改善される。

【0111】

次に、ハイサイド用のMOSFET408を強制的にオフにする動作について説明する。

【0112】

コンパレータ104’は、電流検知回路を構成する抵抗101を流れる電流量に対応した両端電圧が、所定の電圧値よりも高いとき、Hiとなる出力信号を出力する。この場合、ハイサイド用オンオフ回路406には、オン時ディレイ回路404の出力信号がHiで、かつ、コンパレータ104’の出力信号がHiであるときにはHiの信号が供給され、それ以外のとき、Lowの信号が供給されることになる。このため、コンパレータ104’より供給される信号がHiの信号であれば、実質的にオン時ディレイ回路404の出力信号そのものがハイサイド用オンオフ回路406に供給される。一方、電流検知回路を構成する抵抗101を流れる電流値に対応する両端電圧が所定の電圧よりも低くなり、逆流電流が流れる条件に近付くと、コンパレータ104’からはLowの信号が出力されることにより、ハイサイド用オンオフ回路406には、オン時ディレイ回路404からの出力信号に関わらず、Lowの信号が供給されることになる。この結果、ハイサイド用オンオフ回路406は、MOSFET408をオフとすることにより、図17で示されるような逆流を防止させることが可能となる。

【0113】

尚、図13または図16における場合のように、MOSFET22,24のゲートに対してコンパレータ104’の出力結果に対応する信号を供給して、MOSFET22,24を強制的にオフにするようにしてもよい。さらに、コンパレータ104’の出力信号に対応して、MOSFET21乃至24、およびMOSFET408を全てオフするように、制御しても良いし、それらのうちのいずれかをオフとするように制御するようにしてもよい。

【0114】

以上の如く、本技術によれば、全波整流に伴うロスを低減することが可能となる。すなわち、全波整流回路のロスはダイオードで構成された場合、平均電流×順方向電圧VFで決定され、例えば、交流電圧がAC100Vで負荷を200Wとすると、平均電流が約1A程度になり、VF=1.1Vとすると、1×1.1=1.1Wであり、ダイオード4つトータルのロスは4.4W程度になる。

【0115】

一方、MOSFETを用いた同期整流では、MOSFETのロスは実効値電流×実効値電流×オン抵抗で決定され、前記と同じ条件で、実効値電流は約1.5A程度になり、オン抵抗を50mΩとすると、1.5×1.5×0.05≒0.11Wであり、MOSFET4つトータルのロスは0.44W程度とり、3.96Wのロス低減が可能となる。

【0116】

更には、アミューズメント業界の様に、スイッチング電源に入力される交流電圧がAC24Vの場合、MOSFETの耐圧は現状においては十分なものである(耐圧:60V)ので、オン抵抗が更に低いものが使用できる。一方、ダイオードの順方向電圧VFはダイオードの耐圧を下げたとしても極端には下がらず、約0.6V程度である。ダイオードの順方向電圧VFを0.6V、MOSFETのオン抵抗を4mΩとすると、9.3W程度のロス低減が可能となる。

【0117】

これらの効果により、従来であれば大型の放熱器にダイオードを取り付け発熱対策を行っていたが、高効率化することによって放熱器が要らなくなるので、1つのパッケージ化を実現する事が可能となる。

【0118】

また、本技術の全波整流回路によれば、貫通電流と称される、nチャンネルMOSFET21およびnチャンネルMOSFET23に同時に電流が流れる現象を防ぐ事が可能となる。

【0119】

一方、コンデンサインプット型の全波整流の場合、図11で示されるように、交流電源2より出力される出力電圧の1サイクルに対して電力が伝達される期間は短くなる。これは上述したMOSFET21,23とMOSFET22,24のソースとの間に接続された平滑コンデンサ81で整流された脈流電圧を直流に置き換えるためであり、交流電圧が出力電圧よりも高い状態の時のみ交流電源2より電流が流れる(電力が供給される)。また、上記位相検知回路により、例えば、図14の様に1周期の間の一定期間のみMOSFETはオン状態にある。したがって、MOSFETは特性上ドレインからソース及びソースからドレイン双方向電流を流す素子であるため、MOSFETがオンしている間は図9で示される通り、交流電源2の第1の端子2aまたは第2の端子2bと平滑コンデンサ81の低電位側(以後グランドと名づける)の間の電圧は出力電圧とほぼ同じ電圧が印加される。そのため、この時、nチャンネルMOSFET22,24がオン状態にあると図9で示されるように、平滑コンデンサ81に蓄えられた電荷を放電する経路で電流が流れる事になる。

【0120】

しかしながら、電流検出回路を構成する抵抗101に流れる電流値が所定の値よりも低くなった場合、電流検出回路を構成する抵抗101に接続されたコンパレータ104が検知するため、その結果に基づきMOSFET22,24がオフにされる。このように動作することにより、図14で示されるように、平滑コンデンサ81に蓄えられた電荷を放電する担い手であったnチャンネルMOSFET21,24、またはnチャンネルMOSFET22,23の片方、または両方をオフする事によって逆流経路を完全に遮断する事が可能となる。

【0121】

また、nチャンネルMOSFETの内部には必ずソースからドレイン方向に寄生ダイオードが存在する。その為、全てのコンデンサの電荷が0状態で電源投入されたとしても、定常状態に推移するまでの間はMOSFETの寄生ダイオードが電流伝達の担い手となる。つまりは、図14の様に電流の担い手であったMOSFETを急遽オフしたとしても、MOSFETの寄生ダイオードを通じて電流を流すため逆起電力が発生して素子が破壊されたりする事を防止することが可能となる。

【0122】

結果として、図15で示されるように、電流が反転する直前のタイミングで、MOSFET22,24をオフする事によってコンデンサインプット型の同期整流が可能となる。

【0123】

以上の如く、本技術によれば、電力損失を低減すると共に、nチャンネルMOSFETを保護することができるので、動作の安定性を向上させることが可能となる。また、逆方向に流れる電流を遮断することができるので、逆電流による障害を防止することが可能となり、さらに、力率改善回路を付したような場合であっても、同様の制御により逆方向に流れる電流により生じる障害を防止することが可能となる。

【0124】

また、本明細書において、システムとは、複数の装置により構成される装置全体を表すものである。

【符号の説明】

【0125】

1 全波整流回路

11乃至14 ダイオード

21乃至24 MOSFET

31乃至34 寄生ダイオード

51 ダイオード

52 コンデンサ

62 フォトダイオード

63 フォトカプラ

81 平滑コンデンサ

101 抵抗

104,104’ コンパレータ

105,106 トランジスタ

401 力率改善制御回路

402 オン時ディレイ回路

403 反転回路

404 オン時ディレイ回路

405 ローサイド用オンオフ回路

406 ハイサイド用オンオフ回路

407,408 MOSFET

409 インダクタ

【技術分野】

【0001】

本技術は、全波整流回路に関し、特に、電力損失を低減すると共に、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)を保護することにより動作の安定性を向上させるようにした全波整流回路に関する。

【背景技術】

【0002】

従来より、スイッチング電源装置を小型化、軽量化、および高効率化するために、スイッチング電源装置の電力損失を低減することが重要な課題となっていた。特に、スイッチング電源装置に設けられ、交流電圧を全波整流する全波整流回路は電力損失が大きく、全波整流回路の損失の低減は重要な課題となっている。

【0003】

この課題に対応すべく、入力電源より、出力側へ流れる電流をPch-MOSFET(pチャンネルMOSFET)で整流し、負荷側から入力電源に帰還する電流はNch-MOSFET(nチャンネルMOSFET)よりで整流し、全波同期整流を実現している(特許文献1参照)。

【0004】

また、使用するMOSFET全てをPch型のものよりもオン抵抗の小さなNch型のものとすることにより、電力損失を低減させるようにするものが提案されている(特許文献2参照)。

【0005】

しかしながら、特許文献1の技術においては、Pch-MOSFETはNch-MOSFETよりもオン抵抗が大きく、Nch-MOSFETを用いる時よりもロスが大きくなってしまうおそれがある。また、コンパレータを4つ用いたとしても、コンパレータの同相入力の問題や、ゲート−ソース間の耐電圧を超えた電圧がMOSFETに印加される可能性があった。

【0006】

また、特許文献2の技術においては、Nch-MOSFETで構成されており、Pch-MOSFETを用いる時よりもロスは少なくなるが、回路構成では交流電源から出力側へ流れる電流を整流するMOSFETは入力位相が逆になってからオフする制御方法をとっているため貫通電流が流れる可能性があった。

【0007】

そこで、交流電源の位相が切り替わる前に、MOSFETをオフに制御することにより、4個のMOSFETをNch-MOSFETで構成できるようにする全波整流回路の技術が提案されている(特許文献3参照)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平9−131064号公報

【特許文献2】特開2005−295627号公報

【特許文献3】特開2010−178519号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献3の技術においては、負荷と並列にコンデンサを接続する、いわゆるコンデンサインプット型の全波整流回路を構成すると、貫通電流が流れる可能性があった。

【0010】

本技術はこのような状況に鑑みてなされたものであり、特に、コンデンサインプット型の全波整流回路であっても、主要構成部をNch-MOSFETのみで構成し、全波同期整流において、安価な回路構成で、かつ、確実に全波整流を実現できるようにするものである。

【課題を解決するための手段】

【0011】

本技術の一側面の全波整流回路は、交流電源から入力された交流電圧を全波整流する全波整流回路であって、内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第1の端子に接続された第1のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)と、内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第1の端子に接続された第2のMOSFETと、内部の寄生ダイオードにおけるカソードに対応する端子が前記第1のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第2の端子に接続された第3のMOSFETと、内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第2の端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記第2のMOSFETの内部の寄生ダイオードにおけるアノードに対応する端子に接続された第4のMOSFETと、前記交流電源の第1の端子に接続された交流電圧の位相を検知する第1の位相検知回路と、前記交流電源の第2の端子に接続された交流電圧の位相を検知する第2の位相検知回路と、前記第1の位相検知回路の検知結果に基づき、前記第1のMOSFETをオンする第1の制御回路と、前記第2の位相検知回路の検知結果に基づき、前記第3のMOSFETをオンする第2の制御回路と、前記第2および第4のMOSFETに流れる電流値を検知する電流検知回路と、前記電流検知回路の検知結果である電流値が所定値よりも小さくなった場合、前記第1乃至第4のMOSFETのうち、少なくとも1つをオフするように接続された強制遮断回路とを含む。

【0012】

前記第1および前記第3のMOSFETの内部寄生ダイオードのカソードに対応する端子と、前記第2および前記第4のMOSFETの内部寄生ダイオードのアノードに対応する端子との間の電圧によって得られる脈流電圧を平滑するように接続された平滑コンデンサをさらに含ませるようにすることができ、前記電流検知回路には、前記平滑コンデンサと、前記第2および前記第4のMOSFETとの間に電流を検出するための電流検出抵抗と、前記電流検出抵抗に流れる電流値が所定値よりも小さいか否かにより信号を出力するコンパレータとを含ませるようにすることができる。

【0013】

前記コンパレータの最低入力端子は、前記電流検出抵抗を介して前記第2および第4のMOSFETのソース、またはドレインと接続されるようにすることができる。

【0014】

前記強制遮断制御回路には、前記第2および第4のMOSFETの少なくとも1つをオフにする遮断制御回路を含ませるようにすることができる。

【0015】

前記遮断回路には、抵抗、およびトランジスタを含ませるようにすることができ、前記抵抗の一方の端部が前記コンパレータの出力端子に接続され、前記抵抗の他方の端部が前記トランジスタのベースに接続され、前記トランジスタのコレクタが、前記第2および第4のMOSFETのゲートの少なくともそのいずれかに接続されるようにすることができる。

【0016】

前記第1乃至第4のMOSFETは、nチャンネルMOSFETとすることができる。

【0017】

前記第1の制御回路には、前記交流電源の第1の端子の電圧よりも高い電圧を生成する第1のチャージポンプ回路を含ませるようにすることができ、前記第1の位相検知回路の検知結果に基づいて、フォトカプラによって前記第1のチャージポンプ回路より前記第1のMOSFETのゲートに電圧を印加するように接続され、前記第1の端子の電位が前記第2の端子の電位よりも低くならないうちに前記第1のMOSFETのゲートおよびソース間の電圧を所定値より小さくするように接続されるようにすることができる。

【0018】

前記第1のチャージポンプ回路には、第1のダイオードおよび第1のコンデンサを含ませるようにすることができ、前記第1のダイオードのアノードが前記第1のMOSFETの内部寄生ダイオードにおけるカソードに対応する端子、または前記交流電源の第2の端子に接続され、前記第1のダイオードのカソードと前記交流電源の第1の端子との間に第1のコンデンサが接続されるようにすることができる。

【0019】

前記第1のMOSFETのゲートおよびソース間に抵抗を含ませるようにすることができ、前記抵抗の抵抗値は、前記第1の位相検知回路の検知結果で得られるタイミングより、前記交流電源の第1の端子と第2の端子との間の電圧が正から負若しくは負から正に切り替わるタイミングに至るまでの期間内にゲートおよびソース間の電位を第1のMOSFETが確実にオフできる値とすることができる。

【0020】

前記第2の制御回路には、前記交流電源の第2の端子の電圧よりも高い電圧を生成する第2のチャージポンプ回路を含ませるようにすることができ、前記第2の位相検知回路の検知結果に基づいて、フォトカプラによって前記第2のチャージポンプ回路より前記第3のMOSFETのゲートに電圧を印加するように接続され、前記第2の端子の電位が前記第1の端子の電位よりも低くならないうちに前記第3のMOSFETのゲートおよびソース間の電圧を所定値より小さくするように接続されるようにすることができる。

【0021】

前記第2のチャージポンプ回路には、第2のダイオードおよび第2のコンデンサを含ませるようにすることができ、前記第2のダイオードのアノードが前記第3のMOSFETの内部寄生ダイオードにおけるカソードに対応する端子、または前記交流電源の第1の端子に接続され、前記第2のダイオードのカソードと前記交流電源の第2の端子との間に第2のコンデンサが接続されるようにすることができる。

【0022】

前記第3のMOSFETのゲートおよびソース間に抵抗を含ませるようにすることができ、前記抵抗の抵抗値は、前記第2の位相検知回路の検知結果で得られるタイミングより、前記交流電源の第1の端子と第2の端子との間の電圧が正から負若しくは負から正に切り替わるタイミングに至るまでの期間内にゲートおよびソース間の電位を第3のMOSFETが確実にオフできる値とすることができる。

【0023】

本技術の請求項1に記載の全波整流回路を含む電源システムは、力率改善回路と、全波整流された出力に直列接続されたインダクタと、前記インダクタの出力とグランドの間にドレインおよびソースが接続された第5のMOSFETと、前記インダクタの出力と直列に接続されたMOSFETの寄生ダイオードのアノードに対応する端子がインダクタの出力となるように接続された第6のMOSFETとを、請求項1に記載の全波整流回路にさらに含ませるようにすることができ、前記電流検知回路には、前記力率改善回路のグランドと第2および第4のMOSFETの寄生ダイオードにおけるアノードに対応する端子との間の電流値を検知させ、前記強制遮断回路には、前記交流電源の前記電流検知回路の検知結果に基づいて、前記力率改善回路の出力信号を制御して、前記電流値が所定値よりも小さい場合、少なくとも第1乃至第4および第6のMOSFETのうち、少なくとも1つをオフさせるようにすることができる。

【0024】

本技術の一側面の全波整流回路においては、交流電源から入力された交流電圧を全波整流する全波整流回路であって、第1のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)の内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第1の端子に接続され、第2のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第1の端子に接続され、第3のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子が前記第1のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第2の端子に接続され、第4のMOSFETが、内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第2の端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記第2のMOSFETの内部の寄生ダイオードにおけるアノードに対応する端子に接続され、第1の位相検知回路により、前記交流電源の第1の端子に接続された交流電圧の位相が検知され、第2の位相検知回路により、前記交流電源の第2の端子に接続された交流電圧の位相が検知され、第1の制御回路により、前記第1の位相検知回路の検知結果に基づき、前記第1のnチャンネルMOSFETがオンされ、第2の制御回路により、前記第2の位相検知回路の検知結果に基づき、前記第3のnチャンネルMOSFETがオンされ、電流検知回路により、前記第2および第4のMOSFETに流れる電流値が検知され、前記電流検知回路の検知結果である電流値が所定値よりも小さくなった場合、強制遮断回路により、前記第1乃至第4のMOSFETのうち、少なくとも1つがオフされる。

【0025】

すなわち、本技術の全波整流回路は、前記第1の位相検知回路の検知結果に基づき、前記第1のMOSFETがオンされ、前記第2の位相検知回路の検知結果に基づき、前記第3のMOSFETがオンされるので、交流電源の位相が正から負に、または、負から正に切り替わる前後の位相を検出して、位相が切り替わる前に第1のMOSFETおよび第3のMOSFETをオフの状態とすることで、ゲート−ソース間電圧を放電させ、ゲート−ソース間の電圧が放電したタイミングでオンの状態とすることができる。また、電流検知回路により、第2および第4のMOSFETを流れる電流が検知されて、この電流が所定値よりも小さい、位相が切り替わる前後の、電流値が所定値より小さくなるタイミングで、強制遮断回路が第1乃至第4のMOSFETのうち、いずれかをオフにすることができる。この結果、負荷と並列にコンデンサが接続された、いわゆるコンデンサインプット型の全波整流回路においてコンデンサから生じる逆方向の電流を強制的に遮断することができ、貫通電流の発生を抑制することができる。

【発明の効果】

【0026】

本技術によれば、nチャンネルMOSFETのみでもコンデンサインプット型の全波整流を実現することができ、MOSFETを保護することが可能となるので、電力損失を低減すると共に、動作の安定性を向上させることが可能となる。

【図面の簡単な説明】

【0027】

【図1】一般的な全波整流回路の構成例を説明する図である。

【図2】図1の全波整流回路のダイオードをMOSFETに置き換えた全波整流回路の動作を説明する図である。

【図3】図2のMOSFETの内部構成を加えた全波整流回路の動作を説明する図である。

【図4】チャージポンプ回路を説明する図である。

【図5】全波整流回路にチャージポンプ回路を付加する構成例を説明する図である。

【図6】全波整流回路に位相検知回路を付加する構成例を説明する図である。

【図7】全波整流回路における貫通電流の経路を説明する図である。

【図8】nチャンネルMOSFETのみで全波同期整流を実現するための動作を説明する図である。

【図9】全波整流回路における逆流電流の発生経路を説明する図である。

【図10】全波整流回路に力率改善回路を設ける場合の構成例を説明する図である。

【図11】コンデンサインプット型全波整流において発生する波形を説明する波形図である。

【図12】コンデンサインプット型全波整流において発生する波形を説明する波形図である。

【図13】本技術を適用した全波整流回路の第1の実施の形態の構成例を説明する図である。

【図14】図13の全波整流回路における動作を説明する波形図である。

【図15】図13の全波整流回路における動作を説明する波形図である。

【図16】図13の全波整流回路を実現するための詳細な構成例を説明する図である。

【図17】全波整流回路に力率改善回路を付加することにより生じる逆方向の電流の発生経路を説明する図である。

【図18】本技術を適用した全波整流回路の第2の実施の形態の構成例を示す図である。

【発明を実施するための形態】

【0028】

以下、技術を実施するための形態(以下実施の形態とする)について説明する。なお、説明は以下の順序で行なう。

1.第1の実施の形態(コンデンサインプット型全波整流回路)

2.第2の実施の形態(力率改善回路を含む全波整流回路)

【0029】

<1.第1の実施の形態>

[一般的な全波整流回路]

図1は、一般的な全波整流回路の構成例を示す図である。全波整流回路1は、ダイオード11乃至14、および交流電源2、並びに負荷3より構成されている。ダイオード11は、アノードが交流電源2の第1の端子2aに接続されており、カソードが負荷3の一方の端子に接続されている。また、ダイオード12は、アノードが負荷3の他方の端子に接続されており、カソードが交流電源2の第1の端子2aに接続されている。ダイオード13は、アノードが交流電源2の第2の端子2bに接続されており、カソードが負荷3の一方の端子に接続されている。また、ダイオード14は、アノードが負荷3の他方の端子に接続されており、カソードが交流電源2の第2の端子2bに接続されている。

【0030】

このような構成により、交流電源2の第1の端子2aが第2の端子2bよりも電圧が高い場合(この場合の位相を0°乃至180°であるものとする場合)、図1中の点線で示される経路で電流が流れ、負荷3に直流の電力が供給される。また、交流電圧2の第2の端子2bが第1の端子2aよりも電圧が高い場合(位相が180°乃至360°の場合)、図1中の実線で示される経路で電流が流れ負荷3に直流の電力が供給される。

【0031】

[MOSFETを用いた全波整流回路]

ところで、図1の全波整流回路1は、4個のダイオード11乃至14から構成されているが、ダイオードは、発生する熱等により生じるロスが問題となることが知られている。そこで、ダイオードの構成をMOSFETに置換することで、ダイオードロスの問題を解決させることができる。

【0032】

図2は、ダイオード11乃至14に代えて、MOSFET21乃至24を用いるようにした、全波整流回路1の構成例を示している。

【0033】

すなわち、上述した位相が0°乃至180°の場合、MOSFET21,24がオン、かつ、MOSFET22,23がオフの状態とされ、位相が180°乃至360°の場合、MOSFET21,24がオフ、かつ、MOSFET22,23がオンされるように、MOSFET21乃至24が制御されると、図1における全波整流回路と等価な回路を実現させることができ、この場合、ダイオードが全てMOSFETとされたことにより、ダイオードロスの問題が解消されることになる。この様に、MOSFET21乃至24のオン、またはオフを同期して制御し、全波整流を実現する回路を、一般に、全波同期整流回路という。以降においては、全波同期整流回路を単に全波整流回路とも称するものとし、同期整流するものとして説明を進めるものとする。

【0034】

[寄生ダイオード]

MOSFETは、内部に寄生ダイオード(ボディダイオード)と呼ばれるダイオードが存在する。図3は、MOSFET21乃至24のそれぞれの寄生ダイオードをダイオード31乃至34として回路図上に付記した全波整流回路1の構成例を示している。すなわち、ダイオード31は、MOSFET21の内部に寄生するダイオードであり、アノードが交流電源2の第1の端子2aに接続され、カソードが負荷3の一方の端子に接続される。ダイオード32は、MOSFET22の内部に寄生するダイオードであり、アノードが負荷3の他方の端子に接続され、カソードが交流電源2の第1の端子2aに接続される。ダイオード33は、MOSFET23の内部に寄生するダイオードであり、アノードが交流電源2の第2の端子2bに接続され、カソードが負荷3の一方の端子に接続される。ダイオード34は、MOSFET24の内部に寄生するダイオードであり、アノードが負荷3の他方の端子に接続され、カソードが交流電源2の第2の端子2bに接続される。

【0035】

これらのダイオード31乃至34は、それぞれに対応するMOSFET21乃至24がオフにされたとしても、電流が流れることになり、結果として、上述した図1の4個のダイオードからなる全波整流回路における場合のダイオード11乃至14と同様に機能する。尚、寄生ダイオードであるダイオード31乃至34は、MOSFET21乃至24の動作特性上、そのようなダイオードが仮想的に存在すると考えれば回路上で表記できるというものであって、ダイオードとしての回路が実在するものではない。

【0036】

MOSFETは、nチャンネルMOSFETとpチャンネルMOSFETの2種類が存在し、MOSFETがオンした際の抵抗値は、nチャンネルMOSFETの方が、pチャンネルMOSFETよりも小さい事が一般に知られている。nチャンネルMOSFETは、ゲートの電圧がソースの電圧よりも一定以上高くなるときオンになる。また、nチャンネルMOSFETにおいて、内部の寄生ダイオードのアノードに対応する端子はソースである。また、pチャンネルMOSFETは、ゲートの電圧がソースの電圧よりも一定以上低くなるときオンする。また、pチャンネルMOSFETにおいて、内部の寄生ダイオードのアノードに対応する端子はドレインである。従って、例えば、MOSFET21にnチャンネルMOSFETを用いる際には、ソースを第1の端子2aに接続し、pチャンネルMOSFETを用いる際にはドレインを第1の端子2aに接続する。すなわち、nチャンネルMOSFETとpチャンネルMOSFETとでは接続方法が異なる。尚、寄生ダイオード31乃至34は、以降の図中において記載しない場合においても、図3に示されるように構成されるものとして説明を進めるものとする。

【0037】

上述の理由から、MOSFET22,24にpチャンネルMOSFETが用いられた場合、交流電源2の第1の端子2a、および第2の端子2bよりも低い電圧が必要であるため、駆動する上で制御に困難が生じる。また、MOSFET22,24にnチャンネルMOSFETが用いられた場合、ソースに対応する端子の電圧は、交流電源2の第1の端子2aまたは第2の端子2bの電圧よりも低い電圧であるため、nチャンネルMOSFETを駆動するにあたり、制御が容易であると考えられる。

【0038】

また、MOSFET21,23にpチャンネルMOSFETが用いられた場合、交流電源2の第1の端子2aまたは第2の端子2bは、ソースよりも低いため駆動にあたり、制御が容易であると考えられる。一方、MOSFET21,23にnチャンネルMOSFETが用いられた場合、上述の通りソースが交流電源2の第1の端子2aまたは第2の端子2bに接続されるため、第1の端子2aまたは第2の端子2bよりも高い電圧が必要となる。

【0039】

しかしながら、前述の通り、nチャンネルMOSFETの方がpチャンネルMOSFETよりもオン抵抗が小さいので、MOSFET21,23にnチャンネルMOSFETが用いられるようにした方がロスは低減されることになる。そこで、MOSFET21,23にnチャンネルMOSFETを用いるための技術としてチャージポンプ回路が考えられる。

【0040】

[チャージポンプ回路]

ここで、図4を参照して、チャージポンプ回路について説明する。図4の回路は、電源VDD1の正端子にスイッチS1の一方の端部が接続されており、負端子に切替スイッチS2の一方の切替端子、電源VDD2の負端子、およびコンデンサC2の他方の端子が接続されている。スイッチS1は、一方の端子が電源VDD1の正端子に接続され、他方の端子がコンデンサC1の一方の端子、およびスイッチS3の一方の端子に接続されている。コンデンサC1の一方の端子は、スイッチS1の他方の端子、および、スイッチS3の一方の端子に接続される。コンデンサC1の他方の端子は、切替スイッチS2の一方の端子に接続される。スイッチS2の一方の端子は、コンデンサC1の他方の端子に接続され、一方の切替端子は、電源VDD1,VDD2の負端子、およびコンデンサC2の他方の端子に接続されている。スイッチS2の他方の切替端子は、電源VDD2の正端子に接続されている。電源VDD2の正端子は、切替スイッチS2の他方の切替端子に接続され、負端子は、電源VDD1の負端子、切替スイッチS2の一方の切替端子、およびコンデンサC2の他方の端子に接続されている。スイッチS3の一方の端子は、スイッチS1の他方の端子、およびコンデンサC1の一方の端子に接続されており、他方の端子は、コンデンサC2の一方の端子に接続されている。コンデンサC2の一方の端子は、スイッチS3の他方の端子に接続されており、他方の端子は、電源VDD1,VDD2の負端子、および切替スイッチS2の一方の切替端子に接続されている。尚、図4においては、左部、および右部のいずれにおいても同一の回路が示されているが、異なる動作状態を示している。また、電源VDD1,VDD2は、いずれも電圧VDDの直流電源である。

【0041】

例えば、図4の左部に示されるように、スイッチS1がオンとされ、切替スイッチS2が一方の切替端子に接続され、スイッチS3がオフとされる場合、コンデンサC1は電源VDD1の電圧VDDによってVDDに充電される。この状態から、図4の右部で示されるように、スイッチS1がオフとされ、切替スイッチS2が他方の切替端子に接続され、スイッチS3がオンとされる場合、コンデンサC1および電源VDD2とは、直列接続されることになるので、図4の右部における点aの電圧は、VDDの2倍となる。同時にスイッチS3がオンとされることにより、実質的に電圧VDD×2に昇圧された電圧が得られるので、コンデンサC2は、電圧VDD×2の電圧で充電される。この様に蓄えた電荷を利用して入力電圧よりも高い電圧を生成する回路が、チャージポンプ回路である。この回路を応用すれば、交流電源2の第1の端子2aまたは第2の端子2bよりも高い電圧を生成する事が可能となる。

【0042】

図5は、チャージポンプ回路を追加した全波整流回路1の構成例を示している。尚、図5において、図3における全波整流回路1と同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。図5の全波整流回路1において、図3の全波整流回路1と異なる点は、ダイオード51およびコンデンサ52を直列に接続し、MOSFET21に並列に接続した点である。ダイオード51のアノードは、MOSFET21の寄生ダイオード31のカソードに対応する端子に接続されており、カソードは、コンデンサ52の一方の端子に接続されている。また、コンデンサ52は、一方の端子がダイオード51のカソードに接続されており、他方の端子がMOSFET21の寄生ダイオード31のアノード側の端子に接続されている。

【0043】

すなわち、図5で示されるように、MOSFET21に並列に接続された、直列接続されているダイオード51およびコンデンサ52が、チャージポンプ回路として構成される。図5の全波整流回路1により、位相が180°乃至360°となる時、図5の実線で示される経路でコンデンサ52を第2の端子2bおよび第1の端子2aの電位差分だけ充電することが可能となる。また、次に位相が0°乃至180°となる時、コンデンサ52には電荷が蓄積されているので先ほどと同じ原理で入力電圧よりも高い電圧が得られる。得られる電圧は最高で入力電圧の最高値分となり、例えば、交流電源2の電源電圧がAC24Vの場合、AC24V×1.41≒33Vが得られる。次に、位相が0°乃至180°となる時、上記コンデンサ52に蓄えられた電圧を利用してMOSFET21をオンすれば良い。尚、ダイオード51のアノードについては、交流電源2の第2の端子2bに直接接続するようにしてもよい。

【0044】

そこで、上述したような位相のタイミングにおいて、MOSFET21をオンできるように制御する構成として、例えば、図6で示されるような全波整流回路1が考えられる。

【0045】

図6の全波整流回路1において、図5の全波整流回路1と同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。図6の全波整流回路1において、図5の全波整流回路1と異なる点は、抵抗61、フォトダイオード62、フォトカプラ63、および抵抗64を新たに設けた点である。抵抗61、およびフォトダイオード62は、抵抗61の一方の端子が交流電源2の第1の端子2aに接続され、他方の端子がフォトダイオード62のアノードに接続される。フォトダイオード62は、アノードが抵抗61の他方の端子に接続され、カソードが交流電源2の第2の端子2bに接続される。そして、フォトカプラ63は、フォトダイオード62が発光する光を受光できるように物理的に構成されている。すなわち、抵抗61、フォトダイオード62は、直列に接続されて、交流電源2の第1の端子2aおよび第2の端子2bを跨ぐように接続されている。また、フォトカプラ63は、フォトダイオード62が発光するとき、その光を受光でき、フォトカプラ63のエミッタがMOSFET21のゲートに接続され、コレクタが抵抗64の一方の端子に接続され、抵抗64の他方の端子がダイオード51のカソードおよびコンデンサ52の一方の端子と接続される。

【0046】

このように構成されることにより、交流電源2の第1の端子2a、および第2の端子2bのそれぞれの出力電圧の位相に伴って以下のように動作する。すなわち、位相が180°乃至360°となる時、フォトダイオード62は発光しない。従って、この間、図5で示されるように、コンデンサ52が第2の端子2bと第1の端子2aとの電位差分だけ充電される。そして、位相が0°乃至180°となる時、フォトダイオード62は発光する。従って、この間、フォトカプラ63はオンの状態となり、MOSFET21のゲートには、ダイオード51およびコンデンサ52より構成されるチャージポンプ回路で得られた、ソース(第1の端子2a)よりも高い電圧が印加されることになるので、MOSFET21がオンされる。すなわち、抵抗61、フォトダイオード62、フォトカプラ63、および抵抗64が、位相が0°乃至180°であるか、または、180°乃至360°であるかを検知する、位相検知回路を構成している。そして、この位相検知回路の検知結果に基づいて、チャージポンプ回路がコンデンサ52に電圧を充電させると共に、MOSFET21のオン、またはオフが制御されている。

【0047】

尚、MOSFET23においても、MOSFET21におけるチャージポンプ回路、並びに、抵抗61、フォトダイオード62、フォトカプラ63、および抵抗64を設ける。ただし、この場合、MOSFET23がオンされるタイミングが、MOSFET21がオンされるタイミングと180°異なるように構成される必要がある。

【0048】

ところで、MOSFETには入力容量が必ず存在し、一般的にオン抵抗が低いものの方が入力容量は大きい。仮に、第1の端子2aの電圧が、第2の端子2bの電圧よりも低くなっても、MOSFET21がオンしたままであった場合、MOSFET23がオンしていない状態であっても、図7の点線で示されるように、MOSFET23の寄生ダイオード33を通るループで貫通電流が流れてしまう恐れがある。

【0049】

このような貫通電流は、多大なため素子を破壊する恐れが高い。そこで図8で示されるように半周期の一部分だけMOSFET21のゲートを印加し、位相が反転するまで時間の猶予を作り、このΔtの間に完全にコンデンサ52に充電された電荷を放電する事によって、上述した貫通電流を防ぐ事ができる。尚、図8は、第1の端子2aの出力電圧の波形であり、時刻t0乃至t3が、位相が0°乃至180°を示しており、時刻t3以降が位相が180°乃至360°である。すなわち、位相が0°乃至180°のうち、時刻t1乃至t2において、MOSFET21のゲートが印加され、位相が切り替わる近傍の時刻t2乃至t3のΔtにおいては、MOSFET21のゲートが印加されない。すなわち、第1の端子2aの電圧が、第2の端子2bの電圧よりも低くなっても、MOSFET21はオフの状態となるため、図7の点線で示されるような経路による貫通電流は発生しない。尚、この技術については、特開2010−178519号公報により本出願人により出願されている。詳細については、特開2010−178519号公報を参照されたい。

【0050】

しかしながら、例えば、図9で示されるように、出力にコンデンサが追加されると動作上、障害が発生する。すなわち、出力に大きな容量のコンデンサがある場合においては、MOSFETは双方向に電流を流す素子であるため、電源の構成がコンデンサインプット型のとき、例えば、MOSFET21がオンしている間、交流電源2の第1の端子2aは、交流電源2の出力電圧Voにクランプされる。一方、MOSFET21がオンの状態となる、位相が0°乃至180°のタイミングにおいては、MOSFET24もオンの状態とされるので、交流電源2の第2の端子2bはグランド電位にクランプされる。しかしながら、入力電圧は、位相が90°乃至180°の間、交流電源2の出力電圧は減少方向になるため、図9の点線で示されるように、交流電源2を通じて出力電圧を放電する方向に電流が逆流する。従って、結果的に出力電圧は直流の状態を保持できないため、逆流した過大な電流によって、各種の回路を保護するためにヒューズ等が設けられていると、溶断されてしまう可能性がある。

【0051】

尚、上述した特開2010−178519号公報に開示された技術においては、図10で示されるように、インダクタ92からなる力率改善回路を後段に備えた回路が想定されているため、ダイオード93が設けられている。図10の全波整流回路1においては、図2の全波整流回路1と同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。すなわち、図10の全波整流回路1において、図2の全波整流回路1と異なるのは、平滑コンデンサ81、MOSFET91、インダクタ92、およびダイオード93を備えた点である。

【0052】

平滑コンデンサ81は、負荷3に対して並列に接続されている。インダクタ92は、一方の端子がMOSFET21,23の寄生ダイオードのカソードに対応する端子に接続され、他方の端子がMOSFET91の寄生ダイオードのカソードに対応する端子に接続される。ダイオード93は、アノードがインダクタ92の他方の端子、およびMOSFET91の寄生ダイオードがカソードに対応する端子に接続され、カソードが平滑コンデンサ81の一方の端子、および負荷3の一方の端子に接続される。MOSFET91は、寄生ダイオードのカソードに対応する端子が、インダクタ92の他方の端子、およびダイオード93のアノードに接続され、寄生ダイオードのアノードに対応する端子が、MOSFET22,24の寄生ダイオードのアノードに対応する端子、平滑コンデンサ81の他方の端子、および負荷3の他方の端子に接続されている。このような構成により、MOSFET91がオンオフに制御されることで、力率改善回路が実現される。

【0053】

このダイオード93の効果により平滑コンデンサ81の出力に蓄えられた電荷が逆流する事は無い。しかしながら、力率改善回路は必ずしも必要な構成ではないため仕様によっては力率改善回路が要らない場合も多々あり、その場合において同期整流が不可能となってしまう。

【0054】

ところで、図9で示されるような、コンデンサインプット型の全波整流回路1の場合、図11,図12で示される通り、交流電源2より出力される出力電圧の1周期に対して電力が伝達される期間は短くなる。尚、図11,図12においては、時刻t0乃至t14が出力電圧の1周期である。また、電力が伝達される期間は、時刻t11乃至t12であり、時刻t12乃至t13は、電力が伝達されない期間となる。

【0055】

これはMOSFET21,23とMOSFT22,24との間に接続された平滑コンデンサ81で整流された脈流電圧を直流に置き換えるためであり、交流電源2の第1の端子2aの出力電圧よりも高い状態の時のみ交流電源2より電流が流れる(電力が伝達される)。ここで、図11,図12において、点線は、交流電源2の第1の端子2aの出力電圧を、太実線は第1の端子2aの電流値を、細実線は、平滑コンデンサ81の充電電圧を、一点鎖線は、MOSFET21のゲートの印加電圧をそれぞれ示している。

【0056】

また、図6を参照して説明した位相検知回路により、例えば、図12の一点差線で示されるように、交流電源2の第1の端子2aの1周期の間の時刻t31乃至t32で示される一定期間のみMOSFET21はオン状態にある。MOSFET21は、特性上ドレインからソース方向にも、ソースからドレイン方向にも双方向に電流を流す素子であるため、MOSFET21がオンしている間、図9で示されるように、交流電源2の第1の端子2aと平滑コンデンサ81の低電位側(以後グランドと称する)の間の電圧は出力電圧とほぼ同じ電圧が印加される。そのため、MOSFET21をnチャンネルMOSFETで構成するものとし、この状態においてMOSFET24もオンの状態にあると、図9で示されるように、平滑コンデンサ81に蓄えられた電荷を放電する経路で電流が流れる事になる。

【0057】

[本技術を適用した全波整流回路]

上述した平滑コンデンサ81により発生する逆流電流の発生を防止することで、nチャンネルMOSFETのみによりコンデンサインプット型の全波整流回路を実現することができる。

【0058】

図13は、上述した平滑コンデンサ81により発生する逆流電流の発生を防止することで、nチャンネルMOSFETのみにより実現されるコンデンサインプット型の全波整流回路の構成例を示している。尚、図13の全波整流回路1において、図9における全波整流回路1と同様の機能を備えた構成については、同一の符号を付しており、その説明は、適宜省略するものとする。

【0059】

すなわち、図13の全波整流回路1において、図9の全波整流回路1と異なる点は、新たに、抵抗101乃至103、コンパレータ104、およびトランジスタ105,106を新たに設けた点にある。

【0060】

抵抗101は、一方の端子が、MOSFET22,24の寄生ダイオードのアノード側の端子に接続され、他方の端子が、負荷3、および平滑コンデンサ81のそれぞれの他方の端子、およびコンパレータ104の反転入力端子に接続されている。抵抗101は、MOSFET22,24と平滑コンデンサ81との間を流れる電流検出回路として機能し、検出した両端間で発生する電圧値に対応する電圧がコンパレータ104の反転入力端子に入力される。

【0061】

抵抗102は、一方の端子が、抵抗103の他方の端子、およびコンパレータ104の非反転入力端子に接続され、他方の端子が、MOSFET22,24の寄生ダイオードのアノード側の端子、抵抗101の一方の端子、およびトランジスタ105,106のエミッタに接続されている。抵抗103は、一方の端子が、MOSFET21,23の寄生ダイオードのカソード側の端子、並びに、平滑コンデンサ81、および負荷3の一方の端子に接続され、他方の端子が、抵抗102の一方の端子、およびコンパレータ104の非反転入力端子に接続されている。すなわち、抵抗102,103は、コンパレータ104の非反転入力端子に入力する電圧の分圧抵抗を構成している。従って、抵抗102,103のそれぞれ抵抗値は、コンパレータ104の非反転入力端子に入力する電圧が所定の閾値となるように設定される。

【0062】

コンパレータ104は、非反転入力端子が抵抗102の一方の端子、および抵抗103の他方の端子に接続され、反転入力端子が抵抗101の他方の端子、および平滑コンデンサ81、および負荷3の他方の端子に接続され、出力端子がトランジスタ105,106のベースに接続されている。すなわち、コンパレータ104は、電流検出回路を構成する抵抗101の両端電圧の検出結果と、抵抗102,103の分圧比により設定される所定の閾値とを比較し、電流検出回路を構成する抵抗101の両端電圧の検出結果が所定の閾値として設定される電圧より低下するとトランジスタ105,106をオンにする。

【0063】

トランジスタ105,106は、それぞれのベースがコンパレータ104の出力端子に接続され、それぞれのエミッタがMOSFET22,24の寄生ダイオードのアノード側の端子に接続され、それぞれのコレクタがMOSFET22,24のゲートに接続されている。すなわち、トランジスタ105,106は、コンパレータ104によりオンされると、MOSFET22,24を強制的にオフにする。尚、図13においては、寄生ダイオード31乃至34が表記されていないが、上述したように、図3で示されるように内部に寄生して存在している。

【0064】

[図13の全波整流回路の動作説明]

次に、図14,図15のタイミングチャートを参照して、交流電源2の第1の端子2aより出力される交流電圧の1周期分の波形に基づいて、図13の全波整流回路1の動作について説明する。尚、図14において、実線で示される波形は、MOSFET22,24を制御するためにトランジスタ105,106により制御されMOSFET22,24のゲートに印加される電圧値を、点線で示される波形は、交流電源2の第1の端子2aの出力電圧の波形を、一点鎖線で示される波形は、MOSFET21または23のゲートに供給される位相検知回路からの入力電圧を、2点鎖線で示される波形は、第1の端子2aの電流値を、それぞれ示している。また、図15は、図14における時刻T5,T6近傍を拡大した波形図である。

【0065】

時刻T0乃至T1において、MOSFET21乃至24は、いずれもオンしておらず、交流電源2からMOSFET21乃至24のそれぞれの内部に存在する寄生ダイオード31乃至34が逆流を防止しており、負荷3への電力供給が行われない。

【0066】

時刻T1乃至T2において、MOSFET21は、上述した位相検知回路より、ゲートに信号が送り込まれて、オフからオンに変化する。このとき、MOSFET22乃至24はいずれもオフの状態が維持されている。MOSFET21乃至24、またはMOSFET22乃至24の内部に存在する寄生ダイオード31乃至34、または寄生ダイオード32乃至34が逆流を防止しており、負荷3に対して電力は供給されていない。すなわち、このタイミングにおいては、位相検知回路からMOSFET21のゲートに対して信号が送られていない状態であっても実質的に同様の状態となる。そして、時刻T2乃至T3においては、この状態が継続される。

【0067】

時刻T3乃至T4において、MOSFET21は、上述した位相検知回路より、ゲートに信号が送り込まれることにより、オンの状態となっている。また、MOSFET22乃至24はいずれもオフしている。このとき、交流電源2の第1の端子2aおよび第2の端子2b間の電圧は、平滑コンデンサ81の電圧よりも高くなるため、交流電源2の第1の端子2aからMOSFET21を介して、負荷3に電流が流れ、MOSFET24の寄生ダイオード34を介して、交流電源2の第2の端子2bへ帰還電流が流れる。このため、第1の端子2aを流れる電流量が急激に増大するので、対応して抵抗101の両端電圧が急激に上昇する。尚、この時、MOSFET21もオフするように制御し、交流電源2の第1の端子2aからMOSFET21の寄生ダイオード31を介して、負荷3側に電力を供給するようにし、MOSFET24の寄生ダイオード34を介して交流電源2の第2の端子2bへと帰還電流が流れるように制御してもよい。さらに、MOSFET21をオフするようにし、MOSFET24がオンするように制御することも可能であり、その場合、MOSFET21の寄生ダイオード31を介して、負荷3側に電力が供給され、MOSFET24を介して交流電源2の第2の端子2bへ帰還電流が流れる。

【0068】

時刻T4乃至T5において、MOSFET21は、位相検知回路からゲートに信号が供給されるのでオンにされ、同時に、電流検知回路を構成する抵抗101の両端電圧が、コンパレータ104の非反転入力端子の電圧を超えることにより、コンパレータ104からの出力がオフにされ、これに伴ってトランジスタ105,106もオフにされるので、MOSFET22,24は、いずれもオンとされる。交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の電圧よりも高いため、交流電源2の第1の端子2aからMOSFET21を介して負荷3側に電力が供給され、MOSFET24を介して交流電源2の第2の端子2bへ帰還電流が流れる。

【0069】

時刻T5乃至T6において、MOSFET21は、上述した位相検知回路より、ゲートに信号が送り込まれることにより、オンされている。しかしながら、電流検出回路を構成する抵抗101を流れる電流の変化に伴って、減少し、図15で示されるように、時刻T5の直前の時刻T5’において、コンパレータ104は、反転入力端子に供給される電圧が、非反転入力端子に入力される閾値となる電圧よりも低くなるので、出力端子より信号を出力する。これに応じてトランジスタ105,106がオンとされるため、MOSFET22,24は、オフとされる。したがって、時刻T5の時点においては、MOSFET22乃至24はいずれもオフの状態であり、交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の充電電圧よりも高いため、交流電源2の第1の端子2aからMOSFET21を通り負荷3側に電力が供給されて、MOSFET24の寄生ダイオード34を通って交流電源2の第2の端子2bへ帰還電流が流れる。尚、この時、MOSFET21をオフに制御して、MOSFET24のみをオンに制御するようにしてもよいし、または、MOSFET21乃至24を全てオフに制御してもよい。

【0070】

時刻T6乃至T7において、MOSFET21がオンにされ、MOSFET22乃至24がいずれもオフとされているが、MOSFET22乃至24の内部寄生ダイオード32乃至34が逆流を防止しており、負荷3に対して電力の供給が行われない。尚、この時、MOSFET21をオフに制御して、MOSFET24のみをオンに制御してもよいし、または、MOSFET21乃至24の全てをオフに制御してもよい。

【0071】

時刻T7乃至T8において、MOSFET21が、位相検知回路からの信号がなくなり、オンからオフへ推移する。MOSFET22乃至24はいずれもオフのままであり、MOSFET21乃至24、またはMOSFET22乃至24の内部寄生ダイオード31乃至34、または32乃至34が逆流を防止しており、負荷3への電力供給は行われない。

【0072】

時刻T8乃至T10において、MOSFET21乃至24はいずれもオンしておらず、交流電源2からMOSFET21乃至24の内部寄生ダイオード31乃至34が逆流を防止しており、負荷3への電力供給がなされていない。尚、時刻T9において、第1の端子2aの出力電圧が、正から負に反転する。

【0073】

時刻T10乃至T11において、MOSFET23は、位相検知回路からゲートに供給される信号により、オフからオンに推移し、MOSFET21,22,24はいずれもオフのままであり、MOSFET21乃至24、または21,22,24の内部寄生ダイオード31乃至34、または31,32,34が逆流を防止しており、負荷3への電力供給は行われない。尚、この時、MOSFET23のゲートへの位相検知回路から供給される信号が送られないような制御とするようにしてもよい。

【0074】

時刻T11乃至T12において、MOSFET23は、位相検知回路からゲートに供給される信号により、オンしており、MOSFET21,22,24はいずれもオフのままであり、MOSFET21,22,24の内部寄生ダイオード31,32,34が逆流を防止しており、負荷3への電力供給は行われない。尚、この時、MOSFET23もオフしていても同様の効果が得られる。)

【0075】

時刻T12乃至T13において、MOSFET23は、位相検知回路からゲートに供給される信号により、オンしており、MOSFET21,22,24はいずれもオフとされている。また、交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の電圧よりも高くなるため、交流電源2の第2の端子2bからMOSFET23を介して負荷3側に電力が供給され、MOSFET22の寄生ダイオード32を介して交流電源2の第1の端子2aへ帰還電流が流れる。尚、この時、MOSFET23もオフするようにし、MOSFET23の寄生ダイオード33を介して負荷3側に電力を供給させ、MOSFET22の寄生ダイオード32を介して交流電源2の第2の端子2bへ帰還電流が流れるようにしてもよい。さらに、MOSFET23をオフするようにし、MOSFET22がオンするように制御するようにしてもよい。その場合、MOSFET23の寄生ダイオード33を介して負荷3側に電力が供給され、MOSFET22を介して交流電源2の第2の端子2bへ帰還電流が流れる。

【0076】

時刻T13乃至T14において、MOSFET22,23がオンしており、交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の電圧よりも高いため、交流電源2の第2の端子2bからMOSFET23を介して負荷3側に電流が流れMOSFET22を介して交流電源2の第1の端子2aへ帰還電流が流れる。

【0077】

時刻T14乃至T15において、MOSFET23がオンしており、MOSFET21,22,24はいずれもオフしており、交流電源2の第1の端子2aおよび第2の端子2b間の電圧が平滑コンデンサ81の充電電圧よりも高いため、交流電源2の第2の端子2bからMOSFET23を介して負荷3側に電流が流れ、MOSFET22の寄生ダイオード32を介して交流電源2の第1の端子2aへ帰還電流が流れる。すなわち、時刻T5乃至T6と同様に、電流検出回路を構成する抵抗101を流れる電流の変化に伴って、減少し、時刻T15の直前のタイミング(時刻T5’に対応するタイミング)において、コンパレータ104は、反転入力端子に供給される電圧が、非反転入力端子に入力される閾値となる電圧よりも低くなるので、出力端子より信号を出力する。これに応じてトランジスタ105,106がオンとされるため、MOSFET22,24は、オフとされる。尚、この時、MOSFET23をオフしてMOSFET22のみオン制御するようにしても良いし、MOSFET21乃至24の全てをオフとするように制御するようにしてもよい。

【0078】

時刻T15乃至T16において、MOSFET23がオンにされており、MOSFET21,22,24はいずれもオフされており、MOSFET21,22,24の内部寄生ダイオード31,32,34が逆流を防止しており、負荷3への電力供給は行われない。尚、この時、MOSFET23をオフしてMOSFET22のみオンにするように制御してもよいし、MOSFET21乃至24を全てオフとするように制御してもよい。

【0079】

時刻T16乃至T17において、MOSFET23は、オンからオフへと推移し、MOSFET21,22,24はいずれもオフにされており、MOSFET21乃至24、または21,22,24の内部寄生ダイオード31乃至34、または31,32,34が逆流を防止しており、負荷3への電力供給は行われない。

【0080】

時刻T17乃至T18において、MOSFET21乃至24は全てオンにされておらず、交流電源2からMOSFET21乃至24は全て内部寄生ダイオード31乃至34が逆流を防止しており、負荷3への電力供給は行われない。

【0081】

すなわち、時刻T4乃至T5で示されるように、平滑コンデンサ81に蓄えられた電荷を放電する担い手であったnチャンネルMOSFET21,24若しくはnチャンネルMOSFET22,23の片方、または両方をオフする事によって逆流経路を完全に遮断することができる。

【0082】

また、nチャンネルMOSFET21乃至24の内部には必ずソースからドレイン方向に寄生ダイオードが存在する。その為、平滑コンデンサ81の電荷が0状態で電源投入されたとしても、定常状態に推移するまでの間はMOSFET21乃至24の寄生ダイオード31乃至34が電流伝達の担い手となる。つまりは、電流の担い手であったMOSFET21乃至24を急遽オフしたとしても、MOSFET21乃至24の寄生ダイオード31乃至34を介して電流を流すため、逆起電力が発生して阻止が破壊されたりする事はない。

【0083】

このような構成により、電流が反転する前にMOSFET22,24をオフする事ができるので、コンデンサインプット型の同期整流が可能となる。

【0084】

[図13の全波整流回路を応用した全波整流回路]

次に、図16を参照して、図13の全波整流回路1を実現するための詳細な全波整流回路1の構成例について説明する。尚、図16の全波整流回路1において、図6,図13の全波整流回路1において同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。

【0085】

すなわち、図16の全波整流回路1におけるnチャンネルMOSFET21は、ソースが交流電源2の第1の端子2aに接続される。nチャンネルMOSFET22は、ドレインが交流電源2の第1の端子2aに接続される。nチャンネルMOSFET23は、ドレインがnチャンネルMOSFET21のドレインに接続され、ソースが交流電源2の第2の端子2bに接続される。nチャンネルMOSFET24は、ドレインが交流電源2の第2の端子2bに接続され、ソースがnチャンネルMOSFET22のソースに接続される。

【0086】

ダイオード51−1は、アノードがnチャンネルMOSFET21のドレインと接続される。コンデンサ52−1は、ダイオード51−1のカソードと交流電源2の第1の端子2aの間の電圧によりチャージされ、ダイオード51−1と共にMOSFET21を駆動させるためのチャージポンプ回路を構成する。ダイオード51−2は、アノードがnチャンネルMOSFET23のドレインと接続される。コンデンサ52−2は、ダイオード51−2のカソードと交流電源2の第2の端子2bの間の電圧によりチャージされ、ダイオード51−2と共に、MOSFET23を駆動させるためのチャージポンプ回路を構成する。

【0087】

フォトダイオード62−1は、ダイオード62a−1、ツェナーダイオード255−1、および抵抗61−1と共に、交流電源2の第1の端子2aに接続された、交流電圧の位相を検知するMOSFET21を駆動させるための位相検知回路を構成する。

【0088】

NPNトランジスタ253−1は、コレクタにコンデンサ52−1が接続され、エミッタにnチャンネルMOSFET21のゲートが接続され、ベースにツェナーダイオード252−1を介して交流電源2の第1の端子2aと接続される。抵抗64−1は、一方の端子が、コンデンサ52−1と接続され、他方の端子がフォトカプラ63−1の受光側のコレクタに接続される。フォトカプラ63−1の受光側のエミッタは、NPNトランジスタ253−1のベースに接続される。抵抗251−1、ツェナーダイオード252−1、NPNトランジスタ253−1、コンデンサ52−1、フォトカプラ63−1、および抵抗64−1は、MOSFET21を駆動させるための位相検知回路の検知結果、すなわち、フォトダイオード62−1の発光の有無に基づいて、nチャンネルMOSFET21をオンする信号を送る制御回路を構成する。

【0089】

このnチャンネルMOSFET21をオンする信号を送る制御回路は、MOSFET21を駆動させるための位相検知回路の検知結果であるフォトダイオード62−1の発光状態に基づいて、フォトカプラ63−1によってMOSFET21を駆動させるチャージポンプ回路よりMOSFET21のゲートに電圧を印加するように接続され、第1の端子2aの電位が第2の端子2bの電位よりも低くならないうちにMOSFET21のゲートおよびソース間の電圧を所定値より小さくするように制御する。

【0090】

抵抗254−1は、nチャンネルMOSFET21のソース−ゲート間に接続され、MOSFET21の放電回路を構成する。放電回路を構成する抵抗254−1の抵抗値は、MOSFET21を駆動させる位相検知回路の検知結果で得られるタイミングより、交流電源2の第1の端子2aと第2の端子2bとの間の電圧が、正から負または負から正に切り替わるタイミングに至るまでの期間内にゲート−ソース間の電位をMOSFET21が確実にオフできる値とされる。

【0091】

フォトダイオード62−2は、ダイオード62a−2、ツェナーダイオード255−2、および抵抗61−2と共に、交流電源2の第2の端子2bに接続された、交流電圧の位相を検知するMOSFET23を駆動させるための位相検知回路を構成する。

【0092】

NPNトランジスタ253−2は、コレクタがコンデンサ52−2に接続され、エミッタがnチャンネルMOSFET23のゲートに接続され、ベースがツェナーダイオード252−2を介して、交流電源2の第2の端子2bと接続される。抵抗64−2は、一方の端子が第2のコンデンサ52−2と接続され、他方の端子がフォトカプラ63−2の受光側のコレクタに接続される。フォトカプラ63−2の受光側のエミッタは、NPNトランジスタ253−2のベースと接続される。抵抗251−2、ツェナーダイオード252−2、NPNトランジスタ253−2、コンデンサ52−2、フォトカプラ63−2、および抵抗64−2は、MOSFET23を駆動させるための位相検知回路の検知結果、すなわち、フォトダイオード62−2の発光の有無に基づいて、nチャンネルMOSFET23をオンする信号を送る制御回路を構成する。

【0093】

このnチャンネルMOSFET23をオンする信号を送る制御回路は、MOSFET23を駆動させるための位相検知回路の検知結果であるフォトダイオード62−2の発光状態に基づいて、フォトカプラ63−2によってMOSFET23を駆動させるチャージポンプ回路よりMOSFET23のゲートに電圧を印加するように接続され、第2の端子2bの電位が第1の端子2aの電位よりも低くならないうちにMOSFET23のゲートおよびソース間の電圧を所定値より小さくするように制御する。

【0094】

抵抗254−2は、nチャンネルMOSFET23のソース−ゲート間に接続され、MOSFET23の放電回路を構成する。放電回路を構成する抵抗254−2の抵抗値は、MOSFET23を駆動させる位相検知回路の検知結果で得られるタイミングより、交流電源2の第1の端子2aと第2の端子2bとの間の電圧が、正から負または負から正に切り替わるタイミングに至るまでの期間内にゲート−ソース間の電位をMOSFET23が確実にオフできる値とされる。

【0095】

抵抗262−1,264−1は、交流電源2の第2の端子2bとnチャンネルMOSFET22,24のソースの間の電圧を分圧した第1の駆動電圧をnチャンネルMOSFET22のソース−ゲート間に印加する第1の分圧回路を構成する。

【0096】

抵抗261−1,262−2は、交流電源2の第1の端子2aとnチャンネルMOSFET22,24のソースの間の電圧を分圧した第2の駆動電圧をnチャンネルMOSFET24のソース−ゲート間に印加する第2の分圧回路を構成する。

【0097】

平滑コンデンサ81は、nチャンネルMOSFET21,23のドレインおよびnチャンネルMOSFET22,24のソースとの間の電圧により充電される。

【0098】

抵抗101は、平滑コンデンサ81とnチャンネルMOSFET22,24のソースに接続された電流値を検出する電流検出回路を構成する。

【0099】

抵抗102,103は、MOSFET21,23のドレインとMOSFET22,24のソースの間の電圧を分圧した第3の分圧回路を構成する。

【0100】

コンパレータ104は、非反転入力端子に前記第3の分圧回路で分圧された電圧が印加され、反転入力端子に電流検出回路を構成する抵抗101により検出される平滑コンデンサ81とnチャンネルMOSFET22,24のソース間に流れる電流値に対応する電圧が入力され、比較結果をトランジスタ105,106のベースに出力する。

【0101】

トランジスタ105,106は、それぞれベースにコンパレータ104の出力に応じてMOSFET22,24をオフする様に構成され、抵抗211乃至214と共に、MOSFET22,24をオフするための制御回路100を構成する。

【0102】

尚、図16の全波整流回路1は、図13の全波整流回路1の動作を実現させるための詳細な構成であり、動作そのものは、図13における全波整流回路1と同様であるので、その説明は省略する。

【0103】

<第2の実施の形態>

[力率改善回路を含めた場合の問題]

以上においては、コンデンサインプット型の全波整流回路を実現させる構成について説明してきたが、力率改善回路を含めた構成とした場合、同期整流を実現すると、以下のように逆流する電流が発生し、障害が発生する恐れがある。

【0104】

すなわち、例えば、図17で示されるような構成の場合、図中の一点鎖線で示される経路を介して逆流する電流が発生する恐れがある。

【0105】

図17の回路は、AC100VをAC24Vに変換する電源トランス310と、電源トランス310に接続された複数の電源ユニット320−1乃至320−nから構成されている。電源ユニット320−1は、AC24Vを同期整流型ブリッジにより整流する整流回路330と、整流された電圧の力率を改善する力率改善回路340と、直流電圧を出力する出力回路350より構成されている。力率改善回路340は、インダクタLと、MOSFETからなるFET1と、FET2と、FET1およびFET2のスイッチングを制御する制御回路352を備えており、制御回路352は、FET1とFET2のデューテイ比を調整する。

【0106】

[力率改善回路を含む全波整流回路]

以上において、問題となるのは、図17におけるFET1で示されるハイサイド側のオンオフを制御するMOSFETが、逆流電流が発生しているタイミングにおいてオンの状態となり得ることである。したがって、上述した電流検知回路を構成し、逆流電流が発生する直前のタイミングにおいて、ハイサイド側のMOSFETをオフに制御することで力率改善回路を付した全波整流回路により安定した同期整流を実現することができる。

【0107】

図18は、力率改善回路を付した全波整流回路1である。図18の全波整流回路1において、図3,図6,図13,図16の全波整流回路1における構成と同一の機能を備えた構成については、同一の符号を付しており、その説明は適宜省略するものとする。また、図18の全波整流回路1においては、同期全波整流を実現させるための構成、すなわち、MOSFET21乃至24等については、図16の全波整流回路1と同一の機能であり、同一の動作をするものであるので、ここでは、力率改善回路についてのみ説明するものとする。

【0108】

図18の全波整流回路1における力率改善回路は、力率改善制御回路401、オン時ディレイ回路402、反転回路403、オン時ディレイ回路404、ローサイド用オンオフ回路405、ハイサイド用オンオフ回路406、MOSFET407,408、およびインダクタ409より構成される。また、コンパレータ104に代えてコンパレータ104’が設けられている。コンパレータ104’における機能は、コンパレータ104とほぼ同様の機能であるが、非反転入力端子側に電流検知回路を構成する抵抗101の電流値に対応する電圧が入力され、反転入力端子側に固定電圧値を出力する電源410より供給される固定電圧値が閾値電圧値として入力され、出力端子が、ハイサイド用オンオフ回路406に接続されている点が異なる。

【0109】

力率改善制御回路401は、入力端子Vinに同期整流された電圧が入力され、電源端子Vccより図示せぬ電源より電力が供給され、電流検知端子ISが、MOSFET22,24のソースに接続され、帰還電圧入力端子FBがMOSFET408のドレインに接続され、グランド端子GNDが接地され、出力端子outが、オン時ディレイ回路402、および反転回路403に接続されている。オン時ディレイ回路402は、力率改善制御回路401より出力されるローサイド用のMOSFET407をオンに制御する信号を所定時間だけ遅延させてローサイド用オンオフ回路405に供給する。ローサイド用オンオフ回路405は、オン時ディレイ回路402より供給されてくるローサイド用のMOSFET407をオンに制御する信号に基づいてMOSFET407のオンに制御し、それ以外のときオフに制御する。反転回路403は、力率改善制御回路401より供給されてくるローサイド用のMOSFET407をオフに制御する信号を、オンに制御する信号に反転させて、ハイサイド用のMOSFET408をオン時ディレイ回路404に供給する。オン時ディレイ回路404は、反転回路403より出力されるハイサイド用のMOSFET408をオンに制御する信号を所定時間だけ遅延させてハイサイド用オンオフ回路406に供給する。ハイサイド用オンオフ回路406は、オン時ディレイ回路404より供給されてくるハイサイド用のMOSFET408をオンに制御する信号に基づいてMOSFET408のオンに制御し、それ以外のときオフに制御する。

【0110】

このような構成により、MOSFET407,408のオンオフの制御と、インダクタ409により、力率が改善される。

【0111】

次に、ハイサイド用のMOSFET408を強制的にオフにする動作について説明する。

【0112】

コンパレータ104’は、電流検知回路を構成する抵抗101を流れる電流量に対応した両端電圧が、所定の電圧値よりも高いとき、Hiとなる出力信号を出力する。この場合、ハイサイド用オンオフ回路406には、オン時ディレイ回路404の出力信号がHiで、かつ、コンパレータ104’の出力信号がHiであるときにはHiの信号が供給され、それ以外のとき、Lowの信号が供給されることになる。このため、コンパレータ104’より供給される信号がHiの信号であれば、実質的にオン時ディレイ回路404の出力信号そのものがハイサイド用オンオフ回路406に供給される。一方、電流検知回路を構成する抵抗101を流れる電流値に対応する両端電圧が所定の電圧よりも低くなり、逆流電流が流れる条件に近付くと、コンパレータ104’からはLowの信号が出力されることにより、ハイサイド用オンオフ回路406には、オン時ディレイ回路404からの出力信号に関わらず、Lowの信号が供給されることになる。この結果、ハイサイド用オンオフ回路406は、MOSFET408をオフとすることにより、図17で示されるような逆流を防止させることが可能となる。

【0113】

尚、図13または図16における場合のように、MOSFET22,24のゲートに対してコンパレータ104’の出力結果に対応する信号を供給して、MOSFET22,24を強制的にオフにするようにしてもよい。さらに、コンパレータ104’の出力信号に対応して、MOSFET21乃至24、およびMOSFET408を全てオフするように、制御しても良いし、それらのうちのいずれかをオフとするように制御するようにしてもよい。

【0114】

以上の如く、本技術によれば、全波整流に伴うロスを低減することが可能となる。すなわち、全波整流回路のロスはダイオードで構成された場合、平均電流×順方向電圧VFで決定され、例えば、交流電圧がAC100Vで負荷を200Wとすると、平均電流が約1A程度になり、VF=1.1Vとすると、1×1.1=1.1Wであり、ダイオード4つトータルのロスは4.4W程度になる。

【0115】

一方、MOSFETを用いた同期整流では、MOSFETのロスは実効値電流×実効値電流×オン抵抗で決定され、前記と同じ条件で、実効値電流は約1.5A程度になり、オン抵抗を50mΩとすると、1.5×1.5×0.05≒0.11Wであり、MOSFET4つトータルのロスは0.44W程度とり、3.96Wのロス低減が可能となる。

【0116】

更には、アミューズメント業界の様に、スイッチング電源に入力される交流電圧がAC24Vの場合、MOSFETの耐圧は現状においては十分なものである(耐圧:60V)ので、オン抵抗が更に低いものが使用できる。一方、ダイオードの順方向電圧VFはダイオードの耐圧を下げたとしても極端には下がらず、約0.6V程度である。ダイオードの順方向電圧VFを0.6V、MOSFETのオン抵抗を4mΩとすると、9.3W程度のロス低減が可能となる。

【0117】

これらの効果により、従来であれば大型の放熱器にダイオードを取り付け発熱対策を行っていたが、高効率化することによって放熱器が要らなくなるので、1つのパッケージ化を実現する事が可能となる。

【0118】

また、本技術の全波整流回路によれば、貫通電流と称される、nチャンネルMOSFET21およびnチャンネルMOSFET23に同時に電流が流れる現象を防ぐ事が可能となる。

【0119】

一方、コンデンサインプット型の全波整流の場合、図11で示されるように、交流電源2より出力される出力電圧の1サイクルに対して電力が伝達される期間は短くなる。これは上述したMOSFET21,23とMOSFET22,24のソースとの間に接続された平滑コンデンサ81で整流された脈流電圧を直流に置き換えるためであり、交流電圧が出力電圧よりも高い状態の時のみ交流電源2より電流が流れる(電力が供給される)。また、上記位相検知回路により、例えば、図14の様に1周期の間の一定期間のみMOSFETはオン状態にある。したがって、MOSFETは特性上ドレインからソース及びソースからドレイン双方向電流を流す素子であるため、MOSFETがオンしている間は図9で示される通り、交流電源2の第1の端子2aまたは第2の端子2bと平滑コンデンサ81の低電位側(以後グランドと名づける)の間の電圧は出力電圧とほぼ同じ電圧が印加される。そのため、この時、nチャンネルMOSFET22,24がオン状態にあると図9で示されるように、平滑コンデンサ81に蓄えられた電荷を放電する経路で電流が流れる事になる。

【0120】

しかしながら、電流検出回路を構成する抵抗101に流れる電流値が所定の値よりも低くなった場合、電流検出回路を構成する抵抗101に接続されたコンパレータ104が検知するため、その結果に基づきMOSFET22,24がオフにされる。このように動作することにより、図14で示されるように、平滑コンデンサ81に蓄えられた電荷を放電する担い手であったnチャンネルMOSFET21,24、またはnチャンネルMOSFET22,23の片方、または両方をオフする事によって逆流経路を完全に遮断する事が可能となる。

【0121】

また、nチャンネルMOSFETの内部には必ずソースからドレイン方向に寄生ダイオードが存在する。その為、全てのコンデンサの電荷が0状態で電源投入されたとしても、定常状態に推移するまでの間はMOSFETの寄生ダイオードが電流伝達の担い手となる。つまりは、図14の様に電流の担い手であったMOSFETを急遽オフしたとしても、MOSFETの寄生ダイオードを通じて電流を流すため逆起電力が発生して素子が破壊されたりする事を防止することが可能となる。

【0122】

結果として、図15で示されるように、電流が反転する直前のタイミングで、MOSFET22,24をオフする事によってコンデンサインプット型の同期整流が可能となる。

【0123】

以上の如く、本技術によれば、電力損失を低減すると共に、nチャンネルMOSFETを保護することができるので、動作の安定性を向上させることが可能となる。また、逆方向に流れる電流を遮断することができるので、逆電流による障害を防止することが可能となり、さらに、力率改善回路を付したような場合であっても、同様の制御により逆方向に流れる電流により生じる障害を防止することが可能となる。

【0124】

また、本明細書において、システムとは、複数の装置により構成される装置全体を表すものである。

【符号の説明】

【0125】

1 全波整流回路

11乃至14 ダイオード

21乃至24 MOSFET

31乃至34 寄生ダイオード

51 ダイオード

52 コンデンサ

62 フォトダイオード

63 フォトカプラ

81 平滑コンデンサ

101 抵抗

104,104’ コンパレータ

105,106 トランジスタ

401 力率改善制御回路

402 オン時ディレイ回路

403 反転回路

404 オン時ディレイ回路

405 ローサイド用オンオフ回路

406 ハイサイド用オンオフ回路

407,408 MOSFET

409 インダクタ

【特許請求の範囲】

【請求項1】

交流電源から入力された交流電圧を全波整流する全波整流回路において、

内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第1の端子に接続された第1のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)と、

内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第1の端子に接続された第2のMOSFETと、

内部の寄生ダイオードにおけるカソードに対応する端子が前記第1のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第2の端子に接続された第3のMOSFETと、

内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第2の端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記第2のMOSFETの内部の寄生ダイオードにおけるアノードに対応する端子に接続された第4のMOSFETと、

前記交流電源の第1の端子に接続された交流電圧の位相を検知する第1の位相検知回路と、

前記交流電源の第2の端子に接続された交流電圧の位相を検知する第2の位相検知回路と、

前記第1の位相検知回路の検知結果に基づき、前記第1のMOSFETをオンする第1の制御回路と、

前記第2の位相検知回路の検知結果に基づき、前記第3のMOSFETをオンする第2の制御回路と、

前記第2および第4のMOSFETに流れる電流値を検知する電流検知回路と、

前記電流検知回路の検知結果である電流値が所定値よりも小さくなった場合、前記第1乃至第4のMOSFETのうち、少なくとも1つをオフするように接続された強制遮断回路と

を含む全波整流回路。

【請求項2】

前記第1および前記第3のMOSFETの内部寄生ダイオードのカソードに対応する端子と、前記第2および前記第4のMOSFETの内部寄生ダイオードのアノードに対応する端子との間の電圧によって得られる脈流電圧を平滑するように接続された平滑コンデンサをさらに含み、

前記電流検知回路は、

前記平滑コンデンサと、前記第2および前記第4のMOSFETとの間に電流を検出するための電流検出抵抗と、

前記電流検出抵抗に流れる電流値が所定値よりも小さいか否かにより信号を出力するコンパレータとを含む

請求項1に記載の全波整流回路。

【請求項3】

前記コンパレータの最低入力端子は、前記電流検出抵抗を介して前記第2および第4のMOSFETのソース、またはドレインと接続される

請求項2に記載の全波整流回路。

【請求項4】

前記強制遮断回路は、前記第2および第4のMOSFETの少なくとも1つをオフにする遮断制御回路を含む

請求項2に記載の全波整流回路。

【請求項5】

前記遮断制御回路は、抵抗、およびトランジスタを含み、前記抵抗の一方の端部が前記コンパレータの出力端子に接続され、前記抵抗の他方の端部が前記トランジスタのベースに接続され、前記トランジスタのコレクタが、前記第2および第4のMOSFETのゲートの少なくともそのいずれかに接続される

請求項4に記載の全波整流回路。

【請求項6】

前記第1乃至第4のMOSFETは、nチャンネルMOSFETである

請求項1に記載の全波整流回路。

【請求項7】

前記第1の制御回路は、

前記交流電源の第1の端子の電圧よりも高い電圧を生成する第1のチャージポンプ回路を含み、

前記第1の位相検知回路の検知結果に基づいて、フォトカプラによって前記第1のチャージポンプ回路より前記第1のMOSFETのゲートに電圧を印加するように接続され、前記第1の端子の電位が前記第2の端子の電位よりも低くならないうちに前記第1のMOSFETのゲートおよびソース間の電圧を所定値より小さくするように接続される

請求項1に記載の全波整流回路。

【請求項8】

前記第1のチャージポンプ回路は、

第1のダイオードおよび第1のコンデンサを含み、

前記第1のダイオードのアノードが前記第1のMOSFETの内部寄生ダイオードにおけるカソードに対応する端子、または前記交流電源の第2の端子に接続され、前記第1のダイオードのカソードと前記交流電源の第1の端子との間に第1のコンデンサが接続される

請求項7に記載の全波整流回路。

【請求項9】

前記第1のMOSFETのゲートおよびソース間に抵抗を含み、前記抵抗の抵抗値は、前記第1の位相検知回路の検知結果で得られるタイミングより、前記交流電源の第1の端子と第2の端子との間の電圧が正から負若しくは負から正に切り替わるタイミングに至るまでの期間内にゲートおよびソース間の電位を第1のMOSFETが確実にオフできる値である

請求項7に記載の全波整流回路。

【請求項10】

前記第2の制御回路は、

前記交流電源の第2の端子の電圧よりも高い電圧を生成する第2のチャージポンプ回路を含み、

前記第2の位相検知回路の検知結果に基づいて、フォトカプラによって前記第2のチャージポンプ回路より前記第3のMOSFETのゲートに電圧を印加するように接続され、前記第2の端子の電位が前記第1の端子の電位よりも低くならないうちに前記第3のMOSFETのゲートおよびソース間の電圧を所定値より小さくするように接続される

請求項1に記載の全波整流回路。

【請求項11】

前記第2のチャージポンプ回路は、

第2のダイオードおよび第2のコンデンサを含み、

前記第2のダイオードのアノードが前記第3のMOSFETの内部寄生ダイオードにおけるカソードに対応する端子、または前記交流電源の第1の端子に接続され、前記第2のダイオードのカソードと前記交流電源の第2の端子との間に第2のコンデンサが接続される

請求項10に記載の全波整流回路。

【請求項12】

前記第3のMOSFETのゲートおよびソース間に抵抗を含み、前記抵抗の抵抗値は、前記第2の位相検知回路の検知結果で得られるタイミングより、前記交流電源の第1の端子と第2の端子との間の電圧が正から負若しくは負から正に切り替わるタイミングに至るまでの期間内にゲートおよびソース間の電位を第3のMOSFETが確実にオフできる値である

請求項10に記載の全波整流回路。

【請求項13】

力率改善回路と、

全波整流された出力に直列接続されたインダクタと、

前記インダクタの出力とグランドの間にドレインおよびソースが接続された第5のMOSFETと、

前記インダクタの出力と直列に接続されたMOSFETの寄生ダイオードのアノードに対応する端子がインダクタの出力となるように接続された第6のMOSFETとをさらに含み、

前記電流検知回路は、前記力率改善回路のグランドと第2および第4のMOSFETの寄生ダイオードにおけるアノードに対応する端子との間の電流値を検知し、

前記強制遮断回路は、前記交流電源の前記電流検知回路の検知結果に基づいて、前記力率改善回路の出力信号を制御して、前記電流値が所定値よりも小さい場合、少なくとも第1乃至第4および第6のMOSFETのうち、少なくとも1つをオフする

請求項1に記載の全波整流回路を含む電源システム。

【請求項1】

交流電源から入力された交流電圧を全波整流する全波整流回路において、

内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第1の端子に接続された第1のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)と、

内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第1の端子に接続された第2のMOSFETと、

内部の寄生ダイオードにおけるカソードに対応する端子が前記第1のMOSFETの内部の寄生ダイオードにおけるカソードに対応する端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記交流電源の第2の端子に接続された第3のMOSFETと、

内部の寄生ダイオードにおけるカソードに対応する端子が前記交流電源の前記第2の端子に接続され、内部の寄生ダイオードにおけるアノードに対応する端子が前記第2のMOSFETの内部の寄生ダイオードにおけるアノードに対応する端子に接続された第4のMOSFETと、

前記交流電源の第1の端子に接続された交流電圧の位相を検知する第1の位相検知回路と、

前記交流電源の第2の端子に接続された交流電圧の位相を検知する第2の位相検知回路と、

前記第1の位相検知回路の検知結果に基づき、前記第1のMOSFETをオンする第1の制御回路と、

前記第2の位相検知回路の検知結果に基づき、前記第3のMOSFETをオンする第2の制御回路と、

前記第2および第4のMOSFETに流れる電流値を検知する電流検知回路と、

前記電流検知回路の検知結果である電流値が所定値よりも小さくなった場合、前記第1乃至第4のMOSFETのうち、少なくとも1つをオフするように接続された強制遮断回路と

を含む全波整流回路。

【請求項2】

前記第1および前記第3のMOSFETの内部寄生ダイオードのカソードに対応する端子と、前記第2および前記第4のMOSFETの内部寄生ダイオードのアノードに対応する端子との間の電圧によって得られる脈流電圧を平滑するように接続された平滑コンデンサをさらに含み、

前記電流検知回路は、

前記平滑コンデンサと、前記第2および前記第4のMOSFETとの間に電流を検出するための電流検出抵抗と、

前記電流検出抵抗に流れる電流値が所定値よりも小さいか否かにより信号を出力するコンパレータとを含む

請求項1に記載の全波整流回路。

【請求項3】

前記コンパレータの最低入力端子は、前記電流検出抵抗を介して前記第2および第4のMOSFETのソース、またはドレインと接続される

請求項2に記載の全波整流回路。

【請求項4】

前記強制遮断回路は、前記第2および第4のMOSFETの少なくとも1つをオフにする遮断制御回路を含む

請求項2に記載の全波整流回路。

【請求項5】

前記遮断制御回路は、抵抗、およびトランジスタを含み、前記抵抗の一方の端部が前記コンパレータの出力端子に接続され、前記抵抗の他方の端部が前記トランジスタのベースに接続され、前記トランジスタのコレクタが、前記第2および第4のMOSFETのゲートの少なくともそのいずれかに接続される

請求項4に記載の全波整流回路。

【請求項6】

前記第1乃至第4のMOSFETは、nチャンネルMOSFETである

請求項1に記載の全波整流回路。

【請求項7】

前記第1の制御回路は、

前記交流電源の第1の端子の電圧よりも高い電圧を生成する第1のチャージポンプ回路を含み、

前記第1の位相検知回路の検知結果に基づいて、フォトカプラによって前記第1のチャージポンプ回路より前記第1のMOSFETのゲートに電圧を印加するように接続され、前記第1の端子の電位が前記第2の端子の電位よりも低くならないうちに前記第1のMOSFETのゲートおよびソース間の電圧を所定値より小さくするように接続される

請求項1に記載の全波整流回路。

【請求項8】

前記第1のチャージポンプ回路は、

第1のダイオードおよび第1のコンデンサを含み、

前記第1のダイオードのアノードが前記第1のMOSFETの内部寄生ダイオードにおけるカソードに対応する端子、または前記交流電源の第2の端子に接続され、前記第1のダイオードのカソードと前記交流電源の第1の端子との間に第1のコンデンサが接続される

請求項7に記載の全波整流回路。

【請求項9】

前記第1のMOSFETのゲートおよびソース間に抵抗を含み、前記抵抗の抵抗値は、前記第1の位相検知回路の検知結果で得られるタイミングより、前記交流電源の第1の端子と第2の端子との間の電圧が正から負若しくは負から正に切り替わるタイミングに至るまでの期間内にゲートおよびソース間の電位を第1のMOSFETが確実にオフできる値である

請求項7に記載の全波整流回路。

【請求項10】

前記第2の制御回路は、

前記交流電源の第2の端子の電圧よりも高い電圧を生成する第2のチャージポンプ回路を含み、

前記第2の位相検知回路の検知結果に基づいて、フォトカプラによって前記第2のチャージポンプ回路より前記第3のMOSFETのゲートに電圧を印加するように接続され、前記第2の端子の電位が前記第1の端子の電位よりも低くならないうちに前記第3のMOSFETのゲートおよびソース間の電圧を所定値より小さくするように接続される

請求項1に記載の全波整流回路。

【請求項11】

前記第2のチャージポンプ回路は、

第2のダイオードおよび第2のコンデンサを含み、

前記第2のダイオードのアノードが前記第3のMOSFETの内部寄生ダイオードにおけるカソードに対応する端子、または前記交流電源の第1の端子に接続され、前記第2のダイオードのカソードと前記交流電源の第2の端子との間に第2のコンデンサが接続される

請求項10に記載の全波整流回路。

【請求項12】

前記第3のMOSFETのゲートおよびソース間に抵抗を含み、前記抵抗の抵抗値は、前記第2の位相検知回路の検知結果で得られるタイミングより、前記交流電源の第1の端子と第2の端子との間の電圧が正から負若しくは負から正に切り替わるタイミングに至るまでの期間内にゲートおよびソース間の電位を第3のMOSFETが確実にオフできる値である

請求項10に記載の全波整流回路。

【請求項13】

力率改善回路と、

全波整流された出力に直列接続されたインダクタと、

前記インダクタの出力とグランドの間にドレインおよびソースが接続された第5のMOSFETと、

前記インダクタの出力と直列に接続されたMOSFETの寄生ダイオードのアノードに対応する端子がインダクタの出力となるように接続された第6のMOSFETとをさらに含み、

前記電流検知回路は、前記力率改善回路のグランドと第2および第4のMOSFETの寄生ダイオードにおけるアノードに対応する端子との間の電流値を検知し、

前記強制遮断回路は、前記交流電源の前記電流検知回路の検知結果に基づいて、前記力率改善回路の出力信号を制御して、前記電流値が所定値よりも小さい場合、少なくとも第1乃至第4および第6のMOSFETのうち、少なくとも1つをオフする

請求項1に記載の全波整流回路を含む電源システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−244786(P2012−244786A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−112966(P2011−112966)

【出願日】平成23年5月20日(2011.5.20)

【出願人】(000002945)オムロン株式会社 (3,542)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月20日(2011.5.20)

【出願人】(000002945)オムロン株式会社 (3,542)

【Fターム(参考)】

[ Back to top ]