共振回路、発振回路、フィルタ回路及び電子装置

【課題】バイアス電圧によるMEMSレゾネータの共振周波数の変動態様を制御することのできる共振回路を実現する。

【解決手段】本発明の共振回路30は、基板と、該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータ10と、前記MEMSレゾネータの第1の端子10aに接続された第1の入出力部30aと、前記MEMSレゾネータの第2の端子10bに接続された第2の入出力部30bと、少なくとも前記第1の端子10aに電位Vpを供給して前記MEMSレゾネータの前記第1の端子と前記第2の端子の間にバイアス電圧Vcを印加する電圧印加手段20と、前記第1の端子10aと第1の入出力部30aの間に接続され、両端の電位差の変化で容量値が変化する可変設けられた結合容量Cc1と、を具備する。

【解決手段】本発明の共振回路30は、基板と、該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータ10と、前記MEMSレゾネータの第1の端子10aに接続された第1の入出力部30aと、前記MEMSレゾネータの第2の端子10bに接続された第2の入出力部30bと、少なくとも前記第1の端子10aに電位Vpを供給して前記MEMSレゾネータの前記第1の端子と前記第2の端子の間にバイアス電圧Vcを印加する電圧印加手段20と、前記第1の端子10aと第1の入出力部30aの間に接続され、両端の電位差の変化で容量値が変化する可変設けられた結合容量Cc1と、を具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は共振回路、発振回路、フィルタ回路及び電子装置に係り、特に、MEMSレゾネータを用いた共振回路の構成に関する。

【背景技術】

【0002】

最近の電子デバイス市場においては、MEMS(Micro Electro-Mechanical System)技術を用いた製品が加速的に浸透しつつある。MEMS技術を用いた製品とは、半導体製造技術を用いて基板上に形成された微小な構造体(MEMS構造体)を有する電気機械装置(MEMS装置)を言う。MEMS技術を用いたデバイスの具体的な事例としては、加速度センサ、角速度センサ、慣性センサ、圧力センサ等の各種のマイクロセンサ等が挙げられるが、その市場は近年急速に拡大しつつある。このように、MEMS技術は新たなデバイスの創出の可能性を多分に秘めており、今後は微小メカニカルリレー(スイッチ)や可変容量素子等の微小構造体の特徴を生かしたデバイスやそれらの組み合わせが順次実用化されていく見込みである。

【0003】

MEMS技術を用いた新しい応用例として、レゾネータ(振動子、発振子、共振子、共振器などとも言う。本願ではMEMSレゾネータと称する。)が挙げられる。MEMSレゾネータの動作原理としては、静電駆動・検出方式、圧電駆動・検出方式が代表的なものであるが、特に前者はCMOSプロセスのような半導体プロセスとの整合性がよく、小型化や低コスト化に有利な手法といえる。この静電駆動・検出方式は、可動電極と固定電極を有するMEMSレゾネータを形成し、静電力に起因する可動電極の振動を可動電極と固定電極の間の静電容量の変化によって検出するものである。MEMSレゾネータの一般的な透過特性及び位相特性の例は図3(a)及び(b)に示されている。この種のMEMSレゾネータを開示する文献としては、以下の特許文献1乃至3がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国特許第6249073号明細書

【特許文献2】米国特許第6424074号明細書

【特許文献3】特開2004−58228号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、前述のMEMSレゾネータにおいては、通常、振動子の可動電極と固定電極の間に直流バイアス電圧が印加される。この直流バイアス電圧が印加されると、振動子において振動が励起されやすくなり、共振特性がより顕著となる。ただし、振動子の両電極間に生ずる静電引力により可動電極が固定電極に接触してしまうPull−Inの発生を防止するために所定のマージンを確保した状態でバイアス電圧を設定しなければならない。このような状況において、通常、MEMSレゾネータの共振特性を向上させるには上記のマージンを確保しつつバイアス電圧を大きくすることが望まれるが、振動子の共振周波数はこのバイアス電圧の値によって変化する。即ち、印加するバイアス電圧が外的な要因によって変動した場合、MEMSレゾネータの共振周波数が変位するため、MEMSレゾネータを含む共振回路を含む発振回路やフィルタ回路では、前記バイアス電圧の変動により所望の発振周波数、もしくはフィルタ特性が得られなくなるという問題があった。

【0006】

すなわち、MEMSレゾネータの共振周波数は上記のバイアス電圧に依存するため、バイアス電圧を共振周波数と無関係に設定することができず、共振周波数の変化状況を制御できないため、これによって各種の回路構成においてMEMSレゾネータを用いることが難しいという問題点がある。

【0007】

本発明は上記問題点を解決するものであり、バイアス電圧の変動によるMEMSレゾネータの共振周波数の変動を制御することのできる共振回路を実現することにある。

【課題を解決するための手段】

【0008】

斯かる実情に鑑み、本発明の共振回路は、基板と、該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータと、該MEMSレゾネータの前記固定電極と前記可動電極の一方に接続された第1の端子に接続された第1の入出力部と、前記MEMSレゾネータの前記固定電極と前記可動電極の他方に接続された第2の端子に接続された第2の入出力部と、少なくとも前記第1の端子に電位を供給して前記第1の端子と前記第2の端子の間にバイアス電圧を印加する電圧印加手段と、前記第1の端子と前記第1の入出力部の間に接続され、両端の電位差の変化で容量値が変化する可変容量と、を具備することを特徴とする。

【0009】

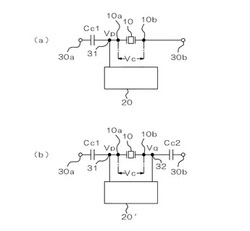

本発明によれば、例えば、図15(a)に示すように、電圧印加手段(20)によりMEMSレゾネータ(10)の第1の端子(10a)と第2の端子(10b)の間にバイアス電圧(Vc)を印加し、前記第1の端子(10a)若しくは第2の端子(10b)に交流電圧を印加することで特定の共振周波数を有する共振動作を生じさせることができるが、電圧印加手段(20)が電位を供給する第1の端子(10a)に接続された第1の入出力部(30a)に、可変容量(Cc1)の一端を接続することにより、その両端の電位差により容量値が変化する構成とすることにより、電圧印加手段(20)により供給される第1の端子(10a)の電位が変化すると可変容量(Cc1)の両端の電位差も変化することから、MEMSレゾネータ(10)に印加されるバイアス電圧(Vc)の変動に応じたMEMSレゾネータ(10)の共振周波数の変化態様を可変容量(Cc1)の容量値の変化特性で変更することが可能になる。したがって、共振周波数のバイアス電圧に対する依存特性を変更することにより、共振周波数の値や変動幅を任意に設計することが可能となる。

【0010】

本発明の一の態様においては、前記可変容量は、その両端の電位差の変化により容量値が単調に変化する電圧依存領域を少なくとも一部に有し、当該電圧依存領域において前記バイアス電圧の増大により容量値が単調に減少する特性を備える。この場合には、バイアス電圧が増大すると本来的には共振周波数を低下させる方向に作用するが、バイアス電圧の増大により可変容量の容量値が減少し、この容量値の減少は共振周波数を増加させる方向に作用するので、可変容量による共振周波数の自動安定効果を得ることができ、バイアス電圧の変化による共振周波数の変動を抑制することが可能になり、共振周波数の安定化を図ることができる。

【0011】

本発明の他の態様においては、前記電圧印加手段は、前記第1の端子に第1の電位を供給するとともに、前記第2の端子を接地電位とする。この場合には、電圧印加手段が第1の端子に第1の電位を供給するが第2の端子の電位が固定値であるため、第1の端子に印加される電位が変化するとMEMSレゾネータに印加される電位差、即ち、レゾネータのバイアス電圧も変化するが、同時に、前記結合容量の他端に印加される電位が一定値である場合、結合容量の両端の電位差も前記バイアス電圧と連動して変化し、結合容量値が変化減少するので、MEMSレゾネータの共振周波数の変化態様を結合容量の容量値の変化で変更することが可能になる。

【0012】

本発明のさらに他の態様においては、前記電圧印加手段は、前記第1の端子に第1の電位を供給するとともに前記第2の端子に第2の電位を供給する。この場合には、図15(b)に示すように、電圧印加手段(20′)によりMEMSレゾネータ(10)の第1の端子(10a)と第2の端子(10b)にそれぞれ供給電位(Vp)及び(Vq)を与えることができるので、MEMSレゾネータ(10)に対してバイアス電圧(Vc)をより確実に与えることができる。また、電圧印加手段(20′)が第1の端子(10a)に可変電位である第1の電位(Vp)を供給するが第2の端子(10b)の電位(Vq)を固定値とすれば、第1の端子(10a)に印加される電位(Vp)が変化するとMEMSレゾネータ(10)に印加される電位差、即ち、レゾネータのバイアス電圧(Vc)も変化するが、同時に、前記可変容量(Cc1)の他端に印加される電位が一定値である場合、可変容量(Cc1)の両端の電位差も前記バイアス電圧(Vc)と連動して変化し、可変容量の容量値が変化するので、MEMSレゾネータ(10)の共振周波数の変化態様を可変容量の容量値の変化で変更することが可能になる。

【0013】

本発明の別の態様においては、前記可変容量と並列に接続された付加容量をさらに有する。これによれば、可変容量と並列に付加容量が接続されることで、結合容量として機能する容量値を確保しつつ、可変容量の容量値や可変特性を振動子の共振特性に整合させることが可能になるので、共振周波数の変動をより低減可能となるとともに、各部の設計の自由度を高めることができる。

【0014】

本発明の別の共振回路は、基板と、該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータと、該MEMSレゾネータの前記固定電極と前記可動電極の一方に接続された第1の端子に接続された第1の入出力部と、前記MEMSレゾネータの前記固定電極と前記可動電極の他方に接続された第2の端子に接続された第2の入出力部と、前記第1の端子に電位を供給することにより前記第1の端子と前記第2の端子の間に前記第1の端子に供給された電位が上昇するに従って増大するバイアス電圧を印加する電圧印加手段と、前記第1の端子と前記第1の入出力部の間に接続され、前記第1の端子に供給された電位が上昇すると容量値が減少する可変容量と、を具備することを特徴とする。ただし、本発明には、他の態様として、上記電圧印加手段において、第1の端子に供給された電位が上昇するに従ってバイアス電圧が減少する場合も含まれる。また、上記第1の端子が供給された電位が上昇するに従ってバイアス電圧が増大する場合と、減少する場合のいずれにおいても、上記可変容量の容量値が増大する構成が含まれる。

【0015】

次に、本発明の電子回路としては、上記のいずれかに記載の共振回路と、該共振回路に接続される増幅回路部を有する外部回路とで構成される発振回路がある。この発振回路においては、前記外部回路が前記第1の入出力部及び前記第2の入出力部に接続される。また、上記のいずれかに記載の共振回路を含むフィルタ回路が挙げられる。このフィルタ回路において、フィルタ回路の入出力間に前記共振回路が直列に接続されるとともに、フィルタ回路の入出力間の前記共振回路の前記入出力部と定(接地)電位との間にも前記共振回路が接続される場合がある。さらに、本発明の電子装置は、上記のいずれかに記載の回路(共振回路、発振回路、フィルタ回路)を含む。

【0016】

また、本発明の共振回路においては、前記MEMSレゾネータ、前記電圧印加手段、前記可変容量が同一基板上に形成されていることが好ましい。また、本発明の発振回路において、前記MEMSレゾネータ、前記電圧印加手段、前記可変容量及び前記増幅回路部が同一基板上に形成されていることが好ましい。さらに、本発明のフィルタ回路において、前記MEMSレゾネータ、前記電圧印加手段及び前記可変容量が同一基板上に形成されていることが好ましい。また、本発明の電子装置において、上記の発振回路と、上記のフィルタ回路とが同一基板上に形成されていることが好ましい。

【0017】

なお、上述の共振回路、電子回路、電子装置における上記基板としては、シリコン基板等の半導体基板、ガラス基板、セラミックス基板などが挙げられるが、MEMSレゾネータを構成することから、シリコン基板等の半導体基板を用いた半導体装置を構成することが好ましい。

【0018】

本発明の一の態様においては、前記可変容量を構成する一対の容量電極のうちの少なくとも一方が前記固定電極と可動電極の少なくとも一方と同材質で構成される。このようにすることで、可変容量を設けることによる製造工程の増加を抑制できる。

【0019】

この場合に、前記可変容量がMIS容量であることが好ましい。これによれば、集積回路技術によって信号回路部を形成する場合に容易かつ効率的に可変容量を形成できる。ここで、前記MIS容量がMOS容量であることが好ましく、さらにMOSFETで構成されることが望ましい。MOSFETはCMOS等の増幅回路に用いられる電子素子であるので、MOS容量をMOSFETで構成することで、さらに容易かつ効率的に可変容量を形成できる。

【0020】

本発明の異なる態様においては、前記可変容量が前記MEMSレゾネータの等価直列容量の10分の一から10倍の範囲内で動作する。ここで言う等価直列容量とは、MEMSレゾネータの電気的な等価回路における、直列共振部の容量値を示す。一般に可変容量の容量特性を自由に設定することは難しいが、可変容量がMEMSレゾネータの等価直列容量(バイアス電圧に連動して変動する容量成分)の10分の一から10倍の範囲内であれば、両者の容量値のオーダーがほぼ同様となるので、可変容量の容量特性によって共振周波数の変動を抑制する効果が高くなる。

【0021】

本発明のさらに異なる態様においては、前記MEMSレゾネータの等価直列容量が1.0×10−11〜10−13[F]の範囲内である。MEMSレゾネータの等価直列容量がこの範囲であれば、通常用いられる結合容量の容量値とほぼ同様のオーダーを有する値となるので、可変容量において結合容量としての機能を確保しつつ、共振周波数の変動の抑制効果を得ることができる。

【発明の効果】

【0022】

本発明によれば、MEMSレゾネータの共振周波数の変化態様を制御することができるので、共振周波数の要求特性に応じた設計を行うことができるという優れた効果を奏し得る。

【図面の簡単な説明】

【0023】

【図1】本発明に係る共振回路を構成するMEMSレゾネータの構成例を示す概略斜視図。

【図2】同MEMSレゾネータの縦断面図(a)及び(b)。

【図3】MEMSレゾネータの通過特性及び位相変位の周波数依存性を示すグラフ(a)及び(b)。

【図4】MEMSレゾネータのバイアス電圧依存性を示すグラフ。

【図5】MEMSレゾネータの等価回路図。

【図6】共振回路の第1実施形態を示す回路図(a)と発振回路構成例を示す構成図(b)。

【図7】共振回路の第2実施形態を示す回路図(a)と発振回路構成例を示す構成図(b)。

【図8】MOSFETによる構成を示す図及び容量特性図。

【図9】電子回路(発振回路)の実施例1の構成を示す回路図。

【図10】電子回路(発振回路)の実施例2の構成を示す回路図。

【図11】電子回路(発振回路)の実施例3の構成を示す回路図。

【図12】電子回路(フィルタ回路)の実施例4の構成を示す回路図。

【図13】電子回路若しくは電子装置の具体的断面構造を示す縦断面図。

【図14】電子回路若しくは電子装置の別の具体的断面構造を示す縦断面図。

【図15】本発明の共振回路の構成例を示す概略構成図(a)及び(b)。

【発明を実施するための形態】

【0024】

次に、添付図面を参照して本発明の実施形態について詳細に説明する。図1は本実施形態のMEMSレゾネータ10の構成例を示す概略斜視図、図2は図1のA−A線及びB−B線に沿った断面を示す同振動子10の断面図(a)及び(b)である。

【0025】

MEMSレゾネータ10は、シリコン単結晶基板等の半導体基板等よりなる基板1上に構成される。基板1上には酸化シリコン(SiO2)等の絶縁膜2が形成され、さらに絶縁膜2上には窒化シリコン等の下地層11が形成される。下地層11上には、ドーピングにより導電性が付与された多結晶シリコン等よりなる固定電極12と、同様の材質よりなる可動電極13とが形成される。ここで、MEMSレゾネータ10の振動子電極を構成する固定電極12と可動電極13の可動部13aは基板1上において適宜の間隔で相互に上下方向に対向配置される。そして、可動部13aは対向部12aとの間に生ずる静電引力に応じて撓み、対向部12aとの間の対向間隔を変化させる方向に可動に構成される。

【0026】

上記固定電極12及び可動電極13の製造においては、まず、下地層11上にCVD法等により上記多結晶シリコン等の導電材料からなる第1層を形成し、この第1層をパターニングすることで、上記固定電極12を形成する。次に、その上にSiO2等から成る犠牲層(図示せず)を前記固定電極12の表面に一定厚だけ形成する。その後に、この上に上記の多結晶シリコン等の導電材料からなる第2層を形成し、これをパターニングすることで構造体の一部が下地層11上に固定された状態で可動電極13が形成される。最後に、緩衝フッ酸等の適宜のエッチング液若しくはエッチングガスにより上記犠牲層を除去することで、可動電極13の上部構造が上記可動部13aとして基板上から分離され、基部において支持されるとともに、固定電極12上に張り出した両持ち梁状に形成される。

【0027】

なお、図示のMEMSレゾネータ10は一対の振動子電極の一方が両持ち梁状に構成されることにより可動部13aとされた両持ち梁構造を有するが、これは本発明の振動子の一例に過ぎず、本発明においては、MEMSレゾネータとして、片持ち梁状に構成されたもの、円盤状に構成されたものなど、種々の形状、構造を採用したものを用いることが可能である。

【0028】

図3は本発明に係るMEMSレゾネータ10の電気的特性を示す概略特性図である。ここで、図3(a)はMEMSレゾネータ10に交流信号を入力したときの通過特性を示すグラフ、図3(b)は位相変位を示すグラフである。このように、MEMSレゾネータ10は適宜の共振周波数を有する共振特性を備えているが、この共振周波数fnは、以下の式(1)で示される。

fn=(1/2π)・(km/meff)1/2・・・(1)

ここで、kmは振動子10の構造から決定されるばね定数、meffは同構造の有効質量である。

【0029】

一方、MEMSレゾネータ10の固定電極12と可動電極13の間に適宜のバイアス電圧(直流バイアス)を印加すると両電極の間に静電引力が発生し、上記ばね定数kmを減少させる様に作用する。このため、上記式(1)により共振周波数fnが低下する。そして、一般に、バイアス電圧が増加するほど共振周波数fnは減少することになる。

【0030】

図4は、MEMSレゾネータ10に印加したバイアス電圧Vbを変化させたときの交流信号の共振特性を示すグラフである。このように、バイアス電圧Vbが増加するほど共振周波数fnは低下する。

【0031】

図5はMEMSレゾネータの等価回路図である。MEMSレゾネータ10は、等価直列容量C1、等価直列インダクタンスL1、等価直列抵抗R1の直列回路部分と、等価並列容量C0とが並列に接続されてなる等価回路によって示される。この等価回路定数で上記直列共振周波数fnを示すと、

fn=(1/2π)・(L1・C1)−1/2・・・(1′)

となる。

【0032】

この場合、上記の等価直列容量C1は以下の式(2)で表される。

C1=η2/km・・・(2)

ここで、ηは電気機械変換係数(振動による変位エネルギーが電気エネルギーに変換されるときの効率)である。そして、上記のバイアス電圧の変位に起因してMEMSレゾネータ10のばね定数kmが低下すると、等価直列容量C1は増加し、これによって上記式(1′)により共振周波数が低下することがわかる。

【0033】

図6(a)には本実施形態の共振回路構成例を示す。ここで、図6(a)に示す第1実施形態の共振回路30では、MEMSレゾネータ10と、前記MEMSレゾネータ10の第1の端子10a側に設けられた第1の入出力部30aと、上記MEMSレゾネータ10の第2の端子部10b側に設けられた第2の入出力部30bと、MEMSレゾネータ10の第1の端子10aと前記共振回路の第1の入出力部30aとの間に接続された結合容量Cc1と、前記MEMSレゾネータ10の第1の端子10aと前記結合容量Cc1との間の端子31に接続された電圧印加手段20とから構成される。

【0034】

ここで、電圧印加手段20は、図示例の場合、電位Vbの電圧源と抵抗Rpとによって構成される。端子31の直流電位Vpは電圧印加手段20での外部印加電圧印加Vbと同値となる。これは、直流的にはレゾネータ10が容量素子として作用し、また、上記結合容量Cc1が、共振回路30の第1の入出力部30aに接続される外部回路との間に介在するためである。

【0035】

また、上記結合容量Cc1は、その両端に印加する電位差(=電圧)により容量値が変化する電圧依存性を有する可変容量で構成する。本実施形態においてCc1は可変容量であるが、これを結合容量と称するのは、共振回路30を外部回路と接続した場合にCc1が結合容量としての機能をも有するからであり、可変容量Cc1自体を何ら限定する趣旨ではない。

【0036】

図6(b)に前記共振回路30を他回路と接続し、発振回路15を構成した場合の構成例を示す。発振回路は、前記共振回路30の他に、増幅回路部16と出力緩衝部17とから構成され、増幅回路16の入力端子16a、出力端子16bの直流電位Vi及びVoは、能動回路の内部素子のバイアス電圧などにより決定し、一定値に設定される。図6(b)において、共振回路30の第1の入出力部30aは増幅回路部16の入力端子16aの電位Viと同電位となり、また、共振回路30の第2の入出力部30bは増幅回路部16の出力端子16bの電位Voと同電位となる。また、図6(a)に示すように、MEMSレゾネータ10の第1の端子10aには、電圧印加手段20により直流電位Vpが印加される。

【0037】

この結果、MEMSレゾネータ10の第1、第2の入力端子間の電位差はVpと端子30bの電位Voとの差分値となり、この値がMEMSレゾネータ10のバイアス電圧Vcとなる。一方で、可変容量で構成された結合容量Cc1の両端の電位差は、前記Vpと端子30aの電位Viとの差分値となり、この値が結合容量Cc1のバイアス電圧となる。

【0038】

この第1実施形態では、結合容量Cc1が接続されるため、上記式(1′)とは異なり、共振周波数fnは以下の式(3)で与えられる。

fn=(1/2π)・(L1・C1)−1/2・{1+C1/(C0+Cc1)}1/2・・・(3)

式(3)は、前記結合容量Cc1が共振周波数を決定する一要素であり、この値を変更する事で共振周波数の制御が可能である事を示している。

【0039】

本実施例では前記の通り上記結合容量Cc1を電圧依存型の可変容量とし、かつMEMSレゾネータの一端に印加される供給電位Vpに連動して前記Cc1の容量値を制御する事を特徴とする。上記結合容量Cc1は供給電位Vpの増加に対し、容量値が減少する特性を有する。

【0040】

レゾネータの機械的なばね定数kmは、前述の通り、バイアス電圧Vcの増加に伴い減少するため、式(2)で示した通り、レゾネータの等価直列容量C1は増加する。これを式(3)にあてはめると、C1の増加により、共振周波数fnは低下するが、同時に結合容量Cc1の値を減少させる事で、共振周波数の変位量を抑制する事が出来る。

【0041】

また、上記の可変容量としては、標準的な半導体プロセスとの整合性を考慮した場合、図8(a)に示されるMOSFETを用いたMOS容量を用いることができる。すなわち、MOSFETのソースとドレインを短絡し、これらとゲートとの間にMOS容量が構成される例を用いることができる。このMOS容量の容量値は図8(b)の右側のグラフに示すように電圧依存性を有する。

【0042】

また、上記の可変容量としては、前記MOS容量の他、一般的にバリキャップ若しくはバラクタと呼ばれる可変容量ダイオード素子を用いても良い。この場合、MOS容量と比較して高周波特性が良好であるため、より高い周波数の回路に本発明を適用する場合はバリキャップを用いる事が好ましい。なお、これら可変容量素子は方向性を有するため、本発明に適用する際にはその方向性に注意を払う必要がある。例えば、図6(a)においては、可変容量素子にMOS容量を用いる場合、端子31の電位Vpが端子30aの電位Viよりも高い場合は、端子31側にMOS容量のゲート側を、端子30a側にMOS容量のドレイン,ソース側を接続する必要がある。逆方向に接続した場合、MOS容量は蓄積状態で動作するために、バイアス電圧に対する容量変位が発生しなくなる。

【0043】

なお、上記のように結合容量そのものを可変容量で構成してもよいが、結合容量の少なくとも一部を可変容量で構成しても構わない。このように結合容量の少なくとも一部を可変容量で構成するとしているのは、結合容量Cc1自体が可変容量のみで構成されていてもよく、或いは、可変容量と、上記電圧領域で実質的に固定された容量値を有する付加容量との合成容量(並列合成容量又は直列合成容量)で構成されていてもよいという意味である。

【0044】

図示例において、上記の可変容量は、共振回路30の動作状態において、MEMSレゾネータ10に印加されるバイアス電圧Vcが増加すると容量値が低下し、バイアス電圧Vcが減少すると容量値が増大するように構成される。すなわち、第1実施形態の場合には、Vc=Vp−Voであるので、第1の電位端子31の電位Vpが上昇するとレゾネータに印加されるバイアス電圧Vcの増加とともに、レゾネータの共振周波数が下がる方向に作用するが、可変容量である結合容量Cc1の端子間の電位差も増加するのでその容量値が低下し、結合容量Cc1の変化分は共振周波数を上昇させる方向に寄与するため、共振回路の共振周波数の変動量を抑制する事が出来る。また、端子31の電位Vpが低下すると、バイアス電圧Vcが減少するとともに、レゾネータの共振周波数が上がる方向に作用するが、結合容量Cc1の端子間の電位差も低下するのでその容量値が増大し、結合容量Cc1の変化分は共振周波数を低下させる方向に寄与するため、共振回路の共振周波数の変動量を抑制することが出来る。

【0045】

なお、本発明の構成は、上記の例とは逆に、第1実施形態の場合、結合容量Cc1を両端電圧が増加すると容量値が単調に増加する電圧依存領域を備えた可変容量で構成することでも実現できる。

【0046】

この場合、端子31に印加されるバイアス電圧の増減に対する周波数変動幅は拡大するように作用するため、本発明の主目的である、バイアス電圧のばらつきに対する周波数の変動を抑制するとは逆の目的で、例えば、バイアス電圧により発振周波数を変動できる、電圧制御発振器(VCO)の出力周波数範囲の拡大や、フィルタ回路における、帯域可変フィルタなどに適用する場合の帯域可変幅の拡大に有用である。

【0047】

例えば、第1実施形態の場合には、Vc=Vp−Voであるので、第1の電位端子31の電位Vpが上昇するとレゾネータに印加されるバイアス電圧Vcの増加とともに、レゾネータの共振周波数が下がる方向に作用するが、可変容量である結合容量Cc1の端子間の電位差も増加するのでその容量値が増加し、結合容量Cc1の変化分も共振周波数を低下させる方向に寄与するため、共振回路の共振周波数の変動量が拡大する。また、端子31の電位Vpが低下すると、バイアス電圧Vcの減少とともに、レゾネータの共振周波数が上がる方向に作用するが、結合容量Cc1の端子間の電位差も低下するため、その容量値も減少し、結合容量Cc1の変化分は共振周波数を上昇させる方向に寄与するため、共振回路の共振周波数の変動量が拡大する。

【0048】

以上のように、可変容量が両端電圧の変化により容量値が単調に変化する電圧依存領域を有し、この電圧依存領域で動作させる場合に、その動作状況に応じて可変容量の電圧依存領域の特性を上述のいずれか(すなわち、両端電圧が増加すると容量値が単調に減少する特性か、或いは、その逆に両端電圧が増加すると容量値が単調に増加する特性か)に設定することにより、バイアス電圧の変化に起因する共振周波数の変動を、可変容量の容量値の変化に起因して共振周波数の変動幅を補償する、または増進させることが可能になる。

【0049】

図7(a)には本実施形態の他の共振回路構成例を示す。ここで、図7(a)に示す第2実施形態の共振回路30′では、MEMSレゾネータ10と、前記MEMSレゾネータ10の第1の端子10a側に設けられた第1の入出力部30aと、上記MEMSレゾネータ10の第2の端子部10b側に設けられた第2の入出力部30bと、MEMSレゾネータ10の第1の端子10aと前記共振回路の第1の入出力部30aとの間に接続された結合容量Cc1と、MEMSレゾネータ10の第2の端子10bと前記共振回路の第2の入出力部30bとの間に接続された結合容量Cc2と、前記MEMSレゾネータ10の第1の端子10aと前記結合容量Cc1との間の端子31に接続された電圧印加手段20Aと、前記MEMSレゾネータ10の第2の端子10bと前記結合容量Cc2との間の端子32に接続された電圧印加手段20Bとから構成される。これらの電圧印加手段20A及び20Bは本発明の電圧印加手段20′を構成する。

【0050】

ここで、電圧印加手段20Aは、図示例の場合、電位Vbの電圧源と抵抗Rpとによって構成される。また、電圧印加手段20Bは、電位Vrefの電圧源と抵抗Rqとによって構成される。端子31の直流電位Vp1は電圧印加手段20での外部印加電圧印加Vbと同値となる。これは、直流的にはレゾネータ10が容量素子として作用し、また、上記結合容量Cc1が、共振回路30の第1の入出力部30aに接続される外部回路との間に介在するためである。また、同様に端子32の直流電位Vp2も電圧印加手段20Bでの外部印加電圧印加Vrefと同値となる。

【0051】

また、上記結合容量Cc1及びCc2は、その両端に印加する電位差(=電圧)により容量値が変化する電圧依存性を有する可変容量で構成する。

【0052】

図7(b)に前記共振回路30′を他回路と接続し、発振回路15′を構成した場合の構成例を示す。発振回路15′は、前記共振回路30′の他に、増幅回路部18と出力緩衝部19とから構成され、増幅回路18の入力端子18a、出力端子18bの直流電位Vi2及びVo2は、能動回路の内部素子のバイアス電圧などにより決定し、一定値に設定される。

【0053】

図7(b)において、共振回路30′の第1の入出力部30aは増幅回路部18の入力端子18aの電位Vi2と同電位となり、また、共振回路30′の第2の入出力部30bは増幅回路部18の出力端子18bの電位Vo2と同電位となる。また、図7(a)を鑑みると、MEMSレゾネータ10の第1の端子10aには電圧印加手段20Aにより直流電位Vp1が印加される。また、MEMSレゾネータ10の第2の端子10bには電圧印加手段20Bにより直流電位Vp2が印加される。

【0054】

この結果、MEMSレゾネータ10の第1、第2の入力端子間の電位差はVp1とVp2との差分値となり、この値がMEMSレゾネータ10のバイアス電圧Vcとなる。一方で、可変容量で構成された結合容量Cc1の両端の電位差は、前記Vp1と端子30aの電位Vi2との差分値となり、この値が結合容量Cc1のバイアス電圧となる。

【0055】

また、可変容量で構成された結合容量Cc2の両端の電位差は、前記Vp2と端子30bの電位Vo2との差分値となり、この値が結合容量Cc2のバイアス電圧となる。

【0056】

この第2実施形態では、結合容量Cc1及びCc2が設けられることで、共振周波数fnは以下の式(4)で与えられる。

fn=(1/2π)・(L1・C1)−1/2・[1+C1(Cc1+Cc2)/{Cc1・Cc2+C0(Cc1+Cc2)}]1/2・・・(4)

なお、この場合にCc1=Cc2であれば、fn=(1/2π)・(L1・C1)−1/2・[1+C1/{0.5Cc1+C0}]1/2・・・(5)となる。

したがって、この場合でも、上記式(1′)で示されるMEMSレゾネータ10自体の共振周波数より高い共振周波数が得られることになる。

【0057】

式(4)、及び式(5)は、前記結合容量Cc1,Cc2が共振周波数を決定する一要素であり、この値を変更する事で共振周波数の制御が可能である事を示している。

【0058】

本実施例では前記の通り上記結合容量Cc1、及びCc2を電圧依存型の可変容量とし、かつMEMSレゾネータの両端に印加されるバイアス電圧Vp1,Vp2に連動して前記Cc1及びCc2の容量値を制御する事を特徴とする。

【0059】

なお、上記結合容量Cc1及びCc2は前記バイアス電圧Vp1,Vp2の増加に対し、減少する特性を有する。レゾネータの機械的なばね定数kmは、前述の通り、バイアス電圧Vpの増加に伴い減少するため、式(2)で示した通り、レゾネータの等価直列容量C1は増加する。これを式(3)にあてはめると、C1の増加により、共振周波数fnは低下するが、同時に結合容量Cc1及びCc2の値を減少させる事で、共振周波数の変位量を抑制する事が出来る。

【0060】

また、上記の可変容量としては、第一の実施例に示した通り、MOS容量や可変容量ダイオードを用いる事で実現できる。また、前記の通り、可変容量素子は方向性を有するため、本発明に適用する際にはその方向性に注意を払う必要がある。例えば、図7(a)においては、可変容量素子にMOS容量を用いる場合、Cc1については、端子31の電位Vp1が端子30aの電位Vi2よりも高い場合は、端子31側にMOS容量のゲート側を、端子30a側にMOS容量のドレイン,ソース側を接続する必要がある。Cc2についても同様である。

【0061】

なお、Vp1もしくはVp2いずれかの電位が、端子30a若しくは端子30bの電位よりも低い場合は、可変容量素子を前記と逆方向に接続する必要がある。また、今回の発明の目的である、レゾネータの共振周波数の変動を抑圧するためには、電圧の増加に伴い、容量が増加する特性を有する可変容量を用いる必要がある。

【0062】

なお、上記のように結合容量そのものを可変容量で構成してもよいが、結合容量の少なくとも一部を可変容量で構成しても構わない。このように結合容量の少なくとも一部を可変容量で構成するとしているのは、結合容量Cc1、もしくはCc2自体が可変容量のみで構成されていてもよく、或いは、可変容量と、上記電圧領域で実質的に固定された容量値を有する付加容量との合成容量(並列合成容量又は直列合成容量)で構成されていてもよいという意味である。また、周波数変動抑制効果は減殺されるが、結合容量Cc1とCc2のどちらか一方を電圧依存性のない固定容量で構成しても良い。

【0063】

図示例において、上記の可変容量は、共振回路30′の動作状態において、MEMSレゾネータ10に印加されるバイアス電圧Vcが増加すると容量値が低下し、バイアス電圧Vcが減少すると容量値が増大するように構成される。すなわち、第2実施形態の場合には、Vc=Vp1−Vp2であるので、端子32の電位Vp2が一定値に固定された状態で、端子31の電位Vp1が上昇するとレゾネータに印加されるバイアス電圧Vcの増加とともに、レゾネータの共振周波数が下がる方向に作用するが、可変容量である結合容量Cc1の端子間の電位差も増加するのでその容量値が低下し、結合容量Cc1の変化分は共振周波数を上昇させる方向に寄与するため、共振回路の共振周波数の変動量を抑制する事が出来る。また、端子31の電位Vp1が低下すると、バイアス電圧Vcが減少するとともに、レゾネータの共振周波数が上がる方向に作用するが、結合容量Cc1の端子間の電位差も低下するのでその容量値が増大し、結合容量Cc1の変化分は共振周波数を低下させる方向に寄与するため、共振回路の共振周波数の変動量を抑制することが出来る。

【0064】

また、図示において、上記の可変容量は、共振回路30′の動作状態において、MEMSレゾネータ10に印加されるバイアス電圧Vcが増加すると容量値が低下し、バイアス電圧Vcが減少すると容量値が増大するように構成される。すなわち、第2実施形態の場合には、Vc=Vp1−Vp2であるので、端子31の電位Vp1が上昇し、端子32の電位Vp2がVp1の変化幅に対して少ない割合で上昇した場合、レゾネータに印加されるバイアス電圧Vcの増加とともに、レゾネータの共振周波数が下がる方向に作用するが、可変容量である結合容量Cc1の端子間の電位差も増加し、また、可変容量である結合容量Cc2の端子間の電位差も増加するので、これらの容量値が低下し、結合容量Cc1,Cc2の変化分は共振周波数を上昇させる方向に寄与するため、共振回路の共振周波数の変動量を抑制する事が出来る。また、端子31の電位Vp1,端子32の電位Vp2が低下した場合も同様に作用し、共振回路の共振周波数の変動量を抑制することが出来る。

【0065】

なお、本発明の構成は、上記の例とは逆に、第2実施形態の場合、結合容量Cc1もしくはCc2を両端電圧が増加すると容量値が単調に増加する電圧依存領域を備えた可変容量で構成することもできる。なお、このように構成する場合の作用については第1実施形態で説明したものと同様である。

【0066】

以上のように、可変容量が両端電圧の変化により容量値が単調に変化する電圧依存領域を有し、この電圧依存領域で動作させる場合に、その動作状況に応じて可変容量の電圧依存領域の特性を上述のいずれか(すなわち、両端電圧が増加すると容量値が単調に減少する特性か、或いは、その逆に両端電圧が増加すると容量値が単調に増加する特性か)に設定することにより、バイアス電圧の変化に起因する共振周波数の変動態様に関して、可変容量の容量値の変化に起因して変動幅を低減させる、または増進させることが可能になる。

【0067】

なお、結合容量の容量値、並びに、結合容量の少なくとも一部を構成する上記各種の可変容量の容量変化率は、実際に要求される共振周波数やバイアス電圧の値による両端電圧の範囲に応じて適宜に設定されることが好ましい。この場合に、可変容量自体の構造を適宜に設定することにより容量値や容量変化率を調整してもよいが、MEMSレゾネータ10に印加されるバイアス電圧と可変容量の両端電圧との関係を適宜に設定してもよい。いずれにしても、バイアス電圧の変動に起因する共振回路30、30′の共振周波数の変動を制御できるように構成すればよい。たとえば、バイアス電圧と可変容量の両端電圧の関係を変更する方法としては、結合容量Cc1、Cc2を可変容量に対し直列若しくは並列に(或いは双方の態様で)接続された他の容量との合成容量で構成する場合に、当該可変容量と他の容量との接続態様や接続数を変更することが挙げられる。

【0068】

図9は、本発明に係る共振回路30と、この共振回路30に接続された信号回路部40とを有する電子回路の実施例を示す概略回路構成図である。ここで、図示例では、第1実施形態と同様の共振回路30を用いた発振回路を構成した場合を示している。なお、図示例では、共振回路30として第1実施形態とは逆のMEMSレゾネータ10の第2の端子10b側にのみ電位供給部32及び結合容量Cc2を接続した場合を示してあるが、図6(a)に示す場合と実質的には等価である。

【0069】

この実施例では、共振回路30の入出力部30a、30bを信号回路部40に接続し、この信号回路部40には、共振回路30と並列に接続された負性抵抗を有する増幅回路INV1と、共振回路30と並列に接続された帰還抵抗Rfbとが設けられる。また、これらの増幅回路INV、帰還抵抗Rfb及び共振回路30の両端部は静電容量Cg及びCdを介して定電位(接地電位)に接続される。また、これらの並列回路は増幅回路INV2に接続され、この増幅回路INV2から出力電位Voutが出力される。

【0070】

図10は電子回路の他の実施例2を示す概略回路構成図である。この実施例2は、上記第2実施形態の共振回路30′と信号回路部40で構成した発振回路を示すもので、共振回路30′以外の構成は図9に示す実施例1と同様である。この実施例2では、共振回路30′においてMEMSレゾネータ10の両側にそれぞれバイアス回路20′の電位供給部31、32及び結合容量Cc1、Cc2が設けられるため、MEMSレゾネータ10のバイアス電圧をより確実に設定する事が可能になる。なお、電位供給部31,32に供給するそれぞれの電位は任意であり、例えば、図示例のように一方に第1の電位Vpを供給し、他方の第2の電位を接地電位とすることでバイアス電圧Vc=Vpを印加することができ、一方に第1の電位+Vp/2を供給し、他方に第2の電位−Vp/2を供給することでも同じバイアス電圧Vc=Vpを印加することができる。

【0071】

図11は電子回路のさらに別の実施例3を示す概略回路構成図である。この実施例3においても、共振回路30″以外の構成は上記各実施例と同様である。共振回路30″では、バイアス回路により第2の電位を与える電位供給部32と結合容量Cc2とが設けられる点で図9に示す実施例1と同様であるが、結合容量Cc2が可変容量Cc2′と付加容量Cc2″が並列に接続された合成容量によって構成される点で異なる。このように、結合容量が可変容量に他の静電容量が並列に接続された構成となっていても構わない。この場合には、結合容量Cc2の容量値が可変容量Cc2′の容量値と付加容量Cc2″の容量値の和となるため、結合容量Cc2の静電容量値を或る程度大きく確保するとともに、結合容量Cc2中の可変容量Cc2′の寄与割合を変えることで、可変容量Cc2′による共振回路30″の共振周波数への影響度合を調整することが可能になる。

【0072】

図12(a)はラダー型フィルタ回路の基本構成及び周波数帯域特性を示す説明図、図12(b)は電子回路の異なる実施例4を示す回路図である。この実施例4も、本発明に係る共振回路30を有する電子回路の実施例であるが、図示例では、第1実施形態と同様の共振回路30を用いたフィルタ回路50を構成した場合を示している。この実施例では、フィルタ回路50の入出力部50aと50bの間に直列共振器Rsを直列に接続するとともに、入出力部50aと50bの間と定電位(接地電位)とのに並列共振器Rpを接続している。そして、これらの直列共振器Rs及び並列共振器Rpとして上述の共振回路30を用いる。

【0073】

図12(a)に示すように、ラダー型フィルタ回路においては、直列共振器Rsと並列共振器Rpによってバンドパスフィルタを構成することができる。一般に、直列共振器Rsの共振周波数Fsrと反共振周波数Fsa、並列共振器Rpの共振周波数Fprと反共振周波数Fpaにおいて、共振周波数FsrとFprを僅かに(通常は数%)ずらすことにより、帯域透過特性を得ることができる。図12(a)に示す特性図では、信号透過率は直列共振器Rsの共振周波数Fsr=並列共振器Rpの反共振周波数Fpaで最大値となり、透過帯域の下限は並列共振器Rpの共振周波数Fpr、透過帯域の上限は直列共振器Rsの反共振周波数Fsaとなる。このような構成では、各共振器の共振周波数を高精度に設定する必要があるため、上述の本発明の構成はきわめて有効である。

【0074】

本実施例4では、例えば、図12(b)に示すように、フィルタ回路50の入出力部50aと50bの間に複数の直列共振器Rsを直列に接続し、入出力部50aと50bの間の各直列共振器Rsの前後位置と定電位である接地電位との間に並列共振器Rpを接続している。このように複数の直列共振器Rsと複数の並列共振器Rpを梯子状に接続している場合には、各共振器間の共振周波数を適宜の異なる値に調整することで所望の帯域を備えたフィルタ回路を構成できる。

【0075】

なお、本実施例では基本的に実施例1の結合容量を合成容量で実現したが、実施例2の結合容量を合成容量で実現してもよい。また、合成容量としては、上記のように複数の容量を並列に接続する場合に限らず、複数の容量を直列に接続してもよい。例えば、上述のMIS構造若しくはMOS構造を有するダイオードで結合容量を構成する場合、半導体中の空乏層と絶縁層(酸化層)が共に誘電体として機能するので、実質的には可変容量と付加容量とが直列に接続された回路構造が構成されたものと見ることもできる。この場合には、接続態様に応じて複数の容量のうちの少なくとも一つの容量である可変容量に印加される両端電圧が小さくなるため、特に可変容量の使用可能な電圧領域が限定されている場合に、当該電圧領域で可変容量を使用するように設計することも考えられる。さらに、結合容量を直列及び/又は並列に接続された複数の容量からなる回路構造で構成しても構わない。

【0076】

ここで、図6(a)に示す第1実施形態についてもう一度検討してみる。この第1実施形態において共振周波数を示す上記式(3)を書き直すと以下の式(6)が得られる。

fn=(1/2π)・L1−1/2・{1/C1+1/(C0+Cc1)}1/2・・・(6)

この式(6)をみると、等価直列容量C1の逆数と、等価並列容量C0と結合容量Cc1の和の逆数とが同じ重みで共振周波数に影響を与えることがわかる。したがって、バイアス電圧の変化に起因する等価直列容量C1の変化率と結合容量Cc1の変化率との関係にも依存するが、両変化率の大きさに極端な差がなければ、C1と、C0とCc1の和とがほぼ同じ値となっている場合に本発明の共振周波数の変動を最も抑制しやすくなることがわかる。

【0077】

しかしながら、本発明では、可変容量を設けることでバイアス電圧の変動に起因するMEMSレゾネータ10の共振周波数の変化をなくすことまでは必ずしも要求されず、当該共振周波数の変化を抑制すれば足りるので、必ずしも上記のように各容量値を精密に設定する必要はない。実際には、等価直列容量C1と等価並列容量C0はMEMSレゾネータ10の構造に依存するために独立に制御することはできないため、結合容量を等価直列容量C1の10分の1から10倍の範囲内で動作するように設定することにより、共振周波数の変動の抑制効果を高めることができる。

【0078】

MEMSレゾネータ10の一般的な構造寸法から見て、等価直列容量C1は10−12〜10−17F程度、等価並列容量C0は10−12〜10−14F程度、等価インダクタンスL1は100〜10−5H程度となる。例えば、結合容量Cc1(可変容量そのもので構成されている場合)が結合容量として最低限要求される容量値である10−12F程度であれば、等価直列容量C1、等価並列容量C0が10−12〜10−14F程度である場合、共振周波数の変動を充分に抑制することが可能になる。特に、MEMSレゾネータ10の構造を等価直列容量C1の値がC0と同じオーダーの値となるように設計すれば、結合容量Cc1の容量値を最低限要求される範囲内としつつ、バイアス電圧の変動に起因する共振周波数の変動をある程度抑制できる。

【0079】

本実施形態の共振回路及びこれを含む電子回路では、バイアス電圧Vcの変動に起因する振動子10の共振周波数の変動態様を可変容量を用いることで制御することができるため、共振特性の安定化や共振周波数の可変幅の増大を図ることができる。また、バイアス電圧による共振周波数の変動態様が制御されるため、バイアス電圧で共振周波数を調整する際に共振周波数の調整精度の向上や調整範囲の増大を図ることができ、高品位の共振回路を構成することも可能になる。

【0080】

本実施形態のMEMSレゾネータ10は、上記結合容量Cc1、Cc2及び信号回路部と共通の基板上に構成されることが電子回路やこれを含む電子装置のコンパクト化、製造コストの低減等を図る上で好ましい。このように構成した一例を図13に示す。図13は、MEMSレゾネータ10と結合容量Cc1を半導体基板上に形成した構造を示す概略縦断面図である。シリコン等の半導体よりなる基板1上には絶縁膜2を介してMEMSレゾネータ10が前述のように構成されている。一方、基板1の表層部には導電領域1A(例えば、基板1がp型基板であればn型不純物領域で構成できる。)が形成され、この周囲に素子間分離膜3が酸化シリコン等の絶縁体で構成される。導電領域1Aは絶縁膜2′を介して基板1上に形成された容量電極4と対向する。ここで、容量電極4は任意の導電材料で構成でき、任意の工程で形成できるが、MEMSレゾネータ10の固定電極12(下部導電層)と同材質で構成され、同工程にて形成されることが好ましい。

【0081】

また、導電領域1Aの一部表面部分には不純物濃度を高めた低抵抗領域1B(上記の例ではn型ドーパントのドーピング濃度を高めた領域)が形成され、この低抵抗領域1Bは基板1上に形成された接続電極5に導電接続される。この接続電極5もまた、任意の導電材料で構成でき、任意の工程で形成できるが、MEMSレゾネータ10の固定電極12(下部導電層)と同材質で構成され、同工程にて形成されることが好ましい。この導電領域1A、絶縁膜2′、容量電極4及び接続電極5により構成されるMOS容量が結合容量Cc1となる。

【0082】

基板1上には、酸化シリコン等よりなる層間絶縁膜6及び8と、MEMSレゾネータ10、結合容量Cc1及び図示しない信号回路部(図示しない基板1の表層部においてCMOS構造等により構成される。)間の接続を行う配線層7及び9とが交互に積層され、上述のように一体化された電子装置が構成される。ここで、上記実施形態の構成では、例えば、配線層7中の配線部7A(図示破線で示す。)によりMEMSレゾネータ10の可動電極13と結合容量Cc1とが導電接続される。図示例の場合には、MEMSレゾネータ10の端子部10a,10b、結合容量Cc1の両端部に相当する部分が接続パッド10x、10y、Cx、Cyとして外部と接続可能に構成され、例えば接続パッド10xが電位供給部31に相当しているが、このような態様に限定されるものではなく、必要のない接続パッドを設けなくても構わない。なお、最上層には保護膜10が酸化シリコンと窒化シリコンの2層構造等により形成される。

【0083】

MEMSレゾネータ10は、上記層間絶縁膜6,8、配線層7、9及び保護膜10よりなる基板1上の積層構造に取り囲まれた収容空間10A内に配置される。この収容空間10AはMEMSレゾネータ10の動作を可能にするための空間であり、必要に応じて内部を減圧したり、適宜に封止したりしてもよい。この収容空間10Aは、たとえば、上記層間絶縁膜6、8及び保護膜10を形成した後にフッ酸系エッチングによりこれらの層間絶縁膜6,8及び保護膜10を除去するリリース工程で形成される。

【0084】

上記のように集積回路技術(半導体製造技術)によってMEMSレゾネータ10、結合容量Cc1及び信号回路部を同一基板1上に一体に構成することで、電子回路や電子装置をコンパクトに構成できるとともに製造が容易になる。

【0085】

図14は別の電子回路若しくは電子装置におけるMEMSレゾネータ10及び結合容量Cc1の構成部分の例を示す。図示以外の構成は図13に示すものと同様である。この例では、図13に示すものと同様の部分には同一符号を付し、それらの説明は省略する。

【0086】

この構成例においては、基板1の表層部に導電領域1C、1Eが形成され、その領域間にゲート絶縁膜2′が配置され、このゲート絶縁膜2′上にゲート電極4′が形成される。また、導電領域1Cは低抵抗領域1Dを介して基板1上のソース電極5Aに導電接続され、導電領域1Dは低抵抗領域1Fを介して基板1上のドレイン電極5Bに導電接続される。これらの構造はMOSFET(MOSトランジスタ)を構成するが、本実施形態では、配線部7Bによってソースとドレインが短絡され、ゲート電極4′とソース・ドレイン間にMOS容量が構成され、これが結合容量Cc1とされる。また、振動子10は配線層7Cにより結合容量Cc1と導電接続される。

【0087】

上記各構成例においては、図14に示すMOS容量を構成するMOSFETと同様のトランジスタ構造によって増幅回路等(CMOS構造)を含む信号回路部が形成できる。

【0088】

なお、本発明の共振回路とこれに接続される信号回路部を含む電子回路若しくは電子装置としては、上述の各実施形態や実施例に示す信号回路部40のように発振回路を構成するものや上記フィルタ回路50等の各種のフィルタ回路を構成するもの以外に、送受信回路などの種々の回路構成を実現することができる。特に、発振回路とフィルタ回路を含む電子装置など、各種の電子装置を構成できる。また、MEMSレゾネータとバイアス回路からなる共振回路、信号回路部、電子回路等をそれぞれ、或いは、複数組み合わせて共通の基板上に構成することができる。

【0089】

尚、本発明の共振回路、発振回路、フィルタ回路及び電子装置は、上述の図示例にのみ限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。例えば、上記の共振回路中には実質的、本質的な動作に影響を与えない種々の回路素子を組み込むことができる。

【符号の説明】

【0090】

1…基板、2…絶縁膜、10…MEMSレゾネータ、10a…第1の端子、10b…第2の端子、11…下地層、12…固定電極、12a…対向部(振動子電極)、13…可動電極、13a…可動部(振動子電極)、20、20′20A、20B…電圧印加手段(バイアス回路)、30…共振回路、30a…第1の入出力部、30b…第2の入出力部、31、32…電位供給部、40…信号回路部、50…フィルタ回路、Cc1、Cc2…結合容量、Cc2′…可変容量、Cc2″…付加容量、C1…等価直列容量、C0…等価並列容量、L1…等価インダクタンス、R1…等価抵抗、INV1…負性抵抗を有する増幅回路

【技術分野】

【0001】

本発明は共振回路、発振回路、フィルタ回路及び電子装置に係り、特に、MEMSレゾネータを用いた共振回路の構成に関する。

【背景技術】

【0002】

最近の電子デバイス市場においては、MEMS(Micro Electro-Mechanical System)技術を用いた製品が加速的に浸透しつつある。MEMS技術を用いた製品とは、半導体製造技術を用いて基板上に形成された微小な構造体(MEMS構造体)を有する電気機械装置(MEMS装置)を言う。MEMS技術を用いたデバイスの具体的な事例としては、加速度センサ、角速度センサ、慣性センサ、圧力センサ等の各種のマイクロセンサ等が挙げられるが、その市場は近年急速に拡大しつつある。このように、MEMS技術は新たなデバイスの創出の可能性を多分に秘めており、今後は微小メカニカルリレー(スイッチ)や可変容量素子等の微小構造体の特徴を生かしたデバイスやそれらの組み合わせが順次実用化されていく見込みである。

【0003】

MEMS技術を用いた新しい応用例として、レゾネータ(振動子、発振子、共振子、共振器などとも言う。本願ではMEMSレゾネータと称する。)が挙げられる。MEMSレゾネータの動作原理としては、静電駆動・検出方式、圧電駆動・検出方式が代表的なものであるが、特に前者はCMOSプロセスのような半導体プロセスとの整合性がよく、小型化や低コスト化に有利な手法といえる。この静電駆動・検出方式は、可動電極と固定電極を有するMEMSレゾネータを形成し、静電力に起因する可動電極の振動を可動電極と固定電極の間の静電容量の変化によって検出するものである。MEMSレゾネータの一般的な透過特性及び位相特性の例は図3(a)及び(b)に示されている。この種のMEMSレゾネータを開示する文献としては、以下の特許文献1乃至3がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国特許第6249073号明細書

【特許文献2】米国特許第6424074号明細書

【特許文献3】特開2004−58228号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、前述のMEMSレゾネータにおいては、通常、振動子の可動電極と固定電極の間に直流バイアス電圧が印加される。この直流バイアス電圧が印加されると、振動子において振動が励起されやすくなり、共振特性がより顕著となる。ただし、振動子の両電極間に生ずる静電引力により可動電極が固定電極に接触してしまうPull−Inの発生を防止するために所定のマージンを確保した状態でバイアス電圧を設定しなければならない。このような状況において、通常、MEMSレゾネータの共振特性を向上させるには上記のマージンを確保しつつバイアス電圧を大きくすることが望まれるが、振動子の共振周波数はこのバイアス電圧の値によって変化する。即ち、印加するバイアス電圧が外的な要因によって変動した場合、MEMSレゾネータの共振周波数が変位するため、MEMSレゾネータを含む共振回路を含む発振回路やフィルタ回路では、前記バイアス電圧の変動により所望の発振周波数、もしくはフィルタ特性が得られなくなるという問題があった。

【0006】

すなわち、MEMSレゾネータの共振周波数は上記のバイアス電圧に依存するため、バイアス電圧を共振周波数と無関係に設定することができず、共振周波数の変化状況を制御できないため、これによって各種の回路構成においてMEMSレゾネータを用いることが難しいという問題点がある。

【0007】

本発明は上記問題点を解決するものであり、バイアス電圧の変動によるMEMSレゾネータの共振周波数の変動を制御することのできる共振回路を実現することにある。

【課題を解決するための手段】

【0008】

斯かる実情に鑑み、本発明の共振回路は、基板と、該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータと、該MEMSレゾネータの前記固定電極と前記可動電極の一方に接続された第1の端子に接続された第1の入出力部と、前記MEMSレゾネータの前記固定電極と前記可動電極の他方に接続された第2の端子に接続された第2の入出力部と、少なくとも前記第1の端子に電位を供給して前記第1の端子と前記第2の端子の間にバイアス電圧を印加する電圧印加手段と、前記第1の端子と前記第1の入出力部の間に接続され、両端の電位差の変化で容量値が変化する可変容量と、を具備することを特徴とする。

【0009】

本発明によれば、例えば、図15(a)に示すように、電圧印加手段(20)によりMEMSレゾネータ(10)の第1の端子(10a)と第2の端子(10b)の間にバイアス電圧(Vc)を印加し、前記第1の端子(10a)若しくは第2の端子(10b)に交流電圧を印加することで特定の共振周波数を有する共振動作を生じさせることができるが、電圧印加手段(20)が電位を供給する第1の端子(10a)に接続された第1の入出力部(30a)に、可変容量(Cc1)の一端を接続することにより、その両端の電位差により容量値が変化する構成とすることにより、電圧印加手段(20)により供給される第1の端子(10a)の電位が変化すると可変容量(Cc1)の両端の電位差も変化することから、MEMSレゾネータ(10)に印加されるバイアス電圧(Vc)の変動に応じたMEMSレゾネータ(10)の共振周波数の変化態様を可変容量(Cc1)の容量値の変化特性で変更することが可能になる。したがって、共振周波数のバイアス電圧に対する依存特性を変更することにより、共振周波数の値や変動幅を任意に設計することが可能となる。

【0010】

本発明の一の態様においては、前記可変容量は、その両端の電位差の変化により容量値が単調に変化する電圧依存領域を少なくとも一部に有し、当該電圧依存領域において前記バイアス電圧の増大により容量値が単調に減少する特性を備える。この場合には、バイアス電圧が増大すると本来的には共振周波数を低下させる方向に作用するが、バイアス電圧の増大により可変容量の容量値が減少し、この容量値の減少は共振周波数を増加させる方向に作用するので、可変容量による共振周波数の自動安定効果を得ることができ、バイアス電圧の変化による共振周波数の変動を抑制することが可能になり、共振周波数の安定化を図ることができる。

【0011】

本発明の他の態様においては、前記電圧印加手段は、前記第1の端子に第1の電位を供給するとともに、前記第2の端子を接地電位とする。この場合には、電圧印加手段が第1の端子に第1の電位を供給するが第2の端子の電位が固定値であるため、第1の端子に印加される電位が変化するとMEMSレゾネータに印加される電位差、即ち、レゾネータのバイアス電圧も変化するが、同時に、前記結合容量の他端に印加される電位が一定値である場合、結合容量の両端の電位差も前記バイアス電圧と連動して変化し、結合容量値が変化減少するので、MEMSレゾネータの共振周波数の変化態様を結合容量の容量値の変化で変更することが可能になる。

【0012】

本発明のさらに他の態様においては、前記電圧印加手段は、前記第1の端子に第1の電位を供給するとともに前記第2の端子に第2の電位を供給する。この場合には、図15(b)に示すように、電圧印加手段(20′)によりMEMSレゾネータ(10)の第1の端子(10a)と第2の端子(10b)にそれぞれ供給電位(Vp)及び(Vq)を与えることができるので、MEMSレゾネータ(10)に対してバイアス電圧(Vc)をより確実に与えることができる。また、電圧印加手段(20′)が第1の端子(10a)に可変電位である第1の電位(Vp)を供給するが第2の端子(10b)の電位(Vq)を固定値とすれば、第1の端子(10a)に印加される電位(Vp)が変化するとMEMSレゾネータ(10)に印加される電位差、即ち、レゾネータのバイアス電圧(Vc)も変化するが、同時に、前記可変容量(Cc1)の他端に印加される電位が一定値である場合、可変容量(Cc1)の両端の電位差も前記バイアス電圧(Vc)と連動して変化し、可変容量の容量値が変化するので、MEMSレゾネータ(10)の共振周波数の変化態様を可変容量の容量値の変化で変更することが可能になる。

【0013】

本発明の別の態様においては、前記可変容量と並列に接続された付加容量をさらに有する。これによれば、可変容量と並列に付加容量が接続されることで、結合容量として機能する容量値を確保しつつ、可変容量の容量値や可変特性を振動子の共振特性に整合させることが可能になるので、共振周波数の変動をより低減可能となるとともに、各部の設計の自由度を高めることができる。

【0014】

本発明の別の共振回路は、基板と、該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータと、該MEMSレゾネータの前記固定電極と前記可動電極の一方に接続された第1の端子に接続された第1の入出力部と、前記MEMSレゾネータの前記固定電極と前記可動電極の他方に接続された第2の端子に接続された第2の入出力部と、前記第1の端子に電位を供給することにより前記第1の端子と前記第2の端子の間に前記第1の端子に供給された電位が上昇するに従って増大するバイアス電圧を印加する電圧印加手段と、前記第1の端子と前記第1の入出力部の間に接続され、前記第1の端子に供給された電位が上昇すると容量値が減少する可変容量と、を具備することを特徴とする。ただし、本発明には、他の態様として、上記電圧印加手段において、第1の端子に供給された電位が上昇するに従ってバイアス電圧が減少する場合も含まれる。また、上記第1の端子が供給された電位が上昇するに従ってバイアス電圧が増大する場合と、減少する場合のいずれにおいても、上記可変容量の容量値が増大する構成が含まれる。

【0015】

次に、本発明の電子回路としては、上記のいずれかに記載の共振回路と、該共振回路に接続される増幅回路部を有する外部回路とで構成される発振回路がある。この発振回路においては、前記外部回路が前記第1の入出力部及び前記第2の入出力部に接続される。また、上記のいずれかに記載の共振回路を含むフィルタ回路が挙げられる。このフィルタ回路において、フィルタ回路の入出力間に前記共振回路が直列に接続されるとともに、フィルタ回路の入出力間の前記共振回路の前記入出力部と定(接地)電位との間にも前記共振回路が接続される場合がある。さらに、本発明の電子装置は、上記のいずれかに記載の回路(共振回路、発振回路、フィルタ回路)を含む。

【0016】

また、本発明の共振回路においては、前記MEMSレゾネータ、前記電圧印加手段、前記可変容量が同一基板上に形成されていることが好ましい。また、本発明の発振回路において、前記MEMSレゾネータ、前記電圧印加手段、前記可変容量及び前記増幅回路部が同一基板上に形成されていることが好ましい。さらに、本発明のフィルタ回路において、前記MEMSレゾネータ、前記電圧印加手段及び前記可変容量が同一基板上に形成されていることが好ましい。また、本発明の電子装置において、上記の発振回路と、上記のフィルタ回路とが同一基板上に形成されていることが好ましい。

【0017】

なお、上述の共振回路、電子回路、電子装置における上記基板としては、シリコン基板等の半導体基板、ガラス基板、セラミックス基板などが挙げられるが、MEMSレゾネータを構成することから、シリコン基板等の半導体基板を用いた半導体装置を構成することが好ましい。

【0018】

本発明の一の態様においては、前記可変容量を構成する一対の容量電極のうちの少なくとも一方が前記固定電極と可動電極の少なくとも一方と同材質で構成される。このようにすることで、可変容量を設けることによる製造工程の増加を抑制できる。

【0019】

この場合に、前記可変容量がMIS容量であることが好ましい。これによれば、集積回路技術によって信号回路部を形成する場合に容易かつ効率的に可変容量を形成できる。ここで、前記MIS容量がMOS容量であることが好ましく、さらにMOSFETで構成されることが望ましい。MOSFETはCMOS等の増幅回路に用いられる電子素子であるので、MOS容量をMOSFETで構成することで、さらに容易かつ効率的に可変容量を形成できる。

【0020】

本発明の異なる態様においては、前記可変容量が前記MEMSレゾネータの等価直列容量の10分の一から10倍の範囲内で動作する。ここで言う等価直列容量とは、MEMSレゾネータの電気的な等価回路における、直列共振部の容量値を示す。一般に可変容量の容量特性を自由に設定することは難しいが、可変容量がMEMSレゾネータの等価直列容量(バイアス電圧に連動して変動する容量成分)の10分の一から10倍の範囲内であれば、両者の容量値のオーダーがほぼ同様となるので、可変容量の容量特性によって共振周波数の変動を抑制する効果が高くなる。

【0021】

本発明のさらに異なる態様においては、前記MEMSレゾネータの等価直列容量が1.0×10−11〜10−13[F]の範囲内である。MEMSレゾネータの等価直列容量がこの範囲であれば、通常用いられる結合容量の容量値とほぼ同様のオーダーを有する値となるので、可変容量において結合容量としての機能を確保しつつ、共振周波数の変動の抑制効果を得ることができる。

【発明の効果】

【0022】

本発明によれば、MEMSレゾネータの共振周波数の変化態様を制御することができるので、共振周波数の要求特性に応じた設計を行うことができるという優れた効果を奏し得る。

【図面の簡単な説明】

【0023】

【図1】本発明に係る共振回路を構成するMEMSレゾネータの構成例を示す概略斜視図。

【図2】同MEMSレゾネータの縦断面図(a)及び(b)。

【図3】MEMSレゾネータの通過特性及び位相変位の周波数依存性を示すグラフ(a)及び(b)。

【図4】MEMSレゾネータのバイアス電圧依存性を示すグラフ。

【図5】MEMSレゾネータの等価回路図。

【図6】共振回路の第1実施形態を示す回路図(a)と発振回路構成例を示す構成図(b)。

【図7】共振回路の第2実施形態を示す回路図(a)と発振回路構成例を示す構成図(b)。

【図8】MOSFETによる構成を示す図及び容量特性図。

【図9】電子回路(発振回路)の実施例1の構成を示す回路図。

【図10】電子回路(発振回路)の実施例2の構成を示す回路図。

【図11】電子回路(発振回路)の実施例3の構成を示す回路図。

【図12】電子回路(フィルタ回路)の実施例4の構成を示す回路図。

【図13】電子回路若しくは電子装置の具体的断面構造を示す縦断面図。

【図14】電子回路若しくは電子装置の別の具体的断面構造を示す縦断面図。

【図15】本発明の共振回路の構成例を示す概略構成図(a)及び(b)。

【発明を実施するための形態】

【0024】

次に、添付図面を参照して本発明の実施形態について詳細に説明する。図1は本実施形態のMEMSレゾネータ10の構成例を示す概略斜視図、図2は図1のA−A線及びB−B線に沿った断面を示す同振動子10の断面図(a)及び(b)である。

【0025】

MEMSレゾネータ10は、シリコン単結晶基板等の半導体基板等よりなる基板1上に構成される。基板1上には酸化シリコン(SiO2)等の絶縁膜2が形成され、さらに絶縁膜2上には窒化シリコン等の下地層11が形成される。下地層11上には、ドーピングにより導電性が付与された多結晶シリコン等よりなる固定電極12と、同様の材質よりなる可動電極13とが形成される。ここで、MEMSレゾネータ10の振動子電極を構成する固定電極12と可動電極13の可動部13aは基板1上において適宜の間隔で相互に上下方向に対向配置される。そして、可動部13aは対向部12aとの間に生ずる静電引力に応じて撓み、対向部12aとの間の対向間隔を変化させる方向に可動に構成される。

【0026】

上記固定電極12及び可動電極13の製造においては、まず、下地層11上にCVD法等により上記多結晶シリコン等の導電材料からなる第1層を形成し、この第1層をパターニングすることで、上記固定電極12を形成する。次に、その上にSiO2等から成る犠牲層(図示せず)を前記固定電極12の表面に一定厚だけ形成する。その後に、この上に上記の多結晶シリコン等の導電材料からなる第2層を形成し、これをパターニングすることで構造体の一部が下地層11上に固定された状態で可動電極13が形成される。最後に、緩衝フッ酸等の適宜のエッチング液若しくはエッチングガスにより上記犠牲層を除去することで、可動電極13の上部構造が上記可動部13aとして基板上から分離され、基部において支持されるとともに、固定電極12上に張り出した両持ち梁状に形成される。

【0027】

なお、図示のMEMSレゾネータ10は一対の振動子電極の一方が両持ち梁状に構成されることにより可動部13aとされた両持ち梁構造を有するが、これは本発明の振動子の一例に過ぎず、本発明においては、MEMSレゾネータとして、片持ち梁状に構成されたもの、円盤状に構成されたものなど、種々の形状、構造を採用したものを用いることが可能である。

【0028】

図3は本発明に係るMEMSレゾネータ10の電気的特性を示す概略特性図である。ここで、図3(a)はMEMSレゾネータ10に交流信号を入力したときの通過特性を示すグラフ、図3(b)は位相変位を示すグラフである。このように、MEMSレゾネータ10は適宜の共振周波数を有する共振特性を備えているが、この共振周波数fnは、以下の式(1)で示される。

fn=(1/2π)・(km/meff)1/2・・・(1)

ここで、kmは振動子10の構造から決定されるばね定数、meffは同構造の有効質量である。

【0029】

一方、MEMSレゾネータ10の固定電極12と可動電極13の間に適宜のバイアス電圧(直流バイアス)を印加すると両電極の間に静電引力が発生し、上記ばね定数kmを減少させる様に作用する。このため、上記式(1)により共振周波数fnが低下する。そして、一般に、バイアス電圧が増加するほど共振周波数fnは減少することになる。

【0030】

図4は、MEMSレゾネータ10に印加したバイアス電圧Vbを変化させたときの交流信号の共振特性を示すグラフである。このように、バイアス電圧Vbが増加するほど共振周波数fnは低下する。

【0031】

図5はMEMSレゾネータの等価回路図である。MEMSレゾネータ10は、等価直列容量C1、等価直列インダクタンスL1、等価直列抵抗R1の直列回路部分と、等価並列容量C0とが並列に接続されてなる等価回路によって示される。この等価回路定数で上記直列共振周波数fnを示すと、

fn=(1/2π)・(L1・C1)−1/2・・・(1′)

となる。

【0032】

この場合、上記の等価直列容量C1は以下の式(2)で表される。

C1=η2/km・・・(2)

ここで、ηは電気機械変換係数(振動による変位エネルギーが電気エネルギーに変換されるときの効率)である。そして、上記のバイアス電圧の変位に起因してMEMSレゾネータ10のばね定数kmが低下すると、等価直列容量C1は増加し、これによって上記式(1′)により共振周波数が低下することがわかる。

【0033】

図6(a)には本実施形態の共振回路構成例を示す。ここで、図6(a)に示す第1実施形態の共振回路30では、MEMSレゾネータ10と、前記MEMSレゾネータ10の第1の端子10a側に設けられた第1の入出力部30aと、上記MEMSレゾネータ10の第2の端子部10b側に設けられた第2の入出力部30bと、MEMSレゾネータ10の第1の端子10aと前記共振回路の第1の入出力部30aとの間に接続された結合容量Cc1と、前記MEMSレゾネータ10の第1の端子10aと前記結合容量Cc1との間の端子31に接続された電圧印加手段20とから構成される。

【0034】

ここで、電圧印加手段20は、図示例の場合、電位Vbの電圧源と抵抗Rpとによって構成される。端子31の直流電位Vpは電圧印加手段20での外部印加電圧印加Vbと同値となる。これは、直流的にはレゾネータ10が容量素子として作用し、また、上記結合容量Cc1が、共振回路30の第1の入出力部30aに接続される外部回路との間に介在するためである。

【0035】

また、上記結合容量Cc1は、その両端に印加する電位差(=電圧)により容量値が変化する電圧依存性を有する可変容量で構成する。本実施形態においてCc1は可変容量であるが、これを結合容量と称するのは、共振回路30を外部回路と接続した場合にCc1が結合容量としての機能をも有するからであり、可変容量Cc1自体を何ら限定する趣旨ではない。

【0036】

図6(b)に前記共振回路30を他回路と接続し、発振回路15を構成した場合の構成例を示す。発振回路は、前記共振回路30の他に、増幅回路部16と出力緩衝部17とから構成され、増幅回路16の入力端子16a、出力端子16bの直流電位Vi及びVoは、能動回路の内部素子のバイアス電圧などにより決定し、一定値に設定される。図6(b)において、共振回路30の第1の入出力部30aは増幅回路部16の入力端子16aの電位Viと同電位となり、また、共振回路30の第2の入出力部30bは増幅回路部16の出力端子16bの電位Voと同電位となる。また、図6(a)に示すように、MEMSレゾネータ10の第1の端子10aには、電圧印加手段20により直流電位Vpが印加される。

【0037】

この結果、MEMSレゾネータ10の第1、第2の入力端子間の電位差はVpと端子30bの電位Voとの差分値となり、この値がMEMSレゾネータ10のバイアス電圧Vcとなる。一方で、可変容量で構成された結合容量Cc1の両端の電位差は、前記Vpと端子30aの電位Viとの差分値となり、この値が結合容量Cc1のバイアス電圧となる。

【0038】

この第1実施形態では、結合容量Cc1が接続されるため、上記式(1′)とは異なり、共振周波数fnは以下の式(3)で与えられる。

fn=(1/2π)・(L1・C1)−1/2・{1+C1/(C0+Cc1)}1/2・・・(3)

式(3)は、前記結合容量Cc1が共振周波数を決定する一要素であり、この値を変更する事で共振周波数の制御が可能である事を示している。

【0039】

本実施例では前記の通り上記結合容量Cc1を電圧依存型の可変容量とし、かつMEMSレゾネータの一端に印加される供給電位Vpに連動して前記Cc1の容量値を制御する事を特徴とする。上記結合容量Cc1は供給電位Vpの増加に対し、容量値が減少する特性を有する。

【0040】

レゾネータの機械的なばね定数kmは、前述の通り、バイアス電圧Vcの増加に伴い減少するため、式(2)で示した通り、レゾネータの等価直列容量C1は増加する。これを式(3)にあてはめると、C1の増加により、共振周波数fnは低下するが、同時に結合容量Cc1の値を減少させる事で、共振周波数の変位量を抑制する事が出来る。

【0041】

また、上記の可変容量としては、標準的な半導体プロセスとの整合性を考慮した場合、図8(a)に示されるMOSFETを用いたMOS容量を用いることができる。すなわち、MOSFETのソースとドレインを短絡し、これらとゲートとの間にMOS容量が構成される例を用いることができる。このMOS容量の容量値は図8(b)の右側のグラフに示すように電圧依存性を有する。

【0042】

また、上記の可変容量としては、前記MOS容量の他、一般的にバリキャップ若しくはバラクタと呼ばれる可変容量ダイオード素子を用いても良い。この場合、MOS容量と比較して高周波特性が良好であるため、より高い周波数の回路に本発明を適用する場合はバリキャップを用いる事が好ましい。なお、これら可変容量素子は方向性を有するため、本発明に適用する際にはその方向性に注意を払う必要がある。例えば、図6(a)においては、可変容量素子にMOS容量を用いる場合、端子31の電位Vpが端子30aの電位Viよりも高い場合は、端子31側にMOS容量のゲート側を、端子30a側にMOS容量のドレイン,ソース側を接続する必要がある。逆方向に接続した場合、MOS容量は蓄積状態で動作するために、バイアス電圧に対する容量変位が発生しなくなる。

【0043】

なお、上記のように結合容量そのものを可変容量で構成してもよいが、結合容量の少なくとも一部を可変容量で構成しても構わない。このように結合容量の少なくとも一部を可変容量で構成するとしているのは、結合容量Cc1自体が可変容量のみで構成されていてもよく、或いは、可変容量と、上記電圧領域で実質的に固定された容量値を有する付加容量との合成容量(並列合成容量又は直列合成容量)で構成されていてもよいという意味である。

【0044】

図示例において、上記の可変容量は、共振回路30の動作状態において、MEMSレゾネータ10に印加されるバイアス電圧Vcが増加すると容量値が低下し、バイアス電圧Vcが減少すると容量値が増大するように構成される。すなわち、第1実施形態の場合には、Vc=Vp−Voであるので、第1の電位端子31の電位Vpが上昇するとレゾネータに印加されるバイアス電圧Vcの増加とともに、レゾネータの共振周波数が下がる方向に作用するが、可変容量である結合容量Cc1の端子間の電位差も増加するのでその容量値が低下し、結合容量Cc1の変化分は共振周波数を上昇させる方向に寄与するため、共振回路の共振周波数の変動量を抑制する事が出来る。また、端子31の電位Vpが低下すると、バイアス電圧Vcが減少するとともに、レゾネータの共振周波数が上がる方向に作用するが、結合容量Cc1の端子間の電位差も低下するのでその容量値が増大し、結合容量Cc1の変化分は共振周波数を低下させる方向に寄与するため、共振回路の共振周波数の変動量を抑制することが出来る。

【0045】

なお、本発明の構成は、上記の例とは逆に、第1実施形態の場合、結合容量Cc1を両端電圧が増加すると容量値が単調に増加する電圧依存領域を備えた可変容量で構成することでも実現できる。

【0046】

この場合、端子31に印加されるバイアス電圧の増減に対する周波数変動幅は拡大するように作用するため、本発明の主目的である、バイアス電圧のばらつきに対する周波数の変動を抑制するとは逆の目的で、例えば、バイアス電圧により発振周波数を変動できる、電圧制御発振器(VCO)の出力周波数範囲の拡大や、フィルタ回路における、帯域可変フィルタなどに適用する場合の帯域可変幅の拡大に有用である。

【0047】

例えば、第1実施形態の場合には、Vc=Vp−Voであるので、第1の電位端子31の電位Vpが上昇するとレゾネータに印加されるバイアス電圧Vcの増加とともに、レゾネータの共振周波数が下がる方向に作用するが、可変容量である結合容量Cc1の端子間の電位差も増加するのでその容量値が増加し、結合容量Cc1の変化分も共振周波数を低下させる方向に寄与するため、共振回路の共振周波数の変動量が拡大する。また、端子31の電位Vpが低下すると、バイアス電圧Vcの減少とともに、レゾネータの共振周波数が上がる方向に作用するが、結合容量Cc1の端子間の電位差も低下するため、その容量値も減少し、結合容量Cc1の変化分は共振周波数を上昇させる方向に寄与するため、共振回路の共振周波数の変動量が拡大する。

【0048】

以上のように、可変容量が両端電圧の変化により容量値が単調に変化する電圧依存領域を有し、この電圧依存領域で動作させる場合に、その動作状況に応じて可変容量の電圧依存領域の特性を上述のいずれか(すなわち、両端電圧が増加すると容量値が単調に減少する特性か、或いは、その逆に両端電圧が増加すると容量値が単調に増加する特性か)に設定することにより、バイアス電圧の変化に起因する共振周波数の変動を、可変容量の容量値の変化に起因して共振周波数の変動幅を補償する、または増進させることが可能になる。

【0049】

図7(a)には本実施形態の他の共振回路構成例を示す。ここで、図7(a)に示す第2実施形態の共振回路30′では、MEMSレゾネータ10と、前記MEMSレゾネータ10の第1の端子10a側に設けられた第1の入出力部30aと、上記MEMSレゾネータ10の第2の端子部10b側に設けられた第2の入出力部30bと、MEMSレゾネータ10の第1の端子10aと前記共振回路の第1の入出力部30aとの間に接続された結合容量Cc1と、MEMSレゾネータ10の第2の端子10bと前記共振回路の第2の入出力部30bとの間に接続された結合容量Cc2と、前記MEMSレゾネータ10の第1の端子10aと前記結合容量Cc1との間の端子31に接続された電圧印加手段20Aと、前記MEMSレゾネータ10の第2の端子10bと前記結合容量Cc2との間の端子32に接続された電圧印加手段20Bとから構成される。これらの電圧印加手段20A及び20Bは本発明の電圧印加手段20′を構成する。

【0050】

ここで、電圧印加手段20Aは、図示例の場合、電位Vbの電圧源と抵抗Rpとによって構成される。また、電圧印加手段20Bは、電位Vrefの電圧源と抵抗Rqとによって構成される。端子31の直流電位Vp1は電圧印加手段20での外部印加電圧印加Vbと同値となる。これは、直流的にはレゾネータ10が容量素子として作用し、また、上記結合容量Cc1が、共振回路30の第1の入出力部30aに接続される外部回路との間に介在するためである。また、同様に端子32の直流電位Vp2も電圧印加手段20Bでの外部印加電圧印加Vrefと同値となる。

【0051】

また、上記結合容量Cc1及びCc2は、その両端に印加する電位差(=電圧)により容量値が変化する電圧依存性を有する可変容量で構成する。

【0052】

図7(b)に前記共振回路30′を他回路と接続し、発振回路15′を構成した場合の構成例を示す。発振回路15′は、前記共振回路30′の他に、増幅回路部18と出力緩衝部19とから構成され、増幅回路18の入力端子18a、出力端子18bの直流電位Vi2及びVo2は、能動回路の内部素子のバイアス電圧などにより決定し、一定値に設定される。

【0053】

図7(b)において、共振回路30′の第1の入出力部30aは増幅回路部18の入力端子18aの電位Vi2と同電位となり、また、共振回路30′の第2の入出力部30bは増幅回路部18の出力端子18bの電位Vo2と同電位となる。また、図7(a)を鑑みると、MEMSレゾネータ10の第1の端子10aには電圧印加手段20Aにより直流電位Vp1が印加される。また、MEMSレゾネータ10の第2の端子10bには電圧印加手段20Bにより直流電位Vp2が印加される。

【0054】

この結果、MEMSレゾネータ10の第1、第2の入力端子間の電位差はVp1とVp2との差分値となり、この値がMEMSレゾネータ10のバイアス電圧Vcとなる。一方で、可変容量で構成された結合容量Cc1の両端の電位差は、前記Vp1と端子30aの電位Vi2との差分値となり、この値が結合容量Cc1のバイアス電圧となる。

【0055】

また、可変容量で構成された結合容量Cc2の両端の電位差は、前記Vp2と端子30bの電位Vo2との差分値となり、この値が結合容量Cc2のバイアス電圧となる。

【0056】

この第2実施形態では、結合容量Cc1及びCc2が設けられることで、共振周波数fnは以下の式(4)で与えられる。

fn=(1/2π)・(L1・C1)−1/2・[1+C1(Cc1+Cc2)/{Cc1・Cc2+C0(Cc1+Cc2)}]1/2・・・(4)

なお、この場合にCc1=Cc2であれば、fn=(1/2π)・(L1・C1)−1/2・[1+C1/{0.5Cc1+C0}]1/2・・・(5)となる。

したがって、この場合でも、上記式(1′)で示されるMEMSレゾネータ10自体の共振周波数より高い共振周波数が得られることになる。

【0057】

式(4)、及び式(5)は、前記結合容量Cc1,Cc2が共振周波数を決定する一要素であり、この値を変更する事で共振周波数の制御が可能である事を示している。

【0058】

本実施例では前記の通り上記結合容量Cc1、及びCc2を電圧依存型の可変容量とし、かつMEMSレゾネータの両端に印加されるバイアス電圧Vp1,Vp2に連動して前記Cc1及びCc2の容量値を制御する事を特徴とする。

【0059】

なお、上記結合容量Cc1及びCc2は前記バイアス電圧Vp1,Vp2の増加に対し、減少する特性を有する。レゾネータの機械的なばね定数kmは、前述の通り、バイアス電圧Vpの増加に伴い減少するため、式(2)で示した通り、レゾネータの等価直列容量C1は増加する。これを式(3)にあてはめると、C1の増加により、共振周波数fnは低下するが、同時に結合容量Cc1及びCc2の値を減少させる事で、共振周波数の変位量を抑制する事が出来る。

【0060】

また、上記の可変容量としては、第一の実施例に示した通り、MOS容量や可変容量ダイオードを用いる事で実現できる。また、前記の通り、可変容量素子は方向性を有するため、本発明に適用する際にはその方向性に注意を払う必要がある。例えば、図7(a)においては、可変容量素子にMOS容量を用いる場合、Cc1については、端子31の電位Vp1が端子30aの電位Vi2よりも高い場合は、端子31側にMOS容量のゲート側を、端子30a側にMOS容量のドレイン,ソース側を接続する必要がある。Cc2についても同様である。

【0061】

なお、Vp1もしくはVp2いずれかの電位が、端子30a若しくは端子30bの電位よりも低い場合は、可変容量素子を前記と逆方向に接続する必要がある。また、今回の発明の目的である、レゾネータの共振周波数の変動を抑圧するためには、電圧の増加に伴い、容量が増加する特性を有する可変容量を用いる必要がある。

【0062】

なお、上記のように結合容量そのものを可変容量で構成してもよいが、結合容量の少なくとも一部を可変容量で構成しても構わない。このように結合容量の少なくとも一部を可変容量で構成するとしているのは、結合容量Cc1、もしくはCc2自体が可変容量のみで構成されていてもよく、或いは、可変容量と、上記電圧領域で実質的に固定された容量値を有する付加容量との合成容量(並列合成容量又は直列合成容量)で構成されていてもよいという意味である。また、周波数変動抑制効果は減殺されるが、結合容量Cc1とCc2のどちらか一方を電圧依存性のない固定容量で構成しても良い。

【0063】

図示例において、上記の可変容量は、共振回路30′の動作状態において、MEMSレゾネータ10に印加されるバイアス電圧Vcが増加すると容量値が低下し、バイアス電圧Vcが減少すると容量値が増大するように構成される。すなわち、第2実施形態の場合には、Vc=Vp1−Vp2であるので、端子32の電位Vp2が一定値に固定された状態で、端子31の電位Vp1が上昇するとレゾネータに印加されるバイアス電圧Vcの増加とともに、レゾネータの共振周波数が下がる方向に作用するが、可変容量である結合容量Cc1の端子間の電位差も増加するのでその容量値が低下し、結合容量Cc1の変化分は共振周波数を上昇させる方向に寄与するため、共振回路の共振周波数の変動量を抑制する事が出来る。また、端子31の電位Vp1が低下すると、バイアス電圧Vcが減少するとともに、レゾネータの共振周波数が上がる方向に作用するが、結合容量Cc1の端子間の電位差も低下するのでその容量値が増大し、結合容量Cc1の変化分は共振周波数を低下させる方向に寄与するため、共振回路の共振周波数の変動量を抑制することが出来る。

【0064】

また、図示において、上記の可変容量は、共振回路30′の動作状態において、MEMSレゾネータ10に印加されるバイアス電圧Vcが増加すると容量値が低下し、バイアス電圧Vcが減少すると容量値が増大するように構成される。すなわち、第2実施形態の場合には、Vc=Vp1−Vp2であるので、端子31の電位Vp1が上昇し、端子32の電位Vp2がVp1の変化幅に対して少ない割合で上昇した場合、レゾネータに印加されるバイアス電圧Vcの増加とともに、レゾネータの共振周波数が下がる方向に作用するが、可変容量である結合容量Cc1の端子間の電位差も増加し、また、可変容量である結合容量Cc2の端子間の電位差も増加するので、これらの容量値が低下し、結合容量Cc1,Cc2の変化分は共振周波数を上昇させる方向に寄与するため、共振回路の共振周波数の変動量を抑制する事が出来る。また、端子31の電位Vp1,端子32の電位Vp2が低下した場合も同様に作用し、共振回路の共振周波数の変動量を抑制することが出来る。

【0065】

なお、本発明の構成は、上記の例とは逆に、第2実施形態の場合、結合容量Cc1もしくはCc2を両端電圧が増加すると容量値が単調に増加する電圧依存領域を備えた可変容量で構成することもできる。なお、このように構成する場合の作用については第1実施形態で説明したものと同様である。

【0066】

以上のように、可変容量が両端電圧の変化により容量値が単調に変化する電圧依存領域を有し、この電圧依存領域で動作させる場合に、その動作状況に応じて可変容量の電圧依存領域の特性を上述のいずれか(すなわち、両端電圧が増加すると容量値が単調に減少する特性か、或いは、その逆に両端電圧が増加すると容量値が単調に増加する特性か)に設定することにより、バイアス電圧の変化に起因する共振周波数の変動態様に関して、可変容量の容量値の変化に起因して変動幅を低減させる、または増進させることが可能になる。

【0067】

なお、結合容量の容量値、並びに、結合容量の少なくとも一部を構成する上記各種の可変容量の容量変化率は、実際に要求される共振周波数やバイアス電圧の値による両端電圧の範囲に応じて適宜に設定されることが好ましい。この場合に、可変容量自体の構造を適宜に設定することにより容量値や容量変化率を調整してもよいが、MEMSレゾネータ10に印加されるバイアス電圧と可変容量の両端電圧との関係を適宜に設定してもよい。いずれにしても、バイアス電圧の変動に起因する共振回路30、30′の共振周波数の変動を制御できるように構成すればよい。たとえば、バイアス電圧と可変容量の両端電圧の関係を変更する方法としては、結合容量Cc1、Cc2を可変容量に対し直列若しくは並列に(或いは双方の態様で)接続された他の容量との合成容量で構成する場合に、当該可変容量と他の容量との接続態様や接続数を変更することが挙げられる。

【0068】

図9は、本発明に係る共振回路30と、この共振回路30に接続された信号回路部40とを有する電子回路の実施例を示す概略回路構成図である。ここで、図示例では、第1実施形態と同様の共振回路30を用いた発振回路を構成した場合を示している。なお、図示例では、共振回路30として第1実施形態とは逆のMEMSレゾネータ10の第2の端子10b側にのみ電位供給部32及び結合容量Cc2を接続した場合を示してあるが、図6(a)に示す場合と実質的には等価である。

【0069】

この実施例では、共振回路30の入出力部30a、30bを信号回路部40に接続し、この信号回路部40には、共振回路30と並列に接続された負性抵抗を有する増幅回路INV1と、共振回路30と並列に接続された帰還抵抗Rfbとが設けられる。また、これらの増幅回路INV、帰還抵抗Rfb及び共振回路30の両端部は静電容量Cg及びCdを介して定電位(接地電位)に接続される。また、これらの並列回路は増幅回路INV2に接続され、この増幅回路INV2から出力電位Voutが出力される。

【0070】

図10は電子回路の他の実施例2を示す概略回路構成図である。この実施例2は、上記第2実施形態の共振回路30′と信号回路部40で構成した発振回路を示すもので、共振回路30′以外の構成は図9に示す実施例1と同様である。この実施例2では、共振回路30′においてMEMSレゾネータ10の両側にそれぞれバイアス回路20′の電位供給部31、32及び結合容量Cc1、Cc2が設けられるため、MEMSレゾネータ10のバイアス電圧をより確実に設定する事が可能になる。なお、電位供給部31,32に供給するそれぞれの電位は任意であり、例えば、図示例のように一方に第1の電位Vpを供給し、他方の第2の電位を接地電位とすることでバイアス電圧Vc=Vpを印加することができ、一方に第1の電位+Vp/2を供給し、他方に第2の電位−Vp/2を供給することでも同じバイアス電圧Vc=Vpを印加することができる。

【0071】

図11は電子回路のさらに別の実施例3を示す概略回路構成図である。この実施例3においても、共振回路30″以外の構成は上記各実施例と同様である。共振回路30″では、バイアス回路により第2の電位を与える電位供給部32と結合容量Cc2とが設けられる点で図9に示す実施例1と同様であるが、結合容量Cc2が可変容量Cc2′と付加容量Cc2″が並列に接続された合成容量によって構成される点で異なる。このように、結合容量が可変容量に他の静電容量が並列に接続された構成となっていても構わない。この場合には、結合容量Cc2の容量値が可変容量Cc2′の容量値と付加容量Cc2″の容量値の和となるため、結合容量Cc2の静電容量値を或る程度大きく確保するとともに、結合容量Cc2中の可変容量Cc2′の寄与割合を変えることで、可変容量Cc2′による共振回路30″の共振周波数への影響度合を調整することが可能になる。

【0072】

図12(a)はラダー型フィルタ回路の基本構成及び周波数帯域特性を示す説明図、図12(b)は電子回路の異なる実施例4を示す回路図である。この実施例4も、本発明に係る共振回路30を有する電子回路の実施例であるが、図示例では、第1実施形態と同様の共振回路30を用いたフィルタ回路50を構成した場合を示している。この実施例では、フィルタ回路50の入出力部50aと50bの間に直列共振器Rsを直列に接続するとともに、入出力部50aと50bの間と定電位(接地電位)とのに並列共振器Rpを接続している。そして、これらの直列共振器Rs及び並列共振器Rpとして上述の共振回路30を用いる。

【0073】

図12(a)に示すように、ラダー型フィルタ回路においては、直列共振器Rsと並列共振器Rpによってバンドパスフィルタを構成することができる。一般に、直列共振器Rsの共振周波数Fsrと反共振周波数Fsa、並列共振器Rpの共振周波数Fprと反共振周波数Fpaにおいて、共振周波数FsrとFprを僅かに(通常は数%)ずらすことにより、帯域透過特性を得ることができる。図12(a)に示す特性図では、信号透過率は直列共振器Rsの共振周波数Fsr=並列共振器Rpの反共振周波数Fpaで最大値となり、透過帯域の下限は並列共振器Rpの共振周波数Fpr、透過帯域の上限は直列共振器Rsの反共振周波数Fsaとなる。このような構成では、各共振器の共振周波数を高精度に設定する必要があるため、上述の本発明の構成はきわめて有効である。

【0074】

本実施例4では、例えば、図12(b)に示すように、フィルタ回路50の入出力部50aと50bの間に複数の直列共振器Rsを直列に接続し、入出力部50aと50bの間の各直列共振器Rsの前後位置と定電位である接地電位との間に並列共振器Rpを接続している。このように複数の直列共振器Rsと複数の並列共振器Rpを梯子状に接続している場合には、各共振器間の共振周波数を適宜の異なる値に調整することで所望の帯域を備えたフィルタ回路を構成できる。

【0075】

なお、本実施例では基本的に実施例1の結合容量を合成容量で実現したが、実施例2の結合容量を合成容量で実現してもよい。また、合成容量としては、上記のように複数の容量を並列に接続する場合に限らず、複数の容量を直列に接続してもよい。例えば、上述のMIS構造若しくはMOS構造を有するダイオードで結合容量を構成する場合、半導体中の空乏層と絶縁層(酸化層)が共に誘電体として機能するので、実質的には可変容量と付加容量とが直列に接続された回路構造が構成されたものと見ることもできる。この場合には、接続態様に応じて複数の容量のうちの少なくとも一つの容量である可変容量に印加される両端電圧が小さくなるため、特に可変容量の使用可能な電圧領域が限定されている場合に、当該電圧領域で可変容量を使用するように設計することも考えられる。さらに、結合容量を直列及び/又は並列に接続された複数の容量からなる回路構造で構成しても構わない。

【0076】

ここで、図6(a)に示す第1実施形態についてもう一度検討してみる。この第1実施形態において共振周波数を示す上記式(3)を書き直すと以下の式(6)が得られる。

fn=(1/2π)・L1−1/2・{1/C1+1/(C0+Cc1)}1/2・・・(6)

この式(6)をみると、等価直列容量C1の逆数と、等価並列容量C0と結合容量Cc1の和の逆数とが同じ重みで共振周波数に影響を与えることがわかる。したがって、バイアス電圧の変化に起因する等価直列容量C1の変化率と結合容量Cc1の変化率との関係にも依存するが、両変化率の大きさに極端な差がなければ、C1と、C0とCc1の和とがほぼ同じ値となっている場合に本発明の共振周波数の変動を最も抑制しやすくなることがわかる。

【0077】

しかしながら、本発明では、可変容量を設けることでバイアス電圧の変動に起因するMEMSレゾネータ10の共振周波数の変化をなくすことまでは必ずしも要求されず、当該共振周波数の変化を抑制すれば足りるので、必ずしも上記のように各容量値を精密に設定する必要はない。実際には、等価直列容量C1と等価並列容量C0はMEMSレゾネータ10の構造に依存するために独立に制御することはできないため、結合容量を等価直列容量C1の10分の1から10倍の範囲内で動作するように設定することにより、共振周波数の変動の抑制効果を高めることができる。

【0078】

MEMSレゾネータ10の一般的な構造寸法から見て、等価直列容量C1は10−12〜10−17F程度、等価並列容量C0は10−12〜10−14F程度、等価インダクタンスL1は100〜10−5H程度となる。例えば、結合容量Cc1(可変容量そのもので構成されている場合)が結合容量として最低限要求される容量値である10−12F程度であれば、等価直列容量C1、等価並列容量C0が10−12〜10−14F程度である場合、共振周波数の変動を充分に抑制することが可能になる。特に、MEMSレゾネータ10の構造を等価直列容量C1の値がC0と同じオーダーの値となるように設計すれば、結合容量Cc1の容量値を最低限要求される範囲内としつつ、バイアス電圧の変動に起因する共振周波数の変動をある程度抑制できる。

【0079】

本実施形態の共振回路及びこれを含む電子回路では、バイアス電圧Vcの変動に起因する振動子10の共振周波数の変動態様を可変容量を用いることで制御することができるため、共振特性の安定化や共振周波数の可変幅の増大を図ることができる。また、バイアス電圧による共振周波数の変動態様が制御されるため、バイアス電圧で共振周波数を調整する際に共振周波数の調整精度の向上や調整範囲の増大を図ることができ、高品位の共振回路を構成することも可能になる。

【0080】

本実施形態のMEMSレゾネータ10は、上記結合容量Cc1、Cc2及び信号回路部と共通の基板上に構成されることが電子回路やこれを含む電子装置のコンパクト化、製造コストの低減等を図る上で好ましい。このように構成した一例を図13に示す。図13は、MEMSレゾネータ10と結合容量Cc1を半導体基板上に形成した構造を示す概略縦断面図である。シリコン等の半導体よりなる基板1上には絶縁膜2を介してMEMSレゾネータ10が前述のように構成されている。一方、基板1の表層部には導電領域1A(例えば、基板1がp型基板であればn型不純物領域で構成できる。)が形成され、この周囲に素子間分離膜3が酸化シリコン等の絶縁体で構成される。導電領域1Aは絶縁膜2′を介して基板1上に形成された容量電極4と対向する。ここで、容量電極4は任意の導電材料で構成でき、任意の工程で形成できるが、MEMSレゾネータ10の固定電極12(下部導電層)と同材質で構成され、同工程にて形成されることが好ましい。

【0081】

また、導電領域1Aの一部表面部分には不純物濃度を高めた低抵抗領域1B(上記の例ではn型ドーパントのドーピング濃度を高めた領域)が形成され、この低抵抗領域1Bは基板1上に形成された接続電極5に導電接続される。この接続電極5もまた、任意の導電材料で構成でき、任意の工程で形成できるが、MEMSレゾネータ10の固定電極12(下部導電層)と同材質で構成され、同工程にて形成されることが好ましい。この導電領域1A、絶縁膜2′、容量電極4及び接続電極5により構成されるMOS容量が結合容量Cc1となる。

【0082】

基板1上には、酸化シリコン等よりなる層間絶縁膜6及び8と、MEMSレゾネータ10、結合容量Cc1及び図示しない信号回路部(図示しない基板1の表層部においてCMOS構造等により構成される。)間の接続を行う配線層7及び9とが交互に積層され、上述のように一体化された電子装置が構成される。ここで、上記実施形態の構成では、例えば、配線層7中の配線部7A(図示破線で示す。)によりMEMSレゾネータ10の可動電極13と結合容量Cc1とが導電接続される。図示例の場合には、MEMSレゾネータ10の端子部10a,10b、結合容量Cc1の両端部に相当する部分が接続パッド10x、10y、Cx、Cyとして外部と接続可能に構成され、例えば接続パッド10xが電位供給部31に相当しているが、このような態様に限定されるものではなく、必要のない接続パッドを設けなくても構わない。なお、最上層には保護膜10が酸化シリコンと窒化シリコンの2層構造等により形成される。

【0083】

MEMSレゾネータ10は、上記層間絶縁膜6,8、配線層7、9及び保護膜10よりなる基板1上の積層構造に取り囲まれた収容空間10A内に配置される。この収容空間10AはMEMSレゾネータ10の動作を可能にするための空間であり、必要に応じて内部を減圧したり、適宜に封止したりしてもよい。この収容空間10Aは、たとえば、上記層間絶縁膜6、8及び保護膜10を形成した後にフッ酸系エッチングによりこれらの層間絶縁膜6,8及び保護膜10を除去するリリース工程で形成される。

【0084】

上記のように集積回路技術(半導体製造技術)によってMEMSレゾネータ10、結合容量Cc1及び信号回路部を同一基板1上に一体に構成することで、電子回路や電子装置をコンパクトに構成できるとともに製造が容易になる。

【0085】

図14は別の電子回路若しくは電子装置におけるMEMSレゾネータ10及び結合容量Cc1の構成部分の例を示す。図示以外の構成は図13に示すものと同様である。この例では、図13に示すものと同様の部分には同一符号を付し、それらの説明は省略する。

【0086】

この構成例においては、基板1の表層部に導電領域1C、1Eが形成され、その領域間にゲート絶縁膜2′が配置され、このゲート絶縁膜2′上にゲート電極4′が形成される。また、導電領域1Cは低抵抗領域1Dを介して基板1上のソース電極5Aに導電接続され、導電領域1Dは低抵抗領域1Fを介して基板1上のドレイン電極5Bに導電接続される。これらの構造はMOSFET(MOSトランジスタ)を構成するが、本実施形態では、配線部7Bによってソースとドレインが短絡され、ゲート電極4′とソース・ドレイン間にMOS容量が構成され、これが結合容量Cc1とされる。また、振動子10は配線層7Cにより結合容量Cc1と導電接続される。

【0087】

上記各構成例においては、図14に示すMOS容量を構成するMOSFETと同様のトランジスタ構造によって増幅回路等(CMOS構造)を含む信号回路部が形成できる。

【0088】

なお、本発明の共振回路とこれに接続される信号回路部を含む電子回路若しくは電子装置としては、上述の各実施形態や実施例に示す信号回路部40のように発振回路を構成するものや上記フィルタ回路50等の各種のフィルタ回路を構成するもの以外に、送受信回路などの種々の回路構成を実現することができる。特に、発振回路とフィルタ回路を含む電子装置など、各種の電子装置を構成できる。また、MEMSレゾネータとバイアス回路からなる共振回路、信号回路部、電子回路等をそれぞれ、或いは、複数組み合わせて共通の基板上に構成することができる。

【0089】

尚、本発明の共振回路、発振回路、フィルタ回路及び電子装置は、上述の図示例にのみ限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。例えば、上記の共振回路中には実質的、本質的な動作に影響を与えない種々の回路素子を組み込むことができる。

【符号の説明】

【0090】

1…基板、2…絶縁膜、10…MEMSレゾネータ、10a…第1の端子、10b…第2の端子、11…下地層、12…固定電極、12a…対向部(振動子電極)、13…可動電極、13a…可動部(振動子電極)、20、20′20A、20B…電圧印加手段(バイアス回路)、30…共振回路、30a…第1の入出力部、30b…第2の入出力部、31、32…電位供給部、40…信号回路部、50…フィルタ回路、Cc1、Cc2…結合容量、Cc2′…可変容量、Cc2″…付加容量、C1…等価直列容量、C0…等価並列容量、L1…等価インダクタンス、R1…等価抵抗、INV1…負性抵抗を有する増幅回路

【特許請求の範囲】

【請求項1】

基板と、

該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータと、

前記MEMSレゾネータの前記固定電極と前記可動電極の一方に接続された第1の端子に接続された第1の入出力部と、

前記MEMSレゾネータの前記固定電極と前記可動電極の他方に接続された第2の端子に接続された第2の入出力部と、

少なくとも前記第1の端子に電位を供給して前記第1の端子と前記第2の端子の間にバイアス電圧を印加する電圧印加手段と、

前記第1の端子と前記第1の入出力部の間に接続され、両端の電位差の変化で容量値が変化する可変容量と、

を具備することを特徴とする共振回路。

【請求項2】

前記可変容量は、その両端の電位差の変化により容量値が単調に変化する電圧依存領域を少なくとも一部に有し、当該電圧依存領域において前記バイアス電圧の増大により容量値が単調に減少する特性を備えることを特徴とする請求項1に記載の共振回路。

【請求項3】

前記電圧印加手段は、前記第1の端子に第1の電位を供給するとともに、前記第2の端子を接地電位とすることを特徴とする請求項1又は2に記載の共振回路。

【請求項4】

前記電圧印加手段は、前記第1の端子に第1の電位を供給するとともに、前記第2の端子に第2の電位を供給することを特徴とする請求項1又は2に記載の共振回路。

【請求項5】

前記可変容量と並列に接続された付加容量をさらに有することを特徴とする請求項1乃至4のいずれか一項に記載の共振回路。

【請求項6】

基板と、

該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータと、

該MEMSレゾネータの前記固定電極と前記可動電極の一方に接続された第1の端子に接続された第1の入出力部と、

前記MEMSレゾネータの前記固定電極と前記可動電極の他方に接続された第2の端子に接続された第2の入出力部と、

前記第1の端子に電位を供給することにより前記第1の端子と前記第2の端子の間に前記第1の端子に供給された電位が上昇するに従って増大するバイアス電圧を印加する電圧印加手段と、

前記第1の端子と前記第1の入出力部の間に接続され、前記第1の端子に供給された電位が上昇すると容量値が減少する可変容量と、

を具備することを特徴とする共振回路。

【請求項7】

請求項1乃至6のいずれか一項に記載の共振回路と、該共振回路に接続される増幅回路部を有する外部回路とで構成された発振回路。

【請求項8】

請求項1乃至6のいずれか一項に記載の共振回路を含むフィルタ回路。

【請求項9】

請求項1乃至8のいずれか一項に記載の回路を含む電子装置。

【請求項10】

前記MEMSレゾネータ、前記電圧印加手段、前記可変容量が同一基板上に形成されていることを特徴とする請求項1乃至6のいずれか一項に記載の共振回路。

【請求項11】

前記MEMSレゾネータ、前記電圧印加手段、前記可変容量及び前記増幅回路部が同一基板上に形成されていることを特徴とする請求項7に記載の発振回路。

【請求項12】

前記MEMSレゾネータ、前記電圧印加手段及び前記可変容量が同一基板上に形成されていることを特徴とする請求項8に記載のフィルタ回路。

【請求項13】

請求項7に記載の発振回路と、請求項8に記載のフィルタ回路とが同一基板上に形成されていることを特徴とする電子装置。

【請求項1】

基板と、

該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータと、

前記MEMSレゾネータの前記固定電極と前記可動電極の一方に接続された第1の端子に接続された第1の入出力部と、

前記MEMSレゾネータの前記固定電極と前記可動電極の他方に接続された第2の端子に接続された第2の入出力部と、

少なくとも前記第1の端子に電位を供給して前記第1の端子と前記第2の端子の間にバイアス電圧を印加する電圧印加手段と、

前記第1の端子と前記第1の入出力部の間に接続され、両端の電位差の変化で容量値が変化する可変容量と、

を具備することを特徴とする共振回路。

【請求項2】

前記可変容量は、その両端の電位差の変化により容量値が単調に変化する電圧依存領域を少なくとも一部に有し、当該電圧依存領域において前記バイアス電圧の増大により容量値が単調に減少する特性を備えることを特徴とする請求項1に記載の共振回路。

【請求項3】

前記電圧印加手段は、前記第1の端子に第1の電位を供給するとともに、前記第2の端子を接地電位とすることを特徴とする請求項1又は2に記載の共振回路。

【請求項4】

前記電圧印加手段は、前記第1の端子に第1の電位を供給するとともに、前記第2の端子に第2の電位を供給することを特徴とする請求項1又は2に記載の共振回路。

【請求項5】

前記可変容量と並列に接続された付加容量をさらに有することを特徴とする請求項1乃至4のいずれか一項に記載の共振回路。

【請求項6】

基板と、

該基板上に形成された固定電極、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極を有するMEMSレゾネータと、

該MEMSレゾネータの前記固定電極と前記可動電極の一方に接続された第1の端子に接続された第1の入出力部と、

前記MEMSレゾネータの前記固定電極と前記可動電極の他方に接続された第2の端子に接続された第2の入出力部と、

前記第1の端子に電位を供給することにより前記第1の端子と前記第2の端子の間に前記第1の端子に供給された電位が上昇するに従って増大するバイアス電圧を印加する電圧印加手段と、

前記第1の端子と前記第1の入出力部の間に接続され、前記第1の端子に供給された電位が上昇すると容量値が減少する可変容量と、

を具備することを特徴とする共振回路。

【請求項7】

請求項1乃至6のいずれか一項に記載の共振回路と、該共振回路に接続される増幅回路部を有する外部回路とで構成された発振回路。

【請求項8】

請求項1乃至6のいずれか一項に記載の共振回路を含むフィルタ回路。

【請求項9】

請求項1乃至8のいずれか一項に記載の回路を含む電子装置。

【請求項10】

前記MEMSレゾネータ、前記電圧印加手段、前記可変容量が同一基板上に形成されていることを特徴とする請求項1乃至6のいずれか一項に記載の共振回路。

【請求項11】

前記MEMSレゾネータ、前記電圧印加手段、前記可変容量及び前記増幅回路部が同一基板上に形成されていることを特徴とする請求項7に記載の発振回路。

【請求項12】

前記MEMSレゾネータ、前記電圧印加手段及び前記可変容量が同一基板上に形成されていることを特徴とする請求項8に記載のフィルタ回路。

【請求項13】

請求項7に記載の発振回路と、請求項8に記載のフィルタ回路とが同一基板上に形成されていることを特徴とする電子装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2010−28792(P2010−28792A)

【公開日】平成22年2月4日(2010.2.4)

【国際特許分類】

【出願番号】特願2009−73813(P2009−73813)

【出願日】平成21年3月25日(2009.3.25)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成22年2月4日(2010.2.4)

【国際特許分類】

【出願日】平成21年3月25日(2009.3.25)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]