内蔵熱電冷却機を備えるマイクロエレクトロニクス・アセンブリおよびその製造方法

【課題】マイクロエレクトロニクス装置を冷却する内蔵熱冷却機(TEC)を含むマイクロエレクトロニクス・アセンブリ、および、マイクロエレクトロニクス・アセンブリを含むシステムを製作する方法を提供する。

【解決手段】方法は、マイクロエレクトロニクス装置を提供し、内蔵TEC120とマイクロエレクトロニクス装置との間に搭載材料がないように、内蔵TECをマイクロエレクトロニクス装置上に直接形成することを含む。内蔵TECは、N型電極116およびP型電極118とそれらを直列に結合する導体素子122〜134からなるカップルの少なくとも1つから構成される。

【解決手段】方法は、マイクロエレクトロニクス装置を提供し、内蔵TEC120とマイクロエレクトロニクス装置との間に搭載材料がないように、内蔵TECをマイクロエレクトロニクス装置上に直接形成することを含む。内蔵TECは、N型電極116およびP型電極118とそれらを直列に結合する導体素子122〜134からなるカップルの少なくとも1つから構成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施例は、マイクロエレクトロニクス装置のための熱電冷却機(built-in

thermoelectric cooler)に関する。

【背景技術】

【0002】

動作中の集積回路ダイのようなマイクロエレクトロニクス装置を冷却する必要性は、当技術分野においてよく認識されている。典型的には、このような装置のスポット冷却は、不均一なダイ・パワー・マップの結果に対して、同一の信頼できる動作を保証し、かつ持続した高温の結果としての装置故障を防ぐために必要とされる。

【0003】

マイクロエレクトロニクス装置の冷却は、先行技術に従う様々な方法で達成された。マイクロエレクトロニクス装置を冷却するための現在の大規模に製造する解決法の例では、液体循環または冷凍に基づいた冷却設計を含む。しかしながら、後にその解決法は、高価であることが明らかとなった。選択肢として、スタンドアロン型の熱電冷却機(thermoelectric cooler:以下、「TEC」という。)は、高価ではないが、しかし有効な冷却オプションを提示するために利用可能となった。周知のように、ペルチエ効果に基づくTEC機能は、2つの相違する材料からなる接合における電流通路によって、冷却効果がもたらされる。電流の流れを逆にすると、発熱効果が観察される場合がある。

【0004】

現在のTECは、一般に3つの異なる製造工程に従って製造される。第1の製造工程に従って、BiまたはTeをベースとする合金(例えば、Bi2Te3またはBiSb)、あるいは、PbTeまたはSiGeのようなTE材料の単結晶インゴットが提供される。その後、そのインゴットは、ウエハへスライスされ、そして正確に寸法取りされたブロックへ分割される。その後、熱電対を製造するために望まれるように、ブロックの適切なものはPドープされ(例えば、アンチモンで)、またNドープされる(例えばセレンで)。その後、一対のPおよびNドープされた熱電対は、Niでめっきされ、ドープしていない熱電対に沿って適切な場所にはんだ付けし、そして結合を形成するために金属化された基板間に挟まれる。その結合は、電気的には直列に熱的には並列に共に接合された1つのN型および1つのP型の熱電対から成る1対の熱電対を含む。基板はアルミナ磁器で製作されるが、ベリリア(berylia)磁器や他の材料が使用されてもよい。多くの結合は、TECを形成するためにビアろう付けのように共に接合される。例えば、単一ステージのモジュールが形成されてもよく、それは熱電対結合の単一層を含む。その後、TECは、同じ冷却を行なうマイクロエレクトロニクス装置に形成(搭載)される。その搭載は、熱インターフェイス・パッドまたは熱グリースを備えた圧縮、はんだまたはエポキシ樹脂によって達成される。アセンブリの結果は、熱グリース、エポキシ樹脂またははんだのように、それらの間に配置された搭載材料によってマイクロエレクトロニクス装置に搭載されたTECとなる。

【0005】

第2の製造工程によれば、上記されるようなインゴットからの作業の代わりに、その熱電対はスパッタリングによって製作される。特に、典型的には、TE材料で作られる3つのスパッタリング・ターゲットが、P型、N型および非ドープ熱電対をスパッタリングするために使用される。このようにして形成された熱電対は、TECを形成するために、電気的には直列に熱的には並列に共に接合される。その後、TECは、上記のように、マイクロエレクトロニクス装置に形成される。

【0006】

第3の製造工程によれば、熱電対は超格子構造(superlattice structure)を有する。超格子構造は、典型的に、各層が数ナノメータの厚みである2つの異なる半導体材料の交互の層から成る構造である。例えば、PまたはN型熱電対は、PまたはN型半導体材料の層を交互にすることで作られる。各層は、一般に約10nm台の厚さである。超格子P型熱電対は、例えば、Bi0.5Sb1.5Te3の層を備えるBi2Te3/Sb2Te3の交互層のように、P型ビスマス・カルコゲニド材料の交互層を含む。超格子N型熱電対は、例えば、Bi2Se3の交互層を備えるBi2Te3の交替層のように、P型ビスマス・カルコゲニド材料を交互層に含む。それぞれの超格子構造もコバルト・アンチモン・方コバルト鉱(cobalt

antimony skutteridite)材料から形成される。上述のように、超格子熱電対の各層は、はんだ付けによって隣接した層に接合され、典型的には厚さ約5ミクロンである構造を達成する。このようにして形成された熱電対は、上述のように、TECを形成するために共に接合され、それは、その後、上述のように、マイクロエレクトロニクス装置に搭載される。

【0007】

不都合なことに、先行技術のTECは、複数の理由からそれらの応用に制限される。現在利用可能なTECは必ずしも特定のマイクロエレクトロニクス装置に特有の熱除去要求を提供しない。加えて、このようなTECは、典型的にはミリメートルの範囲にあるそれらの厚さによる熱流束能力に制限を受ける。さらに、現在利用可能なTECをマイクロエレクトロニクス装置の裏面側へ搭載されるのに必要な搭載材料は、都合の悪いことに全パッケージの熱接触抵抗を増し、それにより、熱除去効率を落とすことになる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−243731号公報

【特許文献2】特開2004−165677号公報

【特許文献3】米国特許第6800933号明細書

【0009】

本発明の実施例は、例として図示されるが、添付図面の形状に制限を与えるものではなく、同種の参照は同じ要素を示す。

【図面の簡単な説明】

【0010】

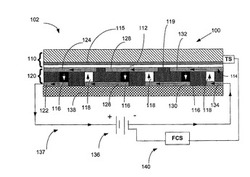

【図1】実施例に従って内蔵TECを具備するマイクロエレクトロニクス装置を含むマイクロエレクトロニクス・アセンブリを図示する。

【図2】図1のアセンブリにおける製造中の様々なステージを図示する。

【図3a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図3b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図3c】図1のアセンブリにおける製造中の様々なステージを図示する。

【図3d】図1のアセンブリにおける製造中の様々なステージを図示する。

【図4】図1のアセンブリにおける製造中の様々なステージを図示する。

【図5a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図5b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図5c】図1のアセンブリにおける製造中の様々なステージを図示する。

【図5d】図1のアセンブリにおける製造中の様々なステージを図示する。

【図6】図1のアセンブリにおける製造中の様々なステージを図示する。

【図7a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図7b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図7c】図1のアセンブリにおける製造中の様々なステージを図示する。

【図7d】図1のアセンブリにおける製造中の様々なステージを図示する。

【図8a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図8b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図9】図1のアセンブリにおける製造中の様々なステージを図示する。

【図10a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図10b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図10c】図1のアセンブリにおける製造中の様々なステージを図示する。

【図10d】図1のアセンブリにおける製造中の様々なステージを図示する。

【図11】本発明の実施例によるマイクロエレクトロニクス・アセンブリ中の内蔵TECによって提供される温度降下を示すグラフである。

【図12】図1のマイクロエレクトロニクス・アセンブリを含むシステムについての概要図である。

【発明を実施するための形態】

【0011】

内蔵熱電冷却機を含むマイクロエレクトロニクス・アセンブリを製作する方法、内蔵熱電冷却機を含むマイクロエレクトロニクス・アセンブリ、および、マイクロエレクトロニクス・アセンブリを含むシステムが、ここに開示される。

【0012】

様々な態様の図示された実施例がその技術内容を他の当業者に伝えるために当業者によって共通に使用される用語を用いて説明される。しかしながら、本発明は、説明された態様の幾つかのみで実施できることは当業者には明らかであろう。説明目的のために、特定の数、材料および構成は、図示された実施例についての完全な理解を提供するために述べられる。しかしながら、特定の詳細事項がなくても、本発明を実施できることは当業者には明らかであろう。他の例では、周知の特徴は、図示された実施例を不明瞭にしないために省略されるか単純化される。

【0013】

様々な動作は、本発明を理解するための最も便宜な手法で、複数の個別の動作として順番に説明されるであろうが、しかしながらこれらの動作は、必ずしもにその順番に依存することを暗示するものとして解釈されるべきではない。特に、これらの動作は、説明の順序であり、実行される必要はない。

【0014】

「ある実施例において」というフレーズが繰り返し使用される。そのフレーズは一般に同じ実施例を参照するものではないが、参照してもよい。用語「成る」、「含む」、および、「有する」は、その内容が他のことを述べない限り、同意語である。

【0015】

図1をまず参照して、配置102は、本発明の実施例に従って形成されたマイクロエレクトロニクス・アセンブリ100を含めて示される。配置102は、以下さらに説明されるように、電気回路137、および、フィードバック制御ループ140をさらに含む。アセンブリ100は、ダイ110のようなマイクロエレクトロニクス装置を含む。図1に示されるように、必要に応じて、ダイ110は、一方である相互接続金属化導体素子124,128,132と他方であるダイ110のシリコン基板115との間の相互拡散を防ぐためにその裏面114(すなわち、内蔵TECを含むその側面)上に提供される初期酸化層112を含み、さらに電気的な絶縁層も提供する。相互接続金属化導体素子(122,124,126,128,130,132,134)は短いので、電気的な絶縁の提供が必要とされる。酸化層112は、シリコン酸化層を含み、周知の方法のいずれかに従って、ダイ110の裏面114上に成長する。好ましくは、酸化層112は、垂直の拡散炉中でダイ110の裏面114上に熱成長する。アセンブリ100は、本発明の実施例によるマイクロエレクトロニクス装置上に構築されたTEC120をさらに含む。図1に示されるように、TEC120とダイ110との間に搭載材料は存在しない。「搭載材料」によって、本発明の態様で意味するものは、1つのマイクロエレクトロニクス・コンポーネントを別のものに物理的に付属させる材料であり、例えば、搭載材料の例には、はんだ、熱グリース、および、エポキシを含むが、しかしこれらに制限されることはない。図示された実施例中のTEC120は、図のように対となるN型電極116およびP型電極118を含み、その電極は、TE材料、例えば、BiまたはTeベースの合金(例えば、Bi2Te3またはBiSb)、またはPbTeまたはSiGeで作製され、他のタイプのTE材料が本発明の実施例の範囲内にあることは理解されるであろう。電極のTE材料は従来のドーパントで適切にドープされるが、例えば、N型ドーパントとしてリン、ヒ素、アンチモン、ビスマス、セレンおよびテルルが使用され、そしてP型ドーパントとしてホウ素、アルミニウム、ガリウムおよびインジウムが使用される。P型およびN型電極は、パターン化された酸化層119によって分離され、それは、当業者によって認識されるように、周知の方法のいずれか1つを使用して提供される。酸化層119の機能は、N型およびP型電極を互いに電気的に分離することである。N型およびP型電極は、相互接続金属化導体素子122,124,126,128,130,132,134によって共に電気的に結合される。導体素子122−134は、例えば、アルミニウム銅合金(約0.5%の銅を含有)、または銅、好ましくは約0.5%の銅を含有するアルミニウム銅合金のようなあらゆる適切な導電材料からなる。本発明の実施例によるTEC120の厚さの範囲は約50ミクロンと約200ミクロンの間であり、電極は約20ミクロンと約50ミクロンの間の厚みを有し、導電材料は厚さとして約10と約100ミクロンの間にある。

【0016】

TEC120によるダイ110の冷却は、ペルチエ効果の機能として生じる。再び図1を参照して、特に、DC電源136はTECに接続され、図示されるように導体素子122,134に同じ電力を供給するために回路137を形成する。回路137中の電子は、回路137中のTEC120を通って図示された矢印の方向に流れ、そうすることでダイの動作中にダイ110から排熱する。熱終端でTECによって廃棄された電力は、ダイの冷却裏面で吸収された電力にTECで放散された電力をプラスした電力に等しい。TEC120は、ダイ110から吸収した熱を放散するために、例えば、インテグレイテッド・ヒート・スプレッダ(IHS:integrated heat spreader)、または液冷冷却板(liquid cooled cold plate)のような従来のヒート・シンク138に結合されてもよい。冷接点、すなわちダイ110とTEC120との間の接合面で吸収された熱は、その回路を通過する電流、および、N型およびP型の電極の対から成るカップルの数に比例した率で、熱接点、またはTEC120とヒート・シンク138との間の接合面の方へ排出される。図1に示されるように、図示されたNおよびPのカップルはTECモジュールへ結合され、ここでそれらは電気的に連続して、また熱的に並行に接続される。TEC120に印加される典型的な電圧は、約3Vから約5Vの範囲であり、12Vまで上げることができる。TECによって提供される局所冷却によって、ダイの全電力は、例えば、その正面からみてダイ上のいずれのポイントにおいても摂氏100度のように、同じ最高温度の規格値を超過せずに増加させることができる。必要があれば、本発明の実施例に従って、フィードバック制御ループ140が、図1に概略的に示されるように、電源136によって電力が供給される電気回路に結合されてもよい。フィードバック制御ループ140は、ダイの温度を検出するためにダイ110に結合されるように概略的に示される温度センサTSを含む。さて、TSは、次に、例えば、TECに供給される電源136の電圧を規制することにより、TEC120を通る電流を規制するフィードバック制御システムFCSに信号を伝える。このように、フィードバック制御ループ140によって、ダイ110の温度の関数としてTEC120によって提供される冷却範囲の管理を行なうことができる。FCSは、1つの従来方式としてTEC120を通る電流を規制するために、TSから温度信号を受け取るためにいずれかの従来のマイクロプロセッサを含んでいてもよい。

【0017】

図1および後続の図はダイとしての要素110に関するが、本発明の実施例はダイを含むマイクロエレクトロニクス・アセンブリに制限されることはなく、それらの範囲内にTECによって達成される冷却を必要とするのに適したあらゆるマイクロエレクトロニクス装置を含むマイクロエレクトロニクス・アセンブリに及ぶことに注目されるべきである。加えて、図1は、複数のカップル(すなわち、電気的に接続されたNおよびP型電極の複数の対)を含むTECモジュールを示すが、本発明の実施例は、その範囲内に単一のカップルからなるTECモジュールを含んでいてもよい。

【0018】

本発明の実施例は、好ましくは、例えばアセンブリ100は、冷却されるべきマイクロエレクトロニクス装置とTECとの間の熱接触抵抗を著しく減少させ、それにより、ホット・スポットでの比較的大きな温度低下が見込め、さらに所要の温度管理の効果を達成するために必要なTECへの入力電力をさらに削減させることができる。このように、TECがはんだ、熱グリースまたはエポキシのような搭載材料によって冷却されるべきマイクロエレクトロニクス装置に搭載されている最先端技術によるTEC技術に比較して、本発明の実施例は、冷却されるべき装置とTECとの間のあらゆる熱接触抵抗を実質的に除去する方法で、搭載材料によって冷却されるべきマイクロエレクトロニクス装置に付けられることと対比して、アセンブリの一部として内蔵されるマイクロエレクトロニクス・アセンブリを提供する。

【0019】

次に図2−図9cを参照すると、図1のアセンブリ100のようなマイクロエレクトロニクス・アセンブリを製作する方法の様々なステージが示される。様々なステージは、以下さらに詳細に説明されるであろう。

【0020】

図2に見られるように、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する第1ステージは、ダイ110のようなマイクロエレクトロニクス装置を提供し、TECの対応するNおよびP型電極対に電気的に結合するために適合した複数の第1の導体素子を提供することを含む。いくつかの実施例によれば、複数の導体素子は、ダイ110上に第1の導電層200の形で相互接続金属化層をまず提供し、次に、複数の第1の導体素子を形成するために第1の導電層200に相互接続パターンを提供することにより用意される。上記のように、ダイ110は、まず酸化物112の層を含み、次にその上に第1の導電層200が、例えば約0.5%の銅を含むアルミニウム銅合金、または銅のみのようなあらゆる導電材料からなり、例えばスパッタリングまたは蒸着のような金属化層を堆積する周知の堆積方法によって堆積することができる。

【0021】

次に図3a−図3dを参照して、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、第1の導電層200中に相互接続パターンを提供することをさらに含む。相互接続パターンの用意により、TEC120の個々のカップルに電力を供給するために、導電層200から個々の導体素子が形成される。図3a−図3dは、第1の導電層200に相互接続パターンを提供する1つの例を示し、その例は、相互接続パターンを層200にエッチングするために、リソグラフィ、または、マスク/現像/エッチング手順を使用することを含む。特に、図3aに見られるように、層200中に相互接続パターンを用意することにより、第1の導電層200上にレジスト層210が形成されることを含む。レジスト層は、周知技術のいずれかに従って、例えば、塗布機または現像機を用いる回転プロセスと通して、提供される。分配されるレジスト、その粘性、および、スピン速度と時間の量は、当業者によって認識されているように、最終レジスト厚および等質性の決定を支援する。従来のレジスト蒸着技術は、本発明の実施例に従って示されるように、レジスト層210を提供するために使用される。

【0022】

次に図3bに見られるように、レジスト層210の予め定める部分が、層200上に提供される相互接続パターンの機能として取り除かれる。図3bに示されるように、ある実施例によれば、レジスト層210の予め定める部分の除去は、図示されるようにレジスト層210を、マスク220を通る光に暴露することによって達成されるが、そのマスクは層200上に提供される相互接続パターンに対応するパターンを表わし、その後、その露光された予め定める部分を現像液を用いて溶解する。マスク220によって提供される相互接続パターンは、マスク220およびレジスト層210を、例えば、ステッパにより図3bの破線の矢印で示されるUV光のような光に暴露することによりにより、レジスト層210上に転写される。光の波長と強さ、および、露光時間は、当業者によって認識されるように、パターンを適切に露光する際の条件である。従来の露光パラメータが本発明の実施例に従って用いられる。その後、レジスト層の露出した部分は、周知な現像液を用いて溶解される。現像時間、温度、および、現像液の濃度は、露出したレジストを適切に溶解する条件である。従来の露光パラメータは、本発明の実施例に従って使用されてもよい。レジスト層210の予め定める部分の除去は、層200上に提供される相互接続パターンを示すパターン化されたレジスト層210’を形成する。

【0023】

次に図3cを参照して、層200の予め定める部分は、層200の上に提供される相互接続パターンの機能として削除される。図3cに示されるように、ある実施例によれば、層200の予め定める部分の除去は、パターン化されたレジスト層’210によって保護されていない層200の部分をエッチングすることにより達成される。本発明の実施例に従って、従来のエッチング・パラメータが使用される。例えば、ある実施例によれば、アルミニウムのエッチャ(etcher)のようなプラズマ(ドライ)エッチャが層230の保護されていない予め定める部分をエッチングするために使用される。レジストによって保護されている領域は、図1に示される第1の導体素子124,128,132を含む、パターン化された相互接続金属化層200’の活性領域になるであろう。図3dに見られるように、エッチングが完了すると、アッシャ(asher)(また、プラズマ・エッチャの一種)は、第1のパターン化された金属化層200’を形成するために残りのレジストを除去するために使用されてもよい。

【0024】

図4に見られるように、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、パターン化された金属化層200’上にTE材料のN型層230を提供することをさらに含む。N型層230の用意は、ある実施例によれば、ドーパントが注入されたTE材料プリカーサ(precursor)のCVDまたはPVD蒸着、または、それとは別に蒸着後にサイト・ドーピング上で後続するTE材料プリカーサのCVD蒸着を含む。N型ドーパントは、例として、リン、ヒ素、アンチモン、ビスマス、セレン、および、テルルを含む。

【0025】

次に図5a−図5dを参照して、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、N型層230中に電極パターンを提供することをさらに含む。電極パターンは、層230から別個のN型電極を形成することにより用意される。図5a−図5dは、N型層230中に電極パターンを提供する1つの例を示すが、その例は、層230に電極パターンをエッチングするためにリソグラフィまたはマスク/現像/エッチング手順を使用することを含む。特に、図5aに見られるように、層230中の電極パターンの用意は、第1の導電層230上にレジスト層240を用意することを含む。本発明の実施例に従って、従来のパラメータがレジスト層を提供するために使用されてもよい。例えば、レジスト層は、上記図3aに関して述べられたのと同じ方法で提供されてもよい。

【0026】

次に図5bに見られるように、N型層230の予め定める部分は、層230上に提供されるべきN型電極パターンの機能として取り除かれる。図3bに示されるように、ある実施例によれば、レジスト層240の予め定める部分の除去は、図示されるようにレジスト層240を、マスク250を通る光に暴露し、そのマスクは層230上に提供される電極パターンに対応するパターンを示しており、その後現像溶液を用いて露出した予め定める部分を溶解することにより達成される。マスク250によって提供される電極パターンは、マスク250およびレジスト210を、例えば、ステッパにより図5bの破線の矢印で示されるUV光のような光に暴露することにより、レジスト層240上に転写される。本発明の実施例に従って従来の露光パラメータが使用されてもよい。例えば、露出は、上記図3bに関して述べられたのと同じ方法で達成される。その後、レジスト層の露出した部分は、周知なものとして、現像溶液を用いて溶解される。本発明の実施例に従って従来の現像パラメータが使用されてもよい。例えば、現像は、上記図3bに関して述べられたのと同じ方法で達成される。レジスト層240の予め定める部分の除去は、層230の上に提供される電極パターンを示すパターン化されたレジスト層240’を形成する。

【0027】

次に図5cを参照して、層230の予め定める部分は、層230上に提供される電極パターンの機能として取り除かれる。図5cに示されるように、ある実施例によれば、層230の予め定める部分の除去は、パターン化されたレジスト層240’によって保護されていない層230の部分をエッチングすることにより達成される。本発明の実施例に従って従来のエッチング・パラメータが使用されてもよい。そのエッチングは、上記図3cに関して説明されたのと同じ方法で行なわれる。例えば、ある実施例によれば、アルミニウムのエッチャのようなプラズマ(ドライ)エッチャが層230の保護されていない予め定める部分をエッチングするために使用される。レジストによって保護される領域は、図1に示されるN型電極116になるであろう。図5dに見られるように、エッチングが完了すると、アッシャ(また、プラズマ・エッチャの一種)は、電極116を含むTE材料のパターン化されたN型層に230’を形成するために残りのレジストを除去するために使用されてもよい。次に図6を参照して、本発明の実施例による内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、酸化層260を層200’,230’の上に提供することを含む。酸化層260は、当業者によって認識される周知の方法のいずれか1つに提供される。酸化層260は、図示されるように、電極116間および図示されるパターン化された導電層200’の導体素子間の間隙を充填する。

【0028】

次に図7a−図7dを参照して、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、酸化層260中の電極パターンを提供することをさらに含む。電極パターンは、層260中に散在した個別のP型電極を形成することにより用意される。図7a−図7dは、酸化層260中に電極パターンを提供する1つの例を示すが、その例は、層260に電極パターンをエッチングするためにリソグラフィまたはマスク/現像/エッチング手順を使用することを含む。特に、図7aに見られるように、層260中の電極パターンの用意は、第1の導電層260上にレジスト層270を用意することを含む。本発明の実施例に従って、従来のパラメータがレジスト層を提供するために使用されてもよい。例えば、レジスト層は、上記図3aに関して述べられたのと同じ方法で提供されてもよい。

【0029】

次に図7bに見られるように、酸化層260の予め定める部分は、層260中に提供されるP型電極パターンの機能として取り除かれる。図7bに示されるように、ある実施例によれば、レジスト層270の予め定める部分の除去は、図示されるようにレジスト層270を、マスク280を通る光に暴露し、そのマスクは層260上に提供される電極パターンに対応するパターンを示しており、その後現像溶液を用いて露出した予め定める部分を溶解することにより達成される。マスク280によって提供される電極パターンは、マスク280およびレジスト270を、例えば、ステッパにより図7bの破線の矢印で示されるUV光のような光に暴露することにより、レジスト層270上に転写される。本発明の実施例に従って従来の露光パラメータが使用されてもよい。例えば、露出は、上記図3bに関して述べられたのと同じ方法で達成される。その後、レジスト層の露出した部分は、周知なものとして、現像溶液を用いて溶解される。本発明の実施例に従って従来の現像パラメータが使用されてもよい。例えば、現像は、上記図3bに関して述べられたのと同じ方法で達成される。レジスト層270の予め定める部分の除去は、層260の上に提供される電極パターンを示すパターン化されたレジスト層270’を形成する。次に図7cを参照して、層260の予め定める部分は、層260上に提供される電極パターンの機能として取り除かれる。図7cに示されるように、ある実施例によれば、層260の予め定める部分の除去は、パターン化されたレジスト層270’によって保護されていない層260の部分をエッチングすることにより達成される。本発明の実施例に従って従来のエッチング・パラメータが使用される。そのエッチングは、上記図3cに関して説明されたのと同じ方法で行なわれる。例えば、ある実施例によれば、アルミニウムのエッチャのようなプラズマ(ドライ)エッチャが層260の保護されていない予め定める部分をエッチングするために使用される。レジストによって保護される領域は、図1に示されるP型電極118になるであろう。図7dに見られるように、エッチングが完了すると、アッシャ(また、プラズマ・エッチャの一種)は、ビア265を画定するTE材料のパターン化されたN型層に260’を形成するために残りのレジストを除去するために使用されてもよい。

【0030】

次に図8a−図8bを参照して、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、パターン化されたILD層のビア中にP型電極を提供することをさらに含む。ある実施例に従うP型電極は、パターン化された酸化層260’のビア265中にTE材料のP型レッグ290を含むP型材料300を提供し、図1に示されるようなP型電極118を形成するためにその後材料300をエッチングすることにより用意される。「レッグ」によって、簡単な説明の内容中に意味することは、TECのコンポーネントを生成するための次のプロセスのために提供される材料の複数のブロックである。P型レッグ290を含むP型材料300の用意は、ある実施例によれば、ドーパントが注入されたTE材料プリカーサのCVDまたはPVD蒸着、または、それとは別に蒸着後にサイト・ドーピング上で後続するTE材料プリカーサのCVD蒸着を含み、その蒸着はILD層上にTE材料プリカーサの層を生成し、ホール中にP型電極が提供される。P型レッグ290を含むP型材料300を用意した後に、レッグ290の一部を含む材料300の一部は、図8bに見られるように、エッチングされ、図示されるようにP型電極およびパターン化された酸化層260”を生成する。

【0031】

図9および図10a−図10dに見られるように、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、例えば対応する対のNおよびP型電極に電気的に結合された図1に示される導体素子122,126,130,134のような複数の第2の導体素子を提供することを含む。第2の導体素子は、いくつかの実施例によれば、まず電極上に第2の導電層310の形状を備える相互接続金属化層を提供し、次に複数の第2の導体素子を形成するために第2の導電層310中に相互接続パターンを提供することを含む。第2の導電層310は、図9に示されるように、第1の導電層200に類似しており、例えば、上述されたように約0.5%の銅を含むアルミニウム銅合金、あるいは銅のみのようなあらゆる導電材料からなり、例えばスパッタリングまたは蒸着のような金属化層を堆積する周知の堆積方法によって堆積することができる。

【0032】

次に図10a−図10dを参照して、図1に示されるTEC120の個別のカップルに電力を供給するために、第1の導電層310中に相互接続パターンを提供することにより、導電層310から別個の導体素子が形成される。図10a−図10dは、第2の導電層310中に相互接続パターンを提供する1つの例を示し、その例は、層310に相互接続パターンをエッチングするために、リソグラフィまたはマスク/現像/エッチング手順を用いることを含む。特に、図10aに見られるように、層310中の相互接続パターンの用意は、第2の導電層310上にレジスト層320を用意することを含む。本発明の実施例に従う従来のパラメータがレジスト層を提供するために使用されてもよい。例えば、レジスト層は、上記図3aに関して述べられたのと同じ方法で提供されてもよい。

【0033】

次に図10bに見られるように、レジスト層320の予め定める部分が層310上に提供される相互接続パターンの機能として取り除かれる。図10bに示されるように、ある実施例に従って、レジスト層320の予め定める部分の除去が、図示されるようなマスク330を通して光をレジスト層320に暴露し、そのマスクは層310上に提供される相互接続パターンに対応するパターンを有しているが、その後現像液の使用により暴露した予め定める部分を溶解することにより達成される。マスク330によって提供される相互接続パターンは、マスク330およびレジスト層320を、例えばステッパにより図10bの破線の矢印で示唆されるようにUV光のような光に暴露させることによりレジスト層320上に転写される。光の波長および強さ、および、露光時間は、すべてパターンを適切に露出させる条件である。本発明の実施例に従う従来の露光パラメータが使用されてもよい。例えば、露光は、上記図3bに関して述べられたのと同じ方法で達成することができる。その後、レジスト層の露光された部分は、現像液を用いて周知な方法で溶解される。現像時間、温度、および、現像液の濃度は、すべて露光したレジストを適切に溶解する条件である。本発明の実施例に従う従来の現像パラメータが使用されてもよい。例えば、現像は、上記図3bに関して述べられたのと同じ方法で達成することができる。レジスト層320の予め定める部分を除去することにより、層310上に提供される相互接続パターンを示すパターン化されたレジスト層320’が形成される。次に図10cを参照して、層310の予め定める部分が層310上に提供される相互接続パターンの機能として取り除かれる。図10c示されるように、ある実施例によれば、層310の予め定める部分の除去は、パターン化されたレジスト層320’によって保護されていない層310の一部をエッチングすることにより達成される。本発明の実施例に従う従来のエッチング・パラメータが使用されてもよい。そのエッチングは、上記図3cに関して述べられたのと同じ方法で達成することができる。例えば、ある実施例によれば、アルミニウムのエッチャのようなプラズマ(ドライ)エッチャが層310の保護されていない予め定める部分をエッチングするために使用されてもよい。レジストによって保護されている領域は、図1に示される第2の導体素子122,126,130,134を含む、パターン化された相互接続金属化層310’の活性領域になるであろう。図10dに見られるように、エッチングが完了すると、アッシャ(また、プラズマ・エッチャの一種)は、パターン化された金属化層310’を形成するために残りのレジストを除去するために使用されてもよい。図10dに示される製作ステージの完成により、内蔵TECを含むマイクロエレクトロニクス・アセンブリ100が形成され、それは図1に示されかつ上述された配置102に使用される。

【0034】

本発明の実施例は、さらに、それらの範囲内にその各側面に単一の相互接続金属化導体素子を備えた単一のカップルTECのようなTECを含み、両方を電気的および熱的に並列に接続された排他的P型電極または排他的N型電極を含む。このような望ましいTECが本発明の実施例に従って提供され、ここで最も共通に使用されるダイより小さいダイの冷却が実施例により熟慮され、そのダイの冷却は2つのスポット上だけの冷却をその上に要求するものであり、および/または、P型およびN型電極の両方を含むTECに典型的に関連した電圧降下が回避される。

【0035】

上述のように、冷却されるべきマイクロエレクトロニクス装置およびその上に搭載されたTECを含む先行技術のアセンブリでは、TEC特性に関する効率の損失は、典型的にはTECが搭載されるマイクロエレクトロニクス装置の後部とその搭載されたTECとの間の熱抵抗によって引き起こされる。熱エネルギーがマイクロエレクトロニクス装置からTECに入るにつれて、熱抵抗によって温度降下が引き起こされる。TECの冷却面(すなわち、マイクロエレクトロニクス装置に直接搭載された側面)の温度降下によって、TECは、熱接触抵抗が存在しなかった場合より低い温度で動作させる。その結果、TECによってマイクロエレクトロニクス装置のホット・スポットにもたらされる冷却低下が不利に行なわれる一方、TECへ要求されるパワー入力が増加する。この点に関して図11に言及され、冷却量または摂氏デルタT対TECに提供される必要な電力であるワット量を示すグラフである。図11に見られるように、本発明の実施例によるマイクロエレクトロニクス・アセンブリ中の内蔵TECは、最先端技術によるマイクロエレクトロニクス装置に従来から搭載された比較対照となるTECによって提供される温度低下より大きい、少なくとも摂氏約1/2度の温度低下を提供することができる。

【0036】

本発明による実施例の別の利点は、冷却されるマイクロエレクトロニクス装置のサイズおよび温度低下の仕様に特に調整されたTECの製作方法を提供することであり、先行技術のTECに対比して、それは一般にセット・サイズおよび形状の標準に従って製造され、その後、サイズと温度低下仕様に必要な最適化をしないでマイクロエレクトロニクス装置上に搭載される。本発明の実施例による製作方法によって、マイクロエレクトロニクス装置の製作者は、TEC製作者からTECを個別に購入するよりむしろ、特定のニーズに適合した内蔵コンポーネントとしてTECを製作し、それからマイクロエレクトロニクス装置と共に同じものに集積することが可能となる利点を有している。

【0037】

図12を参照して、本発明の実施例が使用される多くの可能なシステム900の1つが図示され、マイクロエレクトロニクス配置102はシステム900のサブシステム1000に使用されるマイクロエレクトロニクス・アセンブリ100を含む。サブシステム1000は、例えば、マイクロプロセッサを含む。代替となる実施例では、サブシステム1000は特定用途向けIC(ASIC)を含む。チップセット(例えば、グラフィックス、音および制御チップセット)に見られる集積回路も、本発明の実施例に従ってパッケージにされる。

【0038】

図12に示された実施例については、システム900は、さらにメインメモリ1002、グラフィック・プロセッサ1004、大容量格納装置1006、および/または、バス1100を介して互いに結合された入出力モジュール1008を含む。メモリ1002の例は、スタティック・ランダム・アクセス・メモリ(SRAM)およびダイナミック・ランダム・アクセス・メモリ(DRAM)を含むが、これらに制限されるものではない。大容量格納装置1006の例には、ハードディスク・ドライブ、コンパクト・ディスク・ドライブ(CD)、大容量光ディスク(DVD)などを含むが、これらに制限されるものではない。入出力モジュール1008の例には、キーボード、カーソル制御器、ディスプレイ、ネットワーク・インターフェイスなどを含むが、これらに制限されるものではない。バス1100の例には、周辺機器制御インターフェイス(PCI)バス、および、産業標準アーキテクチャ(ISA)バスなどを含むが、これらに制限されるものではない。様々な実施例では、システム900は、ワイヤレス携帯電話機、個人向け携帯型情報機器、ポケットPC、タブレットPC、ノートPC、デスクトップ・コンピュータ、セットトップ・ボックス、メディア・センターPC、DVDプレーヤ、および、サーバである。特定の実施例が好適な実施例の説明目的のためにここに図示され説明されたが、同じ目的を達成すると意図された広範囲に亘る代替または均等な実施が本発明の範囲を逸脱せずに示されかつ説明された特定の実施例の代わりに用いられることが当業者によって評価されるであろう。当業者は、本発明が極めて広範囲の実施例中で実施されることを容易に認識するであろう。このアプリケーションは、任意の順応またはここに議論された実施例のあらゆる適応または変動をも包含するように意図される。したがって、本発明は、その請求項とその均等によってのみ制限されることは明白に意図されるものである。

【符号の説明】

【0039】

100 マイクロエレクトロニクス・アセンブリ

102 マイクロエレクトロニクス配置

110 ダイ

116 N型電極

118 P型電極

120 TEC

136 DC電源

137 電気回路

138 ヒート・シンク

140 フィードバック制御ループ

【技術分野】

【0001】

本発明の実施例は、マイクロエレクトロニクス装置のための熱電冷却機(built-in

thermoelectric cooler)に関する。

【背景技術】

【0002】

動作中の集積回路ダイのようなマイクロエレクトロニクス装置を冷却する必要性は、当技術分野においてよく認識されている。典型的には、このような装置のスポット冷却は、不均一なダイ・パワー・マップの結果に対して、同一の信頼できる動作を保証し、かつ持続した高温の結果としての装置故障を防ぐために必要とされる。

【0003】

マイクロエレクトロニクス装置の冷却は、先行技術に従う様々な方法で達成された。マイクロエレクトロニクス装置を冷却するための現在の大規模に製造する解決法の例では、液体循環または冷凍に基づいた冷却設計を含む。しかしながら、後にその解決法は、高価であることが明らかとなった。選択肢として、スタンドアロン型の熱電冷却機(thermoelectric cooler:以下、「TEC」という。)は、高価ではないが、しかし有効な冷却オプションを提示するために利用可能となった。周知のように、ペルチエ効果に基づくTEC機能は、2つの相違する材料からなる接合における電流通路によって、冷却効果がもたらされる。電流の流れを逆にすると、発熱効果が観察される場合がある。

【0004】

現在のTECは、一般に3つの異なる製造工程に従って製造される。第1の製造工程に従って、BiまたはTeをベースとする合金(例えば、Bi2Te3またはBiSb)、あるいは、PbTeまたはSiGeのようなTE材料の単結晶インゴットが提供される。その後、そのインゴットは、ウエハへスライスされ、そして正確に寸法取りされたブロックへ分割される。その後、熱電対を製造するために望まれるように、ブロックの適切なものはPドープされ(例えば、アンチモンで)、またNドープされる(例えばセレンで)。その後、一対のPおよびNドープされた熱電対は、Niでめっきされ、ドープしていない熱電対に沿って適切な場所にはんだ付けし、そして結合を形成するために金属化された基板間に挟まれる。その結合は、電気的には直列に熱的には並列に共に接合された1つのN型および1つのP型の熱電対から成る1対の熱電対を含む。基板はアルミナ磁器で製作されるが、ベリリア(berylia)磁器や他の材料が使用されてもよい。多くの結合は、TECを形成するためにビアろう付けのように共に接合される。例えば、単一ステージのモジュールが形成されてもよく、それは熱電対結合の単一層を含む。その後、TECは、同じ冷却を行なうマイクロエレクトロニクス装置に形成(搭載)される。その搭載は、熱インターフェイス・パッドまたは熱グリースを備えた圧縮、はんだまたはエポキシ樹脂によって達成される。アセンブリの結果は、熱グリース、エポキシ樹脂またははんだのように、それらの間に配置された搭載材料によってマイクロエレクトロニクス装置に搭載されたTECとなる。

【0005】

第2の製造工程によれば、上記されるようなインゴットからの作業の代わりに、その熱電対はスパッタリングによって製作される。特に、典型的には、TE材料で作られる3つのスパッタリング・ターゲットが、P型、N型および非ドープ熱電対をスパッタリングするために使用される。このようにして形成された熱電対は、TECを形成するために、電気的には直列に熱的には並列に共に接合される。その後、TECは、上記のように、マイクロエレクトロニクス装置に形成される。

【0006】

第3の製造工程によれば、熱電対は超格子構造(superlattice structure)を有する。超格子構造は、典型的に、各層が数ナノメータの厚みである2つの異なる半導体材料の交互の層から成る構造である。例えば、PまたはN型熱電対は、PまたはN型半導体材料の層を交互にすることで作られる。各層は、一般に約10nm台の厚さである。超格子P型熱電対は、例えば、Bi0.5Sb1.5Te3の層を備えるBi2Te3/Sb2Te3の交互層のように、P型ビスマス・カルコゲニド材料の交互層を含む。超格子N型熱電対は、例えば、Bi2Se3の交互層を備えるBi2Te3の交替層のように、P型ビスマス・カルコゲニド材料を交互層に含む。それぞれの超格子構造もコバルト・アンチモン・方コバルト鉱(cobalt

antimony skutteridite)材料から形成される。上述のように、超格子熱電対の各層は、はんだ付けによって隣接した層に接合され、典型的には厚さ約5ミクロンである構造を達成する。このようにして形成された熱電対は、上述のように、TECを形成するために共に接合され、それは、その後、上述のように、マイクロエレクトロニクス装置に搭載される。

【0007】

不都合なことに、先行技術のTECは、複数の理由からそれらの応用に制限される。現在利用可能なTECは必ずしも特定のマイクロエレクトロニクス装置に特有の熱除去要求を提供しない。加えて、このようなTECは、典型的にはミリメートルの範囲にあるそれらの厚さによる熱流束能力に制限を受ける。さらに、現在利用可能なTECをマイクロエレクトロニクス装置の裏面側へ搭載されるのに必要な搭載材料は、都合の悪いことに全パッケージの熱接触抵抗を増し、それにより、熱除去効率を落とすことになる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−243731号公報

【特許文献2】特開2004−165677号公報

【特許文献3】米国特許第6800933号明細書

【0009】

本発明の実施例は、例として図示されるが、添付図面の形状に制限を与えるものではなく、同種の参照は同じ要素を示す。

【図面の簡単な説明】

【0010】

【図1】実施例に従って内蔵TECを具備するマイクロエレクトロニクス装置を含むマイクロエレクトロニクス・アセンブリを図示する。

【図2】図1のアセンブリにおける製造中の様々なステージを図示する。

【図3a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図3b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図3c】図1のアセンブリにおける製造中の様々なステージを図示する。

【図3d】図1のアセンブリにおける製造中の様々なステージを図示する。

【図4】図1のアセンブリにおける製造中の様々なステージを図示する。

【図5a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図5b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図5c】図1のアセンブリにおける製造中の様々なステージを図示する。

【図5d】図1のアセンブリにおける製造中の様々なステージを図示する。

【図6】図1のアセンブリにおける製造中の様々なステージを図示する。

【図7a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図7b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図7c】図1のアセンブリにおける製造中の様々なステージを図示する。

【図7d】図1のアセンブリにおける製造中の様々なステージを図示する。

【図8a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図8b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図9】図1のアセンブリにおける製造中の様々なステージを図示する。

【図10a】図1のアセンブリにおける製造中の様々なステージを図示する。

【図10b】図1のアセンブリにおける製造中の様々なステージを図示する。

【図10c】図1のアセンブリにおける製造中の様々なステージを図示する。

【図10d】図1のアセンブリにおける製造中の様々なステージを図示する。

【図11】本発明の実施例によるマイクロエレクトロニクス・アセンブリ中の内蔵TECによって提供される温度降下を示すグラフである。

【図12】図1のマイクロエレクトロニクス・アセンブリを含むシステムについての概要図である。

【発明を実施するための形態】

【0011】

内蔵熱電冷却機を含むマイクロエレクトロニクス・アセンブリを製作する方法、内蔵熱電冷却機を含むマイクロエレクトロニクス・アセンブリ、および、マイクロエレクトロニクス・アセンブリを含むシステムが、ここに開示される。

【0012】

様々な態様の図示された実施例がその技術内容を他の当業者に伝えるために当業者によって共通に使用される用語を用いて説明される。しかしながら、本発明は、説明された態様の幾つかのみで実施できることは当業者には明らかであろう。説明目的のために、特定の数、材料および構成は、図示された実施例についての完全な理解を提供するために述べられる。しかしながら、特定の詳細事項がなくても、本発明を実施できることは当業者には明らかであろう。他の例では、周知の特徴は、図示された実施例を不明瞭にしないために省略されるか単純化される。

【0013】

様々な動作は、本発明を理解するための最も便宜な手法で、複数の個別の動作として順番に説明されるであろうが、しかしながらこれらの動作は、必ずしもにその順番に依存することを暗示するものとして解釈されるべきではない。特に、これらの動作は、説明の順序であり、実行される必要はない。

【0014】

「ある実施例において」というフレーズが繰り返し使用される。そのフレーズは一般に同じ実施例を参照するものではないが、参照してもよい。用語「成る」、「含む」、および、「有する」は、その内容が他のことを述べない限り、同意語である。

【0015】

図1をまず参照して、配置102は、本発明の実施例に従って形成されたマイクロエレクトロニクス・アセンブリ100を含めて示される。配置102は、以下さらに説明されるように、電気回路137、および、フィードバック制御ループ140をさらに含む。アセンブリ100は、ダイ110のようなマイクロエレクトロニクス装置を含む。図1に示されるように、必要に応じて、ダイ110は、一方である相互接続金属化導体素子124,128,132と他方であるダイ110のシリコン基板115との間の相互拡散を防ぐためにその裏面114(すなわち、内蔵TECを含むその側面)上に提供される初期酸化層112を含み、さらに電気的な絶縁層も提供する。相互接続金属化導体素子(122,124,126,128,130,132,134)は短いので、電気的な絶縁の提供が必要とされる。酸化層112は、シリコン酸化層を含み、周知の方法のいずれかに従って、ダイ110の裏面114上に成長する。好ましくは、酸化層112は、垂直の拡散炉中でダイ110の裏面114上に熱成長する。アセンブリ100は、本発明の実施例によるマイクロエレクトロニクス装置上に構築されたTEC120をさらに含む。図1に示されるように、TEC120とダイ110との間に搭載材料は存在しない。「搭載材料」によって、本発明の態様で意味するものは、1つのマイクロエレクトロニクス・コンポーネントを別のものに物理的に付属させる材料であり、例えば、搭載材料の例には、はんだ、熱グリース、および、エポキシを含むが、しかしこれらに制限されることはない。図示された実施例中のTEC120は、図のように対となるN型電極116およびP型電極118を含み、その電極は、TE材料、例えば、BiまたはTeベースの合金(例えば、Bi2Te3またはBiSb)、またはPbTeまたはSiGeで作製され、他のタイプのTE材料が本発明の実施例の範囲内にあることは理解されるであろう。電極のTE材料は従来のドーパントで適切にドープされるが、例えば、N型ドーパントとしてリン、ヒ素、アンチモン、ビスマス、セレンおよびテルルが使用され、そしてP型ドーパントとしてホウ素、アルミニウム、ガリウムおよびインジウムが使用される。P型およびN型電極は、パターン化された酸化層119によって分離され、それは、当業者によって認識されるように、周知の方法のいずれか1つを使用して提供される。酸化層119の機能は、N型およびP型電極を互いに電気的に分離することである。N型およびP型電極は、相互接続金属化導体素子122,124,126,128,130,132,134によって共に電気的に結合される。導体素子122−134は、例えば、アルミニウム銅合金(約0.5%の銅を含有)、または銅、好ましくは約0.5%の銅を含有するアルミニウム銅合金のようなあらゆる適切な導電材料からなる。本発明の実施例によるTEC120の厚さの範囲は約50ミクロンと約200ミクロンの間であり、電極は約20ミクロンと約50ミクロンの間の厚みを有し、導電材料は厚さとして約10と約100ミクロンの間にある。

【0016】

TEC120によるダイ110の冷却は、ペルチエ効果の機能として生じる。再び図1を参照して、特に、DC電源136はTECに接続され、図示されるように導体素子122,134に同じ電力を供給するために回路137を形成する。回路137中の電子は、回路137中のTEC120を通って図示された矢印の方向に流れ、そうすることでダイの動作中にダイ110から排熱する。熱終端でTECによって廃棄された電力は、ダイの冷却裏面で吸収された電力にTECで放散された電力をプラスした電力に等しい。TEC120は、ダイ110から吸収した熱を放散するために、例えば、インテグレイテッド・ヒート・スプレッダ(IHS:integrated heat spreader)、または液冷冷却板(liquid cooled cold plate)のような従来のヒート・シンク138に結合されてもよい。冷接点、すなわちダイ110とTEC120との間の接合面で吸収された熱は、その回路を通過する電流、および、N型およびP型の電極の対から成るカップルの数に比例した率で、熱接点、またはTEC120とヒート・シンク138との間の接合面の方へ排出される。図1に示されるように、図示されたNおよびPのカップルはTECモジュールへ結合され、ここでそれらは電気的に連続して、また熱的に並行に接続される。TEC120に印加される典型的な電圧は、約3Vから約5Vの範囲であり、12Vまで上げることができる。TECによって提供される局所冷却によって、ダイの全電力は、例えば、その正面からみてダイ上のいずれのポイントにおいても摂氏100度のように、同じ最高温度の規格値を超過せずに増加させることができる。必要があれば、本発明の実施例に従って、フィードバック制御ループ140が、図1に概略的に示されるように、電源136によって電力が供給される電気回路に結合されてもよい。フィードバック制御ループ140は、ダイの温度を検出するためにダイ110に結合されるように概略的に示される温度センサTSを含む。さて、TSは、次に、例えば、TECに供給される電源136の電圧を規制することにより、TEC120を通る電流を規制するフィードバック制御システムFCSに信号を伝える。このように、フィードバック制御ループ140によって、ダイ110の温度の関数としてTEC120によって提供される冷却範囲の管理を行なうことができる。FCSは、1つの従来方式としてTEC120を通る電流を規制するために、TSから温度信号を受け取るためにいずれかの従来のマイクロプロセッサを含んでいてもよい。

【0017】

図1および後続の図はダイとしての要素110に関するが、本発明の実施例はダイを含むマイクロエレクトロニクス・アセンブリに制限されることはなく、それらの範囲内にTECによって達成される冷却を必要とするのに適したあらゆるマイクロエレクトロニクス装置を含むマイクロエレクトロニクス・アセンブリに及ぶことに注目されるべきである。加えて、図1は、複数のカップル(すなわち、電気的に接続されたNおよびP型電極の複数の対)を含むTECモジュールを示すが、本発明の実施例は、その範囲内に単一のカップルからなるTECモジュールを含んでいてもよい。

【0018】

本発明の実施例は、好ましくは、例えばアセンブリ100は、冷却されるべきマイクロエレクトロニクス装置とTECとの間の熱接触抵抗を著しく減少させ、それにより、ホット・スポットでの比較的大きな温度低下が見込め、さらに所要の温度管理の効果を達成するために必要なTECへの入力電力をさらに削減させることができる。このように、TECがはんだ、熱グリースまたはエポキシのような搭載材料によって冷却されるべきマイクロエレクトロニクス装置に搭載されている最先端技術によるTEC技術に比較して、本発明の実施例は、冷却されるべき装置とTECとの間のあらゆる熱接触抵抗を実質的に除去する方法で、搭載材料によって冷却されるべきマイクロエレクトロニクス装置に付けられることと対比して、アセンブリの一部として内蔵されるマイクロエレクトロニクス・アセンブリを提供する。

【0019】

次に図2−図9cを参照すると、図1のアセンブリ100のようなマイクロエレクトロニクス・アセンブリを製作する方法の様々なステージが示される。様々なステージは、以下さらに詳細に説明されるであろう。

【0020】

図2に見られるように、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する第1ステージは、ダイ110のようなマイクロエレクトロニクス装置を提供し、TECの対応するNおよびP型電極対に電気的に結合するために適合した複数の第1の導体素子を提供することを含む。いくつかの実施例によれば、複数の導体素子は、ダイ110上に第1の導電層200の形で相互接続金属化層をまず提供し、次に、複数の第1の導体素子を形成するために第1の導電層200に相互接続パターンを提供することにより用意される。上記のように、ダイ110は、まず酸化物112の層を含み、次にその上に第1の導電層200が、例えば約0.5%の銅を含むアルミニウム銅合金、または銅のみのようなあらゆる導電材料からなり、例えばスパッタリングまたは蒸着のような金属化層を堆積する周知の堆積方法によって堆積することができる。

【0021】

次に図3a−図3dを参照して、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、第1の導電層200中に相互接続パターンを提供することをさらに含む。相互接続パターンの用意により、TEC120の個々のカップルに電力を供給するために、導電層200から個々の導体素子が形成される。図3a−図3dは、第1の導電層200に相互接続パターンを提供する1つの例を示し、その例は、相互接続パターンを層200にエッチングするために、リソグラフィ、または、マスク/現像/エッチング手順を使用することを含む。特に、図3aに見られるように、層200中に相互接続パターンを用意することにより、第1の導電層200上にレジスト層210が形成されることを含む。レジスト層は、周知技術のいずれかに従って、例えば、塗布機または現像機を用いる回転プロセスと通して、提供される。分配されるレジスト、その粘性、および、スピン速度と時間の量は、当業者によって認識されているように、最終レジスト厚および等質性の決定を支援する。従来のレジスト蒸着技術は、本発明の実施例に従って示されるように、レジスト層210を提供するために使用される。

【0022】

次に図3bに見られるように、レジスト層210の予め定める部分が、層200上に提供される相互接続パターンの機能として取り除かれる。図3bに示されるように、ある実施例によれば、レジスト層210の予め定める部分の除去は、図示されるようにレジスト層210を、マスク220を通る光に暴露することによって達成されるが、そのマスクは層200上に提供される相互接続パターンに対応するパターンを表わし、その後、その露光された予め定める部分を現像液を用いて溶解する。マスク220によって提供される相互接続パターンは、マスク220およびレジスト層210を、例えば、ステッパにより図3bの破線の矢印で示されるUV光のような光に暴露することによりにより、レジスト層210上に転写される。光の波長と強さ、および、露光時間は、当業者によって認識されるように、パターンを適切に露光する際の条件である。従来の露光パラメータが本発明の実施例に従って用いられる。その後、レジスト層の露出した部分は、周知な現像液を用いて溶解される。現像時間、温度、および、現像液の濃度は、露出したレジストを適切に溶解する条件である。従来の露光パラメータは、本発明の実施例に従って使用されてもよい。レジスト層210の予め定める部分の除去は、層200上に提供される相互接続パターンを示すパターン化されたレジスト層210’を形成する。

【0023】

次に図3cを参照して、層200の予め定める部分は、層200の上に提供される相互接続パターンの機能として削除される。図3cに示されるように、ある実施例によれば、層200の予め定める部分の除去は、パターン化されたレジスト層’210によって保護されていない層200の部分をエッチングすることにより達成される。本発明の実施例に従って、従来のエッチング・パラメータが使用される。例えば、ある実施例によれば、アルミニウムのエッチャ(etcher)のようなプラズマ(ドライ)エッチャが層230の保護されていない予め定める部分をエッチングするために使用される。レジストによって保護されている領域は、図1に示される第1の導体素子124,128,132を含む、パターン化された相互接続金属化層200’の活性領域になるであろう。図3dに見られるように、エッチングが完了すると、アッシャ(asher)(また、プラズマ・エッチャの一種)は、第1のパターン化された金属化層200’を形成するために残りのレジストを除去するために使用されてもよい。

【0024】

図4に見られるように、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、パターン化された金属化層200’上にTE材料のN型層230を提供することをさらに含む。N型層230の用意は、ある実施例によれば、ドーパントが注入されたTE材料プリカーサ(precursor)のCVDまたはPVD蒸着、または、それとは別に蒸着後にサイト・ドーピング上で後続するTE材料プリカーサのCVD蒸着を含む。N型ドーパントは、例として、リン、ヒ素、アンチモン、ビスマス、セレン、および、テルルを含む。

【0025】

次に図5a−図5dを参照して、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、N型層230中に電極パターンを提供することをさらに含む。電極パターンは、層230から別個のN型電極を形成することにより用意される。図5a−図5dは、N型層230中に電極パターンを提供する1つの例を示すが、その例は、層230に電極パターンをエッチングするためにリソグラフィまたはマスク/現像/エッチング手順を使用することを含む。特に、図5aに見られるように、層230中の電極パターンの用意は、第1の導電層230上にレジスト層240を用意することを含む。本発明の実施例に従って、従来のパラメータがレジスト層を提供するために使用されてもよい。例えば、レジスト層は、上記図3aに関して述べられたのと同じ方法で提供されてもよい。

【0026】

次に図5bに見られるように、N型層230の予め定める部分は、層230上に提供されるべきN型電極パターンの機能として取り除かれる。図3bに示されるように、ある実施例によれば、レジスト層240の予め定める部分の除去は、図示されるようにレジスト層240を、マスク250を通る光に暴露し、そのマスクは層230上に提供される電極パターンに対応するパターンを示しており、その後現像溶液を用いて露出した予め定める部分を溶解することにより達成される。マスク250によって提供される電極パターンは、マスク250およびレジスト210を、例えば、ステッパにより図5bの破線の矢印で示されるUV光のような光に暴露することにより、レジスト層240上に転写される。本発明の実施例に従って従来の露光パラメータが使用されてもよい。例えば、露出は、上記図3bに関して述べられたのと同じ方法で達成される。その後、レジスト層の露出した部分は、周知なものとして、現像溶液を用いて溶解される。本発明の実施例に従って従来の現像パラメータが使用されてもよい。例えば、現像は、上記図3bに関して述べられたのと同じ方法で達成される。レジスト層240の予め定める部分の除去は、層230の上に提供される電極パターンを示すパターン化されたレジスト層240’を形成する。

【0027】

次に図5cを参照して、層230の予め定める部分は、層230上に提供される電極パターンの機能として取り除かれる。図5cに示されるように、ある実施例によれば、層230の予め定める部分の除去は、パターン化されたレジスト層240’によって保護されていない層230の部分をエッチングすることにより達成される。本発明の実施例に従って従来のエッチング・パラメータが使用されてもよい。そのエッチングは、上記図3cに関して説明されたのと同じ方法で行なわれる。例えば、ある実施例によれば、アルミニウムのエッチャのようなプラズマ(ドライ)エッチャが層230の保護されていない予め定める部分をエッチングするために使用される。レジストによって保護される領域は、図1に示されるN型電極116になるであろう。図5dに見られるように、エッチングが完了すると、アッシャ(また、プラズマ・エッチャの一種)は、電極116を含むTE材料のパターン化されたN型層に230’を形成するために残りのレジストを除去するために使用されてもよい。次に図6を参照して、本発明の実施例による内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、酸化層260を層200’,230’の上に提供することを含む。酸化層260は、当業者によって認識される周知の方法のいずれか1つに提供される。酸化層260は、図示されるように、電極116間および図示されるパターン化された導電層200’の導体素子間の間隙を充填する。

【0028】

次に図7a−図7dを参照して、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、酸化層260中の電極パターンを提供することをさらに含む。電極パターンは、層260中に散在した個別のP型電極を形成することにより用意される。図7a−図7dは、酸化層260中に電極パターンを提供する1つの例を示すが、その例は、層260に電極パターンをエッチングするためにリソグラフィまたはマスク/現像/エッチング手順を使用することを含む。特に、図7aに見られるように、層260中の電極パターンの用意は、第1の導電層260上にレジスト層270を用意することを含む。本発明の実施例に従って、従来のパラメータがレジスト層を提供するために使用されてもよい。例えば、レジスト層は、上記図3aに関して述べられたのと同じ方法で提供されてもよい。

【0029】

次に図7bに見られるように、酸化層260の予め定める部分は、層260中に提供されるP型電極パターンの機能として取り除かれる。図7bに示されるように、ある実施例によれば、レジスト層270の予め定める部分の除去は、図示されるようにレジスト層270を、マスク280を通る光に暴露し、そのマスクは層260上に提供される電極パターンに対応するパターンを示しており、その後現像溶液を用いて露出した予め定める部分を溶解することにより達成される。マスク280によって提供される電極パターンは、マスク280およびレジスト270を、例えば、ステッパにより図7bの破線の矢印で示されるUV光のような光に暴露することにより、レジスト層270上に転写される。本発明の実施例に従って従来の露光パラメータが使用されてもよい。例えば、露出は、上記図3bに関して述べられたのと同じ方法で達成される。その後、レジスト層の露出した部分は、周知なものとして、現像溶液を用いて溶解される。本発明の実施例に従って従来の現像パラメータが使用されてもよい。例えば、現像は、上記図3bに関して述べられたのと同じ方法で達成される。レジスト層270の予め定める部分の除去は、層260の上に提供される電極パターンを示すパターン化されたレジスト層270’を形成する。次に図7cを参照して、層260の予め定める部分は、層260上に提供される電極パターンの機能として取り除かれる。図7cに示されるように、ある実施例によれば、層260の予め定める部分の除去は、パターン化されたレジスト層270’によって保護されていない層260の部分をエッチングすることにより達成される。本発明の実施例に従って従来のエッチング・パラメータが使用される。そのエッチングは、上記図3cに関して説明されたのと同じ方法で行なわれる。例えば、ある実施例によれば、アルミニウムのエッチャのようなプラズマ(ドライ)エッチャが層260の保護されていない予め定める部分をエッチングするために使用される。レジストによって保護される領域は、図1に示されるP型電極118になるであろう。図7dに見られるように、エッチングが完了すると、アッシャ(また、プラズマ・エッチャの一種)は、ビア265を画定するTE材料のパターン化されたN型層に260’を形成するために残りのレジストを除去するために使用されてもよい。

【0030】

次に図8a−図8bを参照して、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、パターン化されたILD層のビア中にP型電極を提供することをさらに含む。ある実施例に従うP型電極は、パターン化された酸化層260’のビア265中にTE材料のP型レッグ290を含むP型材料300を提供し、図1に示されるようなP型電極118を形成するためにその後材料300をエッチングすることにより用意される。「レッグ」によって、簡単な説明の内容中に意味することは、TECのコンポーネントを生成するための次のプロセスのために提供される材料の複数のブロックである。P型レッグ290を含むP型材料300の用意は、ある実施例によれば、ドーパントが注入されたTE材料プリカーサのCVDまたはPVD蒸着、または、それとは別に蒸着後にサイト・ドーピング上で後続するTE材料プリカーサのCVD蒸着を含み、その蒸着はILD層上にTE材料プリカーサの層を生成し、ホール中にP型電極が提供される。P型レッグ290を含むP型材料300を用意した後に、レッグ290の一部を含む材料300の一部は、図8bに見られるように、エッチングされ、図示されるようにP型電極およびパターン化された酸化層260”を生成する。

【0031】

図9および図10a−図10dに見られるように、内蔵TECを含むマイクロエレクトロニクス・アセンブリを製作する方法は、例えば対応する対のNおよびP型電極に電気的に結合された図1に示される導体素子122,126,130,134のような複数の第2の導体素子を提供することを含む。第2の導体素子は、いくつかの実施例によれば、まず電極上に第2の導電層310の形状を備える相互接続金属化層を提供し、次に複数の第2の導体素子を形成するために第2の導電層310中に相互接続パターンを提供することを含む。第2の導電層310は、図9に示されるように、第1の導電層200に類似しており、例えば、上述されたように約0.5%の銅を含むアルミニウム銅合金、あるいは銅のみのようなあらゆる導電材料からなり、例えばスパッタリングまたは蒸着のような金属化層を堆積する周知の堆積方法によって堆積することができる。

【0032】

次に図10a−図10dを参照して、図1に示されるTEC120の個別のカップルに電力を供給するために、第1の導電層310中に相互接続パターンを提供することにより、導電層310から別個の導体素子が形成される。図10a−図10dは、第2の導電層310中に相互接続パターンを提供する1つの例を示し、その例は、層310に相互接続パターンをエッチングするために、リソグラフィまたはマスク/現像/エッチング手順を用いることを含む。特に、図10aに見られるように、層310中の相互接続パターンの用意は、第2の導電層310上にレジスト層320を用意することを含む。本発明の実施例に従う従来のパラメータがレジスト層を提供するために使用されてもよい。例えば、レジスト層は、上記図3aに関して述べられたのと同じ方法で提供されてもよい。

【0033】

次に図10bに見られるように、レジスト層320の予め定める部分が層310上に提供される相互接続パターンの機能として取り除かれる。図10bに示されるように、ある実施例に従って、レジスト層320の予め定める部分の除去が、図示されるようなマスク330を通して光をレジスト層320に暴露し、そのマスクは層310上に提供される相互接続パターンに対応するパターンを有しているが、その後現像液の使用により暴露した予め定める部分を溶解することにより達成される。マスク330によって提供される相互接続パターンは、マスク330およびレジスト層320を、例えばステッパにより図10bの破線の矢印で示唆されるようにUV光のような光に暴露させることによりレジスト層320上に転写される。光の波長および強さ、および、露光時間は、すべてパターンを適切に露出させる条件である。本発明の実施例に従う従来の露光パラメータが使用されてもよい。例えば、露光は、上記図3bに関して述べられたのと同じ方法で達成することができる。その後、レジスト層の露光された部分は、現像液を用いて周知な方法で溶解される。現像時間、温度、および、現像液の濃度は、すべて露光したレジストを適切に溶解する条件である。本発明の実施例に従う従来の現像パラメータが使用されてもよい。例えば、現像は、上記図3bに関して述べられたのと同じ方法で達成することができる。レジスト層320の予め定める部分を除去することにより、層310上に提供される相互接続パターンを示すパターン化されたレジスト層320’が形成される。次に図10cを参照して、層310の予め定める部分が層310上に提供される相互接続パターンの機能として取り除かれる。図10c示されるように、ある実施例によれば、層310の予め定める部分の除去は、パターン化されたレジスト層320’によって保護されていない層310の一部をエッチングすることにより達成される。本発明の実施例に従う従来のエッチング・パラメータが使用されてもよい。そのエッチングは、上記図3cに関して述べられたのと同じ方法で達成することができる。例えば、ある実施例によれば、アルミニウムのエッチャのようなプラズマ(ドライ)エッチャが層310の保護されていない予め定める部分をエッチングするために使用されてもよい。レジストによって保護されている領域は、図1に示される第2の導体素子122,126,130,134を含む、パターン化された相互接続金属化層310’の活性領域になるであろう。図10dに見られるように、エッチングが完了すると、アッシャ(また、プラズマ・エッチャの一種)は、パターン化された金属化層310’を形成するために残りのレジストを除去するために使用されてもよい。図10dに示される製作ステージの完成により、内蔵TECを含むマイクロエレクトロニクス・アセンブリ100が形成され、それは図1に示されかつ上述された配置102に使用される。

【0034】

本発明の実施例は、さらに、それらの範囲内にその各側面に単一の相互接続金属化導体素子を備えた単一のカップルTECのようなTECを含み、両方を電気的および熱的に並列に接続された排他的P型電極または排他的N型電極を含む。このような望ましいTECが本発明の実施例に従って提供され、ここで最も共通に使用されるダイより小さいダイの冷却が実施例により熟慮され、そのダイの冷却は2つのスポット上だけの冷却をその上に要求するものであり、および/または、P型およびN型電極の両方を含むTECに典型的に関連した電圧降下が回避される。

【0035】

上述のように、冷却されるべきマイクロエレクトロニクス装置およびその上に搭載されたTECを含む先行技術のアセンブリでは、TEC特性に関する効率の損失は、典型的にはTECが搭載されるマイクロエレクトロニクス装置の後部とその搭載されたTECとの間の熱抵抗によって引き起こされる。熱エネルギーがマイクロエレクトロニクス装置からTECに入るにつれて、熱抵抗によって温度降下が引き起こされる。TECの冷却面(すなわち、マイクロエレクトロニクス装置に直接搭載された側面)の温度降下によって、TECは、熱接触抵抗が存在しなかった場合より低い温度で動作させる。その結果、TECによってマイクロエレクトロニクス装置のホット・スポットにもたらされる冷却低下が不利に行なわれる一方、TECへ要求されるパワー入力が増加する。この点に関して図11に言及され、冷却量または摂氏デルタT対TECに提供される必要な電力であるワット量を示すグラフである。図11に見られるように、本発明の実施例によるマイクロエレクトロニクス・アセンブリ中の内蔵TECは、最先端技術によるマイクロエレクトロニクス装置に従来から搭載された比較対照となるTECによって提供される温度低下より大きい、少なくとも摂氏約1/2度の温度低下を提供することができる。

【0036】

本発明による実施例の別の利点は、冷却されるマイクロエレクトロニクス装置のサイズおよび温度低下の仕様に特に調整されたTECの製作方法を提供することであり、先行技術のTECに対比して、それは一般にセット・サイズおよび形状の標準に従って製造され、その後、サイズと温度低下仕様に必要な最適化をしないでマイクロエレクトロニクス装置上に搭載される。本発明の実施例による製作方法によって、マイクロエレクトロニクス装置の製作者は、TEC製作者からTECを個別に購入するよりむしろ、特定のニーズに適合した内蔵コンポーネントとしてTECを製作し、それからマイクロエレクトロニクス装置と共に同じものに集積することが可能となる利点を有している。

【0037】

図12を参照して、本発明の実施例が使用される多くの可能なシステム900の1つが図示され、マイクロエレクトロニクス配置102はシステム900のサブシステム1000に使用されるマイクロエレクトロニクス・アセンブリ100を含む。サブシステム1000は、例えば、マイクロプロセッサを含む。代替となる実施例では、サブシステム1000は特定用途向けIC(ASIC)を含む。チップセット(例えば、グラフィックス、音および制御チップセット)に見られる集積回路も、本発明の実施例に従ってパッケージにされる。

【0038】

図12に示された実施例については、システム900は、さらにメインメモリ1002、グラフィック・プロセッサ1004、大容量格納装置1006、および/または、バス1100を介して互いに結合された入出力モジュール1008を含む。メモリ1002の例は、スタティック・ランダム・アクセス・メモリ(SRAM)およびダイナミック・ランダム・アクセス・メモリ(DRAM)を含むが、これらに制限されるものではない。大容量格納装置1006の例には、ハードディスク・ドライブ、コンパクト・ディスク・ドライブ(CD)、大容量光ディスク(DVD)などを含むが、これらに制限されるものではない。入出力モジュール1008の例には、キーボード、カーソル制御器、ディスプレイ、ネットワーク・インターフェイスなどを含むが、これらに制限されるものではない。バス1100の例には、周辺機器制御インターフェイス(PCI)バス、および、産業標準アーキテクチャ(ISA)バスなどを含むが、これらに制限されるものではない。様々な実施例では、システム900は、ワイヤレス携帯電話機、個人向け携帯型情報機器、ポケットPC、タブレットPC、ノートPC、デスクトップ・コンピュータ、セットトップ・ボックス、メディア・センターPC、DVDプレーヤ、および、サーバである。特定の実施例が好適な実施例の説明目的のためにここに図示され説明されたが、同じ目的を達成すると意図された広範囲に亘る代替または均等な実施が本発明の範囲を逸脱せずに示されかつ説明された特定の実施例の代わりに用いられることが当業者によって評価されるであろう。当業者は、本発明が極めて広範囲の実施例中で実施されることを容易に認識するであろう。このアプリケーションは、任意の順応またはここに議論された実施例のあらゆる適応または変動をも包含するように意図される。したがって、本発明は、その請求項とその均等によってのみ制限されることは明白に意図されるものである。

【符号の説明】

【0039】

100 マイクロエレクトロニクス・アセンブリ

102 マイクロエレクトロニクス配置

110 ダイ

116 N型電極

118 P型電極

120 TEC

136 DC電源

137 電気回路

138 ヒート・シンク

140 フィードバック制御ループ

【特許請求の範囲】

【請求項1】

マイクロエレクトロニクス配置において、

マイクロエレクトロニクス装置、および、

内蔵TECと前記マイクロエレクトロニクス装置との間に搭載材料を介在させないで、前記マイクロエレクトロニクス装置に結合された内蔵TEC、から成るマイクロエレクトロニクス・アセンブリと、

前記内蔵TECに電気的に接続され、前記内蔵TECへ電流を供給するために適合した電源を含む電気回路と、

前記マイクロエレクトロニクス装置の温度の機能として前記内蔵TECによって提供される冷却の範囲を制御するために、前記マイクロエレクトロニクス装置のシリコン基板、前記内蔵TEC、および、前記電気回路に結合されたフィードバック制御ループと、

から成ることを特徴とするマイクロエレクトロニクス配置。

【請求項2】

前記内蔵TECは、N型電極、P型電極、カップルの前記N型電極およびP型電極を互いに電気的に結合する複数の導体素子、および、前記導体素子のそれぞれ、前記N型電極のそれぞれ、および、前記P型電極のそれぞれの間のパターン化された絶縁体層を含む少なくとも1つのカップルからなることを特徴とする請求項1記載のマイクロエレクトロニクス配置。

【請求項3】

前記フィードバック制御ループは、前記マイクロエレクトロニクス装置の温度を検出するために、前記マイクロエレクトロニクス装置の前記シリコン基板に結合される温度センサを含み、前記温度センサは、前記電源の電圧を制御することにより前記内蔵TECを介して電流を制御する前記フィードバック制御ループに信号を伝えることを特徴とする請求項1記載のマイクロエレクトロニクス配置。

【請求項4】

前記マイクロエレクトロニクス装置から取り出された熱を放散するために、前記内蔵TECに結合されたヒート・シンクをさらに含むことを特徴とする請求項1記載のマイクロエレクトロニクス配置。

【請求項5】

マイクロエレクトロニクス・アセンブリにおいて、

マイクロエレクトロニクス装置と、

内蔵TECと前記マイクロエレクトロニクス装置との間に搭載材料を介在させないで、前記マイクロエレクトロニクス装置に結合された内蔵TECと、

前記内蔵TECに電気的に接続され、前記内蔵TECに電流を供給するために適合した電源を含む電気回路と、

前記マイクロエレクトロニクス装置の温度の機能として前記内蔵TECによって提供される冷却の範囲を制御するために、前記マイクロエレクトロニクス装置のシリコン基板、前記内蔵TEC、および、前記電気回路に結合されたフィードバック制御ループと、を含み、

前記内蔵TECは、N型電極およびP型電極を含む少なくとも1つのカップル、前記カップルの前記N型電極および前記P型電極を互いに電気的に結合する複数の導体素子、および、前記導体素子のそれぞれ、前記N型電極のそれぞれ、および、前記P型電極のそれぞれの間のパターン化された絶縁体層を含む、

ことを特徴とするマイクロエレクトロニクス・アセンブリ。

【請求項6】

前記マイクロエレクトロニクス装置は、

【請求項7】

マイクロエレクトロニクス・アセンブリであって、

マイクロエレクトロニクス装置、および、

内蔵TECと前記マイクロエレクトロニクス装置との間に搭載材料を介在させないで、前記マイクロエレクトロニクス装置に結合された内蔵TEC、から成るマイクロエレクトロニクス・アセンブリと、

前記内蔵TECに電気的に接続され、前記内蔵TECに電流を供給するために適合した電源を含む電気回路と、

前記マイクロエレクトロニクス装置の温度の機能として前記内蔵TECによって提供される冷却の範囲を制御するために、前記マイクロエレクトロニクス装置のシリコン基板、前記内蔵TEC、および、前記電気回路に結合されたフィードバック制御ループと、

前記マイクロエレクトロニクス・アセンブリに結合されたグラフィック・プロセッサと、を含み、

前記内蔵TECは、N型電極およびP型電極を含む少なくとも1つのカップル、前記カップルの前記N型電極および前記P型電極を互いに電気的に結合する複数の導体素子、および、前記導体素子のそれぞれ、前記N型電極のそれぞれ、および、前記P型電極のそれぞれの間のパターン化された絶縁体層を含む、

ことを特徴とするマイクロエレクトロニクス・システム。

【請求項1】

マイクロエレクトロニクス配置において、

マイクロエレクトロニクス装置、および、

内蔵TECと前記マイクロエレクトロニクス装置との間に搭載材料を介在させないで、前記マイクロエレクトロニクス装置に結合された内蔵TEC、から成るマイクロエレクトロニクス・アセンブリと、

前記内蔵TECに電気的に接続され、前記内蔵TECへ電流を供給するために適合した電源を含む電気回路と、

前記マイクロエレクトロニクス装置の温度の機能として前記内蔵TECによって提供される冷却の範囲を制御するために、前記マイクロエレクトロニクス装置のシリコン基板、前記内蔵TEC、および、前記電気回路に結合されたフィードバック制御ループと、

から成ることを特徴とするマイクロエレクトロニクス配置。

【請求項2】

前記内蔵TECは、N型電極、P型電極、カップルの前記N型電極およびP型電極を互いに電気的に結合する複数の導体素子、および、前記導体素子のそれぞれ、前記N型電極のそれぞれ、および、前記P型電極のそれぞれの間のパターン化された絶縁体層を含む少なくとも1つのカップルからなることを特徴とする請求項1記載のマイクロエレクトロニクス配置。

【請求項3】

前記フィードバック制御ループは、前記マイクロエレクトロニクス装置の温度を検出するために、前記マイクロエレクトロニクス装置の前記シリコン基板に結合される温度センサを含み、前記温度センサは、前記電源の電圧を制御することにより前記内蔵TECを介して電流を制御する前記フィードバック制御ループに信号を伝えることを特徴とする請求項1記載のマイクロエレクトロニクス配置。

【請求項4】

前記マイクロエレクトロニクス装置から取り出された熱を放散するために、前記内蔵TECに結合されたヒート・シンクをさらに含むことを特徴とする請求項1記載のマイクロエレクトロニクス配置。

【請求項5】

マイクロエレクトロニクス・アセンブリにおいて、

マイクロエレクトロニクス装置と、

内蔵TECと前記マイクロエレクトロニクス装置との間に搭載材料を介在させないで、前記マイクロエレクトロニクス装置に結合された内蔵TECと、

前記内蔵TECに電気的に接続され、前記内蔵TECに電流を供給するために適合した電源を含む電気回路と、

前記マイクロエレクトロニクス装置の温度の機能として前記内蔵TECによって提供される冷却の範囲を制御するために、前記マイクロエレクトロニクス装置のシリコン基板、前記内蔵TEC、および、前記電気回路に結合されたフィードバック制御ループと、を含み、

前記内蔵TECは、N型電極およびP型電極を含む少なくとも1つのカップル、前記カップルの前記N型電極および前記P型電極を互いに電気的に結合する複数の導体素子、および、前記導体素子のそれぞれ、前記N型電極のそれぞれ、および、前記P型電極のそれぞれの間のパターン化された絶縁体層を含む、

ことを特徴とするマイクロエレクトロニクス・アセンブリ。

【請求項6】

前記マイクロエレクトロニクス装置は、

【請求項7】

マイクロエレクトロニクス・アセンブリであって、

マイクロエレクトロニクス装置、および、

内蔵TECと前記マイクロエレクトロニクス装置との間に搭載材料を介在させないで、前記マイクロエレクトロニクス装置に結合された内蔵TEC、から成るマイクロエレクトロニクス・アセンブリと、

前記内蔵TECに電気的に接続され、前記内蔵TECに電流を供給するために適合した電源を含む電気回路と、

前記マイクロエレクトロニクス装置の温度の機能として前記内蔵TECによって提供される冷却の範囲を制御するために、前記マイクロエレクトロニクス装置のシリコン基板、前記内蔵TEC、および、前記電気回路に結合されたフィードバック制御ループと、

前記マイクロエレクトロニクス・アセンブリに結合されたグラフィック・プロセッサと、を含み、

前記内蔵TECは、N型電極およびP型電極を含む少なくとも1つのカップル、前記カップルの前記N型電極および前記P型電極を互いに電気的に結合する複数の導体素子、および、前記導体素子のそれぞれ、前記N型電極のそれぞれ、および、前記P型電極のそれぞれの間のパターン化された絶縁体層を含む、

ことを特徴とするマイクロエレクトロニクス・システム。

【図1】

【図2】

【図3a】

【図3b】

【図3c】

【図3d】

【図4】

【図5a】

【図5b】

【図5c】

【図5d】

【図6】

【図7a】

【図7b】

【図7c】

【図7d】

【図8a】

【図8b】

【図9】

【図10a】

【図10b】

【図10c】

【図10d】

【図11】

【図12】

【図2】

【図3a】

【図3b】

【図3c】

【図3d】

【図4】

【図5a】

【図5b】

【図5c】

【図5d】

【図6】

【図7a】

【図7b】

【図7c】

【図7d】

【図8a】

【図8b】

【図9】

【図10a】

【図10b】

【図10c】

【図10d】

【図11】

【図12】

【公開番号】特開2012−99836(P2012−99836A)

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願番号】特願2011−278001(P2011−278001)

【出願日】平成23年12月20日(2011.12.20)

【分割の表示】特願2007−548609(P2007−548609)の分割

【原出願日】平成17年12月27日(2005.12.27)

【出願人】(591003943)インテル・コーポレーション (1,101)

【Fターム(参考)】

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願日】平成23年12月20日(2011.12.20)

【分割の表示】特願2007−548609(P2007−548609)の分割

【原出願日】平成17年12月27日(2005.12.27)

【出願人】(591003943)インテル・コーポレーション (1,101)

【Fターム(参考)】

[ Back to top ]