再構成可能信号処理システム

【課題】 本発明は、故障に対する信頼性を高めた再構成可能信号処理システムの提供を目的とする。

【解決手段】 所定の信号処理機能を有する信号処理ユニットと、所望の信号処理機能に再構成可能な電子デバイスと、前記信号処理ユニットの故障を検出する故障検出手段と、前記電子デバイスを前記信号処理ユニットの信号処理機能に再構成するコンフィギュレーションデータを記憶するメモリとを備え、前記メモリに記憶されたコンフィギュレーションデータに基づいて前記故障検出手段により故障が検出された前記信号処理ユニットの信号処理機能に前記電子デバイスを再構成する再構成可能信号処理システムにおいて、前記信号処理ユニットと前記電子デバイスとを含むネットワーク上に前記メモリを少なくとも2つ以上分散させたことを特徴とする再構成可能信号処理システム。

【解決手段】 所定の信号処理機能を有する信号処理ユニットと、所望の信号処理機能に再構成可能な電子デバイスと、前記信号処理ユニットの故障を検出する故障検出手段と、前記電子デバイスを前記信号処理ユニットの信号処理機能に再構成するコンフィギュレーションデータを記憶するメモリとを備え、前記メモリに記憶されたコンフィギュレーションデータに基づいて前記故障検出手段により故障が検出された前記信号処理ユニットの信号処理機能に前記電子デバイスを再構成する再構成可能信号処理システムにおいて、前記信号処理ユニットと前記電子デバイスとを含むネットワーク上に前記メモリを少なくとも2つ以上分散させたことを特徴とする再構成可能信号処理システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、所望の信号処理機能に再構成可能な電子デバイスによるフェール時の機能を提供する再構成可能信号処理システムに関する。

【背景技術】

【0002】

従来から、フェールセーフ機能付き情報処理装置が知られている(例えば、特許文献1)。このフェールセーフ機能付き情報処理装置は、情報処理回路が故障した場合、その故障した情報処理回路に対応する再構成情報(構成データ)に基づいて、その故障した情報処理回路の機能がFPGA(Field programmable gate arrays)等の再構成可能な電子デバイス上に再現される。

【特許文献1】特開2000−81991号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、上述の従来技術では、構成データを記憶する記憶部が故障等の原因によって再構成情報の読み出しができなくなった場合、故障した情報処理回路の機能が再構成可能な電子デバイス上に再現することができなくなり、フェールセーフ機能を十分に発揮できない。

【0004】

そこで、本発明は、故障に対する信頼性を高めた再構成可能信号処理システムの提供を目的とする。

【課題を解決するための手段】

【0005】

上記課題を解決するため、本発明の一局面によれば、

所定の信号処理機能を有する信号処理ユニットと、

所望の信号処理機能に再構成可能な電子デバイスと、

前記信号処理ユニットの故障を検出する故障検出手段と、

前記電子デバイスを前記信号処理ユニットの信号処理機能に再構成する構成データを記憶する記憶手段とを備え、

前記記憶手段に記憶された構成データに基づいて前記故障検出手段により故障が検出された前記信号処理ユニットの信号処理機能に前記電子デバイスを再構成する再構成可能信号処理システムにおいて、

前記信号処理ユニットと前記電子デバイスとを含むネットワーク上に前記記憶手段を少なくとも2つ以上分散させたことを特徴とする再構成可能信号処理システムが提供される。

本局面によれば、ある信号処理ユニットが故障したとしても、再構成可能な電子デバイスをネットワーク上に少なくとも2つ以上分散させた構成データのいずれかを用いてその故障した信号処理ユニットの信号処理機能に再構成することができるので、システム全体の継続動作が可能となり故障に対する信頼性を高めることができる。

【発明の効果】

【0006】

本発明によれば、故障に対する信頼性を高めることができる。

【発明を実施するための最良の形態】

【0007】

以下、図面を参照して、本発明を実施するための最良の形態の説明を行う。

【0008】

[1.本システムの構成]図2は、本発明の再構成可能信号処理システムを車両用として適用した場合の車両内ネットワークの一構成例を示す図である。図2の左上には放送受信や無線通信を行うためのアナログ回路が示され、図2の左下には画像、距離、車両速度及び加速度等を測定するためのセンサー群が示されている。また、各部のアナログ信号をディジタルデータに変換するアナログディジタルコンバータ(ADC)とネットワーク2aに接続するインターフェース(I/F)が接続されている。なお、無線通信用のアナログ回路には、ネットワーク2aからのディジタルデータをアナログ信号に変換するディジタルアナログコンバータ(DAC)も具備する。

【0009】

また、カーナビゲーション、インタネットのウェブ閲覧、AV(オーディオ・ビデオ)再生及びゲーム等のマルチメディア信号処理のため、CD、DVD及びHD(ハードディスク)のドライブがネットワーク2aに接続されている。さらに、ユーザインターフェースのためのディスプレイやキーボード等の入出力装置もネットワーク2aに接続されている。

【0010】

図2の右下には、ブレーキ、ステアリング及びエンジン等の車両の主要な機械的機能を作動させるアクチュエータが、I/FとDACを介してネットワーク2aに接続されている。また、エアバックやシートベルト等のプリクラッシュシステムの機械的機能を作動させるモータやアクチュエータが、同様に接続されている。

【0011】

また、信号処理ユニット1〜Npがネットワーク2aに接続されている。ネットワーク2aへの接続方法は、車両の各部に分散するようにしている。図3(a)は、7個の信号処理ユニットが車両の各部に分散してネットワーク2a上に位置していることを示す一例である。各信号処理ユニット内部の概略構成の一例を図10に示す。図10では、信号処理ユニットは、再構成可能演算処理回路10aと2個のコンフィギュレーションデータメモリから構成される。再構成可能信号処理回路10aは、FPGAまたはリコンフィギュラブルプロセッサから構成される。FPGA、リコンフィギュラブルプロセッサ及びコンフィギュレーションデータについて、以下の[2.FPGAについて]で説明する。

【0012】

[2.FPGAについて]FPGAのようなプログラマブルな論理回路が、近年普及しつつある。詳細な内部構成は以下の「6.FPGAの内部構成」において記載するが、FPGAは、多数のLUT(Look-up table)とスイッチがチップ上に集積されており、LUTのデータとスイッチ制御情報を外部から書き込むことによって論理回路の再構成が行われ、プロセッサを含む所望の演算処理回路を実現することができる半導体デバイスである。このデバイスを用いれば、信号処理アルゴリズムを高速に且つ最小遅延時間で実行する最適構造の演算処理回路を構築できる。

【0013】

LUTに記憶するデータやスイッチ制御情報等の書き込まれるプログラムは、コンフィギュレーションデータ(構成データ)と呼ばれる。一般的にコンフィギュレーションデータを外部から書き込むためには多数の動作クロックサイクルが必要であるが、最近ではリコンフィギュラブルプロセッサと呼ばれるコンフィギュレーションデータを数クロックで短時間に書き込みと再構成ができる半導体も開発されている。

【0014】

「3.再構成可能信号処理ユニットの構成と故障時の復旧アルゴリズム」ここでは、ある信号処理ユニットが故障した場合に、故障した信号処理ユニットで実行していた演算回路を他の正常な信号処理ユニットに移動する手法について説明する。上述したように、信号処理ユニットは車両の各部に分散しており(図3)、各信号処理ユニットは再構成可能演算処理回路10aと2個のコンフィギュレーションデータメモリから構成される(図10)。

【0015】

ある信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータは別の場所に配置された他の2個の信号処理ユニットのコンフィギュレーションデータメモリに書き込まれている。その対応を図16に示す。ユニットのID番号とは、再構成可能演算処理回路10aの実装されている信号処理ユニットの番号である。例えば、1番の信号処理ユニットの再構成可能演算処理回路10aへロードするコンフィギュレーションデータは、2番と6番の信号処理ユニットのコンフィギュレーションデータメモリに格納されている。

【0016】

信号処理ユニットが故障した場合の復旧の方法について図11を参照しながら説明する。いま、3番の信号処理ユニットが故障したとする。3番の信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータが格納されている2番及び4番の信号処理ユニットが(図16)、3番の信号処理ユニットの故障を検出する。2番及び4番の信号処理ユニットは、3番の信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータをコンフィギュレーションデータメモリより読み出す。2番及び4番の信号処理ユニットは、読み出したコンフィギュレーションデータを7番の信号処理ユニットにネットワーク2aを経由して伝送することによって、その7番の信号処理ユニット内の再構成可能演算処理回路10a上に3番と同一の信号処理回路が再構成する。したがって、故障した3番の信号処理ユニットで行われていた信号処理は、7番の信号処理ユニットで継続して実行されることになる。また、3番の信号処理ユニットが故障したので、6番の信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータが格納されている信号処理ユニットが、2番の信号処理ユニットだけとなり一つ減ってしまう。そこで、7番のコンフィギュレーションメモリに、6番の信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータを格納することによって、故障により一つ減ってしまった状況を回復することができる。なお、7番の信号処理ユニットは、信号処理機能を持たない冗長の信号処理ユニットとして、予めネットワーク2a上に接続されているものである。

【0017】

また、故障を検出する信号処理ユニットは、特に限定しない。例えば、6番の信号処理ユニットが、3番の信号処理ユニットの故障を検出するとともに、2番及び4番の信号処理ユニットに対し3番のコンフィギュレーションデータを7番の信号処理ユニットに伝送する指令を出すようにしてもよい。

【0018】

また、上述の例では、自身のコンフィギュレーションデータが格納されているユニットの数は2個にしていた(以下、「多重化数を2にする」という)。この多重化数は、車両の走行方向と各信号処理ユニットの配置に基づいて決定される。車両が前方に走行していれば、車両フロント部に配置された信号処理ユニットは、衝突等により破損・故障する確率が高くなる。そこで、車両フロント部に配置された信号処理ユニットのコンフィギュレーションデータが格納されている信号処理ユニットの数を多くすることによって、衝突等による破損・故障に対する信頼性を向上させることができる。逆に、車両リヤ部に配置された信号処理ユニットに対しては、多重化数を減らすことも可能である。また、少なくとも2つ以上分散させておくことによって、1つのコンフィギュレーションデータメモリが故障したとしても、少なくとももう一つは残っているので、故障に対する信頼性も向上する。

【0019】

また、信号処理ユニットとその信号処理ユニットのコンフィギュレーションデータが格納されている信号処理ユニットとの位置関係は、できるだけ離したほうがよい。衝突等によって、それらが両方とも破損・故障してしまうことを避けるためである。例えば、車両フロント部に配置された2番の信号処理ユニットのコンフィギュレーションデータは、車両中間部に配置された5番及び車両リヤ部に配置された6番の信号処理ユニットに格納されている。

【0020】

ところで、コンフィギュレーションデータをロードする前に、信号処理ユニットが正常かどうかの検査が行われる。信号処理ユニットの故障診断は、自立分散的に行われ、自らが自己診断機能を有している。再構成可能演算処理回路10aにテスト用コンフィギュレーションデータをロードする。その回路10aに対し外部から入力信号を加えて、または、回路内部で信号を発生させて、所定の参照信号と比較して一致すれば、その再構成可能演算処理回路10aは正常と判断し、図3(b)に示されるように、フラグに“OK”と表示する。一方、不一致ならば故障と判断して、フラグに“NG”を表示する。“OK”と表示されたフラグを有する信号処理ユニットに対して、コンフィギュレーションデータがロードされると、そのフラグの表示は“BUSY”に変わる。また、自己診断機能が故障していた場合には、“NG”と表示する。このようにすることによって、どの信号処理ユニットが故障しているか否か(“OK”か“NG”)、使用可能か否か(“OK”か“BUSY”)を判別することができる。なお、正常であった場合はそのユニットにロードを行い、正常でなかった場合は正常なものが見つかるまで、他のユニットのフラグを検査する。

【0021】

上記のようなネットワーク2a上を伝送するコンフィギュレーションデータやフラグ情報は、図13で示されるネットワーク伝送用パケットで伝送する。宛先アドレスは、宛先の信号処理ユニットのIDアドレス(図16にあるような信号処理ユニットのID番号)、その信号処理ユニット内部の再構成可能演算処理回路10aのIDアドレス及びその回路内の演算要素(加算器等)のIDアドレスから構成される。送信元アドレスも、送信元の信号処理ユニットに関して、上記の宛先アドレスと同様の構成である。データ部は、図2のセンサー群からの出力データ、演算結果の演算用データまたはコンフィギュレーションデータ等である。信頼性を向上させるためにCRC(Cyclic redundancy checksum)が付加される。

【0022】

ネットワーク2aから信号処理ユニットに伝送されたパケットは、以下のように信号処理ユニット内で信号処理される。図14は、信号処理ユニットの構成の一例を示す図である。パケット分解部14aは、ネットワーク2aから伝送されたパケットの解析を行い、コンフィギュレーションデータ、演算入力データ若しくは読み取ったフラグの情報なのかを判別する。コンフィギュレーションデータならば、再構成可能演算処理回路14h(10a)にダウンロードを行う。演算入力データならば、その再構成された演算処理回路14hに演算データとして入力される。フラグならば、フラグ変化検出回路14iに入力される。フラグの変化によって他の信号処理ユニットが故障したことが判定される。

【0023】

パケット分解部14aを介したデータは、テーブル14に規定された対応関係に従って、マルチプレクサDMUX14dを介して、再構成可能演算処理回路14hやコンフィギュレーションデータメモリ等に出力される。コンフィギュレーションデータメモリは、NCM個分用意される。なお、NCMは多重化数を表す。他の信号処理ユニットの故障が検出された場合には、再構成可能演算処理回路10aによる演算結果データとコンフィギュレーションデータメモリからその故障した信号処理ユニットに対応するコンフィギュレーションデータが読み出される。読み出されたそれらのデータは、マルチプレクサMUX14eを経由した後に、パケット生成部14cによって生成された図13のデータパケットでネットワーク2aに送出される。

【0024】

再構成可能演算処理回路10aの検査は、まず、テスト信号発生回路を構成するためのコンフィギュレーションデータをテスト回路14fからロードする。そして、構成されたテスト信号発生回路から出力されたデータをテスト回路14f内の参照データと比較することによって、故障しているかどうかが判定される。その結果をフラグレジスタに設定する。

【0025】

[4.コンフィギュレーションデータのダウンロード手法]コンフィギュレーションデータを再構成可能演算処理回路10aにダウンロードすることによって、所望の回路が実現されるが、一般的なFPGAの場合、コンフィギュレーションデータのダウンロードが完了するまでにデータのビット数に依存したクロック数分の時間がかかる。たとえ1クロックで瞬時にダウンロードと再構成が完了して演算回路が切り替わったと仮定しても、ディジタル信号処理で頻繁に使用されるFIRフィルタは過去のデータを現在の出力の計算に使用するために、過去の入力データをコンフィギュレーションメモリに記憶させておく必要がある。したがって、新しく再構成が行われた直後の回路状態ではアクチュエータ等に対して送るべき出力データがしばらく現れない現象が発生する。それを解決するのが以下の手法である。

【0026】

図5は、本ダウンロード手法の一例を示す図である。簡単のために、2個のセンサー1,2、各センサーに対応する信号処理ユニット1,2若しくはアクチュエータ1,2、未使用の信号処理ユニット3及びネットワーク2aから構成される。

【0027】

図5(a)は、新しいコンフィギュレーションデータをロードする前の状態である。センサー1からの信号は、処理Aを処理する信号処理回路が搭載されている信号処理ユニット1に伝送される。信号処理ユニット1による処理Aの結果が、アクチュエータ1に伝送されて駆動する。センサー2、処理Bを処理する信号処理ユニット2及びアクチュエータ2も同様にデータが伝送される。未使用の信号処理ユニット3はネットワーク2aと制御信号の授受を行うが、データの授受を行わない。

【0028】

いま、センサー1による信号検出からアクチュエータ1の駆動までの上記の処理Aを処理Cに代える場合について説明する。図5(b)において、まず、信号処理ユニット1または2が、未使用の信号処理ユニット3に対して、起動制御信号を伝送する。

【0029】

図5(c)において、信号処理ユニット3に対して、図16のテーブルに従って、信号処理ユニット2(もしくは、(図5上には記載していないが)信号処理ユニット4)からコンフィギュレーションデータがロードされる。そして、信号処理ユニット3は、そのコンフィギュレーションデータに基づいて再構成が行われ、処理Cを処理する信号処理回路を実現する。

【0030】

図5(d)において、センサー1からの信号は、処理Cを処理する信号処理ユニット3でも受信する。しかし、信号処理ユニット3による処理3の処理結果データの送信は行わない。

【0031】

図5(e)において、信号処理ユニット3は、処理3の処理結果データのアクチュエータ1への送信を開始する。同時に、信号処理ユニット1の動作を停止させる。

【0032】

このように、冗長な信号処理ユニットを設け、既存の処理を実行中にコンフィギュレーションデータのロードと再構成を行い、データ受信を行わせて、データ送信とともに既存の信号処理ユニットを停止させる。このように再構成を行うことによって、アクチュエータ1へのデータの流れの滞りやデータ不連続点の発生を防止する。

【0033】

[5.信号処理の切り替え方法]それでは、より具体的な信号処理ユニットの処理例について説明する。図4は、その障害物発見時の信号処理の一例を示す。この例では、ある車両が通常運転の時から衝突事故に至るまでの信号処理内容の変移が示されている。簡単のため、信号処理の種類は、走行・制動系、安全系、マルチメディアアプリケーション系の3種類とした。走行・制動系の信号処理には、通常走行のための基本的なエンジン制御、ステアリング制御及びブレーキ制御等がある。安全系の信号処理には、未然に事故を防ぐためのアクティブセーフティ関連制御等がある。マルチメディアアプリケーション(以下、MMAという)系の信号処理には、カーナビゲーションや車内エンタテイメントのためのDVD・ビデオ再生技術やブロードバンドインタネットアクセスのための超高速無線通信技術等のいわゆるマルチメディア信号処理制御がある。

【0034】

図4の左側には信号処理のフローチャートが、右側にはそのときの信号処理ユニット全体の再構成可能演算処理回路のハードウェアリソースに対しての各アプリケーションの使用率が示されている。例えば、5つの信号処理ユニットが3つの信号処理を分担し、その使用率で処理する。もしくは、各信号処理ユニットのそれぞれがその使用率で3つの信号処理を行い、相互に協調制御すると考えてもよい。もしくは、信号処理ユニット1が走行・制動系信号処理を、信号処理ユニット2が安全系信号処理を、信号処理ユニット3がMMA系信号処理を担当し、全体としてその使用率になると考えてもよい。以下にこのフローチャートの説明を行う。

【0035】

通常走行時には、信号処理ユニット全体として、コンフィギュレーションデータ0がロードされている(ステップ40)。コンフィギュレーションデータ0は、カーナビゲーションやインタネット接続のためのMMA系信号処理や、エンジン・ステアリング制御等の走行・制動系信号処理の使用率が比較的使用率高い。また、安全系信号処理は低精度ではあるが、レーダーによる距離測定や障害物監視や白線レーントラッキング等のための画像処理を常に行っている。

【0036】

MMA系信号処理は、GPS、TV・ラジオ、無線LAN・携帯電話のRF・IFアナログ回路からAD変換されたディジタルデータ、または、CD・DVD・HDドライブからのディジタルデータが,ネットワーク2aを経由して,対応する信号処理ユニットに転送された後に、スピーカーやディスプレイ等のユーザI/Fに転送されることによって行われる。

【0037】

安全系信号処理は、図2におけるカメラ、レーザーレーダー、ミリ波レーダーによって検出された外界情報が、ネットワーク2aを経由して、対応する信号処理ユニットに送信されることによって行われる。処理精度は、走行速度に依存し、高速走行の方が低速走行よりも高くなる。

【0038】

いま、TVカメラからの画像上に障害物を検知したと仮定する(ステップ41)。安全系の測定精度を高めた信号処理を実現するコンフィギュレーションデータ1が、ネットワーク2a経由で信号処理ユニットにロードされる。この信号処理ユニットは、詳細な処理を行って(ステップ41)、その障害物に対し対策が必要なのか、または、必要ないのかを判断する(ステップ42)。

【0039】

対策が必要ないと判断されれば、通常走行時の回路使用状況に戻すために、再度コンフィギュレーションメモリからネットワーク2a経由でコンフィギュレーションデータ1が再度ロードされる。

【0040】

対策が必要あると判断されたならば、走行・制御系の信号処理の使用率を増加させて精度を高めた信号処理の組み合わせを実装するコンフィギュレーションデータ2が同様にロードされる(ステップ43)。これにより、ステアリングやブレーキ制御を補強して、ブレーキアシストや横滑り防止制御を起動して衝突を回避させる。このとき、図2における各車輪の速度センサー、加速度センサー、舵角センサーからの信号をネットワーク2a経由で信号処理ユニットに伝送して処理した後、ブレーキ、ステアリング、スロットルのアクチュエータが作動する。そして、コンフィギュレーションデータ2がロードされた信号処理ユニットは、衝突回避可否を判断する(ステップ44)。

【0041】

センサーからの信号によって衝突が回避できたと判明すれば、通常走行時の回路使用状況に戻すために、再度コンフィギュレーションメモリからネットワーク2a経由でコンフィギュレーションデータ1が再度ロードされる。

【0042】

センサーからの信号によって、今後、衝突が回避できないと判断したならば、コンフィギュレーションメモリよりコンフィギュレーションデータ3をロードして、プリクラッシュシステムの信号処理回路を信号処理ユニット上に実現する(ステップ45)。プリクシャッシュシステムを実現する信号処理ユニットがシートベルトモーターを駆動させてシートベルトを巻き取ることによって、乗員が速やかに拘束される。また、その信号処理ユニットがブレーキのアクチュエータを駆動させてブレーキアシストを作動させることによって、衝突速度が低減する。また、その信号処理ユニットによって、エアバックアクチュエータを駆動させてエアバックシステムを作動させることによって、乗員の衝突の衝撃が和らぐ。

【0043】

衝突(ステップ46)後は、コンフィギュレーションデータ4がコンフィギュレーションメモリよりロードされる(ステップ47)。これにより、衝突による故障から免れた信号処理ユニット上に、GPSや無線通信等のMMA系信号処理を実現する回路が実現し、事故現場の位置を測定して、緊急無線通信を行う。

【0044】

したがって、上述の信号処理ユニットの処理例をまとめると、以下のことがいえる。車両では多種多様な信号処理が行われるが、一般的に、全ての信号処理回路の稼働率が必ずしも高くはなく、必要とされる演算精度や時間的精度が必ずしも高くなければならないとも限らない。これらの要求精度は、走行状況によって変動する。

【0045】

例えば、通常走行の場合には、MMA系信号処理やエンジン制御信号処理を優先するために、これらの信号処理には高い精度が要求され、ステアリングやブレーキ制御の安全系信号処理にはそれほどの高い精度は要求されない。一方、センサーによって異常が検出された場合には、優先順位の高い安全系信号処理に高い精度が要求される。

【0046】

したがって、本信号処理の全体の流れは、図1に示されるように、まず、センサーからのセンシングデータの入力によって走行状況を判断し(ステップ10)、現在のハードウェアリソース(使用可能ハードウェア量)情報を取得する(ステップ11)。そして、最適なコンフィギュレーションデータを選択できるように、信号処理機能の演算精度やクロック周波数を変動させる(ステップ12)。具体的には、演算回路のデータビット数を低くして演算回路規模を縮小したり、クロック周波数を低くして演算器の個数を減少したりすることによって、ハードウェアの使用率を下げる。その逆をすることによって、ハードウェア使用率を上げる。そして、図16の対応関係となるように、そのコンフィギュレーションデータが所定の信号処理ユニットにロードされ(ステップ13)、コンフィギュレーションメモリに書き込まれる(ステップ14)。その後、各信号処理ユニットがそれぞれに割り当てられた信号処理を開始する(ステップ15)。

【0047】

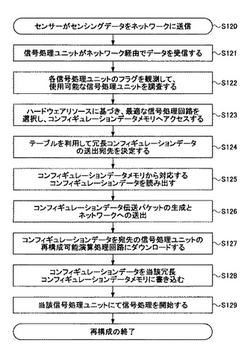

さらに、本発明に基づく再構成可能信号処理システムの全体的な流れは、図12にまとめられる。図2のセンサー群からのセンシングデータがネットワーク2a上に送出されると(ステップ120)、そのデータに対応する処理をする信号処理ユニットがそのデータを受信する(ステップ121)。各信号処理ユニットは、図3のように、お互いのフラグを観測して、使用可能な信号処理ユニットを調査する(ステップ122)。図4のように、ハードウェアリソースに基づき、最適な信号処理回路を選択し、コンフィギュレーションデータメモリにアクセスする(ステップ123)。図16等のテーブルに基づいて、コンフィギュレーションデータの宛先となる信号処理ユニットを決定する(ステップ124)。読み出されたコンフィギュレーションデータは(ステップ125)、図13のパケット構成でネットワーク2aに送出される(ステップ126)。送出されたコンフィギュレーションデータは、宛先の信号処理ユニットの再構成可能演算処理回路にダウンロードされる(ステップ127)。いずれかの信号処理ユニットが故障した場合には、その故障した信号処理ユニットのコンフィギュレーションデータが、冗長な信号処理ユニットの再構成可能演算処理回路にダウンロードされるとともに、その故障した信号処理ユニットが格納していたコンフィギュレーションデータが、冗長な信号処理ユニットのコンフィギュレーションメモリに書き込まれる(ステップ128)。再構成可能演算処理回路にコンフィギュレーションデータがダウンロードされた信号処理ユニットは、信号処理を開始する(ステップ129)。

【0048】

[6.FPGAの内部構成]上述した発明を実現するために必要な、所望の信号処理機能に再構成可能な電子デバイスについて、FPGAを具体例に挙げて、以下説明する。図6は、FPGAの内部構成の一例である。まず、FPGAチップ6aには外部からコンフィギュレーションデータが供給され、コンフィギュレーションデータメモリに書き込まれる。コンフィギュレーションデータメモリは、図6上では図示されていない。コンフィギュレーションデータメモリは、後述するが、FPGAを構成する各ブロックに分散されている。このコンフィギュレーションデータによって各部の機能がプログラムされる。プログラム可能な論理回路ブロックであるCLB(Configurable logic block)6bは、対応するコンフィギュレーションデータによって、ユーザが所望する小規模な論理回路に構成できる。説明をわかりやすくするために、図6では3×3のCLBから構成されるFPGAを示しているが、実際には数十×数十ものCLBが集積される比較的大規模な構成のFPGAもある。

【0049】

IOB(Input/output blocks)6cは、チップ外とチップ内の信号のインターフェース回路であり、一種の電流増幅器でもある。対応するコンフィギュレーションデータによって所定の論理振幅電圧に設定され、外部論理電圧を内部の論理電圧に変換する機能を有する。

【0050】

RC(Routing channel)6dは、各ブロック接続するデータバスである。プログラム可能なスイッチであるCB(Connection block)6eとSB(Switch block)6fはマトリクス状に配置される。CBは、CLBとCLBの間、SBとSBの間及びCLBとIOBの間の接続を行う。SBは、CBとCBの間及びCBとIOBの間の接続を行う。

【0051】

なお、図6ではコンフィギュレーションデータのコンフィギュレーションメモリへの入力と分配を行うハードウェア構成の図示は省略している。

【0052】

図7は、CLBの内部構成の一例を示す。CLBは、4入力1出力のLUT7a,7b、3入力1出力のLUT7c、キャリ生成専用のプログラム可能な論理回路であるCL(Carry logic)7d,7e、9個のマルチプレクサ(7f〜7n)及び2個のレジスタ7o,7pから構成される。CLBはSRAM(Static Random Access Memory)であり、入力はアドレスに相当する。4入力と3入力のLUTには、それぞれ16ビットと8ビットのコンフィギュレーションデータをダウンロードして任意の論理回路を構成することができる。さらに、各マルチプレクサの制御信号を貯えるコンフィギュレーションメモリ7qも具備している。

【0053】

図15は、4入力のLUTの真理値表の一例を示す図である。CLは、対応するコンフィギュレーションデータによって、あらかじめ定義されているいくつかの論理回路の一つを実現できる。また、各マルチプレクサの制御信号もコンフィギュレーションデータによって設定される。種々のコンフィギュレーションデータをCLBに与えることによってレジスタを含む所望の論理回路を実現することができる。

【0054】

図8は、SBの構成例を示す。バス8a,8b,8c,8dはそれぞれ上下左右に配置されている。スイッチ8eは各バスのビット線の交差点に対角線上に配置され、入力は4方向のビット線に接続される。スイッチの4方向からの各ビット線間にトランジスタ8fのソースとドレインが接続されている。ドランジスタのゲートにはコンフィギュレーションメモリのセル8gが接続され、セルに書き込まれた信号によって4方向のビット線のオン・オフ制御を行う。なお、コンフィギュレーションメモリへの入力信号や制御信号の記述は省略している。

【0055】

図9は、CBの構成例を示す。図中、上下に配置されているバス9aはSBに接続されるバスである。交差した左側のバス9bと右側のバス9cはIOB又はCLBに接続されるバスである。スイッチ9dは、各バスのビット線に接続され、各ビット線間にトランジスタ9eのソースとドレインが接続され、そのドランジスタのゲート電圧を制御する信号はコンフィギュレーションメモリのセル9fに書き込まれている。セルの信号によってトランジスタのオン・オフ制御を行う。なお、コンフィギュレーションメモリへ書き込むデータ信号や制御信号の記述は省略している。

【0056】

IOBも同様に、内部のコンフィギュレーションメモリのセルのデータによって、入出力信号の電圧レベル、出力電流の最大値、レジスタの挿入・非挿入等の設定が行われる。

【0057】

以上のように、コンフィギュレーションメモリに所望の回路を実現するデータを書き込むことによって、CB,SB,CLB,IOBに対するプログラムが行われ、所望の仕様の論理回路をFPGA上に実現できる。図2のネットワーク2a経由でコンフィギュレーションデータが図7のコンフィギュレーショメモリへロードされる。回路の再構成時間はその転送時間とメモリの書き込み時間に依存する。リコンフィギュラブルプロセッサの構成においては、コンフィギュレーションメモリを複数用意して、出力を切り替えることによって一瞬に回路を再構成できる。さらに、演算単位も粒度の細かいLUTのみならず、ビット幅の比較的大きい論理または数値演算を行う粒度の荒いプログラマブル演算器も複数用意している場合もある。

【0058】

以上、本発明の好ましい実施例について詳説したが、本発明は、上述した実施例に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施例に種々の変形及び置換を加えることができる。

【0059】

上述の実施例では、車両での適用について詳細な説明をしたが、本発明は、船舶、飛行機及びロボット等にも適用可能である。

【図面の簡単な説明】

【0060】

【図1】本発明の再構成可能信号処理システムの全体的な処理の流れを示す図である。

【図2】本発明の再構成可能信号処理システムを車両用として適用した場合の車両内ネットワークの一構成例を示す図である。

【図3】分散化された信号処理ユニットの車両上での配置の一例である。

【図4】障害物発見時の信号処理の一例である。

【図5】本発明に基づく再構成時に信号処理を連続的に行うためのコンフィギュレーションデータのロード手法の一例である。

【図6】FPGAの構成例を示す図である。

【図7】CLBの内部構成例を示す図である。

【図8】SBの構成例を示す図である。

【図9】CBの構成例を示す図である。

【図10】信号処理ユニット内部の概略構成の一例である。

【図11】信号処理ユニット故障時の復旧のための再構成手法の一例である。

【図12】信号処理ユニットへのコンフィギュレーションデータ伝送手法の一例である。

【図13】ネットワーク伝送用パケットの一構成例である。

【図14】信号処理ユニット内部の一構成例である。

【図15】4入力LUTの真理値表の一例である。

【図16】信号処理ユニットとそのコンフィギュレーションデータが格納されているユニットとの対応テーブルの一例である。

【符号の説明】

【0061】

2a ネットワーク

10a 再構成可能演算処理回路

【技術分野】

【0001】

本発明は、所望の信号処理機能に再構成可能な電子デバイスによるフェール時の機能を提供する再構成可能信号処理システムに関する。

【背景技術】

【0002】

従来から、フェールセーフ機能付き情報処理装置が知られている(例えば、特許文献1)。このフェールセーフ機能付き情報処理装置は、情報処理回路が故障した場合、その故障した情報処理回路に対応する再構成情報(構成データ)に基づいて、その故障した情報処理回路の機能がFPGA(Field programmable gate arrays)等の再構成可能な電子デバイス上に再現される。

【特許文献1】特開2000−81991号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、上述の従来技術では、構成データを記憶する記憶部が故障等の原因によって再構成情報の読み出しができなくなった場合、故障した情報処理回路の機能が再構成可能な電子デバイス上に再現することができなくなり、フェールセーフ機能を十分に発揮できない。

【0004】

そこで、本発明は、故障に対する信頼性を高めた再構成可能信号処理システムの提供を目的とする。

【課題を解決するための手段】

【0005】

上記課題を解決するため、本発明の一局面によれば、

所定の信号処理機能を有する信号処理ユニットと、

所望の信号処理機能に再構成可能な電子デバイスと、

前記信号処理ユニットの故障を検出する故障検出手段と、

前記電子デバイスを前記信号処理ユニットの信号処理機能に再構成する構成データを記憶する記憶手段とを備え、

前記記憶手段に記憶された構成データに基づいて前記故障検出手段により故障が検出された前記信号処理ユニットの信号処理機能に前記電子デバイスを再構成する再構成可能信号処理システムにおいて、

前記信号処理ユニットと前記電子デバイスとを含むネットワーク上に前記記憶手段を少なくとも2つ以上分散させたことを特徴とする再構成可能信号処理システムが提供される。

本局面によれば、ある信号処理ユニットが故障したとしても、再構成可能な電子デバイスをネットワーク上に少なくとも2つ以上分散させた構成データのいずれかを用いてその故障した信号処理ユニットの信号処理機能に再構成することができるので、システム全体の継続動作が可能となり故障に対する信頼性を高めることができる。

【発明の効果】

【0006】

本発明によれば、故障に対する信頼性を高めることができる。

【発明を実施するための最良の形態】

【0007】

以下、図面を参照して、本発明を実施するための最良の形態の説明を行う。

【0008】

[1.本システムの構成]図2は、本発明の再構成可能信号処理システムを車両用として適用した場合の車両内ネットワークの一構成例を示す図である。図2の左上には放送受信や無線通信を行うためのアナログ回路が示され、図2の左下には画像、距離、車両速度及び加速度等を測定するためのセンサー群が示されている。また、各部のアナログ信号をディジタルデータに変換するアナログディジタルコンバータ(ADC)とネットワーク2aに接続するインターフェース(I/F)が接続されている。なお、無線通信用のアナログ回路には、ネットワーク2aからのディジタルデータをアナログ信号に変換するディジタルアナログコンバータ(DAC)も具備する。

【0009】

また、カーナビゲーション、インタネットのウェブ閲覧、AV(オーディオ・ビデオ)再生及びゲーム等のマルチメディア信号処理のため、CD、DVD及びHD(ハードディスク)のドライブがネットワーク2aに接続されている。さらに、ユーザインターフェースのためのディスプレイやキーボード等の入出力装置もネットワーク2aに接続されている。

【0010】

図2の右下には、ブレーキ、ステアリング及びエンジン等の車両の主要な機械的機能を作動させるアクチュエータが、I/FとDACを介してネットワーク2aに接続されている。また、エアバックやシートベルト等のプリクラッシュシステムの機械的機能を作動させるモータやアクチュエータが、同様に接続されている。

【0011】

また、信号処理ユニット1〜Npがネットワーク2aに接続されている。ネットワーク2aへの接続方法は、車両の各部に分散するようにしている。図3(a)は、7個の信号処理ユニットが車両の各部に分散してネットワーク2a上に位置していることを示す一例である。各信号処理ユニット内部の概略構成の一例を図10に示す。図10では、信号処理ユニットは、再構成可能演算処理回路10aと2個のコンフィギュレーションデータメモリから構成される。再構成可能信号処理回路10aは、FPGAまたはリコンフィギュラブルプロセッサから構成される。FPGA、リコンフィギュラブルプロセッサ及びコンフィギュレーションデータについて、以下の[2.FPGAについて]で説明する。

【0012】

[2.FPGAについて]FPGAのようなプログラマブルな論理回路が、近年普及しつつある。詳細な内部構成は以下の「6.FPGAの内部構成」において記載するが、FPGAは、多数のLUT(Look-up table)とスイッチがチップ上に集積されており、LUTのデータとスイッチ制御情報を外部から書き込むことによって論理回路の再構成が行われ、プロセッサを含む所望の演算処理回路を実現することができる半導体デバイスである。このデバイスを用いれば、信号処理アルゴリズムを高速に且つ最小遅延時間で実行する最適構造の演算処理回路を構築できる。

【0013】

LUTに記憶するデータやスイッチ制御情報等の書き込まれるプログラムは、コンフィギュレーションデータ(構成データ)と呼ばれる。一般的にコンフィギュレーションデータを外部から書き込むためには多数の動作クロックサイクルが必要であるが、最近ではリコンフィギュラブルプロセッサと呼ばれるコンフィギュレーションデータを数クロックで短時間に書き込みと再構成ができる半導体も開発されている。

【0014】

「3.再構成可能信号処理ユニットの構成と故障時の復旧アルゴリズム」ここでは、ある信号処理ユニットが故障した場合に、故障した信号処理ユニットで実行していた演算回路を他の正常な信号処理ユニットに移動する手法について説明する。上述したように、信号処理ユニットは車両の各部に分散しており(図3)、各信号処理ユニットは再構成可能演算処理回路10aと2個のコンフィギュレーションデータメモリから構成される(図10)。

【0015】

ある信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータは別の場所に配置された他の2個の信号処理ユニットのコンフィギュレーションデータメモリに書き込まれている。その対応を図16に示す。ユニットのID番号とは、再構成可能演算処理回路10aの実装されている信号処理ユニットの番号である。例えば、1番の信号処理ユニットの再構成可能演算処理回路10aへロードするコンフィギュレーションデータは、2番と6番の信号処理ユニットのコンフィギュレーションデータメモリに格納されている。

【0016】

信号処理ユニットが故障した場合の復旧の方法について図11を参照しながら説明する。いま、3番の信号処理ユニットが故障したとする。3番の信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータが格納されている2番及び4番の信号処理ユニットが(図16)、3番の信号処理ユニットの故障を検出する。2番及び4番の信号処理ユニットは、3番の信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータをコンフィギュレーションデータメモリより読み出す。2番及び4番の信号処理ユニットは、読み出したコンフィギュレーションデータを7番の信号処理ユニットにネットワーク2aを経由して伝送することによって、その7番の信号処理ユニット内の再構成可能演算処理回路10a上に3番と同一の信号処理回路が再構成する。したがって、故障した3番の信号処理ユニットで行われていた信号処理は、7番の信号処理ユニットで継続して実行されることになる。また、3番の信号処理ユニットが故障したので、6番の信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータが格納されている信号処理ユニットが、2番の信号処理ユニットだけとなり一つ減ってしまう。そこで、7番のコンフィギュレーションメモリに、6番の信号処理ユニットの再構成可能演算処理回路10aのコンフィギュレーションデータを格納することによって、故障により一つ減ってしまった状況を回復することができる。なお、7番の信号処理ユニットは、信号処理機能を持たない冗長の信号処理ユニットとして、予めネットワーク2a上に接続されているものである。

【0017】

また、故障を検出する信号処理ユニットは、特に限定しない。例えば、6番の信号処理ユニットが、3番の信号処理ユニットの故障を検出するとともに、2番及び4番の信号処理ユニットに対し3番のコンフィギュレーションデータを7番の信号処理ユニットに伝送する指令を出すようにしてもよい。

【0018】

また、上述の例では、自身のコンフィギュレーションデータが格納されているユニットの数は2個にしていた(以下、「多重化数を2にする」という)。この多重化数は、車両の走行方向と各信号処理ユニットの配置に基づいて決定される。車両が前方に走行していれば、車両フロント部に配置された信号処理ユニットは、衝突等により破損・故障する確率が高くなる。そこで、車両フロント部に配置された信号処理ユニットのコンフィギュレーションデータが格納されている信号処理ユニットの数を多くすることによって、衝突等による破損・故障に対する信頼性を向上させることができる。逆に、車両リヤ部に配置された信号処理ユニットに対しては、多重化数を減らすことも可能である。また、少なくとも2つ以上分散させておくことによって、1つのコンフィギュレーションデータメモリが故障したとしても、少なくとももう一つは残っているので、故障に対する信頼性も向上する。

【0019】

また、信号処理ユニットとその信号処理ユニットのコンフィギュレーションデータが格納されている信号処理ユニットとの位置関係は、できるだけ離したほうがよい。衝突等によって、それらが両方とも破損・故障してしまうことを避けるためである。例えば、車両フロント部に配置された2番の信号処理ユニットのコンフィギュレーションデータは、車両中間部に配置された5番及び車両リヤ部に配置された6番の信号処理ユニットに格納されている。

【0020】

ところで、コンフィギュレーションデータをロードする前に、信号処理ユニットが正常かどうかの検査が行われる。信号処理ユニットの故障診断は、自立分散的に行われ、自らが自己診断機能を有している。再構成可能演算処理回路10aにテスト用コンフィギュレーションデータをロードする。その回路10aに対し外部から入力信号を加えて、または、回路内部で信号を発生させて、所定の参照信号と比較して一致すれば、その再構成可能演算処理回路10aは正常と判断し、図3(b)に示されるように、フラグに“OK”と表示する。一方、不一致ならば故障と判断して、フラグに“NG”を表示する。“OK”と表示されたフラグを有する信号処理ユニットに対して、コンフィギュレーションデータがロードされると、そのフラグの表示は“BUSY”に変わる。また、自己診断機能が故障していた場合には、“NG”と表示する。このようにすることによって、どの信号処理ユニットが故障しているか否か(“OK”か“NG”)、使用可能か否か(“OK”か“BUSY”)を判別することができる。なお、正常であった場合はそのユニットにロードを行い、正常でなかった場合は正常なものが見つかるまで、他のユニットのフラグを検査する。

【0021】

上記のようなネットワーク2a上を伝送するコンフィギュレーションデータやフラグ情報は、図13で示されるネットワーク伝送用パケットで伝送する。宛先アドレスは、宛先の信号処理ユニットのIDアドレス(図16にあるような信号処理ユニットのID番号)、その信号処理ユニット内部の再構成可能演算処理回路10aのIDアドレス及びその回路内の演算要素(加算器等)のIDアドレスから構成される。送信元アドレスも、送信元の信号処理ユニットに関して、上記の宛先アドレスと同様の構成である。データ部は、図2のセンサー群からの出力データ、演算結果の演算用データまたはコンフィギュレーションデータ等である。信頼性を向上させるためにCRC(Cyclic redundancy checksum)が付加される。

【0022】

ネットワーク2aから信号処理ユニットに伝送されたパケットは、以下のように信号処理ユニット内で信号処理される。図14は、信号処理ユニットの構成の一例を示す図である。パケット分解部14aは、ネットワーク2aから伝送されたパケットの解析を行い、コンフィギュレーションデータ、演算入力データ若しくは読み取ったフラグの情報なのかを判別する。コンフィギュレーションデータならば、再構成可能演算処理回路14h(10a)にダウンロードを行う。演算入力データならば、その再構成された演算処理回路14hに演算データとして入力される。フラグならば、フラグ変化検出回路14iに入力される。フラグの変化によって他の信号処理ユニットが故障したことが判定される。

【0023】

パケット分解部14aを介したデータは、テーブル14に規定された対応関係に従って、マルチプレクサDMUX14dを介して、再構成可能演算処理回路14hやコンフィギュレーションデータメモリ等に出力される。コンフィギュレーションデータメモリは、NCM個分用意される。なお、NCMは多重化数を表す。他の信号処理ユニットの故障が検出された場合には、再構成可能演算処理回路10aによる演算結果データとコンフィギュレーションデータメモリからその故障した信号処理ユニットに対応するコンフィギュレーションデータが読み出される。読み出されたそれらのデータは、マルチプレクサMUX14eを経由した後に、パケット生成部14cによって生成された図13のデータパケットでネットワーク2aに送出される。

【0024】

再構成可能演算処理回路10aの検査は、まず、テスト信号発生回路を構成するためのコンフィギュレーションデータをテスト回路14fからロードする。そして、構成されたテスト信号発生回路から出力されたデータをテスト回路14f内の参照データと比較することによって、故障しているかどうかが判定される。その結果をフラグレジスタに設定する。

【0025】

[4.コンフィギュレーションデータのダウンロード手法]コンフィギュレーションデータを再構成可能演算処理回路10aにダウンロードすることによって、所望の回路が実現されるが、一般的なFPGAの場合、コンフィギュレーションデータのダウンロードが完了するまでにデータのビット数に依存したクロック数分の時間がかかる。たとえ1クロックで瞬時にダウンロードと再構成が完了して演算回路が切り替わったと仮定しても、ディジタル信号処理で頻繁に使用されるFIRフィルタは過去のデータを現在の出力の計算に使用するために、過去の入力データをコンフィギュレーションメモリに記憶させておく必要がある。したがって、新しく再構成が行われた直後の回路状態ではアクチュエータ等に対して送るべき出力データがしばらく現れない現象が発生する。それを解決するのが以下の手法である。

【0026】

図5は、本ダウンロード手法の一例を示す図である。簡単のために、2個のセンサー1,2、各センサーに対応する信号処理ユニット1,2若しくはアクチュエータ1,2、未使用の信号処理ユニット3及びネットワーク2aから構成される。

【0027】

図5(a)は、新しいコンフィギュレーションデータをロードする前の状態である。センサー1からの信号は、処理Aを処理する信号処理回路が搭載されている信号処理ユニット1に伝送される。信号処理ユニット1による処理Aの結果が、アクチュエータ1に伝送されて駆動する。センサー2、処理Bを処理する信号処理ユニット2及びアクチュエータ2も同様にデータが伝送される。未使用の信号処理ユニット3はネットワーク2aと制御信号の授受を行うが、データの授受を行わない。

【0028】

いま、センサー1による信号検出からアクチュエータ1の駆動までの上記の処理Aを処理Cに代える場合について説明する。図5(b)において、まず、信号処理ユニット1または2が、未使用の信号処理ユニット3に対して、起動制御信号を伝送する。

【0029】

図5(c)において、信号処理ユニット3に対して、図16のテーブルに従って、信号処理ユニット2(もしくは、(図5上には記載していないが)信号処理ユニット4)からコンフィギュレーションデータがロードされる。そして、信号処理ユニット3は、そのコンフィギュレーションデータに基づいて再構成が行われ、処理Cを処理する信号処理回路を実現する。

【0030】

図5(d)において、センサー1からの信号は、処理Cを処理する信号処理ユニット3でも受信する。しかし、信号処理ユニット3による処理3の処理結果データの送信は行わない。

【0031】

図5(e)において、信号処理ユニット3は、処理3の処理結果データのアクチュエータ1への送信を開始する。同時に、信号処理ユニット1の動作を停止させる。

【0032】

このように、冗長な信号処理ユニットを設け、既存の処理を実行中にコンフィギュレーションデータのロードと再構成を行い、データ受信を行わせて、データ送信とともに既存の信号処理ユニットを停止させる。このように再構成を行うことによって、アクチュエータ1へのデータの流れの滞りやデータ不連続点の発生を防止する。

【0033】

[5.信号処理の切り替え方法]それでは、より具体的な信号処理ユニットの処理例について説明する。図4は、その障害物発見時の信号処理の一例を示す。この例では、ある車両が通常運転の時から衝突事故に至るまでの信号処理内容の変移が示されている。簡単のため、信号処理の種類は、走行・制動系、安全系、マルチメディアアプリケーション系の3種類とした。走行・制動系の信号処理には、通常走行のための基本的なエンジン制御、ステアリング制御及びブレーキ制御等がある。安全系の信号処理には、未然に事故を防ぐためのアクティブセーフティ関連制御等がある。マルチメディアアプリケーション(以下、MMAという)系の信号処理には、カーナビゲーションや車内エンタテイメントのためのDVD・ビデオ再生技術やブロードバンドインタネットアクセスのための超高速無線通信技術等のいわゆるマルチメディア信号処理制御がある。

【0034】

図4の左側には信号処理のフローチャートが、右側にはそのときの信号処理ユニット全体の再構成可能演算処理回路のハードウェアリソースに対しての各アプリケーションの使用率が示されている。例えば、5つの信号処理ユニットが3つの信号処理を分担し、その使用率で処理する。もしくは、各信号処理ユニットのそれぞれがその使用率で3つの信号処理を行い、相互に協調制御すると考えてもよい。もしくは、信号処理ユニット1が走行・制動系信号処理を、信号処理ユニット2が安全系信号処理を、信号処理ユニット3がMMA系信号処理を担当し、全体としてその使用率になると考えてもよい。以下にこのフローチャートの説明を行う。

【0035】

通常走行時には、信号処理ユニット全体として、コンフィギュレーションデータ0がロードされている(ステップ40)。コンフィギュレーションデータ0は、カーナビゲーションやインタネット接続のためのMMA系信号処理や、エンジン・ステアリング制御等の走行・制動系信号処理の使用率が比較的使用率高い。また、安全系信号処理は低精度ではあるが、レーダーによる距離測定や障害物監視や白線レーントラッキング等のための画像処理を常に行っている。

【0036】

MMA系信号処理は、GPS、TV・ラジオ、無線LAN・携帯電話のRF・IFアナログ回路からAD変換されたディジタルデータ、または、CD・DVD・HDドライブからのディジタルデータが,ネットワーク2aを経由して,対応する信号処理ユニットに転送された後に、スピーカーやディスプレイ等のユーザI/Fに転送されることによって行われる。

【0037】

安全系信号処理は、図2におけるカメラ、レーザーレーダー、ミリ波レーダーによって検出された外界情報が、ネットワーク2aを経由して、対応する信号処理ユニットに送信されることによって行われる。処理精度は、走行速度に依存し、高速走行の方が低速走行よりも高くなる。

【0038】

いま、TVカメラからの画像上に障害物を検知したと仮定する(ステップ41)。安全系の測定精度を高めた信号処理を実現するコンフィギュレーションデータ1が、ネットワーク2a経由で信号処理ユニットにロードされる。この信号処理ユニットは、詳細な処理を行って(ステップ41)、その障害物に対し対策が必要なのか、または、必要ないのかを判断する(ステップ42)。

【0039】

対策が必要ないと判断されれば、通常走行時の回路使用状況に戻すために、再度コンフィギュレーションメモリからネットワーク2a経由でコンフィギュレーションデータ1が再度ロードされる。

【0040】

対策が必要あると判断されたならば、走行・制御系の信号処理の使用率を増加させて精度を高めた信号処理の組み合わせを実装するコンフィギュレーションデータ2が同様にロードされる(ステップ43)。これにより、ステアリングやブレーキ制御を補強して、ブレーキアシストや横滑り防止制御を起動して衝突を回避させる。このとき、図2における各車輪の速度センサー、加速度センサー、舵角センサーからの信号をネットワーク2a経由で信号処理ユニットに伝送して処理した後、ブレーキ、ステアリング、スロットルのアクチュエータが作動する。そして、コンフィギュレーションデータ2がロードされた信号処理ユニットは、衝突回避可否を判断する(ステップ44)。

【0041】

センサーからの信号によって衝突が回避できたと判明すれば、通常走行時の回路使用状況に戻すために、再度コンフィギュレーションメモリからネットワーク2a経由でコンフィギュレーションデータ1が再度ロードされる。

【0042】

センサーからの信号によって、今後、衝突が回避できないと判断したならば、コンフィギュレーションメモリよりコンフィギュレーションデータ3をロードして、プリクラッシュシステムの信号処理回路を信号処理ユニット上に実現する(ステップ45)。プリクシャッシュシステムを実現する信号処理ユニットがシートベルトモーターを駆動させてシートベルトを巻き取ることによって、乗員が速やかに拘束される。また、その信号処理ユニットがブレーキのアクチュエータを駆動させてブレーキアシストを作動させることによって、衝突速度が低減する。また、その信号処理ユニットによって、エアバックアクチュエータを駆動させてエアバックシステムを作動させることによって、乗員の衝突の衝撃が和らぐ。

【0043】

衝突(ステップ46)後は、コンフィギュレーションデータ4がコンフィギュレーションメモリよりロードされる(ステップ47)。これにより、衝突による故障から免れた信号処理ユニット上に、GPSや無線通信等のMMA系信号処理を実現する回路が実現し、事故現場の位置を測定して、緊急無線通信を行う。

【0044】

したがって、上述の信号処理ユニットの処理例をまとめると、以下のことがいえる。車両では多種多様な信号処理が行われるが、一般的に、全ての信号処理回路の稼働率が必ずしも高くはなく、必要とされる演算精度や時間的精度が必ずしも高くなければならないとも限らない。これらの要求精度は、走行状況によって変動する。

【0045】

例えば、通常走行の場合には、MMA系信号処理やエンジン制御信号処理を優先するために、これらの信号処理には高い精度が要求され、ステアリングやブレーキ制御の安全系信号処理にはそれほどの高い精度は要求されない。一方、センサーによって異常が検出された場合には、優先順位の高い安全系信号処理に高い精度が要求される。

【0046】

したがって、本信号処理の全体の流れは、図1に示されるように、まず、センサーからのセンシングデータの入力によって走行状況を判断し(ステップ10)、現在のハードウェアリソース(使用可能ハードウェア量)情報を取得する(ステップ11)。そして、最適なコンフィギュレーションデータを選択できるように、信号処理機能の演算精度やクロック周波数を変動させる(ステップ12)。具体的には、演算回路のデータビット数を低くして演算回路規模を縮小したり、クロック周波数を低くして演算器の個数を減少したりすることによって、ハードウェアの使用率を下げる。その逆をすることによって、ハードウェア使用率を上げる。そして、図16の対応関係となるように、そのコンフィギュレーションデータが所定の信号処理ユニットにロードされ(ステップ13)、コンフィギュレーションメモリに書き込まれる(ステップ14)。その後、各信号処理ユニットがそれぞれに割り当てられた信号処理を開始する(ステップ15)。

【0047】

さらに、本発明に基づく再構成可能信号処理システムの全体的な流れは、図12にまとめられる。図2のセンサー群からのセンシングデータがネットワーク2a上に送出されると(ステップ120)、そのデータに対応する処理をする信号処理ユニットがそのデータを受信する(ステップ121)。各信号処理ユニットは、図3のように、お互いのフラグを観測して、使用可能な信号処理ユニットを調査する(ステップ122)。図4のように、ハードウェアリソースに基づき、最適な信号処理回路を選択し、コンフィギュレーションデータメモリにアクセスする(ステップ123)。図16等のテーブルに基づいて、コンフィギュレーションデータの宛先となる信号処理ユニットを決定する(ステップ124)。読み出されたコンフィギュレーションデータは(ステップ125)、図13のパケット構成でネットワーク2aに送出される(ステップ126)。送出されたコンフィギュレーションデータは、宛先の信号処理ユニットの再構成可能演算処理回路にダウンロードされる(ステップ127)。いずれかの信号処理ユニットが故障した場合には、その故障した信号処理ユニットのコンフィギュレーションデータが、冗長な信号処理ユニットの再構成可能演算処理回路にダウンロードされるとともに、その故障した信号処理ユニットが格納していたコンフィギュレーションデータが、冗長な信号処理ユニットのコンフィギュレーションメモリに書き込まれる(ステップ128)。再構成可能演算処理回路にコンフィギュレーションデータがダウンロードされた信号処理ユニットは、信号処理を開始する(ステップ129)。

【0048】

[6.FPGAの内部構成]上述した発明を実現するために必要な、所望の信号処理機能に再構成可能な電子デバイスについて、FPGAを具体例に挙げて、以下説明する。図6は、FPGAの内部構成の一例である。まず、FPGAチップ6aには外部からコンフィギュレーションデータが供給され、コンフィギュレーションデータメモリに書き込まれる。コンフィギュレーションデータメモリは、図6上では図示されていない。コンフィギュレーションデータメモリは、後述するが、FPGAを構成する各ブロックに分散されている。このコンフィギュレーションデータによって各部の機能がプログラムされる。プログラム可能な論理回路ブロックであるCLB(Configurable logic block)6bは、対応するコンフィギュレーションデータによって、ユーザが所望する小規模な論理回路に構成できる。説明をわかりやすくするために、図6では3×3のCLBから構成されるFPGAを示しているが、実際には数十×数十ものCLBが集積される比較的大規模な構成のFPGAもある。

【0049】

IOB(Input/output blocks)6cは、チップ外とチップ内の信号のインターフェース回路であり、一種の電流増幅器でもある。対応するコンフィギュレーションデータによって所定の論理振幅電圧に設定され、外部論理電圧を内部の論理電圧に変換する機能を有する。

【0050】

RC(Routing channel)6dは、各ブロック接続するデータバスである。プログラム可能なスイッチであるCB(Connection block)6eとSB(Switch block)6fはマトリクス状に配置される。CBは、CLBとCLBの間、SBとSBの間及びCLBとIOBの間の接続を行う。SBは、CBとCBの間及びCBとIOBの間の接続を行う。

【0051】

なお、図6ではコンフィギュレーションデータのコンフィギュレーションメモリへの入力と分配を行うハードウェア構成の図示は省略している。

【0052】

図7は、CLBの内部構成の一例を示す。CLBは、4入力1出力のLUT7a,7b、3入力1出力のLUT7c、キャリ生成専用のプログラム可能な論理回路であるCL(Carry logic)7d,7e、9個のマルチプレクサ(7f〜7n)及び2個のレジスタ7o,7pから構成される。CLBはSRAM(Static Random Access Memory)であり、入力はアドレスに相当する。4入力と3入力のLUTには、それぞれ16ビットと8ビットのコンフィギュレーションデータをダウンロードして任意の論理回路を構成することができる。さらに、各マルチプレクサの制御信号を貯えるコンフィギュレーションメモリ7qも具備している。

【0053】

図15は、4入力のLUTの真理値表の一例を示す図である。CLは、対応するコンフィギュレーションデータによって、あらかじめ定義されているいくつかの論理回路の一つを実現できる。また、各マルチプレクサの制御信号もコンフィギュレーションデータによって設定される。種々のコンフィギュレーションデータをCLBに与えることによってレジスタを含む所望の論理回路を実現することができる。

【0054】

図8は、SBの構成例を示す。バス8a,8b,8c,8dはそれぞれ上下左右に配置されている。スイッチ8eは各バスのビット線の交差点に対角線上に配置され、入力は4方向のビット線に接続される。スイッチの4方向からの各ビット線間にトランジスタ8fのソースとドレインが接続されている。ドランジスタのゲートにはコンフィギュレーションメモリのセル8gが接続され、セルに書き込まれた信号によって4方向のビット線のオン・オフ制御を行う。なお、コンフィギュレーションメモリへの入力信号や制御信号の記述は省略している。

【0055】

図9は、CBの構成例を示す。図中、上下に配置されているバス9aはSBに接続されるバスである。交差した左側のバス9bと右側のバス9cはIOB又はCLBに接続されるバスである。スイッチ9dは、各バスのビット線に接続され、各ビット線間にトランジスタ9eのソースとドレインが接続され、そのドランジスタのゲート電圧を制御する信号はコンフィギュレーションメモリのセル9fに書き込まれている。セルの信号によってトランジスタのオン・オフ制御を行う。なお、コンフィギュレーションメモリへ書き込むデータ信号や制御信号の記述は省略している。

【0056】

IOBも同様に、内部のコンフィギュレーションメモリのセルのデータによって、入出力信号の電圧レベル、出力電流の最大値、レジスタの挿入・非挿入等の設定が行われる。

【0057】

以上のように、コンフィギュレーションメモリに所望の回路を実現するデータを書き込むことによって、CB,SB,CLB,IOBに対するプログラムが行われ、所望の仕様の論理回路をFPGA上に実現できる。図2のネットワーク2a経由でコンフィギュレーションデータが図7のコンフィギュレーショメモリへロードされる。回路の再構成時間はその転送時間とメモリの書き込み時間に依存する。リコンフィギュラブルプロセッサの構成においては、コンフィギュレーションメモリを複数用意して、出力を切り替えることによって一瞬に回路を再構成できる。さらに、演算単位も粒度の細かいLUTのみならず、ビット幅の比較的大きい論理または数値演算を行う粒度の荒いプログラマブル演算器も複数用意している場合もある。

【0058】

以上、本発明の好ましい実施例について詳説したが、本発明は、上述した実施例に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施例に種々の変形及び置換を加えることができる。

【0059】

上述の実施例では、車両での適用について詳細な説明をしたが、本発明は、船舶、飛行機及びロボット等にも適用可能である。

【図面の簡単な説明】

【0060】

【図1】本発明の再構成可能信号処理システムの全体的な処理の流れを示す図である。

【図2】本発明の再構成可能信号処理システムを車両用として適用した場合の車両内ネットワークの一構成例を示す図である。

【図3】分散化された信号処理ユニットの車両上での配置の一例である。

【図4】障害物発見時の信号処理の一例である。

【図5】本発明に基づく再構成時に信号処理を連続的に行うためのコンフィギュレーションデータのロード手法の一例である。

【図6】FPGAの構成例を示す図である。

【図7】CLBの内部構成例を示す図である。

【図8】SBの構成例を示す図である。

【図9】CBの構成例を示す図である。

【図10】信号処理ユニット内部の概略構成の一例である。

【図11】信号処理ユニット故障時の復旧のための再構成手法の一例である。

【図12】信号処理ユニットへのコンフィギュレーションデータ伝送手法の一例である。

【図13】ネットワーク伝送用パケットの一構成例である。

【図14】信号処理ユニット内部の一構成例である。

【図15】4入力LUTの真理値表の一例である。

【図16】信号処理ユニットとそのコンフィギュレーションデータが格納されているユニットとの対応テーブルの一例である。

【符号の説明】

【0061】

2a ネットワーク

10a 再構成可能演算処理回路

【特許請求の範囲】

【請求項1】

所定の信号処理機能を有する信号処理ユニットと、

所望の信号処理機能に再構成可能な電子デバイスと、

前記信号処理ユニットの故障を検出する故障検出手段と、

前記電子デバイスを前記信号処理ユニットの信号処理機能に再構成する構成データを記憶する記憶手段とを備え、

前記記憶手段に記憶された構成データに基づいて前記故障検出手段により故障が検出された前記信号処理ユニットの信号処理機能に前記電子デバイスを再構成する再構成可能信号処理システムにおいて、

前記信号処理ユニットと前記電子デバイスとを含むネットワーク上に前記記憶手段を少なくとも2つ以上分散させたことを特徴とする再構成可能信号処理システム。

【請求項2】

前記ネットワーク上の車両フロント部分に配置された信号処理ユニットの信号処理機能に再構成する構成データを記憶する記憶手段の数は、前記ネットワーク上の車両リヤ部分に配置された信号処理ユニットの信号処理機能に再構成する構成データを記憶する記憶手段の数よりも多い請求項1記載の再構成可能信号処理システム。

【請求項3】

前記電子デバイスのハードウェアリソースに基づいて前記所定の信号処理機能の演算精度を変更する演算精度変更手段を備える請求項1記載の再構成可能信号処理システム。

【請求項4】

前記電子デバイスのハードウェアリソースに基づいて前記所定の信号処理機能のクロック周波数を変更するクロック周波数変更手段を備える請求項1記載の再構成可能信号処理システム。

【請求項5】

前記電子デバイスを再構成する構成データは、車両の走行状況と前記電子デバイスのハードウェアリソースとに基づいて変更する請求項1記載の再構成可能信号処理システム。

【請求項6】

前記故障検出手段は、更に、前記電子デバイスの故障有無を検出し、

前記故障検出手段により前記電子デバイスの故障が無いと検出された後に、該電子デバイスの再構成を行う請求項1記載の再構成可能信号処理システム。

【請求項1】

所定の信号処理機能を有する信号処理ユニットと、

所望の信号処理機能に再構成可能な電子デバイスと、

前記信号処理ユニットの故障を検出する故障検出手段と、

前記電子デバイスを前記信号処理ユニットの信号処理機能に再構成する構成データを記憶する記憶手段とを備え、

前記記憶手段に記憶された構成データに基づいて前記故障検出手段により故障が検出された前記信号処理ユニットの信号処理機能に前記電子デバイスを再構成する再構成可能信号処理システムにおいて、

前記信号処理ユニットと前記電子デバイスとを含むネットワーク上に前記記憶手段を少なくとも2つ以上分散させたことを特徴とする再構成可能信号処理システム。

【請求項2】

前記ネットワーク上の車両フロント部分に配置された信号処理ユニットの信号処理機能に再構成する構成データを記憶する記憶手段の数は、前記ネットワーク上の車両リヤ部分に配置された信号処理ユニットの信号処理機能に再構成する構成データを記憶する記憶手段の数よりも多い請求項1記載の再構成可能信号処理システム。

【請求項3】

前記電子デバイスのハードウェアリソースに基づいて前記所定の信号処理機能の演算精度を変更する演算精度変更手段を備える請求項1記載の再構成可能信号処理システム。

【請求項4】

前記電子デバイスのハードウェアリソースに基づいて前記所定の信号処理機能のクロック周波数を変更するクロック周波数変更手段を備える請求項1記載の再構成可能信号処理システム。

【請求項5】

前記電子デバイスを再構成する構成データは、車両の走行状況と前記電子デバイスのハードウェアリソースとに基づいて変更する請求項1記載の再構成可能信号処理システム。

【請求項6】

前記故障検出手段は、更に、前記電子デバイスの故障有無を検出し、

前記故障検出手段により前記電子デバイスの故障が無いと検出された後に、該電子デバイスの再構成を行う請求項1記載の再構成可能信号処理システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2006−155176(P2006−155176A)

【公開日】平成18年6月15日(2006.6.15)

【国際特許分類】

【出願番号】特願2004−344064(P2004−344064)

【出願日】平成16年11月29日(2004.11.29)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【出願人】(502087460)株式会社トヨタIT開発センター (232)

【Fターム(参考)】

【公開日】平成18年6月15日(2006.6.15)

【国際特許分類】

【出願日】平成16年11月29日(2004.11.29)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【出願人】(502087460)株式会社トヨタIT開発センター (232)

【Fターム(参考)】

[ Back to top ]