出力遮断回路および電子機器

【課題】 簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる出力遮断回路および電子機器を提供する。

【解決手段】 時刻t1に負荷が地絡し、出力電流Ioutが増大すると、電流検出用抵抗Rsでの電圧降下が増加し、トランジスタQ2がオンとなる。トランジスタQ2は、直流電源11から供給される電流をコレクタ電流Icとしてゲート抵抗Rgに流し、ゲート電圧VGを上昇させ、出力電流Ioutを制限電流値Ilimで制限する。ゲート抵抗Rgを流れる電流の一部がタイマ用コンデンサC1を充電し、トランジスタQ3のベース電圧が上昇すると、トランジスタQ3はオンになる。トランジスタQ3がオンになると、トランジスタQ2はフルオン状態となり、トランジスタQ1のゲートソース間の電圧がほぼ0Vとなり、トランジスタQ1はオフし、シャットダウン状態となる。

【解決手段】 時刻t1に負荷が地絡し、出力電流Ioutが増大すると、電流検出用抵抗Rsでの電圧降下が増加し、トランジスタQ2がオンとなる。トランジスタQ2は、直流電源11から供給される電流をコレクタ電流Icとしてゲート抵抗Rgに流し、ゲート電圧VGを上昇させ、出力電流Ioutを制限電流値Ilimで制限する。ゲート抵抗Rgを流れる電流の一部がタイマ用コンデンサC1を充電し、トランジスタQ3のベース電圧が上昇すると、トランジスタQ3はオンになる。トランジスタQ3がオンになると、トランジスタQ2はフルオン状態となり、トランジスタQ1のゲートソース間の電圧がほぼ0Vとなり、トランジスタQ1はオフし、シャットダウン状態となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、過電流に対して電源回路を保護する出力遮断回路および電子機器に関する。

【背景技術】

【0002】

図1は、従来の技術による出力遮断回路9を備える電源回路90の回路構成を示す図である。電源回路90は、直流電源11と出力部13との間に、出力遮断回路9の電流検出用抵抗素子(以下「抵抗素子」を単に「抵抗」という)Rsと、PチャネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor:以下単に「トランジスタ」という)Q1からなるスイッチ回路とがこの順序で設けられている。

【0003】

トランジスタQ1は、ソースが電流検出用抵抗Rsに接続され、ドレインが出力部13、および一端が接地されているコンデンサCoutの他端に接続され、ゲートがゲート抵抗を介して接地されている。出力部13には、図示しない負荷が接続されている。トランジスタQ1に過電流が流れていない状態、つまり出力遮断回路9が働いていない状態では、トランジスタQ1のゲート電圧VGは、ほぼグランドレベルになっており、トランジスタQ1を導通状態にしているが、ゲート電流は、ほぼゼロである。

【0004】

出力遮断回路9は、電流検出用抵抗Rsの他に、PNP型のバイポーラトランジスタ(以下単に「トランジスタ」という)Q2と、抵抗R1とを含んで構成されている。トランジスタQ2は、エミッタが直流電源11と電流検出用抵抗Rsとの接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗との接続点に接続され、ベースが抵抗R1の一端に接続されている。抵抗R1の他端は、電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続されている。

【0005】

出力遮断回路9は、トランジスタQ1を流れる電流が増加し、電流検出用抵抗Rsでの電圧降下が規定値以上になったとき、トランジスタQ2を導通状態とすることによって、トランジスタQ1のゲートソース間の電圧差を小さくして、トランジスタQ1を流れる電流を制限する。負荷が地絡したとき、つまり出力部13から出力される出力電流が異常に増大したとき、トランジスタQ2に電流が流れるときのエミッタとベースと間の電圧降下(以下「ベースエミッタ間電圧」という)をVBEとすると、トランジスタQ1を流れる制限された電流の電流値をIlimとすると、制限電流値Ilimは、VBE/Rsで求められる。すなわち、出力遮断回路9は、制限電流値Ilim=VBE/Rsで電流制限をかける。

【0006】

特許文献1に記載されるDC(直流)−DCコンバータの入力回路は、入力回路に流れる電流を制御するためのNチャネルMOSFETと、NチャネルMOSFETに直列に接続されている入力電流検出用抵抗と、入力電流検出用抵抗の両端間の電圧に応じてNチャネルMOSFETのゲート電圧を制御するNPNトランジスタと、NチャネルMOSFETのソースゲート間に設けられるコンデンサとを含んで構成されている。NPNトランジスタは、入力電流検出用抵抗の両端間の電圧に応じたコレクタ電流によって、NチャネルMOSFETのゲート電圧を下げて、NチャネルMOSFETのオン抵抗を制御し、突入電流の防止と入力電流の遮断とを行っている。さらに、入力電流検出用抵抗の電圧を平均化し、平均化した電圧が基準電圧を超えたとき、NPNトランジスタのコレクタ電流を増加させて、NチャネルMOSFETをオフにする回路を有する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3302951号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、入力電圧が高い場合、あるいは制限電流値Llimが大きく設定されている場合、負荷が地絡すると、トランジスタQ1および電流検出用抵抗Rsでの電力損失が増大して許容損失を超えると、トランジスタQ1および電流検出用抵抗Rsが破壊される可能性がある。これを避けるためには、トランジスタQ1および電流検出用抵抗Rsの許容電流および許容電力を大きくする必要がある。許容電流および許容電力が大きい部品は、その大きさが大きくなり、またコストも増大するという問題がある。

【0009】

特許文献1に記載されるDC−DCコンバータの入力回路は、負荷が短絡し、入力電流検出用抵抗の電圧を平均化した電圧が基準電圧を超えたとき、NチャネルMOSFETをオフにすることができるが、平均化した電圧が基準電圧を超えたことを、コンパレータを用いて検出しており、回路規模が大きくなるという問題がある。

【0010】

本発明の目的は、簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる出力遮断回路および電子機器を提供することである。

【課題を解決するための手段】

【0011】

本発明(1)は、入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている電流検出用抵抗素子と、

エミッタが直流電源に接続され、ベースが電流検出用抵抗素子と第1のトランジスタの入力端子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給するPNP型の第2のトランジスタと、

制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になった時点から予め定める時間を計時する計時手段と、

エミッタが接地され、コレクタが第2のトランジスタのベースに接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき導通状態となり、制御端子の電圧が第1のトランジスタが遮断状態となる電圧になる電流を、第1の抵抗素子へ第2のトランジスタに供給させるNPN型の第3のトランジスタとを含むことを特徴とする出力遮断回路である。

【0012】

また本発明(5)は、入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている電流検出用抵抗素子と、

エミッタが直流電源に接続され、ベースが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給するPNP型の第2のトランジスタと、

制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になり、出力端子の電圧が予め定める第3の電圧まで低下した時点から予め定める時間を計時する計時手段と、

エミッタが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき、導通状態となるPNP型の第3のトランジスタと、

制御端子の電圧を分圧した電圧を監視し、監視する制御端子の電圧を分圧した電圧が、第1のトランジスタを遮断状態とする電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、第3のトランジスタを遮断状態にするための遮断信号を第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする出力遮断回路である。

また本発明(8)は、前記出力遮断回路を備える電子機器である。

【発明の効果】

【0013】

本発明(1)によれば、電流検出用抵抗素子は、入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている。PNP型の第2のトランジスタは、エミッタが直流電源に接続され、ベースが電流検出用抵抗素子と第1のトランジスタの入力端子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給する。計時手段によって、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になった時点から予め定める時間が計時される。そして、NPN型の第3のトランジスタは、エミッタが接地され、コレクタが第2のトランジスタのベースに接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき導通状態となり、制御端子の電圧が第1のトランジスタが遮断状態となる電圧になる電流を、第1の抵抗素子へ第2のトランジスタに供給させる。

【0014】

したがって、負荷が地絡している間、電流制限の後、第1のトランジスタをオフとするので、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができるので、発熱を抑えることができる。すなわち、簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる。

【0015】

また本発明(5)によれば、電流検出用抵抗素子は、入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている。PNP型の第2のトランジスタは、エミッタが直流電源に接続され、ベースが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧を第1のトランジスタが予め定める電流値の電流を出力する電圧にするための電流を第1の抵抗素子へ供給する。計時手段によって、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になり、出力端子の電圧が予め定める第3の電圧まで低下した時点から予め定める時間が計時される。PNP型の第3のトランジスタは、エミッタが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき、導通状態となる。そして、制御手段によって、制御端子の電圧を分圧した電圧を監視し、監視する制御端子の電圧を分圧した電圧が、第1のトランジスタを遮断状態とする電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、第3のトランジスタを遮断状態にするための遮断信号を前記第3のトランジスタのベースに出力する。したがって、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができるので、発熱を抑えることができる。

【0016】

また本発明(8)によれば、前記出力遮断回路を備えるので、正常時は動作電流がゼロになり、暗電流を小さくすることができ、また、過電流時は出力を遮断して、消費電流を小さくすることができ、バッテリ切れの可能性を低減することができる。

【図面の簡単な説明】

【0017】

【図1】従来の技術による出力遮断回路9を備える電源回路90の回路構成を示す図である。

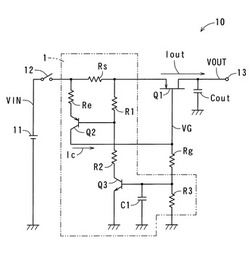

【図2】本発明の第1実施形態である出力遮断回路1を備える電源回路10の回路構成を示す図である。

【図3】出力遮断回路1の動作を説明するためのタイムチャートである。

【図4】本発明の第2実施形態である出力遮断回路1aを備える電源回路10aの回路構成を示す図である。

【図5】本発明の第3実施形態である出力遮断回路1bを備える電源回路10bの回路構成を示す図である。

【図6】出力遮断回路1bの動作を説明するためのタイムチャートである。

【図7】本発明の第4実施形態である出力遮断回路1cを備える電源回路10cの回路構成を示す図である。

【図8】本発明の第5実施形態である出力遮断回路1dを備える電源回路10dの回路構成を示す図である。

【図9】本発明の第6実施形態である出力遮断回路1eを備える電源回路10eの回路構成を示す図である。

【図10】出力遮断回路1eの動作を説明するためのタイムチャートである。

【図11】本発明の第7実施形態である出力遮断回路1fを備える電源回路10fの回路構成を示す図である。

【図12】出力遮断回路1fの動作を説明するためのタイムチャートである。

【図13】本発明の第8実施形態である出力遮断回路1gを備える電源回路10gの回路構成を示す図である。

【図14】本発明の第9実施形態である出力遮断回路1hを備える電源回路10hの回路構成を示す図である。

【図15】出力遮断回路1hの動作を説明するためのタイムチャートである。

【図16】本発明の第10実施形態である出力遮断回路1jを備える電源回路10jの回路構成を示す図である。

【図17】本発明の第11実施形態である出力遮断回路1kを備える電源回路10kの回路構成を示す図である。

【図18】出力遮断回路1kの動作を説明するためのタイムチャートである。

【図19】本発明の第12実施形態である出力遮断回路1mを備える電源回路10mの回路構成を示す図である。

【図20】車載用のAVN装置100の構成を示す図である。

【発明を実施するための形態】

【0018】

図2は、本発明の第1実施形態である出力遮断回路1を備える電源回路10の回路構成を示す図である。電源回路10は、直流電源11、スイッチ12、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1を含んで構成されている。

【0019】

直流電源11は、直流電圧、たとえば12Vを出力するバッテリであり、スイッチ12の一端に接続されている。スイッチ12は、一端が直流電源11に接続され、他端が後述する電流検出用抵抗素子Rsの一端に接続され、直流電源11を出力するか否かを切り換えるスイッチである。以下、抵抗素子のことを単に「抵抗」ともいう。

【0020】

第1のトランジスタであるトランジスタQ1は、たとえばPチャネルのMOSFET(Metal Oxide Semiconductor Field Effect Transistor)によって構成されており、入力端子であるソースが後述する電流検出用抵抗Rsの他端に接続され、出力端子であるドレインが出力部13、およびコンデンサCoutの一端に接続され、制御端子であるゲートがゲート抵抗Rgの一端に接続されている。コンデンサCoutは、一端がトランジスタQ1のドレイン、および出力部13に接続され、他端が接地されている。出力部13は、トランジスタQ1のドレイン、およびコンデンサCoutの一端に接続され、さらに図示しない負荷に接続されている。第1の抵抗素子であるゲート抵抗Rgは、一端がトランジスタQ1のゲートに接続され、他端が後述する抵抗R3を介して接地されている。

【0021】

出力遮断回路1は、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R3、トランジスタQ2,Q3、およびタイマ用コンデンサC1を含んで構成されている。電流検出用抵抗素子である電流検出用抵抗Rsは、電流検出用抵抗Rsを流れる電流の電流値を検出するための抵抗であり、一端がスイッチ12の他端に接続され、他端がトランジスタQ1のソースに接続されている。

【0022】

エミッタ抵抗Reは、一端がスイッチ12と電流検出用抵抗Rsとの接続点に接続され、他端がトランジスタQ2のエミッタに接続されている。抵抗R1は、一端が電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、他端がトランジスタQ2のベース、および抵抗R2の一端に接続されている。第2のトランジスタであるトランジスタQ2は、たとえばPNP型のバイポーラトランジスタによって構成され、エミッタがエミッタ抵抗の他端に接続され、ベースが抵抗R1と抵抗R2との接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗Rgとの接続点に接続されている。

【0023】

第2の抵抗素子である抵抗R2は、一端が抵抗R1の他端、およびトランジスタQ2のベースに接続され、他端がトランジスタQ3のコレクタに接続されている。第3のトランジスタであるトランジスタQ3は、たとえばNPN型のバイポーラトランジスタによって構成され、コレクタが抵抗R2に接続され、エミッタが接地され、ベースがゲート抵抗Rgと抵抗R3との接続点、およびタイマ用コンデンサC1の一端に接続されている。抵抗R3は、一端がゲート抵抗Rgの他端、トランジスタQ3のベース、およびタイマ用コンデンサC1の一端に接続され、他端が接地されている。タイマ用コンデンサC1は、一端がゲート抵抗Rgと抵抗R3との接続点、およびトランジスタQ3のベースに接続され、他端が接地されている。ゲート抵抗RgおよびトランジスタQ3は、計時手段を構成する。

【0024】

直流電源11の出力は、スイッチ12を介して、入力電圧VINとして、電流検出用抵抗Rsの一端に印加される。トランジスタQ1のソースには、入力電圧VINよりも電流検出用抵抗Rsでの電圧降下分の電圧だけ低い電圧が印加される。出力部13から負荷に供給される出力電流Ioutが、負荷が必要とする電流値であるとき、電流検出用抵抗Rsでの電圧降下によるトランジスタQ2のエミッタとベースとの電位差が、トランジスタQ2のベースエミッタ間電圧VBE未満であり、トランジスタQ2は遮断状態(以下「オフ」という)である。

【0025】

トランジスタQ2がオフであるとき、トランジスタQ1のゲート電流として流れる電流は、極めて少ないので、直列に接続されているゲート抵抗Rgおよび抵抗R3での電圧降下も小さく、トランジスタQ1のゲート電圧VGは、ほぼ0Vである。トランジスタQ3は、ベースの電圧がほぼ0Vであるのでオフである。トランジスタQ1は、ゲート電圧VGがソース電圧よりも低いので、導通状態(以下「オン」という)である。したがって、出力遮断回路1は、正常な期間、つまり出力電流Ioutとして負荷が必要とする電流値の電流を供給している期間では、負荷電流、つまり出力電流Ioutのみが電源回路10に流れ、トランジスタQ2,Q3には、電流は流れない。

【0026】

図3は、出力遮断回路1の動作を説明するためのタイムチャートである。正常な期間では、ゲート電圧VGおよびトランジスタQ3のベース電圧(図では「Q3ベース」という)は、ほぼ0Vである。出力地絡の期間は、出力部13が地絡している期間である。地絡は、たとえば基板間を接続するフレキシブル基板のコネクタのショート、あるいは基板上での半田くずによるショートなどによって発生する。

【0027】

時刻t1に負荷が地絡すると、出力電流Ioutが増大する。出力電流Ioutが増大すると、電流検出用抵抗Rsでの電圧降下が増加する。電流検出用抵抗Rsでの電圧降下が予め定める電圧になると、トランジスタQ2は、直流電源11から供給される電流をコレクタ電流Icとしてゲート抵抗Rgに流す。予め定める電圧は、エミッタ抵抗での電圧降下と、トランジスタQ2のベースエミッタ間電圧VBEと、抵抗R1での電圧降下とを加算した電圧である。コレクタ電流Icがゲート抵抗Rgに流れると、ゲート電圧VGが上昇し、トランジスタQ1のゲートソース間の電圧差が少なくなるので、出力電流Ioutが制限電流値Ilimで制限される。電流制限の期間の時間(以下「電流制限時間」という)Tdは、ゲート抵抗の抵抗値およびタイマ用コンデンサC1の静電容量で決まる。すなわち、電流制限時間Tdは、タイマ用コンデンサC1をゲート抵抗Rgから流れる電流で充電し、タイマ用コンデンサC1の両端電圧がトランジスタQ3のベースエミッタ間電圧VBEになるまでの時間である。ベースエミッタ間電圧VBEは、約0.6Vである。

【0028】

ゲート抵抗Rgを流れる電流の一部がタイマ用コンデンサC1を充電し、トランジスタQ3のベース電圧が上昇する。トランジスタQ3のベース電圧が上昇し、時刻t2に、ベース電圧が、トランジスタQ3のベースエミッタ間電圧VBEに達すると、トランジスタQ3はオンになる。トランジスタQ3がオンになると、トランジスタQ2のベース電流が増加し、トランジスタQ2はフルオン状態、つまり短絡状態となる。トランジスタQ2がフルオン状態になると、トランジスタQ1のゲートソース間の電圧がほぼ0Vとなり、トランジスタQ1はオフし、シャットダウンの期間に入る。

【0029】

地絡した直後の出力電流Ioutの制限電流値Ilimは、トランジスタQ1のゲートソース間の電圧をVGSとし、トランジスタQ2のコレクタ電流をIcとし、トランジスタQ2のベースエミッタ間電圧VBEをVBE2とし、トランジスタQ2の電流増幅率をβとすると、式(1),(2)が成立する。

VIN=Rs×Ilim+VGS+Rg×Ic …(1)

Rs×Ilim=Re×Ic+VBE2+R1×(Ic/β) …(2)

【0030】

トランジスタQ2のベース電流Ic/β≒0とすると、式(1),(2)から式(3)が成立する。

Ilim=VBE2/Rs+Re×(VIN−VGS−VBE)

/((Rg+Re)×Rs) …(3)

【0031】

ここで、式(3)のエミッタ抵抗Reの抵抗値が0オームである場合、Ilim=VBE2/Rsとなる。トランジスタQ2のベースエミッタ間電圧VBE2は、−2mV/度Cの温度特性があるので、高温になると、制限電流値Ilimは低下する。また。式(3)からエミッタ抵抗Reが0オームでない場合、第2項の分だけ制限電流値Ilimが大きく、その分トランジスタQ2の温度特性を小さくすることができる。制限電流値Ilimは、予め定める電流値である。

【0032】

抵抗R2,R3,Rg、トランジスタQ3、およびタイマ用コンデンサC1は、タイマラッチ回路を構成し、ゲート電圧VGが上昇し電流制限を開始した時点から電流制限時間Tdを計時し、電流制限時間Tdが計時された時点で、トランジスタQ2をフルオン状態として、トランジスタQ1をオフとし、トランジスタQ1をシャットダウン状態とする。

【0033】

このように、出力遮断回路1は、出力電流Ioutを制限電流値Ilimに制限する電流制限機能と、トランジスタQ1を強制的にオフにするシャットダウン機能とを兼ね備えている。そして、ゲート抵抗Rgは、トランジスタQ1のゲート電圧VGをバイアスするゲートバイアス機能と、タイマ用コンデンサC1を充電する機能とを兼ね備えており、出力遮断回路1は、より簡単な回路構成で実現することができる。

【0034】

図4は、本発明の第2実施形態である出力遮断回路1aを備える電源回路10aの回路構成を示す図である。電源回路10aは、図2に示した電源回路10に、出力電圧VOUTを検出するための抵抗Ra,Rbを追加した回路である。出力遮断回路1aは、図2に示した出力遮断回路1と同じ回路構成である。出力遮断回路1aを除く電源回路10aの構成要素のうち図2に示した電源回路10の構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0035】

図2に示した電源回路10は、負荷が地絡し、シャットダウンの期間に入ると、負荷での地絡が解除されても、トランジスタQ2,Q3ともオンの状態を維持するので、シャットダウンの状態(以下「シャットダウン状態」という)を解除するためには、一旦スイッチ12を切断した後、再度接続する必要がある。これを可能とするために、電源回路10aは、出力電圧VOUTを抵抗Ra,Rbで分圧した電圧を、たとえばマイクロコンピュータ(以下「マイコン」という)によって監視し、出力電圧VOUTがグランドレベルまで下がったとき、負荷が地絡したと判断し、マイコンによってスイッチ12を一旦切断した後、再度接続する。電源回路10aは、正常な期間でも、抵抗Ra,Rbに電流が流れるので、無駄な消費電流が発生する。

【0036】

図5は、本発明の第3実施形態である出力遮断回路1bを備える電源回路10bの回路構成を示す図である。電源回路10bは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1bを含んで構成されている。電源回路10bの構成要素のうち図2に示した電源回路10の構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0037】

出力遮断回路1bは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R3、トランジスタQ2,Q3、タイマ用コンデンサC1、およびマイコン14を含んで構成されている。出力遮断回路1bの構成要素のうち図2に示した出力遮断回路1の構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0038】

マイコン14は、ゲート電圧VGがFail信号として入力ポートINまたはアナログデジタル変換ポートADに入力され、出力ポートOUTからRestart信号がトランジスタQ3のベースに出力される。遮断信号であるRestart信号は、トランジスタQ1のシャットダウン状態を解除するための信号である。

【0039】

制御手段であるマイコン14は、たとえば図示しない中央処理装置(以下「CPU」という)および図示しない記憶装置を含んで構成され、CPUは、記憶装置に記憶されるプログラムを実行することによって、Fail信号を監視し、Fail信号に基づいて、Restart信号の出力を制御する。マイコン14は、Fail信号、つまりゲート電圧VGがトランジスタQ1をオフとする電圧になったとき、シャットダウン状態になったことを検出する。マイコン14は、ゲート電圧VGがトランジスタQ1をオフとする電圧になった時点から、たとえば予め定める第2の時間を計時し、予め定める第2の時間が計時されたときに、Restart信号を出力する。シャットダウンするまでの時間、つまり電流制限時間Tdは、数ms〜数十msであるが、予め定める第2の時間は、電流制限時間Tdより長い時間であってもよい。

【0040】

図6は、出力遮断回路1bの動作を説明するためのタイムチャートである。時刻t1に、負荷に地絡が発生してから、時刻t2に、トランジスタQ1がオフになり、シャットダウンの期間に入るまでの動作は、図3に示したタイムチャートでの動作と同じであり、説明は省略する。

【0041】

マイコン14は、Fail信号によって、ゲート電圧VGがトランジスタQ1をオフとする電圧になったことを検出し、Restart信号をローレベル(図6では、Restart信号をハイレベルで表わしている)とすることによって、トランジスタQ3をオフとする。トランジスタQ3がオフになると、トランジスタQ2のベース電流が減少するので、トランジスタQ2のコレクタ電流が減少する。トランジスタQ2のコレクタ電流が減少すると、ゲート電圧VGが下がり、トランジスタQ1はオンとなる。

【0042】

負荷の地絡が解除されていない場合、トランジスタQ1がオンとなると、地絡がないときに負荷が必要とする電流よりも多い電流が流れるので、トランジスタQ2はオンの状態を継続する。すなわち、トランジスタQ2は、トランジスタQ1を制限電流値Ilimで電流制限を行う。

【0043】

トランジスタQ3のベース電圧は、Restart信号によってグランドレベルまで下げられているが、時刻t4にRestart信号が解除されると、トランジスタQ2のコレクタ電流Icが継続してゲート抵抗に供給されているので、コレクタ電流Icの一部がタイマ用コンデンサC1に充電される。Restart信号が解除されてから電流制限時間Tdが経過した時刻t5に、トランジスタQ3が再びオンとなり、トランジスタQ1をオフとする。

【0044】

時刻t6に負荷の地絡が解除されている場合、Restart信号が出力されると、トランジスタQ3がオフになり、トランジスタQ1はオンとなる。トランジスタQ1がオンとなったとき、負荷の地絡が解除されて出力電流Ioutが減少しているので、電流検出用抵抗Rsを流れる電流は、地絡がないときに負荷が必要とする電流になっており、電流検出用抵抗Rsでの電圧降下が下がり、トランジスタQ2はオフとなり、電源回路10bは、正常な状態に復帰する。

【0045】

出力遮断回路1bは、電流制限のみを継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができ、発熱を抑えることができる。また、シャットダウン状態になってから予め定める第2の時間が経過したときに、Restart信号によってトランジスタQ3をオフにしているので、負荷での地絡が解除されていれば、電源回路10bを正常な状態に復帰させることができる。

【0046】

また、電流制限を行うことなく、いきなりシャットダウンするのではなく、電流制限を行った後シャットダウンするので、負荷に静電容量の大きいコンデンサがあるときに生じるラッシュ電流を防止することができ、また瞬間的な過電流の場合に、シャットダウンすることを防止することができる。

【0047】

図7は、本発明の第4実施形態である出力遮断回路1cを備える電源回路10cの回路構成を示す図である。電源回路10cは、図5に示した電源回路10bの変形例である。図5に示した電源回路10bは、入力電圧VINがマイコン14に供給される電圧よりも低い場合に適用されるが、入力電圧VINがマイコン14に供給される電圧よりも高い場合、トランジスタQ2がオンになると、トランジスタQ1のゲート電圧VGがマイコン14に供給される電圧よりも高くなるため、ゲート電圧VGを直接マイコン14に入力することができない。電源回路10cは、ゲート電圧VGを直接マイコン14に入力することができる電圧に下げてマイコン14に入力している。

【0048】

電源回路10cは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1cを含んで構成されている。電源回路10bの構成要素のうち図5に示した電源回路10bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0049】

ゲート抵抗Rg1は、一端がトランジスタQ1のゲート、およびトランジスタQ2のコレクタに接続され、他端がゲート抵抗Rg2の一端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続されている。ゲート抵抗Rg2は、一端がゲート抵抗Rg1の他端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続され、他端が抵抗R3の一端、タイマ用コンデンサC1の一端、トランジスタQ3のベース、および後述するトランジスタQ4のコレクタに接続されている。

【0050】

第1の抵抗素子であるゲート抵抗Rg1,Rg2は、入力電圧VINがマイコンに供給される電圧よりも高い場合、図2に示した電源回路10で用いられるゲート抵抗Rgの代わりに用いられるゲート抵抗であり、マイコン14に入力するFail信号の電圧が、マイコンに供給される電圧よりも低い電圧になるように分圧する。

【0051】

出力遮断回路1cは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R5、トランジスタQ2〜Q4、タイマ用コンデンサC1、およびマイコン14を含んで構成されている。出力遮断回路1cの構成要素のうち図5に示した出力遮断回路1bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0052】

トランジスタQ4は、たとえばNPN型のバイポーラトランジスタであり、コレクタが抵抗R3の一端、タイマ用コンデンサC1の一端、トランジスタQ3のベース、およびゲート抵抗Rg2の他端に接続され、エミッタが接地され、ベースが抵抗R4の一端および抵抗R5の一端に接続されている。抵抗R4は、一端がトランジスタQ4のベース、および抵抗R5の一端に接続され、他端がマイコン14の出力ポートOUTに接続されている。抵抗R5は、一端がトランジスタQ4のベース、および抵抗R4の一端に接続され、他端が接地されている。マイコン14、トランジスタQ4、および抵抗R4,R5は、制御手段である。

【0053】

図5に示したマイコン14は、Restart信号をローレベルで出力したが、図7に示したマイコン14は、Restart信号をハイレベルで出力する。Restart信号が出力されると、トランジスタQ4がオンになり、トランジスタQ3のベース電圧をグランドレベルまで下げて、トランジスタQ3をオフにする。

【0054】

図8は、本発明の第5実施形態である出力遮断回路1dを備える電源回路10dの回路構成を示す図である。電源回路10dは、図5に示した電源回路10bの変形例であり、電源回路10cと同様に、ゲート電圧VGを直接マイコン14に入力することができる電圧に下げてマイコン14に入力している。

【0055】

電源回路10dは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1dを含んで構成されている。電源回路10dの構成要素のうち図5に示した電源回路10bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0056】

出力遮断回路1dは、図7に示した出力遮断回路1cの変形例であり、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R6、トランジスタQ2〜Q4、タイマ用コンデンサC1、マイコン14、およびダイオードD1を含んで構成されている。出力遮断回路1dの構成要素のうち図7に示した出力遮断回路1cの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0057】

抵抗R6は、一端がトランジスタQ1のゲート、トランジスタQ2のコレクタ、ゲート抵抗Rgの一端に接続され、他端がマイコン14の入力ポートINまたはアナログデジタル変換ポートAD、およびダイオードD1のカソードに接続されている。ダイオードD1は、たとえばツェナーダイオードによって構成され、アノードが接地され、カソードが抵抗R6の他端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続されている。

【0058】

入力電圧VINがマイコンに供給される電圧よりも高い場合、出力遮断回路1dは、抵抗R6とダイオードD1によって、マイコン14に入力するFail信号の電圧を、マイコンに供給される電圧よりも低い電圧になるようにしている。マイコン14、トランジスタQ4、抵抗R4〜R6、およびダイオードD1は、制御手段である。

【0059】

出力遮断回路1bは、正常な期間では、負荷電流、つまり出力電流Ioutのみが電源回路10bに流れ、トランジスタQ2,Q3には、電流は流れない。また、出力遮断回路1c,1dは、正常な期間では、負荷電流のみが電源回路10c,10dに流れ、トランジスタQ2〜Q4には、電流は流れない。

【0060】

図9は、本発明の第6実施形態である出力遮断回路1eを備える電源回路10eの回路構成を示す図である。上述した実施の形態では、マイコン14は、ゲート電圧VGを監視して、トランジスタQ1がオフになり、シャットダウン状態になったことを検出したが、出力遮断回路1eは、トランジスタQ3のコレクタの電圧を監視してシャットダウン状態になったことを検出する。

【0061】

電源回路10eは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1eを含んで構成されている。電源回路10eの構成要素のうち図8に示した電源回路10dの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0062】

出力遮断回路1eは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R5,R7、トランジスタQ2〜Q4、タイマ用コンデンサC1、マイコン14、およびダイオードD2を含んで構成されている。出力遮断回路1eの構成要素のうち図8に示した出力遮断回路1dの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0063】

ダイオードD2は、アノードがマイコン14の入力ポートINまたはアナログデジタル変換ポートAD、および抵抗R7の一端に接続され、カソードが抵抗R2とトランジスタQ3のコレクタとの接続点に接続されている。抵抗R7は、一端がマイコン14の入力ポートINまたはアナログデジタル変換ポートAD、およびダイオードD2のアノードに接続され、他端に、マイコン14に印加される直流電圧VDDが印加されている。

【0064】

マイコン14は、Fail信号として、トランジスタQ3のコレクタの電圧を監視している。Fail信号がローレベルになると、シャットダウンが行われたこと、すなわちトランジスタQ1がオフになったことを検出することができる。

【0065】

ダイオードD2は、入力電圧VINがマイコン14に印加される直流電圧VDDよりも高い場合、トランジスタQ3がオフのときに、入力電圧VINが、直流電圧VDD以上の電圧で、電流検出用抵抗Rsおよび抵抗R1,R2を介してマイコン14の入力ポートINまたはアナログデジタル変換ポートADに印加されることを防止するために設けられるダイオードである。マイコン14、トランジスタQ4、抵抗R4、R5,R7、およびダイオードD2は、制御手段である。

【0066】

図10は、出力遮断回路1eの動作を説明するためのタイムチャートである。このタイムチャートは、図6に示したタイムチャートと、Fail信号を除いて同じである。Fail信号は、トランジスタQ3のコレクタの電圧を表す信号であるので、トランジスタQ3がオンの期間、つまりシャットダウンの期間だけ、ローレベルとなる。

【0067】

図11は、本発明の第7実施形態である出力遮断回路1fを備える電源回路10fの回路構成を示す図である。上述した実施の形態では、電流制限時間Tdを、タイマ用コンデンサC1を用いて計時したが、出力遮断回路1fは、マイコン14が電流制限時間Tdを計時する。

【0068】

電源回路10fは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1fを含んで構成されている。電源回路10fの構成要素のうち図5に示した電源回路10bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0069】

ゲート抵抗Rg1は、一端がトランジスタQ1のゲート、およびトランジスタQ2のコレクタに接続され、他端がゲート抵抗Rg2の一端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続されている。ゲート抵抗Rg2は、一端がゲート抵抗Rg1の他端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続され、他端が接地されている。

【0070】

ゲート抵抗Rg1,Rg2は、入力電圧VINがマイコン14に供給される電圧よりも高い場合、図5に示した電源回路10bで用いられるゲート抵抗Rgの代わりに用いられるゲート抵抗であり、マイコン14に入力するFail信号の電圧が、マイコン14に供給される電圧よりも低い電圧になるように分圧する。

【0071】

出力遮断回路1fは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1,R2,R8,R9、トランジスタQ2,Q3、およびマイコン14を含んで構成されている。出力遮断回路1fの構成要素のうち図5に示した出力遮断回路1bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0072】

抵抗R8は、一端がトランジスタQ3のベース、および抵抗R9の一端に接続され、他端がマイコン14の出力ポートOUTに接続されている。抵抗R9は、一端がトランジスタQ3のベース、および抵抗R8の一端に接続され、他端が接地されている。

【0073】

マイコン14は、Fail信号によってゲート電圧VGを監視し、ゲート電圧VGをゲート抵抗Rg1とゲート抵抗Rg2とで分圧した電圧が、ゲート電圧VGが制限電圧になる電圧になったとき、電流制限が行われたこと、すなわちトランジスタQ2がオンになったことを検出する。制限電圧は、ゲート電圧VGがトランジスタQ1を制限電流値Ilimの出力電流を出力させる電圧である。マイコン14は、正常の期間、およびRestart信号を出力するときに、ローレベルを出力し、トランジスタQ3をオン、そしてトランジスタQ1をオフにして、シャットダウン状態とするときに、ハイレベルを出力する。マイコン14、および抵抗R8,R9は、制御手段である。

【0074】

抵抗R2およびトランジスタQ3は、ラッチ回路を構成し、電流制限時間Tdが計時された時点で、トランジスタQ2をフルオン状態として、トランジスタQ1をオフとし、トランジスタQ1をシャットダウン状態とする。

【0075】

図12は、出力遮断回路1fの動作を説明するためのタイムチャートである。時刻t11に負荷が地絡すると、トランジスタQ2がオンとなり、コレクタ電流Icがゲート抵抗Rg1,Rg2に供給され、ゲート電圧VGが上昇する。ゲート電圧VGが上昇すると、トランジスタQ1の出力電流IOUTが制限電流値Ilimに制限される。このとき、ゲート電圧VGをゲート抵抗Rg1とゲート抵抗Rg2とで分圧した電圧が上昇して、電流制限が行われる電圧になるので、マイコン14は、電流制限が行われたことを検出することができる。

【0076】

マイコン14は、電流制限が行われたことを検出してから、電流制限時間Tdを計時し、電流制限時間Tdが経過した時刻t12に、Restart信号をローレベルからハイレベルに変化させて、トランジスタQ3をオンとする。トランジスタQ3がオンになると、トランジスタQ2はフルオン状態となり、トランジスタQ1をオフし、シャットダウン状態とする。トランジスタQ1がオフになる。このとき、ゲート電圧VGは、トランジスタQ1をオフになる電圧まで上昇している。

【0077】

マイコン14は、トランジスタQ1をシャットダウンしてから、予め定める第2の時間を計時し、予め定める第2の時間を計時した時刻t13に、Restart信号をハイレベルからローレベルに変化させる。Restart信号がローレベルになると、トランジスタQ3はオフとなり、トランジスタQ1はオンとなる。しかし、負荷の地絡が解除されていないと、トランジスタQ2はオンのままで、電流制限がかかった状態になる。

【0078】

マイコン14は、ゲート電圧VGがシャットダウンの状態の電圧から電流制限の状態の電圧に下がったことを時刻t14に検出すると、まだ負荷の地絡が解除されていないので、電流制限時間Tdを計時し、電流制限時間Tdが経過した時刻t15に、Restart信号をローレベルからハイレベルに変化させ、トランジスタQ1を再びオフとし、シャットダウン状態とする。

【0079】

マイコン14は、トランジスタQ1をオフしてから、予め定める第2の時間を計時し、予め定める第2の時間を計時した時刻t17に、Restart信号をハイレベルからローレベルに変化させる。時刻t15と時刻t17との間の時刻t16に負荷の地絡が解除されていると、時刻t17にRestart信号がローレベルになり、トランジスタQ3がオフ、そしてトランジスタQ1がオンになったとき、トランジスタQ2はオフになり、電源回路10fは、正常な動作を再開する。

【0080】

出力遮断回路1fは、タイマ用コンデンサC1が不要であり、回路構成を簡単化することができる。

【0081】

図13は、本発明の第8実施形態である出力遮断回路1gを備える電源回路10gの回路構成を示す図である。電源回路10gは、図11に示した電源回路10fの変形例である。電源回路10gは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1gを含んで構成されている。電源回路10gの構成要素のうち図11に示した電源回路10fの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0082】

出力遮断回路1gは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1,R2,R8〜R10、トランジスタQ2,Q3,Q5、およびマイコン14を含んで構成されている。出力遮断回路1gの構成要素のうち図11に示した出力遮断回路1fの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0083】

トランジスタQ5は、たとえばNPN型のバイポーラトランジスタであり、ベースがゲート抵抗Rg1とゲート抵抗Rg2との接続点に接続され、コレクタが抵抗R10の一端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続され、エミッタが接地されている。抵抗R10は、一端がトランジスタQ5のコレクタ、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続されて、他端に、マイコン14に印加される直流電圧VDDが印加されている。

【0084】

トランジスタQ2がオフのとき、つまりゲート電圧VGがほぼ0Vのとき、トランジスタQ5はオフで、コレクタの電圧、つまりFail信号は、ハイレベルである。トランジスタQ2がオンになり、電流制限が行われると、Fail信号は、ゲート電圧VGが制限電圧になる電圧である。トランジスタQ3がオンになりシャットダウンの状態になると、グランドレベルになる。マイコン14は、Fail信号の電圧を監視することによって、正常の状態か、電流制限の状態か、シャットダウン状態かを検出することができる。マイコン14、トランジスタQ5、および抵抗R8〜R10は、制御手段である。

【0085】

出力遮断回路1fは、正常な期間では、負荷電流のみが電源回路10fに流れ、トランジスタQ2,Q3には、電流は流れない。また、出力遮断回路1gは、正常な期間では、負荷電流のみが電源回路10gに流れ、トランジスタQ2,Q3,Q5には、電流は流れない。

【0086】

図14は、本発明の第9実施形態である出力遮断回路1hを備える電源回路10hの回路構成を示す図である。図14(a)は、電源回路10hの回路構成を示す図である。電源回路10hは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1hを含んで構成されている。電源回路10hの構成要素のうち図11に示した電源回路10fの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0087】

出力遮断回路1hは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R11,R12、トランジスタQ2,Q6、タイマ用コンデンサC2、マイコン14,およびトランジスタ部Tr1,Tr2を含んで構成されている。出力遮断回路1hは、図5に示した出力遮断回路1bのトランジスタQ3およびタイマ用コンデンサC1の代わりに、トランジスタQ6およびタイマ用コンデンサC2を用いる回路である。出力遮断回路1hの構成要素のうち図5に示した出力遮断回路1bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0088】

上述したタイマ用コンデンサC1は、ゲート電圧VGの上昇を契機に電流制限時間Tdを計時するコンデンサであるが、タイマ用コンデンサC2は、出力電圧VOUTの低下を契機に電流制限時間Tdを計時するコンデンサである。

【0089】

図14(b)は、トランジスタ部Tr1の構成を示す図であり、図14(c)は、トランジスタ部Tr2の構成を示す図である。トランジスタ部Tr1は、トランジスタQ7、および抵抗R13,R14によって構成されている。トランジスタQ7は、たとえばPNP型のバイポーラトランジスタによって構成され、ベースが抵抗R13の一端、および抵抗R14の一端に接続され、エミッタが抵抗R13の他端、および電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、コレクタがトランジスタQ6のベースに接続されている。

【0090】

トランジスタ部Tr2は、トランジスタQ8、および抵抗R15,R16によって構成されている。トランジスタQ8は、たとえばNPN型のバイポーラトランジスタによって構成され、ベースが抵抗R15の一端、および抵抗R16の一端に接続され、エミッタが抵抗R15の他端に接続されているとともに、接地され、コレクタが抵抗R14の他端に接続されている。抵抗R16は、他端がマイコン14の出力ポートOUTに接続されている。

【0091】

トランジスタQ6は、たとえばPNP型のバイポーラトランジスタであり、エミッタが電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、ベースがトランジスタQ7のコレクタに接続され、コレクタがトランジスタQ2のコレクタ、トランジスタQ1のゲート、およびゲート抵抗Rg1の一端に接続されている。タイマ用コンデンサC2は、一端が電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、他端がトランジスタQ6のベースとトランジスタQ7のコレクタとの接続点に接続されている。

【0092】

抵抗R11は、一端が電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、他端がトランジスタQ6のベースとトランジスタQ7のコレクタとの接続点に接続されている。抵抗R12は、一端がトランジスタQ6のベースとトランジスタQ7のコレクタとの接続点に接続され、他端がトランジスタQ1のドレインと出力部13との接続点に接続されている。トランジスタ部Tr1,Tr2、およびマイコン14は、制御手段である。抵抗R12およびタイマ用コンデンサC2は、計時手段である。

【0093】

抵抗R11,R12、トランジスタQ6、およびタイマ用コンデンサC2は、タイマラッチ回路を構成し、電流制限を開始したことによって出力電圧VOUTが予め定める第3の電圧まで低下した時点から電流制限時間Tdを計時し、電流制限時間Tdが計時された時点で、トランジスタQ1をオフとし、トランジスタQ1をシャットダウン状態とする。

【0094】

図15は、出力遮断回路1hの動作を説明するためのタイムチャートである。トランジスタQ1がオンの状態で、負荷が短絡していないとき、トランジスタQ6のベース電圧はほぼトランジスタQ6のエミッタと同じ電圧であり、トランジスタQ6はオフの状態である。

【0095】

時刻t21に負荷が地絡すると、出力電流Ioutが増大する。出力電流Ioutが増大すると、電流検出用抵抗Rsでの電圧降下が増加する。電流検出用抵抗Rsでの電圧降下が、予め定める電圧になると、トランジスタQ2にベース電流が流れ、トランジスタQ2は、直流電源11から供給される電流をコレクタ電流Icとしてゲート抵抗Rg1,Rg2に流し、ゲート電圧VGは上昇する。ゲート電圧VGが上昇し、制限電圧になると、トランジスタQ1のゲートソース間の電圧差が少なくなるので、出力電流Ioutが制限電流値Ilimで制限される。予め定める電圧は、エミッタ抵抗での電圧降下とトランジスタQ2のベースエミッタ間電圧VBEとを加算した電圧である。

【0096】

また、時刻t21に負荷が地絡すると、出力電流Ioutが制限電流値Ilimで制限され、出力電圧VOUTが低下するので、トランジスタQ6のベース電圧(図では「Q6ベース」という)は、低下を開始する。電流制限時間Tdが経過した時刻t22に、トランジスタQ6のベースとエミッタとの間の電圧がベースエミッタ間電圧VBEになると、ベース電流が流れ、トランジスタQ6がオンになる。トランジスタQ6がオンになると、トランジスタQ1のゲート電圧VGとソース電圧との差がなくなり、トランジスタQ1はオフになり、シャットダウン状態となる。電流制限時間Tdは、抵抗R12の抵抗値およびタイマ用コンデンサC2の静電容量で決まる。

【0097】

マイコン14が、Restart信号をハイレベルとすると、トランジスタQ8がオン、そしてトランジスタQ7がオンとなる。トランジスタQ7がオンになると、トランジスタQ6のベース電圧とエミッタ電圧とがほぼ同じ電圧になるので、トランジスタQ6がオフとなる。トランジスタQ6がオフになると、ゲート電圧VGが制限電圧まで下がり、トランジスタQ1がオンとなり、シャットダウン状態が解除される。

【0098】

負荷の地絡が解除されていない場合、電流検出用抵抗Rsでの電圧降下は、エミッタ抵抗での電圧降下とトランジスタQ2のベースエミッタ間電圧VBEとを加算した電圧であり、トランジスタQ2はオンの状態を継続する。すなわち、トランジスタQ2は、トランジスタQ1がオンになっているので、電流制限を行う。トランジスタQ6のベース電圧とエミッタ電圧とは、Restart信号によってほぼ同じ電圧にされているが、時刻t24にRestart信号が解除されても、電流制限が行われており、抵抗R12の負荷側、つまり出力電圧VOUTが低下しているので、タイマ用コンデンサC2が接続されているトランジスタQ6のベース電圧が低下し始める。Restart信号が解除されてから電流制限時間Tdが経過した時刻t25に、トランジスタQ6が再びオンとなり、トランジスタQ1をオフとする。

【0099】

時刻t26で負荷の地絡が解除された場合、Restart信号が出力されると、トランジスタQ6がオフになり、トランジスタQ1はオンとなる。トランジスタQ1がオンとなったとき、負荷の地絡が解除されて出力電流Ioutが減少しているので、電流検出用抵抗Rsでの電圧降下はエミッタ抵抗での電圧降下とトランジスタQ2のベースエミッタ間電圧VBEとを加算した電圧未満になっており、トランジスタQ2はオフとなる。電源回路10hは、正常な状態に復帰する。

【0100】

図16は、本発明の第10実施形態である出力遮断回路1jを備える電源回路10jの回路構成を示す図である。電源回路10jは、図14に示した電源回路10hの変形例である。電源回路10jは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1jを含んで構成されている。電源回路10jの構成要素のうち図14に示した電源回路10hの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0101】

出力遮断回路1hは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R10〜R12、トランジスタQ2,Q5,Q6、タイマ用コンデンサC2、マイコン14,およびトランジスタ部Tr1,Tr2を含んで構成されている。出力遮断回路1jの構成要素のうち図14に示した出力遮断回路1hの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。トランジスタQ5および抵抗R10は、図13に示したトランジスタQ5および抵抗R10と同じである。トランジスタ部Tr1,Tr2、マイコン14、抵抗R10、およびトランジスタQ5は、制御手段である。

【0102】

出力遮断回路1hは、正常な期間では、負荷電流のみが電源回路10hに流れ、トランジスタQ2,Q6〜Q8には、電流は流れない。また、出力遮断回路1jは、正常な期間では、負荷電流のみが電源回路10jに流れ、トランジスタQ2,Q5〜Q8には、電流は流れない。

【0103】

図17は、本発明の第11実施形態である出力遮断回路1kを備える電源回路10kの回路構成を示す図である。上述したタイマ用コンデンサC1による電流制限時間Tdの計時は、ゲート電圧VGの上昇を契機に行ったが、出力遮断回路1kでは、出力電圧VOUTの低下を契機に行う。

【0104】

電源回路10kは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1kを含んで構成されている。電源回路10kの構成要素のうち図9に示した電源回路10eの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0105】

出力遮断回路1kは、図9に示した出力遮断回路1eの変形例である。出力遮断回路1kは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1,R2,R4,R5,R7,R11,R12,R17,R18、トランジスタQ2〜Q4,Q9、タイマ用コンデンサC1、マイコン14、およびダイオードD2を含んで構成されている。出力遮断回路1kの構成要素のうち図9に示した出力遮断回路1eの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0106】

第4のトランジスタであるトランジスタQ9は、たとえばPNP型のバイポーラトランジスタによって構成され、エミッタが電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、ベースが抵抗R11の一端、および抵抗R12の一端に接続され、コレクタが抵抗17の一端に接続されている。抵抗R11は、一端がトランジスタQ9のベース、および抵抗R12の一端に接続され、他端が電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続されている。第3の抵抗素子である抵抗R12は、一端がトランジスタQ9のベース、および抵抗R12の一端に接続され、他端がトランジスタQ1のドレインと出力部13との接続点に接続されている。

【0107】

第4の抵抗素子である抵抗17は、一端がトランジスタQ9のコレクタに接続され、他端が抵抗18の一端に接続されている。第5の抵抗素子である抵抗18は、一端が抵抗17の他端に接続され、他端が接地されている。トランジスタQ3のベース、コンデンサであるタイマ用コンデンサC1の一端、およびトランジスタQ4のコレクタは、図9に示した出力遮断回路1eでは、ゲート抵抗Rgと抵抗R3との接続点に接続されているが、出力遮断回路1kでは、抵抗R17と抵抗R18との接続点に接続されている。

【0108】

抵抗R1,R2,R11,R12,R17,R18、トランジスタQ3,Q9、およびタイマ用コンデンサC1は、タイマラッチ回路を構成し、電流制限を開始したことによって出力電圧VOUTが低下した時点から電流制限時間Tdを計時し、電流制限時間Tdが計時された時点で、トランジスタQ1をオフとし、トランジスタQ1をシャットダウン状態とする。

【0109】

図17に示した出力遮断回路1kは、ゲート電圧VGが上昇しても、回路上、コンデンサC1へ電流が流れないため、出力電流Ioutの増加に応じて計時を開始する構成としている。

【0110】

図18は、出力遮断回路1kの動作を説明するためのタイムチャートである。タイムチャートそのものは、図6に示したタイムチャートと同じであり、タイマラッチ回路の動作の相違点のみを説明する。負荷が短絡していない状態では、トランジスタQ1のドレインの電圧は、ほぼソースの電圧に等しいので、トランジスタQ9は、オフである。

【0111】

時刻t1に負荷が地絡すると、トランジスタQ2がオンとなり、出力電流Ioutが制限電流値Ilimで制限される。出力電流Ioutが制限電流値Ilimで制限されると、出力電圧VOUTが低下するので、抵抗R12によって、トランジスタQ9のベースにベース電流が流れ、トランジスタQ9がオンになる。

【0112】

トランジスタQ9がオンになると、タイマ用コンデンサC1の電圧が、抵抗R17の抵抗値とタイマ用コンデンサC1の静電容量との積で決まる時定数で上昇し、時刻t2にベースエミッタ間電圧VBEになると、トランジスタQ3がオンとなる。トランジスタQ3がオンになると、トランジスタQ2のベース電流が増加し、トランジスタQ2はフルオン状態となる。トランジスタQ2がフルオン状態になると、トランジスタQ1のゲートソース間の電圧がほぼ0Vとなり、トランジスタQ1はオフし、シャットダウン状態となる。

【0113】

マイコン14が、Restart信号をハイレベルとし、トランジスタQ4をオンとすることによって、トランジスタQ3をオフとする。トランジスタQ3がオフになると、トランジスタQ2のベース電流が減少するので、トランジスタQ2のコレクタ電流が減少する。トランジスタQ2のコレクタ電流が減少すると、ゲート電圧VGが下がり、トランジスタQ1はオンとなる。

【0114】

負荷の地絡が解除されていない場合、トランジスタQ2はオンの状態を継続し、出力電流Ioutは、制限電流値Ilimに制限されているので、トランジスタQ9は、オンの状態を継続する。トランジスタQ3のベース電圧は、Restart信号によってグランドレベルまで下げられているが、時刻t4にRestart信号が解除されると、トランジスタQ9の電流が抵抗17に供給されるので、タイマ用コンデンサC1の電圧が上昇する。Restart信号が解除されてから電流制限時間Tdが経過した時刻t5に、トランジスタQ3が再びオンとなり、トランジスタQ1をオフとする。

【0115】

時刻t6に負荷の地絡が解除され、時刻t5にトランジスタQ1がオフとなった時点から予め定める第2の時間が経過した時刻t7に、マイコン14は、Restart信号を出力する。Restart信号が出力されると、トランジスタQ3がオフになり、トランジスタQ1もオンとなる。トランジスタQ1がオンとなったとき、負荷の地絡が解除されて出力電流Ioutが減少しているので、電流検出用抵抗Rsでの電圧降下は、エミッタ抵抗での電圧降下とトランジスタQ2のベースエミッタ間電圧VBEとを加算した電圧未満になっており、トランジスタQ2はオフとなり、電源回路10kは、正常な状態に復帰する。

【0116】

図19は、本発明の第12実施形態である出力遮断回路1mを備える電源回路10mの回路構成を示す図である。電源回路10mは、図17に示した電源回路10kの変形例である。電源回路10mは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1mを含んで構成されている。電源回路10mの構成要素のうち図17に示した電源回路10kの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0117】

出力遮断回路1mは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1,R2,R4,R5,R7,R11,R12,R17〜R19、トランジスタQ2〜Q4,Q9、タイマ用コンデンサC1、マイコン14、およびダイオードD2〜4を含んで構成されている。出力遮断回路1mの構成要素のうち図17に示した出力遮断回路1kの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。出力遮断回路1mは、図17に示した抵抗17の代わりに、直列に接続した抵抗R19,R20を用いており、ダイオードD3,D4が追加されている。

【0118】

第6の抵抗素子である抵抗19は、一端がトランジスタQ9のコレクタに接続され、他端が抵抗17の一端、およびダイオードD3のアノードに接続されている。ダイオードD3は、アノードが抵抗R19と抵抗17との接続点に接続され、カソードがダイオードD4のアノードに接続されている。ダイオードD4は、アノードがダイオードD3のカソードに接続され、カソードが接地されている。

【0119】

クランプ部であるダイオードD3,D4は、抵抗R19と抵抗17との接続点の電圧を、予め定める第3の電圧、たとえばダイオードの1個分の電圧降下VFの2倍の電圧以下になるようにクランプしている。したがって、トランジスタQ9がオンとなり、トランジスタQ9から抵抗R19に供給される電流の電流値が増加しても、抵抗R19と抵抗17との接続点の電圧を2VFにすることができるので、タイマ用コンデンサC1を充電する電流は、トランジスタQ9から抵抗R19に供給される電流に依存せず、一定値にすることができる。したがって、電流制限時間を一定の時間にすることができる。

【0120】

たとえばタイマ用コンデンサC1の静電容量をC1、抵抗R17の抵抗値をR17とすると、電流制限時間Tdは、C1×R17である。タイマ用コンデンサC1および抵抗R17に温度変動の小さいものを用いれば、温度変動による電流制限時間Tdの変動を小さくすることができる。

【0121】

出力遮断回路1k,1mは、正常な期間では、負荷電流のみが電源回路10k,10mに流れ、トランジスタQ2〜Q4,Q9には、電流は流れない。

【0122】

出力遮断回路1,1a〜1mを用いる電源回路10,10a〜10mは、たとえば車載用のオーディオ機器、ビデオ機器、ナビゲーション装置、これらを組み合わせた装置、あるいは携帯電話機などバッテリを用いている電子機器に適用することができる。

【0123】

図2に示した出力遮断回路1、図4に示した出力遮断回路1a、図5に示した出力遮断回路1b、図7に示した出力遮断回路1c、図8に示した出力遮断回路1dおよび図9に示した出力遮断回路1eは、負荷電流を徐々に単調増加させた場合、ゲート電圧VGが上昇して、トランジスタQ1に電流制限がかかるより先にトランジスタQ3がオンして出力が遮断される。これに対して、図14に示した出力遮断回路1h、図16に示した出力遮断回路1jおよび図17に示した出力遮断回路1kは、トランジスタQ3がないので、負荷電流を徐々に単調増加させた場合でも、ゲート電圧VGが上昇して電流制限がかかった後で出力が遮断される。

【0124】

すなわち、出力遮断回路1,1a〜1eは、出力が地絡したときの電流制限値Ilimと、負荷電流を徐々に増加させたときトランジスタQ3がオンして出力電流を遮断する第2の出力電流値Ilim2とは異なるが、出力遮断回路1h,1j,1kは、電流制限値Ilimと第2の出力電流値Ilim2とは同じになる。

【0125】

電流制限値Ilimは、式(3)で求められ、抵抗Reによって、その温度変動を小さくすることができる。しかしながら、第2の出力電流値Ilim2は、トランジスタQ3のベースエミッタ間電圧VBE3=R3×Ic、およびRs×Ilim2=Re×Ic+トランジスタQ2のVBE2という関係から、式(4)で表わされ、抵抗Reがあっても温度特性は変わらない。ここに、Rs,Re,R3は、それぞれ抵抗Rs,Re,R3の抵抗値である。

Ilim2=VBE2/Rs+VBE3×Re/(R3×Rs) …(4)

【0126】

したがって、出力遮断回路1,1a〜1eは、負荷電流を徐々に増加させたときに、出力を遮断する電流値の温度変動が大きいという欠点があるが、出力遮断回路1h,1j,1kは、抵抗Reによってその温度変動を小さくすることができる。

【0127】

図20は、車載用のAVN(Audio Video Navigation)装置100の構成を示す図である。AVN装置100は、バッテリ101、オーディオ基板102および電子回路103を含んで構成されている。オーディオ基板102は、バッテリ101を除く、出力遮断回路1を備える電源回路10を含んで構成されている。電子回路103は、たとえばLED群、LEDドライバ、モータ、センサ、あるいはランプなどによって構成されている。

【0128】

バッテリ101および出力遮断回路1を含む電源回路10の電圧は、負荷である制御回路105に印加されている。オーディオ基板102と電子回路103とはフレキシブル基板106によって接続されている。

【0129】

図20に示した例は、出力遮断回路1を備える電源回路10を用いたが、出力遮断回路1a〜1mを用いる電源回路10a〜10mのいずれを用いてもよい。出力遮断回路1,1a〜1mは、正常に動作しているとき、出力遮断回路1,1a〜1mで用いるトランジスタは、いずれもオフであり、暗電流が少なく、バッテリを用いる電子機器では有用である。また、出力遮断回路1,1a〜1mは、簡単な回路構成で実現されるので、電子機器を小型化し、かつコストダウンを図ることができる。

【0130】

このように、電流検出用抵抗Rsは、ソース、負荷に接続されているドレイン、およびゲート抵抗Rgを介して接地されているゲートを備えるトランジスタQ1のソースに一端が接続され、他端が直流電源に接続されている。PNP型のトランジスタQ2は、エミッタが直流電源に接続され、ベースが電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗Rgとの接続点に接続され、電流検出用抵抗Rsの電圧降下が予め定める電圧になると、ゲートの電圧が、トランジスタQ1が予め定める電流値の電流を出力する電圧になる電流をゲート抵抗Rgへ供給する。計時手段、たとえばゲート抵抗RgおよびトランジスタQ3によって、ゲートの電圧が、トランジスタQ1が予め定める電流値の電流を出力する電圧になった時点から予め定める時間が計時される。そして、NPN型のトランジスタQ3は、エミッタが接地され、コレクタが抵抗R2を介してトランジスタQ2のベースに接続され、ベースがゲート抵抗RgとトランジスタQ3との接続点に接続され、ゲート抵抗RgおよびトランジスタQ3によって予め定める時間が計時されたとき導通状態となり、ゲートの電圧がトランジスタQ1が遮断状態となる電圧になる電流を、ゲート抵抗RgへトランジスタQ2に供給させる。

【0131】

したがって、負荷が地絡している間、電流制限の後、トランジスタQ1をオフとするので、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができ、発熱を抑えることができる。すなわち、簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる。

【0132】

さらに、制御手段によって、ゲートの電圧が監視され、監視されるゲートの電圧が、トランジスタQ1が遮断状態になる電圧になった時点から経過した時間が計時され、計時された時間が予め定める第2の時間になったとき、トランジスタQ3を遮断状態にするためのRestart信号がトランジスタQ3のベースに出力される。制御手段は、たとえば出力遮断回路1bでは、マイコン14であり、出力遮断回路1cでは、マイコン14、トランジスタQ4、および抵抗R4,R5であり、出力遮断回路1dでは、マイコン14、トランジスタQ4、抵抗R4〜R6、およびダイオードD1である。したがって、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができ、発熱を抑えることができる。すなわち、簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる。

【0133】

さらに、マイコン14、トランジスタQ4、抵抗R4、R5,R7、およびダイオードD2によって、トランジスタQ3のコレクタと抵抗R2との接続点の電圧が監視され、監視される前記接続点の電圧が、トランジスタQ1が遮断状態になる電圧になった時点から経過した時間が計時され、計時された時間が予め定める第2の時間になったとき、トランジスタQ3を遮断状態にするためのRestart信号がトランジスタQ3のベースに出力される。したがって、図2に示した出力遮断回路1、図4に示した出力遮断回路1a、図5に示した出力遮断回路1b、図7に示した出力遮断回路1c、および図8に示した出力遮断回路1dでは、電流制限時にもFail信号が出力されるが、図9に示した出力遮断回路1eは、タイマ時間後シャットダウンされた時点で、Fail信号が出力される。また、入力電圧VINがマイコン14に供給される電圧より高い場合、トランジスタQ3がオフの状態のとき、入力電圧VINが、電流検出用抵抗Rs、および抵抗R1,R2を介して、マイコン14の入力ポートINの印加されることを防止することができる。

【0134】

さらに、制御手段によって、計時手段が含まれ、ゲートの電圧が監視され、監視されるゲートの電圧が、トランジスタQ1が遮断状態になる電圧になった時点から経過した時間が計時され、計時された時間が予め定める第2の時間になったとき、トランジスタQ3を遮断状態にするためのRestart信号がトランジスタQ3のベースに出力される。制御手段は、たとえば出力遮断回路1fでは、マイコン14、および抵抗R8,R9であり、出力遮断回路1gでは、マイコン14、トランジスタQ5、および抵抗R8〜R10である。したがって、タイマ用コンデンサC1を用いることなく、電流制限時間Tdの時間を計時することができるので、部品を減らし、回路を簡単化することができる。

【0135】

さらに、電流検出用抵抗Rsは、ソース、負荷に接続されているドレイン、およびゲート抵抗Rg1,Rg2を介して接地されているゲートを備えるトランジスタQ1のソースに一端が接続され、他端が直流電源に接続されている。PNP型のトランジスタQ2は、エミッタが直流電源に接続され、ベースがトランジスタQ1のソースと電流検出用抵抗Rsとの接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗Rg1,Rg2との接続点に接続され、電流検出用抵抗Rsの電圧降下が予め定める電圧になると、ゲートの電圧が、トランジスタQ1が予め定める電流値の電流を出力する電圧になる電流をゲート抵抗Rg1,Rg2へ供給する。抵抗R12およびタイマ用コンデンサC2によって、ゲートの電圧が、トランジスタQ1が予め定める電流値の電流を出力する電圧になり、出力端子13の電圧が予め定める第3の電圧まで低下した時点から予め定める時間が計時される。PNP型のトランジスタQ3は、エミッタがトランジスタQ1のソースと電流検出用抵抗Rsとの接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗Rg1との接続点に接続され、ベースが抵抗R12およびタイマ用コンデンサC2に接続され、抵抗R12およびタイマ用コンデンサC2によって予め定める時間が計時されたとき、導通状態となる。そして、制御手段によって、ゲートの電圧を分圧した電圧を監視し、監視するゲートの電圧を分圧した電圧が、トランジスタQ1を遮断状態とする電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、トランジスタQ3を遮断状態にするためのRestart信号をトランジスタQ3のベースに出力する。制御手段は、たとえば出力遮断回路1hでは、トランジスタ部Tr1,Tr2、およびマイコン14であり、出力遮断回路1jでは、トランジスタ部Tr1,Tr2、マイコン14、抵抗R10、およびトランジスタQ5である。

【0136】

したがって、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができるので、発熱を抑えることができる。

【0137】

さらに、前記計時手段は、PNP型のトランジスタQ9と、抵抗R12と、抵抗R17と、抵抗R18と、タイマ用コンデンサC1とを含む。トランジスタQ9は、エミッタが電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続されている。抵抗R12は、一端がトランジスタQ9のベースに接続され、他端がドレインに接続されている。抵抗R17は、一端がトランジスタQ9のコレクタに接続されている。抵抗R18は、一端が抵抗R17の他端に接続され、他端が接地されている。そして、タイマ用コンデンサC1は、一端がトランジスタQ3のベース、および抵抗R17と抵抗R18との接続点に接続され、他端が接地されている。

【0138】

さらに、前記計時手段は、ダイオードD3,D4を含む。ダイオードD3,D4は、トランジスタQ9のコレクタと抵抗R17との間に設けられる抵抗R19と、抵抗R17と抵抗R19との接続点の電圧を予め定める第2の電圧、たとえば2VF以下にする。したがって、入力電圧が変動しても、計時手段を構成するタイマ用コンデンサC1を充電する電流の電流値を一定値にすることができ、電流制限時間Tdを一定の時間にすることができる。

【0139】

さらに、出力遮断回路1,1a〜1mのうちのいずれか1つを備えるので、正常時は動作電流がゼロになり、暗電流を小さくすることができ、また、過電流時は出力を遮断して、消費電流を小さくすることができ、バッテリ切れの可能性を低減することができる。

【符号の説明】

【0140】

1,1a〜1m,9 出力遮断回路

10,10a〜10m,90 電源回路

11 直流電源

12 スイッチ

13 出力部

14 マイコン

100 AVN装置100

101 バッテリ

102 オーディオ基板

103 電子回路

105 制御回路

106 フレキシブル基板

C1,C2 タイマ用コンデンサ

Cout コンデンサ

D1〜D4 ダイオード

R1〜R19,Ra,Rb 抵抗

Re エミッタ抵抗

Rg,Rg1,Rg2 ゲート抵抗

Rs 電流検出用抵抗

Q1〜Q9 トランジスタ

Tr1,Tr2 トランジスタ部

【技術分野】

【0001】

本発明は、過電流に対して電源回路を保護する出力遮断回路および電子機器に関する。

【背景技術】

【0002】

図1は、従来の技術による出力遮断回路9を備える電源回路90の回路構成を示す図である。電源回路90は、直流電源11と出力部13との間に、出力遮断回路9の電流検出用抵抗素子(以下「抵抗素子」を単に「抵抗」という)Rsと、PチャネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor:以下単に「トランジスタ」という)Q1からなるスイッチ回路とがこの順序で設けられている。

【0003】

トランジスタQ1は、ソースが電流検出用抵抗Rsに接続され、ドレインが出力部13、および一端が接地されているコンデンサCoutの他端に接続され、ゲートがゲート抵抗を介して接地されている。出力部13には、図示しない負荷が接続されている。トランジスタQ1に過電流が流れていない状態、つまり出力遮断回路9が働いていない状態では、トランジスタQ1のゲート電圧VGは、ほぼグランドレベルになっており、トランジスタQ1を導通状態にしているが、ゲート電流は、ほぼゼロである。

【0004】

出力遮断回路9は、電流検出用抵抗Rsの他に、PNP型のバイポーラトランジスタ(以下単に「トランジスタ」という)Q2と、抵抗R1とを含んで構成されている。トランジスタQ2は、エミッタが直流電源11と電流検出用抵抗Rsとの接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗との接続点に接続され、ベースが抵抗R1の一端に接続されている。抵抗R1の他端は、電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続されている。

【0005】

出力遮断回路9は、トランジスタQ1を流れる電流が増加し、電流検出用抵抗Rsでの電圧降下が規定値以上になったとき、トランジスタQ2を導通状態とすることによって、トランジスタQ1のゲートソース間の電圧差を小さくして、トランジスタQ1を流れる電流を制限する。負荷が地絡したとき、つまり出力部13から出力される出力電流が異常に増大したとき、トランジスタQ2に電流が流れるときのエミッタとベースと間の電圧降下(以下「ベースエミッタ間電圧」という)をVBEとすると、トランジスタQ1を流れる制限された電流の電流値をIlimとすると、制限電流値Ilimは、VBE/Rsで求められる。すなわち、出力遮断回路9は、制限電流値Ilim=VBE/Rsで電流制限をかける。

【0006】

特許文献1に記載されるDC(直流)−DCコンバータの入力回路は、入力回路に流れる電流を制御するためのNチャネルMOSFETと、NチャネルMOSFETに直列に接続されている入力電流検出用抵抗と、入力電流検出用抵抗の両端間の電圧に応じてNチャネルMOSFETのゲート電圧を制御するNPNトランジスタと、NチャネルMOSFETのソースゲート間に設けられるコンデンサとを含んで構成されている。NPNトランジスタは、入力電流検出用抵抗の両端間の電圧に応じたコレクタ電流によって、NチャネルMOSFETのゲート電圧を下げて、NチャネルMOSFETのオン抵抗を制御し、突入電流の防止と入力電流の遮断とを行っている。さらに、入力電流検出用抵抗の電圧を平均化し、平均化した電圧が基準電圧を超えたとき、NPNトランジスタのコレクタ電流を増加させて、NチャネルMOSFETをオフにする回路を有する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3302951号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、入力電圧が高い場合、あるいは制限電流値Llimが大きく設定されている場合、負荷が地絡すると、トランジスタQ1および電流検出用抵抗Rsでの電力損失が増大して許容損失を超えると、トランジスタQ1および電流検出用抵抗Rsが破壊される可能性がある。これを避けるためには、トランジスタQ1および電流検出用抵抗Rsの許容電流および許容電力を大きくする必要がある。許容電流および許容電力が大きい部品は、その大きさが大きくなり、またコストも増大するという問題がある。

【0009】

特許文献1に記載されるDC−DCコンバータの入力回路は、負荷が短絡し、入力電流検出用抵抗の電圧を平均化した電圧が基準電圧を超えたとき、NチャネルMOSFETをオフにすることができるが、平均化した電圧が基準電圧を超えたことを、コンパレータを用いて検出しており、回路規模が大きくなるという問題がある。

【0010】

本発明の目的は、簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる出力遮断回路および電子機器を提供することである。

【課題を解決するための手段】

【0011】

本発明(1)は、入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている電流検出用抵抗素子と、

エミッタが直流電源に接続され、ベースが電流検出用抵抗素子と第1のトランジスタの入力端子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給するPNP型の第2のトランジスタと、

制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になった時点から予め定める時間を計時する計時手段と、

エミッタが接地され、コレクタが第2のトランジスタのベースに接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき導通状態となり、制御端子の電圧が第1のトランジスタが遮断状態となる電圧になる電流を、第1の抵抗素子へ第2のトランジスタに供給させるNPN型の第3のトランジスタとを含むことを特徴とする出力遮断回路である。

【0012】

また本発明(5)は、入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている電流検出用抵抗素子と、

エミッタが直流電源に接続され、ベースが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給するPNP型の第2のトランジスタと、

制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になり、出力端子の電圧が予め定める第3の電圧まで低下した時点から予め定める時間を計時する計時手段と、

エミッタが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき、導通状態となるPNP型の第3のトランジスタと、

制御端子の電圧を分圧した電圧を監視し、監視する制御端子の電圧を分圧した電圧が、第1のトランジスタを遮断状態とする電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、第3のトランジスタを遮断状態にするための遮断信号を第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする出力遮断回路である。

また本発明(8)は、前記出力遮断回路を備える電子機器である。

【発明の効果】

【0013】

本発明(1)によれば、電流検出用抵抗素子は、入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている。PNP型の第2のトランジスタは、エミッタが直流電源に接続され、ベースが電流検出用抵抗素子と第1のトランジスタの入力端子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給する。計時手段によって、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になった時点から予め定める時間が計時される。そして、NPN型の第3のトランジスタは、エミッタが接地され、コレクタが第2のトランジスタのベースに接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき導通状態となり、制御端子の電圧が第1のトランジスタが遮断状態となる電圧になる電流を、第1の抵抗素子へ第2のトランジスタに供給させる。

【0014】

したがって、負荷が地絡している間、電流制限の後、第1のトランジスタをオフとするので、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができるので、発熱を抑えることができる。すなわち、簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる。

【0015】

また本発明(5)によれば、電流検出用抵抗素子は、入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている。PNP型の第2のトランジスタは、エミッタが直流電源に接続され、ベースが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧を第1のトランジスタが予め定める電流値の電流を出力する電圧にするための電流を第1の抵抗素子へ供給する。計時手段によって、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になり、出力端子の電圧が予め定める第3の電圧まで低下した時点から予め定める時間が計時される。PNP型の第3のトランジスタは、エミッタが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき、導通状態となる。そして、制御手段によって、制御端子の電圧を分圧した電圧を監視し、監視する制御端子の電圧を分圧した電圧が、第1のトランジスタを遮断状態とする電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、第3のトランジスタを遮断状態にするための遮断信号を前記第3のトランジスタのベースに出力する。したがって、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができるので、発熱を抑えることができる。

【0016】

また本発明(8)によれば、前記出力遮断回路を備えるので、正常時は動作電流がゼロになり、暗電流を小さくすることができ、また、過電流時は出力を遮断して、消費電流を小さくすることができ、バッテリ切れの可能性を低減することができる。

【図面の簡単な説明】

【0017】

【図1】従来の技術による出力遮断回路9を備える電源回路90の回路構成を示す図である。

【図2】本発明の第1実施形態である出力遮断回路1を備える電源回路10の回路構成を示す図である。

【図3】出力遮断回路1の動作を説明するためのタイムチャートである。

【図4】本発明の第2実施形態である出力遮断回路1aを備える電源回路10aの回路構成を示す図である。

【図5】本発明の第3実施形態である出力遮断回路1bを備える電源回路10bの回路構成を示す図である。

【図6】出力遮断回路1bの動作を説明するためのタイムチャートである。

【図7】本発明の第4実施形態である出力遮断回路1cを備える電源回路10cの回路構成を示す図である。

【図8】本発明の第5実施形態である出力遮断回路1dを備える電源回路10dの回路構成を示す図である。

【図9】本発明の第6実施形態である出力遮断回路1eを備える電源回路10eの回路構成を示す図である。

【図10】出力遮断回路1eの動作を説明するためのタイムチャートである。

【図11】本発明の第7実施形態である出力遮断回路1fを備える電源回路10fの回路構成を示す図である。

【図12】出力遮断回路1fの動作を説明するためのタイムチャートである。

【図13】本発明の第8実施形態である出力遮断回路1gを備える電源回路10gの回路構成を示す図である。

【図14】本発明の第9実施形態である出力遮断回路1hを備える電源回路10hの回路構成を示す図である。

【図15】出力遮断回路1hの動作を説明するためのタイムチャートである。

【図16】本発明の第10実施形態である出力遮断回路1jを備える電源回路10jの回路構成を示す図である。

【図17】本発明の第11実施形態である出力遮断回路1kを備える電源回路10kの回路構成を示す図である。

【図18】出力遮断回路1kの動作を説明するためのタイムチャートである。

【図19】本発明の第12実施形態である出力遮断回路1mを備える電源回路10mの回路構成を示す図である。

【図20】車載用のAVN装置100の構成を示す図である。

【発明を実施するための形態】

【0018】

図2は、本発明の第1実施形態である出力遮断回路1を備える電源回路10の回路構成を示す図である。電源回路10は、直流電源11、スイッチ12、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1を含んで構成されている。

【0019】

直流電源11は、直流電圧、たとえば12Vを出力するバッテリであり、スイッチ12の一端に接続されている。スイッチ12は、一端が直流電源11に接続され、他端が後述する電流検出用抵抗素子Rsの一端に接続され、直流電源11を出力するか否かを切り換えるスイッチである。以下、抵抗素子のことを単に「抵抗」ともいう。

【0020】

第1のトランジスタであるトランジスタQ1は、たとえばPチャネルのMOSFET(Metal Oxide Semiconductor Field Effect Transistor)によって構成されており、入力端子であるソースが後述する電流検出用抵抗Rsの他端に接続され、出力端子であるドレインが出力部13、およびコンデンサCoutの一端に接続され、制御端子であるゲートがゲート抵抗Rgの一端に接続されている。コンデンサCoutは、一端がトランジスタQ1のドレイン、および出力部13に接続され、他端が接地されている。出力部13は、トランジスタQ1のドレイン、およびコンデンサCoutの一端に接続され、さらに図示しない負荷に接続されている。第1の抵抗素子であるゲート抵抗Rgは、一端がトランジスタQ1のゲートに接続され、他端が後述する抵抗R3を介して接地されている。

【0021】

出力遮断回路1は、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R3、トランジスタQ2,Q3、およびタイマ用コンデンサC1を含んで構成されている。電流検出用抵抗素子である電流検出用抵抗Rsは、電流検出用抵抗Rsを流れる電流の電流値を検出するための抵抗であり、一端がスイッチ12の他端に接続され、他端がトランジスタQ1のソースに接続されている。

【0022】

エミッタ抵抗Reは、一端がスイッチ12と電流検出用抵抗Rsとの接続点に接続され、他端がトランジスタQ2のエミッタに接続されている。抵抗R1は、一端が電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、他端がトランジスタQ2のベース、および抵抗R2の一端に接続されている。第2のトランジスタであるトランジスタQ2は、たとえばPNP型のバイポーラトランジスタによって構成され、エミッタがエミッタ抵抗の他端に接続され、ベースが抵抗R1と抵抗R2との接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗Rgとの接続点に接続されている。

【0023】

第2の抵抗素子である抵抗R2は、一端が抵抗R1の他端、およびトランジスタQ2のベースに接続され、他端がトランジスタQ3のコレクタに接続されている。第3のトランジスタであるトランジスタQ3は、たとえばNPN型のバイポーラトランジスタによって構成され、コレクタが抵抗R2に接続され、エミッタが接地され、ベースがゲート抵抗Rgと抵抗R3との接続点、およびタイマ用コンデンサC1の一端に接続されている。抵抗R3は、一端がゲート抵抗Rgの他端、トランジスタQ3のベース、およびタイマ用コンデンサC1の一端に接続され、他端が接地されている。タイマ用コンデンサC1は、一端がゲート抵抗Rgと抵抗R3との接続点、およびトランジスタQ3のベースに接続され、他端が接地されている。ゲート抵抗RgおよびトランジスタQ3は、計時手段を構成する。

【0024】

直流電源11の出力は、スイッチ12を介して、入力電圧VINとして、電流検出用抵抗Rsの一端に印加される。トランジスタQ1のソースには、入力電圧VINよりも電流検出用抵抗Rsでの電圧降下分の電圧だけ低い電圧が印加される。出力部13から負荷に供給される出力電流Ioutが、負荷が必要とする電流値であるとき、電流検出用抵抗Rsでの電圧降下によるトランジスタQ2のエミッタとベースとの電位差が、トランジスタQ2のベースエミッタ間電圧VBE未満であり、トランジスタQ2は遮断状態(以下「オフ」という)である。

【0025】

トランジスタQ2がオフであるとき、トランジスタQ1のゲート電流として流れる電流は、極めて少ないので、直列に接続されているゲート抵抗Rgおよび抵抗R3での電圧降下も小さく、トランジスタQ1のゲート電圧VGは、ほぼ0Vである。トランジスタQ3は、ベースの電圧がほぼ0Vであるのでオフである。トランジスタQ1は、ゲート電圧VGがソース電圧よりも低いので、導通状態(以下「オン」という)である。したがって、出力遮断回路1は、正常な期間、つまり出力電流Ioutとして負荷が必要とする電流値の電流を供給している期間では、負荷電流、つまり出力電流Ioutのみが電源回路10に流れ、トランジスタQ2,Q3には、電流は流れない。

【0026】

図3は、出力遮断回路1の動作を説明するためのタイムチャートである。正常な期間では、ゲート電圧VGおよびトランジスタQ3のベース電圧(図では「Q3ベース」という)は、ほぼ0Vである。出力地絡の期間は、出力部13が地絡している期間である。地絡は、たとえば基板間を接続するフレキシブル基板のコネクタのショート、あるいは基板上での半田くずによるショートなどによって発生する。

【0027】

時刻t1に負荷が地絡すると、出力電流Ioutが増大する。出力電流Ioutが増大すると、電流検出用抵抗Rsでの電圧降下が増加する。電流検出用抵抗Rsでの電圧降下が予め定める電圧になると、トランジスタQ2は、直流電源11から供給される電流をコレクタ電流Icとしてゲート抵抗Rgに流す。予め定める電圧は、エミッタ抵抗での電圧降下と、トランジスタQ2のベースエミッタ間電圧VBEと、抵抗R1での電圧降下とを加算した電圧である。コレクタ電流Icがゲート抵抗Rgに流れると、ゲート電圧VGが上昇し、トランジスタQ1のゲートソース間の電圧差が少なくなるので、出力電流Ioutが制限電流値Ilimで制限される。電流制限の期間の時間(以下「電流制限時間」という)Tdは、ゲート抵抗の抵抗値およびタイマ用コンデンサC1の静電容量で決まる。すなわち、電流制限時間Tdは、タイマ用コンデンサC1をゲート抵抗Rgから流れる電流で充電し、タイマ用コンデンサC1の両端電圧がトランジスタQ3のベースエミッタ間電圧VBEになるまでの時間である。ベースエミッタ間電圧VBEは、約0.6Vである。

【0028】

ゲート抵抗Rgを流れる電流の一部がタイマ用コンデンサC1を充電し、トランジスタQ3のベース電圧が上昇する。トランジスタQ3のベース電圧が上昇し、時刻t2に、ベース電圧が、トランジスタQ3のベースエミッタ間電圧VBEに達すると、トランジスタQ3はオンになる。トランジスタQ3がオンになると、トランジスタQ2のベース電流が増加し、トランジスタQ2はフルオン状態、つまり短絡状態となる。トランジスタQ2がフルオン状態になると、トランジスタQ1のゲートソース間の電圧がほぼ0Vとなり、トランジスタQ1はオフし、シャットダウンの期間に入る。

【0029】

地絡した直後の出力電流Ioutの制限電流値Ilimは、トランジスタQ1のゲートソース間の電圧をVGSとし、トランジスタQ2のコレクタ電流をIcとし、トランジスタQ2のベースエミッタ間電圧VBEをVBE2とし、トランジスタQ2の電流増幅率をβとすると、式(1),(2)が成立する。

VIN=Rs×Ilim+VGS+Rg×Ic …(1)

Rs×Ilim=Re×Ic+VBE2+R1×(Ic/β) …(2)

【0030】

トランジスタQ2のベース電流Ic/β≒0とすると、式(1),(2)から式(3)が成立する。

Ilim=VBE2/Rs+Re×(VIN−VGS−VBE)

/((Rg+Re)×Rs) …(3)

【0031】

ここで、式(3)のエミッタ抵抗Reの抵抗値が0オームである場合、Ilim=VBE2/Rsとなる。トランジスタQ2のベースエミッタ間電圧VBE2は、−2mV/度Cの温度特性があるので、高温になると、制限電流値Ilimは低下する。また。式(3)からエミッタ抵抗Reが0オームでない場合、第2項の分だけ制限電流値Ilimが大きく、その分トランジスタQ2の温度特性を小さくすることができる。制限電流値Ilimは、予め定める電流値である。

【0032】

抵抗R2,R3,Rg、トランジスタQ3、およびタイマ用コンデンサC1は、タイマラッチ回路を構成し、ゲート電圧VGが上昇し電流制限を開始した時点から電流制限時間Tdを計時し、電流制限時間Tdが計時された時点で、トランジスタQ2をフルオン状態として、トランジスタQ1をオフとし、トランジスタQ1をシャットダウン状態とする。

【0033】

このように、出力遮断回路1は、出力電流Ioutを制限電流値Ilimに制限する電流制限機能と、トランジスタQ1を強制的にオフにするシャットダウン機能とを兼ね備えている。そして、ゲート抵抗Rgは、トランジスタQ1のゲート電圧VGをバイアスするゲートバイアス機能と、タイマ用コンデンサC1を充電する機能とを兼ね備えており、出力遮断回路1は、より簡単な回路構成で実現することができる。

【0034】

図4は、本発明の第2実施形態である出力遮断回路1aを備える電源回路10aの回路構成を示す図である。電源回路10aは、図2に示した電源回路10に、出力電圧VOUTを検出するための抵抗Ra,Rbを追加した回路である。出力遮断回路1aは、図2に示した出力遮断回路1と同じ回路構成である。出力遮断回路1aを除く電源回路10aの構成要素のうち図2に示した電源回路10の構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0035】

図2に示した電源回路10は、負荷が地絡し、シャットダウンの期間に入ると、負荷での地絡が解除されても、トランジスタQ2,Q3ともオンの状態を維持するので、シャットダウンの状態(以下「シャットダウン状態」という)を解除するためには、一旦スイッチ12を切断した後、再度接続する必要がある。これを可能とするために、電源回路10aは、出力電圧VOUTを抵抗Ra,Rbで分圧した電圧を、たとえばマイクロコンピュータ(以下「マイコン」という)によって監視し、出力電圧VOUTがグランドレベルまで下がったとき、負荷が地絡したと判断し、マイコンによってスイッチ12を一旦切断した後、再度接続する。電源回路10aは、正常な期間でも、抵抗Ra,Rbに電流が流れるので、無駄な消費電流が発生する。

【0036】

図5は、本発明の第3実施形態である出力遮断回路1bを備える電源回路10bの回路構成を示す図である。電源回路10bは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1bを含んで構成されている。電源回路10bの構成要素のうち図2に示した電源回路10の構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0037】

出力遮断回路1bは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R3、トランジスタQ2,Q3、タイマ用コンデンサC1、およびマイコン14を含んで構成されている。出力遮断回路1bの構成要素のうち図2に示した出力遮断回路1の構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0038】

マイコン14は、ゲート電圧VGがFail信号として入力ポートINまたはアナログデジタル変換ポートADに入力され、出力ポートOUTからRestart信号がトランジスタQ3のベースに出力される。遮断信号であるRestart信号は、トランジスタQ1のシャットダウン状態を解除するための信号である。

【0039】

制御手段であるマイコン14は、たとえば図示しない中央処理装置(以下「CPU」という)および図示しない記憶装置を含んで構成され、CPUは、記憶装置に記憶されるプログラムを実行することによって、Fail信号を監視し、Fail信号に基づいて、Restart信号の出力を制御する。マイコン14は、Fail信号、つまりゲート電圧VGがトランジスタQ1をオフとする電圧になったとき、シャットダウン状態になったことを検出する。マイコン14は、ゲート電圧VGがトランジスタQ1をオフとする電圧になった時点から、たとえば予め定める第2の時間を計時し、予め定める第2の時間が計時されたときに、Restart信号を出力する。シャットダウンするまでの時間、つまり電流制限時間Tdは、数ms〜数十msであるが、予め定める第2の時間は、電流制限時間Tdより長い時間であってもよい。

【0040】

図6は、出力遮断回路1bの動作を説明するためのタイムチャートである。時刻t1に、負荷に地絡が発生してから、時刻t2に、トランジスタQ1がオフになり、シャットダウンの期間に入るまでの動作は、図3に示したタイムチャートでの動作と同じであり、説明は省略する。

【0041】

マイコン14は、Fail信号によって、ゲート電圧VGがトランジスタQ1をオフとする電圧になったことを検出し、Restart信号をローレベル(図6では、Restart信号をハイレベルで表わしている)とすることによって、トランジスタQ3をオフとする。トランジスタQ3がオフになると、トランジスタQ2のベース電流が減少するので、トランジスタQ2のコレクタ電流が減少する。トランジスタQ2のコレクタ電流が減少すると、ゲート電圧VGが下がり、トランジスタQ1はオンとなる。

【0042】

負荷の地絡が解除されていない場合、トランジスタQ1がオンとなると、地絡がないときに負荷が必要とする電流よりも多い電流が流れるので、トランジスタQ2はオンの状態を継続する。すなわち、トランジスタQ2は、トランジスタQ1を制限電流値Ilimで電流制限を行う。

【0043】

トランジスタQ3のベース電圧は、Restart信号によってグランドレベルまで下げられているが、時刻t4にRestart信号が解除されると、トランジスタQ2のコレクタ電流Icが継続してゲート抵抗に供給されているので、コレクタ電流Icの一部がタイマ用コンデンサC1に充電される。Restart信号が解除されてから電流制限時間Tdが経過した時刻t5に、トランジスタQ3が再びオンとなり、トランジスタQ1をオフとする。

【0044】

時刻t6に負荷の地絡が解除されている場合、Restart信号が出力されると、トランジスタQ3がオフになり、トランジスタQ1はオンとなる。トランジスタQ1がオンとなったとき、負荷の地絡が解除されて出力電流Ioutが減少しているので、電流検出用抵抗Rsを流れる電流は、地絡がないときに負荷が必要とする電流になっており、電流検出用抵抗Rsでの電圧降下が下がり、トランジスタQ2はオフとなり、電源回路10bは、正常な状態に復帰する。

【0045】

出力遮断回路1bは、電流制限のみを継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができ、発熱を抑えることができる。また、シャットダウン状態になってから予め定める第2の時間が経過したときに、Restart信号によってトランジスタQ3をオフにしているので、負荷での地絡が解除されていれば、電源回路10bを正常な状態に復帰させることができる。

【0046】

また、電流制限を行うことなく、いきなりシャットダウンするのではなく、電流制限を行った後シャットダウンするので、負荷に静電容量の大きいコンデンサがあるときに生じるラッシュ電流を防止することができ、また瞬間的な過電流の場合に、シャットダウンすることを防止することができる。

【0047】

図7は、本発明の第4実施形態である出力遮断回路1cを備える電源回路10cの回路構成を示す図である。電源回路10cは、図5に示した電源回路10bの変形例である。図5に示した電源回路10bは、入力電圧VINがマイコン14に供給される電圧よりも低い場合に適用されるが、入力電圧VINがマイコン14に供給される電圧よりも高い場合、トランジスタQ2がオンになると、トランジスタQ1のゲート電圧VGがマイコン14に供給される電圧よりも高くなるため、ゲート電圧VGを直接マイコン14に入力することができない。電源回路10cは、ゲート電圧VGを直接マイコン14に入力することができる電圧に下げてマイコン14に入力している。

【0048】

電源回路10cは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1cを含んで構成されている。電源回路10bの構成要素のうち図5に示した電源回路10bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0049】

ゲート抵抗Rg1は、一端がトランジスタQ1のゲート、およびトランジスタQ2のコレクタに接続され、他端がゲート抵抗Rg2の一端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続されている。ゲート抵抗Rg2は、一端がゲート抵抗Rg1の他端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続され、他端が抵抗R3の一端、タイマ用コンデンサC1の一端、トランジスタQ3のベース、および後述するトランジスタQ4のコレクタに接続されている。

【0050】

第1の抵抗素子であるゲート抵抗Rg1,Rg2は、入力電圧VINがマイコンに供給される電圧よりも高い場合、図2に示した電源回路10で用いられるゲート抵抗Rgの代わりに用いられるゲート抵抗であり、マイコン14に入力するFail信号の電圧が、マイコンに供給される電圧よりも低い電圧になるように分圧する。

【0051】

出力遮断回路1cは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R5、トランジスタQ2〜Q4、タイマ用コンデンサC1、およびマイコン14を含んで構成されている。出力遮断回路1cの構成要素のうち図5に示した出力遮断回路1bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0052】

トランジスタQ4は、たとえばNPN型のバイポーラトランジスタであり、コレクタが抵抗R3の一端、タイマ用コンデンサC1の一端、トランジスタQ3のベース、およびゲート抵抗Rg2の他端に接続され、エミッタが接地され、ベースが抵抗R4の一端および抵抗R5の一端に接続されている。抵抗R4は、一端がトランジスタQ4のベース、および抵抗R5の一端に接続され、他端がマイコン14の出力ポートOUTに接続されている。抵抗R5は、一端がトランジスタQ4のベース、および抵抗R4の一端に接続され、他端が接地されている。マイコン14、トランジスタQ4、および抵抗R4,R5は、制御手段である。

【0053】

図5に示したマイコン14は、Restart信号をローレベルで出力したが、図7に示したマイコン14は、Restart信号をハイレベルで出力する。Restart信号が出力されると、トランジスタQ4がオンになり、トランジスタQ3のベース電圧をグランドレベルまで下げて、トランジスタQ3をオフにする。

【0054】

図8は、本発明の第5実施形態である出力遮断回路1dを備える電源回路10dの回路構成を示す図である。電源回路10dは、図5に示した電源回路10bの変形例であり、電源回路10cと同様に、ゲート電圧VGを直接マイコン14に入力することができる電圧に下げてマイコン14に入力している。

【0055】

電源回路10dは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1dを含んで構成されている。電源回路10dの構成要素のうち図5に示した電源回路10bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0056】

出力遮断回路1dは、図7に示した出力遮断回路1cの変形例であり、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R6、トランジスタQ2〜Q4、タイマ用コンデンサC1、マイコン14、およびダイオードD1を含んで構成されている。出力遮断回路1dの構成要素のうち図7に示した出力遮断回路1cの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0057】

抵抗R6は、一端がトランジスタQ1のゲート、トランジスタQ2のコレクタ、ゲート抵抗Rgの一端に接続され、他端がマイコン14の入力ポートINまたはアナログデジタル変換ポートAD、およびダイオードD1のカソードに接続されている。ダイオードD1は、たとえばツェナーダイオードによって構成され、アノードが接地され、カソードが抵抗R6の他端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続されている。

【0058】

入力電圧VINがマイコンに供給される電圧よりも高い場合、出力遮断回路1dは、抵抗R6とダイオードD1によって、マイコン14に入力するFail信号の電圧を、マイコンに供給される電圧よりも低い電圧になるようにしている。マイコン14、トランジスタQ4、抵抗R4〜R6、およびダイオードD1は、制御手段である。

【0059】

出力遮断回路1bは、正常な期間では、負荷電流、つまり出力電流Ioutのみが電源回路10bに流れ、トランジスタQ2,Q3には、電流は流れない。また、出力遮断回路1c,1dは、正常な期間では、負荷電流のみが電源回路10c,10dに流れ、トランジスタQ2〜Q4には、電流は流れない。

【0060】

図9は、本発明の第6実施形態である出力遮断回路1eを備える電源回路10eの回路構成を示す図である。上述した実施の形態では、マイコン14は、ゲート電圧VGを監視して、トランジスタQ1がオフになり、シャットダウン状態になったことを検出したが、出力遮断回路1eは、トランジスタQ3のコレクタの電圧を監視してシャットダウン状態になったことを検出する。

【0061】

電源回路10eは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1eを含んで構成されている。電源回路10eの構成要素のうち図8に示した電源回路10dの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0062】

出力遮断回路1eは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1〜R5,R7、トランジスタQ2〜Q4、タイマ用コンデンサC1、マイコン14、およびダイオードD2を含んで構成されている。出力遮断回路1eの構成要素のうち図8に示した出力遮断回路1dの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0063】

ダイオードD2は、アノードがマイコン14の入力ポートINまたはアナログデジタル変換ポートAD、および抵抗R7の一端に接続され、カソードが抵抗R2とトランジスタQ3のコレクタとの接続点に接続されている。抵抗R7は、一端がマイコン14の入力ポートINまたはアナログデジタル変換ポートAD、およびダイオードD2のアノードに接続され、他端に、マイコン14に印加される直流電圧VDDが印加されている。

【0064】

マイコン14は、Fail信号として、トランジスタQ3のコレクタの電圧を監視している。Fail信号がローレベルになると、シャットダウンが行われたこと、すなわちトランジスタQ1がオフになったことを検出することができる。

【0065】

ダイオードD2は、入力電圧VINがマイコン14に印加される直流電圧VDDよりも高い場合、トランジスタQ3がオフのときに、入力電圧VINが、直流電圧VDD以上の電圧で、電流検出用抵抗Rsおよび抵抗R1,R2を介してマイコン14の入力ポートINまたはアナログデジタル変換ポートADに印加されることを防止するために設けられるダイオードである。マイコン14、トランジスタQ4、抵抗R4、R5,R7、およびダイオードD2は、制御手段である。

【0066】

図10は、出力遮断回路1eの動作を説明するためのタイムチャートである。このタイムチャートは、図6に示したタイムチャートと、Fail信号を除いて同じである。Fail信号は、トランジスタQ3のコレクタの電圧を表す信号であるので、トランジスタQ3がオンの期間、つまりシャットダウンの期間だけ、ローレベルとなる。

【0067】

図11は、本発明の第7実施形態である出力遮断回路1fを備える電源回路10fの回路構成を示す図である。上述した実施の形態では、電流制限時間Tdを、タイマ用コンデンサC1を用いて計時したが、出力遮断回路1fは、マイコン14が電流制限時間Tdを計時する。

【0068】

電源回路10fは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1fを含んで構成されている。電源回路10fの構成要素のうち図5に示した電源回路10bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0069】

ゲート抵抗Rg1は、一端がトランジスタQ1のゲート、およびトランジスタQ2のコレクタに接続され、他端がゲート抵抗Rg2の一端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続されている。ゲート抵抗Rg2は、一端がゲート抵抗Rg1の他端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続され、他端が接地されている。

【0070】

ゲート抵抗Rg1,Rg2は、入力電圧VINがマイコン14に供給される電圧よりも高い場合、図5に示した電源回路10bで用いられるゲート抵抗Rgの代わりに用いられるゲート抵抗であり、マイコン14に入力するFail信号の電圧が、マイコン14に供給される電圧よりも低い電圧になるように分圧する。

【0071】

出力遮断回路1fは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1,R2,R8,R9、トランジスタQ2,Q3、およびマイコン14を含んで構成されている。出力遮断回路1fの構成要素のうち図5に示した出力遮断回路1bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0072】

抵抗R8は、一端がトランジスタQ3のベース、および抵抗R9の一端に接続され、他端がマイコン14の出力ポートOUTに接続されている。抵抗R9は、一端がトランジスタQ3のベース、および抵抗R8の一端に接続され、他端が接地されている。

【0073】

マイコン14は、Fail信号によってゲート電圧VGを監視し、ゲート電圧VGをゲート抵抗Rg1とゲート抵抗Rg2とで分圧した電圧が、ゲート電圧VGが制限電圧になる電圧になったとき、電流制限が行われたこと、すなわちトランジスタQ2がオンになったことを検出する。制限電圧は、ゲート電圧VGがトランジスタQ1を制限電流値Ilimの出力電流を出力させる電圧である。マイコン14は、正常の期間、およびRestart信号を出力するときに、ローレベルを出力し、トランジスタQ3をオン、そしてトランジスタQ1をオフにして、シャットダウン状態とするときに、ハイレベルを出力する。マイコン14、および抵抗R8,R9は、制御手段である。

【0074】

抵抗R2およびトランジスタQ3は、ラッチ回路を構成し、電流制限時間Tdが計時された時点で、トランジスタQ2をフルオン状態として、トランジスタQ1をオフとし、トランジスタQ1をシャットダウン状態とする。

【0075】

図12は、出力遮断回路1fの動作を説明するためのタイムチャートである。時刻t11に負荷が地絡すると、トランジスタQ2がオンとなり、コレクタ電流Icがゲート抵抗Rg1,Rg2に供給され、ゲート電圧VGが上昇する。ゲート電圧VGが上昇すると、トランジスタQ1の出力電流IOUTが制限電流値Ilimに制限される。このとき、ゲート電圧VGをゲート抵抗Rg1とゲート抵抗Rg2とで分圧した電圧が上昇して、電流制限が行われる電圧になるので、マイコン14は、電流制限が行われたことを検出することができる。

【0076】

マイコン14は、電流制限が行われたことを検出してから、電流制限時間Tdを計時し、電流制限時間Tdが経過した時刻t12に、Restart信号をローレベルからハイレベルに変化させて、トランジスタQ3をオンとする。トランジスタQ3がオンになると、トランジスタQ2はフルオン状態となり、トランジスタQ1をオフし、シャットダウン状態とする。トランジスタQ1がオフになる。このとき、ゲート電圧VGは、トランジスタQ1をオフになる電圧まで上昇している。

【0077】

マイコン14は、トランジスタQ1をシャットダウンしてから、予め定める第2の時間を計時し、予め定める第2の時間を計時した時刻t13に、Restart信号をハイレベルからローレベルに変化させる。Restart信号がローレベルになると、トランジスタQ3はオフとなり、トランジスタQ1はオンとなる。しかし、負荷の地絡が解除されていないと、トランジスタQ2はオンのままで、電流制限がかかった状態になる。

【0078】

マイコン14は、ゲート電圧VGがシャットダウンの状態の電圧から電流制限の状態の電圧に下がったことを時刻t14に検出すると、まだ負荷の地絡が解除されていないので、電流制限時間Tdを計時し、電流制限時間Tdが経過した時刻t15に、Restart信号をローレベルからハイレベルに変化させ、トランジスタQ1を再びオフとし、シャットダウン状態とする。

【0079】

マイコン14は、トランジスタQ1をオフしてから、予め定める第2の時間を計時し、予め定める第2の時間を計時した時刻t17に、Restart信号をハイレベルからローレベルに変化させる。時刻t15と時刻t17との間の時刻t16に負荷の地絡が解除されていると、時刻t17にRestart信号がローレベルになり、トランジスタQ3がオフ、そしてトランジスタQ1がオンになったとき、トランジスタQ2はオフになり、電源回路10fは、正常な動作を再開する。

【0080】

出力遮断回路1fは、タイマ用コンデンサC1が不要であり、回路構成を簡単化することができる。

【0081】

図13は、本発明の第8実施形態である出力遮断回路1gを備える電源回路10gの回路構成を示す図である。電源回路10gは、図11に示した電源回路10fの変形例である。電源回路10gは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1gを含んで構成されている。電源回路10gの構成要素のうち図11に示した電源回路10fの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0082】

出力遮断回路1gは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1,R2,R8〜R10、トランジスタQ2,Q3,Q5、およびマイコン14を含んで構成されている。出力遮断回路1gの構成要素のうち図11に示した出力遮断回路1fの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0083】

トランジスタQ5は、たとえばNPN型のバイポーラトランジスタであり、ベースがゲート抵抗Rg1とゲート抵抗Rg2との接続点に接続され、コレクタが抵抗R10の一端、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続され、エミッタが接地されている。抵抗R10は、一端がトランジスタQ5のコレクタ、およびマイコン14の入力ポートINまたはアナログデジタル変換ポートADに接続されて、他端に、マイコン14に印加される直流電圧VDDが印加されている。

【0084】

トランジスタQ2がオフのとき、つまりゲート電圧VGがほぼ0Vのとき、トランジスタQ5はオフで、コレクタの電圧、つまりFail信号は、ハイレベルである。トランジスタQ2がオンになり、電流制限が行われると、Fail信号は、ゲート電圧VGが制限電圧になる電圧である。トランジスタQ3がオンになりシャットダウンの状態になると、グランドレベルになる。マイコン14は、Fail信号の電圧を監視することによって、正常の状態か、電流制限の状態か、シャットダウン状態かを検出することができる。マイコン14、トランジスタQ5、および抵抗R8〜R10は、制御手段である。

【0085】

出力遮断回路1fは、正常な期間では、負荷電流のみが電源回路10fに流れ、トランジスタQ2,Q3には、電流は流れない。また、出力遮断回路1gは、正常な期間では、負荷電流のみが電源回路10gに流れ、トランジスタQ2,Q3,Q5には、電流は流れない。

【0086】

図14は、本発明の第9実施形態である出力遮断回路1hを備える電源回路10hの回路構成を示す図である。図14(a)は、電源回路10hの回路構成を示す図である。電源回路10hは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1hを含んで構成されている。電源回路10hの構成要素のうち図11に示した電源回路10fの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0087】

出力遮断回路1hは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R11,R12、トランジスタQ2,Q6、タイマ用コンデンサC2、マイコン14,およびトランジスタ部Tr1,Tr2を含んで構成されている。出力遮断回路1hは、図5に示した出力遮断回路1bのトランジスタQ3およびタイマ用コンデンサC1の代わりに、トランジスタQ6およびタイマ用コンデンサC2を用いる回路である。出力遮断回路1hの構成要素のうち図5に示した出力遮断回路1bの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0088】

上述したタイマ用コンデンサC1は、ゲート電圧VGの上昇を契機に電流制限時間Tdを計時するコンデンサであるが、タイマ用コンデンサC2は、出力電圧VOUTの低下を契機に電流制限時間Tdを計時するコンデンサである。

【0089】

図14(b)は、トランジスタ部Tr1の構成を示す図であり、図14(c)は、トランジスタ部Tr2の構成を示す図である。トランジスタ部Tr1は、トランジスタQ7、および抵抗R13,R14によって構成されている。トランジスタQ7は、たとえばPNP型のバイポーラトランジスタによって構成され、ベースが抵抗R13の一端、および抵抗R14の一端に接続され、エミッタが抵抗R13の他端、および電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、コレクタがトランジスタQ6のベースに接続されている。

【0090】

トランジスタ部Tr2は、トランジスタQ8、および抵抗R15,R16によって構成されている。トランジスタQ8は、たとえばNPN型のバイポーラトランジスタによって構成され、ベースが抵抗R15の一端、および抵抗R16の一端に接続され、エミッタが抵抗R15の他端に接続されているとともに、接地され、コレクタが抵抗R14の他端に接続されている。抵抗R16は、他端がマイコン14の出力ポートOUTに接続されている。

【0091】

トランジスタQ6は、たとえばPNP型のバイポーラトランジスタであり、エミッタが電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、ベースがトランジスタQ7のコレクタに接続され、コレクタがトランジスタQ2のコレクタ、トランジスタQ1のゲート、およびゲート抵抗Rg1の一端に接続されている。タイマ用コンデンサC2は、一端が電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、他端がトランジスタQ6のベースとトランジスタQ7のコレクタとの接続点に接続されている。

【0092】

抵抗R11は、一端が電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、他端がトランジスタQ6のベースとトランジスタQ7のコレクタとの接続点に接続されている。抵抗R12は、一端がトランジスタQ6のベースとトランジスタQ7のコレクタとの接続点に接続され、他端がトランジスタQ1のドレインと出力部13との接続点に接続されている。トランジスタ部Tr1,Tr2、およびマイコン14は、制御手段である。抵抗R12およびタイマ用コンデンサC2は、計時手段である。

【0093】

抵抗R11,R12、トランジスタQ6、およびタイマ用コンデンサC2は、タイマラッチ回路を構成し、電流制限を開始したことによって出力電圧VOUTが予め定める第3の電圧まで低下した時点から電流制限時間Tdを計時し、電流制限時間Tdが計時された時点で、トランジスタQ1をオフとし、トランジスタQ1をシャットダウン状態とする。

【0094】

図15は、出力遮断回路1hの動作を説明するためのタイムチャートである。トランジスタQ1がオンの状態で、負荷が短絡していないとき、トランジスタQ6のベース電圧はほぼトランジスタQ6のエミッタと同じ電圧であり、トランジスタQ6はオフの状態である。

【0095】

時刻t21に負荷が地絡すると、出力電流Ioutが増大する。出力電流Ioutが増大すると、電流検出用抵抗Rsでの電圧降下が増加する。電流検出用抵抗Rsでの電圧降下が、予め定める電圧になると、トランジスタQ2にベース電流が流れ、トランジスタQ2は、直流電源11から供給される電流をコレクタ電流Icとしてゲート抵抗Rg1,Rg2に流し、ゲート電圧VGは上昇する。ゲート電圧VGが上昇し、制限電圧になると、トランジスタQ1のゲートソース間の電圧差が少なくなるので、出力電流Ioutが制限電流値Ilimで制限される。予め定める電圧は、エミッタ抵抗での電圧降下とトランジスタQ2のベースエミッタ間電圧VBEとを加算した電圧である。

【0096】

また、時刻t21に負荷が地絡すると、出力電流Ioutが制限電流値Ilimで制限され、出力電圧VOUTが低下するので、トランジスタQ6のベース電圧(図では「Q6ベース」という)は、低下を開始する。電流制限時間Tdが経過した時刻t22に、トランジスタQ6のベースとエミッタとの間の電圧がベースエミッタ間電圧VBEになると、ベース電流が流れ、トランジスタQ6がオンになる。トランジスタQ6がオンになると、トランジスタQ1のゲート電圧VGとソース電圧との差がなくなり、トランジスタQ1はオフになり、シャットダウン状態となる。電流制限時間Tdは、抵抗R12の抵抗値およびタイマ用コンデンサC2の静電容量で決まる。

【0097】

マイコン14が、Restart信号をハイレベルとすると、トランジスタQ8がオン、そしてトランジスタQ7がオンとなる。トランジスタQ7がオンになると、トランジスタQ6のベース電圧とエミッタ電圧とがほぼ同じ電圧になるので、トランジスタQ6がオフとなる。トランジスタQ6がオフになると、ゲート電圧VGが制限電圧まで下がり、トランジスタQ1がオンとなり、シャットダウン状態が解除される。

【0098】

負荷の地絡が解除されていない場合、電流検出用抵抗Rsでの電圧降下は、エミッタ抵抗での電圧降下とトランジスタQ2のベースエミッタ間電圧VBEとを加算した電圧であり、トランジスタQ2はオンの状態を継続する。すなわち、トランジスタQ2は、トランジスタQ1がオンになっているので、電流制限を行う。トランジスタQ6のベース電圧とエミッタ電圧とは、Restart信号によってほぼ同じ電圧にされているが、時刻t24にRestart信号が解除されても、電流制限が行われており、抵抗R12の負荷側、つまり出力電圧VOUTが低下しているので、タイマ用コンデンサC2が接続されているトランジスタQ6のベース電圧が低下し始める。Restart信号が解除されてから電流制限時間Tdが経過した時刻t25に、トランジスタQ6が再びオンとなり、トランジスタQ1をオフとする。

【0099】

時刻t26で負荷の地絡が解除された場合、Restart信号が出力されると、トランジスタQ6がオフになり、トランジスタQ1はオンとなる。トランジスタQ1がオンとなったとき、負荷の地絡が解除されて出力電流Ioutが減少しているので、電流検出用抵抗Rsでの電圧降下はエミッタ抵抗での電圧降下とトランジスタQ2のベースエミッタ間電圧VBEとを加算した電圧未満になっており、トランジスタQ2はオフとなる。電源回路10hは、正常な状態に復帰する。

【0100】

図16は、本発明の第10実施形態である出力遮断回路1jを備える電源回路10jの回路構成を示す図である。電源回路10jは、図14に示した電源回路10hの変形例である。電源回路10jは、直流電源11、トランジスタQ1、ゲート抵抗Rg1,Rg2、コンデンサCout、出力部13および出力遮断回路1jを含んで構成されている。電源回路10jの構成要素のうち図14に示した電源回路10hの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0101】

出力遮断回路1hは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R10〜R12、トランジスタQ2,Q5,Q6、タイマ用コンデンサC2、マイコン14,およびトランジスタ部Tr1,Tr2を含んで構成されている。出力遮断回路1jの構成要素のうち図14に示した出力遮断回路1hの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。トランジスタQ5および抵抗R10は、図13に示したトランジスタQ5および抵抗R10と同じである。トランジスタ部Tr1,Tr2、マイコン14、抵抗R10、およびトランジスタQ5は、制御手段である。

【0102】

出力遮断回路1hは、正常な期間では、負荷電流のみが電源回路10hに流れ、トランジスタQ2,Q6〜Q8には、電流は流れない。また、出力遮断回路1jは、正常な期間では、負荷電流のみが電源回路10jに流れ、トランジスタQ2,Q5〜Q8には、電流は流れない。

【0103】

図17は、本発明の第11実施形態である出力遮断回路1kを備える電源回路10kの回路構成を示す図である。上述したタイマ用コンデンサC1による電流制限時間Tdの計時は、ゲート電圧VGの上昇を契機に行ったが、出力遮断回路1kでは、出力電圧VOUTの低下を契機に行う。

【0104】

電源回路10kは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1kを含んで構成されている。電源回路10kの構成要素のうち図9に示した電源回路10eの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0105】

出力遮断回路1kは、図9に示した出力遮断回路1eの変形例である。出力遮断回路1kは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1,R2,R4,R5,R7,R11,R12,R17,R18、トランジスタQ2〜Q4,Q9、タイマ用コンデンサC1、マイコン14、およびダイオードD2を含んで構成されている。出力遮断回路1kの構成要素のうち図9に示した出力遮断回路1eの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0106】

第4のトランジスタであるトランジスタQ9は、たとえばPNP型のバイポーラトランジスタによって構成され、エミッタが電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、ベースが抵抗R11の一端、および抵抗R12の一端に接続され、コレクタが抵抗17の一端に接続されている。抵抗R11は、一端がトランジスタQ9のベース、および抵抗R12の一端に接続され、他端が電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続されている。第3の抵抗素子である抵抗R12は、一端がトランジスタQ9のベース、および抵抗R12の一端に接続され、他端がトランジスタQ1のドレインと出力部13との接続点に接続されている。

【0107】

第4の抵抗素子である抵抗17は、一端がトランジスタQ9のコレクタに接続され、他端が抵抗18の一端に接続されている。第5の抵抗素子である抵抗18は、一端が抵抗17の他端に接続され、他端が接地されている。トランジスタQ3のベース、コンデンサであるタイマ用コンデンサC1の一端、およびトランジスタQ4のコレクタは、図9に示した出力遮断回路1eでは、ゲート抵抗Rgと抵抗R3との接続点に接続されているが、出力遮断回路1kでは、抵抗R17と抵抗R18との接続点に接続されている。

【0108】

抵抗R1,R2,R11,R12,R17,R18、トランジスタQ3,Q9、およびタイマ用コンデンサC1は、タイマラッチ回路を構成し、電流制限を開始したことによって出力電圧VOUTが低下した時点から電流制限時間Tdを計時し、電流制限時間Tdが計時された時点で、トランジスタQ1をオフとし、トランジスタQ1をシャットダウン状態とする。

【0109】

図17に示した出力遮断回路1kは、ゲート電圧VGが上昇しても、回路上、コンデンサC1へ電流が流れないため、出力電流Ioutの増加に応じて計時を開始する構成としている。

【0110】

図18は、出力遮断回路1kの動作を説明するためのタイムチャートである。タイムチャートそのものは、図6に示したタイムチャートと同じであり、タイマラッチ回路の動作の相違点のみを説明する。負荷が短絡していない状態では、トランジスタQ1のドレインの電圧は、ほぼソースの電圧に等しいので、トランジスタQ9は、オフである。

【0111】

時刻t1に負荷が地絡すると、トランジスタQ2がオンとなり、出力電流Ioutが制限電流値Ilimで制限される。出力電流Ioutが制限電流値Ilimで制限されると、出力電圧VOUTが低下するので、抵抗R12によって、トランジスタQ9のベースにベース電流が流れ、トランジスタQ9がオンになる。

【0112】

トランジスタQ9がオンになると、タイマ用コンデンサC1の電圧が、抵抗R17の抵抗値とタイマ用コンデンサC1の静電容量との積で決まる時定数で上昇し、時刻t2にベースエミッタ間電圧VBEになると、トランジスタQ3がオンとなる。トランジスタQ3がオンになると、トランジスタQ2のベース電流が増加し、トランジスタQ2はフルオン状態となる。トランジスタQ2がフルオン状態になると、トランジスタQ1のゲートソース間の電圧がほぼ0Vとなり、トランジスタQ1はオフし、シャットダウン状態となる。

【0113】

マイコン14が、Restart信号をハイレベルとし、トランジスタQ4をオンとすることによって、トランジスタQ3をオフとする。トランジスタQ3がオフになると、トランジスタQ2のベース電流が減少するので、トランジスタQ2のコレクタ電流が減少する。トランジスタQ2のコレクタ電流が減少すると、ゲート電圧VGが下がり、トランジスタQ1はオンとなる。

【0114】

負荷の地絡が解除されていない場合、トランジスタQ2はオンの状態を継続し、出力電流Ioutは、制限電流値Ilimに制限されているので、トランジスタQ9は、オンの状態を継続する。トランジスタQ3のベース電圧は、Restart信号によってグランドレベルまで下げられているが、時刻t4にRestart信号が解除されると、トランジスタQ9の電流が抵抗17に供給されるので、タイマ用コンデンサC1の電圧が上昇する。Restart信号が解除されてから電流制限時間Tdが経過した時刻t5に、トランジスタQ3が再びオンとなり、トランジスタQ1をオフとする。

【0115】

時刻t6に負荷の地絡が解除され、時刻t5にトランジスタQ1がオフとなった時点から予め定める第2の時間が経過した時刻t7に、マイコン14は、Restart信号を出力する。Restart信号が出力されると、トランジスタQ3がオフになり、トランジスタQ1もオンとなる。トランジスタQ1がオンとなったとき、負荷の地絡が解除されて出力電流Ioutが減少しているので、電流検出用抵抗Rsでの電圧降下は、エミッタ抵抗での電圧降下とトランジスタQ2のベースエミッタ間電圧VBEとを加算した電圧未満になっており、トランジスタQ2はオフとなり、電源回路10kは、正常な状態に復帰する。

【0116】

図19は、本発明の第12実施形態である出力遮断回路1mを備える電源回路10mの回路構成を示す図である。電源回路10mは、図17に示した電源回路10kの変形例である。電源回路10mは、直流電源11、トランジスタQ1、ゲート抵抗Rg、コンデンサCout、出力部13および出力遮断回路1mを含んで構成されている。電源回路10mの構成要素のうち図17に示した電源回路10kの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。

【0117】

出力遮断回路1mは、電流検出用抵抗Rs、エミッタ抵抗Re、抵抗R1,R2,R4,R5,R7,R11,R12,R17〜R19、トランジスタQ2〜Q4,Q9、タイマ用コンデンサC1、マイコン14、およびダイオードD2〜4を含んで構成されている。出力遮断回路1mの構成要素のうち図17に示した出力遮断回路1kの構成要素と同じ構成要素については、同じ参照符を付して、重複を避けるために説明は省略する。出力遮断回路1mは、図17に示した抵抗17の代わりに、直列に接続した抵抗R19,R20を用いており、ダイオードD3,D4が追加されている。

【0118】

第6の抵抗素子である抵抗19は、一端がトランジスタQ9のコレクタに接続され、他端が抵抗17の一端、およびダイオードD3のアノードに接続されている。ダイオードD3は、アノードが抵抗R19と抵抗17との接続点に接続され、カソードがダイオードD4のアノードに接続されている。ダイオードD4は、アノードがダイオードD3のカソードに接続され、カソードが接地されている。

【0119】

クランプ部であるダイオードD3,D4は、抵抗R19と抵抗17との接続点の電圧を、予め定める第3の電圧、たとえばダイオードの1個分の電圧降下VFの2倍の電圧以下になるようにクランプしている。したがって、トランジスタQ9がオンとなり、トランジスタQ9から抵抗R19に供給される電流の電流値が増加しても、抵抗R19と抵抗17との接続点の電圧を2VFにすることができるので、タイマ用コンデンサC1を充電する電流は、トランジスタQ9から抵抗R19に供給される電流に依存せず、一定値にすることができる。したがって、電流制限時間を一定の時間にすることができる。

【0120】

たとえばタイマ用コンデンサC1の静電容量をC1、抵抗R17の抵抗値をR17とすると、電流制限時間Tdは、C1×R17である。タイマ用コンデンサC1および抵抗R17に温度変動の小さいものを用いれば、温度変動による電流制限時間Tdの変動を小さくすることができる。

【0121】

出力遮断回路1k,1mは、正常な期間では、負荷電流のみが電源回路10k,10mに流れ、トランジスタQ2〜Q4,Q9には、電流は流れない。

【0122】

出力遮断回路1,1a〜1mを用いる電源回路10,10a〜10mは、たとえば車載用のオーディオ機器、ビデオ機器、ナビゲーション装置、これらを組み合わせた装置、あるいは携帯電話機などバッテリを用いている電子機器に適用することができる。

【0123】

図2に示した出力遮断回路1、図4に示した出力遮断回路1a、図5に示した出力遮断回路1b、図7に示した出力遮断回路1c、図8に示した出力遮断回路1dおよび図9に示した出力遮断回路1eは、負荷電流を徐々に単調増加させた場合、ゲート電圧VGが上昇して、トランジスタQ1に電流制限がかかるより先にトランジスタQ3がオンして出力が遮断される。これに対して、図14に示した出力遮断回路1h、図16に示した出力遮断回路1jおよび図17に示した出力遮断回路1kは、トランジスタQ3がないので、負荷電流を徐々に単調増加させた場合でも、ゲート電圧VGが上昇して電流制限がかかった後で出力が遮断される。

【0124】

すなわち、出力遮断回路1,1a〜1eは、出力が地絡したときの電流制限値Ilimと、負荷電流を徐々に増加させたときトランジスタQ3がオンして出力電流を遮断する第2の出力電流値Ilim2とは異なるが、出力遮断回路1h,1j,1kは、電流制限値Ilimと第2の出力電流値Ilim2とは同じになる。

【0125】

電流制限値Ilimは、式(3)で求められ、抵抗Reによって、その温度変動を小さくすることができる。しかしながら、第2の出力電流値Ilim2は、トランジスタQ3のベースエミッタ間電圧VBE3=R3×Ic、およびRs×Ilim2=Re×Ic+トランジスタQ2のVBE2という関係から、式(4)で表わされ、抵抗Reがあっても温度特性は変わらない。ここに、Rs,Re,R3は、それぞれ抵抗Rs,Re,R3の抵抗値である。

Ilim2=VBE2/Rs+VBE3×Re/(R3×Rs) …(4)

【0126】

したがって、出力遮断回路1,1a〜1eは、負荷電流を徐々に増加させたときに、出力を遮断する電流値の温度変動が大きいという欠点があるが、出力遮断回路1h,1j,1kは、抵抗Reによってその温度変動を小さくすることができる。

【0127】

図20は、車載用のAVN(Audio Video Navigation)装置100の構成を示す図である。AVN装置100は、バッテリ101、オーディオ基板102および電子回路103を含んで構成されている。オーディオ基板102は、バッテリ101を除く、出力遮断回路1を備える電源回路10を含んで構成されている。電子回路103は、たとえばLED群、LEDドライバ、モータ、センサ、あるいはランプなどによって構成されている。

【0128】

バッテリ101および出力遮断回路1を含む電源回路10の電圧は、負荷である制御回路105に印加されている。オーディオ基板102と電子回路103とはフレキシブル基板106によって接続されている。

【0129】

図20に示した例は、出力遮断回路1を備える電源回路10を用いたが、出力遮断回路1a〜1mを用いる電源回路10a〜10mのいずれを用いてもよい。出力遮断回路1,1a〜1mは、正常に動作しているとき、出力遮断回路1,1a〜1mで用いるトランジスタは、いずれもオフであり、暗電流が少なく、バッテリを用いる電子機器では有用である。また、出力遮断回路1,1a〜1mは、簡単な回路構成で実現されるので、電子機器を小型化し、かつコストダウンを図ることができる。

【0130】

このように、電流検出用抵抗Rsは、ソース、負荷に接続されているドレイン、およびゲート抵抗Rgを介して接地されているゲートを備えるトランジスタQ1のソースに一端が接続され、他端が直流電源に接続されている。PNP型のトランジスタQ2は、エミッタが直流電源に接続され、ベースが電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗Rgとの接続点に接続され、電流検出用抵抗Rsの電圧降下が予め定める電圧になると、ゲートの電圧が、トランジスタQ1が予め定める電流値の電流を出力する電圧になる電流をゲート抵抗Rgへ供給する。計時手段、たとえばゲート抵抗RgおよびトランジスタQ3によって、ゲートの電圧が、トランジスタQ1が予め定める電流値の電流を出力する電圧になった時点から予め定める時間が計時される。そして、NPN型のトランジスタQ3は、エミッタが接地され、コレクタが抵抗R2を介してトランジスタQ2のベースに接続され、ベースがゲート抵抗RgとトランジスタQ3との接続点に接続され、ゲート抵抗RgおよびトランジスタQ3によって予め定める時間が計時されたとき導通状態となり、ゲートの電圧がトランジスタQ1が遮断状態となる電圧になる電流を、ゲート抵抗RgへトランジスタQ2に供給させる。

【0131】

したがって、負荷が地絡している間、電流制限の後、トランジスタQ1をオフとするので、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができ、発熱を抑えることができる。すなわち、簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる。

【0132】

さらに、制御手段によって、ゲートの電圧が監視され、監視されるゲートの電圧が、トランジスタQ1が遮断状態になる電圧になった時点から経過した時間が計時され、計時された時間が予め定める第2の時間になったとき、トランジスタQ3を遮断状態にするためのRestart信号がトランジスタQ3のベースに出力される。制御手段は、たとえば出力遮断回路1bでは、マイコン14であり、出力遮断回路1cでは、マイコン14、トランジスタQ4、および抵抗R4,R5であり、出力遮断回路1dでは、マイコン14、トランジスタQ4、抵抗R4〜R6、およびダイオードD1である。したがって、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができ、発熱を抑えることができる。すなわち、簡単な回路構成で、素子の大きさを小さくすることができ、かつ負荷が短絡したとき、その素子の破壊を防止することができる。

【0133】

さらに、マイコン14、トランジスタQ4、抵抗R4、R5,R7、およびダイオードD2によって、トランジスタQ3のコレクタと抵抗R2との接続点の電圧が監視され、監視される前記接続点の電圧が、トランジスタQ1が遮断状態になる電圧になった時点から経過した時間が計時され、計時された時間が予め定める第2の時間になったとき、トランジスタQ3を遮断状態にするためのRestart信号がトランジスタQ3のベースに出力される。したがって、図2に示した出力遮断回路1、図4に示した出力遮断回路1a、図5に示した出力遮断回路1b、図7に示した出力遮断回路1c、および図8に示した出力遮断回路1dでは、電流制限時にもFail信号が出力されるが、図9に示した出力遮断回路1eは、タイマ時間後シャットダウンされた時点で、Fail信号が出力される。また、入力電圧VINがマイコン14に供給される電圧より高い場合、トランジスタQ3がオフの状態のとき、入力電圧VINが、電流検出用抵抗Rs、および抵抗R1,R2を介して、マイコン14の入力ポートINの印加されることを防止することができる。

【0134】

さらに、制御手段によって、計時手段が含まれ、ゲートの電圧が監視され、監視されるゲートの電圧が、トランジスタQ1が遮断状態になる電圧になった時点から経過した時間が計時され、計時された時間が予め定める第2の時間になったとき、トランジスタQ3を遮断状態にするためのRestart信号がトランジスタQ3のベースに出力される。制御手段は、たとえば出力遮断回路1fでは、マイコン14、および抵抗R8,R9であり、出力遮断回路1gでは、マイコン14、トランジスタQ5、および抵抗R8〜R10である。したがって、タイマ用コンデンサC1を用いることなく、電流制限時間Tdの時間を計時することができるので、部品を減らし、回路を簡単化することができる。

【0135】

さらに、電流検出用抵抗Rsは、ソース、負荷に接続されているドレイン、およびゲート抵抗Rg1,Rg2を介して接地されているゲートを備えるトランジスタQ1のソースに一端が接続され、他端が直流電源に接続されている。PNP型のトランジスタQ2は、エミッタが直流電源に接続され、ベースがトランジスタQ1のソースと電流検出用抵抗Rsとの接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗Rg1,Rg2との接続点に接続され、電流検出用抵抗Rsの電圧降下が予め定める電圧になると、ゲートの電圧が、トランジスタQ1が予め定める電流値の電流を出力する電圧になる電流をゲート抵抗Rg1,Rg2へ供給する。抵抗R12およびタイマ用コンデンサC2によって、ゲートの電圧が、トランジスタQ1が予め定める電流値の電流を出力する電圧になり、出力端子13の電圧が予め定める第3の電圧まで低下した時点から予め定める時間が計時される。PNP型のトランジスタQ3は、エミッタがトランジスタQ1のソースと電流検出用抵抗Rsとの接続点に接続され、コレクタがトランジスタQ1のゲートとゲート抵抗Rg1との接続点に接続され、ベースが抵抗R12およびタイマ用コンデンサC2に接続され、抵抗R12およびタイマ用コンデンサC2によって予め定める時間が計時されたとき、導通状態となる。そして、制御手段によって、ゲートの電圧を分圧した電圧を監視し、監視するゲートの電圧を分圧した電圧が、トランジスタQ1を遮断状態とする電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、トランジスタQ3を遮断状態にするためのRestart信号をトランジスタQ3のベースに出力する。制御手段は、たとえば出力遮断回路1hでは、トランジスタ部Tr1,Tr2、およびマイコン14であり、出力遮断回路1jでは、トランジスタ部Tr1,Tr2、マイコン14、抵抗R10、およびトランジスタQ5である。

【0136】

したがって、電流制限を継続する場合よりも、電流検出用抵抗RsおよびトランジスタQ1での電力損失を低減することができるので、発熱を抑えることができる。

【0137】

さらに、前記計時手段は、PNP型のトランジスタQ9と、抵抗R12と、抵抗R17と、抵抗R18と、タイマ用コンデンサC1とを含む。トランジスタQ9は、エミッタが電流検出用抵抗RsとトランジスタQ1のソースとの接続点に接続されている。抵抗R12は、一端がトランジスタQ9のベースに接続され、他端がドレインに接続されている。抵抗R17は、一端がトランジスタQ9のコレクタに接続されている。抵抗R18は、一端が抵抗R17の他端に接続され、他端が接地されている。そして、タイマ用コンデンサC1は、一端がトランジスタQ3のベース、および抵抗R17と抵抗R18との接続点に接続され、他端が接地されている。

【0138】

さらに、前記計時手段は、ダイオードD3,D4を含む。ダイオードD3,D4は、トランジスタQ9のコレクタと抵抗R17との間に設けられる抵抗R19と、抵抗R17と抵抗R19との接続点の電圧を予め定める第2の電圧、たとえば2VF以下にする。したがって、入力電圧が変動しても、計時手段を構成するタイマ用コンデンサC1を充電する電流の電流値を一定値にすることができ、電流制限時間Tdを一定の時間にすることができる。

【0139】

さらに、出力遮断回路1,1a〜1mのうちのいずれか1つを備えるので、正常時は動作電流がゼロになり、暗電流を小さくすることができ、また、過電流時は出力を遮断して、消費電流を小さくすることができ、バッテリ切れの可能性を低減することができる。

【符号の説明】

【0140】

1,1a〜1m,9 出力遮断回路

10,10a〜10m,90 電源回路

11 直流電源

12 スイッチ

13 出力部

14 マイコン

100 AVN装置100

101 バッテリ

102 オーディオ基板

103 電子回路

105 制御回路

106 フレキシブル基板

C1,C2 タイマ用コンデンサ

Cout コンデンサ

D1〜D4 ダイオード

R1〜R19,Ra,Rb 抵抗

Re エミッタ抵抗

Rg,Rg1,Rg2 ゲート抵抗

Rs 電流検出用抵抗

Q1〜Q9 トランジスタ

Tr1,Tr2 トランジスタ部

【特許請求の範囲】

【請求項1】

入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている電流検出用抵抗素子と、

エミッタが直流電源に接続され、ベースが電流検出用抵抗素子と第1のトランジスタの入力端子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給するPNP型の第2のトランジスタと、

制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になった時点から予め定める時間を計時する計時手段と、

エミッタが接地され、コレクタが第2のトランジスタのベースに接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき導通状態となり、制御端子の電圧が第1のトランジスタが遮断状態となる電圧になる電流を、第1の抵抗素子へ第2のトランジスタに供給させるNPN型の第3のトランジスタとを含むことを特徴とする出力遮断回路。

【請求項2】

前記制御端子の電圧を監視し、監視する前記制御端子の電圧が、第1のトランジスタが遮断状態になる電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、前記第3のトランジスタを遮断状態にするための遮断信号を前記第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする請求項1に記載の出力遮断回路。

【請求項3】

前記第3のトランジスタのコレクタと第2の抵抗素子との接続点の電圧を監視し、監視する前記接続点の電圧が、第1のトランジスタが遮断状態になる電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、前記第3のトランジスタを遮断状態にするための遮断信号を前記第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする請求項1に記載の出力遮断回路。

【請求項4】

前記計時手段を含み、前記制御端子の電圧を監視し、監視する前記接続点の電圧が、第1のトランジスタが遮断状態になる電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、前記第3のトランジスタを遮断状態にするための遮断信号を前記第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする請求項1に記載の出力遮断回路。

【請求項5】

入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている電流検出用抵抗素子と、

エミッタが直流電源に接続され、ベースが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給するPNP型の第2のトランジスタと、

制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になり、出力端子の電圧が予め定める第3の電圧まで低下した時点から予め定める時間を計時する計時手段と、

エミッタが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき、導通状態となるPNP型の第3のトランジスタと、

制御端子の電圧を分圧した電圧を監視し、監視する制御端子の電圧を分圧した電圧が、第1のトランジスタを遮断状態とする電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、第3のトランジスタを遮断状態にするための遮断信号を第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする出力遮断回路。

【請求項6】

前記計時手段は、

エミッタが電流検出用抵抗素子と第1のトランジスタの入力端子との接続点に接続されているPNP型の第4のトランジスタと、

一端が第4のトランジスタのベースに接続され、他端が出力端子に接続されている第3の抵抗素子と、

一端が第4のトランジスタのコレクタに接続されている第4の抵抗素子と、

一端が第4の抵抗素子の他端に接続され、他端が接地されている第5の抵抗素子と、

一端が前記第3のトランジスタのベース、および第4の抵抗素子と第5の抵抗素子との接続点に接続され、他端が接地されているコンデンサとを含むことを特徴とする請求項1に記載の出力遮断回路。

【請求項7】

前記計時手段は、

前記第4のトランジスタのコレクタと第4の抵抗素子との間に設けられる第6の抵抗素子と、

第4の抵抗素子と第6の抵抗素子との接続点の電圧を予め定める第3の電圧以下にするクランプ部とをさらに含むことを特徴とする請求項6に記載の出力遮断回路。

【請求項8】

請求項1〜7のいずれか1つに記載の出力遮断回路を備える電子機器。

【請求項1】

入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている電流検出用抵抗素子と、

エミッタが直流電源に接続され、ベースが電流検出用抵抗素子と第1のトランジスタの入力端子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給するPNP型の第2のトランジスタと、

制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になった時点から予め定める時間を計時する計時手段と、

エミッタが接地され、コレクタが第2のトランジスタのベースに接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき導通状態となり、制御端子の電圧が第1のトランジスタが遮断状態となる電圧になる電流を、第1の抵抗素子へ第2のトランジスタに供給させるNPN型の第3のトランジスタとを含むことを特徴とする出力遮断回路。

【請求項2】

前記制御端子の電圧を監視し、監視する前記制御端子の電圧が、第1のトランジスタが遮断状態になる電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、前記第3のトランジスタを遮断状態にするための遮断信号を前記第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする請求項1に記載の出力遮断回路。

【請求項3】

前記第3のトランジスタのコレクタと第2の抵抗素子との接続点の電圧を監視し、監視する前記接続点の電圧が、第1のトランジスタが遮断状態になる電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、前記第3のトランジスタを遮断状態にするための遮断信号を前記第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする請求項1に記載の出力遮断回路。

【請求項4】

前記計時手段を含み、前記制御端子の電圧を監視し、監視する前記接続点の電圧が、第1のトランジスタが遮断状態になる電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、前記第3のトランジスタを遮断状態にするための遮断信号を前記第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする請求項1に記載の出力遮断回路。

【請求項5】

入力端子、負荷に接続されている出力端子、および第1の抵抗素子を介して接地されている制御端子を備える第1のトランジスタの入力端子に一端が接続され、他端が直流電源に接続されている電流検出用抵抗素子と、

エミッタが直流電源に接続され、ベースが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、電流検出用抵抗素子の電圧降下が予め定める電圧になると、制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になる電流を第1の抵抗素子へ供給するPNP型の第2のトランジスタと、

制御端子の電圧が、第1のトランジスタが予め定める電流値の電流を出力する電圧になり、出力端子の電圧が予め定める第3の電圧まで低下した時点から予め定める時間を計時する計時手段と、

エミッタが第1のトランジスタの入力端子と電流検出用抵抗素子との接続点に接続され、コレクタが第1のトランジスタの制御端子と第1の抵抗素子との接続点に接続され、ベースが計時手段に接続され、計時手段によって予め定める時間が計時されたとき、導通状態となるPNP型の第3のトランジスタと、

制御端子の電圧を分圧した電圧を監視し、監視する制御端子の電圧を分圧した電圧が、第1のトランジスタを遮断状態とする電圧になった時点から経過した時間を計時し、計時した時間が予め定める第2の時間になったとき、第3のトランジスタを遮断状態にするための遮断信号を第3のトランジスタのベースに出力する制御手段をさらに含むことを特徴とする出力遮断回路。

【請求項6】

前記計時手段は、

エミッタが電流検出用抵抗素子と第1のトランジスタの入力端子との接続点に接続されているPNP型の第4のトランジスタと、

一端が第4のトランジスタのベースに接続され、他端が出力端子に接続されている第3の抵抗素子と、

一端が第4のトランジスタのコレクタに接続されている第4の抵抗素子と、

一端が第4の抵抗素子の他端に接続され、他端が接地されている第5の抵抗素子と、

一端が前記第3のトランジスタのベース、および第4の抵抗素子と第5の抵抗素子との接続点に接続され、他端が接地されているコンデンサとを含むことを特徴とする請求項1に記載の出力遮断回路。

【請求項7】

前記計時手段は、

前記第4のトランジスタのコレクタと第4の抵抗素子との間に設けられる第6の抵抗素子と、

第4の抵抗素子と第6の抵抗素子との接続点の電圧を予め定める第3の電圧以下にするクランプ部とをさらに含むことを特徴とする請求項6に記載の出力遮断回路。

【請求項8】

請求項1〜7のいずれか1つに記載の出力遮断回路を備える電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2011−41393(P2011−41393A)

【公開日】平成23年2月24日(2011.2.24)

【国際特許分類】

【出願番号】特願2009−186050(P2009−186050)

【出願日】平成21年8月10日(2009.8.10)

【出願人】(000237592)富士通テン株式会社 (3,383)

【Fターム(参考)】

【公開日】平成23年2月24日(2011.2.24)

【国際特許分類】

【出願日】平成21年8月10日(2009.8.10)

【出願人】(000237592)富士通テン株式会社 (3,383)

【Fターム(参考)】

[ Back to top ]