出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、出力駆動回路及びトランジスタ出力回路に関し、特に、出力トランジスタのゲートに、ソース−ドレイン間の降伏電圧より小さく、ゲート−ソース間の降伏電圧より大きい高電圧が印加される場合、安定して動作可能な出力駆動回路及びトランジスタ出力回路に関する。

【背景技術】

【0002】

Pチャネルトランジスタ、例えばPチャネル−LDMOSの動作電圧は、ソース−ドレイン間の降伏電圧BVsd、ソース−ゲート間の降伏電圧BVsg及びゲート−ドレイン間の降伏電圧BVgdによって決まる。このうち、ソース−ゲート間の降伏電圧BVsgが一番小さい。ソース−ゲート間の降伏電圧BVsgは、ゲート酸化物の厚さによって決まる。これは、酸化物(Oxide)の厚さによって、トランジスタの閾値電圧Vth、ソース−ドレイン間の電流Isd、オン抵抗Ronなどが決まり、ゲート酸化物の厚さを無制限厚くすることができないためである。電源電圧がソース−ドレイン間の降伏電圧BVsdより小さく、ソース−ゲート間の降伏電圧BVsgより大きい場合、ソース端子に電源電圧を接続し、ドレイン端子に低電位(グラウンドなど)を接続しても間題がない。

【0003】

しかし、このようなトランジスタを動作させるためには、ゲート端子に電源電圧及び低電位(グラウンド)電圧を印加すると、ソース−ゲート間の電圧Vsgに電源電圧がかかるようになり、該電源電圧は、ソース−ゲート間の降伏電圧BVsgより大きいので、トランジスタ素子が破壊される恐れがある。

【0004】

図6は、従来の出力駆動回路を概略的に示す図面である。

【0005】

図6では、スイッチSW1がオフすると、電源電圧Vdd及び出力トランジスタT1のゲートに接続された抵抗R及びツェナーダイオードZ1に所与の電流Iが流れ、ツェナーダイオードZ1によって出力トランジスタT1のソース−ゲート間の電位をソース−ゲート間の降伏電圧BVsgより小さく閾値電圧Vthより大きくすることによって、出力トランジスタT1を駆動させる。逆に、スイッチSW1はオンし、出力トランジスタT1のゲート電位が電源電圧Vdd及び出力トランジスタT1のゲートに接続された抵抗Rによって電源電圧Vddまで上昇して、出力トランジスタT1をオフさせる。

【0006】

一方、図6と異なり、比較的高い周波数で動作させるために、出力トランジスタT1をオフさせる手段を、抵抗Rではなく、カレントミラー(Current Mirror)を用いる場合もある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】韓国特許第10−0489870号公報

【特許文献2】特開2008−147755号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

図6の従来技術では、出力トランジスタT1のゲート−ソースのキャパシタを、抵抗を通じて充電すると共に電流源を通じて放電するため、比較的高い周波数に対して不利で、出力トランジスタT1のオン状態を維持するために電流Iが抵抗R、及びツェナーダイオードZ1を通じて流れ続けて、消費電流が増大するという短所がある。

【0009】

また、比較的高い周波数で動作させるために、出力トランジスタT1をオフさせる手段としてカレントミラーを用いる場合、出力トランジスタT1のゲート−ソースのキャパシタンスを早い速度で充電するためには、高いカレントミラー比を持たなければならない。図6と同様に、出力トランジスタT1のゲート−ソースのキャパシタンスを早い速度で放電するためには、大電流Iが必要になる。また、この場合にも、図6のように、出力トランジスタT1のオン状態を維持するためには、大電流IがツェナーダイオードZ1を通じて流れ続けるため、消費電流が高いという短所を有する。

【0010】

本発明は、上記の間題点に鑑みて成されたものであって、その目的は、出力トランジスタのゲートに、ソース−ドレイン間の降伏電圧より小さく、ゲート−ソース間の降伏電圧より大きい高電圧が印加される場合に、安定して動作可能な出力駆動回路及びトランジスタ出力回路を提供することにある。

【0011】

また、本発明の他の目的は、高い周波数動作でも安定した動作を行うと共に、低い消費電流でも安定した動作を行う出力駆動回路及びトランジスタ出力回路を提供することにある。

【課題を解決するための手段】

【0012】

上記目的を解決するために、本発明によれば、第1のスイッチのオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタを含む第1の駆動回路部と、該第1のスイッチと相補的に動作する第2のスイッチのオン動作によって生成されたワンショットパルスとによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタを含む第2の駆動回路部と、前記第1の駆動回路部と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチのオン動作によって放電された出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部と、を含む出力駆動回路が提供される。

【0013】

本発明によれば、前記第2の駆動回路部は、第1のスイッチと相補的に動作すると共に、オン動作によって出力駆動電圧クランピング部を通じて流れる電流を、低電圧電源端へと切り換える第2のスイッチと、該第2のスイッチのオン動作によって、第2のトランジスタを駆動させるためのワンショットパルスを生成するパルス生成器と、該ワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させるNチャネルの第2のトランジスタと、を含む。

【0014】

本発明によれば、前記第1の駆動回路部は、第1のスイッチと、高電圧電源端にソース電極が接続され、第1のスイッチのオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給するPチャネルの第1のトランジスタと、該第1のスイッチのオン動作によって、高電圧電源端から第1のトランジスタのゲートに供給される駆動電圧をクランピングする第1のトランジスタ駆動電圧クランピング部と、を含む。

【0015】

また、本発明によれば、第1のトランジスタ駆動電圧クランピング部は、高電圧電源端と第1のトランジスタのゲートとの間に配置され、互いに並列接続された抵抗と第1のツェナーダイオードとを含む。

【0016】

また、本発明によれば、第1のトランジスタ駆動電圧クランピング部は、高電圧電源端と第1のトランジスタのゲートとの間に配置された第1のツェナーダイオードと、該第1のツェナーダイオードに並列接続されたカレントミラーと、該第1のトランジスタのゲートに対向する前記カレントミラーの下端に接続され、第1のスイッチと相補的に動作する第3のスイッチとを含む。

【0017】

本発明によれば、カレントミラーは、高電圧電源端にソース電極が接続された第3及び第4のトランジスタのミラー構造で構成され、該第3及び第4のトランジスタは、PチャネルMOSFETまたはPチャネルLDMOSFETであり、第4のトランジスタのドレイン電極は、第1のトランジスタのゲートに接続され、第3のトランジスタのドレイン電極は、第3のスイッチと第3及び第4のトランジスタのゲート電極とに接続される。第3のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETで構成される。

【0018】

また、本発明によれば、出力駆動電圧クランピング部は、高電圧電源端と出力トランジスタのゲートとの間に配置された第2のツェナーダイオードを含む。

【0019】

また、本発明によれば、第1のトランジスタのゲート−ソースのキャパシタンスは、出力トランジスタのゲート−ソースのキャパシタンスより小さいし。

【0020】

また、本発明によれば、第1及び第2のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETで構成される。

【0021】

また、本発明によれば、出力トランジスタは、第2の駆動回路部の駆動によって駆動されて高電圧電源を出力するPチャネルMOSFETまたはPチャネルLDMOSFETである。

【0022】

また、上記目的を解決するために、本発明の他の例によれば、高電圧電源端にソース電極が接続され、駆動によってドレイン電極を通じて高電圧電源を出力するPチャネル出力トランジスタと、該Pチャネル出力トランジスタと相補的に動作し、駆動によってPチャネル出力トランジスタのドレイン電極と接続されたドレイン電極からソース電極が接続された低電圧電源端に電源を出力するNチャネル出力トランジスタと、相補的スイッチング動作によってPチャネル及びNチャネル出力トランジスタの各々を駆動する前述の実施形態のうちのいずれか一つによる出力駆動回路とを含むトランジスタ出力回路が提供される。

【0023】

本発明によれば、出力駆動回路の出力駆動電圧クランピング部は、高電圧電源端とPチャネル出力トランジスタのゲートとの間に配置された第2のツェナーダイオードを含む。

【0024】

また、本発明によれば、出力駆動回路の第1及び第2のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETで構成される。

【発明の効果】

【0025】

本発明によれば、出力トランジスタのゲートにソース−ドレイン間の降伏電圧より小さくゲート−ソース間の降伏電圧より大きい高電圧が印加される場合、安定して動作可能な出力駆動回路及びトランジスタ出力回路を得ることができる。

【0026】

また、本発明によれば、高い周波数動作でも安定な動作を行うと共に、低い消費電流でも安定な動作を行う出力駆動回路及びトランジスタ出力回路を得ることができる。

【0027】

本発明の多様な実施形態によって直接的に言及されなかった多様な効果が、本発明の実施形態による多様な構成から、該当技術分野において通常の知識を有する者によって導出されることができることは自明である。

【図面の簡単な説明】

【0028】

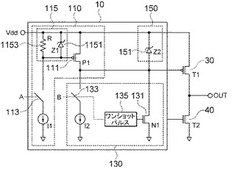

【図1】本発明の一実施形態による出力駆動回路を概略的に示すブロック図である。

【図2】本発明の一実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図である。

【図3】本発明の一実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図である。

【図4】本発明の一実施形態による出力駆動回路のシミュレーション結果を示すグラフである。

【図5】本発明の一実施形態によるワンショットパルスの効果を示すグラフである。

【図6】従来の出力駆動回路を概略的に示す図面である。

【発明を実施するための形態】

【0029】

以下、本発明の好適な実施の形態を、図面を参照して詳細に説明する。次に示される各実施の形態は、当業者にとって本発明の思想が十分に伝達されることができるようにするために例として挙げられるものである。従って、本発明は、以下示している各実施の形態に限定されることなく、他の形態で具体化されることができる。そして、図面において、装置の大きさ及び厚さなどは、便宜上誇張して表現されることがある。明細書全体に渡って同一の参照符号は、同一の構成要素を示している。

【0030】

具体的な説明に先立ち、本明細書において一つの構成要素が他の構成要素と「直接接続」または「直接結合」のように言及されない限り、単に「接続」また「結合」の表現で言及された場合は、「直接的に」接続または結合されてもよく、ひいては、それらの間に異なる構成要素が挿入されて接続または結合されるような形態でもよい。

【0031】

本明細書上に、例えば、単数の表現が記載されていても、発明の概念に反していなく、解釈上矛盾するかまたは明白に異なるように解釈されない限り、複数の構成全体を代表する概念として使われることもあるに留意されたい。

【0032】

本明細書で使われた用語は、実施形態を説明するためのものであって、本発明を制限しようとするものではない。本明細書において、単数形は、特別に言及しない限り複数形も含む。明細書で使われる「含む」とは、言及された構成要素、ステップ、動作及び/又は、素子は、一つ以上の他の構成要素、ステップ、動作及び/又は、素子の存在または追加を排除しないことに理解されたい。

【0033】

まず、図面を参照して、本発明の第1の実施形態による出力駆動回路について詳記する。

【0034】

図1は、本発明の一実施形態による出力駆動回路を概略的に示すブロック図であり、図2は、本発明の一実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図であり、図3は、本発明の一実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図である。図4は、本発明の一実施形態による出力駆動回路のシミュレーション結果を示すグラフであり、図5は、本発明の一実施形態によるワンショットパルスの効果を示すグラフである。

【0035】

図1、図2及び図3を参照して、本発明の実施形態による出力駆動回路について説明する。図1、図2及び図3を参照して、出力駆動回路10は、第1の駆動回路部110、第2の駆動回路部130及び出力駆動電圧クランピング部150を含む。

【0036】

詳しくは、第1の駆動回路部110は、第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源(Vdd)を供給する第1のトランジスタ111を含む。一例として、出力トランジスタは、Pチャネルトランジスタ30であってもよい。また一例として、出力トランジスタは、PチャネルMOSFETまたはPチャネルLDMOS(Latera1 Double Diffused Metal Oxide Semiconductor)FETであってもよい。出力トランジスタがPチャネルトランジスタの場合、第1のトランジスタ111の駆動によってゲートにソース電極に供給される高電圧電源(Vdd)が同じく供給されるため、トランジスタはオフされる。また一例として、第1のトランジスタ111は、Pチャネルトランジスタ、例えば、PチャネルMOSFETまたはPチャネルLDMOSFETであってもよい。また一例として、第1のスイッチ113は、NチャネルMOSFETまたはNチャネルLDMOSFETで構成されてもよい。

【0037】

一実施形態において、図2及び図3に示すように、第1の駆動回路部110は、第1のスイッチ113と、第1のトランジスタ111と、第1のトランジスタ駆動電圧クランピング部115とを含む。

【0038】

第1のトランジスタ111はPチャネルトランジスタであってもよく、このPチャネルトランジスタは、高電圧電源端(Vdd)にソース電極が接続され、第1のスイッチ113のオン動作によって駆動される。Pチャネルトランジスタは、その駆動によって出力トランジスタ、例えばPチャネルの出力トランジスタのゲートに高電圧電源(Vdd)を供給する。これによって、高電圧電源(Vdd)をゲート電源として印加されるPチャネル出力トランジスタ30は、オフ動作する。

【0039】

次に、図2及び図3に示すように、第1のトランジスタ駆動電圧クランピング部115は、第1のスイッチ113のオン動作によって、高電圧電源端(Vdd)から第1のトランジスタ111のゲートに供給される駆動電圧をクランピングする。これによって、第1のトランジスタ111のソース−ゲート間の電圧が降伏電圧(BVsg)を超えないように第1のトランジスタ111が保護される。

【0040】

詳しくは、図2に示すように、第1のトランジスタ駆動電圧クランピング部115は、高電圧電源端(Vdd)と第1のトランジスタ111のゲートとの間に配置され、抵抗1153及び第1のツェナーダイオード1151を含む。抵抗1153及び第1のツェナーダイオード1151は、高電圧電源端(Vdd)と第1のトラングスタ111のゲートとの間に配置され、互いに並列接続される。第1のスイッチ113のオン動作によって、抵抗1153及び第1のツェナーダイオード1151を通じて流れる定電流I1が、第1のスイッチ113を通じて低電圧電源(Vss)、例えばグラウンドを通じて流出されるようになる。

【0041】

また、図3を参照して、他の実施形態について詳記する。図3に示すように、第1のトランジスタ駆動電圧クランピング部115は、図2の抵抗1153をカレントミラー構造で代替することができる。例えば、第1のトランジスタ駆動電圧クランピング部115は、高電圧電源端(Vdd)と第1のトランジスタ111のゲートとの間に配置された第1のツェナーダイオード1151と、該第1のツェナーダイオード1151に並列接続されたカレントミラーと、第1のトランジスタ111のゲートに対向するカレントミラーの下端に接続され、第1のスイッチ113と相補的に動作する第3のスイッチ1157とを含む。また、図3に示すように、カレントミラーは、高電圧電源端(Vdd)にソース電極が接続された第3及び第4のトランジスタ1155、1156のミラー構造で構成される。第4のトランジスタ1156のドレイン電極は、第1のトランジスタ111のゲートに接続され、第3のトランジスタ1155のドレイン電極は、第3のスイッチ1157と第3及び第4のトランジスタ1155、1156のゲート電極に接続される。第3及び第4のトランジスタ1155、1156は、PチャネルMOSFETまたはPチャネルLDMOSFETであってもよい。また、第3のスイッチ1157は、NチャネルMOSFETまたはNチャネルLDMOSFETで構成されてもよい。

【0042】

また、図2及び図3を参照して、本発明の他の実施形態について説明する。第1のトランジスタ111のゲート−ソースのキャパシタンスは、出力トランジスタのゲート−ソースのキャパシタンスより小さい。第1のトランジスタ111のゲート−ソースのキャパシタンスを、出力トランジスタのゲート−ソースのキャパシタンスより充分に小さくすることによって、第1のトランジスタ駆動電圧クランピング部での充電速度を早くすることができる。第1のトランジスタ111は、出力トランジスタより小さなサイズで形成されてもよい。例えば、第1のトランジスタ111が、例えばPチャネル出力トランジスタ30より充分に小さい場合、すなわち、例えば1/20程度に小さなサイズの場合、第1のトランジスタ111のゲート−ソースのキャパシタンスが、Pチャネル出力トランジスタ30のゲート−ソースのキャパシタンスより充分に小さいので、第1のトランジスタ駆動電圧クランピング部での充電速度、特に第1のトランジスタ駆動電圧クランピング部の抵抗1153による充電速度が早くなることになる。これによって、第1のスイッチ113のオン動作によって、第1のトランジスタ駆動電圧クランピング部を通じて流れる電流源11が小さい場合にも、Pチャネルの第1のトランジスタ111を充分に早い速度でオフさせることができる。したがって、電流源11を小さく設計することができ、消費電流も減らして比較的高い周波数でも動作が容易になるようにできる。

【0043】

一実施形態によれば、第1のスイッチ113は、Nチャネルトランジスタ、例えば、NチャネルMOSFETまたはNチャネルLDMOSFETで構成されてもよい。Nチャネルトランジスタの場合、ゲート−ソース間の降伏電圧(BVgs)は、例えば、5V程度と低いが、ドレイン−ソース間の降伏電圧(BVds)は、高電圧電源(Vdd)に相当する高耐圧を有するようになる。

【0044】

図2を参照して、第1の駆動回路部110の動作の一例について詳記する。図2に示すように、第1の駆動回路部110の第1のスイッチ113のAと第2の駆動回路部130の第2のスイッチ133のBとは、異なる位相にて動作する。第1のスイッチ113のAがオフされると、第2のスイッチ133のBはオンされ、第1のスイッチ113のAがオンすると、第2のスイッチ133のBはオフされるようになる。第1のスイッチ113のAがオフされ、第2のスイッチ133のBがオンされると、抵抗1153(R)及び第1のツェナーダイオード1151(Z1)に電流源I1の電流が流れるようになり、第1のトランジスタ111(P1)のゲート電位は、閾値電圧Vthより大きく、ソース−ゲート間の降伏電圧BVsgより小さくなって、第1のトランジスタ111(P1)がオン動作する。すると、出力トランジスタT1のゲート−ソースのキャパシタンスが早く充電され、出力トランジスタT1をオフさせる。

【0045】

また、図3を参照して、第1の駆動回路部110の動作の他例について詳記する。図3に示すように、第1の駆動回路部110の第1のスイッチ113のAと、第2の駆動回路部130の第2のスイッチ133のBとは、異なる位相にて動作する。第1の駆動回路部110の第1のスイッチ113のAと第3のスイッチ1157のAとも相補的に動作する。詳しくは、第1のスイッチ113Aのがオフされると、第2のスイッチ133のB及び第3のスイッチ1157はオンされる。また、第1のスイッチ113のAがオンされると、第2のスイッチ133のB及び第3のスイッチ1157はオフされる。第1のスイッチ113のAがオンされ、第3のスイッチ1157がオフされると、カレントミラー構造の第3及び第4のトランジスタ1155、1156によって、カレントミラー比分、第4のトランジスタ1156(P3)に電流が流れるようになる。すると、第1のトランジスタ111(P1)のゲート−ソースのキャパシタンスを充電させ、第1のトランジスタ111(P1)のゲート電位を高電圧電源(Vdd)まで上がるようにして、第1のトランジスタ111(P1)をオフさせる。反対に、第1のスイッチ113Aがオフされ、第3のスイッチ1157がオンされると、第1のスイッチ113Aを通じて電流源I1が流れるようになる。すると、第1のトランジスタ111(P1)のゲート電位は、閾値電圧Vthより大きく、ソース−ゲート間の降伏電圧BVsgより小さくなって、第1のトランジスタ111(P1)がオン動作する。第1のトランジスタ111(P1)がオン動作すると、出力トランジスタT1のゲート−ソースのキャパシタンスが早く充電され、出力トランジスタT1をオフさせる。図3に示すように、第1のトランジスタ111(P1)が出力トランジスタ30(T1)よりずっと小さいため、I3のように小さな電流でも早いスイッチングができる。

【0046】

続いて、図1、図2及び図3を参照して、第2の駆動回路部130について説明する。第2の駆動回路部130は、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作により生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む。一例として、第2のトランジスタ131は、Nチャネルトランジスタ、例えば、NチャネルMOSFETまたはNチャネルLDMOSFETが挙げられる。第2のトランジスタ131が駆動されると、ドレイン電極に接続された出力トランジスタのゲートから充電されていたゲート−ソースのキャパシタンスを、ソース電極に接続される低電圧電源、例えばグラウンドへと、急に抜き取って放電させることができる。

【0047】

この実施形態において、出力トランジスタは、第2の駆動回路部130の駆動によって駆動される。一例として、出力トランジスタは、Pチャネルトランジスタ30であってもよい。また一例として、出力トランジスタは、第2の駆動回路部130の駆動によって高電圧電源(Vdd)を出力するPチャネルMOSFETまたはPチャネルLDMOSFETであってもよい。

【0048】

一実施形態において、図2を参照して、第2の駆動回路部130についてより詳しく説明する。第2の駆動回路部130は、第2のスイッチ133、パルス生成器135及び第2のトランジスタ131を含む。第2のスイッチ133は、第1の駆動回路部110の第1のスイッチ113と相補的に動作する。第2のスイッチ133のオン動作によって出力駆動電圧クランピング部150を通じて流れる電流を、低電圧電源端(Vss)へと切り換える。パルス生成器135は、第2のスイッチ133のオン動作によって動作し、第2のトランジスタ131を駆動させるためのワンショットパルスを生成する。第2のトランジスタ131はNチャネルトランジスタであってもよく、このNチャネルの第2のトランジスタ131は、パルス生成器135によって生成されたワンショットパルスを、ゲート電源として入力され駆動される。Nチャネルの第2のトランジスタ131の駆動によって、ドレイン電極に接続された出力トランジスタのゲート電極からゲート−ソースのキャパシタンスを放電させ、電流をソース電極に接続された低電圧電源(Vss)、例えばグラウンドへと流す。Nチャネルの第2のトランジスタ131によって、出力トランジスタのゲート電極のゲート−ソースのキャパシタンスを急に放電させた後、オン動作した第2のスイッチ133を通じて、出力駆動電圧クランピング部150を通って流れる電流を低電圧電源端へと流すと、放電した出力トランジスタのゲート電位が一定に維持される。これによって、出力トランジスタが駆動され、Pチャネル出力トランジスタ30からソース電極の高電圧電源(Vdd)がドレイン電極を通じて出力される。

【0049】

また、一実施形態によれば、第2のスイッチ133としては、Nチャネルトランジスタ、例えば、NチャネルMOSFETまたはNチャネルLDMOSFETが挙げられる。この第2のスイッチ133を形成するNチャネルトランジスタは、ゲート−ソース間の降伏電圧(BVgs)が、例えば5V程度と低いが、ドレイン−ソース間の降伏電圧(BVds)は、高電圧電源(Vdd)に相当する高い耐圧を有するようになる。

【0050】

また、図2及び図3を参照して、第2の駆動回路部130の動作について詳記する。図2及び図3に示すように、第1の駆動回路部110の第1のスイッチ113Aと第2の駆動回路部130の第2のスイッチ113Bとは、互いに異なる位相にて動作する。第1のスイッチ113Aがオンされ第2のスイッチ133Bがオフされると、パルス生成器135で生成されたワンショットパルスによって、第2のトランジスタ131(N1)が瞬間的に動作し、出力トランジスタT1のゲート−ソースのキャパシタンスを早く放電させる。該ワンショットパルスによって、第2のトランジスタ131(N1)は、ゲート−ソースのキャパシタンスを早く放電させた後オフされる。出力駆動電圧クランピング部150の第2のツェナーダイオード151(Z2)には、電流源I2の電流が流れ、出力トランジスタT1のゲート−ソースのキャパシタンスが放電した状態で、出力トランジスタT1のゲート電位が一定に維持され、出力トランジスタT1が動作する。この出力トランジスタT1の駆動によって、高電圧電源(Vdd)がソース電極から、ドレイン電極を通じて出力されるようになる。

【0051】

出力トランジスタT1のオン動作を保持させる電流源I2は、ワンショットパルスによって動作する第2のトランジスタ131(N1)が、先に出力トランジスタT1のゲート−ソースのキャパシタンスを放電させるため、小さく設計されてもよい。それに伴って、消費電流も減らすと共に、比較的高い周波数でも動作が容易になる。

【0052】

次に、図1、図2及び図3を参照して、出力駆動電圧クランピング部150について説明する。出力駆動電圧クランピング部150は、第1の駆動回路部110と並列されるように高電圧電源端(Vdd)と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる。これによって、第2の駆動回路部130の駆動で、詳しくは、第2のスイッチ133のオン動作で、出力トランジスタが駆動され、該出力トランジスタを通じて高電圧電源(Vdd)が出力される。

【0053】

図2及び図3に示すように、一実施形態において、出力駆動電圧クランピング部150は、高電圧電源端(Vdd)と出力トランジスタのゲートとの間に配置された第2のツェナーダイオード151を含む。第2のスイッチ133のオン動作によって、第2のトランジスタ131がワンショットパルスにより駆動され、出力トランジスタのゲート電極に充電されたゲート−ソースのキャパシタンスを瞬間的に放電させる。該放電の後、第2のスイッチ133によって、第2のツェナーダイオード151を通じて流れる定電流電流源I2がグラウンドへと流出されることになる。これによって、出力トランジスタのゲート電位が一定に維持され、Pチャネルの出力トランジスタが駆動するようになる。出力駆動電圧クランピング部150、例えば図2及び図3の第2のツェナーダイオード151(Z2)は、例えば、Pチャネル出力トランジスタ30(T1)のソース−ゲート間の電圧が降伏電圧BVsgを超えないようにして、出力トレンジストトT1を保護する。

【0054】

図4を参照して、本発明の実施形態によるシミュレーションの結果について説明する。

【0055】

図4は、図2の実施形態による回路のシミュレーション結果を示す波形図である。高電圧電源(Vdd)にVdd=20Vを印加し、出力トランジスタ30(T1)の定格作動電圧(Recommended Operating Voltage)で、ソース−ゲート間電圧Vsg≦12V、ソース−ドレイン間電圧Vsd≦0VであるPチャネルLDMOSで構成された回路をシミュレーションした。

【0056】

波形/Aは第1のスイッチ113のAの制御信号で、波形/Bは第2のスイッチ133のBの制御信号で、波形/One_Shotはワンショットパルスの出力波形で、波形/N1/Dは、ワンショットパルスによって第2のトランジスタ131(N1)のドレインに流れる電流で、波形/D0/NEGは、第2のツェナーダイオード151(Z2)に流れる電流で、波形/Vgは出力トランジスタT1のゲート電位である。

【0057】

第1及び第2のスイッチ113のA、133のBは、シミュレーションのように0V/5Vによってコントロールされる。第1のスイッチ113のAに5Vの信号が入力されると、第1のスイッチ113のAはオフされ、第1のトランジスタ111(P1)がオンされる。すると、出力トランジスタT1のゲート電位を20Vとして印加し、ソース−ゲート間電位を0Vにして、出力トランジスタT1をオフさせる。反対に、第1のスイッチ113のAに0Vの信号を印加し、第2のスイッチ133のBに5Vの信号を印加すると、第1のスイッチ113のAはオンされ、第2のスイッチ133のBはオフされる。第2のスイッチ133のBがオフされると、ワンショットパルスによって出力トランジスタT1のゲート−ソースのキャパシタンスが放電し、電流源I2と第2のツェナーダイオード151(Z2)とによって、出力トランジスタT1のゲート電位Vgは、8.687Vに維持され、ソース−ゲート間電位Vsgは、Vsg=20−8.687=11.723Vとして、定格作動電庄内の電圧を有し、正常にオンされる。第2のツェナーダイオード151(Z2)に低い100uAが流れても、出力トランジスタT1のゲート電位Vgが8.687Vとして、出力トランジスタT1がオン状態を維持することを分かる。

【0058】

図5を参照して、ワンショットパルスによる動作について説明する。このため、図5では、図4中の破線区間内のシミュレーション波形を拡大して示す。

【0059】

ワンショットパルスは、第2のスイッチ133のBの制御電圧が、0Vから5Vに変わる時に生成されるパルスであって、図5のシミュレーション結果のように、100nsのパルス信号が生成されることが分かる。この信号によって、実施形態による回路の第2のトランジスタ131(N1)が瞬間的にオンされ、4mAの電流で出力トランジスタT1のゲート−ソースのキャパシタンスを放電させ、出力トランジスタT1のゲート電圧Vgの立ち下がりタイム(falling time)が25nsで、早い速度でオンされることが分かる。

【0060】

すなわち、従来の出力駆動回路では、図5のシミュレーション結果のように、早い速度でオンさせ、該オン状態を維持するためには、4mAの電流が必要となるが、本実施形態による回路は、ワンショットパルスによって迅速にオンさせ、1OOusの電流で、オン状態を維持することができる。そのため消費電流が非常に小さくなる。

【0061】

次に、本発明の第2の実施形態によるトランジスタ出力回路について説明する。図2は、本発明の一実施形態によるトランジスタ出力回路を示す回路図である。図3は、本発明の他の実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図である。

【0062】

図2及び図3に示すように、本実施形態によるトランジスタ出力回路は、Pチャネル出力トランジスタ30、Nチャネル出力トランジスタ40及び出力駆動回路10を含む。図2及び図3に示すように、出力駆動回路10とPチャネル及びNチャネル出力トランジスタ30、40との接続は、出力駆動回路10が、相補的にPチャネル及びNチャネル出力トランジスタ30、40を駆動させることを示している。出力駆動回路10は、前述の第1の実施形態に示す出力駆動回路10である。したがって、本実施形態の説明に当って、先の出力駆動回路10の実施形態を参照し、重複する説明は省略することにする。

【0063】

図2及び図3に示すように、Pチャネル出力トランジスタ30は、高電圧電源端(Vdd)にソース電極が接続され、駆動によってドレイン電極を通じて高電圧電源(Vdd)を出力する。前述の実施形態による出力駆動回路10がPチャネル出力トランジスタ30を駆動させる。

【0064】

Nチャネル出力トランジスタ40は、Pチャネル出力トランジスタ30と相補的に動作する。Nチャネル出力トランジスタ40は、その駆動によって、Pチャネル出力トランジスタ30のドレイン電極に接続されたドレイン電極から、ソース電極が接続された低電圧電源端へと電源を出力する。前述の実施形態による出力駆動回路10が、Pチャネル出力トランジスタ30を駆動させることと相補的に、Nチャネル出力トランジスタ40を駆動させるようになる。

【0065】

出力駆動回路10における第2の駆動回路部130の第2のスイッチ133のオン動作によって、Pチャネル出力トランジスタ30が駆動され、第2のスイッチ133と相補的に動作する第1のスイッチ113のオン動作によって、Nチャネル出力トランジスタ40が駆動される。

【0066】

また、一実施形態によれば、出力駆動回路10の出力駆動電圧クランピング部150は、高電圧電源端(Vdd)とPチャネル出力トランジスタ30のゲートとの間に配置された第2のツェナーダイオード151を含んであってもよい。

【0067】

また、他の実施形態によれば、出力駆動回路10の第1及び第2のスイッチ113、133は、それぞれ、NチャネルMOSFETまたはNチャネルLDMOSFETで構成されてもよい。

【0068】

今回開示された実施の形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、前記した実施の形態の説明では、なくて特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0069】

10 出力駆動回路

30 Pチャネル出力トランジスタ

40 Nチャネル出力トランジスタ

110 第1の駆動回路部

111 第1のトランジスタ

113 第1のスイッチ

115 第1のトランジスタ駆動電圧クランピング部

1151 第1のツェナーダイオード

1153 抵抗

1155 第3のトランジスタ

1156 第4のトランジスタ

1157 第3のスイッチ

130 第2の駆動回路部

131 第2のトランジスタ

133 第2のスイッチ

135 パルス生成器

150 出力駆動電圧クランピング部

151 第2のツェナーダイオード

【技術分野】

【0001】

本発明は、出力駆動回路及びトランジスタ出力回路に関し、特に、出力トランジスタのゲートに、ソース−ドレイン間の降伏電圧より小さく、ゲート−ソース間の降伏電圧より大きい高電圧が印加される場合、安定して動作可能な出力駆動回路及びトランジスタ出力回路に関する。

【背景技術】

【0002】

Pチャネルトランジスタ、例えばPチャネル−LDMOSの動作電圧は、ソース−ドレイン間の降伏電圧BVsd、ソース−ゲート間の降伏電圧BVsg及びゲート−ドレイン間の降伏電圧BVgdによって決まる。このうち、ソース−ゲート間の降伏電圧BVsgが一番小さい。ソース−ゲート間の降伏電圧BVsgは、ゲート酸化物の厚さによって決まる。これは、酸化物(Oxide)の厚さによって、トランジスタの閾値電圧Vth、ソース−ドレイン間の電流Isd、オン抵抗Ronなどが決まり、ゲート酸化物の厚さを無制限厚くすることができないためである。電源電圧がソース−ドレイン間の降伏電圧BVsdより小さく、ソース−ゲート間の降伏電圧BVsgより大きい場合、ソース端子に電源電圧を接続し、ドレイン端子に低電位(グラウンドなど)を接続しても間題がない。

【0003】

しかし、このようなトランジスタを動作させるためには、ゲート端子に電源電圧及び低電位(グラウンド)電圧を印加すると、ソース−ゲート間の電圧Vsgに電源電圧がかかるようになり、該電源電圧は、ソース−ゲート間の降伏電圧BVsgより大きいので、トランジスタ素子が破壊される恐れがある。

【0004】

図6は、従来の出力駆動回路を概略的に示す図面である。

【0005】

図6では、スイッチSW1がオフすると、電源電圧Vdd及び出力トランジスタT1のゲートに接続された抵抗R及びツェナーダイオードZ1に所与の電流Iが流れ、ツェナーダイオードZ1によって出力トランジスタT1のソース−ゲート間の電位をソース−ゲート間の降伏電圧BVsgより小さく閾値電圧Vthより大きくすることによって、出力トランジスタT1を駆動させる。逆に、スイッチSW1はオンし、出力トランジスタT1のゲート電位が電源電圧Vdd及び出力トランジスタT1のゲートに接続された抵抗Rによって電源電圧Vddまで上昇して、出力トランジスタT1をオフさせる。

【0006】

一方、図6と異なり、比較的高い周波数で動作させるために、出力トランジスタT1をオフさせる手段を、抵抗Rではなく、カレントミラー(Current Mirror)を用いる場合もある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】韓国特許第10−0489870号公報

【特許文献2】特開2008−147755号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

図6の従来技術では、出力トランジスタT1のゲート−ソースのキャパシタを、抵抗を通じて充電すると共に電流源を通じて放電するため、比較的高い周波数に対して不利で、出力トランジスタT1のオン状態を維持するために電流Iが抵抗R、及びツェナーダイオードZ1を通じて流れ続けて、消費電流が増大するという短所がある。

【0009】

また、比較的高い周波数で動作させるために、出力トランジスタT1をオフさせる手段としてカレントミラーを用いる場合、出力トランジスタT1のゲート−ソースのキャパシタンスを早い速度で充電するためには、高いカレントミラー比を持たなければならない。図6と同様に、出力トランジスタT1のゲート−ソースのキャパシタンスを早い速度で放電するためには、大電流Iが必要になる。また、この場合にも、図6のように、出力トランジスタT1のオン状態を維持するためには、大電流IがツェナーダイオードZ1を通じて流れ続けるため、消費電流が高いという短所を有する。

【0010】

本発明は、上記の間題点に鑑みて成されたものであって、その目的は、出力トランジスタのゲートに、ソース−ドレイン間の降伏電圧より小さく、ゲート−ソース間の降伏電圧より大きい高電圧が印加される場合に、安定して動作可能な出力駆動回路及びトランジスタ出力回路を提供することにある。

【0011】

また、本発明の他の目的は、高い周波数動作でも安定した動作を行うと共に、低い消費電流でも安定した動作を行う出力駆動回路及びトランジスタ出力回路を提供することにある。

【課題を解決するための手段】

【0012】

上記目的を解決するために、本発明によれば、第1のスイッチのオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタを含む第1の駆動回路部と、該第1のスイッチと相補的に動作する第2のスイッチのオン動作によって生成されたワンショットパルスとによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタを含む第2の駆動回路部と、前記第1の駆動回路部と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチのオン動作によって放電された出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部と、を含む出力駆動回路が提供される。

【0013】

本発明によれば、前記第2の駆動回路部は、第1のスイッチと相補的に動作すると共に、オン動作によって出力駆動電圧クランピング部を通じて流れる電流を、低電圧電源端へと切り換える第2のスイッチと、該第2のスイッチのオン動作によって、第2のトランジスタを駆動させるためのワンショットパルスを生成するパルス生成器と、該ワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させるNチャネルの第2のトランジスタと、を含む。

【0014】

本発明によれば、前記第1の駆動回路部は、第1のスイッチと、高電圧電源端にソース電極が接続され、第1のスイッチのオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給するPチャネルの第1のトランジスタと、該第1のスイッチのオン動作によって、高電圧電源端から第1のトランジスタのゲートに供給される駆動電圧をクランピングする第1のトランジスタ駆動電圧クランピング部と、を含む。

【0015】

また、本発明によれば、第1のトランジスタ駆動電圧クランピング部は、高電圧電源端と第1のトランジスタのゲートとの間に配置され、互いに並列接続された抵抗と第1のツェナーダイオードとを含む。

【0016】

また、本発明によれば、第1のトランジスタ駆動電圧クランピング部は、高電圧電源端と第1のトランジスタのゲートとの間に配置された第1のツェナーダイオードと、該第1のツェナーダイオードに並列接続されたカレントミラーと、該第1のトランジスタのゲートに対向する前記カレントミラーの下端に接続され、第1のスイッチと相補的に動作する第3のスイッチとを含む。

【0017】

本発明によれば、カレントミラーは、高電圧電源端にソース電極が接続された第3及び第4のトランジスタのミラー構造で構成され、該第3及び第4のトランジスタは、PチャネルMOSFETまたはPチャネルLDMOSFETであり、第4のトランジスタのドレイン電極は、第1のトランジスタのゲートに接続され、第3のトランジスタのドレイン電極は、第3のスイッチと第3及び第4のトランジスタのゲート電極とに接続される。第3のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETで構成される。

【0018】

また、本発明によれば、出力駆動電圧クランピング部は、高電圧電源端と出力トランジスタのゲートとの間に配置された第2のツェナーダイオードを含む。

【0019】

また、本発明によれば、第1のトランジスタのゲート−ソースのキャパシタンスは、出力トランジスタのゲート−ソースのキャパシタンスより小さいし。

【0020】

また、本発明によれば、第1及び第2のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETで構成される。

【0021】

また、本発明によれば、出力トランジスタは、第2の駆動回路部の駆動によって駆動されて高電圧電源を出力するPチャネルMOSFETまたはPチャネルLDMOSFETである。

【0022】

また、上記目的を解決するために、本発明の他の例によれば、高電圧電源端にソース電極が接続され、駆動によってドレイン電極を通じて高電圧電源を出力するPチャネル出力トランジスタと、該Pチャネル出力トランジスタと相補的に動作し、駆動によってPチャネル出力トランジスタのドレイン電極と接続されたドレイン電極からソース電極が接続された低電圧電源端に電源を出力するNチャネル出力トランジスタと、相補的スイッチング動作によってPチャネル及びNチャネル出力トランジスタの各々を駆動する前述の実施形態のうちのいずれか一つによる出力駆動回路とを含むトランジスタ出力回路が提供される。

【0023】

本発明によれば、出力駆動回路の出力駆動電圧クランピング部は、高電圧電源端とPチャネル出力トランジスタのゲートとの間に配置された第2のツェナーダイオードを含む。

【0024】

また、本発明によれば、出力駆動回路の第1及び第2のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETで構成される。

【発明の効果】

【0025】

本発明によれば、出力トランジスタのゲートにソース−ドレイン間の降伏電圧より小さくゲート−ソース間の降伏電圧より大きい高電圧が印加される場合、安定して動作可能な出力駆動回路及びトランジスタ出力回路を得ることができる。

【0026】

また、本発明によれば、高い周波数動作でも安定な動作を行うと共に、低い消費電流でも安定な動作を行う出力駆動回路及びトランジスタ出力回路を得ることができる。

【0027】

本発明の多様な実施形態によって直接的に言及されなかった多様な効果が、本発明の実施形態による多様な構成から、該当技術分野において通常の知識を有する者によって導出されることができることは自明である。

【図面の簡単な説明】

【0028】

【図1】本発明の一実施形態による出力駆動回路を概略的に示すブロック図である。

【図2】本発明の一実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図である。

【図3】本発明の一実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図である。

【図4】本発明の一実施形態による出力駆動回路のシミュレーション結果を示すグラフである。

【図5】本発明の一実施形態によるワンショットパルスの効果を示すグラフである。

【図6】従来の出力駆動回路を概略的に示す図面である。

【発明を実施するための形態】

【0029】

以下、本発明の好適な実施の形態を、図面を参照して詳細に説明する。次に示される各実施の形態は、当業者にとって本発明の思想が十分に伝達されることができるようにするために例として挙げられるものである。従って、本発明は、以下示している各実施の形態に限定されることなく、他の形態で具体化されることができる。そして、図面において、装置の大きさ及び厚さなどは、便宜上誇張して表現されることがある。明細書全体に渡って同一の参照符号は、同一の構成要素を示している。

【0030】

具体的な説明に先立ち、本明細書において一つの構成要素が他の構成要素と「直接接続」または「直接結合」のように言及されない限り、単に「接続」また「結合」の表現で言及された場合は、「直接的に」接続または結合されてもよく、ひいては、それらの間に異なる構成要素が挿入されて接続または結合されるような形態でもよい。

【0031】

本明細書上に、例えば、単数の表現が記載されていても、発明の概念に反していなく、解釈上矛盾するかまたは明白に異なるように解釈されない限り、複数の構成全体を代表する概念として使われることもあるに留意されたい。

【0032】

本明細書で使われた用語は、実施形態を説明するためのものであって、本発明を制限しようとするものではない。本明細書において、単数形は、特別に言及しない限り複数形も含む。明細書で使われる「含む」とは、言及された構成要素、ステップ、動作及び/又は、素子は、一つ以上の他の構成要素、ステップ、動作及び/又は、素子の存在または追加を排除しないことに理解されたい。

【0033】

まず、図面を参照して、本発明の第1の実施形態による出力駆動回路について詳記する。

【0034】

図1は、本発明の一実施形態による出力駆動回路を概略的に示すブロック図であり、図2は、本発明の一実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図であり、図3は、本発明の一実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図である。図4は、本発明の一実施形態による出力駆動回路のシミュレーション結果を示すグラフであり、図5は、本発明の一実施形態によるワンショットパルスの効果を示すグラフである。

【0035】

図1、図2及び図3を参照して、本発明の実施形態による出力駆動回路について説明する。図1、図2及び図3を参照して、出力駆動回路10は、第1の駆動回路部110、第2の駆動回路部130及び出力駆動電圧クランピング部150を含む。

【0036】

詳しくは、第1の駆動回路部110は、第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源(Vdd)を供給する第1のトランジスタ111を含む。一例として、出力トランジスタは、Pチャネルトランジスタ30であってもよい。また一例として、出力トランジスタは、PチャネルMOSFETまたはPチャネルLDMOS(Latera1 Double Diffused Metal Oxide Semiconductor)FETであってもよい。出力トランジスタがPチャネルトランジスタの場合、第1のトランジスタ111の駆動によってゲートにソース電極に供給される高電圧電源(Vdd)が同じく供給されるため、トランジスタはオフされる。また一例として、第1のトランジスタ111は、Pチャネルトランジスタ、例えば、PチャネルMOSFETまたはPチャネルLDMOSFETであってもよい。また一例として、第1のスイッチ113は、NチャネルMOSFETまたはNチャネルLDMOSFETで構成されてもよい。

【0037】

一実施形態において、図2及び図3に示すように、第1の駆動回路部110は、第1のスイッチ113と、第1のトランジスタ111と、第1のトランジスタ駆動電圧クランピング部115とを含む。

【0038】

第1のトランジスタ111はPチャネルトランジスタであってもよく、このPチャネルトランジスタは、高電圧電源端(Vdd)にソース電極が接続され、第1のスイッチ113のオン動作によって駆動される。Pチャネルトランジスタは、その駆動によって出力トランジスタ、例えばPチャネルの出力トランジスタのゲートに高電圧電源(Vdd)を供給する。これによって、高電圧電源(Vdd)をゲート電源として印加されるPチャネル出力トランジスタ30は、オフ動作する。

【0039】

次に、図2及び図3に示すように、第1のトランジスタ駆動電圧クランピング部115は、第1のスイッチ113のオン動作によって、高電圧電源端(Vdd)から第1のトランジスタ111のゲートに供給される駆動電圧をクランピングする。これによって、第1のトランジスタ111のソース−ゲート間の電圧が降伏電圧(BVsg)を超えないように第1のトランジスタ111が保護される。

【0040】

詳しくは、図2に示すように、第1のトランジスタ駆動電圧クランピング部115は、高電圧電源端(Vdd)と第1のトランジスタ111のゲートとの間に配置され、抵抗1153及び第1のツェナーダイオード1151を含む。抵抗1153及び第1のツェナーダイオード1151は、高電圧電源端(Vdd)と第1のトラングスタ111のゲートとの間に配置され、互いに並列接続される。第1のスイッチ113のオン動作によって、抵抗1153及び第1のツェナーダイオード1151を通じて流れる定電流I1が、第1のスイッチ113を通じて低電圧電源(Vss)、例えばグラウンドを通じて流出されるようになる。

【0041】

また、図3を参照して、他の実施形態について詳記する。図3に示すように、第1のトランジスタ駆動電圧クランピング部115は、図2の抵抗1153をカレントミラー構造で代替することができる。例えば、第1のトランジスタ駆動電圧クランピング部115は、高電圧電源端(Vdd)と第1のトランジスタ111のゲートとの間に配置された第1のツェナーダイオード1151と、該第1のツェナーダイオード1151に並列接続されたカレントミラーと、第1のトランジスタ111のゲートに対向するカレントミラーの下端に接続され、第1のスイッチ113と相補的に動作する第3のスイッチ1157とを含む。また、図3に示すように、カレントミラーは、高電圧電源端(Vdd)にソース電極が接続された第3及び第4のトランジスタ1155、1156のミラー構造で構成される。第4のトランジスタ1156のドレイン電極は、第1のトランジスタ111のゲートに接続され、第3のトランジスタ1155のドレイン電極は、第3のスイッチ1157と第3及び第4のトランジスタ1155、1156のゲート電極に接続される。第3及び第4のトランジスタ1155、1156は、PチャネルMOSFETまたはPチャネルLDMOSFETであってもよい。また、第3のスイッチ1157は、NチャネルMOSFETまたはNチャネルLDMOSFETで構成されてもよい。

【0042】

また、図2及び図3を参照して、本発明の他の実施形態について説明する。第1のトランジスタ111のゲート−ソースのキャパシタンスは、出力トランジスタのゲート−ソースのキャパシタンスより小さい。第1のトランジスタ111のゲート−ソースのキャパシタンスを、出力トランジスタのゲート−ソースのキャパシタンスより充分に小さくすることによって、第1のトランジスタ駆動電圧クランピング部での充電速度を早くすることができる。第1のトランジスタ111は、出力トランジスタより小さなサイズで形成されてもよい。例えば、第1のトランジスタ111が、例えばPチャネル出力トランジスタ30より充分に小さい場合、すなわち、例えば1/20程度に小さなサイズの場合、第1のトランジスタ111のゲート−ソースのキャパシタンスが、Pチャネル出力トランジスタ30のゲート−ソースのキャパシタンスより充分に小さいので、第1のトランジスタ駆動電圧クランピング部での充電速度、特に第1のトランジスタ駆動電圧クランピング部の抵抗1153による充電速度が早くなることになる。これによって、第1のスイッチ113のオン動作によって、第1のトランジスタ駆動電圧クランピング部を通じて流れる電流源11が小さい場合にも、Pチャネルの第1のトランジスタ111を充分に早い速度でオフさせることができる。したがって、電流源11を小さく設計することができ、消費電流も減らして比較的高い周波数でも動作が容易になるようにできる。

【0043】

一実施形態によれば、第1のスイッチ113は、Nチャネルトランジスタ、例えば、NチャネルMOSFETまたはNチャネルLDMOSFETで構成されてもよい。Nチャネルトランジスタの場合、ゲート−ソース間の降伏電圧(BVgs)は、例えば、5V程度と低いが、ドレイン−ソース間の降伏電圧(BVds)は、高電圧電源(Vdd)に相当する高耐圧を有するようになる。

【0044】

図2を参照して、第1の駆動回路部110の動作の一例について詳記する。図2に示すように、第1の駆動回路部110の第1のスイッチ113のAと第2の駆動回路部130の第2のスイッチ133のBとは、異なる位相にて動作する。第1のスイッチ113のAがオフされると、第2のスイッチ133のBはオンされ、第1のスイッチ113のAがオンすると、第2のスイッチ133のBはオフされるようになる。第1のスイッチ113のAがオフされ、第2のスイッチ133のBがオンされると、抵抗1153(R)及び第1のツェナーダイオード1151(Z1)に電流源I1の電流が流れるようになり、第1のトランジスタ111(P1)のゲート電位は、閾値電圧Vthより大きく、ソース−ゲート間の降伏電圧BVsgより小さくなって、第1のトランジスタ111(P1)がオン動作する。すると、出力トランジスタT1のゲート−ソースのキャパシタンスが早く充電され、出力トランジスタT1をオフさせる。

【0045】

また、図3を参照して、第1の駆動回路部110の動作の他例について詳記する。図3に示すように、第1の駆動回路部110の第1のスイッチ113のAと、第2の駆動回路部130の第2のスイッチ133のBとは、異なる位相にて動作する。第1の駆動回路部110の第1のスイッチ113のAと第3のスイッチ1157のAとも相補的に動作する。詳しくは、第1のスイッチ113Aのがオフされると、第2のスイッチ133のB及び第3のスイッチ1157はオンされる。また、第1のスイッチ113のAがオンされると、第2のスイッチ133のB及び第3のスイッチ1157はオフされる。第1のスイッチ113のAがオンされ、第3のスイッチ1157がオフされると、カレントミラー構造の第3及び第4のトランジスタ1155、1156によって、カレントミラー比分、第4のトランジスタ1156(P3)に電流が流れるようになる。すると、第1のトランジスタ111(P1)のゲート−ソースのキャパシタンスを充電させ、第1のトランジスタ111(P1)のゲート電位を高電圧電源(Vdd)まで上がるようにして、第1のトランジスタ111(P1)をオフさせる。反対に、第1のスイッチ113Aがオフされ、第3のスイッチ1157がオンされると、第1のスイッチ113Aを通じて電流源I1が流れるようになる。すると、第1のトランジスタ111(P1)のゲート電位は、閾値電圧Vthより大きく、ソース−ゲート間の降伏電圧BVsgより小さくなって、第1のトランジスタ111(P1)がオン動作する。第1のトランジスタ111(P1)がオン動作すると、出力トランジスタT1のゲート−ソースのキャパシタンスが早く充電され、出力トランジスタT1をオフさせる。図3に示すように、第1のトランジスタ111(P1)が出力トランジスタ30(T1)よりずっと小さいため、I3のように小さな電流でも早いスイッチングができる。

【0046】

続いて、図1、図2及び図3を参照して、第2の駆動回路部130について説明する。第2の駆動回路部130は、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作により生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む。一例として、第2のトランジスタ131は、Nチャネルトランジスタ、例えば、NチャネルMOSFETまたはNチャネルLDMOSFETが挙げられる。第2のトランジスタ131が駆動されると、ドレイン電極に接続された出力トランジスタのゲートから充電されていたゲート−ソースのキャパシタンスを、ソース電極に接続される低電圧電源、例えばグラウンドへと、急に抜き取って放電させることができる。

【0047】

この実施形態において、出力トランジスタは、第2の駆動回路部130の駆動によって駆動される。一例として、出力トランジスタは、Pチャネルトランジスタ30であってもよい。また一例として、出力トランジスタは、第2の駆動回路部130の駆動によって高電圧電源(Vdd)を出力するPチャネルMOSFETまたはPチャネルLDMOSFETであってもよい。

【0048】

一実施形態において、図2を参照して、第2の駆動回路部130についてより詳しく説明する。第2の駆動回路部130は、第2のスイッチ133、パルス生成器135及び第2のトランジスタ131を含む。第2のスイッチ133は、第1の駆動回路部110の第1のスイッチ113と相補的に動作する。第2のスイッチ133のオン動作によって出力駆動電圧クランピング部150を通じて流れる電流を、低電圧電源端(Vss)へと切り換える。パルス生成器135は、第2のスイッチ133のオン動作によって動作し、第2のトランジスタ131を駆動させるためのワンショットパルスを生成する。第2のトランジスタ131はNチャネルトランジスタであってもよく、このNチャネルの第2のトランジスタ131は、パルス生成器135によって生成されたワンショットパルスを、ゲート電源として入力され駆動される。Nチャネルの第2のトランジスタ131の駆動によって、ドレイン電極に接続された出力トランジスタのゲート電極からゲート−ソースのキャパシタンスを放電させ、電流をソース電極に接続された低電圧電源(Vss)、例えばグラウンドへと流す。Nチャネルの第2のトランジスタ131によって、出力トランジスタのゲート電極のゲート−ソースのキャパシタンスを急に放電させた後、オン動作した第2のスイッチ133を通じて、出力駆動電圧クランピング部150を通って流れる電流を低電圧電源端へと流すと、放電した出力トランジスタのゲート電位が一定に維持される。これによって、出力トランジスタが駆動され、Pチャネル出力トランジスタ30からソース電極の高電圧電源(Vdd)がドレイン電極を通じて出力される。

【0049】

また、一実施形態によれば、第2のスイッチ133としては、Nチャネルトランジスタ、例えば、NチャネルMOSFETまたはNチャネルLDMOSFETが挙げられる。この第2のスイッチ133を形成するNチャネルトランジスタは、ゲート−ソース間の降伏電圧(BVgs)が、例えば5V程度と低いが、ドレイン−ソース間の降伏電圧(BVds)は、高電圧電源(Vdd)に相当する高い耐圧を有するようになる。

【0050】

また、図2及び図3を参照して、第2の駆動回路部130の動作について詳記する。図2及び図3に示すように、第1の駆動回路部110の第1のスイッチ113Aと第2の駆動回路部130の第2のスイッチ113Bとは、互いに異なる位相にて動作する。第1のスイッチ113Aがオンされ第2のスイッチ133Bがオフされると、パルス生成器135で生成されたワンショットパルスによって、第2のトランジスタ131(N1)が瞬間的に動作し、出力トランジスタT1のゲート−ソースのキャパシタンスを早く放電させる。該ワンショットパルスによって、第2のトランジスタ131(N1)は、ゲート−ソースのキャパシタンスを早く放電させた後オフされる。出力駆動電圧クランピング部150の第2のツェナーダイオード151(Z2)には、電流源I2の電流が流れ、出力トランジスタT1のゲート−ソースのキャパシタンスが放電した状態で、出力トランジスタT1のゲート電位が一定に維持され、出力トランジスタT1が動作する。この出力トランジスタT1の駆動によって、高電圧電源(Vdd)がソース電極から、ドレイン電極を通じて出力されるようになる。

【0051】

出力トランジスタT1のオン動作を保持させる電流源I2は、ワンショットパルスによって動作する第2のトランジスタ131(N1)が、先に出力トランジスタT1のゲート−ソースのキャパシタンスを放電させるため、小さく設計されてもよい。それに伴って、消費電流も減らすと共に、比較的高い周波数でも動作が容易になる。

【0052】

次に、図1、図2及び図3を参照して、出力駆動電圧クランピング部150について説明する。出力駆動電圧クランピング部150は、第1の駆動回路部110と並列されるように高電圧電源端(Vdd)と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる。これによって、第2の駆動回路部130の駆動で、詳しくは、第2のスイッチ133のオン動作で、出力トランジスタが駆動され、該出力トランジスタを通じて高電圧電源(Vdd)が出力される。

【0053】

図2及び図3に示すように、一実施形態において、出力駆動電圧クランピング部150は、高電圧電源端(Vdd)と出力トランジスタのゲートとの間に配置された第2のツェナーダイオード151を含む。第2のスイッチ133のオン動作によって、第2のトランジスタ131がワンショットパルスにより駆動され、出力トランジスタのゲート電極に充電されたゲート−ソースのキャパシタンスを瞬間的に放電させる。該放電の後、第2のスイッチ133によって、第2のツェナーダイオード151を通じて流れる定電流電流源I2がグラウンドへと流出されることになる。これによって、出力トランジスタのゲート電位が一定に維持され、Pチャネルの出力トランジスタが駆動するようになる。出力駆動電圧クランピング部150、例えば図2及び図3の第2のツェナーダイオード151(Z2)は、例えば、Pチャネル出力トランジスタ30(T1)のソース−ゲート間の電圧が降伏電圧BVsgを超えないようにして、出力トレンジストトT1を保護する。

【0054】

図4を参照して、本発明の実施形態によるシミュレーションの結果について説明する。

【0055】

図4は、図2の実施形態による回路のシミュレーション結果を示す波形図である。高電圧電源(Vdd)にVdd=20Vを印加し、出力トランジスタ30(T1)の定格作動電圧(Recommended Operating Voltage)で、ソース−ゲート間電圧Vsg≦12V、ソース−ドレイン間電圧Vsd≦0VであるPチャネルLDMOSで構成された回路をシミュレーションした。

【0056】

波形/Aは第1のスイッチ113のAの制御信号で、波形/Bは第2のスイッチ133のBの制御信号で、波形/One_Shotはワンショットパルスの出力波形で、波形/N1/Dは、ワンショットパルスによって第2のトランジスタ131(N1)のドレインに流れる電流で、波形/D0/NEGは、第2のツェナーダイオード151(Z2)に流れる電流で、波形/Vgは出力トランジスタT1のゲート電位である。

【0057】

第1及び第2のスイッチ113のA、133のBは、シミュレーションのように0V/5Vによってコントロールされる。第1のスイッチ113のAに5Vの信号が入力されると、第1のスイッチ113のAはオフされ、第1のトランジスタ111(P1)がオンされる。すると、出力トランジスタT1のゲート電位を20Vとして印加し、ソース−ゲート間電位を0Vにして、出力トランジスタT1をオフさせる。反対に、第1のスイッチ113のAに0Vの信号を印加し、第2のスイッチ133のBに5Vの信号を印加すると、第1のスイッチ113のAはオンされ、第2のスイッチ133のBはオフされる。第2のスイッチ133のBがオフされると、ワンショットパルスによって出力トランジスタT1のゲート−ソースのキャパシタンスが放電し、電流源I2と第2のツェナーダイオード151(Z2)とによって、出力トランジスタT1のゲート電位Vgは、8.687Vに維持され、ソース−ゲート間電位Vsgは、Vsg=20−8.687=11.723Vとして、定格作動電庄内の電圧を有し、正常にオンされる。第2のツェナーダイオード151(Z2)に低い100uAが流れても、出力トランジスタT1のゲート電位Vgが8.687Vとして、出力トランジスタT1がオン状態を維持することを分かる。

【0058】

図5を参照して、ワンショットパルスによる動作について説明する。このため、図5では、図4中の破線区間内のシミュレーション波形を拡大して示す。

【0059】

ワンショットパルスは、第2のスイッチ133のBの制御電圧が、0Vから5Vに変わる時に生成されるパルスであって、図5のシミュレーション結果のように、100nsのパルス信号が生成されることが分かる。この信号によって、実施形態による回路の第2のトランジスタ131(N1)が瞬間的にオンされ、4mAの電流で出力トランジスタT1のゲート−ソースのキャパシタンスを放電させ、出力トランジスタT1のゲート電圧Vgの立ち下がりタイム(falling time)が25nsで、早い速度でオンされることが分かる。

【0060】

すなわち、従来の出力駆動回路では、図5のシミュレーション結果のように、早い速度でオンさせ、該オン状態を維持するためには、4mAの電流が必要となるが、本実施形態による回路は、ワンショットパルスによって迅速にオンさせ、1OOusの電流で、オン状態を維持することができる。そのため消費電流が非常に小さくなる。

【0061】

次に、本発明の第2の実施形態によるトランジスタ出力回路について説明する。図2は、本発明の一実施形態によるトランジスタ出力回路を示す回路図である。図3は、本発明の他の実施形態による出力駆動回路を含むトランジスタ出力回路を示す回路図である。

【0062】

図2及び図3に示すように、本実施形態によるトランジスタ出力回路は、Pチャネル出力トランジスタ30、Nチャネル出力トランジスタ40及び出力駆動回路10を含む。図2及び図3に示すように、出力駆動回路10とPチャネル及びNチャネル出力トランジスタ30、40との接続は、出力駆動回路10が、相補的にPチャネル及びNチャネル出力トランジスタ30、40を駆動させることを示している。出力駆動回路10は、前述の第1の実施形態に示す出力駆動回路10である。したがって、本実施形態の説明に当って、先の出力駆動回路10の実施形態を参照し、重複する説明は省略することにする。

【0063】

図2及び図3に示すように、Pチャネル出力トランジスタ30は、高電圧電源端(Vdd)にソース電極が接続され、駆動によってドレイン電極を通じて高電圧電源(Vdd)を出力する。前述の実施形態による出力駆動回路10がPチャネル出力トランジスタ30を駆動させる。

【0064】

Nチャネル出力トランジスタ40は、Pチャネル出力トランジスタ30と相補的に動作する。Nチャネル出力トランジスタ40は、その駆動によって、Pチャネル出力トランジスタ30のドレイン電極に接続されたドレイン電極から、ソース電極が接続された低電圧電源端へと電源を出力する。前述の実施形態による出力駆動回路10が、Pチャネル出力トランジスタ30を駆動させることと相補的に、Nチャネル出力トランジスタ40を駆動させるようになる。

【0065】

出力駆動回路10における第2の駆動回路部130の第2のスイッチ133のオン動作によって、Pチャネル出力トランジスタ30が駆動され、第2のスイッチ133と相補的に動作する第1のスイッチ113のオン動作によって、Nチャネル出力トランジスタ40が駆動される。

【0066】

また、一実施形態によれば、出力駆動回路10の出力駆動電圧クランピング部150は、高電圧電源端(Vdd)とPチャネル出力トランジスタ30のゲートとの間に配置された第2のツェナーダイオード151を含んであってもよい。

【0067】

また、他の実施形態によれば、出力駆動回路10の第1及び第2のスイッチ113、133は、それぞれ、NチャネルMOSFETまたはNチャネルLDMOSFETで構成されてもよい。

【0068】

今回開示された実施の形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、前記した実施の形態の説明では、なくて特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0069】

10 出力駆動回路

30 Pチャネル出力トランジスタ

40 Nチャネル出力トランジスタ

110 第1の駆動回路部

111 第1のトランジスタ

113 第1のスイッチ

115 第1のトランジスタ駆動電圧クランピング部

1151 第1のツェナーダイオード

1153 抵抗

1155 第3のトランジスタ

1156 第4のトランジスタ

1157 第3のスイッチ

130 第2の駆動回路部

131 第2のトランジスタ

133 第2のスイッチ

135 パルス生成器

150 出力駆動電圧クランピング部

151 第2のツェナーダイオード

【特許請求の範囲】

【請求項1】

第1のスイッチのオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタを含む第1の駆動回路部と、

前記第1のスイッチと相補的に動作する第2のスイッチのオン動作によって生成されたワンショットパルスによって駆動され、前記出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタを含む第2の駆動回路部と、

前記第1の駆動回路部と並列されるように高電圧電源端と前記出力トランジスタのゲートとの間に配置され、前記第2のスイッチのオン動作によって放電した前記出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部

とを含む出力駆動回路。

【請求項2】

前記第2の駆動回路部は、

前記第1のスイッチと相補的に動作すると共にオン動作によって前記出力駆動電圧クランピング部を通じて流れる電流を低電圧電源端へと切り換える第2のスイッチと、

前記第2のスイッチのオン動作によって、前記第2のトランジスタを駆動させるための前記ワンショットパルスを生成するパルス生成器と、

前記ワンショットパルスによって駆動され、前記出力トランジスタのゲート−ソースのキャパシタンスを放電させるNチャネルの第2のトランジスタ

とを含む請求項1lに記載の出力駆動回路。

【請求項3】

前記第1の駆動回路部は、

第1のスイッチと、

前記高電圧電源端にソース電極が接続され、前記第1のスイッチのオン動作によって駆動され、前記出力トランジスタのゲートに前記高電圧電源を供給するPチャネルの第1のトランジスタと、

前記第1のスイッチのオン動作によって前記高電圧電源端から前記第1のトランジスタのゲートに供給される駆動電圧をクランピングする第1のトランジスタ駆動電圧クランピング部

とを含む請求項1に記載の出力駆動回路。

【請求項4】

前記第1の駆動回路部は、

第1のスイッチと、

前記高電圧電源端にソース電極が接続され、前記第1のスイッチのオン動作によって駆動され、前記出力トランジスタのゲートに前記高電圧電源を供給するPチャネルの第1のトランジスタと、

前記第1のスイッチのオン動作によって、前記高電圧電源端から前記第1のトランジスタのゲートに供給される駆動電圧をクランピングする第1のトランジスタ駆動電圧クランピング部

とを含む請求項2に記載の出力駆動回路。

【請求項5】

前記第1のトランジスタ駆動電圧クランピング部は、前記高電圧電源端と前記第1のトランジスタのゲートとの間に配置され、互いに並列接続された抵抗と第1のツェナーダイオードとを含む請求項3または4に記載の出力駆動回路。

【請求項6】

前記第1のトランジスタ駆動電圧クランピング部は、前記高電圧電源端と前記第1のトランジスタのゲートとの間に配置された第1のツェナーダイオードと、前記第1のツェナーダイオードに並列接続されたカレントミラーと、前記第1のトランジスタのゲートに対向する前記カレントミラーの下端に接続され、前記第1のスイッチと相補的に動作する第3のスイッチとを含む請求項3または4に記載の出力駆動回路。

【請求項7】

前記カレントミラーは、前記高電圧電源端にソース電極が接続された第3及び第4のトランジスタのミラー構造で構成され、

前記第3及び第4のトランジスタは、PチャネルMOSFETまたはPチャネルLDMOSFETであり、

前記第4のトランジスタのドレイン電極は、前記第1のトランジスタのゲートに接続され、前記第3のトランジスタのドレイン電極は、前記第3のスイッチ及び前記第3及び第4のトランジスタのゲート電極に接続され、

前記第3のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETから成る請求項6に記載の出力駆動回路。

【請求項8】

前記出力駆動電圧クランピング部は、前記高電圧電源端と前記出力トランジスタのゲートとの間に配置された第2のツェナーダイオードを含む請求項1〜4のうちのいずれか一つに記載の出力駆動回路。

【請求項9】

前記第1のトランジスタのゲート−ソースのキャパシタンスが、前記出力トランジスタのゲート−ソースのキャパシタンスより小さい請求項1〜4のうちのいずれか一つに記載の出力駆動回路。

【請求項10】

前記第1及び第2のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETから成る請求項1〜4のうちのいずれか一つに記載の出力駆動回路。

【請求項11】

前記出力トランジスタは、前記第2の駆動回路部の駆動によって駆動され、前記高電圧電源を出力するPチャネルMOSFETまたはPチャネルLDMOSFETである請求項1〜4のうちのいずれか一つに記載の出力駆動回路。

【請求項12】

高電圧電源端にソース電極が接続され、駆動によってドレイン電極を通じて高電圧電源を出力するPチャネル出力トランジスタと、

前記Pチャネル出力トランジスタと相補的に動作し、駆動によって前記Pチャネル出力トランジスタのドレイン電極と接続されたドレイン電極から、ソース電極が接続された低電圧電源端へと電源を出力するNチャネル出力トランジスタと、

相補的スイッチング動作によって、前記Pチャネル及びNチャネル出力トランジスタの各々を駆動する請求項1〜4のうちのいずれか一つによる出力駆動回路とを含むトランジスタ出力回路。

【請求項13】

前記出力駆動回路の出力駆動電圧クランピング部は、前記高電圧電源端と前記Pチャネル出力トランジスタのゲートとの間に配置された第2のツェナーダイオードを含む請求項12に記載のトランジスタ出力回路。

【請求項14】

前記出力駆動回路の第1及び第2のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETから成る請求項12に記載のトランジスタ出力回路。

【請求項1】

第1のスイッチのオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタを含む第1の駆動回路部と、

前記第1のスイッチと相補的に動作する第2のスイッチのオン動作によって生成されたワンショットパルスによって駆動され、前記出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタを含む第2の駆動回路部と、

前記第1の駆動回路部と並列されるように高電圧電源端と前記出力トランジスタのゲートとの間に配置され、前記第2のスイッチのオン動作によって放電した前記出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部

とを含む出力駆動回路。

【請求項2】

前記第2の駆動回路部は、

前記第1のスイッチと相補的に動作すると共にオン動作によって前記出力駆動電圧クランピング部を通じて流れる電流を低電圧電源端へと切り換える第2のスイッチと、

前記第2のスイッチのオン動作によって、前記第2のトランジスタを駆動させるための前記ワンショットパルスを生成するパルス生成器と、

前記ワンショットパルスによって駆動され、前記出力トランジスタのゲート−ソースのキャパシタンスを放電させるNチャネルの第2のトランジスタ

とを含む請求項1lに記載の出力駆動回路。

【請求項3】

前記第1の駆動回路部は、

第1のスイッチと、

前記高電圧電源端にソース電極が接続され、前記第1のスイッチのオン動作によって駆動され、前記出力トランジスタのゲートに前記高電圧電源を供給するPチャネルの第1のトランジスタと、

前記第1のスイッチのオン動作によって前記高電圧電源端から前記第1のトランジスタのゲートに供給される駆動電圧をクランピングする第1のトランジスタ駆動電圧クランピング部

とを含む請求項1に記載の出力駆動回路。

【請求項4】

前記第1の駆動回路部は、

第1のスイッチと、

前記高電圧電源端にソース電極が接続され、前記第1のスイッチのオン動作によって駆動され、前記出力トランジスタのゲートに前記高電圧電源を供給するPチャネルの第1のトランジスタと、

前記第1のスイッチのオン動作によって、前記高電圧電源端から前記第1のトランジスタのゲートに供給される駆動電圧をクランピングする第1のトランジスタ駆動電圧クランピング部

とを含む請求項2に記載の出力駆動回路。

【請求項5】

前記第1のトランジスタ駆動電圧クランピング部は、前記高電圧電源端と前記第1のトランジスタのゲートとの間に配置され、互いに並列接続された抵抗と第1のツェナーダイオードとを含む請求項3または4に記載の出力駆動回路。

【請求項6】

前記第1のトランジスタ駆動電圧クランピング部は、前記高電圧電源端と前記第1のトランジスタのゲートとの間に配置された第1のツェナーダイオードと、前記第1のツェナーダイオードに並列接続されたカレントミラーと、前記第1のトランジスタのゲートに対向する前記カレントミラーの下端に接続され、前記第1のスイッチと相補的に動作する第3のスイッチとを含む請求項3または4に記載の出力駆動回路。

【請求項7】

前記カレントミラーは、前記高電圧電源端にソース電極が接続された第3及び第4のトランジスタのミラー構造で構成され、

前記第3及び第4のトランジスタは、PチャネルMOSFETまたはPチャネルLDMOSFETであり、

前記第4のトランジスタのドレイン電極は、前記第1のトランジスタのゲートに接続され、前記第3のトランジスタのドレイン電極は、前記第3のスイッチ及び前記第3及び第4のトランジスタのゲート電極に接続され、

前記第3のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETから成る請求項6に記載の出力駆動回路。

【請求項8】

前記出力駆動電圧クランピング部は、前記高電圧電源端と前記出力トランジスタのゲートとの間に配置された第2のツェナーダイオードを含む請求項1〜4のうちのいずれか一つに記載の出力駆動回路。

【請求項9】

前記第1のトランジスタのゲート−ソースのキャパシタンスが、前記出力トランジスタのゲート−ソースのキャパシタンスより小さい請求項1〜4のうちのいずれか一つに記載の出力駆動回路。

【請求項10】

前記第1及び第2のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETから成る請求項1〜4のうちのいずれか一つに記載の出力駆動回路。

【請求項11】

前記出力トランジスタは、前記第2の駆動回路部の駆動によって駆動され、前記高電圧電源を出力するPチャネルMOSFETまたはPチャネルLDMOSFETである請求項1〜4のうちのいずれか一つに記載の出力駆動回路。

【請求項12】

高電圧電源端にソース電極が接続され、駆動によってドレイン電極を通じて高電圧電源を出力するPチャネル出力トランジスタと、

前記Pチャネル出力トランジスタと相補的に動作し、駆動によって前記Pチャネル出力トランジスタのドレイン電極と接続されたドレイン電極から、ソース電極が接続された低電圧電源端へと電源を出力するNチャネル出力トランジスタと、

相補的スイッチング動作によって、前記Pチャネル及びNチャネル出力トランジスタの各々を駆動する請求項1〜4のうちのいずれか一つによる出力駆動回路とを含むトランジスタ出力回路。

【請求項13】

前記出力駆動回路の出力駆動電圧クランピング部は、前記高電圧電源端と前記Pチャネル出力トランジスタのゲートとの間に配置された第2のツェナーダイオードを含む請求項12に記載のトランジスタ出力回路。

【請求項14】

前記出力駆動回路の第1及び第2のスイッチは、NチャネルMOSFETまたはNチャネルLDMOSFETから成る請求項12に記載のトランジスタ出力回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−42474(P2013−42474A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2012−84462(P2012−84462)

【出願日】平成24年4月3日(2012.4.3)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成24年4月3日(2012.4.3)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

[ Back to top ]