分周回路、分周装置及び電子機器

【課題】位相同期した出力信号及びその反転信号を生成・出力できる分周回路の実現。

【解決手段】分周回路1は、クロック信号生成部10と、分周信号生成部20と、出力信号生成部30とから構成される。出力信号生成部30からは、共通のクロック信号CLOCKによって動作/不動作が切り替えられるクロックドインバーターX15,X19によって、位相がほぼ完全に一致した出力信号OUT,XOUTが生成・出力される。

【解決手段】分周回路1は、クロック信号生成部10と、分周信号生成部20と、出力信号生成部30とから構成される。出力信号生成部30からは、共通のクロック信号CLOCKによって動作/不動作が切り替えられるクロックドインバーターX15,X19によって、位相がほぼ完全に一致した出力信号OUT,XOUTが生成・出力される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力信号を分周して出力する分周回路等に関する。

【背景技術】

【0002】

GPS受信装置等の電子機器では、内部発振器による発振信号を分周して所望の周波数の信号を得るための分周回路が用いられる(例えば、特許文献1参照)。この分周回路としては、一般的には、回路構成が容易なことから、入力信号を1/2分周する複数の分周回路を縦続接続することで構成される。

【0003】

図4は、従来の分周回路1Bの回路構成の一例である。図4に示すように、従来の分周回路1Bは、入力信号CLを1/2分周した出力信号OUT、及び、その反転信号XOUTを出力する回路であり、(1)クロック信号生成部10と、(2)分周信号生成部20と、(3)出力信号生成部30Bとから構成される。

【0004】

クロック信号生成部10は、入力信号CLをもとに、この入力信号CLと周波数が同一であり、互いに逆相のクロック信号CLOCK,XCLOCKを生成する。分周信号生成部20は、クロック信号CLOCK,XCLOCKをもとに、周波数が入力信号CLの1/2の反転分周信号XQを生成する。出力信号生成部30Bは、反転分周信号XQをもとに、周波数が入力信号CLの1/2であって、互いに逆相の出力信号OUT,XOUTを生成する。

【0005】

また、図5は、従来の分周回路1Bにおける信号波形である。図5では、横軸を時刻t、縦軸を信号レベルとして、上から順に、入力信号CL、クロック信号CLOCK,XCLCK、クロックドインバーターX6の出力信号XM、インバーターX7の出力信号M、反転分周信号XQ、インバーターX9の出力信号Q、出力信号OUT,XOUTそれぞれの信号波形を示している。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−187556号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、図4に示した従来の分周回路1Bでは、入力信号CLを1/2分周した反転分周信号XQを、インバーターX12が反転増幅した信号を出力信号OUTとしている。また、反転分周信号XQを、縦続接続されたインバーターX13,X14それぞれが反転増幅した信号を反転出力信号XOUTとして出力している。つまり、反転分周信号XQに対して、1つのインバーターX12を介した信号を出力信号OUTとし、2つのインバーターX13,X14を介した信号を反転出力信号XOUTとしている。このため、図5に示すように、出力信号OUT,XOUTの位相がずれる。

【0008】

分周回路を複数段接続して使用する場合、回路全体の素子数を減らすため、出力信号OUT,XOUTを、それぞれ、次段のクロック信号CLOCK、XCLOCKとして入力する。このとき、出力信号OUT,XOUTの位相がずれていると、次段の分周回路におけるクロック信号CLOCK,XCLOCKが同時に「H」レベルとなる期間が生じ、誤動作の要因となり得る。

【0009】

本発明は、上記事情に鑑みてなされたものであり、位相同期した出力信号及びその反転信号を生成・出力できる分周回路を実現することを目的としている。

【課題を解決するための手段】

【0010】

上記課題を解決するための第1の形態は、入力信号をもとに生成された、前記入力信号と同一周波数であって互いに同期し且つ反転した位相を有するクロック信号、及び、反転クロック信号をもとに、前記入力信号を分周した分周信号を生成する分周部と、前記分周信号をもとに、前記クロック信号及び前記反転クロック信号を用いて、前記分周信号と同一周波数であって互いに同期し且つ反転した位相を有する出力信号、及び、反転出力信号を生成する出力信号生成部とを備えた分周回路である。

【0011】

この第1の形態によれば、分周信号と同一周波数であって、互いに同期し且つ反転した位相を有する出力信号及びその反転出力信号を生成・出力する分周回路が実現される。

【0012】

第2の形態として、第1の形態の分周回路であって、前記出力信号生成部は、前記出力信号の位相と前記反転出力信号の位相とを同期させるために、前記クロック信号に応じて動作するクロックドインバーター部を有する分周回路を構成しても良い。

【0013】

この第2の形態によれば、クロック信号に応じて動作するクロックドインバーター部によって、位相同期された出力信号及び反転出力信号が生成される。

【0014】

この場合、第3の形態として、前記出力信号生成部は、前記クロックドインバーター部の出力レベルを保持するレベル保持部を有する分周回路を構成しても良い。

【0015】

この第3の形態によれば、クロックドインバーター部が動作してないときにも、クロックドインバーター部の直前の出力レベルが保持される。

【0016】

更にこの場合、第4の形態として、前記レベル保持部は、前記レベル保持部が有するトランジスターのゲート容量、或いは、配線容量で前記出力レベルを保持するように構成しても良い。

【0017】

また、第5の形態として、N段(Nは2以上の整数)の分周器が縦続接続されて構成された分周装置であって、第1段の分周器は、入力信号をもとに、前記クロック信号及び前記反転クロック信号を生成するクロック信号生成部と、第1〜第4の何れかの形態の分周回路とを備え、第n段(n=2,3,・・・,N)の分周器は、第(n−1)段の分周器から出力される出力信号が前記クロック信号として入力され、前記反転出力信号が前記反転クロック信号として入力される第1〜第4の何れかの形態の分周回路を備えて構成された分周装置を構成しても良い。

【0018】

この第5の形態によれば、複数の分周器が縦続接続されて構成された分周装置において、分周器から出力される出力信号及び反転出力信号を、それぞれ、次段の分周器のクロック信号及び反転クロック信号として入力することができる。

【0019】

更に、第6の形態として、第1〜第4の何れかの形態の分周回路、又は、第5の形態の分周装置を備えた電子機器を構成しても良い。

【図面の簡単な説明】

【0020】

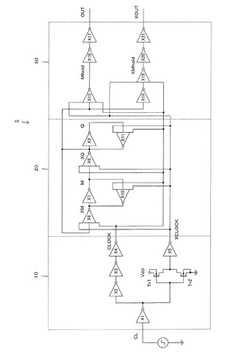

【図1】分周回路の回路構成図。

【図2】分周回路における信号波形図。

【図3】Set/Reset回路を付加した分周回路の回路構成図。

【図4】従来の分周回路の回路構成図。

【図5】従来の分周回路における信号波形図。

【発明を実施するための形態】

【0021】

以下、図面を参照して、本発明の実施形態を説明する。

【0022】

[構成]

図1は、本実施形態における分周回路1の回路構成図である。なお、図1において、図4に示した従来の分周回路1Bと同一の構成要素については同符号を付している。この分周回路1は、入力信号CLの周波数を1/2倍(1/2分周)した出力信号OUT、及び、この出力信号OUTと同一周波数であり且つ位相が逆相の反転信号XOUT(出力信号OUT,XOUT)を生成・出力する。また、分周回路1は、(1)クロック信号生成部10と、(2)分周信号生成部20(分周部)と、(3)出力信号生成部30とから構成される。

【0023】

クロック信号生成部10は、入力信号CLをもとに、入力信号CLと周波数が同一であり、互いに位相同期したクロック信号CLOCK、及び、このクロック信号CLOCKと同一周波数であり且つ位相が逆相の反転信号XCLOCK(クロック信号CLOCK,XCLOCK)を生成する。このクロック信号生成部10は、インバーターX1,X2,X3,X4,X5と、トランジスターTr1,Tr2とを有する。

【0024】

分周信号生成部20は、クロック信号生成部10にて生成されたクロック信号CLOCK,XCLOCKをもとに、入力信号CLを1/2分周した反転分周信号XQを生成する。この分周信号生成部20は、クロックドインバーターX6,X8,X10,X11と、インバーターX7,X9とを有する。

【0025】

クロックドインバーターX6は、制御信号としてクロック信号CLOCKが入力され、反転分周信号XQを反転増幅して信号XMとして出力する。この信号XMは、インバーターX7により反転増幅されて信号Mとされる。クロックドインバーターX10は、制御信号として反転クロック信号XCLOCKが入力され、信号Mを反転増幅して信号XMとして出力する。

【0026】

また、クロックドインバーターX10は、信号XMのレベル保持回路として機能する。すなわち、クロックドインバーターX6の動作時には、クロックドインバーターX10は不動作であり、クロックドインバーターX6によって、反転分周信号XQの反転信号が信号XMとなる。一方、クロックドインバーターX6の不動作時には、クロックドインバーターX10が動作し、このクロックドインバーターX10によって、信号Mの反転信号が信号XMとなる。つまり、クロックドインバーターX6の不動作時には、クロックドインバーターX10によって、クロックドインバーターX6が不動作となる直前の信号XMのレベルが保持される。

【0027】

クロックドインバーターX8は、制御信号としてクロック信号XCLOCKが入力され、信号Mを反転増幅して反転分周信号XQとして出力する。この反転分周信号XQは、インバーターX9により反転増幅されて分周信号Qとされる。クロックドインバーターX11は、制御信号として信号CLOCKが入力され、分周信号Qを反転増幅して反転分周信号XQとして出力する。

【0028】

また、クロックドインバーターX11は、反転分周信号XQのレベル保持回路として機能する。すなわち、クロックドインバーターX8の動作時には、クロックドインバーターX11は不動作であり、クロックドインバーターX8によって、信号Mの反転信号が反転分周信号XQとなる。一方、クロックドインバーターX8の不動作時には、クロックドインバーターX11が動作し、このクロックドインバーターX11によって、分周信号Qの反転信号が反転分周信号XQとなる。つまり、クロックドインバーターX8の不動作時には、クロックドインバーターX11によって、クロックドインバーターX8が不動作となる直前の反転分周信号XQのレベルが保持される。

【0029】

出力信号生成部30は、分周信号生成部20にて生成された反転分周信号XQをもとに、反転分周信号XQと周波数が同一であり、互いに位相同期した出力信号OUT、及び、その反転信号XOUT(出力信号OUT,XOUT)を生成する。この出力信号生成部30は、クロックドインバーターX15,X19(クロックドインバーター部)と、インバーターX16,X17,X18,X20,X21とを有する。

【0030】

クロックドインバーターX15は、制御信号としてクロック信号CLOCKが入力され、反転分周信号XQを反転増幅して信号Mholdとして出力する。インバーターX18は、反転分周信号XQを反転増幅して出力する。クロックドインバーターX19は、制御信号として信号CLOCKが入力され、インバーターX18の出力信号(すなわち、反転分周信号XQの反転信号)を反転増幅して信号XMholdとして出力する。

【0031】

つまり、反転分周信号XQは、クロックドインバーターX15によって反転増幅されて信号Mholdとなるとともに、インバーターX18、及び、クロックドインバーターX19それぞれによって反転増幅されて信号XMholdとなる。従って、信号Mhold,XMholdは、互いに逆相の信号となっている。

【0032】

また、クロックドインバーターX15,X19それぞれには、制御信号として共通の信号CLOCKが入力されている。つまり、クロックドインバーターX15,X19それぞれの動作/不動作の切替タイミングは一致しており、従って、信号Mhold,XMholdそれぞれの変化タイミングは一致する。

【0033】

そして、信号Mholdは、インバーターX16,X17それぞれによって反転増幅されて、出力信号OUTとして出力される。信号XMholdは、インバーターX20,X21それぞれによって反転増幅されて、反転出力信号XOUTとして出力される。

【0034】

また、インバーターX16,X17は、信号Mholdのレベル保持回路(レベル保持部)として機能する。すなわち、クロックドインバーターX15の不動作時に、インバーターX16,X17それぞれを構成するトランジスターのゲート容量や配線容量等によって、クロックドインバーターX15が不動作となる直前の信号Mholdの出力レベルが保持される。

【0035】

また、インバーターX20,X21は、信号XMholdのレベル保持回路(レベル保持部)として機能する。すなわち、クロックドインバーターX19の不動作時に、インバーターX20,X21を構成するトランジスターのゲート容量や配線容量等によって、クロックドインバーターX19が不動作となる直前の信号XMholdの出力レベルが保持される。

【0036】

[動作]

次に、信号波形を参照して、この分周回路1の動作を説明する。図2は、分周回路1における信号波形図である。図2では、横軸を時刻t、縦軸を信号レベルとして、上から順に、入力信号CL、クロック信号CLOCK及び反転クロック信号XCLOCK、信号XM、信号M、反転分周信号XQ、分周信号Q、出力信号OUT,XOUTのそれぞれの信号波形を示している。また、クロック信号CLOCK、及び、出力信号XOUTは実線で示し、反転クロック信号XCLOCK、及び、出力信号OUTは破線で示している。

【0037】

先ず、時刻t0において、クロック信号CLOCKが「H」レベル、反転クロック信号XCLOCKが「L」レベル、反転分周信号XQが「H」レベルである。

【0038】

このとき、クロックドインバーターX6は「動作」し、クロックドインバーターX10は「不動作」である。つまり、クロックドインバーターX6によって、反転分周信号XQの反転信号が信号XMとなり、信号XMは「L」レベルとなる。そして、インバーターX7によって、信号XMの反転信号が信号Mとなり、信号Mは「H」レベルとなる。

【0039】

また、クロックドインバーターX8は「不動作」であり、クロックドインバーターX11は「動作」している。つまり、インバーターX9によって、反転分周信号XQの反転信号が分周信号Qとなり、分周信号Qは「L」レベルとなる。そして、クロックドインバーターX11によって、分周信号Qの反転信号が反転分周信号XQとなり、反転分周信号XQは「H」レベルが保持される。

【0040】

また、クロックドインバーターX15は「動作」しており、このクロックドインバーターX15によって、反転分周信号XQの反転信号が信号Mholdとなる。つまり、出力信号XOUTは「L」レベルとなる。また、クロックドインバーターX19は「動作」しており、このクロックドインバーターX19によって、インバーターX18の出力信号(反転分周信号XQの反転信号)の反転信号が信号XMholdとなる。つまり、反転出力信号XOUTは「H」レベルとなる。

【0041】

次いで、時刻t1において、クロック信号CLOCKが「H」レベルから「L」レベルに変化し、反転クロック信号XCLOCKが「L」レベルから「H」レベルに変化すると、クロックドインバーターX6が「不動作」となるとともに、クロックドインバーターX10が「動作」する。つまり、クロックドインバーターX10によって、信号Mの反転信号が信号XMとなり、信号XMは「L」レベルが保持され、信号Mは「H」レベルが保持される。

【0042】

また、クロックドインバーターX8が「動作」するとともに、クロックドインバーターX11が「不動作」となる。つまり、クロックドインバーターX8によって、信号Mの反転信号が反転分周信号XQとなり、反転分周信号XQが「H」レベルから「L」レベルに変化する。そして、インバーターX9によって、反転分周信号XQの反転信号が分周信号Qとなり、分周信号Qが「L」レベルから「H」にレベルに変化する。このとき、インバーターX9を通過しているため、分周信号Qは、反転信号XQに遅れて変化する。

【0043】

また、クロックドインバーターX15,X19が「不動作」となる。従って、クロックドインバーターX15が「不動作」となる直前の信号Mholdのレベルが、インバーターX16,X17によって保持され、出力信号XOUTは「L」レベルが保持される。また、クロックドインバーターX19が「不動作」となる直前の信号XMholdのレベルが、インバーターX20,X21によって保持され、反転出力信号XOUTは「H」レベルが保持される。

【0044】

続いて、時刻t2において、クロック信号CLOCKが「L」レベルから「H」レベルに変化し、反転クロック信号XCLOCKが「H」レベルから「L」レベルに変化すると、クロックドインバーターX6が「動作」するとともに、クロックドインバーターX10が「不動作」となる。つまり、クロックドインバーターX6によって、反転分周信号XQの反転信号が信号XMとなり、信号XMが「L」レベルから「H」レベルに変化する。そして、インバーターX7によって、信号Mが「H」レベルから「L」レベルに変化する。このとき、インバーターX7を通過しているため、信号Mは、信号XMに遅れて変化する。

【0045】

また、クロックドインバーターX8が「不動作」となり、クロックドインバーターX11が「動作」する。つまり、クロックドインバーターX11によって、分周信号Qの反転信号が反転分周信号XQとなり、クロックドインバーターX8が不動作となる直前の反転分周信号XQのレベルが保持される。すなわち、反転分周信号XQは「L」レベルが保持され、分周信号Qは「H」レベルが保持される。

【0046】

また、クロックドインバーターX15,X19が「動作」する。つまり、クロックドインバーターX15により、反転分周信号XQの反転信号が信号Mholdとなる。従って、信号Mholdは「L」レベルから「H」レベルに変化し、出力信号OUTは「L」レベルから「H」レベルに変化する。また、クロックドインバーターX19により、インバーターX18の出力信号の反転信号が、信号XMholdとなる。従って、信号XMholdは「H」レベルから「L」レベルに変化し、反転出力信号XOUTは「H」レベルから「L」レベルに変化する。

【0047】

ここで、クロックドインバーターX15,X19は、共通のクロック信号CLOCKによって動作/不動作が切り替わる。つまり、クロックドインバーターX15,X19それぞれの出力信号である信号Mhold,XMholdの変化タイミングはほぼ一致し、従って、出力信号OUT,XOUTの変化タイミングもほぼ一致する。

【0048】

以降も同様に、クロック信号CLOCK,XCLOCKのレベル変化に応じて、各信号のレベルが変化する。

【0049】

[作用・効果]

このように、本実施形態の分周回路1によれば、共通のクロック信号CLOCKによって動作/不動作が切り替えられるクロックドインバーターX15,X19によって、位相がほぼ完全に互いに逆位相となる出力信号OUT,XOUTが出力される。

【0050】

[変形例]

なお、本発明の適用可能な実施形態は、上述の実施形態に限定されることなく、本発明の趣旨を逸脱しない範囲で適宜変更可能なのは勿論である。

【0051】

(A)分周回路1を複数段接続

例えば、分周回路1(分周器)を複数段(N段。「N」は2以上の整数)縦続接続して分周装置を構成する場合、(n−1)段目の分周回路1の出力信号OUTを、次段(n段目)の分周回路1のクロック信号CLOCKとして入力するとともに、(n−1)段目の分周回路1の出力信号XOUTを、次段(n段目)の分周回路1の反転クロック信号XCLOCKとして入力することができる。但し、n=2,3,・・・,N、である。つまり、この場合、1段目の分周回路1は、クロック信号生成部10(クロック信号生成部)を含むが、2段目以降(n>2)の分周回路1は、クロック信号生成部10(クロック信号)は含まなくとも良い。

【0052】

(B)Set/Reset回路を付加

また、分周回路1に、信号M、及び、分周信号Qをセット/リセットする回路を付加しても良い。図3は、セット/リセット回路を付加した分周回路1Aの回路構成図である。この分周回路1Aは、図1に示した分周回路1において、インバーターX7に替えて、ORゲートOR1及びNANDゲートNAND1を設けるとともに、インバーターX9に替えて、ORゲートOR2及びNANDゲートNAND2を設けた構成となっている。なお、図1に示した分周回路1と同一の構成要素については同符号を付し、その説明を省略する。

【0053】

ORゲートOR1には、信号XMと、リセット信号Resetが入力される。NANDゲートNAND1には、ORゲートOR1の出力信号と、インバーターX20の出力信号、すなわちセット信号Setの反転信号とが入力される。このNANDゲートNAND1の出力信号が信号Mとなる。ORゲートOR2には、反転分周信号XQと、リセット信号Resetが入力される。NANDゲートNAND2には、ORゲートOR2の出力信号と、インバーターX20の出力信号、すなわちセット信号Setの反転信号とが入力される。このNANDゲートNAND2の出力信号が分周信号Qとなる。

【0054】

セット信号Set、及び、リセット信号Resetがともに「L」レベルの場合、ORゲートOR1の出力信号は、信号XMに等しい。そして、NANDゲートNAND1の出力信号は、ORゲートOR1の出力信号の反転信号となる。つまり、ORゲートOR1及びNANDゲートNAND1は、インバーターX7と同様の動作となる。また、ORゲートOR2の出力信号は、分周信号Qに等しい。そして、NANDゲートNAND2の出力信号は、ORゲートOR2の出力信号の反転信号となる。つまり、ORゲートOR2及びNANDゲートNAND2は、インバーターX9と同様の動作となる。

【0055】

そして、リセット信号Resetが「L」レベルのまま、セット信号Setが「H」レベルとなると、NANDゲートNAND1,NAND2の出力信号は、それぞれ、ORゲートOR1,OR2の出力信号に関わらず「H」レベルとなる。つまり、信号M、及び、分周信号Qは、それぞれ、「H」レベルにセットされる。

【0056】

また、セット信号Setが「L」レベルのまま、リセット信号Resetが「H」レベルとなると、ORゲートOR1,OR2の出力信号が、それぞれ、信号XM、及び、反転分周信号XQに関わらず「H」レベルとなる。そして、NANDゲートNAND1,NAND2の出力信号は、それぞれ、「H」レベルとなる。つまり、信号M、及び、分周信号Qは、それぞれ、「L」レベルにリセットされる。

【0057】

(C)レベル保持部

また、上述の実施形態における分周回路1では、信号Mhold,XMholdのレベルを保持するレベル保持部として、インバーターX16,X17,X20,X21が有するトランジスターのゲート容量等によって実現したが、入力信号CLが低周波数の信号の場合には、これに替えてコンデンサーによって実現しても良い。

【符号の説明】

【0058】

1(1A,1B) 分周回路、10 クロック信号生成部、

20(20A) 分周信号生成部、30(30B) 出力信号生成部

【技術分野】

【0001】

本発明は、入力信号を分周して出力する分周回路等に関する。

【背景技術】

【0002】

GPS受信装置等の電子機器では、内部発振器による発振信号を分周して所望の周波数の信号を得るための分周回路が用いられる(例えば、特許文献1参照)。この分周回路としては、一般的には、回路構成が容易なことから、入力信号を1/2分周する複数の分周回路を縦続接続することで構成される。

【0003】

図4は、従来の分周回路1Bの回路構成の一例である。図4に示すように、従来の分周回路1Bは、入力信号CLを1/2分周した出力信号OUT、及び、その反転信号XOUTを出力する回路であり、(1)クロック信号生成部10と、(2)分周信号生成部20と、(3)出力信号生成部30Bとから構成される。

【0004】

クロック信号生成部10は、入力信号CLをもとに、この入力信号CLと周波数が同一であり、互いに逆相のクロック信号CLOCK,XCLOCKを生成する。分周信号生成部20は、クロック信号CLOCK,XCLOCKをもとに、周波数が入力信号CLの1/2の反転分周信号XQを生成する。出力信号生成部30Bは、反転分周信号XQをもとに、周波数が入力信号CLの1/2であって、互いに逆相の出力信号OUT,XOUTを生成する。

【0005】

また、図5は、従来の分周回路1Bにおける信号波形である。図5では、横軸を時刻t、縦軸を信号レベルとして、上から順に、入力信号CL、クロック信号CLOCK,XCLCK、クロックドインバーターX6の出力信号XM、インバーターX7の出力信号M、反転分周信号XQ、インバーターX9の出力信号Q、出力信号OUT,XOUTそれぞれの信号波形を示している。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−187556号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、図4に示した従来の分周回路1Bでは、入力信号CLを1/2分周した反転分周信号XQを、インバーターX12が反転増幅した信号を出力信号OUTとしている。また、反転分周信号XQを、縦続接続されたインバーターX13,X14それぞれが反転増幅した信号を反転出力信号XOUTとして出力している。つまり、反転分周信号XQに対して、1つのインバーターX12を介した信号を出力信号OUTとし、2つのインバーターX13,X14を介した信号を反転出力信号XOUTとしている。このため、図5に示すように、出力信号OUT,XOUTの位相がずれる。

【0008】

分周回路を複数段接続して使用する場合、回路全体の素子数を減らすため、出力信号OUT,XOUTを、それぞれ、次段のクロック信号CLOCK、XCLOCKとして入力する。このとき、出力信号OUT,XOUTの位相がずれていると、次段の分周回路におけるクロック信号CLOCK,XCLOCKが同時に「H」レベルとなる期間が生じ、誤動作の要因となり得る。

【0009】

本発明は、上記事情に鑑みてなされたものであり、位相同期した出力信号及びその反転信号を生成・出力できる分周回路を実現することを目的としている。

【課題を解決するための手段】

【0010】

上記課題を解決するための第1の形態は、入力信号をもとに生成された、前記入力信号と同一周波数であって互いに同期し且つ反転した位相を有するクロック信号、及び、反転クロック信号をもとに、前記入力信号を分周した分周信号を生成する分周部と、前記分周信号をもとに、前記クロック信号及び前記反転クロック信号を用いて、前記分周信号と同一周波数であって互いに同期し且つ反転した位相を有する出力信号、及び、反転出力信号を生成する出力信号生成部とを備えた分周回路である。

【0011】

この第1の形態によれば、分周信号と同一周波数であって、互いに同期し且つ反転した位相を有する出力信号及びその反転出力信号を生成・出力する分周回路が実現される。

【0012】

第2の形態として、第1の形態の分周回路であって、前記出力信号生成部は、前記出力信号の位相と前記反転出力信号の位相とを同期させるために、前記クロック信号に応じて動作するクロックドインバーター部を有する分周回路を構成しても良い。

【0013】

この第2の形態によれば、クロック信号に応じて動作するクロックドインバーター部によって、位相同期された出力信号及び反転出力信号が生成される。

【0014】

この場合、第3の形態として、前記出力信号生成部は、前記クロックドインバーター部の出力レベルを保持するレベル保持部を有する分周回路を構成しても良い。

【0015】

この第3の形態によれば、クロックドインバーター部が動作してないときにも、クロックドインバーター部の直前の出力レベルが保持される。

【0016】

更にこの場合、第4の形態として、前記レベル保持部は、前記レベル保持部が有するトランジスターのゲート容量、或いは、配線容量で前記出力レベルを保持するように構成しても良い。

【0017】

また、第5の形態として、N段(Nは2以上の整数)の分周器が縦続接続されて構成された分周装置であって、第1段の分周器は、入力信号をもとに、前記クロック信号及び前記反転クロック信号を生成するクロック信号生成部と、第1〜第4の何れかの形態の分周回路とを備え、第n段(n=2,3,・・・,N)の分周器は、第(n−1)段の分周器から出力される出力信号が前記クロック信号として入力され、前記反転出力信号が前記反転クロック信号として入力される第1〜第4の何れかの形態の分周回路を備えて構成された分周装置を構成しても良い。

【0018】

この第5の形態によれば、複数の分周器が縦続接続されて構成された分周装置において、分周器から出力される出力信号及び反転出力信号を、それぞれ、次段の分周器のクロック信号及び反転クロック信号として入力することができる。

【0019】

更に、第6の形態として、第1〜第4の何れかの形態の分周回路、又は、第5の形態の分周装置を備えた電子機器を構成しても良い。

【図面の簡単な説明】

【0020】

【図1】分周回路の回路構成図。

【図2】分周回路における信号波形図。

【図3】Set/Reset回路を付加した分周回路の回路構成図。

【図4】従来の分周回路の回路構成図。

【図5】従来の分周回路における信号波形図。

【発明を実施するための形態】

【0021】

以下、図面を参照して、本発明の実施形態を説明する。

【0022】

[構成]

図1は、本実施形態における分周回路1の回路構成図である。なお、図1において、図4に示した従来の分周回路1Bと同一の構成要素については同符号を付している。この分周回路1は、入力信号CLの周波数を1/2倍(1/2分周)した出力信号OUT、及び、この出力信号OUTと同一周波数であり且つ位相が逆相の反転信号XOUT(出力信号OUT,XOUT)を生成・出力する。また、分周回路1は、(1)クロック信号生成部10と、(2)分周信号生成部20(分周部)と、(3)出力信号生成部30とから構成される。

【0023】

クロック信号生成部10は、入力信号CLをもとに、入力信号CLと周波数が同一であり、互いに位相同期したクロック信号CLOCK、及び、このクロック信号CLOCKと同一周波数であり且つ位相が逆相の反転信号XCLOCK(クロック信号CLOCK,XCLOCK)を生成する。このクロック信号生成部10は、インバーターX1,X2,X3,X4,X5と、トランジスターTr1,Tr2とを有する。

【0024】

分周信号生成部20は、クロック信号生成部10にて生成されたクロック信号CLOCK,XCLOCKをもとに、入力信号CLを1/2分周した反転分周信号XQを生成する。この分周信号生成部20は、クロックドインバーターX6,X8,X10,X11と、インバーターX7,X9とを有する。

【0025】

クロックドインバーターX6は、制御信号としてクロック信号CLOCKが入力され、反転分周信号XQを反転増幅して信号XMとして出力する。この信号XMは、インバーターX7により反転増幅されて信号Mとされる。クロックドインバーターX10は、制御信号として反転クロック信号XCLOCKが入力され、信号Mを反転増幅して信号XMとして出力する。

【0026】

また、クロックドインバーターX10は、信号XMのレベル保持回路として機能する。すなわち、クロックドインバーターX6の動作時には、クロックドインバーターX10は不動作であり、クロックドインバーターX6によって、反転分周信号XQの反転信号が信号XMとなる。一方、クロックドインバーターX6の不動作時には、クロックドインバーターX10が動作し、このクロックドインバーターX10によって、信号Mの反転信号が信号XMとなる。つまり、クロックドインバーターX6の不動作時には、クロックドインバーターX10によって、クロックドインバーターX6が不動作となる直前の信号XMのレベルが保持される。

【0027】

クロックドインバーターX8は、制御信号としてクロック信号XCLOCKが入力され、信号Mを反転増幅して反転分周信号XQとして出力する。この反転分周信号XQは、インバーターX9により反転増幅されて分周信号Qとされる。クロックドインバーターX11は、制御信号として信号CLOCKが入力され、分周信号Qを反転増幅して反転分周信号XQとして出力する。

【0028】

また、クロックドインバーターX11は、反転分周信号XQのレベル保持回路として機能する。すなわち、クロックドインバーターX8の動作時には、クロックドインバーターX11は不動作であり、クロックドインバーターX8によって、信号Mの反転信号が反転分周信号XQとなる。一方、クロックドインバーターX8の不動作時には、クロックドインバーターX11が動作し、このクロックドインバーターX11によって、分周信号Qの反転信号が反転分周信号XQとなる。つまり、クロックドインバーターX8の不動作時には、クロックドインバーターX11によって、クロックドインバーターX8が不動作となる直前の反転分周信号XQのレベルが保持される。

【0029】

出力信号生成部30は、分周信号生成部20にて生成された反転分周信号XQをもとに、反転分周信号XQと周波数が同一であり、互いに位相同期した出力信号OUT、及び、その反転信号XOUT(出力信号OUT,XOUT)を生成する。この出力信号生成部30は、クロックドインバーターX15,X19(クロックドインバーター部)と、インバーターX16,X17,X18,X20,X21とを有する。

【0030】

クロックドインバーターX15は、制御信号としてクロック信号CLOCKが入力され、反転分周信号XQを反転増幅して信号Mholdとして出力する。インバーターX18は、反転分周信号XQを反転増幅して出力する。クロックドインバーターX19は、制御信号として信号CLOCKが入力され、インバーターX18の出力信号(すなわち、反転分周信号XQの反転信号)を反転増幅して信号XMholdとして出力する。

【0031】

つまり、反転分周信号XQは、クロックドインバーターX15によって反転増幅されて信号Mholdとなるとともに、インバーターX18、及び、クロックドインバーターX19それぞれによって反転増幅されて信号XMholdとなる。従って、信号Mhold,XMholdは、互いに逆相の信号となっている。

【0032】

また、クロックドインバーターX15,X19それぞれには、制御信号として共通の信号CLOCKが入力されている。つまり、クロックドインバーターX15,X19それぞれの動作/不動作の切替タイミングは一致しており、従って、信号Mhold,XMholdそれぞれの変化タイミングは一致する。

【0033】

そして、信号Mholdは、インバーターX16,X17それぞれによって反転増幅されて、出力信号OUTとして出力される。信号XMholdは、インバーターX20,X21それぞれによって反転増幅されて、反転出力信号XOUTとして出力される。

【0034】

また、インバーターX16,X17は、信号Mholdのレベル保持回路(レベル保持部)として機能する。すなわち、クロックドインバーターX15の不動作時に、インバーターX16,X17それぞれを構成するトランジスターのゲート容量や配線容量等によって、クロックドインバーターX15が不動作となる直前の信号Mholdの出力レベルが保持される。

【0035】

また、インバーターX20,X21は、信号XMholdのレベル保持回路(レベル保持部)として機能する。すなわち、クロックドインバーターX19の不動作時に、インバーターX20,X21を構成するトランジスターのゲート容量や配線容量等によって、クロックドインバーターX19が不動作となる直前の信号XMholdの出力レベルが保持される。

【0036】

[動作]

次に、信号波形を参照して、この分周回路1の動作を説明する。図2は、分周回路1における信号波形図である。図2では、横軸を時刻t、縦軸を信号レベルとして、上から順に、入力信号CL、クロック信号CLOCK及び反転クロック信号XCLOCK、信号XM、信号M、反転分周信号XQ、分周信号Q、出力信号OUT,XOUTのそれぞれの信号波形を示している。また、クロック信号CLOCK、及び、出力信号XOUTは実線で示し、反転クロック信号XCLOCK、及び、出力信号OUTは破線で示している。

【0037】

先ず、時刻t0において、クロック信号CLOCKが「H」レベル、反転クロック信号XCLOCKが「L」レベル、反転分周信号XQが「H」レベルである。

【0038】

このとき、クロックドインバーターX6は「動作」し、クロックドインバーターX10は「不動作」である。つまり、クロックドインバーターX6によって、反転分周信号XQの反転信号が信号XMとなり、信号XMは「L」レベルとなる。そして、インバーターX7によって、信号XMの反転信号が信号Mとなり、信号Mは「H」レベルとなる。

【0039】

また、クロックドインバーターX8は「不動作」であり、クロックドインバーターX11は「動作」している。つまり、インバーターX9によって、反転分周信号XQの反転信号が分周信号Qとなり、分周信号Qは「L」レベルとなる。そして、クロックドインバーターX11によって、分周信号Qの反転信号が反転分周信号XQとなり、反転分周信号XQは「H」レベルが保持される。

【0040】

また、クロックドインバーターX15は「動作」しており、このクロックドインバーターX15によって、反転分周信号XQの反転信号が信号Mholdとなる。つまり、出力信号XOUTは「L」レベルとなる。また、クロックドインバーターX19は「動作」しており、このクロックドインバーターX19によって、インバーターX18の出力信号(反転分周信号XQの反転信号)の反転信号が信号XMholdとなる。つまり、反転出力信号XOUTは「H」レベルとなる。

【0041】

次いで、時刻t1において、クロック信号CLOCKが「H」レベルから「L」レベルに変化し、反転クロック信号XCLOCKが「L」レベルから「H」レベルに変化すると、クロックドインバーターX6が「不動作」となるとともに、クロックドインバーターX10が「動作」する。つまり、クロックドインバーターX10によって、信号Mの反転信号が信号XMとなり、信号XMは「L」レベルが保持され、信号Mは「H」レベルが保持される。

【0042】

また、クロックドインバーターX8が「動作」するとともに、クロックドインバーターX11が「不動作」となる。つまり、クロックドインバーターX8によって、信号Mの反転信号が反転分周信号XQとなり、反転分周信号XQが「H」レベルから「L」レベルに変化する。そして、インバーターX9によって、反転分周信号XQの反転信号が分周信号Qとなり、分周信号Qが「L」レベルから「H」にレベルに変化する。このとき、インバーターX9を通過しているため、分周信号Qは、反転信号XQに遅れて変化する。

【0043】

また、クロックドインバーターX15,X19が「不動作」となる。従って、クロックドインバーターX15が「不動作」となる直前の信号Mholdのレベルが、インバーターX16,X17によって保持され、出力信号XOUTは「L」レベルが保持される。また、クロックドインバーターX19が「不動作」となる直前の信号XMholdのレベルが、インバーターX20,X21によって保持され、反転出力信号XOUTは「H」レベルが保持される。

【0044】

続いて、時刻t2において、クロック信号CLOCKが「L」レベルから「H」レベルに変化し、反転クロック信号XCLOCKが「H」レベルから「L」レベルに変化すると、クロックドインバーターX6が「動作」するとともに、クロックドインバーターX10が「不動作」となる。つまり、クロックドインバーターX6によって、反転分周信号XQの反転信号が信号XMとなり、信号XMが「L」レベルから「H」レベルに変化する。そして、インバーターX7によって、信号Mが「H」レベルから「L」レベルに変化する。このとき、インバーターX7を通過しているため、信号Mは、信号XMに遅れて変化する。

【0045】

また、クロックドインバーターX8が「不動作」となり、クロックドインバーターX11が「動作」する。つまり、クロックドインバーターX11によって、分周信号Qの反転信号が反転分周信号XQとなり、クロックドインバーターX8が不動作となる直前の反転分周信号XQのレベルが保持される。すなわち、反転分周信号XQは「L」レベルが保持され、分周信号Qは「H」レベルが保持される。

【0046】

また、クロックドインバーターX15,X19が「動作」する。つまり、クロックドインバーターX15により、反転分周信号XQの反転信号が信号Mholdとなる。従って、信号Mholdは「L」レベルから「H」レベルに変化し、出力信号OUTは「L」レベルから「H」レベルに変化する。また、クロックドインバーターX19により、インバーターX18の出力信号の反転信号が、信号XMholdとなる。従って、信号XMholdは「H」レベルから「L」レベルに変化し、反転出力信号XOUTは「H」レベルから「L」レベルに変化する。

【0047】

ここで、クロックドインバーターX15,X19は、共通のクロック信号CLOCKによって動作/不動作が切り替わる。つまり、クロックドインバーターX15,X19それぞれの出力信号である信号Mhold,XMholdの変化タイミングはほぼ一致し、従って、出力信号OUT,XOUTの変化タイミングもほぼ一致する。

【0048】

以降も同様に、クロック信号CLOCK,XCLOCKのレベル変化に応じて、各信号のレベルが変化する。

【0049】

[作用・効果]

このように、本実施形態の分周回路1によれば、共通のクロック信号CLOCKによって動作/不動作が切り替えられるクロックドインバーターX15,X19によって、位相がほぼ完全に互いに逆位相となる出力信号OUT,XOUTが出力される。

【0050】

[変形例]

なお、本発明の適用可能な実施形態は、上述の実施形態に限定されることなく、本発明の趣旨を逸脱しない範囲で適宜変更可能なのは勿論である。

【0051】

(A)分周回路1を複数段接続

例えば、分周回路1(分周器)を複数段(N段。「N」は2以上の整数)縦続接続して分周装置を構成する場合、(n−1)段目の分周回路1の出力信号OUTを、次段(n段目)の分周回路1のクロック信号CLOCKとして入力するとともに、(n−1)段目の分周回路1の出力信号XOUTを、次段(n段目)の分周回路1の反転クロック信号XCLOCKとして入力することができる。但し、n=2,3,・・・,N、である。つまり、この場合、1段目の分周回路1は、クロック信号生成部10(クロック信号生成部)を含むが、2段目以降(n>2)の分周回路1は、クロック信号生成部10(クロック信号)は含まなくとも良い。

【0052】

(B)Set/Reset回路を付加

また、分周回路1に、信号M、及び、分周信号Qをセット/リセットする回路を付加しても良い。図3は、セット/リセット回路を付加した分周回路1Aの回路構成図である。この分周回路1Aは、図1に示した分周回路1において、インバーターX7に替えて、ORゲートOR1及びNANDゲートNAND1を設けるとともに、インバーターX9に替えて、ORゲートOR2及びNANDゲートNAND2を設けた構成となっている。なお、図1に示した分周回路1と同一の構成要素については同符号を付し、その説明を省略する。

【0053】

ORゲートOR1には、信号XMと、リセット信号Resetが入力される。NANDゲートNAND1には、ORゲートOR1の出力信号と、インバーターX20の出力信号、すなわちセット信号Setの反転信号とが入力される。このNANDゲートNAND1の出力信号が信号Mとなる。ORゲートOR2には、反転分周信号XQと、リセット信号Resetが入力される。NANDゲートNAND2には、ORゲートOR2の出力信号と、インバーターX20の出力信号、すなわちセット信号Setの反転信号とが入力される。このNANDゲートNAND2の出力信号が分周信号Qとなる。

【0054】

セット信号Set、及び、リセット信号Resetがともに「L」レベルの場合、ORゲートOR1の出力信号は、信号XMに等しい。そして、NANDゲートNAND1の出力信号は、ORゲートOR1の出力信号の反転信号となる。つまり、ORゲートOR1及びNANDゲートNAND1は、インバーターX7と同様の動作となる。また、ORゲートOR2の出力信号は、分周信号Qに等しい。そして、NANDゲートNAND2の出力信号は、ORゲートOR2の出力信号の反転信号となる。つまり、ORゲートOR2及びNANDゲートNAND2は、インバーターX9と同様の動作となる。

【0055】

そして、リセット信号Resetが「L」レベルのまま、セット信号Setが「H」レベルとなると、NANDゲートNAND1,NAND2の出力信号は、それぞれ、ORゲートOR1,OR2の出力信号に関わらず「H」レベルとなる。つまり、信号M、及び、分周信号Qは、それぞれ、「H」レベルにセットされる。

【0056】

また、セット信号Setが「L」レベルのまま、リセット信号Resetが「H」レベルとなると、ORゲートOR1,OR2の出力信号が、それぞれ、信号XM、及び、反転分周信号XQに関わらず「H」レベルとなる。そして、NANDゲートNAND1,NAND2の出力信号は、それぞれ、「H」レベルとなる。つまり、信号M、及び、分周信号Qは、それぞれ、「L」レベルにリセットされる。

【0057】

(C)レベル保持部

また、上述の実施形態における分周回路1では、信号Mhold,XMholdのレベルを保持するレベル保持部として、インバーターX16,X17,X20,X21が有するトランジスターのゲート容量等によって実現したが、入力信号CLが低周波数の信号の場合には、これに替えてコンデンサーによって実現しても良い。

【符号の説明】

【0058】

1(1A,1B) 分周回路、10 クロック信号生成部、

20(20A) 分周信号生成部、30(30B) 出力信号生成部

【特許請求の範囲】

【請求項1】

入力信号をもとに生成された、前記入力信号と同一周波数であって互いに同期し且つ反転した位相を有するクロック信号、及び、反転クロック信号をもとに、前記入力信号を分周した分周信号を生成する分周部と、

前記分周信号をもとに、前記クロック信号及び前記反転クロック信号を用いて、前記分周信号と同一周波数であって互いに同期し且つ反転した位相を有する出力信号、及び、反転出力信号を生成する出力信号生成部と、

を備えた分周回路。

【請求項2】

前記出力信号生成部は、

前記出力信号の位相と前記反転出力信号の位相とを同期させるために、前記クロック信号に応じて動作するクロックドインバーター部、

を有する、

請求項1に記載の分周回路。

【請求項3】

前記出力信号生成部は、

前記クロックドインバーター部の出力レベルを保持するレベル保持部、

を有する、

請求項2に記載の分周回路。

【請求項4】

前記レベル保持部は、

前記レベル保持部が有するトランジスターのゲート容量、或いは、配線容量で前記出力レベルを保持する、

請求項3に記載の分周回路。

【請求項5】

N段(Nは2以上の整数)の分周器が縦続接続されて構成された分周装置であって、

第1段の分周器は、

入力信号をもとに、前記クロック信号及び前記反転クロック信号を生成するクロック信号生成部と、

請求項1〜4の何れか一項に記載の分周回路と、

を備え、

第n段(n=2,3,・・・,N)の分周器は、

第(n−1)段の分周器から出力される出力信号が前記クロック信号として入力され、前記反転出力信号が前記反転クロック信号として入力される請求項1〜4の何れか一項に記載の分周回路、

を備えて構成された分周装置。

【請求項6】

請求項1〜4の何れか一項に記載の分周回路、又は、請求項5に記載の分周装置を備えた電子機器。

【請求項1】

入力信号をもとに生成された、前記入力信号と同一周波数であって互いに同期し且つ反転した位相を有するクロック信号、及び、反転クロック信号をもとに、前記入力信号を分周した分周信号を生成する分周部と、

前記分周信号をもとに、前記クロック信号及び前記反転クロック信号を用いて、前記分周信号と同一周波数であって互いに同期し且つ反転した位相を有する出力信号、及び、反転出力信号を生成する出力信号生成部と、

を備えた分周回路。

【請求項2】

前記出力信号生成部は、

前記出力信号の位相と前記反転出力信号の位相とを同期させるために、前記クロック信号に応じて動作するクロックドインバーター部、

を有する、

請求項1に記載の分周回路。

【請求項3】

前記出力信号生成部は、

前記クロックドインバーター部の出力レベルを保持するレベル保持部、

を有する、

請求項2に記載の分周回路。

【請求項4】

前記レベル保持部は、

前記レベル保持部が有するトランジスターのゲート容量、或いは、配線容量で前記出力レベルを保持する、

請求項3に記載の分周回路。

【請求項5】

N段(Nは2以上の整数)の分周器が縦続接続されて構成された分周装置であって、

第1段の分周器は、

入力信号をもとに、前記クロック信号及び前記反転クロック信号を生成するクロック信号生成部と、

請求項1〜4の何れか一項に記載の分周回路と、

を備え、

第n段(n=2,3,・・・,N)の分周器は、

第(n−1)段の分周器から出力される出力信号が前記クロック信号として入力され、前記反転出力信号が前記反転クロック信号として入力される請求項1〜4の何れか一項に記載の分周回路、

を備えて構成された分周装置。

【請求項6】

請求項1〜4の何れか一項に記載の分周回路、又は、請求項5に記載の分周装置を備えた電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2011−250057(P2011−250057A)

【公開日】平成23年12月8日(2011.12.8)

【国際特許分類】

【出願番号】特願2010−120178(P2010−120178)

【出願日】平成22年5月26日(2010.5.26)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成23年12月8日(2011.12.8)

【国際特許分類】

【出願日】平成22年5月26日(2010.5.26)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]