分周回路およびPLL回路

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、高周波数において広い範囲での分周が可能な分周器回路およびそれを利用したPLL回路に関し、特に注入同期型発振器を使用した分周回路およびそれを利用したPLL回路に関する。

【背景技術】

【0002】

近年、無線通信に利用される周波数帯域は、一層高周波数になる傾向にあり、それに応じて装置内部に設けられるPLL回路のVCO(電圧制御発振器)が出力するクロックの周波数も高周波数にする必要がある。通常、基準周波数は、VCOが発生するクロック周波数よりはるかに低い周波数であり、クロック周波数を分周して低周波数にする必要があり、分周回路が使用される。VCOが数十GHzのクロックを発生する場合、分周回路を通常のデジタル回路で構成するのは難しく、VCOが出力するクロックをある程度の周波数まで分周するプリスケーラには、アナログ分周回路が使用される。アナログ分周回路は、例えば、電流モードロジック分周回路や注入同期型分周回路(Injection Locked Frequency Divider: ILFD)で実現できる。電流モードロジック分周回路は、広い同期領域を有するが、消費電力が大きいという問題がある。本発明は、注入同期型分周回路に関する。

【0003】

図1は、注入同期型分周回路の概略構成を示す図である。

【0004】

注入同期型分周回路(ILFD)10は、発振回路11と、同期信号生成回路12と、を有する。発振回路11は、自己発振回路であり、同期信号生成回路12から注入される同期信号に応じて発振周波数が変化可能である。同期信号生成回路12は、入力発振信号(クロック)Nf0から、発振回路11を目標とする分周信号の周波数で発振させるための同期信号を生成して、発振回路11に注入する。

【0005】

図2は、注入同期型分周回路のモデルを示す図であり、(A)がN分周するモデルを、(B)が2分周するモデルを示す。

【0006】

図2の(A)に示すように、このモデルでは、基本周波数f0の信号(クロック)は、非線形(Nonlinearity)のトランスコンダクタンス(transconductance)を有するトランジスタを通過し、高次の高調波を発生する。発振回路に何も注入されない時には、これらの高調波は発振回路内のローパスフィルタ(LPF)により減衰され多くが減衰される。しかしながら、同期信号が注入されると、これらの高調波は注入された同期信号と混合され、多くの付加的な高調波が発生する。もしこれらの高調波の1つが発振器の自己発振周波数に近く且つ十分なパワーを有していると、発振器の周波数はこの周波数に引き込まれてその周波数にロック(同期)する。この動作が、(N−1)次の高調波が、N次の高調波の同期信号と混合され、発振器の基本周波数に近い高調波を発生し、それにロックするダイレクト変換である。Nが増加するにしたがって、(N−1)次の高調波が弱くなるので、ロック範囲は狭くなる。さらに、注入同期型分周回路の特定の高調波のレベルは、その発生プロセスが線形でなく、多くの要因に影響されるため、制御できない。そのため、ロック範囲が狭くなり、特定の分周比に必要な注入パワーを制限するという問題がある。

【0007】

以上のように、注入同期型分周回路のロック範囲および必要な注入パワーは分周比に応じて異なるが、一般に2分周の場合が、ロック範囲が広く、注入パワーが小さい。図2の(B)は、2分周の注入同期型分周回路のモデルを示す。

【0008】

注入同期型分周回路は、各種の構成が知られているが、その1つに、複数個の遅延要素をリング状に接続したリングオシレータ(リング状発振回路)を利用する回路がある。リングオシレータは、複数個の遅延要素を、前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続した構成を有する。リングオシレータは、広く知られている回路である。

【0009】

図3は、2段のリングオシレータを利用した注入同期型分周回路の構成例を示す図であり、(A)がブロック図を、(B)が遅延要素を差動型のバッファ回路で実現した具体的な回路例を、それぞれ示す。ここでは、MOSトランジスタを使用した例を示したが、これに限定されるものではない。

【0010】

リングオシレータを利用した注入同期型分周回路では、発振動作を行なう遅延要素の一部に同期信号を印加して高調波を発生することにより、リングオシレータを同期信号に対応した周波数で発振させる。注入同期型分周回路には、発振信号を出力する部分に同期信号を印加するダイレクト方式と、発振動作する差動対に並列に設けた差動対に同期信号を印加するパラレル方式と、差動対の出力ノードと反対側のノードを共通に接続した共通接続ノードに同期信号を印加する方式と、がある。一般に、差動対を形成するトランジスタはテールトランジスタと呼ばれるので、ここでは共通接続ノードに同期信号を印加する方式をテール方式と呼び、共通接続ノードをテールと称するものとする。

【0011】

図3は、テール方式のリングオシレータを利用した注入同期型分周回路を示している。遅延要素DL1およびDL2は、差動型バッファ(インバータ)であり、1段目の遅延要素DL1の正出力out+および負出力out−を、2段目の遅延要素DL2の負入力in−および正入力in+に接続し、2段目の遅延要素DL2の正出力out+および負出力out−を、1段目の遅延要素DL1の正入力in+および負入力in−に接続する。これにより、1段目の入力に対応する2段目の出力が反転されて再び1段目の入力に戻されることになり、リングオシレータは発振する。リングオシレータの発振周波数は、同期信号の注入が無ければ、2個の遅延要素DL1およびDL2の遅延時間により決定される。

【0012】

遅延要素DL1は、差動型バッファであり、差動対を形成する2個のNMOSトランジスタのゲートに入力信号が入力され、2個のNMOSトランジスタのドレインから出力信号が出力される。2個のNMOSトランジスタのソースは、共通ノード、すなわちテールに接続され、共通ノード(テール)は、ソース用トランジスタM1およびM2を介して接地される。ソース用トランジスタM1およびM2のゲートには、抵抗を介してDCバイアス電圧が印加される。

【0013】

図3の注入同期型分周回路では、1段目の遅延要素DL1のソース用トランジスタM1のゲートにはさらに容量が接続され、容量の他方の端子に同期信号RF2+が印加される。一方、2段目の遅延要素DL1のソース用トランジスタM2のゲートにも容量が接続されるが、容量の他方の端子は接地される。同期信号RF2+は、注入同期型分周回路の出力する分周信号の周波数f0の2倍の周波数2f0の信号である。言い換えれば、図3の注入同期型分周回路は、周波数2f0の入力発振信号を、周波数f0の分周信号に分周する2分周回路である。

【先行技術文献】

【非特許文献】

【0014】

【非特許文献1】P. Mayr, C. Weyers, and U. Langmann, “A 90GHz 65nm CMOS Injection-Locked Frequency Divider”, IEEE International Solid-State Circuits Conference, Feb. 2007, pp.198-199

【発明の概要】

【発明が解決しようとする課題】

【0015】

注入同期型分周回路のロックしやすい周波数は、注入同期型分周回路の回路特性により決定され、プロセスのばらつきなどの影響を受ける。上記のように、注入同期型分周回路のロック範囲および必要な注入パワーは分周比に応じて異なり、特に高い分周比でロックして安定して動作するのが難しいという問題があった。これに対して、図2の(B)に示すような2分周の注入同期型分周回路のモデルは、一般に、ロック範囲が広く、注入パワーが小さい。そこで、非特許文献1は、2分周の注入同期型分周回路を2個直列に接続して4分周(×4)を行なうことを記載している。

【0016】

しかし、注入同期型分周回路を2個使用した場合、回路面積が大きくなり、消費電力も増加するという問題がある。もし8分周する場合には、注入同期型分周回路を3個使用することになり、回路面積および消費電力はさらに増加するという問題がある。

【0017】

本発明は、2分周、8分周、さらには8分周可能な注入同期型分周回路を、より簡単な構成で実現することを目的とする。

【課題を解決するための手段】

【0018】

本発明の分周回路は、注入同期型であり、入力発振信号を4分周する場合に、M(Mは偶数)個の遅延要素を含むリングオシレータを利用したテール方式の注入同期型分周回路で、M/2個離れた2つの遅延要素のテールを差動対に接続し、入力発振信号がゲートに印加されるトランジスタを差動対に接続して、差動対に入力発振信号の差動信号、すなわち入力発振信号を2分周した信号を発生させる。入力発振信号を8分周する場合には、遅延要素のテールに接続される差動対の部分を2段階構成、すなわち縦積み構成にする。

【0019】

言い換えれば、本発明の分周回路は、前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続されたM(2以上の整数)個の遅延要素を有する発振回路と、入力発振信号から遅延要素の状態変化を規制する同期信号を生成し、生成した同期信号を前記複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を備え、発振回路から入力発振信号の分周信号を出力する分周回路であって、Mは偶数であり、遅延要素は、制御端子に入力信号が入力される分周トランジスタを有し、分周トランジスタの一方の被制御端子から出力が得られ、分周トランジスタの他方の被制御端子が注入ノードであり、同期信号注入回路は、発振回路のM/2個離れた2つの遅延要素の分周トランジスタの注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対と、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続され、制御端子に入力発振信号が入力可能である信号注入トランジスタと、を有することを特徴とする。

【0020】

図4は、本発明の分周回路のモデル図であり、(A)4分周の場合を、(B)が8分周の場合を示す。図4を参照して、本発明の原理を説明する。

【0021】

本発明の分周回路では、N次の高調波の同期信号は、発振回路の基本周波数f0のN/2次の高調波と混合され、さらにN/4次の高調波と混合されるという具合に、発振回路の基本周波数f0に近い周波数の高調波が発生されるまで繰り返される。図4の(A)に示す4分周の場合には、まず4f0の同期信号が2次高調波と混合され、さらに1次高調波と混合されて、発振回路は基本周波数f0に近い周波数で発振するようにロックされる。図4の(B)に示す8分周の場合には、8f0の同期信号が4次高調波と混合され、さらに2次高調波と混合され、最後に1次高調波と混合されて、発振回路は基本周波数f0に近い周波数で発振するようにロックされる。

【0022】

図2の(A)に示した従来例では、同期信号を(N−1)次の高調波と混合していたのに対して、本発明では、N/2次の高調波と混合する。N/2次の高調波の方が、(N−1)次の高調波と比べてはるかに大きなパワーであり、注入同期型の分周回路に大きな同期信号を注入することができる。

【0023】

本発明によれば、基本周波数f0のより高次の高調波を発生する必要があるが、これは信号のN相を混合して(N−1)次までのすべての高調波を相殺して、N次の高調波を発生することにより実現される。同期信号を発生する各段階で、同期動作に悪影響を与える低次および強い高調波をすべてフィルタリングして、所望の次数の高調波のみを残す。これにより、同期信号は各段階でもっとも強い高調波と混合されるので、他に強くなって発振する分周比は無くなる。これにより、分周比が重複することが無くなり、所望の分周比を確実に得ることができる。

【0024】

さらに、図2の(B)の2分周回路を2個直列に接続して4分周する場合には、2個の2分周回路のロック範囲は、1段目と2段目の2分周回路のそれぞれのロック範囲を合成したものとなる。製造プロセスの関係から、2個の2分周回路は、異なる特性を有し、ロック範囲も異なるので、その分実質的なロック範囲が狭くなる。これに対して、本発明の分周回路では、リングオシレータを有する分周回路は1個のみであり、同期信号を生成する同期信号生成回路で、N/2n次の高調波を発生するので、ロック範囲が狭くなることはない。

【0025】

さらに、本発明によれば、同期信号を注入する同期信号生成回路の途中の段階を切り替えることにより、より低分周比の発振信号を同期信号として入力することもできる。例えば、図4の(A)では、2f0を入力して、4f0を入力しなければ2分周回路として動作し、4f0を入力して、2f0を入力しなければ4分周回路として動作する。同様に、図4の(B)では、2f0を入力して、4f0および8f0を入力しなければ2分周回路として動作し、4f0を入力して、2f0および8f0を入力しなければ4分周回路として動作し、8f0を入力して、2f0および4f0を入力しなければ8分周回路として動作する。

【発明の効果】

【0026】

本発明によれば、4分周以上の2i(iは整数)分周が可能で、所望の周波数で安定してロックする分周回路を、小さな回路規模で実現でき、消費電力も小さくできる。

【図面の簡単な説明】

【0027】

【図1】図1は、注入同期型分周回路の概略構成を示す図である。

【図2】図2は、注入同期型分周回路のモデルを示す図であり、(A)がN分周するモデルを、(B)が2分周するモデルを示す。

【図3】図3は、2段のリングオシレータを利用した注入同期型分周回路の構成例を示す図であり、(A)がブロック図を、(B)が遅延要素を差動型のバッファ回路で実現した具体的な回路例を、それぞれ示す。

【図4】図4は、本発明の分周回路のモデル図であり、(A)4分周の場合を、(B)が8分周の場合を示す。

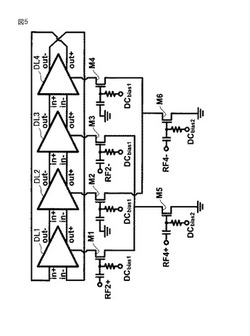

【図5】図5は、本発明の第1実施形態の分周回路の構成を示す図である。

【図6】図6は、第1実施形態の分周回路で使用する遅延要素を形成する差動型のバッファ回路の回路例を示す図である。

【図7】図7は、第1実施形態の分周回路の動作を説明する図であり、入力発振信号RF4+およびRF4−が入力され、RF2+およびRF2−は入力されない場合の動作を示す。

【図8】図8は、本発明の第2実施形態の分周回路の構成を示す図である。

【図9】図9は、第2実施形態の分周回路の動作を説明する図であり、入力発振信号RF8+およびRF8−が入力され、RF4+およびRF4−は入力されない場合の動作を示す。

【図10】図10は、本発明の第3実施形態の分周回路の構成を示す図である。

【図11】図11は、本発明の第4実施形態の分周回路の構成を示す図である。

【図12】図12は、PMOS電流源の遅延要素DL1P〜DL4Pを使用してリングオシレータを形成し、同期信号生成回路をPMOSトランジスタM1P〜M5Pで実現した変形例の分周回路を示す図である。

【図13】図13は、変形例で使用する遅延要素の構成例を示す図である。

【図14】図14は、本発明の分周回路を使用したPLL回路の構成例を示す図である。

【発明を実施するための形態】

【0028】

図5は、本発明の第1実施形態の分周回路の構成を示す図である。また、図6は、第1実施形態の分周回路で使用する遅延要素DL1〜DL4を形成する差動型のバッファ回路の回路例を示す図である。以下の説明では、MOSトランジスタを使用した例を説明するが、本発明はこれに限定されるものではなく、バイポーラトランジスタ等を使用することも可能である。これに関連して、MOSトランジスタのゲート等の制御信号が入力される端子を制御端子と、MOSトランジスタのソースおよびドレイン等の制御信号により電流が制御される端子を被制御端子と称する場合がある。

【0029】

第1実施形態の分周回路は、差動の入力発振信号RF4+およびRF4−またはRF2+およびRF2−が選択的に入力され、RF4+およびRF4−を入力した場合には入力発振信号を4分周した信号を発生し、RF2+およびRF2−を入力した場合には入力発振信号を2分周した信号を発生する。

【0030】

図5に示すように、第1実施形態の分周回路は、4個の遅延要素DL1〜DL4をリング状に接続した発振器(リングオシレータ)と、トランジスタM1からM6を含む同期信号生成回路と、を有する。

【0031】

リングオシレータは、前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続された4個の遅延要素DL1〜DL4を有する。遅延要素DL1〜DL4は、図6に示すバッファ回路などで形成されるが、それに限定されるものではなく、遅延要素として動作可能であればどのような回路でもよい。図6のバッファ回路は、図3の(B)に示した回路であり、広く知られているので説明は省略するが、端子Tuneに直流(DC)バイアス電圧を印加することにより、動作速度を調整する。

【0032】

図5に示すように、1段目の遅延要素DL1の正出力out+および負出力out−を、2段目の遅延要素DL2の負入力in−および正入力in+に接続する。以下、4段目まで同様に接続し、4段目の遅延要素DL4の正出力out+および負出力out−を、1段目の遅延要素DL1の正入力in+および負入力in−に接続する。これにより、1段目の入力に対応する4段目の出力が反転されて再び1段目の入力に戻されることになり、リングオシレータは発振する。リングオシレータの発振周波数は、同期信号の注入が無ければ、4個の遅延要素DL1〜DL4の遅延時間により決定される。

【0033】

遅延要素DL1〜DL4の差動対の共通ノード(テール)は、補助注入トランジスタM1〜M4のドレインにそれぞれ接続される。補助注入トランジスタM1とM3のソースは共通接続ノードに接続され、この共通接続ノードとグランドの間に信号注入トランジスタM5が接続される。同様に、補助注入トランジスタM2とM4のソースは共通接続ノードに接続され、この共通接続ノードとグランドの間に信号注入トランジスタM6が接続される。したがって、補助注入トランジスタM1とM3およびM2とM4は、差動対を形成する。

【0034】

信号注入トランジスタM5のゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4+が印加可能に構成されている。信号注入トランジスタM6のゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4−が印加可能に構成されている。補助注入トランジスタM1のゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して入力発振信号のRF2+が印加可能に構成されている。補助注入トランジスタM3のゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して入力発振信号のRF2−が印加可能に構成されている。補助注入トランジスタM2およびM4のゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して接地されている。なお、容量を介さずに、各バイアス電圧でバイアスされたRF4+,RF4−,RF2+,RF2−等の信号をゲートに入力可能にしてもよい。

【0035】

図7は、第1実施形態の分周回路の動作を説明する図であり、入力発振信号RF4+およびRF4−が入力され、RF2+およびRF2−は入力されない場合の動作を示す。

【0036】

図7の(C)に示すように、入力発振信号RF4+およびRF4−として、周波数4f0の発振信号が信号注入トランジスタM5およびM6のゲートに入力される。なお、図示を容易にするために、図7の(C)では、入力発振信号RF4+のみを示し、RF4−の図示は省略している。RF4−は、RF4+の逆相の信号である。

【0037】

補助注入トランジスタM1とM3のゲートには第1バイアス電圧DCbias1が印加されており、補助注入トランジスタM1とM3は、所定のトランスコンダクタンスを有する状態である。この状態で、信号注入トランジスタM5が、ゲートに印加されるRF4+に応じてトランスコンダクタンスを変化させると、信号注入トランジスタM5のトランスコンダクタンスの変化により発生した信号に、上記の高調波を重畳した信号が、補助注入トランジスタM1とM3のソースを接続した共通接続ノードに発生する。この信号には、RF4+とRF4+の2分周信号の差成分、すなわちRF4+の2分周成分が多く含まれる。共通接続ノードに発生した信号は、補助注入トランジスタM1とM3のドレインに伝達されるが、この時、補助注入トランジスタM1とM3のドレインに発生する信号は、補助注入トランジスタM1とM3の特性差により、逆相になる。言い換えれば、補助注入トランジスタM1とM3のドレインには、RF4+とRF4+の2分周信号との差成分、すなわちRF4+の2分周成分を多く含む逆相の信号が発生する。図7の(B)の実線と破線は、補助注入トランジスタM1とM3のドレインに発生する信号を示す。これらの信号は、図7の(C)のRF4+の周波数が1/2の2次高調波信号、すなわちRF4+を2分周した信号であり、逆相の信号である。

【0038】

補助注入トランジスタM1とM3のドレインは、さらに遅延要素DL1およびDL3の差動対の接続ノードに接続されており、遅延要素DL1およびDL3の差動対のトランジスタのオン・オフ動作は、補助注入トランジスタM1とM3のドレインの信号の影響を受ける。

【0039】

以上の説明は、信号注入トランジスタM6、補助注入トランジスタM2とM4、および遅延要素DL2およびDL4の差動対についても同様であり、遅延要素DL2およびDL4の差動対のトランジスタのオン・オフ動作は、補助注入トランジスタM2とM4のドレインの信号の影響を受ける。

【0040】

リングオシレータは、以上のような各部の信号相互の影響を受けて、RF4+およびRF−の周波数4f0を4分周した周波数f0にロックして発振する。ロックした状態では、リングオシレータの最終段の出力信号、すなわち1段目の遅延要素DL1の入力信号は、図7の(A)において実線で示す信号のようになり、3段目の遅延要素DL3の入力信号は、図7の(B)において実線で示す信号のようになる。

【0041】

第1実施形態の分周回路において、入力発振信号RF2+およびRF2−が入力され、RF4+およびRF4−は入力されない場合には、図7の(B)の2次高調波として、RF2+およびRF2−が直接入力されることになり、リングオシレータは、図7の(A)に示すRF2+およびRF2−の2分周信号を出力する。

【0042】

図8は、本発明の第2実施形態の分周回路の構成を示す図である。

【0043】

第2実施形態の分周回路は、差動の入力発振信号RF8+およびRF8−またはRF2+およびRF2−が選択的に入力され、RF8+およびRF8−を入力した場合には入力発振信号を8分周した信号を発生し、RF4+およびRF4−を入力した場合には入力発振信号を4分周した信号を発生する。

【0044】

図8に示すように、第2実施形態の分周回路は、8個の遅延要素DL1A〜DL8Aをリング状に接続した発振器(リングオシレータ)と、トランジスタM1AからM14Aを含む同期信号生成回路と、を有する。

【0045】

リングオシレータは、前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続された8個の遅延要素DL1A〜DL8Aを有する。遅延要素DL1A〜DL8Aは、図6に示すバッファ回路などで形成されるが、それに限定されるものではない。

【0046】

遅延要素DL1A〜DL8Aの差動対の共通ノード(テール)は、初段注入トランジスタM1A〜M8Aのドレインにそれぞれ接続される。初段注入トランジスタM1AとM5Aのソースは、共通接続ノードに接続され、その共通ノードは、さらに補助注入トランジスタM9Aのドレインに接続される。以下同様に、M2AとM4Aのソースは、M10Aのドレインに共通に接続され、M3AとM7Aのソースは、M11Aのドレインに共通に接続され、M4AとM8Aのソースは、M12Aのドレインに共通に接続される。さらに、M9AとM11Aのソースは、M13Aのドレインに共通に接続され、M10AとM12Aのソースは、M14Aのドレインに共通に接続される。初段注入トランジスタM1AとM5A、M2AとM4A、M3AとM7A、およびM4AとM8Aは、差動対を形成する。同様に、M9AとM11A、およびM10AとM12Aのソースは、差動対を形成する。

【0047】

信号注入トランジスタM13Aのゲートは、抵抗を介して第3バイアス電圧DCbias3が印加されると共に、容量を介して入力発振信号RF8+が印加可能に構成されている。信号注入トランジスタM13Aのゲートは、抵抗を介して第3バイアス電圧DCbias3が印加されると共に、容量を介して入力発振信号RF8−が印加可能に構成されている。補助注入トランジスタM9Aのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号のRF4+が印加可能に構成されている。補助注入トランジスタM11Aのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号のRF4−が印加可能に構成されている。他のトランジスタM1A〜M8A、M10AおよびM12Aのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して接地されている。

【0048】

以上のように、第2実施形態の分周回路は、第1実施形態の分周回路において、同期信号生成回路を3段階構成にしてもので、2段目のM9AおよびM11Aの差動対と1段目のM13A、および2段目のM10AおよびM12Aの差動対と1段目のM14Aは、第1実施形態と同様に、RF8+およびRF8−の2次高調波を、M9AおよびM11Aのドレインと、M10AおよびM12Aのドレインに発生する。1段目のM1AおよびM5Aの差動対と2段目のM9Aは、同様に、RF8+およびRF8−の4次高調波を、M1AおよびM5Aのドレインに発生する。以下同様に、1段目の初段注入トランジスタM1A〜M8Aのドレイン、すなわち遅延要素DL1A〜DL8Aのテールに、RF8+およびRF8−の4次高調波が印加される。

【0049】

図9は、第2実施形態の分周回路の動作を説明する図であり、入力発振信号RF8+およびRF8−が入力され、RF4+およびRF4−は入力されない場合の動作を示す。

【0050】

図9の第2実施形態の分周回路の動作は、段数が1段増加した以外は、第1実施形態の分周回路の動作と同じであるので、説明は省略する。

【0051】

図10は、本発明の第3実施形態の分周回路の構成を示す図である。

【0052】

第3実施形態の分周回路は、差動の入力発振信号RF4+が入力され、RF4+を4分周した信号を発生する。

【0053】

図10に示すように、第3実施形態の分周回路は、2個の遅延要素DL1B〜DL2Bをリング状に接続した発振器(リングオシレータ)と、トランジスタM1BからM3Bを含む同期信号生成回路と、を有する。

【0054】

リングオシレータは、前段の出力信号が後段の入力信号として入力し、後段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、後段から初段への入力信号が反転するように接続された2個の遅延要素DL1B〜DL2Bを有する。遅延要素DL1BおよびDL2Bは、図6に示すバッファ回路などで形成されるが、それに限定されるものではない。

【0055】

遅延要素DL1BおよびDL2Bの差動対の共通ノード(テール)は、それぞれ補助注入トランジスタM1BおよびM2Bのドレインに接続される。M1BとM2Bのソースは、信号注入トランジスタM3Bを介して接地される。

【0056】

信号注入トランジスタM3Bのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4+が印加される。補助注入トランジスタM1BおよびM2Bのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して接地されている。

【0057】

以上のように、第3実施形態の分周回路は、第1実施形態の分周回路において、リングオシレータを2段構成にしてもので、入力発振信号RF4+のみを入力し、RF4−は入力しないが、第1実施形態と同様に、RF4+の1/4の周波数にロックし、RF4+を4分周した分周信号を出力する。第3実施形態の分周回路の動作は、第1実施形態の説明と同様であり、説明は省略する。

【0058】

図11は、本発明の第4実施形態の分周回路の構成を示す図である。

【0059】

第4実施形態の分周回路は、差動の入力発振信号RF4+およびRF4−またはRF2+およびRF2−が選択的に入力され、RF4+およびRF4−を入力した場合には入力発振信号を4分周した信号を発生し、RF2+およびRF2−を入力した場合には入力発振信号を2分周した信号を発生する。

【0060】

図11に示すように、第4実施形態の分周回路は、4個の遅延要素DL1〜DL4をリング状に接続した発振器(リングオシレータ)と、トランジスタM1からM6を含む同期信号生成回路と、を有する。

【0061】

リングオシレータは、第1実施形態と同様であり、説明は省略する。

【0062】

遅延要素DL1〜DL4の差動対の共通ノード(テール)は、補助注入トランジスタM1C〜M4Cのドレインにそれぞれ接続される。補助注入トランジスタM1C〜M4Cのソースは接地される。補助注入トランジスタM1Cのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して入力発振信号のRF2+が印加可能に構成されている。補助注入トランジスタM3Cのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して入力発振信号のRF2−が印加可能に構成されている。補助注入トランジスタM2CおよびM4Cのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して接地されている。

【0063】

補助注入トランジスタM1CとM3Cのドレインの間には、信号注入トランジスタM5Cが接続されている。同様に、補助注入トランジスタM2CとM4Cのドレインの間には、信号注入トランジスタM5Cが接続されている。信号注入トランジスタM5Cのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4+が印加可能に構成されている。信号注入トランジスタM6Cのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4−が印加可能に構成されている。

【0064】

第4実施形態の分周回路において、入力発振信号RF4+およびRF4−が入力され、RF2+およびRF2−は入力されない場合の動作を説明する。この場合も、第1実施形態と同様に、信号注入トランジスタM5Cは、ゲートに印加されるRF4+に応じてトランスコンダクタンスを変化させる。これに応じて、補助注入トランジスタM2CとM4Cのドレイン間のコンダクタンスが変化すると共に、補助注入トランジスタM2CとM4Cのドレインに、RF4+の高調波を発生する。この高調波は、RF4+の2次高調波成分、すなわちRF4+の2分周成分が多く含まれ、M2Cのドレインの信号とM4Cのドレインの信号は逆相の信号である。したがって、第1実施例で説明したのと同様に、遅延要素DL1およびDL3の差動対のトランジスタのオン・オフ動作が、補助注入トランジスタM1CとM3Cのドレインの信号の影響を受け、リングオシレータは、RF4+およびRF−の周波数4f0を4分周した周波数f0にロックして発振する。

【0065】

以上説明した第1から第4実施形態では、PMOS電流源の遅延要素を使用し、同期信号生成回路のトランジスタをNMOSで実現した例を説明した。しかし、NMOS電流源の遅延要素を使用することも、クロスカップルした電流源を使用することも、PMOSが抵抗を介してダイオード接続されたものを使用することなどが可能である。また、同期信号生成回路のトランジスタをPMOSで実現することも可能である。

【0066】

図12は、PMOS電流源の遅延要素DL1P〜DL4Pを使用してリングオシレータを形成し、同期信号生成回路をPMOSトランジスタM1P〜M6Pで実現した変形例の分周回路を示す図であり、図13は変形例で使用する遅延要素の構成例を示す図である。

【0067】

この変形例は、第1実施形態の分周回路を上記のように変更したのみであり、説明は省略する。

【0068】

さらに、以上説明した第1から第4実施形態および変形例では、遅延要素は差動型であったが、単相信号を入出力するが単相型の遅延要素を使用することも可能である。

【0069】

本発明の分周回路は、PLL回路の一部として使用することが可能である。

【0070】

図14は、本発明の分周回路を使用したPLL回路の構成例を示す図である。

【0071】

図14に示すように、PLL回路は、電圧制御発振器(VCO)21と、VCO21の出力するクロックfoutを分周して分周クロックを出力する分周回路22と、基準クロックfinと分周クロックの位相差および周波数差を検出して制御信号を出力する位相周波数検出回路23と、制御信号に応じてレベル信号を生成するチャージポンプ(CP)24と、レベル信号の低周波数成分を抽出した低周波数信号を出力するローパスフィルタ(LPF)25と、を有し、VCO21は、ローパスフィルタ25の出力する低周波数信号に応じて発振周波数を変化させる。

【0072】

ここで、クロックfoutの周波数が非常に高い場合、例えば10GHz以上の場合、クロックfoutの分周回路をデジタル回路で形成するのは非常に難しい。そこで、クロックfoutをアナログ回路で形成されるプリスケーラで、クロックfoutをある程度の周波数まで分周した後、デジタル回路で形成したデジタル分周回路でさらに分周することが行なわれる。例えば、図14で、分周回路22を、20GHzのクロックfoutを4分周するプリスケーラと、4分周した5GHzの分周クロックをさらに分周するデジタル分周器で構成する。

【0073】

プリスケーラを安定した分周比で動作可能な従来の2分周回路で実現する場合、2分周回路を直列に2段接続することになり、回路規模および消費電力が大きく、ロック範囲も狭くなるという問題がある。8分周するプリスケーラの場合には3個の2分周回路を直列に接続する必要があり、この問題はより顕著になる。

【0074】

これに対して、第1から第4実施形態および変形例で説明した本発明の分周回路を使用してプリスケーラを実現すると、上記の問題を低減できる。さらに、本発明の分周回路は、入力発振信号の入力ノードを変更することにより、分周回路の分周比を、2分周、4分周、さらには8分周に設定でき、広い範囲のクロックfoutに対応可能である。例えば、2GHzから8GHzの自己発振範囲を有する本発明の4分周回路を使用すれば、2GHzから8GHzの範囲のクロックfoutに対応可能な分周回路およびそれを使用したPLL回路が実現できる。

【0075】

以上、本発明の実施形態を説明したが、記載した実施形態は発明を説明するためのもので、当業者には、特許請求の範囲において各種の変形例があり得ることが容易に理解可能である。

【産業上の利用可能性】

【0076】

本発明は、高速の発振信号を分周する分周回路、およびそれを使用する回路に適用可能である。

【符号の説明】

【0077】

10 注入同期型周波数分周回路(ILFD)

11 発振回路

12 同期信号精製回路

21 電圧制御発振器(VCO)

22 分周回路

23 位相・周波数検出回路

24 チャージポンプ

25 ローパスフィルタ(LPF)

DL1,…DL4,DL1A,…DL8A 遅延要素

M1,…M6,M1A,…M14A,M1B,M2B,M1C,…M6C トランジスタ

【技術分野】

【0001】

本発明は、高周波数において広い範囲での分周が可能な分周器回路およびそれを利用したPLL回路に関し、特に注入同期型発振器を使用した分周回路およびそれを利用したPLL回路に関する。

【背景技術】

【0002】

近年、無線通信に利用される周波数帯域は、一層高周波数になる傾向にあり、それに応じて装置内部に設けられるPLL回路のVCO(電圧制御発振器)が出力するクロックの周波数も高周波数にする必要がある。通常、基準周波数は、VCOが発生するクロック周波数よりはるかに低い周波数であり、クロック周波数を分周して低周波数にする必要があり、分周回路が使用される。VCOが数十GHzのクロックを発生する場合、分周回路を通常のデジタル回路で構成するのは難しく、VCOが出力するクロックをある程度の周波数まで分周するプリスケーラには、アナログ分周回路が使用される。アナログ分周回路は、例えば、電流モードロジック分周回路や注入同期型分周回路(Injection Locked Frequency Divider: ILFD)で実現できる。電流モードロジック分周回路は、広い同期領域を有するが、消費電力が大きいという問題がある。本発明は、注入同期型分周回路に関する。

【0003】

図1は、注入同期型分周回路の概略構成を示す図である。

【0004】

注入同期型分周回路(ILFD)10は、発振回路11と、同期信号生成回路12と、を有する。発振回路11は、自己発振回路であり、同期信号生成回路12から注入される同期信号に応じて発振周波数が変化可能である。同期信号生成回路12は、入力発振信号(クロック)Nf0から、発振回路11を目標とする分周信号の周波数で発振させるための同期信号を生成して、発振回路11に注入する。

【0005】

図2は、注入同期型分周回路のモデルを示す図であり、(A)がN分周するモデルを、(B)が2分周するモデルを示す。

【0006】

図2の(A)に示すように、このモデルでは、基本周波数f0の信号(クロック)は、非線形(Nonlinearity)のトランスコンダクタンス(transconductance)を有するトランジスタを通過し、高次の高調波を発生する。発振回路に何も注入されない時には、これらの高調波は発振回路内のローパスフィルタ(LPF)により減衰され多くが減衰される。しかしながら、同期信号が注入されると、これらの高調波は注入された同期信号と混合され、多くの付加的な高調波が発生する。もしこれらの高調波の1つが発振器の自己発振周波数に近く且つ十分なパワーを有していると、発振器の周波数はこの周波数に引き込まれてその周波数にロック(同期)する。この動作が、(N−1)次の高調波が、N次の高調波の同期信号と混合され、発振器の基本周波数に近い高調波を発生し、それにロックするダイレクト変換である。Nが増加するにしたがって、(N−1)次の高調波が弱くなるので、ロック範囲は狭くなる。さらに、注入同期型分周回路の特定の高調波のレベルは、その発生プロセスが線形でなく、多くの要因に影響されるため、制御できない。そのため、ロック範囲が狭くなり、特定の分周比に必要な注入パワーを制限するという問題がある。

【0007】

以上のように、注入同期型分周回路のロック範囲および必要な注入パワーは分周比に応じて異なるが、一般に2分周の場合が、ロック範囲が広く、注入パワーが小さい。図2の(B)は、2分周の注入同期型分周回路のモデルを示す。

【0008】

注入同期型分周回路は、各種の構成が知られているが、その1つに、複数個の遅延要素をリング状に接続したリングオシレータ(リング状発振回路)を利用する回路がある。リングオシレータは、複数個の遅延要素を、前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続した構成を有する。リングオシレータは、広く知られている回路である。

【0009】

図3は、2段のリングオシレータを利用した注入同期型分周回路の構成例を示す図であり、(A)がブロック図を、(B)が遅延要素を差動型のバッファ回路で実現した具体的な回路例を、それぞれ示す。ここでは、MOSトランジスタを使用した例を示したが、これに限定されるものではない。

【0010】

リングオシレータを利用した注入同期型分周回路では、発振動作を行なう遅延要素の一部に同期信号を印加して高調波を発生することにより、リングオシレータを同期信号に対応した周波数で発振させる。注入同期型分周回路には、発振信号を出力する部分に同期信号を印加するダイレクト方式と、発振動作する差動対に並列に設けた差動対に同期信号を印加するパラレル方式と、差動対の出力ノードと反対側のノードを共通に接続した共通接続ノードに同期信号を印加する方式と、がある。一般に、差動対を形成するトランジスタはテールトランジスタと呼ばれるので、ここでは共通接続ノードに同期信号を印加する方式をテール方式と呼び、共通接続ノードをテールと称するものとする。

【0011】

図3は、テール方式のリングオシレータを利用した注入同期型分周回路を示している。遅延要素DL1およびDL2は、差動型バッファ(インバータ)であり、1段目の遅延要素DL1の正出力out+および負出力out−を、2段目の遅延要素DL2の負入力in−および正入力in+に接続し、2段目の遅延要素DL2の正出力out+および負出力out−を、1段目の遅延要素DL1の正入力in+および負入力in−に接続する。これにより、1段目の入力に対応する2段目の出力が反転されて再び1段目の入力に戻されることになり、リングオシレータは発振する。リングオシレータの発振周波数は、同期信号の注入が無ければ、2個の遅延要素DL1およびDL2の遅延時間により決定される。

【0012】

遅延要素DL1は、差動型バッファであり、差動対を形成する2個のNMOSトランジスタのゲートに入力信号が入力され、2個のNMOSトランジスタのドレインから出力信号が出力される。2個のNMOSトランジスタのソースは、共通ノード、すなわちテールに接続され、共通ノード(テール)は、ソース用トランジスタM1およびM2を介して接地される。ソース用トランジスタM1およびM2のゲートには、抵抗を介してDCバイアス電圧が印加される。

【0013】

図3の注入同期型分周回路では、1段目の遅延要素DL1のソース用トランジスタM1のゲートにはさらに容量が接続され、容量の他方の端子に同期信号RF2+が印加される。一方、2段目の遅延要素DL1のソース用トランジスタM2のゲートにも容量が接続されるが、容量の他方の端子は接地される。同期信号RF2+は、注入同期型分周回路の出力する分周信号の周波数f0の2倍の周波数2f0の信号である。言い換えれば、図3の注入同期型分周回路は、周波数2f0の入力発振信号を、周波数f0の分周信号に分周する2分周回路である。

【先行技術文献】

【非特許文献】

【0014】

【非特許文献1】P. Mayr, C. Weyers, and U. Langmann, “A 90GHz 65nm CMOS Injection-Locked Frequency Divider”, IEEE International Solid-State Circuits Conference, Feb. 2007, pp.198-199

【発明の概要】

【発明が解決しようとする課題】

【0015】

注入同期型分周回路のロックしやすい周波数は、注入同期型分周回路の回路特性により決定され、プロセスのばらつきなどの影響を受ける。上記のように、注入同期型分周回路のロック範囲および必要な注入パワーは分周比に応じて異なり、特に高い分周比でロックして安定して動作するのが難しいという問題があった。これに対して、図2の(B)に示すような2分周の注入同期型分周回路のモデルは、一般に、ロック範囲が広く、注入パワーが小さい。そこで、非特許文献1は、2分周の注入同期型分周回路を2個直列に接続して4分周(×4)を行なうことを記載している。

【0016】

しかし、注入同期型分周回路を2個使用した場合、回路面積が大きくなり、消費電力も増加するという問題がある。もし8分周する場合には、注入同期型分周回路を3個使用することになり、回路面積および消費電力はさらに増加するという問題がある。

【0017】

本発明は、2分周、8分周、さらには8分周可能な注入同期型分周回路を、より簡単な構成で実現することを目的とする。

【課題を解決するための手段】

【0018】

本発明の分周回路は、注入同期型であり、入力発振信号を4分周する場合に、M(Mは偶数)個の遅延要素を含むリングオシレータを利用したテール方式の注入同期型分周回路で、M/2個離れた2つの遅延要素のテールを差動対に接続し、入力発振信号がゲートに印加されるトランジスタを差動対に接続して、差動対に入力発振信号の差動信号、すなわち入力発振信号を2分周した信号を発生させる。入力発振信号を8分周する場合には、遅延要素のテールに接続される差動対の部分を2段階構成、すなわち縦積み構成にする。

【0019】

言い換えれば、本発明の分周回路は、前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続されたM(2以上の整数)個の遅延要素を有する発振回路と、入力発振信号から遅延要素の状態変化を規制する同期信号を生成し、生成した同期信号を前記複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を備え、発振回路から入力発振信号の分周信号を出力する分周回路であって、Mは偶数であり、遅延要素は、制御端子に入力信号が入力される分周トランジスタを有し、分周トランジスタの一方の被制御端子から出力が得られ、分周トランジスタの他方の被制御端子が注入ノードであり、同期信号注入回路は、発振回路のM/2個離れた2つの遅延要素の分周トランジスタの注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対と、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続され、制御端子に入力発振信号が入力可能である信号注入トランジスタと、を有することを特徴とする。

【0020】

図4は、本発明の分周回路のモデル図であり、(A)4分周の場合を、(B)が8分周の場合を示す。図4を参照して、本発明の原理を説明する。

【0021】

本発明の分周回路では、N次の高調波の同期信号は、発振回路の基本周波数f0のN/2次の高調波と混合され、さらにN/4次の高調波と混合されるという具合に、発振回路の基本周波数f0に近い周波数の高調波が発生されるまで繰り返される。図4の(A)に示す4分周の場合には、まず4f0の同期信号が2次高調波と混合され、さらに1次高調波と混合されて、発振回路は基本周波数f0に近い周波数で発振するようにロックされる。図4の(B)に示す8分周の場合には、8f0の同期信号が4次高調波と混合され、さらに2次高調波と混合され、最後に1次高調波と混合されて、発振回路は基本周波数f0に近い周波数で発振するようにロックされる。

【0022】

図2の(A)に示した従来例では、同期信号を(N−1)次の高調波と混合していたのに対して、本発明では、N/2次の高調波と混合する。N/2次の高調波の方が、(N−1)次の高調波と比べてはるかに大きなパワーであり、注入同期型の分周回路に大きな同期信号を注入することができる。

【0023】

本発明によれば、基本周波数f0のより高次の高調波を発生する必要があるが、これは信号のN相を混合して(N−1)次までのすべての高調波を相殺して、N次の高調波を発生することにより実現される。同期信号を発生する各段階で、同期動作に悪影響を与える低次および強い高調波をすべてフィルタリングして、所望の次数の高調波のみを残す。これにより、同期信号は各段階でもっとも強い高調波と混合されるので、他に強くなって発振する分周比は無くなる。これにより、分周比が重複することが無くなり、所望の分周比を確実に得ることができる。

【0024】

さらに、図2の(B)の2分周回路を2個直列に接続して4分周する場合には、2個の2分周回路のロック範囲は、1段目と2段目の2分周回路のそれぞれのロック範囲を合成したものとなる。製造プロセスの関係から、2個の2分周回路は、異なる特性を有し、ロック範囲も異なるので、その分実質的なロック範囲が狭くなる。これに対して、本発明の分周回路では、リングオシレータを有する分周回路は1個のみであり、同期信号を生成する同期信号生成回路で、N/2n次の高調波を発生するので、ロック範囲が狭くなることはない。

【0025】

さらに、本発明によれば、同期信号を注入する同期信号生成回路の途中の段階を切り替えることにより、より低分周比の発振信号を同期信号として入力することもできる。例えば、図4の(A)では、2f0を入力して、4f0を入力しなければ2分周回路として動作し、4f0を入力して、2f0を入力しなければ4分周回路として動作する。同様に、図4の(B)では、2f0を入力して、4f0および8f0を入力しなければ2分周回路として動作し、4f0を入力して、2f0および8f0を入力しなければ4分周回路として動作し、8f0を入力して、2f0および4f0を入力しなければ8分周回路として動作する。

【発明の効果】

【0026】

本発明によれば、4分周以上の2i(iは整数)分周が可能で、所望の周波数で安定してロックする分周回路を、小さな回路規模で実現でき、消費電力も小さくできる。

【図面の簡単な説明】

【0027】

【図1】図1は、注入同期型分周回路の概略構成を示す図である。

【図2】図2は、注入同期型分周回路のモデルを示す図であり、(A)がN分周するモデルを、(B)が2分周するモデルを示す。

【図3】図3は、2段のリングオシレータを利用した注入同期型分周回路の構成例を示す図であり、(A)がブロック図を、(B)が遅延要素を差動型のバッファ回路で実現した具体的な回路例を、それぞれ示す。

【図4】図4は、本発明の分周回路のモデル図であり、(A)4分周の場合を、(B)が8分周の場合を示す。

【図5】図5は、本発明の第1実施形態の分周回路の構成を示す図である。

【図6】図6は、第1実施形態の分周回路で使用する遅延要素を形成する差動型のバッファ回路の回路例を示す図である。

【図7】図7は、第1実施形態の分周回路の動作を説明する図であり、入力発振信号RF4+およびRF4−が入力され、RF2+およびRF2−は入力されない場合の動作を示す。

【図8】図8は、本発明の第2実施形態の分周回路の構成を示す図である。

【図9】図9は、第2実施形態の分周回路の動作を説明する図であり、入力発振信号RF8+およびRF8−が入力され、RF4+およびRF4−は入力されない場合の動作を示す。

【図10】図10は、本発明の第3実施形態の分周回路の構成を示す図である。

【図11】図11は、本発明の第4実施形態の分周回路の構成を示す図である。

【図12】図12は、PMOS電流源の遅延要素DL1P〜DL4Pを使用してリングオシレータを形成し、同期信号生成回路をPMOSトランジスタM1P〜M5Pで実現した変形例の分周回路を示す図である。

【図13】図13は、変形例で使用する遅延要素の構成例を示す図である。

【図14】図14は、本発明の分周回路を使用したPLL回路の構成例を示す図である。

【発明を実施するための形態】

【0028】

図5は、本発明の第1実施形態の分周回路の構成を示す図である。また、図6は、第1実施形態の分周回路で使用する遅延要素DL1〜DL4を形成する差動型のバッファ回路の回路例を示す図である。以下の説明では、MOSトランジスタを使用した例を説明するが、本発明はこれに限定されるものではなく、バイポーラトランジスタ等を使用することも可能である。これに関連して、MOSトランジスタのゲート等の制御信号が入力される端子を制御端子と、MOSトランジスタのソースおよびドレイン等の制御信号により電流が制御される端子を被制御端子と称する場合がある。

【0029】

第1実施形態の分周回路は、差動の入力発振信号RF4+およびRF4−またはRF2+およびRF2−が選択的に入力され、RF4+およびRF4−を入力した場合には入力発振信号を4分周した信号を発生し、RF2+およびRF2−を入力した場合には入力発振信号を2分周した信号を発生する。

【0030】

図5に示すように、第1実施形態の分周回路は、4個の遅延要素DL1〜DL4をリング状に接続した発振器(リングオシレータ)と、トランジスタM1からM6を含む同期信号生成回路と、を有する。

【0031】

リングオシレータは、前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続された4個の遅延要素DL1〜DL4を有する。遅延要素DL1〜DL4は、図6に示すバッファ回路などで形成されるが、それに限定されるものではなく、遅延要素として動作可能であればどのような回路でもよい。図6のバッファ回路は、図3の(B)に示した回路であり、広く知られているので説明は省略するが、端子Tuneに直流(DC)バイアス電圧を印加することにより、動作速度を調整する。

【0032】

図5に示すように、1段目の遅延要素DL1の正出力out+および負出力out−を、2段目の遅延要素DL2の負入力in−および正入力in+に接続する。以下、4段目まで同様に接続し、4段目の遅延要素DL4の正出力out+および負出力out−を、1段目の遅延要素DL1の正入力in+および負入力in−に接続する。これにより、1段目の入力に対応する4段目の出力が反転されて再び1段目の入力に戻されることになり、リングオシレータは発振する。リングオシレータの発振周波数は、同期信号の注入が無ければ、4個の遅延要素DL1〜DL4の遅延時間により決定される。

【0033】

遅延要素DL1〜DL4の差動対の共通ノード(テール)は、補助注入トランジスタM1〜M4のドレインにそれぞれ接続される。補助注入トランジスタM1とM3のソースは共通接続ノードに接続され、この共通接続ノードとグランドの間に信号注入トランジスタM5が接続される。同様に、補助注入トランジスタM2とM4のソースは共通接続ノードに接続され、この共通接続ノードとグランドの間に信号注入トランジスタM6が接続される。したがって、補助注入トランジスタM1とM3およびM2とM4は、差動対を形成する。

【0034】

信号注入トランジスタM5のゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4+が印加可能に構成されている。信号注入トランジスタM6のゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4−が印加可能に構成されている。補助注入トランジスタM1のゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して入力発振信号のRF2+が印加可能に構成されている。補助注入トランジスタM3のゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して入力発振信号のRF2−が印加可能に構成されている。補助注入トランジスタM2およびM4のゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して接地されている。なお、容量を介さずに、各バイアス電圧でバイアスされたRF4+,RF4−,RF2+,RF2−等の信号をゲートに入力可能にしてもよい。

【0035】

図7は、第1実施形態の分周回路の動作を説明する図であり、入力発振信号RF4+およびRF4−が入力され、RF2+およびRF2−は入力されない場合の動作を示す。

【0036】

図7の(C)に示すように、入力発振信号RF4+およびRF4−として、周波数4f0の発振信号が信号注入トランジスタM5およびM6のゲートに入力される。なお、図示を容易にするために、図7の(C)では、入力発振信号RF4+のみを示し、RF4−の図示は省略している。RF4−は、RF4+の逆相の信号である。

【0037】

補助注入トランジスタM1とM3のゲートには第1バイアス電圧DCbias1が印加されており、補助注入トランジスタM1とM3は、所定のトランスコンダクタンスを有する状態である。この状態で、信号注入トランジスタM5が、ゲートに印加されるRF4+に応じてトランスコンダクタンスを変化させると、信号注入トランジスタM5のトランスコンダクタンスの変化により発生した信号に、上記の高調波を重畳した信号が、補助注入トランジスタM1とM3のソースを接続した共通接続ノードに発生する。この信号には、RF4+とRF4+の2分周信号の差成分、すなわちRF4+の2分周成分が多く含まれる。共通接続ノードに発生した信号は、補助注入トランジスタM1とM3のドレインに伝達されるが、この時、補助注入トランジスタM1とM3のドレインに発生する信号は、補助注入トランジスタM1とM3の特性差により、逆相になる。言い換えれば、補助注入トランジスタM1とM3のドレインには、RF4+とRF4+の2分周信号との差成分、すなわちRF4+の2分周成分を多く含む逆相の信号が発生する。図7の(B)の実線と破線は、補助注入トランジスタM1とM3のドレインに発生する信号を示す。これらの信号は、図7の(C)のRF4+の周波数が1/2の2次高調波信号、すなわちRF4+を2分周した信号であり、逆相の信号である。

【0038】

補助注入トランジスタM1とM3のドレインは、さらに遅延要素DL1およびDL3の差動対の接続ノードに接続されており、遅延要素DL1およびDL3の差動対のトランジスタのオン・オフ動作は、補助注入トランジスタM1とM3のドレインの信号の影響を受ける。

【0039】

以上の説明は、信号注入トランジスタM6、補助注入トランジスタM2とM4、および遅延要素DL2およびDL4の差動対についても同様であり、遅延要素DL2およびDL4の差動対のトランジスタのオン・オフ動作は、補助注入トランジスタM2とM4のドレインの信号の影響を受ける。

【0040】

リングオシレータは、以上のような各部の信号相互の影響を受けて、RF4+およびRF−の周波数4f0を4分周した周波数f0にロックして発振する。ロックした状態では、リングオシレータの最終段の出力信号、すなわち1段目の遅延要素DL1の入力信号は、図7の(A)において実線で示す信号のようになり、3段目の遅延要素DL3の入力信号は、図7の(B)において実線で示す信号のようになる。

【0041】

第1実施形態の分周回路において、入力発振信号RF2+およびRF2−が入力され、RF4+およびRF4−は入力されない場合には、図7の(B)の2次高調波として、RF2+およびRF2−が直接入力されることになり、リングオシレータは、図7の(A)に示すRF2+およびRF2−の2分周信号を出力する。

【0042】

図8は、本発明の第2実施形態の分周回路の構成を示す図である。

【0043】

第2実施形態の分周回路は、差動の入力発振信号RF8+およびRF8−またはRF2+およびRF2−が選択的に入力され、RF8+およびRF8−を入力した場合には入力発振信号を8分周した信号を発生し、RF4+およびRF4−を入力した場合には入力発振信号を4分周した信号を発生する。

【0044】

図8に示すように、第2実施形態の分周回路は、8個の遅延要素DL1A〜DL8Aをリング状に接続した発振器(リングオシレータ)と、トランジスタM1AからM14Aを含む同期信号生成回路と、を有する。

【0045】

リングオシレータは、前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続された8個の遅延要素DL1A〜DL8Aを有する。遅延要素DL1A〜DL8Aは、図6に示すバッファ回路などで形成されるが、それに限定されるものではない。

【0046】

遅延要素DL1A〜DL8Aの差動対の共通ノード(テール)は、初段注入トランジスタM1A〜M8Aのドレインにそれぞれ接続される。初段注入トランジスタM1AとM5Aのソースは、共通接続ノードに接続され、その共通ノードは、さらに補助注入トランジスタM9Aのドレインに接続される。以下同様に、M2AとM4Aのソースは、M10Aのドレインに共通に接続され、M3AとM7Aのソースは、M11Aのドレインに共通に接続され、M4AとM8Aのソースは、M12Aのドレインに共通に接続される。さらに、M9AとM11Aのソースは、M13Aのドレインに共通に接続され、M10AとM12Aのソースは、M14Aのドレインに共通に接続される。初段注入トランジスタM1AとM5A、M2AとM4A、M3AとM7A、およびM4AとM8Aは、差動対を形成する。同様に、M9AとM11A、およびM10AとM12Aのソースは、差動対を形成する。

【0047】

信号注入トランジスタM13Aのゲートは、抵抗を介して第3バイアス電圧DCbias3が印加されると共に、容量を介して入力発振信号RF8+が印加可能に構成されている。信号注入トランジスタM13Aのゲートは、抵抗を介して第3バイアス電圧DCbias3が印加されると共に、容量を介して入力発振信号RF8−が印加可能に構成されている。補助注入トランジスタM9Aのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号のRF4+が印加可能に構成されている。補助注入トランジスタM11Aのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号のRF4−が印加可能に構成されている。他のトランジスタM1A〜M8A、M10AおよびM12Aのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して接地されている。

【0048】

以上のように、第2実施形態の分周回路は、第1実施形態の分周回路において、同期信号生成回路を3段階構成にしてもので、2段目のM9AおよびM11Aの差動対と1段目のM13A、および2段目のM10AおよびM12Aの差動対と1段目のM14Aは、第1実施形態と同様に、RF8+およびRF8−の2次高調波を、M9AおよびM11Aのドレインと、M10AおよびM12Aのドレインに発生する。1段目のM1AおよびM5Aの差動対と2段目のM9Aは、同様に、RF8+およびRF8−の4次高調波を、M1AおよびM5Aのドレインに発生する。以下同様に、1段目の初段注入トランジスタM1A〜M8Aのドレイン、すなわち遅延要素DL1A〜DL8Aのテールに、RF8+およびRF8−の4次高調波が印加される。

【0049】

図9は、第2実施形態の分周回路の動作を説明する図であり、入力発振信号RF8+およびRF8−が入力され、RF4+およびRF4−は入力されない場合の動作を示す。

【0050】

図9の第2実施形態の分周回路の動作は、段数が1段増加した以外は、第1実施形態の分周回路の動作と同じであるので、説明は省略する。

【0051】

図10は、本発明の第3実施形態の分周回路の構成を示す図である。

【0052】

第3実施形態の分周回路は、差動の入力発振信号RF4+が入力され、RF4+を4分周した信号を発生する。

【0053】

図10に示すように、第3実施形態の分周回路は、2個の遅延要素DL1B〜DL2Bをリング状に接続した発振器(リングオシレータ)と、トランジスタM1BからM3Bを含む同期信号生成回路と、を有する。

【0054】

リングオシレータは、前段の出力信号が後段の入力信号として入力し、後段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、後段から初段への入力信号が反転するように接続された2個の遅延要素DL1B〜DL2Bを有する。遅延要素DL1BおよびDL2Bは、図6に示すバッファ回路などで形成されるが、それに限定されるものではない。

【0055】

遅延要素DL1BおよびDL2Bの差動対の共通ノード(テール)は、それぞれ補助注入トランジスタM1BおよびM2Bのドレインに接続される。M1BとM2Bのソースは、信号注入トランジスタM3Bを介して接地される。

【0056】

信号注入トランジスタM3Bのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4+が印加される。補助注入トランジスタM1BおよびM2Bのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して接地されている。

【0057】

以上のように、第3実施形態の分周回路は、第1実施形態の分周回路において、リングオシレータを2段構成にしてもので、入力発振信号RF4+のみを入力し、RF4−は入力しないが、第1実施形態と同様に、RF4+の1/4の周波数にロックし、RF4+を4分周した分周信号を出力する。第3実施形態の分周回路の動作は、第1実施形態の説明と同様であり、説明は省略する。

【0058】

図11は、本発明の第4実施形態の分周回路の構成を示す図である。

【0059】

第4実施形態の分周回路は、差動の入力発振信号RF4+およびRF4−またはRF2+およびRF2−が選択的に入力され、RF4+およびRF4−を入力した場合には入力発振信号を4分周した信号を発生し、RF2+およびRF2−を入力した場合には入力発振信号を2分周した信号を発生する。

【0060】

図11に示すように、第4実施形態の分周回路は、4個の遅延要素DL1〜DL4をリング状に接続した発振器(リングオシレータ)と、トランジスタM1からM6を含む同期信号生成回路と、を有する。

【0061】

リングオシレータは、第1実施形態と同様であり、説明は省略する。

【0062】

遅延要素DL1〜DL4の差動対の共通ノード(テール)は、補助注入トランジスタM1C〜M4Cのドレインにそれぞれ接続される。補助注入トランジスタM1C〜M4Cのソースは接地される。補助注入トランジスタM1Cのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して入力発振信号のRF2+が印加可能に構成されている。補助注入トランジスタM3Cのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して入力発振信号のRF2−が印加可能に構成されている。補助注入トランジスタM2CおよびM4Cのゲートは、抵抗を介して第1バイアス電圧DCbias1が印加されると共に、容量を介して接地されている。

【0063】

補助注入トランジスタM1CとM3Cのドレインの間には、信号注入トランジスタM5Cが接続されている。同様に、補助注入トランジスタM2CとM4Cのドレインの間には、信号注入トランジスタM5Cが接続されている。信号注入トランジスタM5Cのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4+が印加可能に構成されている。信号注入トランジスタM6Cのゲートは、抵抗を介して第2バイアス電圧DCbias2が印加されると共に、容量を介して入力発振信号RF4−が印加可能に構成されている。

【0064】

第4実施形態の分周回路において、入力発振信号RF4+およびRF4−が入力され、RF2+およびRF2−は入力されない場合の動作を説明する。この場合も、第1実施形態と同様に、信号注入トランジスタM5Cは、ゲートに印加されるRF4+に応じてトランスコンダクタンスを変化させる。これに応じて、補助注入トランジスタM2CとM4Cのドレイン間のコンダクタンスが変化すると共に、補助注入トランジスタM2CとM4Cのドレインに、RF4+の高調波を発生する。この高調波は、RF4+の2次高調波成分、すなわちRF4+の2分周成分が多く含まれ、M2Cのドレインの信号とM4Cのドレインの信号は逆相の信号である。したがって、第1実施例で説明したのと同様に、遅延要素DL1およびDL3の差動対のトランジスタのオン・オフ動作が、補助注入トランジスタM1CとM3Cのドレインの信号の影響を受け、リングオシレータは、RF4+およびRF−の周波数4f0を4分周した周波数f0にロックして発振する。

【0065】

以上説明した第1から第4実施形態では、PMOS電流源の遅延要素を使用し、同期信号生成回路のトランジスタをNMOSで実現した例を説明した。しかし、NMOS電流源の遅延要素を使用することも、クロスカップルした電流源を使用することも、PMOSが抵抗を介してダイオード接続されたものを使用することなどが可能である。また、同期信号生成回路のトランジスタをPMOSで実現することも可能である。

【0066】

図12は、PMOS電流源の遅延要素DL1P〜DL4Pを使用してリングオシレータを形成し、同期信号生成回路をPMOSトランジスタM1P〜M6Pで実現した変形例の分周回路を示す図であり、図13は変形例で使用する遅延要素の構成例を示す図である。

【0067】

この変形例は、第1実施形態の分周回路を上記のように変更したのみであり、説明は省略する。

【0068】

さらに、以上説明した第1から第4実施形態および変形例では、遅延要素は差動型であったが、単相信号を入出力するが単相型の遅延要素を使用することも可能である。

【0069】

本発明の分周回路は、PLL回路の一部として使用することが可能である。

【0070】

図14は、本発明の分周回路を使用したPLL回路の構成例を示す図である。

【0071】

図14に示すように、PLL回路は、電圧制御発振器(VCO)21と、VCO21の出力するクロックfoutを分周して分周クロックを出力する分周回路22と、基準クロックfinと分周クロックの位相差および周波数差を検出して制御信号を出力する位相周波数検出回路23と、制御信号に応じてレベル信号を生成するチャージポンプ(CP)24と、レベル信号の低周波数成分を抽出した低周波数信号を出力するローパスフィルタ(LPF)25と、を有し、VCO21は、ローパスフィルタ25の出力する低周波数信号に応じて発振周波数を変化させる。

【0072】

ここで、クロックfoutの周波数が非常に高い場合、例えば10GHz以上の場合、クロックfoutの分周回路をデジタル回路で形成するのは非常に難しい。そこで、クロックfoutをアナログ回路で形成されるプリスケーラで、クロックfoutをある程度の周波数まで分周した後、デジタル回路で形成したデジタル分周回路でさらに分周することが行なわれる。例えば、図14で、分周回路22を、20GHzのクロックfoutを4分周するプリスケーラと、4分周した5GHzの分周クロックをさらに分周するデジタル分周器で構成する。

【0073】

プリスケーラを安定した分周比で動作可能な従来の2分周回路で実現する場合、2分周回路を直列に2段接続することになり、回路規模および消費電力が大きく、ロック範囲も狭くなるという問題がある。8分周するプリスケーラの場合には3個の2分周回路を直列に接続する必要があり、この問題はより顕著になる。

【0074】

これに対して、第1から第4実施形態および変形例で説明した本発明の分周回路を使用してプリスケーラを実現すると、上記の問題を低減できる。さらに、本発明の分周回路は、入力発振信号の入力ノードを変更することにより、分周回路の分周比を、2分周、4分周、さらには8分周に設定でき、広い範囲のクロックfoutに対応可能である。例えば、2GHzから8GHzの自己発振範囲を有する本発明の4分周回路を使用すれば、2GHzから8GHzの範囲のクロックfoutに対応可能な分周回路およびそれを使用したPLL回路が実現できる。

【0075】

以上、本発明の実施形態を説明したが、記載した実施形態は発明を説明するためのもので、当業者には、特許請求の範囲において各種の変形例があり得ることが容易に理解可能である。

【産業上の利用可能性】

【0076】

本発明は、高速の発振信号を分周する分周回路、およびそれを使用する回路に適用可能である。

【符号の説明】

【0077】

10 注入同期型周波数分周回路(ILFD)

11 発振回路

12 同期信号精製回路

21 電圧制御発振器(VCO)

22 分周回路

23 位相・周波数検出回路

24 チャージポンプ

25 ローパスフィルタ(LPF)

DL1,…DL4,DL1A,…DL8A 遅延要素

M1,…M6,M1A,…M14A,M1B,M2B,M1C,…M6C トランジスタ

【特許請求の範囲】

【請求項1】

前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続されたM(2以上の整数)個の遅延要素を有する発振回路と、

入力発振信号から前記遅延要素の状態変化を規制する同期信号を生成し、生成した前記同期信号を前記複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を備え、前記発振回路から前記入力発振信号の分周信号を出力する分周回路であって、

前記Mは偶数であり、

前記遅延要素は、制御端子に入力信号が入力される分周トランジスタを有し、前記分周トランジスタの一方の被制御端子から出力が得られ、前記分周トランジスタの他方の被制御端子が注入ノードであり、

前記同期信号注入回路は、

前記発振回路のM/2個離れた2つの前記遅延要素の前記分周トランジスタの前記注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対と、

前記注入差動対の前記注入ノードとの接続ノードに、前記入力発振信号の差動信号を発生するように前記注入差動対に接続され、制御端子に前記入力発振信号が入力可能である信号注入トランジスタと、を有することを特徴とする分周回路。

【請求項2】

前記遅延要素は、並列に設けられ、一方の被制御端子が前記注入ノードに共通に接続された2個の前記分周トランジスタを有する分周差動対を備え、差動入力信号が前記2個の分周トランジスタの制御端子に入力され、差動出力信号が前記分周トランジスタの前記分周共通ノードと反対側の2つの被制御端子から出力され、

前段の差動出力信号が後段の差動入力信号として入力し、最終段の差動出力信号が初段の差動入力信号として入力する請求項1記載の分周回路。

【請求項3】

前記注入差動対の前記2個の補助注入トランジスタは、前記注入ノードに接続される被制御端子と反対側の被制御端子が注入共通ノードに接続され、

前記信号注入トランジスタは、前記注入共通ノードと電源端子との間に接続される請求項2記載の分周回路。

【請求項4】

前記注入差動対の前記2個の補助注入トランジスタは、前記注入ノードと電源端子との間に接続され、

前記信号注入トランジスタは、前記注入ノード間に接続される請求項2記載の分周回路。

【請求項5】

前記M=4であり、

第1と第2の2つの前記同期信号注入回路を備え、

前記第1の同期信号注入回路の前記2個の補助注入トランジスタは、前記発振回路の1番目と3番目の前記遅延要素の前記注入ノードに接続され、

前記第2の同期信号注入回路の前記2個の補助注入トランジスタは、前記発振回路の2番目と4番目の前記遅延要素の前記注入ノードに接続され、

前記第1の同期信号注入回路の前記信号注入トランジスタの制御端子には、第2DCバイアス電圧でバイアスされた前記入力発振信号が入力可能であり、

前記第2の同期信号注入回路の前記信号注入トランジスタの制御端子には、第2DCバイアス電圧でバイアスされた前記入力発振信号の逆相信号が入力可能である請求項3または4記載の分周回路。

【請求項6】

前記第1の同期信号注入回路の前記2個の補助注入トランジスタの制御端子には、第1DCバイアス電圧でバイアスされた第2入力発振信号の正相信号と逆相信号が入力可能であり、

前記第2の同期信号注入回路の前記2個の補助注入トランジスタの制御端子は、第1DCバイアス電圧でバイアスされる請求項5記載の分周回路。

【請求項7】

前記M=8であり、

8個の前記遅延要素の前記注入ノードに接続される8個の初段注入トランジスタを備え、

前記8個の初段注入トランジスタの4個離れた2個の前記初段注入トランジスタは、前記注入ノードに接続される被制御端子と反対側の被制御端子が初段共通ノードに接続されて4個の初段注入差動対をなし、

第1および第2の2つの前記同期信号注入回路を備え、

前記第1の同期信号注入回路の前記2個の補助注入トランジスタは、1番目と3番目の前記初段注入差動対の前記初段共通ノードに接続され、

前記第2の同期信号注入回路の前記2個の補助注入トランジスタは、2番目と4番目の前記初段注入差動対の前記初段共通ノードに接続され、

前記第1の同期信号注入回路の前記信号注入トランジスタの制御端子には、第3DCバイアス電圧でバイアスされた前記入力発振信号の逆相信号が入力可能であり、

前記第2の同期信号注入回路の前記信号注入トランジスタの制御端子には、第3DCバイアス電圧でバイアスされた前記入力発振信号が入力可能である請求項3または4記載の分周回路。

【請求項8】

前記第1の同期信号注入回路の前記2個の補助注入トランジスタの制御端子には、第2DCバイアス電圧でバイアスされた第2入力発振信号の正相信号と逆相信号が入力可能であり、

前記第2の同期信号注入回路の前記2個の補助注入トランジスタの制御端子は、第2DCバイアス電圧でバイアスされ、

前記8個の初段注入トランジスタの制御端子は、第1DCバイアス電圧でバイアスされる請求項7記載の分周回路。

【請求項9】

電圧制御発振器と、

前記電圧制御発振器の出力するクロックを分周して分周クロックを出力する分周回路と、

基準クロックと前記分周クロックの位相差および周波数差を検出して制御信号を出力する位相周波数検出回路と、

前記制御信号に応じてレベル信号を生成するチャージポンプと、

前記レベル信号の低周波数成分を抽出した低周波数信号を出力するローパスフィルタと、を備え、

前記電圧制御発振器は、前記ローパスフィルタの出力する前記低周波数信号に応じて発振周波数を変化させるPLL回路であって、

前記分周回路は、請求項1から8のいずれか1項記載の分周回路を備えることを特徴とするPLL回路。

【請求項1】

前段の出力信号が後段の入力信号として入力し、最終段の出力信号が初段の入力信号として入力し、初段の入力信号に対して、最終段から初段への入力信号が反転するように接続されたM(2以上の整数)個の遅延要素を有する発振回路と、

入力発振信号から前記遅延要素の状態変化を規制する同期信号を生成し、生成した前記同期信号を前記複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を備え、前記発振回路から前記入力発振信号の分周信号を出力する分周回路であって、

前記Mは偶数であり、

前記遅延要素は、制御端子に入力信号が入力される分周トランジスタを有し、前記分周トランジスタの一方の被制御端子から出力が得られ、前記分周トランジスタの他方の被制御端子が注入ノードであり、

前記同期信号注入回路は、

前記発振回路のM/2個離れた2つの前記遅延要素の前記分周トランジスタの前記注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対と、

前記注入差動対の前記注入ノードとの接続ノードに、前記入力発振信号の差動信号を発生するように前記注入差動対に接続され、制御端子に前記入力発振信号が入力可能である信号注入トランジスタと、を有することを特徴とする分周回路。

【請求項2】

前記遅延要素は、並列に設けられ、一方の被制御端子が前記注入ノードに共通に接続された2個の前記分周トランジスタを有する分周差動対を備え、差動入力信号が前記2個の分周トランジスタの制御端子に入力され、差動出力信号が前記分周トランジスタの前記分周共通ノードと反対側の2つの被制御端子から出力され、

前段の差動出力信号が後段の差動入力信号として入力し、最終段の差動出力信号が初段の差動入力信号として入力する請求項1記載の分周回路。

【請求項3】

前記注入差動対の前記2個の補助注入トランジスタは、前記注入ノードに接続される被制御端子と反対側の被制御端子が注入共通ノードに接続され、

前記信号注入トランジスタは、前記注入共通ノードと電源端子との間に接続される請求項2記載の分周回路。

【請求項4】

前記注入差動対の前記2個の補助注入トランジスタは、前記注入ノードと電源端子との間に接続され、

前記信号注入トランジスタは、前記注入ノード間に接続される請求項2記載の分周回路。

【請求項5】

前記M=4であり、

第1と第2の2つの前記同期信号注入回路を備え、

前記第1の同期信号注入回路の前記2個の補助注入トランジスタは、前記発振回路の1番目と3番目の前記遅延要素の前記注入ノードに接続され、

前記第2の同期信号注入回路の前記2個の補助注入トランジスタは、前記発振回路の2番目と4番目の前記遅延要素の前記注入ノードに接続され、

前記第1の同期信号注入回路の前記信号注入トランジスタの制御端子には、第2DCバイアス電圧でバイアスされた前記入力発振信号が入力可能であり、

前記第2の同期信号注入回路の前記信号注入トランジスタの制御端子には、第2DCバイアス電圧でバイアスされた前記入力発振信号の逆相信号が入力可能である請求項3または4記載の分周回路。

【請求項6】

前記第1の同期信号注入回路の前記2個の補助注入トランジスタの制御端子には、第1DCバイアス電圧でバイアスされた第2入力発振信号の正相信号と逆相信号が入力可能であり、

前記第2の同期信号注入回路の前記2個の補助注入トランジスタの制御端子は、第1DCバイアス電圧でバイアスされる請求項5記載の分周回路。

【請求項7】

前記M=8であり、

8個の前記遅延要素の前記注入ノードに接続される8個の初段注入トランジスタを備え、

前記8個の初段注入トランジスタの4個離れた2個の前記初段注入トランジスタは、前記注入ノードに接続される被制御端子と反対側の被制御端子が初段共通ノードに接続されて4個の初段注入差動対をなし、

第1および第2の2つの前記同期信号注入回路を備え、

前記第1の同期信号注入回路の前記2個の補助注入トランジスタは、1番目と3番目の前記初段注入差動対の前記初段共通ノードに接続され、

前記第2の同期信号注入回路の前記2個の補助注入トランジスタは、2番目と4番目の前記初段注入差動対の前記初段共通ノードに接続され、

前記第1の同期信号注入回路の前記信号注入トランジスタの制御端子には、第3DCバイアス電圧でバイアスされた前記入力発振信号の逆相信号が入力可能であり、

前記第2の同期信号注入回路の前記信号注入トランジスタの制御端子には、第3DCバイアス電圧でバイアスされた前記入力発振信号が入力可能である請求項3または4記載の分周回路。

【請求項8】

前記第1の同期信号注入回路の前記2個の補助注入トランジスタの制御端子には、第2DCバイアス電圧でバイアスされた第2入力発振信号の正相信号と逆相信号が入力可能であり、

前記第2の同期信号注入回路の前記2個の補助注入トランジスタの制御端子は、第2DCバイアス電圧でバイアスされ、

前記8個の初段注入トランジスタの制御端子は、第1DCバイアス電圧でバイアスされる請求項7記載の分周回路。

【請求項9】

電圧制御発振器と、

前記電圧制御発振器の出力するクロックを分周して分周クロックを出力する分周回路と、

基準クロックと前記分周クロックの位相差および周波数差を検出して制御信号を出力する位相周波数検出回路と、

前記制御信号に応じてレベル信号を生成するチャージポンプと、

前記レベル信号の低周波数成分を抽出した低周波数信号を出力するローパスフィルタと、を備え、

前記電圧制御発振器は、前記ローパスフィルタの出力する前記低周波数信号に応じて発振周波数を変化させるPLL回路であって、

前記分周回路は、請求項1から8のいずれか1項記載の分周回路を備えることを特徴とするPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−106062(P2013−106062A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−246362(P2011−246362)

【出願日】平成23年11月10日(2011.11.10)

【出願人】(396023993)株式会社半導体理工学研究センター (150)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月10日(2011.11.10)

【出願人】(396023993)株式会社半導体理工学研究センター (150)

【Fターム(参考)】

[ Back to top ]