列変換回路、および、列変換方法

【課題】論理回路の増大を抑制しながら列変換モードを拡張可能な列変換回路を提供すること。

【解決手段】変換後の列数Nを設定する列変換モード設定部11と、M個のメモリ12と、各メモリ12におけるライトアドレスを生成するとともに次のM列入力データの書込位置を示すようライトアドレスを更新するライトアドレス生成部13と、M列入力データの各ビットを、各メモリ12のライトアドレスの位置に書き込むライトデータ制御部14と、M個のメモリ12のうちN個を示す選択信号を生成するとともに次の他のN個を示すよう選択信号を更新する選択信号生成部15と、選択信号が示すN個の各メモリ12におけるリードアドレスを生成するリードアドレス生成部16と、リードアドレス生成部16を制御するリードアドレス更新制御部17と、選択信号およびリードアドレスに従いM個のメモリ12からN列データを読み出すデータ選択出力部18とを備える。

【解決手段】変換後の列数Nを設定する列変換モード設定部11と、M個のメモリ12と、各メモリ12におけるライトアドレスを生成するとともに次のM列入力データの書込位置を示すようライトアドレスを更新するライトアドレス生成部13と、M列入力データの各ビットを、各メモリ12のライトアドレスの位置に書き込むライトデータ制御部14と、M個のメモリ12のうちN個を示す選択信号を生成するとともに次の他のN個を示すよう選択信号を更新する選択信号生成部15と、選択信号が示すN個の各メモリ12におけるリードアドレスを生成するリードアドレス生成部16と、リードアドレス生成部16を制御するリードアドレス更新制御部17と、選択信号およびリードアドレスに従いM個のメモリ12からN列データを読み出すデータ選択出力部18とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ディジタル信号の伝送において信号列数の変換を行う列変換回路に関する。

【背景技術】

【0002】

ディジタル信号の伝送において、信号列数の変換を行う列変換回路が知られている。このような列変換回路は、例えば、多値変復調通信方式によるディジタル信号の伝送において用いられる。

【0003】

このような列変換回路の一例が、特許文献1に記載されている。特許文献1に記載された列変換回路は、第1のクロック信号により入力されるM列の入力データを、M/N倍の周波数の第2のクロック信号によりN列に変換して出力する。この列変換回路は、第1および第2のクロック信号のうち高周波数側のクロック信号を発生する発振回路と、この発振回路からのクロック信号をMとNの比で分周して低周波数側のクロック信号とする分周回路と、M列をN列に変換する回路とを備えている。

【0004】

また、このような列変換回路の他の一例を図24に示す。

【0005】

図24において、列変換回路90は、16列入力データを2列、4列、または5列に変換する回路である。この列変換回路90は、ライトデータ制御回路91と、5個のライトバッファ(16bit FF)920〜924(以降、総称してライトバッファ92ともいう)と、リードデータ制御回路93と、データセレクト回路94とを含む。1つのライトバッファ92は、16ビットのデータを格納可能なバッファ(フリップフロップ回路)である。図24に示すQ(i)は、各ライトバッファ92に保持される各ビットのデータを表している。また、図24に示すComb(i)は、各Q(i)から読み出されるデータを表している。また、この列変換回路90では、2列、4列、または5列のいずれの列数に変換するかを示す列変換モード設定信号が設定される。

【0006】

ライトデータ制御回路91は、列変換モードに応じて、16列入力データの書き込み先のライトバッファ92の選択およびその書き込みタイミングを制御する。具体的には、ライトデータ制御回路91は、列変換モードに応じて、ライトEN(i)信号を所定のタイミングで有効(High:以降、‘H’とも記載する)にする。有効となっているライトEN(i)に対応したライトバッファ92iには、16列入力データが格納される。以降、16列入力データを、“ライトデータ[15:0]”とも記載する。また、以降において、データの名称の後に記載する“[m−1:0]”は、そのデータがmビットであることを表す。また、そのデータの名称の後に“[i:j]”と記載した場合は、そのmビットのデータのうち、最下位を0ビット目と数えて、下位からiビット目からjビット目までのデータを表しているものとする。

【0007】

例えば、2列変換モードであれば、ライトデータ制御回路91は、ライトEN(0)およびライトEN(1)を、所定のタイミングで交互に有効にする。これにより、2列変換モードであれば、ライトバッファ920、921に、ライトデータ[15:0]が順次格納される。

【0008】

リードデータ制御回路93は、列変換モードに応じて、ライトバッファ92に格納されたデータの読み出しタイミングを制御する。具体的には、リードデータ制御回路93は、リードカウントRDENCNT(0から列変換モードに応じた上限値までをカウント)を生成する。例えば、2列変換モードであれば、リードデータ制御回路93は、0〜15までのリードカウントを生成する。

【0009】

データセレクト回路94は、リードデータ制御回路93の制御の基に、ライトバッファ92に格納されたデータを、列変換モードに応じた列数ずつ選択して出力する。具体的には、データセレクト回路94は、リードカウントにしたがって、ライトバッファ92iに格納されたデータを、列変換モードに対応したN列(2列、4列、または、5列)に並び替える。例えば、2列変換モードであれば、データセレクト回路94は、ライトバッファ920のQ(15)〜Q(0)およびライトバッファ921のQ(31)〜Q(16)の計32ビットから2列ずつを、リードカウント0〜15にしたがって順次選択して出力する。

【0010】

このような図24の列変換回路90の動作について、図面を参照して説明する。

【0011】

まず、2列変換モードにおけるライト側タイミングチャートを図25に示す。ライト側は、ライトCLKにしたがって動作する。

【0012】

ライトデータ先頭パルスは、16列入力データの入力開始時に有効‘H’となる信号である。

【0013】

ライトデータイネーブル信号は、ライトデータ[15:0]のライトタイミングを制御する信号である。ライトデータイネーブル信号は、列変換モード設定信号に応じた所定のタイミングで有効‘H’となる。例えば、2列変換モードの場合、16CLK毎に1CLKの期間有効‘H’となる。

【0014】

ライトデータ[15:0]は、16列入力データである。図示の“1000(hex)”、“1001(hex)”は、16列入力データの一例を16進表記したものである。

【0015】

ライトアドレスカウンタは、ライトデータ制御回路91において、0から最大カウント値までを繰り返しカウントするカウンタである。この最大カウント値は、列変換モードに応じて設定される。図25では、2列変換モードなので、ライトアドレスカウンタの最大カウント値として1がセットされている。ライトアドレスカウンタは、ライトデータ先頭パルスおよびライトデータイネーブル信号が共に有効‘H’時に、ライトCLKに同期して0に初期化される。そして、ライトデータイネーブル信号が有効となる度に、ライトCLKに同期して1へのカウントアップおよび0への初期化を繰り返す。

【0016】

ライトEN(i)信号は、ライトアドレスカウンタがiに変化すると、ライトCLKに同期して‘H’となる。

【0017】

ライトデータ[15:0]は、ライトEN(i)が‘H’となったタイミングで、ライトCLKの立ち上がりエッジでライトバッファ92iに格納される。

【0018】

このようにして、2列変換モードでは、ライトデータ[15:0]は、ライトバッファ920およびライトバッファ921に順次格納される。

【0019】

次に、2列変換モードにおけるリード側タイミングチャートを図26に示す。リード側は、リードCLKにしたがって動作する。リードCLKは、ライトCLKの2倍の周波数で動作するクロック信号である。

【0020】

リードデータ先頭パルスは、リード動作の開始を示している。リードデータ先頭パルスは、ライトデータ先頭パルス‘H’およびライトEN(0)‘H’の論理積をライトCLKの立ち上がりエッジで1回サンプリングした信号を、リードCLKに乗せ換えて生成される。

【0021】

リードCLKカウンタは、リードデータ先頭パルスが有効時に、リードCLKに同期して0に初期化される。また、リードCLKカウンタは、リードCLKに同期して、0〜3までを繰り返しカウントする。

【0022】

リードアドレスカウンタRDENCNTは、リードデータ先頭パルスが有効時に、リードCLKに同期して0に初期化される。また、リードアドレスカウンタは、リードCLKカウンタが3となった時、リードCLKに同期して、+1のカウントアップを実行する。また、2列変換モードにおいて、リードアドレスカウンタRDENCNTの最大カウント値は15にセットされる。つまり、リードアドレスカウンタは、0〜15までを繰り返しカウントする。

【0023】

このリードアドレスカウンタRDENCNTは、データセレクト回路94において選択するデータを示している。例えば、データセレクト回路94は、リードアドレスカウンタが0の時は、ライトバッファ920のComb(15−14)を選択し、リードアドレスカウンタが1の時は、Comb(13−12)を選択する。同様に、データセレクト回路94は、リードアドレスカウンタが7までは、ライトバッファ920に格納されたデータの2つを選択する。また、データセレクト回路94は、リードアドレスカウンタが8の時は、ライトバッファ921のComb(31−30)を選択し、リードアドレスカウンタが9の時は、Comb(29−28)を選択する。同様に、データセレクト回路94は、リードアドレスカウンタが15までは、ライトバッファ921に格納されたデータの2つを選択する。そして、データセレクト回路94は、リードデータ先頭パルスに基づいて生成される列変換後先頭パルスが有効となると、選択した2列のデータを順次出力する。

【0024】

次に、このような図24の列変換回路90の4列変換モードにおける動作について、タイミングチャート図27〜図28を用いて説明する。

【0025】

4列変換モードでも、2列変換モードと同様に、2つのライトバッファ920および921が用いられる。したがって、図27において、4列変換モードにおけるライト側の動作は、2列変換モードにおける動作とほぼ同様である。ただし、4列変換モードでは、ライトデータイネーブル信号は、8CLK毎に1CLK期間有効‘H’となる。

【0026】

次に、4列変換モードにおけるリード側タイミングチャートを図28に示す。

【0027】

リードアドレスカウンタRDENCNTの最大カウント値は、4列変換モードにおいて7にセットされる。つまり、リードアドレスカウンタRDENCNTは、リードデータ先頭パルスが有効時にリードCLKに同期して0に初期化された後、0〜7までを繰り返しカウントする。リードアドレスカウンタのカウントアップは、2列変換モードと同様、リードCLKカウンタが3となった時に実行される。

【0028】

4列変換モードにおいて、データセレクト回路94は、リードアドレスカウンタが0の時は、ライトバッファ920のComb(15−12)を選択し、リードアドレスカウンタが1の時は、Comb(11−8)を選択する。同様に、データセレクト回路94は、リードアドレスカウンタが3までは、ライトバッファ920に格納されたデータの4つを選択する。また、データセレクト回路94は、リードアドレスカウンタが4の時は、ライトバッファ921のComb(31−28)を選択し、リードアドレスカウンタが5の時は、Comb(27−24)を選択する。同様に、データセレクト回路94は、リードアドレスカウンタが7までは、ライトバッファ921に格納されたデータの4つを選択する。そして、データセレクト回路94は、リードデータ先頭パルスに基づいて生成される列変換後先頭パルスが有効となると、選択した4列の出力データを順次出力する。

【0029】

同様に、図24に示した列変換回路90は、5列変換モードにおいては、ライトバッファ920〜924を用いる。すなわち、5列変換モードにおいて、ライトアドレスカウンタの最大カウント値は、4にセットされる。そして、ライトデータ制御回路91は、ライトEN(0)〜ライトEN(4)のうち1つずつを順次有効‘H’に切り替えていく。そして、ライトEN(0)〜ライトEN(4)にしたがい、ライトバッファ920〜924にライトデータ[15:0]が順次格納される。

【0030】

また、5列変換モードにおいて、リード側では、リードアドレスカウンタの最大カウント値は15にセットされる。つまり、リードアドレスカウンタは、0〜15までを繰り返しカウントする。そして、データセレクト回路94は、リードアドレスカウンタの値にしたがって、ライトバッファ920のComb(15−0)〜ライトバッファ924のComb(79−64)までの計80ビットから5列ずつを、リードカウント0〜15にしたがって順次選択して出力する。

【0031】

このように、図24に示した列変換回路90は、変換後の列数(列変換モード)に応じた個数のライトバッファ92を必要とする。これは、16ビットの入力データが格納されたライトバッファ92から、変換後の列数であるNビットずつ選択出力していくためには、16ビット×ライトバッファの個数n=M×nビットが、Nで割り切れるだけの個数nのライトバッファを必要とするからである。ただし、図24に示した列変換回路90は、このように算出された個数nが1となった場合であっても、最低2つのライトバッファ92を必要としている。これは、格納されたデータが読み出されないうちに次のデータで上書きされることを防ぐためである。

【先行技術文献】

【特許文献】

【0032】

【特許文献1】特開平5-218999号公報

【発明の概要】

【発明が解決しようとする課題】

【0033】

ここで、図24に示した列変換回路90において、さらに他の列変換モード(例えば、6〜16列変換)に機能拡張することを考える。列変換回路90は、列変換モードの拡張のためには、列変換モードに応じた個数のライトバッファ92を必要とする。

【0034】

例えば、16列入力データに対して、6列変換機能を実現させるには、3つのライトバッファ92が必要となる。また、16列入力データに対して、7列変換機能を実現させるには、7つのライトバッファ92が必要となる。また、16列入力データに対して、8列変換機能を実現させるには、2つのライトバッファ92が必要となる。また、16列入力データに対して、9列変換モードを実現させるには、9つのライトバッファ92が必要となる。また、16列入力データに対して、10列変換モードを実現させるには、5つのライトバッファ92が必要となる。

【0035】

このように、図24に示した列変換回路90では、16ビット入力データに対して変換可能な列数(列変換モード)を拡張するためには、ライト側における論理回路の増大が問題となる。

【0036】

また、図24に示した列変換回路90において、変換可能な列数の増加に伴い、データセレクト回路94におけるデータ選択の論理段数が膨大に膨れ上がる。したがって、図24に示した列変換回路90では、変換可能な列数の拡張には、リード側における論理回路の増大も問題となる。

【0037】

このように、図24の列変換回路90では、変換可能な列数の拡張には、論理回路の多大な増加が必要となるという課題があった。

【0038】

また、特許文献1に記載された列変換回路において、多様な列数Nへ変換可能な列変換モードを搭載することを考える。例えば、特許文献1の図1には、4列の入力データを1列に変換する回路が図示されている。この列変換回路において、変換可能な列数を拡張するためには、メモリに入力されるバス幅の増加、分周回路の増設、列変換回路の複雑化が必要となる。したがって、特許文献1においても、多様な列数へ変換可能な列変換モードを拡張する際の、論理回路の増大を抑制することは難しかった。

【0039】

本発明は、上述の課題を解決するためになされたもので、変換後の列数を設定する列変換モードを搭載した列変換回路において、論理回路の増大を抑えながら変換後の列数を容易に拡張可能な列変換回路を提供することを目的とする。

【課題を解決するための手段】

【0040】

本発明の列変換回路は、M(Mは正の整数)列の入力データをN(NはM>Nを満たす正の整数)列に変換する列変換回路であって、変換後の列数Nを表す列変換モードを設定する列変換モード設定部と、少なくともM個の所定サイズのメモリと、前記M個の各メモリにおけるデータ書き込み位置を示すライトアドレスを生成するとともに、前記M個の各メモリにおいて該ライトアドレスの示す位置に前記M列の入力データの各ビットが格納されると、次のM列の入力データのデータ書き込み位置を示すよう前記ライトアドレスを更新するライトアドレス生成部と、前記M列の入力データの各ビットを、前記M個の各メモリの前記ライトアドレスの示す位置に書き込むよう制御するライトデータ制御部と、前記M個のメモリのうち選択対象となるN個を示す選択信号を前記列変換モードに応じて生成するとともに、該選択信号が示すN個のメモリからデータが出力されると、次の他のN個を示すよう、前記列変換モードに応じて前記選択信号を更新する選択信号生成部と、前記選択信号が示すN個の前記各メモリにおけるデータ読み出し位置を示すリードアドレスを生成するリードアドレス生成部と、前記選択信号の更新に伴い、前記リードアドレス生成部を前記列変換モードに応じて制御するリードアドレス更新制御部と、前記M個のメモリから、前記選択信号および前記リードアドレスにしたがってN列のデータを読み出して出力するデータ選択出力部と、を備える。

【0041】

また、本発明の列変換方法は、少なくともM(Mは正の整数)個の所定サイズのメモリを用いて、変換後の列数N(NはM>Nを満たす正の整数)を表す列変換モードを設定し、前記M個の各メモリにおけるデータ書き込み位置を示すライトアドレスを生成し、前記M列の入力データの各ビットを、前記M個の各メモリの前記ライトアドレスの示す位置に書き込み、前記M個の各メモリにおいて次のM列の入力データのデータ書き込み位置を示すよう前記ライトアドレスを更新していきながら、以降のM列の入力データの書き込みを順次行い、前記M個のメモリのうち選択対象となるN個を示す選択信号を前記列変換モードに応じて生成し、前記選択信号が示すN個の前記各メモリにおけるデータ読み出し位置を示すリードアドレスを生成し、前記M個のメモリから、前記選択信号および前記リードアドレスにしたがってN列のデータを読み出して出力し、前記M個のメモリのうち次の選択対象となる他のN個を示すよう、前記列変換モードに応じて前記選択信号を更新し、更新された選択信号が示すN個の前記各メモリにおけるデータ読み出し位置を示すよう、前記列変換モードに応じて前記リードアドレスを生成し、選択信号が更新される毎に、該選択信号、および、該選択信号に応じて生成されたリードアドレスにしたがって、以降のN列のデータの出力を行う。

【発明の効果】

【0042】

変換後の列数を設定する列変換モードを搭載した列変換回路において、論理回路の増大を抑えながら変換後の列数を容易に拡張可能な列変換回路を提供することができる。

【図面の簡単な説明】

【0043】

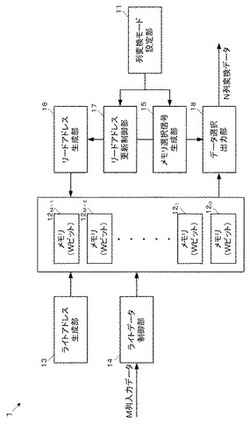

【図1】本発明の第1の実施の形態としての列変換回路の構成を示すブロック図である。

【図2】本発明の第2の実施の形態としての列変換回路の構成を示す図である。

【図3】本発明の第2の実施の形態としての列変換回路に入力される16列入力データを模式的に説明する図である。

【図4】本発明の第2の実施の形態におけるメモリのデータ格納領域を模式的に説明する図である。

【図5】本発明の第2の実施の形態におけるリードアドレス生成回路の構成を示す図である。

【図6】本発明の第2の実施の形態におけるリードイネーブル生成回路およびリードデータセレクト生成回路の構成を示す図である。

【図7】本発明の第2の実施の形態としての列変換回路の2列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図8】本発明の第2の実施の形態としての列変換回路の4列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図9】本発明の第2の実施の形態としての列変換回路の5列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図10】本発明の第2の実施の形態としての列変換回路の6列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図11】本発明の第2の実施の形態としての列変換回路の7列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図12】本発明の第2の実施の形態としての列変換回路によって16列入力データの各ビットが16個のメモリに格納されることを説明する模式図である。

【図13】本発明の第2の実施の形態としての列変換回路の2列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図14】本発明の第2の実施の形態としての列変換回路が出力する2列変換データを模式的に説明する図である。

【図15】本発明の第2の実施の形態としての列変換回路の4列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図16】本発明の第2の実施の形態としての列変換回路が出力する4列変換データを模式的に説明する図である。

【図17】本発明の第2の実施の形態としての列変換回路の5列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図18】本発明の第2の実施の形態としての列変換回路が出力する5列変換データを模式的に説明する図である。

【図19】本発明の第2の実施の形態としての列変換回路の6列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図20】本発明の第2の実施の形態としての列変換回路が出力する6列変換データを模式的に説明する図である。

【図21】本発明の第2の実施の形態としての列変換回路の7列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図22】本発明の第2の実施の形態としての列変換回路が出力する7列変換データを模式的に説明する図である。

【図23】本発明の第2の実施の形態としての列変換回路に8列変換モード、9列変換モード、および10列変換モードを拡張する場合の回路構成を示す図である。

【図24】関連技術の列変換回路の構成を示す図である。

【図25】関連技術の列変換回路の2列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図26】関連技術の列変換回路の2列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図27】関連技術の列変換回路の4列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図28】関連技術の列変換回路の4列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【発明を実施するための形態】

【0044】

以下、本発明の実施の形態について、図面を参照して詳細に説明する。

【0045】

(第1の実施の形態)

本発明の第1の実施の形態としての列変換回路1のブロック構成を図1に示す。

【0046】

図1において、列変換回路1は、列変換モード設定部11と、M個のメモリ120〜12Mー1(以下、総称してメモリ12ともいう)と、ライトアドレス生成部13と、ライトデータ制御部14と、選択信号生成部15と、リードアドレス生成部16と、リードアドレス更新制御部17と、データ選択出力部18とを備える。列変換回路1は、入力されるM列のデータを、N列に変換して出力する回路である。列変換回路1において、入力データの列数Mはあらかじめ定められている。また、出力列数Nは、あらかじめ定められた1つ以上の列数から選択可能となっている。なお、本実施の形態において、MおよびNは正の整数であり、M>Nである。

【0047】

列変換モード設定部11は、変換後の列数Nを表す列変換モードを設定する。つまり、列変換回路1は、M列の入力データを、列変換モード設定部11において設定された列変換モードが示すN列に変換する。

【0048】

各メモリ12は、所定サイズWを有している。例えば、各メモリ12は、256ビットのRAM(Random Access Memory)によって構成されていてもよい。M個の各メモリ12には、M列の入力データの各ビットが格納される。つまり、M個のメモリ12は、M列の入力データを、W個まで格納することが可能である。

【0049】

ライトアドレス生成部13は、M個の各メモリ12において共通のデータ書き込み位置を示すライトアドレスを生成する。もし、各メモリ12のサイズが256ビットであれば、ライトアドレスは、1ビット目〜256ビット目までのいずれかを示す情報である。M個の各メモリ12において、ライトアドレス生成部13が生成したライトアドレスが示す位置には、M列の入力データの各ビットが格納される。

【0050】

また、ライトアドレス生成部13は、M個の各メモリ12のライトアドレスが示す位置にM列の入力データの各ビットが格納されると、次のM列の入力データの書き込み位置を示すようライトアドレスを更新する。例えば、ライトアドレスがiビット目を示しているとき、次のライトアドレスは、i+1ビット目を示すものであってもよい。

【0051】

ライトデータ制御部14は、M列の入力データの各ビットを、各メモリ12のライトアドレスの示す位置に書き込む。例えば、ライトアドレスが1ビット目を示している場合、ライトデータ制御部14は、M個の各メモリ12の1ビット目(合計Mビット)に、M列の入力データを書き込む。

【0052】

選択信号生成部15は、M個のメモリ12のうちN個を示す選択信号を生成する。このNは、列変換モード設定部11において設定された列変換モードが示す数値である。つまり、選択信号生成部15は、列変換モード設定部11の設定内容に応じて動作する。

【0053】

また、選択信号生成部15は、選択信号が示すN個のメモリ12からデータが出力されると、次の他のN個を示すよう選択信号を更新する。例えば、Mが16でNが2である場合、選択信号生成部15が、ある時点でメモリ1215〜1214を示す選択信号を生成していたとする。そして、このメモリ1215〜1214からデータが出力されると、選択信号生成部15は、次のメモリ1213〜1212を示す選択信号を生成する。また、選択信号生成部15は、全てのメモリ12を順次示す選択信号を生成した後は、再び最初に選択したメモリ12からを順次示す選択信号を生成していく。例えば、Mが16でNが4である場合、選択信号生成部15は、メモリ1215〜1212、メモリ1211〜128、メモリ127〜124、メモリ123〜120をそれぞれ示すよう、選択信号を順次更新した後、再びメモリ1215〜1212から順に示すよう、選択信号を更新していく。また、Mが16でNが5である場合、選択信号生成部15は、メモリ1215〜1211、メモリ1210〜126、メモリ125〜121をそれぞれ示すよう、選択信号を順次更新した後、メモリ120およびメモリ1215〜1212、メモリ1211〜127の順に示すよう、選択信号を更新していく。

【0054】

リードアドレス生成部16は、選択信号が示すN個の各メモリ12におけるリードアドレスを生成する。もし、各メモリ12のサイズが256ビットであれば、リードアドレスは、1ビット目〜256ビット目までのいずれかを示す情報である。このとき、リードアドレス生成部16は、選択信号が示すN個のメモリ12のうち、既に一旦リードアドレスを生成済みのメモリ12については、前回生成したリードアドレスの位置を次の位置に更新するようにする。例えば、前回のリードアドレスがiビット目を示しているとき、次のリードアドレスは、i+1ビット目であってもよい。

【0055】

リードアドレス更新制御部17は、リードアドレス生成部16を、列変換モードに応じて制御する。つまり、リードアドレス更新制御部17は、リードアドレス生成部16に対して、変換後の列数Nに応じて次にいずれのN個のメモリ12におけるリードアドレスを更新すればよいかを通知する。

【0056】

データ選択出力部18は、選択信号およびリードアドレスに基づいて、M個のメモリ12からN列のデータを読み出して出力する。つまり、データ選択出力部18は、M個のメモリ12のうち選択信号が示すN個のメモリ12において、各リードアドレスが示す各位置の計Nビットを選択出力する。

【0057】

以上のように構成された列変換回路1の動作について説明する。なお、列変換モード設定部11には、変換後の列数Nを表す列変換モードがあらかじめ設定されているものとする。

【0058】

まず、ライト側の動作について説明する。

【0059】

M列の入力データが列変換回路1に入力されると、列変換回路1はライト動作を開始する。

【0060】

ここでは、まず、ライトアドレス生成部13は、M個の各メモリ12におけるライトアドレスを生成する。ここで、最初に生成されるライトアドレスは、例えば、M個の各メモリ12における1ビット目を示すものであってもよい。

【0061】

次に、ライトデータ制御部14は、1つ目のM列の入力データの各ビットを、M個の各メモリ12のライトアドレスが示す位置に書き込む。

【0062】

次に、ライトアドレス生成部13は、M個の各メモリ12における次のデータ書き込み位置を示すようライトアドレスを更新する。ここで、更新されるライトアドレスは、例えば、前回の1ビット目に1を加算した2ビット目を示すものであってもよい。

【0063】

次に、ライトデータ制御部14は、2つ目のM列の入力データを、M個の各メモリ12のライトアドレスが示す位置に書き込む。

【0064】

このように、ライトアドレス生成部13により更新されるライトアドレスを用いて、ライトデータ制御部14は、M列の入力データをM個のメモリ12に書き込んでいく。

【0065】

次に、リード側の動作について説明する。

【0066】

1つ目のM列の入力データがM個のメモリ12に書き込まれた後、列変換回路1は、任意の時点からリード動作を開始する。

【0067】

ここでは、まず、選択信号生成部15は、M個のメモリ12のうち選択対象となるN個を示す選択信号を、列変換モードに応じて生成する。例えば、選択信号生成部15は、Mが16でNが2であれば、メモリ1215およびメモリ1214を示す選択信号を生成してもよい。

【0068】

次に、リードアドレス生成部16は、生成された選択信号が示すN個の各メモリ12におけるリードアドレスを生成する。例えば、リードアドレス生成部16は、メモリ1215およびメモリ1214の各1ビット目を示すリードアドレスを生成する。

【0069】

次に、データ選択出力部18は、M個のメモリ12から、選択信号およびリードアドレスにしたがって、N列のデータを読み出し、1つ目のN列変換データとして出力する。例えば、選択信号がメモリ1215およびメモリ1214を示しており、これらの各メモリにおけるリードアドレスが1ビット目を示している場合、データ選択出力部18は、メモリ1215およびメモリ1214の各1ビット目に格納されている合計2ビットのデータを、1つ目の2列変換データとして出力する。

【0070】

次に、選択信号生成部15は、M個のメモリ12のうち次の選択対象となる他のN個を示すよう、列変換モードに応じて選択信号を更新する。例えば、選択信号生成部15は、メモリ1213およびメモリ1212を示すよう選択信号を更新してもよい。

【0071】

次に、リードアドレス更新制御部17は、更新された選択信号が示すN個の各メモリ12におけるリードアドレスを生成するよう、リードアドレス生成部16に通知する。例えば、リードアドレス更新制御部17は、メモリ1213およびメモリ1212の各リードアドレスを生成するよう、リードアドレス生成部16に通知する。

【0072】

そして、リードアドレス生成部16は、リードアドレス更新制御部17の制御にしたがって、リードアドレスを生成する。例えば、リードアドレス生成部16は、メモリ1213およびメモリ1212の各1ビット目を示すリードアドレスを生成する。

【0073】

次に、データ選択出力部18は、M個のメモリ12から、選択信号およびリードアドレスにしたがって、N列のデータを読み出し、2つ目のN列変換データとして出力する。例えば、選択信号がメモリ1213およびメモリ1212を示しており、これらの各メモリにおけるリードアドレスが1ビット目を示している場合、データ選択出力部18は、メモリ1213およびメモリ1212の各1ビット目に格納されている合計2ビットのデータを、2つ目の2列変換データとして出力する。

【0074】

このようなリード動作を繰り返すことにより、列変換回路1は、1つ目のM列の入力データのMビットをN列変換して出力する。例えば、Mが16でNが2であれば、列変換回路1は、8つ目まで2列変換データを出力すると、1つ目の16列入力データの2列変換処理を終えたことになる。

【0075】

次に、選択信号生成部15は、M個のメモリ12のうち次の選択対象となるN個を示すよう、列変換モードに応じて選択信号を更新する。ここで、選択信号生成部15は、M個のメモリ12の全てを順次示す選択信号を生成済みなので、再度、最初のN個を示すよう選択信号を更新する。例えば、Mが16でNが2の場合について説明する。このとき、既にメモリ1215からメモリ120までの16個を順次示す選択信号を生成済みなので、選択信号生成部15は、再度メモリ1215およびメモリ1214を示すよう選択信号を更新する。

【0076】

次に、リードアドレス更新制御部17は、更新された選択信号が示すN個の各メモリ12におけるリードアドレスを更新するよう、リードアドレス生成部16に通知する。例えば、リードアドレス更新制御部17は、メモリ1215およびメモリ1214におけるリードアドレスを生成するよう、リードアドレス生成部16に通知する。

【0077】

そして、リードアドレス生成部16は、リードアドレス更新制御部17の制御にしたがって、リードアドレスを更新する。例えば、リードアドレス更新制御部17からメモリ1215およびメモリ1214のリードアドレス生成を通知された場合について説明する。この場合、リードアドレス生成部16は、既にこれらの各メモリについて1ビット目を示すリードアドレスを生成しているので、これらに1を加算して2ビット目を示すよう各リードアドレスを更新する。

【0078】

次に、データ選択出力部18は、M個のメモリ12から、選択信号およびリードアドレスにしたがって、N列のデータを読み出し、N列変換データとして出力する。例えば、選択信号がメモリ1215およびメモリ1214を示し、これらの各メモリにおけるリードアドレスが2ビット目を示している場合、データ選択出力部18は、メモリ1215およびメモリ1214の各2ビット目に格納されている合計2ビットのデータを、9つ目の2列変換データとして出力する。

【0079】

列変換回路1は、このようなリード動作を繰り返す。

【0080】

なお、上記動作の説明では、MがNで割り切れる(M=16、N=2)場合を例として説明を行ったが、これ以外の場合も、列変換回路1は同様に動作することにより列変換処理を行う。

【0081】

例えば、16列変換データを5列に変換する場合(M=16、N=5)の動作について説明する。この場合も、列変換回路1のライト側の動作は、上述の動作と同様である。

【0082】

また、この場合、リード動作において、選択信号生成部15は、メモリ12を5つずつ示すよう選択信号を更新していく。例えば、選択信号生成部15は、メモリ1215〜メモリ1211の5つ、メモリ1210〜メモリ126の5つ、メモリ125〜メモリ121の5つ、メモリ120およびメモリ1215〜メモリ1212の5つ、といった順に選択信号を更新していけばよい。

【0083】

そして、リードアドレス更新制御部17は、メモリ1215〜メモリ1211の5つ、メモリ1210〜メモリ126の5つ、メモリ125〜メモリ121の5つ、メモリ120およびメモリ1215〜メモリ1212の5つ、といった順に、リードアドレスを生成するよう、リードアドレス生成部16に通知していけばよい。ここで、リードアドレス生成部16は、メモリ120およびメモリ1215〜メモリ1212の5つにおけるリードアドレスを更新するよう通知された場合、メモリ1215については、1ビット目を示すリードアドレスを生成し、メモリ120〜メモリ123については、前回の1ビット目を更新して2ビット目を示すリードアドレスを生成するようにすればよい。

【0084】

そして、このとき、データ選択出力部18は、メモリ120の1ビット目およびメモリ1215〜メモリ1212の2ビット目の合計5ビットを、4つ目の5列変換データとして出力することになる。

【0085】

以上で、列変換回路1の動作の説明を終了する。

【0086】

なお、上述の動作において、列変換回路1は、任意のn個のM列入力データのライト動作開始から、該n個のM列入力データをN列変換して出力するリード動作開始までを一定期間に保つよう動作することが好ましい。ここで、nは、M列入力データn個分に相当するM×nビットが変換後の列数Nで割り切れるような値である。例えば、Mが16でNが5であれば、nは5となる。この場合、列変換回路1は、任意の5個のM列入力データのライト動作開始から、該5個のM列入力データをN列変換して出力するリード動作開始までを一定期間に保つよう動作することが好ましい。

【0087】

次に、本発明の第1の実施の形態の効果について述べる。

【0088】

本実施の形態としての列変換回路は、論理回路の増大を抑えながら、変換後の列数を容易に拡張可能である。

【0089】

その理由は、本実施の形態において、ライト側におけるライトアドレス生成部およびライトデータ制御部の構成および動作は、列変換モードの設定に依存することがないからである。どの列変換モードにおいても、ライトアドレス生成部は、ライトアドレスを同様に更新する。そして、ライトデータ制御部は、M列入力データを、M個のメモリにおいてライトアドレスが示す位置に格納していく。これにより、本実施の形態としての列変換回路は、列変換モードを拡張しても、ライト側に回路を増設する必要がない。

【0090】

また、リード側において、リードアドレス生成部およびデータ選択出力部の構成および動作は、列変換モードの設定に依存することがないからである。どの列変換モードにおいても、リードアドレス生成回路は、リードアドレス更新制御部の制御にしたがってN個ずつリードアドレスを更新する。また、どの列変換モードにおいても、データ選択出力部は、選択信号にしたがって、M個のメモリのうちN個においてリードアドレスの示す位置のデータを選択出力するからである。そして、本実施の形態としての列変換回路は、列変換モードを拡張する場合、拡張する列変換モードの列数に応じてリードアドレス更新制御部および選択信号生成部の構成を拡張すればよい。これらの各部の構成の拡張は、データセレクト回路の論理段数の増設等と比較して遙かに少ない増設量で済む。したがって、本実施の形態としての列変換回路は、列変換モードを拡張しても、リード側の回路増設量をより低減することができる。

【0091】

(第2の実施の形態)

次に、本発明の第2の実施の形態について、図面を参照して詳細に説明する。

【0092】

<構成>

まず、本発明の第2の実施の形態としての列変換回路10の構成を、図2に示す。図2において、列変換回路10は、16列入力データを、2列、4列、5列、6列、および7列のいずれかに変換可能な回路である。つまり、本発明において、Mに16を適用し、Nに2、4、5、6、7を適用したものである。

【0093】

図2において、列変換回路10は、本発明の列変換モード設定部の一実施形態として、列変換モード設定信号110が入力されるインタフェースを含む。また、列変換回路10は、本発明のメモリの一実施形態として、16個のRAM(0)〜RAM(15)を含む。また、列変換回路10は、本発明のライトアドレス生成部の一実施形態として、ライトアドレス生成回路130を含む。また、列変換回路10は、本発明のライトデータ制御部の一実施形態として、ライトデータ制御回路140を含む。また、列変換回路10は、本発明のリードアドレス生成部の一実施形態として、リードアドレス生成回路160を含む。また、列変換回路10は、本発明のリードアドレス更新制御部の一実施形態としてリードイネーブル生成回路170を含む。また、列変換回路10は、本発明の選択信号生成部の一実施形態として、リードデータセレクト生成回路150を含む。また、列変換回路10は、本発明のデータ選択出力部の一実施形態として、データセレクト・リタイミング回路180を含む。

【0094】

また、ライトアドレス生成回路130およびライトデータ制御回路140は、クロック信号(ライトCLK)に基づいて動作する。また、リードデータセレクト生成回路150と、リードアドレス生成回路160と、リードイネーブル生成回路170と、データセレクト・リタイミング回路180とは、クロック信号(リードCLK)に基づいて動作する。リードCLKは、ライトCLKに対して2倍の周波数で動作するクロック信号である。

【0095】

図2において、列変換モード設定信号110は、2列変換モード、4列変換モード、5列変換モード、6列変換モード、および7列変換モードのいずれかを表す。例えば、"000"は2列変換モードを表し、"001"は、4列変換モードを表し、"010"は、5列変換モードを表し、"011"は、6列変換モードを表し、"100"は、7列変換モードを表していてもよい。

【0096】

ライトデータ[15:0]は、16列入力データである。ライトデータ[15:0]は、先頭の16列から順次入力される。図3を用いて、ライトデータ[15:0]について説明する。図3において、i番目に入力されるライトデータ[15:0]は、“i−15”〜”i−0”で表されている。また、以降、”i−j”を、「i番目に入力されるライトデータ[15:0]のjビット目」ともいう。また、ライトデータ先頭パルスは、1番目のライトデータ[15:0]が入力されたことを示す信号である。また、ライトデータ[15:0]は、256個(合計4096ビット分)を、1ユニットとして入力されていく。

【0097】

各RAM(0)〜(15)は、1ビットのデータを256個格納可能なRAM(1bit×256W_RAM)によって構成される。図4に、RAM(0)〜(15)のデータ格納領域を示す。図4において、“i−j”は、RAM(j)におけるiビット目の格納領域を表している。つまり、図4に示す“RAM(j)”(ただし、jは0〜15)の記載の右に並ぶ“1−j”〜“256−j”までが、1つのRAM(j)のデータ格納領域を表している。このように、16個のRAM(0)〜(15)は、ライトデータ1ユニット(16列データ×256=4096ビット分)のデータを、格納可能である。

【0098】

ライトアドレス生成回路130は、0〜255までの値を繰り返すライトアドレス[7:0]を生成する。このライトアドレス[7:0]は、16個のRAM(j)において共通のデータ書き込み位置を示す。すなわち、ライトアドレス0〜255は、各RAM(j)の1〜256ビット目の位置を表している。ライトアドレス生成回路130は、ライトデータイネーブル信号が有効‘H’となる度に、ライトアドレス[7:0]を+1カウントアップする。

【0099】

ここで、ライトデータイネーブル信号について説明する。ライトデータイネーブル信号は、16列ライトデータ[15:0]をRAMに書き込むタイミングを示す信号である。ライトデータイネーブル信号は、列変換モードに応じて異なるタイミングで有効となる。これは、ライト動作およびリード動作が一定期間を保ちながら行われるようにするためである。ライトデータイネーブル信号については詳細を後述する。

【0100】

図2に戻り、ライトデータ制御回路140について説明する。ライトデータ制御回路140は、ライトデータ[15:0]をRAM(15)〜(0)に格納するタイミングを制御する。つまり、ライトデータ制御回路140は、ライトデータ[15:0]の各ビットを、ライトデータイネーブル信号に基づくタイミングで、RAM(15)〜(0)に出力する。このとき、ライトデータ[15:0]の各ビットは、RAM(15)〜(0)において、ライトアドレス[7:0]が示す位置に格納される。

【0101】

リードアドレス生成回路160は、16個の各RAM(j)について、リードアドレス[7:0]を生成する。1つのリードアドレス[7:0]は、1個のRAM(j)におけるデータ読み出し位置を示す。リードアドレス生成回路160は、後述のリードイネーブル生成回路170から出力されるRAM_EN[15:0]信号に基づいて、16本のリードアドレス[7:0]のうちN本を更新する。リードイネーブル生成回路170から出力されるRAM_EN[15:0]信号は、列変換モードに応じて異なるものである。したがって、リードアドレス生成回路160は、16本のリードアドレス[7:0]を、列変換モードに応じて異なるタイミングでそれぞれ更新していく。

【0102】

リードアドレス生成回路160の詳細を、図5に示す。リードアドレス生成回路160は、16個のカウンタRD_ADR(15)〜(0)を用いて、16本のリードアドレス[7:0]を生成する。これらのカウンタRD_ADR(15)〜(0)の初期値は、列変換モードにより異なるものが設定される。ここで、カウンタRD_ADR(15)〜(0)の初期値について説明する。

【0103】

まず、2列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表1に示す。

【0104】

【表1】

【0105】

次に、4列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表2に示す。

【0106】

【表2】

【0107】

次に、5列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表3に示す。

【0108】

【表3】

【0109】

次に、6列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表4に示す。

【0110】

【表4】

【0111】

次に、7列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表5に示す。

【0112】

【表5】

【0113】

上記表1〜表5に示したように、カウンタRD_ADR(15)〜RD_ADR(0)は、リードデータ先頭パルスが有効時に、リードCLKの立ち上がりエッジで、各表に示した値に初期設定される。すなわち、これらの値が、各変換モードにおける16本のリードアドレスの初期値となる。そして、これらのカウンタRD_ADR(15)〜(0)は、リードCLKに基づく所定のタイミングで、対応する入力信号RAM_EN(15)〜RAM_EN(0)が‘H’であれば、+1のカウントアップを実行する。RAM_EN信号については、詳細を後述する。これにより、リードアドレス生成回路160は、16本のリードアドレスとして、それぞれの初期値から初めて、0〜255を繰り返す値を生成する。

【0114】

また、図5に示すように、リードアドレス生成回路160は、生成した16本のリードアドレスをRAM(15)〜(0)に対して出力する。これにより、RAM(15)〜(0)からは、それぞれのリードアドレスの示す位置に格納された1ビットずつの合計16ビットのRAM格納データ[15:0]が出力されることになる。

【0115】

次に、リードイネーブル生成回路170およびリードデータセレクト生成回路150の詳細を、図6を用いて説明する。

【0116】

図6において、リードデータセレクト生成回路150は、列変換モード毎に、リードデータセレクト信号を生成する回路を含む。ここで、リードデータセレクト信号は、本発明の選択信号の一実施形態である。リードデータセレクト信号は、M個のRAM(j)のうち選択対象となるN個を示す。具体的には、リードデータセレクト生成回路150は、2列変換リードデータセレクト生成回路150a、4列変換リードデータセレクト生成回路150b、5列変換リードデータセレクト生成回路150c、6列変換リードデータセレクト生成回路150d、7列変換リードデータセレクト生成回路150e(以降、総称してN列変換リードデータセレクト生成回路150ともいう)を有する。

【0117】

各N列変換リードデータセレクト生成回路150は、それぞれ対応する列変換モードに応じてリードデータセレクト信号RAM_SEL[15:0]を生成し、データセレクト・リタイミング回路180に出力する。このリードデータセレクト信号RAM_SEL[15:0]は、16個のRAM(15)〜RAM(0)から出力される16ビットのRAM格納データ[15:0]において、選択対象となるNビットのデータ位置を示しているとも言える。

【0118】

また、各N列変換リードデータセレクト生成回路150は、カウント値RDENCNTが変化する度にRAM_SEL[15:0]を更新する。

【0119】

ここで、カウント値RDENCNTについて説明する。カウント値RDENCNTは、リードCLKの4CLK毎にカウントアップされる信号である。ただし、列変換モード設定信号110に応じて、RDENCNTの最大カウント値には、異なる値が設定される。カウント値RDENCNTは、16個のRAM(j)のうちN個ずつが順次選択されていく際に、再び同一の組み合わせのN個のRAM(j)が選択されるまでの選択回数に基づき設定される。例えば、2列変換モードでは、RDENCNTが0のとき、RAM(15)、RAM(14)が選択され、RDENCNTが1のとき、RAM(13)、RAM(12)が選択されていくとすると、RDENCNTが7のとき、RAM(1)、RAM(0)が選択されることになる。そして、次に選択されるのは、再びRAM(15)、RAM(14)となるため、RDENCNTの最大カウント値は7である。また、同様に、4列変換モードでは、RDENCNTの最大カウント値は3である。また、同様に、5列変換モードでは、RDENCNTの最大カウント値は15である。また、同様に、6列変換モードでは、RDENCNTの最大カウント値は7である。また、同様に、7列変換モードでは、RDENCNTの最大カウント値は15である。

【0120】

次に、2列変換リードデータセレクト生成回路150aについて説明する。2列変換リードデータセレクト生成回路150aは、2列変換モードで0〜7を繰り返すカウンタRDENCNTを用いて動作する。2列変換リードデータセレクト生成回路150aが、RDENCNTの値に応じて出力する信号の一覧を、表6に示す。

【0121】

【表6】

【0122】

表6に示すように、例えば、2列変換リードデータセレクト生成回路150aは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)=‘H’およびRAM_SEL(14)=‘H’を出力する。

【0123】

また、例えば、2列変換リードデータセレクト生成回路150aは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(13)=‘H’およびRAM_SEL(12)=‘H’を出力する。

【0124】

このように、2列変換リードデータセレクト生成回路150aは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SEL[15:0]のうち2つずつを‘H’とするよう切り替えながら出力していく。

【0125】

次に、4列変換リードデータセレクト生成回路150bについて説明する。4列変換リードデータセレクト生成回路150bは、4列変換モードで0〜3を繰り返すカウンタRDENCNTを用いて動作する。4列変換リードデータセレクト生成回路150bが、RDENCNTの値に応じて出力する信号の一覧を、表7に示す。

【0126】

【表7】

【0127】

表7に示すように、例えば、4列変換リードデータセレクト生成回路150bは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)〜RAM_SEL(12)を有効‘H’にして出力する。

【0128】

また、例えば、4列変換リードデータセレクト生成回路150bは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(11)〜RAM_SEL(8)を有効‘H’にして出力する。

【0129】

このように、4列変換リードデータセレクト生成回路150bは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SEL[15:0]のうち4つずつを‘H’とするよう切り替えながら出力していく。

【0130】

次に、5列変換リードデータセレクト生成回路150cについて説明する。5列変換リードデータセレクト生成回路150cは、5列変換モードで0〜15を繰り返すカウンタRDENCNTを用いて動作する。5列変換リードデータセレクト生成回路150cが、RDENCNTの値に応じて出力する信号の一覧を、表8に示す。

【0131】

【表8】

【0132】

表8に示すように、例えば、5列変換リードデータセレクト生成回路150cは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)〜RAM_SEL(11)を有効‘H’にして出力する。

【0133】

また、例えば、5列変換リードデータセレクト生成回路150cは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(10)〜RAM_SEL(6)を有効‘H’にして出力する。

【0134】

このように、5列変換リードデータセレクト生成回路150cは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SELのうち5つずつを‘H’とするよう切り替えながら出力していく。

【0135】

次に、6列変換リードデータセレクト生成回路150dについて説明する。6列変換リードデータセレクト生成回路150dは、6列変換モードで0〜7を繰り返すカウンタRDENCNTを用いて動作する。6列変換リードデータセレクト生成回路150dが、RDENCNTの値に応じて出力する信号の一覧を、表9に示す。

【0136】

【表9】

【0137】

表9に示すように、例えば、6列変換リードデータセレクト生成回路150dは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)〜RAM_SEL(10)を有効‘H’にして出力する。

【0138】

また、例えば、6列変換リードデータセレクト生成回路150dは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(9)〜RAM_SEL(4)を有効‘H’にして出力する。

【0139】

このように、6列変換リードデータセレクト生成回路150dは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SEL[15:0]のうち6つずつを‘H’とするよう切り替えながら出力していく。

【0140】

次に、7列変換リードデータセレクト生成回路150eについて説明する。7列変換リードデータセレクト生成回路150eは、7列変換モードで0〜15を繰り返すカウンタRDENCNTを用いて動作する。7列変換リードデータセレクト生成回路150eが、RDENCNTの値に応じて出力する信号の一覧を、表10に示す。

【0141】

【表10】

【0142】

表10に示すように、例えば、7列変換リードデータセレクト生成回路150eは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)〜RAM_SEL(9)を有効‘H’にして出力する。

【0143】

また、例えば、7列変換リードデータセレクト生成回路150eは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(8)〜RAM_SEL(2)を有効‘H’にして出力する。

【0144】

このように、7列変換リードデータセレクト生成回路150eは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SEL[15:0]のうち7つずつを‘H’とするよう切り替えながら出力していく。

【0145】

次に、リードイネーブル生成回路170について説明する。

【0146】

図6において、リードイネーブル生成回路170は、列変換モード毎に、リードイネーブル信号を生成する回路を含む。ここで、リードイネーブル信号は、16本のリードアドレスのうち、更新対象となるN本を示す。具体的には、リードイネーブル生成回路170は、2列変換リードイネーブル生成回路170aと、4列変換リードイネーブル生成回路170bと、5列変換リードイネーブル生成回路170cと、6列変換リードイネーブル生成回路170dと、7列変換リードイネーブル生成回路170eとを含む。これらの各回路を、以降、総称してN列変換リードイネーブル生成回路170ともいう。

【0147】

各N列変換リードイネーブル生成回路170は、16本のリードアドレスのうち更新対象となるN本を示すリードイネーブル信号RAM_EN[15:0]を、リードアドレス生成回路160に対して出力する。

【0148】

また、各N列変換リードイネーブル生成回路170は、カウント値RDENCNTに応じて、RD_TIM信号が有効となると、RAM_EN[15:0]を更新する。ここで、RD_TIM信号は、カウント値RDENCNTが変化後リードCLKで3CLK目に1CLK期間有効となる信号である。言い換えると、RD_TIM信号は、カウント値RDENCNTが変化する直前の1CLK期間で有効となる。これにより、各N列変換リードイネーブル生成回路170は、RDENCNT値の次の変化のタイミングでリードアドレスが更新されるよう、RAM_EN[15:0]信号をリードアドレス生成回路160に出力することになる。

【0149】

次に、2列変換リードイネーブル生成回路170aについて説明する。2列変換リードイネーブル生成回路170aは、2列変換モードで0〜7を繰り返すカウンタRDENCNTを用いて動作する。ここで、2列変換リードイネーブル生成回路170aが、RDENCNTの値に応じて出力する信号の一覧を、表11に示す。

【0150】

【表11】

【0151】

表11に示すように、例えば、2列変換リードイネーブル生成回路170aは、RDENCNT=0およびRD_TIM=‘H’ならば、リードアドレス生成回路160に対して、RAM_EN(13)=‘H’およびRAM_EN(12)=‘H’を出力する。

【0152】

また、例えば、2列変換リードイネーブル生成回路170aは、RDENCNT=1かつRD_TIM=‘H’ならば、リードアドレス生成回路160に対して、RAM_EN(11)=‘H’およびRAM_EN(10)=‘H’を出力する。

【0153】

このように、2列変換リードイネーブル生成回路170aは、RD_TIM=‘H’となる度、RDENCNTの値に応じて、RAM_EN[15:0]のうち2つずつを‘H’とするよう切り替えながら出力していく。

【0154】

次に、4列変換リードイネーブル生成回路170bについて説明する。4列変換リードイネーブル生成回路170bは、4列変換モードで0〜3を繰り返すカウンタRDENCNTを用いて動作する。4列変換リードイネーブル生成回路170bが、RDENCNTの値に応じて出力する信号の一覧を、表12に示す。

【0155】

【表12】

【0156】

表12に示すように、例えば、4列変換リードイネーブル生成回路170bは、RDENCNT=0かつRD_TIM=‘H’ならば、リードアドレス生成回路160に対して、RAM_EN(11)〜RAM_EN(8)をそれぞれ‘H’として出力する。

【0157】

また、例えば、4列変換リードイネーブル生成回路170bは、RDENCNT=1かつRD_TIM=‘H’ならば、RAM_EN(7)〜RAM_EN(4)をそれぞれ‘H’として出力する。

【0158】

このように、4列変換リードイネーブル生成回路170bは、RD_TIM=‘H’となる度、RDENCNTの値に応じて、RAM_EN[15:0]のうち4つずつを‘H’とするよう切り替えながら出力していく。

【0159】

次に、5列変換リードイネーブル生成回路170cについて説明する。5列変換リードイネーブル生成回路170cは、5列変換モードで0〜15を繰り返すカウンタRDENCNTを用いて動作する。5列変換リードイネーブル生成回路170cが、RDENCNTの値に応じて出力する信号の一覧を、表13に示す。

【0160】

【表13】

【0161】

表13に示すように、例えば、5列変換リードイネーブル生成回路170cは、RDENCNT=0かつRD_TIM=‘H’ならば、リードアドレス生成回路160に対して、RAM_EN(10)〜RAM_EN(6)をそれぞれ‘H’として出力する。

【0162】

また、例えば、5列変換リードイネーブル生成回路170cは、RDENCNT=1かつRD_TIM=‘H’ならば、リードアドレス生成回路160に対して、RAM_EN(5)〜RAM_EN(1)をそれぞれ‘H’として出力する。

【0163】

このように、5列変換リードイネーブル生成回路170cは、RD_TIM=‘H’となる度、RDENCNTの値に応じて、RAM_EN[15:0]のうち5つずつを‘H’とするよう切り替えながら出力していく。

【0164】

次に、6列変換リードイネーブル生成回路170dについて説明する。6列変換リードイネーブル生成回路170dは、6列変換モードで0〜7を繰り返すカウンタRDENCNTを用いて動作する。6列変換リードイネーブル生成回路170dが、RDENCNTの値に応じて出力する信号の一覧を、表14に示す。

【0165】

【表14】

【0166】

表14に示すように、例えば、6列変換リードイネーブル生成回路170dは、RDENCNT=0かつRD_TIM=‘H’ならば、リードアドレス生成回路160に対して、RAM_EN(9)〜RAM_EN(4)をそれぞれ‘H’として出力する。

【0167】

また、例えば、6列変換リードイネーブル生成回路170dは、RDENCNT=1かつRD_TIM=‘H’ならば、リードアドレス生成回路160に対して、RAM_EN(3)〜RAM_EN(0)およびRAM_EN(15)〜RAM_EN(14)をそれぞれ‘H’として出力する。

【0168】

このように、6列変換リードイネーブル生成回路170dは、RD_TIM=‘H’となる度、RDENCNTの値に応じて、RAM_EN[15:0]のうち6つずつを‘H’とするよう切り替えながら出力していく。

【0169】

次に、7列変換リードイネーブル生成回路170eについて説明する。7列変換リードイネーブル生成回路170eは、7列変換モードで0〜15を繰り返すカウンタRDENCNTを用いて動作する。7列変換リードイネーブル生成回路170eが、RDENCNTの値に応じて出力する信号の一覧を、表15に示す。

【0170】

【表15】

【0171】

表15に示すように、例えば、7列変換リードイネーブル生成回路170eは、RDENCNT=0かつRD_TIM=‘H’ならば、リードアドレス生成回路160に対して、RAM_EN(8)〜RAM_EN(2)をそれぞれ‘H’として出力する。

【0172】

また、例えば、7列変換リードイネーブル生成回路170eは、RDENCNT=1かつRD_TIM=‘H’ならば、リードアドレス生成回路160に対して、RAM_EN(1)〜RAM_EN(0)およびRAM_EN(15)〜RAM_EN(11)をそれぞれ‘H’として出力する。

【0173】

このように、7列変換リードイネーブル生成回路170eは、RD_TIM=‘H’となる度、RDENCNTの値に応じて、RAM_ENのうち7つずつを‘H’とするよう切り替えながら出力していく。

【0174】

次に、図2に戻り、データセレクト・リタイミング回路180について説明する。

【0175】

データセレクト・リタイミング回路180は、データセレクト回路181およびリタイミング回路182を有する。

【0176】

データセレクト回路181には、RAM格納データ[15:0]およびRAM_SEL[15:0]が入力される。前述のように、RAM格納データ[15:0]は、RAM(15)〜RAM(0)においてそれぞれのリードアドレスの示す位置に格納された1ビットずつの合計16ビットのデータである。データセレクト回路181は、前述のRDENCNTのカウント値が変わる毎に、RAM格納データ[15:0]のうち、RAM_SEL[15:0]の示す位置に格納されたデータを選択する。ここで、RAM_SEL[15:0]は、16ビットのうち列変換モードに応じたNビットが有効‘H’となっている。よって、データセレクト回路181は、列変換モードに応じたN列を選択することになる。

【0177】

そして、リタイミング回路182は、データセレクト回路181により選択されたN列のデータを、RD_TIM信号の有効‘H’後、リードCLKの立ち上がりエッジでリタイミングして出力する。データセレクト・リタイミング回路180から出力されるデータが、N列変換データ[N−1:0]となる。

【0178】

<動作>

以上のように構成された列変換回路10の動作について、図面を参照して詳細に説明する。

【0179】

<ライト動作>

まず、ライト動作について、図7〜図11を参照して説明する。列変換回路10は、ライトデータ先頭パルスが有効‘H’になると、ライト動作を開始する。ライトデータ先頭パルスは、図7〜図11に示すように、2列変換モードでは16CLK期間、4列変換モードでは8CLK期間、5列〜7列変換モードでは4CLK期間、それぞれ有効となる。

【0180】

以降、列変換回路10には、ライトデータイネーブル信号が所定のタイミングで入力される。ここで、ライトデータイネーブル信号は、列変換モードに応じて異なるタイミングで有効となる。

【0181】

2列変換モードでは、図7に示すように、ライトデータイネーブル信号は、ライトCLKの16CLK毎に1CLKの期間有効となる。

【0182】

4列変換モードでは、図8に示すように、ライトデータイネーブル信号は、ライトCLKの8CLK毎に1CLKの期間有効となる。

【0183】

5列変換モードでは、図9に示すように、ライトデータイネーブル信号は、ライトCLKの4CLK毎に2回、8CLK毎に3回、合計で32CLK毎に5回、それぞれ1CLKの期間有効となる。

【0184】

6列変換モードでは、図10に示すように、ライトデータイネーブル信号は、ライトCLKの4CLK毎に2回、8CLK毎に1回、合計16CLK毎に3回、それぞれ1CLKの期間有効となる。

【0185】

7列変換モードでは、図11に示すように、ライトデータイネーブル信号は、ライトCLKの4CLK毎に6回、8CLK毎に1回、合計32CLK毎に7回、それぞれ1CLKの期間有効となる。

【0186】

以降のライト動作の説明は、各列変換モードにおいて共通である。

【0187】

ライトアドレス生成回路130は、ライトデータ先頭パルスおよびライトデータイネーブル信号が共に有効‘H’時に、ライトCLKの立ち上がりエッジにより、ライトアドレスを0に初期化する。

【0188】

そして、ライトアドレス生成回路130は、ライトデータイネーブル信号が有効‘H’時に、ライトCLKの立ち上がりエッジにより、ライトアドレスに対して+1のカウントアップを実行する。

【0189】

そして、ライトアドレス生成回路130は、ライトアドレスが255であり、かつ、ライトデータイネーブル信号が有効‘H’時に、ライトCLKの立ち上がりエッジにより、ライトアドレスを再度0に初期化する。

【0190】

これにより、ライトアドレスは、0〜255を繰り返すことになる。各変換モードにおけるライトアドレスは、図2〜図7にそれぞれ示した通りとなる。

【0191】

次に、ライトデータ制御回路140は、ライトデータ[15:0]を、RAM(15)〜(0)に対して出力する。このとき、ライトデータ制御回路140は、ライトデータイネーブル信号を用いることにより、ライトアドレスおよびライトデータの変化点が一致するよう、タイミングを調整する。具体的には、ライトデータ制御回路140は、ライトデータ[15:0]のうちライトデータ(15)を、RAM(15)に対して出力する。同様に、ライトデータ制御回路140は、ライトデータ[15:0]のうちライトデータ(j)を、RAM(j)に対して出力する。言い換えると、ライトデータ制御回路140は、ライトデータ[15:0]を1列データに分割し、各1列データを、RAM(15)〜RAM(0)のそれぞれに対して出力する。例えば、図2〜図7において、1つ目のライトデータ[15:0]“1000(hex)”は、ライトデータイネーブル信号に同期して16個のRAM(j)のアドレス0の位置に格納される。同様に、2番目のライトデータ[15:0]“1001(hex)”は、ライトデータイネーブル信号に同期して16個のRAM(j)のアドレス1の位置に格納される。

【0192】

このように、列変換回路10は、列変換モードの設定に関わらず、ライトアドレスを0〜255まで繰り返し更新する。そして、列変換回路10は、ライトアドレスが更新される毎に、次のライトデータ[15:0]を16個のRAM(j)のライトアドレスが示す位置に格納していく。

【0193】

このような列変換回路10のライト動作により、RAM(15)〜RAM(0)に格納されるライトデータのイメージを図12に示す。図12において、1ユニット目の先頭の16ビットのライトデータ(1-15〜1-0)は、ライトアドレスが0となるタイミングで、RAM(15)〜RAM(0)の1ビット目(1-15〜1-0)に格納される。次に、2番目の16ビットライトデータ(2-15〜2-0)は、ライトアドレスが1となるタイミングで、RAM(15)〜RAM(0)の2ビット目(2-15〜2-0)に格納される。そして、1ユニット目の最後にあたる256番目の16ビットライトデータ(256-15〜256-0)は、ライトアドレスが255となるタイミングで、RAM(15)〜RAM(0)の256ビット目(256-15〜256-0)に格納される。以降、2ユニット目のライトデータは、再びRAM(15)〜RAM(0)のライトアドレス0から順に格納されていく。なお、各RAM(15)〜(10)の各ライトアドレスの位置に既に格納されているデータは、同一のライトアドレスの位置に次のユニットのライトデータが格納される前に、後述のリード動作により読み出されている。

【0194】

以上で、ライト動作の説明を終了する。

【0195】

次に、リード動作について説明する。

【0196】

<2列変換モードにおけるリード動作>

2列変換モードにおけるリード側のタイミングチャートを図13に示す。

【0197】

ここでは、まず、リードデータ先頭パルスが有効‘H’となると、列変換回路10は、リード動作を開始する。

【0198】

リードCLKカウンタは、リードデータ先頭パルスが有効‘H’時に、リードCLKの立ち上がりエッジでカウント値を0に初期化する。その後、リードCLKカウンタは、リードCLKに同期して0〜3までを繰り返しカウントする。

【0199】

リードイネーブルRD_TIM信号は、リードCLKカウンタが3で有効‘H’となる。RD_TIM信号は、リードイネーブル生成回路160から出力されるRAM_EN[15:0]の更新タイミングを示す。また、RD_TIM信号は、リタイミング回路182から変換データを出力するタイミングも示している。

【0200】

リードイネーブルカウンタRDENCNTは、リードデータ先頭パルスが有効時に、0に初期化される。この時、リード側の2列変換モード"000"が設定されるとともに、RDENCNTの最大カウント値が7にセットされる。前述のように、リードイネーブルカウンタRDENCNTは、リードイネーブル信号RAM_EN[15:0]およびリードデータセレクト信号RAM_SEL[15:0]の更新を制御する値となる。

【0201】

また、リードデータ先頭パルスが有効時に、RAM(15)およびRAM(14)のリードアドレスは、0に初期設定される。また、RAM(13)〜RAM(0)のリードアドレスは、255に初期設定される。これらの値は、前述のように、表1に示した16個のカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値である。

【0202】

次に、データセレクト回路181は、列変換先頭パルスが有効になると、初期設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=0であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(15)およびRAM_SEL(14)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[15:14]を選択する。

【0203】

次に、リタイミング回路182は、RDENCNT=0かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[15:14]をリタイミングして出力する。これが、1つ目の2列変換データ[1:0]となる。図13には、1つ目の2列変換データ[1:0]として、“00”(2進表記)を示している。これは、図7に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の15〜14ビット目に相当する。なお、前述のように、16列入力データの0〜15ビット目とは、最下位〜最上位までの各ビットをそれぞれ示すものとする。

【0204】

次に、RDENCNT=0、かつ、RD_TIM=‘H’のタイミングで、リードイネーブル生成回路170は、RAM_EN(13)およびRAM_EN(12)を‘H’としてRAM_EN[15:0]を出力する。つまり、リードイネーブル生成回路170は、リードアドレス生成回路160に対して、次の選択先となるRAM(13)およびRAM(12)におけるリードアドレスを+1カウントアップするタイミングを出力している。

【0205】

次に、リードアドレス生成回路160は、RAM(13)およびRAM(12)のリードアドレスを、それまでの255を+1カウントアップして0に更新する。この時点で、RAM(15)〜RAM(12)のリードアドレスは、0に設定され、RAM(11)〜RAM(0)のリードアドレスは、255に設定されている。

【0206】

次に、データセレクト回路181は、更新された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=1であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(13)およびRAM_SEL(12)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[13:12]を選択する。

【0207】

次に、リタイミング回路182は、RDENCNT=1かつRD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[13:12]をリタイミングして出力する。これが、2つ目の2列変換データ[1:0]となる。図13には、2つ目の2列変換データ[1:0]として、“01”(2進表記)を示している。これは、図7に示した1つ目の16列入力データの一例“1000” (16進表記)、すなわち、=”0001 0000 0000 0000”(2進表記)の13〜12ビット目に相当する。

【0208】

このようにして、2列変換モードでは、RDENCNTのカウント値が0〜7を繰り返す。そして、リードデータセレクト生成回路150は、RDENCNTのカウント値が変化すると、RAM(15)〜RAM(0)の16個のRAMのうち選択対象となる2つのRAMを示すよう、RAM_SEL[15:0]のうち‘H’となる2ビットを順次切り替える。また、リードイネーブル生成回路170は、RD_TIM信号が有効となる毎に、RDENCNTのカウント値の次の変化のタイミングで更新する2本のリードアドレスを示すよう、RAM_EN[15:0]のうち‘H’となる2ビットを順次切り替える。そして、リードアドレス生成回路160は、RAM_EN[15:0]が示すRAM(j)におけるリードアドレスをカウントアップする。そして、データセレクト・リタイミング回路180は、RAM_SEL[15:0]およびリードアドレスに基づいて、2列変換データを選択出力していく。

【0209】

このようにして出力される2列変換データは、図14に示すとおりとなる。図14において、i−jは、i番目に入力されたライトデータのjビット目のデータを示している。つまり、1番目のライトデータの15〜14ビット目のデータが、1つ目の2列変換データであることを表している。

【0210】

以上のように動作することにより、2列変換モードでは、列変換回路10は、16列入力データ1つ分を1単位として、ライト動作およびリード動作を繰り返していく。これは、16列入力データ1つ分の16ビットが変換後の列数2で割り切れるためである。このとき、列変換回路10は、任意の1つの16列入力データのライト動作の開始から、該1つの16列入力データを2列変換データに変換して順次出力するリード動作の開始までを一定期間に保つように動作している。

【0211】

以上で、2列変換モードにおける列変換回路10の動作の説明を終了する。

【0212】

<4列変換モードにおけるリード動作>

次に、4列変換モードにおけるリード側のタイミングチャートを図15に示す。

【0213】

ここでは、4列変換モードにおける列変換回路10の動作が、2列変換モードにおける動作と異なる点を中心に述べる。

【0214】

まず、リードデータ先頭パルスが有効‘H’となると、列変換回路10はリード動作を開始する。

【0215】

リードイネーブルカウンタRDENCNTの最大カウント値は、4列変換モードでは、3にセットされる。RDENCNTの初期化およびカウントアップのタイミングは、2列変換モードの場合と同様である。

【0216】

また、16本のリードアドレスの初期値は、2列変換モードの場合と異なる。リードデータ先頭パルスが有効時に、RAM(15)〜RAM(12)のリードアドレスは、0に初期設定される。また、RAM(11)〜RAM(0)のリードアドレスは、255に初期設定される。これらの値は、前述のように、表2に示した16個のカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値である。

【0217】

次に、データセレクト回路181は、列変換先頭パルスが有効になると、初期設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=0であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(15)〜RAM_SEL(12)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[15:12]を選択する。

【0218】

次に、リタイミング回路182は、RDENCNT=0かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[15:12]をリタイミングして出力する。これが、1つ目の4列変換データ[3:0]となる。図15には、1つ目の4列変換データ[3:0]として、“1”(16進表記)、すなわち、“0001”(2進表記)を示している。これは、図8に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の15〜12ビット目に相当する。

【0219】

次に、RDENCNT=0、かつ、RD_TIM=‘H’のタイミングで、リードイネーブル生成回路170は、RAM_EN(11)〜RAM_EN(8)を‘H’としてRAM_EN[15:0]を出力する。つまり、リードイネーブル生成回路170は、リードアドレス生成回路160に対して、次の選択先となるRAM(11)〜RAM(8)におけるリードアドレスを+1カウントアップするタイミングを出力している。

【0220】

次に、リードアドレス生成回路160は、RAM(11)〜RAM(8)のリードアドレスを、それまでの255を+1カウントアップして0に更新する。この時点で、RAM(15)〜RAM(8)のリードアドレスは、0に設定され、RAM(7)〜RAM(0)のリードアドレスは、255に設定されている。

【0221】

次に、データセレクト回路181は、新たに設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=1であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(11)〜RAM_SEL(8)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[11:8]を選択する。

【0222】

次に、リタイミング回路182は、RDENCNT=1、かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[11:8]をリタイミングして出力する。これが、2つ目の4列変換データ[3:0]となる。図15には、2つ目の4列変換データ[3:0]として、“0”(16進表記)、すなわち、“0000”(2進表記)を示している。これは、図8に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の11〜8ビット目に相当する。

【0223】

このようにして、4列変換モードでは、RDENCNTのカウント値が0〜3を繰り返す。そして、リードデータセレクト生成回路150は、RDENCNTのカウント値が変化すると、RAM(15)〜RAM(0)の16個のRAMのうち選択対象となる4つのRAMを示すよう、RAM_SEL[15:0]のうち‘H’となる4ビットを順次切り替える。また、リードイネーブル生成回路170は、RD_TIM信号が有効となる毎に、RDENCNTのカウント値の次の変化のタイミングで更新する4本のリードアドレスを示すよう、RAM_EN[15:0]のうち‘H’となる4ビットを順次切り替える。そして、リードアドレス生成回路160は、RAM_EN[15:0]が示すRAM(j)におけるリードアドレスをカウントアップする。そして、データセレクト・リタイミング回路180は、RAM_SEL[15:0]およびリードアドレスに基づいて、4列変換データを選択出力していく。

【0224】

このようにして出力される4列変換データは、図16に示すとおりとなる。図16において、i−jは、i番目に入力されたライトデータのjビット目のデータを示している。つまり、1番目のライトデータの15〜13ビット目までの4ビットのデータが、1つ目の4列変換データであることを表している。

【0225】

以上のように動作することにより、4列変換モードでは、列変換回路10は、16列入力データ1つ分を1単位として、ライト動作およびリード動作を繰り返していく。これは、16列入力データ1つ分の16ビットが変換後の列数4で割り切れるためである。このとき、列変換回路10は、任意の1つの16列入力データのライト動作の開始から、該1つの16列入力データを4列変換データに変換して順次出力するリード動作の開始までを一定期間に保つように動作している。

【0226】

以上で、4列変換モードにおける列変換回路10の動作の説明を終了する。

【0227】

<5列変換モードにおけるリード動作>

次に、5列変換モードにおけるリード側のタイミングチャートを図17に示す。

【0228】

ここでは、5列変換モードにおける列変換回路10の動作が、2列変換モードにおける動作と異なる点を中心に述べる。

【0229】

まず、リードデータ先頭パルスが有効‘H’となると、列変換回路10はリード動作を開始する。

【0230】

リードイネーブルカウンタRDENCNTの最大カウント値は、5列変換モードでは、15にセットされる。RDENCNTの初期化およびカウントアップのタイミングは、2列変換モードの場合と同様である。

【0231】

また、16本のリードアドレスの初期値は、2列変換モードの場合と異なる。リードデータ先頭パルス有効時に、RAM(15)〜RAM(11)のリードアドレスは、0に初期設定される。また、RAM(10)〜RAM(0)のリードアドレスは、255に初期設定される。これらの値は、前述のように、表3に示した16個のカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値である。

【0232】

次に、データセレクト回路181は、列変換先頭パルスが有効になると、初期設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=0であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(15)〜RAM_SEL(11)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[15:11]を選択する。

【0233】

次に、リタイミング回路182は、RDENCNT=0かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[15:11]をリタイミングして出力する。これが、1つ目の5列変換データ[4:0]となる。図17には、1つ目の5列変換データ[4:0]として、“02”(16進表記)、すなわち、“00010”(2進表記)を示している。これは、図9に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の15〜11ビット目に相当する。

【0234】

次に、RDENCNT=0、かつ、RD_TIM=‘H’のタイミングで、リードイネーブル生成回路170は、RAM_EN(10)〜RAM_EN(6)を‘H’としてRAM_EN[15:0]を出力する。つまり、リードイネーブル生成回路170は、リードアドレス生成回路160に対して、次の選択先となるRAM(10)〜RAM(6)におけるリードアドレスを+1カウントアップするタイミングを出力している。

【0235】

次に、リードアドレス生成回路160は、RAM(10)〜RAM(6)のリードアドレスを、それまでの255を+1カウントアップして0に更新する。この時点で、RAM(15)〜RAM(6)のリードアドレスは、0に設定され、RAM(5)〜RAM(0)のリードアドレスは、255に設定されている。

【0236】

次に、データセレクト回路181は、新たに設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=1であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(10)〜RAM_SEL(6)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[10:6]を選択する。

【0237】

次に、リタイミング回路182は、RDENCNT=1、かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[10:6]をリタイミングして出力する。これが、2つ目の5列変換データ[4:0]となる。図17には、1つ目の5列変換データ[4:0]として、“00”(16進表記)、すなわち、“00000”(2進表記)を示している。これは、図9に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の10〜6ビット目に相当する。

【0238】

このようにして、5列変換モードでは、RDENCNTのカウント値が0〜15を繰り返す。そして、リードデータセレクト生成回路150は、RDENCNTのカウント値が変化すると、RAM(15)〜RAM(0)の16個のRAMのうち選択対象となる5つのRAMを示すよう、RAM_SEL[15:0]のうち‘H’となる5ビットを順次切り替える。また、リードイネーブル生成回路170は、RD_TIM信号が有効となる毎に、RDENCNTのカウント値の次の変化のタイミングで更新する5本のリードアドレスを示すよう、RAM_EN[15:0]のうち‘H’となる5ビットを順次切り替える。そして、リードアドレス生成回路160は、RAM_EN[15:0]が示すRAM(j)におけるリードアドレスをカウントアップする。そして、データセレクト・リタイミング回路180は、RAM_SEL[15:0]およびリードアドレスに基づいて、5列変換データを選択出力していく。

【0239】

このようにして出力される5列変換データは、図18に示すとおりとなる。図18において、i−jは、i番目に入力されたライトデータのjビット目のデータを示している。つまり、1番目のライトデータの15〜11ビット目までの5ビットのデータが、1つ目の5列変換データであることを表している。

【0240】

以上のように動作することにより、5列変換モードでは、列変換回路10は、16列入力データ5つ分を1単位として、ライト動作およびリード動作を繰り返していく。これは、16列入力データ5つ分の80ビットが変換後の列数5で割り切れるためである。このとき、列変換回路10は、任意の5つの16列入力データのライト動作の開始から、該5つの16列入力データを5列変換データに変換して順次出力するリード動作の開始までを一定期間に保つように動作している。

【0241】

以上で、5列変換モードにおける列変換回路10の動作の説明を終了する。

【0242】

<6列変換モードにおけるリード動作>

次に、6列変換モードにおけるリード側のタイミングチャートを図19に示す。

【0243】

ここでは、6列変換モードにおける列変換回路10の動作が、2列変換モードにおける動作と異なる点を中心に述べる。

【0244】

まず、リードデータ先頭パルスが有効‘H’となると、列変換回路10はリード動作を開始する。

【0245】

リードイネーブルカウンタRDENCNTの最大カウント値は、6列変換モードでは、7にセットされる。RDENCNTの初期化およびカウントアップのタイミングは、2列変換モードの場合と同様である。

【0246】

また、16本のリードアドレスの初期値は、2列変換モードの場合と異なる。リードデータ先頭パルス有効時に、RAM(15)〜RAM(10)のリードアドレスは、0に初期設定される。また、RAM(9)〜RAM(0)のリードアドレスは、255に初期設定される。これらの値は、前述のように、表4に示した16個のカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値である。

【0247】

次に、データセレクト回路181は、列変換先頭パルスが有効になると、初期設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=0であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(15)〜RAM_SEL(10)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[15:10]を選択する。

【0248】

次に、リタイミング回路182は、RDENCNT=0かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[15:10]をリタイミングして出力する。これが、1つ目の6列変換データ[5:0]となる。図19には、1つ目の6列変換データ[5:0]として、“04”(16進表記)、すなわち、“000100”(2進表記)を示している。これは、図10に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の15〜10ビット目に相当する。

【0249】

次に、RDENCNT=0、かつ、RD_TIM=‘H’のタイミングで、リードイネーブル生成回路170は、RAM_EN(9)〜RAM_EN(4)を‘H’としてRAM_EN[15:0]を出力する。つまり、リードイネーブル生成回路170は、リードアドレス生成回路160に対して、次の選択先となるRAM(9)〜RAM(4)におけるリードアドレスを+1カウントアップするタイミングを出力している。

【0250】

次に、リードアドレス生成回路160は、RAM(9)〜RAM(4)のリードアドレスを、それまでの255を+1カウントアップして0に更新する。この時点で、RAM(15)〜RAM(4)のリードアドレスは、0に設定され、RAM(3)〜RAM(0)のリードアドレスは、255に設定されている。

【0251】

次に、データセレクト回路181は、新たに設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=1であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(9)〜RAM_SEL(4)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[9:4]を選択する。

【0252】

次に、リタイミング回路182は、RDENCNT=1、かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[9:4]をリタイミングして出力する。これが、2つ目の6列変換データ[4:0]となる。図19には、2つ目の6列変換データ[5:0]として、“00”(16進表記)、すなわち、“000000”(2進表記)を示している。これは、図10に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の9〜4ビット目に相当する。

【0253】

次に、RDENCNT=1、かつ、RD_TIM=‘H’のタイミングで、リードイネーブル生成回路170は、RAM_EN(3)〜RAM_EN(0)およびRAM_EN(15)〜RAM_EN(14)を‘H’としてRAM_EN[15:0]を出力する。つまり、リードイネーブル生成回路170は、リードアドレス生成回路160に対して、次の選択先となるRAM(3)〜RAM(0)およびRAM_EN(15)〜RAM_EN(14)におけるリードアドレスを+1カウントアップするタイミングを出力している。

【0254】

次に、リードアドレス生成回路160は、RAM(3)〜RAM(0)のリードアドレスを、それまでの255を+1カウントアップして0に更新する。また、リードアドレス生成回路160は、RAM(15)〜RAM(14)のリードアドレスを、それまでの0を+1カウントアップして1に更新する。この時点で、RAM(15)〜RAM(14)のリードアドレスは、1に設定され、RAM(13)〜RAM(0)のリードアドレスは、0に設定されている。

【0255】

次に、データセレクト回路181は、新たに設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=2であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(3)〜RAM_SEL(0)およびRAM_SEL(15)〜RAM_SEL(14)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[3:0][15:14]を選択する。

【0256】

次に、リタイミング回路182は、RDENCNT=2、かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[3:0][15:14]をリタイミングして出力する。これが、3つ目の6列変換データ[4:0]となる。図19には、3つ目の6列変換データ[5:0]として、“00”(16進表記)、すなわち、“000000”(2進表記)を示している。これは、図10に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の3〜0ビット目、および、2つ目の16列入力データの一例“1001”(16進表記)、すなわち、”0001 0000 0000 0001”(2進表記)の15〜14ビット目に相当する。

【0257】

このようにして、6列変換モードでは、RDENCNTのカウント値が0〜7を繰り返す。そして、リードデータセレクト生成回路150は、RDENCNTのカウント値が変化すると、RAM(15)〜RAM(0)の16個のRAMのうち選択対象となる6つのRAMを示すよう、RAM_SEL[15:0]のうち‘H’となる6ビットを順次切り替える。また、リードイネーブル生成回路170は、RD_TIM信号が有効となる毎に、RDENCNTのカウント値の次の変化のタイミングで更新する6本のリードアドレスを示すよう、RAM_EN[15:0]のうち‘H’となる6ビットを順次切り替える。そして、リードアドレス生成回路160は、RAM_EN[15:0]が示すRAM(j)におけるリードアドレスをカウントアップする。そして、データセレクト・リタイミング回路180は、RAM_SEL[15:0]およびリードアドレスに基づいて、6列変換データを選択出力していく。

【0258】

このようにして出力される6列変換データは、図20に示すとおりとなる。図20において、i−jは、i番目に入力されたライトデータのjビット目のデータを示している。つまり、1番目のライトデータの15〜10ビット目までの6ビットのデータが、1つ目の6列変換データであることを表している。

【0259】

以上のように動作することにより、6列変換モードでは、列変換回路10は、16列入力データ3つ分を1単位として、ライト動作およびリード動作を繰り返していく。これは、16列入力データ3つ分の48ビットが変換後の列数6で割り切れるためである。このとき、列変換回路10は、任意の3つの16列入力データのライト動作の開始から、該3つの16列入力データを6列変換データに変換して順次出力するリード動作の開始までを一定期間に保つように動作している。

【0260】

以上で、6列変換モードにおける列変換回路10の動作の説明を終了する。

【0261】

<7列変換モードにおけるリード動作>

次に、7列変換モードにおけるリード側のタイミングチャートを図21に示す。

【0262】

ここでは、7列変換モードにおける列変換回路10の動作が、2列変換モードにおける動作と異なる点を中心に述べる。

【0263】

まず、リードデータ先頭パルスが有効‘H’となると、列変換回路10はリード動作を開始する。

【0264】

リードイネーブルカウンタRDENCNTの最大カウント値は、7列変換モードでは、15にセットされる。RDENCNTの初期化およびカウントアップのタイミングは、2列変換モードの場合と同様である。

【0265】

また、16本のリードアドレスの初期値は、2列変換モードの場合と異なる。リードデータ先頭パルス有効時に、RAM(15)〜RAM(9)のリードアドレスは、0に初期設定される。また、RAM(8)〜RAM(0)のリードアドレスは、255に初期設定される。これらの値は、前述のように、表5に示した16個のカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値である。

【0266】

次に、データセレクト回路181は、列変換先頭パルスが有効になると、初期設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=0であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(15)〜RAM_SEL(9)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[15:9]を選択する。

【0267】

次に、リタイミング回路182は、RDENCNT=0かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[15:9]をリタイミングして出力する。これが、1つ目の7列変換データ[6:0]となる。図21には、1つ目の7列変換データ[6:0]として、“08”(16進表記)、すなわち、“0001000”(2進表記)を示している。これは、図11に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の15〜9ビット目に相当する。

【0268】

次に、RDENCNT=0、かつ、RD_TIM=‘H’のタイミングで、リードイネーブル生成回路170は、RAM_EN(8)〜RAM_EN(2)を‘H’としてRAM_EN[15:0]を出力する。つまり、リードイネーブル生成回路170は、リードアドレス生成回路160に対して、次の選択先となるRAM(8)〜RAM(2)におけるリードアドレスを+1カウントアップするタイミングを出力している。

【0269】

次に、リードアドレス生成回路160は、RAM(8)〜RAM(2)のリードアドレスを、それまでの255を+1カウントアップして0に更新する。この時点で、RAM(15)〜RAM(2)のリードアドレスは、0に設定され、RAM(1)〜RAM(0)のリードアドレスは、255に設定されている。

【0270】

次に、データセレクト回路181は、新たに設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=1であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(8)〜RAM_SEL(2)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[8:2]を選択する。

【0271】

次に、リタイミング回路182は、RDENCNT=1、かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[8:2]をリタイミングして出力する。これが、2つ目の7列変換データ[6:0]となる。図21には、2つ目の7列変換データ[6:0]として、“00”(16進表記)、すなわち、“0000000”(2進表記)を示している。これは、図11に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の8〜2ビット目に相当する。

【0272】

次に、RDENCNT=1、かつ、RD_TIM=‘H’のタイミングで、リードイネーブル生成回路170は、RAM_EN(1)〜RAM_EN(0)およびRAM_EN(15)〜RAM_EN(11)を‘H’としてRAM_EN[15:0]を出力する。つまり、リードイネーブル生成回路170は、リードアドレス生成回路160に対して、次の選択先となるRAM(1)〜RAM(0)およびRAM_EN(15)〜RAM_EN(11)におけるリードアドレスを+1カウントアップするタイミングを出力している。

【0273】

次に、リードアドレス生成回路160は、RAM(1)〜RAM(0)のリードアドレスを、それまでの255を+1カウントアップして0に更新する。また、リードアドレス生成回路160は、RAM(15)〜RAM(11)のリードアドレスを、それまでの0を+1カウントアップして1に更新する。この時点で、RAM(15)〜RAM(11)のリードアドレスは、1に設定され、RAM(10)〜RAM(0)のリードアドレスは、0に設定されている。

【0274】

次に、データセレクト回路181は、新たに設定された16個のリードアドレス値を用いて、リードCLKの立ち上がりエッジにより、RAM(15)〜RAM(0)からRAM格納データ[15:0]を読み出す。このとき、RDENCNT=2であるため、リードデータセレクト生成回路150から出力されるリードデータセレクト信号RAM_SEL[15:0]のうち、RAM_SEL(1)〜RAM_SEL(0)およびRAM_SEL(15)〜RAM_SEL(11)が有効‘H’となっている。そこで、データセレクト回路181は、RAM_SEL[15:0]にしたがって、RAM格納データ[15:0]のうち、RAM格納データ[1:0][15:11]を選択する。

【0275】

次に、リタイミング回路182は、RDENCNT=2、かつ、RD_TIM=‘H’のタイミングで、リードCLKの立ち上がりエッジにより、RAM格納データ[1:0][15:11]をリタイミングして出力する。これが、3つ目の7列変換データ[6:0]となる。図21には、3つ目の7列変換データ[6:0]として、“02”(16進表記)、すなわち、“0000010”(2進表記)を示している。これは、図11に示した1つ目の16列入力データの一例“1000”(16進表記)、すなわち、”0001 0000 0000 0000”(2進表記)の1〜0ビット目と、図11に示した2つ目の16列入力データの一例“1001”(16進表記)、すなわち、”0001 0000 0000 0001”(2進表記)の15〜11ビット目に相当する。

【0276】

このようにして、7列変換モードでは、RDENCNTのカウント値が0〜15を繰り返す。そして、リードデータセレクト生成回路150は、RDENCNTのカウント値が変化すると、RAM(15)〜RAM(0)の16個のRAMのうち選択対象となる7つのRAMを示すよう、RAM_SEL[15:0]のうち‘H’となる7ビットを順次切り替える。また、リードイネーブル生成回路170は、RD_TIM信号が有効となる毎に、RDENCNTのカウント値の次の変化のタイミングで更新する7本のリードアドレスを示すよう、RAM_EN[15:0]のうち‘H’となる7ビットを順次切り替える。そして、リードアドレス生成回路160は、RAM_EN[15:0]が示すRAM(j)におけるリードアドレスをカウントアップする。そして、データセレクト・リタイミング回路180は、RAM_SEL[15:0]およびリードアドレスに基づいて、7列変換データを選択出力していく。

【0277】

このようにして出力される7列変換データは、図22に示すとおりとなる。図22において、i−jは、i番目に入力されたライトデータのjビット目のデータを示している。つまり、1番目のライトデータの15〜9ビット目までの7ビットのデータが、1つ目の7列変換データであることを表している。

【0278】

以上のように動作することにより、7列変換モードでは、列変換回路10は、16列入力データ7つ分を1単位として、ライト動作およびリード動作を繰り返していく。これは、16列入力データ7つ分の112ビットが変換後の列数7で割り切れるためである。このとき、列変換回路10は、任意の7つの16列入力データのライト動作の開始から、該7つの16列入力データを7列変換データに変換して順次出力するリード動作の開始までを一定期間に保つように動作している。

【0279】

以上で、7列変換モードにおける列変換回路10の動作の説明を終了する。

【0280】

<列変換モードの拡張>

次に、列変換回路10の列変換モードを拡張する場合を考える。例えば、列変換回路10を、新たに8列変換モード、9列変換モード、10列変換モードに対応させる。このとき、列変換回路10は、ライト側の回路を列変換モードに関わらず共有しているので、新たな回路をライト側に必要としない。ただし、列変換回路10には、8列、9列、10列の各変換モードに応じたライトデータイネーブル信号が入力されるようにする。

【0281】

また、この場合、列変換回路10は、リード側で、リードイネーブル信号RAM_EN[15:0]およびリードデータセレクト信号RAM_SEL[15:0]を列変換モードに応じて生成する必要がある。したがって、図23に破線で示すように、列変換回路10は、リードイネーブル生成回路170に、8列変換リードイネーブル生成回路170fと、9列変換リードイネーブル生成回路170gと、10列変換リードイネーブル生成回路170hとをさらに含めるようにすればよい。そして、リードアドレスの初期値は、8列、9列、10列の各変換モードに応じて適宜設定されればよい。また、図23に破線で示すように、列変換回路10は、リードデータセレクト生成回路150に、8列変換リードデータセレクト生成回路150fと、9列変換リードデータセレクト生成回路150gと、10列変換リードデータセレクト生成回路150hとをさらに含めるようにすればよい。そして、リードデータセレクト信号の初期値は、8列、9列、10列の各変換モードに応じて適宜設定されればよい。

【0282】

<効果>

次に、本発明の第2の実施の形態の効果について述べる。

【0283】

本実施の形態としての列変換回路は、論理回路の増大を抑えながら、変換後の列数を容易に拡張可能である。

【0284】

その理由は、本実施の形態において、ライトアドレス生成回路およびライトデータ制御回路の構成および動作は、列変換モードの設定に依存することがないからである。どの列変換モードにおいても、ライトアドレス生成回路は、同一の範囲(0〜255)の値を繰り返すライトアドレスを生成する。また、どの列変換モードにおいても、ライトデータ制御回路は、16列入力データを、16個のRAMにおいてライトアドレスが示す位置に格納する。これにより、本実施の形態としての列変換回路は、列変換モードを拡張しても、ライト側に新たな回路を必要としない。

【0285】

また、さらなる理由として、本実施の形態において、リードアドレス生成回路およびデータセレクト・リタイミング回路の構成および動作は、列変換モードの設定に依存することがないからである。どの列変換モードにおいても、リードアドレス生成回路は、リードイネーブル信号にしたがうことによりN個ずつリードアドレスを更新する。また、どの列変換モードにおいても、データセレクト・リタイミング回路は、リードデータセレクト信号にしたがうことにより、16個のRAMのうちN個のRAMにおいてリードアドレスの示す位置のデータを選択出力するからである。そして、本実施の形態としての列変換回路は、列変換モードを拡張するためには、拡張列数に応じたリードイネーブル信号を生成するリードイネーブル生成回路、および、拡張列数に応じたリードデータセレクト信号を生成するリードデータセレクト生成回路を増設するだけでよい。このようなリードイネーブル生成回路およびリードデータセレクト生成回路の増設は、データセレクト回路の論理段数の増強等と比較して少ない増設量で済む。

【0286】

また、本実施の形態としての列変換回路は、所定サイズの16個のメモリを使用し、ライト動作およびリード動作を一定間隔に保ちながら実行することにより、より多くのデータを溜めることができる。したがって、本実施の形態としての列変換回路は、16列の入力データの入力開始後、リード動作を開始するタイミングの自由度を向上させることになる。

【0287】

なお、本実施の形態としての列変換回路は、さらに各メモリにおけるリードアドレスをモニタリングするリードアドレスモニタリング部を備えてもよい。これにより、本実施の形態としての列変換回路は、変換後の列数を容易に拡張可能な列変換回路の実行処理の観測を容易にすることができる。

【0288】

なお、本実施の形態の説明において、16列入力データを、2列、4列、5列、6列、および、7列に変換する列変換回路を中心に説明を行ったが、本発明において、MおよびNの値を限定するものではない。その他の列数Mの入力データに対応させる場合、列変換回路は、各種カウンタの初期値や最大値を適切な値に設定する。また、この場合、列変換回路は、MビットのうちRDENCNT値に応じたNビットを有効とするリードイネーブル信号を生成するリードイネーブル生成回路を、各列変換モードに応じて備えるようにする。また、この場合、列変換回路は、MビットのうちRDENCNT値に応じたNビットを有効とするリードデータセレクト信号を生成するリードデータセレクト生成回路を、各列変換モードに応じて備えるようにする。これにより、本実施の形態としての列変換回路は、M列の入力データを多様な列数に変換する列変換モードを、容易に拡張可能となる。

【0289】

また、本発明は、上述した各実施の形態に限定されず、様々な態様で実施されることが可能である。

【符号の説明】

【0290】

1、10 列変換回路

11 列変換モード設定部

12、120〜12M−1 メモリ

13 ライトアドレス生成部

14 ライトデータ制御部

15 選択信号生成部

16 リードアドレス生成部

17 リードアドレス更新制御部

18 データ選択出力部

130 ライトアドレス生成回路

140 ライトデータ制御回路

150 リードデータセレクト生成回路

150a〜150h N列変換リードデータセレクト生成回路

160 リードアドレス生成回路

170 リードイネーブル生成回路

170a〜170h N列変換リードイネーブル生成回路

180 データセレクト・リタイミング回路

181 データセレクト回路

182 リタイミング回路

90 列変換回路

91 ライトデータ制御回路

92、920〜924 ライトバッファ

93 リードデータ制御回路

94 データセレクト回路

【技術分野】

【0001】

本発明は、ディジタル信号の伝送において信号列数の変換を行う列変換回路に関する。

【背景技術】

【0002】

ディジタル信号の伝送において、信号列数の変換を行う列変換回路が知られている。このような列変換回路は、例えば、多値変復調通信方式によるディジタル信号の伝送において用いられる。

【0003】

このような列変換回路の一例が、特許文献1に記載されている。特許文献1に記載された列変換回路は、第1のクロック信号により入力されるM列の入力データを、M/N倍の周波数の第2のクロック信号によりN列に変換して出力する。この列変換回路は、第1および第2のクロック信号のうち高周波数側のクロック信号を発生する発振回路と、この発振回路からのクロック信号をMとNの比で分周して低周波数側のクロック信号とする分周回路と、M列をN列に変換する回路とを備えている。

【0004】

また、このような列変換回路の他の一例を図24に示す。

【0005】

図24において、列変換回路90は、16列入力データを2列、4列、または5列に変換する回路である。この列変換回路90は、ライトデータ制御回路91と、5個のライトバッファ(16bit FF)920〜924(以降、総称してライトバッファ92ともいう)と、リードデータ制御回路93と、データセレクト回路94とを含む。1つのライトバッファ92は、16ビットのデータを格納可能なバッファ(フリップフロップ回路)である。図24に示すQ(i)は、各ライトバッファ92に保持される各ビットのデータを表している。また、図24に示すComb(i)は、各Q(i)から読み出されるデータを表している。また、この列変換回路90では、2列、4列、または5列のいずれの列数に変換するかを示す列変換モード設定信号が設定される。

【0006】

ライトデータ制御回路91は、列変換モードに応じて、16列入力データの書き込み先のライトバッファ92の選択およびその書き込みタイミングを制御する。具体的には、ライトデータ制御回路91は、列変換モードに応じて、ライトEN(i)信号を所定のタイミングで有効(High:以降、‘H’とも記載する)にする。有効となっているライトEN(i)に対応したライトバッファ92iには、16列入力データが格納される。以降、16列入力データを、“ライトデータ[15:0]”とも記載する。また、以降において、データの名称の後に記載する“[m−1:0]”は、そのデータがmビットであることを表す。また、そのデータの名称の後に“[i:j]”と記載した場合は、そのmビットのデータのうち、最下位を0ビット目と数えて、下位からiビット目からjビット目までのデータを表しているものとする。

【0007】

例えば、2列変換モードであれば、ライトデータ制御回路91は、ライトEN(0)およびライトEN(1)を、所定のタイミングで交互に有効にする。これにより、2列変換モードであれば、ライトバッファ920、921に、ライトデータ[15:0]が順次格納される。

【0008】

リードデータ制御回路93は、列変換モードに応じて、ライトバッファ92に格納されたデータの読み出しタイミングを制御する。具体的には、リードデータ制御回路93は、リードカウントRDENCNT(0から列変換モードに応じた上限値までをカウント)を生成する。例えば、2列変換モードであれば、リードデータ制御回路93は、0〜15までのリードカウントを生成する。

【0009】

データセレクト回路94は、リードデータ制御回路93の制御の基に、ライトバッファ92に格納されたデータを、列変換モードに応じた列数ずつ選択して出力する。具体的には、データセレクト回路94は、リードカウントにしたがって、ライトバッファ92iに格納されたデータを、列変換モードに対応したN列(2列、4列、または、5列)に並び替える。例えば、2列変換モードであれば、データセレクト回路94は、ライトバッファ920のQ(15)〜Q(0)およびライトバッファ921のQ(31)〜Q(16)の計32ビットから2列ずつを、リードカウント0〜15にしたがって順次選択して出力する。

【0010】

このような図24の列変換回路90の動作について、図面を参照して説明する。

【0011】

まず、2列変換モードにおけるライト側タイミングチャートを図25に示す。ライト側は、ライトCLKにしたがって動作する。

【0012】

ライトデータ先頭パルスは、16列入力データの入力開始時に有効‘H’となる信号である。

【0013】

ライトデータイネーブル信号は、ライトデータ[15:0]のライトタイミングを制御する信号である。ライトデータイネーブル信号は、列変換モード設定信号に応じた所定のタイミングで有効‘H’となる。例えば、2列変換モードの場合、16CLK毎に1CLKの期間有効‘H’となる。

【0014】

ライトデータ[15:0]は、16列入力データである。図示の“1000(hex)”、“1001(hex)”は、16列入力データの一例を16進表記したものである。

【0015】

ライトアドレスカウンタは、ライトデータ制御回路91において、0から最大カウント値までを繰り返しカウントするカウンタである。この最大カウント値は、列変換モードに応じて設定される。図25では、2列変換モードなので、ライトアドレスカウンタの最大カウント値として1がセットされている。ライトアドレスカウンタは、ライトデータ先頭パルスおよびライトデータイネーブル信号が共に有効‘H’時に、ライトCLKに同期して0に初期化される。そして、ライトデータイネーブル信号が有効となる度に、ライトCLKに同期して1へのカウントアップおよび0への初期化を繰り返す。

【0016】

ライトEN(i)信号は、ライトアドレスカウンタがiに変化すると、ライトCLKに同期して‘H’となる。

【0017】

ライトデータ[15:0]は、ライトEN(i)が‘H’となったタイミングで、ライトCLKの立ち上がりエッジでライトバッファ92iに格納される。

【0018】

このようにして、2列変換モードでは、ライトデータ[15:0]は、ライトバッファ920およびライトバッファ921に順次格納される。

【0019】

次に、2列変換モードにおけるリード側タイミングチャートを図26に示す。リード側は、リードCLKにしたがって動作する。リードCLKは、ライトCLKの2倍の周波数で動作するクロック信号である。

【0020】

リードデータ先頭パルスは、リード動作の開始を示している。リードデータ先頭パルスは、ライトデータ先頭パルス‘H’およびライトEN(0)‘H’の論理積をライトCLKの立ち上がりエッジで1回サンプリングした信号を、リードCLKに乗せ換えて生成される。

【0021】

リードCLKカウンタは、リードデータ先頭パルスが有効時に、リードCLKに同期して0に初期化される。また、リードCLKカウンタは、リードCLKに同期して、0〜3までを繰り返しカウントする。

【0022】

リードアドレスカウンタRDENCNTは、リードデータ先頭パルスが有効時に、リードCLKに同期して0に初期化される。また、リードアドレスカウンタは、リードCLKカウンタが3となった時、リードCLKに同期して、+1のカウントアップを実行する。また、2列変換モードにおいて、リードアドレスカウンタRDENCNTの最大カウント値は15にセットされる。つまり、リードアドレスカウンタは、0〜15までを繰り返しカウントする。

【0023】

このリードアドレスカウンタRDENCNTは、データセレクト回路94において選択するデータを示している。例えば、データセレクト回路94は、リードアドレスカウンタが0の時は、ライトバッファ920のComb(15−14)を選択し、リードアドレスカウンタが1の時は、Comb(13−12)を選択する。同様に、データセレクト回路94は、リードアドレスカウンタが7までは、ライトバッファ920に格納されたデータの2つを選択する。また、データセレクト回路94は、リードアドレスカウンタが8の時は、ライトバッファ921のComb(31−30)を選択し、リードアドレスカウンタが9の時は、Comb(29−28)を選択する。同様に、データセレクト回路94は、リードアドレスカウンタが15までは、ライトバッファ921に格納されたデータの2つを選択する。そして、データセレクト回路94は、リードデータ先頭パルスに基づいて生成される列変換後先頭パルスが有効となると、選択した2列のデータを順次出力する。

【0024】

次に、このような図24の列変換回路90の4列変換モードにおける動作について、タイミングチャート図27〜図28を用いて説明する。

【0025】

4列変換モードでも、2列変換モードと同様に、2つのライトバッファ920および921が用いられる。したがって、図27において、4列変換モードにおけるライト側の動作は、2列変換モードにおける動作とほぼ同様である。ただし、4列変換モードでは、ライトデータイネーブル信号は、8CLK毎に1CLK期間有効‘H’となる。

【0026】

次に、4列変換モードにおけるリード側タイミングチャートを図28に示す。

【0027】

リードアドレスカウンタRDENCNTの最大カウント値は、4列変換モードにおいて7にセットされる。つまり、リードアドレスカウンタRDENCNTは、リードデータ先頭パルスが有効時にリードCLKに同期して0に初期化された後、0〜7までを繰り返しカウントする。リードアドレスカウンタのカウントアップは、2列変換モードと同様、リードCLKカウンタが3となった時に実行される。

【0028】

4列変換モードにおいて、データセレクト回路94は、リードアドレスカウンタが0の時は、ライトバッファ920のComb(15−12)を選択し、リードアドレスカウンタが1の時は、Comb(11−8)を選択する。同様に、データセレクト回路94は、リードアドレスカウンタが3までは、ライトバッファ920に格納されたデータの4つを選択する。また、データセレクト回路94は、リードアドレスカウンタが4の時は、ライトバッファ921のComb(31−28)を選択し、リードアドレスカウンタが5の時は、Comb(27−24)を選択する。同様に、データセレクト回路94は、リードアドレスカウンタが7までは、ライトバッファ921に格納されたデータの4つを選択する。そして、データセレクト回路94は、リードデータ先頭パルスに基づいて生成される列変換後先頭パルスが有効となると、選択した4列の出力データを順次出力する。

【0029】

同様に、図24に示した列変換回路90は、5列変換モードにおいては、ライトバッファ920〜924を用いる。すなわち、5列変換モードにおいて、ライトアドレスカウンタの最大カウント値は、4にセットされる。そして、ライトデータ制御回路91は、ライトEN(0)〜ライトEN(4)のうち1つずつを順次有効‘H’に切り替えていく。そして、ライトEN(0)〜ライトEN(4)にしたがい、ライトバッファ920〜924にライトデータ[15:0]が順次格納される。

【0030】

また、5列変換モードにおいて、リード側では、リードアドレスカウンタの最大カウント値は15にセットされる。つまり、リードアドレスカウンタは、0〜15までを繰り返しカウントする。そして、データセレクト回路94は、リードアドレスカウンタの値にしたがって、ライトバッファ920のComb(15−0)〜ライトバッファ924のComb(79−64)までの計80ビットから5列ずつを、リードカウント0〜15にしたがって順次選択して出力する。

【0031】

このように、図24に示した列変換回路90は、変換後の列数(列変換モード)に応じた個数のライトバッファ92を必要とする。これは、16ビットの入力データが格納されたライトバッファ92から、変換後の列数であるNビットずつ選択出力していくためには、16ビット×ライトバッファの個数n=M×nビットが、Nで割り切れるだけの個数nのライトバッファを必要とするからである。ただし、図24に示した列変換回路90は、このように算出された個数nが1となった場合であっても、最低2つのライトバッファ92を必要としている。これは、格納されたデータが読み出されないうちに次のデータで上書きされることを防ぐためである。

【先行技術文献】

【特許文献】

【0032】

【特許文献1】特開平5-218999号公報

【発明の概要】

【発明が解決しようとする課題】

【0033】

ここで、図24に示した列変換回路90において、さらに他の列変換モード(例えば、6〜16列変換)に機能拡張することを考える。列変換回路90は、列変換モードの拡張のためには、列変換モードに応じた個数のライトバッファ92を必要とする。

【0034】

例えば、16列入力データに対して、6列変換機能を実現させるには、3つのライトバッファ92が必要となる。また、16列入力データに対して、7列変換機能を実現させるには、7つのライトバッファ92が必要となる。また、16列入力データに対して、8列変換機能を実現させるには、2つのライトバッファ92が必要となる。また、16列入力データに対して、9列変換モードを実現させるには、9つのライトバッファ92が必要となる。また、16列入力データに対して、10列変換モードを実現させるには、5つのライトバッファ92が必要となる。

【0035】

このように、図24に示した列変換回路90では、16ビット入力データに対して変換可能な列数(列変換モード)を拡張するためには、ライト側における論理回路の増大が問題となる。

【0036】

また、図24に示した列変換回路90において、変換可能な列数の増加に伴い、データセレクト回路94におけるデータ選択の論理段数が膨大に膨れ上がる。したがって、図24に示した列変換回路90では、変換可能な列数の拡張には、リード側における論理回路の増大も問題となる。

【0037】

このように、図24の列変換回路90では、変換可能な列数の拡張には、論理回路の多大な増加が必要となるという課題があった。

【0038】

また、特許文献1に記載された列変換回路において、多様な列数Nへ変換可能な列変換モードを搭載することを考える。例えば、特許文献1の図1には、4列の入力データを1列に変換する回路が図示されている。この列変換回路において、変換可能な列数を拡張するためには、メモリに入力されるバス幅の増加、分周回路の増設、列変換回路の複雑化が必要となる。したがって、特許文献1においても、多様な列数へ変換可能な列変換モードを拡張する際の、論理回路の増大を抑制することは難しかった。

【0039】

本発明は、上述の課題を解決するためになされたもので、変換後の列数を設定する列変換モードを搭載した列変換回路において、論理回路の増大を抑えながら変換後の列数を容易に拡張可能な列変換回路を提供することを目的とする。

【課題を解決するための手段】

【0040】

本発明の列変換回路は、M(Mは正の整数)列の入力データをN(NはM>Nを満たす正の整数)列に変換する列変換回路であって、変換後の列数Nを表す列変換モードを設定する列変換モード設定部と、少なくともM個の所定サイズのメモリと、前記M個の各メモリにおけるデータ書き込み位置を示すライトアドレスを生成するとともに、前記M個の各メモリにおいて該ライトアドレスの示す位置に前記M列の入力データの各ビットが格納されると、次のM列の入力データのデータ書き込み位置を示すよう前記ライトアドレスを更新するライトアドレス生成部と、前記M列の入力データの各ビットを、前記M個の各メモリの前記ライトアドレスの示す位置に書き込むよう制御するライトデータ制御部と、前記M個のメモリのうち選択対象となるN個を示す選択信号を前記列変換モードに応じて生成するとともに、該選択信号が示すN個のメモリからデータが出力されると、次の他のN個を示すよう、前記列変換モードに応じて前記選択信号を更新する選択信号生成部と、前記選択信号が示すN個の前記各メモリにおけるデータ読み出し位置を示すリードアドレスを生成するリードアドレス生成部と、前記選択信号の更新に伴い、前記リードアドレス生成部を前記列変換モードに応じて制御するリードアドレス更新制御部と、前記M個のメモリから、前記選択信号および前記リードアドレスにしたがってN列のデータを読み出して出力するデータ選択出力部と、を備える。

【0041】

また、本発明の列変換方法は、少なくともM(Mは正の整数)個の所定サイズのメモリを用いて、変換後の列数N(NはM>Nを満たす正の整数)を表す列変換モードを設定し、前記M個の各メモリにおけるデータ書き込み位置を示すライトアドレスを生成し、前記M列の入力データの各ビットを、前記M個の各メモリの前記ライトアドレスの示す位置に書き込み、前記M個の各メモリにおいて次のM列の入力データのデータ書き込み位置を示すよう前記ライトアドレスを更新していきながら、以降のM列の入力データの書き込みを順次行い、前記M個のメモリのうち選択対象となるN個を示す選択信号を前記列変換モードに応じて生成し、前記選択信号が示すN個の前記各メモリにおけるデータ読み出し位置を示すリードアドレスを生成し、前記M個のメモリから、前記選択信号および前記リードアドレスにしたがってN列のデータを読み出して出力し、前記M個のメモリのうち次の選択対象となる他のN個を示すよう、前記列変換モードに応じて前記選択信号を更新し、更新された選択信号が示すN個の前記各メモリにおけるデータ読み出し位置を示すよう、前記列変換モードに応じて前記リードアドレスを生成し、選択信号が更新される毎に、該選択信号、および、該選択信号に応じて生成されたリードアドレスにしたがって、以降のN列のデータの出力を行う。

【発明の効果】

【0042】

変換後の列数を設定する列変換モードを搭載した列変換回路において、論理回路の増大を抑えながら変換後の列数を容易に拡張可能な列変換回路を提供することができる。

【図面の簡単な説明】

【0043】

【図1】本発明の第1の実施の形態としての列変換回路の構成を示すブロック図である。

【図2】本発明の第2の実施の形態としての列変換回路の構成を示す図である。

【図3】本発明の第2の実施の形態としての列変換回路に入力される16列入力データを模式的に説明する図である。

【図4】本発明の第2の実施の形態におけるメモリのデータ格納領域を模式的に説明する図である。

【図5】本発明の第2の実施の形態におけるリードアドレス生成回路の構成を示す図である。

【図6】本発明の第2の実施の形態におけるリードイネーブル生成回路およびリードデータセレクト生成回路の構成を示す図である。

【図7】本発明の第2の実施の形態としての列変換回路の2列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図8】本発明の第2の実施の形態としての列変換回路の4列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図9】本発明の第2の実施の形態としての列変換回路の5列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図10】本発明の第2の実施の形態としての列変換回路の6列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図11】本発明の第2の実施の形態としての列変換回路の7列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図12】本発明の第2の実施の形態としての列変換回路によって16列入力データの各ビットが16個のメモリに格納されることを説明する模式図である。

【図13】本発明の第2の実施の形態としての列変換回路の2列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図14】本発明の第2の実施の形態としての列変換回路が出力する2列変換データを模式的に説明する図である。

【図15】本発明の第2の実施の形態としての列変換回路の4列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図16】本発明の第2の実施の形態としての列変換回路が出力する4列変換データを模式的に説明する図である。

【図17】本発明の第2の実施の形態としての列変換回路の5列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図18】本発明の第2の実施の形態としての列変換回路が出力する5列変換データを模式的に説明する図である。

【図19】本発明の第2の実施の形態としての列変換回路の6列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図20】本発明の第2の実施の形態としての列変換回路が出力する6列変換データを模式的に説明する図である。

【図21】本発明の第2の実施の形態としての列変換回路の7列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図22】本発明の第2の実施の形態としての列変換回路が出力する7列変換データを模式的に説明する図である。

【図23】本発明の第2の実施の形態としての列変換回路に8列変換モード、9列変換モード、および10列変換モードを拡張する場合の回路構成を示す図である。

【図24】関連技術の列変換回路の構成を示す図である。

【図25】関連技術の列変換回路の2列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図26】関連技術の列変換回路の2列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【図27】関連技術の列変換回路の4列変換モードにおけるライト側の動作を説明するタイミングチャートである。

【図28】関連技術の列変換回路の4列変換モードにおけるリード側の動作を説明するタイミングチャートである。

【発明を実施するための形態】

【0044】

以下、本発明の実施の形態について、図面を参照して詳細に説明する。

【0045】

(第1の実施の形態)

本発明の第1の実施の形態としての列変換回路1のブロック構成を図1に示す。

【0046】

図1において、列変換回路1は、列変換モード設定部11と、M個のメモリ120〜12Mー1(以下、総称してメモリ12ともいう)と、ライトアドレス生成部13と、ライトデータ制御部14と、選択信号生成部15と、リードアドレス生成部16と、リードアドレス更新制御部17と、データ選択出力部18とを備える。列変換回路1は、入力されるM列のデータを、N列に変換して出力する回路である。列変換回路1において、入力データの列数Mはあらかじめ定められている。また、出力列数Nは、あらかじめ定められた1つ以上の列数から選択可能となっている。なお、本実施の形態において、MおよびNは正の整数であり、M>Nである。

【0047】

列変換モード設定部11は、変換後の列数Nを表す列変換モードを設定する。つまり、列変換回路1は、M列の入力データを、列変換モード設定部11において設定された列変換モードが示すN列に変換する。

【0048】

各メモリ12は、所定サイズWを有している。例えば、各メモリ12は、256ビットのRAM(Random Access Memory)によって構成されていてもよい。M個の各メモリ12には、M列の入力データの各ビットが格納される。つまり、M個のメモリ12は、M列の入力データを、W個まで格納することが可能である。

【0049】

ライトアドレス生成部13は、M個の各メモリ12において共通のデータ書き込み位置を示すライトアドレスを生成する。もし、各メモリ12のサイズが256ビットであれば、ライトアドレスは、1ビット目〜256ビット目までのいずれかを示す情報である。M個の各メモリ12において、ライトアドレス生成部13が生成したライトアドレスが示す位置には、M列の入力データの各ビットが格納される。

【0050】

また、ライトアドレス生成部13は、M個の各メモリ12のライトアドレスが示す位置にM列の入力データの各ビットが格納されると、次のM列の入力データの書き込み位置を示すようライトアドレスを更新する。例えば、ライトアドレスがiビット目を示しているとき、次のライトアドレスは、i+1ビット目を示すものであってもよい。

【0051】

ライトデータ制御部14は、M列の入力データの各ビットを、各メモリ12のライトアドレスの示す位置に書き込む。例えば、ライトアドレスが1ビット目を示している場合、ライトデータ制御部14は、M個の各メモリ12の1ビット目(合計Mビット)に、M列の入力データを書き込む。

【0052】

選択信号生成部15は、M個のメモリ12のうちN個を示す選択信号を生成する。このNは、列変換モード設定部11において設定された列変換モードが示す数値である。つまり、選択信号生成部15は、列変換モード設定部11の設定内容に応じて動作する。

【0053】

また、選択信号生成部15は、選択信号が示すN個のメモリ12からデータが出力されると、次の他のN個を示すよう選択信号を更新する。例えば、Mが16でNが2である場合、選択信号生成部15が、ある時点でメモリ1215〜1214を示す選択信号を生成していたとする。そして、このメモリ1215〜1214からデータが出力されると、選択信号生成部15は、次のメモリ1213〜1212を示す選択信号を生成する。また、選択信号生成部15は、全てのメモリ12を順次示す選択信号を生成した後は、再び最初に選択したメモリ12からを順次示す選択信号を生成していく。例えば、Mが16でNが4である場合、選択信号生成部15は、メモリ1215〜1212、メモリ1211〜128、メモリ127〜124、メモリ123〜120をそれぞれ示すよう、選択信号を順次更新した後、再びメモリ1215〜1212から順に示すよう、選択信号を更新していく。また、Mが16でNが5である場合、選択信号生成部15は、メモリ1215〜1211、メモリ1210〜126、メモリ125〜121をそれぞれ示すよう、選択信号を順次更新した後、メモリ120およびメモリ1215〜1212、メモリ1211〜127の順に示すよう、選択信号を更新していく。

【0054】

リードアドレス生成部16は、選択信号が示すN個の各メモリ12におけるリードアドレスを生成する。もし、各メモリ12のサイズが256ビットであれば、リードアドレスは、1ビット目〜256ビット目までのいずれかを示す情報である。このとき、リードアドレス生成部16は、選択信号が示すN個のメモリ12のうち、既に一旦リードアドレスを生成済みのメモリ12については、前回生成したリードアドレスの位置を次の位置に更新するようにする。例えば、前回のリードアドレスがiビット目を示しているとき、次のリードアドレスは、i+1ビット目であってもよい。

【0055】

リードアドレス更新制御部17は、リードアドレス生成部16を、列変換モードに応じて制御する。つまり、リードアドレス更新制御部17は、リードアドレス生成部16に対して、変換後の列数Nに応じて次にいずれのN個のメモリ12におけるリードアドレスを更新すればよいかを通知する。

【0056】

データ選択出力部18は、選択信号およびリードアドレスに基づいて、M個のメモリ12からN列のデータを読み出して出力する。つまり、データ選択出力部18は、M個のメモリ12のうち選択信号が示すN個のメモリ12において、各リードアドレスが示す各位置の計Nビットを選択出力する。

【0057】

以上のように構成された列変換回路1の動作について説明する。なお、列変換モード設定部11には、変換後の列数Nを表す列変換モードがあらかじめ設定されているものとする。

【0058】

まず、ライト側の動作について説明する。

【0059】

M列の入力データが列変換回路1に入力されると、列変換回路1はライト動作を開始する。

【0060】

ここでは、まず、ライトアドレス生成部13は、M個の各メモリ12におけるライトアドレスを生成する。ここで、最初に生成されるライトアドレスは、例えば、M個の各メモリ12における1ビット目を示すものであってもよい。

【0061】

次に、ライトデータ制御部14は、1つ目のM列の入力データの各ビットを、M個の各メモリ12のライトアドレスが示す位置に書き込む。

【0062】

次に、ライトアドレス生成部13は、M個の各メモリ12における次のデータ書き込み位置を示すようライトアドレスを更新する。ここで、更新されるライトアドレスは、例えば、前回の1ビット目に1を加算した2ビット目を示すものであってもよい。

【0063】

次に、ライトデータ制御部14は、2つ目のM列の入力データを、M個の各メモリ12のライトアドレスが示す位置に書き込む。

【0064】

このように、ライトアドレス生成部13により更新されるライトアドレスを用いて、ライトデータ制御部14は、M列の入力データをM個のメモリ12に書き込んでいく。

【0065】

次に、リード側の動作について説明する。

【0066】

1つ目のM列の入力データがM個のメモリ12に書き込まれた後、列変換回路1は、任意の時点からリード動作を開始する。

【0067】

ここでは、まず、選択信号生成部15は、M個のメモリ12のうち選択対象となるN個を示す選択信号を、列変換モードに応じて生成する。例えば、選択信号生成部15は、Mが16でNが2であれば、メモリ1215およびメモリ1214を示す選択信号を生成してもよい。

【0068】

次に、リードアドレス生成部16は、生成された選択信号が示すN個の各メモリ12におけるリードアドレスを生成する。例えば、リードアドレス生成部16は、メモリ1215およびメモリ1214の各1ビット目を示すリードアドレスを生成する。

【0069】

次に、データ選択出力部18は、M個のメモリ12から、選択信号およびリードアドレスにしたがって、N列のデータを読み出し、1つ目のN列変換データとして出力する。例えば、選択信号がメモリ1215およびメモリ1214を示しており、これらの各メモリにおけるリードアドレスが1ビット目を示している場合、データ選択出力部18は、メモリ1215およびメモリ1214の各1ビット目に格納されている合計2ビットのデータを、1つ目の2列変換データとして出力する。

【0070】

次に、選択信号生成部15は、M個のメモリ12のうち次の選択対象となる他のN個を示すよう、列変換モードに応じて選択信号を更新する。例えば、選択信号生成部15は、メモリ1213およびメモリ1212を示すよう選択信号を更新してもよい。

【0071】

次に、リードアドレス更新制御部17は、更新された選択信号が示すN個の各メモリ12におけるリードアドレスを生成するよう、リードアドレス生成部16に通知する。例えば、リードアドレス更新制御部17は、メモリ1213およびメモリ1212の各リードアドレスを生成するよう、リードアドレス生成部16に通知する。

【0072】

そして、リードアドレス生成部16は、リードアドレス更新制御部17の制御にしたがって、リードアドレスを生成する。例えば、リードアドレス生成部16は、メモリ1213およびメモリ1212の各1ビット目を示すリードアドレスを生成する。

【0073】

次に、データ選択出力部18は、M個のメモリ12から、選択信号およびリードアドレスにしたがって、N列のデータを読み出し、2つ目のN列変換データとして出力する。例えば、選択信号がメモリ1213およびメモリ1212を示しており、これらの各メモリにおけるリードアドレスが1ビット目を示している場合、データ選択出力部18は、メモリ1213およびメモリ1212の各1ビット目に格納されている合計2ビットのデータを、2つ目の2列変換データとして出力する。

【0074】

このようなリード動作を繰り返すことにより、列変換回路1は、1つ目のM列の入力データのMビットをN列変換して出力する。例えば、Mが16でNが2であれば、列変換回路1は、8つ目まで2列変換データを出力すると、1つ目の16列入力データの2列変換処理を終えたことになる。

【0075】

次に、選択信号生成部15は、M個のメモリ12のうち次の選択対象となるN個を示すよう、列変換モードに応じて選択信号を更新する。ここで、選択信号生成部15は、M個のメモリ12の全てを順次示す選択信号を生成済みなので、再度、最初のN個を示すよう選択信号を更新する。例えば、Mが16でNが2の場合について説明する。このとき、既にメモリ1215からメモリ120までの16個を順次示す選択信号を生成済みなので、選択信号生成部15は、再度メモリ1215およびメモリ1214を示すよう選択信号を更新する。

【0076】

次に、リードアドレス更新制御部17は、更新された選択信号が示すN個の各メモリ12におけるリードアドレスを更新するよう、リードアドレス生成部16に通知する。例えば、リードアドレス更新制御部17は、メモリ1215およびメモリ1214におけるリードアドレスを生成するよう、リードアドレス生成部16に通知する。

【0077】

そして、リードアドレス生成部16は、リードアドレス更新制御部17の制御にしたがって、リードアドレスを更新する。例えば、リードアドレス更新制御部17からメモリ1215およびメモリ1214のリードアドレス生成を通知された場合について説明する。この場合、リードアドレス生成部16は、既にこれらの各メモリについて1ビット目を示すリードアドレスを生成しているので、これらに1を加算して2ビット目を示すよう各リードアドレスを更新する。

【0078】

次に、データ選択出力部18は、M個のメモリ12から、選択信号およびリードアドレスにしたがって、N列のデータを読み出し、N列変換データとして出力する。例えば、選択信号がメモリ1215およびメモリ1214を示し、これらの各メモリにおけるリードアドレスが2ビット目を示している場合、データ選択出力部18は、メモリ1215およびメモリ1214の各2ビット目に格納されている合計2ビットのデータを、9つ目の2列変換データとして出力する。

【0079】

列変換回路1は、このようなリード動作を繰り返す。

【0080】

なお、上記動作の説明では、MがNで割り切れる(M=16、N=2)場合を例として説明を行ったが、これ以外の場合も、列変換回路1は同様に動作することにより列変換処理を行う。

【0081】

例えば、16列変換データを5列に変換する場合(M=16、N=5)の動作について説明する。この場合も、列変換回路1のライト側の動作は、上述の動作と同様である。

【0082】

また、この場合、リード動作において、選択信号生成部15は、メモリ12を5つずつ示すよう選択信号を更新していく。例えば、選択信号生成部15は、メモリ1215〜メモリ1211の5つ、メモリ1210〜メモリ126の5つ、メモリ125〜メモリ121の5つ、メモリ120およびメモリ1215〜メモリ1212の5つ、といった順に選択信号を更新していけばよい。

【0083】

そして、リードアドレス更新制御部17は、メモリ1215〜メモリ1211の5つ、メモリ1210〜メモリ126の5つ、メモリ125〜メモリ121の5つ、メモリ120およびメモリ1215〜メモリ1212の5つ、といった順に、リードアドレスを生成するよう、リードアドレス生成部16に通知していけばよい。ここで、リードアドレス生成部16は、メモリ120およびメモリ1215〜メモリ1212の5つにおけるリードアドレスを更新するよう通知された場合、メモリ1215については、1ビット目を示すリードアドレスを生成し、メモリ120〜メモリ123については、前回の1ビット目を更新して2ビット目を示すリードアドレスを生成するようにすればよい。

【0084】

そして、このとき、データ選択出力部18は、メモリ120の1ビット目およびメモリ1215〜メモリ1212の2ビット目の合計5ビットを、4つ目の5列変換データとして出力することになる。

【0085】

以上で、列変換回路1の動作の説明を終了する。

【0086】

なお、上述の動作において、列変換回路1は、任意のn個のM列入力データのライト動作開始から、該n個のM列入力データをN列変換して出力するリード動作開始までを一定期間に保つよう動作することが好ましい。ここで、nは、M列入力データn個分に相当するM×nビットが変換後の列数Nで割り切れるような値である。例えば、Mが16でNが5であれば、nは5となる。この場合、列変換回路1は、任意の5個のM列入力データのライト動作開始から、該5個のM列入力データをN列変換して出力するリード動作開始までを一定期間に保つよう動作することが好ましい。

【0087】

次に、本発明の第1の実施の形態の効果について述べる。

【0088】

本実施の形態としての列変換回路は、論理回路の増大を抑えながら、変換後の列数を容易に拡張可能である。

【0089】

その理由は、本実施の形態において、ライト側におけるライトアドレス生成部およびライトデータ制御部の構成および動作は、列変換モードの設定に依存することがないからである。どの列変換モードにおいても、ライトアドレス生成部は、ライトアドレスを同様に更新する。そして、ライトデータ制御部は、M列入力データを、M個のメモリにおいてライトアドレスが示す位置に格納していく。これにより、本実施の形態としての列変換回路は、列変換モードを拡張しても、ライト側に回路を増設する必要がない。

【0090】

また、リード側において、リードアドレス生成部およびデータ選択出力部の構成および動作は、列変換モードの設定に依存することがないからである。どの列変換モードにおいても、リードアドレス生成回路は、リードアドレス更新制御部の制御にしたがってN個ずつリードアドレスを更新する。また、どの列変換モードにおいても、データ選択出力部は、選択信号にしたがって、M個のメモリのうちN個においてリードアドレスの示す位置のデータを選択出力するからである。そして、本実施の形態としての列変換回路は、列変換モードを拡張する場合、拡張する列変換モードの列数に応じてリードアドレス更新制御部および選択信号生成部の構成を拡張すればよい。これらの各部の構成の拡張は、データセレクト回路の論理段数の増設等と比較して遙かに少ない増設量で済む。したがって、本実施の形態としての列変換回路は、列変換モードを拡張しても、リード側の回路増設量をより低減することができる。

【0091】

(第2の実施の形態)

次に、本発明の第2の実施の形態について、図面を参照して詳細に説明する。

【0092】

<構成>

まず、本発明の第2の実施の形態としての列変換回路10の構成を、図2に示す。図2において、列変換回路10は、16列入力データを、2列、4列、5列、6列、および7列のいずれかに変換可能な回路である。つまり、本発明において、Mに16を適用し、Nに2、4、5、6、7を適用したものである。

【0093】

図2において、列変換回路10は、本発明の列変換モード設定部の一実施形態として、列変換モード設定信号110が入力されるインタフェースを含む。また、列変換回路10は、本発明のメモリの一実施形態として、16個のRAM(0)〜RAM(15)を含む。また、列変換回路10は、本発明のライトアドレス生成部の一実施形態として、ライトアドレス生成回路130を含む。また、列変換回路10は、本発明のライトデータ制御部の一実施形態として、ライトデータ制御回路140を含む。また、列変換回路10は、本発明のリードアドレス生成部の一実施形態として、リードアドレス生成回路160を含む。また、列変換回路10は、本発明のリードアドレス更新制御部の一実施形態としてリードイネーブル生成回路170を含む。また、列変換回路10は、本発明の選択信号生成部の一実施形態として、リードデータセレクト生成回路150を含む。また、列変換回路10は、本発明のデータ選択出力部の一実施形態として、データセレクト・リタイミング回路180を含む。

【0094】

また、ライトアドレス生成回路130およびライトデータ制御回路140は、クロック信号(ライトCLK)に基づいて動作する。また、リードデータセレクト生成回路150と、リードアドレス生成回路160と、リードイネーブル生成回路170と、データセレクト・リタイミング回路180とは、クロック信号(リードCLK)に基づいて動作する。リードCLKは、ライトCLKに対して2倍の周波数で動作するクロック信号である。

【0095】

図2において、列変換モード設定信号110は、2列変換モード、4列変換モード、5列変換モード、6列変換モード、および7列変換モードのいずれかを表す。例えば、"000"は2列変換モードを表し、"001"は、4列変換モードを表し、"010"は、5列変換モードを表し、"011"は、6列変換モードを表し、"100"は、7列変換モードを表していてもよい。

【0096】

ライトデータ[15:0]は、16列入力データである。ライトデータ[15:0]は、先頭の16列から順次入力される。図3を用いて、ライトデータ[15:0]について説明する。図3において、i番目に入力されるライトデータ[15:0]は、“i−15”〜”i−0”で表されている。また、以降、”i−j”を、「i番目に入力されるライトデータ[15:0]のjビット目」ともいう。また、ライトデータ先頭パルスは、1番目のライトデータ[15:0]が入力されたことを示す信号である。また、ライトデータ[15:0]は、256個(合計4096ビット分)を、1ユニットとして入力されていく。

【0097】

各RAM(0)〜(15)は、1ビットのデータを256個格納可能なRAM(1bit×256W_RAM)によって構成される。図4に、RAM(0)〜(15)のデータ格納領域を示す。図4において、“i−j”は、RAM(j)におけるiビット目の格納領域を表している。つまり、図4に示す“RAM(j)”(ただし、jは0〜15)の記載の右に並ぶ“1−j”〜“256−j”までが、1つのRAM(j)のデータ格納領域を表している。このように、16個のRAM(0)〜(15)は、ライトデータ1ユニット(16列データ×256=4096ビット分)のデータを、格納可能である。

【0098】

ライトアドレス生成回路130は、0〜255までの値を繰り返すライトアドレス[7:0]を生成する。このライトアドレス[7:0]は、16個のRAM(j)において共通のデータ書き込み位置を示す。すなわち、ライトアドレス0〜255は、各RAM(j)の1〜256ビット目の位置を表している。ライトアドレス生成回路130は、ライトデータイネーブル信号が有効‘H’となる度に、ライトアドレス[7:0]を+1カウントアップする。

【0099】

ここで、ライトデータイネーブル信号について説明する。ライトデータイネーブル信号は、16列ライトデータ[15:0]をRAMに書き込むタイミングを示す信号である。ライトデータイネーブル信号は、列変換モードに応じて異なるタイミングで有効となる。これは、ライト動作およびリード動作が一定期間を保ちながら行われるようにするためである。ライトデータイネーブル信号については詳細を後述する。

【0100】

図2に戻り、ライトデータ制御回路140について説明する。ライトデータ制御回路140は、ライトデータ[15:0]をRAM(15)〜(0)に格納するタイミングを制御する。つまり、ライトデータ制御回路140は、ライトデータ[15:0]の各ビットを、ライトデータイネーブル信号に基づくタイミングで、RAM(15)〜(0)に出力する。このとき、ライトデータ[15:0]の各ビットは、RAM(15)〜(0)において、ライトアドレス[7:0]が示す位置に格納される。

【0101】

リードアドレス生成回路160は、16個の各RAM(j)について、リードアドレス[7:0]を生成する。1つのリードアドレス[7:0]は、1個のRAM(j)におけるデータ読み出し位置を示す。リードアドレス生成回路160は、後述のリードイネーブル生成回路170から出力されるRAM_EN[15:0]信号に基づいて、16本のリードアドレス[7:0]のうちN本を更新する。リードイネーブル生成回路170から出力されるRAM_EN[15:0]信号は、列変換モードに応じて異なるものである。したがって、リードアドレス生成回路160は、16本のリードアドレス[7:0]を、列変換モードに応じて異なるタイミングでそれぞれ更新していく。

【0102】

リードアドレス生成回路160の詳細を、図5に示す。リードアドレス生成回路160は、16個のカウンタRD_ADR(15)〜(0)を用いて、16本のリードアドレス[7:0]を生成する。これらのカウンタRD_ADR(15)〜(0)の初期値は、列変換モードにより異なるものが設定される。ここで、カウンタRD_ADR(15)〜(0)の初期値について説明する。

【0103】

まず、2列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表1に示す。

【0104】

【表1】

【0105】

次に、4列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表2に示す。

【0106】

【表2】

【0107】

次に、5列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表3に示す。

【0108】

【表3】

【0109】

次に、6列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表4に示す。

【0110】

【表4】

【0111】

次に、7列変換モードにおけるカウンタRD_ADR(15)〜RD_ADR(0)の初期設定値を、表5に示す。

【0112】

【表5】

【0113】

上記表1〜表5に示したように、カウンタRD_ADR(15)〜RD_ADR(0)は、リードデータ先頭パルスが有効時に、リードCLKの立ち上がりエッジで、各表に示した値に初期設定される。すなわち、これらの値が、各変換モードにおける16本のリードアドレスの初期値となる。そして、これらのカウンタRD_ADR(15)〜(0)は、リードCLKに基づく所定のタイミングで、対応する入力信号RAM_EN(15)〜RAM_EN(0)が‘H’であれば、+1のカウントアップを実行する。RAM_EN信号については、詳細を後述する。これにより、リードアドレス生成回路160は、16本のリードアドレスとして、それぞれの初期値から初めて、0〜255を繰り返す値を生成する。

【0114】

また、図5に示すように、リードアドレス生成回路160は、生成した16本のリードアドレスをRAM(15)〜(0)に対して出力する。これにより、RAM(15)〜(0)からは、それぞれのリードアドレスの示す位置に格納された1ビットずつの合計16ビットのRAM格納データ[15:0]が出力されることになる。

【0115】

次に、リードイネーブル生成回路170およびリードデータセレクト生成回路150の詳細を、図6を用いて説明する。

【0116】

図6において、リードデータセレクト生成回路150は、列変換モード毎に、リードデータセレクト信号を生成する回路を含む。ここで、リードデータセレクト信号は、本発明の選択信号の一実施形態である。リードデータセレクト信号は、M個のRAM(j)のうち選択対象となるN個を示す。具体的には、リードデータセレクト生成回路150は、2列変換リードデータセレクト生成回路150a、4列変換リードデータセレクト生成回路150b、5列変換リードデータセレクト生成回路150c、6列変換リードデータセレクト生成回路150d、7列変換リードデータセレクト生成回路150e(以降、総称してN列変換リードデータセレクト生成回路150ともいう)を有する。

【0117】

各N列変換リードデータセレクト生成回路150は、それぞれ対応する列変換モードに応じてリードデータセレクト信号RAM_SEL[15:0]を生成し、データセレクト・リタイミング回路180に出力する。このリードデータセレクト信号RAM_SEL[15:0]は、16個のRAM(15)〜RAM(0)から出力される16ビットのRAM格納データ[15:0]において、選択対象となるNビットのデータ位置を示しているとも言える。

【0118】

また、各N列変換リードデータセレクト生成回路150は、カウント値RDENCNTが変化する度にRAM_SEL[15:0]を更新する。

【0119】

ここで、カウント値RDENCNTについて説明する。カウント値RDENCNTは、リードCLKの4CLK毎にカウントアップされる信号である。ただし、列変換モード設定信号110に応じて、RDENCNTの最大カウント値には、異なる値が設定される。カウント値RDENCNTは、16個のRAM(j)のうちN個ずつが順次選択されていく際に、再び同一の組み合わせのN個のRAM(j)が選択されるまでの選択回数に基づき設定される。例えば、2列変換モードでは、RDENCNTが0のとき、RAM(15)、RAM(14)が選択され、RDENCNTが1のとき、RAM(13)、RAM(12)が選択されていくとすると、RDENCNTが7のとき、RAM(1)、RAM(0)が選択されることになる。そして、次に選択されるのは、再びRAM(15)、RAM(14)となるため、RDENCNTの最大カウント値は7である。また、同様に、4列変換モードでは、RDENCNTの最大カウント値は3である。また、同様に、5列変換モードでは、RDENCNTの最大カウント値は15である。また、同様に、6列変換モードでは、RDENCNTの最大カウント値は7である。また、同様に、7列変換モードでは、RDENCNTの最大カウント値は15である。

【0120】

次に、2列変換リードデータセレクト生成回路150aについて説明する。2列変換リードデータセレクト生成回路150aは、2列変換モードで0〜7を繰り返すカウンタRDENCNTを用いて動作する。2列変換リードデータセレクト生成回路150aが、RDENCNTの値に応じて出力する信号の一覧を、表6に示す。

【0121】

【表6】

【0122】

表6に示すように、例えば、2列変換リードデータセレクト生成回路150aは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)=‘H’およびRAM_SEL(14)=‘H’を出力する。

【0123】

また、例えば、2列変換リードデータセレクト生成回路150aは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(13)=‘H’およびRAM_SEL(12)=‘H’を出力する。

【0124】

このように、2列変換リードデータセレクト生成回路150aは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SEL[15:0]のうち2つずつを‘H’とするよう切り替えながら出力していく。

【0125】

次に、4列変換リードデータセレクト生成回路150bについて説明する。4列変換リードデータセレクト生成回路150bは、4列変換モードで0〜3を繰り返すカウンタRDENCNTを用いて動作する。4列変換リードデータセレクト生成回路150bが、RDENCNTの値に応じて出力する信号の一覧を、表7に示す。

【0126】

【表7】

【0127】

表7に示すように、例えば、4列変換リードデータセレクト生成回路150bは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)〜RAM_SEL(12)を有効‘H’にして出力する。

【0128】

また、例えば、4列変換リードデータセレクト生成回路150bは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(11)〜RAM_SEL(8)を有効‘H’にして出力する。

【0129】

このように、4列変換リードデータセレクト生成回路150bは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SEL[15:0]のうち4つずつを‘H’とするよう切り替えながら出力していく。

【0130】

次に、5列変換リードデータセレクト生成回路150cについて説明する。5列変換リードデータセレクト生成回路150cは、5列変換モードで0〜15を繰り返すカウンタRDENCNTを用いて動作する。5列変換リードデータセレクト生成回路150cが、RDENCNTの値に応じて出力する信号の一覧を、表8に示す。

【0131】

【表8】

【0132】

表8に示すように、例えば、5列変換リードデータセレクト生成回路150cは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)〜RAM_SEL(11)を有効‘H’にして出力する。

【0133】

また、例えば、5列変換リードデータセレクト生成回路150cは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(10)〜RAM_SEL(6)を有効‘H’にして出力する。

【0134】

このように、5列変換リードデータセレクト生成回路150cは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SELのうち5つずつを‘H’とするよう切り替えながら出力していく。

【0135】

次に、6列変換リードデータセレクト生成回路150dについて説明する。6列変換リードデータセレクト生成回路150dは、6列変換モードで0〜7を繰り返すカウンタRDENCNTを用いて動作する。6列変換リードデータセレクト生成回路150dが、RDENCNTの値に応じて出力する信号の一覧を、表9に示す。

【0136】

【表9】

【0137】

表9に示すように、例えば、6列変換リードデータセレクト生成回路150dは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)〜RAM_SEL(10)を有効‘H’にして出力する。

【0138】

また、例えば、6列変換リードデータセレクト生成回路150dは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(9)〜RAM_SEL(4)を有効‘H’にして出力する。

【0139】

このように、6列変換リードデータセレクト生成回路150dは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SEL[15:0]のうち6つずつを‘H’とするよう切り替えながら出力していく。

【0140】

次に、7列変換リードデータセレクト生成回路150eについて説明する。7列変換リードデータセレクト生成回路150eは、7列変換モードで0〜15を繰り返すカウンタRDENCNTを用いて動作する。7列変換リードデータセレクト生成回路150eが、RDENCNTの値に応じて出力する信号の一覧を、表10に示す。

【0141】

【表10】

【0142】

表10に示すように、例えば、7列変換リードデータセレクト生成回路150eは、RDENCNT=0ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(15)〜RAM_SEL(9)を有効‘H’にして出力する。

【0143】

また、例えば、7列変換リードデータセレクト生成回路150eは、RDENCNT=1ならば、データセレクト・リタイミング回路180に対して、RAM_SEL(8)〜RAM_SEL(2)を有効‘H’にして出力する。

【0144】

このように、7列変換リードデータセレクト生成回路150eは、RDENCNTが変化する度に、そのカウント値に応じて、RAM_SEL[15:0]のうち7つずつを‘H’とするよう切り替えながら出力していく。

【0145】

次に、リードイネーブル生成回路170について説明する。

【0146】

図6において、リードイネーブル生成回路170は、列変換モード毎に、リードイネーブル信号を生成する回路を含む。ここで、リードイネーブル信号は、16本のリードアドレスのうち、更新対象となるN本を示す。具体的には、リードイネーブル生成回路170は、2列変換リードイネーブル生成回路170aと、4列変換リードイネーブル生成回路170bと、5列変換リードイネーブル生成回路170cと、6列変換リードイネーブル生成回路170dと、7列変換リードイネーブル生成回路170eとを含む。これらの各回路を、以降、総称してN列変換リードイネーブル生成回路170ともいう。

【0147】

各N列変換リードイネーブル生成回路170は、16本のリードアドレスのうち更新対象となるN本を示すリードイネーブル信号RAM_EN[15:0]を、リードアドレス生成回路160に対して出力する。

【0148】